# Surface Potential-Based Polycrystalline-Silicon Thin-Film Transistors Compact Model by Nonequilibrium Approach

| 著者                | Ikeda H., Sano N.                     |  |  |

|-------------------|---------------------------------------|--|--|

| journal or        | IEEE transactions on electron devices |  |  |

| publication title |                                       |  |  |

| volume            | 60                                    |  |  |

| number            | 10                                    |  |  |

| page range        | 3417-3423                             |  |  |

| year              | 2013-10                               |  |  |

| 権利                | (C)2013 IEEE                          |  |  |

| URL               | http://hdl.handle.net/2241/120079     |  |  |

doi: 10.1109/TED.2013.2278274

**Surface Potential-Based Polycrystalline-Silicon Thin-Film** Transistors Compact Model by Non-Equilirium Approach

Hiroyuki Ikeda and Nobuyuki Sano

Institute of Applied Physics, University of Tsukuba,

1-1-1 Tennoudai, Tsukuba, Ibaraki 305-8573, Japan

We propose a surface potential-based polycrystalline-silicon thin-film transistors

(poly-Si TFTs) compact model taking a non-equilibrium state into account. A drain

current model considers grain boundary (GB) trap-related physical phenomena:

composite mobility of GB and intragrain, GB bias-induced mobility modulation,

transient behavior due to carrier capture and emission at GBs, pinch-off voltage

lowering, and GB trap-assisted leakage current. Besides, photo-induced current

behavior is also considered by introducing quasi-Fermi potential. A capacitance

model is derived from physically partitioned terminal charges and coupled to the drain

current behavior. This compact model allows us to accurately simulate static

characteristics of various types of poly-Si TFTs including temperature and luminance

dependence. Furthermore, this model succeeded to simulate frequency dependence of

circuit performance derived from the trap-related transient behavior, which was

verified by evaluating delay time in a 21-stage inverter chain. The good agreements

with the measurements of both static and dynamic characteristics confirm the validity

of the compact model.

Index Terms- Thin Film Transistors, Semiconductor device modeling, Circuit

simulation, SPICE

\*E-mail address: ikeda@hermes.esys.tsukuba.ac.jp

- 1 -

#### 1. Introduction

Polycrystalline-silicon thin-film transistors (Poly-Si TFTs) have been increasingly used for the pixel and driver circuits in flat-panel displays application such as smart phones, tablet PCs, and LCD/OLED TVs. High mobility and stability of poly-Si TFTs are preferable to reduce pixel circuits area for high resolution displays and to realize a "system-on-glass" which provides various functional circuits on the periphery of a display. Electrical property of poly-Si TFTs is influenced by poly-Si grain size  $(L_g)$  and grain boundary (GB) trap charge [1], [2]. Accordingly, poly-Si TFTs show various output characteristics depending on the fabrication process. Therefore, accurate compact model for circuit simulation is a key issue to design display circuits employing poly-Si TFTs. Thus far, several poly-Si TFTs compact models have been proposed for circuit simulations [3]-[5]. These are threshold voltage  $(V_{th})$ -based piecewise models in which model equations are provided for the individual operational regions of poly-Si TFTs. Connecting the individual equations requires artificial parameters, which sometimes causes a simulation error. Besides, the terminal capacitances in their models are not generated from the partitioned terminal charges but composed analytically. This is one of the reasons for breaking the charge conservation law in circuit simulation [6]. To improve the above drawbacks in the previous models, a surface potential-based poly-Si TFTs (defined hereinafter as SPT) model was proposed [7]. This model well reproduces various static output characteristics of poly-Si TFTs. However, it in insufficient to describe GB trap-related physical phenomena: GB bias-induced mobility modulation (GBMM) [8], transient current due to carrier capture and emission at GBs or time domain mobility modulation (TDMM) [9], pinch-off voltage lowering (PVL) [10]. In addition, it is

impossible to describe photo-induced current [11] peculiar to display circuits. Therefore, more physical and widely applicable poly-Si TFTs compact model has been required. The purpose of this work is to propose a new generation of SPT model to satisfy the above requirements.

#### 2. Modeling Framework

#### A. Assumptions

A poly-Si film is divided by grains and the GBs run through the film perpendicular to the surface. Free carriers in poly-Si are trapped at the GBs giving rise to the GB barrier potential. In a TFT structure, distribution of electrostatic potential becomes two-dimensional and complicated. Then, we introduce several assumptions to make a new SPT compact model simple.

- (A-1) A GB trap state density model is symmetric between acceptor- and donor-types.

- (A-2) Intragrain (IG) surface potential is calculated with spatially averaged GB trap charge density.

- (A-3) GB potential at poly-Si surface is calculated based on the IG surface potential.

- (A-4) Electric field is set to be zero at the back surface.

- (A-5) GB trap charge is unchanged along the channel.

- (A-6) Photo-injected carrier density is constant.

- (A-7) Quasi-Fermi potential of hole  $\phi_{fp}$  is evaluated in the flat-band condition.

- The (A-2) overestimates the GB trap charge and the (A-3) underestimates the channel free charge in subthreshold region. However, this is reasonable in on-region. We give priority to on-region in a compact model. The (A-5) was confirmed by device

simulation [10] to work approximately at the least in the linear region. The (A-7) is allowable because hole density does not affect the on current. In addition, the flat-band state is a unique point for us to evaluate the  $\phi_{fp}$ . The (A-1), (A-4), and (A-6) are trivial.

#### B. GB Trap Model

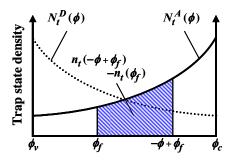

We define an acceptor- and a donor-type trap state density per unit GB area as

$$N_t^A(\phi) = N_{\text{te}} \exp[\gamma(\phi_c - \phi)] + N_{\text{to}}$$

(1)

and

$$N_t^D(\phi) = N_{\text{te}} \exp[\gamma(\phi - \phi_v)] + N_{\text{to}}$$

, (2)

where  $\phi_c$  and  $\phi_v$  refer to the conduction- and valence-band potentials,  $N_{\text{te}}$ ,  $N_{\text{to}}$ , and  $\gamma$  are the model parameters. When we consider GB trap charge as neutral in the flat-band condition ( $\phi$ =0), effective trap density per unit GB area  $N_t(\phi)$  is described as

$$\begin{split} N_{t}(\phi) &= [p_{t}(\phi) - p_{t}(0)] - [n_{t}(\phi) - n_{t}(0)] \\ &= q \int_{\phi_{f}}^{-\phi + \phi_{f}} N_{t}^{D}(\phi') d\phi' - q \int_{-\phi + \phi_{f}}^{\phi_{f}} N_{t}^{A}(\phi') d\phi' \end{split} , \tag{3}$$

where  $p_t$  and  $n_t$  refer to the hole and electron trap density, respectively (Fig. 1). Then, average GB trap charge density per unit volume  $q_t(\phi)$  is given [12] by

$$q_t(\phi) = \frac{2q}{L_g} \cdot N_t(\phi) \ . \tag{4}$$

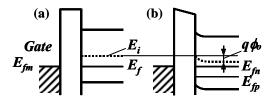

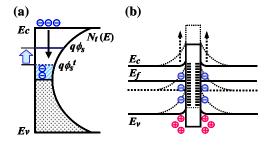

# C. Photo-induced effect

Illumination causes Fermi-level split and flat-band voltage ( $V_{\rm fb}$ ) shift. In n-channel (n-ch) TFTs, electron Fermi potential stays almost the same at the  $V_{\rm fb}$  because electron can commute between the  $n^+$  region and the channel region giving rise to an

increase in the  $V_{\rm fb}$  as illustrated in Fig. 2. Considering carrier balance, the  $V_{\rm fb}$  shift  $\phi_o$  and the  $\phi_{\rm fp}$  are given by

$$\phi_o = \frac{1}{\beta} \ln \left[ 1 + \exp(\beta \phi_f) \cdot \left( \frac{n_{\text{ph}}}{n_i} \right) \right], \qquad (5)$$

and

$$\phi_{\text{fp}} = \phi_o + \frac{1}{\beta} \ln \left[ 2 \sinh \beta \phi_f + \exp[\beta (\phi_o - \phi_f)] \right].$$

(6)

Here,  $n_{\rm ph}$  refers to the photo-injected carrier density and  $\beta$  stands for q/kT.

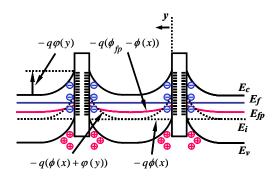

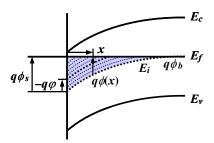

#### D. Surface and GB Potentials

Figure 3 defines physical quantities discussed in this section. Based on (4) and (6), Poisson equation for surface potential is written as

$$\frac{d^2\phi(x)}{dx^2} = \frac{2qn_i}{\varepsilon_s} \left[ \frac{1}{2} \left\{ \exp[\beta(\phi(x) - \phi_f)] - \exp[\beta(\phi_{fp} - \phi(x))] \right\} + \sinh\beta\phi_f \right] - \frac{1}{\varepsilon_s} q_t(\phi(x)) . \tag{7}$$

By integrating (7) from  $\phi_b$  to  $\phi_s$ , surface charge  $Q_s$  is obtained as

$$Q_{s}(\phi_{s},\phi_{b})^{2} = \frac{4q\varepsilon_{s}n_{i}}{\beta} \left\{ \frac{1}{2} \left( \exp[\beta(\phi_{s} - \phi_{f})] + \exp[\beta(\phi_{fp} - \phi_{s})] \right) - \frac{1}{2} \left( \exp[\beta(\phi_{b} - \phi_{f})] + \exp[\beta(\phi_{fp} - \phi_{b})] \right) + \beta(\phi_{s} - \phi_{b}) \sinh\beta\phi_{f} \right\} - 2\varepsilon_{s} \int_{\phi_{b}}^{\phi_{s}} q_{t}(\phi) d\phi$$

(8)

On the other hand, back surface potential  $\phi_b$  is related to  $\phi_s$  by

$$\phi_s = \phi_b - \frac{\rho_b}{2\varepsilon_s} \cdot t_{\rm Si}^2 , \qquad (9)$$

where,  $\rho_b$  and  $t_{Si}$  refer to the charge density at back surface and poly-Si film thickness.

Then,

$$C_{\text{ox}}(V_{\text{geff}} - \phi_s) = Q_s(\phi_s, \phi_b)$$

(10)

determines  $\phi_s$ . The  $V_{\text{geff}}$  is defined by  $V_{\text{gs}} - V_{\text{fb}}$ .

GB potential is formed by the deviation of charge density in the vicinity of the GB from that in the IG. Then, Poisson equation for the GB potential is written as

$$\frac{d^2\varphi(y)}{dy^2} = \frac{qn_i}{\varepsilon_s} \left[ \exp[\beta(\varphi(y) - \phi_f')] - \exp[\beta(\phi_{fp}' - \varphi(y))] + \exp(\beta\phi_{fp}') - \exp(-\beta\phi_f') \right]$$

(11)

with notation of  $\phi'_f \equiv \phi_f - \phi_s$ , and  $\phi'_{fp} \equiv \phi_{fp} - \phi_s$ . By integrating (11) from 0 to  $\phi_t$ , GB trap charge  $Q_t$  is obtained as

$$Q_{t}(\phi_{t})^{2} = \frac{8q\varepsilon_{s}n_{i}}{\beta} \left\{ \exp[\beta(\phi_{t} - \phi_{f}')] + \exp[\beta(\phi_{fp}' - \phi_{t})] \right\} + \beta\phi_{t}[\exp(\beta\phi_{fp}') - \exp(-\beta\phi_{f}')] - [\exp(-\beta\phi_{f}') + \exp(\beta\phi_{fp}')] \right\}.$$

(12)

Then,

$$Q_t(\phi_t) = qN_t(\phi_s + \phi_t)$$

(13)

determines  $\phi_t$ .

#### E. Drain Current

Drain current equation in on-region follows the surface potential-based modeling scheme [13], [14]. Then, the drain current is expressed as

$$I_{\text{on}} = -\frac{W}{L} \mu_u \left\{ \int_{\phi_{s0}}^{\phi_{sL}} Q_n(\phi) d\phi - \frac{1}{\beta} [Q_n(L) - Q_n(0)] \right\} , \qquad (14)$$

where  $Q_n$  refers to the free charge density per unit surface area and subscript '0' and 'L' denote source and drain edges, respectively. The  $Q_n$  is obtained by subtracting depleted body charge  $Q_b$  from the surface charge  $Q_s$  given by (8). The  $Q_b$  is defined as

$$Q_{b}(\phi_{s},\phi_{b})^{2} = \frac{4q\varepsilon_{s}n_{i}}{\beta} \left\{ \frac{1}{2} \left( \exp[\beta(\phi_{fp} - \phi_{s})] - \exp[\beta(\phi_{fp} - \phi_{b})] \right) + \beta(\phi_{s} - \phi_{b}) \sinh\beta\phi_{f} \right\}$$

$$-2\varepsilon_{s} \int_{\phi_{b}}^{\phi_{s}} q_{t}(\phi) d\phi$$

$$(15)$$

Then, total drain current is given by

$$I_{\rm ds} = (I_{\rm on} + I_{\rm off}) \cdot f_{\rm hc} , \qquad (16)$$

where  $I_{\text{off}}$  is the off-current discussed later,  $f_{\text{hc}}$  is the hot carrier factor [15].

# F. Terminal Charges and Capacitances

According to the surface potential-based modeling scheme, gate charge  $Q_g$  is expressed as

$$Q_g = \frac{W^2 \mu_u}{I_{ds}} \left\{ \int_{\phi_{s0}}^{\phi_{sL}} Q_n(\phi)^2 d\phi - \frac{1}{2\beta} [Q_n(L)^2 - Q_n(0)^2] \right\}. \tag{17}$$

In general, terminal charge is the charge responding the terminal voltage. Therefore, when we define source charge  $Q_s$ , the  $Q_s$  does not respond to the drain voltage, that is,

$$Q_s(V_{gs}, V_{ds}) = Q_s(V_{gs}, V_{ds} = 0) = -\frac{1}{2}Q_g(V_{gs}, V_{ds} = 0)$$

(18)

The  $Q_s$  is physically partitioned, and consequently, drain charge is given by

$$Q_d(V_{gs}, V_{ds}) = -Q_g(V_{gs}, V_{ds}) - Q_s(V_{gs}, V_{ds}) .$$

(19)

On the other hand,  $Q_g$  is invariant under a simultaneous voltage shift with arbitrary value at the individual terminals. This principle leads to

$$\frac{\partial Q_g}{\partial V_g} + \frac{\partial Q_g}{\partial V_d} + \frac{\partial Q_g}{\partial V_s} = 0 . (20)$$

This gives a relationship between the gate-to-source and gate-to-drain capacitances  $C_{\rm gs}$  and  $C_{\rm gd}$ , that is,

$$C_{\rm gs} = \frac{\partial Q_{\rm g}}{\partial V_{\sigma}} - C_{\rm gd} . \tag{21}$$

Based on (17) and (21),  $C_{\rm gs}$  and  $C_{\rm gd}$  are obtained.

#### 3. GB trap-induced physical phenomena

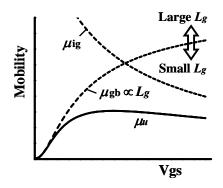

#### A. Composite Mobility

Poly-Si film is considered as a series resistance composed of IGs and GBs. IG mobility decreases with the vertical gate electric field. Since various factors affect the carrier transport, the IG mobility is semi-empirically modeled [16] as

$$\mu_{ig} = \frac{\mu_{igo}}{\left[1 + \left(\frac{E_{s.eff}}{E_o}\right)\right]^{g_n}},$$

(22)

where  $Es_{\text{eff}}$  refers to the effective gate electric field and  $\mu_{\text{igo}}$ ,  $g_n$ ,  $E_o$  are the model parameters. GB carrier transport is controlled by thermionic emission at GBs. The GB mobility is modeled [1], [2] as

$$\mu_{\rm gb} = \mu_{\rm gbo} L_g \exp(\beta \phi_t) , \qquad (23)$$

where  $\mu_{\rm gbo}$  is the model parameter. Based on (22) and (23), unified composite mobility  $\mu_u$  is given by

$$\mu_u = (\mu_{ig}^{-1} + \mu_{gb}^{-1})^{-1}$$

(24)

When  $L_g$  is small or gate electric field is weak, low GB mobility dominates the total mobility as illustrated in Fig. 4.

# B. GBMM effect

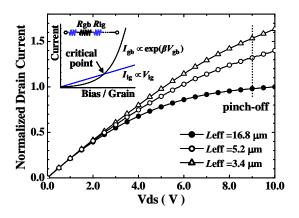

Output characteristics of poly-Si TFTs deviate from the scaling law of long channel MOSFETs. Figure 5 shows the output characteristics of TFTs with  $L_g$  = 86 nm and effective channel length  $L_{\rm eff}$  = 3.4, 5.2, and 16.8  $\mu$ m at  $V_{\rm gs}$  = 10.5 V which are normalized at  $V_{\rm ds}$  = 0.2 V. Pinch-off voltages of the TFTs are almost the same. However, drain current anomalously increases with  $V_{\rm ds}$  as the  $L_{\rm eff}$  decreases. This is

caused by the conductance or mobility modulation of poly-Si film. Linear current-voltage (*I-V*) characteristic of IG is expressed as

$$j_{\rm ig} = q n_{\rm ig} \cdot \mu_{\rm ig} \frac{V_{\rm ig}}{L_g} \equiv g_{\rm ig} \cdot V_{\rm ig}$$

(25)

and nonlinear I-V characteristic of GB is expressed as

$$j_{gb} = 2qn_{ig} \cdot v_{th} \exp(\beta \phi_t) \sinh\left[\frac{\beta (V_{gb} - V_{\delta})}{2}\right]$$

$$\equiv g_{gb} \frac{2}{\beta} \sinh\left[\frac{\beta (V_{gb} - V_{\delta})}{2}\right]$$

(26)

where  $n_{ig}$ ,  $v_{th}$ , and  $V_{\delta}$  refer to the IG carrier density, thermal velocity, and the parameter of the voltage drop at GBs. The  $g_{ig}$  and  $g_{gb}$  are the IG and GB conductance. While  $V_{ds}$  is small,  $V_{gb}$  increases with  $V_{ds}$  and low GB conductance dominates the drain current and keeps on increasing. Beyond the balancing point between the IG and GB conductance,  $V_{gb}$  saturates and the IG conductance controls the drain current instead and the anomalous current increase ceases as illustrated in the inset of Fig. 5. This behavior is described by the following equation which is obtained by equating (25) with (26).

$$\frac{\beta}{2} \cdot \frac{g_{ig}}{g_{gb}} \cdot \frac{L_g}{L_{eff}} \cdot \left[ V_{ds} - \left( \frac{L_{eff}}{L_g} + 1 \right) \cdot V_{gb} \right] = \sinh \left[ \frac{\beta (V_{gb} - V_{\delta})}{2} \right]. \tag{27}$$

This equation indicates that  $g_{ig}/g_{gb}$  and  $L_g/L_{eff}$  are the parameters to influence the  $V_{gb}$ . In other words, this is a scaling equation for the GBMM effect.

#### C. TDMM effect

TDMM effect is a transient phenomenon derived from carrier capture and emission at GBs, which is observed when switching on and off a poly-Si TFT. Poly-Si

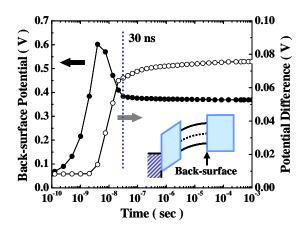

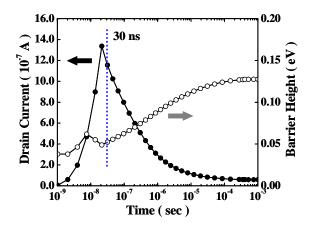

film contains average trap density on the order of  $10^{18}$  cm<sup>-3</sup> [17], which corresponds to life time of 1 ns by rough estimation. Accordingly, when switching on, remaining holes in the IGs rapidly recombine with electrons and the IGs reach almost stationary state in 1 ns or so. Then, electron capture follows at the GBs accompanying the increase in the GB barrier height (Fig. 6). This increase in the barrier height causes the GB mobility modulation. The above statement was verified by 2-D device simulation [18]. The device parameters are:  $L = 6.0 \mu m$ ,  $L_g = 300 \text{ nm}$ ,  $T_{si} = 50 \text{ nm}$ , and gate oxide film thickness  $T_{ox} = 145 \text{ nm}$ . The GB trap density model is given as follows.

$$N_t(E) = N_{ta} \exp[(E - E_c)/W]$$

(28)

The trap parameters are:  $N_{\rm ta} = 5.0 \times 10^{21}~{\rm cm}^{-3} {\rm eV}^{-1}$ ,  $W = 0.025~{\rm eV}$ . The capture cross section of electron and hole are  $\sigma_n = 1.0 \times 10^{-15}$  and  $\sigma_p = 1.0 \times 10^{-13}~{\rm cm}^2$ , respectively. The gate voltage  $V_{\rm gs}$  was switched on from 0.0 to 3.3 V in 20 ns. Figure 7 shows the transient behavior of the surface and back-surface potential, while Fig. 8 shows that of the GB barrier height and drain current. In Fig. 7, the back-surface potential fluctuates in the rising time and reaches almost stationary state in 30 ns, right after the bias rise. In Fig. 8, the drain current begins decreasing simultaneously with the increase in the barrier height at 20 ns. Switching-off transient behavior is similarly verified. As a result, we have only to consider carrier capture and emission at GBs to model TDMM effect.

In the case of mono-energetic trap state, rate equation for electron capture is described [19], [20] by

$$\left. \frac{dn_t}{dt} \right|_{\text{cap.}} = c_n \cdot n \cdot (N_t - n_t), \qquad (29)$$

where  $c_n$  stands for  $\sigma_n v_{\text{th}}$ , and life time  $\tau$  is given by  $(c_n \cdot n)^{-1}$ . By using time step  $\Delta t$ , (29) can be rewritten as

$$n_t(t + \Delta t) - n_t(t) = [N_t - n_t(t)] \cdot [1 - \exp(-c_n n \Delta t)]$$

(30)

We expand (30) to continuously distributed trap states at channel surface (Fig. 9) with assumption of simple superposition. Then, we obtain the time variation of trap charge density as

$$\Delta \langle Q_t \rangle = -\frac{2q^2}{L_g} \int [N_t(\varphi, x) - n_t(\varphi, x, t)] \cdot \{1 - \exp[-c_n n_i \Delta t \exp(\beta \phi(x))]\} d\varphi dx$$

$$= -\frac{2q^2}{L_g} \int_{-\phi}^{0} d\varphi \int_{\phi_b}^{\phi_s} \frac{d\phi}{E(\phi)} [N_t(\varphi, \phi) - n_t(\varphi, \phi, t)] \cdot \{1 - \exp[-c_n n_i \Delta t \exp(\beta \phi)]\} \tag{31}$$

Here, the second factor in the integrand substantially behaves as  $\Delta t/\tau \approx 1$  with  $\phi$  larger than a critical value  $\phi_c$ . In addition, we can focus on the surface region because the trap state density is exponentially high near the conduction-band edge and potential increases near the surface. Then, (31) is simplified as

$$\Delta \langle Q_t \rangle \approx -\frac{4q^2}{L_g} \frac{(\phi_s - \phi_c)}{E_s} \frac{\Delta t}{\tau} \int_{-\phi_s}^{0} [N_t(\varphi) - n_t(\varphi, t)] d\varphi . \tag{32}$$

The  $E_s$  refers to the surface electric field. This integral means the subtraction of the transient trap density from the stationary trap density. Then, (32) is rewritten as

$$\Delta \langle Q_t \rangle = \frac{4(\phi_s - \phi_s^t)}{L_g \cdot E_s} \frac{\Delta t}{\tau} [Q_t(\phi_s) - Q_t(\phi_s^t)] , \qquad (33)$$

where  $\phi_s^t$  refers to the transient surface potential or trap filling level in the GB trap and  $\phi_c$  in (32) was replaced by  $\phi_s^t$ . On the other hand, the trap term in (8) can be rewritten by using (4) as follows.

$$\frac{4}{L_g} \int_{\phi_b}^{\phi_s} Q_t(\phi) d\phi = 2 \int_{\phi_b}^{\phi_s} q_t(\phi) d\phi = 2 \int_{\phi_b}^{\phi_s} q_t(\phi) d\phi$$

$$= 2 \int_{T_{S_i}}^{0} q_t(x) \frac{d\phi}{dx} dx \approx 2E_{\text{eff}} \int_{0}^{T_{S_i}} q_t(x) dx = E_s \cdot \langle Q_t \rangle$$

(34)

Here,  $\langle Q_t \rangle$  refers to the GB trap charge density per surface area. In transient state, only  $\phi_s^t$  varies, and consequently, (34) becomes

$$\frac{4}{L_g} Q_t(\phi_s^t) \cdot \Delta \phi_s^t = E_s \cdot \Delta \langle Q_t \rangle . \tag{35}$$

Finally, we obtain the relationship between the time variation of  $\phi^t_s$  and that of  $\langle Q_t \rangle$  in the case of switching-on as

$$\Delta \phi_s^t = (\phi_s - \phi_s^t) \cdot \left[ \frac{Q_t(\phi_s) - Q_t(\phi_s^t)}{Q_t(\phi_s^t)} \right] \cdot \frac{\Delta t}{\tau} . \tag{36}$$

When switching-off, the relationship is similarly obtained as

$$\Delta \phi_s^t = -(\phi_s^t - \phi_s) \cdot \left[ \frac{Q_t(\phi_s^t) - Q_t(\phi_s)}{Q_t(\phi_s^t)} \right] \cdot \frac{\Delta t}{\tau} . \tag{37}$$

These relationships describe the trap-related transient behavior.

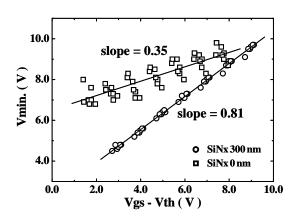

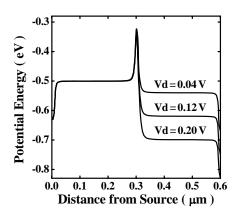

#### D. PVL effect

GB traps are terminated through hydrogenation process such as diffusion from silicon nitride (SiN<sub>x</sub>) film deposited by the plasma-enhanced chemical vapor deposition (PE CVD) method. When the hydrogenation efficiency is low, huge amount of traps remain at the GBs, and then, PVL phenomenon appears. Gate voltage dependence of the observed pinch-off voltage becomes smaller than that of the ideal pinch-off voltage  $V_{gs}$ – $V_{th}$  keeping linear relationship between them as shown in Fig. 10. There are two possible mechanisms for the PVL phenomenon. One is GB current saturation. When the GB trap density is high, most of the bias is applied to GBs. Since GB current is proportional to the difference in the carrier density across the GBs, the current does not increase further as long as the source-side barrier height remains the same as shown in Fig. 11. The other is "early depletion" at the drain edge. When the IG conductance at the drain edge decreases to become comparable with the GB conductance, current also saturates even when the IG region is not depleted. This is

because current saturation is caused by the increase in the voltage drop near the drain edge. In any case, pinch-off appears earlier than in the ideal case. Considering the complicated physics in the PVL phenomenon, we adopt a semi-empirical model for the PVL by employing the relationship in Fig. 10 expressed as

$$V_{\text{p.observed}} = \alpha_{\text{pvl}} \cdot V_{\text{p.ideal}}$$

(38)

#### E. Off Current

In the off-state of poly-Si TFTs, drain current consists of three components: generation, gate-induced drain leakage (GIDL) [21], and diffusion current. Since poly-Si film contains huge number of traps, many carriers are generated via the traps in the depletion region of the drain junction. The generation current model is described by

$$I_{\text{gen}} = I_{\text{geno}} W \cdot N_t(0) \sqrt{V_{\text{ds}}} \exp(-\beta \phi_{\text{gen}}) , \qquad (39)$$

where  $I_{\text{geno}}$  is the model parameter,  $N_t(0)$  and  $\phi_{\text{gen}}$  refer to the trap density at the mid gap and activation potential for the generation. The GIDL is enhanced through tunneling via traps in poly-Si TFTs [22]. Then, the GIDL current becomes temperature dependent because the trap-assisted process is thermally activated. The trap-assisted GIDL current model is described by

$$I_{\text{gidl}} = W \cdot A_{\text{gidl}} \exp(-\beta \phi_{\text{gidl}}) (V_{\text{dg}} - V_i) \exp\left(\frac{-B_{\text{gidl}}}{V_{\text{dg}} - V_i}\right) \cdot \left[1 - \exp\left(-\frac{\beta V_{\text{ds}}}{C_{\text{gidl}}}\right)\right], \quad (40)$$

where  $A_{\rm gidl}$ ,  $B_{\rm gidl}$ ,  $C_{\rm gidl}$  are the model parameters and  $\phi_{\rm gidl}$  is the activation potential. The diffusion current becomes dominant when poly-Si TFTs are illuminated. Since electron is minority carrier in  $V_{\rm gs} < V_{\rm fb}$ , photo-generated electron diffuses to the drain region of n-ch TFTs. The diffusion current model is described by

$$I_{\rm di} = I_{\rm dio}(W \cdot t_{\rm Si}) N \cdot \left[ 1 - \exp\left(-\frac{\beta V_{\rm ds}}{\alpha_{di}}\right) \right] , \qquad (41)$$

where  $I_{\rm dio}$ ,  $\alpha_{\rm di}$  are the model parameters and N is the average carrier density per surface area.

#### 4. Comparison with Measurements

#### A. Sample Preparation

Poly-Si TFTs with bottom-gate structure were fabricated on glass substrates. At first, the gate electrodes of molybdenum were defined. Then, silicon oxide (SiO<sub>2</sub>) gate-insulator and amorphous silicon (a-Si) films were deposited successively by the PE CVD method, followed by the excimer laser annealing (ELA) crystallization process. Thickness of the gate-insulator was an alternative of 65 or 145 nm and that of a-Si was 40 nm. Poly-Si grain size was controlled by changing the ELA condition. Poly-Si islands were defined after the ion implantation for  $n^+$  and LDD regions with dosage of  $7.5 \times 10^{19}$  and  $1.8 \times 10^{17}$  cm<sup>-3</sup>, respectively. A composite inter-layer of SiO<sub>2</sub> and SiN<sub>x</sub> films were deposited successively by the PE CVD method. Before the metallization, hydrogenation of poly-Si film was performed by 2-hour annealing at  $400^{\circ}$ C in N<sub>2</sub> atmosphere, capped with the inter-layer SiN<sub>x</sub> film.

#### B. Static Characteristics

Here, we verify the validity of the static characteristics of the model. All the evaluated samples are *n*-ch device without LDD structure and have drawn channel

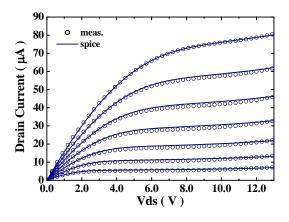

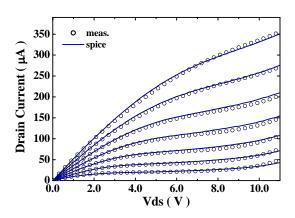

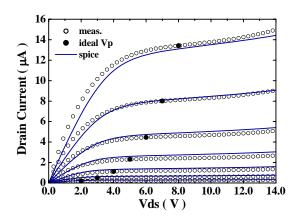

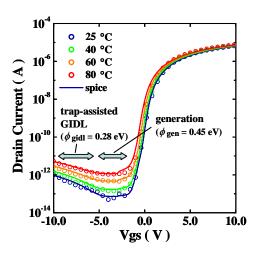

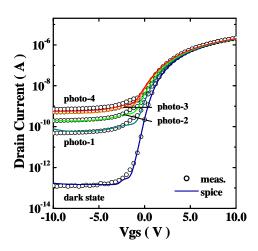

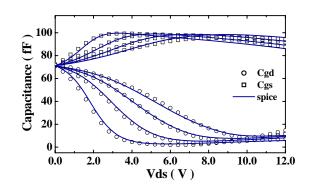

length (L) of 20  $\mu$ m in common. Figures 12 and 13 show output characteristics of type-1 and -2 poly-Si TFTs with same dimension of  $T_{\rm ox} = 65$  nm,  $L_{\rm g} = 86$  nm, and respective channel length L = 18 and 6  $\mu$ m. In Fig. 12, drain current is well reproduced by the model. In Fig. 13, drain current keeps on increasing beyond the pinch-off point and current value is higher than that estimated in Fig. 12 by a simple scaling raw at any  $V_{\rm ds}$ . The GBMM effect is well reproduced by the SPT model. Figure 14 shows output characteristics of a type-3 TFT with  $T_{\rm ox} = 145$  nm,  $L_g = 260$  nm, and  $L = 18 \, \mu \rm m$ . This sample has no inter-layer SiN<sub>x</sub> film, then, the poly-Si film is not hydrogenated. Closed circles in the output characteristics show the ideal pinch-off voltage evaluated by the  $V_{\rm th}$  value. The ideal pinch-off voltages seem higher for the output characteristics. The PVL effect is also well reproduced here. Model parameters for output characteristics of type-1 to -3 are listed in Table-I. Figure 15 shows transfer characteristics of a TFT with  $T_{ox} = 65$  nm,  $L_g = 120$  nm, and L = 8  $\mu m$  at four different temperatures. Drain current increases with temperature as a whole. In the off-region, the plateau and the  $V_{\rm gs}$  dependent portions respectively correspond to the generation and trap-assisted GIDL currents. Activation energy of the trap-assisted GIDL is smaller than that of the generation. Figure 16 shows transfer characteristics of a TFT with  $T_{\rm ox} = 145$  nm,  $L_g = 300$  nm, and  $L = 18 \, \mu \rm m$  with five illumination levels including a dark state. Drain current in off- and sbthreshold-regions increases with the luminance, while on-current remains almost the same. This is a big difference from the temperature dependence in Fig. 15. Finally, Fig. 17 shows  $V_{\rm ds}$  dependence of the terminal capacitance  $C_{\rm gs}$  and  $C_{\rm gd}$  of the TFT in Fig. 12. As shown in Figs. 12-17, the SPT model can simulate static characteristics of poly-Si TFTs with good accuracy.

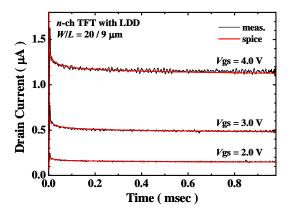

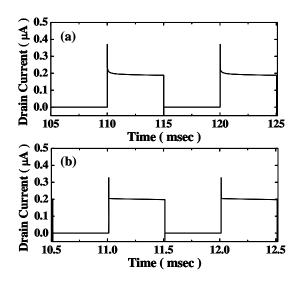

#### C. Dynamic Characteristics

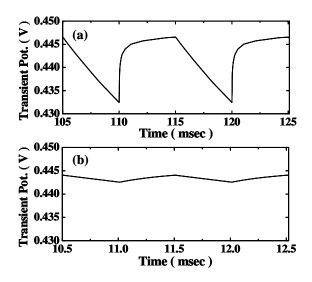

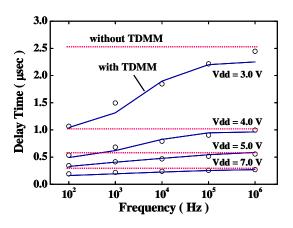

Dynamic characteristics significantly influence the transient analysis of circuit simulations. Most essential issue in poly-Si TFTs is the TDMM effect. Figure 18 shows measured and simulated transient currents by single switching-on of an n-ch TFT with LDD structure and  $T_{\rm ox}=145$  nm,  $L_{\rm g}=300$  nm, and L=9  $\mu \rm m$ . The drain current decays from high initial current value in millisecond time range. Such current decay can cause frequency dependence of circuit performance. Figure 19 shows simulated transient currents by sequential switching at 100 Hz and 1 kHz. Higher peak and larger decay current is observed in the case of 100 Hz driving. This frequency dependence is derived from the transient behavior of the GB traps. Figure 20 shows simulated transient potential  $\phi^t_s$  corresponding to the current in Fig. 19. In 100 Hz driving,  $\phi^t_s$  decreases sufficiently in the off-time and rapidly increases at switching on. This causes higher peak and larger decay current. In 1 kHz driving, on the other hand,  $\phi^t_s$  cannot decrease much in the off-time, and consequently,  $\phi^t_s$  stays within high value range. This causes lower peak and smaller decay current.

Following the previous discussion, a 21-stage inverter chain was prepared to verify the model performance by evaluating the frequency dependence of the delay time. The device parameters are  $T_{\rm ox}=145$  nm,  $L_g=300$  nm, and L=9  $\mu$ m for both n-and p-ch TFTs of the inverter. N-ch TFTs have channel width W=20  $\mu$ m, overlap capacitance  $C_{\rm gso}=C_{\rm gdo}=3.13$  fF, and LDD structures on both source and drain sides with resistance R-LDD=3.8 k $\Omega$ . P-ch TFTs have W=30  $\mu$ m and  $C_{\rm gso}=C_{\rm gdo}=4.35$  fF. Input voltage ( $V_{\rm in}$ ) of the inverter chain was set to be same as the high DC voltage ( $V_{\rm dd}$ ). Figure 21 shows measured and simulated frequency dependence of the delay time. The measured delay time increases with the frequency as a whole. We find that

this frequency dependence is well reproduced only by incorporating the TDMM effect. Without the TDMM effect, frequency dependence does not appear.

#### 6. Conclusions

A new generation of SPT model has been developed considering the effect of carrier capture and emission, photo-induced carrier injection, and PVL phenomenon on the carrier transport. This model has realized simulation of GB trap-related frequency dependence of circuit performance and that of photo-induced current behavior. This model is the most suitable to simulate poly-Si TFTs circuits in display device with good accuracy.

#### [List of References]

- [1] J. Y. W. Seto, "The electrical properties of polycrystalline silicon films," *J. Appl. Phys.*, vol. 46, pp. 5247-5254, Dec. 1975.

- [2] G. Baccarani, B. Riccò, and G. Spadini, "Transport properties of polycrystalline silicon films," *J. Appl. Phys.*, vol. 49, pp. 5565-5570, Nov. 1978.

- [3] C. C. Li, H. Ikeda, T. Inoue, and P. K. Ko, "A physical poly-silicon thin film transistors model for circuit simulations," in *IEDM Tech. Dig.* (Washington DC), Dec. 1993, pp. 497-500.

- [4] M. S. Shur, H. C. Slade, M. D. Jacunski, A. A. Owusu, and T. Ytterdal, "Spice models for amorphous silicon and polysilicon thin film transistors," *J. Electrochem. Soc.*, vol. 144, pp. 2833-2839, Aug. 1997.

- [5] G.-Y. Yang, S.-H. Hur, and C.-H. Han, "A physical-based analytical turn-on model of polysilicon thin-film transistors for circuit simulation," *IEEE Trans*. *Electron Devices*, vol. 46, no. 1, pp. 165-172, Jan. 1999.

- [6] R. Gharabagi and M. A. El-Nokali, "A charge-based model for short-channel MOS transistor capacitances," *IEEE Trans. Electron Devices*, vol. 37, no. 4, pp. 1064-1073, Apr. 1990.

- [7] H. Ikeda, "Surface potential based poly-Si thin-film transistor model for spice," in *IEDM Tech. Dig.* (San Francisco, CA), Dec. 2006, pp. 183-186.

- [8] H. Ikeda, "Analysis of grain boundary induced nonlinear output characteristics in polycrystalline-silicon thin-film transistors," *Jpn. J. Appl. Phys.*, vol. 45, no. 3A, pp. 1540-1547, Mar. 2006.

- [9] H. Ikeda, "Characterization of switching transient behaviors in polycrystalline-silicon thin-film transistors," *Jpn. J. Appl. Phys.*, vol. 43, no. 2, pp. 477-484, Feb. 2004.

- [10] H. Ikeda and N. Sano, "Pinch-off voltage lowering in polycrystalline silicon thin-film transistors," *Jpn. J. Appl. Phys.*, vol. 50, 014301, Jan. 2011.

- [11] H. Ikeda, "Photon-induced current of polycrystalline-silicon thin-film transistors," *Appl. Phys. Lett.*, vol. 78, no. 21, pp. 3259-3261, May 2001.

- [12] H. Ikeda, "Evaluation of trap states in polycrystalline-silicon thin-film transistors by mobility and capacitance measurements," *J. Appl. Phys.*, vol. 91, no. 7, pp. 4637-4645, Apr. 2002.

- [13] J. R. Brews, "A charge-sheet model of the MOSFET," *Solid-State Electron.*, vol. 21, pp. 345-355, Jun. 1978.

- [14] M. M.-Mattausch, U. Feldmann, A. Rahm, M. Bollu, and D. Savignac, "Unified complete MOSFET model for analysis of digital and analog circuits," *IEEE Trans. Comput.-Aided Des.*, vol. 15, no. 1, pp. 1-7, Jan. 1996.

- [15] W. Liu, X. Jin, X. Xi, J. Chen, M.-C. Jeng, Z. Liu, Y. Cheng, K. Chen, M. Chan, K. Hui, J. Huang, R. Tu, P. K. Ko, and C. Hu, "BSIM3v3.3 MOSFET Model User's Manual," University of California, Berkeley, CA 94720, 2005.

- [16] S. R. Banna, P. C. H. Chan, M. Chan, and P. K. Ko, "A physically based compact device model for fully depleted and nearly fully depleted SOI MOSFET," *IEEE Trans. Electron Devices*, vol. 43, no. 11, pp. 1914-1923, Nov. 1996.

- [17] G. Fortunato and P. Migliorato, "Determination of gap state density in polycrystalline silicon by field-effect conductance," *Appl. Phys. Lett.*, vol. 49, no. 16, pp. 1025-1027, Oct. 1986.

- [18] ATLAS software, Silvaco International, 4701 Patrick Henry Drive, Bldg. 2, Santa Clara, CA 95054, U.S.A.

- [19] W. Shockley and W. T. Read, "Statistics of the recombinations of holes and electrons," *Phys. Rev.*, vol. 87, no. 5, pp. 835-842, Sep. 1952.

- [20] R. N. Hall, "Electron-hole recombination in germanium," *Phys. Rev.*, vol. 87, pp. 387-387, 1952.

- [21] J. Chen, T. Y. Chan, I. C. Chen, P. K. Ko, and C. Hu, "Subbreakdown drain leakage current in MOSFET," *IEEE Electron Device Lett.*, vol. 8, no. 11, pp. 515-517, Nov. 1987.

- [22] J. G. Fossum, A. O.-Conde, H. Shichijo, and S. K. Banerjee, "Anomalous leakage current in LPCVD polysilicon MOSFET's," *IEEE Trans. Electron Devices*, vol. 32, no. 9, pp. 1878-1884, Sep. 1985.

#### [List of figure captions]

- Fig. 1. A diagram for the symmetric GB trap state density model. Effective acceptortype trap density is defined by  $n_t(-\phi + \phi_f) - n_t(\phi_f)$ .

- Fig. 2. A band diagram at MOS surface. (a) Dark (equilibrium) state.  $E_f$  coincides with  $E_{fm}$ . (b) Illuminated state. Electron Fermi level  $E_{fn}$  coincides with  $E_{fm}$ . Surface band bends upward due to the split in  $E_f$ .

- Fig. 3. A band diagram of a poly-Si TFT channel region. Carrier trapping at GBs causes barrier potential. GB potential is measured from the base surface potential. Neumann boundary condition is applied at the back surface.

- Fig. 4.  $V_{\rm gs}$  dependence of composite mobility  $\mu_u$  composed of IG and GB mobility.

- Fig. 5. Drain current normalized at  $V_{\rm ds} = 0.2$  V. Current increases anomalously with  $V_{\rm ds}$  as  $L_{\rm eff}$  decreases despite almost the same pinch-off voltage. In this bias region, GB conductance is dominant. Beyond the critical point, IG conductance becomes dominant instead (inset).

- Fig. 6. Origin of the TDMM effect in switching on. (a) Electron capture process at GBs. (b) Electron capture and increase in GB barrier height.

- Fig. 7. Device simulation result of switch-on time evolution of the IG back-surface potential and potential difference between the both surfaces.

- Fig. 8. Device simulation result of switch-on transient drain current and the GB barrier height at the surface.

- Fig. 9. Definition of continuously distributed trap states in the channel surface.

- Fig. 10. Relationship between observed pinch-off voltage and ideal one. For convenience, we evaluated the observed pinch-off by gds-minimizing point  $V_{\min}$ . Thickness of SiN<sub>x</sub> film controls hydrogenation efficiency in poly-Si.

- Fig. 11. Device simulation result in the case of high GB trap density. Most of the bias is applied to the GB.

- Fig. 12. Output characteristics of a poly-Si TFT with  $T_{ox} = 65$  nm,  $L_g = 86$  nm, and  $L = 18 \mu m$ .

- Fig. 13. Output characteristics of a poly-Si TFT with  $T_{ox} = 65$  nm,  $L_g = 86$  nm, and  $L = 6 \mu m$ .

- Fig. 14. Output characteristics of a poly-Si TFT with  $T_{\rm ox}$  = 145 nm,  $L_g$  = 260 nm, and L = 18  $\mu$ m. Poly-Si film is not hydrogenated. Closed circle refers to the ideal pinch-off voltage.

- Fig. 15. Transfer characteristics of a poly-Si TFT with  $T_{ox}$  = 65 nm,  $L_g$  = 120 nm, and L = 8  $\mu$ m at four different temperatures.

- Fig. 16. Transfer characteristics of a poly-Si TFT with  $T_{ox} = 145$  nm,  $L_g = 300$  nm, and  $L = 18 \mu m$  with five illumination levels. Photo-1 to -4 correspond to the  $n_{ph}$ s of  $1.40 \times 10^{13}$ ,  $4.30 \times 10^{13}$ ,  $1.10 \times 10^{14}$ , and  $1.42 \times 10^{14}$  cm<sup>-3</sup>.

- Fig. 17.  $V_{\rm ds}$  dependence of terminal capacitance  $C_{\rm gs}$  and  $C_{\rm gd}$  of a poly-Si TFT with  $T_{\rm ox}$  = 65 nm,  $L_{\rm g}$  = 86 nm, and L = 18  $\mu$ m.

- Fig. 18. Measured and simulated transient current by single switching of an *n*-ch TFT with LDD structure with  $V_{ds} = 0.2 \text{ V}$ .

- Fig. 19. Simulated transient current by sequential switching of an *n*-ch TFT with LDD structure ( $V_{\rm ds} = 0.1 \text{ V}$ ). (a) 100 Hz switching case. (b) 1 kHz switching case.

- Fig. 20. Simulated transient potential  $\phi_s^t$  by sequential switching of an *n*-ch TFT with LDD structure ( $V_{\rm ds} = 0.1 \text{ V}$ ). (a) 100 Hz switching case. (b) 1 kHz switching case.

- Fig. 21. Measured and simulated frequency dependence of delay time in a 21-stage inverter chain. Open circle refers to the measured data.

# [Table captions and tables]

Table I. Model parameters for output characteristics of poly-Si TFTs in Figs. 12-14.

| Parameter                                                     | Type-1                 | Type-2                 | Type-3                |

|---------------------------------------------------------------|------------------------|------------------------|-----------------------|

| $N_{\mathrm{te}}$ ( cm <sup>-2</sup> eV <sup>-1</sup> )       | 1.20×10 <sup>13</sup>  | 1.32×10 <sup>13</sup>  | 3.72×10 <sup>13</sup> |

| $N_{ m to}$ ( cm <sup>-2</sup> eV <sup>-1</sup> )             | $-4.00 \times 10^{11}$ | $-4.00 \times 10^{11}$ | 1.60×10 <sup>12</sup> |

| γ (eV <sup>-1</sup> )                                         | 3.57                   | 3.70                   | 2.15                  |

| $V_{ m fb}$ (V)                                               | -3.0                   | -3.2                   | -11.7                 |

| $\mu_{\rm igo} \ (\ {\rm cm}^2 {\rm V}^{-1} {\rm s}^{-1} \ )$ | 1.10×10 <sup>3</sup>   | 1.20×10 <sup>3</sup>   | 1.00×10 <sup>3</sup>  |

| $g_n$ (1)                                                     | 0.56                   | 0.40                   | 0.10                  |

| $E_o$ ( V cm <sup>-1</sup> )                                  | 1.7×10 <sup>4</sup>    | 1.1×10 <sup>4</sup>    | 1.0×10 <sup>4</sup>   |

| $\mu_{\rm gbo}$ ( cm V <sup>-1</sup> s <sup>-1</sup> )        | 1.18×10 <sup>7</sup>   | 1.06×10 <sup>7</sup>   | 1.10×10 <sup>8</sup>  |

| α <sub>gbmm</sub> (1)                                         | 0.09                   | 0.14                   | 0.01                  |

| α <sub>pvl</sub> (1)                                          | 1.00                   | 1.00                   | 0.443                 |

Fig. 1. H. Ikeda and N. Sano

Fig. 2. H. Ikeda and N. Sano

Fig. 3. H. Ikeda and N. Sano

Fig. 4. H. Ikeda and N. Sano

Fig. 5. H. Ikeda and N. Sano

Fig. 6. H. Ikeda and N. Sano

Fig. 7. H. Ikeda and N. Sano

Fig. 8. H. Ikeda and N. Sano

Fig. 9. H. Ikeda and N. Sano

Fig. 10. H. Ikeda and N. Sano

Fig. 11. H. Ikeda and N. Sano

Fig. 12. H. Ikeda and N. Sano

Fig. 13. H. Ikeda and N. Sano

Fig. 14. H. Ikeda and N. Sano

Fig. 15. H. Ikeda and N. Sano

Fig. 16. H. Ikeda and N. Sano

Fig. 17. H. Ikeda and N. Sano

Fig. 18. H. Ikeda and N. Sano

Fig. 19. H. Ikeda and N. Sano

Fig. 20. H. Ikeda and N. Sano

Fig. 21. H. Ikeda and N. Sano