# GPU DEVICES FOR SAFETY-CRITICAL SYSTEMS: A SURVEY

Jon Perez-Cerrolaza<sup>†</sup>, Jaume Abella<sup>‡</sup>, Leonidas Kosmidis<sup>‡</sup>, Alejandro J. Calderon<sup>†</sup>, Francisco J. Cazorla<sup>‡</sup>, Jose Luis Flores<sup>†</sup>

<sup>†</sup>Ikerlan Technology Research Centre, Basque Research and Technology Alliance (BRTA), Spain <sup>‡</sup>Barcelona Supercomputing Center (BSC), Spain

### **ABSTRACT**

Graphics Processing Unit (GPU) devices and their associated software programming languages and frameworks can deliver the computing performance required to facilitate the development of next-generation high-performance safety-critical systems such as autonomous driving systems. However, the integration of complex, parallel and computationally demanding software functions with different safety-criticality levels on GPU devices with shared hardware resources contributes to several safety certification challenges. This survey categorizes and provides an overview of research contributions that address GPU devices' random hardware failures, systematic failures and independence of execution.

# 1 Introduction

High-performance computing devices such as GPUs and multi-core devices are increasingly considered for the development of safety-critical systems in multiple domains such as transportation (e.g., automotive [15, 203, 141, 13], railway [20], avionics [21, 27], space [105, 196, 9]) and industrial machinery (e.g., wind turbines, industrial control robots) [153, 11]. This trend answers the need for higher computational performance and higher on-chip integration of functions required to facilitate the development of next-generation safety-critical systems. For example, the automotive domain Autonomous Driving (AD) and Advanced Driver-Assistance Systems (ADAS) require unprecedented levels of computing performance to process computationally-demanding algorithms such as computer vision perception and Machine Learning (ML) algorithms [121, 141]. Moreover, there is also a cross-domain trend towards the integration of different safety criticality functions (a.k.a., mixed-criticality) in a reduced number of high-performance computing devices reducing hardware's solution size, weight, and power costs and potentially increasing the overall system reliability by a reduction of components, cables and connectors [153, 11].

A GPU, or graphics processing unit, is a computing device specialized in image processing acceleration and output display. However, as the provided high computing capacity enables the acceleration of computationally demanding algorithms and ML-based software, their usage and device specialization has evolved in the last decades from initial home applications (e.g., GPU for gaming) to new application domains such as safety-critical autonomous systems [196, 140]. Several technical challenges have been addressed as part of this evolution, such as reliability improvements and safety compliance [4, 15, 13, 140]. Also, during the last decade, the innovative nature of the semiconductor sector has developed GPU devices with steadily shrinking technologies down to the current 7 nm while continuously increasing the overall computing capacity.

Safety is defined as the "absence of catastrophic consequences on the u ser(s) and the environment" [22]. Safety-critical systems are programmable electronics systems whose failure can lead to catastrophic consequences, like environmental damage or human casualties (e.g., autonomous driving system accident). Thus, in several domains, strict certification processes must be followed for the development and certification of such sy stems. This implies high development costs where, as a rule of thumb, "the higher the safety integrity level, the higher the cost of safety certification" [11]. For example, the highest criticality industrial systems [92] must ensure an extremely low failure probability of up to  $10^{-9}$  per hour of operation (approximately 114.155 years). This imposes strict technical requirements to mitigate to such low levels the probability of failure due to random hardware errors (e.g., memory

bit flip) and systematic errors (e.g., human, process and tool errors), and to achieve independence of execution among integrated functions. In this context, the development and certification of safety-critical systems based on Commercial Off-The-Shelf (COTS) GPU devices designed to maximize the average performance is a challenge [153, 11, 15, 141, 13].

This work provides a survey of GPU devices for the development of safety-critical systems with a categorization of selected research contributions that address GPU devices' random hardware failures (§4), systematic failures (§5), and independence of execution (§6). And Table 1 summarizes the threats, safety measures and techniques described in the corresponding Sections (§4, §5, §6). This survey targets both researchers and safety systems developers, providing a comprehensive view the state-of-the-art required to carry out a diligent development of safety-critical systems, whenever applicable safety standards have none or limited consideration of GPU devices [61, 153]. Regarding safety standards, both IEC 61508 [92] and ISO 26262 [95] are considered the reference functional safety standards in this survey.

The remainder of this survey is organized as follows. Section 2 describes basic concepts and terminology. Section 3 describes GPU device-specific features and challenges, along with the classification criteria and metrics used in this survey. Based on this, Sections 4, 5 and 6 categorize and provide an overview of research contributions that address GPU devices' random hardware failures (§4), systematic failures (§5), and independence of execution (§6). Section 7 summarizes the similarities and particular characteristics of other domains that do not consider IEC 61508 as a reference safety standard (avionics and space). Section 8 discusses links to related research topics and future trends to be considered in the development of GPU device-based safety-critical systems. Finally, Section 9 describes the overall conclusion and future research directions.

# 2 Background

This section summarizes basic concepts and terms used within the survey, such as GPU terminology, safety certification standards and fundamental safety technical requirements. The survey uses the NVIDIA CUDA terminology for GPUs, the dependable computing terminology defined by Avižienis et al. [22] and the functional safety terminology defined by IEC 61508-4 and ISO 26262-1 safety standards [92, 95]. We also integrate the terminology of several research fields described by referenced survey and review publications (e.g., Fault Injection (FI) techniques [28]).

# 2.1 Graphics Processing Unit (GPU)

A GPU device is a high-performance many-core processor with associated industry-standard software programming languages and Application Programming Interfaces (APIs) [141, 196]. Using NVIDIA CUDA terminology for convenience within the survey (see Table 2 for OpenCL terminology used by other semiconductor companies such as AMD), the GPU main processing units are the Streaming Multiprocessors (SMs). Each SM comprises several scalar cores and other resources such as registers, shared memories and schedulers. A scalar core is a pipelined Arithmetic Logic Unit (ALU) capable of executing integer and floating-point operations. The SMs execution management is performed by the host, composed of one or more CPU core(s).

Functions executed on the SMs are known as *kernels*. Before launching a kernel to the SMs, the user prepares the data to be processed using host memory, reserves the corresponding amount of GPU memory and triggers a copy operation from host to GPU memory. Once the SM kernel execution finishes the result is copied back to the host memory from the GPU memory. In *embedded GPU* devices, since global memory is shared between CPU cores and SMs, this may be done more efficiently by defining a single region of shared memory to avoid the memory copy operations. For that purpose, it is possible to use OpenCL Shared Virtual Memory (SVM) and CUDA Unified Virtual Memory (UVM) features, yet taking into consideration the need to manage memory consistency.

When launching a kernel to the SM, the user specifies a *grid* configuration with the number of *blocks* and threads per block to be executed. At the hardware level, the threads of a block are partitioned into *warps*, groups of 32 lockstep threads. The warp scheduler(s) of each SM fetch, decode and issue instructions to the execution pipelines. During the execution, resources like shared memory and registers are shared by the warps being scheduled.

GPU software programming is commonly based on standardized APIs such as Compute Unified Device Architecture (CUDA), Open Computing Language (OpenCL), Open Graphics Library (OpenGL) variants, Vulkan, Open Multi-Processing (OpenMP) [56] and Open Accelerators (OpenACC). Some of them are primarily built for graphics, such as OpenGL variants, while others for general-purpose computations (e.g., CUDA, OpenCL, OpenMP, OpenACC). Some of them support both graphics and compute, such as Vulkan. From those, OpenGL SC (Safety-Critical), is the only one of these APIs designed to comply with safety-critical systems' requirements [27].

Table 1: Categorization of the related works

|                           | Example Threats                                                                                                                                                                                                                                                                                                                                                                  | Safety Measures and Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Sect |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Random<br>HW<br>failures  | PVT variability [143] Device aging [143] Transient faults (soft errors) [143] Permanent faults [143] Shared resources error propagation [195, 138, 140, 170, 51]                                                                                                                                                                                                                 | · Application-agnostic:  - Detection with redundancy without diversity [163, 6, 191, 178, 199, 57, 73, 138, 99, 164, 34, 170, 120, 140, 77, 127, 139] and with diversity [13, 14, 8, 12]  - Detection and/or correction with coding (e.g., ECC) and checkers [57, 120, 169, 139, 108, 124, 125, 140, 132]  - Recovery with re-execution or checkpoints [71, 175, 180, 135, 115, 124]  - Mitigation with shielding and reconfiguration [153, 127, 91, 193]  - Application-dependent:  - Detection and fault-tolerance algorithmic approaches [35, 138, 169, 170, 168, 195, 140, 49, 50, 110, 139, 156, 102, 202, 80, 204, 58, 76]  - Fault-tolerance based on intrinsic application and/or input data characteristics [63, 78, 159, 158] | §4   |

| Systematic failures       | · Systematic faults (e.g., human, tools, process) · Software programming languages and frameworks not-compliant with safety standards [183, 15, 92, 95]                                                                                                                                                                                                                          | · Application-agnostic:     - Software: Safety standard compliant programming languages and frameworks (e.g., OpenGL SC [23, 27]), 'safe language subsets' (e.g., Brook auto [183]) and tool qualification [184, 27]     - Device hardware: Safety standard ASIC development requirements [92, 3] and development techniques for mass-produced devices (e.g., [103, 149])                                                                                                                                                                                                                                                                                                                                                               | §5   |

| Indepen.<br>of            | Temporal interference and spatial interference                                                                                                                                                                                                                                                                                                                                   | Temporal independence and spatial independence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | §6   |

| Execution · Temporal      | · Kernel execution time variability [141, 142,                                                                                                                                                                                                                                                                                                                                   | · Application-agnostic:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | §6.1 |

| Independence              | <ul> <li>Host application(s) interactions with driver stack [141, 142, 16, 17, 59]</li> <li>Memory contention [141, 142, 46, 96, 100]</li> <li>Shared resources (e.g., shared memory)</li> <li>Lack of information [46, 142, 16, 14], documentation inconsistencies [200, 144, 14] and partial understandability of temporal behavior [142, 100, 40, 144, 96, 18, 39]</li> </ul> | - Device hardware architecture and component-specific (e.g., memory [70, 43, 68, 101, 109, 104], cache [69, 87, 154, 96, 97, 194])  - Exclusive access policies [96, 97, 194]  - Software virtualization [84, 114, 141, 41, 174, 112]  - WCET analysis [48, 29, 30, 85, 33, 16, 90, 89, 88]  - Execution time variability reduction and management [18, 41, 42, 67, 82, 84, 88, 142, 144, 200, 101, 70, 68, 109, 43, 141, 147, 47, 81, 24]  - Temporal diagnostics [25, 153]  - Application-dependent [176, 62]                                                                                                                                                                                                                         |      |

| · Spatial<br>Independence | Shared resources [100, 46] Cache/Memory coherency [153] Parallel execution of kernels [200, 136] Software memory transfer mechanisms [46] Software frameworks and middlewares [96, 46]                                                                                                                                                                                           | Application-agnostic:     Device hardware architecture, components [155, 128, 141] and memory coherency support     Exclusive access policies [112, 111]     Software virtualization [84, 114, 141, 174, 112]     Memory transfer and memory coherency support     Spatial diagnostics [153]                                                                                                                                                                                                                                                                                                                                                                                                                                            | §6.2 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                  | Safety measures and techniques that can be used, adapted or extended from multi-core devices and FPGAs [127, 153, 143, 31, 75]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

Table 2: Summary of GPU terminology equivalence (CUDA, OpenCL)

| Terminology | Terms          |                    |         |            |           |           |

|-------------|----------------|--------------------|---------|------------|-----------|-----------|

| CUDA        | streaming      | scalar core        | grid    | block      | thread    | warp      |

|             | multiprocessor |                    |         |            |           |           |

| OpenCL      | compute unit   | processing element | NDRange | work-group | work-item | wavefront |

# 2.2 Safety Certification Standards

IEC 61508 [92] generic safety standard is considered as a reference by several industrial and ground transportation domains such as industrial machinery (ISO 13849 [94]), robotics (ISO 10218 [93]), automotive (ISO 26262 [95]) and railway (EN 5012X [60]). For further details concerning domain-specific safety standards and certification processes, refer to Martinez et al. [122]. However, among all these safety standards, there is considerable variability in terminology, definitions and requirements. For example, in IEC 61508, the Safety Integrity Level (SIL) is defined with a discrete level range where number one is the lowest (SIL1) and four is the highest (SIL4), while in ISO 26262, the level is defined by the Automotive Safety Integrity Level (ASIL) with a range from 'A' the lowest (ASIL-A) to 'D' the highest (ASIL-D). Therefore, the survey considers IEC 61508 as a reference safety standard and takes into technical consideration previously listed industrial and ground transportation domains. Besides, the automotive

domain is a common target application for GPU devices and provides guidelines for applying the safety standard to semiconductors (ISO 26262-11). Thus, both IEC 61508 and ISO 26262 are considered reference safety standards in the survey. Nonetheless, several additional domain-specific safety standards do not consider IEC 61508 as a reference standard. Section 7 summarizes the specific characteristics of these domains (e.g., space).

Both reference safety standards require the adoption of *safety measures* (ISO 26262-1 §3.141) to avoid, detect, control and/or mitigate *random hardware failures* ("failure that can occur unpredictably during the lifetime of a hardware element and that follows a distribution probability" [95]) and *systematic failures* ("failure related in a deterministic way to a certain cause, that can only be eliminated by a change of the design or of the manufacturing process, operational procedures, documentation or other relevant factors" [95]). And safety standards already propose some example safety measures as recommended or not recommended for a given SIL (e.g., IEC 61508-3 Table A.2).

Finally, IEC 61508-4 (§3.2.11) classifies software off-line tools as class TI if it does not contribute to the executable software code (e.g., document editor), T2 if it "supports the test or verification of the design or executable code" (e.g., test tool) and T3 if it "generates outputs which can directly or indirectly contribute to the executable code" [92] (e.g., software compiler). And IEC 61508-3 (§7.4.4) describes tool qualification requirements for T2 and T3 classes. Besides, ISO 26262-8 (§11.4.5/6) defines the Tool Confidence Level (TCL) classification (TCL1-3), where TCL3 is assigned if a tool error impact is severe and the error detection coverage is low (e.g., software compiler).

#### 2.3 Fundamental Safety Technical Requirements

The development of IEC 61508 and/or ISO 26262 compliant safety-critical systems with devices that have on-chip redundancy (e.g., GPU devices) requires addressing at least the following fundamental safety technical requirements already defined for multi-core devices [153]:

- Reliability of an item (e.g., transistor, cache, device) is defined as the "ability to perform as required, without failure, for a given time interval, under given conditions" [2]. And the reliability measure is defined as the "probability of performing as required for the time interval (t1, t2), under given conditions" [2], which is quantified as the failure rate ( $\lambda$ ) of a device, the number of failures per  $10^9$  device operation hours, measured in Failures In Time (FIT).

- Diagnostic Coverage (DC) stands for "the fraction of dangerous failures detected by automatic on-line diagnostic tests" [92]. It is expressed as coverage percentage and classified in ranges: low  $(60\% \le DC < 90\%)$ , medium  $(90\% \le DC < 99\%)$  and high  $(DC \ge 99\%)$  [92].

- *Temporal independence* implies that "one element shall not cause another element to function incorrectly by taking too high a share of the available processor execution time, or by blocking execution of the other element by locking a shared resource of some kind" [92]. The reference standards [92, 95] recommend techniques such as *temporal predictability* (e.g., design time scheduling), temporal diagnostics and Worst-Case Execution Time (WCET) analysis.

- Spatial independence implies that "data used by one element shall not be changed by another element" [92]. For instance, exclusive access is a widely used technique to support spatial independence with shared resources [111, 112].

The survey uses both reliability definitions provided by the standard IEC 60050 [2] to support the reconciliation of the definition variability among research contributions that propose techniques to improve the reliability of items and improve reliability measures (e.g., [22, 153, 28]). However, neither IEC 61508 nor ISO 26262 define the term reliability, and internal references are scarce and mostly related to failure rate estimation. Nevertheless, as these standards state, the failure rate can be reduced (reliability increase) using, for example, control and mitigation techniques such as redundancy and fault tolerance (IEC 61508-4 §3.4.6, §3.6.3). Hence, Section 4 describes reliability research contributions that propose techniques to control and mitigate random hardware failures.

In addition to this, the Probability of dangerous Failure per Hour (PFH) is the average system failure frequency. The PFH depends, among other parameters, on both the device reliability ( $\lambda$ ) and the DC [92]. The higher the reliability and/or the DC, the lower the PFH. The automotive domain defines different probability calculation formulas and methods (e.g., Probabilistic Metric for Random Hardware Failures (PMHF) in ISO 26262-5) that are also based at least on both parameters.

Finally, the integration of several software elements on a single device must ensure the *independence of execution*, so "that elements will not adversely interfere with each other's execution behavior such that a dangerous failure would occur" [92] (IEC 61508-3 Annex F). This requirement is equivalent to *Freedom from Interference (FFI)* [95] (ISO 26262-11 §5.4.2). And described *spatial independence* and *temporal independence* techniques are fundamental to achieve such freedom from interference and independence of execution (see Section 6).

# 3 GPU Device

The development of GPU-based safety-critical embedded systems requires a careful analysis and understanding of the underlying GPU device architecture with associated software programming languages and frameworks, taking into consideration the provided built-in safety measures (e.g., diagnostics, fault tolerance techniques), along with the execution independence risks that need to be mitigated (e.g., temporal interference). From a research perspective, there is a considerable research fragmentation linked to the different nature of threats and technical challenges that must be tackled. This section provides a common technical foundation based on which the following random hardware failures (§4), systematic failures (§5) and independence of execution (§6) Sections can categorize the research contributions. This Section provides an introduction (§3.1), describes a GPU taxonomy and metrics (§3.2), and summarizes GPU-specific features and challenges for both the device hardware (§3.3) and associated software programming languages and frameworks (§3.4).

#### 3.1 Introduction

There is a cross-domain research interest in the potential applicability of GPU devices for the development of nextgeneration safety systems (e.g., automotive [176, 114, 170, 119, 182, 38, 79, 26, 171, 197, 15], railway [21, 20], avionics [27, 192, 126, 21], space [36, 105, 106, 107, 74, 116, 162, 196, 36, 9]). Both GPU and multi-core devices could potentially meet the computational and mixed-criticality integration requirements. However, while multi-cores ease programmability and flexibility, GPU devices and their associated programming languages and frameworks provide higher computing capacity [105] for applications characterized by high computational performance and parallelizable software algorithms, either for the safety function itself or for other integrated applications (mixedcriticality). Examples of computationally-demanding applications are graphics processing [192], computer vision perception [182], ML [118, 54], mathematics calculations and domain-specific computing-intensive functions (e.g., space [105, 162], automotive [79], railway [20]). Furthermore, GPU devices can provide very high ratios of computational performance per power consumption (W) [105], key in domains such as space where available power is limited [105, 162]. However, the most common functional safety software applications are sequential [79, 104]. Therefore, the effort required to parallelize and accelerate the execution of software portions versus the achievable gain in execution time (Ahmdahl's law [83]) and computing resource utilization [79], limits discrete GPU devices' competitiveness with respect to multi-core devices concurrent execution of sequential applications. Nonetheless, both discrete and embedded GPU devices with one or multiple CPU cores, can potentially combine both advantages and enable the integration of safety sequential applications (in CPU cores) and parallelizable software algorithms (in SMs) [12]. For example, Renesas R-Car H3 [5] and NVIDIA Xavier [4] devices include ARM cores suitable for the implementation of safety functions (e.g., lockstep mode) [13]. In this context, the selection of which functions/algorithms (or portions of them) are assigned to SMs or CPU cores becomes relevant, because some algorithms are amenable to SMs and other algorithms are not (e.g., space domain analysis [105, 106, 107]).

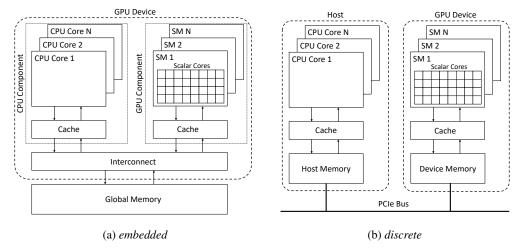

The integration of safety measures to manage random hardware failures (see Section 4) with a reasonable cost and shared memory management are key technical challenges that can limit the applicability of GPU devices for the development of safety-critical systems. Concerning shared memory management, in highly parallel computing architectures, the temporal and energy cost of arithmetic and logical operations can become negligible, compared with the cost of data transfers and memory accesses. For example, global memory operations can require two orders of magnitude more time than arithmetic and local memory operations [54]. So, device designers do not only need to optimize the parallel computational performance of the SMs, but especially the shared memory architecture (e.g., memory, cache(s)) and the interconnect components that perform data transfers. As shown in Figure 1a, in order to optimize maximum average performance, both the CPU cores and SMs share a common memory interconnect that arbitrates data access to a shared memory architecture composed with L2/L3 caches and shared memory components. In addition to this, in order to improve the maximum usage of resources and maximum computational performance of the GPU, several intermediate logic units (e.g., instruction dispatch units, Load Store Unit (LSU)) and hardware schedulers are required (e.g., warp schedulers).

## 3.2 Taxonomy and Metrics

This section describes the criteria used within the survey to classify GPU devices, safety software allocation scenarios, and GPU device reliability evaluation metrics.

## 3.2.1 GPU Device Types

Currently available *GPU devices* (or *devices* for short) go beyond the basic definition of graphics processing unit, and can be classified according to different taxonomies. This survey defines in Table 3 a GPU classification taxonomy

Figure 1: Generic block-diagram architecture of hard embedded and discrete GPUs

that combines several sources [105, 141, 153, 200]. We use this taxonomy to classify and describe GPU devices and features including the computing specialization (*graphics*, *computing*), device type (*discrete*, *integrated | embedded*), implementation type (*hard*, *soft*) and safety compliance (*generic*, *safety*). For example, Xavier [4] is a *hard embedded safety computing GPU* device: a specialized ASIC device (*hard*), where the GPU component (SMs) is integrated in the same physical die with CPU cores (*embedded*), with a dedicated lock-step CPU compliant with ISO 26262 and IEC 61508 safety standards (*safety*), and natively supporting general-purpose parallel computing APIs (*computing*).

We use the term *GPU component* (or GPU for short) to refer to the SM(s) and associated hardware logic/blocks/registers/components, such as the shared cache, required to execute kernel(s) in the SM(s). If the GPU is implemented as an embedded element, see Figure 1 (left), the *GPU component* will be part of the Multi-Processor Systems-on-a-Chip (MPSoC) device along with the *CPU component* and other on-SoC components like I/O controllers. Instead, if the GPU is implemented as a stand-alone device, see Figure 1 (right), the terms *GPU component* and *GPU device* are the same. In the former case, *embedded GPU*, the integration can either be hard (ASIC), soft (e.g., FPGA) or combinations thereof (e.g., MPSoC with integrated FPGA). Finally, High-Level Synthesis (HLS) [131, 86] based soft-GPU solutions are considered outside the scope of the survey as they do not require the implementation of SM(s).

| Feature               | Type         | Description                                                                                                                                                       |  |

|-----------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Computing             | Graphics     | GPUs capable of using only graphics APIs (e.g., OpenGL ES/SC).                                                                                                    |  |

| Specialization        | Computing    | GPUs natively supporting general-purpose parallel computing (e.g., CUDA, OpenCL, OpenMP, OpenACC, Vulkan) and graphics APIs.                                      |  |

| Device Type           | Discrete     | GPU implemented as a different physical module, connected to a host system through a connection interface such as PCIe. Usually, it contains its own DRAM memory. |  |

|                       | Integrated / | GPU implemented in the same physical module with CPU cores, i.e. die as a part of a Systems-on-a-                                                                 |  |

|                       | Embedded     | Chip (SoC). Usually shares the same main memory with other computing components.                                                                                  |  |

| Implementatio<br>Type | n Hard       | GPUs provided as specialized ASIC or as part of a multi-core SoC / MPSoC device.                                                                                  |  |

|                       | Soft         | GPUs provided as solutions to be integrated in FPGAs either as soft-core IP or HLS of a higher-level programming framework such as OpenCL.                        |  |

| Safety<br>Compliance  | Generic      | General-purpose GPU (GPGPU) optimized for maximum average performance.                                                                                            |  |

|                       | Safety       | GPU designed to comply with one or several safety standards.                                                                                                      |  |

Table 3: GPU classification taxonomy

## 3.2.2 GPU Safety Software Allocation Scenarios

A safety function is fail-safe if the safety function or the diagnostics can lead the system to a safe state if required (e.g., train stop). By contrast, it is fail-operational if, even in the presence of a failure, the developer must guarantee degraded or full system operation (e.g., autonomous driving). We describe techniques that safety engineers can use to design fail-safe or fail-operational safety-critical systems based on the defined architectural and fault tolerance strategies. For example, the fail-operational architecture for autonomous vehicles described by Yoshida [203] uses redundant and diverse hardware platforms that combine multi-core devices and a GPU device.

Regarding the allocation of safety software function(s) to a GPU device, we identify nine possible basic combinations as shown in Table 4:

- The combination where no safety application is executed in the GPU(s) and the CPU cores, is considered 'outside the scope' of the survey (safety-critical systems). See for example other generic surveys such as CPU-GPU heterogeneous computing techniques [130].

- The combinations where the GPU(s) execute one or more safety function(s) but not the CPU cores, are considered 'not feasible' because the CPU cores manage the execution of GPU(s). Thus, CPU cores should execute at least a portion of these safety function(s).

- The combinations where CPU cores execute one or more safety function(s) but not the GPU(s), are considered scenarios already covered by the survey on multi-core devices [153]. In this case, the GPU(s) are non-safety-related computing accelerator components.

- The combinations where CPU cores and GPU(s) execute one or more safety function(s) are considered within the technical scope of the survey.

## 3.2.3 GPU Device Reliability Evaluation Metrics

GPU device reliability evaluations are commonly performed by methods such as Fault Injection (FI) and vulnerability factor metric estimations [187, 170, 46, 51]. FI methods deliberately introduce errors to analyze the reliability and susceptibility of the device to such errors. Table 5 classifies FI methods and tools used to evaluate the reliability and resilience of GPU devices and components, using the FI taxonomy defined by Benso et al. [28]: *execution/simulation* and *software/hardware*. And the basic effects of a FI action are: *no effect* (an error is not induced, or implemented safety measures correct it), *functional interruption* (e.g., crash) and Silent Data Corruption (SDC) (the induced error corrupts data or the GPU internal state) [139].

Execution and software-based FI is performed with tools that inject software errors in a software application running on a device (e.g., SASSIFI [78]). Besides, simulation and software-based FI is executed with specialized GPU soft models where software errors are injected on a simulated/emulated device (e.g., FlexGrip [165]). Within the scope of the survey, the focus of these software-based FI techniques is not to inject software application errors (e.g., software bugs) but the (expected) software errors generated by random hardware errors. These FI techniques can be used to obtain probability-based metric estimates such as the Architectural Vulnerability Factor (AVF) and Program Vulnerability Factor (PVF). The AVF metric provides a probabilistic quantification of a transient hardware error leading to a computation error [187, 3] (ISO 26262-11 §4.6.1.8). That is, the fraction of transient hardware errors that lead to a computation error. Besides, the PVF quantifies software program(s) vulnerability metrics when executed on a given device. Moreover, additional metric specializations can also be defined, restricting the PVF analysis to particular portions of an algorithm [170, 46]. Finally, execution and hardware-based FI campaigns provide empirical failure rate measurements using specialized laboratories (e.g., neutron beam), extreme operating conditions (e.g., high temperature) or in-field testing in harsh environments.

The ISO 26262 defines two hardware architectural metrics, Single-Point Fault Metric (SPFM) and Latent Fault Metric (LFM), which measure the robustness (the higher, the better) of a given item to different types of faults (e.g., single-point, latent multi-point, residual faults) based on design (e.g., safe faults) and DC safety measures. And both AVF and PVF vulnerability factors can be used to estimate the fraction of safe failures for derating purposes, which potentially reduces the considered *residual failure* rate, reducing the PMHF and increasing the SPFM [95] (ISO 26262-5 Annex C).

# 3.3 Device Hardware - Components

The most relevant GPU device architectural components are described in Section 2.1 and Figure 1. Except for the SM, all described components are also common for multi-core devices: *processing units* (CPU cores, SMs), *memory*

Table 4: Basic allocation combinations of safety software function(s) in a GPU device

| GPU(s)            |                   | CPU core(s) |                                     |  |

|-------------------|-------------------|-------------|-------------------------------------|--|

|                   | Non-safety        | Safety      | Mixed-Criticality                   |  |

| Non-safety        | Outside the scope | Se          | See multi-core devices survey [153] |  |

| Safety            | Not feasible      | Sco         | ope of the survey: CPU core(s) and  |  |

| Mixed-Criticality | Not feasible      |             | GPU(s) execute safety function(s)   |  |

Table 5: A classification of Fault Injection (FI) based reliability measurement/analysis

| FI Type        | GPU device                               | Tool                        | References                |

|----------------|------------------------------------------|-----------------------------|---------------------------|

| Execution and  | NVIDIA Tesla K20/K40, GeForce 900        | SASSIFI tool                | [160, 78, 159, 158, 170]  |

| software-based | NVIDIA Tesla K20, GeForce 900            | LLFI fault injector variant | [117]                     |

| FI             |                                          |                             |                           |

|                | NVIDIA Tesla C                           | GPU-Qin tool, cuda-gdb      | [63, 64, 66, 65]          |

|                | NVIDIA Titan V                           | NVBitFI                     | [186]                     |

| Simulation and | NVIDIA G80 (Soft-GPU)                    | FlexGrip model (VHDL)       | [165, 163]                |

| software-based | NVIDIA Fermi (Soft-GPU)                  | Soft-GPU model (VHDL)       | [133]                     |

| FI             |                                          |                             |                           |

|                | AMD Radeon HD 7000                       | SIFI, based on Multi2Sim    | [177, 187, 190, 189, 188] |

|                | NVIDIA Quadro FX, GeForce 400            | GUFI, based on GPGPU-Sim    |                           |

| Execution and  | NVIDIA Kepler, Tesla, GeForce 400, Tegra | Neutron-beam                | [157, 169, 161, 138, 140, |

|                | X1, Titan X                              |                             | 185, 72, 139]             |

| hardware-based | NVIDIA Tesla K20, Tesla C                | Extreme operation           | [55, 134]                 |

| FI             |                                          |                             |                           |

Table 6: Classification summary of referenced hard GPUs: microarchitecture and CPU core type

| Mfr.    | Microarch. | CPU cores: Discrete GPUs (None), Embedded GPUs (e.g., ARM, x86)                          |

|---------|------------|------------------------------------------------------------------------------------------|

| AMD     | Vega 8     | x86 [36]                                                                                 |

|         | Terascale  | None [190, 189, 51]                                                                      |

|         | GCN        | x86 [144, 80, 145, 27, 191]                                                              |

| ARM     | Bifrost    | None [105]; ARM [176]                                                                    |

|         | Midgard    | None [74, 116, 40]                                                                       |

| Intel   | HD 530     | x86 [46, 50]                                                                             |

| NVIDIA  | Tesla      | None [40, 39, 26, 51, 74, 125, 124, 135, 199]                                            |

|         | Volta      | None [119, 54, 100, 201]; ARM [12, 14, 34, 40, 47, 162, 15, 25, 32, 39, 47, 105, 142]    |

|         | Pascal     | None [12, 14, 13, 16, 40, 169, 39, 96, 81, 120]; ARM [18, 9, 40, 42, 41, 25, 39, 109,    |

|         |            | 142, 200]                                                                                |

|         | Maxwell    | None [40, 78, 117, 39, 50, 74, 116]; ARM [38, 40, 46, 79, 169, 39, 43, 69, 68, 70, 74,   |

|         |            | 116, 147, 146, 200]                                                                      |

|         | Kepler     | None [74, 116, 35, 140, 170, 160, 78, 117, 157, 169, 134, 50, 49, 51, 97, 101, 167, 200, |

|         |            | 139]; ARM [46, 43, 74, 85, 116, 200]                                                     |

|         | Turing     | None [40, 80, 142]                                                                       |

|         | Fermi      | None [33, 30, 140, 63, 161, 138, 55, 50, 49, 51, 64, 66, 65, 72, 74, 135, 182, 139, 174, |

|         |            | 6, 187, 161, 59, 67, 72]                                                                 |

| Renesas |            | ARM [203, 32, 105]                                                                       |

|         | VR         |                                                                                          |

| Vivante | GC2000     | None [114]                                                                               |

(e.g., device memory, cache) and *data paths* (interconnection network and shared bus). Hence, both GPU and multicore components share multiple common techniques [127, 143, 153]. In this survey we emphasize those particularly relevant for GPU devices.

**Processing Units** As described in Sections 2.1 and 3.2.1, the SMs and the CPU cores are the two common and distinct processing units of a GPU device, which could also integrate additional device-specific accelerators (e.g., deep learning accelerator [4]). Table 6 summarizes the GPU microarchitectures analyzed or used (e.g., case study) by referenced research contributions to facilitate the search for microarchitecture-specific techniques, solutions, and examples. As explained in Section 2.1, CPU cores (with their local register files and cache memories) offload work on the GPU(s), monitor execution, and provide a user interface to use the GPU(s) [196]. Commonly, they are part of multi-core CPU components for performance reasons (e.g., [4]). Therefore, systems equipped with GPU devices inherit those multi-core device characteristics summarized in the survey by Perez et al. [153], in terms of reliability, DC, temporal and spatial independence.

**Memory** As described in Section 2.1 and shown in Figure 1, a GPU device contains several memory components such as device memory, cache(s) and external global memory. GPU devices also include local SRAM memories for predictable and low latency data sharing and communication across threads executing either concurrently or serially. Those SRAM memories are explicitly managed by software and hence, fall in the category of Scratchpad Memory (SPM). The extreme case corresponds to register files, whose size in GPU devices may be similar to the size of L1

caches in CPU cores. Therefore, while they are referred to as register files, in essence, they are not too different from an SPM.

Discrete GPU devices feature their own DRAM memory, which is distinct from the one used by the CPU cores. These two DRAM memories are generally non-coherent among the host (CPU cores) and GPU(s), thus needing the host to copy data into the GPU(s) memory region before starting computation and retrieving output data back to host memory when GPU(s) computation is complete. Such a memory management model avoids the need for managing data coherence across the host and the GPU(s). However, it may cause a non-negligible performance degradation. More recent embedded GPUs use a single DRAM memory shared with the CPU cores in the same SoC with hardware support for coherence [196]. Note that shared memory in embedded GPUs is different from OpenCL SVM and CUDA UVM [39, 40], which are programmability features to simplify GPU programming. By default, the programming model in both types of GPUs is the same and requires explicit copies. In fact, it is argued that unified memory should be avoided in real-time systems (e.g., [137] §3.1) due to its black box implementation [137, 39, 40]. However, when it is used, its implementation on embedded GPUs takes advantage of the physically shared DRAM.

In those systems where memory is not coherent across the CPU cores and the GPU(s) (e.g., discrete GPU), it is particularly critical to keep data local in the GPU(s) to minimize performance costs due to data transfers. Instead, in embedded GPUs while keeping data local is still preferable from a performance perspective, fetching data from memory is less costly. In both cases, GPU devices typically need to manage large amounts of data. Hence, memory is a key component with a significant impact on hardware random failures and independence of execution.

**Data Paths** Interconnection networks and shared buses for GPU devices, either internal or external to connect the CPU cores, GPU(s) and the shared memory, are generally subject to the same requirements as those for multi-core devices. Therefore, we refer the reader to a survey on multi-core devices [153] for further details regarding reliability, DC, temporal and spatial independence. In both cases, namely CPU cores and GPUs, this component is key to providing high average computing performance. Thus, silicon manufacturers tend to provide none or limited public information about the internal design and deployed safety measures to manage random hardware errors, temporal interference and spatial interference.

## 3.4 Device Software - Parallel Computing Languages and Frameworks

GPU devices support only a subset of the many parallel programming models and tools [56]. In fact, embedded GPU and safety GPU devices support even fewer options since the software stack of GPU devices is dominated by closed source drivers and libraries, in order to maintain the secrecy about the proprietary designs [200, 145, 39, 107]. Hence, the available programming models and supported operating systems for each GPU are limited to the ones supported by the vendor, which is frequently dictated by its customers. Some GPU manufacturers follow a more open approach, such as Broadcom, whose VideoCore IV GPU is the only embedded GPU with publicly available specifications. Others like AMD and Intel, despite that they do not provide information about the internals of their hardware designs, they do publicly provide the description of the hardware/software interface of their devices so that open source or safety-critical drivers can be developed. In fact, both of these companies offer open source device drivers for their GPUs, while AMD also supports a proprietary driver, which usually performs better than the open source one.

The primary function of GPU devices has been graphics acceleration, therefore graphics APIs such as OpenGL are used for this purpose. OpenGL has experienced a long evolution over the years, and has variants for serving the desktop and gaming domain (OpenGL), embedded devices (OpenGL ES) and safety-critical systems (OpenGL SC). Some low-end solutions such as ARM's Mali-400 found in MPSoCs used in safety-critical systems, such as the Xilinx Zynq Ultrascale+, only support graphics operations (*graphics GPUs*), using the OpenGL ES version. However, to our knowledge, there is no publicly available information of this API to be used in a safety-critical context. There are two reasons for this: the OpenGL ES contains features that are not appropriate for critical environments, such as dynamic allocation. Moreover, OpenGL ES implementations are closed source and only supported in general-purpose operating systems such as Linux and Android.

Some higher-end safety GPU devices, such as NVIDIA Xavier, support both desktop and embedded versions of OpenGL, but not the safety-critical one. In addition to these, the latest high-end GPU devices also support Vulkan, a low-level API that allows both, the execution of graphics and general-purpose compute workloads. Thanks to this, Vulkan provides almost full control over the GPU hardware, allowing for reduced time overhead of GPU code launches [47].

Besides graphics APIs, most of the latest GPU devices also natively support general-purpose computing APIs (for *computing GPUs*), which are widely used in high-performance computing, and are also investigated for use in real-time and critical systems. The most widely GPU programming model is CUDA, which is proprietary and supported

only by NVIDIA GPUs. Due to its closed source nature, CUDA presents several challenges for use in critical systems. For example, the authors of [200] have detected cases in which programs written in CUDA behave differently from the NVIDIA documentation. Similarly, Calderón et al. [39] showed that the memory allocated by the NVIDIA driver exceeds by far the requested memory by the application.

AMD GPU devices support a CUDA-compatible language called HIP, which has an open source implementation on top of AMD's open source GPU software stack (ROCm). Some authors [145, 107] argue that due to the more open approach of AMD in terms of software programming models, they present a good candidate for use in critical systems. However, frequent changes in the development of these APIs [145] complicate the use of such methods in practice.

Besides these pure GPU languages and APIs, there are also other higher-level ways to program GPUs. For example, OpenMP has recently added support for GPUs through its accelerator offloading mode. This allows to easily annotate a portion of an application source code with directives in order to be executed on a GPU, without significant changes in the application source code. In a similar way, OpenACC, which is an OpenMP-like language for GPUs, offers the same functionality, using similar syntax, but higher performance compared to OpenMP.

## 3.5 Software Application

The software application executed in a given GPU device can be generalized as a set of software applications to be executed in the CPU cores and GPU(s). In order to enable the mixed-criticality integration of software application(s) of different criticality, Burgio et al. [38] propose a software stack composed of virtualization technology (hypervisor), General Purpose Operating System (GPOS) (e.g., Linux) and domain-specific stacks (e.g., AUTOSAR). These solutions are also common for multi-core devices and are described as related research in Section 8.2.

#### 4 Random Hardware Failures

Random hardware failures occur unpredictably. They cannot be (completely) avoided, but only controlled, mitigated and/or detected in order to comply with (extremely) low probability failure ranges and specific metric ranges defined by safety standards (e.g., ISO 26262 PMHF, SPFM, LFM; IEC 61508 PFH). This Section introduces random hardware errors (§4.1) and describes safety measures to control, mitigate and detect errors (§4.2). As introduced in Section 3.3, GPU and multi-core devices share multiple common architectural components and GPUs already integrate, adapt or extend safety measures outlined in multi-core and FPGA device surveys [31, 153, 127, 143] (e.g., Error-Correcting Code (ECC) for memory). Hence, this section focuses on those works and features particularly relevant for GPU devices.

## 4.1 Introduction

Advances in manufacturing processes, electronic design automation tools and CMOS downscaling technology enable the production of 7 nm devices. However, this downscaling gives rise to several threats for reliability such as *Process, Voltage and Temperature (PVT) variability, device aging, transient faults (soft errors)* and *permanent faults* [143]. Two opposite trends exist due to this technology scaling: decreased reliability due to the use of smaller devices and lower supply voltage, thus increasing susceptibility to particle strikes and small defects, and increased reliability due to requiring smaller area for any given circuit, thus decreasing the susceptible area. The resulting FIT rates, in general, are kept low by applying mitigation techniques at the process level (e.g., improved lithographic process), or deploying fault tolerance solutions (e.g., hardening, redundancy). Moreover, some types of advanced manufacturing technologies, such as Fully Depleted Silicon On Insulator (FD-SOI), are inherently immune to certain radiation effects such as latch-ups, which provides increased reliability for certain domains such as space, while products from different fabs or using different manufacturing processes have been observed to have different reliability properties [127]. However, whether all those solutions are applied to improve raw reliability in COTS GPU devices is privately known (e.g., manufacturers) but generally not publicly known.

The optimization towards the highest computational performance is a potential risk for safety-related software execution, since, as already analyzed by Oliveira and Wunderlich et al. [195, 138], the corruption of shared resources such as hardware tasks schedulers and memory caches can lead to the corruption of thread data and downstreaming thread data [140, 170, 51]. There are several reasons, which can also be extrapolated to safety-related application domains, that make *generic GPUs* more error-prone and therefore less reliable than multi-core devices [51]:

• The optimization for maximum average performance and massive parallelism, where (1) the execution depends on several unreliable computing and communication units with no integrated error detection

mechanism and undisclosed documentation for analysis, and (2) an error in a shared resource such as shared memory, scheduler and dispatcher can lead to downstreaming thread errors.

• The higher density of memory, higher number of computing units executing in parallel and a higher ratio of failures due to overheating compared to CPUs [51] can potentially lead to a higher number of errors and reduced reliability.

However, hard embedded safety GPU devices already address these issues, bringing them on par with safety-related multi-core devices. For example, the latest automotive devices designed to comply with ISO 26262 and optionally IEC 61508 safety standard, such as NVIDIA's Xavier [4, 34], Renesas's M3 or ARM's Mali G78AE, already contain features that improve their reliability, such as ECC protection or virtualization, which can also be used for time and space partitioning. Moreover, embedded GPU devices have some relevant differences compared to discrete GPU devices counterparts used in high-performance computing that vary their reliability concerns. For instance, among other factors, smaller area potentially contributes to lower exposure to cosmic radiation, and their power profile is lower, which means that the heat they generate is also lower and, in fact, similar to that of multi-core devices [105]. However, device-specific analysis are required as these factors are just some device-specific relevant factors, but not the only ones to be considered.

Nonetheless, to the best of our knowledge, there are neither consolidated comparative research studies for safety-related systems as opposed to supercomputers [51, 117], nor public reliability measurements provided by GPU device silicon manufacturers as opposed to multi-core device silicon manufacturers (e.g., [198]) that could enable a quantitative comparison of two diverse but functionally equivalent implementations in GPU and multi-core/FPGA devices. Besides, Table 5 (page 8) provides a classification summary of fault injection-based campaigns, from which only a subset focuses on AVF metric estimation or generic reliability and resilience evaluation of the GPU device not linked to a specific software application. For example, radiation sensitivity evaluation campaigns have been implemented to experimentally measure the sensitivity of GPU devices and mitigation provided by integrated ECCs. And the neutron sensitivity experiments described by Oliveira et al. [138] show that even with ECC protecting memory and registers, the overall reliability of the device is jeopardized by errors in the logic and scheduler. This is so because several key resources and components are not protected by such mechanisms (e.g., warp scheduler, thread scheduler, interconnect, instruction dispatch units, pipeline stages, ALUs, LSU), and even internal documentation required for analysis is not disclosed [140, 160, 120, 64].

As characterized by fault injection reliability assessments, vulnerability outcome probabilities are dependent on the executed software application and instruction groups, the way the software stresses the hardware resources, the type of memory usage (e.g., general-purpose registers files, local memory) and can have a time-varying behavior correlated with executed kernel(s) characteristics [160, 78, 190, 51]. For example, a matrix multiplication algorithm software executed (with the required hardware components) in different GPU devices can lead to a significant FIT values variability range, between approximately 150 (FX5600) to 250 (Radeon 7970) [190].

Besides, the extensive analyses conducted to understand GPU errors on large scale supercomputers [123, 179, 134, 51] have drawn relevant insights on the reliability of generic GPU devices and the importance of managing random hardware errors, e.g., GPU as predominant FIT contributor [123], high random hardware error rates and high error correction rates (e.g., 99.997%) [123].

Santos et al. [169] provide an empirical analysis of the soft error sensitivity of a neural network-based object detection library on three different NVIDIA GPU devices: Kepler K40, Maxwell Tegra X1 and Pascal Titan X. Authors observe that the Tegra X1 error rate halves that of the K40, which is attributed to the smaller area used by the former (20nm technology) compared to the latter (28nm technology). While area could justify error rate to halve, using smaller transistors could easily lead to increased soft error susceptibility, as discussed before. Therefore, although not public information is given, we expect some additional process or fault tolerance solutions to be in place for Tegra X1 w.r.t. K40. The authors also observe a 10x lower FIT rate for Titan X w.r.t. K40. A number of factors contribute to such reduction: (1) the use of 3-D transistors (FinFET technology) instead of standard CMOS, which provides 10x lower sensitivity per bit to particle strikes. (2) The Pascal architecture is particularly devised for neural network execution. Hence, it is expected that fewer resources are used, therefore further decreasing FIT rates. However, it is difficult to draw solid conclusions from the results of these analyzes, due to the multiple factors that can potentially affect the sensitivity to transient errors and because multiple factors are even not publicly known, e.g., microarchitecture details, different number and mixes of SRAM and flip-flop cells.

Finally, the deployment of *soft GPUs* (VHDL) on FPGAs can take advantage of the 'safe execution environment' that can be provided by modern FPGAs and SoCs/MPSoCs with integrated FPGA(s) [31]. For example, FPGAs use several hardening techniques and fault tolerance mechanisms for increasing reliability and enable their usage in harsh environments such as aerospace [31, 153].

#### 4.2 Safety measures to control, mitigate and detect errors

Safety measures to control, mitigate and detect errors, are commonly implemented using hardware built-in safety mechanisms and complementary software-only techniques. As briefly explained in Section 3.1, integrating safety measures with a reasonable cost is a key technical challenge. The integration of hardware built-in safety mechanisms (e.g., diagnostics, fault tolerance, redundancy, hardening) can increase the silicon die area, power consumption and cost, and performance decrease [153]. For example, the deployment of GPU devices for harsh industrial environments such as automotive grade-0 (operating temperature range between –40°C to 150°C) and space [105], needs to consider a trade-off between performance and reliability. This occurs because the development of devices designed to operate in those environments needs to consider larger hardened transistors, wider wires, circuit design constraints, diagnostics, and fault-tolerance mechanisms that reduce the overall computing performance and increase the cost [15, 153, 127]. Moreover, in some cases, COTS devices such as GPUs cannot be designed with the same reliable nano-technologies used for other critical components for that domain (e.g., space, avionics). In this case, the industry takes advantage of the inherent variability of the produced chips, so the most reliable devices can be selected out of a given batch, after passing a predefined set of screening and stress tests (e.g., thermal, vibration). Additionally, another common approach to manage this trade-off is the implementation of software-based safety measures, using and extending existing hardware built-in safety mechanisms or implementing additional software-only safety measures.

GPU devices provide a rich set of computing hardware that could be potentially used to implement generic redundancy and diversity techniques such as spatial diversity, temporal diversity, computation unit layout diversity. For example, software redundancy is a common technique for reliability improvement that can be implemented with additional requirements such as cache sharing limitation among threads, which mitigate the effect of common shared resources corruption as identified in fault-injection campaigns [138]. Redundancy can also be combined with spatial diversity, such as blocks duplication and distribution in different SMs, to further reduce the probability of common cause failure and improve reliability [138]. In addition, diverse redundancy can be applied at kernel level, exploiting the scheduling properties of the GPU devices to ensure that blocks from redundant kernels are executed by different SMs [14]. Similarly, this idea can be applied in the design of new GPU device architectures [13]. However, the practical exploitation of these techniques is limited for developers due to the lack of information and software execution control due to 'black box' hardware components (e.g., ECC algorithm [139]) and 'software frameworks' that manage such resources [15] (e.g., resource allocation [40]). These 'black box' hardware and 'software frameworks' are key elements to provide competitive devices with maximum average performance, so information provided by silicon manufacturers is none or limited [98], and several research initiatives aim at providing an understanding of the implemented management [40, 18].

Therefore, selecting and combining sufficient and cost-effective safety measures becomes a device and application-specific challenge. For example, given a software safety function that requires a medium DC and uses a set of (design-time identified) device hardware resources, the safety engineer needs to use available hardware built-in safety mechanisms that commonly provide low to medium DC (e.g., ECC for memory) and complementary software-only techniques to achieve a medium DC. In this context, this subsection describes hardware and software safety measures for most relevant GPU components (§4.2.1) and software-only safety measures (§4.2.2).

Moreover, due to the high variability of GPU devices and microarchitectures used in research contributions (see Table 6 on page 8), along with different experimental scenarios (e.g., case study, method, programming style [72]), it becomes difficult to compare proposed safety measures and select the appropriate ones without performing device and application-specific analyses. Besides, the potential adaptation to the safety-critical domain of generic high-performance computing domain research contributions is not straightforward, as it requires to comply with strict safety standards requirements and associated technical challenges. For example:

- Depth and rigor: Adapted safety measures need to meet the depth and rigor required by safety standards. For example, the naïve implementation of software Duplication with Comparison (DWC) of (just) the output results does not guarantee a medium DC, as at least sufficient and representative intermediate calculation results should also be compared to detect latent errors. And the device-specific benefits of spatial/temporal diversity should also be analyzed.

- *Not recommended* techniques: Whenever a safety measure is not-recommended, reasonable and sufficient justification should be provided if used. For example, *backward recovery* technique (e.g., checkpoint and restart) is considered not-recommended (e.g., IEC 61508-3 Table A.2) because hard temporal deadlines could be potentially missed in case of several consecutive backward recoveries.

- *Dynamic*: Dynamic and reconfigurable behavior are commonly considered not recommended due to the difficulty of providing sufficient evidence of correct and safe behavior under all possible scenarios. However, not all designs have to be static, and it is possible to use limited and design time defined dynamic behaviors.

• *Tool qualification*: Techniques that rely on off-line software tools that modify/instrument software source code need to consider tool qualification requirements (e.g., T3, TCL3).

# 4.2.1 Components

This subsection summarizes hardware built-in and software-based safety measures that control, mitigate and detect random hardware errors at SM, memory and data path components. As SMs also integrate memory and data path (sub)components, the described SM safety measures can be complemented with memory and data path specialized safety measures.

**Processing Units** Due to the limited public documentation, controllability and observability of SM architectures, few works target the reliability of SMs explicitly. In general, works attempt to improve SMs (and other components simultaneously) employing different software-based redundancy techniques for the whole SM, its cores only, or parts of those cores (e.g., pipeline registers [163]) using available underutilized resources in order to reduce the computing overhead [6, 191, 178, 199, 57, 73]. Some authors combine software redundancy with diversity to mitigate common cause failures by, for instance, making redundant threads execute with some staggering in different cores [13, 14, 8].

Besides, most analyses and solutions for error detection on SMs are also software-based, employing diverse and different approaches. For example, some works adapt common techniques such as redundancy to detect execution errors (e.g., DWC [99], instruction replication [120]) and *backward recovery*-based techniques [71, 175, 180, 135]. And other works propose specialized adaptations such as control flow and data flow checkers [132] and dynamic DWC to detect permanent errors [164].

As previously explained, due to the high variability of considered devices, microarchitectures and scenarios, the application of previously summarized diverse example techniques require a device and application-specific analysis with the required *depth and rigor*. Besides, techniques that rely on tools such as compilers (e.g., [191, 132]) shall consider *tool qualification* requirements, *dynamic* actions (e.g., [164, 6]) shall be safely managed and *backward recovery*-based techniques shall safely manage their generic *not recommendation* rationale.

Memory Memory concerns for GPU devices are shared for multi-core devices [127, 57]. In general, GPUs have higher memory performance demands than CPUs due to their increased computational capacity, which calls for larger amounts of data being transferred per time unit. Hence, reliability threats for multi-cores are further exacerbated for GPUs. Nowadays, ECC is a common built-in error detection (diagnostic) and recovery mechanism (fault tolerance) integrated in memories [120, 169], which can result in an effective reduction in the number of errors (e.g., 4x reduction [169]) should they occur while data is stored or whenever transmitted. And in order to improve reliability, new technologies have emerged (e.g., phase change memories, normally used for storage but also considered as main memory [113]) and advanced manufacturing technologies (e.g., 3D stack) [153, 127]. For example, Zhang et al. [193] have observed that 3D stacking brings a shielding effect where inner dies may get more than 90% of the particle strikes filtered. Hence, if GPU devices are integrated with 3D memory dies on-chip for performance reasons, soft error reductions may be obtained at the same time. Similar observations have been raised in multiple works that exploit heterogeneous exposure to particle strikes of the different layers due to shielding effects to trade-off between performance and reliability [127]. Note, however, that, despite soft error mitigation achieved with 3D stacking, such designs have some disadvantages related to their challenging heat dissipation, fabrication costs, and yield loss w.r.t. conventional 2D designs [53].

The reliability improvement of cache memories is crucial because most of the device area is devoted to cache SRAM memory, which is susceptible to transient faults [143]. Therefore, nowadays ECC is also commonly integrated in caches, e.g., in the recent NVIDIA Ampere architecture the first and second level caches are ECC protected [108]. However, it should be taken into account that increasing the cache size can lead to a higher soft error rate increase (superlinear) [127]. In addition to this, generic high-performance computing device techniques are also potentially applicable, such as 4-layer 3D stacked cache memory design to drastically reduce the innermost layer vulnerability to soft errors and usage of Spin-Transfer Torque RAM (STT-RAM) technology for caches [153, 127]. Finally, cache coherency diagnosis is briefly explained in Section 6.2.

Concerning DRAM-based *global memory*, some authors have studied the relevance of different types of faults, namely transient and permanent, in DRAM memory devices, concluding that permanent faults are more significant in memory [91]. While this study is not GPU-specific, it is particularly relevant for GPU devices due to their strong dependence on (abundant) data fetched (frequently) from memory. Hwang et al. [91] also show that decommissioning faulty pages is an effective solution with negligible cost in general to detect and control permanent errors. But this a *dynamic* behavior that needs to be defined at design time. Concerning transient errors, Maruyama et al. have seen that it was common having ECC protected DRAM memory for CPUs, but at that time, its use was not available for

GPU devices [124, 125]. Hence, they proposed a combination of software-based ECC diagnostic and checkpointing for GPU memory to tolerate faults. However neutron-beam FI experiments have shown that software-based ECC could lead to a significant reduction of SDC (e.g., one order of magnitude) but even higher functional interruption rates than unprotected executions (e.g., 55% increase for matrix-to-matrix multiplication) due to random hardware errors associated with the hardware resources required to execute the ECC software [139]. So, in the absence of a hardware built-in ECC mechanism, the usage of software-based ECC for safety-critical systems requires a careful device-specific analysis (depth and rigor).

Moreover, DDR memories (mainly DDR3 and DDR4) suffer the "row hammer" effect, in which memory cells may leak some of their charges to nearby cells when accessed. While these effects have been mitigated to some extent, they are expected to exacerbate as memory technology scales down. Therefore, GPU devices accessing large DDR memories (several gigabytes) at high frequency may suffer reliability problems due to the row hammer effect [196]. This effect, either as a random hardware failure where the memory content is unintentionally modified or as a result of an intentional security exploitation, can lead to memory content corruption (a memory error).

**Data path** As explained in Section 3.3, interconnection networks and shared buses are key to providing high average computing performance, and manufacturers tend to provide none or limited public information. Thus, error detection is usually performed with software-only techniques (§4.2.2) that do not diagnose the data path itself but the errors that can be generated [153] (indirect diagnosis).

#### 4.2.2 Software-Only Techniques

Software-only techniques can be used to increase reliability whenever hardware support is not sufficient. Software techniques are either application-agnostic (e.g., software redundant execution [34, 12, 14, 170, 120, 140, 57, 191], multithreading-based soft error fault tolerance [77, 57, 191]), application-dependent (e.g., Algorithmic-Based Fault Tolerance (ABFT) [35, 138, 169, 170, 168, 195], application-specific [102]) and/or combinations of the previous [170]. Equivalent solutions can be generally used in both GPU and multi-core devices. But, a fundamental difference is that controllability in GPU devices is much lower than in multi-core devices, for instance, when implementing software-only diverse redundancy with strong guarantees on multi-core devices [12] and limited guarantees on GPU devices [14] due to the inability to monitor progress in the GPU once kernels are offloaded. Oliveira et al. [140] provide an extensive description of software mitigation techniques for non-safety-related uses of GPUs. In addition to this, there is a reported correlation between the measured reliability and the executed applications [63, 78, 159], and even the explored application input sizes and biased input values [158, 159] (e.g., 30% failure rate increase with input size change [159]).