Portland State University PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

1997

# New Approaches to Column Compatibility Checking and Column-Based Input/Output Encoding for Curtis Decompositions of Completely or Incompletely Specified Switching Functions

Michael A. Burns Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Electrical and Computer Engineering Commons Let us know how access to this document benefits you.

#### **Recommended Citation**

Burns, Michael A., "New Approaches to Column Compatibility Checking and Column-Based Input/Output Encoding for Curtis Decompositions of Completely or Incompletely Specified Switching Functions" (1997). *Dissertations and Theses.* Paper 6318. https://doi.org/10.15760/etd.8173

This Thesis is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

#### THESIS APPROVAL

The abstract and thesis of Qihong Chen for the Master of Science in Electrical and Computer Engineering were presented June 25, 1998, and accepted by the thesis committee and the department.

#### ABSTRACT

An abstract of the thesis of Qihong Chen for the Master of Science in Electrical and Computer Engineering presented June 25, 1998.

Title: The Design of Cube Calculus Machine Using SRAM-based FPGA Reconfigurable Hardware DEC's PeRLe-1 Board

Cube calculus is an algebraic model used to process boolean functions. Cube calculus operations are widely used in logic optimization, logic synthesis, image processing and recognition, machine learning, and other applications which require massive logic operations.

The cube calculus operations can be carried out on general-purpose computers. Since these operations can involve several levels of nested loops, this approach has poor performance.

A cube calculus machine which has a special data path designed to speed up cube calculus operations is presented in this thesis. This cube calculus machine can execute cube calculus operations 10 to 25 times faster than the software approach on a general-purpose computer.

This thesis proposes a complete design of the Cube Calculus Machine Version II (CCM2). In this design, the CCM acts as a coprocessor of the host computer; it accepts a set of instructions that let the CCM carry out cube calculus operations. This design is mapped on a reconfigurable hardware DEC PeRLe-1 board.

#### THE DESIGN OF CUBE CALCULUS MACHINE USING SRAM-BASED FPGA RECONFIGURABLE HARDWARE DEC'S PERLE-1 BOARD

by QIHONG CHEN

A thesis submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE in ELECTRICAL AND COMPUTER ENGINEERING

> Portland State University 1998

#### ACKNOWLEDGEMENTS

I would like to thank Dr. Marek A. Perkowski, my advisor, who patiently guided and encouraged me through this master program.

I also would like to thank Dr. Douglas V. Hall and Dr. Sarah Mocas for their valuable comments, suggestions on my thesis and their willingness to be in my thesis defense committee.

Finally, I would like to thank Laura Riddell and Shirley Clark for their continuous support and help throughout my studies at Portland State University.

## CONTENTS

| L] | IST (       | OF TABLES iv                                                                                   |            |  |

|----|-------------|------------------------------------------------------------------------------------------------|------------|--|

| L  | ST C        | OF FIGURES                                                                                     | v          |  |

| 1  | Intr        | roduction                                                                                      | 1          |  |

| 2  | A F         | Review of Cube Calculus                                                                        | 7          |  |

|    | 2.1         | Sets                                                                                           | 7          |  |

|    | 2.2         | The Concept of A Cube                                                                          | 8          |  |

|    | 2.3         | Cube Calculus Operations                                                                       | 10         |  |

|    |             | 2.3.1 Simple combinational cube operations                                                     | 11         |  |

|    |             | 2.3.2 Complex combinational cube operations                                                    | 12         |  |

|    |             | 2.3.3 Sequential cube operations                                                               | 16         |  |

|    |             | 2.3.4 Summary of cube calculus operations                                                      | <b>2</b> 1 |  |

|    | 2.4         | Positional Notation and Cube                                                                   |            |  |

|    |             | Operations in Positional Notation                                                              | 22         |  |

|    |             | 2.4.1 Positional notation                                                                      | 22         |  |

|    |             | 2.4.2 Set operations in positional notation                                                    | 23         |  |

|    |             | 2.4.3 Set relations in positional notation                                                     | 25         |  |

|    |             | 2.4.4 Summary of cube operations in positional notation                                        | 26         |  |

| 3  | Cul         | be Calculus Machine                                                                            | 29         |  |

|    | <b>3</b> .1 | Formalism for main algorithm for cube                                                          |            |  |

|    |             | calculus operation                                                                             | 29         |  |

|    | 3.2         | The general programmable patterns                                                              | <b>3</b> 1 |  |

|    | 3.3         | The data path of CCM                                                                           | 33         |  |

|    |             | <b>3.3.1</b> Iterative network                                                                 | 33         |  |

|    |             | 3.3.2 The algorithm of the CCM                                                                 | 36         |  |

|    |             | 3.3.3 The signal ready $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 42         |  |

|    | 3.4         | Iterative Logic Unit and Iterative Cell                                                        | 43         |  |

|    |             | 3.4.1 Handling multi-valued variables                                                          | 44         |  |

|    |             | 3.4.2 The design of an iterative cell                                                          | 49         |  |

|    | 3.5         | The architecture of the CCM                                                                    | 55         |  |

|    | 3.6         | The Operation Control Unit (OCU)                                                               | 55         |  |

|    | 3.7         | Pre-relation/Pre-operation                                                                     | 58         |  |

| 4 | PA  | M and DECPeRLe-1                               | 62         |

|---|-----|------------------------------------------------|------------|

|   | 4.1 | PAM                                            | 63         |

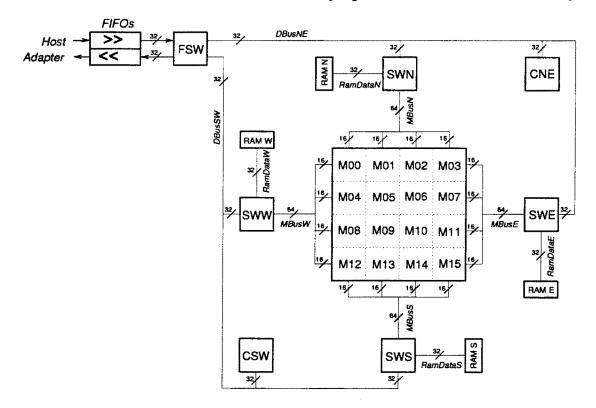

|   | 4.2 | PeRLe-1 Board                                  | 65         |

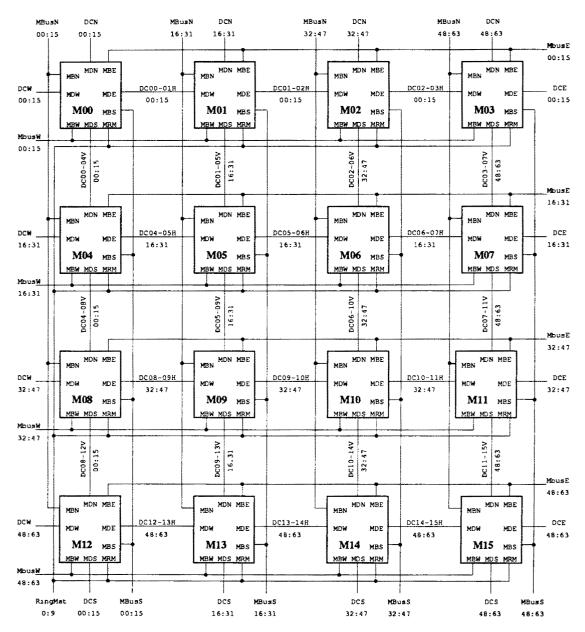

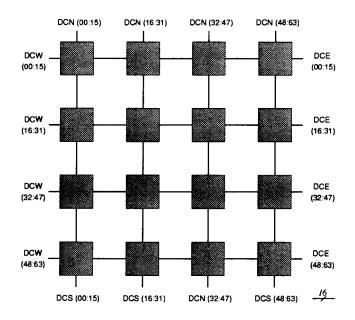

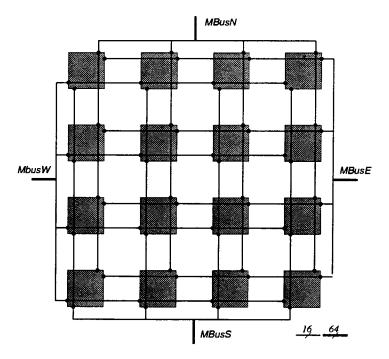

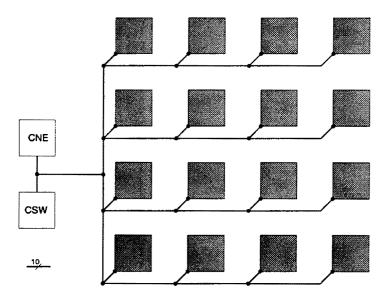

|   |     | 4.2.1 Computational matrix                     | 67         |

|   |     | 4.2.2 Switches and I/O buses                   | 69         |

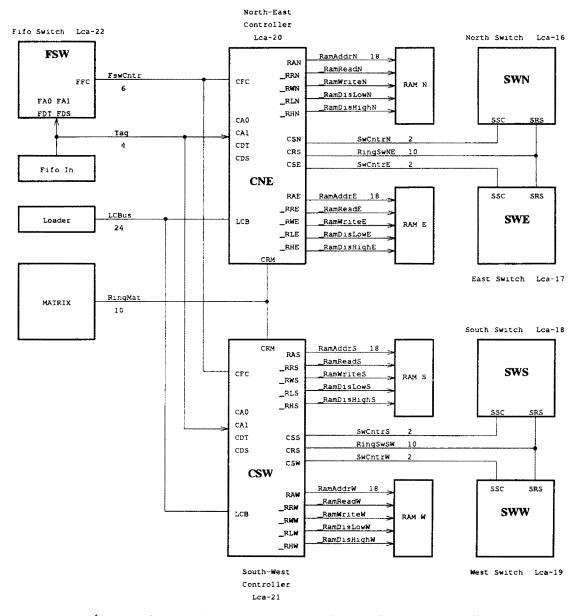

|   |     | 4.2.3 Control resource                         | 70         |

|   |     | 4.2.4 Memory subsystem                         | 72         |

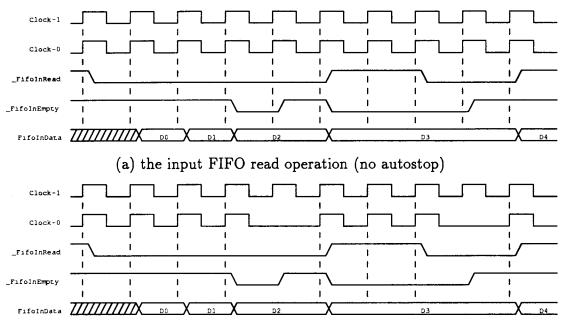

|   |     | 4.2.5 Clock subsystem                          | 74         |

|   |     | 4.2.6 Host interface                           | 76         |

|   |     | 4.2.7 Performance                              | <b>8</b> 0 |

|   |     | 4.2.8 The runtime library                      | 80         |

|   | 4.3 | Programming                                    | 82         |

| 5 | The | e Design of Cube Calculus Machine Co-processor | 85         |

| Ŭ | 5.1 | Executing Patterns                             | 86         |

|   | 5.2 | The Design of the CCM                          | 88         |

|   | 0.2 | $5.2.1$ Data Bus $\ldots$                      | 89         |

|   |     | 5.2.2 Memory and Address Units                 | 90         |

|   |     | 5.2.3 Registers                                | 90         |

|   |     | 5.2.4 Dataflow mode                            | 92         |

|   | 5.3 | Instructions and Their Encoding                | 94         |

|   |     | 5.3.1 Set Accumulator                          | 94         |

|   |     | 5.3.2 Set Tri-state Buffers                    | 95         |

|   |     | 5.3.3 Set Registers                            | 97         |

|   |     | 5.3.4 Execute                                  | 99         |

|   |     |                                                | 101        |

|   | 5.4 | •                                              | 102        |

|   | 5.5 |                                                | 107        |

| 6 | CC  | M Assembly 1                                   | 11         |

| U | 6.1 | •                                              | 11         |

|   | 6.2 | Examples of Using CCM Assembly                 |            |

|   | -   |                                                |            |

| 7 |     |                                                | 22         |

|   | 7.1 | • •                                            | 22         |

|   | 7.2 |                                                | 23         |

|   |     | • •                                            | 24         |

|   |     |                                                | 26         |

|   |     |                                                | 26         |

|   |     |                                                | .27        |

|   |     |                                                | .27        |

|   |     | 7.2.6 Test two complex cases                   | .28        |

| 8  | Design Evaluation                                                                                                                                                                                                                                 | 130                                                                |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 9  | Applications of Cube Calculus Machine9.1Satisfiability Problem9.2Tautology Problem                                                                                                                                                                | <b>135</b><br>136<br>137                                           |

| 10 | Conclusions and Future Work                                                                                                                                                                                                                       | 139                                                                |

| RI | EFERENCES                                                                                                                                                                                                                                         | 141                                                                |

| AI | PPENDICES                                                                                                                                                                                                                                         | 146                                                                |

| A  | Test Programs                                                                                                                                                                                                                                     | 147                                                                |

| в  | VHDL Codes         it_ident.vhd         it_oper.vhd         it_state.vhd         it_count.vhd         it_empty.vhd         it_cell.vhd         pcountd.vhd         ilu_cu.vhd         ilu.vhd         biu_vhd         ccm.vhd         testccm.vhd | 152<br>153<br>154<br>155<br>158<br>159<br>162<br>166<br>174<br>180 |

| С  | The C program to perform disjoint-sharp operation                                                                                                                                                                                                 | 198                                                                |

## LIST OF TABLES

| 1.1         | Notation                                                         | 6   |

|-------------|------------------------------------------------------------------|-----|

| 2.1         | Cube Calculus Operations                                         | 22  |

| 2.2         | Positional Notation for binary literals                          | 23  |

| 2.3         | The partial relation of sharp operation                          | 26  |

| 2.4         | Cube Calculus Operations in bitwise function and relation type   | 27  |

| <b>3</b> .1 | The Output Values of Bitwise Functions Used in Cube Operations . | 33  |

| 3.2         | Pre-relation and Pre-relation of the Cube Calculus Operations    | 58  |

| 3.3         | Decomposed Pre-relation and Pre-operation of the Cube Operations | 59  |

| 3.4         | Encoded Pre-relation and Pre-operation of the Cube Operations    | 60  |

| 4.1         | PeRLe-1 Timing Characteristics                                   | 81  |

| 8.1         | Compare CCM (1.33 MHz) with software approach                    | 132 |

| 8.2         |                                                                  |     |

## LIST OF FIGURES

| 2.1        | Intersection operation example                                         | 11         |

|------------|------------------------------------------------------------------------|------------|

| 2.2        | Supercube operation example                                            | 12         |

| 2.3        | Prime operation example                                                | 13         |

| 2.4        | Prime operation example                                                | 14         |

| 2.5        | Cofactor operation example                                             | 16         |

| 2.6        | Crosslink example                                                      | 18         |

| 2.7        | A complex crosslink example                                            | 18         |

| 2.8        | Sharp example                                                          | 20         |

| 2.9        | Disjoint sharp example                                                 | 21         |

| 3.1        |                                                                        | 32         |

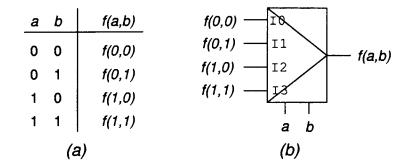

| 3.1<br>3.2 | Realizing an arbitrary function of two binary variables                |            |

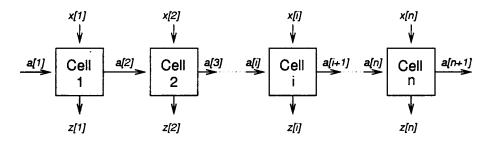

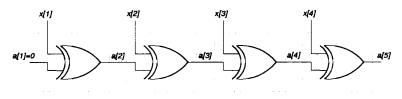

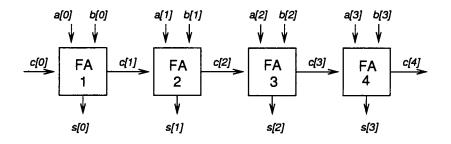

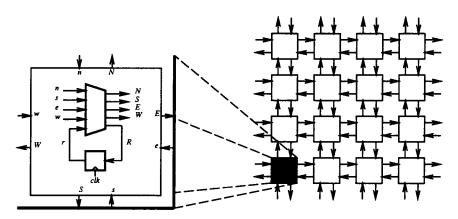

| 3.2<br>3.3 | A Simple Iterative Network                                             | 34         |

| 3.3<br>3.4 | Parity Checker                                                         | 35         |

|            | Ripple-Carry Binary Adder                                              | 35         |

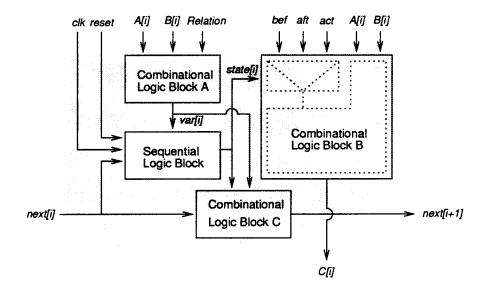

| 3.5<br>3.6 | An simplified iterative cell of the CCM                                | 37         |

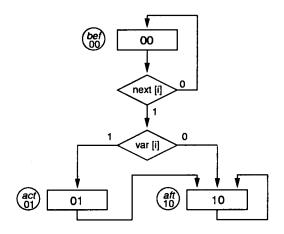

|            | The SM chart of the FSM                                                | 38         |

| 3.7        | The iterative network of the CCM                                       | <b>3</b> 9 |

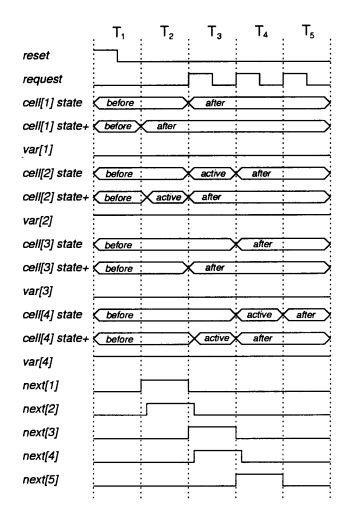

| 3.8        | Timing diagram of Example 3.3                                          | 40         |

| 3.9        | The rule of naming signals                                             | 44         |

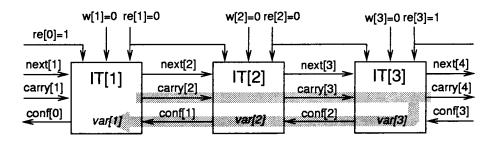

| 3.10       | Three iterative cells combined together to process a 6-valued variable | 46         |

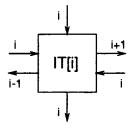

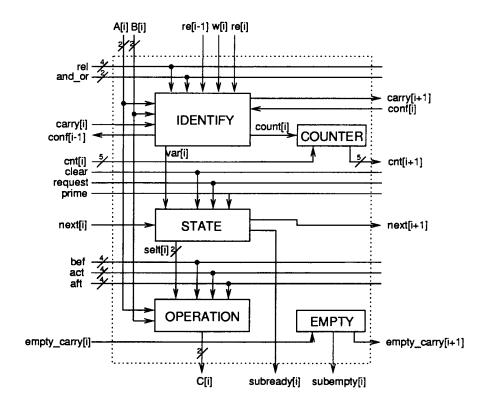

| 3.11       | The block diagram of a Iterative Cell (IT)                             | 49         |

|            | Block OPERATION of IT                                                  | 50         |

|            | counter                                                                | 53         |

|            | Iterative network used to generate <i>empty</i> signal                 | 54         |

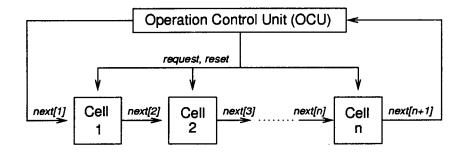

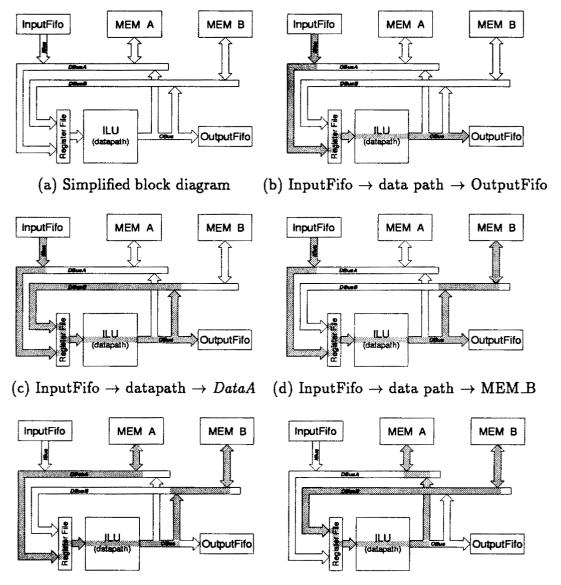

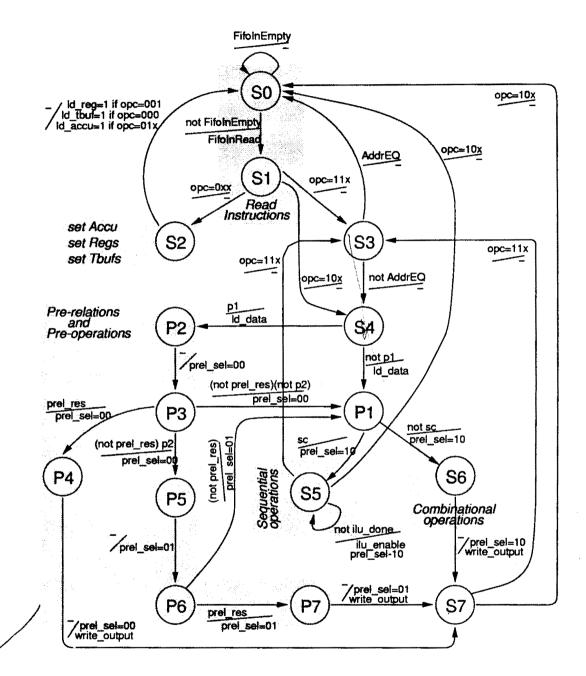

|            | The simplified block diagram of the CCM                                | 55         |

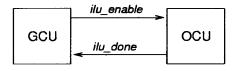

|            | The communication between the GCU and the OCU                          | 56         |

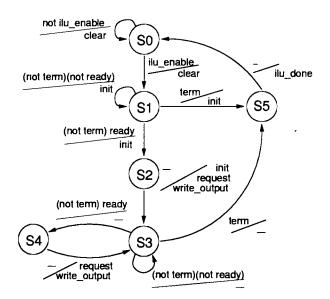

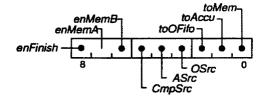

|            | The state diagram of the OCU                                           | 56         |

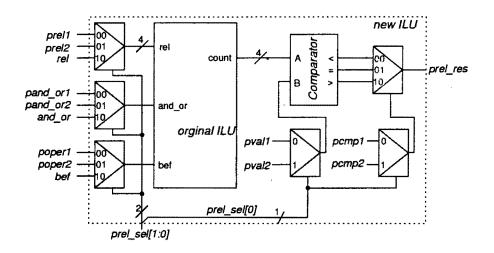

| 3.18       | Realization of Pre-relation/Pre-operation                              | 60         |

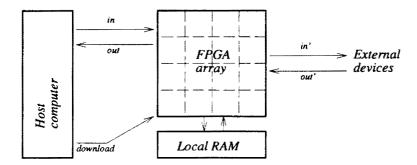

| 4.1        | A simple PAM                                                           | 63         |

| 4.2        | PAMs as virtual machines                                               | 64         |

| 4.3        | PeRLe-1 architecture                                                   | 65         |

| 4.4        | PeRLe-1 matrix                                                         | 66         |

| 4.5        | PeRLe-1 Direct connection                                              | 67         |

| 4.6        | PeRLe-1 Matrix data buses                                              | 68         |

| 4.7        | PeRLe-1 Matrix rings                                                   | 69         |

|            |                                                                        |            |

| 4.8  | PeRLe-1 control wires                                            |

|------|------------------------------------------------------------------|

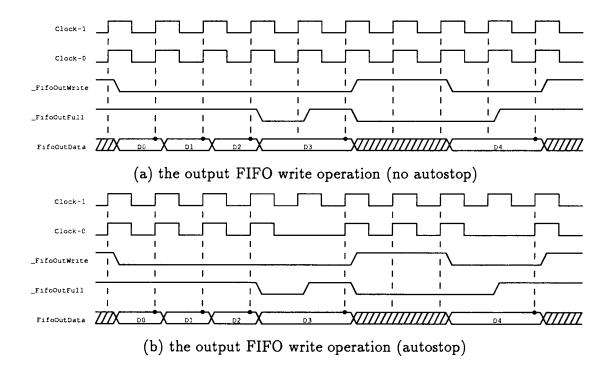

| 4.9  | The input FIFO operation                                         |

| 4.10 | The output FIFO operation                                        |

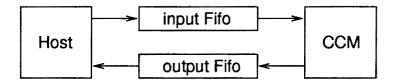

| 5.1  | Communication between the host and the CCM 85                    |

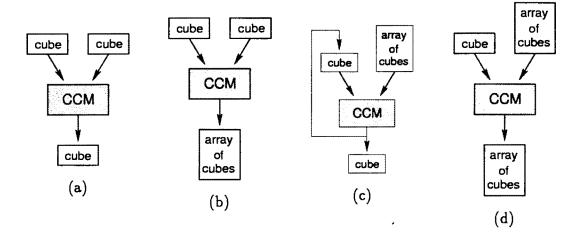

| 5.2  | Cube operation patterns                                          |

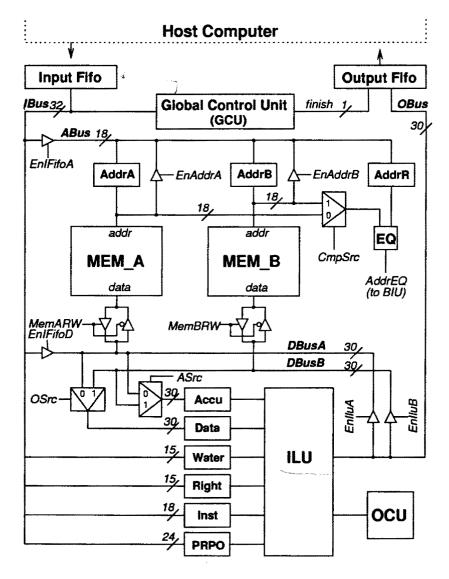

| 5.3  | The Block Diagram of Our Design                                  |

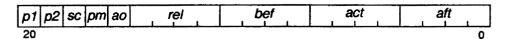

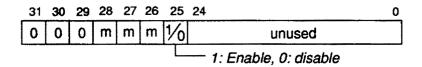

| 5.4  | The content of <i>instruction</i> register                       |

| 5.5  | The content of prpo register                                     |

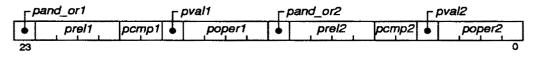

| 5.6  | The dataflow modes of the CCM                                    |

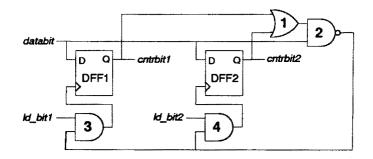

| 5.7  | Avoiding contention which would result from multiple drivers 95  |

| 5.8  | Timing diagram of special circuit for avoiding bus contention 96 |

| 5.9  | the format of config register                                    |

| 5.10 | The state diagram of the GCU                                     |

|      | The outline of mapping                                           |

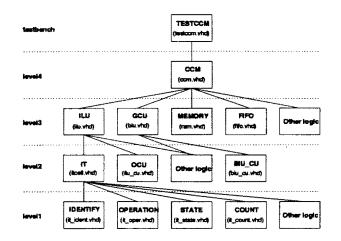

| 7.1  | Hierarchical structure of the CCM                                |

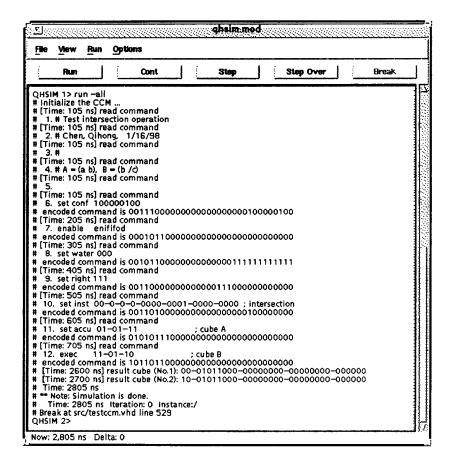

| 7.2  | The simulation of Test1                                          |

## CHAPTER 1

### Introduction

Cube Calculus is an algebraic model used to process boolean functions [26, 27, 28, 29, 30, 34, 37, 16, 32, 43]. Cube calculus operations are widely used in logic optimization, logic synthesis, image processing and recognition, machine learning, and other applications which require massive logic operations.

The cube calculus operations can be implemented on general-purpose computers at the cost of control overhead. Almost all general-purpose computers are of traditional Von Neumann computer architecture. In traditional Von Neumann computer architecture, the control is located in the program that is stored in the memory. This results in a considerable control overhead. Since the instructions have to be fetched from the memory, if an algorithm contains loops, the same instruction will be read many times. This makes the memory interface the bottleneck of these architectures, especially when the memory bus is not as fast as the internal processor bus. Also, in many commonly used computer architectures, there is very little parallel processing, even in modern RISC or Pentium processors. The cube calculus operations involve several-level nested loops, that leads to poor performance on conventional computer architectures. The slow processing speed of the cube calculus operations is the bottleneck of many application such as logic synthesis, machine learning, and others.

This thesis presents a variant design of Cube Calculus Machine version II (CCM2 for short), a special hardware which has an innovative data path designed to execute cube operations efficiently. This design is mapped onto a DEC PeRLe-1 board, one of the earliest platforms for Reconfigurable Computing (RC). In our design, the CCM acts as a co-processor to the host computer. The host computer needs only

to issue the commands (CCM instructions) to the CCM and obtain the result from the CCM.

The first version of the CCM was introduced in 1989 by Luis S. Kida and Dr. Marek Perkowski as a general purpose logic computer with a data path designed specifically to execute cube calculus operations. The second version of CCM (CCM2) was designed by a group of students in Dr. Perkowski's EE510 Computer Architecture for Robotics and Artificial Intelligence course during the 1991-1992 school year.

The CCM architecture is based on an observation that many cube calculus operations can be described in a general equation of certain logic/set equation (see Chapter 2 and Chapter 3). In this general format, the literals of the operand cubes are divided into three types of literals, according to a *relation* of literals of operand cubes. This relation is defined by the type of cube calculus operation. As the resultant cubes are generated, the literals of the operand cubes go through a sequence of literal types. The value of a literal in the resultant cube depends not only on the corresponding literals in the operand cubes, but also on the current types of these literals.

This general format of an equation is implemented in the Iterative Logic Unit (ILU for short) of the CCM architecture. The ILU consists of an array of Iterative Cells (ITs). Each IT can process two bits, either as a binary variable or a portion of a multi-valued variable in *positional notation*. Each IT contains a Finite State Machine (FSM) to keep track of the current type of literal that is being processed. The value of a resultant literal is not only calculated from the operand literals, but also from the current state of the FSM of the given IT.

A considerable part of the control of the CCM is implemented in its data path, which is the ILU. Once the ILU has received a cube calculus operation, the only control that is needed from the Control Unit of the ILU (called *Operation Control* Unit in our design) is the clock signal for the output of the resultant cubes.

One version of the ILU with 8 ITs of the CCM2 has been implemented by David W. Foote on 2 Xilinx XC3090 FPGAs [17]. Simulation and experimental

results have shown that cube calculus operations executed on the FPGA Cube Calculus Machine are 10 to 25 times faster than those executed by using the software approach on a conventional computer. The larger the input cube, the more speed gain can be obtained by using the CCM.

Since our design is targeted for DEC PeRLe-1, a pioneer of Reconfigurable Computing (RC), let us take a look at Reconfigurable Computing. Reconfigurable Computing [1, 2] is a relatively new term that describes computer and controller systems that can be configured "on-the-fly" to meet the needs of the target application.

FPGAs contain a large number of diverse logic gates and registers, which can be connected together in widely different ways to achieve a desired function. SRAMbased variants extend the capabilities of standard FPGA by allowing new configuration data to be downloaded into the device by the main system in a fraction of a second. Therefore, SRAM-based FPGAs are reconfigurable computing elements.

Computing circuits built from SRAM-based FPGAs can meet the true goal of parallel processing, executing algorithms in circuitry with inherent parallelism of hardware, while avoiding the instruction fetch and load/store bottlenecks of traditional Von Neumann architectures. There are many computationally intensive algorithms that can benefit from being partially or wholly implemented in hardware. Typically, these algorithms are too specialized to justify the expense of manufacturing custom IC devices. Just as often, the "algorithm space" is very large, and it may be impractical to perform enough simulations to find the optimal approach before committing to custom hardware.

With an FPGA-based "configurable co-processor" the user can design exactly the special hardware required for a given task without having to construct new hardware for each application. Different tasks can be time-multiplexed into the same FPGAs. Errors can be corrected and different algorithmic approaches explored, with no further hardware expense.

Several universities and research laboratories have been exploring the use of SRAM-based FPGAs to implement multi-purpose, high-speed co-processors for accelerating operations in computer systems. Using these systems, desktop workstations have delivered the performance of supercomputers for specific applications. In particular, two projects have gained considerable attention: the PeRLe systems from DEC's Paris Research Lab, and the SPLASH machines from the Supercomputer Research Center. These systems consist of FPGA-based attached processors in engineering workstations, complete with programming tools and run-time environments, and have been the target for a variety of "real world" applications.

DEC's Paris Research Laboratory has designed and implemented four generations of FPGA-based reconfigurable co-processors called Programmable Active Memories (PAMs) [5, 6, 7, 8, 9]. The most-widely used version, the PeRLe-1, is based on a  $4 \times 4$  array of XC3090 FPGAs. Developed applications include long multiplication, RSA cryptography, heat and LaPlace equations, a sound synthesizer and many others [9].

The Supercomputer Research Center (SRC) has designed two generations of the SPLASH processor based on a linear array of FPGAs [2, 4]. The SPLASH-1 includes a 32-stage linear logic array with a VME interface to a Sun workstation. Each stage consists of an XC3090 FPGA and a 128 Kbyte static memory buffer. The first application of the SPLASH-1 was to implement a systolic algorithm for onedimensional pattern matching during DNA research, where it out-performed a Cray-2 by a factor of 325 and a custom-built nMOS device by a factor of 45. The SPASH-2 system is based on XC4010 FPGA devices, and has been used to implement a number of applications, including string searches and image processing[4].

The successes of these and other early projects have fueled the interest of the research community. The IEEE now devotes an entire annual workshop to FPGA-based computing, IEEE workshop on FPGAs for Custom Computing Machines (FCCM)[3].

FPGA-based reconfigurable processors are available for a broad range of applications, including scientific computing, database manipulation, design automation, cryptography, image processing and real-time digital signal processing. FPGAbased processors can exploit the fact that most of the processing time for a computeintensive tasks is spent in a relatively small portion of the code, and hardware acceleration of that portion can significantly improve the overall performance.

In the long term, expected advances in FPGA density, performance and architecture may offer more significant advances than single processor solutions can promise. While many important hardware and software challenges remain, it is conceivable that reconfigurable processors constructed from SRAM-based programmable logic eventually will replace today's general-purpose processors, providing the basis for systems that automatically will alter their own hardware to best solve the problem at hand.

The CCM2 of PSU was originally meant to be fit into silicon, and the design of the CCM2 chip had been layed out and simulated from the extracted circuit. Due to the lack of VLSI fabrication funding, the attempt to fabricate CCM2 chip failed.

As of Spring 1992, the "old" Xilinx tools and two Xilinx XC3090 chips were available to the EE department at PSU, and the core of the CCM2, the ILU with 8 ITs, was mapped onto these two chips by David W. Foote [17].

As of 94/95, a DEC PeRLe-1 board was available to the EE department at PSU. Unfortunately, there was no documentation and development tools available. As of July 97, the documentation of the board became available. As of this writing, the development tools for DEC PeRLe-1 board are still not usable because a special C++ compiler that can collaborate with this board is needed. We expect the complete development tools to be available in the near future.

The design of the CCM presented in this thesis is a variant of CCM2, and is targeted at the PeRLe-1 board. Therefore, this design tightly depends on the architecture of the PeRLe-1 board. For the first time it is a complete design, including Global Control (GCU), ILU with 15 ITs, and Operation Control Unit (OCU). My design accepts a set of instructions that are optimized for practical applications. The CCM communicates with the host computer through the input and output FIFOs. The host issues the commands to the CCM through the input FIFO, and gets the results from the output FIFO. The instructions do not limit the CCM to execute only the cube calculus operations introduced in this thesis, actually, the CCM can execute all cube calculus operations that can be described in the general format of equations (see Chapter 2 and Chapter 3 for detail).

Once the development tools for the PeRLe-1 board become available, this design will be realized on the PeRLe-1 board, and the corresponding C/C++ based cube operation library (see section section 6.1) will be implemented on the host computer.

The following chapters are organized as follows: Chapter 2 presents a subset of cube calculus operations. Chapter 3 introduces the Iterative Logic Unit of the CCM2. This section gives a detailed description of the design and functionality of the ILU. Chapter 4 introduces the DEC PeRLe-1 board in detail, the programming method is also given in this chapter. Chapter 5 presents our design of the CCM2, including the design of Global Control Unit, and mapping on the PeRLe-1 board. Chapter 6 presents CCM assembly language. Chapter 7 present the simulation result of our design described in VHDL. Chapter 8 evaluates our design of the CCM. Chapter 9 shows some possible applications of the CCM. Chapter 10 gives a conclusion of the tasks that were accomplished in this thesis and a list of further work that is necessary to be performed to complete a ready-to-be-used Cube Calculus Machine.

In this thesis, the notations shown in Table 1.1 are used to represent different type of objects.

| Туре            | Font                                 | Example                |  |

|-----------------|--------------------------------------|------------------------|--|

| variable        | lower case letter                    | $a, b, x, x_i$         |  |

| literal         | lower case letter                    | $\bar{a}, x_i^{0,1,3}$ |  |

| cube            | upper case letter                    | A, B                   |  |

| array of cubes  | upper case letter with arrow on head | $\vec{A}, \vec{B}$     |  |

| set             | curly braces                         | $\{0,1,\ldots,n\}$     |  |

| the name of set | upper case letter                    | P, S                   |  |

Table 1.1: Notation

### CHAPTER 2

## A Review of Cube Calculus

Most of the efficient modern logic synthesis programs use the so-called *cube* calculus to represent and process Boolean functions. This representation is used in U.C.Berkeley programs, including the well-known Espresso [37], MIS II and SIS, and many others [29, 30, 16, 32]. This calculus has been used for Boolean minimizers, tautology and satisfiability checkers, verifiers and other software tools[31].

In this chapter, the concept of a *set* is presented first because it is used as a fundament of cube calculus; then the concept of cube and the cube calculus are presented. The last part of this chapter presents positional notation of cubes and how to carry out the cube calculus in positional notation.

#### **2.1** Sets

A set is a collection of objects called *elements* or *members*. As listed in Table 1.1, we use curly braces to indicate sets.

For instance, the set of all integer between 0 and 5 is written as:

$$\{0,1,2,3,4,5\}$$

the infinite set of all positive, odd integers can be describe by:

The membership of a element a in a set A is denoted by  $a \in A$  to mean "a is an element of A". A set which has no element is called an *empty set* (denoted by  $\emptyset$ ). The empty set is a subset of all sets. The elements contained in a set are either listed explicitly or described by their properties.

The following relations between two sets are used in cube calculus:

- Two sets A and B are equal, or identical, if they contain precisely the same elements. It is denoted by A = B.

- A set A is said to be a subset of B if every element of A is also an element of B. It it denoted by A ⊆ B.

- If  $A \subseteq B$ , and B contains at least one element which is not contained in A, then A is said to be *proper subset* of B. It is denoted by  $A \subset B$ .

The elements of the sets are taken from universal set (U). The following basic set operations are used in cube calculus:

- The complement of A in universal set U (denoted by  $\neg A$ ) is the set of all elements of U that are not elements of A.

- The intersection of A and B (denoted by  $A \cap B$ ) is the set containing the elements that are in both A and B.

- The union of A and B (denoted by  $A \cup B$ ) is the set containing the elements that are in either A or B.

**Example 2.1.** Assuming that the universal set U is  $\{0,1,2,3,4,5\}$ , a set A is  $\{0,1,2,3\}$  and another set B is  $\{2,3,4\}$ . Then  $\neg A = \{4,5\}$ ,  $A \cap B = \{2,3\}$ , and  $A \cup B = \{0,1,2,3,4\}$ .

The universal set U of possible values of a binary variable is  $\{0,1\}$ . For a binary variable a, literal  $\bar{a}$  means that literal is true when variable a is 0, and can be described by  $a^{\{0\}}$ , where  $\{0\}$  is the true set of literal  $\bar{a}$ . More detailed discussion on sets can be found in [35, 36].

### 2.2 The Concept of A Cube

The basic concepts of cube calculus are a cube and an array of cubes. A cube is a product of literals. For example, product  $\bar{a}bc\bar{d}$  is a cube. An array of cubes is a sum of cubes. A logic function can be represented by a cube or an array of cubes. For instance, a simple 2-input binary logic function AND can be described by a cube as:  $f_{AND}(a, b) = ab$ ; another simple 2-input binary logic function XOR (exclusive OR) can be described by an array of cubes as:  $f_{XOR}(a, b) = \bar{a}b + a\bar{b}$ .

In a binary logic, a *literal* is a binary variable with negation or without negation  $(x \text{ or } \bar{x})$ . In a multi-valued logic a literal  $(x_i^{S_i})$  is a variable  $(x_i)$  with its set of values  $(S_i)$  for which the variable is true.

A multi-valued input, two-valued output, incompletely specified switching function (*multi-valued function* for short) is a mapping:

$$f(x_1, x_2, \cdots, x_n): P_1 \times P_2 \times \cdots \times P_n \mapsto B$$

(2.1)

where  $x_i$  is a multi-valued ( $p_i$ -valued) variable,  $P_i = \{0, 1, 2, \dots, p_i - 1\}$  is the set of values that variable  $x_i$  may assume,  $B = \{0, 1, x\}$  (x denotes a don't care value). n denotes the number of variables (positions). For any subset  $S_i \in P_i$ ,  $x_i^{S_i}$  is a literal of  $x_i$  representing the function such that:

$$\mathbf{x}_{i}^{S_{i}} = \begin{cases} 1 & \text{if } \mathbf{x}_{i} \in S_{i} \\ 0 & \text{if } \mathbf{x}_{i} \notin S_{i} \end{cases}$$

(2.2)

$S_i$  is called *true values set* (*true set* for short) of literal  $x_i^{S_i}$ . For example, a fourvalued input logic of  $x^{\{1,2,3\}} = 1$  if  $x \in \{1,2,3\}$ , which means  $x^{\{1,2,3\}} = 1$  if x = 1 or x = 2 or x = 3; otherwise,  $x^{\{1,2,3\}} = 0$ . We always assume that the set of possible values of a *n*-valued logic variable is  $\{0, 1, 2, ..., n-1\}$ .

A product of literals,  $x_1^{S_1} x_2^{S_2} \cdots x_n^{S_n}$ , is referred to as a *product term* (also called *product* or *term* for short), and can be represented by a cube. A product term that includes literals for all function variables  $x_1, x_2, \ldots, x_n$  is called a *full term*. Any literal of the form  $x_i^{P_i}$  is always equal to 1 since the literal is true for all possible values of  $x_i$ , thus  $x_i^{P_i} x_j^{S_j}$  can be written as  $x_j^{S_j}$ .

A sum of products is denoted as a Sum-Of-Products Expression (SOPE) while a product of sums is called a Product-Of-Sums Expression (POSE). An EXOR of products will be called a Exclusive Sum Of Products form (ESOP). A product of EXORs will be called a Product Of Exclusive Sums expression (POES). SOPE, POSE, ESOP and POES are all represented as an arrays of cubes. Products of SOPEs (PSOPEs) are also used for the Generalized Propositional Formulas form. They are represented as arrays of arrays of cubes.

The degree of a cube is the number of literals in the cube that are not equal to one (in other word,  $P_i \neq S_i$ ).

Example 2.2. The degree of cube  $a^{\{0\}}b^{\{1\}}c^{\{1\}}d^{\{0,1\}}$  is 3 (assuming a,b,c and d are binary variables).

The *difference* of two cubes is the number of variables for which the corresponding literals have different true sets. The *distance* of two cubes is the number of variables for which the corresponding literals have disjoint true sets.

**Example 2.3.** Given two cubes  $A = a^{\{0,1\}}b^{\{0\}}c^{\{0\}}$ ,  $B = a^{\{1,2\}}b^{\{1\}}c^{\{0\}}$ . The difference of cubes A and B is 2 because they have different true sets on variables a and b. The distance of cubes A and B is 1 because they have disjoint true sets on variable b.

### 2.3 Cube Calculus Operations

The cube calculus operations presented in this thesis can be categorized into three groups: simple combinational operations, complex combinational operations and sequential operations.

Each cube operation has one or two operand cube(s). Cubes A and B are used to represent these arguments and they can be described by:

$$A = x_1^{S_1^A} x_2^{S_2^A} \cdots x_i^{S_i^A} \cdots x_n^{S_n^A}$$

(2.3)

$$B = x_1^{S_1^B} x_2^{S_2^B} \cdots x_i^{S_i^B} \cdots x_n^{S_n^B}$$

(2.4)

where  $S_i^A$  and  $S_i^B$  are the true sets of literal  $x_i^{S_i^A}$  and  $x_i^{S_i^B}$ , respectively. *n* is the number of variables. In this chapter, *S* represents the true set of a literal, the subscript of *S* represents the index of the variable, the superscript of *S* represents the operand cube (*A* or *B*).

#### 2.3.1 Simple combinational cube operations

Simple combinational cube operations are defined as single set operations. Such a set operation is applied on all pairs of true sets  $S_i^A$  and  $S_i^B$  of corresponding literals of operand cubes. A simple combinational cube operation produces one resultant cube. The *intersection* and the *supercube* are simple combinational cube operations presented in this section.

#### Intersection

The intersection of two cubes A and B is the cube that is included in both A and B. The intersection operation of cubes A and B is defined as follows:

$$A \cap B = \begin{cases} x_1^{S_1^A \cap S_1^B} \cdots x_n^{S_n^A \cap S_n^B} & \text{if there is no such } i \text{ that } S_i^A \cap S_i^B = \emptyset \\ \emptyset & \text{otherwise} \end{cases}$$

(2.5)

Where  $S_i^A \cap S_i^B$  is a set intersection operation.  $\emptyset$  denotes an empty set, and  $\emptyset$  denotes a contradiction.

**Example 2.4.** Assuming two cubes A = ab and  $B = b\tilde{c}$ , where a, b and c are binary variables. The intersection of two cubes A and B is the following:

$$A = ab = abx = a^{\{1\}}b^{\{1\}}c^{\{0,1\}}$$

$$B = b\bar{c} = xb\bar{c} = a^{\{0,1\}}b^{\{1\}}c^{\{0\}}$$

$$A \cap B = a^{\{1\}}\cap\{0,1\}}b^{\{1\}}\cap\{1\}c^{\{0,1\}}\cap\{0\} = a^{\{1\}}b^{\{1\}}c^{\{0\}} = ab\bar{c}$$

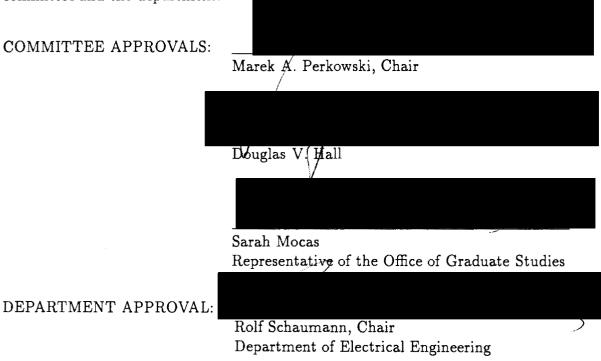

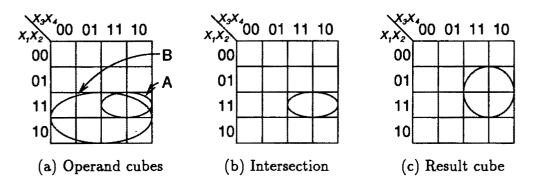

Figure 2.1: Intersection operation example

Example 2.4 is illustrated in Figure 2.1 by Karnaugh map. The intersection operation can be used in function decomposition [40, 41].

#### Supercube

The supercube of two cubes A and B is the smallest cube that includes cubes A and B. The supercube operation of cubes A and B is defined as follows:

$$A \cup B = x_1^{S_1^A \cup S_1^B} \cdots x_n^{S_n^A \cup S_n^B}$$

(2.6)

Where  $S_i^A \cup S_i^B$  is a set union.

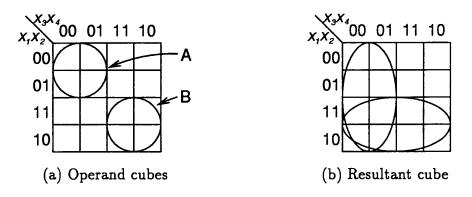

Example 2.5. The supercube on two cubes A and B used in Example 2.4 follows:

$A \cup B = a^{\{1\}\cup\{0,1\}}b^{\{1\}\cup\{1\}}c^{\{0,1\}\cup\{0\}} = a^{\{0,1\}}b^{\{1\}}c^{\{0,1\}} = b$

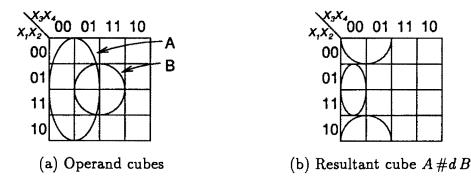

$\begin{array}{c} bc \\ 0 \\ 0 \\ 1 \\ \end{array}$

(a) Operand cubes

(b) Resultant cube

Figure 2.2: Supercube operation example

Example 2.5 is illustrated in Figure 2.2 by Karnaugh map. The supercube operation can be used in graph coloring problem [42].

#### 2.3.2 Complex combinational cube operations

Complex combinational cube operations are defined as two set operations and one set relation. These two set operations are called *before* (*bef* for short) and *active* (*act* for short). All variables whose pair of true sets  $S_i^A$  and  $S_i^B$  satisfy *relation* are said to be *special variables*. The *Active* set operation is applied on all pairs of true sets  $S_i^A$  and  $S_i^B$  of special variables. The *before* set operation is applied on the others. A complex combinational cube operation produces one resultant cube like simple combinational cube operation. Prime is an example of complex combinational cube operation.

#### Prime

The prime operation of two cubes A and B is defined as:

$$A'B = x_1^{S_1^A} \cdots x_{k-1}^{S_{k-1}^A} x_k^{S_k^A \cup S_k^B} x_{k+1}^{S_{k+1}^A} \cdots x_{l-1}^{S_{l-1}^A} x_l^{S_l^A \cup S_l^B} x_{l+1}^{S_{l+1}^A} \cdots x_n^{S_n^A}$$

(2.7)

Where the relation for the prime operation is  $S_i^A \cap S_i^B \neq \emptyset$ . The active set operation is  $S_i^A \cup S_i^B$ , and the before set operation is  $S_i^A$ . In the above equation, variables  $x_k$  and  $x_l$  are the special variables.

**Example 2.6.** Assuming two cubes  $A = \bar{x_1}x_2x_3x_4$  and  $B = x_1\bar{x_3}$ , where  $x_1, x_2, x_3$  and  $x_4$  are binary variables. The prime of A'B is defined as follows:

$$A = \bar{x_1} x_2 x_3 x_4 = x_1^{\{0\}} x_2^{\{1\}} x_3^{\{1\}} x_4^{\{1\}}$$

$$B = x_1 \bar{x_3} = x_1 x \bar{x_3} x = x_1^{\{1\}} x_2^{\{0,1\}} x_3^{\{0\}} x_4^{\{0,1\}}$$

Because:

$$S_2^A \cap S_2^B = \{1\} \cap \{0,1\} = \{1\} \neq \emptyset$$

$$S_4^A \cap S_4^B = \{1\} \cap \{0,1\} = \{1\} \neq \emptyset$$

variable  $x_2$  and  $x_4$  are special variables. Therefore,

$$A'B = x_1^{S_1^A} x_2^{S_2^A \cup S_2^B} x_3^{S_4^A \cup S_4^B} = x_1^{\{0\}} x_2^{\{0,1\}} x_3^{\{1\}} x_4^{\{0,1\}} = \bar{x_1} x_3$$

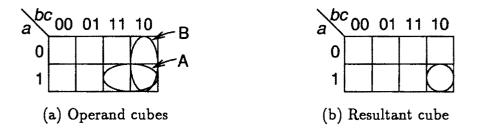

Figure 2.3: Prime operation example

Example 2.6 is illustrated in Figure 2.3 by Karnaugh map. The prime operation is used in the ESOP minimization program EXORCISM, developed by Dr. Perkowski and his former students [29, 30].

#### Consensus

The consensus operation on cubes A and B is defined as follows:

$$A * B = \begin{cases} A \cap B & \text{when } distance(A, B) = 0 \\ \phi & \text{when } distance(A, B) > 1 \\ A *_{basic} B & \text{when } distance(A, B) = 1 \end{cases}$$

(2.8)

where  $A *_{basic} B$  is defined as follows:

$$A *_{basic} B = x_1^{S_1^A \cap S_1^B} \cdots x_{k-1}^{S_{k-1}^A \cap S_{k-1}^B} x_k^{S_k^A \cup S_k^B} x_{k+1}^{S_{k+1}^A \cap S_{k+1}^B} \cdots x_n^{S_n^A \cap S_n^B}$$

(2.9)

where  $S_k^A \cap S_k^B = \emptyset$ . For basic consensus operation, the *before* set operation is  $S_i^A \cap S_i^B$ , the *active* set operation is  $S_i^A \cup S_i^B$ , and the *relation* is always true.

**Example 2.7.** Assuming two cubes  $A = x_1x_2\bar{x_3}$  and  $B = x_1\bar{x_2}$ , where  $x_1$ ,  $x_2$ ,  $x_3$  and  $x_4$  are binary variables. Because the distance of cubes A and B is 1, then cubes A and B have consensus as follows:

$$A = x_1 x_2 \bar{x_3} = x_1^{\{1\}} x_2^{\{1\}} x_3^{\{0\}} x_4^{\{0,1\}}$$

$$B = x_1 \bar{x_2} = x_1 \bar{x_2} x x = x_1^{\{1\}} x_2^{\{0\}} x_3^{\{0,1\}} x_4^{\{0,1\}}$$

Because:

$$S_2^A \cap S_2^B = \{1\} \cap \{0\} = \emptyset$$

variable  $x_2$  is a special variable. Therefore,

$$A * B = x_1^{S_1^A \cap S_1^B} x_2^{S_2^A \cup S_2^B} x_3^{S_3^A \cap S_3^B} x_4^{S_4^A \cap S_4^B} = x_1^{\{1\} \cap \{1\}} x_2^{\{0\} \cup \{1\}} x_3^{\{0\} \cap \{0,1\}} x_4^{\{0,1\} \cap \{0,1\}} = x_1 \bar{x_3} - x_1 \bar{x_3} - x_1 \bar{x_3} - x_1 \bar{x_4} - x_1 \bar{x_5} - x_1 \bar{x_5}$$

Figure 2.4: Prime operation example

Example 2.7 is illustrated in Figure 2.4 by Karnaugh map. The consensus operation is used for finding prime implicants, and finding prime implicant is a basic step of the well-known Quine-McCluskey algorithm that is used for two-level logic minimization and its variants [23], as well as many other basic algorithms for

two-level, three-level and multi-level logic minimization and machine learning [33].

#### Cofactor

The cofactor operation of two cubes A and B is defined as:

$$A \mid B = \begin{cases} A \mid_{basic} B & \text{when } A \cap B \neq \emptyset \\ \emptyset & \text{otherwise} \end{cases}$$

(2.10)

where  $A \mid_{basic} B$  is defined as follows:

$$A|_{basic} B = x_1^{S_1^A \cap S_1^B} \cdots x_{k-1}^{S_{k-1}^A \cap S_{k-1}^B} x_k^U x_{k+1}^{S_{k+1}^A \cap S_{k+1}^B} \cdots x_{l-1}^{S_{l-1}^A \cap S_{l-1}^B} x_l^U x_{l+1}^{S_{l+1}^A \cap S_{l+1}^B} \cdots x_n^{S_n^A \cap S_n^B}$$

$$(2.11)$$

Where the relation for cofactor operation is  $S_i^A \supseteq S_i^B$ . The result of the *active* set operation is always U (universal set), and the *before* set operation is  $S_i^A \cap S_i^B$ . In the above equation, variables  $x_k$  and  $x_l$  are special variables.

**Example 2.8.** Assuming two cubes  $A = x_1x_2x_3$  and  $B = x_1$ , where  $x_1$ ,  $x_2$ ,  $x_3$  and  $x_4$  are binary variables. The cofactor of A|B is defined as follows:

$$A = x_1 x_2 x_3 = x_1 x_2 x_3 x = x_1^{\{1\}} x_2^{\{1\}} x_3^{\{1\}} x_4^{\{0,1\}}$$

$$B = x_1 = x_1 x x x = x_1^{\{1\}} x_2^{\{0,1\}} x_3^{\{0,1\}} x_4^{\{0,1\}}$$

Because:

$$\begin{split} S_1^A &= \{1\} \ , S_1^B &= \{1\} \ \to \ S_1^A \supseteq S_1^B \\ S_2^A &= \{1\} \ , S_2^B &= \{0,1\} \ \to \ S_2^A \not\supseteq S_2^B \\ S_3^A &= \{1\} \ , S_3^B &= \{0,1\} \ \to \ S_3^A \not\supseteq S_3^B \\ S_4^A &= \{0,1\} \ , S_4^B &= \{0,1\} \ \to \ S_4^A \supseteq S_4^B \end{split}$$

variable  $x_1$  and  $x_4$  are special variables. Therefore,

$$A|B = x_1^U x_2^{S_2^A \cap S_2^B} x_3^{S_3^A \cap S_3^B} x_4^U = x_1^{\{0,1\}} x_2^{\{1\} \cap \{0,1\}} x_3^{\{1\} \cap \{0,1\}} x_4^{\{0,1\}} = x_2 x_3$$

Figure 2.5: Cofactor operation example

This example is illustrated in Figure 2.5 by a Karnaugh map. In the Karnaugh map, first we calculate the intersection of cubes A and B, the intersection result is shown in Figure 2.5(b), then we remove variable  $x_1$  which means in the result cube, variable  $x_1$  can be either 1 or 0 (don't care); the result cube is shown in Figure 2.5(c). If there is no intersection of two operand cubes, then the cofactor is an empty cube. The cofactor operation is an important operation used in function decomposition [40, 41].

#### 2.3.3 Sequential cube operations

All sequential cube operations are defined as a single formula that has three set operations and one set relation. These three set operations are called *before* (*bef* for short), *active* (*act* for short) and *after*(aft for short), respectively. All variables whose pair of true sets  $S_i^A$  and  $S_i^B$  satisfy relation are said to be special variables.

The sequential cube operations produces m resultant cubes, where m is the number of special variables for a given operation. The sequential cube operations can be generally described by the following fundamental equation:

$$A(op)B = \left\{ x_{1}^{aft(S_{1}^{A},S_{1}^{B})} \cdots x_{i-1}^{aft(S_{i-1}^{A},S_{i-1}^{B})} x_{i}^{act(S_{i}^{A},S_{i}^{B})} x_{i+1}^{bef(S_{i+1}^{A},S_{i+1}^{B})} \cdots x_{n}^{bef(S_{n}^{A},S_{n}^{B})} \right.$$

$$\left| \text{ for such } i = 1, \dots, n, \text{ that } relation(S_{i}^{A},S_{i}^{B}) \text{ is true} \right\}$$

$$(2.12)$$

where  $x_i$  is a special variable, bef, act and aft are set operations. Every spe-

cial variable produces a resultant cube according to Equation 2.12. This equation is a general pattern of all cube calculus operations and it was mentioned in the introduction.

#### Crosslink

The crosslink operation on cubes A and B produces an array of cubes defined as:

$$A \square B = \left\{ x_1^{S_1^B} \cdots x_{i-1}^{S_{i-1}^B} x_i^{S_i^A \cup S_i^B} x_{i+1}^{S_{i+1}^A} \cdots x_n^{S_n^A} \\ \left| \text{ for such } i = 1, \dots, n, \text{ that } S_i^A \cap S_i^B = \phi \right\}$$

(2.13)

For crosslink operation, the before set operation is  $bef(S_i^A, S_i^B) = S_i^A$ , the active set operation is  $act(S_i^A, S_i^B) = S_i^A \cup S_i^B$ , the after set operation is  $aft(S_i^A, S_i^B) = S_i^B$ , and the relation is  $S_i^A \cap S_i^B = \emptyset$ . The crosslink operation can only be applied to two cubes when the two operand cubes are of the same degree, and x (don't care) must be in same position(s).

**Example 2.9.** Assuming variables  $x_1, x_2, x_3$  and  $x_4$  are binary, two cubes  $A = \bar{x_1}\bar{x_3}$ and  $B = x_1x_3$ , the crosslink operation  $A \square B$  follows:

$$A = \bar{x_1}\bar{x_3} = \bar{x_1}x\bar{x_3}x = x_1^{\{0\}}x_2^{\{0,1\}}x_3^{\{0\}}x_4^{\{0,1\}}$$

$$B = x_1x_3 = x_1x\bar{x_3}x = x_1^{\{1\}}x_2^{\{0,1\}}x_3^{\{1\}}x_4^{\{0,1\}}$$

Because:

$$S_1^A \cap S_1^B = \{0\} \cap \{1\} = \emptyset$$

$$S_3^A \cap S_3^B = \{0\} \cap \{1\} = \emptyset$$

the variable  $x_1$  and  $x_3$  are special variables. And two resultant cubes are:

$$x_1^{S_1^A \cup S_1^B} x_2^{S_2^A} x_3^{S_4^A} = x_1^{\{0\} \cup \{1\}} x_2^{\{0,1\}} x_3^{\{0\}} x_4^{\{0,1\}} = x_1^{\{0,1\}} x_2^{\{0,1\}} x_3^{\{0\}} x_4^{\{0,1\}} = \bar{x_3} \\ x_1^{S_1^B} x_2^{S_2^B} x_3^{S_4^A \cup S_3^B} x_4^{S_4} = x_1^{\{1\}} x_2^{\{0,1\}} x_3^{\{0\} \cup \{1\}} x_4^{\{0,1\}} = x_1^{\{1\}} x_2^{\{0,1\}} x_3^{\{0,1\}} = x_1 \\ x_1^{\{1\}} x_2^{\{0,1\}} x_3^{\{1\}} x_4^{\{1\}} = x_1^{\{1\}} x_2^{\{0,1\}} x_3^{\{1\}} x_4^{\{1\}} = x_1^{\{1\}} x_2^{\{0,1\}} x_3^{\{1\}} x_4^{\{1\}} = x_1 \\ x_1^{\{1\}} x_2^{\{1\}} x_3^{\{1\}} x_4^{\{1\}} = x_1^{\{1\}} x_4^{\{1\}} x_4^{\{1\}} x_4^{\{1\}} = x_1^{\{1\}} x_4^{\{1\}} x_$$

Therefore,

$$A \Box B = \bar{x_1}\bar{x_3} \Box x_1x_3 = \bar{x_3} + x_1$$

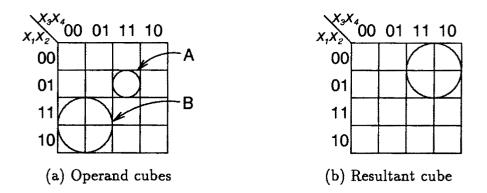

Figure 2.6: Crosslink example

The Example 2.9 is illustrated in Figure 2.6 by Karnaugh map. The crosslink operation can be used in the minimization of logic functions in some canonical forms based on EXOR logic, for instance, the Generalized Reed Muller form [29], as well as the general-purpose AND/EXOR form called ESOPs. The function  $f = \bar{x}_1 \bar{x}_3 + x_1 x_3$  can be realized using EXOR gates as:

$f=\bar{x_1}\bar{x_3}+x_1x_3=\bar{x_3}\oplus x_1$

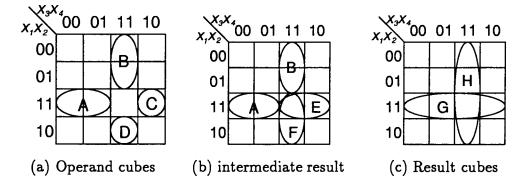

Figure 2.7: A complex crosslink example

Another more complex example is shown in Figure 2.7. As shown in Figure 2.7(a), we have a function  $f = A \oplus B \oplus C \oplus D$ , where A, B, C and D are four cubes. First, we calculate  $C \square D$  and obtain cubes E and F, and the function becomes  $f = A \oplus B \oplus E \oplus F$  as shown in Figure 2.7(b). Second we calculate  $A \square E$  and  $B \square F$ , and obtain cubes G and H; therefore, the function is simplified as  $f = G \oplus H$ .

The crosslink operation is used in ESOP minimization program EXORCISM, developed by Dr. Perkowski and his former student Martin Helliwell in 1988/89 [29, 30]. A more powerful cube operation, called *exorlink*, and a new ESOP minimization program EXORCISM-MV-2 based on *exorlink* operation was developed by Dr. Perkowski and his former student Ning Song in 1993 [16, 32, 43].

#### Sharp

The (non-disjoint) sharp operation on cubes A and B is defined as follows:

$$A \ \# \ B = \begin{cases} A & \text{when } A \cap B = \emptyset \\ \\ \phi & \text{when } A \subseteq B \\ \\ A \ \#_{basic} B & \text{otherwise} \end{cases}$$

(2.14)

where  $A \#_{basic} B$  is defined as follows:

$$A \#_{basic} B = \left\{ x_1^{S_1^A} \cdots x_{i-1}^{S_{A,i-1}} x_i^{S_i^A \cap (\neg S_i^B)} x_{i+1}^{S_{A,i+1}} \cdots x_n^{S_n^A} \right.$$

$$\left. \left. \left. \text{for such } i = 1, \dots, n, \text{ that } \neg (S_i^A \subseteq S_i^B) \right. \right\}$$

(2.15)

For sharp operation, the before set operation is  $S_i^A$ , the active set operation is  $S_{i}^A \cap (\neg S_i^B)$ , the after set operation is  $S_i^A$ , and the relation is  $\neg (S_i^A \subseteq S_i^B)$ .

**Example 2.10.** Assuming variables  $x_1$ ,  $x_2$ ,  $x_3$  and  $x_4$  are binary, two cubes  $A = \bar{x_3}$  and  $B = x_2x_4$ , the sharp operation A # B follows:

$$A = \bar{x_3} = x x \bar{x_3} x = x_1^{\{0,1\}} x_2^{\{0,1\}} x_3^{\{0\}} x_4^{\{0,1\}}$$

$$B = x_2 x_4 = x x_2 x x_4 = x_1^{\{0,1\}} x_2^{\{1\}} x_3^{\{0,1\}} x_4^{\{1\}}$$

Because:

$$\neg (S_2^A \subseteq S_2^B) = \neg (\{0,1\} \subseteq \{1\}) = true$$

$$\neg (S_{A,4} \subseteq S_{B,4}) = \neg (\{0,1\} \subseteq \{1\}) = true$$

variables  $x_2$  and  $x_4$  are special variables. Thus, 2 resultant cubes are:

$$x_1^{S_1^A} x_2^{S_2^A \cap (\neg S_2^B)} x_3^{S_3^A} x_4^{S_4^A} = x_1^{\{0,1\}} x_2^{\{0,1\} \cap (\neg \{1\})} x_3^{\{0\}} x_4^{\{0,1\}} = x_1^{\{0,1\}} x_2^{\{0\}} x_3^{\{0\}} x_4^{\{0,1\}} = \bar{x}_2 \bar{x}_3$$

$$x_1^{S_1^A} x_2^{S_2^A} x_3^{S_3^A} x_4^{S_4^A \cap (\neg S_4^B)} = x_1^{\{0,1\}} x_2^{\{0,1\}} x_3^{\{0\}} x_4^{\{0,1\} \cap (\neg \{1\})} = x_1^{\{0,1\}} x_2^{\{0,1\}} x_3^{\{0\}} x_4^{\{0\}} = \bar{x}_3 \bar{x}_4$$

Therefore,

$$A \ \# \ B = \bar{x_3} \ \# \ x_2 x_4 = \bar{x_2} \bar{x_3} + \bar{x_3} \bar{x_4}$$

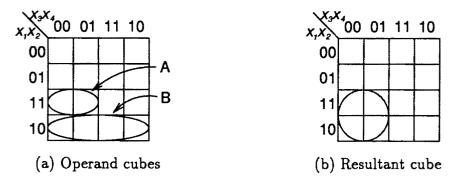

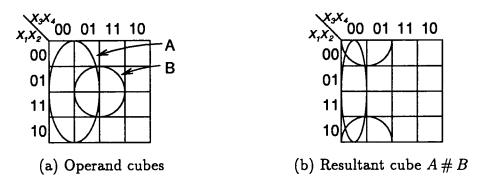

Figure 2.8: Sharp example

Remember, universal set U of possible values of a binary variable is  $\{0,1\}$ , therefore,  $\neg\{1\} = \{0\}$ . This example is also illustrated in Figure 2.8 by a Karnaugh map. The sharp operation can be used in the tautology problem [33].

#### Disjoint sharp

c]

The disjoint sharp operation on cubes A and B is defined as follows:

$$A \ \#d \ B = \begin{cases} A & \text{when } A \cap B = \emptyset \\ \\ \phi & \text{when } A \subseteq B \\ A \ \#d_{basic}B & \text{otherwise} \end{cases}$$

(2.16)

where  $A # d_{basic} B$  is defined as follows:

$$A \ \#d_{basic} \ B = \left\{ x_1^{S_1^A \cap S_1^B} \cdots x_{i-1}^{S_{i-1}^A \cap S_{i-1}^B} x_i^{S_i^A \cap (\neg S_i^B)} x_{i+1}^{S_{i+1}^A} \cdots x_n^{S_n^A} \\ \left| \text{ for such } i = 1, \dots, n, \text{ that } \neg (S_i^A \subseteq S_i^B) \right\}$$

$$(2.17)$$

For disjoint sharp operation, the *before* set operation is  $S_i^A$ , the *active* set operation is  $S_{A_i} \cap (\neg S_i^B)$ , the *after* set operation is  $S_i^A \cap S_i^B$ , and the *relation* is  $\neg (S_i^A \subseteq S_i^B)$ .

**Example 2.11.** The disjoint sharp operation A # d B, where A and B are used in Example 2.5, is calculated as follows:

Since the relation of disjoint sharp is the same as sharp, therefore variables  $x_2$

and  $x_4$  are still special variables. Thus, two resultant cubes are:

$$\begin{aligned} x_1^{S_1^A \cap S_1^B} x_2^{S_2^A \cap (\neg S_2^B)} x_3^{S_4^A} x_4^{S_4^A} &= x_1^{\{0,1\} \cap \{0,1\}} x_2^{\{0,1\} \cap (\neg \{1\})} x_3^{\{0\}} x_4^{\{0,1\}} \\ &= x_1^{\{0,1\}} x_2^{\{0\}} x_3^{\{0\}} x_4^{\{0,1\}} = \bar{x_2} \bar{x_3} \\ x_1^{S_1^A \cap S_1^B} x_2^{S_2^A \cap S_2^B} x_3^{S_4^A \cap (\neg S_4^B)} &= x_1^{\{0,1\} \cap \{0,1\}} x_2^{\{0,1\} \cap \{1\}} x_3^{\{0\} \cap \{0,1\}} x_4^{\{0,1\} \cap (\neg \{1\})} \\ &= x_1^{\{0,1\}} x_2^{\{1\}} x_3^{\{0\}} x_4^{\{0\}} = x_2 \bar{x_3} \bar{x_4} \end{aligned}$$

Therefore,

$$A \ \# d \ B = \bar{x_3} \ \# d \ x_2 x_4 = \bar{x_2} \bar{x_3} + x_2 \bar{x_3} \bar{x_4}$$

The Example 2.11 is also illustrated in Figure 2.9 by a Karnaugh map. The disjoint sharp operation can be used in tautology problem [33] and in conversions between SOP and ESOP representations.

#### 2.3.4 Summary of cube calculus operations

From the above formulas (2.3 to 2.15), it is can be seen that sequential cube operations are the most complex operations in three groups of cube operations. The sequential cube operations are defined by three set operations and one set relation. For the consistency of description, all cube operations in these three groups can be generally described by three set operations and one set relation. For simple combinational cube operations, only one set operation is used (called *before*); For complex combinational cube operations, two set operations and one set relation are used.

Figure 2.9: Disjoint sharp example

All cube operations (some of them are basic operations) described in this chapter are summarized in Table 2.1. Every row describes one cube operation. For each operation, its name, notation, set relation and three set operations (called *output functions* in the table) are listed from left to right, respectively.

| Operation      | Notation           | Relation                        | Ου                 | tput Functio              | ons               |

|----------------|--------------------|---------------------------------|--------------------|---------------------------|-------------------|

| Operation      | notation           | Relation                        | before             | active                    | after             |

| crosslink      | $A \square B$      | $S^A_i\cap S^B_i= \emptyset$    | $S_i^A$            | $S^A_i \cup S^B_i$        | $S_i^B$           |

| sharp          | $A \#_{basic} B$   | $\neg(S^A_i \subseteq S^B_i)$   | $S_i^A$            | $S_i^A \cap (\neg S_i^B)$ | $S_i^A$           |

| disjoint sharp | $A \# d_{basic} B$ | $\neg(S^A_i \subseteq S^B_i)$   | $S_i^A$            | $S^A_i \cap (\neg S^B_i)$ | $S^A_i\cap S^B_i$ |

| consensus      | A *basic B         | 1                               | $S^A_i \cap S^B_i$ | $S^A_i \cup S^B_i$        | $S^A_i\cap S^B_i$ |

| intersection   | $A \cap B$         | 1                               | $S^A_i \cap S^B_i$ | _                         | -                 |

| supercube      | $A \cup B$         | 1                               | $S^A_i \cup S^B_i$ | -                         | -                 |

| prime          | A 'B               | $S^A_i\cap S^B_i\neq \emptyset$ | $S_i^A$            | $S^A_i \cup S^B_i$        | -                 |

| cofactor       | $A \mid_{basic} B$ | $S^A_i \supseteq S^B_i$         | $S^A_i \cap S^B_i$ | U                         | -                 |

Table 2.1: Cube Calculus Operations

## 2.4 Positional Notation and Cube Operations in Positional Notation

From the above section, it can be seen that all cube operations are broken down into several set relations and set operations, and it is easy to carry out these set relations and set operations by hand. Now, the problem is how to represent sets in some way that they can be processed most efficiently by computers. Our answer to this problem is the *positional notation*.

#### 2.4.1 Positional notation

In *Positional notation*, every possible value of a variable (binary or multi-valued) is represented by one bit, 0 or 1. Thus, a *p*-valued variable is represented by a

string of p-bit; The *i*-th possible value is represented by the *i*-th bit. If the literal of this variable is true for a specific possible value (say the *i*-th possible value), the corresponding bit (the *i*-th bit) is set to 1, otherwise, it is set to 0.

For example, a four-valued variable x is represented by a string of 4-bit. Literal  $x^{\{0,2\}}$  is represented by 1010 because the first and third possible values let the literal be true.

The positional notation for binary literals is shown in table 2.2. The don't care means the variable can be either 0 or 1, so both bits are set to 1. The contradiction means that the literal is not true for any possible value of variable, so both bits are set to 0. The last two cases, don't care and contradiction, can be extended to multi-valued variables. For p-valued variable, the string of 1's (the number of 1's is p) presents a don't care, and the string of 0's (the number of 0 is p) presents a contradiction.

#### 2.4.2 Set operations in positional notation

As listed in Table 2.1, all set operations used in cube operations are based on three basic set operations: intersection, union and complement. These three set operations can be executed using bitwise operations in positional notation:

• The set intersection operation can be executed using *bitwise AND* on two strings of bits that represent two true sets of literals in positional notation.

**Example 2.12.** Assume two literals  $x^{\{0,1,2\}}$  and  $x^{\{0,2,3\}}$ , where x is a 4-valued variable. Thus two true sets of these two literals are  $\{0,1,2\}$  and  $\{0,2,3\}$ ,

| Binary literals            | Positional Notation                    |

|----------------------------|----------------------------------------|

| $ar{m{x}}$                 | $\bar{x} = x^0 = x^{10} \to 10$        |

| x                          | $x = x^1 = x^{01} \to 01$              |

| x (don't care)             | $\mathbf{x} = x^{0,1} = x^{11} \to 11$ |

| $\epsilon$ (contradiction) | $\epsilon = x^{\phi} = x^{00} \to 00$  |

Table 2.2: Positional Notation for binary literals

respectively. The intersection of these two true sets is  $\{0,1,2\} \cap \{0,2,3\} = \{0,2\}$ . In positional notation, set  $\{0,1,2\}$  is represented by 1110, and set  $\{0,2,3\}$  is represented by 1011. The bitwise AND of 1110 and 1011 is 1010, which means set  $\{0,2\}$ , and this is just what we want. Therefore, the set intersection operation is executed by bitwise AND in positional notation.

• The set union operation can be executed using *bitwise OR* on two string of bits that represent two true sets of literals in positional notation.

**Example 2.13.** Assume two literals  $x^{\{0,2\}}$  and  $x^{\{3\}}$ , where x is a 4-valued variable. Thus two true sets of these two literals are  $\{0,2\}$  and  $\{3\}$ , respectively. The union of these two true sets is  $\{0,2\} \cup \{3\} = \{0,2,3\}$ . In positional notation, set  $\{0,2\}$  is represented by 1010, and set  $\{3\}$  is represented by 0001. The bitwise OR of 1010 and 0001 is 1011, which means set  $\{0,2,3\}$ , and this is just what we want. Therefore, the set union operation is executed by bitwise OR in positional notation.

• The set complement operation can be executed using *bitwise NOT* on the string of bits that represents the true set of literal in positional notation.

**Example 2.14.** Assume a literal  $x^{\{0,2\}}$ , where x is a 4-valued variables. Thus the true sets of the literal is  $\{0,2\}$ . The complement of the true set is  $\neg\{0,2\} = \{1,3\}$  (the  $U = \{0,1,2,3\}$  for 4-valued variable). In positional notation, set  $\{0,2\}$  is represented by 1010. The bitwise NOT of 1010 is 0101, which means set  $\{1,3\}$ , and this is just what we want. Therefore, the set complement operation is executed by bitwise NOT in positional notation.

All other set operations can be done by combining these three basic set operations.

**Example 2.15.** Assume two literals  $S^A = x^{\{0,2\}}$  and  $S^B = x^{\{2,3\}}$ , where x is a 4-valued variables. Thus two true sets of these two literals are  $S^A = \{0,2\}$  and  $S^B = \{2,3\}$ , respectively. The set operation is:

$S^A \cap (\neg S^B) = 1010 \ AND \ (NOT \ 0011) = 1010 \ AND \ 1100 = 1000$ where AND and OR are bitwise operations. The result 1000 represents set  $\{0\}$ , which is correct result. This kind of set operation is called *set difference*, and is used in sharp and disjoint sharp cube operations.

#### 2.4.3 Set relations in positional notation

The result of set relation is *true* or *false* and can be represented by one bit, 1 presents *true* and 0 presents *false*. The set relation can not be done by bitwise function because it is the function of all bits of two operand sets in positional notation.

Set relation is broken down into two parts in positional notation, partial relation and relation type. The partial relation determines whether or not a pair of the same possible value of two literals satisfy the relation "locally". The relation type determines the method of combining partial relations.

Assuming there are two literals  $x^A$  and  $x^B$ , where x is p-valued variable x, A is positional notation of true set of literal  $x^A$ , and  $A = [a_0, a_2, \ldots, a_{p-1}]$ , where  $a_i$ presents the (i + 1)-th possible value of the literal (Note: the possible value starts with 0, ends with p - 1), and  $a_i \in \{0, 1\}$ . Similarly,  $B = [b_0, b_1, \ldots, b_{p-1}]$ , where  $b_i \in \{0, 1\}$ .

For the crosslink operation, the set relation is  $S^A \cap S^B = \emptyset$ . Thus partial relation is  $a_i \cdot b_i = 0$ , or  $\overline{a_i} + \overline{b_i} = 1$  (from De Morgan's theorem). If and only if all pairs of possible values satisfy this partial relation, then the set relation is satisfied. This can be written as:

$$relation(A, B) = (\overline{a_0} + \overline{b_0}) \cdot (\overline{a_1} + \overline{b_1}) \cdots (\overline{a_{p-1}} + \overline{b_{p-1}})$$

Therefore, the partial relation is  $\overline{a_i} + \overline{b_i} = 1$ , and the relation type of crosslink operation is AND type because AND function is used to combining all partial relations.

An example of OR type relation is the one used in the sharp operation, where the relation is  $\neg(S^A \subseteq S^B)$ . Thus partial relation is  $\neg(A_i \subseteq B_i)$ , where  $A_i$  is the subset of the true set  $S^A$ . If the set  $S^A$  includes the possible value i - 1, then the set  $A_i$  has one element that is the possible value i - 1 and is represented by  $a_i = 1$ ; otherwise, the set  $A_i$  is an empty set and is represented by  $a_i = 0$ . It can be seen that  $a_i$  is the *i*-th bit of the bit string that represents the set  $S^A$  in positional notation. The same thing is with  $B_i$  and  $b_i$ .

| $a_i$ | $b_i$ | $A_i \subseteq B_i$ | $\neg (A_i \subseteq B_i)$ | $a_i \cdot \overline{b_i}$ |

|-------|-------|---------------------|----------------------------|----------------------------|

| 0     | 0     | 1                   | 0                          | 0                          |

| 0     | 1     | 1                   | 0                          | 0                          |

| 1     | 0     | 0                   | 1                          | 1                          |

| 1     | 1     | 1                   | 0                          | 0                          |

Table 2.3: The partial relation of sharp operation

Table 2.3 shows how to find the partial relation function for the sharp operation. The first column shows two bits  $a_i$  and  $b_i$ . The next two columns show the value of the negated partial relation and the partial relation itself, the last column shows the bitwise function used to determine the partial relation. In the first two rows,  $a_i = 0$  means that the set  $A_i$  is an empty set, and it is subset of all sets, thus  $A_i \subseteq B_i$  are 1's (true). In the third row,  $a_i = 1$  means that the set  $A_i$  includes one element that is possible value i - 1, and  $b_i = 0$  means that the set  $B_i$  is an empty set, thus  $A_i \subseteq B_i$  is 0 (false). In the fourth row,  $a_i = b_i = 1$  means that the sets  $A_i$ and  $B_i$  include one same element that is possible value i - 1, thus sets  $A_i$  and  $B_i$ are equal, and  $A_i \subseteq B_i$  is 1 (true). Therefore, the set relation of sharp operation can be determined by:

$$relation(A,B) = (a_0 \cdot \overline{b_0}) + (a_1 \cdot \overline{b_1}) + \ldots + (a_{p-1} \cdot \overline{b_{p-1}})$$

where the partial relation function is  $a_i \cdot \overline{b_i}$ , and the relation type is OR.

### 2.4.4 Summary of cube operations in positional notation

From the above discussion, before, active, after set operations and partial (set) relation can be defined by bitwise functions on bits. Therefore, all cube operations

(some of them are basic operations) can be completely specified by 4 bitwise functions and *relation type*. Table 2.4 summarizes all cube operations described in this chapter in bitwise functions and relation type.

|                |                      | Rela                    | tion     | <b>Output Function</b> |                     |                 |

|----------------|----------------------|-------------------------|----------|------------------------|---------------------|-----------------|

| Operation      | Notation             | partial                 | relation | before                 | active              | after           |

|                |                      | relation                | type     | 5                      |                     |                 |

| crosslink      | $A \Box B$           | $\bar{a_i} + \bar{b_i}$ | and      | a <sub>i</sub>         | $a_i + b_i$         | bi              |

| sharp          | $A \#_{basic} B$     | $a_i \cdot \bar{b_i}$   | or       | a <sub>i</sub>         | $a_i \cdot ar{b_i}$ | $a_i$           |

| disjoint sharp | $A \ \# d_{basic} B$ | $a_i \cdot \bar{b_i}$   | or       | ai                     | $a_i \cdot ar{b_i}$ | $a_i \cdot b_i$ |

| consensus      | $A *_{basic} B$      | 1                       | and      | $a_i \cdot b_i$        | $a_i + b_i$         | $a_i \cdot b_i$ |

| intersection   | $A \cap B$           | -                       | _        | $a_i \cdot b_i$        | -                   | -               |

| super cube     | $A \cup B$           | -                       | -        | $a_i + b_i$            | _                   | _               |

| prime          | A 'B                 | $a_i \cdot b_i$         | or       | ai                     | $a_i + b_i$         | -               |

| cofactor       | $A _{basic}B$        | $a_i + ar{b_i}$         | and      | $a_i \cdot b_i$        | 1                   | -               |

Table 2.4: Cube Calculus Operations in bitwise function and relation type

The following examples show the entire procedure to carry out cube calculus operations in positional notation.

**Example 2.16.** Variables  $x_1$ ,  $x_2$  and  $x_3$  all have 3 possible values, thus the sets of possible values are  $P_1 = P_2 = P_3 = \{0, 1, 2\}$ . A cube of  $x_1^{\{0,1\}} x_2^{\{2\}} x_3^{\{0,1,2\}}$  is denoted as  $x_1^{110} x_2^{010} x_3^{111}$  in positional notation; and it is written as [110-010-111] for simplifying.

**Example 2.17.** Assuming cubes  $A = x_1x_2$  and  $B = x_2x_3\bar{x_4}$ , where variables  $x_1$ ,  $x_2$ ,  $x_3$  and  $x_4$  are binary, the intersection of cubes A and B follows:

$$A \cap B = x_1 x_2 \cap x_2 x_3 \bar{x_4}$$

= $x_1^{\{1\}} x_2^{\{1\}} x_3^{\{0,1\}} x_4^{\{0,1\}} \cap x_1^{\{0,1\}} x_2^{\{1\}} x_3^{\{1\}} x_4^{\{0\}}$

= $x_1^{[01]} x_2^{[01]} x_3^{[11]} x_4^{[11]} \cap x_1^{[11]} x_2^{[01]} x_3^{[01]} x_4^{[10]}$

$$= x_1^{[01]\cdot[11]} x_2^{[01]\cdot[01]} x_3^{[11]\cdot[01]} x_4^{[11]\cdot[10]}$$

$$= x_1^{[01]} x_2^{[01]} x_3^{[01]} x_4^{[10]}$$

$$= x_1 x_2 x_3 \bar{x_4}$$

where  $\cdot$  is bitwise AND operation.

When two opposite literals are multiplied, if the contradiction is generated from the bitwise operation, then there is no resultant cube, which means that there is no intersection between two operand cubes.

**Example 2.18.** Assuming cubes A = ab and  $B = a\overline{b}$ , where a and b are binary variables. Then the intersection of cubes A and B is:

$ab \cdot a\overline{b} = [01 - 01] \cdot [01 - 10] = [01 - \underbrace{00}_{\epsilon}]$

where 00 is a contradiction symbol for a binary variable, and the contradiction is denoted by  $\epsilon$  (see Table 2.2).

Example 2.19. Redo the crosslink operation shown in Example 2.8 in positional notation as follows:

$$A = \bar{x_1}\bar{x_3} = x_1^{\{0\}}x_2^{\{0,1\}}x_3^{\{0,1\}}x_4^{\{0,1\}} = \begin{bmatrix} a_{1,0}a_{1,1} & a_{2,0}a_{2,1} & a_{3,0}a_{3,1} & a_{4,0}a_{4,1} \\ 1 & 0 & -1 & 1 & -1 & 0 & -1 & 1 \end{bmatrix}$$

$$B = x_1x_3 = x_1^{\{1\}}x_2^{\{0,1\}}x_3^{\{1\}}x_4^{\{0,1\}} = \begin{bmatrix} b_{1,0}b_{1,1} & b_{2,0}b_{2,1} & b_{3,0}b_{3,1} & b_{4,0}b_{4,1} \\ 0 & 1 & -1 & 1 & -0 & 1 & -1 & 1 \end{bmatrix}$$

where the header of bit is the name of the bit. The subscript of bit name has two parts separated by comma (','), the first part represents the index of the variable, and the second part represents the possible value. This notation will also be used in the next chapter. Because:

$$\begin{aligned} relation(A_1, B_1) &= (\overline{a_{1,0}} + \overline{b_{1,0}}) \cdot (\overline{a_{1,1}} + \overline{b_{1,1}}) = (\overline{1} + \overline{0}) \cdot (\overline{0} + \overline{1}) = 1\\ relation(A_2, B_2) &= (\overline{a_{2,0}} + \overline{b_{2,0}}) \cdot (\overline{a_{2,1}} + \overline{b_{2,1}}) = (\overline{1} + \overline{1}) \cdot (\overline{1} + \overline{1}) = 0\\ relation(A_3, B_3) &= (\overline{a_{3,0}} + \overline{b_{3,0}}) \cdot (\overline{a_{3,1}} + \overline{b_{3,1}}) = (\overline{1} + \overline{0}) \cdot (\overline{0} + \overline{1}) = 1\\ relation(A_4, B_4) &= (\overline{a_{4,0}} + \overline{b_{4,0}}) \cdot (\overline{a_{4,1}} + \overline{b_{4,1}}) = (\overline{1} + \overline{1}) \cdot (\overline{1} + \overline{1}) = 0\\ the variables x_1 and x_3 are special variables. The two resultant cubes are:\\ x_1^{A_1 + B_1} x_2^{A_2} x_3^{A_3} x_4^{A_4} &= x_1^{[10] + [01]} x_2^{[11]} x_3^{[10]} x_4^{[11]} = x_1^{[11]} x_2^{[11]} x_3^{[10]} x_4^{[11]} = \overline{x_3}\\ x_1^{B_1} x_2^{B_2} x_3^{A_3 + B_3} x_4^{A_4} &= x_1^{[01]} x_2^{[11]} x_3^{[10] + [01]} x_4^{[11]} = x_1^{[01]} x_2^{[11]} x_3^{[11]} x_4^{[11]} = x_1 \end{aligned}$$

where '+' is the bitwise OR operation.

# CHAPTER 3

# **Cube Calculus Machine**

The software-based approach is the simplest and cheapest way to realize cube calculus operations. Since the algorithm of a sequential cube calculus operation involves several-level nested loops, it leads to poor performance on general purpose computers. In some applications, such as logic minimization systems, or logic-based machine learning systems, there are so many cube calculus operations, that the software-based approach makes those applications unacceptable for practical sized problems due to poor performance. For speeding up the cube calculus operations, the cube calculus machine was invented.

# 3.1 Formalism for main algorithm for cube calculus operation

The architecture of the Cube Calculus Machine (CCM) results from an attempt to optimize the execution of the most complex cube operation, sequential cube calculus operations, like crosslink and sharp. Almost all cube calculus operations have two operand cubes described in Formulas 2.3 and 2.4. Re-write these two operand cubes in positional notation as:

$$A = x_1^{A_1} x_2^{A_2} \cdots x_i^{A_i} \cdots x_n^{A_n}$$

$$B = x_1^{B_1} x_2^{B_2} \cdots x_i^{B_i} \cdots x_n^{B_n}$$

(3.1)

where  $A_i = (a_{i,1}, a_{i,2}, \dots, a_{i,m}, \dots, a_{i,p_i})$ , which is the true set of literal  $x_i^{A_i}$  in position notation. For each bit  $a_{i,m}$  from  $A_i$ ,  $a_{i,m} \in \{0, 1\}$ . The bit  $a_{i,m}$  represents the *m*-th possible value of the *i*-th variable. Similarly,  $B_i = (b_{i,1}, b_{i,2}, \dots, b_{i,m}, \dots, b_{i,p_i})$

and for each bit  $b_{i,m}$  from  $B_i$ ,  $b_{i,m} \in \{0,1\}$ . Example 2.18 shows how to use this notation.

The sequential cube operations are generally described by Equation 2.12. Rewrite the equation in positional notation as:

$$A(op) B = \vec{C} \tag{3.2}$$

where resultant array of cubes  $\vec{C}$  is:

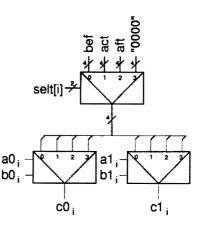

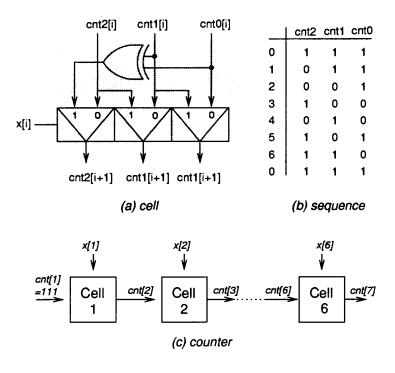

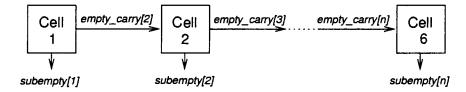

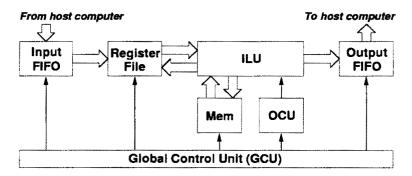

$$\vec{C} = \left\{ X_{1}^{aft(A_{1},B_{1})} \cdots X_{i-1}^{aft(A_{i-1},B_{i-1})} X_{i}^{act(A_{i},B_{i})} X_{i+1}^{bef(A_{i+1},B_{i+1})} \cdots X_{n}^{bef(A_{n},B_{n})} \right.$$