# **Calhoun: The NPS Institutional Archive**

# **DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2023-03

# DESIGN AND IMPLEMENTATION OF A DATA ACQUISITION SYSTEM WITH IN-SITU PICOAMMETER FOR AUTOMATED RELIABILITY TESTING

# Ramos, Richard A.

Monterey, CA; Naval Postgraduate School

https://hdl.handle.net/10945/72044

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

# THESIS

# DESIGN AND IMPLEMENTATION OF A DATA ACQUISITION SYSTEM WITH IN-SITU PICOAMMETER FOR AUTOMATED RELIABILITY TESTING

by

Richard A. Ramos

March 2023

Thesis Advisor: Second Reader: Todd R. Weatherford Matthew A. Porter

Approved for public release. Distribution is unlimited.

| REPORT I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                        | Fo                                                                                                                       | rm Approved OMB<br>No. 0704-0188                                                                                                                                                                                                                       |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington, DC, 20503. |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                          |                                                                                                                                                                                                                                                        |  |

| 1. AGENCY USE ONLY<br>(Leave blank)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2. REPORT DATE<br>March 2023                                                                                                                                                                                                                                                                                                                                                                                    | 3. REPORT TY                                                                                                                                                                           |                                                                                                                          | DATES COVERED<br>'s thesis                                                                                                                                                                                                                             |  |

| 4. TITLE AND SUBTITLE5. FUNDING NUMBERSDESIGN AND IMPLEMENTATION OF A DATA ACQUISITION SYSTEM<br>WITH IN-SITU PICOAMMETER FOR AUTOMATED RELIABILITY<br>TESTING5. FUNDING NUMBERS6. AUTHOR(S) Richard A. Ramos6. AUTHOR(S) Richard A. Ramos6. AUTHOR(S) Richard A. Ramos                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                          |                                                                                                                                                                                                                                                        |  |

| 7. PERFORMING ORGANI<br>Naval Postgraduate School<br>Monterey, CA 93943-5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ZATION NAME(S) AND ADDF                                                                                                                                                                                                                                                                                                                                                                                         | RESS(ES)                                                                                                                                                                               |                                                                                                                          | ORMING<br>IZATION REPORT<br>R                                                                                                                                                                                                                          |  |

| 9. SPONSORING / MONITO<br>ADDRESS(ES)<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DRING AGENCY NAME(S) AN                                                                                                                                                                                                                                                                                                                                                                                         | D                                                                                                                                                                                      | MONIT                                                                                                                    | NSORING /<br>ORING AGENCY<br>T NUMBER                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>TES</b> The views expressed in this t<br>e Department of Defense or the U.                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                        | he author a                                                                                                              | and do not reflect the                                                                                                                                                                                                                                 |  |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT       12b. DISTRIBUTION CODE         Approved for public release. Distribution is unlimited.       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                          |                                                                                                                                                                                                                                                        |  |

| as gallium nitride (GaN) and<br>silicon (Si). Understanding<br>implementation in military a<br>needed, but it is difficult an<br>modular reliability testing<br>designed to perform automa<br>with sub-nA resolution. Ne<br>diode, two GaN diodes, an<br>reverse-bias tests that were r                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>00 words)</b><br>itary has been exploring the us<br>d silicon carbide (SiC) due to t<br>the reliability of these high-p<br>systems. However, it remains t<br>id expensive to produce. This t<br>subsystem in the form of a ne<br>ted, in-situ leakage current me<br>xt, a wide sample of devices c<br>id a field effect transistor (FE<br>recorded by the system. Finally,<br>achieved leakage current resol | heir promising m<br>erformance WBG<br>o be tested becau<br>hesis looks at the<br>ovel data acquisi<br>asurements of up<br>onsisting of a res<br>T) were subjects<br>the results of the | aterial pr<br>GS device<br>use good-<br>e design a<br>tion syste<br>to four d<br>sistor, two<br>ed to var<br>use validat | operties, as compared to<br>es is paramount to their<br>quality reliability data is<br>and implementation of a<br>em. First, a system was<br>evices under test (DUT)<br>o Zener diodes, a power<br>ious voltage sweep and<br>tion tests were processed |  |

| bandgap, diode, high voltage, p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ng, GaN, gallium nitride, SiC, silic<br>power devices, leakage current, in-<br>ansimpedance amplifier, TIA, curr                                                                                                                                                                                                                                                                                                | situ measurement,                                                                                                                                                                      | low-side                                                                                                                 | 15. NUMBER OF<br>PAGES<br>113<br>16. PRICE CODE                                                                                                                                                                                                        |  |

| 17. SECURITY<br>CLASSIFICATION OF<br>REPORT<br>Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18. SECURITY<br>CLASSIFICATION OF THIS<br>PAGE<br>Unclassified                                                                                                                                                                                                                                                                                                                                                  | 19. SECURITY<br>CLASSIFICATI<br>ABSTRACT<br>Unclassified                                                                                                                               | ION OF                                                                                                                   | 20. LIMITATION OF<br>ABSTRACT<br>UU                                                                                                                                                                                                                    |  |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                        |                                                                                                                          | -<br>Standard Form 298 (Rev. 2-89)<br>rescribed by ANSI Std. 239-18                                                                                                                                                                                    |  |

Approved for public release. Distribution is unlimited.

## DESIGN AND IMPLEMENTATION OF A DATA ACQUISITION SYSTEM WITH IN-SITU PICOAMMETER FOR AUTOMATED RELIABILITY TESTING

Richard A. Ramos Captain, United States Marine Corps BS, United States Naval Academy, 2016

Submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

## NAVAL POSTGRADUATE SCHOOL March 2023

Approved by: Todd R. Weatherford Advisor

> Matthew A. Porter Second Reader

Douglas J. Fouts Chair, Department of Electrical and Computer Engineering

## ABSTRACT

In recent years, the military has been exploring the use of wide bandgap semiconductors (WBGS) such as gallium nitride (GaN) and silicon carbide (SiC) due to their promising material properties, as compared to silicon (Si). Understanding the reliability of these high-performance WBGS devices is paramount to their implementation in military systems. However, it remains to be tested because good-quality reliability data is needed, but it is difficult and expensive to produce. This thesis looks at the design and implementation of a modular reliability testing subsystem in the form of a novel data acquisition system. First, a system was designed to perform automated, in-situ leakage current measurements of up to four devices under test (DUT) with sub-nA resolution. Next, a wide sample of devices consisting of a resistor, two Zener diodes, a power diode, two GaN diodes, and a field effect transistor (FET) were subjected to various voltage sweep and reverse-bias tests that were recorded by the system. Finally, the results of those validation tests were processed and analyzed. The system achieved leakage current resolutions below 100 pA, demonstrating its ability to measure various devices.

# **TABLE OF CONTENTS**

| I.   | INT | RODUCTION                                               | 1  |

|------|-----|---------------------------------------------------------|----|

|      | A.  | MOTIVATION                                              | 1  |

|      | B.  | PROBLEM STATEMENT AND RESEARCH OBJECTIVES               | 4  |

|      | C.  | RELATED WORK                                            | 5  |

|      | D.  | THESIS ORGANIZATION                                     | 6  |

| II.  | BAC | CKGROUND                                                | 7  |

|      | A.  | MATERIAL PROPERTIES OF WBGS                             | 7  |

|      |     | 1. Baliga's Figure of Merit                             | 8  |

|      |     | 2. PN Diode Leakage Current                             |    |

|      | B.  | OPERATIONAL AMPLIFIERS                                  | 10 |

|      |     | 1. Ideal Closed-Loop Gain (Inverting and Non-inverting) | 12 |

|      |     | 2. Non-ideal Op-amp Model                               | 14 |

|      |     | 3. Frequency Response and Bandwidth                     | 15 |

|      |     | 4. Closed Loop Op-amp Circuit Stability                 | 16 |

|      | C.  | TRANSIMPEDANCE AMPLIFIER CONFIGURATION                  |    |

|      |     | 1. TIA Stability Analysis                               | 21 |

|      |     | 2. TIA Noise Analysis                                   | 28 |

|      |     | 3. Calculating the Total RMS Noise Voltage              | 32 |

| III. | SYS | TEM DESIGN                                              | 35 |

|      | A.  | SYSTEM OVERVIEW                                         | 35 |

|      | B.  | DESIGN OF LEAKAGE MEASUREMENT BOARD                     |    |

|      |     | 1. TIA Component Selection                              | 36 |

|      |     | 2. Noise Analysis and Reduction                         |    |

|      |     | 3. Circuit Design Prototyping and PCB Design            |    |

|      | C.  | DESIGN OF DAQ BOARD                                     |    |

|      |     | 1. Component Selection                                  |    |

|      |     | 2. Configuration and Control of ADC                     |    |

|      |     | 3. DAQ PCB Layout and PCB Design                        |    |

|      | D.  | MBED MICROCONTROLLER                                    |    |

|      |     | 1. SPI Interface with AD974                             | 57 |

|      |     | 2. Programming of Microcontroller                       | 58 |

| IV.  | SYS | TEM TESTING AND DATA ANALYSIS                           | 59 |

|      | А.  | SYSTEM TESTING                                          | 59 |

|      |     | vii                                                     |    |

|      | В.     | SYS     | TEM CALIBRATION               | 61 |

|------|--------|---------|-------------------------------|----|

|      | C.     | SYS     | TEM VALIDATION                | 62 |

|      |        | 1.      | Resistor Tests                | 63 |

|      |        | 2.      | Zener Diode Tests             | 64 |

|      |        | 3.      | Si Power Diode Test           | 69 |

|      |        | 4.      | GaN Diode Tests               |    |

|      |        | 5.      | IRF540Z Power FET Test        |    |

| V.   | CON    | ICLUS   | SION AND FUTURE WORK          | 81 |

|      | A.     | CON     | NCLUSION                      | 81 |

|      | B.     | FUT     | URE WORK                      | 82 |

| APP  | ENDIX  | X A. AI | OC CONTROL BOARD MBED PROGRAM | 83 |

| APP  | ENDIX  | K B. LA | ABVIEW PROGRAMS               |    |

| LIST | Г OF R | EFERI   | ENCES                         | 89 |

| INIT | FIAL D | ISTRI   | BUTION LIST                   |    |

# **LIST OF FIGURES**

| Navy Marine Expeditionary Ship Interdiction System Source: [2]           | 1                                                              |

|--------------------------------------------------------------------------|----------------------------------------------------------------|

| Applications of GaN and SiC vs. Si. Source: [8]                          | 3                                                              |

| R <sub>on,sp</sub> vs. V <sub>br</sub> of Other Materials. Source: [3]   | 9                                                              |

| Circuit Symbol for an Op-amp. Source: [17]1                              | 1                                                              |

| Inverting Closed-Loop Configuration. Source: [18]12                      | 2                                                              |

| Non-Inverting Closed-Loop Configuration. Source: [18]                    | 3                                                              |

| Non-ideal Inverting Op-amp Model. Source: [17]                           | 4                                                              |

| Open-Loop Gain of Non-ideal Op-Amp. Source: [18]10                       | 5                                                              |

| Block Diagram Model of Closed-Loop Gain. Source: [18]17                  | 7                                                              |

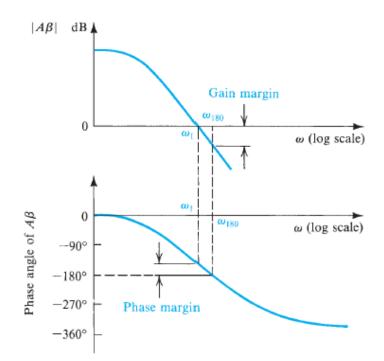

| Illustration of Gain Margin and Phase Margin. Source: [18]               | 3                                                              |

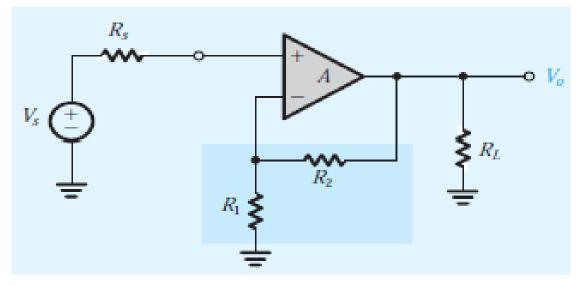

| Example of Non-inverting Feedback Amplifier. Source: [18] 19             | 9                                                              |

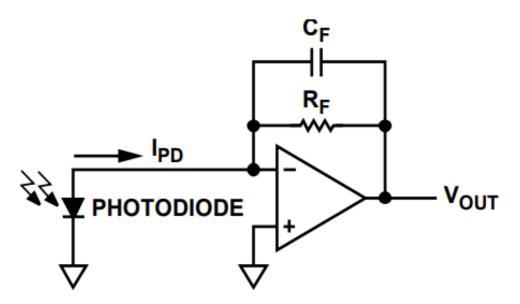

| TIA with Photodiode. Source: [19]20                                      | )                                                              |

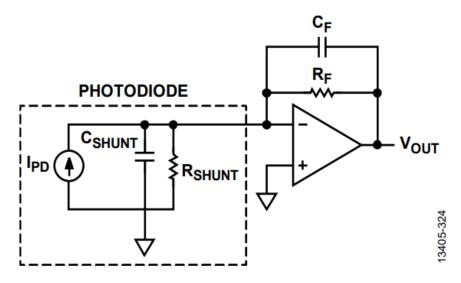

| TIA with Equivalent Photodiode Model. Source: [19]22                     | 1                                                              |

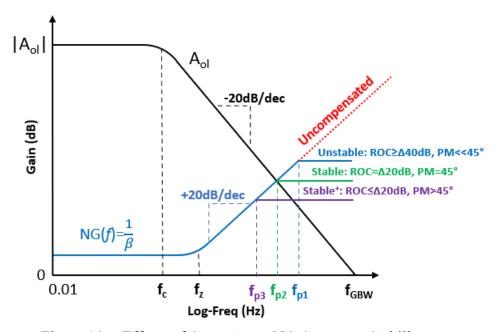

| Effects of Cf on Aol vs. NG Crossover Stability                          | 5                                                              |

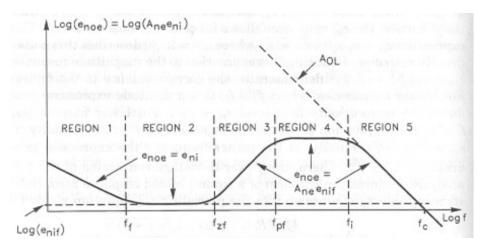

| TIA Noise Model. Source: [20]                                            | 9                                                              |

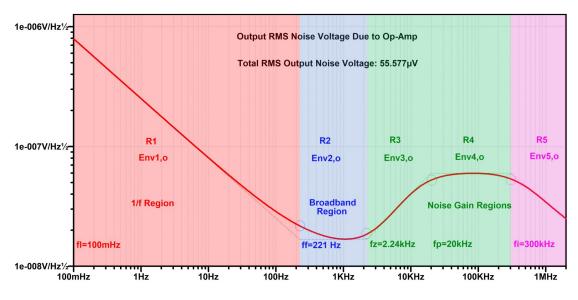

| Frequency Response of e <sub>nv,in</sub> by Region. Source: [20]         | 1                                                              |

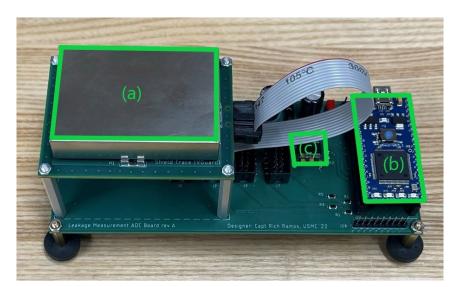

| LoSPRaDC: (a) LMB, (b) Mbed, (c) DAQ Board                               | 5                                                              |

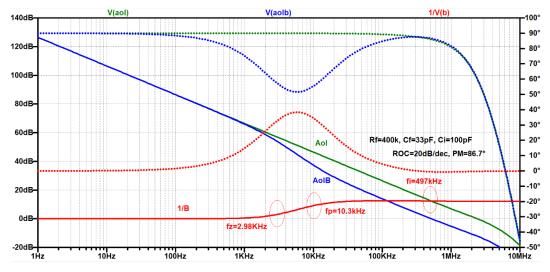

| LTSpice Stability plot for Range 1, C <sub>i</sub> =100 pF               | 7                                                              |

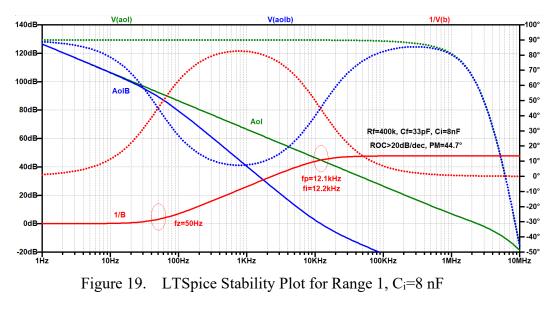

| LTSpice Stability Plot for Range 1, C <sub>i</sub> =8 nF                 | 7                                                              |

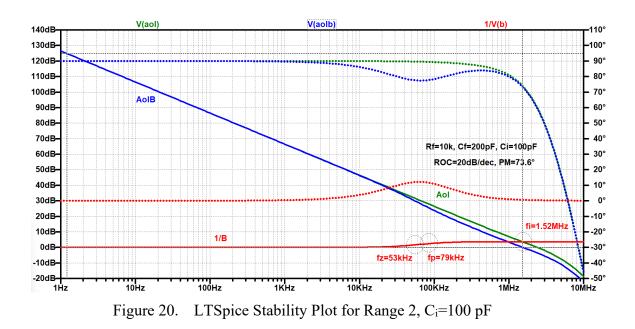

| LTSpice Stability Plot for Range 2, C <sub>i</sub> =100 pF               | 3                                                              |

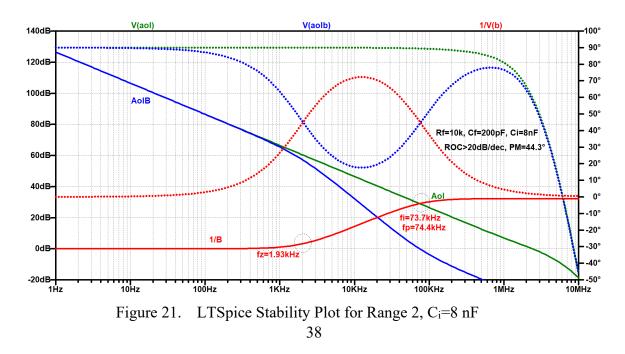

| LTSpice Stability Plot for Range 2, C <sub>i</sub> =8 nF                 | 3                                                              |

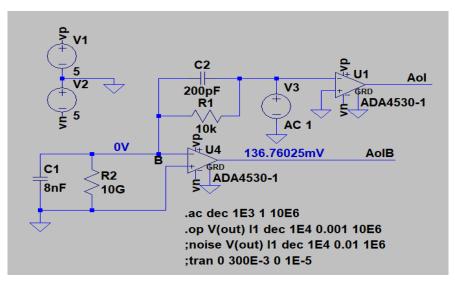

| LTSpice Circuit for Plotting $A_{ol}$ , $A_{ol}\beta$ , and $\beta^{-1}$ | 9                                                              |

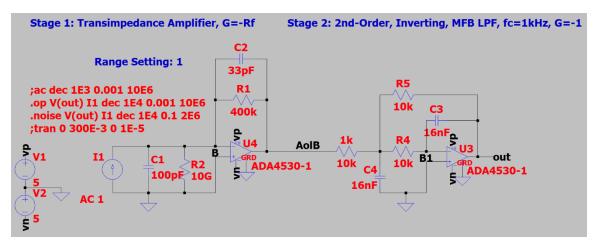

| LTSpice Noise Model for Stages 1 and 2 of Range 1 40                     | )                                                              |

|                                                                          | Navy Marine Expeditionary Ship Interdiction System Source: [2] |

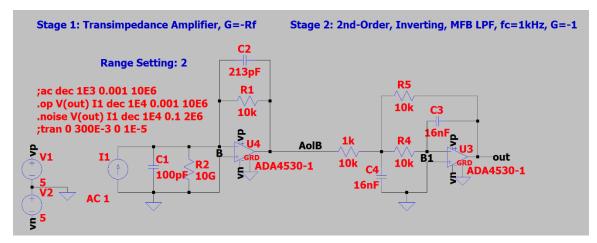

| Figure 24. | LTSpice Noise Model for Stages 1 and 2 of Range 2                                    | 40 |

|------------|--------------------------------------------------------------------------------------|----|

| Figure 25. | LTSpice E <sub>nvR</sub> Regions of ADA4530-1                                        | 41 |

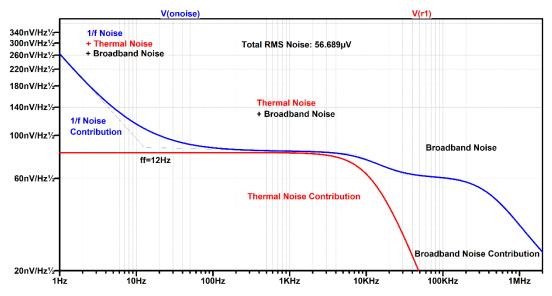

| Figure 26. | LTSpice Noise Analysis of Stage 1 TIA, Range 1, C <sub>i</sub> =100 pF               | 42 |

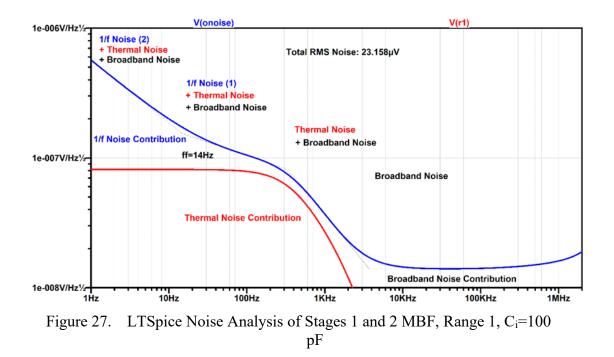

| Figure 27. | LTSpice Noise Analysis of Stages 1 and 2 MBF, Range 1, $C_i$ =100 pF                 | 42 |

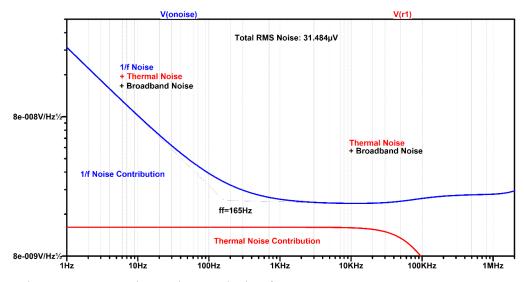

| Figure 28. | LTSpice Noise Analysis of Stage 1 TIA, Range 2, Ci=100 pF                            | 43 |

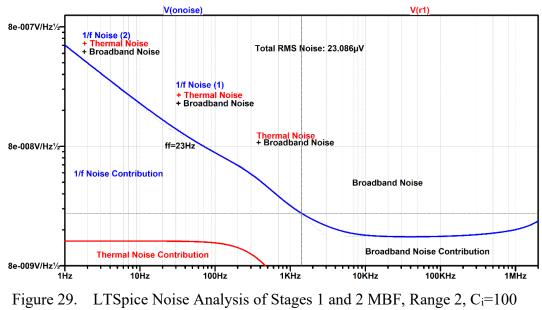

| Figure 29. | LTSpice Noise Analysis of Stages 1 and 2 MBF, Range 2, C <sub>i</sub> =100 pF        | 43 |

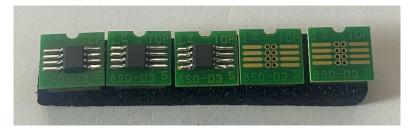

| Figure 30. | SOIC-8 SMT to DIP PCB with ADA4530-1                                                 | 44 |

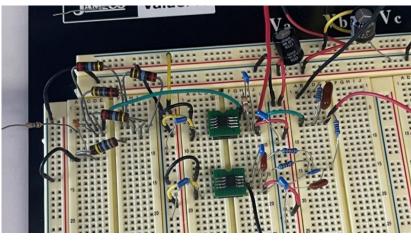

| Figure 31. | Prototype of LMB                                                                     | 44 |

| Figure 32. | Stage 1 dc Operation Validation Test                                                 | 45 |

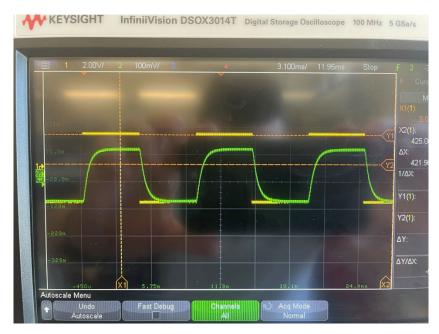

| Figure 33. | Single Pulse Transient Response of Prototype Circuit                                 | 46 |

| Figure 34. | Multi Pulse Transient Response of Prototype Circuit                                  | 46 |

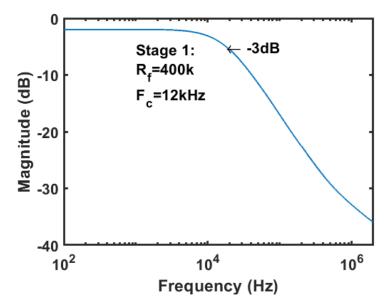

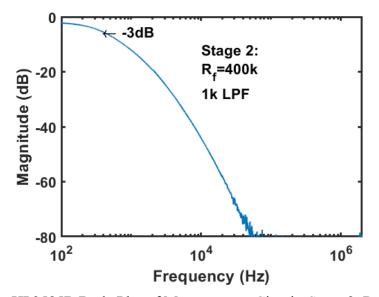

| Figure 35. | HP3585B Bode Plot of Measurement Circuit: Stage 1, Range 1                           | 47 |

| Figure 36. | HP3585B Bode Plot of Measurement Circuit: Stage 2, Range 1                           | 47 |

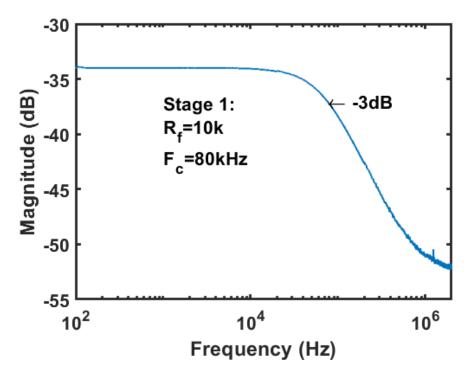

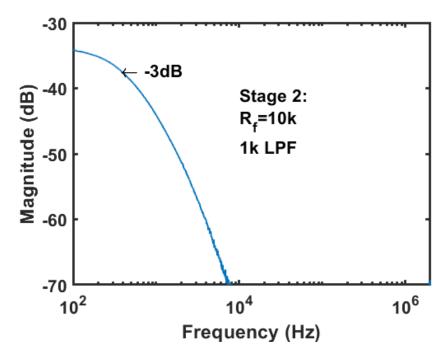

| Figure 37. | HP3585B Bode Plot of Measurement Circuit: Stage 1, Range 2                           | 48 |

| Figure 38. | HP3585B Bode Plot of Measurement Circuit: Stage 2, Range 2                           | 48 |

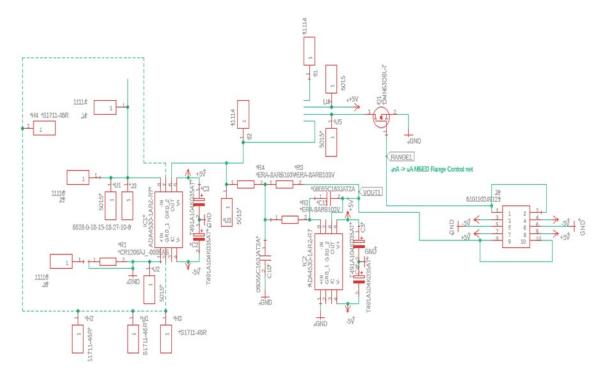

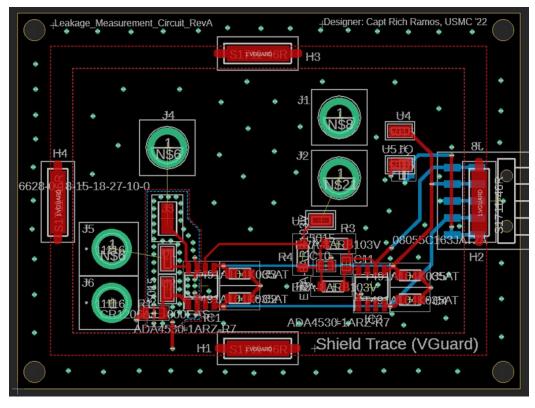

| Figure 39. | EAGLE LMB Schematic                                                                  | 49 |

| Figure 40. | EAGLE LMB Layout                                                                     | 50 |

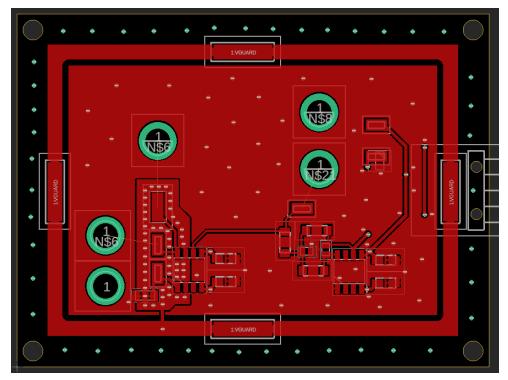

| Figure 41. | Layer 1 of LMB                                                                       | 51 |

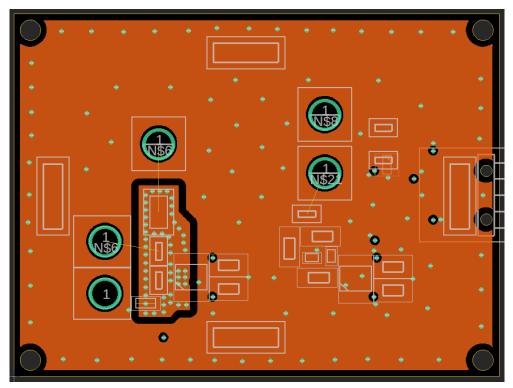

| Figure 42. | Layer 3 of LMB                                                                       | 51 |

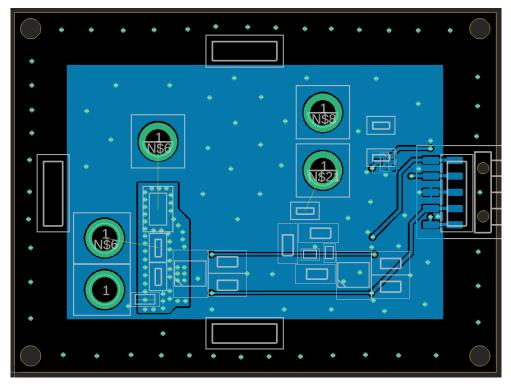

| Figure 43. | Layer 4 of LMB                                                                       | 52 |

| Figure 44. | LMB: (a.1) TIA, (a.2) LPF, (b) $C_{f1}   R_{f1}$ , (c) $C_{f2}   R_{f2}$ , (d) Relay | 53 |

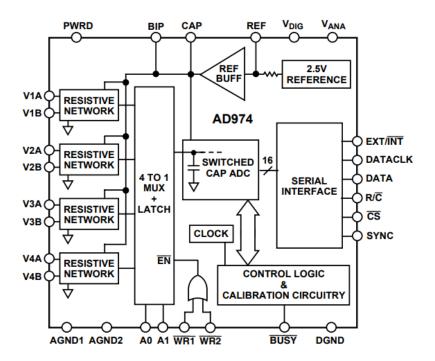

| Figure 45. | Functional Block Diagram of AD974. Source: [28]                                      | 54 |

| Figure 46. | AD974, A1 and A0 Truth Table                                                         | 54 |

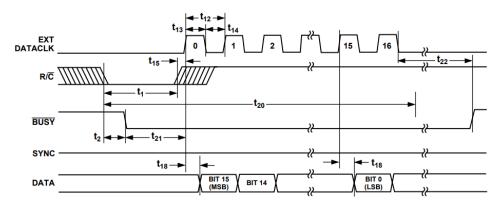

| Figure 47. | AD974 Timing Diagram for Data Conversion. Source: [28]                                         | 55 |

|------------|------------------------------------------------------------------------------------------------|----|

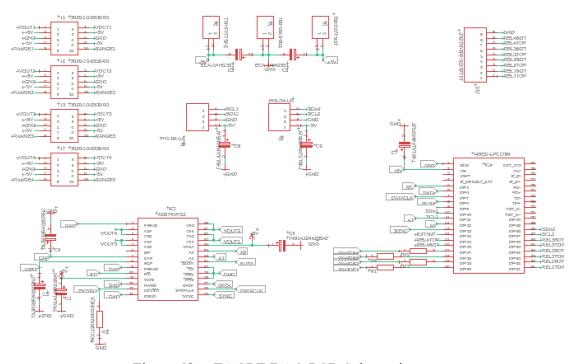

| Figure 48. | EAGLE DAQ PCB Schematic                                                                        | 56 |

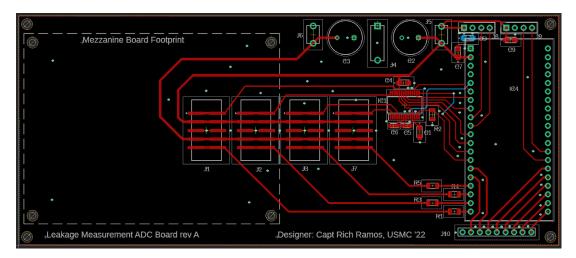

| Figure 49. | EAGLE DAQ PCB Layout                                                                           | 57 |

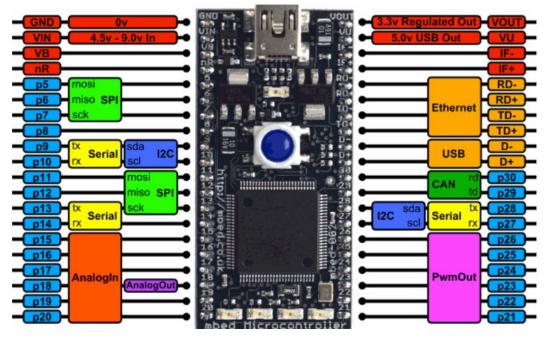

| Figure 50. | Mbed LPC1768 Pinout Diagram. Source: [29]                                                      | 58 |

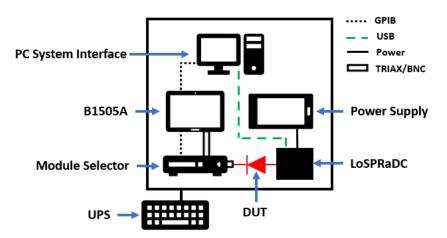

| Figure 51. | Block Diagram of LoSPRaDC Testing System                                                       | 59 |

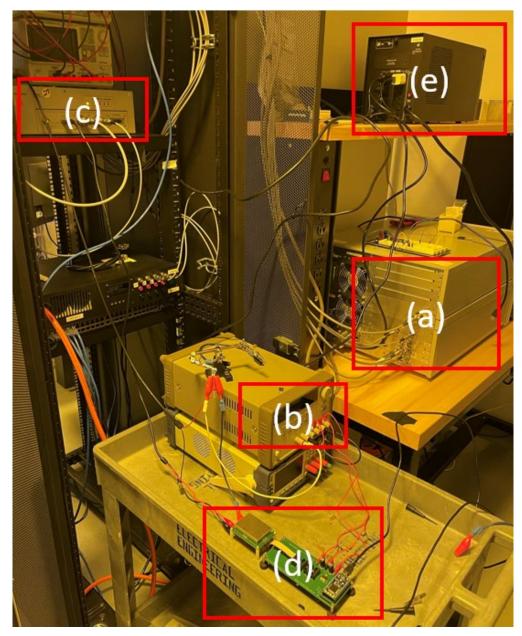

| Figure 52. | Test System Setup: (a) B1505A, (b) Power Supply, (c) Module<br>Selector, (d) LoSPRaDC, (e) UPS | 60 |

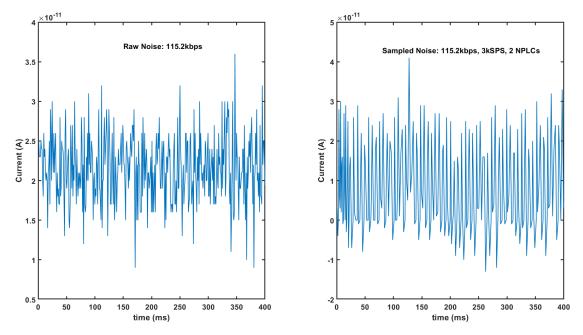

| Figure 53. | Noise Samples Collected from LoSPRaDC                                                          | 61 |

| Figure 54. | R <sub>f</sub> Calibration Example                                                             | 62 |

| Figure 55. | 400 kΩ Resistor IV Plots, 3 kSPS                                                               | 63 |

| Figure 56. | 400 kΩ Resistor IV Plots, 6 kSPS                                                               | 63 |

| Figure 57. | Full 400 k $\Omega$ Resistor IV Plots of All Sampling Ranges                                   | 64 |

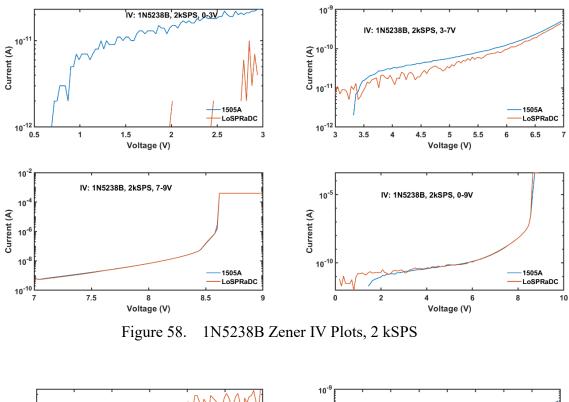

| Figure 58. | 1N5238B Zener IV Plots, 2 kSPS                                                                 | 65 |

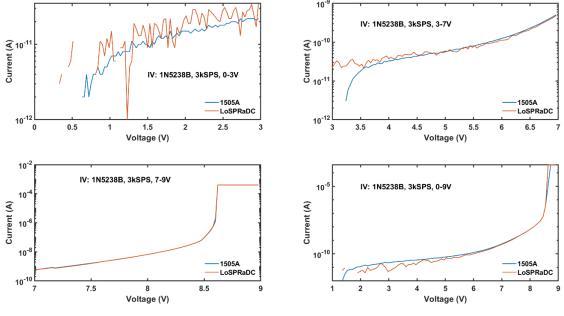

| Figure 59. | 1N5238B Zener IV Plots, 3 kSPS                                                                 | 65 |

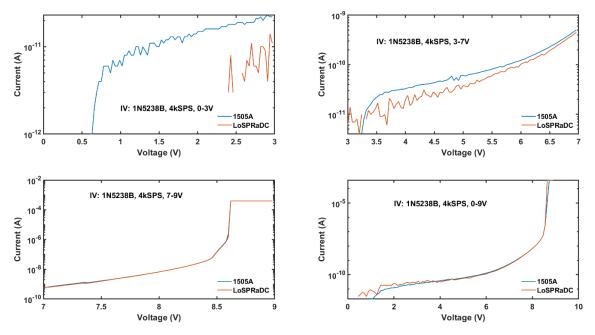

| Figure 60. | 1N5238B Zener IV Plots, 4kSPS                                                                  | 66 |

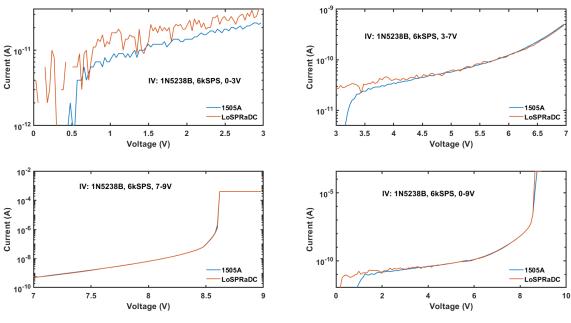

| Figure 61. | 1N5238B Zener IV Plots, 6 kSPS                                                                 | 66 |

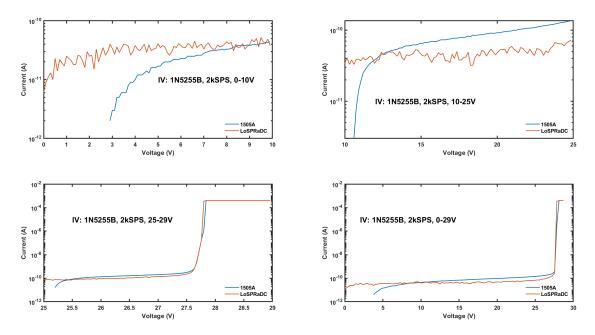

| Figure 62. | 1N5255B Zener IV Plots, 2 kSPS                                                                 | 67 |

| Figure 63. | 1N5255B Zener IV Plots, 3 kSPS                                                                 | 68 |

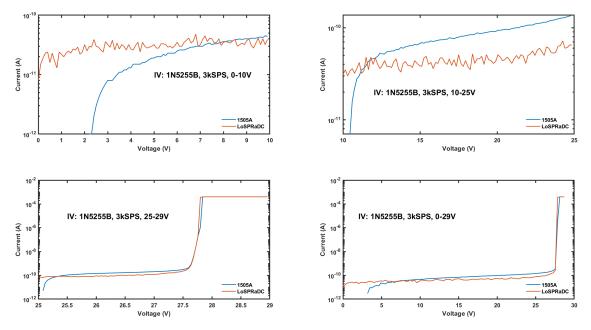

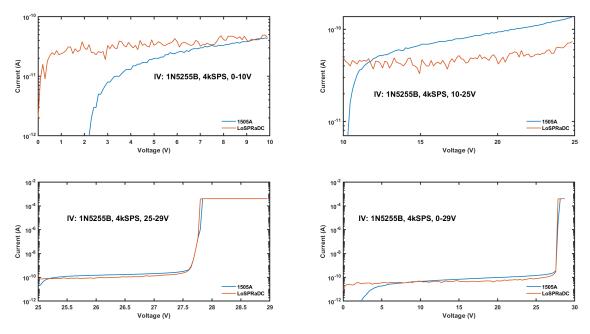

| Figure 64. | 1N5255B Zener IV Plots, 4 kSPS                                                                 | 68 |

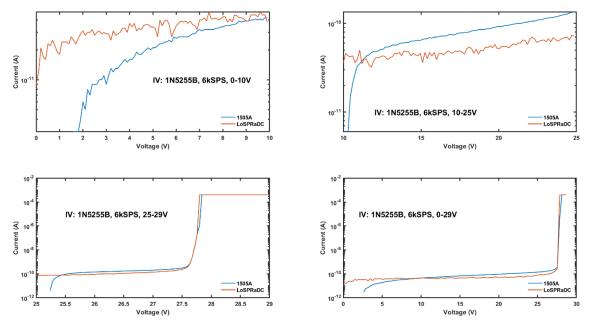

| Figure 65. | 1N5255B Zener IV Plots, 6 kSPS                                                                 | 69 |

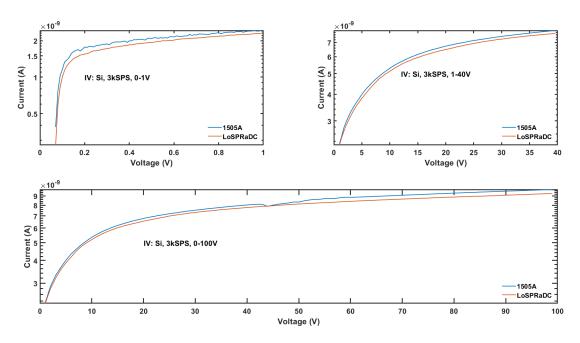

| Figure 66. | Si IV Plots, 3 kSPS                                                                            | 70 |

| Figure 67. | Si IV Plots, 4 kSPS                                                                            | 70 |

| Figure 68. | Si IV Plots, 6 kSPS                                                                            | 71 |

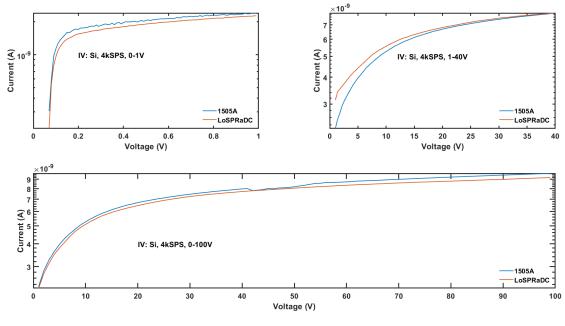

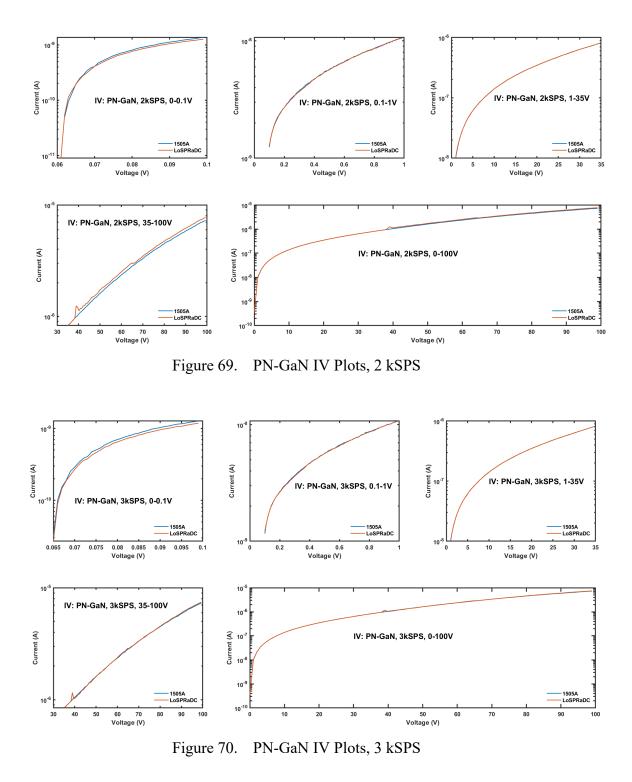

| Figure 69. | PN-GaN IV Plots, 2 kSPS                                                                        | 72 |

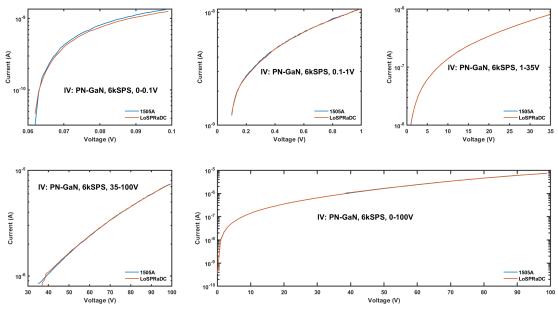

| Figure 70. | PN-GaN IV Plots, 3 kSPS                                                                        | 72 |

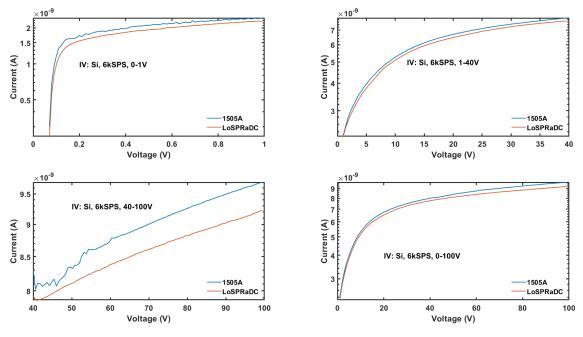

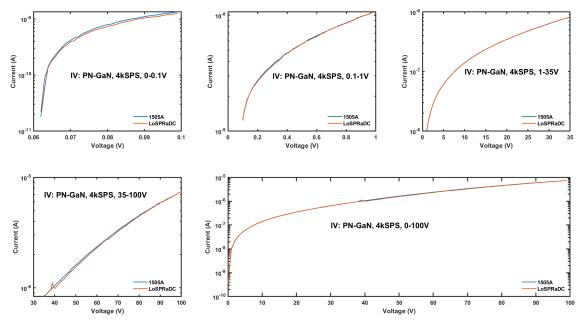

| Figure 71. | PN-GaN IV Plots, 4 kSPS                    | 73 |

|------------|--------------------------------------------|----|

| Figure 72. | PN-GaN IV Plots, 6 kSPS                    | 73 |

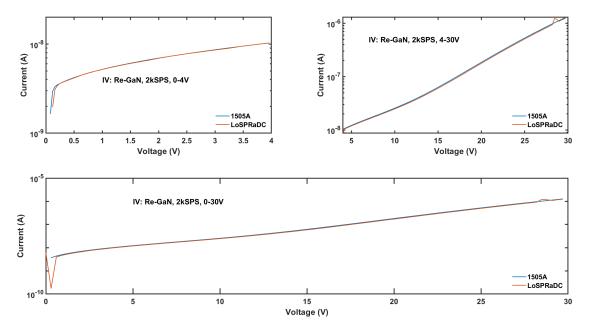

| Figure 73. | Re/GaN IV Plots, 2 kSPS                    | 74 |

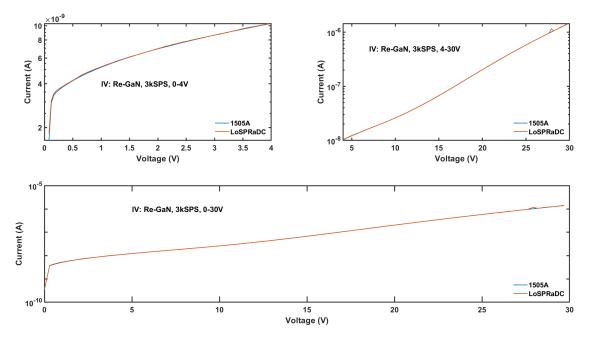

| Figure 74. | Re/GaN IV Plots, 3 kSPS                    | 75 |

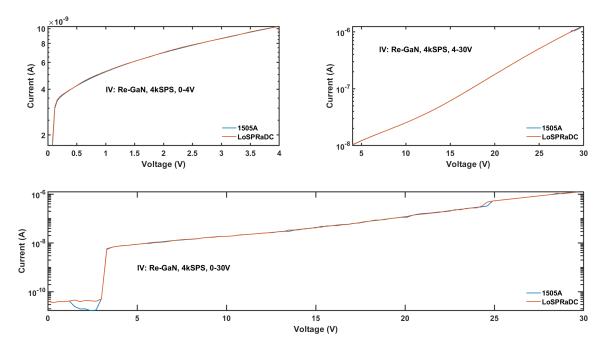

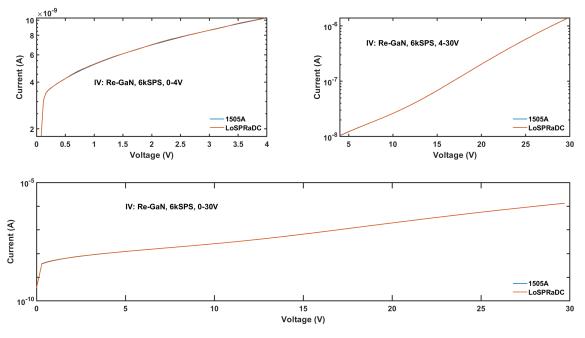

| Figure 75. | Re/GaN IV Plots, 4 kSPS                    | 75 |

| Figure 76. | Re/GaN IV Plots, 6 kSPS                    | 76 |

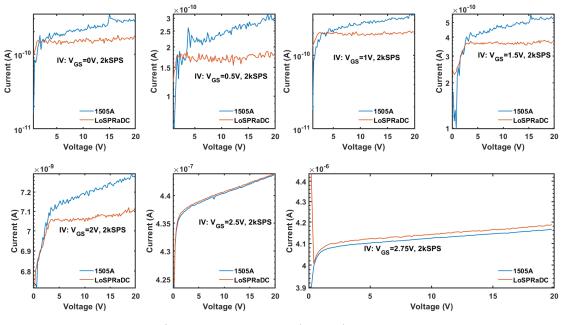

| Figure 77. | FET IV Plots, 2 kSPS                       | 77 |

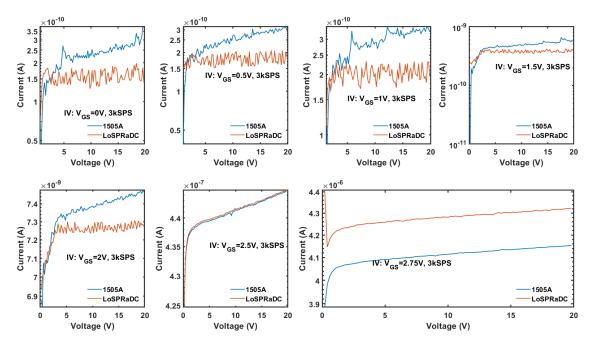

| Figure 78. | FET IV Plots, 3 kSPS                       | 77 |

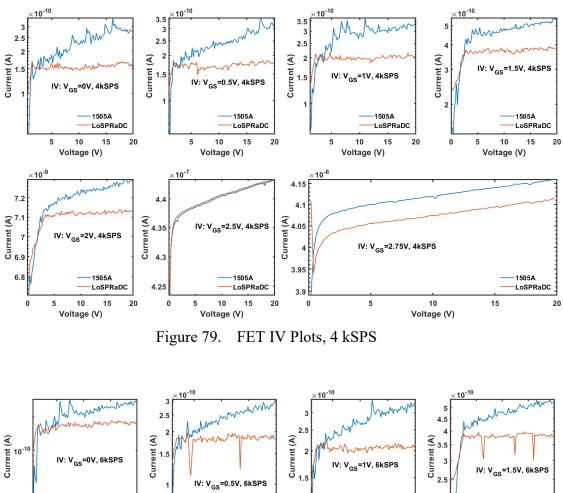

| Figure 79. | FET IV Plots, 4 kSPS                       | 78 |

| Figure 80. | FET IV Plots, 6 kSPS                       | 78 |

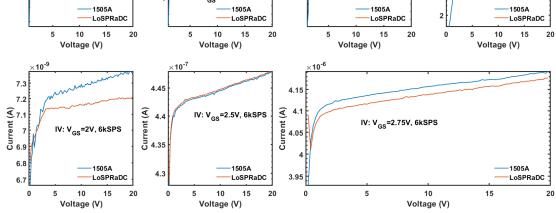

| Figure 81. | MOSFET Output Characteristic Curve         | 79 |

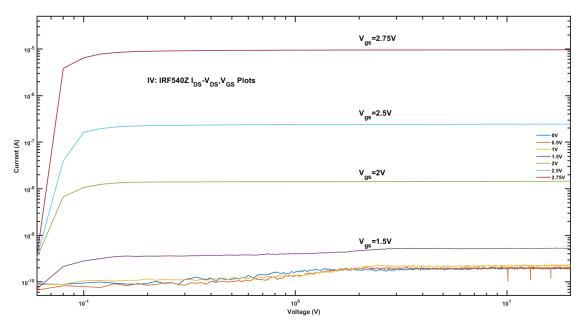

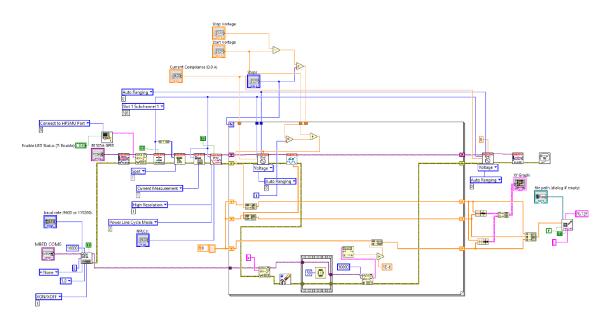

| Figure 82. | Front Control Panel of LoSPRaDC LabVIEW VI | 37 |

| Figure 83. | Block Diagram of LoSPRaDC LabVIEW VI       | 37 |

# LIST OF TABLES

| Table 1. | Material and Electrical Properties of Semiconductors. Source: [14] |

|----------|--------------------------------------------------------------------|

| Table 2. | Aol vs. NG Stability Factors. Adapted from [21]                    |

xiv

# LIST OF ACRONYMS AND ABBREVIATIONS

| AI               | artificial intelligence                                          |

|------------------|------------------------------------------------------------------|

| BFOM             | Baliga Figure of Merit                                           |

| DAQ              | data acquisition                                                 |

| dc               | direct current                                                   |

| DIP              | dual in-line package                                             |

| DUT              | device under test                                                |

| EDA              | electronic design automation                                     |

| EMI              | electromagnetic interference                                     |

| EMP              | electromagnetic pulse                                            |

| FET              | field effect transistor                                          |

| GaN              | gallium nitride                                                  |

| HTOL             | high temperature operating life                                  |

| HTRB             | high temperature reverse bias                                    |

| HV               | high voltage                                                     |

| IDE              | integrated development environment                               |

| ΙΟ               | input-output                                                     |

| I-V              | current-voltage                                                  |

| I-V-T            | current, voltage, temperature                                    |

| I <sup>2</sup> C | Inter-Integrated Circuit                                         |

| JFET             | junction field effect transistor                                 |

| JLTV             | Joint Light Tactical Vehicle                                     |

| LMB              | leakage measurement board                                        |

| LoSPRaDC         | Low Side Picoammeter for Reliability and Device Characterization |

| LPF              | low-pass filter                                                  |

| LSB              | least significant bit                                            |

| MFB              | multi feedback                                                   |

| MOSFET           | metal oxide semiconductor field effect transistor                |

|                  | X/X /                                                            |

| MPSMU  | medium power source measurement unit   |

|--------|----------------------------------------|

| NBW    | noise bandwidth                        |

| NPLC   | number of power-line-cycles            |

| PCB    | printed circuit board                  |

| PDF    | probability density function           |

| PSD    | power spectral density                 |

| PTFE   | polytetrafluoroethylene                |

| Re/GaN | Rhenium/GaN                            |

| RMS    | root-mean-square                       |

| RTOS   | real-time operating system             |

| Si     | silicon                                |

| SiC    | silicon carbide                        |

| SIGINT | signals intelligence                   |

| SMS    | stress-measure-stress                  |

| SMT    | surface mount                          |

| SOIC-8 | small outline integrated circuit 8-pin |

| SPI    | serial port interface                  |

| SPS    | samples per second                     |

| TIA    | transimpedance amplifier               |

| USMC   | United States Marine Corps             |

| USNA   | United States Naval Academy            |

| USB    | universal serial bus                   |

| UPS    | uninterrupted power supply             |

| VI     | virtual instrument                     |

| WBGS   | Wide Bandgap Semiconductor             |

# ACKNOWLEDGMENTS

I would like to express my deepest appreciation to my advisor, Dr. Todd Weatherford, for this research opportunity, his invaluable insight into semiconductor devices, and introduction to the world of amateur radio. I am also extremely grateful to my second reader, Mr. Matthew Porter, for his profound belief in my abilities, unparalleled patience, and friendship. I would also like to sincerely thank the rest of the professors and supporting staff within the Electrical and Computer Engineering Department at the Naval Postgraduate School. Your contributions to my academic and professional development will follow me for the rest of my career and I look forward to these onto my own students. I'd also like to acknowledge the assistance and support of the Electrical and Computer Engineering Department at the United States Naval Academy, thank you for affording me the opportunity to complete my thesis unencumbered.

Lastly, I would like to thank my wife, Kayla, for her undying love, selfless sacrifice, and heavenly patience, without which I would have never succeeded in this endeavor. I will cherish every dinner at Mezzaluna, trip to Big Sur, and walk along the Monterey Peninsula coast with Monty and Poncho for the rest of our lives.

xviii

# I. INTRODUCTION

## A. MOTIVATION

The United States Marine Corps (USMC) is currently navigating through a largescale institutional modernization. At the forefront of this modernization is the adoption and implementation of multiple advanced electronic technologies, from AI (artificial intelligence) at the edge, capable of rapidly processing collected signals intelligence (SIGINT) on the front lines, to autonomous Joint-Light Tactical Vehicles (JLTV) equipped with area-denial weapon systems, shown in Figure 1 [1]. While the USMC seeks to adopt state-of-the-art electronic systems, these systems must be able to meet the harsh and demanding expeditionary requirements inherent to the mission of the USMC. When designing these advanced electronic systems that will support distributed operations in a contested maritime environment, particular care must be taken to optimize their performance against their energy efficiency and size.

Figure 1. Navy Marine Expeditionary Ship Interdiction System Source: [2].

The greatest challenge to the implementation of these advanced systems are limited power resources; these resource limitations are created by existing power generation equipment, bulky power electronic distribution systems, and low energy density storage technology [3]. These systems all share one thing in common, they are beholden to the limitations of their primary semiconductor material, silicon (Si). These systems based on Si semiconductor power devices have simply reached the upper thresholds of performance and efficiency per unit area, as governed by the nature of their intrinsic material properties with respect to the modern demands of electronic systems [4]. Therefore, more research into new power semiconductor materials is needed to overcome these limitations.

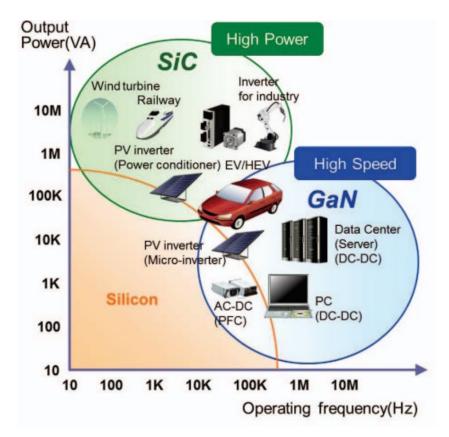

In recent years, the military has been exploring the use of wide bandgap semiconductors (WBGS) such as gallium nitride (GaN) and silicon carbide (SiC) in power electronic devices due to their promising material properties, as compared to Si, as shown in Figure 2 [5]. GaN and SiC offer several advantages over Si for power applications, such as higher temperature operation thresholds, which allows for the design of electronic devices with smaller form factors; higher critical electric field and electron mobility, which allows for greater current densities and increased protection against electromagnetic pulse (EMP) events; resistance to radiation effects, which limits the durability of traditional Si devices in space; and higher frequency operation, which improves the performance of radar systems [6], [7].

Figure 2. Applications of GaN and SiC vs. Si. Source: [8].

Given these improved performance characteristics, WBGS are one of the most promising technologies for next generation solid-state power devices. This research directly pushes the USMC closer to meeting its expeditionary requirements for advanced electronic systems capable of higher performance while becoming more physically compact, energy efficient, and reliable. While determining the physical dimensionality and energy efficiency of a system is relatively simple, determining the reliability of WBGS devices is not. Understanding the reliability of these high performance WBGS devices is paramount to their implementation in military systems but remains untested because good quality reliability data is needed, but it is difficult and expensive to produce. To understand device reliability, systems capable of accurately measuring device characteristics are needed.

#### **B. PROBLEM STATEMENT AND RESEARCH OBJECTIVES**

A modular and affordable system capable of automatically measuring, and constantly monitoring, the amount of leakage current generated by multiple devices-undertest (DUTs) while they are being electrically stressed in parallel during reliability tests is needed for ongoing testing of the reliability of WBGS at the Naval Postgraduate School (NPS). Historically, semiconductor reliability testing at NPS has been done primarily using the high temperature operating life (HTOL) method; there is a distinct need at NPS for a low-cost system to perform automated high temperature reverse bias (HTRB) testing.

HTOL is a semiconductor reliability testing method during which a DUT is subjected to operation at a constant current over a fixed interval of time while also being held at a fixed temperature. Such a test can be automated via a stress-measure-stress (SMS) modification: between each measurement period, the current, voltage, and temperature (I-V-T) characteristics of the device are recorded to identify changes, which are indicative of potential failure mechanisms. HTRB is like HTOL, except that it holds a device at a fixed voltage over a fixed time interval to evaluate time-dependent breakdown characteristics. With previous prototype HTRB systems developed at NPS, DUTs could only be characterized between stress cycles; DUT leakage currents during stressing could not be adequately monitored. The lack of this capability resulted in the destruction of numerous DUTs during electrical stress cycles due to the inability of the system to monitor leakage currents and disconnect DUTs which were approaching nominal failure conditions. As such, researchers were not able to conduct deterministic failure analysis on these devices.

This thesis examines the research, development, and implementation of a novel insitu low-side automatic leakage current measurement system capable of picoampereresolution, from 1 nA to 400  $\mu$ A, that can be integrated with high voltage (HV) HTRB reliability tests. This system, referred to as the Low Side Picoammeter for Reliability and Device Characterization (LoSPRaDC), is specifically designed to be implemented as a subsystem within an upgraded SMS system for a future combined HTRB/HTOL system design. This upgraded system is being designed to support HV HTRB testing up to 5 kV and high current HTOL testing up to 30 A. Ultimately, the overall system is intended to be used by various students, such as those at NPS and the United States Naval Academy (USNA), and researchers, such as those at the Naval Research Lab (NRL), for reliability research and testing of high-power and WBGS devices.

After developing the LoSPRaDC, the performance of the system was examined through the extraction of measurement data for the leakage current and voltage (I-V) characterization of several example DUTs. This was done by comparing the leakage current data produced by the LoSPRaDC against the data extracted from the Keysight B1505A Power Device Analyzer / Curve Tracer medium power source measurement unit (MPSMU) module used to electrically stress a selection of DUTs. The DUTs used to perform this validation testing consist of one Re/GaN diode manufactured at Pennsylvania State University, as well as commercially available devices such as one vertical GaN PN diode, two Si Zener diodes, one Si power diode, one resistor, and one field-effect transistor (FET).

## C. RELATED WORK

In 2019, Clemmer conducted a reliability study on Pd-GaN diodes using the original SMS HTOL system at NPS [9]. His research showed the ability of an HTOL system to collect in-situ I-V-T measurements during the period between electrical stress tests. This study recommended updates to the HTOL system for conducting better reliability tests and minimizing noise in the data [9].

In 2021, O'Neal conducted reliability study using a student developed HTOL/ HTRB system at NPS [10]. During his research, he tested Pd-GaN devices under HTOL and HTRB conditions. His research showed that such an adaptable and modular testing system was relatively simple to implement which made it ideal for educational institutions to perform reliability research using a cost-effective system. In his paper, he also spoke about future work related to the need for testing three-terminal devices [10].

In 2022, Kavanaugh upgraded the existing HTOL system by increasing the magnitude of current and temperature stress that could be generated by the system [11]. He also implemented a spectrometer to measure the electroluminescence of the DUT. His research showed that electroluminescence spectral analysis could be used to monitor the health of direct bandgap semiconductors over time [11].

## D. THESIS ORGANIZATION

This thesis is organized as follows. Chapter II provides background information on WBGS and operational amplifier (op-amp) theory, including the implementation of reverse-feedback current amplifiers designed using a transimpedance amplifier configuration and the benefits of this current sensing method over a shunt resistor. Specifically, TIA stability considerations and the effects of various noise interference is presented. In Chapter III, the system design of LoSPRaDC along with the system testing and validation methodologies is covered. In Chapter IV, the system testing and validation testing results are presented. Finally, Chapter V presents the conclusions of the validation testing, along with recommendations on future work relating to the overall testing system

# II. BACKGROUND

This chapter discusses the motivation and background necessary to understand the design and operation of the LoSPRaDC system developed in this thesis. This chapter first motivates the need for a picoampere-capable measurement system in WBGS device reliability testing by discussing the properties of WBGS materials. Then, an introduction to op-amps provides the background needed to understand the effects of noise and stability in an amplifier designed to measure the low leakage currents generated by WBGS devices.

### A. MATERIAL PROPERTIES OF WBGS

Si has remained dominant as the material of choice for the power semiconductor industry due to its abundant availability, low-cost, and relative ease of manufacturing into substrates for integrated circuits (IC); however, its intrinsic material properties limit its performance in high-speed power switching devices, HV protection, and high temperature applications [12]. This is mostly due to the tradeoff that exists between breakdown voltage and on-state resistance, limiting the minimum charge per unit cross-sectional area, or current density, that Si can withstand [13]. Because of the intrinsic material properties of WBGS, higher electron mobility and lower on-state resistance, they are the materials of choice to replace Si for high-frequency and high-power applications, such as power electronics, radar, and solid-state lighting.

GaN and SiC are classified as WBGS because they have an energy gap between their valence and conduction bands, or bandgap, that is greater than 2.2 eV [9]. A comparison of the material properties of GaN and SiC to Si is shown in Table 1.

| Parameter                       | Symbol                   | Unit                     | Si   | SiC  | GaN   |  |

|---------------------------------|--------------------------|--------------------------|------|------|-------|--|

| Bandgap                         | $E_c$                    | eV                       | 1.12 | 3.2  | 3.43  |  |

| Relative Dielectric<br>Constant | $\epsilon_s$             | -                        | 11.9 | 10   | 9.5   |  |

| Electron Mobility               | $\mu_n$                  | cm <sup>2</sup> /(V.s)   | 1500 | 700  | 2000  |  |

| Peak Electron Velocity          | Vpeak                    | $10^7 \cdot \text{cm/s}$ | 1    | 2    | 2.5   |  |

| Critical Electric Field         | $E_c$                    | MV/cm                    | 0.3  | 3.0  | 3.3   |  |

| Baliga Figure of Merit          | $\epsilon_s \mu_n E_c^2$ | W/cm <sup>2</sup>        | 1    | 392* | 1416* |  |

| * Normalized to Si              |                          |                          |      |      |       |  |

Table 1.

Material and Electrical Properties of Semiconductors. Source: [14].

#### 1. Baliga's Figure of Merit

Baliga's Figure of Merit (BFOM) is a widely accepted metric used to compare the suitability of a semiconductor material for use in power device applications through the examination of materials by their potential for minimizing on-state loss in a power semiconductor device design. It comes from the denominator of (1), which is used to determine the specific on-state resistance of the ideal drift region ( $R_{on,sp}$ ) based on the breakdown voltage ( $V_{br}$ ), dielectric constant ( $\varepsilon_s$ ), electron mobility ( $\mu_n$ ), and critical field strength ( $E_{crit}$ ) of the given material [12], [15].

$$R_{on,sp} = \frac{4V_{br}^2}{\varepsilon_s \mu_n E_{crit}^3}$$

(1)

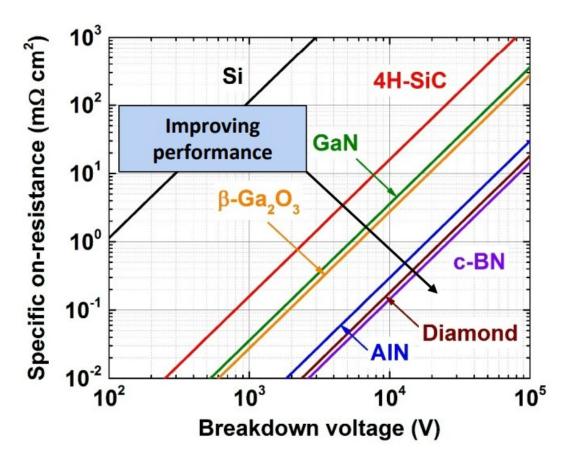

The BFOM, defined in (2), defines the material parameters which minimize the  $R_{on,sp}$  of a power semiconductor drift layer for a desired  $V_{br}$ . Figure 3 provides an example of the BFOM limits for Si, GaN, and SiC, which demonstrate an improvement of over four orders of magnitude offered by the utilization of GaN over Si for power applications.

$$BFOM = \varepsilon_s \mu_n E_{crit}^3 \tag{2}$$

Figure 3. R<sub>on,sp</sub> vs. V<sub>br</sub> of Other Materials. Source: [3].

## 2. PN Diode Leakage Current

Another material property that must be discussed takes place at the PN junction formed between p-type and n-type semiconductors. This interface between acceptor and donor doped semiconductors forms a barrier potential caused by the change of Fermi levels between each material in an area known as the depletion region. This depletion region grows under reverse-bias and limits current flow. The I-V function for an ideal diode is shown in (3), where  $I_D$  is the diode current,  $I_s$  is the saturation current, q is the elementary charge, V is the potential across the device, k is the Boltzmann constant, and T is the temperature in degrees Kelvin.

$$I_{D} = I_{S}(e^{qV/kT} - 1)$$

(3)

When a  $p^+$ -n device is reverse biased, the ideal saturation current is represented by (4), where A is the area of the device,  $n_i$  is the intrinsic carrier concentration,  $N_D$  is the donor concentration,  $D_P$  is hole diffusion coefficient, and  $\tau$  is the carrier lifetime [16].

$$I_{S} = -qAn_{i}^{2} \left(\frac{1}{N_{D}}\right) \sqrt{\frac{D_{P}}{\tau}}$$

(4)

The intrinsic carrier concentration is defined in (5), where  $N_C$  and  $N_V$  are the density of states in the conduction and valence bands. The intrinsic carrier concentration is exponentially related to the bandgap energy; therefore, it can be concluded that a larger bandgap, as found in WBGS, is directly correlated to an exponentially low intrinsic carrier concentration [16].

$$n_i = \sqrt{N_C N_V} \cdot e^{-(E_g/2kT)}$$

(5)

The further reduction of this already small intrinsic carrier concentration to the reverse saturation current, shown in (4), is what explains the low leakage currents characteristic of WBGS devices based on PN junctions. These low reverse leakage current values are what motivates the need for picoampere-capable measurements during the HTRB reliability testing of WBGS devices.

### **B. OPERATIONAL AMPLIFIERS**

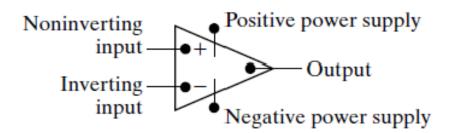

An op-amp is a type of electronic amplifier that is widely used in a variety of circuit applications, including amplifiers, filters, oscillators, and comparators. Op-amps are designed to have a high gain and a high input impedance, making them ideal for amplifying small signals from sensors or other sources. They typically have two input terminals, labeled as the inverting input and the non-inverting input, two power supply input terminals, labeled as the positive and negative power supplies, and a single output terminal. These are commonly presented as shown in Figure 4.

Figure 4. Circuit Symbol for an Op-amp. Source: [17].

The output voltage of the op-amp is proportional to the difference in voltage between its two inputs, this output can be positive or negative. This relationship is defined in (6), where  $V_{out}$  is the output voltage,  $V^+$  is the non-inverting input voltage,  $V^-$  is the inverting input voltage, and  $A_{ol}$  is the open-loop gain.

$$V_{out} = A_{ol}(V^{+} - V^{-})$$

(6)

Ideal op-amps have infinite gain and bandwidth, meaning they can amplify signals of any frequency with the same amount of gain; however, op-amps are almost never used in the open-loop configuration. This is because the limit of the gain of an op-amps is determined by the saturation range set by the positive and negative power supplies to the circuit, which limits the maximum signal which can be applied between V+ and V-. To mitigate this, op-amps are almost always implemented with a feedback mechanism, referred to as a closed-loop configuration, which is either positive or negative [18].

#### 1. Ideal Closed-Loop Gain (Inverting and Non-inverting)

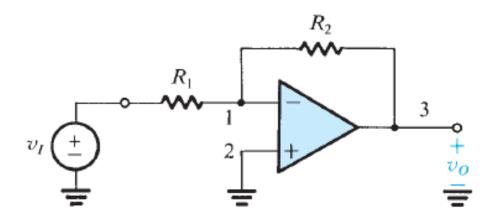

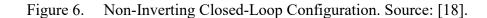

When a connection is made between either of the input terminals and the output terminal of an op-amp, it is said to be configured in a closed-loop configuration. Figure 5 shows a resistor, R<sub>2</sub>, connected from the output terminal to the inverting terminal; thus, this op-amp is said to be in an inverting configuration.

Figure 5. Inverting Closed-Loop Configuration. Source: [18].

Since the non-inverting terminal is tied to ground, it will have a value very close to zero. This op-amp has a voltage source connected to its non-inverting terminal across a resistor, but because an op-amp will output the difference between its input terminals, the voltage at the non-inverting terminal will also be essentially zero. This results from the op-amp producing a negative output that will feedback to the non-inverting terminal to equalize it with the value of the inverting terminal; the mechanism of this action is referred to as a virtual short, or virtual ground, as in Figure 5, because an op-amp with negative feedback will always drive the potential between its input terminals to zero. The closed-loop gain, G, output voltage, V<sub>out</sub>, and input impedance, Z<sub>in</sub>, of this configuration are defined in (7), (8), and (9).

$$G = Gain = \frac{V_{out}}{V_{in}} \tag{7}$$

$$V_{out} = -V_{in} \left(\frac{R_2}{R_1}\right) \rightarrow \frac{V_{out}}{V_{in}} = -\left(\frac{R_2}{R_1}\right)$$

(8)

$$Z_{in} = R_1 \tag{9}$$

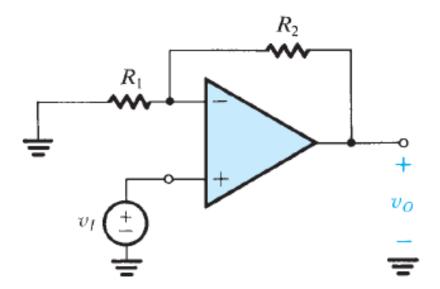

Figure 6 shows a voltage source connected to the non-inverting input and the inverting input attached to a resistor,  $R_1$ , that is connected to ground. The same principles apply in this case, except that the virtual ground is now equal to  $V_{in}$ . In this case, the input impedance,  $Z_{in}$ , is equal to infinity, but in the non-ideal case it would be equal to the impedance of the op-amp itself.

$$V_{out} = V_{in} \left( 1 + \frac{R_2}{R_1} \right) \longrightarrow \frac{V_{out}}{V_{in}} = \left( 1 + \frac{R_2}{R_1} \right)$$

(10)

$$Z_{in} = \infty \tag{11}$$

### 2. Non-ideal Op-amp Model

Figure 7 shows the non-ideal model of the op-amp in a non-inverting configuration. Here, the previously infinite input-impedance is replaced with the finite input-impedance  $R_i$ , the zero-output impedance is replaced with the non-zero-output impedance  $R_o$ , and the open-loop gain, A, is now finite. While V<sup>+</sup> is still tied to ground, the value of V<sup>-</sup> is no longer equal to V<sup>+</sup> due to the small voltage drop across  $R_i$ . Because of these non-ideal factors, the previous equations from the ideal model are no longer true and must be re-calculated by setting up new equations for V<sub>in</sub> and V<sub>out</sub>, as shown in (12) [17].

Figure 7. Non-ideal Inverting Op-amp Model. Source: [17].

Equation 1:

$$\frac{V^{-} - V_{in}}{R_{s}} + \frac{V^{-} - V^{+}}{R_{i}} + \frac{V^{-} - V_{out}}{R_{f}} = 0$$

Equation 2:

$$\frac{V_{out} - V^{-}}{R_{f}} + \frac{V_{out} - A(V^{+} - V^{-})}{R_{o}} = 0$$

(12)

Setting  $V^{+}$  to zero and solving each equation in terms of  $V_{in}$  and  $V_{out}$  simplifies to,

$$\left(\frac{1}{R_s} + \frac{1}{R_i} + \frac{1}{R_f}\right) V^- - \frac{1}{R_f} V_{out} = \frac{1}{R_s} V_{in}$$

$$\left(\frac{A}{R_o} - \frac{1}{R_f}\right) V^- + \left(\frac{1}{R_f} + \frac{1}{R_o}\right) V_{out} = 0 ,$$

(13)

where combining both equations and solving for V<sub>out</sub> yields,

$$V_{out} = \frac{-A + \begin{pmatrix} R_o \\ R_f \end{pmatrix}}{\frac{R_s}{R_f} \left(1 + A + \frac{R_o}{R_i}\right) + \left(1 + \frac{R_s}{R_i}\right) + \frac{R_o}{R_f}} V_{in}.$$

(14)

Equation (14) is the transfer function of the non-ideal inverting op-amp configuration in Figure 7. From here, the closed-loop gain,  $A_{cl}$ , can be calculated by simply dividing by  $V_{in}$ . This demonstrates the effect that a finite-input impedance and open-loop gain has on the performance of an op-amp and why a very high input-impedance and open-loop gain are needed to maintain the conditions for a virtual short [17].

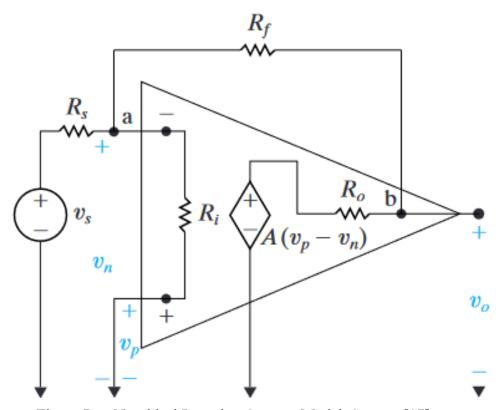

#### 3. Frequency Response and Bandwidth

One of the most limiting factors to the performance of any non-ideal op-amp is the frequency response. In the case of the ideal op-amp, the frequency response is constant across an infinite bandwidth range. In the case of the non-ideal op-amp, however, the bandwidth of the op-amp is finite and determined by the internal parasitic capacitances of the device. For this reason, many op-amps are internally compensated, which means they are built with a known value capacitor to control their operational stability and which gives the op-amp frequency response a dominant real pole at low frequency [18].

The use of this capacitor to ensure the stability of an op-amp over a particular operational frequency range is known as frequency compensation [18]. Figure 8 shows an example of the frequency response for a generic, internally compensated, op-amp with a corner frequency at 10 Hz and a gain roll-off of -20 dB/decade through the unity-gain

bandwidth at 0 dB and 10<sup>6</sup> Hz, or 10 MHz, which equals the open-loop bandwidth of this device. This point where the open-loop gain curve crosses 0 dB is indicative of the finite nature of a non-ideal op-amps bandwidth [18].

Figure 8. Open-Loop Gain of Non-ideal Op-Amp. Source: [18].

### 4. Closed Loop Op-amp Circuit Stability

The previous section introduced the idea of stability in an op-amp over its openloop bandwidth, and some of the mechanisms by which to ensure said stability. This section will primarily focus on the closed-loop bandwidth, how it is related to the open-loop bandwidth, and the concept of phase margin as well as how it can be used to quickly identify whether a closed-loop op-amp circuit will be stable.

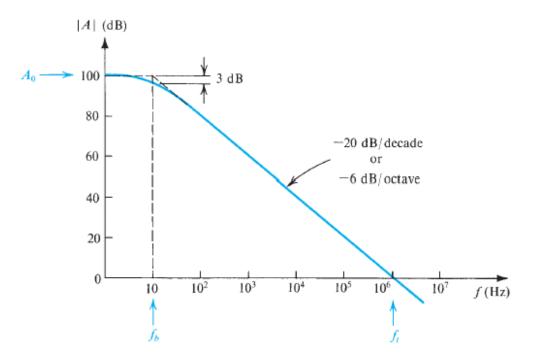

The closed-loop behavior of an op-amp with feedback can be modeled by a block diagram, as shown in Figure 9. In Figure 9, A represents the open loop op-amp gain, or  $A_{ol}$ ,  $\beta$  represents the feedback factor [18], and  $x_i$ ,  $x_o$ , and  $x_f$  represent  $V_{in}$ ,  $V_{out}$ , and  $V_{fb}$ , respectively.

Figure 9. Block Diagram Model of Closed-Loop Gain. Source: [18].

With these terms defined, a few relationships and equations relating to the gain can now be derived,

$$\beta = \text{Feedback Factor} = \frac{V_{fb}}{V_{out}}$$

(15)

$$A_{cl} = \text{Closed-Loop Gain} = \frac{A_{ol}}{(1 + A_{ol}\beta)}$$

(16)

$$\text{Loop Gain}=A_{ol}\beta \tag{17}$$

$$A_{cl} = \lim_{A_{ol} \to \infty} \left( \frac{A_{ol}}{1 + A_{ol}\beta} \right) = \frac{1}{\beta}$$

(18)

Equation (16) shows that the model in Figure 9 becomes unstable when loop gain, (17), is equal to -1, because this is when the denominator of closed-loop gain, shown in (16), is equal to 0, causing  $A_{cl}$  to equal infinity. This may not seem possible because the lowest value for loop gain magnitude is 0 dB. However, the loop gain can become negative due to the phase shift of the gain. When the system experiences a phase shift of -180°, there is an inversion of the gain, so when loop gain is 0 dB and there is a -180° phase shift, the value of loop gain, shown in (17), becomes -1, therefore, the system becomes unstable.

Figure 10. Illustration of Gain Margin and Phase Margin. Source: [18].

The margin of stability between loop gain and a -180° phase shift is known as the phase margin [18]. Phase margin, visually depicted in Figure 10, is defined as the difference between the loop gain phase angle and -180°, at the point where loop gain magnitude equals 0 dB. If the phase angle is greater than -180° when the loop gain equals 0 dB, then the circuit is stable. When designing an op-amp circuit with closed-loop feedback, or a feedback amplifier, the phase margin can be used to quickly determine the degree of its stability. For this reason, feedback amplifiers are typically designed to have a phase margin greater than 45° [18].

Using Figure 11 as an example, (15) through (18) would be used to define the following equations:

$$\beta = \frac{V_{fb}}{V_{out}} = \frac{R_1}{R_1 + R_2}$$

(19)

$$\therefore A_{cl} = \frac{A_{ol}}{\left(1 + A_{ol}\left(\frac{R_1}{R_1 + R_2}\right)\right)}$$

(20)

$$\therefore A_{cl} = \lim_{A_{ol} \to \infty} \left( \frac{A_{ol}}{1 + A_{ol} \left( \frac{R_1}{R_1 + R_2} \right)} \right) = \frac{1}{\left( \frac{R_1}{R_1 + R_2} \right)} = \frac{R_1 + R_2}{R_1} = 1 + \frac{R_2}{R_1}$$

(21)

Figure 11. Example of Non-inverting Feedback Amplifier. Source: [18].

Equations (19) and (21) show that loop gain is the product of  $\beta$  and A<sub>ol</sub>. If the openloop gain is real and constant, then the circuit will be stable at all frequency values as the phase of the loop gain remains zero at all frequencies [18].

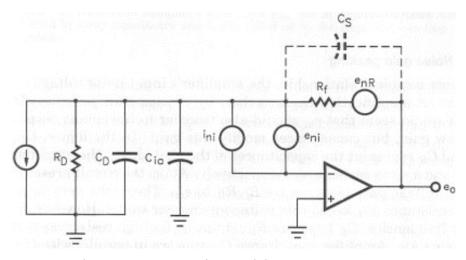

# C. TRANSIMPEDANCE AMPLIFIER CONFIGURATION

The transimpedance amplifier (TIA) op-amp configuration, also referred to as a current to voltage converter or current feedback amplifier, is one of the methods most frequently used by designers to amplify the low-level currents produced by various types of sensors into a useful output voltage that can be measured by an analog-to-digital converter (ADC). A TIA schematic is typically referenced with a photodiode with its

cathode connected to ground and anode connected to the inverting input terminal of an opamp, as in Figure 12.

Figure 12. TIA with Photodiode. Source: [19].

In Figure 12,  $C_F$  and  $R_F$  refer to the feedback capacitor, which includes any resistive capacitance, and the feedback resistor,  $I_{PD}$  refers to the photocurrent and dark current generated by the photodiode, and  $V_{OUT}$  represents the output voltage.

Figure 13 shows another common representation of a TIA circuit where the photodiode is modeled by a current source in parallel with a capacitor and resistor, connected between the inverting input and ground.  $C_{SHUNT}$  represents the junction capacitance of the photodiode and  $R_{SHUNT}$  represents the equivalent input resistance of the photodiode as seen by the op-amp. Conveniently, this model is also representative of many types of devices, with I<sub>PD</sub> used to model the low-level leakage current of the device. Given this similarity, equations derived for this model can be applied to predict performance of the TIA circuit for DUT current sensing applications.

Figure 13. TIA with Equivalent Photodiode Model. Source: [19].

## 1. TIA Stability Analysis

To derive the transfer function for the TIA, new parameters must first be defined, based on (15) through (18). For these derivations,  $R_{SHUNT}$  will be represented by  $R_i$ , for input resistance;  $C_{SHUNT}$  will be represented by  $C_i$ , for input capacitance;  $I_{PD}$  will be represented by  $I_{in}$ , for input current, and V<sup>-</sup> and V<sup>+</sup> will represent the inverting and noninverting input terminals, respectively.

$Z_{\rm f}$  and  $Z_{\rm i}$ , (22) and (23), represent the feedback and input impedances corresponding to the parallel combinations of  $C_{\rm f}$  with  $R_{\rm f}$  and  $C_{\rm i}$  with  $R_{\rm i}$ .

$$Z_f = \frac{R_f}{1 + sR_fC_f} \tag{22}$$

$$Z_i = \frac{R_i}{1 + sR_iC_i} \tag{23}$$

The transfer function derivation begins with setting up the current equation at V<sup>-</sup>,

$$\frac{V^{-} - V_{out}}{Z_{f}} + \frac{V^{-}}{Z_{i}} - I_{in} = 0$$

(24)

then, proceeding to solve for  $V^{\mbox{-}}$  in terms of  $I_{in}$  and  $V_{out}$  yields,

$$I_{in} = \frac{V^{-} - V_{out}}{Z_{f}} + \frac{V^{-}}{Z_{i}}$$

$$I_{in} = \frac{V^{-}}{Z_{f}} - \frac{V_{out}}{Z_{f}} + \frac{V^{-}}{Z_{i}}$$

$$I_{in} + \frac{V_{out}}{Z_{f}} = V^{-} \left(\frac{1}{Z_{f}} + \frac{1}{Z_{i}}\right)$$

$$I_{in} + \frac{V_{out}}{Z_{f}} = V^{-} \left(\frac{Z_{f} + Z_{i}}{Z_{f}Z_{i}}\right)$$

$$V^{-} = \left(I_{in} + \frac{V_{out}}{Z_{f}}\right) \left(\frac{Z_{f}Z_{i}}{Z_{f} + Z_{i}}\right)$$

$$V^{-} = \left(\frac{Z_{f}Z_{i}}{Z_{f} + Z_{i}}\right) I_{in} + \left(\frac{Z_{i}}{Z_{f} + Z_{i}}\right) V_{out}.$$

(25)

Finally, simplifying the impedances in (25) yields,

$$\left(\frac{Z_i}{Z_f + Z_i}\right) \rightarrow \beta$$

$$\left(\frac{Z_f Z_i}{Z_f + Z_i}\right) \rightarrow \left[Z_f \parallel Z_i\right]$$

$$V^- = \left[Z_f \parallel Z_i\right] I_{in} + \beta V_{out}.$$

(26)

Thus, defining Vout and using (26) for V<sup>-</sup> yields,

$$V_{out} = A_{ol}(V^+ - V^-) = -A_{ol}V^-$$

$$\therefore V_{out} = -A_{ol}\left(\left[Z_f \mid \mid Z_i\right]I_{in} + \beta V_{out}\right), \qquad (27)$$

and finally, by solving for  $V_{\text{out},}$

$$V_{out} \left( 1 + A_{ol} \beta \right) = -I_{in} \left[ Z_f \parallel Z_i \right] A_{ol}$$

$$\therefore V_{out} = -I_{in} \left[ Z_f \parallel Z_i \right] \frac{A_{ol}}{1 + A_{ol} \beta} \quad .$$

(28)

The frequency dependence of the TIA assuming an ideal op-amp can be found by taking the limit of  $A_{ol}$  in (28). From (18), taking the limit of  $A_{cl}$  as  $A_{ol} \rightarrow \infty$  yields the following,

$$V_{out} = -I_{in} \left[ Z_f \parallel Z_i \right] \lim_{A_{ol} \to \infty} \left( \frac{A_{ol}}{1 + A_{ol} \beta} \right)$$

$$\therefore V_{out} = -I_{in} \left[ Z_f \parallel Z_i \right] \frac{1}{\beta}$$

(29)

Finally, expanding and simplifying (29) yields the TIA transfer function,

$$V_{out} = -I_{in} \frac{Z_f Z_i}{Z_f + Z_i} \frac{Z_f + Z_i}{Z_i}$$

$$\therefore V_{out} = -I_{in} Z_f = -I_{in} \frac{R_f}{1 + sR_f C_f}$$

(30)

Noise gain (NG) is the inverse of the feedback factor, shown in (15). The NG transfer function, shown in (31), is derived by placing a noise source in series with  $V^+$  of the TIA and solving for the closed-loop gain. This is important because noise incident at  $V^+$  is amplified by the closed-loop gain, which can cause oscillations that lead to instability. From (29), when A<sub>ol</sub> is large, the TIA transfer function is dominated by the contribution of NG.

$$\frac{1}{\beta} = \text{Noise Gain} = \frac{Z_f + Z_i}{Z_i}$$

(31)

Solving the NG transfer function at all frequencies can be done by combining (22), (23) and (31) as follows,

$$NG(f) = \frac{1}{\beta} = \frac{Z_f + Z_i}{Z_i} = \left(\frac{R_f + R_i}{R_i}\right) \left(\frac{1 + s\frac{R_f R_i}{R_f + R_i} (C_f + C_i)}{1 + sC_f R_f}\right).$$

(32)

Equation (32) shows that NG has a constant contribution at low frequency direct current (dc) governed by  $R_f$  and  $R_i$ . It also has a single zero, whose frequency can be represented by  $f_z$ , from (22), and a single pole, whose frequency can be represented by  $f_p$ , from (23). Since NG is the inverse of feedback factor, the zeros and poles of the feedback factor becomes the poles and zeros of the NG. The location of  $f_z$  is governed by  $C_i$  and compensated by  $C_f$ . This concept will be covered in further detail later in the thesis.

$$f_{z} = \frac{1}{2\pi \left[R_{f} \parallel R_{i}\right] \left(C_{f} + C_{i}\right)}$$

Given  $R_{i} \gg R_{f}, \left[R_{f} \parallel R_{i}\right] \cong R_{f}$

$\therefore f_{z} = \frac{1}{2\pi R_{f} \left(C_{f} + C_{i}\right)}$

(33)

$$f_p = \frac{1}{2\pi R_f C_f} \tag{34}$$

Substituting for s and redefining the dc NG contribution in (32) yields,

$$NG(0) = DC NG = \left(\frac{R_f + R_i}{R_i}\right)$$

$$NG(f) = NG(0) \left[\frac{1 + j\frac{f}{f_z}}{1 + j\frac{f}{f_p}}\right].$$

(35)

Therefore, at low frequencies, NG is dominated by the input and feedback resistances. Since the input resistance is based on the effective resistance across a zerobiased PN diode, the value of  $R_i$  is typically greater than 10<sup>9</sup>  $\Omega$ , or 10 G $\Omega$ . The fullspectrum behavior of NG can be understood by again revisiting (32) to derive the high frequency contribution of NG,

$$NG(\infty) = \frac{1}{\beta} = \frac{Z_f + Z_i}{Z_i} = \left(\frac{R_f + R_i}{R_i}\right) \left(\frac{1 + s\frac{R_f R_i}{R_f + R_i} (C_f + C_i)}{1 + sC_f R_f}\right).$$

(36)

Next, taking the limit as s approaches infinity yields,

$$\lim_{s \to \infty} \frac{1}{\beta} = \frac{Z_f + Z_i}{Z_i} = \left(\frac{R_f + R_i}{R_i}\right) \left(\frac{1 + s \frac{R_f R_i}{R_f + R_i} \left(C_f + C_i\right)}{1 + s C_f R_f}\right)$$

$$= \left(\frac{R_f + R_i}{R_i}\right) \left(\frac{\frac{R_f R_i}{R_f + R_i} \left(C_f + C_i\right)}{\frac{R_f + R_i}{C_f R_f}}\right)$$

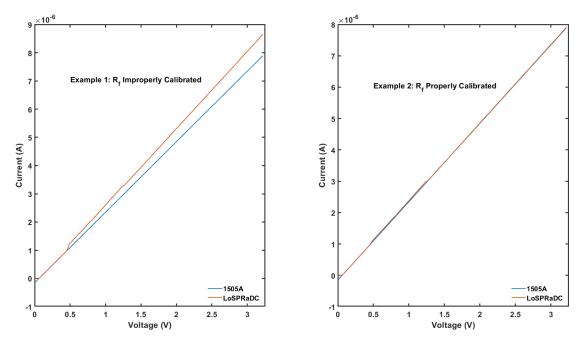

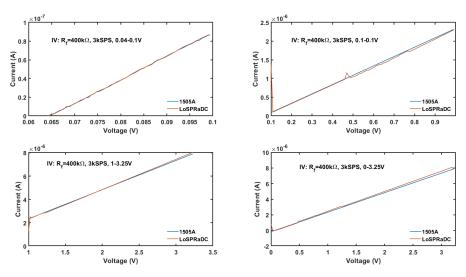

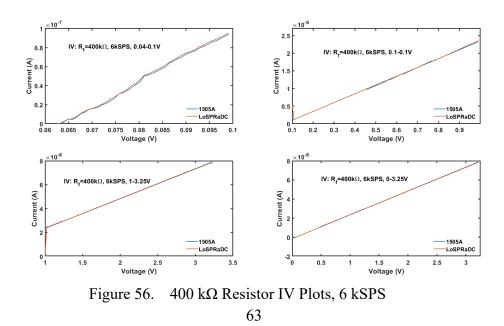

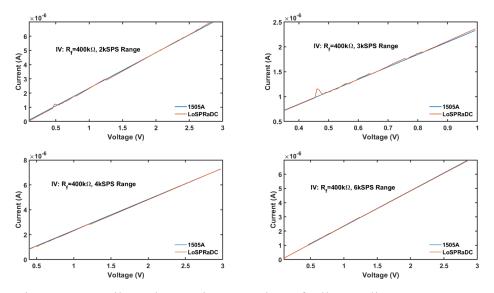

$$\therefore \lim_{s \to \infty} \frac{1}{\beta} = \frac{C_f + C_i}{C_f} \qquad (37)$$