# DESIGN AND ANALYSIS OF DISCRETE HIGH SLEW RATE LOW NOISE VOLTAGE REGULATOR FOR RF TRANSCEIVER SYSTEM

Oleh

Mardiana binti Mohamad Noor

Disertasi ini dikemukakan kepada UNIVERSITI SAINS MALAYSIA

Sebagai memenuhi sebahagian daripada syarat keperluan untuk ijazah dengan kepujian

SARJANA MUDA KEJURUTERAAN (KEJURUTERAAN ELEKTRONIK)

Pusat Pengajian Kejuruteraan Elektrik dan Elektronik Universiti Sains Malaysia

Mac 2005

#### **ABSTRAK**

Sistem komunikasi terdiri daripada pelbagai litar, oleh itu sumber voltan yang stabil adalah penting untuk mendapatkan isyarat output yang dikehendaki. Masalah yang selalu dihadapi dalam mendapatkan sumber voltan yang stabil adalah seperti riak dan perubahan arus sehala yang tidak menentu. Litar pengatur voltan linear merupakan litar sumber voltan untuk menghasilkan output yang stabil. Untuk memperluaskan lagi penggunaan litar ini dalam sistem komunikasi, satu langkah untuk mengimplementasikan penggunaannya dalam litar berfrekuensi tinggi telah dilaksanakan dalam projek ini. Tiga jenis litar pengatur voltan telah dibina iaitu pengatur voltan positif, pengatur voltan negatif dan litar pengatur voltan penolakan riak. Litar skematik asas untuk melaksanakan litar-litar ini diambil daripada litar terkamil LM317 dan µA723. Litar pengatur voltan positif berfungsi untuk mengesan puncak positif voltan riak input manakala litar pengatur voltan negatif pula berfungsi sebaliknya. Litar pengatur voltan penolakan riak bertindak sebagai litar penolakan riak automatik yang mana akan menolak riak yang dikesan oleh litar pengatur voltan positif dan negatif dan seterusnya memberikan input yang stabil kepada litar seterusnya. Oleh kerana gandaan yang dihasilkan oleh litar pengatur voltan penolakan riak ini adalah sangat kecil, litar ini juga boleh digunakan di dalam litar mampatan gandaan. Kesemua litar yang digunakan di dalam projek ini merupakan penukaran terus daripada skematik yang digunakan untuk litar berfrekuensi rendah kepada litar yang berfrekuensi tinggi dengan menggunakan mikrostrip sebagai talian penghantaran.

#### ABSTRACT

Communication system consists of various circuits and having a good and regulated source is crucial in order to get the desired signals at the output. The common problems in getting such good sources are spikes, ripple and fluctuating DC input. Linear voltage regulator is a source circuit to supply a steady, constant output. In addition to its basic function, an attempt to implement its usage in the radio frequency circuits has been made through out this project. Three regulator circuits have been designed, which are negative voltage regulator, positive voltage regulator and ripple rejection voltage regulator. The basic schematics for these circuits were implemented from two types of integrated chips; LM317 and µA723. The positive voltage regulator is used to detect positive peak of ripple input voltage and negative voltage regulator performs vice versa task. Ripple rejection voltage regulator acts as an auto-ripple rejecter circuit, which will reject the ripple detected by positive and negative voltage regulators and supply smooth and constant input to the next circuitry. As the gain of the ripple rejection voltage regulator is very small compared to the input voltage, this regulator also can be applied in the gain compression circuit. Those circuits designed in this project are direct transformation from the schematics used in the low frequencies to the design using microstrips for RF circuits.

### **ACKNOWLEDGEMENTS**

I would like to take this opportunity to thank all the people who had made my life easier while undertaking this project. I would like to take this opportunity to express my greatest appreciation to my supervisor, En.Basir Saibon, for taking me under his wings, his kind instruction and the direction he provided. More importantly is his readiness to give advice and guide me along throughout this period of endeavor.

Not to forget the technicians of RF laboratory, En. Abd. Latip Abd. Hamid and En. Rozaidee Ishak for being so helpful during the completion of this project.

I would like to thank my colleague, Tan Wen Qi for his guide and his readiness to offer helping hand when I'm in trouble. Not to forget my second examiner, Dr. Mohd Ansor Yusof for his willingness going through my report.

Last but not least, to anyone who is not mentioned here thank you for supporting me. I really appreciate all your kindness and attention. Thank You.

# TABLE OF CONTENTS

|                |          |                                               | Page |

|----------------|----------|-----------------------------------------------|------|

| ABSTRAK        |          |                                               | ii   |

| ABSTRACT       |          |                                               | iii  |

| ACKNOWLEDG     | EMENT    |                                               | iv   |

| TABLE OF CON   | TENTS    |                                               | v    |

| LIST OF FIGURE | ES AND 7 | ΓABLES                                        | viii |

| CHAPTER 1      | INT      | RODUCTION                                     |      |

|                | 1.1      | Introduction                                  | 1    |

|                | 1.2      | Scope of the Project                          | 3    |

| CHAPTER 2      | LITI     | ERATURE SURVEY                                |      |

|                | 2.1      | Introduction to Linear Regulator              | 4    |

|                | 2.2      | Zener Diode Voltage Regulator                 | 5    |

|                | 2.3      | Regulation with a Varying Input Voltage (Line |      |

|                |          | Regulation)                                   | 6    |

|                | 2.4      | Regulation with the Varying Load              |      |

|                |          | (Load Regulation)                             | 7    |

|                | 2.5      | Drawbacks of the Zener Diode Voltage          |      |

|                |          | Regulator Applications                        | 8    |

|                | 2.6      | The Feedback Network                          | 9    |

|                | 2.7      | Noise in Integrated Circuit                   | 10   |

|                | 2.8      | Introduction to Slew Rate                     | 15   |

|                | 2.9      | Circuit Gain                                  | 16   |

| 2. | 10 | Reflection Coefficient, $\Gamma_0$ |           | 16 |

|----|----|------------------------------------|-----------|----|

| 2. | 11 | Voltage Standing Wave Ratio        | o, (VSWR) | 18 |

| 2. | 12 | Return Loss                        |           | 19 |

| 2. | 13 | Stability Considerations           |           | 19 |

| 2. | 14 | Microstrip Characteristics         |           | 21 |

| 2. | 15 | Linearity of Regulator             |           | 22 |

| 2. | 16 | Ripple Rejection Percentage        |           | 22 |

## CHAPTER 3 CIRCUITS IMPLEMENTATION

| 3.1 | µA723 Integrated Circuit      |                     | 23 |

|-----|-------------------------------|---------------------|----|

| 3.2 | LM317 Integrated Circuit      |                     | 25 |

| 3.3 | Positive and Negative Voltage | e Regulator Circuit | 26 |

| 3.4 | Ripple Rejection Voltage Reg  | gulator Circuit     | 28 |

| CHAPTER 4 | RESU | JLTS                 |

|-----------|------|----------------------|

|           | 4.1  | Analysis Method      |

|           | 4.2  | Results and Analysis |

|           | 4.3  | Discussion71         |

## CHAPTER 5 CONCLUSION

| 5.1 | Summary       |                | 75 |

|-----|---------------|----------------|----|

| 5.2 | Suggestion fo | r Future Works | 77 |

## REFERENCES

## APPENDIX A: LM317 DATASHEET

## APPENDIX B: µA723 DATASHEET

## **LIST OF FIGURES AND TABLES**

| Chapter 1: |                          |                            |   |

|------------|--------------------------|----------------------------|---|

| Figure 1.1 | RF Design Hexagon        |                            | 1 |

| Figure 1.2 | Voltage regulator design | n in RF transceiver system |   |

## Chapter 2:

| Figure 2.1  | Characteristic of zener diode                                         |

|-------------|-----------------------------------------------------------------------|

| Figure 2.2  | Basic zener diode voltage regulator circuit                           |

| Figure 2.3  | Line regulation in zener regulator                                    |

| Figure 2.4  | Load regulation in zener regulator                                    |

| Figure 2.5  | Output waveform from zener diode voltage regulator plotted on         |

|             | the same axis with the input waveform                                 |

| Figure 2.6  | Output waveform from zener diode voltage regulator                    |

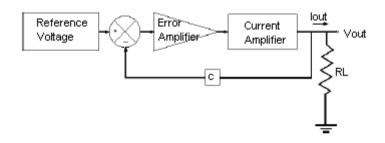

| Figure 2.7  | Block diagram of voltage regulator                                    |

| Figure 2.8  | Two port network representing signal and noise power                  |

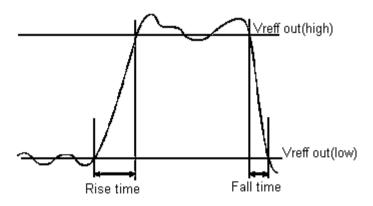

| Figure 2.9  | The measurement of slew rate parameters                               |

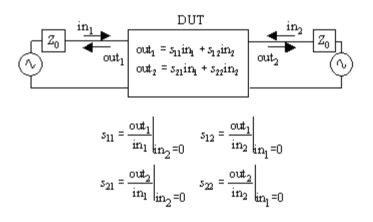

| Figure 2.1( | A two-port S-parameter matrix records the reflection coefficients and |

|             | transmission gain from both sides of the DUT16                        |

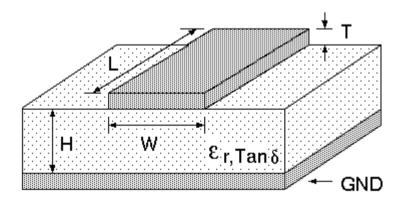

| Figure 2.1  | Cross section of a microstrip                                         |

## Chapter 3:

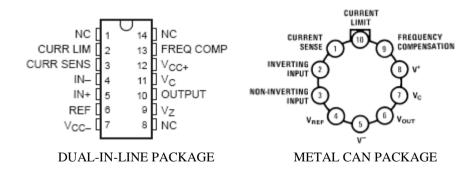

| Figure 3.1  | A723 chip                                                           |

|-------------|---------------------------------------------------------------------|

| Figure 3.2  | A723 pin connection (top view)                                      |

| Figure 3.3  | A723 functional block diagram24                                     |

| Figure 3.4  | A723 schematic diagram24                                            |

| Figure 3.5  | 2.2.2.2.2.2.2.2.2.2.2.2.2.2.2.2.2.2.2.                              |

| Figure 3.6  | LM317 functional block diagram2                                     |

| Figure 3.7  | LM317 schematic diagram                                             |

| Figure 3.8  | Connection of the positive regulator to the $\mu$ A723 chip2        |

| Figure 3.9  | Connection of the negative regulator to the $\mu$ A723 chip2        |

| Figure 3.10 | Connection of ripple rejection voltage regulator to the LM317 chip2 |

## Chapter 4:

| Figure 4.1    | Ideal output from the positive voltage regulator when given        |

|---------------|--------------------------------------------------------------------|

| S             | sinusoidal input voltage                                           |

| Figure 4.2    | Ideal output from the negative voltage regulator when given        |

| S             | sinusoidal input voltage                                           |

| Figure 4.3 Id | deal output from the ripple rejection voltage regulator when given |

| 2.            | .22 mVp-p sinusoidal input voltage to the ripple rejection circuit |

| Figure 4.4    | Graphical output for positive voltage regulator when               |

| V             | $V_{in} = 1.4V \text{ at } 1.9 \text{GHz}$                         |

| Figure 4.5    | Graphical output for positive voltage regulator when               |

| V             | V <sub>in</sub> =2.8V at 1.9GHz34                                  |

| Figure 4.6 The graph shows linear relationship between input and output voltage35                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.7 Relationship between positive peak offset and input voltage                                                                            |

| Figure 4.8 Relationship between negative peak offset and input voltage                                                                            |

| Figure 4.9 The graph shows that slew rate of the positive voltage regulator                                                                       |

| increasing with frequency                                                                                                                         |

| Figure 4.10 Stability circles for circuit positive voltage regulator A                                                                            |

| Figure 4.11 Stability circles for circuit positive voltage regulator B                                                                            |

| Figure 4.12 Stability circles for circuit positive voltage regulator C   40                                                                       |

| Figure 4.13 Graphical output from S-parameter simulation for positive voltage                                                                     |

| regulator with $\epsilon_r$ =9.6, H=0.25mm, T=34.79 $\mu$ m, W=0.625mm,                                                                           |

| $L=1.25$ mm, $Zo=50\Omega$ 41                                                                                                                     |

| Figure 4.14 Graphical output for noise factor from S-parameter simulation for positive                                                            |

| voltage regulator with $\varepsilon_r$ =9.6, H=0.25mm, T=34.79 $\mu m,$ W=0.625mm,                                                                |

| L=1.25mm, Zo= $50\Omega$ 41                                                                                                                       |

| Figure 4.15         Graphical output from S-parameter simulation for positive voltage         regulator                                           |

| with $\varepsilon_r\!=\!4.0,$ H=0.762mm, T=34.79 $\mu$ m, W=0.625mm, L=1.25mm,                                                                    |

| $Zo=50\Omega$ 42                                                                                                                                  |

| Figure 4.16 Graphical output for noise factor from S-parameter simulation for positive                                                            |

| voltage regulator with $\varepsilon_r\!=\!\!4.0,$ H=0.762mm, T=34.79 $\mu m,$ W=0.625mm,                                                          |

| $L=1.25$ mm, $Zo=50\Omega$                                                                                                                        |

|                                                                                                                                                   |

| Figure 4.17 Graphical output from S-parameter simulation for positive voltage                                                                     |

| Figure 4.17 Graphical output from S-parameter simulation for positive voltage regulator with $\epsilon_r$ =4.0, H=0.762mm, T=34.79µm, W=5.6157mm, |

| Figure 4.18 Graphical output for noise figure from S-parameter simulation for positive                               |

|----------------------------------------------------------------------------------------------------------------------|

| voltage regulator with $\varepsilon_r$ =4.0, H=0.762mm, T=34.79 $\mu$ m, W=5.6157mm,                                 |

| $L=11.23$ mm, $Zo=16.67\Omega$ 43                                                                                    |

| Figure 4.19         Layout of positive voltage regulator using Alumina                                               |

| Figure 4.20 The graph shows linear relationship between input and output voltage47                                   |

| Figure 4.21 Graphical output for negative voltage regulator when                                                     |

| V <sub>in</sub> =1.4V at 1.9GHz                                                                                      |

| Figure 4.22 Graphical output for negative voltage regulator when                                                     |

| V <sub>in</sub> =2.8V at 1.9GHz                                                                                      |

| Figure 4.23 Relationship between positive peak offset and input voltage                                              |

| Figure 4.24 Relationship between negative peak offset and input voltage                                              |

|                                                                                                                      |

| Figure 4.25 The graph shows that slew rate of the negative voltage regulator increasing                              |

| Figure 4.25       The graph shows that slew rate of the negative voltage regulator increasing         with frequency |

|                                                                                                                      |

| with frequency                                                                                                       |

| Figure 4.29 Graphical output for noise factor from S-parameter simulation for negative |

|----------------------------------------------------------------------------------------|

| voltage regulator with $\epsilon_r$ =4.0, H=0.762mm, T=34.79µm, W=0.625mm,             |

| L=1.25mm, Zo=50Ω54                                                                     |

| Figure 4.30 Graphical output from S-parameter simulation for negative voltage          |

| regulator S-parameter simulation result with $\epsilon_r$ =4.0, H=0.762mm,             |

| $T=34.79\mu m$ , $W=5.6157mm$ , $L=11.23mm$ , $Zo=16.67\Omega$ 55                      |

| Figure 4.31 Graphical output for noise factor from S-parameter simulation for negative |

| voltage regulator S-parameter simulation result with $\varepsilon_r$ =4.0, H=0.762mm,  |

| $T=34.79\mu m$ , $W=5.6157mm$ , $L=11.23mm$ , $Zo=16.67\Omega$ 55                      |

| Figure 4.32    Layout of negative voltage regulator using FR4                          |

| Figure 4.33 Graph showing linearity between input and output voltage                   |

| Figure 4.34       Graph showing linearity between input and output voltage             |

| Figure 4.35 Graph showing linearity between input and output voltage                   |

| Figure 4.36 Ripple rejection input and output voltage from transient response analysis |

| for ripple rejection circuit designed using FR4 (Microstrip of | characteristics: |

|----------------------------------------------------------------|------------------|

|----------------------------------------------------------------|------------------|

$$\epsilon_r$$

=4.0,H=0.762mm,T=34.798 $\mu$ m,W=0.625mm,L=1.250mm,Zo= 50 $\Omega$ ).....63

# Figure 4.37 Graph showing the linear relationship between output

Figure 4.39 Stability circles for circuit ripple rejection voltage regulator C ......67

**Figure 4.40** Graphical output from S-parameter simulation for ripple rejection regulator with  $\epsilon_r$ =9.6, H=0.25mm, T=34.79µm, W=0.625mm,L=1.25mm ......68

| Figure 4.42 | Graphical output from S-parameter simulation for ripple rejection voltage |  |

|-------------|---------------------------------------------------------------------------|--|

|             | regulator with $\epsilon_r$ =4.0, H=0.762mm, T=34.79 $\mu$ m, W=0.625mm,  |  |

|             | L=1.25mm, Zo= 50Ω69                                                       |  |

**Figure 4.43** Graphical output for noise factor from S-parameter simulation for ripple rejection voltage regulator with  $\epsilon_r$ =4.0, H=0.762mm, T=34.79µm, W=0.625mm, L=1.25mm, Zo= 50Ω .....69

Figure 4.44 Graphical output from S-parameter simulation for ripple rejection voltage regulator with  $\epsilon_r$ =4.0, H=0.762mm, T=34.79µm, W=5.6157mm, L=11.23mm, Zo= 0.25 $\Omega$  .....70

| <b>Table 4.4</b> Results for the negative voltage regulator                                       |

|---------------------------------------------------------------------------------------------------|

| <b>Table 4.5</b> Slew rate of the negative voltage regulator with varying frequency               |

| Table 4.6 Results from the negative voltage regulator s-parameter simulation with different       |

| microstrip characteristics                                                                        |

| Table 4.7 Output from the ripple rejection regulator using different microstrip                   |

| characteristics(Microstrip characteristics: Substrate= Alumina, $\varepsilon_r$ =9.6,             |

| H=0.25mm, T=34.798μm, W=0.625mm, L=1.250mm, Zo= 50Ω)57                                            |

| <b>Table 4.8</b> Output from the ripple rejection regulator using different microstrip            |

| characteristics (Microstrip characteristics: $\varepsilon_r$ =4.0, H=0.762mm, T=34.798 $\mu$ m,   |

| W=0.625mm, L=1.250mm, Zo= 50Ω)                                                                    |

| <b>Table 4.9</b> Output from the ripple rejection regulator using different microstrip            |

| characteristics (Microstrip characteristics: $\varepsilon_r$ =4.0, H=0.762mm, T=34.798 $\mu$ m,   |

| W=5.6157mm, L=11.23mm, Zo= 0.25Ω)61                                                               |

| <b>Table 4.10</b> Results from the transient response simulation for ripple rejection voltage     |

| regulator using different microstrip characteristics                                              |

| Table 4.11         Output voltage of the ripple rejection voltage regulator                       |

| at different frequencies64                                                                        |

| <b>Table 4.12:</b> Slew rate of the ripple rejection voltage regulator at different frequencies65 |

| <b>Table 4.13</b> Results from the s-parameter simulation for ripple rejection voltage regulator  |

| with different microstrip characteristics                                                         |

| Table 4.14 Positive voltage regulator                                                             |

| Table 4.15 Negative voltage regulator                                                             |

| Table 4.16 Ripple rejection voltage regulator                                                     |

#### **Chapter 1**

#### **INTRODUCTION**

#### 1.1 Introduction

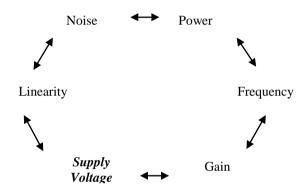

RF circuits must process analog signals with a wide dynamic range at high frequencies. It is interesting to note that the signal must be treated as analog even if the modulation is digital or the amplitude carries no information. The trade-offs involved in the design of such circuits can be summarized in the RF Design Hexagon, where almost any two of the six parameters trade with each other to some extent (Behzad Razavi 2001).

Figure 1.1 RF Design Hexagon (Source: Behzad Razavi 2001)

In the communication system, we cannot overlook the importance of having a good source in the early stages of the system. Communication system consists of various circuits and having a good and regulated source is crucial in order to get the desired signals at the output. The common problems in getting such good sources are spikes, ripple and fluctuating DC input.

Voltage regulator circuits designed throughout this project should perform an excellent task to minimize the flaw of the RF circuitry element such as band pass filters performance which used in the transceiver circuits. Regulator circuits perform important task because it is nearly impossible to design an ideal filter (without having ripple) in reality. Regulator circuits will make the ripple as constant as possible and this will help in the realization of the ideal filter.

Voltage regulator circuits designed through out this project are basically using the schematics that usually used in the low frequency range which utilization is in devices such as microprocessor board. Schematics from two integrated circuits will be implemented which are LM317 and  $\mu$ A723.

Because of the availability and excellent performances for most of the voltage regulators in the market, people nowadays treat voltage regulators as a 'black-box' that will function automatically once the switch is on. The famous three-terminal regulator such as LM317 which is simple and easy to use is the most sought after regulator products which the enhancement of their functions and capabilities is revolving through times. Many established manufacturers such as National Semiconductor, TEXAS and SGS Thompson have produced their very own products of voltage regulators and one of the recent products of National Semiconductor is a low noise 150mA Voltage Regulator, LP3999 for powering RF and analog circuits.

Through this project voltage regulators used are treated as a 'white box' where the large circuits of the existing voltage regulators is implemented using the schematics of LM317 and  $\mu$ A723. Instead of the complexity of the LM317 which consist almost 30 active transistors in one chip, the design is used to design a ripple rejection regulator which functions to give smoother and better source to the circuit that will be used.

The LM317 schematic circuit that is used is taken from US Microwave. This voltage regulator is exceptionally easy to use and requires only two external resistors to set the output voltage. Further it employs internal current limiting; thermal shutdown and safe area compensation making it essentially blow-out proof. The USM LM317 serves a wide variety of applications including the local and on card regulation.

The schematic circuit of  $\mu$ A723 voltage regulator is taken from TEXAS Instruments data sheet which is known as a precision voltage regulator. It is the direct replacements for Fairchild  $\mu$ A723c fourteen-terminal classical design and features high ripple rejection, excellent input and load regulation, excellent temperature stability and low standby current. The circuit consists of a temperature-compensated referencevoltage amplifier, an error amplifier, a 150-mA output transistor and an adjustable output current limiter.

$\mu$ A723 is the essential circuit to build positive and negative voltage regulators. In this project  $\mu$ A723 is not use to supply the RF circuit with the positive or negative

voltage values but their function is to detect the ripple constructed in the positive and negative cycles of the supply voltage.

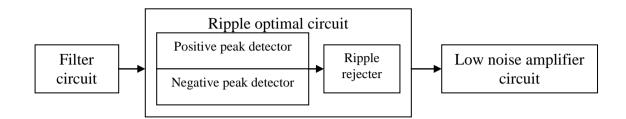

The application of the design in RF transceiver system is as illustrated below:

Figure 1.2 Voltage regulator design in RF transceiver system

Ideally, the output of the filter circuit should be ripple free but in practical this phenomenon is not possible as many variations exist. Ripple optimal circuit is used to eliminate or at least minimize the ripples exist in the filter circuits and give the smooth input to the amplifier circuit in the transceiver system.

Firstly for this particular project the operating bandwidth is determined which is between 80MHz to 200MHz which means the ripple optimal circuit can be used for the signal filtered between this ranges.

Secondly, the output of the filtered signal becomes the input to the ripple optimal circuit. The ripple optimal circuit will measure the ripples in positive voltage peak and then switches to measure the ripples in the negative voltage peak.

Thirdly, the ripple rejecter will reject the ripples measured by those two circuits and the smoother voltage will be supplied to the amplifier circuit in the transceiver system.

### **1.2** Scope of the Project

This project covers schematics drawings, analysis and layout of positive voltage regulator, negative voltage regulator and ripple rejection voltage regulator. Upon completion of this project, several design tools and computation tools will be used. The tools are Electronics Workbench 5.12 and Agilent Advanced Design System (ADS) 2004A for the design works, Z-match Software and Microsoft Excel XP for the computation.

#### Chapter 2

#### LITERATURE SURVEY

#### 2.1 Introduction to Linear Regulator

In electronics, a voltage regulator is a source circuit designed to supply a steady, constant voltage output. Voltage regulators operate by comparing the actual output voltage to some internal fixed reference voltage. Any difference is amplified and used to control the series regulation element, which usually one or more heavy-duty transistors. This forms a negative feedback control loop. If the load demands changes, a rise in current will generally cause a small drop in the output voltage, which will cause the circuit to turn on the series element more strongly, restoring the voltage to its desired level.

Solid state regulator semiconductor chips in either fixed or variable types. Common solid-state series voltage regulators are the LM78xx (for positive voltages) and LM79xx (for negative voltages), and common fixed voltages are 5V (for transistor-transistor logic circuit) and 12V for example in personal computer.

Linear regulators exist in two basic forms: series regulators and shunt regulators. Series regulators are the more common form. The series regulator works by providing a path from the supply voltage to the load through a variable resistance (the main transistor is in the "top half" of the voltage divider).

The shunt regulator works by providing a path from the supply voltage to ground through a variable resistance (the main transistor is in the "bottom half" of the voltage divider). The current through the shunt regulator is diverted away from the load and flows uselessly to ground, making this form even less efficient than the series regulator. It is, however, simpler, sometimes consisting of just a voltage-reference diode, and is used in very low powered circuits where the wasted current is too small to be of concern.

All linear regulators require an input voltage at least some minimum amount higher than the desired output voltage. That minimum amount is called the drop out voltage. For example, a common regulator such as the 7805 has an output voltage of 5 V, but can only maintain this if the input voltage remains above about 7 V. Its drop-out voltage is therefore 7 V - 5 V = 2 V. When the supply voltage is less than about 2 V above the desired output voltage, as is the case in low-voltage microprocessor power supplies, so-called low dropout regulators (LDOs) must be used.

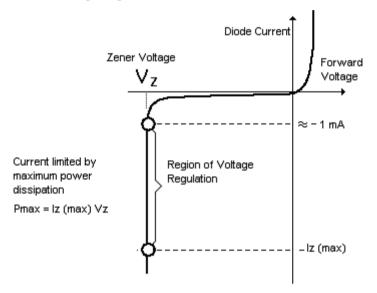

### 2.2 Zener Diode Voltage Regulator

A voltage regulator circuit is required to "maintain a constant dc output voltage" across the load terminals instead of the variation of input main voltage and changes in temperature and load current. The fact that zener diode voltage  $V_z$  remains the same instead of changes in zener current,  $I_z$  at the negative saturation region enables it to be an essential element in voltage regulator circuit.

Figure 2.1 Characteristic of zener diode (Source: Sheng Bao, Dept. of Information Engineering, Nanjing Univ. of P. & T.)

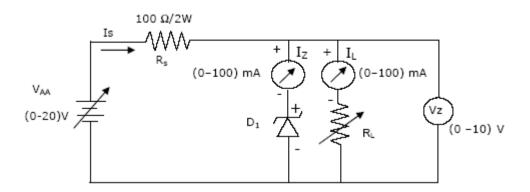

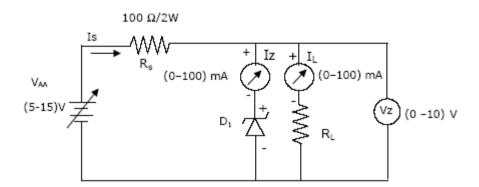

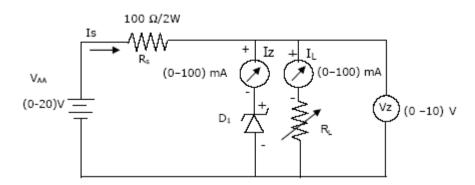

The basic circuit for a voltage regulator consists of a zener diode, voltage source, current limiting and load resistors is shown in **Figure 2.2**. For this purpose, a zener diode is operated always in the reverse biased condition. Here, the zener diode is operated in its breakdown region and is used to regulate the voltage across a load when there are variations in the supply voltage or load current.

Figure 2.2 Basic zener diode voltage regulator circuit (Source: www.ycmou.com)

The **Figure 2.2** shows the zener voltage regulator, it consists of a current limiting resistor  $R_s$  connected in series with the input voltage  $V_s$  and zener diode is connected in parallel with the load  $R_L$  in reversed biased condition. The output voltage is always selected with a breakdown voltage  $V_z$  of the diode.

The input source current,

$$I_s = I_z + I_l \tag{2.1}$$

The drop across the series resistance,

$$\mathbf{R}_s = V_{in} - V_z \tag{2.2}$$

Current flowing through it,

$$I_{S} = \frac{V_{in} - V_{Z}}{R_{S}} \tag{2.3}$$

From equation (2.1) and (2.2), we get,

$$\frac{\left(V_{in} - V_{z}\right)}{R_{s}} = I_{z} + I_{l} \tag{2.4}$$

#### 2.3 Regulation with a Varying Input Voltage (Line Regulation)

It is defined as the change in regulated voltage with respect to variation in line voltage with respect to variation in line voltage. Input voltage varies but the load resistance remains constant hence, the load current also remains constant. As the input voltage increases, from equation (2.3)  $I_s$  also increases accordingly. Therefore, zener current  $I_z$  will increase to. The extra voltage is dropped across the  $R_s$ . Since, increased

$I_z$  will still have a constant  $V_z$  and  $V_z$  is equal to  $V_{out}$  and hence the output voltage will remain constant.

If there is a decrease in  $V_{in}$ ,  $I_z$  decreases as load current remains constant and voltage drop across  $R_s$  is reduced. But even though  $I_z$  may change,  $V_z$  remains constant hence, output voltage still remains constant.

Figure 2.3 Line regulation in zener regulator (Source: www.ycmou.com)

Using the formula, line regulation is calculated as below

% Line regulation =

$$\frac{V HL - V LL}{V NOM} x100$$

(2.5)

Note that output voltage as a load voltage with high line voltage ' $V_{HL}$ ' and as a load voltage with low line voltage ' $V_{LL}$ '.  $V_{NOM}$  is the nominal load voltage under the typical operating conditions. For example  $V_{NOM} = 9.5 \pm 4.5$ V.

#### 2.4 Regulation with the Varying Load (Load Regulation)

It is defined as change in load voltage with respect to variations in load current. To calculate this regulation, input voltage is set to constant so that the output voltage varies due to the changes in the load resistance value. Consider output voltage is increased due to increasing in the load current, the left of the equation (2.4) is constant as the input voltage  $V_{in}$ ,  $I_s$  and  $R_s$  is constant. Then as load current changes, the zener current  $I_z$  will also change but in the opposite direction way such that the sum of  $I_z$  and  $I_L$  will remain constant. Thus, the load current increases, the zener current decreases but sum is still remains constant. From reverse bias characteristic even  $I_z$  changes,  $V_z$  remains the same thus the output voltage remains fairly constant.

Figure 2.4 Load regulation in zener regulator (Source: www.ycmou.com)

The load regulation can still be calculated by

%Load regulation =

$$\frac{(V_{NL} - V_{FL})}{V_{FL}} x100$$

(2.6)

Note that there is no load voltage  $V_{NL}$  for maximum load resistance value and full load voltage  $V_{FL}$  for minimum load resistance value.

### 2.5 Drawbacks of the Zener Diode Voltage Regulator Applications

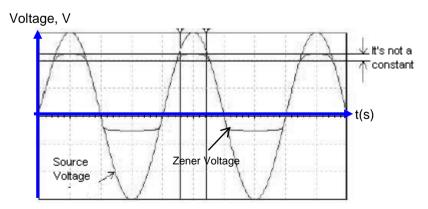

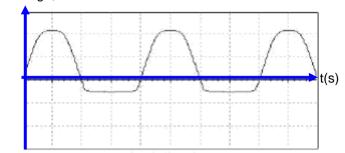

The simplest regulation circuit using zener diode has many disadvantages. Firstly it can not provide a truly constant voltage. The wave form in **Figure 2.6** has a nonlinear curve while the true constant voltage is the horizontal line. Secondly, if we put them together, we will find that the voltage of zener diode is not an exact constant even the source voltage is high enough to make the zener diode reverse bias break down but instead there is still some little curve at the edge.

Figure 2.5 Output waveform from zener diode voltage regulator plotted on the same axis with the input waveform (Source: Sheng Bao, Dept. of Information Engineering, Nanjing Univ. of P. & T.)

Zener voltage, V

Figure 2.6 Output waveform from zener diode voltage regulator (Source: Sheng Bao, Dept. of Information Engineering, Nanjing Univ. of P. & T.)

Because of the drawbacks of the classical zener diode voltage regulator, the applicable voltage regulator which is a feedback-network-based circuit is implemented.

#### 2.6 The Feedback Network

It consists of three parts: the reference voltage, the controlled source and the error amplifier. A regulator changes some quantities that affect the output voltage when the output does not match our requirement. So the circuit contains a sampling terminal to obtain the information about the output. Also it contains a reference voltage in order to judge whether the output matches our requirement and this two information would be compared so that the adjusting device can make operation to regulate the output according to the compared result. A linear regulator is a voltage regulator based on the operation of a transistor within its linear region.

Figure 2.7 Block diagram of voltage regulator (Source: Sheng Bao, Dept. of Information Engineering, Nanjing Univ. of P. & T.)

The reference voltage is provided by a source that is constant. We can easily find two reference voltages, the ground and the zener diode. The real ground is difficult to find and in many cases the ground is not really connected. So zener diode is used. If the voltage over the two terminals of zener diode doesn't alternate very frequently and the voltage is much higher than the breakdown voltage, it could be considered as a reference voltage.

The comparator is also called the error amplifier. It is such kind of device that its output is related to the voltage difference of two input terminal. It is actually a specially connected operational amplifier. The operational amplifier has a very typical application is the difference amplifier. The closed loop gain is determined by the resistors in the feedback network. So it is sure an ideal device of making the comparator. The relationship of output voltage and input difference should be the same with the controlled source. For example, if the output of comparator is an exponential function of the power output voltage, then the controlled source should control the power output voltage.

The feedback signal needs to be applied by the controlled source. Generally, this job is done by BJT and FET whose control signal is sent by the comparator. The output voltage is regulated by meaning of controlling the output current.

#### 2.7 Noise in Integrated Circuit

Noise however is one of the main constraints to design electronics circuits. The noise phenomenon is considered here are caused by the small current change and voltage fluctuations that are generated within the devices themselves and we specifically exclude extraneous pickup of man-made signals that can also be a problem in high-gain circuits. The existence of noise is basically due to the fact that electrical charge is not continuous but is carried in discrete amounts equal to the electron charge, and thus noise is associated with fundamental processes in the integrated-circuit devices.

Various sources of electronic noise are considered such as Shot Noise, Thermal Noise, Flicker Noise, Burst Noise and Avalanche Noise. Shot Noise is always associated with a direct-current flow and is present in diodes, MOS, transistors and bipolar transistor. Thermal Noise is generated by a completely different mechanism from Shot Noise. In conventional resistors it is due to the random thermal motion of the electrons and is unaffected by the presence or absence of direct current but is related to

absolute temperature, T. Flicker Noise is a type of noise found in all active devices, as well as in some discrete passive elements such as carbon resistors. Flicker Noise is caused mainly by traps associated with contamination and crystal defects. Burst Noise is found in some integrated circuits and discrete transistors and is cause by the presence of heavy-metal ion contamination. Avalanche Noise is a form of random noise produced by zener or avalanche breakdown in a p-n junction.

Methods of circuit calculations with noise generators as sources must be established, and attention is now given to this problem. Consider a noise current source with mean-square value

$$i^2 = S(f) \Delta f \tag{2.7}$$

where S(f) is the noise spectral density. The value of S(f) is plotted versus frequency. In a small bandwidth  $\Delta f$  the mean- square value of the noise current is given by the equation above and the rms value can be written as

$$i = \sqrt{S(f) \Delta f} \tag{2.8}$$

The noise current in bandwidth  $\Delta f$  can be represented approximately by a sinusoidal current generator with rms value *i*. If the noise current in bandwidth  $\Delta f$  is now applied as an input signal to a circuit, its effect can be calculated by substituting the sinusoidal generator and performing circuit analysis in the usual fashion. When the circuit response to the sinusoid is calculated, the mean square value of the output sinusoid gives the mean-square value of the output noise in bandwidth  $\Delta f$ . Thus network noise calculations reduce to a familiar sinusoidal circuit-analysis calculation. The only difference occurs when multiple noise sources are applied, as is usually the case in practical circuits. Each noise is represented by a separate sinusoidal generator, and the output contribution of each one is separately calculated. The total output noise in bandwidth  $\Delta f$  is calculated as a mean-square value by adding the individual mean-square contributions from each output sinusoid. This depends, however, on the original noise sources being independent. For example consider two resistors R<sub>1</sub> and R<sub>2</sub> connected in series. Resistors R<sub>1</sub> and R<sub>2</sub> have respective noise generators.

$$\overline{v_1^2} = 4kt R_1 \Delta f \tag{2.9}$$

$$\overline{v_1^2} = 4ktR_2\Delta f \tag{2.10}$$

In order to calculate the mean-square noise voltage  $v_T^2$  produced by two resistors in series, let  $v_T(t)$  be the instantaneous values of the individual generators. Then

$$\overline{v_T(t)} = v_1(t) + v_2(t)$$

(2.11)

and thus

$$\overline{v_T(t)^2} = \overline{\left[v_1(t) + v_2(t)\right]^2}$$

(2.12)

$$\overline{v_T(t)^2} = \overline{v_1(t)^2} + \overline{v_2(t)^2} + \overline{2v_1(t)v_2(t)}$$

(2.13)

Now since noise generators  $v_1(t)$  and  $v_2(t)$  arise from separate resistors, they must be independent. Thus the average value of their product

$$\overline{vT^2} = \overline{v1^2} + \overline{v2^2}$$

(2.14)

Thus the mean-square value of the sum of a number of independent noise generators is the sum of the individual mean-square values. Substituting the equations;

$$\overline{vT^2} = 4Kt(R_1 + R_2)\Delta f \tag{2.15}$$

The equation above is just the value that would be predicted for thermal noise in resistor  $(R_1 + R_2)$  and thus the results are consistent. These results are also consistent with the representation of the noise generators by independent sinusoids as described earlier. It is easily shown that when two or more such generators are connected in series, the mean square value of the total voltage is the mean-square value of the individual mean-square values.

The most general method of specifying the noise performance of circuits is by specifying input noise generators. However, a number of specialized methods of specifying noise performance have been developed that are convenient in particular situations. Two of these methods are now described.

The noise figure (F) is a commonly used method of specifying the noise performance of a circuit or a device. Its disadvantage is that it is limited to situations where the source impedance is resistive, and this precludes its use in many applications where noise performance is important. However, it is widely used as a measure of noise performance in communication systems.

The definition of noise figure of a circuit is

$$F = \frac{\text{input S/N ratio}}{\text{output S/N ratio}}$$

(2.16)

F is usually expressed in decibels. The utility of the noise figure concept is apparent from the definition, as its gives a direct measure of the signal-to-noise (S/N) ration degradation that is caused by the circuit. For example, if the S/N ratio at the input to circuit is 50dB, and the circuit noise figure is 5dB, then the S/N ratio at the output of the circuit is 45dB.

Consider the circuit below, where S represents signal power and N represents noise power. The input noise power  $N_i$  is always taken as the noise in the source resistance. The output noise power  $N_o$  is the total output noise including the circuit contribution and noise transmitted and noise transmitted from the source resistance.

Figure 2.8 Two port network representing signal and noise power (Source: Gray, Hurst, Lewis, Meyer 2001)

The noise figure (F) is

$$F = \frac{S_i N_o}{N_i S_o} \tag{2.17}$$

For an ideal noiseless amplifier, all output noise comes from the source resistance at the input, and thus G is the circuit power gain, then the output signal,  $S_o$  and the output noise  $N_o$  are given by

$$S_o = GS_i \tag{2.18}$$

$$N_o = GN_i \tag{2.19}$$

A useful alternative definition of *F* may be derived as follows;

$$F = \frac{S_i N_o}{N_i S_o} \tag{2.20}$$

$$=\frac{N_{O}}{GN_{i}}$$

(2.21)

Equation (2.21) can be expressed as below

$$F = \frac{\text{Total output noise}}{\text{That part of the output noise due to the source resistance}}$$

(2.22)

Note that since *F* is specified by a power ratio, the value in decibels is given by  $10\log_{10}$  (numerical ratio).

The calculations of the previous sections have shown that the noise parameters of most circuits vary with frequency, thus the bandwidth must be specified when the noise figure of a circuit is calculated. The noise figure is often specified for a small bandwidth  $\Delta f$  at a frequency f where  $\Delta f \ll f$ . This is called the spot noise figure and applies to tuned amplifiers and also to broadband amplifiers that may be followed by frequency selective circuits. For broadband amplifiers whose output is utilized over a wide bandwidth, an average noise figure is often specified. This requires calculation of the total output noise over the frequency band of interest using the methods described. (Gray, Hurst, Lewis, Meyer 2001)

From the S-parameter simulation using ADS, input and output noise factors are represented by nf(1) and nf(2) respectively and expressed in decibels. From these values we can determine the circuit noise figure, *F*.

$$F = \frac{P_{No}}{P_{Ni}G_A} \tag{2.23}$$

where  $P_{No}$  and  $P_{Ni}$  is the total available noise power at the output and input respectively and  $G_A$  is the gain of the circuit. (Guillermo Gonzalez, 1997)

### 2.8 Introduction to Slew Rate

One of the practical limitations is the rate at which the output voltage changes. The limiting rate of change for a device is called its slew rate. Slew rate is the maximum rate of change of the output voltage,  $\Delta V_{out}$  in response to a step input voltage,  $\Delta t$ .

Slew rate =

$$\left| \frac{\Delta V_{\text{out}}}{\Delta_t} \right|_{\text{max}}$$

(2.24)

The slew rate imposes high frequency limitations on the devices. At some critical frequency, an output swing equal to the supply voltages will require a slew rate faster than slew rate of the device. Above that frequency, the amplitude of distortion free output voltage swing will be limited.

There are two types of slew rate; rising slew rate and falling slew rate.

Falling slew rate =

$$\frac{(V_{reff out low}) \cdot (V_{reff out high})}{Fall time(\Delta t)} \quad V/s \quad (2.25)$$

Rising slew rate =

$$\frac{\left(V_{\text{reff out high}}\right) - \left(V_{\text{reff out low}}\right)}{\text{Fall time}(\Delta t)} \quad V/s \quad (2.26)$$

Figure 2.9 The measurement of slew rate parameters (Source: www.zone.ni.com)

#### 2.9 Circuit Gain

Gain is the factor by which the signal is amplified and often expressed in decibels (dB). In low frequencies, gain as a function of frequency is commonly referred to as the magnitude of the frequency response function. In high frequencies, S-parameters are analogous to frequency response as will be explained in the latter stage.

Circuit gain =

$$|\mathbf{S}_{21}|$$

(2.27)

S-parameter is the abbreviation of scattering parameters which express the reflection and transmission coefficients between incident and reflection waves. It describes completely the behavior of a device under linear conditions at microwave frequency range. Each parameter is typically characterized by magnitude, decibel and decibel and phase.

**Figure 2.10** A two-port S-parameter matrix records the reflection coefficients and transmission gain from both sides of the DUT (**Source:** www.sss.mag.com)

### **2.10** Reflection Coefficient, $\Gamma_0$

Reflection coefficient is defined as the ratio of the incident to the reflected wave along a transmission line. Reflection coefficient at any position, d,

$$\Gamma_{in} = \frac{B_1}{A_1} e^{-2j\beta d} \tag{2.28}$$

at load end where d=0

$$\Gamma_o = \Gamma_{in}(o) = \frac{B_1}{A_1} \tag{2.29}$$

where  $B_1$  is the incident wave and  $A_1$  is the reflected wave, hence can be expressed in the form

$$\Gamma_{in}(d) = \Gamma_{o}e^{-j2\beta d} \tag{2.30}$$

$$V(d) = A_1 \left( e^{j\beta d} + \Gamma_0 e^{-j\beta d} \right) = A_1 e^{j\beta d} \left( 1 + \Gamma_0 e^{-j2\beta d} \right)$$

(2.31)

and

$$I(d) = \frac{A_1}{Z_o} \left( e^{j\beta d} + \Gamma_o e^{-j\beta d} \right) = \frac{A_1}{Z_o} e^{j\beta d} \left( 1 + \Gamma_o e^{-j2\beta d} \right)$$

(2.32)

The value of the complex constant A<sub>1</sub> is obtained by using a known value of V(d) (for i.e., a boundary condition), usually the value of V(d) at the source end (i.e., at d=l). Of course, the value of V(d) at d=l depends on the source amplitude and phase and source impedance connected to the line at d=l. The input impedance of the transmission line at any position, d is defined as

$$Z_{in}(d) = \frac{V(d)}{I(d)} = Z_o \frac{e^{j\beta d} + \Gamma_o^{-j\beta d}}{e^{j\beta d} - \Gamma_o^{-j\beta d}}$$

(2.33)

In the equation above, the constant  $\Gamma_0$  can be evaluated using the boundary condition at the load, namely that the value of the input impedance at d=0 must be equal to  $z_L$ . That is,

$$Z_{in}(0) = Z_L \tag{2.34}$$

Then from (2.33)

$$\Gamma_o = \frac{Z_L - Z_o}{Z_L + Z_o} \tag{2.35}$$

During the Advanced Design System (ADS) S-parameter simulation,  $S_{11}$  and  $S_{22}$  give the value of reflection coefficients at terminated output and input respectively. From the reflection coefficient we can derive the reflection loss, return loss and VSWR of the circuit.

#### 2.11 Voltage Standing Wave Ratio, (VSWR)

The degree to which terminating resistance matches the characteristic impedance is indicated using the VSWR.VSWR, may be illustrated by considering the voltage at various points along a cable driving a poorly matched antenna. The addition of the two waves traveling in opposite directions in a transmission line produces a standing-wave pattern-that is a sinusoidal function of time whose amplitude is a function of position. (Guillermo Gonzalez, 1997)

The magnitude of the voltage along the line is given by

$$|V(d)| = |A_1| |1 + |\Gamma_0 e^{-j2\beta d}|$$

(2.36)

From (4.16), it follows that the maximum value of |V(d)| along the line has the value

$$|V(d)|_{\max} = |A_1|(1+|\Gamma_0|)$$

(2.37)

and the minimum value of |V(d)| is

$$|V(d)|_{\min} = |A_1|(1-|\Gamma_0|)$$

(2.38)

These value are used to define the voltage wave standing ratio (VSWR), namely

VSWR =

$$\frac{|V(d)|_{\max}}{|V(d)|_{\min}} = \frac{1+|\Gamma_o|}{1-|\Gamma_o|}$$

(2.39)

From the S-parameter simulation, we can get the value of VSWR in

$$VSWR_{in} = \frac{1 + |S_{11}|}{1 - |S_{11}|}$$

(2.40)

and the value of VSWR out is

$$VSWR_{out} = \frac{1 + |S_{22}|}{1 - |S_{22}|}$$

(2.41)

A mismatched antenna reflects some of the incident power back toward the transmitter and since this reflected wave is traveling in the opposite direction as the incident wave, there will be some points along the cable where the two waves are in phase and other points where the waves are out of phase (assuming a sufficiently long cable). If one could attach an RF voltmeter at these two points, the two voltages could be measured and their ratio would be the VSWR. By convention, this ratio is calculated with the higher voltage in the numerator so that the VSWR is one or greater. The VSWR for terminations between these two extremes may be calculated by considering the interaction of the reflected wave with the incident wave to determine the minimum and maximum voltages. But, as it turns out, the VSWR is simply the ratio of the resistance of the termination and the characteristic impedance of the line. For example, a 75 ohm load will give a VSWR of 1.5 when used to terminate a 50 ohm cable since 75/50 = 1.5. A 25 ohm resistor will give a VSWR of 2 since 50/25 = 2. Note that the larger resistance is always used in the numerator by convention.

### 2.12 Return Loss

Return loss is simply the amount of power that is lost to the load and does not return as a reflection. High return loss is usually desired even though "loss" has negative connotations. Return loss is commonly expressed in decibels. If one half of the power does not reflect from the load, the return loss is 3dB.

Input return loss =

$$10\log_{10}|\mathbf{S}_{11}|^2|\mathbf{dB}$$

(2.42)

Output return loss =

$$10\log_{10}|s_{22}|^2$$

dB (2.43)

### 2.13 Stability Considerations

The stability of a circuit, or its resistance to oscillate, is a very important consideration in a design and can be determined from the S parameters, the matching network, and the terminations. In a two-port network, oscillations are possible either input or output port presents a negative resistance. This occurs when  $|\Gamma_{in}| > 1 \text{ or } |\Gamma_{out}| > 1$ , which for unilateral device occurs when S|11| > 1 or |S22| > 1. For example a unilateral transistor is a transistor where  $S_{12} = 0$  (or its effect so small that it can be set equal to zero). If  $S_{12} = 0$ , it follows from (2.46) and (2.47) that  $|\Gamma_{in}| = |S_{11}|$  and  $|\Gamma_{out}| = |S_{22}|$ . Hence, if  $S_{11} > 1$  the transistor presents a negative resistance at the input, and if  $S_{22} > 1$  the transistor presents a negative resistance at the output.

The two-port network is said to unconditionally stable at a given frequency if the real parts of  $Z_{in}$  and  $Z_{out}$  are greater than zero for all passive load and source impedances. If the two-port is not unconditionally stable, it is potentially unstable. That is some passive load and source terminations can produce input and output impedances having a negative real part.

In term of reflection coefficients, the conditions for unconditionally stability at a given frequency are

$$\left|\Gamma_{s}\right| < 1 \tag{2.44}$$

$$|\Gamma_L| < 1 \tag{2.45}$$

$$\left|\Gamma_{in}\right| = \left|S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}\right| < 1$$

(2.46)

$$\left|\Gamma_{out}\right| = \left|S_{22} + \frac{S_{12}S_{21}\Gamma_s}{1 - S_{11}\Gamma_s}\right| < 1$$

(2.47)

We now return to the necessary and sufficient conditions for a two-port network to be unconditionally stable. A straightforward but somewhat lengthy manipulation of (2.44) to (2.47) results in the following necessary and sufficient conditions for conditional stability

and

$$1 - |s_{11}|^2 > |s_{12}s_{21}| \tag{2.49}$$

$$1 - |s_{22}|^2 > |s_{12}s_{21}| \tag{2.50}$$

where

$$\mathbf{K} = \frac{1 - |s_{11}|^2 - |s_{22}|^2 + |\Delta|^2}{2|s_{12}s_{21}|}$$

(2.51)

and

$$\Delta = S_{11}S_{22} - S_{12}S_{21} \tag{2.52}$$

Hence, a convenient way of expressing the necessary and sufficient conditions for unconditional stability is determine by the stability factors, K and  $\Delta$  where

$$K > 1$$

(2.53)

$$\left|\Delta\right| < 1 \tag{2.54}$$

From a theoretical point of view, a two-port network can have any value of K and  $|\Delta|$ . From a practical point of view, most microwave transistors produced by manufacturers are either unconditionally stable or potentially unstable with K <1 and  $|\Delta|$  <1. In fact, in potentially unstable transistors most practical values of K are such that 0<K<1. (Guillermo Gonzalez, 1997)

#### 2.14 Microstrip Characteristics

As circuits have been reduced in size with integrated semiconductor electron devices, a transmission structure was required that was compatible with circuit construction techniques to provide guided waves over limited distances. This was realized with a planar form of single wire transmission line over a ground plane, called microstrip. Microstrip employs a flat strip conductor suspended above a ground plane by a low-loss dielectric material. The size of the circuit can be reduced through judicious use of a dielectric constant some 2-10 times that of free space (or air), with a penalty that the existence of two different dielectric constants (below and above the strip) makes the circuit difficult to analyze in closed form (and also introduces a variability of propagation velocity with frequency that can be a limitation on some applications).The advantages of microstrip have been well established, and it is a convenient form of transmission line structure for probe measurements of voltage, current and waves.

Figure 2.11 Cross section of a microstrip ( Source: Dan McMahill,http://prdownloads.sourceforge.net)

The most important characteristics of microstrip is its dimension, substrate used to construct microstrips and characteristic impedance,  $Z_{\Omega}$ .

$$Z_{O} = \frac{87}{\sqrt{\varepsilon_{r} + 1.41}} \ln\left(\frac{5.98H}{0.8W + T}\right)$$

(2.55)

The typical substrate used in microstrip is FR4 with  $\epsilon_r = 4$ , H=30mil and T=1.37mil where

$$1 \text{mil} = 2.54 \text{x}_{10}^{-5} \text{m} \tag{2.56}$$

### 2.15 Linearity of Regulator

Linearity of regulator is the relationship between input and output and the main target is to determine its linearity region and input limit to the regulator. It is desirable to get the almost constant output voltage due to the change of input voltage. This can be determined by monitoring the slope of the linear equation which is

$$y = mx + c \tag{2.57}$$

where *m* is the slope and *c* is the intersection of the linearity line. The linearity level of the relationship between input and output voltage is determined by the correlation factor,  $R^2$ .

#### 2.16 **Ripple Rejection Percentage**

For the ripple rejection regulator, the input voltage sinusoidal is treated as noise input to the circuit. The output from the ripple rejection circuit should be constant which is as small as possible compared to the input. The percentage of input voltage rejected by the circuit over the input voltage is called ripple rejection percentage.

Ripple rejection percentage (%) =

$$\left(\frac{V_{in} - V_{out}}{V_{in}}\right) x \ 100\%$$

(2.58)

### **Chapter Three**

#### **CIRCUITS IMPLEMENTATION**

#### 3.1 µA723 Integrated Circuit

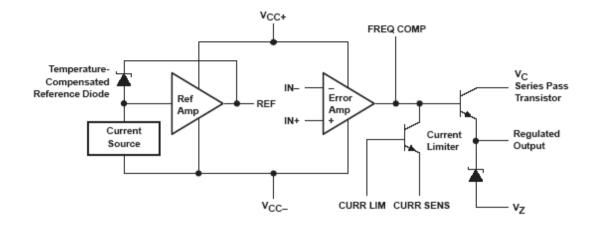

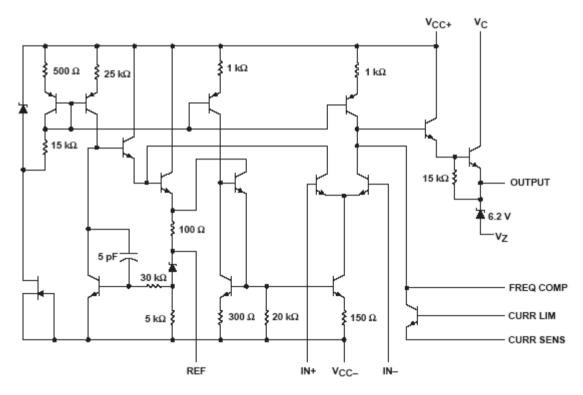

As illustrated below,  $\mu$ A723 integrated circuit is a fourteen-terminal integrated chip. It is a precision integrated circuit voltage regulator, featuring high ripple rejection, excellent input and load regulation, excellent temperature stability and low standby current. The circuit consists of a temperature compensated reference voltage amplifier, an error amplifier, a 150Ma output transistor and an adjustable output current limiter.

The  $\mu$ A723 is designed for use in positive or negative power supplies as a series, shunt, switching or floating regulator.

**Figure 3.1** µA723 chip (**Source:** µA723 Precision Voltage Regulators Datasheet from TEXAS INSTRUMENT)

Figure 3.2 µA723 pin connection (top view) (Source: µA723 Precision Voltage Regulators Datasheet from TEXAS INSTRUMENT)

**Figure 3.3** µA723 functional block diagram (**Source:** µA723 Precision Voltage Regulators Datasheet from TEXAS INSTRUMENT)

**Figure 3.4** µA723 schematic diagram (**Source:** µA723 Precision Voltage Regulators Datasheet from TEXAS INSTRUMENT)