# DESIGN AND ANALYSIS OF CMOS BASED RFIC BANDPASS FILTER (BPF) FOR 1.9GHz RANGE FOR CDMA APPLICATIONS

Oleh

Ngoh Say Kit

Disertasi ini dikemukakan kepada UNIVERSITI SAINS MALAYSIA

Sebagai memenuhi sebahagian daripada syarat keperluan untuk ijazah dengan kepujian

# SARJANA MUDA KEJURUTERAAN (KEJURUTERAAN ELEKTRONIK)

Pusat Pengajian Kejuruteraan Elektrik Dan Elektronik Universiti Sains Malaysia

# ABSTRACT

The rapid development of wireless applications has created a demand for low-cost, compact, low-power hardware solutions. This demand has driven efforts to realize fully integrated, "single-chip" solution systems. While substantial progress had been made in the integration of many RF and baseband processing elements through the development of new technologies and refinements of existing technologies, progress in the area of fully integrated filters has been limited due to the losses (low Q) associated with integrated passive elements in standard IC process. The work in this report focuses on the design and analysis of CMOS based RFIC bandpass filter for center frequency of 1.90Hz. The entire design and analysis of the filter circuit have been carried out by ultilizing Cadence IC Design Tools (version 5.033). This report present a methodology for designing a Q-enhanced bandpass filter with active negative resistance generator circuitry to compensate for the filter losses due to the low quality factor of monolithic spiral inductors. The first phase of this work focus on the design and simulation of an ideal, fully integrated second order Butterworth bandpass filter (with -3dB bandwidth of 200MHz centered at 1.9GHz, corrensponding to the CDMA2000 Standard) ultilizing Cadence IC Design Tools with Silterra 0.18um Design Kit. The ideal bandpass filter which based on the paper work calculation is first constructed by using Silterra SMCMOS ideal component and the simulation results are observed. The ideal circuit is then simulated by using Silterra RF component (which include all parasitic effects) to show the actual filter performance. In the second phase of this work, a FET-based active negative resistance circuit is developed and being added into the bandpass filter circuitry to compensate the filter loss. With features of Cadence IC Design Tools, the filter is analyzed and optimized to obtain the best response. The best filter design achieves  $\approx$  0dB of passband gain or insertion loss while consuming 8.8mA of current from  $a \pm 1.8V$  source (31.69mW). The filter provides more than 10dB of rejection at 1.5GHz and 2.5GHz. In the filter passband, the noise figure is 5.25dB and input return loss is -20dB. The filter response only suffered a minor frequency shift for a wide range of operating temperature. The bandpass filter has potential application as RF filters in CMOS integrated transceiver designs.

# ACKNOWLEDGEMENT

First of all, I would like to express my sincere appreciation and gratitude to my project's supervisor, Mr. Basir Saibon for his valuable advice, guidance and willingness to share his expertise. Throughout this long period, he had given me best supports which help a lot on my completion of the project. From his guidance, my project has been completed in a good manner and my report writing skill has been improved dramatically.

I would like to express my gratitude and sincere thanks to Dr. Tun Zainal, for his great efforts on providing a stable networking and server for us who are doing IC Design final year project. With his willingness to help and guide me to master the Cadence IC Design Tools, my project can be completed on time.

Next, I would like to thank Mr. Tan Yee Chyan, a Master student on providing valuable information regarding my project and some useful tips and ways to use the Cadence software.

Special thanks to En. Ahmad Ahzam Latib, technician of VLSI Lab for their willingness to provide assistant on how to access to the Cadence Server and provide me problem-free computers to run my project simulations.

Next, I would like to thank all my family and friends, who have supported and worked hard together with me, giving me moral support and ideas to complete my final year project. Without them, this project cannot be accomplished in a good manner.

Last but not least, my acknowledgments would not be complete without expressing my appreciation to all members of University Science Malaysia. It is a great pleasure to pursue my knowledge in such an amazing environment. University Science Malaysia has successfully provided me the scenario of real engineering world.

# **TABLE OF CONTENTS**

Page

| ABSTRACT     |                                           | 1  |

|--------------|-------------------------------------------|----|

| ACKNOWLED    | GEMENT                                    | 2  |

| LIST OF FIGU | RES                                       | 6  |

| LIST OF TABL | ES                                        | 9  |

|              |                                           |    |

| CHAPTER 1    | INTRODUCTION                              |    |

| 1.1 Backgr   | ound of Project                           | 10 |

| 1.2 Objecti  | ve and Scope of Project                   | 11 |

| 1.3 Project  | Methodology                               | 11 |

| 1.4 Structu  | re of the Report                          | 12 |

|              |                                           |    |

| CHAPTER 2    | PROJECT OVERVIEW AND THEORY               |    |

| 2.1 Bandpa   | ass Filter Type                           | 13 |

| 2.2 Filter C | Drder                                     | 16 |

| 2.3 Filter I | mplementation                             | 16 |

| 2.4 Filter T | Topology                                  | 18 |

| 2.5 Resona   | tor Qs                                    | 19 |

| 2.6 Q-Enha   | anced Inductors                           | 20 |

| 2.7 Filter C | Characteristics                           |    |

| 2.7.1        | Gain and Phase                            | 21 |

| 2.7.2        | S-Parameters                              | 22 |

| 2.7.3        | Noise Figure                              | 24 |

| 2.7.4        | Linearity                                 |    |

|              | 2.7.4.1 1-dB Compression Point            | 24 |

|              | 2.7.4.2 Third-order Intercept Point (IP3) | 25 |

# CHAPTER 3 BANDPASS FILTER DESIGN AND SIMULATION

| 3.1 | Design                                          | Specification              | 27 |

|-----|-------------------------------------------------|----------------------------|----|

| 3.2 | Second-Order Butterworth Bandpass Filter Design |                            | 27 |

| 3.3 | Schematic Entry                                 |                            | 30 |

| 3.4 | Simulat                                         | ion Results and Comparison |    |

|     | 3.4.1                                           | Gain and Phase Response    | 31 |

|     | 3.4.2                                           | S-Parameter Response       | 34 |

|     | 3.4.3                                           | Noise Figure               | 35 |

| 3.5 | Discuss                                         | ion                        | 37 |

# CHAPTER 4 NEGATIVE RESISTANCE CIRCUITS AND Q-ENHANCED RESONATORS

| 4.1 | Negativ                       | e Resistance Circuit Topologies         | 39 |

|-----|-------------------------------|-----------------------------------------|----|

| 4.2 | Derivati                      | on of Common-Source Capacitive Feedback | 41 |

| 4.3 | Modifie                       | d Common-Source Capacitive Feedback     | 43 |

| 4.4 | Parallel                      | Equivalent Model                        | 44 |

| 4.5 | 5 Q-Enhancement of Resonators |                                         |    |

|     | 4.5.1                         | Negative Resistance Design              | 47 |

|     | 4.5.2                         | Bias Circuit Design                     | 49 |

|     | 4.5.3                         | Capacitance Equalization                | 50 |

#### CHAPTER 5 BANDPASS FILTER TUNING AND OPTIMIZATION

| 5.1 | Schema  | tic Entry               | 52 |

|-----|---------|-------------------------|----|

| 5.2 | Simulat | ion Results             |    |

|     | 5.2.1   | Gain and Phase Response | 57 |

|     | 5.2.2   | S-Parameter Response    | 59 |

|     | 5.2.3   | Noise Figure            | 61 |

|     | 5.2.4   | Transient Response      | 62 |

|     | 5.2.5   | Linearity               | 64 |

| 5.2.6          | Temperature Variations (-30°C, -4°C, 22°C, 48°C, 74°C, 100°C)                                     | 66 |

|----------------|---------------------------------------------------------------------------------------------------|----|

| 5.2.7          | Supply Voltage Variations ( $\pm 1.0V$ , $\pm 1.375V$ , $\pm 1.75V$ , $\pm 2.125V$ , $\pm 2.5V$ ) | 73 |

| 5.3 Discussion |                                                                                                   | 79 |

# CHAPTER 6 LAYOUT DESIGN

| 6.1 | Layout Entry                                                               | 83 |

|-----|----------------------------------------------------------------------------|----|

| 6.2 | Design Rules Check (DRC), Layout Extraction, Layout Versus Schematic (LVS) | 86 |

| 6.3 | Discussion                                                                 | 87 |

# CHAPTER 7 CONCLUSIONS AND FUTURE WORK

| 7.1 Concl  | Conclusions                                       |    |

|------------|---------------------------------------------------|----|

| 7.2 Future | e Work                                            |    |

| 7.2.1      | Improved Frequency Response                       | 89 |

| 7.2.2      | Negative Resistance Circuits / Stability Analysis | 89 |

| 7.2.3      | Bias Tracker Circuit                              | 90 |

|            |                                                   |    |

| REFERE     | NCES                                              | 91 |

92

# LIST OF FIGURES

| FIGURE | TITLE                                                                                                                                                                                                                                              | PAGE |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1    | Using a filter to reduce the effect of an undesired signal at frequency f2, while retaining desired signal at frequency f1.                                                                                                                        | 13   |

| 2.2    | Amplitude response comparison (left) and maximized view at cutoff frequency (right)                                                                                                                                                                | 15   |

| 2.3    | Impulse response comparison (left) and step response comparison (right)                                                                                                                                                                            | 15   |

| 2.4    | Gain response at transition band of a second order filter (left) and fourth order filter (right).                                                                                                                                                  | 16   |

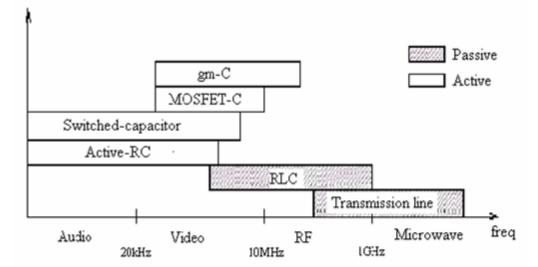

| 2.5    | Various filter implementations for different frequency range.                                                                                                                                                                                      | 17   |

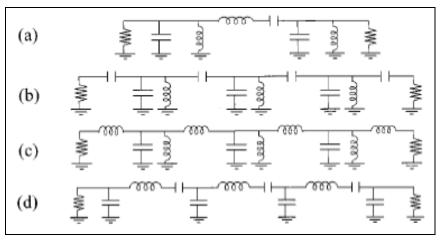

| 2.6    | <ul> <li>(a) Ladder topology</li> <li>(b) Narrowband-coupled-resonator topology (Top-C coupled)</li> <li>(c) Narrowband-coupled-resonator topology (Top-L coupled)</li> <li>(d) Narrowband-coupled-resonator topology (Shunt-C coupled)</li> </ul> | 18   |

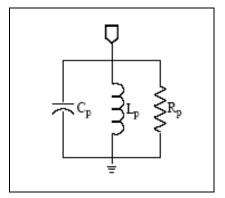

| 2.7    | Parallel RLC resonator.                                                                                                                                                                                                                            | 19   |

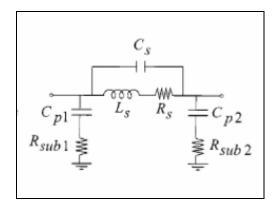

| 2.8    | Physical model of an on-chip spiral inductor.                                                                                                                                                                                                      | 20   |

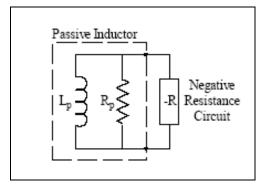

| 2.9    | The Q-enhancement concept.                                                                                                                                                                                                                         | 21   |

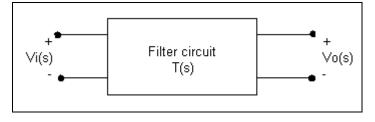

| 2.10   | Filter represent by two-port network.                                                                                                                                                                                                              | 21   |

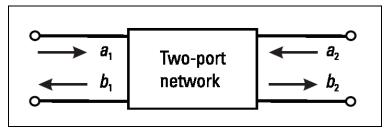

| 2.11   | General two-port system with incident and reflected waves.                                                                                                                                                                                         | 22   |

| 2.12   | Measurement of 1-dB Compression Point, Pin1dB for bandpass filter<br>in a receiver front end.                                                                                                                                                      | 25   |

| 2.13   | Third-order intercept point plot.                                                                                                                                                                                                                  | 26   |

| 3.1    | Second order Butterworth bandpass filter. Note that $C_s$ is the compensated resonator capacitance (Eqn. 3.5)                                                                                                                                      | 28   |

| 3.2    | <ul><li>(Top) Ideal bandpass filter circuit (using SMCMOS ideal component)</li><li>(Bottom) Actual bandpass filter circuit (using SilRF actual component)</li></ul>                                                                                | 30   |

| 3.3    | Gain and phase response of ideal bandpass filter.                                                                                                                                                                                                  | 31   |

| 3.4    | Gain and phase response of actual bandpass filter.                                                                                                                                                                                                 | 31   |

| 3.5    | Detailed gain response of ideal bandpass filter.                                                                                                                                                                                                   | 32   |

| 3.6    | Detailed gain response of actual bandpass filter.                                                                                                                                                                                                  | 32   |

| 3.7  | S11 and S21 response of ideal bandpass filter.                                                                                                           | 34 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.8  | S11 and S21 response of actual bandpass filter.                                                                                                          | 34 |

| 3.9  | Noise figure of ideal bandpass filter.                                                                                                                   | 35 |

| 3.10 | Noise figure of actual bandpass filter.                                                                                                                  | 36 |

| 4.1  | Common-gate inductive feedback: (a) Circuit; (b) Equivalent circuit.                                                                                     | 39 |

| 4.2  | Common-source capacitive feedback: (a) Gate output circuit;<br>(b) Equivalent circuit; (c) Drain output circuit.                                         | 40 |

| 4.3  | Common-source capacitive feedback: Small-signal equivalent circuit.                                                                                      | 42 |

| 4.4  | Modified common-source capacitive feedback: Small-signal equivalent circuit.                                                                             | 44 |

| 4.5  | Parallel equivalent negative resistance circuit.                                                                                                         | 45 |

| 4.6  | Equivalent circuits of Q-enhanced resonators near parallel resonance.                                                                                    | 47 |

| 4.7  | Estimated frequency response of resonator loss and negative resistance                                                                                   | 48 |

| 4.8  | Connection between negative resistance circuit and bias circuits.                                                                                        | 49 |

| 4.9  | <ul> <li>(a) Bias circuit: resistor-only</li> <li>(b) Bias circuit: resistor-MOSFET</li> <li>(c) Bias circuit: MOSFET-only</li> </ul>                    | 50 |

| 4.10 | Illustration of frequency shift due to negative resistance circuit: (a)<br>Without preshifted passive resonator (b) With preshifted passive<br>resonator | 51 |

| 5.1  | Complete second-order Butterworth filter schematic.                                                                                                      | 53 |

| 5.2  | Complete filter circuit with negative resistance generator and bias circuits in block level.                                                             | 54 |

| 5.3  | Negative resistance generator circuit with NMOS transistors in block level.                                                                              | 55 |

| 5.4  | Transistors connected in parallel to form a larger value.                                                                                                | 56 |

| 5.5  | Bias circuits to supply positive voltage (left) and negative voltage (right).                                                                            | 56 |

| 5.6  | Simulation of bandpass filter with calculated currents passing through the supply voltages (shown in green box).                                         | 57 |

| 5.7  | Gain and phase response.                                                                                                                                 | 57 |

| 5.8  | Detailed gain response.                                                                                                                                  | 58 |

| 5.9  | S21 response.                                                                                                                                            | 59 |

| 5.10 | S21 response at the range of 1.80GHz – 2.00GHz.                                                                              | 59 |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

| 5.11 | S11 response.                                                                                                                | 60 |

| 5.12 | S21 and S11 response at the range of 1.80GHz – 2.00GHz.                                                                      | 60 |

| 5.13 | Noise figure of complete bandpass filter.                                                                                    | 61 |

| 5.14 | Comparison of input signal magnitude (top) with output signal magnitude for frequency 1.10GHz, 1.50GHz and 1.90GHz (bottom). | 62 |

| 5.15 | Transient response for input signal at 1.90GHz (bottom) and the corresponding output signal (top).                           | 62 |

| 5.16 | 1-dB Compression Point plot.                                                                                                 | 64 |

| 5.17 | Input-referred Third-order Intercept Point (IIP3) plot.                                                                      | 64 |

| 5.18 | Gain and phase response for different temperature range.<br>(-30°C, -4°C, 22°C, 48°C, 74°C, 100°C)                           | 66 |

| 5.19 | Detailed gain response for different temperature range.<br>(-30°C, -4°C, 22°C, 48°C, 74°C, 100°C)                            | 67 |

| 5.20 | S21 response for different temperature range.<br>(-30°C, -4°C, 22°C, 48°C, 74°C, 100°C)                                      | 68 |

| 5.21 | S11 response for different temperature range.<br>(-30°C, -4°C, 22°C, 48°C, 74°C, 100°C)                                      | 69 |

| 5.22 | Combined S11 and S21 response for different temperature range.<br>(-30°C, -4°C, 22°C, 48°C, 74°C, 100°C)                     | 70 |

| 5.23 | Noise Figure (NF) for different temperature range.<br>(-30°C, -4°C, 22°C, 48°C, 74°C, 100°C)                                 | 71 |

| 5.24 | Gain and phase response for different positive voltage range (Vdd).<br>(+1.0V, +1.375V, +1.75V, +2.125V, +2.5V)              | 73 |

| 5.25 | Gain and phase response for different negative voltage range (Vee).<br>(-1.0V, -1.375V, -1.75V, -2.125V, -2.5V)              | 74 |

| 5.26 | S11 and S21 response for different positive voltage range (Vdd).<br>(+1.0V, +1.375V, +1.75V, +2.125V, +2.5V)                 | 75 |

| 5.27 | S11 and S21 response for different negative voltage range (Vee).<br>(-1.0V, -1.375V, -1.75V, -2.125V, -2.5V)                 | 76 |

| 5.28 | Noise Figure (NF) for different positive voltage range (Vdd).<br>(+1.0V, +1.375V, +1.75V, +2.125V, +2.5V)                    | 77 |

| 5.29 | Noise Figure (NF) for different negative voltage range (Vee).<br>(-1.0V, -1.375V, -1.75V, -2.125V, -2.5V)                    | 77 |

| 6.1  | Complete layout design with die area dimension and pin labeling.                                                             | 83 |

| 6.2  | Negative resistance generator circuit.                                                                                       | 84 |

| 6.3 | NMOS transistor block.                                                        | 85 |

|-----|-------------------------------------------------------------------------------|----|

| 6.4 | Bias circuits to supply positive voltage (top) and negative voltage (bottom). | 85 |

| 6.5 | Dimension of pad frame (a) and spiral inductor (b).                           | 86 |

# LIST OF TABLES

| TABLE | TITLE                                                                | PAGE |

|-------|----------------------------------------------------------------------|------|

| 3.1   | Important parameters of bandpass filter.                             | 27   |

| 3.2   | Comparison of simulation parameters with desired parameters.         | 37   |

| 5.1   | Component values for filter schematic in Figure 5.1.                 | 52   |

| 5.2   | Comparison of various simulation parameters with desired parameters. | 79   |

| 5.3   | Specification of optimized second-order Butterworth bandpass filter. | 82   |

### CHAPTER 1 INTRODUCTION

#### **1.1 BACKGROUND OF PROJECT**

The growth of modern communications systems operating at radio frequency has led to the development of highly integrated tranceivers. One of the factors that limit the integration of RF tranceivers is the low quality of the passive components in the commercially available IC processes [B. Georgescu, 2003]. RF bandpass filters are one of the key functional blocks in wireless communication systems and are used to attenuate interference signal in undesired frequency bands while allowing signals in desired frequency bands to pass through with minimal loss. The integration of filter on-chip offers several advantages. Performance can be improved by the elimination of parasitics inherent in elements such as the package and bondwires. In addition, inter-stage matching requirements can be reduced since the design is no longer constrained to system impedance of off-chip elements. The cost of RF transceiver is reduced due to fewer external components. Furthermore power dissipation is also reduced because RF signals need not to travel off-chip thru package pins to an external filter on the PCB (Printed Circuit Board).

Despite the advantages, the integration of RF bandpass filter in IC (especially very high frequency passive RF filter) remains a challenge because the quality factor of monolithic spiral inductors is very low (<10). The low quality factor of on-chip inductors will leads to high insertion loss in passive filter implementations [T. Soorapanth and S. Simon Wong, 2002]. On the other hand, active filter implementations, such as gm-C filter require power and have potential problems with linearity. Due to process variations, they will also require some forms of feedback in many cases to set their frequency of operation and to set the Q precisely. In addition, if care is not taken, filter with active Q enhancement can be unstable to implement at above-gigahertz frequencies [J. Rogers and C. Plett, 2003].

Thus, passive RLC filter is more preferable at the gigahertz range. A more acceptable solution is to implement a semipassive filter using on-chip passive elements with active loss compensation circuitry to improve the overall filter quality factor.

#### **1.2 OBJECTIVE AND SCOPE OF PROJECT**

The objective of this project is to design a bandpass filter with center frequency 1.9GHz and -3dB bandwidth of 200MHz with the aid of Silterra RF 0.18µm Design Kit on Cadence IC Design Tools. The bandpass filter has potential as RF filter for a super-heterodyne architecture RF receiver for Code-Division Multiple Access (CDMA) communication applications.

The scope of this project is to conduct analysis on the filter which includes filter gain response, phase response, insertion loss and input return loss response, noise characteristic, linearity, power consumption, etc. The major concern on the bandpass filter design is its filter gain and loss responses, stability and noise characteristic. Other aspects which are not so important have been tradeoff to improve towards the major characteristics of the filter.

#### **1.3 PROJECT METHODOLOGY**

In this project, the design of bandpass filter is divided into 4 stages:

- (1) Ideal and actual filter : design and simulation.

- (2) Negative resistance circuit design (for loss compensation).

- (3) Actual filter (with loss compensation circuitry) tuning and optimization.

- (4) Layout Design.

In the first stage, both ideal and actual second order Butterworth passive RLC bandpass filter are designed and constructed based on theoretical calculations to illustrate the filter response. The simulation is done by using Cadence Spectre with Silterra SMCMOS 0.18µm and Silterra RF 0.18µm Design Kits. All simulation results of ideal and actual filters are compared

In the second stage, an active negative resistance circuit is designed to compensate for the actual filter loss. The design of the active circuitry is done according to some theory and assumptions. In the third stage, the active negative resistance circuitry is added into the filter to improve the performance of it. The whole circuit is then undergoing tuning and optimization process to improve the critical parameters of the filter.

In the last stage, the schematic circuit is transferred to IC layout using Cadence Virtuoso-Layout, where component and block routing are done on it. After that, pad frames will be added to the complete layout. Finally, the complete layout will undergo Design Rules Check (DRC), Layout Extraction and Layout Versus Schematic (LVS) process.

#### **1.4 STRUCTURE OF REPORT**

Basically this report is consists of seven chapter. Chapter 2 explains the theory and background of a bandpass filter. This chapter also gives a brief overview on some aspects related to the project. Chapter 3 explains the steps to design the filter in this project. This chapter also including simulation results based on the designed ideal and actual filter. Discussion on the simulation results and improvement method also included. Chapter 4 gives a detailed explanation on how to design a loss compensation circuit (negative resistance generator) to improve the filter performance. This includes various methods to design the circuit and the effects of adding the circuit to the filter resonator. Chapter 5 discuss about the simulation results of the optimized filter with loss compensation circuit designed in previous chapter. Also included is the comparison of the ideal, actual and optimized filter simulation results with the desired specifications. A finalized bandpass filter specification is showed at the end of this chapter. Chapter 6 explains the layout design of the complete filter and the problem arises from DRC, Layout Extraction and LVS test. Chapter 7 concludes the findings, observations and results based on all previous chapters. Also included is the potential application and future work for this project.

# CHAPTER 2 PROJECT OVERVIEW AND THEORY

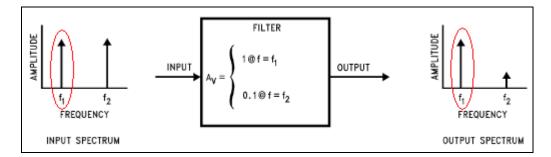

A bandpass filter is a device that passes signals at certain frequency ranges while preventing the passage of others [R. Mancini, 2002]. Example: consider a situation where a useful signal at frequency f1 has been contaminated with an unwanted signal at f2. If the contaminated signal is passed through a circuit (Figure 2.1) that has very low gain at f2 compared to f1, the undesired signal can be removed, and the useful signal will remain. The gain of the filter at any frequency other than f1 and f2 is not concerned as long as f2 is sufficiently attenuated relative to f1, the performance of the filter will be satisfactory [K. Lacanette, 1991]. Bandpass filter circuits are used in a wide variety of applications.

**Figure 2.1**: Using a filter to reduce the effect of an undesired signal at frequency f2, while retaining desired signal at frequency f1.

#### 2.1 BANDPASS FILTER TYPE

Currently there are many types of filters. Typical all-pole filter are Butterworth, Chebyshev and Bessel filter. There is also another filter which is Elliptic filter but it is not suitable for this project because it will cause serious stopband ripple. The advantages and disadvantages of the three all-pole filters are as below:

**Butterworth:** This filter has the flattest possible pass-band magnitude response. Attenuation is –3dB at the design cutoff frequency. Attenuation above the cutoff frequency is a moderately steep –20dB/decade pole. The pulse response of the Butterworth filter has moderate overshoot and ringing. Butterworth filter is often used when precise signal levels are required across the entire passband [R. Mancini, 2002].

*Advantages*: Maximally flat magnitude response in the pass-band. Good all-around performance. Pulse response better than Chebyshev. Rate of attenuation better than Bessel.

Disadvantages: Some overshoot and ringing in step response.

**Chebyshev**: This filter type has steeper attenuation above the cutoff frequency than Butterworth. This advantage comes at the penalty of amplitude variation (ripple) in the passband. Unlike Butterworth and Bessel responses, which have 3dB attenuation at the cutoff frequency, Chebyshev cutoff frequency is defined as the frequency at which the response falls below the ripple band. For a given number of poles, a steeper cutoff can be achieved by allowing more passband ripple. The number of cycles of ripple in the passband is equal to the order of the filter. The Chebyshev has even more ringing in its pulse response than the Butterworth. Chebyscheff filters are often used in filter banks, where the frequency content of a signal is of more importance than a constant amplification [R. Mancini, 2002].

*Advantages*: Better attenuation beyond the pass-band than Butterworth. *Disadvantages*: Ripple in pass-band. Considerable ringing in step response.

**Bessel:** This filter has excellent pulse response (minimal overshoot and ringing) and great linear phase response. For a given number of poles, its magnitude response is not as flat, nor is its attenuation beyond the –3dB cutoff frequency as steep as the Butterworth. It takes a higher order Bessel filter to give a magnitude response which approaches that of a given Butterworth filter, but Bessel filters can provide an optimum square-wave transmission behavior [R. Mancini, 2002].

*Advantages*: Best step response - very little overshoot or ringing. *Disadvantages*: Slower rate of attenuation beyond the passband than Butterworth.

The gain and phase response of a filter can be optimized to satisfy one of the following three criteria:

a) A maximum passband flatness,

b) An immediate passband-to-stopband transition,

c) A linear phase response.

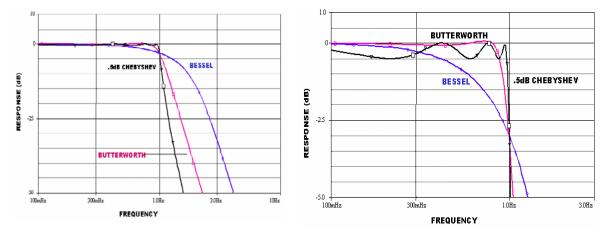

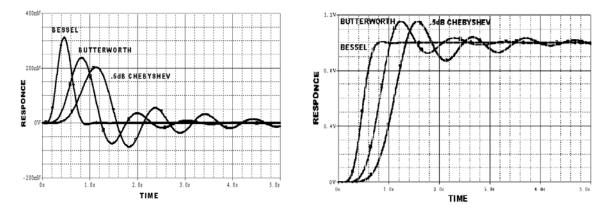

Figure 2.2 and Figure 2.3 show the responses of several all pole filters (low-pass filter), namely the Bessel, Butterworth and Chebyshev (in this case of 0.5 dB ripple). An 8 pole filter is used as the basis for the comparison. The responses have been normalized for a cutoff of 1 Hz.

Figure 2.2: Amplitude response comparison (left) and maximized view at cutoff frequency (right)

Figure 2.3: Impulse response comparison (left) and step response comparison (right)

It is easy to see the tradeoffs in the various responses. Moving from Bessel through Butterworth to Chebyshev, notice that the amplitude discrimination improves as the transient behavior gets progressively poorer. Butterworth filter type had been chosen for this project because it provides good all-around performance based on the benchmarking figures above.

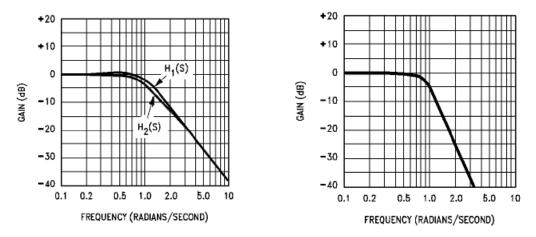

#### 2.2 FILTER ORDER

The order of a filter is important for several reasons. It is directly related to the number of components in the filter, and therefore to its cost, its physical size, and the complexity of the design task. Therefore, higher-order filters are more expensive, take up more space, and are more difficult to design. The primary advantage of a higher order filter is that it will have a steeper rolloff slope at the transition band (passband to stopband) than a similar lower-order filter, as shown at Figure 2.4.

**Figure 2.4**: Gain response at transition band of a second order filter (left) and fourth order filter (right).

For the ease of design, the order of bandpass filter for this project is set to lowest which is second order. Although higher order filter will result in steeper transition band rolloff, but it will also cause circuit complexity and thus more design problem.

#### 2.3 FILTER IMPLEMENTATION

Typically, there are many ways to construct a filter such as passive RLC, active RC, switched-capacitor, MOSFET-C and gm-C (OTA). The following is the description of each implementation:

a) Passive RLC – this implementation involves passive or lumped elements to construct a filter. The main advantage was it can be realized at very high frequency especially in the gigahertz range. The filter is more stable and consumes less power. The main drawbacks of it were larger die area consumption and poorer Q-factor due to

component losses especially the inductor loss. Passive filter are more suitable for radio frequency (RF) and microwave applications.

- b) gm-C the basic building block of gm-C filter was operational transconductor amplifier (OTA). gm-C filter consumes more power and have potential problems with linearity. Besides, it can be unstable to implement at above-gigahertz frequencies [Y. Sun, 2002].

- c) Active RC this implementation ultilizes op-amp and other passive component to construct a filter. The limited gain and bandwidth of the op-amp were the major constrains for this type of filter at very high frequency. This implementation also required more components and higher complexity than gm-C implementation [R. Schaumann, M.S. Ghausi and K.R. Laker, 1990].

- d) MOSFET-C this implementation was almost same with active RC, except the resistors were replaced by MOSFET which operate at triode region. Due to the similarity with active RC implementation, MOSFET-C had limited capability at high frequency [D. Johns and K. Martin, 1997].

- e) Switched-capacitor this filter was constructed from op-amp, capacitor, switch and clock. This type of filter has gain popularity because of its better frequency response, linearity and dynamic range. However, switched-capacitor filter require proper time domain sampling to avoid signal aliasing, thus limited its capability at high frequency [D. Johns and K. Martin, 1997].

Figure 2.5: Various filter implementations for different frequency range.

From Figure 2.5, it can be clearly seen that Passive RLC is chosen as the suitable implementation for this project. However, an active compensation circuitry is added into the filter circuit to compensate for the filter loss due to lossy component.

#### 2.4 FILTER TOPOLOGY

A few topologies (or architecture) for passive filter implementation are available currently, typical topologies are ladder topology and narrowband-coupled-resonator topology (which include Top-C coupled, Shunt-C coupled and Top-L coupled), as shown in Figure 2.6.

Figure 2.6: (a) Ladder topology

(b) Narrowband-coupled-resonator topology (Top-C coupled)

(c) Narrowband-coupled-resonator topology (Top-L coupled)

(d) Narrowband-coupled-resonator topology (Shunt-C coupled)

The ladder topology ultilizes both series and parallel resonators. The main drawback of this topology is the filter component value spread is very large for a typical filter specification [T. Soorapanth and S. Simon Wong, 2002]. A more suitable design is the narrowband-coupled-resonator topology because it only ultilizes one type of resonator, either in series or parallel. Another side advantage is the inductor value can be chosen to be same for all resonators, which helps simplify the implementation of the filter by using Silterra RF 0.18um Design Kit. However, for Top-L coupled topology, the coupling inductor can be too large to be realized. Furthermore, this topology maximizes, rather than minimizes, the number of inductors. The Shunt-C coupled topology is less desirable from a construction viewpoint because both ends of the inductor are above ground potential. Also, parasitic

capacitance to ground at the node between the series inductor can be problematic. The Top-C coupled structure (ultilizing parallel LC resonator) which used in this project is excellent narrowband filter and provided alternatives when increased attenuation on either the lowside or the highside of the passband is desired [R.W. Rhea, 1995]. One of the advantages of the Top-C coupled topology are the number of inductors is minimized, which are a great enhanced in this project using Silterra RF design Kit with fixed inductor value.

#### 2.5 **RESONATOR Qs**

The filters designed in this report are based on shunt parallel LC resonators. Therefore, in analyzing the loss and Q of the resonators, the parallel equivalent model (Figure 2.7) of the resonator is used.

Figure 2.7: Parallel RLC resonator.

Given the loss resistance, the quality factor (Q) of the resonator can be found. The Q of a resonator is defined as the ratio of maximum instantaneous energy stored in the circuit to the energy dissipated per cycle [H.L. Krauss, C.W. Bostian, and F.H. Raab, 1980]. Therefore, the unloaded Q of the resonator is a measure of the loss of the resonator relative to the reactance of the resonator and can be computed by:

$$Q_{unloaded} = \frac{R_p}{2\pi \cdot f \cdot L_p} \tag{2.1}$$

Ideally, the resonator would have no loss (infinite  $R_p$ ) resulting in an infinite Q. Short of that, maximizing  $R_p$  by minimizing the loss will maximize the Q of the resonator. However, when this resonator is driven by a system (modeled by a Thevenin equivalent source), the resonator will be loaded by the external source resistance ( $R_{s,ext}$ ). This external resistance will not add loss to the resonator itself, but will change the frequency response of the impedance of the resonator due to the increased energy dissipation. The effect of this loading can be seen in the loaded Q of the resonator:

$$\frac{1}{Q_{loaded}} = \frac{1}{Q_{unloaded}} + \frac{1}{Q_{ext}}$$

(2.2)

where Q<sub>ext</sub> is given by:

$$Q_{ext} = \frac{2\pi \cdot f \cdot L_s}{R_{s,ext}} = \frac{R_{p,ext}}{2\pi \cdot f \cdot L_p}$$

(2.3)

Finally, the loaded Q of the resonator can be used to find the half-power bandwidth of the resonator input impedance using the following relation:

$$Q_{loaded} = \frac{f_o}{BW}$$

(2.4)

#### 2.6 Q-ENHANCED INDUCTORS

Basically, the loss of a resonator is mainly due to its lossy spiral inductor. The loss in a monolithic inductor is due to three mechanisms: metal wire resistance  $R_s$ , capacitive coupling to substrate  $C_{pi}$ , and magnetic coupling to the substrate  $R_{subi}$  [B. Razavi, 1998]. The physical model of an on-chip spiral inductor together with its loss contributor is shown in Figure 2.8.

Figure 2.8: Physical model of an on-chip spiral inductor.

Q-enhancement refers to the use of an active device to generate a negative resistance that compensates for the resistive losses of a physical (lossy) spiral inductor (Figure 2.9). This negative resistance cancels the (parallel equivalent) resistance due to the

loss of the inductor, thus effectively improving the Q of the inductor. Furthermore, if the loss of the inductor is dominant over the loading effects, reducing the inductor loss will also lead to an improvement in the resonator Qloaded.

Figure 2.9: The Q-enhancement concept.

The negative resistance circuit can be realized using active elements in many different topologies (to be discussed in Chapter 4). The resulting Q-enhanced inductor can then be used in L-C filter topologies. In theory, a negative resistance circuit could also be used to eliminate the loss of a capacitor. However, the non-ideal effects resulting from the addition of active devices outweigh the cancellation of the nominal loss of the capacitor.

### 2.7 FILTER CHARACTERISTICS

#### 2.7.1 Gain and Phase

The filters are linear circuits that can be represented by the general two-port network shown in Figure 2.10 [A.S. Sedra and K.C. Smith, 1998].

Figure 2.10: Filter represent by two-port network.

The filter transfer function T(s) is the ratio of the output voltage  $V_0(s)$  to the input voltage  $V_i(s)$ ,

$$T(s) = \frac{V_o(s)}{V_i(s)} \tag{2.5}$$

The filter transmission is found by evaluating T(s) for physical frequencies, s = jw, and can be expressed in terms of its magnitude and phase as

$$T(jw) = |T(jw)|e^{j\phi(w)}$$

(2.6)

The magnitude of transmission is often expressed in desibels in terms of the gain function

$$G_{dB} \equiv 20 \log_{10} \left| T(jw) \right|$$

$$= 20 \log_{10} \frac{V_o}{V_i}$$

(2.7)

A filter shapes the frequency spectrum of the input signal,  $|V_i(jw)|$ , according to the magnitude of the transfer function |T(jw)|, thus providing an output  $V_0(jw)$  with a spectrum

$$\left|V_{o}(jw)\right| = \left|T(jw)\right| \cdot \left|V_{i}(jw)\right|$$

(2.8)

Also, the phase characteristics of the signal are modified as it passes through the filter according to the filter phase function  $\phi(w)$ .

## 2.7.2 S-Parameters

S-Parameters are a way of calculating a two-port network in terms of incident and reflected (or scattered) power [J. Rogers and C. Plett, 2003]. Referring to Figure 2.11, assuming port 1 is the input, a1 is the input wave, b1 is the reflected wave, and b2 is the transmitted wave. Note that if a transmission line is terminated in its characteristic impedance, then the load absorbs all incident power traveling along the transmission line and there is no reflection.

Figure 2.11: General two-port system with incident and reflected waves.

The S-parameters can be used to describe the relationship between these waves as follows:

$$b_1 = S_{11}a_1 + S_{12}a_2 \tag{2.9}$$

$$b_2 = S_{22}a_2 + S_{21}a_1 \tag{2.10}$$

This can also be written in a matrix as

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \cdot \begin{bmatrix} a_1 \\ a_2 \end{bmatrix} = \begin{bmatrix} b \end{bmatrix} = \begin{bmatrix} S \end{bmatrix} \cdot \begin{bmatrix} a \end{bmatrix}$$

(2.11)

Thus, S-parameters are reflection or transmission coefficients and are usually normalized to a particular impedance. S11, S22, S21, and S12 will now each be defined.

$$S_{11} = \frac{b_1}{a_1}\Big|_{a_2=0}$$

(2.12)

S11 is the input reflection coefficient measured with the output terminated with Zo. This means the output is matched and all power is transmitted into the load, thus a2 is zero.

$$S_{21} = \frac{b_2}{a_1}\Big|_{a_2=0} \tag{2.13}$$

S21, the forward transmission coefficient, is also measured with the output terminated with Zo. S21 is equivalent to gain.

$$S_{22} = \frac{b_2}{a_2} \bigg|_{a1=0}$$

(2.14)

S22 is the output reflection coefficient measured by applying a source at the output and with the input terminated with Zo.

$$S_{12} = \frac{b_1}{a_2}\Big|_{a1=0}$$

(2.15)

S12 is the reverse transmission coefficient measured with the input terminated with Zo.

For filters, parameters S11 and S21 are particular important. S11 is related to input return loss of a filter. Ideally the S11 value around the center frequency of a bandpass filter should be a negative value. The more negative the value means that less power is reflected at the input, which is better for filter. S21 is related to gain or insertion loss (how much power is loss in going through the filter) of a filter. Ideally the S21 value at the passband of a bandpass filter should be zero (that means all power tranferred from input to output). A negative S21 value means that insertion loss occurred for that particular filter (signal loss when transferred from input to output).

#### 2.7.3 Noise Figure

This characteristic determines the level of noise for a particular system. For a filter, if the noise figure is high, the signal loss and distortion at the output is serious. Noise figure is defined as the ratio of signal-to-noise ratio (SNR) at the input port to the SNR of output port.

$$NF = \frac{SNR_i}{SNR_o}$$

(2.16)

where SNR<sub>i</sub> = signal-to-noise ratio at input

SNR<sub>o</sub> = signal-to-noise ratio at output

Noise Figure in desibel (dB),

$$NF = 10\log_{10}\left(\frac{\frac{S_{in}}{N_{in}}}{\frac{S_{out}}{N_{out}}}\right)$$

(2.17)

where S is the signal power and N is the noise power.

#### 2.7.4 Linearity

At high frequencies, and particularly with narrowband circuits, it is more common to characterize the distortion produced by a circuit in terms of a compression point or an intercept point. These metrics characterize the circuit rather than the signal, and as such it is not necessary to specify the signal level at which the circuit was characterized.

#### 2.7.4.1 1-dB Compression Point

Active components are limited to the amount of power that can be provided. When operating within the linear region of the component, gain through the component is constant for a given frequency. As the input signal is increased in power, a point is reached where the power of the signal at the output is not amplified by the same amount as the smaller signal. At the point where the input signal is amplified by an amount 1 dB less than the small signal