# Novel DVFS Methodologies For Power-Efficient Mobile MPSoC

### Somdip Dey

School of Computer Science and Electronic Engineering

University of Essex

A thesis submitted for the degree of  $Doctor\ of\ Philosophy$

**April**, 2022

This thesis is dedicated to

Maa, Soma Dey, and Baba, Sudip Dey

for their unconditional love and faith on me.

Baba passed away on 4th January, 2022,

and was not able to see me get the doctorate,

but his blessings are always with me.

### Acknowledgements

I would like to take this opportunity to extend my thanks to many people who directly and indirectly supported me during my PhD journey. First of all, I would like to thank my parents - Sudip Dey and Soma Dey, and Min Zhang, my ex-partner, without whom I might never have found this PhD program. Although we might not be together any more, but I am glad that I came across this funded PhD at the University of Essex under the supervision of Dr. Amit Kumar Singh and Prof. Klaus Dieter McDonald-Maier. Next, it goes without saying that how lucky I have been to be supervised by Dr. Amit Kumar Singh and Prof. Klaus Dieter McDonald-Maier, who have always supported me and have given me the full freedom to pursue my research during my PhD. I couldn't have asked for any better to be my mentor and advisor during my PhD journey than Dr. Amit Kumar Singh and Prof. Klaus Dieter McDonald-Maier.

Many thanks also to everyone in the Embedded and Intelligent Systems Laboratory at the University of Essex for their continued support, advise and friendship. I would also like to thank Dr. Vishwanathan Mohan and Dr. Morteza Varasteh for being my supervisory panel members and for keeping me on track with the PhD program. Further, my sincere thanks to all my colleagues and friends (Dani, Karthik, Albert, Andrea, Gregory, Omi, Raul, Antoine, Masha, Ritesh, Ramesh, Luis) at the Samsung R&D Institute UK, who have provided me with a plethora of knowledge in the commercial edge / mobile computing domain, for being supportive when I needed, great drinking sessions and, of course, amazing muscle aching badminton sessions.

Finally, greatest thanks go to my family members (the big Indian family), who are living thousands of miles away, for understanding why I had to bail on the socials and family gatherings; for understanding that I have been busy with my PhD.

#### **Abstract**

Low power mobile computing systems such as smartphones and wearables have become an integral part of our daily lives and are used in various ways to enhance our daily lives. Majority of modern mobile computing systems are powered by multi-processor System-on-a-Chip (MPSoC), where multiple processing elements are utilized on a single chip. Given the fact that these devices are battery operated most of the times, thus, have limited power supply and the key challenges include catering for performance while reducing the power consumption. Moreover, the reliability in terms of lifespan of these devices are also affected by the peak thermal behaviour on the device, which retrospectively also make such devices vulnerable to temperature side-channel attack. This thesis is concerned with performing Dynamic Voltage and Frequency Scaling (DVFS) on different processing elements such as CPU & GPU, and memory unit such as RAM to address the aforementioned challenges. Firstly, we design a Computer Vision based machine learning technique to classify applications automatically into different categories of workload such that DVFS could be performed on the CPU to reduce the power consumption of the device while executing the application. Secondly, we develop a reinforcement learning based agent to perform DVFS on CPU and GPU while considering the user's interaction with such devices to optimize power consumption and thermal behaviour. Next, we develop a heuristic based automated agent to perform DVFS on CPU, GPU and RAM to optimize the same while executing an application. Finally, we explored the affect of DVFS on CPUs leading to vulnerabilities against temperature side-channel attack and hence, we also designed a methodology to secure against such attack while improving the reliability in terms of lifespan of such devices.

# **Contents**

| 1 | Intr | Introduction                                                        |    |  |  |  |

|---|------|---------------------------------------------------------------------|----|--|--|--|

|   | 1.1  | Motivation                                                          | 1  |  |  |  |

|   | 1.2  | Key Challenges                                                      | 6  |  |  |  |

|   | 1.3  | Contributions                                                       | 7  |  |  |  |

|   | 1.4  | Thesis Outline                                                      | 8  |  |  |  |

|   | 1.5  | Publications                                                        | 9  |  |  |  |

| 2 | Bac  | kground                                                             | 12 |  |  |  |

|   | 2.1  | Introduction                                                        | 12 |  |  |  |

|   | 2.2  | Recent Emerging Technologies in Power and Thermal Management in MP- |    |  |  |  |

|   |      | SoC                                                                 | 17 |  |  |  |

|   |      | 2.2.1 Heterogeneity in Processing Cores in the Machine Learning Era | 17 |  |  |  |

|   |      | 2.2.2 Convolutional Neural Networks and Deep Learning               | 17 |  |  |  |

|   |      | 2.2.3 Reinforcement Learning                                        | 18 |  |  |  |

|   | 2.3  | Dynamic Power Management                                            | 19 |  |  |  |

|   |      | 2.3.1 Proactive Approaches                                          | 19 |  |  |  |

|   |      | 2.3.2 Reactive Approaches                                           | 21 |  |  |  |

|   | 2.4  | Dynamic Thermal Management                                          | 22 |  |  |  |

|   |      | 2.4.1 Proactive Approaches                                          | 22 |  |  |  |

|   |      | 2.4.2 Reactive Approaches                                           | 23 |  |  |  |

|   | 2.5  | Dynamic Power and Thermal Management                                | 23 |  |  |  |

|   |      | 2.5.1 Proactive Approaches                                          | 24 |  |  |  |

|   |      | 2.5.2 Reactive Approaches                                           | 24 |  |  |  |

|   | 2.6  | Temperature Side-Channel Attacks                                    | 25 |  |  |  |

|   | 27   | Summary                                                             | 28 |  |  |  |

| 3 | Peri | formin | ng DVFS on CPU                                                    | 29 |

|---|------|--------|-------------------------------------------------------------------|----|

|   | 3.1  | Prolog | gue to First Contributory Article                                 | 29 |

|   |      | 3.1.1  | Article Details                                                   | 29 |

|   |      | 3.1.2  | Media coverage                                                    | 30 |

|   | 3.2  | Introd | duction & Motivation                                              | 30 |

|   |      | 3.2.1  | Contributions                                                     | 34 |

|   | 3.3  | Motiv  | vational Case Study                                               | 35 |

|   |      | 3.3.1  | Traditional Feature Extraction from Source Code                   | 35 |

|   |      | 3.3.2  | Filling up the gap                                                | 36 |

|   | 3.4  | Prelin | ninaries                                                          | 37 |

|   |      | 3.4.1  | Pre-trained Networks and Transfer Learning                        | 37 |

|   | 3.5  | SoCoo  | deCNN: How it Works                                               | 37 |

|   |      | 3.5.1  | Pre-process Source-Code                                           | 38 |

|   |      |        | 3.5.1.1 IR Generator                                              | 38 |

|   |      |        | 3.5.1.2 Code Cleanser                                             | 38 |

|   |      | 3.5.2  | Process Source-Code IR                                            | 40 |

|   | 3.6  | Pixela | ntor: Pixel Wise Differentiator of Images                         | 42 |

|   |      | 3.6.1  | Overview of Pixelator                                             | 42 |

|   |      | 3.6.2  | Comparison of Pixelator with other popular methodologies          | 43 |

|   |      |        | 3.6.2.1 An example demonstrating the importance of Pixelator $$ . | 44 |

|   | 3.7  | Exper  | rimental and Validation Results of SoCodeCNN                      | 46 |

|   |      | 3.7.1  | Experimental Setup                                                | 46 |

|   |      | 3.7.2  | Experimental Results                                              | 49 |

|   |      | 3.7.3  | Where the CNN is looking                                          | 54 |

|   | 3.8  | Applie | cation of SoCodeCNN in optimizing                                 |    |

|   |      | powe   | r consumption using DVFS on CPU                                   | 55 |

|   |      | 3.8.1  | Hardware & Software Infrastructure                                | 55 |

|   |      | 3.8.2  | DVFS on CPU utilizing SoCodeCNN in MPSoCs                         | 57 |

|   |      | 3.8.3  | Results                                                           | 58 |

|   |      | 3.8.4  | Advantage of SoCodeCNN based DVFS                                 | 61 |

|   | 3.9  | Discu  | ssion                                                             | 61 |

|   | 3 10 | Sumn   | nary                                                              | 62 |

| 4 | Peri | forming DVFS on CPU and GPU                                              | 63 |

|---|------|--------------------------------------------------------------------------|----|

|   | 4.1  | Prologue to Second Contributory Chapter                                  | 63 |

|   |      | 4.1.1 Article Details                                                    | 63 |

|   |      | 4.1.2 Media coverage                                                     | 64 |

|   | 4.2  | Introduction & Motivation                                                | 64 |

|   |      | 4.2.1 Contributions                                                      | 68 |

|   | 4.3  | System, Metric and Problem Formulation                                   | 69 |

|   |      | 4.3.1 Hardware & Software Infrastructure                                 | 69 |

|   |      | 4.3.2 Metric and Problem Definition                                      | 70 |

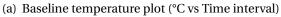

|   | 4.4  | Motivational Case Study: Effect of DVFS on CPU & GPU in Note 9           | 72 |

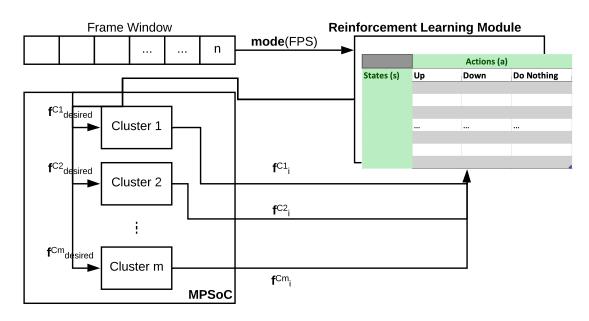

|   | 4.5  | Proposed Methodology: Next                                               | 77 |

|   |      | 4.5.1 Overview of Next                                                   | 77 |

|   |      | 4.5.2 Online Reinforcement Learning                                      | 78 |

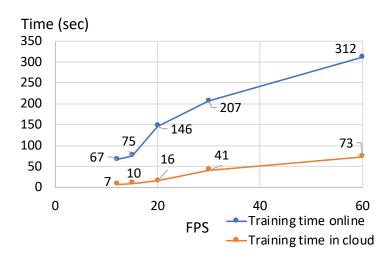

|   |      | 4.5.3 Offline training using Federated Learning or in Cloud              | 81 |

|   | 4.6  | Experimental Results                                                     | 82 |

|   |      | 4.6.1 Experimental setup                                                 | 82 |

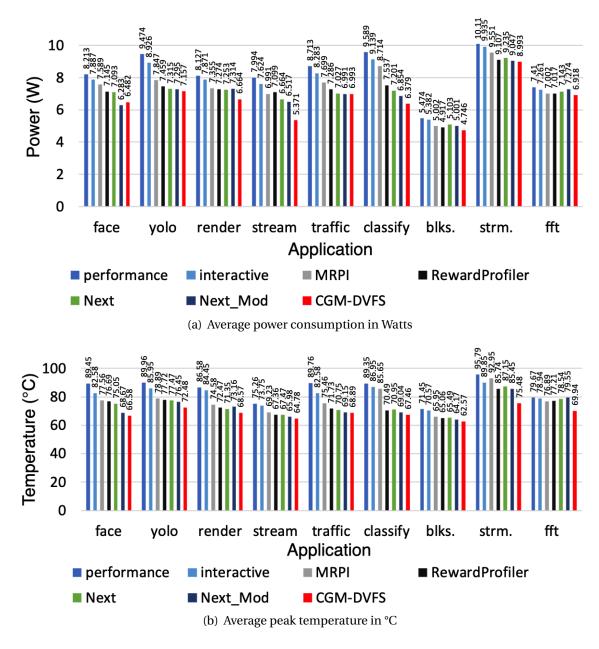

|   |      | 4.6.2 Power evaluation                                                   | 82 |

|   |      | 4.6.3 Thermal evaluation                                                 | 84 |

|   |      | 4.6.4 Analysis of power and thermal evaluation                           | 84 |

|   |      | 4.6.5 Overhead analysis                                                  | 84 |

|   | 4.7  | Scalability of Next across MPSoC platforms                               | 85 |

|   |      | 4.7.1 Hardware & Software Infrastructure                                 | 85 |

|   |      | 4.7.2 Modification of Next for Odroid XU4                                | 85 |

|   |      | 4.7.3 Experimental applications                                          | 86 |

|   |      | 4.7.4 Experimental results and Comparative study                         | 87 |

|   | 4.8  | Discussion                                                               | 89 |

|   | 4.9  | Summary                                                                  | 89 |

| 5 | Dow  | forming DVES on CDIL CDIL and DAM                                        | 90 |

| Э |      | forming DVFS on CPU, GPU and RAM  Drologue to Third Contributory Chapter | 90 |

|   | 5.1  | Prologue to Third Contributory Chapter                                   |    |

|   |      | 5.1.1 Article Details                                                    | 90 |

|   | F 2  | 5.1.2 Media coverage                                                     | 91 |

|   | 5.2  | Introduction & Motivation                                                | 91 |

|   | E 2  | 5.2.1 Contributions                                                      | 92 |

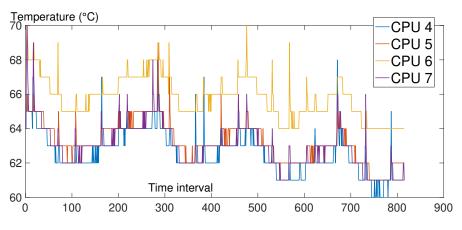

|   | 5.3  | Motivational Case Study: Effect of DVFS on memory                        | 93 |

|   | 5.4  | System model and problem formulation                                     | 97 |

|   |     | 5.4.1  | Hardware & Software Infrastructure                                       | . 97  |

|---|-----|--------|--------------------------------------------------------------------------|-------|

|   |     | 5.4.2  | Problem formulation                                                      | 97    |

|   | 5.5 | Propo  | osed methodology: CGM-DVFS                                               | 97    |

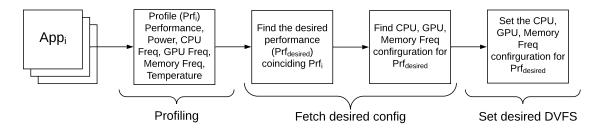

|   |     | 5.5.1  | Overview of CGM-DVFS                                                     | 98    |

|   |     | 5.5.2  | Steps in details                                                         | 98    |

|   |     |        | 5.5.2.1 Profiling                                                        | 98    |

|   |     |        | 5.5.2.2 Fetch desired config & Set desired DVFS                          | 100   |

|   |     | 5.5.3  | Justification of the design choices                                      | 100   |

|   | 5.6 | Exper  | imental results                                                          | 101   |

|   |     | 5.6.1  | Experimental applications                                                | 101   |

|   |     | 5.6.2  | Evaluation and Comparative study                                         | 101   |

|   | 5.7 | Discu  | ssion                                                                    | 105   |

|   | 5.8 | Sumn   | nary                                                                     | 106   |

| 6 | DVF | S & Te | mperature Side-Channel Attack                                            | 108   |

|   | 6.1 | Prolog | gue to Fourth Contributory Chapter                                       | 108   |

|   |     | 6.1.1  | Article Details                                                          | 108   |

|   | 6.2 | Introd | luction & Motivation                                                     | 109   |

|   |     | 6.2.1  | Contributions                                                            | 112   |

|   | 6.3 | Threa  | t Model                                                                  | 113   |

|   | 6.4 | System | m model and problem formulation                                          | . 115 |

|   |     | 6.4.1  | Hardware & Software Infrastructure of Galaxy Note 9                      | . 115 |

|   |     | 6.4.2  | Hardware & Software Infrastructure of Odroid XU4                         | . 116 |

|   |     | 6.4.3  | Problem formulation                                                      | . 116 |

|   |     | 6.4.4  | Importance of $	au$ , $\omega$ and $	heta$ in TSMP metric                | 118   |

|   | 6.5 | Propo  | osed Methodology: DATE                                                   | 120   |

|   |     | 6.5.1  | Overview of DATE                                                         | 120   |

|   |     | 6.5.2  | Learning Module                                                          | 120   |

|   |     | 6.5.3  | Decision Module                                                          | 122   |

|   | 6.6 | Case S | Study: Performing a real attack on Galaxy Note9 and Odroid XU4 $$ . $$ . | 124   |

|   |     | 6.6.1  | Dataset and CNN Model                                                    | 125   |

|   |     | 6.6.2  | Predicting passwords                                                     | 128   |

|   | 6.7 | Exper  | imental and Evaluation Results                                           | 129   |

|   |     | 6.7.1  | Hardware & Software Setup for Experiments                                | 129   |

|   |     | 6.7.2  | Experimental Results                                                     | 131   |

|   |     | 6.7.3  | Effect on Device Reliability                                             | 136   |

|              | 6.8 | Discu  | ssion                                                             | 137 |

|--------------|-----|--------|-------------------------------------------------------------------|-----|

|              | 6.9 | Sumn   | nary                                                              | 137 |

| 7            | Con | clusio | n                                                                 | 138 |

|              | 7.1 | Achie  | vements and impact                                                | 138 |

|              | 7.2 | Extens | sions and future work                                             | 140 |

|              |     | 7.2.1  | Automated program/application classification to perform bespoke   |     |

|              |     |        | DVFS on CPU, GPU and RAM                                          | 140 |

|              |     | 7.2.2  | Prioritizing QoE alongside QoS                                    | 141 |

|              |     | 7.2.3  | Reducing exploration time of application agnostic RL approaches . | 141 |

|              |     | 7.2.4  | Deep Learning and Reinforcement Learning to secure against tem-   |     |

|              |     |        | perature side-channel attack                                      | 142 |

| Bibliography |     |        |                                                                   | 143 |

# **List of Figures**

| 1.1  | Percentage of average power consumed by the big CPUs, LITTLE CPUs, GPUs, Memory and rest of the components such as the fan (active cooling), hardware storage & on-chip communication network of the Exynos 5422 |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | MPSoC while idle vs executing streamcluster benchmark                                                                                                                                                            | 4  |

| 2.1  | Resource management [Singh et al., 2020]                                                                                                                                                                         | 15 |

| 2.2  | Representative diagram of Deep Learning model                                                                                                                                                                    | 18 |

| 2.3  | Representative diagram of intelligent agent                                                                                                                                                                      | 19 |

| 3.1  | Histogram of source-code of "Hello, World" program vs Histogram of source-                                                                                                                                       |    |

|      | code of it with an additional integer variable initialization (Gray level vs                                                                                                                                     |    |

|      | Number of pixels)                                                                                                                                                                                                | 31 |

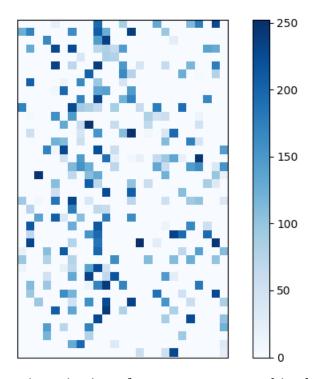

| 3.2  | Differences in activation of neurons represented in shades of blue colour                                                                                                                                        |    |

|      | encoding                                                                                                                                                                                                         | 31 |

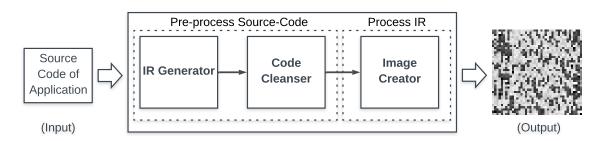

| 3.3  | Block diagram of SoCodeCNN                                                                                                                                                                                       | 37 |

| 3.4  | Processing of LLVM IR Code of Program 1 by IR Generator and Code Cleanser                                                                                                                                        |    |

|      | modules                                                                                                                                                                                                          | 39 |

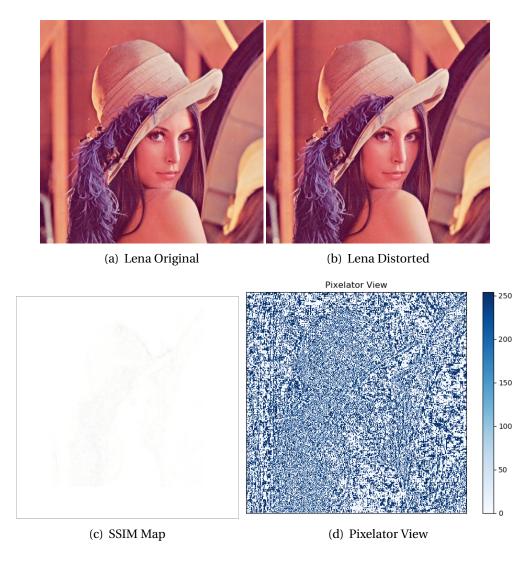

| 3.5  | Highlighting differences between distorted Lena and reference Lena im-                                                                                                                                           |    |

|      | ages using SSIM and Pixelator                                                                                                                                                                                    | 45 |

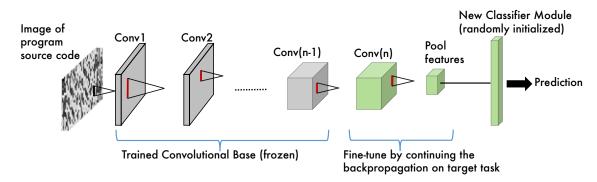

| 3.6  | Network architecture used for fine-tuning                                                                                                                                                                        | 47 |

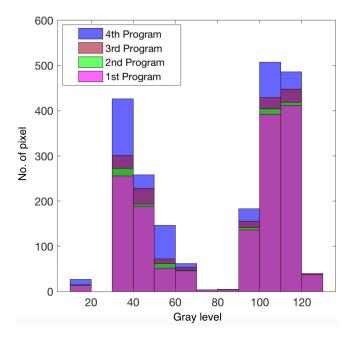

| 3.7  | Histogram of source-code of 1st, 2nd, 3rd and 4th Program                                                                                                                                                        | 51 |

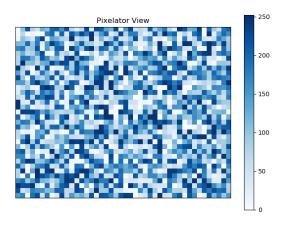

| 3.8  | Differences in pixel of 1st and 2nd Program using Pixelator view                                                                                                                                                 | 52 |

| 3.9  | Deep Dream Images of three different types of program source-codes: Com-                                                                                                                                         |    |

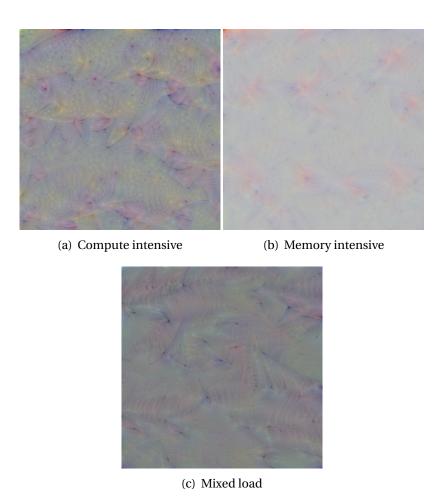

|      | pute, Memory & Mixed                                                                                                                                                                                             | 52 |

| 3.10 | Classification of MiBench [Guthaus et al., 2001] benchmark suits (Bench-                                                                                                                                         |    |

|      | mark vs Confidence in % for a specific class)                                                                                                                                                                    | 53 |

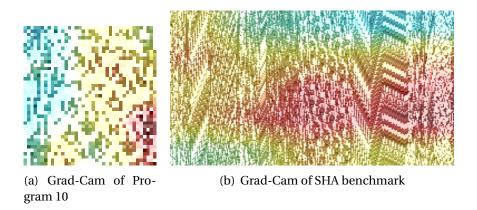

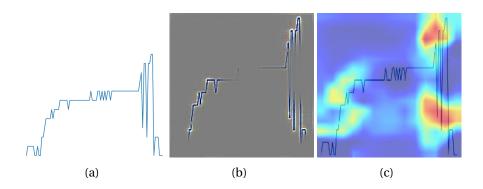

| 3.11 | Grad-Cam visualization                                                                                                                                                                                           | 54 |

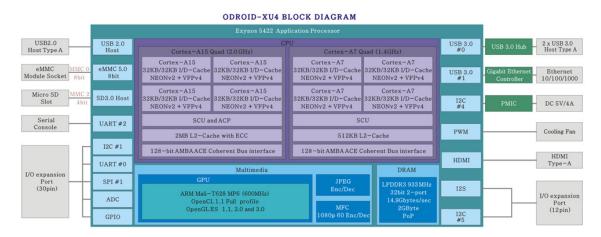

| 3.12 | Odroid XU4 [odr, b] MPSoC block diagram highlighting major components                                                                                                                                            | 55 |

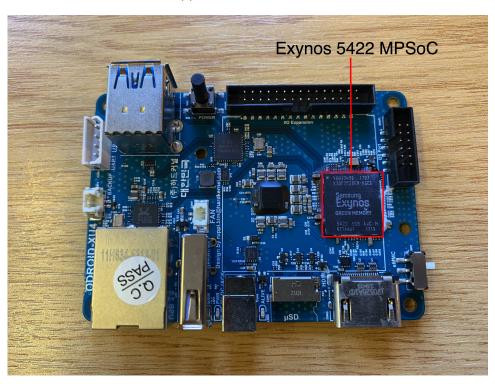

| 3.13 | Odroid XU4 development board and Exynos 5422 MPSoC                                                                                                                                                               | 56 |

| 3.14 | Block diagram of power management agent, APM, using SoCodeCNN                 | 57 |

|------|-------------------------------------------------------------------------------|----|

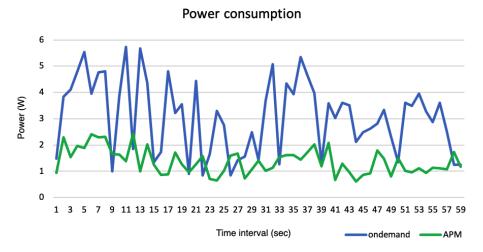

| 3.15 | Power consumption of executing Program 9 on ondemand vs APM                   | 59 |

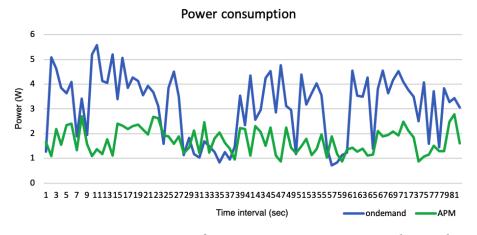

| 3.16 | Power consumption of executing Program 10 on ondemand vs APM                  | 59 |

| 3.17 | Power consumption of executing Program 10 on ondemand vs APM                  | 60 |

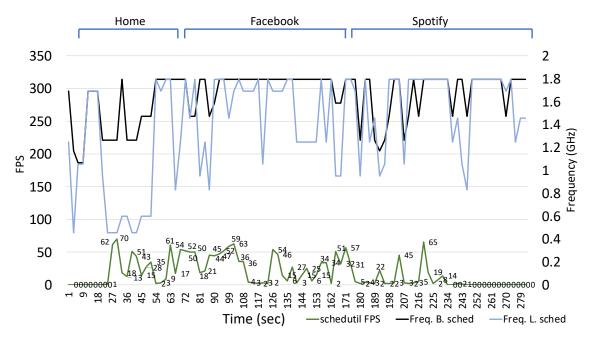

| 4.1  | FPS generation, operating frequency of big and LITTLE CPUs in Samsung         |    |

|      | Note 9 while using home screen, Facebook and Spotify apps during a ses-       |    |

|      | sion on schedutil governor                                                    | 65 |

| 4.2  | Interaction between the user and an app on a smartphone happens through       |    |

|      | display/UI                                                                    | 65 |

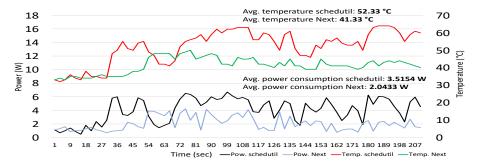

| 4.3  | Power consumption and temperature of big CPUs on Samsung Note 9 while         |    |

|      | using home screen, Facebook and Spotify apps during a session on schedu-      |    |

|      | til vs Next                                                                   | 68 |

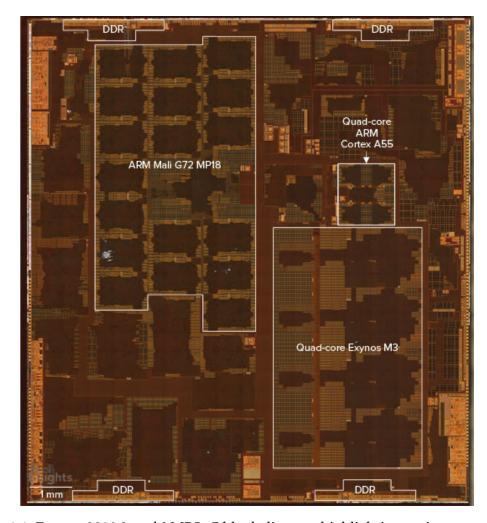

| 4.4  | Exynos 9810 [exy, b] MPSoC block diagram highlighting major components        | 70 |

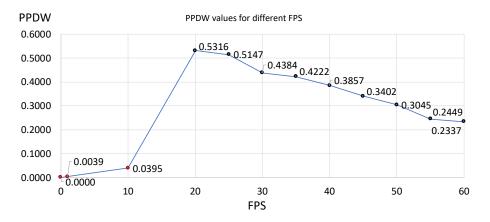

| 4.5  | PPDW value trend as the FPS, peak temperature of big CPUs and power           |    |

|      | consumption scale accordingly                                                 | 71 |

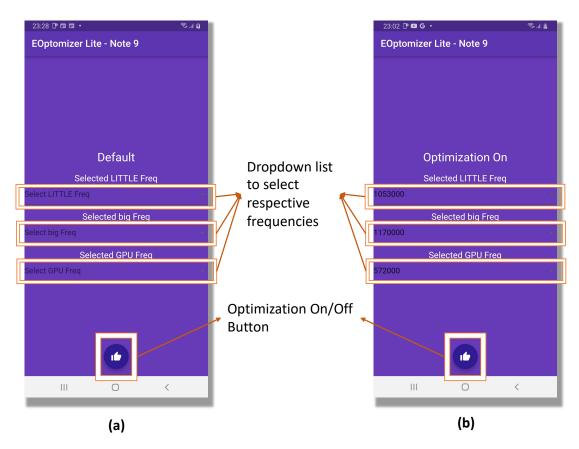

| 4.6  | Graphical interface of 'EOptomizer Lite - Note 9' mobile app [eop, ]. (a)     |    |

|      | shows the app UI when CPUs & GPUs operate on default frequencies of the       |    |

|      | schedutil governor; (b) shows the app UI when the CPUs & GPUs operate         |    |

|      | at a chosen frequency for LITTLE & big CPUs and GPUs respectively             | 73 |

| 4.7  | Block digram of Next agent                                                    | 79 |

| 4.8  | Increase in training time for online vs cloud (offline) as the frame rate in- |    |

|      | creases at part of the chosen states                                          | 80 |

| 4.9  | Average power consumption for different mobile applications using schedu-     |    |

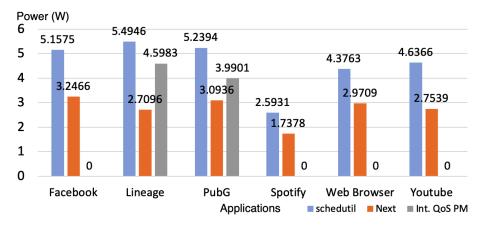

|      | til, Next and Int. QoS PM approaches                                          | 83 |

| 4.10 | Average peak temperature of big CPUs and the device for different mobile      |    |

|      | applications using schedutil, Next and Int. QoS PM approaches                 | 83 |

| 4.11 | Average power consumption (Watts) and average peak temperature (°C)           |    |

|      | on Odroid XU4 (Exynos 5422 MPSoC) while executing different applica-          |    |

|      | tions on different methodologies: performance, interactive, MRPI, Reward-     |    |

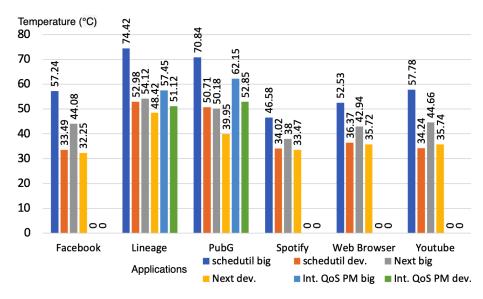

|      | Profiler & Next                                                               | 88 |

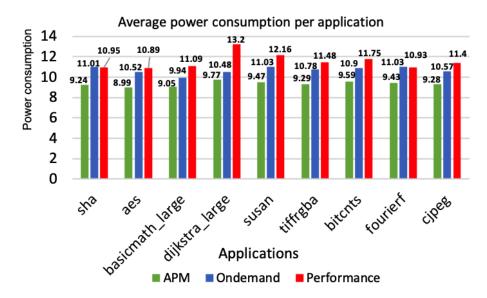

| 5.1  | Average power consumption (Watts) while executing different benchmark         |    |

|      | applications on different approaches                                          | 92 |

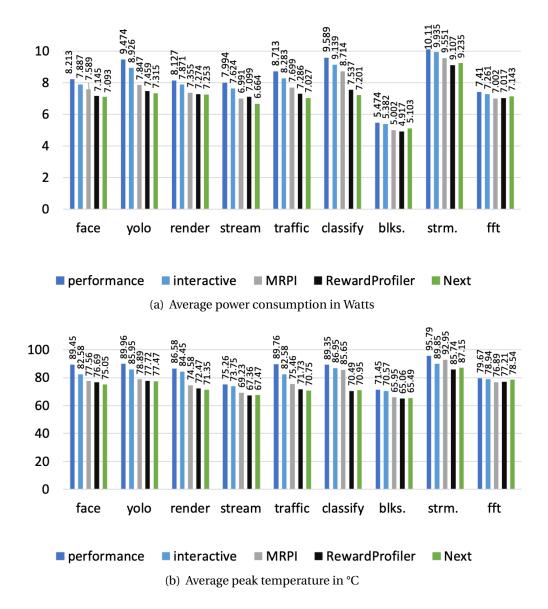

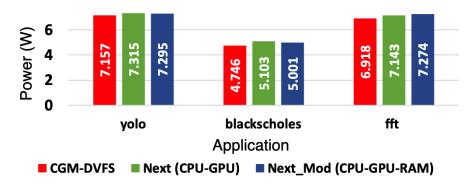

| 5.2  | Block diagram illustrating CGM-DVFS Methodology                               | 98 |

| 5.3  | Average power consumption (Watts) and average peak temperature (°C) of Odroid XU4 while executing different applications on different methodologies: performance, interactive, MRPI, RewardProfiler, Next, Next_Mod |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | & CGM-DVFS                                                                                                                                                                                                          | 103 |

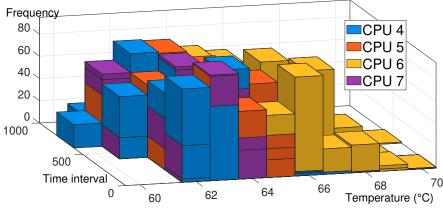

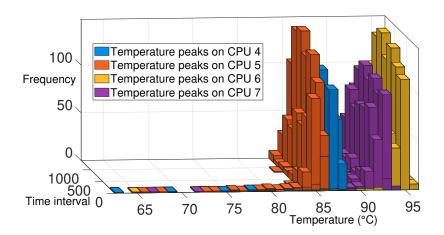

| 6.1  | Temperature readings on 4 ARM A15 big CPU cores while idle                                                                                                                                                          | 110 |

| 6.2  | Temperature peaks on 4 ARM A15 big CPU cores while executing Blacksc-                                                                                                                                               | 111 |

| 6.3  | holes benchmark                                                                                                                                                                                                     | 111 |

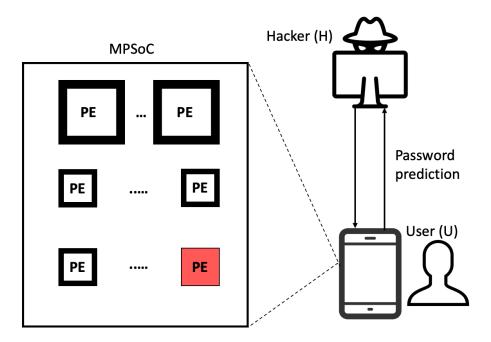

| 0.3  | side-channel attack, where PE represents the processing elements of the                                                                                                                                             |     |

|      | smartphone utilizing MPSoC, H represents the hacker & U represents the                                                                                                                                              |     |

|      | user of the smartphone utilizing MPSoC                                                                                                                                                                              | 113 |

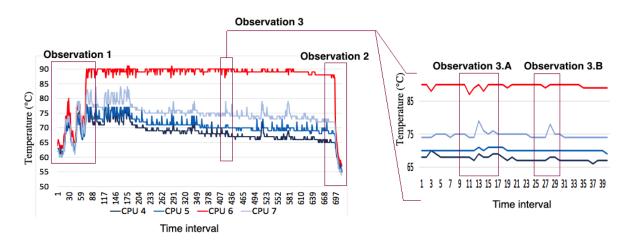

| 6.4  | Observations of thermal behavior of four ARM Cortex A15 (big) CPUs on                                                                                                                                               | 115 |

| 0.1  | Odroid XU4 while performing RSA encryption and decryption                                                                                                                                                           | 118 |

| 6.5  | Proposed Methodology: DATE                                                                                                                                                                                          |     |

| 6.6  | Architecture of ResNet50 CNN model with modified last fully connected                                                                                                                                               | 121 |

| 0.0  | layer used in password classification                                                                                                                                                                               | 127 |

| 6.7  | Graphical representation of thermal behavior (time interval vs tempera-                                                                                                                                             |     |

|      | ture in °C) of encryption operation using the following passwords: 111111,                                                                                                                                          |     |

|      | 123456, passw0rd & football                                                                                                                                                                                         | 128 |

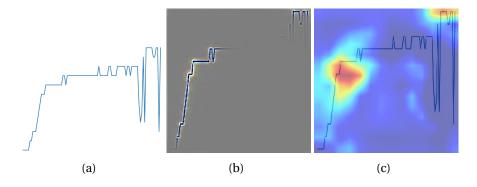

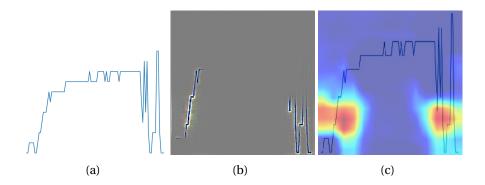

| 6.8  | Focus area of ResNet50 network on a representative graph of password:                                                                                                                                               |     |

|      | 111111                                                                                                                                                                                                              | 130 |

| 6.9  | Focus area of ResNet50 network on a representative graph of password:                                                                                                                                               |     |

|      | 123456                                                                                                                                                                                                              | 130 |

| 6.10 | Focus area of ResNet50 network on a representative graph of password:                                                                                                                                               |     |

|      | Football                                                                                                                                                                                                            | 130 |

| 6.11 | Focus area of ResNet50 network on a representative graph of password:                                                                                                                                               |     |

|      | passw0rd                                                                                                                                                                                                            | 131 |

| 6.12 | Table showing maximum operating temperature of ARM A15 (big) CPUs                                                                                                                                                   |     |

|      | for different applications along with baseline temperature and values of                                                                                                                                            |     |

|      | Baseline Maximum Thermal Deviation $(\tau)$ for corresponding CPUs                                                                                                                                                  | 132 |

| 6.13 | Table showing least average operating temperature of ARM A15 (big) CPUs                                                                                                                                             |     |

|      | for different applications and values of Spatial Maximum Thermal Devia-                                                                                                                                             |     |

|      | tion ( $	au$ ) for corresponding CPUs                                                                                                                                                                               | 132 |

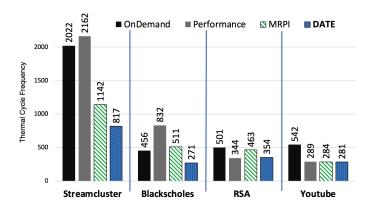

| 6.14 | Frequency of thermal cycles for different benchmarking applications on                                                                                                                                              |     |

|      | different power and mapping schemes                                                                                                                                                                                 | 133 |

| 6.15 | Temperature peaks of 4 ARM A15 big CPU cores while executing Blacksc-  |     |

|------|------------------------------------------------------------------------|-----|

|      | holes benchmark using DATE                                             | 133 |

| 6.16 | Temperature peaks of 4 ARM A15 big CPU cores while executing Blacksc-  |     |

|      | holes benchmark using Linux's Ondemand and Performance governors .     | 134 |

| 6.17 | Histograms of temperature peaks of ARM big CPUs for Blackscholes using |     |

|      | ondemand governor vs DATE (Frequency vs temperature (°C))              | 135 |

# Chapter 1

## Introduction

Mobile computing systems [B'far, 2004, Satyanarayanan, 2010, Lukowicz et al., 2004, Singh et al., 2020, Isuwa et al., 2022] such as smartphones and smart wearables utilizing Multi-Processor System-on-a-Chip (MPSoC) have become an integral part of our daily lives. Given the fact that these devices are easily accessible to us and are mostly battery operated, the key objectives are to optimize performance, power consumption, thermal behaviour and security of such devices. One of the most popular ways to achieve these objectives is to perform Dynamic Voltage and Frequency Scaling (DVFS) on different processing elements such as CPU, GPU (Graphical Processing Unit) and RAM (Random Access Memory). In this chapter, we explore the concept of DVFS and its operational importance in MPSoCs. This chapter offers reflections on some of the key challenges of operating an MPSoC. The major contributions made by this thesis in an attempt to address these challenges are also highlighted. A snapshot of each chapter is also presented here to illustrate the structure of the thesis. Finally, the publications that were made during the period of this research are listed at the end of the chapter.

#### 1.1 Motivation

Modern smartphones such as Samsung Galaxy S20, Note20, iPhone and wearable devices such as Samsung Galaxy Watch and Apple Watch devices have become an integral part of most people's daily lives. We heavily rely on these battery operated smart devices to perform a plethora of day-to-day tasks such as controlling our smart home [Jiang et al., 2004, Wang et al., 2013, Kumar and Lee, 2014], watching our favourite TV series, playing your favourite games and keeping track of our social and active lives. With an increase in the performance demand of embedded/mobile applications, which cannot be satisfied by simply increasing the operating frequency of a single-core processor or by customizing the single processor core, we could notice the rise of Multi-Processor

System-on-a-chip [Jerraya and Wolf, 2004, Wolf et al., 2008, Singh et al., 2013], where multiple processing cores are utilized on a single chip system.

Moreover, most of these modern battery operated smartphones and wearables now come equipped with heterogeneous Multi-Processor System-on-a-Chip (MPSoC) [Kumar et al., 2005, Dey et al., 2019d], which utilizes different types of processing cores such as CPU, GPU (Graphical Processing Unit), to cater for the performance and power consumption requirement of executing different types of applications on such devices. According to several studies [Singh et al., 2013, Reddy et al., 2017, Dey et al., 2019c], especially by Singh et al. [Singh et al., 2013], applications, consisting of several workloads/tasks, could be classified into three different types: compute intensive, memory intensive, and mixed (compute and memory intensive), based on the number of instructions per cycle or memory accesses. To execute these different types of workloads heterogeneous MPSoCs come equipped with different types of processing elements such as CPU & GPU, and memory units such as RAM (Random Access Memory) [Patterson and Hennessy, 2016].

Given the fact that these embedded/mobile devices operate on battery, one of the key challenges of operating such devices is reducing the power consumption of the device so that these devices could operate longer on battery without the need of charging. According to [Muthukaruppan et al., 2013], there are five popular methods leading to the reduction of power consumption in mobile platforms utilizing MPSoCs, which includes:

- 1. *Dynamic Power Management* (DPM) allows idle processing elements or other idle components of the system to be suspended if required in order to reduce power consumption [Gupta et al., 2017].

- 2. *Dynamic Voltage Frequency Scaling* (DVFS) allows processing elements to operate at variable voltage and frequency (V-F) levels [Shin et al., 2000, Khriji et al., 2022] to reduce power consumption. DVFS manages power consumption of the processing elements by balancing the trade-off between performance and power consumption. The main ideology behind DVFS is to vary the operating voltage (V) and frequency (F) of a processing element dynamically, based on the current workload and performance requirements. By adjusting the voltage and frequency, DVFS can achieve optimal performance while minimizing power consumption. More details on DVFS and power consumption are provided in section 2.1 of Chapter 2.

- 3. Customization of the processing elements to match the processing needed of a workload on an MPSoC [Lin and Fei, 2010].

- 4. Customizing cache based memory access [Gordon-Ross et al., 2004].

- 5. Mapping tasks of an application to the processing elements so that workload could be balanced across all processing elements in an MPSoC. This improves utilization of the processing elements effectively and reduces power consumption on the device [Benoit and Robert, 2008].

At the operating system level, we could only use DPM and DVFS based methodologies for power consumption reduction, which could further add to the resource mapping and allocation techniques. Thus, software based profiling systems mostly utilize these two methodologies to profile power consumption for a set of applications on heterogeneous MPSoCs. Moreover, out of the aforementioned methodologies, DVFS is a very popular mechanism used to reduce the power consumption of the MPSoC by the means of reducing the dynamic power consumption ( $P \propto V^2 f$ ) by reducing the operating frequency of the processing elements. Since, the dynamic power consumption in an MPSoC is proportional to the operating frequency of the processing elements, as shown in the equation, executing the application on a reduced operating frequency leads to a reduced power consumption of the device.

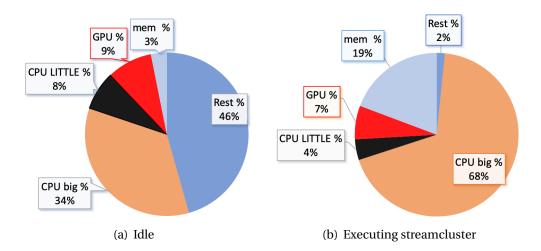

In majority of the modern heterogeneous MPSoCs, CPU, GPU and RAM support DVFS, where each of these components affects the total power consumption of the device differently for different types of applications. For example, when we observed the power consumption due to the effects of DVFS in CPU, GPU and RAM (denoted as memory only) in Odroid XU4 [odr, b], utilizing Exynos 5422 MPSoC [exy, a], while idle (when no other application is executing other than background processes of the OS), we observed that big CPUs, LITTLE CPUs, GPU and memory consumes 34%, 8%, 9% and 3% of the average power consumption respectively of the device on an average (as shown in Fig. 1.1.(a)). Here, the Exynos 5422 MPSoC utilizes ARM's big.LITTLE processor technology [Kim et al., 2014], where two different types of CPUs (big and LITTLE) are utilized to cater for performance and power consumption requirements of executing applications. In Fig. 1.1.(a), the average power consumed by the big CPUs, LITTLE CPUs, GPUs, Memory and rest of the components such as the fan (active cooling), hardware storage & on-chip communication network of the Exynos 5422 MPSoC while idle is 3.53 watts (W).

In order to observe the effect of DVFS of each of the major components (big CPUs, LITTLE CPUs, GPU and memory) of the MPSoC the power consumption was recorded while operating each of these components in their maximum operating frequency and minimum operating frequency consecutively to measure the percentage of total power

consumption that is attributed to the maximum and minimum frequency. Fig. 1.1.(b) illustrates the percentage of total power consumption of big CPUs, LITTLE CPUs, GPU, memory and rest of the components in the Exynos 5422 MPSoC while executing Streamcluster benchmark (in native mode) from the PARSEC benchmark suite [Bienia, 2011a]. The average power consumed by the big CPUs, LITTLE CPUs, GPUs, Memory and rest of the components of the Exynos 5422 MPSoC while executing Streamcluster benchmark is 10.11 watts (W). Streamcluster benchmark was chosen because it reflects a mixed workload (both compute intensive and memory intensive) [Dev et al., 2019c] to mimic the workload of most of the popular applications used by the users. From Fig. 1.1 one interesting observation is that in a mixed workload application the big CPU, LITTLE CPU, GPU and memory can contribute to 68%, 4%, 7% and 19% of the average power consumption respectively, which constitutes a majority of the power consumed on the platform, and hence, DVFS in CPU, GPU and memory plays an important role towards the total power consumption of the device. Note that in Fig. 1.1.(a), the rest of the components such as the fan (active cooling), hardware storage & on-chip communication network of the Exynos 5422 MPSoC separate to the big CPU, LITTLE CPU, GPU and memory while idle might be consuming almost 46% of the average power consumed but in reality the rest of the components are consuming only 1.62 watts (W) as the average power consumption of the Exynos 5422 MPSoC while idle is 3.53 watts.

Figure 1.1: Percentage of average power consumed by the big CPUs, LITTLE CPUs, GPUs, Memory and rest of the components such as the fan (active cooling), hardware storage & on-chip communication network of the Exynos 5422 MPSoC while idle vs executing streamcluster benchmark

On the other hand, power consumption in these mobile platforms utilizing MPSoC has a direct correlation with the heat dissipation in such devices [DeVogeleer et al.,

2014, De Vogeleer et al., ]. Therefore, increased power consumption in these MPSoCs leads to an increased heat dissipation, which retrospectively increases the peak temperature of the processing elements. Moreover, according to studies [Chantem et al., 2010, Coskun et al., 2007, Zhou et al., 2015, Singh et al., 2020] an increase in the operating temperature by 10-15° centigrade in the MPSoC could reduce the lifespan of the MPSoC by 2×. Additionally, an increase in peak temperature of the processing elements such as CPU in the MPSoC could also expose vulnerabilities related to thermal side-channel attack [Hutter and Schmidt, 2013, Masti et al., 2015, Bartolini et al., 2016], compromising sensitive data such as password while processing information on the DVFS enabled CPUs. Therefore, given these pieces of evidence, it is crucial to perform DVFS in mobile MPSoCs such that the performance requirement of the executing applications could be achieved while reducing power consumption, peak temperature of the device and improve security against thermal side-channel attack.

That said, the majority of traditional approaches to perform DVFS include dynamic power or thermal management or both [Singh et al., 2020]. Dynamic power and thermal management could be of two types, Proactive and Reactive. In Proactive, the methodologies try to pro-actively determine the future state(s) of the system and take actions to optimize either power consumption or thermal behaviour or both, whereas, in Reactive, the methodologies are reactive in nature and only take actions in order to perform optimizations when a certain state is met. For proactive management, the state could be future temperature by using a temperature estimation model or future workload by using workload estimation model, and actions could be resource selection and/or operating voltage (V) or operating frequency (F) control. In comparison, the state for reactive management could be the current workload or temperature. Whatsoever, these states are typically determined with the help of hardware performance monitoring counters providing data about metrics such as power consumption and performance. Moreover, these performance counters are special registers in the hardware that hold the value for the respective state(s) and are usually manufacturing vendor locked to be accessible. This makes it particularly difficult to perform DVFS for different types of applications (workloads) in the software layers of the OS if access to these performance counters is not accessible. Additionally, incorporating these hardware performance counters are expensive and increases the size of the MPSoC, especially in consumer devices such as smartphones. Therefore, this calls for an approach capable of performing DVFS based on the type of application (workload) without the need to access such performance counters.

Moreover, when it comes to consumer devices such as smartphones, user's satisfaction in terms of Quality of Service (QoS) plays an important role [Pathania et al., 2014, Sahin and Coskun, 2015, Shafik et al., 2016, Peters et al., 2016, Bhat et al., 2018]. At the same time on such devices, most of the existing methodologies related to optimizing performance [Pathania et al., 2015, Gupta et al., 2017] only consider performance and power consumption together in a metric such as Performance Per Watt (PPW) while not considering temperature into such metrics. This calls for an approach which is capable of performing DVFS while taking QoS, performance, power consumption and thermal behaviour into consideration. Additionally, all the published studies and methodologies only perform DVFS on CPU or GPU or memory or a combination of these but not on all of them together. Therefore, it is crucial to be able to perform DVFS on all these components of the MPSoC to achieve better performance, power and temperature optimization.

On the other hand, performing DVFS on processing cores leads to heat dissipation and propagation on the core, which can be observed over time in order to deduce security flaws. This type of an attack is called temperature based side-channel attack and could be directly correlated to DVFS since increased operating frequency on a processing core leads to increased heat dissipation as pointed out in [Hutter and Schmidt, 2013, Masti et al., 2015, Bartolini et al., 2016]. Henceforth, devising DVFS approaches to secure against such attack is very important while catering for the performance requirements of the executing application on the MPSoC.

To address the aforementioned shortcomings we need unorthodox approaches to perform DVFS in MPSoCs and this thesis introduces such approaches. In the following subsection, we will explore some of the key challenges in MPSoCs that this thesis is trying to address.

### 1.2 Key Challenges

**Reduced power consumption**. Most of the smartphones and smart wearables utilizing MPSoCs operate by stand-alone power supply like battery and henceforth, this calls for power optimization on such devices in order to increase the operational time of the systems and reduce the power consumption costs in the process.

**Reduced peak temperature**. An increase in temperature of the processing elements in the MPSoC in smartphones and smart wearables could lead to the reduction of lifespan of the device. Moreover, an increase in the peak temperature could also increase the overall thermal behaviour of the device itself and hence, contributing to discomfort of

the user. Therefore, this calls for optimization of peak temperature of the processing elements of the MPSoC.

Improved security against thermal side-channel attack. Compute intensive tasks such as encryption and decryption on the processing elements in the MPSoC could lead to surge in the peak temperature, which exposes vulnerability to temperature based side-channel attacks. Such an attack in the smartphones and smart wearables could be exploited by Malwares or hackers and henceforth, this calls for an approach to secure such devices from thermal side-channel attack.

#### 1.3 Contributions

To address the aforementioned key challenges, the main contributions of this thesis are fourfold, which have been made during the course of this research, and are summarized as follows:

- 1. Given the fact that smartphone users are ever increasing along with an increased availability of mobile applications [Cruz et al., 2019], different types of applications demand different performance and power consumption requirements. We developed the first ever methodology to classify applications automatically into the three categories: compute intensive, memory intensive and mixed workload; such that DVFS could be performed on the CPU to reduce the power consumption of the device while executing the application.

- 2. Smartphones and smart wearables come equipped with touch enabled display, on which the user interacts to perform a task. Throughout the day, the user's interaction behaviour with the application on these devices through touch interaction changes over time, and henceforth, DVFS needs to be performed to consider the user's interaction with the applications. We developed the first approach to perform DVFS on CPU and GPU while considering the user's mobile usage behaviour, performance of the executing application, power consumption and temperature of the device. We also introduce a metric based on performance, power consumption and thermal behaviour as well.

- 3. Although for most applications, which are compute intensive and mixed work-load, performing DVFS on CPU and GPU could lead to massive reduction in power consumption and peak temperature of the device, however, for many applications, which are more memory intensive, performing DVFS on RAM along with

DVFS on CPU and GPU could lead to more power saving and reduction in thermal behaviour. To address this, we developed the first approach to perform DVFS on CPU, GPU and RAM.

4. Temperature based side-channel attack could be a real threat on smartphones and smart wearables. We developed the first machine learning based mechanism to perform temperature side-channel attack in a real smartphone platform and then developed an approach to secure such devices from these types of attacks. We also proposed a metric to evaluate security of such devices against temperature side-channel attacks.

#### 1.4 Thesis Outline

The remainder of this thesis is organized as follows:

**Chapter 2 (Background):** We review the existing relevant literature that serves as the background for the research conducted in this thesis. We start by examining the role of DVFS in the reduction of power consumption and peak temperature on mobile platforms employing MPSoC and explore the related proposed approaches in this area.

**Chapter 3 (Performing DVFS on CPU)**: We introduce an automated technique to classify applications and then perform DVFS on CPU to cater for the performance requirement of the executing application along with reduced power consumption.

**Chapter 4 (Performing DVFS on CPU and GPU)**: We introduce a software agent that performs DVFS on CPU and GPU while taking the user's interaction with the touch enabled mobile device into consideration such that power consumption and peak temperature of the device could be reduced while catering for performance.

**Chapter 5 (Performing DVFS on CPU, GPU and RAM)**: We introduce a software agent that performs DVFS on CPU, GPU and RAM to cater for the performance requirement of the executing application while consuming the least power and reducing peak temperature in the process.

**Chatper 6 (DVFS & Temperature Side-Channel Attack)**: We introduce a novel machine learning approach to perform temperature based side-channel attack in real mobile platforms utilizing MPSoC to explore the threat of such attacks. We then introduce a mechanism to secure such devices against temperature based side-channel attacks using DVFS approach.

**Chatper 7 (Conclusion)**: We conclude this work in this chapter, providing a summary of the key contributions made throughout this thesis. Additionally, potential future directions as an extension are also provided.

#### 1.5 Publications

The research conducted in this thesis has resulted in several peer-reviewed publications listed below in chronological order:

- 1. **Somdip Dey**, Amit Kumar Singh, Klaus McDonald-Maier, "Energy Efficiency and Reliability of Computer Vision Applications on Heterogeneous Multi-Processor Systems-on-Chips (MPSoCs)", presented at MaRIONet Summer School, Glasgow, UK, 16-20th July, 2018.

- Somdip Dey, Grigorios Kalliatakis, Sangeet Saha, Amit Kumar Singh, Shoaib Ehsan, and Klaus McDonald-Maier. "MAT-CNN-SOPC: Motionless Analysis of Traffic Using Convolutional Neural Networks on System-On-a-Programmable-Chip", 2018 NASA/ESA Conference on Adaptive Hardware and Systems (AHS 2018), 2018.

- 3. **Somdip Dey**, Enrique Zaragoza Guajardo, Karunakar Reddy Basireddy, Amit Kumar Singh and Klaus McDonald-Maier, "EdgeCoolingMode: An Agent Based Thermal Management Mechanism for DVFS Enabled Heterogeneous MPSoCs", The 32nd International Conference on VLSI Design and 18th International Conference on Embedded Systems (VLSID), 2019.

- 4. Samuel Isuwa, **Somdip Dey**, Amit Kumar Singh and Klaus McDonald-Maier, "TEEM: Online Thermal- and Energy-EfficiencyManagement on CPU-GPU MPSoCs", 2019 Design, Automation, and Test in Europe Conference (DATE), 2019.

- 5. Somdip Dey, Sangeet Saha, Xiaohang Wang, Amit Kumar Singh and Klaus McDonald-Maier, "RewardProfiler: A Reward Based Design Space Profiler on DVFS Enabled MPSoCs", 5<sup>th</sup> IEEE International Conference on Edge Computing and Scalable Cloud (IEEE EdgeCom), 2019.

- 6. **Somdip Dey**, Amit Kumar Singh, Xiaohang Wang and Klaus McDonald-Maier, "Dead-Pool: Performance Deadline Based FrequencyPooling and Thermal Management Agent in DVFS Enabled MPSoCs", 5<sup>th</sup> IEEE International Conference on Edge Computing and Scalable Cloud (IEEE EdgeCom), 2019.

- 7. **Somdip Dey**, Amit Kumar Singh and Klaus McDonald-Maier, "P-EdgeCoolingMode: An Agent Based Performance Aware Thermal Management Unit for DVFS Enabled Heterogeneous MPSoCs", IET Computers & Digital Techniques, 2019.

- 8. **Somdip Dey**, Amit Kumar Singh, Xiaohang Wang and Klaus McDonald-Maier, "User Interaction Aware Reinforcement Learning for Power and Thermal Efficiency of CPU-GPU Mobile MPSoCs", 2020 Design, Automation and Test in Europe Conference (DATE 2020).

- 9. **Somdip Dey**, Amit Kumar Singh, Klaus McDonald-Maier, "New approaches to DVFS in mobile MPSoC for power-, thermal-efficiency and reliability", presented at 16th International Summer School on Advanced Computer Architecture and Compilation for High-performance Embedded Systems (ACACES 2020), Fiuggi, Italy, 12-18 July, 2020.

- 10. **Somdip Dey**, Amit Kumar Singh, Dilip Kumar Prasad and Klaus McDonald-Maier, "SoCodeCNN: Program Source Code for Visual CNN Classification Using Computer Vision Methodology", IEEE Access. [Most popular paper of IEEE Access & IEEE Xplore Digital Library from December, 2019 to August, 2020]

- 11. Khadidja Gaffour, Mohammed Kamal Benhaoua, **Somdip Dey**, Amit Singh and Benyamina Abou El Hassan, "Dynamic clustering approach for Run-time Applications Mapping on NoC-Based Multi/Many-core systems", Second international conference on Embedded & Distributed Systems (EDiS'2020), 2020.

- 12. Amit Kumar Singh, **Somdip Dey**, Karunakar Reddy Basireddy, Klaus McDonald-Maier, Geoff Merrett, Bashir Al-Hashimi, "Dynamic Energy and Thermal Management of Multi-Core Mobile Platforms: A Survey", IEEE Design & Test. [**One of the most popular paper of IEEE Design & Test magazine in IEEE Xplore Digital Library since October, 2020]**

- 13. **Somdip Dey**, Amit Singh, Dilip Prasad, Klaus McDonald-Maier, "Temporal Motionless Analysis of Videos", 31st IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP 2020). [**One of the most popular paper of ASAP conference series in IEEE Xplore Digital Library since August, 2020]**

- 14. **Somdip Dey**, Amit Singh, Dilip Prasad, Klaus McDonald-Maier, "IRON-MAN: An Approach To Perform Temporal Motionless Analysis of Video using CNN in MP-SoC," in IEEE Access. [Most popular paper of IEEE Access on September, 2020]

- 15. **Somdip Dey**, Suman Saha, Amit Kumar Singh, and Klaus McDonald-Maier, "FruitVeg-CNN: Power- and Memory-Efficient Classification of Fruits & Vegetables Using

- CNN in Mobile MPSoC", 2020 IEEE 17th India Council International Conference (INDICON 2020), 2020.

- 16. **Somdip Dey**, Amit Kumar Singh and Klaus McDonald-Maier, "ThermalAttackNet: Are CNNs Making It Easy To Perform Temperature Side-Channel Attack In Mobile Edge Devices?" in Future Internet 13, no. 6: 146. [Most viewed paper of Future Internet since June, 2021]

- 17. **Somdip Dey**, Amit Kumar Singh, Xiaohang Wang and Klaus McDonald-Maier, "DATE: Defense Against TEmperature Side-Channel Attacks in DVFS Enabled MPSoCs." (**Under revision**)

- 18. **Somdip Dey**, Samuel Isuwa, Amit Kumar Singh and Klaus McDonald-Maier, "Asynchronous Hybrid Deep Learning: A Deep Learning Based Resource Mapping in DVFS Enabled Mobile MPSoCs", 2021 IEEE 7th World Forum on Internet of Things (WF-IoT). IEEE, 2021.

- 19. **Somdip Dey**, Samuel Isuwa, Suman Saha, Amit Kumar Singh and Klaus McDonald-Maier, "CPU-GPU-Memory DVFS for Power-Efficient Mobile MPSoC" in Future Internet.

- 20. Samuel Isuwa, **Somdip Dey**, Andre P. Ortega, Amit Kumar Singh, Bashir Al-Hashimi and Geoff Merrett, "QUAREM: Maximising QoE through Adaptive Resource Management in Mobile MPSoC Platforms" in ACM Transactions on Embedded Computing Systems.

# **Chapter 2**

# **Background**

Multi-core embedded mobile platforms such as smartphones and smart wearables are on the rise as they enable efficient parallel processing to meet ever-increasing performance requirements. However, since these platforms need to cater for increasingly dynamic applications (workloads), efficient dynamic resource management is desired mainly to enhance the power and thermal efficiency for better user experience with increased operational time and lifetime of these mobile devices. Moreover security, especially against temperature side-channel attack, is one of the key requirements in such platforms. In this chapter, we first discuss some of the key concepts related to dynamic power and thermal management approaches along with the importance of security approaches against temperature side-channel attack, and then we explore the related published works for multi-core mobile platforms.

### 2.1 Introduction

Multi-Processor System-on-a-Chip (MPSoC) consists of different components such as microprocessors, memory chips, etc. developed through CMOS (Complementary Metal Oxide Semiconductor) technology. The total power consumption ( $P_{total}$ ) in a CMOS integrated circuit is dependent on two components, as shown in Eq. 2.3 [Basireddy, 2019]:

- Static power consumption ( $P_{static}$ ), which is the power consumed when the transistors are not in the process of switching (activity). It is represented by Eq. 2.1, where V is the operating voltage and  $I_{leakage}$  is the leakage current [Jan et al., 2003].

- Dynamic power consumption ( $P_{dynamic}$ ), which is the sum of transient power consumption and capacitive load power. Transient power is the power consumed

when the circuit changes logic states such as 0 bit to 1 bit or vice-versa, whereas the capacitive load power is the power used to charge the load capacitance. Dynamic power is represented by Eq. 2.2, where  $\alpha$  is the activity factor <sup>1</sup>, C is the capacitance, V is the operating voltage, and F is the operating frequency [Jan et al., 2003].

$$P_{static} = V \times I_{leakage} \tag{2.1}$$

$$P_{dynamic} = \alpha \times C \times V^2 \times F \tag{2.2}$$

$$P_{total} = P_{static} + P_{dynamic} \tag{2.3}$$

Therefore, when an application is executing on the MPSoC, the total energy ( $E_{total}$ ) consumption in the system is represented by the product of total power consumption and the execution time ( $T_{app}$ ) of the application, as shown in the following equation.

$$E_{total} = P_{total} \times T_{app} \tag{2.4}$$

Moreover, as mentioned in section 1.1, DVFS performs power management of the processing elements by varying the operating voltage (V) and frequency (F) of the respective processing elements dynamically based on the current workload and performance requirements, the total power consumption  $(P_{total})$  is also affected by the the operating voltage (V) and frequency (F). As shown in the above equations 2.1, 2.2 and 2.3, dynamic power  $(P_{dynamic})$  is proportional to the square of the voltage and directly proportional to the frequency, while static power  $(P_{static})$  is directly proportional to the voltage. Therefore, scaling both voltage and frequency concurrently by performing DVFS provides a more effective way to reduce power consumption. That said, we need to keep in mind that in most of the modern MPSoCs such as Exynos 5422 [Prakash et al., 2015], the operating voltage and frequency come paired together for each type of processing elements such as CPUs & GPUs, thus, by scaling the operating frequency the operating voltage is automatically scaled alongside.

Modern embedded mobile platforms ranging from smartphones to wearable devices employ heterogeneous Multi-Processor Systems-on-Chips (MPSoCs), which utilizes several types of processing cores such as ARM's big.LITTLE with DVFS capabilities

<sup>&</sup>lt;sup>1</sup>The activity factor ( $\alpha$ ) is a dimensionless quantity, ranging from 0 to 1, that represents the average switching activity of a digital circuit or processor. It is used to capture the dynamic behavior of the circuit and estimate the dynamic power consumption.

are available within a single chip, to deliver performance as well as power efficient computing.

Previously simply increasing the operating frequency of a single-core processor was able to cater for performance criteria of mobile applications, however, with time we could notice a paradigm shift to the adoption of multi-core systems in mobile devices to satisfy the needs of more complex applications. Additionally, simply increasing the operating frequency of single core leads to high power consumption and heat dissipation.

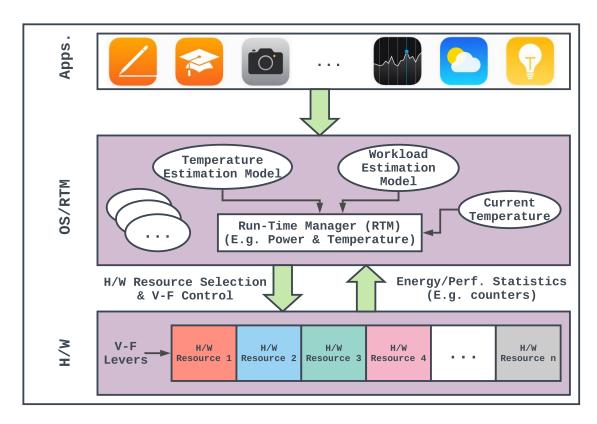

In order to overcome the challenges associated with power consumption, heat dissipation and performance requirement of executing applications on mobile platforms, chip manufactures are integrating multiple processing cores (processing elements) operating at low frequencies, where the cores can cohesively communicate with each other [Singh et al., 2017a]. Over the decades, thanks to Moore's Law, now we cannot just fit many cores on a single chip but also cores of different processing capabilities onto the same chip to better fit our needs. The hardware (H/W) layer in Figure 2.1 shows an example chip containing many cores (resources) of different capabilities (colors). Such systems with multiple processing cores enable us to leverage the increased parallelism of the platform by partitioning applications (shown in the Appl. layer in Figure 2.1) into many small tasks and assigning the tasks to different cores (by H/W resource selection in Figure 2.1) in order to perform parallel executions towards satisfying the increased performance requirements, power consumption and heat dissipation [Hanumaiah and Vrudhula, 2012].

In these systems, the partitioning of applications is referred to as functional partitioning [Singh et al., 2017a]. This kind of procedure requires in-depth application knowledge and involves finding the tasks, adding synchronization and inter-task communication in the tasks, management of the memory hierarchy communication and checking of the parallelized code (tasks) to ensure for correct functionality. When heterogeneous multi-core system is in place, a task binding process, which specifies the types of cores on which the tasks can be allocated along with the allocation cost, is required [Smit et al., 2005]. In order to compute the allocation cost of the task, the binding process analyzes the implementation cost such as performance, power consumption and resource utilization of each task on supported heterogeneous cores such as general purpose processor (GPP), digital signal processor (DSP), graphics processing unit (GPU) and coarse grain re-configurable hardware. At the moment, the most popular mobile platforms such as Samsung Exynos 5410, Exynos 5422 and Qualcomm's Snapdragon MP-SoCs host ARM's big and LITTLE GPPs along with other dedicated GPUs and DSPs [Dey et al., 2019d, Dey et al., 2019b, Pathania et al., 2014, Tan et al., 2018]. Although ARM's

Figure 2.1: Resource management [Singh et al., 2020]

big cores are sometimes too powerful for some types of applications and end up wasting a lot of power while executing them, on the other hand ARM's LITTLE cores could be less powerful to run the similar applications. In order to overcome such issues with processing capabilities, future trend in heterogeneous multi-core architecture is heading towards having more number of cores with variable processing capacities, which is not just limited to just two types such of ARM's big.LITTLE [Lin et al., 2016, Rupley et al., 2016], as we can already observe in Exynos 9825 (powering Samsung Galaxy 10 & Note 10 devices) [exy, c] and Exynos 990 (powering Samsung Galaxy 20 & Note 20 devices) [exy, d] MPSoCs.

Power efficient execution of applications on multi-processor systems is desired in order to improve the operation time of battery-powered systems. This requires development of efficient run-time management (RTM) approaches, as shown in the OS/RTM layer of Figure 2.1. For decades several research and implementation works have focused on optimizing power at circuit, architecture and system levels. On the other hand, on systems utilizing MPSoCs if proper power consumption control measures are not taken then it could lead to heat generation in the system. The availability of multiple PEs on the system in comparison with uniprocessors can lead to more nonuniformity

of heat generation & dissipation, leading to spatial temperature gradients (STGs) across the chip. Additionally, the variety of the workloads, which could be processed at the same time, may cause large temporal heat generation/dissipation leading to temporal thermal gradients (TTGs) at a single point on the chip. In the meantime, STGs, TTGs and thermal cycles lead to reduced performance and reliability of the system over the period of time [Iranfar et al., 2018]. If there is an increase of 10 °C to 20 °C for metallic structures then the lifetime reliability may decrease up to 16 times, thus, optimizing thermal behaviour of the mobile platform is very important for such devices. Not to mention, STG and TTG on the PEs in the chip could also expose vulnerabilities related to temperature (thermal) side-channel attacks [Hutter and Schmidt, 2013, Masti et al., 2015, Bartolini et al., 2016].

In this chapter, we explore the approaches available for dynamically optimizing power consumption and thermal behaviour on multi-core mobile platforms. First, we observe some of the recent trends in power and thermal management in MPSoCs. Also, given the fact that power consumption and heat dissipation on MPSoC devices could also lead to temperature side-channel attacks, we also explore studies related to that topic. We have segregated the surveyed methodologies into three categories: Dynamic Power Management, Dynamic Thermal Management, & Dynamic Power and Thermal Management; where each of the categories has two sub-categories: Proactive, where the methodologies are trying to pro-actively determine the future state and take actions to optimize either power consumption or thermal behaviour or both; & Reactive, where the methodologies are reactive in nature and only take actions to optimize either power consumption or thermal behaviour or both when a certain state is reached. Keep in mind, though power and energy consumption are distinct from each other, power consumption of executing apps are evaluated over the execution time of such apps (see Eq. 2.4) and hence, we use the term "energy" in some context when we observe the power consumption over the execution time period.

For proactive management, the state could be future temperature by using a temperature estimation model or future workload by using workload estimation mode and actions could be resource selection and/or voltage-frequency (V-F) control, as shown in Figure 2.1. In contrast, the state for reactive management could be current workload or temperature, as shown in Figure 2.1. The states are typically determined with the help of performance monitoring counters providing statistics about metrics such as power and performance. After we have explored the approaches on dynamically optimizing power consumption and thermal behaviour, we explore approaches related to temperature side-channel attacks.

**Chapter organization**: For ease of navigation within this chapter, the rest of the chapter is organized as follows. Recent emerging technologies in power and thermal management in MPSoCs are discussed in Sec. 2.2. Existing work on *Dynamic Power Management* (discussed in Sec. 2.3), *Dynamic Thermal Management* (discussed in Sec. 2.4) and *Dynamic Power and Thermal Management* (discussed in Sec. 2.5) are segregated into *Proactive* and *Reactive* approaches. In Sec. 2.6 we explore existing work on thermal side-channel attack, and finally, the chapter is concluded in Sec. 2.7.

# 2.2 Recent Emerging Technologies in Power and Thermal Management in MPSoC

Before we explore some of the existing works in power and thermal management, let us explore some of the emerging technologies that are being used for power and thermal management in MPSoCs. In this section, we explore some of these recent emerging technologies as they evolve. The rationale for discussing these emerging technologies in this section is to establish their relevance as they will be subsequently employed within the research presented throughout this thesis.

### 2.2.1 Heterogeneity in Processing Cores in the Machine Learning Era

As already mentioned most of the modern MPSoCs come equipped with heterogeneous processing elements such as big CPUs, LITTLE, CPUs, GPUs and DSPs [Dey et al., 2019d, Dey et al., 2019b, Pathania et al., 2014, Tan et al., 2018], however, with the evolution and popularity of machine learning algorithms in recent times we can also see emergence of neural processing units (NPUs), which are specifically integrated into the chip circuit that implements all the necessary control and arithmetic logic to execute machine learning algorithms [Patterson et al., 2012, Bouvier et al., 2021]. With rise in complexity in homogeneity in the processing elements in the MPSoC, several methodologies have been proposed to optimize either performance, power consumption, temperature and reliability of the MPSoC or a multiple of these objectives together.

### 2.2.2 Convolutional Neural Networks and Deep Learning

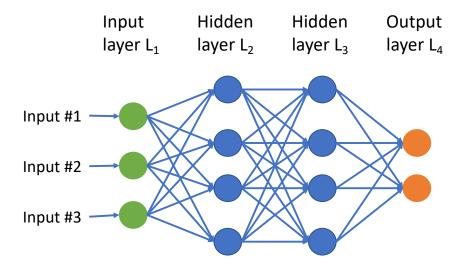

A Deep Learning (DL) model [Krizhevsky et al., 2017] consists of an input layer, several intermediate (hidden) layers stacked on top of each other and an output layer. Fig. 2.2 shows a representative diagram of DL model. In the input layer, which is the first layer of the model, the raw values of data features are fed into it. In each of the hidden layers a

mathematical operation called convolution is applied to extract specific features, which is then utilized to predict the label of the raw data in the last (output) layer of the DL network. Most of the time, if a model utilizes an input layer, a hidden layer and an output layer then the model is denoted as Convolutional Neural Network (CNN) model or simply, CovNet. If such a model uses a lot of stacked hidden layers only then it is denoted as a DL model or Deep Neural Networks (DNN).

Figure 2.2: Representative diagram of Deep Learning model

#### 2.2.3 Reinforcement Learning

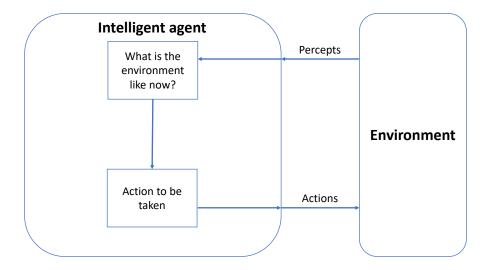

Reinforcement learning (RL) [Sutton and Barto, 2018] is a type of machine learning algorithm where an intelligent agent, which is a computing system that perceives its environment to take actions autonomously in order to achieve cumulative rewards based on the knowledge gathered from the environment. Fig. 2.3 shows a representative diagram of an intelligent agent. Here, reward could be optimizing performance or power consumption or thermal efficiency or combination of these together. Several studies [Shafik et al., 2016, Maurer et al., 2020, Yu et al., 2020] on utilizing reinforcement learning for computing resource management have been proposed. One of the biggest advantage of using RL for resource management is that the system is capable of learning autonomously how to manage the resources online dynamically.

Figure 2.3: Representative diagram of intelligent agent

### 2.3 Dynamic Power Management

In this section, we explore the dynamic power management approaches that are currently available in MPSoCs. The studies mentioned in this section only focus on dynamic power management without explicitly considering dynamic thermal management on the MPSoC.

To improve power consumption and/or to meet performance constraint in multicore mobile platforms, various approaches for DVFS and/or mapping have been proposed using offline, online or hybrid (online optimization facilitated by offline analysis results) optimization for resource management [Goraczko et al., 2008, Singh et al., 2017a, Singh et al., 2017b, Basireddy et al., 2018, Reddy et al., 2017, Quan and Pimentel, 2015, Gupta et al., 2017, Shafik et al., 2016, Cochran et al., 2011, Van Craeynest et al., 2012, Aalsaud et al., 2016b, Sozzo et al., 2016, Donyanavard et al., 2016, Petrucci et al., 2015, Schranzhofer et al., 2010, Hölzenspies et al., 2008, Quan and Pimentel, 2013, Stamoulis and Marculescu, 2016, Mandal et al., 2019]. Depending on the control mechanism, runtime power management approaches can be further classified into two categories: proactive [Shafik et al., 2016, Hölzenspies et al., 2008, Gupta et al., 2017] and reactive [Goraczko et al., 2008, Schranzhofer et al., 2010, Quan and Pimentel, 2013, Weissel and Bellosa, 2002, Singleton et al., 2005, Mandal et al., 2019].

### 2.3.1 Proactive Approaches

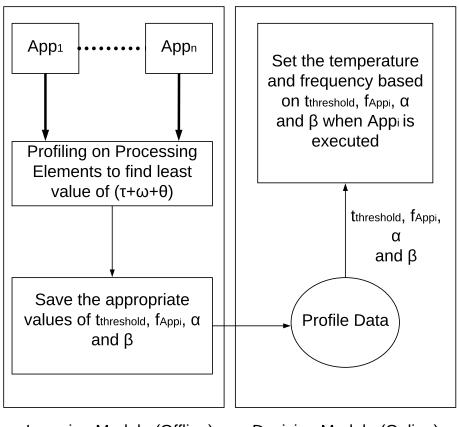

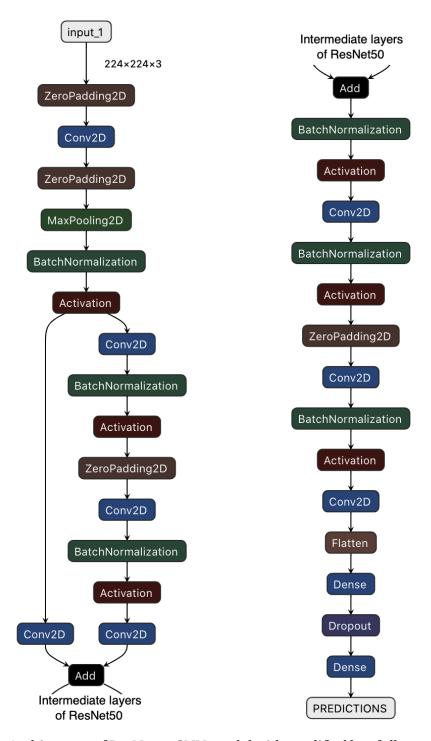

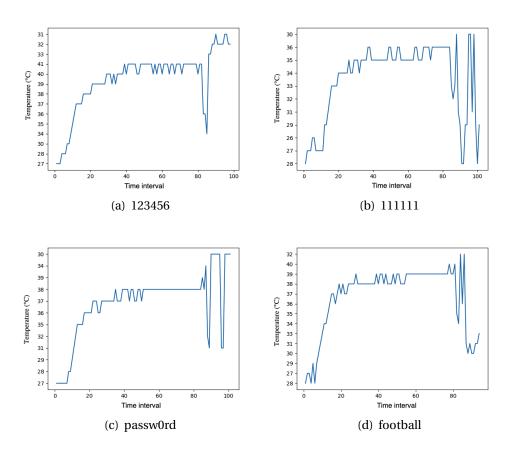

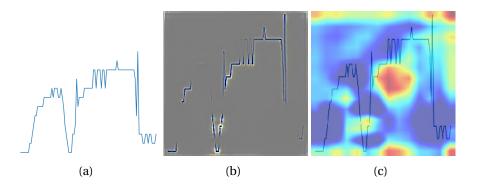

To adapt to dynamic application workloads efficiently, proactive control-based approaches have also been investigated [Shafik et al., 2016, Hölzenspies et al., 2008, Gupta et al.,