Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# Low Power Analog Processing for Ultra-High-Speed Receivers with RF Correlation

# Jaswinder Lota<sup>1</sup>, Member, IEEE and A. Demosthenous<sup>2</sup>, Fellow, IEEE

<sup>1</sup>Department of Engineering and Construction, University of East London, London E16 2RD UK

Corresponding author: Jaswinder Lota (j.lota@uel.ac.uk).

"This work was supported in part by the XXX."

ABSTRACT Ultra-high-speed data communication receivers (Rxs) conventionally require analog digital converters (ADC)s with high sampling rates which have design challenges in terms of adequate resolution and power. This leads to ultra-high-speed Rxs utilising expensive and bulky high-speed oscilloscopes which are extremely inefficient for demodulation, in terms of power and size. Designing energy-efficient mixed-signal and baseband units for ultra-high-speed Rxs requires a paradigm approach detailed in this paper that circumvents the use of power-hungry ADCs by employing low-power analog processing. The low-power analog Rx employs direct-demodulation with RF correlation using low-power comparators. The Rx is able to support multiple modulations with highest modulation of 16-QAM reported so far for direct-demodulation with RF correlation. Simulations using Matlab, Simulink R2020a® indicate sufficient symbol-error rate (SER) performance at a symbol rate of 8 GS/s for the 71 GHz Urban Micro Cell and 140 GHz indoor channels. Power analysis undertaken with current analog, hybrid and digital beamforming approaches requiring ADCs indicates considerable power savings. This novel approach can be adopted for ultra-high-speed Rxs envisaged for beyond fifth generation (B5G)/sixth generation (6G)/ terahertz (THz) communication without the power-hungry ADCs, leading to low-power integrated design solutions.

INDEX TERMS Analog-processing, beyond fifth-generation (B5G), RF-correlation, THz, ultra-high-speed

#### I. INTRODUCTION

Tera hertz (THz) electromagnetic spectrum applications such as imaging have been extensively used in radio astronomy, with the first astronomical THz images dating back to the 1960s. Since 1990 there has been much progress in THz time-domain spectroscopy for tissue characterisation and cancer detection due to advances in femtosecond optoelectronics. New antenna and CMOS integrated-chip technologies are fast emerging as an alternative for realizing affordable THz systems. This together with the availability of wider bandwidths in the THz spectrum motivates more innovative applications e.g. novel cognition, sensing, imaging, communications, and positioning capabilities that may be employed by automated machinery, autonomous cars, and new human interfaces [1].

Policy and research communities have yet to agree on the range of frequencies that would form the THz communication band. However, the Federal Communications Commission (FCC) in November 2019 formally opened up the spectrum between 95 GHz-3 THz [2] for experimental purposes termed as THz communication, beyond fifth-generation (B5G) and sixth-generation (6G) communication. This spectrum has many challenges such as narrow or pencil beam antennae demanding accurate line-of-sight (LOS) communication with frequent beam alignment for the mobile users. Mitigating such challenges will require research on topics such as channel modelling, antenna design, fast antenna beam alignment, radio resource management, and protocol design.

The spectrum has ultra-high-speed data in Gb/s requiring low-power and compact integrated-chips that are challenging to design. Due to the degradation of active device performance

VOLUME XX, 2017

<sup>&</sup>lt;sup>2</sup>Department of Electronic and Electrical Engineering, University College London, London UK

at frequencies close to its maximum operating frequency, the operating frequency cannot be arbitrarily high. Current state-of-the-art CMOS technologies enable circuits operating up to 1.3 THz, to detect both the amplitude and phase of signals up to 1.2 THz, and signal amplitudes up to 10 THz. [3]. Other CMOS implementations include a 240-GHz QPSK transceiver with a data rate of 16- Gb/s and a 300-GHz radio-frequency (RF) transmitter (Tx) that can support 105-Gb/s with 32-QAM [4],[5].

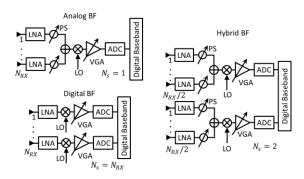

To cater for the high path loss that occurs in signal transmission the ultra-high-speed receiver (Rx) antenna frontend (AFE) will require beamforming to increase antenna directivity. As frequency increases the beamforming directional antennas incur a lower path loss for the same aperture area [6]. Beamforming can be employed in the analog and/or digital domains. Analog beamforming (ABF) is performed at either RF or at an intermediate frequency (IF) through a phase shifter (PS) and a low noise amplifier (LNA) per antenna element as shown in Fig.1, where  $N_{RX}$  is the number of antenna elements and  $N_S$  is the number of baseband chains. The antenna elements can be employed as uniform linear arrays or uniform rectangular arrays (URA). This reduces power consumption as only one down-conversion chain is required with a variable gain amplifier (VGA) and an analog-to-digital converter (ADC) per digital stream. The VGA ensures that the signal power is adequate to drive the ADC. Certain applications require a high beamforming gain which is done by increasing  $N_{RX}$  to 64, 128 or 256. For these hybrid beamforming (HBF) is preferred in order to reduce the number of PS, down-conversion chains and ADCs as  $N_{RX}$  is high. HBF with two RF chains as shown in Fig. 1 where each RF chain has its down-conversion chain, VGA and ADC. Partial beamforming is done by PS in the RF domain and by digitally in baseband. For digital beamforming (DBF) shown in Fig. 1, beamforming is performed digitally in baseband. This overcomes the limitation of being able to transmit/receive at few or only fixed directions in ABF and HBF. Since each antenna element requires its own down-conversion stage along with a VGA and ADC, DBF becomes very powerhungry for large numbers of antenna elements. Even for a lower number power requirements remain high in the case of high-speed data due to power-hungry high-speed ADCs and VGAs, requiring higher sampling rates and larger gain ranges respectively to compensate for the reduced beamforming gain

ABF utilizing one RF chain has significant advantage in energy efficiency. PSs can be employed with low resolution which are easier to realize and are more energy-efficient. To circumvent the restriction of limited beamforming directions, the optimal continuous phase ABF can be obtained, and quantize the phase of PS to a finite set [7]–[9], employ codebooks [10]-[14], or machine learning [15]. Recent novel approaches indicate the similar performance of ABF PSs with low and high resolutions in mmWave downlink multicast systems [16]. Similar approaches in ABF and HBF have been proposed for THz communication [17]-[20]. The choice of

beamforming and the associated transceiver depends on the application, but in most cases, HBF and DBF architectures require multiple energy-intensive RF chains and have relatively high-power consumption.

Fig. 1. Analog, hybrid and digital beamforming.

Post AFE Rxs are either employed as direct-conversion i.e. direct-demodulation [21], [22] or IF conversion [23], [24] architectures for demodulating data. To demodulate the raw bit information, the Rxs with ultra-high-speed data will require high-resolution ADCs with sampling rates at least 2-4 times the symbol rate  $T_S$  of the modulated baseband or IF signals to avoid aliasing [25]. However, signal-to-noise-distortion ratio (SNDR) and spurious-free-dynamic range (SFDR) both degrade with an increase in the ADC sampling rate leading to poor resolution. Current state-of-the-art high-speed Rxs therefore employ expensive and bulky high-speed oscilloscopes to demodulate data [26], [27]. This leads to ultra-high-speed Rxs being extremely energy inefficient for demodulation. Channel bonding is an alternative solution but requires several parallel data converters with a high level of calibration [21]. Accordingly designing energy-efficient mixed-signal and baseband units for ultra-high-speed Rxs is challenging and requires a paradigm approach. One such approach is to design high-speed Rxs with directdemodulation requiring no ADCs. Such architectures are reported but support only single and low-order OOK, BPSK, QPSK modulations and have large latency, or have architectures that are not suitable for ultra-high-speed data

We detail further the design challenges in ultra-high-speed ADCs, direct-demodulation without ADCs and motivations for adopting the approach in this paper.

## A. Ultra-High-Speed ADC

ADC is one of the most power-hungry blocks for Rxs. The effective number of bits (ENOB) of an ADC is its dynamic range above the noise levels (quantization and thermal) that is available for measuring the signal input amplitude. ENOB can be increased by increasing quantization levels for Nyquist ADCs or its sampling frequency ( $f_s$ ) to above the Nyquist frequency as in oversampling ADCs. A trade-off however exists between power dissipation  $P_d$ , ENOB and  $f_s$  determined in a figure-of-merit  $FOM_{ADC}$  [28]:

$$FOM_{ADC} = \frac{P_d}{(f_S 2^{ENOB})} \tag{1}$$

Sampling data is fundamental to an ADC and hence the power required for it acts as a lower bound to  $P_d$ . The thermal sampling noise  $N_{TS} = kT/C_s$ , where  $C_s$  is the sampling capacitor of the ADC, k Boltzmann's Constant, and T the temperature in Kelvin [29]. Typically,  $C_s$  is chosen large enough such that  $N_{TS}$  of the same order as the ADC's quantization noise  $N_Q$ . Assuming that an n-bit ADC is designed such that  $N_{TS}$ ,  $N_Q$  leads to the following minimum value of  $C_s$  [29]:

$$C_s = \frac{12kT2^{2n}}{V_{in}^2} \tag{2}$$

where,  $V_{in}$  is the full-scale voltage at the ADC input. For an ideal n-bit ADC [29]:

$$ENOB = n - 0.5 \tag{3}$$

For high-resolution ADCs n > 10,  $P_d$  is dominated by sampling thermal noise and grows proportionally as  $2^{2n}$ . For low-resolution ADCs n < 6,  $P_d$  is dominated by component mismatch and capacitor size, proportionate to  $2^n$  [29]. As technology and supply voltages scale to lower values, the permissible noise levels reduce further requiring larger values of  $C_s$  for a given resolution [29], and for low- resolution ADCs, the energy efficiency becomes limited by thermal noise.

For high-speed demodulation a minimum resolution is required across the entire bandwidth. Due to parasitic capacitances the ADC power and speed becomes a nonlinear relation leading to a lower  $FOM_{ADC}$ . ADCs operating above a certain  $FOM_{ADC}$  thus degrade performance of resolution and speed [30]. To increase the sampling speed without degrading the  $FOM_{ADC}$ , time interleaving ADCs are used which run at lower sampling speed. However, these require power-hungry front-end drivers and are prone to timing and gain mismatches [31], [32]. Hence they have limited ENOB and require high power e.g. 950mW [33].

## B. Direct-demodulation without ADC

High-speed Rxs with direct-modulation and requiring no ADCs are reported in [21], [22], [34]-[36]. However, these are either architecture specific such as for spread spectrum systems, or support only single low-order modulations such as OOK, BPSK and QPSK. Ultra-high-speed Rxs will require higher modulation formats for increased data rates and should be adaptive to be able to support multiple modulations depending on channel conditions. Direct-modulation for 8-PSK and higher-order modulations become challenging as the boundary decisions for symbols reduce hence becoming more susceptible to noise. An 8-PSK direct-demodulation based on the arctangent technique in parallel with a digital phasedlocked loop (PLL) is presented in [37]. This however requires large lookup tables and memory increasing latency which becomes extremely challenging to implement at ultra-highspeeds. A technique that overcomes this limitation is described in [38], which however is limited to 8-PSK. This paper

proposes a novel low-power analog processing (LPAP) Rx with ABF, employing direct-demodulation and RF correlation without the power-hungry high-speed ADCs. Below are the main contributions of the paper not reported so far in the available literature:

- The Rx design is able to support multiple modulations of BPSK, 4-QAM, along with the highest modulation of 16-QAM reported so far for direct-demodulation with RF correlation and with a single architecture.

- Simulations of the Rx employed with ABF indicate sufficient symbol of error (SER) performance with a symbol rate of 8 GS/s for 71 GHz Urban Micro (UMi) Cell and 140 GHz indoor (InH) channels.

- Power and linearity analysis are undertaken with the current ABF, BHF and DBF configurations requiring ADCs, indicating considerable power savings and SFDR.

Section II details the LPAP Rx architecture, channel model, RF signal power at AFE, phase noise model, comparator and digital decoder design. Simulation results in section III provide for the BER curves, equalizer performance, blocking and interference analysis. The circuit component values, linearity and power comparison analysis for various Rx architectures, are detailed in section IV with conclusions in section V.

## **II. LOW POWER ANALOG PROCESSING**

#### A. Receiver Architecture

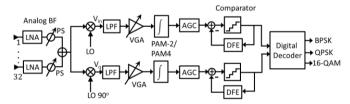

The LPAP Rx consists of 32 antenna elements each followed by LNA and PS as shown in Fig. 2. The input signal is a BPSK/QPSK/16-QAM RF signal with a symbol rate of 8 GS/s. The signal is converted to in phase  $(V_{in})$  and quadrature phase  $(V_a)$  components by two LOs at RF, one in-phase with the RF signal, and other with a 90° phase difference. For direct-demodulation Rxs there are widely employed available synchronization techniques for such pilots/training sequences; and for mitigating the I/Q imbalances which can be employed. The low pass filters (LPF) are employed to filter out any interference signals in the proximity of the RF signal. Since  $V_{in}$ ,  $V_a$  are low pass baseband signals this overcomes any sharp roll-off requirements for the LPF, hence lowering the power requirements. The LPF is a single pole RC filter with a 3dB cut-off at 12 GHz. The VGAs provide sufficient amplification for a stable signal reference value in the subsequent stages.

Fig. 2. LPAP Rx architecture.

At the integrator outputs  $V_{in}$ ,  $V_q$  are pulse amplitude modulated (PAM) signals with two-levels (PAM-2) for BPSK/QPSK modulation. For 16-QAM  $V_{in}$ ,  $V_q$  are four-level PAM signals (PAM-4). The automatic gain controls (AGC) ensure a certain voltage level at the comparator. Decision feedback equalizers (DFE) remove any inter-symbol interference (ISI) and channel distortion. The equalized signals are then decoded by the decoder that enables demodulation of BPSK/OPSK/16-OAM signal.

## B. Channel Model and RF Signal Power

Based on the 3D statistical channel model in [39], [40], an open-source MATLAB-based statistical simulator NYUSim v3.1, has been developed by New York University (NYU) [41]. The simulator generates 3D angle-of-departure (AOD) and angle-of-arrival (AOA) power spectra and power delay profiles (PDPs) that match measured field results from 0.1-148 GHz RF frequencies. This is based on over 15,000 PDPs that were measured and used to derive directional omnidirectional path loss models and extract small-scale channel statistics such as the number of time clusters, cluster delays, and cluster powers. In the 3GPP TR 38.901 outdoor channel model for frequencies above 0.5 GHz [42], the number of clusters is unrealistically large which is not supported by the real-world measurements at mmWave bands [39], [40], [43]. In contrast, in the outdoor statistical model implemented in NYUSim v3.1, the number of time clusters ranges from 1 to 6, and the mean number of spatial lobes is about 2 which is upper-bounded by 5. These are obtained from field observations and are much smaller than those in the 3GPP channel model [44], [45]. To realistically quantify the signal power received  $P_r$  at AFE, NYUSIM v3.1 is employed in this paper for simulating the 71 GHz and 140 GHz channels, as the simulator is built from field data which gives more realistic results.

Input values for NYUSim v3.1 are given in TABLE I indicated as channel parameters which include atmospheric conditions, spatial consistency and antenna parameters, where HPBW is the half power beamwidth and  $N_{TX}$  number of antenna elements in the Tx array. Spatial consistency mode is applicable in outdoor channels, where the Rx moves along a specific path generating correlated and consecutive channel impulse responses for successive sampling points on the path. The path can be selected as linear or hexagonal. Spatially correlated large-scale parameters such as shadow fading, and time-variant small-scale parameters such as angles, power, delay and phase of each multipath component are generated [46], [47]. In addition the effects of human blockage causing temporal shadowing for both indoor and outdoor channels are modelled. For this the default setting option is used in this paper where an average mean attenuation for human blockage is implemented based on a linear fit applicable to the Tx/Rx antenna HPBW [48].

The PDPs generated are weighted by the Tx and Rx antenna directivity given as [39]:

$$G(\theta, \phi) = \max\left(G_0 e^{-\alpha \theta^2 - \beta \phi^2}, \frac{G_0}{100}\right) \tag{4}$$

$$G(\theta, \phi) = \max \left( G_0 e^{-\alpha \theta^2 - \beta \phi^2}, \frac{G_0}{100} \right)$$

(4)

$$\alpha = \frac{4 \log_e 2}{\theta_{3dB}^2}, \beta = \frac{4 \log_e 2}{\phi_{3dB}^2}, G_0 = \frac{41253\eta}{\theta_{3dB}\phi_{3dB}}$$

(5)

where,  $(\theta, \phi)$  are the azimuth and elevation angle offsets from the boresight direction in degrees,  $G_0$  is the maximum directive boresight gain in linear units,  $(\theta_{3dB}, \phi_{3dB})$  are the azimuth and elevation HPBW in degrees,  $\alpha$ ,  $\beta$  are parameters that depend on the HPBW values, and  $\eta = 0.7$  is the typical average antenna efficiency. Conventionally, the HPBW of an antenna array is a function of the number of antenna elements and the antenna spacing, but here in the simulator three parameters i.e., the HPBW, number of antenna elements, and antenna spacing can be independently specified, since there may be a wide range of beamforming approaches as in Fig. 1, in all of which different individual antenna element types (e.g., patch antennas, vertical antennas, horns) can be used.

TABLE I **NYUSIMV3 PARAMETER SETTINGS**

| <b>Channel Parameters</b>               |                              |                                                                           |

|-----------------------------------------|------------------------------|---------------------------------------------------------------------------|

| Frequency (0.1-148 GHz)<br>Channel      | 71 GHz, 140 GHz.<br>UMi, InH | As allocated by FCC.<br>71 GHz Urban micro<br>outdoor, 148 GHz<br>Indoor. |

| Tx Rx Separation                        | 50 m, 25 m                   | Normal UMi outdoor,<br>InH indoor values.                                 |

| Tx Power                                | 35 dBm, 30 dBm               | Normal UMi, InH base station power.                                       |

| Base station height                     | 15 m, 3 m                    | Normal UMi, InH base station heights.                                     |

| Rx height                               | 1.5 m                        | Normal height.                                                            |

| Number of Rx locations                  | 200                          | Mean of 200 simulations.                                                  |

| Barometric Pressure                     | 1013.25 mbar                 | Standard atmospheric condition.                                           |

| Humidity                                | 50 %                         | Standard atmospheric condition.                                           |

| Rain Rate                               | 0 mm/hr                      | Standard atmospheric condition.                                           |

| Polarisation                            | Co-polarization              | Co-polarization of Tx and Rx antenna URAs are considered.                 |

| Spatial Consistency<br>Parameters       |                              |                                                                           |

| Correlation Distance                    | 10 m                         | Standard simulator setting.                                               |

| Rx Track Type                           | Linear                       | To ensure realistic path profile.                                         |

| Rx Moving Direction                     | 45°                          | Standard simulator setting.                                               |

| Rx Velocity                             | 10 m/s                       | Velocity assumed in UMi channel.                                          |

| Rx Moving Distance                      | 10 m                         | Distance in Tx-Rx separation.                                             |

| Antenna Parameters                      |                              | •                                                                         |

| Tx Array Type                           | URA                          | URA is considered in this paper.                                          |

| Rx Array Type                           | URA                          | URA is considered in this paper.                                          |

| No. of Tx elements                      | $N_{TX}$                     | 256                                                                       |

| No. of Tx elements                      | $N_{RX}$                     | 32                                                                        |

| Tx/Rx Antenna<br>Azimuth/Elevation HPBW | 7° – 360°                    | 7°, 7° lower limit for NYU.                                               |

VOLUME XX 2023

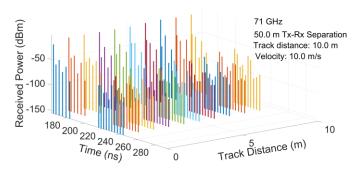

The PDP profile generated for 71 GHz channel is shown in Fig. 3.

Fig. 3. PDP 71 GHz channel.

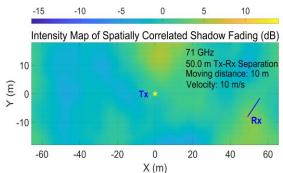

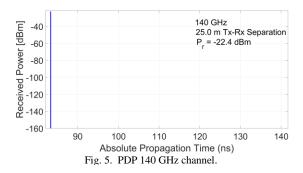

The variation in PDP due to shadow fading for the mobile Rx is shown in Fig. 4 for a Rx track at 45°. The PDP profile for the 140 GHz channel is shown in Fig. 5.

Fig. 4. 71 GHz channel variation in PDP due to Rx mobility.

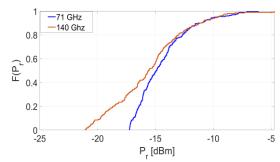

The cumulative distribution function F(.) of  $P_r$  for 200 simulations is shown in Fig. 6. More than 200 simulations show no change in statistical values. The mean power values obtained are -14.44 dBm and -15.55 dBm for the 71 GHz and 140 GHz channels respectively. The mean value of PDP variation obtained is  $\pm$  6 dB accounting for user mobility in the 71 GHz channel. Accordingly,  $P_r$  at the input to AFE assumed are -21 dBm and -16 dBm for the 71 GHz and 140 GHz respectively.

Fig. 6. Cumulative density function of power received.

The thermal noise power for a bandwidth (B) of 8 GHz is calculated as -75.09 dBm using

$N_T = 10log \left[\frac{kTB}{10^{-3}}\right]$  (6) where,  $k = 1.380648 \times 10^{-23}$  J/K is the Bolztmann's

where,  $k = 1.380648 \times 10^{-23}$  J/K is the Bolztmann's constant and T = 280 the noise temperature in Kelvin.

#### C. Local Oscillator Phase Noise

A common circuit solution for LO is frequency generation with a voltage controlled oscillator (VCO). Several parameters that can be employed in VCO design and the performance is well captured by a Figure-of-Merit ( $FOM_{VCO}$ ) which accounts for power, different semiconductor technologies and circuitry topologies where:

$FOM_{VCO} = L$   $(f) - 20 \log \left(\frac{f_o}{f}\right) + 10 \log \left(P_{VCO} / 1mW\right)$  (7) where, L (f) is the phase noise in dBc/Hz at a frequency offset f,  $f_o$  is the oscillation frequency, and  $P_{VCO}$  the power consumption in mW. On a linear scale both L (f) and  $P_{VCO}$  are  $\propto f_o^2$ . In order to maintain the phase noise level at a certain offset when increasing  $f_o$  by a factor  $\alpha$  requires the power to be increased by  $\alpha^2$ , assuming a fixed  $FOM_{VCO}$ . Conversely, for a fixed power consumption and  $FOM_{VCO}$  the phase noise will increase by  $\alpha^2$ , or 6dB per every doubling of  $f_o$ . A common way to suppress LO phase noise is to apply a PLL, where the VCO which is locked to a highly stable reference, normally a low frequency crystal oscillator, by use of a phase frequency detector, filter and counter. The PLL compares the phase of a reference signal to the phase of an adjustable feedback signal to ensure a steady higher frequency output.

Different strategies can be employed for implementation of signal generation and distribution such as centralized PLL generation (one PLL for all baseband chains), distributed PLL generation (one PLL per baseband chain) and semi-distributed PLL generation (baseband chains within a group sharing a common PLL). The different strategies have not yet been investigated. A comparison could lead to some potential advantages/disadvantages for implementation in mmWave or higher frequencies, forming a basis for future study. The total phase noise of a PLL is composed of contributions from the VCO outside the loop bandwidth and the reference oscillator inside the loop. A significant noise contribution is also added by the phase detector and the divider. This poses significant challenges when employing higher frequencies with phase sensitive modulation such as 16-QAM in ultra-high-speed

Rxs. As the VCO phase noise increases by 6dB per doubling of the frequency, an increase in VCO frequency from 3 GHz to 30 GHz would result in phase noise degradation of 20 dB for a given offset frequency.

Another contributing factor that increases phase noise at higher frequencies is the degradation in quality factor (Q)value and low signal power. In order to achieve low phase noise, the Q-value and signal power need to be maximized while minimizing the noise figure of the active device, which is challenging to achieve when the signal frequency increases. For monolithic circuits, the Q-value of the on-chip resonator decreases as frequency increases due to an increase of parasitic losses due to substrate effects and resistance of metal tracks. The fundamental VCO frequency is therefore generally limited to ~15 GHz while employing frequency multipliers for higher frequency requirements. In addition, the up-conversion of the  $\frac{1}{2}$  noise creates an added slope in the vicinity of the carrier frequency. The  $\frac{1}{6}$  noise depends on technology, where planar devices such as FET, PHEMT and CMOS are seen to have a higher noise level than vertical bipolar devices like Si bipolar, SiGe HBT and GaAs HBTs.

Existing phase noise models include Leeson's model [49] and those developed by Hijimira and Lee [50], Rael and Abidi [51], and Razavi [52]. A phase noise model that gives accurate results when compared with actual prototypes is the single-sideband (SSB) pole-zero model developed by the IEEE 802.15.3c task group [53]. The phase noise at offset frequency *f* in dBc/Hz is given by:

$$L(f) = L(0) \cdot \frac{1 + \left(\frac{f}{f_z}\right)^2}{1 + \left(\frac{f}{f_p}\right)^2} \tag{8}$$

where  $f_z$  and  $f_p$  are the pole and zero frequencies respectively. The model was extended and employed by 3GPP for mmWave circuits which is a generalization of the multipole/zero model extended to fractional orders in [54] where:

$$L(f) = L(0) \frac{\prod_{n=1}^{N} 1 + (\frac{f}{f_{z,n}})^{\alpha_{z,n}}}{\prod_{m=1}^{M} 1 + (\frac{f}{f_{p,m}})^{\alpha_{p,m}}}$$

(9)

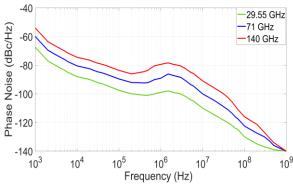

In [54] the modelled phase noise obtained by (9) is compared with a research prototype PLL designed in a 28nm FD-SOI CMOS process indicating accurate results. This is for distributed PLL generation at 29.55 GHz. The model is used by 3GPP to estimate PLL phase noise at higher frequencies of 45 GHz and 70 GHz [53]. The same method is followed in this paper to estimate the PLL phase noise at 71 GHz and 140 GHz. When the PLL phase noise profile is given at frequency  $f_0$  with phase noise  $L(f_0)$ , the correct phase noise L(f) at any other oscillation frequency f according to Lesson's equation is [49]:

$$L(f) = L(f_o)20\log_{10}\left(\frac{f}{f_o}\right) \tag{10}$$

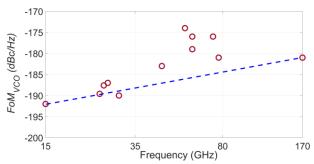

Here  $f_o$ = 29.55 GHz is the carrier frequency with a known phase noise profile. The  $FOM_{VCO}$  degrades at higher frequencies as shown in Fig. 7, which shows  $FOM_{VCO}$  versus frequency for several state-of-the-art published VCOs implemented in CMOS [55]-[67]. The  $FOM_{VCO}$  envelope

indicated by the dashed line showing the trend of the best VCOs has a 9 dB per decade slope and is used to derive parameters for phase noise models at 71 GHz and 140 GHz. The steps from 29.55 GHz to 71 and 140 GHz correspond to 0.38 and 0.68 decades, for which the corresponding phase noise degradations are listed in TABLE II. The  $20log_{10}\left(\frac{f}{f_o}\right)$  degradation is an overall degradation for the phase noise characteristics except for the high frequency noise floor region that is assumed to be constant. The  $FOM_{VCO}$  degradation affects only the VCO contribution starting at an offset of a few MHz.

Fig. 7.  $FOM_{VCO}$  for state-of the art VCOs implemented in CMOS.

#### TABLE II FOM DEGRADATION

| f         | $20log_{10}\left(\frac{f}{f_0}\right)$ degradation | FOM <sub>VCO</sub> degradation |

|-----------|----------------------------------------------------|--------------------------------|

| 29.55 GHz | 0 dB                                               | 0                              |

| 71 GHz    | 7.6 dB                                             | 3.4 dB                         |

| 140 GHz   | 13.5 dB                                            | 6.12 dB                        |

|           |                                                    |                                |

To determine the phase noise characteristics, the phase noise is first increased by the  $20log_{10}\left(\frac{f}{f_0}\right)$  degradation according to TABLE II. Then parameters  $f_{z,n}$ ,  $\alpha_{z,n}$ ,  $f_{p,m}$ , and  $\alpha_{p,m}$  are altered to obtain specified  $FOM_{VCO}$  degradation at 30MHz offset while maintaining a constant phase noise of -140dBc/Hz at large offset and at the hump around 1.55MHz offset. The resulting phase noise characteristics are shown in Fig. 8, with parameters listed in Table III for 71 GHz and 140 GHz.

Fig. 8. Phase noise estimation for PLLs at 71 GHz and 140 GHz.

| TABLE III                    |

|------------------------------|

| PHASE NOISE MODEL PARAMETERS |

| 71 GHz,  | PSD(0) 39.6 dB |                |               |                |

|----------|----------------|----------------|---------------|----------------|

| n.m      | $f_{z,n}$      | $\alpha_{z,n}$ | $f_{p,m}$     | $\alpha_{p,m}$ |

| 1        | $3(10^3)$      | 2.37           | 1             | 3.3            |

| 2        | $395(10^3)$    | 2.7            | $1.55 (10^6)$ | 3.3            |

| 3        | $758 (10^6)$   | 2.53           | $30(10^6)$    | 1              |

| 140 GHz, | PSD(0) 45.5 dI | 3              |               |                |

| 1        | $3(10^3)$      | 2.37           | 1             | 3.3            |

| 2        | $245(10^3)$    | 2.7            | $1.55 (10^6)$ | 3.3            |

| 3        | $1144 (10^6)$  | 2.53           | $30(10^6)$    | 1              |

## D. Comparator and Digital Decoder

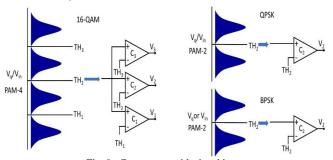

Three single-bit comparators  $C_1$ ,  $C_2$  and  $C_3$  are employed for 16-QAM demodulation as shown in Fig.9 where the input is a PAM-4  $V_a/V_{in}$  signal. The effects of process voltage temperature variation (PVT) can be countered by employing automatic gain control (AGC) [68], [31] and adaptive reference voltage generators [69], [70]. A PAM signal offers superior performance in comparison to non-return-to-zero (NRZ) signalling under the effects of inter-symbol interference (ISI) and clock jitter [71], achieving data rates of 100 Gbps [72], [73]. The threshold values for  $C_1$ ,  $C_2$  and  $C_3$ are set as  $TH_1$ ,  $TH_2$  and  $TH_3$  respectively. The comparator output voltage levels  $V_1$ ,  $V_2$  and  $V_3$  are high or low depending on the amplitude level of the input signal. For QPSK the Rx utilises two  $C_2$  comparators, one each for  $V_q$  and  $V_{in}$  and PAM-2 inputs. For BSPK a single  $C_2$  comparator is utilised for either  $V_q$  or  $V_{in}$  and a PAM-2 input.

Fig. 9. Comparator with signal inputs.

Comparators can be implemented with one or two stages of preamplification followed by a track and latch stage. Normally a low gain (~10) preamplifier reduces the kickback caused by fast output transitions while reducing the probability of metastability. Higher gain values can increase the time constant thereby reducing the speed. The latch alternates between a reset phase and positive feedback stage that generates full-swing digital signals from the preamplifier output. State-of-art comparators can sample at 14 GS/s [74] and interleaving comparators can be employed to increase the sampling rates.

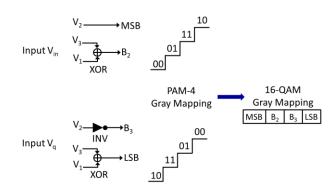

The digital decoder for 16-QAM is shown in Fig. 10. With  $V_{in}$  as input, the decoder employs  $V_2$  as MSB and a second bit  $B_2$  is produced by XORing  $V_3$  and  $V_1$ . This results in a two-bit Gray mapping output of  $V_{in}$ . With  $V_q$  as the input, bit  $B_3$  is obtained by inverting  $V_2$ , and the LSB is produced by XORing

Fig. 10. Digital decoder for 16-QAM.

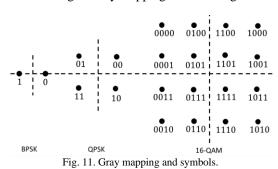

$V_3$  and  $V_1$ . Bits  $B_3$  and LSB also result in a two-bit Gray mapped output of  $V_q$ . The final symbol is obtained by combining  $V_{in}$  and  $V_q$  bits, resulting in a four-bit 16-QAM symbol according to Gray mapping shown in Fig. 11.

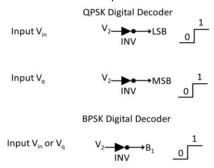

The QPSK and BPSK decoders are shown in Fig. 12. For demodulating the QPSK symbol decoder inverts  $V_2$  to obtain the MSB, and the LSB from inputs  $V_q$  and  $V_{in}$  respectively. This results in a QPSK symbol with Gray mapping shown in Fig. 11. For a BPSK symbol the output bit  $B_1$  is obtained by inverting  $V_2$  from either  $V_q$  or  $V_{in}$  as the input.

Fig. 12. Digital decoder for QPSK, BPSK.

The truth table values for four 16-QAM symbols are shown in TABLE IV which provides the PAM-4 2-bit quantised outputs for  $V_{in}$  and  $V_q$ . All 16-QAM symbols in Fig. 11 can be generated using appropriate combinations of  $V_{in}$  and  $V_q$  output values. The truth tables for QPSK and BPSK decoders are shown in TABLE V

TABLE IV TRUTH TABLE 16-QAM DECODER

|   |       |       | $V_{ir}$ | ı   |       |       |       |       | $V_q$ |     |

|---|-------|-------|----------|-----|-------|-------|-------|-------|-------|-----|

| 1 | $I_3$ | $V_2$ | $V_1$    | MSB | $B_2$ | $V_3$ | $V_2$ | $V_1$ |       | LSB |

|   | 1     | 1     | 1        | 1   | 0     | 1     | 1     | 1     | 0     | 0   |

| ( | 0     | 1     | 1        | 1   | 1     | 0     | 1     | 1     | 0     | 1   |

|   | 0     | 0     | 1        | 0   | 1     | 0     | 0     | 1     | 1     | 1   |

| ( | 0     | 0     | 0        | 0   | 0     | 0     | 0     | 0     | 1     | 0   |

| TABLE V     |

|-------------|

| TRUTH TABLE |

|            | QPSK       |     |     | BPSK          |       |

|------------|------------|-----|-----|---------------|-------|

| $V_2[V_q]$ | $V_2[V_q]$ | MSB | LSB | $V_2[V_{in}]$ | $B_1$ |

| 1          | 1          | 0   | 0   | 1             | 0     |

| 0          | 1          | 0   | 1   | 0             | 1     |

| 0          | 0          | 1   | 1   |               |       |

| 1          | 0          | 1   | 0   |               |       |

#### **III. SIMULATION RESULTS**

The LPAP Rx in Fig.2 was implemented in Simulink Matlab R2020a®. Simulations were undertaken for the signal inputs generated by the NYUSim v3.1 71 GHz and 140 GHz channels. Thermal noise was generated according to (6) and the LO phase noise as in Fig. 8. The Rx component values such as gain, insertion loss, linearity and noise figure employed are detailed in section IV.

#### A. BER Curves

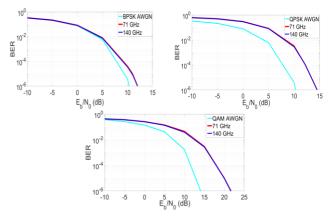

The BER curves for the LPAP Rx and the ideal theoretical values with no channel coding for AWGN channels are shown in Fig 12. The LPAP performance is similar for 71 GHz and 140 GHz channels with the 140 GHz performing marginally better. This can be attributed to the signal at AFE being higher at -16 dBm for 140 GHz channel, as compared to -21 dBm for the 71 GHz channel.

Fig. 12. LPAP Rx BER curves.

## B. Decision Feedback Equalizer

A continuous time linear equalizer (CTLE), feed-forward equalizer (FFE), decision feedback equalizer (DFE) or a combination of these are normally employed for channel

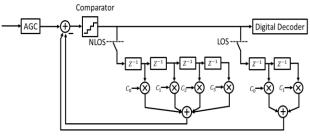

equalization [75], [76]. Another approach is to employ spatiotemporal equalization with beamforming in mmWave channels [77]. A DFE offers a significant advantage over CTLE and FFE since it cancels post-cursor ISI without noise and crosstalk amplification between the in-phase and quadrature channels. The DFE employed is shown in Fig.13.

Fig. 13. DFE for LPAP Rx.

The automatic gain control (AGC) ensures a certain voltage level at the DFE input. It applies an adaptive variable gain to the input waveform to achieve the desired RMS output voltage. Averaging the RMS voltage over a specified number of symbols, AGC performs by increasing or decreasing the gain, or keeping the gain constant. The DFE samples data at each clock sample time and the amplitude of the waveform is adjusted by a correction voltage. The zero-forcing algorithm is employed to determine the correction factors necessary to eliminate ISI. Due to the sparse nature of mmWave channels a two-tap DFE is sufficient to equalize the 71 GHz LOS or noline-of-sight (NLOS), and 140 GHz LOS channels. For the 140 GHz NLOS) channel a 4-tap DFE is required due to increased multipaths that occur indoors with sufficient power levels leading to ISI.

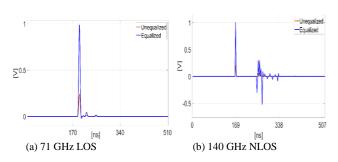

The normalized impulse response waveforms for the DFE are shown in Fig. 14 for the 71 GHz LOS and 140 GHz NLOS channel where more multipaths are visible for the latter.

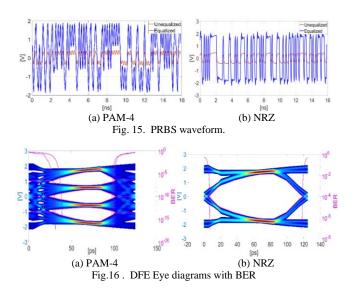

Fig. 14. DFE Impulse response.

The pseudo-random binary sequence waveforms for PAM-4 (16-QAM) and NRZ (QPSK/BPSK) are shown in Fig.15. Eye diagrams and BER for PAM-4 and NRZ are shown in Fig.16.

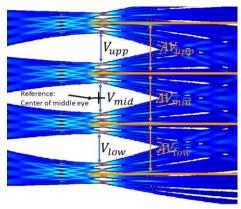

The signal quality parameters for PAM-4 and NRZ are eye linearity (EL), vertical eye closure (VEC) and channel operating margin (COM) [78], [79]. EL is a measure of variance in amplitude separation (distribution) between the different PAM-4 levels. EL is always equal to or less than 1.0. The value 1.0 indicates that the separations between all levels are equal. EL is given by [78]:

$$EL = \frac{min(AV_{upp}, AV_{mid} \text{ and } AV_{low})}{max(AV_{upp}, AV_{mid} \text{ and } AV_{low})}$$

where  $AV_{xxx}$  is the mean of central 5% of eye amplitude values

as shown in Fig 17. The *VEC* penalty is [78]:

$$VEC = 20 \log_{10} \left( max \left[ \frac{AV_{upp}}{V_{upp}}, \frac{AV_{mid}}{V_{mid}}, \frac{AV_{low}}{V_{low}} \right] \right)$$

The *COM* is defined as [79]:

$$COM = 20\log_{10}\left(\frac{A_s}{N}\right) \tag{13}$$

where N is the peak BER noise and  $A_s$  is the peak signal. COM combines the eye-mask and frequency-domain masks, with user-defined equalization parameters at the Rx. COM produces a signal-to-noise ratio (SNR) as a final value, which represents the channel performance and must be > 3 dB. The PAM-4 and NRZ measured parameters along with the DFE coefficient values are shown in TABLE VI.

Fig. 17. Eye measurements.

#### TABLE VI DFE EYE Parameters

| Parameter         |              | Value                |           |               |

|-------------------|--------------|----------------------|-----------|---------------|

|                   |              | LOS                  |           | NLOS          |

|                   | PAM-4        | NRZ                  | PAM-4     | NRZ           |

| Eye Height Upper  | 0.81641 V    | 3.01 V               | 0.53835 V | 1.6188 V      |

| Eye Height Center | 0.81636 V    | -                    | 0.53702 V | -             |

| Eye Height Lower  | 0.81642 V    | -                    | 0.5385 V  | -             |

| Eye Width Upper   | 65.51 ps     | 112.34 ps            | 81.05 ps  | 116.21 ps     |

| Eye Width Center  | 75.68 ps     | -                    | 81.54 ps  | -             |

| Eye Width Lower   | 65.51 ps     | -                    | 81.05 ps  | -             |

| Eye Area Upper    | 44.78 Vps    | 242.72 Vps           | 38.29 Vps | 148.63 Vps    |

| Eye Area Center   | 45.03 Vps    | -                    | 38.22 Vps | -             |

| Eye Area Lower    | 44.80 Vps    | -                    | 38.28 Vps | -             |

| COM               | 10.84  dB    | 18.47 dB             | 46.14 dB  | 54.85 dB      |

| VEC               | 2.91 dB      | 1.1024 dB            | 0.042  dB | 0.0157 dB     |

| Eye Linearity     | 0.9979       | -                    | 0.9975    | -             |

| DFE Tap Weights   | [-0.6041, -0 | [-0.6041, -0.1951] V |           | 5, -0.0280,   |

|                   |              |                      | -0.000    | 01 -0.0021] V |

| Interior PAM-4    | 1.162 V      |                      | 0.54015   | V             |

| Threshold         |              |                      |           |               |

### C. Blocking and Interference

During beamforming the beam can be directed towards the Rx and prevent interference to nearby Rxs. The effects of interfering power which is offset by 5° in azimuth can be reduced by ~3-8dB depending upon the elevation offset [80]. This is for HPBWs from 13.4°-25.8°. Lower values of interference are likely since the Rx HPBW considered is 7° [81].

Rx protection from noise and interference can be achieved through requirements for performance parameters like ACS (adjacent channel selectivity) and blocking characteristics. Since the standards for ultra-high-speed Rxs are not available the 5G New Radio (NR) parameters are adopted for quantifying the interference as below:

- ACS is a measure of a Rx's ability to receive a wanted signal at its assigned channel frequency in the presence of an adjacent channel signal at a given frequency offset from the center frequency of the assigned channel. The required ACS is 23 dB (Table 7.5-1 [82]).

- Blocking characteristic is a measure of Rx's ability to receive a wanted signal at its assigned channel frequency in the presence of an unwanted interferer on frequencies other than those of the adjacent channels, without this unwanted input signal causing a degradation in Rx performance beyond a specified limit. (Table 7.2.2-1, 7.2.2-2 and 7.2.2-3 [82]). The blocker in the vicinity of a 71 GHz channel would be the 60 GHz IEEE 80211.ad signal.

The measured ACS for LPAP Rx with an adjacent signal at 79 GHz is 26 dB. For blocking, the LPAP Rx is able to demodulate the signal with CW interferer up to -6 dBm without any degradation in signal quality. For both cases it is assumed that the LPAP Rx and the interfering signals are perfectly beam aligned as the worst-case scenario.

Beamforming and network function virtualization (NFV) currently adopted for 5G networks provide an inherent

9 VOLUME XX 2023

mechanism that would mitigate interference. High-frequency bands make it possible to increase antenna element density without increasing the physical size of the antenna which allows much narrower beams to be formed For 5G networks NFV is employed to perform the majority of processing needed to run commercial networks, via virtual network functions and by scheduling users. This can reduce interference significantly.

#### IV. CIRCUIT COMPONENTS AND POWER ANALYSIS

#### A. Receiver Linearity and Distortion

The state-of-the-art CMOS circuit parameters including nonidealities considered for simulation to obtain the BER curves in Fig. 12 are summarized in TABLE VII. The gain, noise figure and the third intercept point in various stages indicated by  $i \in [1,5]$  of the LPAP Rx are given by  $G_i$ ,  $NF_i$  and  $IIP_{3,i}$ respectively.

TABLE VII

|   | CIRCUIT PARAMETERS /NON-IDEALITIES |                                                                                  |  |  |  |  |  |

|---|------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| i | Component                          | Values                                                                           |  |  |  |  |  |

|   |                                    | G <sub>1</sub> 18 dB, NF <sub>1</sub> 8 dB, IP <sub>3,1</sub> -2.1 dBm, 11.7 mW  |  |  |  |  |  |

| 2 | Phase Shifter [84,85]              | 2                                                                                |  |  |  |  |  |

|   |                                    | G <sub>3</sub> 11.6 dB, NF <sub>3</sub> 15.8 dB IP <sub>3,3</sub> 3 dBm, 6.3 mW  |  |  |  |  |  |

|   | . ,                                | G <sub>4</sub> -1.5 dB                                                           |  |  |  |  |  |

| 5 |                                    | G <sub>5</sub> 11 dB, NF <sub>5</sub> 9.05 dB, IP <sub>3,5</sub> 26 dBm, 22.5 mW |  |  |  |  |  |

| - |                                    | As per equation (6)                                                              |  |  |  |  |  |

| - | PLL                                | Phase Noise as per Fig. 8                                                        |  |  |  |  |  |

According to International Telecommunication Union-Radio (ITU-R) recommendation the SFDR of a Rx accounting for distortion is given by:

$$SFDR = \frac{2}{3}(174 + IIP_3 - NF - 10\log_{10}B)$$

(14)

where  $IIP_3$  and NF are the total third intercept point and noise figure of the Rx. The  $IIP_3$  of M stages is given by [89]:

$$IIP_3 = \left[\sum_{i=1}^{M} \frac{\prod_{1}^{i-1} G_i}{IIP_{3,i}}\right]^{-1} \tag{15}$$

The noise factor for

$$M$$

stages is given by the Friss's formula:

$$f_M = f_1 + \frac{f_2 - 1}{G_1} + \frac{f_3 - 1}{G_1 G_2} + \dots + \frac{f_M - 1}{G_1 G_2 \dots G_{M-1}}$$

where  $NF = 10 \log_{10} f$  (16)

where  $NF = 10 \log_{10} f_M$ .

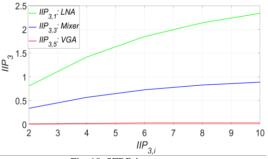

Using the values in TABLE VII, and from (14)-(16) the SFDR for the LPAP Rx is 46.48 dB. For a fixed bandwidth the design process requires a trade-off between the NF and IIP<sub>3</sub>. Loss in front of a Rx stage improves the IIP3, while increasing gain improves the NF. This is in contradiction to when defining the system specifications in each stage as a common practice and considering each performance parameter separately. Currently, there exists no technique for optimisation. Consider  $IIP_3$  in (15) as a function such that:

$$f(x, y, z) = IIP_3 (17)$$

where  $x = IIP_{3,1}$ ,  $y = IIP_{3,3}$ ,  $z = IIP_{3,5}$ ; and gains  $G_i$  as constants  $\forall i$ . The gradient of f(x, y, z) is given by:

$$\nabla f(x, y, z) = \begin{bmatrix} \frac{y^2 z^2}{\theta} \\ \frac{C_2 x^2 z^2}{\theta} \\ \frac{C_3 x^2 y^2}{\theta} \end{bmatrix}$$

(18)

where:

$\theta = [yz + C_1xyz + C_2xz + C_3xy]^2,$  $C_1 = G_1 + G_1 G_2 G_3,$  $C_2 = G_1G_2$  and  $C_3 = G_1G_2G_3G_4$ . The normalised gradient vector is given by:

$\nabla f_n(x, y, z) = 1.0\hat{X} + 0.5986\hat{Y} + 0.0003\hat{Z}$ From (19) we infer that increasing  $IIP_{3,1}$  would increase  $IIP_3$ at a faster rate than for any increase in  $IIP_{3,3}$  or  $IIP_{3,5}$ . This is shown in Fig. 18 where increase in IIP<sub>3</sub> is plotted for every 2 dB increase in  $IIP_{3,i}$ , i = 1,3,5. Further increase in SFDR can only be achieved by lowering  $NF_1$ . The LNA can accordingly be designed by employing SiGe HBTs. Such highperformance BiCMOS technology platforms with higher integration levels are currently being employed to address ultra-high-speed data rates [90]. Design of a wideband SiGe HBT LNA with  $G_1 = 20.2$  dB,  $IIP_{3.1} = 8.36$  and  $NF_1 =$ 3.7dB is given in [91], which improves the SFDR to 50.1 dB. The LNA power consumption is 17 mW.

Fig. 18. SFDR improvement.

#### **B.** Discussion

For LPAP Rx, AFE and comparator technology determine the feasibility of demodulation. How high the RF frequencies can be processed is determined by the AFE and the comparator sampling rate determines the data symbol rate. Current BiCMOS/CMOS technology permits implementing the design of Rxs with low-power AFE with carrier frequencies as high as 125 GHz [37], and similar technology can be employed for implementing the LPAP Rx detailed in this paper. The comparators must have sufficiently high sampling rates to cover the wide signal bandwidth for ultra-high-speed data transfer. Assuming the power consumption values indicated in TABLE VII, the power breakdown as per configurations in TABLE VIII are given in TABLE IX. The state-of-the-art ADC in 20 nm CMOS has a  $FOM_{ADC}$  of 0.24 pJ, sampling rate of 16 GS/s with ENOB 6 bits [33]. Using (1) and  $FOM_{ADC} = 0.24$ pJ the power consumed by the ADC is determined. High-speed comparators are widely employed as low-power voltage slicers for decoding PAM-4/PAM-2

VOLUME XX 2023 10

signals. Power consumption can be as low as ~1.7 mW for a 28-nm CMOS voltage slicer clocking at 30 GS/s [92], which is assumed in this paper.

TABLE VIII

RX CONFIGURATIONS

| RX CONFIGURATIONS |                             |                                    |     |            |  |  |  |

|-------------------|-----------------------------|------------------------------------|-----|------------|--|--|--|

| Rx                | N <sub>RX</sub> /PS/<br>LNA | / N <sub>S</sub> /VGA/<br>LO/Mixer | ADC | Comparator |  |  |  |

| ABI               | 32                          | 1                                  | 1   | X          |  |  |  |

| HBI               | 32                          | 2                                  | 2   | X          |  |  |  |

| DBI               | 32                          | 32                                 | 32  | X          |  |  |  |

| LPA               | P 32                        | 2                                  | X   | 2          |  |  |  |

TABLE VIII

POWER CONSUMPTION\*

|      | 1 OWER CONSONI TION |       |      |        |            |        |  |  |  |

|------|---------------------|-------|------|--------|------------|--------|--|--|--|

| Rx   | LNA                 | MIXER | VGA  | ADC    | Comparator | Total  |  |  |  |

| ABF  | 374.4               | 6.3   | 22.5 | 122.9  | -          | 526.1  |  |  |  |

| HBF  | 374.4               | 12.6  | 45   | 245.8  | -          | 677.8  |  |  |  |

| DBF  | 374.4               | 201.6 | 720  | 3932.8 | -          | 5228.8 |  |  |  |

| LPAP | 374.4               | 12.6  | 45   | -      | 1.7        | 433.7  |  |  |  |

<sup>\*</sup>In mW

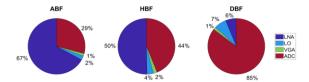

The power breakdown of ABF, HBF and DBF is given in Fig. 19. The ADCs contribute the largest share ranging from 29% to as high as 85%, which is avoided by not employing them in the proposed LPAP Rx.

Fig. 19. ADC power consumption.

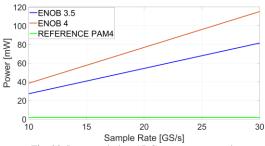

There are alternative approaches when using low-resolution ADCs i.e. 3.5-4 ENOB to lower the power requirements [93]-[99]. However, they do not consider the effect of wide bandwidths as in the case of ultra-high-speed data and algorithms at moderate sample rates of about 1GS/s [93]-[99]. For the expected ultra-high-speed data rates ADC power requirements will remain high even for lower resolutions. In comparison employing comparators the power requirements remain much lower for the similar data rates expected as shown in Fig. 20. The reference power taken is 1.7 mw, which is for a PAM-4 comparator at a sample rate of 30 GS/s [92].

Fig. 20. Low resolution ADC power consumption.

The alternative approaches of low-resolution ADC algorithms are complex to implement and require additional

signal algorithms such as for synchronization, user scheduling and beamforming [94]-[98]. When employing low-resolution ADCs with ENOB of 3.5-4 the power requirement is 82mW-115mW at a sample rate of 30 GS/s, not accounting for the overheads for the additional signalling algorithms.

#### **V. CONCLUSIONS**

Designing energy-efficient mixed-signal and baseband units for ultra-high-speed Rxs require a paradigm approach such as analog processing which is detailed in this paper. The novel approach is based on RF correlation that can process ultra-high-speed data envisaged for B5G/6G/THz Rxs without the power-hungry ADCs. Circuit non-idealities such as linearity, noise figure, insertion loss, thermal and phase noise are taken into consideration. The 3GPP mmWave phase noise model is adopted to accurately model performance of LOs implemented in 28nm FD-SOI CMOS process. Two PAM-4 low voltage slicers are employed to replace the power-hungry ADCs. The digital decoder is not only able to support multiple modulations with a single architecture but also with the highest modulation reported so far for 16-QAM employing direct-demodulation. The digital decoder conforms to Gray mapping for the baseband signals minimizing the probability of bit error. Power analyses undertaken for current beamforming approaches requiring ADCs indicate a promising approach towards designing ultra-high-speed Rxs with low-power analog integrated circuit design solutions.

#### **REFERENCES**

- T. S. Rappaport, et.al., "Wireless communications and applications above 100 GHz: opportunities and challenges for 6G and beyond," *IEEE Access*, vol. 7, no. 9, pp. 78729–78757, May 2019.

- [2] FCC Media Release, Nov. 2019. [Online] Available: https://docs.fcc.gov/public/attachments/DOC-356588A1.pdf.

- [3] Kenneth K.O, et.al, "Opening THz for everyday applications," *IEEE Commun. Mag.*, vol. 57, no. 8, pp. 70–76, Aug. 2019.

- [4] S. Kang, S. V. Thyagarajan, and A. M. Niknejad, "A 240 GHz Fully Integrated Wideband QPSK Transmitter in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 10, Oct. 2015, pp. 2256–67.

- [5] K. Takano et al., "A 105Gb/s 300GHz CMOS Transmitter," in Proc. IEEE Int'l. Solid-State Circuits Conf., Feb. 2017, San Francisco, CA, pp. 308–09.

- [6] T. S. Rappaport, et. al., Millimeter Wave Wireless Communications. Pearson/Prentice Hall c. 2015.

- [7] F. Sohrabi and W. Yu, "Hybrid digital and analog beamforming design for large-scale antenna arrays," *IEEE J. Sel. Topics Signal Process.*, vol. 10, no. 3, pp. 501–513, Apr. 2016.

- [8] J.-C. Chen, "Hybrid beamforming with discrete phase shifters for millimeter-wave massive MIMO systems," *IEEE Trans. Veh. Technol.*, vol. 66, no. 8, pp. 7604–7608, Aug. 2017.

- [9] Z. Wang, M. Li, Q. Liu, and A. L. Swindlehurst, "Hybrid precoder and combiner design with low resolution phase shifters in mmWave MIMO systems," *IEEE J. Sel. Topics Signal Process.*, vol. 12, no. 2, pp. 1–14, May 2018.

- [10] P. Raviteja, Y. Hong, and E. Viterbo, "Analog beamforming with low resolution phase shifters," *IEEE Wireless Commun. Lett.*, vol. 6, no. 4, pp. 502–505, Aug. 2017.

- [11] Y. Sun and C. Qi, "Weighted sum-rate maximization for analog beamforming and combining in millimeter wave massive MIMO communications," *IEEE Commun. Lett.*, vol. 21, no. 8, pp. 1883–1886, Aug. 2017.

- [12] O. E. Ayach, S. Rajagopal, S. Abu-Surra, Z. Pi, and R. W. Heath, Jr.,

- "Spatially sparse precoding in millimeter wave MIMO systems," *IEEE Trans. Wireless Commun.*, vol. 13, no. 3, pp. 1499–1513, Mar. 2014

- [13] J. Zhang, Y. Huang, Q. Shi, J. Wang, and L. Yang, "Codebook design for beam alignment in millimeter wave communication systems," *IEEE Trans. Commun.*, vol. 65, no. 11, pp. 4980–4995, Jul. 2017.

- [14] M. Li, Z. Wang, H. Li, Q. Liu, and L. Zhou, "A hardware-efficient hybrid beamforming solution for mmWave MIMO systems," *IEEE Wireless Commun.*, vol. 26, no. 1, pp. 137–143, Feb. 2019.

- [15] X. Gao, L. Dai, Y. Sun, S. Han, and C.-L. I, "Machine learning inspired energy-efficient hybrid precoding for mmWave massive MIMO systems," in Proc. *IEEE Int. Conf. Commun. (ICC)*, Paris, France, May 2017, pp. 1–6.

- [16] Z. Wang, Q. Liu, M. Li and W. Kellerer, "Energy Efficient Analog Beamformer Design for mmWave Multicast Transmission," *IEEE Trans. Green Comms. Net.*, vol. 3, no. 2, pp.552-564, Jun. 2019.

- [17] C. Lin and Geoffrey Ye Li, "Adaptive Beamforming with resource allocation for distance-aware multi-user indoor Terahertz communications," *IEEE Trans. Comm.*, vol. 63, no. 8, pp. 2985-2995, Aug. 2015.

- [18] M. Aminu, "Beamforming and Transceiver HW Design for THz Band", in Proc. 52nd Asilomar Conf. Sig. Syst. and Comp., Pacific Grove CA, USA, Oct. 2018.

- [19] D Li, D Qiao and L. Zhan, "Performance Analysis of Indoor THz Communications with One-Bit Precoding", in Proc. IEEE Global Comm. Con., (GLOBECOM 2018), Abu Dhabi, UAE, Dec 2018.

- [20] S. A. Busari, et. al., "Generalized Hybrid Beamforming for Vehicular Connectivity Using THz Massive MIMO," *IEEE Trans. Veh. Tech.*, vol. 68, no. 9, pp. 8372 – 8383, Sept. 2019.

- [21] Okada et al., "20.3 a 64-QAM 60GHz CMOS transceiver with 4-channel bonding," in *IEEE Int. Solid-State Circuits Conf. (ISSCC)* Dig. Tech. Papers, Feb. 2014, pp. 346–347.

- [22] S. V. Thyagarajan, S. Kang, and A. M. Niknejad, "A 240 GHz fully integrated wideband QPSK receiver in 65 nm CMOS," *IEEE J. Solid State Circuits*, vol. 50, no. 10, pp. 2268–2280, Oct. 2015.

- [23] K.K. Tokgoz, et,al., "A 20 Gb/s 16-QAM,CMOS millimeter-wave wireless transceiver" in Proc. *IEEE Int. Solid-State Circuits Conf.* (ISSC) Dig. Tech. Papers, Feb 2018, pp. 168-170.

- [24] K.K. Tokgoz, et,al., "A 56 Gb/s W-band CMOS wireless transceiver," in Proc. *IEEE Int. Solid-State Circuits Conf. (ISSC)* Dig. Tech. Papers, Jan 2016, pp. 242-243.

- [25] A. Oppenheim et. al., Digital Signal Processing. London, UK.:Pearson, 2015.

- [26] DPO77002SX Product Support. [Online]. Available: https://www.tek.com/oscilloscope/dpo77002sx

- [27] Keysight Technologies Infiniium 90000L Series Oscilloscopes. [Online]. Available: http://literature.cdn.keysight.com/litweb/pdf/5990-7368EN.pdf

- [28] R. H. Walden, "Analog-to-digital converter survey and analysis," IEEE J. Sel. Areas Commun., vol. 17, no. 4, pp. 539–550, Apr. 1999.

- [29] T. Sundstrom, B. Murmann, and C. Svensson, "Power dissipation bounds for high-speed Nyquist analog-to-digital converters," *IEEE Trans. Circuits Syst. I*, Reg. Papers, vol. 56, no. 3, pp. 509–518, Mar. 2009.

- [30] B. Razavi, "Design considerations for interleaved ADCs," *IEEE J. Solid-State Circuits*, vol. 48, no. 8, pp. 1806–1817, Aug. 2013.

- [31] D. Cui et al., "A 320 mW 32Gb/s 8b ADC-based PAM-4 analog frontend with programmable gain control and analog peaking in 28nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC)* Dig. Tech. Papers, Jan./Feb. 2016, pp. 58–59.

- [32] M. El-Chammas and B. Murmann, "General analysis on the impact of phase-skew in time-interleaved ADCs," *IEEE Trans. Circuits Syst. I*, Reg. Papers, vol. 56, no. 5, pp. 902–910, May 2009.

- [33] J. Cao et al., "A transmitter and receiver for 100 Gb/s coherent networks with integrated 4 \_ 64GS/s 8b ADCs and DACs in 20 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC)* Dig. Tech. Papers, Feb. 2017, pp. 484–485.

- [34] N. Dolatsha et al., "A compact 130 GHz fully packaged point-to-point wireless system with 3D-printed 26dBi lens antenna achieving 12.5 Gb/s at 1.55 pJ/b/m," in *IEEE Int. Solid-State Circuits Conf. (ISSCC)* Dig. Tech. Papers, Feb. 2017, pp. 306–307.

- [35] A. Baier and P. W. Baier, "Digital Matched Filtering of Arbitrary Spread-Spectrum Waveforms using Correlators with Binary Quantization," MILCOM 1983 - IEEE Military Communications Conference, Washington, DC, USA, 1983, pp. 418-423, doi: 10.1109/MILCOM.1983.4794730

- [36] B. Aazhang and H. V. Poor, "Performance of DS/SSMA communications in impulsive channels. II. Hard-limiting correlation receivers," in IEEE Transactions on Communications, vol. 36, no. 1, pp. 88-97, Jan. 1988, doi: 10.1109/26.273.

- [37] N. Deltimple et al., "Cartesian feedback with digital enhancement for CMOS RF transmitter," Proc. Linearization Efficiency Enhancement Techniques Silicon Power Amplifiers, Nov. 2014, pp. 3.

- [38] H. Mohammed, H. Wang, A. Cathelin and P. Heydari, "A 115–135-GHz 8PSK Receiver Using Multi-Phase RF-Correlation-Based Direct-Demodulation Method," *IEEE J. Solid State Circuits*, vol. 54, no. 9, pp.2435–2448, Sept. 2015.

- [39] M.K. Samimi and T.S. Rappaport, "3-D Millimeter-Wave Statistical Channel Model for 5G Wireless System Design," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 7, pp. 2207-2225, Jul. 2016.

- [40] T. S. Rappaport, G. R. MacCartney, Jr., M. K. Samimi, and S. Sun, "Wideband millimeter-wave propagation measurements and channel models for future wireless communication system design," *IEEE Trans. Commun.*, vol. 63, no. 9, pp. 3029–3056, Sep. 2015.

- [41] NYUWIRELESS NYUSIM v3.0 Open Source Downloadable 5G/6G Channel Simulator Software [Online]. Available: http://wireless.engineering.nyu.edu/nyusim

- [42] 3GPP, "Study on channel model for frequencies from 0.5 to 100 GHz," 3rd Generation Partnership Project (3GPP), TR 38.901 V14.1.1, Jul. 2017. [Online]. Available: https://portal.3gpp.org/desktopmodules/Specifications/Specification Details.aspx?specificationId=3173

- [43] S. Sun, T. S. Rappaport, M. Shafi, P. Tang, J. Zhang, and P. J. Smith, "Propagation models and performance evaluation for 5G mmWave bands," *IEEE Trans. Veh. Technol.*, vol. 67, no. 9, pp. 8422–8439, Sep. 2018.

- [44] T. S. Rappaport, S. Sun, and M. Shafi, "Investigation and comparison of 3GPP and NYUSIM channel models for 5G wireless communications," in 2017 IEEE 86th Veh. Technol. Conf. (VTC-Fall), Sep. 2017, pp. 1–5.

- [45] T. S. Rappaport, S. Sun, and M. Shafi, "5G channel model with improved accuracy and efficiency in mmWave bands," *IEEE 5G Tech Focus*, vol. 1, no. 1, Mar. 2017.

- [46] S. Ju and T. S. Rappaport, "Simulating motion incorporating spatial consistency into the NYUSIM channel model," in 2018 IEEE 88th Veh. Technol. Conf. Workshops, pp. 1–6, Aug. 2018.

- [47] S. Ju and T. S. Rappaport, "Millimeter-wave extended NYUSIM channel model for spatial consistency," in 2018 IEEE Global Commun. Conf. (Globecom), pp. 1–6, Dec. 2018.

- [48] G. R. MacCartney, Jr., T. S. Rappaport, and S. Rangan, "Rapid fading due to human blockage in pedestrian crowds at 5g millimeter-wave frequencies," in 2017 IEEE Global Commun. Conf. (GLOBECOM), Dec. 2017, pp. 1–7.

- [49] A. Hajimiri and T. H. Lee, "A general theory of phase noise in electrical oscillators," *IEEE J. of Solid-State Circuits*, vol. 33, no. 2, pp. 179-194 Feb. 1998.

- [50] T. H. Lee and A Hajimiri, "Oscillator phase noise: a tutorial," *IEEE J. of Solid-State Circuits*, vol. 35, no. 3, pp. 326-336 Mar. 2000. doi:10.1109/4.826814

- [51] J. J. Rael and A. A. Abidi, "Physical processes of phase noise in differential LC oscillator," in *Proc. IEEE Custom Integr. Circuits Conf.*, May 2000. doi:10.1109/CICC.2000.852732.

- [52] B.Razavi, "A study of phase noise in CMOS oscillators," *IEEE J. of Solid-State Circuits*, vol. 31, no. 3, pp. 331-343, March 1996. doi: 10.1109/4.494195

- [53] Choi, C. S., et. al., RF Impairment Models for 60GHz-Band SYS/PHY, Simulation, *IEEE Document* 802.15-06-0477-01-003c, November 2006.

- [54] Study on new radio access technology: Radio Frequency (RF) and coexistence aspects (Release 14), TR 38.803 V14.2.0 (2017-09) 3rd Generation Partnership Project.

- [55] H. Jia, B. Chi, L. Kuang and Z. Wang, "A 47.6–71.0-GHz 65-nm CMOS VCO based on magnetically coupled π-type LC network," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 5, pp. 1645-1657, May 2015, doi: 10.1109/TMTT.2015.2415487

- [56] A. Agrawal and A. Natarajan, "Series resonator mode switching for area-efficient octave tuning-tange CMOS LC-oscillators," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 5, pp. 1569-1579, May 2017, doi: 10.1109/TMTT.2016.2647723.

- [57] H. Guo, Y. Chen, P. Mak and R. P. Martins, "A 0.083-mm<sup>2</sup> 25.2-to-29.5 GHz multi-LC-tank class-F234 VCO with a 189.6-dBc/Hz FOM," *IEEE J. Solid-State Circuits*, vol. 1, no. 4, pp. 86-89, April 2018, doi: 10.1109/LSSC.2018.2851499.

- [58] Y. Peng, J. Yin, P. Mak and R. P. Martins, "Low-phase-noise wideband mode-switching quad-core-coupled mm-wave VCO using a single-center-tapped switched inductor," *IEEE J. Solid-State Circuits*, vol. 53, no. 11, pp. 3232-3242, Nov. 2018, doi: 10.1109/JSSC.2018.2867269.

- [59] A. Basaligheh, P. Saffari, W. Winkler and K. Moez, "A wide tuning range, low phase noise, and area efficient dual-band millimeter-wave CMOS VCO based on switching cores," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 8, pp. 2888-2897, Aug. 2019, doi: 10.1109/TCSI.2019.2901253.

- [60] N. Jahan, A. Barakat and R. K. Pokharel, "A –192.7-dBc/Hz FoM Ku-Band VCO using a DGS resonator with a high-band transmission pole in 0.18-µm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 29, no. 12, pp. 814-817, Dec. 2019, doi: 10.1109/LMWC.2019.2950525.

- [61] Y. Fu, L. Li, D. Wang and X. Wang, "A –193.6 dBc/Hz FoMT 28.6-to-36.2 GHz Dual-core CMOS VCO for 5G applications," *IEEE Access*, vol. 8, pp. 62191-62196, Mar. 2020, doi: 10.1109/ACCESS.2020.2983796.

- [62] X. Liu and H. C. Luong, "A 170-GHz 23.7% tuning-range CMOS injection-locked LO generator with third-harmonic enhancement," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 7, pp. 2668-2678, July 2020, doi: 10.1109/TMTT.2020.2986757.

- [63] Y. Huang, Y. Chen, H. Guo, P. -I. Mak and R. P. Martins, "A 3.3-mW 25.2-to-29.4-GHz current-reuse VCO using a single-turn multi-tap inductor and differential-only switched-capacitor arrays with a 187.6-dBc/Hz FOM," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 11, pp. 3704-3717, Nov. 2020, doi: 10.1109/TCSI.2020.3013259.

- [64] A. Basaligheh, P. Saffari, I. M. Filanovsky and K. Moez, "A 65–81 GHz CMOS dual-mode VCO using high quality factor transformer-based inductors," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 12, pp. 4533-4543, Dec. 2020, doi: 10.1109/TCSI.2020.3004859.

- [65] Y. -H. Chang, "Low-voltage dual-band CMOS voltage-controlled oscillator for Ka-Band and V-Band applications," *IEEE Microw. Wireless Compon. Lett.*, Jul. 2021, doi: 10.1109/LMWC.2021.3097212.

- [66] L. Gomes et al., "77.3-GHz standing-wave oscillator based on an asymmetrical tunable slow-wave coplanar stripline resonator," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 8, pp. 3158-3169, Aug. 2021, doi: 10.1109/TCSI.2021.3060579.

- [67] H. Guo, Y. Chen, C. Yang, P. -I. Mak and R. P. Martins, "A millimeter-wave CMOS VCO featuring a mode-ambiguity-aware multi-resonant-RLCM tank," *IEEE Trans. Circuits Syst. I, Reg. Papers*, (Early Access Jul 2021) doi: 10.1109/TCSI.2021.3096196.m

- [68] C.-T. Hung, Y.-P. Huang, and W.-Z. Chen, "A 40 Gb/s PAM-4 receiver with 2-Tap DFE based on automatically non-even level tracking," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2018, pp. 213–214.

- [69] L. Tang, W. Gai, L. Shi, X. Xiang, K. Sheng, and A. He, "A 32Gb/s 133 mW PAM-4 transceiver with DFE based on adaptive clock phase and threshold voltage in 65 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 114–115.

- [70] P.-J. Peng, J.-F. Li, L.-Y. Chen, and J. Lee, "A 56Gb/s PAM-4/NRZ transceiver in 40 nm CMOS," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2017, pp. 110–111.

- [71] J. Lee, M.-S. Chen, and H.-D. Wang, "Design and comparison of three 20-Gb/s backplane transceivers for duobinary, PAM4, and NRZ data," *IEEE J. Solid-State Circuits*, vol. 43, no. 9, pp. 2120–2133, Sep. 2008.

- [72] A. Cevrero et al., "6.1 A 100Gb/s 1.1pJ/b PAM-4 RX with dual-mode 1-tap PAM-4/3-Tap NRZ speculative DFE in 14nm CMOS FinFET," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2019, pp. 112–113.

- [73] "IEEE Standard for Ethernet Amendment 2: Physical Layer Specifications and Management Parameters for 100 Gb/s Operation Over Backplanes and Copper Cables," IEEE Std 802.3bj-2014 (Amendment to IEEE Std 802.3-2012 as amended by IEEE Std 802.3bk-2013), pp. 1–368, 2014.

- [74] A. T. Ramkaj, S. J. Steyaert and F. Tavernier, "A 13 .5-Gb/s 5-mV-Sensitivity 26.8-ps-CLK-OUT Delay Triple-Latch Feedforward Dynamic Comparator in 28-nm CMOS" IEEE J. Solid-State Circuits Lett., vol.2, no. 9, pp. 167–170, Sep. 2019.

- [75] F. Loi, E. Mammei, S. Erba, M. Bassi and A. Mazzanti, "A 25mW highly linear continuous-time FIR equalizer for 25Gb/s serial links in 28-nm CMOS," *IEEE Trans. Circuits Syst. I.*, vol. 64, no. 7, pp. 1903–1913, Jul. 2017.

- [76] Petricli, H. Zhang, E. Monaco, G. Albasini and A. Mazzanti, "A 112 Gb/s PAM-4 RX front-end with unclocked decision feedback qualizer," *IEEE Trans. Circuits Syst. II*., vol. 68, no. 1, pp. 256–260, Jul. 2021.

- [77] A.I. Hussein, S. Kundu and J. Paramesh "Adaptive Beamforming Assisted Decision Feedback Equalization for Millimeter Wave Receivers," in 2015 IEEE Global Commun. Conf. (GLOBECOM), Dec. 2015. doi: 10.1109/GLOCOM.2015.7417817.

- [78] IEEE Std P802.3bs, June 2016.

- [79] IEEE Std. 802.3bj-2014 (Amendment to IEEE Std. 802.3-2012), Annex 93A.1 Channel Operating Margin.

- [80] S. K. Yong, M. E. Sahin, and Y. H. Kim, "On the effects of misalignment and angular spread on the beamforming performance", in *Proc. IEEE Consumer Commun. and Networking Conf. (CCNC)*, Las Vegas, NV, Jan. 2007.

- [81] J. Kokkoniemi, et. Al., "Impact of beam misalignment on THz wireless systems," Nano Commun. Netw. Elsevier, vol. 24, May 2020.

- [82] 3GPP NR, Base Station (BS) radio transmission and reception (Release 16), TS 138.104 v16.7.0, ETSI, April 2021. [Online]. Available: <a href="https://www.etsi.org/deliver/etsi">https://www.etsi.org/deliver/etsi</a> ts/138100\_138199/138104/16.07.0 0\_60/ts\_138104v160700p.pdf

- [83] M. Vigilante and P. Reynaert., "A 68.1-to96.4 GHz variable-gain low-noise amplifier in 28 nm CMOS," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC), San Francisco, CA, USA, Jan./Feb. 2016, doi: 10.1109/ISSCC.2016.7418056.

- [84] R. Garg and A. S. Natarajan, "A 28-GHz low-power phased-array receiver front-end with 360° RTPS phase shift range," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4703–4714, Nov. 2017.

- [85] W. H. Woods, et. al., "CMOS millimetre wave phase shifter based on tunable transmission lines," in *Proc. IEEE Custom Integr. Circuits Conf.*, May 2013. doi: 10.1109/CICC.2013.6658442

- [86] Y. Lin, et. al., "6.3 mW 94 GHz CMOS down-conversion mixer with 11.6 dB gain and 54 dB LO-RF isolation," *IEEE Microw. Wireless Compon. Lett.*, Aug. 2016, doi: 10.1109/LMWC.2016.2585562

- [87] L. Gao and G. M. Rebeiz., "Wideband bandpass filter for 5G millimeter-wave application in 45-nm CMOS silicon-on-insulator," IEEE Electron Device Lett., vol. 42, no. 8, pp. 1244–1247, Aug. 2021, doi: 10.1109/LED.2021.3089656.

- [88] V. Asgari and L. Belostotski, "Wdieband 28-nm CMOS variable-gain amplifer," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no.1, pp. 37-47, Jan 2020, doi: 10.1109/TCSI.2019.2942492.

- [89] J. Heuvel, J. Linnartz and P. Baltus, "Optimizing throughput for limited receiver circuit power," in *Proc. IEEE Int. Sym. Ckts. Sys. Conf.*, *ISCAS*, Paris, France, 2010.

- [90] T. Zimmer, "SiGe HBTs and BiCMOS technology for present and future millimeter-wave systems," *IEEE J. Microw.*, vol. 1, no. 1, Jan. 2021, doi: 10.1109/JMW.2020.3031831

- [91] P. Singh, et. al., "Low power, wideband SiGe HBT LNA covering 57-64 GHz band," 26<sup>th</sup> Int. Sym. VLSI Design and Test, VDAT 2022, Springer, Jammu, India, Jul. 2022, pp. 160-170.

- [92] K. Chen, W. Wei-Ting Kuo and A. Emami, "A 60-Gb/s PAM4 wireline receiver with 2-tap direct decision feedback equalization employing track-and-regenerate slicers in 28-nm CMOS," IEEE J. Solid-State Circuits, vol. 56, no. 3, pp. 750-762, Oct. 2020, doi: 10.1109/JSSC.2020.3025285

- [93] K. Roth and J. A. Nossek,, "Achievable Rate and Energy Efficiency of Hybrid and Digital Beamforming Receivers With Low Resolution ADC," *IEEE J. Sel. Areas Commun.*, vol. 35, no. 9, pp. 2056-2068, Sep. 2017.

- [94] W.B. Abbas, F. Gomez-Cuba and M. Zorzi, "Millimeter Wave Receiver Efficiency: A Comprehensive Comparison of Beamforming Schemes With Low Resolution ADCs," *IEEE Trans. Wire. Commun.*, vol. 16, no. 12, pp. 8131-8145, Dec. 2017

- [95] D. Zhu, et.al., "Directional Frame Timing Synchronization in Wideband Millimeter-Wave Systems With Low-Resolution ADCs," *IEEE Trans. Wire. Commun.*, vol. 18, no. 11, pp. 5350-5364, Nov. 2019.

- [96] J. Choi, G. Lee, B. L. Evans,, "User Scheduling for Millimeter Wave Hybrid Beamforming Systems With Low-Resolution ADCs," *IEEE Trans. Wire. Commun.*, vol. 18, no. 4, pp. 2401-2414, Apr. 2019.

- [97] J. Choi, G. Lee and B.L. Evans, "Two-Stage Analog Combining in Hybrid Beamforming Systems With Low-Resolution ADCs," *IEEE Trans. Sig. Proc.*, vol. 67, no. 9, pp. 2410-2425, May. 2019.

- [98] J. Yang, et.al., "Fast Beam Training Architecture for Hybrid mmWave Transceivers," *IEEE Trans. Veh. Tech.*, vol. 69, no. 3, pp. 2700-27155, Mar. 2020.

- [99] S. Dutta, et.al., "A Case for Digital Beamforming at mmWave," *IEEE Trans. Wire. Commun.*, vol. 19, no. 2, pp. 756-770, Feb. 2020.

#### **JASWINDER LOTA (SM, IEEE)**

received the B.Sc. degree from National Defence Academy, Pune, India, the B.Eng. degree in electrical engineering from the Naval College of Engineering, Pune, India, the M.Eng. degree in radar and communication engineering from the Indian Institute of Technology Delhi, New Delhi, India, and the Ph.D. degree from the University of Westminster, London, U.K., in 2007. In 1989, he was

with the Indian Navy, in various roles in engineering for radar, EW, and weapon systems. During 2006–2009, he was a Senior Technologist with Sepura Plc., Cambridge, U.K., for development of TETRA-2 mobile radios. Since 2009, he has been with the University of East London, London, U.K., where he has been a Reader since 2014, and was a Senior Lecturer during 2009–2014. Since 2013, he has been a Visiting Academic with the Department of Electronics and Electrical Engineering, University College London, London, U.K. His research interests include wireless communications, signal processing, circuits and systems.

Dr. Lota is a chartered engineering and since 2018, he has been an Associate Editor for IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS. He was a Guest Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS Special Issue 2017 on the CASS Flagship Conferences. In 2015, he was a Guest Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS Special Issue on Biomedical and Bioelectronic Circuits for Enhanced Diagnosis and Therapy

ANDREAS DEMOSTHENOUS (Fellow, IEEE) received the B.Eng. degree in electrical and electronic engineering from the University of Leicester, Leicester, U.K., the M.Sc. degree in telecommunications technology from Aston University, Birmingham, U.K., and the Ph.D. degree in electronic and electrical engineering from University College London (UCL), London, U.K., in 1992, 1994, and 1998, respectively. He is currently a Professor with the Department of

Electronic and Electrical Engineering, UCL, and leads the Bioelectronics Group. He has made outstanding contributions to improving safety and performance in integrated circuit design for active medical devices, such as spinal cord and brain stimulators. He has numerous collaborations for cross-disciplinary research, both within the U.K. and internationally. He has authored more than 350 articles in journals and international conference proceedings, several book chapters, and holds a number of patents. His research interests include analog and mixed-signal integrated circuits for biomedical, sensor, and signal processing applications.

Dr. Demosthenous is a Fellow of the Institution of Engineering and Technology, and a Chartered Engineer. He was the co-recipient of a number of best paper awards and has graduated many Ph.D. Students. He was an Associate Editor from 2006 to 2007 and the Deputy Editor-in-Chief from 2014 to 2015 of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS, and an Associate Editor from 2008 to 2009 and the Editor-in-Chief from 2016 to 2019 of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS. He is an Associate Editor of the IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS and is on the International Advisory Board of Physiological Measurement. He has served on the technical committees of international conferences, ESSCIRC, ISCAS and ICECS.