# DEVELOPMENT OF AN AREA-EFFICIENT AND LOW-POWER FIVE-TRANSISTOR SRAM FOR LOW-POWER SOC

by

Hooman Jarollahi B.A.Sc., Engineering Science Simon Fraser University, 2008

## THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

In the School of Engineering Science

© Hooman Jarollahi 2010 SIMON FRASER UNIVERSITY Summer 2010

All rights reserved. However, in accordance with the *Copyright Act of Canada*, this work may be reproduced, without authorization, under the conditions for *Fair Dealing*. Therefore, limited reproduction of this work for the purposes of private study, research, criticism, review and news reporting is likely to be in accordance with the law, particularly if cited appropriately.

#### **APPROVAL**

**Date Defended/Approved:**

Name: Hooman Jarollahi Degree: Master of Applied Science (M.A.Sc.) Title of Thesis: **DEVELOPMENT OF AN AREA-EFFICIENT AND LOW-**POWER FIVE-TRANSISTOR SRAM FOR LOW-**POWER SOC Examining Committee:** Chair: Dr. Shahram Payandeh, P.Eng. Professor, School of Engineering Science Dr. Richard F. Hobson, P.Eng. Senior Supervisor Professor, School of Engineering Science Dr. Marek Syrzycki Supervisor Professor, School of Engineering Science Dr. Glenn H. Chapman, P.Eng. Internal Examiner Professor, School of Engineering Science

June 3, 2010

## Declaration of Partial Copyright Licence

The author, whose copyright is declared on the title page of this work, has granted to Simon Fraser University the right to lend this thesis, project or extended essay to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users.

The author has further granted permission to Simon Fraser University to keep or make a digital copy for use in its circulating collection (currently available to the public at the "Institutional Repository" link of the SFU Library website <www.lib.sfu.ca> at: <a href="http://ir.lib.sfu.ca/handle/1892/112>">http://ir.lib.sfu.ca/handle/1892/112></a>) and, without changing the content, to translate the thesis/project or extended essays, if technically possible, to any medium or format for the purpose of preservation of the digital work.

The author has further agreed that permission for multiple copying of this work for scholarly purposes may be granted by either the author or the Dean of Graduate Studies.

It is understood that copying or publication of this work for financial gain shall not be allowed without the author's written permission.

Permission for public performance, or limited permission for private scholarly use, of any multimedia materials forming part of this work, may have been granted by the author. This information may be found on the separately catalogued multimedia material and in the signed Partial Copyright Licence.

While licensing SFU to permit the above uses, the author retains copyright in the thesis, project or extended essays, including the right to change the work for subsequent purposes, including editing and publishing the work in whole or in part, and licensing other parties, as the author may desire.

The original Partial Copyright Licence attesting to these terms, and signed by this author, may be found in the original bound copy of this work, retained in the Simon Fraser University Archive.

Simon Fraser University Library Burnaby, BC, Canada

#### **ABSTRACT**

The purpose of this thesis is to introduce a new low-power, reliable and high-performance five-transistor (5T) SRAM in 65nm CMOS technology, which can be used for cache memory in processors and low-power portable devices. An area reduction of ~13% compared to a conventional 6T cell is possible. A biasing ground line is charged by channel leakage current from memory cells in standby, and is used to pre-charge a single bit-line and bias the negative supply voltage of each memory cell to suppress standby leakage power. A major standby power reduction is gained compared to conventional 5T and 6T designs, and up to ~30% compared to previous low-power 6T designs. Read, write, and standby performance and reliability issues are discussed and compared with conventional and low-power 6T SRAM designs.

**Keywords:** Static Random Access Memory; Five-transistor SRAM; Low-power SRAM; Area-efficient SRAM; Leakage-power reduction

#### **ACKNOWLEDGEMENTS**

I would like to thank my supervisor, Professor Richard Hobson, who believed in me in the first place, taught me how to conduct research and apply the knowledge behind it to this thesis. His encouragement, guidance and support from the initial to the final level enabled me to complete this thesis.

In addition, I thank my parents who have always supported me unconditionally especially during the completion of this thesis.

Lastly, I offer my regards and gratitude to anyone who supported me in any respect in the completion of this thesis.

Hooman Jarollahi

## **TABLE OF CONTENTS**

| App                | roval          |                                                                      | ii  |

|--------------------|----------------|----------------------------------------------------------------------|-----|

| Abs                | tract          |                                                                      | iii |

| Ack                | nowled         | gements                                                              | iv  |

| Tab                | le of Co       | ntents                                                               | V   |

| List               | of Figu        | es                                                                   | vii |

| List               | of Table       | es                                                                   | xi  |

| Glos               | ssary          |                                                                      | xii |

| 1: lr              | ntroduc        | tion                                                                 | 1   |

| 1.1                | SRAM           | block organization and structure                                     | 4   |

| 1.2                | CMOS           | S SRAM and technology scaling                                        | 6   |

| 1.3                |                | nold voltage variations and causes                                   |     |

| 1.4                | Leaka          | ge current sources                                                   | 10  |

|                    | 1.4.1          | Reverse-biased junction leakage current (I <sub>i</sub> )            | 12  |

|                    | 1.4.2          | Gate induced drain leakage (I <sub>GIDL</sub> )                      |     |

|                    | 1.4.3          | Gate direct-tunnelling leakage (I <sub>g</sub> )                     |     |

|                    | 1.4.4          | Sub-threshold (weak inversion) leakage (I <sub>sth</sub> )           |     |

| 1.5                |                | operation failure                                                    |     |

| 1.6                |                | ty analysis                                                          |     |

|                    | 1.6.1<br>1.6.2 | Static Noise Margin (SNM)                                            |     |

|                    | 1.6.2          | Read Noise Margin (RNM) Butterfly diagrams                           |     |

|                    | 1.6.4          | Static noise margin measurement using SPICE                          |     |

| 1.7                | _              | noise margin and supply voltages                                     |     |

| 1.8                |                | ology corners and static noise margin in SRAM                        |     |

| 2: 6               | T SRAI         | // operation                                                         | 26  |

| 2.1                |                | by mode                                                              |     |

| 2.2                |                | pperation                                                            |     |

| 2.3                |                | of PMOS mismatch on RNM using non-rotated original butterfly         |     |

|                    |                | ms                                                                   | 35  |

| 2.4                |                | of the cell differential voltage on SNM and RNM of a conventional 6T | 27  |

| 2.5                |                |                                                                      |     |

| 2.5<br>2.6         | •              |                                                                      |     |

| 2.0<br>2.7         |                | of V <sub>DDM</sub> variations on write and write recovery delay     |     |

| 2. <i>1</i><br>2.8 |                | of cell voltage, cell ratio, and threshold voltage on SNM            |     |

| 2.0                |                | ential biasing scheme to mitigate the effect of $V_{\pm}$ variations |     |

|                    |                |                                                                      |     |

| 3: P         | Proposed 5T SRAM (5TSDG) Design                               | 48  |

|--------------|---------------------------------------------------------------|-----|

| 3.1          | Standby mode                                                  | 50  |

| 3.2          | Read operation                                                | 64  |

|              | 3.2.1 V <sub>SSM</sub> stability in dynamic mode of operation | 74  |

|              | 3.2.2 Read power consumption                                  | 79  |

| 3.3          | Write operation                                               | 81  |

|              | 3.3.1 Write Margin (WM)                                       | 88  |

|              | 3.3.2 Write power consumption                                 | 89  |

| 4: L         | _ayout Design                                                 | 90  |

|              | Layout extraction and Post-Layout Simulations (PLS)           |     |

| <b>5</b> : D | Discussions, Conclusions and future work                      | 96  |

| App          | pendices                                                      | 98  |

|              | 98                                                            |     |

|              | pendix B                                                      |     |

| Ref          | erence                                                        | 100 |

### **LIST OF FIGURES**

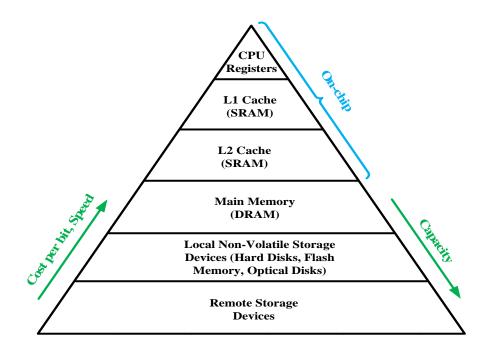

| Fig. | 1.1 Personal computer (PC) memory hierarchy                                                                                                                                                                          | 2        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

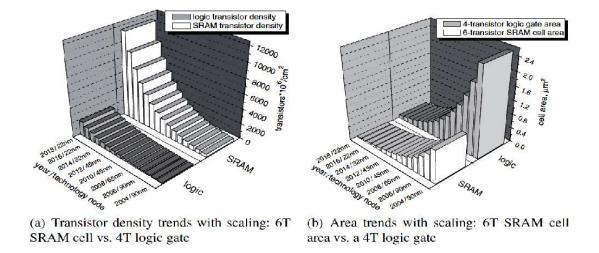

| Fig. | 1.2 Prediction of microprocessor technology density and area trends of 6T SRAM and 4T logic gates vs. year and technology node (Courtesy of [3]).                                                                    | 2        |

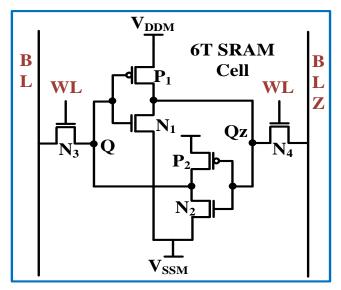

| Fig. | 1.3 A conventional 6T SRAM cell                                                                                                                                                                                      | 5        |

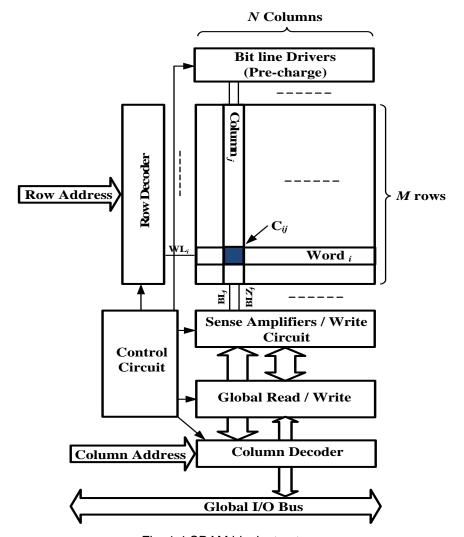

| Fig. | 1.4 SRAM block structure.                                                                                                                                                                                            | 6        |

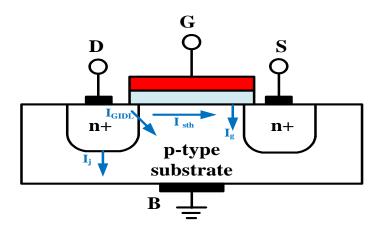

| Fig. | 1.5 Leakage current sources in an NMOS transistor.                                                                                                                                                                   | 11       |

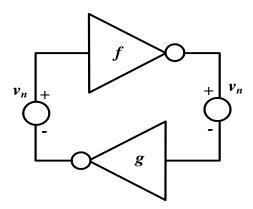

| Fig. | 1.6 Cross-coupled inverters with the presence of DC noise sources $v_n$                                                                                                                                              | 16       |

| Fig. | 1.7 Schematic of a 6T SRAM cell in read mode with two adverse polarity noise sources $(v_n)$ .                                                                                                                       | 17       |

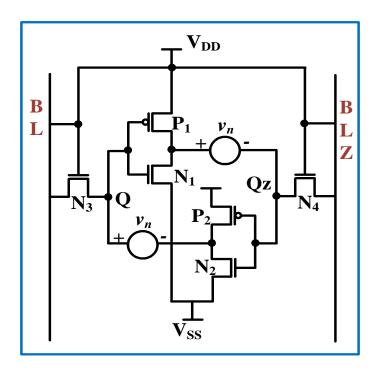

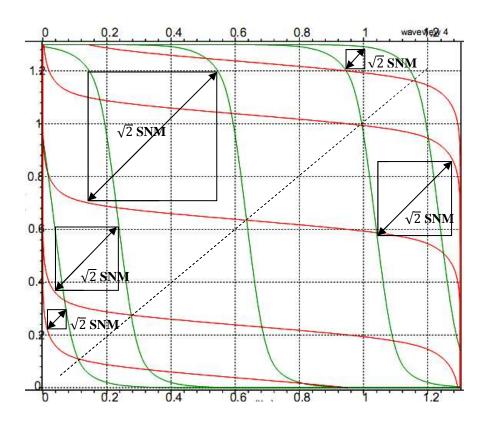

| Fig. | 1.8 SNM (Left) and RNM (Right) measurement technique using VTC curves of cross-coupled inverters <i>f</i> and <i>g</i> in standby and when accessed respectively                                                     | 18       |

| Fig. | 1.9 Butterfly diagrams of a conventional 6T SRAM cell showing the effect of the magnitude of the noise source, $v_n$ (0-400mV), on SNM and metastable point.                                                         | 19       |

| Fig. | 1.10 SNM estimation of conventional 6T SRAM, based on "maximum squares" in a 45° rotated coordinate system                                                                                                           | 21       |

| Fig. | 1.11 Circuit implementation of SNM measurement using rotated butterfly diagrams                                                                                                                                      | 23       |

| Fig. | 2.1 A conventional 6T SRAM cell                                                                                                                                                                                      | 27       |

| Fig. | 2.2 The butterfly diagrams of a conventional 6T cell in rotated coordinate system and the difference between two VTC curves (Bottom) showing the effect of mismatch in the $V_{th}$ of the PMOS device (load) on SNM | 28       |

| Fig. | 2.3 Effect of V <sub>th</sub> mismatch of the PMOS device on SNM in a conventional 6T cell (TT coner).                                                                                                               | 28       |

| Fig. | 2.4 A sense amplifier circuit used in read operation for a conventional 6T SRAM cell                                                                                                                                 | 31       |

| Fig. | 2.5 Read operation in a conventional 6T SRAM cell                                                                                                                                                                    | 31       |

| Fig. | 2.6 Butterfly diagrams of a conventional 6T cell in rotated coordinate system and the difference between the two VTC curves (top) showing the                                                                        | 24       |

| ⊏i~  | effect of mismatch in the threshold voltage of PMOS device on RNM                                                                                                                                                    | 34<br>34 |

| r (1 | Z Z EDECLOLENIUS INISTRAICH ON KINIVI                                                                                                                                                                                | 54       |

| Fig. 2.8 Original style butterfly diagrams showing the effect of P-type transistor<br>V <sub>th</sub> mismatch on RNM                                                                                  |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Fig. 2.9 SNM and RNM comparison and the effect of PMOS $V_{th}$ mismatch                                                                                                                               | 37      |

| Fig. 2.10 Family of butterfly diagrams (top) and the VTC difference function curves of a conventional 6T cell illustrating the effect of cell voltage variations on SNM.                               | 38      |

| Fig. 2.11 Family of butterfly diagrams and the VTC difference function curves (Bottom) of a conventional 6T cell illustrating the effect of cell voltage variations on RNM.                            |         |

| Fig. 2.12 Effect of cell voltage on SNM and RNM in a conventional 6T cell (V <sub>SSM</sub> =0V).                                                                                                      | 39      |

| Fig. 2.13 Simplified write circuits for 6T SRAMs (Bit-line pre-charge pull-up devices not shown)                                                                                                       | 41      |

| Fig. 2.14 Write operation in a conventional 6T SRAM cell                                                                                                                                               | 43      |

| Fig. 2.15 PMOS $V_{\text{th}}$ mismatch effect on write delay in the conventional 6T cell.                                                                                                             | 44      |

| Fig. 2.16 Effect of V <sub>DDM</sub> variation on write delay in the conventional 6T cell                                                                                                              | 44      |

| Fig. 2.17 Comparisons of write recovery period for single vs. differential $V_{DDM}$ methods at $V_{DD}$ =0.75V, $V_{DDM1}$ =0.60, $V_{DDM2}$ =0.85 (SS corner, 120°C).                                | 47      |

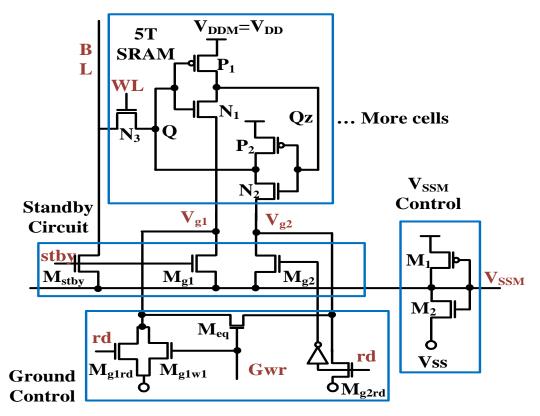

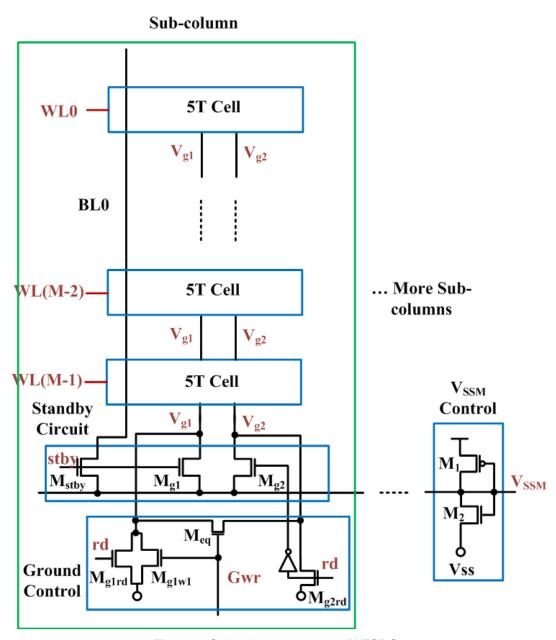

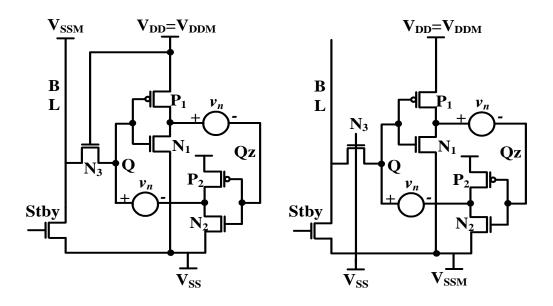

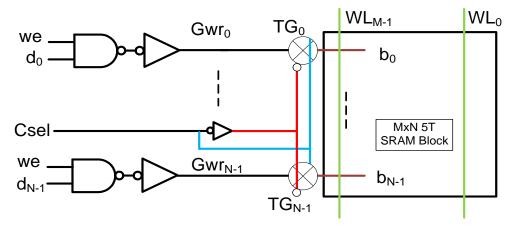

| Fig. 3.1 5TSDG structure with sub-column V <sub>SS</sub> control                                                                                                                                       | 50      |

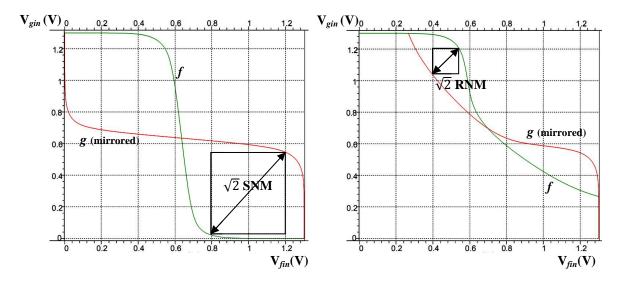

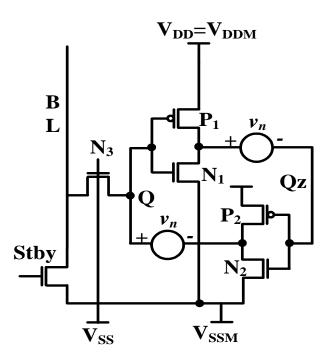

| Fig. 3.2 A 5T SRAM cell with two adverse polarity noise sources $v_n$                                                                                                                                  | 53      |

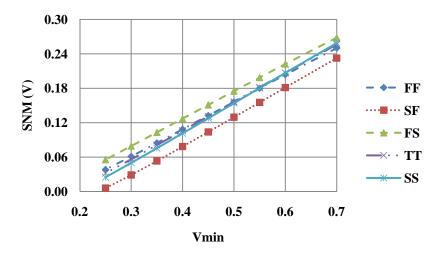

| Fig. 3.3 Relationship between Vmin=V <sub>DDM</sub> -V <sub>SSM</sub> and SNM of 5TSDG in various corners                                                                                              | 54      |

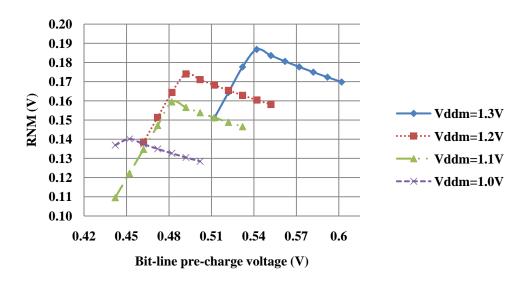

| Fig. 3.4 RNM variations vs. bit-line biasing (=V <sub>SSM</sub> ) - Supply voltage (Worst Care FS Corner)                                                                                              |         |

| Fig. 3.5 5TSDG cell: Storing a '0' (Left) and a '1' (Right)                                                                                                                                            | 55      |

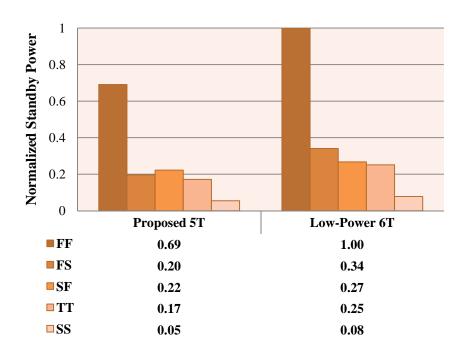

| Fig. 3.6 Normalized standby power consumption of various V <sub>th</sub> combinations in 5T cell.                                                                                                      | a<br>57 |

| Fig. 3.7 Effect of Temperature on V <sub>SSM</sub> with and without voltage regulation for different corners                                                                                           | 59      |

| Fig. 3.8 5TSDG vs. a low-power 6T cell comparison when storing a '0'                                                                                                                                   | 60      |

| Fig. 3.9 5TSDG vs. low-power 6T SRAM designs: (64Kb SRAM array and peripheral circuits, FF corner on the left, 120°C, 50% '0's 50% '1's stored in the array).                                          | 61      |

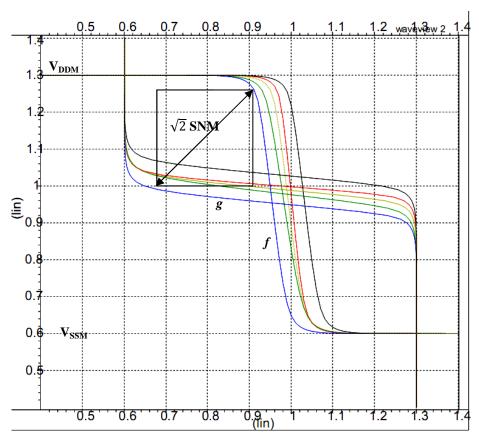

| Fig. 3.10. Butterfly diagrams for different corners for 5T SRAM in standby (SF, SS, TT, FF, FS corners from bottom up).                                                                                | 62      |

| Fig. 3.11 Sub-column structure of 5TSDG.                                                                                                                                                               | 63      |

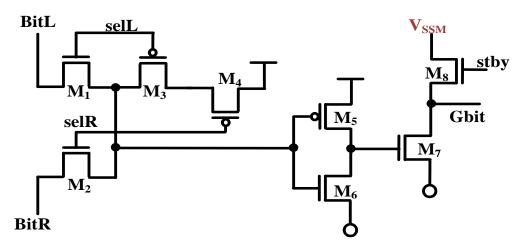

| Fig. 3.12 Sense amplifier used in 5TSDG read operation                                                                                                                                                 |         |

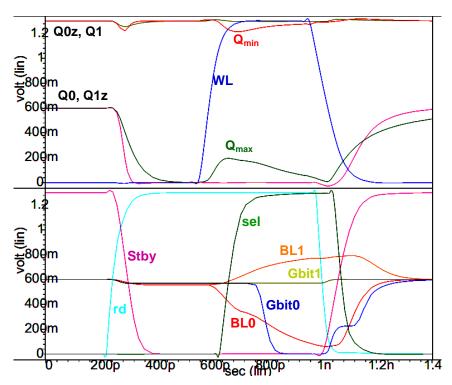

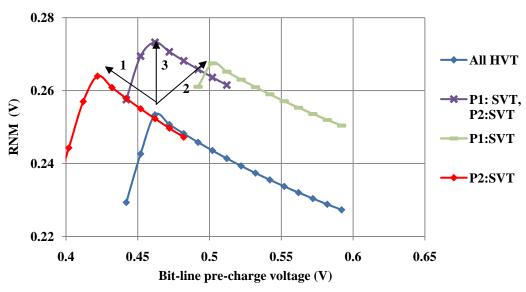

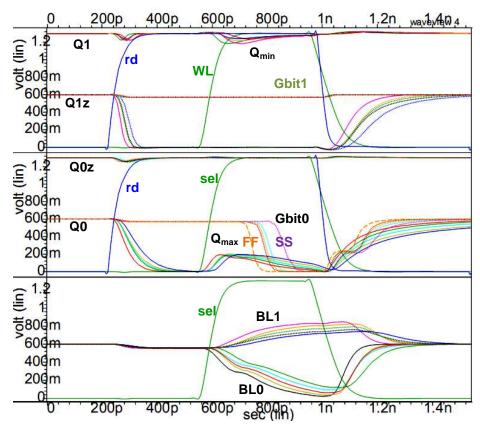

| Fig. 3.13 Read operation in a 5TSDG cell, typical corner (TT), 120°C, Q0-Q0z-BL0-Gbit0 and Q1-Q1z-BL1-Gbit1 are related to a cell storing a '0' a '1' respectively and sharing the same word-line (WL) |         |

| Fig. | 3.14 | Comparison between 51SDG when accessed (Left) with the cell in standby with the presence of the noise sources, $v_n$                                                                               | 67 |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

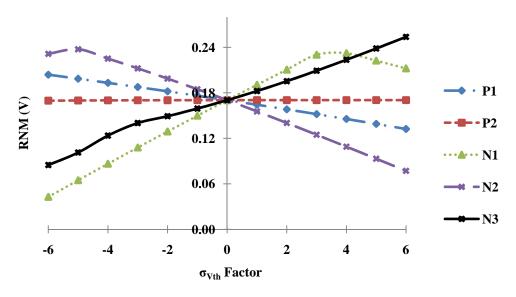

| Fig. | 3.15 | Effect of V <sub>th</sub> variations on RNM varying each single transistor in a 5T cell (Worst case: Relative to FS corner, 120°C)                                                                 |    |

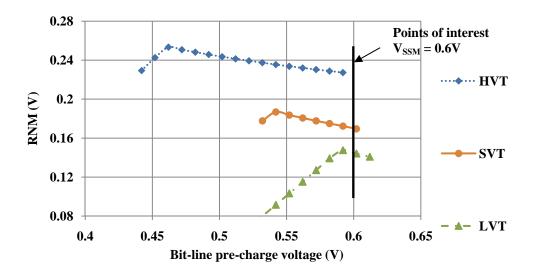

| Fig. | 3.16 | . RNM variations vs. bit-line biasing voltage (=V <sub>SSM</sub> ) for three threshold voltages of the access transistor (N <sub>3</sub> ) in FS corner                                            | 68 |

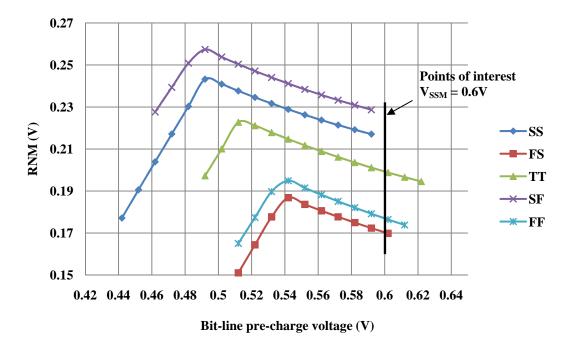

| Fig. | 3.17 | RNM variations vs. bit-line biasing (=V <sub>SSM</sub> ) for various corners in 5TSDG                                                                                                              | 69 |

| Fig. | 3.18 | Effect of the threshold of P <sub>2</sub> transistor on RNM. All transistors are HVT unless otherwise specified                                                                                    | 70 |

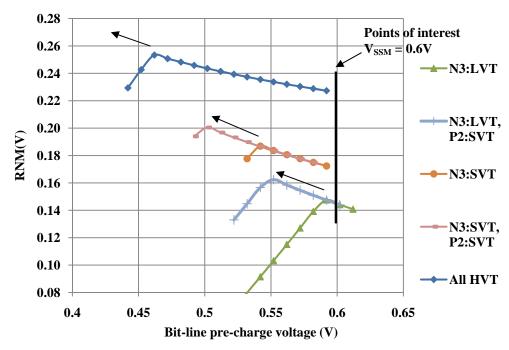

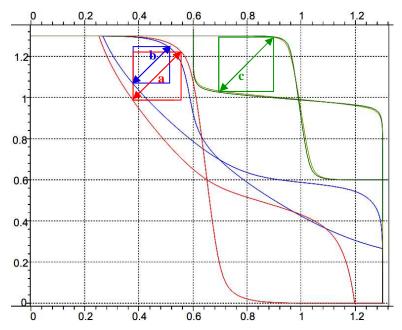

| Fig. | 3.19 | Effect of changing the threshold voltage of the load transistors (P <sub>1</sub> and P <sub>2</sub> ) on optimum RNM (All transistors are HVT unless otherwise specified.                          | 71 |

| Fig. | 3.20 | Read '0' and read '1' operations in 5TSDG in different corners (superimposed). BL0-Gbit0, and BL1-Gbit1 are the bit-lines and sense amplifier outputs for cells storing a '0' and '1' respectively | 72 |

| Fig. | 3.21 | Standard (Left) and rotated (Right) butterfly diagrams of 5TSDG when accessed (Read mode) in different corners                                                                                     | 73 |

| Fig. | 3.22 | Butterfly diagrams of 5TSDG and low-power 6T cells in read and standby modes: a: RNM <sub>5T</sub> , b: RNM <sub>6T</sub> , c: SNM <sub>5T</sub> ≈ SNM <sub>6T</sub>                               | 74 |

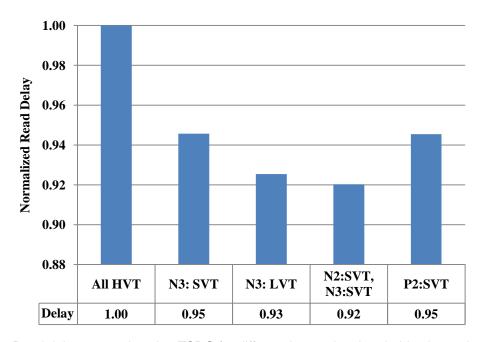

| Fig. | 3.23 | Read delay comparison in 5TSDG for different interesting threshold voltages in the cell (All transistors are assumed to be HVT unless otherwise specified)                                         | 74 |

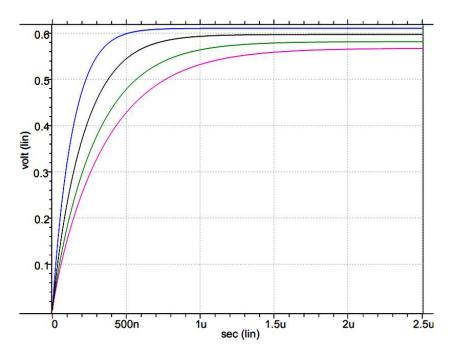

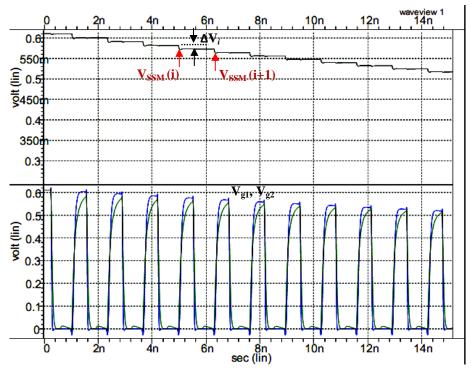

| Fig. | 3.24 | The response of V <sub>SSM</sub> when forced to '0' volts and left floating in standby for 64Kb, 128Kb, 256Kb, and 512Kb from left to right for 5T SRAM array (FF corner, 120°C)                   | 77 |

| Fig. | 3.25 | Worst case effect of read operation on V <sub>SSM</sub> (64Kb array 16 bits/word (all '0's), FF, 120°C).                                                                                           | 78 |

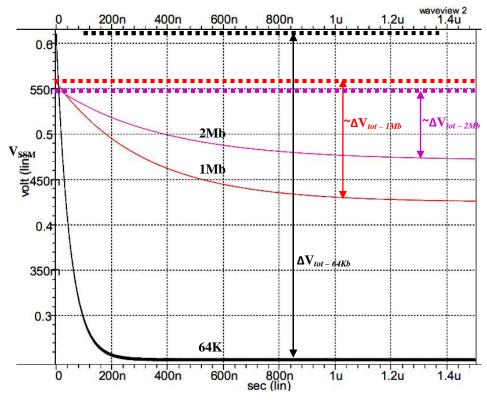

| Fig. | 3.26 | V <sub>SSM</sub> Saturation during several read operations for 64Kb, 1Mb and 2Mb 5T SRAM arrays (64 bits/word, FF, 120°C)                                                                          | 78 |

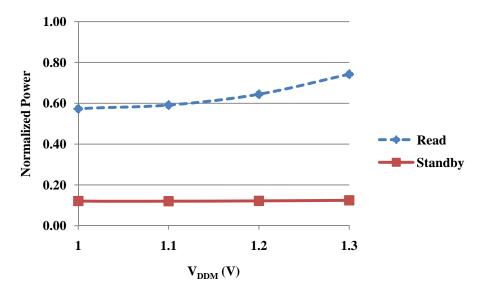

| Fig. | 3.27 | Comparison of normalized read and standby power vs. V <sub>DDM</sub> for 5TSDG, 64x16 bit block, reading 16 '0's continuously from 16-bit words (FF corner, 120°C)                                 | 80 |

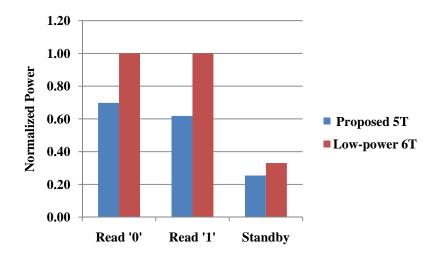

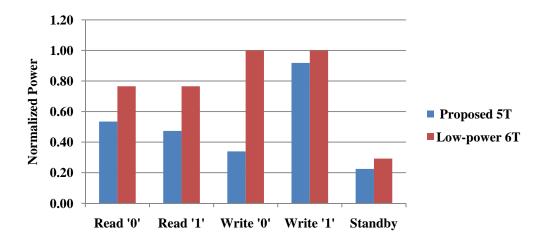

| Fig. | 3.28 | Case study results of the worst-case normalized power consumption for standby mode and read operation of 5TSDG in comparison with low-power 6T design (FF, 120°C), 1.00 ≈ 25.8 mW                  | 81 |

| Fig. | 3.29 | The write circuitry for 5TSDG (Not including the ground control circuit needed in write operation).                                                                                                | 84 |

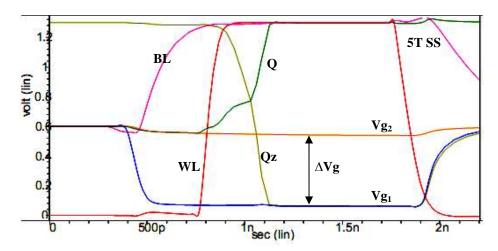

| Fig. | 3.30 | W1 operation of 5TSDG in slow corner (SS) (120°C)                                                                                                                                                  | 84 |

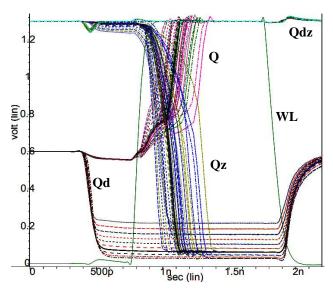

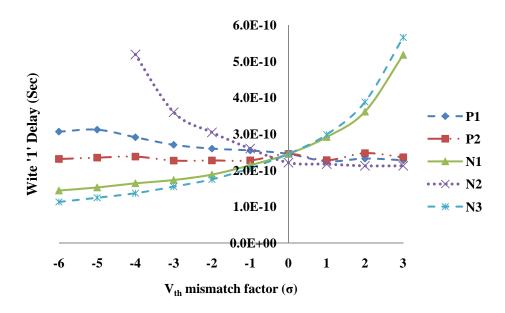

| Fig. | 3.31 | W1 operation and effect of various $V_{th}$ variations applied on each transistor at a time (-6 $\sigma$ to 4 $\sigma$ ) relative to SS corner in a writing and                                    |    |

|            | a disturbed cell (Q, Qz and Qd, Qdz), 120°C, Note that Qdz is not disturbed                                                                                                            | 85 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

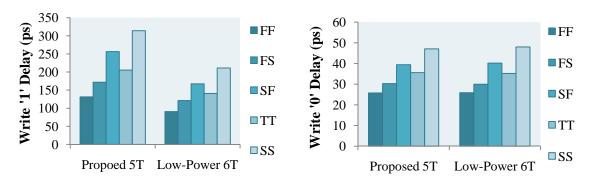

| Fig. 3.32  | Write '1' (left) and Write '0' (right) delay comparison in different corners between a 5TSDG and a low-power 6T cell (120°C).                                                          | 85 |

| Fig. 3.33  | Effect of Vth mismatch on write '1' delay in worst case corner (SS), $V_{g1}$ =0.07, $V_{g2}$ =0.47                                                                                    | 86 |

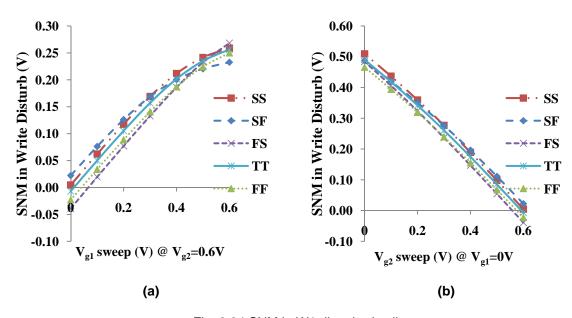

| Fig. 3.34  | SNM in W1 disturbed cells                                                                                                                                                              | 87 |

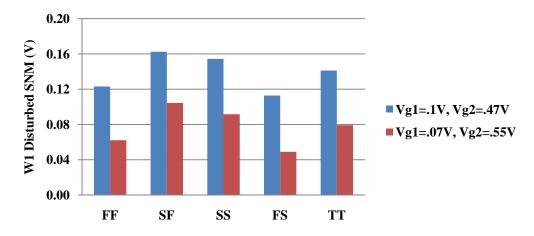

| Fig. 3.35  | The SNM of W1 disturbed cells in different corners and different $M_{\text{eq}}$ strengths.                                                                                            | 88 |

| Fig. 3.36  | Case study results of the worst-case write power consumption in comparison with read and standby power for 5TSDG vs. low-power 6T design (FF, $120^{\circ}$ C), $1.00 \approx 33.8$ mW | 89 |

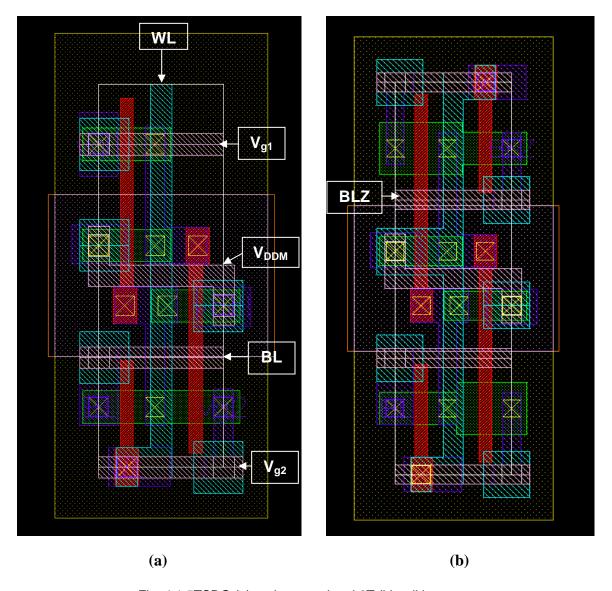

| Fig. 4.1 5 | STSDG (a) and conventional 6T (b) cell layouts                                                                                                                                         | 92 |

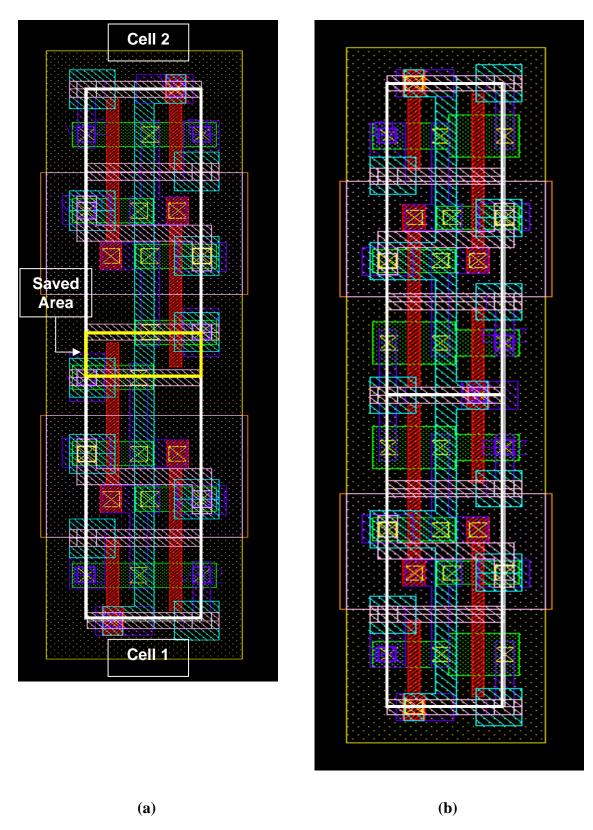

| Fig. 4.2 5 | STSDG (a) and conventional 6T (b) pair of cells sharing same word-line (WL), Total lengths and widths not to precise scale                                                             | 93 |

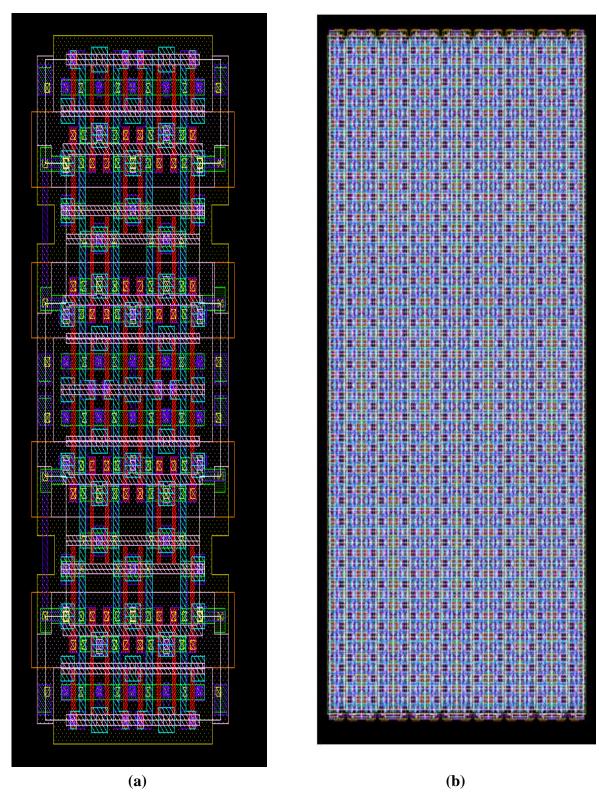

| Fig. 4.3 A | A 4x4 (a), and a 64x16 cell array of 5TSDG. Total lengths and widths not to precise scale                                                                                              | 94 |

|            |                                                                                                                                                                                        |    |

## **LIST OF TABLES**

| TABLE 2.1 Maximum vertical distance measurements of RNM using non-rotated butterfly diagrams.                                | 36 |

|------------------------------------------------------------------------------------------------------------------------------|----|

| TABLE 3.1. Different types of SRAM cells used in this chapter, $V_{DD}=V_{DDM}=1.3V$ ,                                       | 50 |

| TABLE 3.2. Transistor biasing voltages in standby for a cell storing a '0' (Q='0')                                           | 55 |

| TABLE 3.3 Transistor biasing voltages in standby for a cell storing a '1' (Q='1')                                            | 56 |

| TABLE 3.4. Worst-case standby leakage current and RNM comparison in different SRAM types (not including peripheral circuits) | 60 |

| TABLE 3.5 5TSDG: Trip point voltage vs. Q <sub>max</sub> and Q <sub>min</sub> , 120°C)                                       | 68 |

| TABLE 3.6. RNM and W1 comparison for different V <sub>th</sub> for N <sub>3</sub> , at worst case RNM (FS corner, 120°C).    | 83 |

#### **GLOSSARY**

BL Bit-line

BSIM Berkeley Short-channel IGFET Model

CMOS Complementary Metal Oxide Semiconductor (PMOS and NMOS)

CR (β) Cell Ratio

DRAM Dynamic Random Access Memory

DRV Data Retention Voltage

DIBL Drain Induced Barrier Lowering

GIDL Gate Induced Drain Leakage

Gwr Global Write

Gbit Global Bit-line (Global Read)

HVT High Threshold Voltage

I<sub>sth</sub> Sub-threshold Current

I<sub>g</sub> Gate Leakage Current

LER Line Edge Roughness

LG Gate Length

LVT Low Threshold Voltage

NBTI Negative Bias Temperature Instability

PBTI Positive Bias Temperature Instability

PC Personal Computer

RD Random Dopant

RNM Read Noise Margin

SNM Static Noise Margin

SPICE Simulation Program with Integrated Circuit Emphasis

SRAM Static Random Access Memory

SVT Standard Threshold Voltage

V<sub>DDM</sub> Positive Supply Voltage of Memory

V<sub>SSM</sub> Negative Supply Voltage of Memory

VTC Voltage Transfer Curve

V<sub>t</sub> Thermal Voltage

V<sub>th</sub> Threshold Voltage

WL Word-line

WM Write Margin

W1M Write '1' Margin

W0M Write '0' Margin

5T Five-Transistor

6T Six-Transistor

β<sub>p</sub> Load Ratio

σ<sub>N</sub> Number of standard deviations of the threshold voltage of N-type MOS

#### 1: INTRODUCTION

With the recent aggressive CMOS technology scaling, standby leakage power is increased nearly five times each technology generation while active power remains constant [7]. In addition, process variations and hence performance fluctuations are widely noticed in 65nm and beyond CMOS technologies [5]. Fig. 1.1 illustrates the memory hierarchy of a personal computer (PC). A significant part of today's microprocessor chips consists of SRAM cells and it is predicted to reach 90% of the chip area in some applications by 2013 [3][9]. Although not the most power and area efficient type, Static Random Access Memories (SRAMs) are attractive due to their higher reliability and performance compared to other types of memories. Thus, they are used extensively in processors as cache memories in different levels, and consequently account for a large amount of power consumption, and the chip area in most System on Chip (SoC) applications. Fig. 1.2 demonstrates a prediction of the transistor density in high volume microprocessors consisting of 6T SRAM cells and 4T logic gates and area trends with respect to year and technology nodes [3]. Therefore, SRAM density growth is much more rapid than the logic elements and hence, it shows the significance of development of new power and area reduction techniques for this type of memory. Leakage power reduction, especially in more advanced technologies, is particularly important in portable and battery-powered electronics such as cellular phones, PDAs,

wireless, and low-power biomedical devices since standby leakage power ultimately determines the battery life.

Fig. 1.1 Personal computer (PC) memory hierarchy.

Fig. 1.2 Prediction of microprocessor technology density and area trends of 6T SRAM and 4T logic gates vs. year and technology node (Courtesy of [3]).

Unlike other types of storage devices, such as DRAMs, where data needs to be refreshed due to the destructive nature of their operations, SRAMs have higher performance in the sense that the stored value needs to be written to the cell only once. Therefore, SRAMs are storage elements, which are suitable to high performance applications although they consume more power. 6T SRAM cells are typically used in high performance cache memories in microprocessors due to their symmetry in cell layout, high stability and reliability. Five-transistor (5T) SRAMs are attractive due to their advantage in area and power efficiency compared to 6T SRAMs due to one fewer transistor and a single bit-line [1][2][14][15]. Research in the past on this type of memory has been mostly focused on improving performance and stability while maintaining the promised area saving in a particular technology node. On the other hand, with continuous scaling down of CMOS transistors, new techniques have been developed in 6T SRAMs such as Dynamic Standby Mode [9][17], Data Retention Voltage (DRV) method [7], and well biasing, some of which are summarized in [7] and [9]. Therefore, in order to suppress leakage power consumption and combat performance fluctuations due to process variations, the previous research in 5T SRAMs such as [14] and [15], can no longer compete with current 6T SRAMs and that is why 6T SRAMs are still predominantly used in current systems.

In this thesis, an improved low-power design of a 5T SRAM cell featuring differential ground lines (5TSDG), and a novel biasing technique are introduced that will guarantee operation under all process variations and temperatures while taking benefit of area reduction. Also, this design has improved performance

compared to previous research results in [2][14][15]. Another 5T SRAM type known as the "Portless" memory, is introduced in [23] which appears to need larger PMOS and access transistors than 5TSDG.

Throughout this thesis, all simulation results have been obtained using ST 65nm CMOS models with BSIM4 and HSPICE. In the following sections of this chapter, some related background and previous research work is presented. In Chapter 2, operation of a 6T SRAM and simulation results addressing common issues are discussed. In Chapter 3, the proposed 5T SRAM (5TSDG) is introduced, and the results are compared with previous research in this area. In Chapter 4, layout design of 5TSDG structure is presented in comparison with the conventional 6T cell, and the area saving opportunity is illustrated. Finally, In Chapter 5, a summary of this research, potential future work, and conclusions are presented.

#### 1.1 SRAM block organization and structure

A typical SRAM cell is, like other types of storage devices, a device that is capable of holding a '0' or a '1', and is also capable of being written to and read from without causing disturbance in neighbouring cells or the destruction of its own stored data. Essentially, a 6T SRAM cell consists of a pair of cross-coupled inverters connected to two wires known, as true and complementary bit-lines (BL, BLZ), via two access transistors enabling the cell to communicate with outside when word-line (WL) is enabled as shown in Fig. 1.3. The operation of a 6T SRAM cell is discussed in detail in Chapter 2.

Fig. 1.3 A conventional 6T SRAM cell.

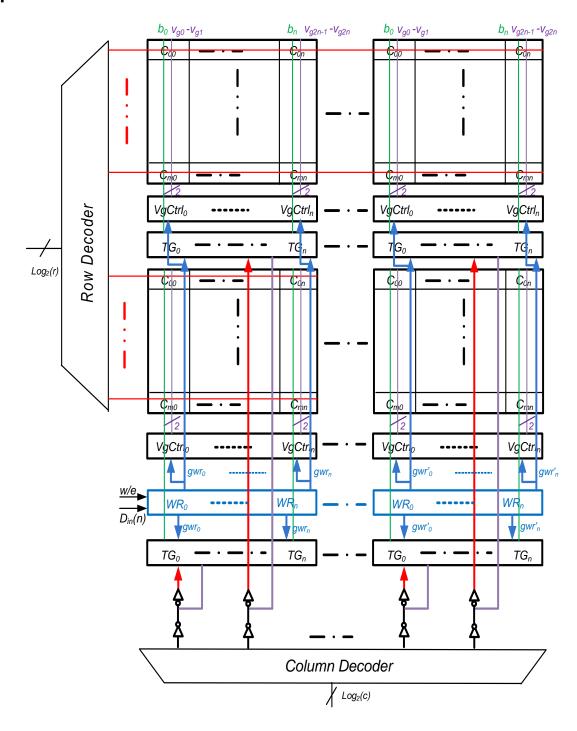

A simplified and popular 6T SRAM block structure is demonstrated in Fig. 1.4. A memory array is usually divided into blocks and sub-blocks, each including columns. Each column can be divided into two or more sub-columns. Row and column decoders can be staged with pre-decoders to optimize efficiency. In Fig. 1.4, an  $M \times N$  sub-block is shown with M rows and N columns. In this example, there are no sub-columns and thereby, the sense amplifier and write circuits are required one per column. In a case where more sub-columns are required (for power and performance requirements), a sub-column and its adjacent one can share a sense amplifier. The row and column decoders decode M rows and N columns given the row and column addresses. For example, if a cell in row i and column j is to be accessed ( $C_{ij}$ ), the row decoder will provide the word-line WL<sub>i</sub>, and the column decoder will provide the column address to the write and sense amplifier circuits as well as the input output bus (Global I/O). The column decoder allows sharing a sense amplifier between 2, 4 or more sub-columns.

The control circuitry generates the timing signals required to control the memory array.

Fig. 1.4 SRAM block structure.

#### 1.2 CMOS SRAM and technology scaling

A microprocessor chip mainly consists of cache memory and computing core(s). As shown in Fig. 1.1, SRAM cells are used as on-chip cache in different levels and are designed based on performance and power requirements. The demand for high-density SRAM structures continues to grow so rapidly that millions of SRAM cells, tightly packed beside each other, occupy most of the SoC

area. Hence, SRAMs will ultimately account for a major part of the chip cost and power consumption. Chip area efficiency, minimized to its design limits, low-power consumption, high performance, reliability in data storage, and a yield in ultra-large scales are the main objectives in any SoC. Therefore, it is essential to find a balance between cost, memory density, power consumption and performance depending on the design requirements. With increasing demand on these types of memories and growth of CMOS scaling, designers encounter complications and effects, such as leakage power and parameter mismatch, which were more or less negligible in previous generations. Technology scaling has the following major aspects:

- Scaling down of the transistor critical dimensions: Results in reduction

of the total chip area and power consumption, and improves the

performance due to reduction parasitics, and hence signal swing delay.

- Scaling the operation voltage: Results in lower static and dynamic power consumption, but may affect performance.

On the other hand, scaling transistor dimensions increases the design's susceptibility to random fluctuations in the transistor parameters, and therefore results in more challenges in manufacturing repeatability and reliability. In technology scaling, gate oxide thickness needs to be scaled to maintain effective gate control on the channel region. However, smaller gate oxide thickness will exponentially add to the leakage power [20]. Therefore, more accurate simulation models, such as BSIM v.4, are required for design purposes. Major types of process variations appear in the transistor's threshold voltage, V<sub>th</sub>, and mobility,

which will cause a mismatch in drive current. SRAMs are low-current, sensitive, and bi-stable devices in which performance and reliability can be affected by parameter mismatch.

The significance of the above issues is better recognized in high density and large-scale memory structures containing millions of storage cells.

#### 1.3 Threshold voltage variations and causes

Some of the major factors that cause threshold voltage mismatch and operation failure in neighbouring transistors specifically in an array of SRAM cells are summarized in [3][5][6][11] and are pointed out in the following:

- **Discrete Dopant (RD) effect:** Random fluctuations in the number of location of the dopant atoms in the channel,

- Variation of poly-silicon critical dimensions: gate length (Lg)

variations,

- Line Edge Roughness (LER): Caused by 1) limitation of the

resolution of lithography and 2) the grainy nature of photo resist and

poly gate. The effect of line width roughness is random and cannot be

corrected by optical proximity correction,

- Short channel effects (V<sub>th</sub> roll-off, Drain Induced Barrier Lowering (DIBL, see section 1.4),

- Gate dielectric material and thickness: Reduction in thickness

results in the reduction of the threshold voltage. Increase of thickness

will add to the probability of mismatch due to more surface potential perturbations.

The doping level of the channel needs to be increased to maintain a reasonable short-channel threshold voltage roll-off. As a result, the mobility of electrons and holes is decreased and the junction leakage, either from band-to-band tunnelling or from Gate-Induced Drain Leakage (GIDL), will be increased [11].

A comparison of threshold voltage variations in different technology nodes and transistor structures such as Poly gate with Oxide, Metal gate with high K dielectric, Omega FinFET, and Nanowire FinFet is reported in [11]. The comparison shows that in each transistor type, smaller dimensions will result in an increase in the  $V_{th}$  fluctuations and Nanowire FinFet has the smallest number of  $V_{th}$  variations among other types of transistors.

The standard deviation of the total threshold voltage variation,  $\sigma_{Vth-total}$ , can be modelled as the sum of variances of three major variation sources: Lg, LER and RD standard deviations,  $\sigma_{Vt-Lg}$ ,  $\sigma_{Vt-LER}$  and  $\sigma_{Vt-RD}$  respectively [11], as expressed in equation 1.1.

$$\sigma_{Vth-total}^{2} = \sigma_{Vth-Lg}^{2} + \sigma_{Vth-LER}^{2} + \sigma_{Vth-RD}^{2}$$

(1.1)

These V<sub>th</sub> variation components for a nominal gate length of 35nm were studied by [10]. For a gate length of larger than 35nm, the effect of fluctuations due to random doping dominates the other two sources [10].

A comparison between different gate oxide thicknesses and corresponding variations in V<sub>th</sub> is reported in [11]. The three sources of V<sub>th</sub> variations can be reduced with decreased gate dielectric thickness due to less surface potential perturbation under the enhanced gate controllability. The reduction in thickness can be achieved by using metal-gate and high-k dielectric for low standby power devices. However, this improvement will depend on timely implementation of reliable high-k gate dielectric, and well work-function modulated metal gate [11].

There are other limiting factors in scaling transistors than process variation and leakage that affect the stability, cell area and performance of the SRAM. For example, NBTI (Negative Bias Temperature Instability), is a limiting factor in the scaling of PMOS. At high negative bias and elevated temperature, the PMOS V<sub>th</sub> slowly shifts to become more negative and hence reducing PMOS current drive and affecting cell stability, margin, and minimum operating voltage of SRAM. This long-term V<sub>th</sub> drift and other gate oxide related V<sub>th</sub> degradation mechanisms must be accounted for over the life span of usage.

In addition, PBTI (Positive Bias Temperature Instability), is a limiting factor of NMOS scaling. With high-K gate materials, similar to NBTI  $V_{th}$  shift in NMOS also can occur [10].

#### 1.4 Leakage current sources

SRAM cells are storage devices arranged in a large array of cells in which they are mostly in standby mode, holding either a '0' or a '1', and few are actually

in an active read/write mode. Before analyzing leakage sources in an SRAM cell, leakage sources in a standard CMOS transistor are studied. Fig. 1.5 shows major sources of leakage current in typical CMOS transistors. In general, leakage is increased by temperature and higher differential voltage between two nodes. In SRAM cells, a mixture of active and leakage current sources constitute the total power consumption of the memory array. The magnitude of the leakage current is relatively increased as technology is scaled, and therefore, leakage current can no longer be neglected as it used to be in older generations of CMOS devices. On the other hand, technology scaling has helped reduce the cell differential V<sub>DD</sub>-V<sub>SS</sub>, one of the effective methods known to suppress leakage power. Unfortunately, this causes delay in digital logic design by reducing the gate drive [20]. A thorough analysis of leakage current sources is reported in [20] and is summarized in the following sections.

Fig. 1.5 Leakage current sources in an NMOS transistor.

Major sources of leakage in MOS devices are as follows:

#### 1.4.1 Reverse-biased junction leakage current (I<sub>i</sub>)

Also known as junction leakage, flows from the drain or source of a MOS device to the substrate. In an NMOS, the substrate is often tied to ground to reduce threshold voltage and hence optimize performance. Therefore, with increase of drain voltage, the reverse biased PN junction leakage is increased. This type of leakage depends on the drain area and doping concentration. In addition, it has a high temperature dependency and is generally negligible compared to other types of leakage.

#### 1.4.2 Gate induced drain leakage (I<sub>GIDL</sub>)

This type of leakage occurs due to the field effect in the drain junction and is highly dependent on the drain to substrate voltage  $V_{DB}$ , drain to gate voltage  $V_{DG}$ , and oxide thickness Tox. Higher  $V_{DB}$  and smaller Tox will increase GIDL with a fixed  $V_{DG}$ .

#### 1.4.3 Gate direct-tunnelling leakage (I<sub>a</sub>)

This type of leakage flows from gate to substrate through the direct tunnelling of electrons through a leaky insulating gate oxide. PMOS transistors have one order of magnitude smaller  $I_g$  compared to NMOS when using silicon dioxide in the gate. This type of leakage has an exponential relation with gate oxide thickness. Thicker oxide thickness will result in lower leakage current.

#### 1.4.4 Sub-threshold (weak inversion) leakage (I<sub>sth</sub>)

This type of leakage flows from drain to source of the transistor operating in weak inversion region. In addition, this is the dominant leakage source in

current CMOS technologies in comparison with other types of leaking currents. In more advanced technologies, I<sub>sth</sub> is noticed more widely since as the technology advances and transistor dimensions scale down, the threshold voltage of the transistor is also scaled. At lower threshold voltages I<sub>sth</sub> is increased. Equation 1.2 shows how I<sub>sth</sub> is calculated and how it is related to V<sub>th</sub> [20].

$$I_{sth} = \frac{W}{L} \mu v_t C_s e^{\frac{V_{GS} - V_{th} + \eta V_{DS}}{nv_t}} (1 - e^{\frac{-V_{DS}}{v_t}})$$

(1.2)

where, W and L denote the width and the length of the transistor,  $\mu$  denotes the carrier mobility,  $v_t$  is thermal voltage which is a function of temperature,  $C_s$  is the summation of depletion region capacitance and the interface trap capacitance per unit area of the gate,  $\eta$  is the DIBL coefficient, n is the slope shape factor and is a function of oxide thickness and  $C_s$ ,  $V_{th}$  is the threshold voltage of the MOS device. Therefore, reducing the oxide thickness which results in the reduction of  $V_{th}$ , will result in the sub-threshold current increasing exponentially.

In summary, the total leakage current of a CMOS transistor when it is OFF ( $V_{GS}$  = 0) will lack the gate leakage factor and can be expressed as

$$I_{lkg} = I_{sth} + I_i + I_{GIDL} ag{1.3}$$

The total leakage current  $I_{lkg}$  does not include gate tunnelling leakage current,  $I_g$ , since that current only occurs when the MOS device is in the "ON" mode of operation whereas  $I_{lkg}$  is only indicating the total leakage sources when the gate to source voltage (V<sub>GS</sub>) is zero.

#### 1.5 SRAM operation failure

SRAM operation failure (soft errors) can be categorized to the following types:

- Storage Hold (Standby) failure: It can occur when the stored data state is, *flipped*, during the memory standby state due to the existence of noise in the environment. Some of the sources of disturbances are caused by α particles, cross talk, and thermal noise [16].

- Read upset: Also known as destructive read, occurs when the stored data in a cell is corrupted when accessed, due to the bit-line current flow into the memory.

- Write operation failure: Unsuccessful attempt to store new data into the cell.

- Write disturb: Also known as destructive write, occurs in an attempt to write into a cell causing a neighbouring cell to change its state.

#### 1.6 Stability analysis

Cell stability is an important factor in SRAM design since it determines the sensitivity of the cell to process variations and operating conditions. Another important aspect in memory design is cell area since more than 75% of the total chip area is determined by the SRAM area. These two factors are correlated in the sense that increasing stability requires larger cells. The basic cross-coupled inverter pairs may seem deceptively simple in appearance; however, limited

success has been achieved to analytically model stability. Therefore, simulation methods are used in this thesis to measure and analyze stability margins.

A popular methodology to measure the stability and reliability of an SRAM cell in different operation modes is by measuring noise margins. "In general, Noise Margin (NM) is the maximum spurious signal that can be accepted by the device when used in a system while still maintaining the correct operation [3]." The noise margin of a cell in standby is called Static Noise Margin (SNM). In read mode, when the cell is accessed, the noise margin is known as Read Noise Margin (RNM). Methods to measure and calculate these stability parameters are explained in detail in the following sections.

#### 1.6.1 Static Noise Margin (SNM)

Static noise margin (SNM) indicates the maximum tolerance of an SRAM cell to perturbations and is measured using the voltage transfer curves (VTC) of the inverter pairs used in the SRAM cell, and drawing a curve known as *Butterfly diagram* discussed in section 1.6.3.

Fig. 1.6 shows the schematic of the cross-coupled inverters f and g used in the SRAM cell in standby (access transistors OFF) and two DC static noise sources. SNM is defined to be the maximum value of the noise sources ( $v_n$ ) that can be tolerated by the cell before initiating the state toggle. The presence of the two DC noise sources with opposite polarities applied to the input of each inverter will create a pessimistic disturbance condition for a cell in standby.

Fig. 1.6 Cross-coupled inverters with the presence of DC noise sources  $v_n$ .

SNM is reported to be reduced four times when transistors are scaled down from 250nm CMOS technology down to 50nm technology [3].

#### 1.6.2 Read Noise Margin (RNM)

Similar to SNM, RNM is measured by drawing and mirroring the VTC curves of the cross-coupled inverters. The difference is that since during read operation the access transistors conduct and are connected to pre-charged bitlines, in measuring RNM, the gates of the access transistors are clamped to V<sub>DD</sub> and the bit-lines are clamped to the biasing voltage (in this case also V<sub>DD</sub>) as shown in Fig. 1.7. Therefore, RNM indicates the tolerance of the cell to environmental perturbation or process variations when the cell is accessed.

Fig. 1.7 Schematic of a 6T SRAM cell in read mode with two adverse polarity noise sources  $(v_n)$ .

Fig. 1.7 is the schematic of a conventional 6T SRAM cell with added adverse static noise sources to the input of the inverters. The gates and the bit-line sides of the access transistors,  $N_3$  and  $N_4$ , are connected to  $V_{DD}$  to construct a worst-case read condition. For measuring the static noise margin, the two access transistors are removed from the circuit while keeping the noise sources similar to the read case.

#### 1.6.3 Butterfly diagrams

A butterfly diagram consists of the VTC curves of the two cross-coupled inverters in an SRAM cell. Fig. 1.8 depicts the graphical representation of the butterfly diagrams used to determine SNM and RNM of an SRAM cell with inverters *f* and *g*. Graphically, the diagonal length of the maximum square that can fit in each side of the butterfly diagram is defined to be the noise margin. This

curve has two steady state points at each end indicating the state of the cell storing either a '1' or a '0'. The midpoint of the butterfly diagram, where the two VTC curves cross each other is known as the meta-stable point. If the amount of disturbance reaches this point, small perturbations will cause the cell to either restore the disturbed cell to its original stored value through the feedback path or initiate the state toggle or the data corruption depending on the direction of the perturbation. The meta-stable point is a good estimation of the trip point, though trip point is usually measured using a different circuit structure. In summary, if a perturbation occurs in the cell, the feedback inverter will restore the value to the steady state points as long as the perturbation is not larger than the trip point of the cell. If larger, the cell is flipped to read the opposite steady state point on the other side of the butterfly diagram.

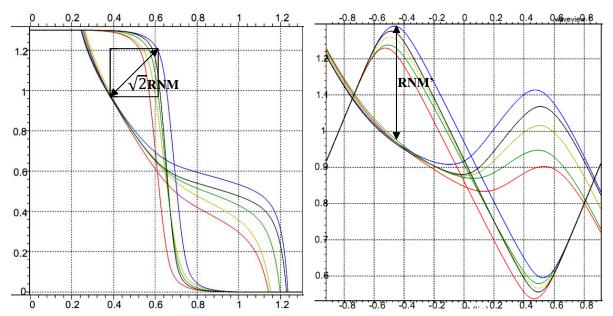

Fig. 1.8 SNM (Left) and RNM (Right) measurement technique using VTC curves of cross-coupled inverters *f* and *g* in standby and when accessed respectively.

The meta-stable point is shifted as the noise source increases in magnitude. With higher amount of the noise disturbance, SNM is decreased, meaning that the probability of data corruption in standby is increased.

This decay in the stability margin during read can affect the reliability of the data storage significantly meaning that once a bit is stored in a cell, it is more vulnerable to change its state after small perturbations in the system environment. Using carefully sized transistors can limit this decay in RNM.

Fig. 1.9 Butterfly diagrams of a conventional 6T SRAM cell showing the effect of the magnitude of the noise source,  $v_n$  (0-400mV), on SNM and meta-stable point.

#### 1.6.4 Static noise margin measurement using SPICE

A typical method to measure SNM or RNM is by first drawing and mirroring the VTC curves. The length of the diagonal of the maximum square fitting in each side of the butterfly diagram is graphically determined. Then the

minimum value of these two is selected to represent SNM for worst-case scenario. However, this method requires numerical work post-circuit analysis. In addition, many designers rely on visual graphical observations.

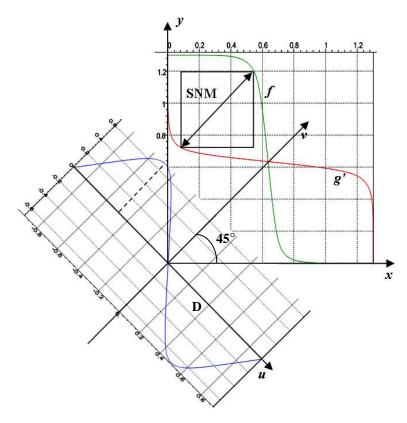

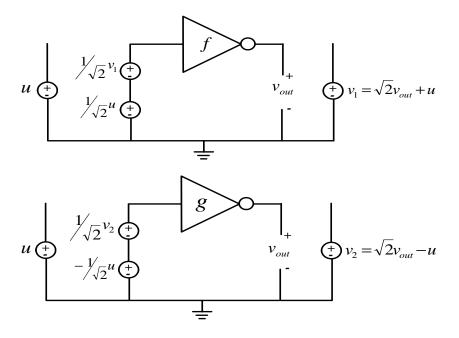

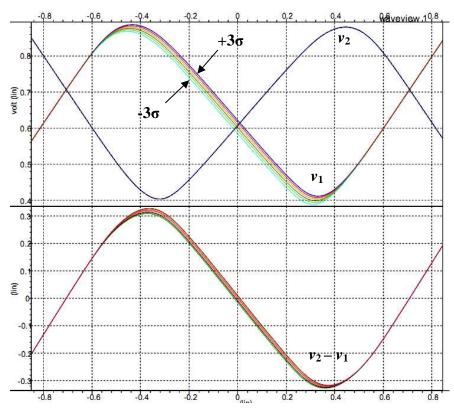

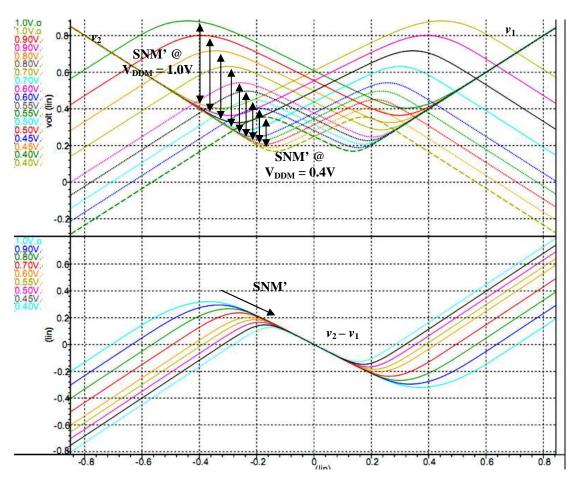

A method proposed by [16] is an alternative and "easy to use" technique in estimating SNM using Spice circuit simulations. The idea is to rotate the butterfly diagram by 45 degrees so that the diagonal of the squares appears to be vertical in the new coordinate system to facilitate measurements. Given that the original coordinate system in which VTC curves are drawn in a typical way has x and y coordinates, the new coordinate system will have y and y coordinates.

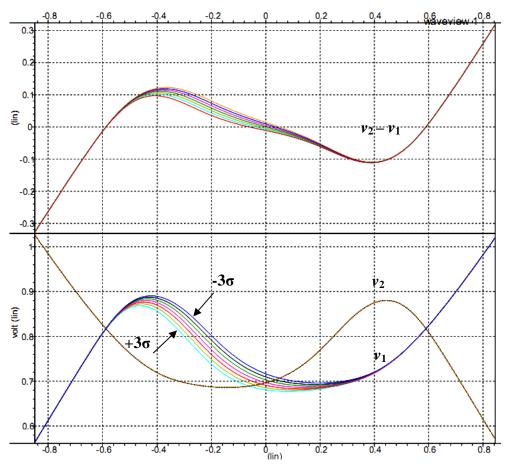

As shown in Fig. 1.10, *f* and *g* are the voltage characteristic curves of the cross-coupled inverters in the SRAM cell. *g'* is the mirrored version of *g*. Curve D is the difference between the two curves in the new 45 degree rotated coordinate system. The peaks of the difference curve are where in the original curve, the SNM values are maximized. By comparing the absolute values of peaks and choosing the minimum, RNM or SNM is calculated depending on the purpose.

Fig. 1.10 SNM estimation of conventional 6T SRAM, based on "maximum squares" in a 45° rotated coordinate system.

In order to transform (x,y) coordinate to (u,v), the 45 degree rotated system is defined as:

$$x = \frac{1}{\sqrt{2}}u + \frac{1}{\sqrt{2}}v\tag{1.4}$$

$$y = -\frac{1}{\sqrt{2}}u + \frac{1}{\sqrt{2}}v \tag{1.5}$$

There are two inverter characteristic curves:

$$y_1 = f(x) \text{ and } y_2 = g(x)$$

(1.6)

Substituting equation 1.4 and 1.5 in 1.6 we get:

$$-\frac{1}{\sqrt{2}}u + \frac{1}{\sqrt{2}}v_1 = f(\frac{1}{\sqrt{2}}u + \frac{1}{\sqrt{2}}v_1)$$

$$v_1 = u + \sqrt{2}f(\frac{1}{\sqrt{2}}u + \frac{1}{\sqrt{2}}v_1)$$

Similarly, g'(x) can be transformed into the (u, v) coordinate system by first applying the inverse function operation on  $F_2(x)$  to calculate  $F'_2(x)$  and second by applying the rotation operation.

$$y_2 = g(x)$$

$$x = g'(y_2)$$

$$v_2 = -u + \sqrt{2}g(-\frac{1}{\sqrt{2}}u + \frac{1}{\sqrt{2}}v_2)$$

The circuit implementation of this method, which can be simulated using SPICE models, is discussed in further detail in [16] and is used in this thesis to measure and compare stability margins for both 6T and 5TSDG designs.

Comparison results are illustrated in detail in Chapter 3. The schematic of the stability measurement circuit is depicted in Fig. 1.11.

Fig. 1.11 Circuit implementation of SNM measurement using rotated butterfly diagrams.

The absolute values of the maximum and minimum are the values of the diagonals of the maximum squares. Finally, multiplying the smaller of the two by  $1/\sqrt{2}$  will result in the SNM of the SRAM cell as shown in equation 1.7.

$$NM = \frac{1}{\sqrt{2}} \cdot \min \begin{cases} \max(|v_1(u) - v_2(u)|, & -\frac{1}{\sqrt{2}} < u < 0 \\ \max(|v_1(u) - v_2(u)|, & 0 < u < +\frac{1}{\sqrt{2}} \end{cases}$$

(1.7)

where  $v_1$  and  $v_2$  are the characteristic curves of the inverters and u is the sweeping DC voltage used to obtain  $v_1$  and  $v_2$ .

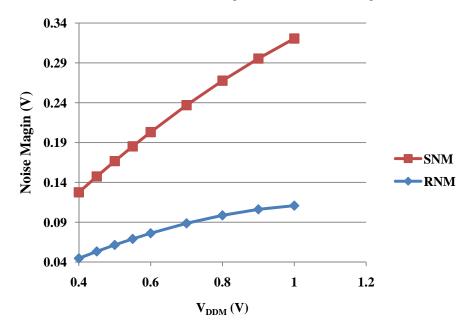

### 1.7 Read noise margin and supply voltages

One of the important design factors in SRAM design is sensitivity to voltage scaling. As discussed earlier, more advanced technologies will enable standard digital IC designers to lower the supply voltage to reduce power consumption, and limit the voltage swing period, but of course with performance

penalties. An analysis on the effect of supply voltages on SNM and RNM in a conventional 6T SRAM is reported in [8]. The authors show the relationship between SNM of a 6T SRAM cell when accessed (RNM), cell supply voltage and bit-line pre-charge voltage. Higher cell voltages will cause more stability in the cell since the current drive of the storage inverters is increased due to higher differentials making it harder for the noise to take over the cell voltage and flip the cell value. On the other hand, higher bit-line pre-charge voltages will reduce the noise margin since a higher read upset voltage is induced during read due to higher current flow from the bit-line through the cell. On the other hand, lowering bit-line voltage below the trip point will also disturb the read operation by either flipping the cell (writing a '0' on the cell node storing a '1') or cause a false trigger on the sense amplifier. Therefore, the amount of charge stored on the bit-lines, which is directly related to the pre-charge voltage and bit-line wire length, must be limited by the designer. When the pre-charge voltage of the bit-line reaches a certain biasing level (near the cell supply voltage), [8] shows that RNM is saturated.

### 1.8 Technology corners and static noise margin in SRAM

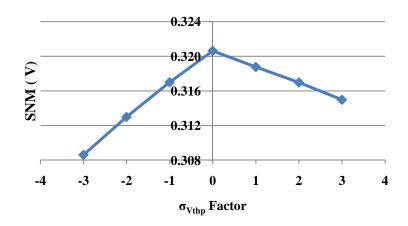

In a conventional 6T SRAM design, yield is directly related to SNM distribution. If  $\mu$  is the mean and  $\sigma$  is the variance of the SNM distribution in a memory block, it is reported that,  $\mu$ -6 $\sigma$  of SNM is required to exceed 0.04×V<sub>DD</sub> to reach a 90% yield on 1MB SRAM. Transistor mismatch and parameter variations result in increased variations in threshold voltages. This will lead to a reduction in  $\mu$ -6 $\sigma$  and increases the number of unstable SRAM cells which affects SRAM

yield. Typically, this translates into a requirement that minimum SNM, be greater than 20% of a typical SNM [3].

In [3], the authors report that in all corners, the symmetry point is mostly at 0% deviation from  $\mu$ . In other words, the most stable case is when there is no mismatch in  $V_{th}$ . The effect of  $V_{th}$  variation is increased in devices with lower threshold voltages. In the following a summary of the mismatch effect on SNM is given for each transistor (see Fig. 1.7 for transistor names and schematic):

**Driver transistors (N<sub>1</sub>, N<sub>2</sub>):** Seem to have the largest effect on the butterfly diagram and hence, the SNM due to their larger W/L ratio compared to other transistors in the SRAM cell.

Access Transistors ( $N_3$ ,  $N_4$ ): As  $V_{th}$  decreases in the access transistor, a strong negative impact is observed on the RNM. In an experiment by [3], the measurements were taken in a worst-case read-accessed SRAM cell. Thus, the access transistors were effectively connected in parallel with the load transistors. Thus, reducing the  $V_{th}$  of the access transistor compromises the low level stored in the cell, which in turn reduces the RNM.

Load transistors (P<sub>1</sub> and P<sub>2</sub>): Seem to have the least impact on the SNM due to its weaker current drive and typically smaller W/L ratio.

In Chapter 2, the design and operation of a conventional SRAM is presented in further detail.

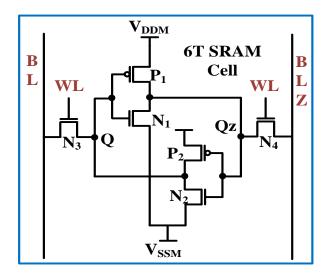

#### 2: 6T SRAM OPERATION

In this chapter, the design and operation of a conventional six-transistor (6T) SRAM is presented in various modes of operation. A conventional 6T cell consists of two cross-coupled inverters (P<sub>1</sub>-N<sub>1</sub>, P<sub>2</sub>-N<sub>2</sub>) connected to two bit-lines (BL, BLZ) through access transistors (N<sub>3</sub>, N<sub>4</sub>) as shown in Fig. 2.1. The word-line (WL) is used to access the cell during read or write. Therefore, the operations of a 6T SRAM cell can be categorized into standby mode, read, and write operations which will be explained in this chapter. In more advanced and lowpower 6T designs, the positive and negative supply voltage, V<sub>DDM</sub> and V<sub>SSM</sub>, can be controlled by additional circuitry to limit the cell differential especially in standby mode to save power consumption. This procedure is also known as sleep mode method (see [20]) both in memory and digital logic design when the device is in standby. The transistors constituting the 6T cell are ratioed and depending on performance, area and power requirements, length and width parameters can be adjusted. Use of high threshold MOS devices is also another technique to reduce power with performance penalties. There are two important ratios in designing a conventional 6T cell denoted by cell ratio, β, and load ratio,  $\beta_p$ , in this thesis. In Fig. 2.1,  $P_1$  and  $P_2$  are also known as load transistors and  $N_1$ and N<sub>2</sub> are known as driver, and N<sub>3</sub> and N<sub>4</sub> are called access transistors. The cell and load ratios are defined by

$$\beta = \frac{{{{W_{N_2}}/{L_{N_2}}}}}{{{{W_{N_3}}/{L_{N_3}}}}} = \frac{{{{W_{N_4}}/{L_{N_4}}}}}{{{{W_{N_4}}/{L_{N_4}}}}} \text{ and } \beta_p = \frac{{{{W_{N_2}}/{L_{N_2}}}}}{{{{{W_{P_2}}/{L_{P_2}}}}}} = \frac{{{{W_{N_4}}/{L_{N_4}}}}}{{{{{W_{P_1}}/{L_{P_1}}}}}}$$

where W and L denote the width and length of the MOS devices in Fig. 2.1.

Fig. 2.1 A conventional 6T SRAM cell.

#### 2.1 Standby mode

The two cross-coupled inverters will construct a true and a complementary storage node, Q and Qz, to store either a '0' or a '1' into the cell. These inverters play the role of a closed loop feedback system that can cancel the effect of perturbations to a degree, depending on the stability of cell, restoring the disturbed data to the original value.

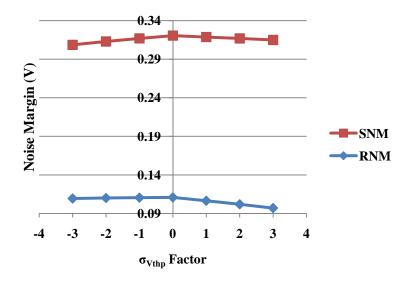

As shown in Fig. 2.2, it can be observed that the SNM value will reach its highest when there is no mismatch in the PMOS threshold voltage i.e.  $\sigma_{Vthp} = 0$ . Also the higher the  $V_{th}$  variations on the PMOS in a 6T cell, the lower the value for SNM. As shown in Fig. 2.3, there is a symmetry across standard deviation

factor  $\sigma_{Vthp}$  = 0. The larger the  $\sigma_{Vthp}$  value, the threshold voltage for the mismatch PMOS will increase making it harder to turn on and work well as a pull up transistor and thereby reducing the SNM.

Fig. 2.2 The butterfly diagrams of a conventional 6T cell in rotated coordinate system and the difference between two VTC curves (Bottom) showing the effect of mismatch in the  $V_{th}$  of the PMOS device (load) on SNM.

Fig. 2.3 Effect of V<sub>th</sub> mismatch of the PMOS device on SNM in a conventional 6T cell (TT coner).

#### 2.2 Read operation

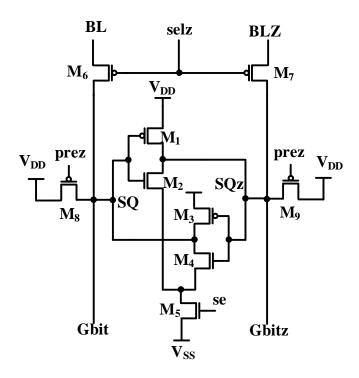

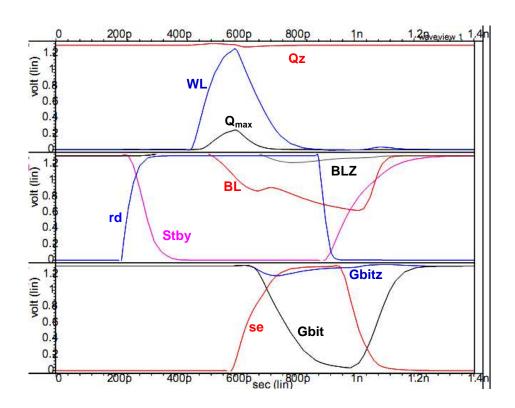

In read operation, the bit-lines are first pre-charged high to V<sub>DD</sub> and left floating. Since the bit-lines are shared with other cells in the same sub-column (see Fig. 1.4), they are capacitive elements consisting of mostly wire and junction capacitors. The schematic of a simple sense amplifier used in this thesis for the read operation of the 6T SRAM cell is depicted in Fig. 2.4. In a case when a '0' is stored in the cell (Q=V<sub>SSM</sub>, QZ=V<sub>DDM</sub>), when the word-line, WL, is raised, the true bit-line (BL) is pulled down to V<sub>SSM</sub> via N<sub>2</sub> while the complementary bit-line (BLZ) remains floating at the pre-charged value (V<sub>DD</sub>) as shown in Fig. 2.5 (see also [3]). The sense amplifier can be designed to function with small differentials between BL and BLZ. Therefore, in order to increase performance and reduce the dynamic power consumption, the bit-line swing in read does not have to be from pre-charge voltage all the way down to V<sub>SSM</sub> (see Fig. 2.5). The two PMOS devices connected to BL and BLZ (M<sub>6</sub> and M<sub>7</sub>) are to isolate the sense amplifier from the bit-lines when the sub-column is not selected for read. With the presence of two cross-coupled inverter pairs, M<sub>1</sub>-M<sub>2</sub> and M<sub>3</sub>-M<sub>4</sub>, this sense amplifier operates in a similar way as a memory cell does without the access transistors. M<sub>5</sub> is connected to the source nodes of the inverter pairs to disconnect them from V<sub>SS</sub> in standby for pre-charge purposes. Small voltage differentials between BL and BLZ when column is selected i.e. select signal is active (sel), and the sense enable pulse (se) will cause the inverter pairs to turn on and drive the sense amplifier outputs Gbit and Gbitz to full rail voltages. M<sub>8</sub>

and  $M_9$  are pre-charge devices to pre-charge and let Gbit and Gbitz float prior to read, and are enabled by *prez* pulses. Generally, design parameters characterizing a sense amplifier are defined by

- The amplitude of the differential input signal

- The minimum detectable signal

- The gain  $(G = \frac{V_{out}}{V_{in}})$

- The tolerance against environmental disturbance and mismatches

- Sense delay which can be measured in different ways such as from when the word-line reaches 50%  $V_{DD}$  to when sense output (global bit-line) reaches 50%  $V_{DDM}$ .

The gain of the sense amplifier is a function of the bit-line pre-charge voltage. The sense delay is partly related to the SRAM cell ratio ( $\beta$ ), and can be adjusted depending on the power and delay requirements. Larger  $\beta$  values will reduce read delays up to a saturation point, and will also add to the power consumption and the chip area.

Fig. 2.4 A sense amplifier circuit used in read operation for a conventional 6T SRAM cell.

Fig. 2.5 Read operation in a conventional 6T SRAM cell.

Due to the capacitive nature of the bit-line, the current flow from either BL or BLZ through  $N_1$  or  $N_2$  during read when the word-line is raised, will cause a temporary rise on the '0' node of a 6T cell noted as  $Q_{max}$  shown in Fig. 2.5. Once the word-line is raised, the drain to source voltage  $(V_{DS})$  of  $N_2$  is 0V since a '0' is stored into the cell, and hence,  $N_2$  is weakly ON. The cell node Q has a capacitance of  $C_Q$  which will be charged by the current flow from the bit-line, and once charged, the  $V_{DS}$  of  $N_2$  will no longer be 0V, which then will turn  $N_2$  on more strongly and thereby the charges on  $C_Q$  will be drained to  $V_{SS}$ . The amount of charges flown from BL to Q is dependent on the capacitance of the bit-line,  $C_{bit}$  and the cell ratio,  $\beta$ .

The length of the bit-lines, which is determined by the number of cells shared on the same wire, determines the bit-line capacitance, and consequently influences the value of  $Q_{max}$  along with  $\beta$ . The value of  $Q_{max}$  during read has a direct effect on read-stability since if  $Q_{max}$  is larger than the trip point of the inverter pairs, the read operation will turn into a write and hence the stored data is corrupted. Furthermore, read performance is also affected by longer bit-lines since it will take longer for the bit-lines to be pulled down by the driver transistor ( $N_1$  or  $N_2$ ) in the cell depending on the stored value. Therefore, in conventional 6T cells, cell ratio ( $\beta$ ) is designed based on the length of the bit-lines to maintain stability, and improve performance. Smaller bit-line segments will result in less power consumption during read but require more peripheral circuits and hence more area is needed. Therefore, a designer should find a reasonable balance between required read performance, area and power. In addition, cell  $\beta$  plays an

important role in read-stability meaning that larger values of  $\beta$  will cause  $Q_{max}$  to be reduced since the driver transistor ( $N_1$  or  $N_2$ ), driving the '0' side of the cell, is turned on more strongly during read.

Mismatch in the threshold voltage of a cell can result in a cell to become more susceptible to data corruption. As shown in Fig. 2.6, it is observed that the RNM value will reach its highest when there is no mismatch in the PMOS threshold voltage factor i.e.  $\sigma_{Vthp} = 0$ . In addition,  $V_{thp}$  variations on the PMOS in a 6T cell will result in lower values for RNM. It can be easily observed that there is a symmetry across  $\sigma_{Vthp} = 0$ . Larger  $\sigma_{Vthp}$  values translate into increase of threshold voltage making the transistor harder to turn on and hence reducing the RNM. Another phenomenon to observe is that the static noise margin value is nearly twice as much the RNM margin when compared. This reduction is due to the fact that the cell is much more vulnerable to state loss when it is being accessed than when it is in the standby mode. When the cell is being accessed, the two access transistors are on and one of the bit-lines is pulled down by one of the NMOS devices of the cross-coupled inverter pairs (N<sub>1</sub> or N<sub>2</sub>). If the current flowing in the channel of  $N_3$  or  $N_4$  is higher than  $N_1$  or  $N_2$  respectively, the read operation will cause a read upset turning a read into initiating a state toggle.

Fig. 2.6 Butterfly diagrams of a conventional 6T cell in rotated coordinate system and the difference between the two VTC curves (top) showing the effect of mismatch in the threshold voltage of PMOS device on RNM.

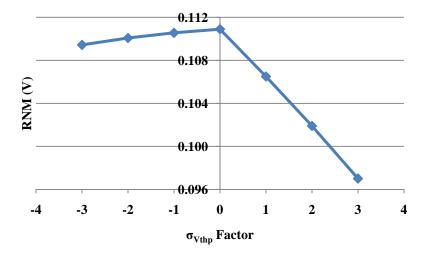

Fig. 2.7 Effect of PMOS mismatch on RNM.

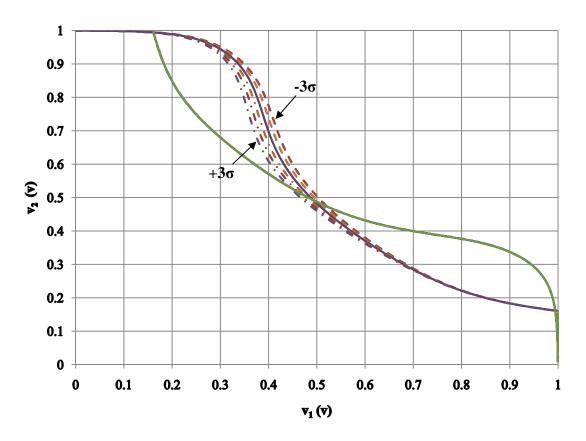

# 2.3 Effect of PMOS mismatch on RNM using non-rotated original butterfly diagrams

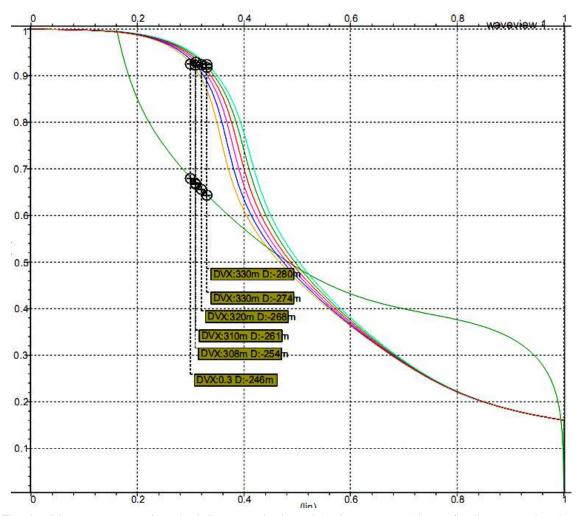

In order to verify the simulation results from the rotated coordinate system method, another experiment was run using regular VTC curves. Fig. 2.8 depicts the original 6T SRAM butterfly diagram consisting of the two VTC curves of the inverters. Comparing these curves with the rotated ones in Fig. 2.6, it is observed that the results are consistent numerically. The central solid line belongs to  $\sigma_{Vthp}$  = 0. Graphically observing this figure, the larger the  $\sigma_{Vthp}$  value gets numerically, the diagonal length of the biggest square in each side will become smaller.

Fig. 2.8 Original style butterfly diagrams showing the effect of P-type transistor  $V_{th}$  mismatch on RNM.

It might be an interesting question to investigate how vertical measurements between the standard VTC curves translate into SNM. Fig A.1 depicts the non-rotated butterfly family of curves with maximum vertical distance measurements. The disadvantage of the vertical measurement is that the maximum distance never switches to the other side of the curve since it is not diagonal. These graphs are illustrated just to compare the results with the rotated versions explained earlier. The maximum vertical measurements are shown in TABLE 2.1.

TABLE 2.1 Maximum vertical distance measurements of RNM using non-rotated butterfly diagrams.

| σ factor              | -3  | -2  | -1  | 0   | 1   | 2   | 3   |

|-----------------------|-----|-----|-----|-----|-----|-----|-----|

| Vertical Distance(mV) | 280 | 280 | 274 | 268 | 261 | 254 | 246 |

Finally, Fig. 2.9 depicts a comparison between the SNM and RNM measured from rotated curves proposed by [16]. SNM values are about two times larger than RNM. Therefore, a design must be tolerant to environmental disturbances to achieve reasonable RNM values, which will hence result in acceptable SNM values accordingly.

Fig. 2.9 SNM and RNM comparison and the effect of PMOS V<sub>th</sub> mismatch.

## 2.4 Effect of the cell differential voltage on SNM and RNM of a conventional 6T SRAM cell

The voltage differential across the memory cell has a significant importance in the determination of its noise margins. Smaller differentials will result in the inverter transistors turning on weaker and therefore becoming less effective to in tolerating environmental disturbances. Fig. 2.10 and Fig. 2.11 depict simulations results for various cell differential voltages and the effects on SNM and RNM respectively. These results show that higher cell voltage will increase the noise margin by making the VTC curves capable of fitting larger squares. The difference function shown at the bottom of these two figures shows how the peak difference is shifted and lowered as the cell voltage is changed. It is important to note that since the structure of the conventional 6T SRAM is symmetrical in terms of the transistor's sizes and their threshold voltages, the butterfly diagrams in both standby and read modes are also symmetrical across the meta-stable point (see Fig. 2.10 and Fig. 2.11).

Fig. 2.10 Family of butterfly diagrams (top) and the VTC difference function curves of a conventional 6T cell illustrating the effect of cell voltage variations on SNM.

Fig. 2.11 Family of butterfly diagrams and the VTC difference function curves (Bottom) of a conventional 6T cell illustrating the effect of cell voltage variations on RNM.

Fig. 2.12 Effect of cell voltage on SNM and RNM in a conventional 6T cell (V<sub>SSM</sub>=0V).

#### 2.5 Write operation

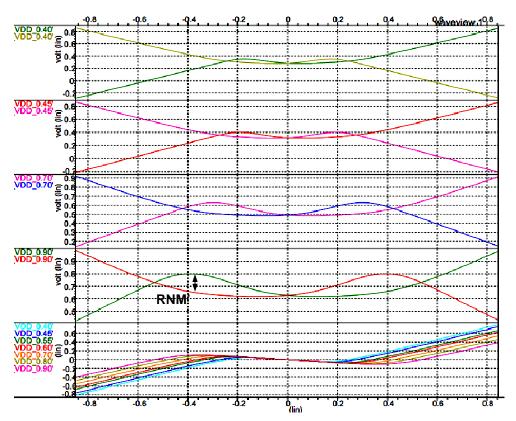

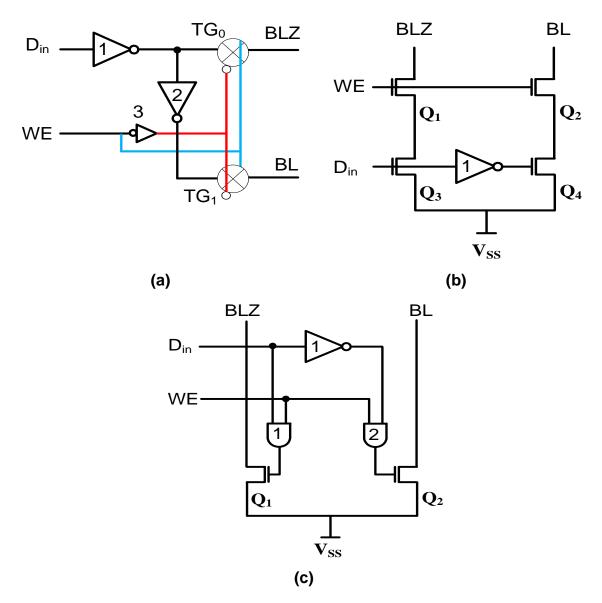

In write operation, whether writing a '0' (W0) or writing a '1' (W1), the bitlines are pre-charged high similar to read. The write circuit drives the global write signals, and is connected to the bit-line through transmission gates (activated by TG\_ON) or pass transistors (see Fig. 2.13). Therefore, in a write operation BL or BLZ is pulled down depending on whether data is a '0' or a '1' respectively. In case of W1, assuming that the cell is storing a '0' (Q=0, Qz=1), when the wordline is raised, since BLZ is driven low by the write driver, Qz is pulled down and hence P<sub>2</sub> starts to turn on. When P<sub>2</sub> is turned on, it pulls Q high to V<sub>DDM</sub> causing N<sub>1</sub> to turn on and pull Qz down to V<sub>SSM</sub>. The performance of the write operation, also known as write-ability, is highly dependent on the cell ratio β. In this example, P<sub>1</sub> opposes the attempt to pull QZ down since it is turned on. On the other hand one can not write a '1' by pulling BL high due to the read stability requirement as explained in the read section. Therefore, the load transistors (P<sub>1</sub> and P<sub>2</sub>) must be weaker than the access transistors (N<sub>3</sub> and N<sub>4</sub>) and are usually designed to have minimum size.

Fig. 2.13 Simplified write circuits for 6T SRAMs (Bit-line pre-charge pull-up devices not shown).

Three typical types of write drivers for a 6T SRAM column are shown in Fig. 2.13 (see also [3]). The purpose of a write driver is to discharge one of the bit-lines (BL or BLZ) depending on the data status when the write enable is active (WE). The circuit in (a) writes into a cell by pulling down BL or BLZ driven by inverters 1 and 2 and via transmission gates TG<sub>0</sub> and TG<sub>1</sub> depending on data value (D<sub>in</sub>). Inverter 3 is used to drive WE and its complement to activate the

transmission gates. Write circuit in (b) uses  $Q_1$ - $Q_3$  and  $Q_2$ - $Q_4$  NMOS devices to discharge BL or BLZ. Inverter 1 is used to drive the complement value of data to drive BL's gate. If  $D_{in}$  is a '0', inverter 1 will turn  $Q_4$  on and once WE is active, it will pull BL to  $V_{SS}$  resulting a write '0' operation. On the other hand, if  $D_{in}$  is a '1', it will turn on  $Q_3$  and once WE is active, BLZ is pulled down via  $Q_1$  and  $Q_3$  resulting a '0' to be written onto  $Q_2$  of the cell and activating write recovery process to store a '1' into the cell. In (c) the two AND gates 1 and 2 will prepare gate voltage for two pass transistors  $Q_1$  and  $Q_2$  depending on  $D_{in}$  and WE status. Inverter 1 drives AND gate 2 such that if  $D_{in}$  is '0', and WE is active, BL is driven low. The strength of the driver circuit is dependent on the capacitance of the bit-lines and power vs. performance requirements. Fig. 2.14 shows the write operation in a conventional 6T cell where, TG\_ON is the signal that turns on the transmission gate in Fig. 2.13 (a), Gwr and Gwrz are the global write signals connected to the bit-lines via the transmission gates, and WE is the write enabler.

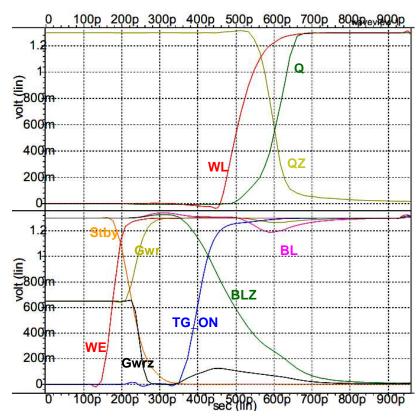

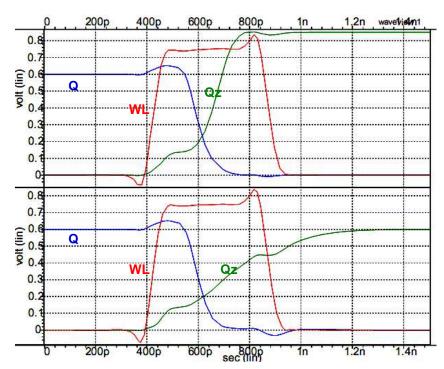

Fig. 2.14 Write operation in a conventional 6T SRAM cell.

# 2.6 Threshold voltage variation of the PMOS device on write delay

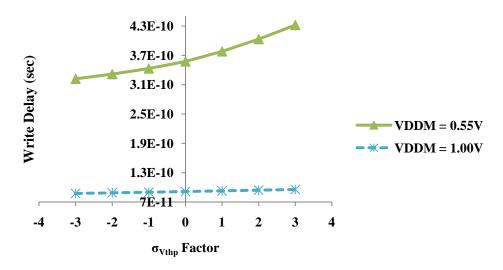

The effect of threshold voltage variation on PMOS devices is interesting since they determine the write recovery performance and are weakest devices in a 6T SRAM cell. In addition, the current drive in PMOS devices is lower than that of NMOS due to having lower carrier mobility in these devices. In an experiment asserting threshold voltage mismatch between PMOS devices in a conventional 6T cell, the write recovery delay was measured from WL=50%  $V_{DDM}$  voltage to QZ =80%  $V_{DDM}$  (see Fig. 2.15). Simulation results show that higher values in the standard deviation factor for the threshold voltage in the PMOS device ( $\sigma_{Vthp}$ ), will make it harder for the PMOS (in this case  $P_2$  raising QZ) to turn on during write

recovery process and hence adding to the delay. This effect is exponentially more severe in lower  $V_{\text{DDM}}$  voltages as shown in Fig. 2.15 and Fig. 2.16.

Fig. 2.15 PMOS V<sub>th</sub> mismatch effect on write delay in the conventional 6T cell.

#### 2.7 Effect of V<sub>DDM</sub> variations on write and write recovery delay

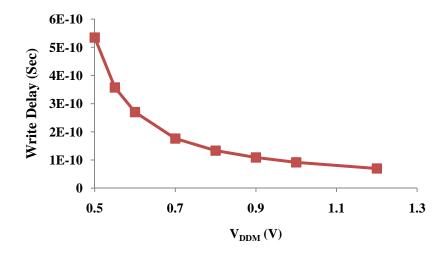

In some low-power applications, it is required to reduce cell differential voltage for power saving purposes. This reduction of voltage has an inverse relationship with write delay shown in Fig. 2.16.

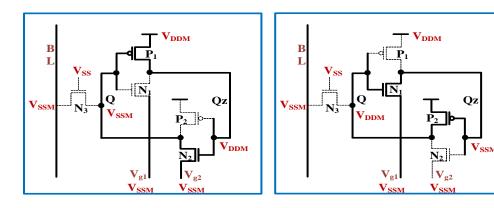

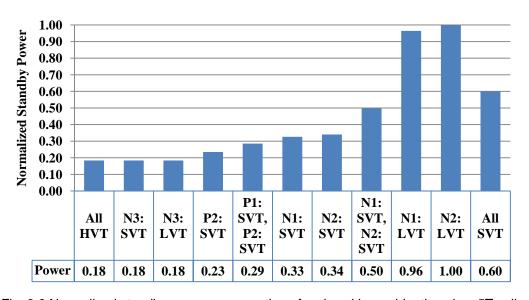

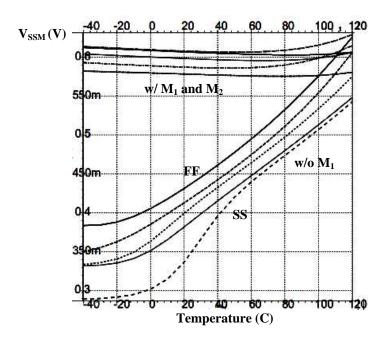

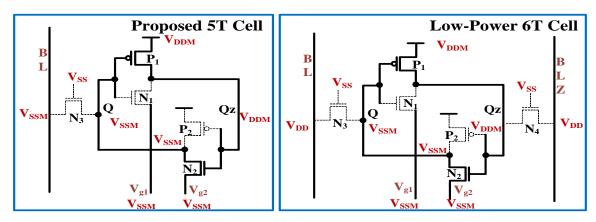

Fig. 2.16 Effect of V<sub>DDM</sub> variation on write delay in the conventional 6T cell.