# ABSTRACT

| Title of dissertation:    | Studying the Impact of Multicore<br>Processor Scaling on Cache Coherence<br>Directories via Reuse Distance Analysis |

|---------------------------|---------------------------------------------------------------------------------------------------------------------|

|                           | Minshu Zhao, Doctor of Philosophy, 2015                                                                             |

| Dissertation directed by: | Professor Donald Yeung<br>Department of Electrical and Computer Engineering                                         |

Directories are one key part of a processor's cache coherence hardware, and constitute one of the main bottlenecks in multicore processor scaling, *e.g.* core count and cache size scaling. Many research effects have tried to improve the scalability of the directory, but most of them only simulate a few architecture configurations. It is important to study the directory's architecture dependency, as the CPUs continue to scale. This is because besides applications, directory behaviors are also highly sensitive to architecture. Varying *core count* directly affect s the amount of sharing in the directory, and varying the *data cache hierarchy* affects the directory access stream. But unfortunately, exploring the huge design space of multiple core counts and cache configurations is challenging using traditional architectural simulation due to the slow speed of simulations.

This thesis studies the directory using multicore reuse distance analysis. It extends existing multicore reuse distance techniques, developing a method to extract directory access information from the parallel LRU stacks used to acquire privatestack reuse distance profiles. This thesis implements this method in a PIN-based profiler to study the directory behavior, including the directory access pattern and directory content, and to analyze current directory techniques.

The profile results show that the directory accesses are highly dependent on cache size, exhibiting a 3.5x drop when scaling the data cache size from 16KB to 1MB; the sharing causes the ratio of directory entry to cache blocks to drop below 50%; and the majority of the accesses are to a small percentage of the directory entries. Cache simulations are performed to validate the profiling results, showing the profiled results are within 14.5% of simulation on average. This thesis also analyzes different directory techniques using the insights from the profiler. The case studies on the Cuckoo, DGD, SCD techniques and multi-level directories show that required directory size varies significantly with CPU scaling, the opportunity of compressing private data decreases with cache scaling, reducing the sharer list size is an effective technique and a small L1 directory is sufficient to capture most of the latency critical accesses respectively.

# Studying the Impact of Multicore Processor Scaling on Cache Coherence Directories via Reuse Distance Analysis

by

Minshu Zhao

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2015

Advisory Committee: Professor Donald Yeung, Chair/Advisor Professor Manoj Franklin Professor Bruce Jacob Professor Ankur Srivastava Professor Alan Sussman © Copyright by Minshu Zhao 2015

# Dedication

To my parents, who have been always there for me.

# Acknowledgments

First, I would like to thank my advisor, Dr. Donald Yeung, for his patience, encouragement and immense knowledge. His advice and guidance helped me all the way from taking courses through writing this thesis. He made the last six years a rewarding journey.

My thanks also goes to the members of my committee, Dr. Franklin, Dr. Jacob, Dr. Srivastava and Dr. Sussman, for their insightful comments, hard questions and extreme patience.

I also would like to thank my fellow students in the lab, Meng-Ju Wu, Inseok Choi, Michael Badamo and Jeff Casarona for their support, feedback, suggestions and friendship. In particular, I am grateful to Dr. Meng-Ju Wu, who laid the foundation for this work, enlightened me the direction of research and gave me many insightful discussions.

Finally, I would like to thank my parents, Yunyi Zhao and Chao Zhu, who encouraged me to pursue Ph.D. study in the first place and supported me all the way through my study emotionally.

# Table of Contents

| Li | st of '     | Tables                        | vi  |

|----|-------------|-------------------------------|-----|

| Li | st of l     | Figures                       | vii |

| 1  | Intro       | oduction                      | 1   |

| 2  | Bacl        | kground on Directory          | 9   |

|    | 2.1         | Cache Coherence and Directory | 9   |

|    |             |                               | 11  |

|    |             |                               | 14  |

|    |             |                               | 15  |

|    |             | 1                             | 17  |

|    |             | 1                             | 18  |

|    |             | ±                             | 18  |

|    | 2.2         |                               | 19  |

| 0  | <b>D</b> 1  |                               | ~ 4 |

| 3  |             |                               | 24  |

|    | 3.1         |                               | 24  |

|    | 3.2         |                               | 28  |

|    |             |                               | 28  |

|    |             |                               | 29  |

|    | 3.3         | Cache Sharing Behavior        | 31  |

|    | 3.4         | Core Count Scaling Behavior   | 33  |

| 4  | Ana         | lysis Framework               | 35  |

|    | 4.1         |                               | 35  |

|    | 4.2         | J.                            | 38  |

|    | ±• <b>=</b> |                               | 44  |

|    | 4.3         |                               | 44  |

|    | 4.4         |                               | 45  |

|    |             |                               |     |

| 5  | Directory Cache Profiler                   | 48   |

|----|--------------------------------------------|------|

|    | 5.1 Profiler Process Flowchart             | . 48 |

|    | 5.2 Profiler Implementation                | . 50 |

|    | 5.2.1 LRU Stacks                           | . 50 |

|    | 5.2.2 Counters                             | . 51 |

| 6  | Profile Studies and Results                | 55   |

|    | 6.1 Experimental Setup                     | . 55 |

|    | 6.2 Study 1: Directory Access Frequency    |      |

|    | 6.2.1 Cache Size Scaling                   |      |

|    | 6.2.2 Core Count Scaling                   |      |

|    | 6.3 Study 2: Directory Coverage            |      |

|    | 6.3.1 Cache Size Scaling                   |      |

|    | 6.3.2 Core Count Scaling                   |      |

|    | 6.4 Study 3: Directory Access Distribution |      |

|    | 6.4.1 Cache Size Scaling                   | . 75 |

|    | 6.4.2 Core Count Scaling                   |      |

| 7  | Cache Simulations and Validations          | 85   |

| •  | 7.1 Experimental Setup                     |      |

|    | 7.2 Study 1: Directory Access Frequency    |      |

|    | 7.3 Study 2: Directory Coverage            |      |

|    | 7.4 Study 3: Directory Access Distribution |      |

| 8  | Case Studies and Discussions               | 98   |

| Ū. | 8.1 Cuckoo Technique Discussion            |      |

|    | 8.1.1 Experimental Setup                   |      |

|    | 8.1.2 Experiment results                   |      |

|    | 8.2 DGD Technique Discussion               |      |

|    | 8.2.1 Experimental Setup                   |      |

|    | 8.2.2 Experiment results                   |      |

|    | 8.3 SCD Technique Discussion               |      |

|    | 8.3.1 Experimental Setup                   |      |

|    | 8.3.2 Experimental Results                 |      |

|    | 8.4 Multi-Level Technique Discussion       |      |

|    | 8.4.1 Experimental Setup                   |      |

|    | 8.4.2 Private Cache Results                |      |

|    | 8.4.3 Shared Cache Impact                  |      |

|    | 8.5 Directory Access Frequency Discussion  |      |

| 9  | Conclusion                                 | 124  |

| Bi | bliography                                 | 126  |

| ום | onographi                                  | 140  |

# List of Tables

| 2.1 | Access mode, cache hit or miss, cache block state, directory access<br>and comments for MESI protocol                  | 16  |

|-----|------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Access mode, PRD, $PRD_{remote}$ and sharer count characterization of data cache transactions and T1–T3 categorization | 42  |

| 6.1 | Parallel benchmarks used in the evaluations                                                                            | 56  |

| 6.2 | Cache-miss APKI at 3 private cache sizes, sharing-induced APKI,                                                        |     |

|     | and APKI for 16- and 256-core CPUs.                                                                                    | 58  |

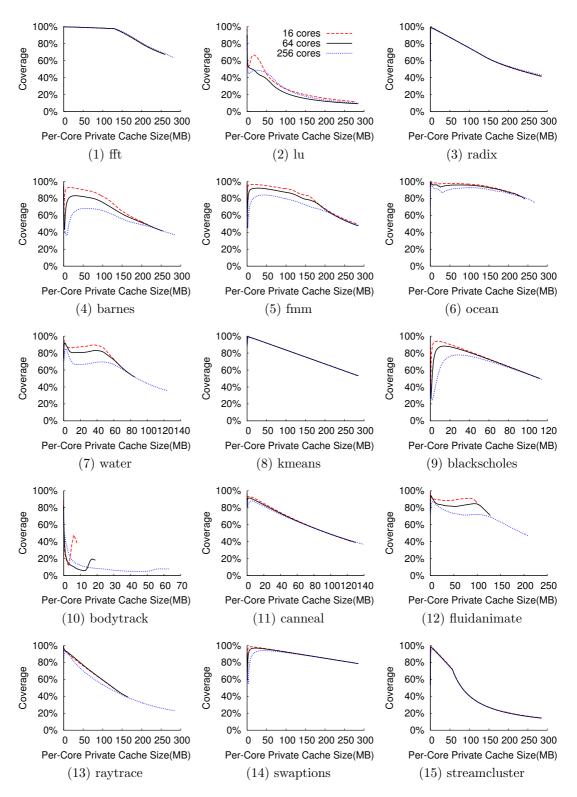

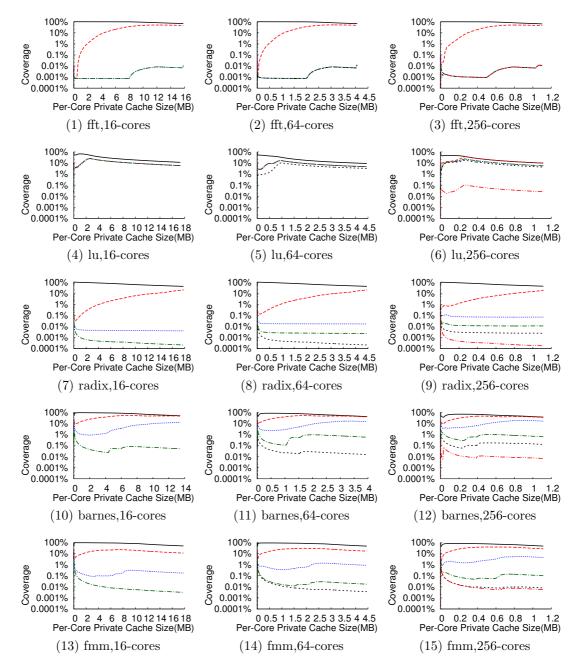

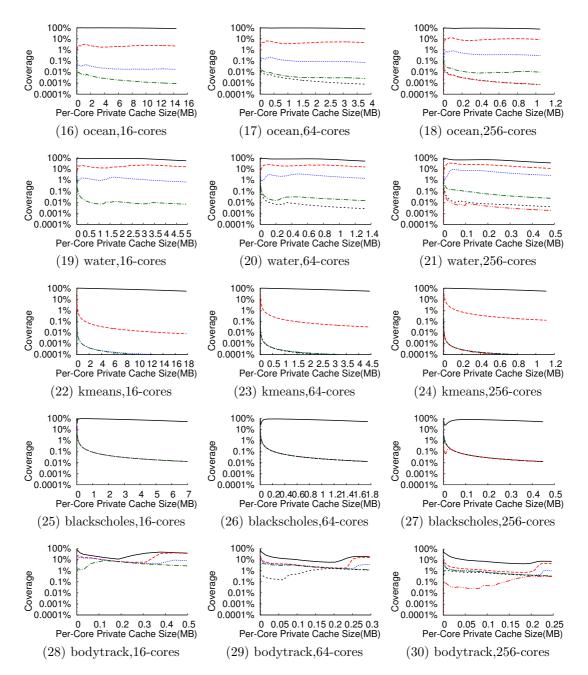

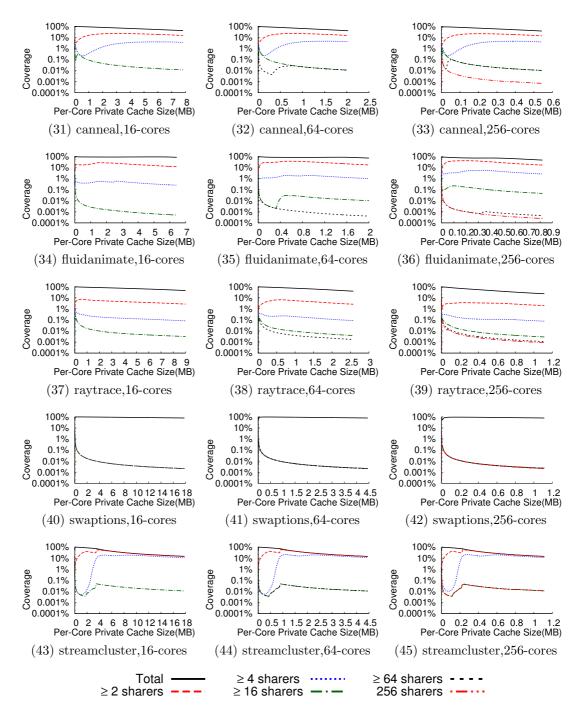

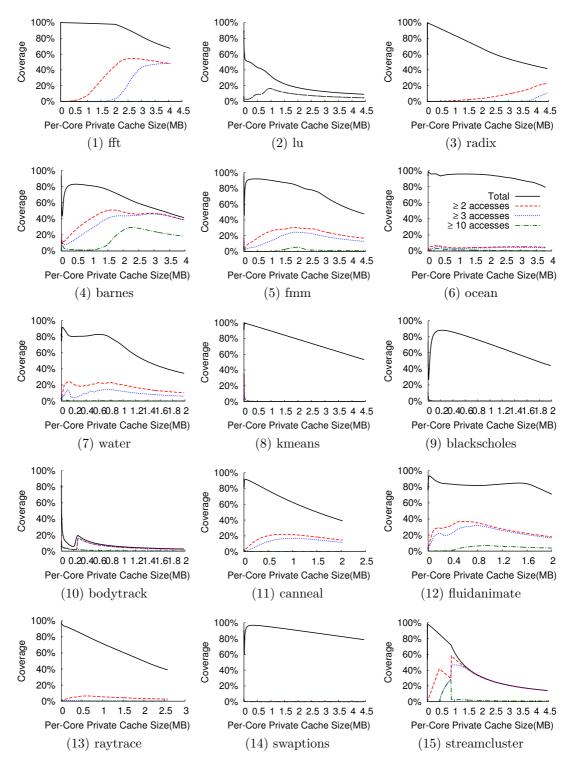

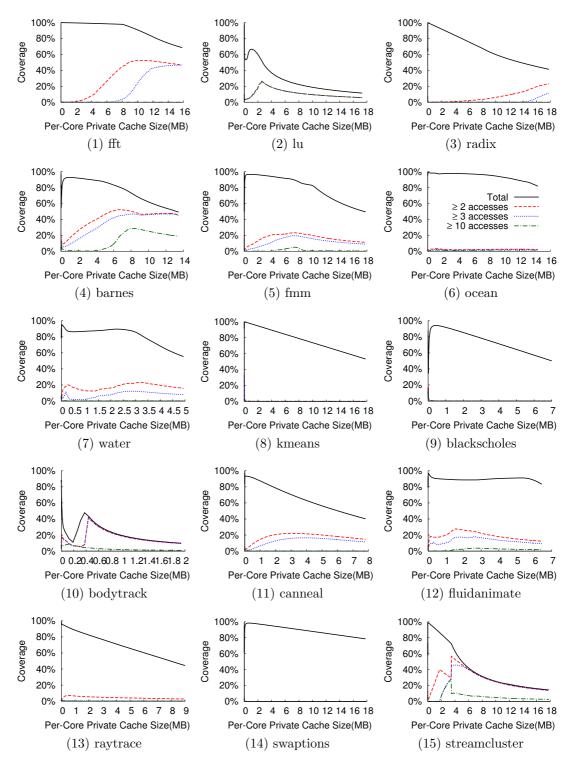

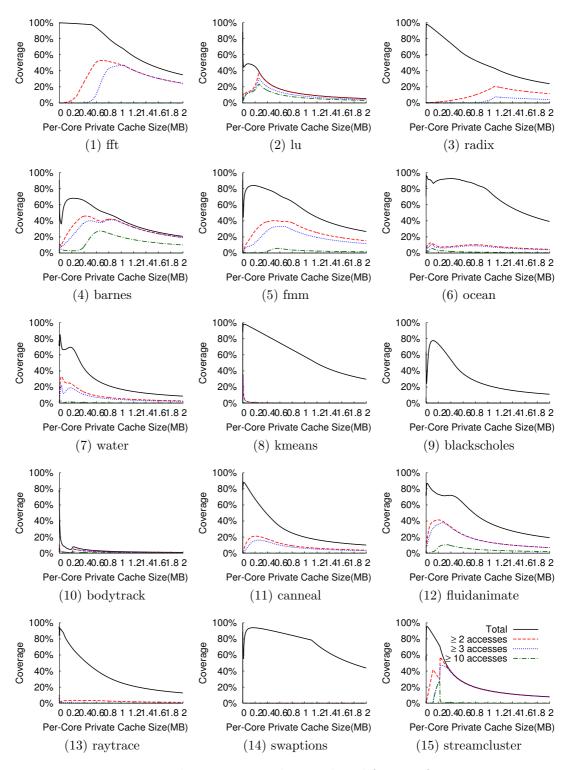

| 6.3 | Coverage for all entries                                                                                               | 65  |

| 6.4 | Percentage of multi-shared entries                                                                                     | 67  |

| 6.5 | Coverage drop in coverage due to core count scaling                                                                    | 71  |

| 6.6 | Percent accesses destined to $\geq$ 3-access entries, percent entries with                                             |     |

|     | $\geq 3$ accesses, and percent T2 accesses destined to $\geq 3$ -access entries.                                       | 78  |

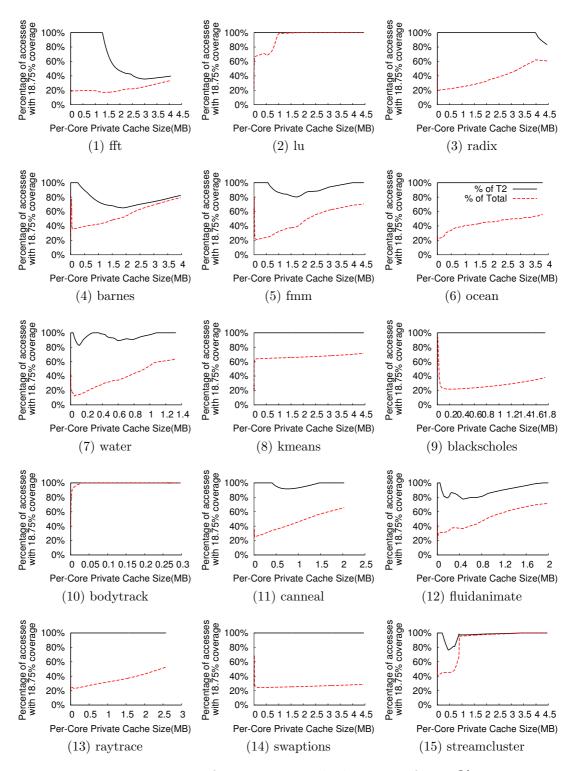

| 6.7 | Percentage of accesses towards directory of 18.75% coverage                                                            | 79  |

| 6.8 | Percentage Difference in accesses destined to $\geq$ 3-access entries, en-                                             |     |

|     | tries with $\geq 3$ accesses, and T2 accesses destined to $\geq 3$ -access entries                                     |     |

|     | for 16-cores and 256-cores from 64-cores, at 64MB.                                                                     | 81  |

| 7.1 | Data and directory cache parameters for simulation validation                                                          | 85  |

| 8.1 | Data and directory cache parameters for cuckoo experiments                                                             | 99  |

| 8.2 | DGD Coverage; Compare DGD with profiled total coverage                                                                 | 106 |

| 8.3 | SCD Coverage; Compare SCD with profiled total coverage                                                                 |     |

| 8.4 | Data and directory cache parameters for two level directory                                                            |     |

|     |                                                                                                                        |     |

# List of Figures

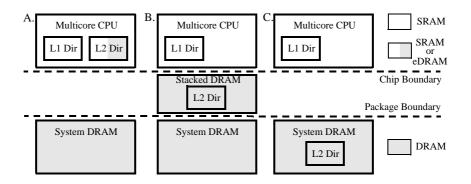

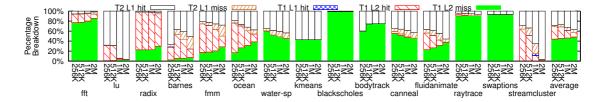

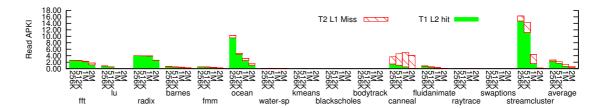

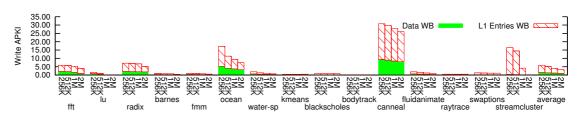

| 2.1                                                                                                             | Directory Accesses in a Multicore Cache Hierarchy                           | 10                                                             |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4                                                                                        | memory reference streams for uniprocessor and multicore                     | 24<br>25<br>32<br>33                                           |

| $4.1 \\ 4.2 \\ 4.3$                                                                                             | Directory Accesses in a Multicore Cache Hierarchy                           | 36<br>38<br>39                                                 |

| $5.1 \\ 5.2$                                                                                                    | Process Flowchart of the Profiler                                           | $\begin{array}{c} 48\\ 50 \end{array}$                         |

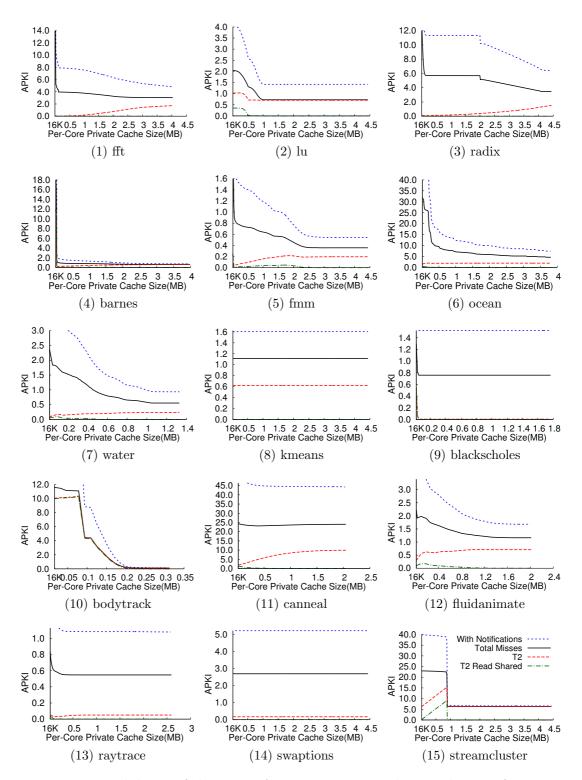

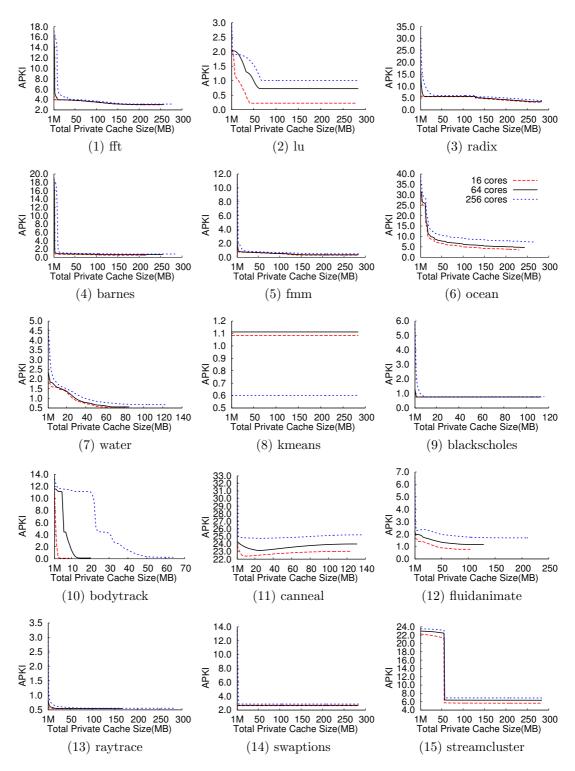

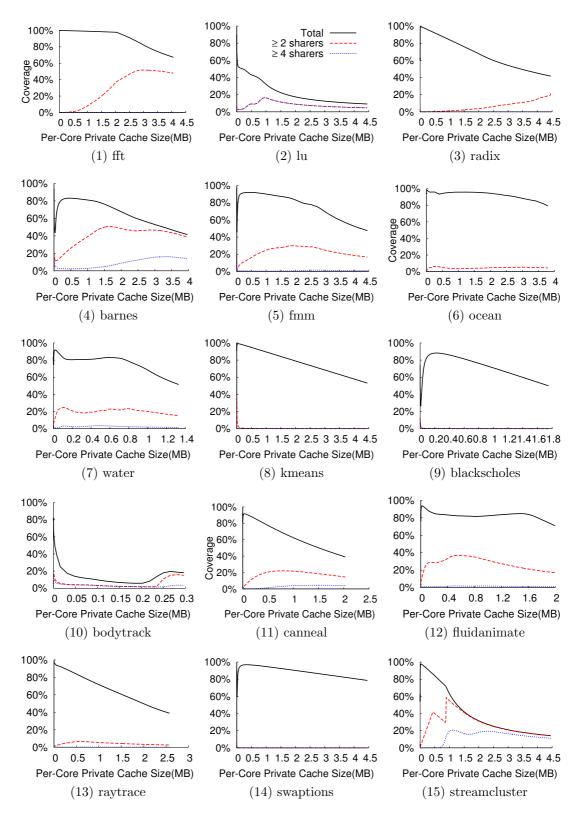

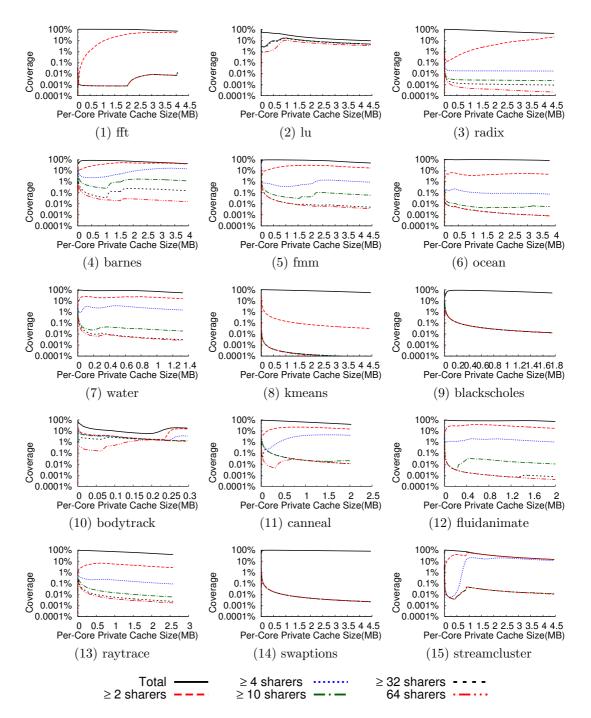

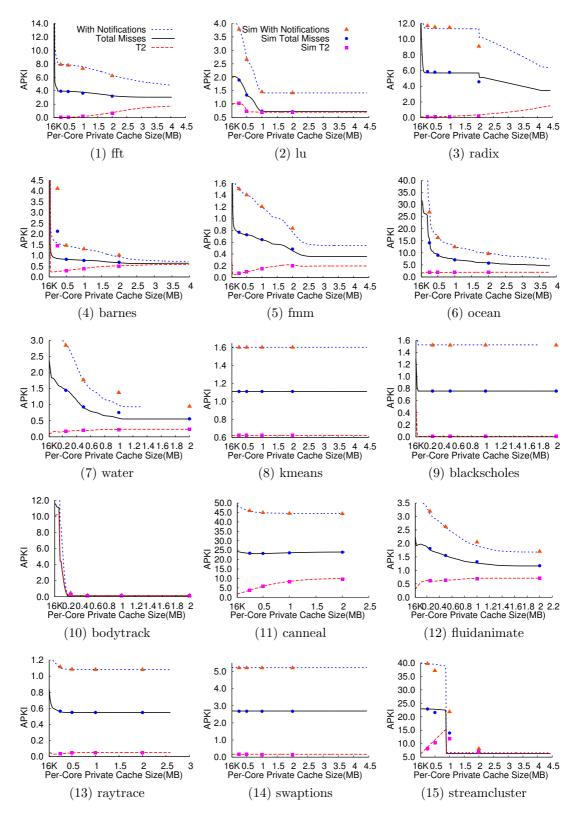

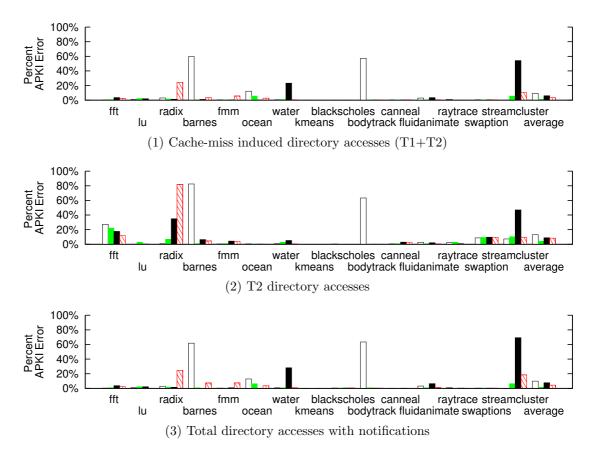

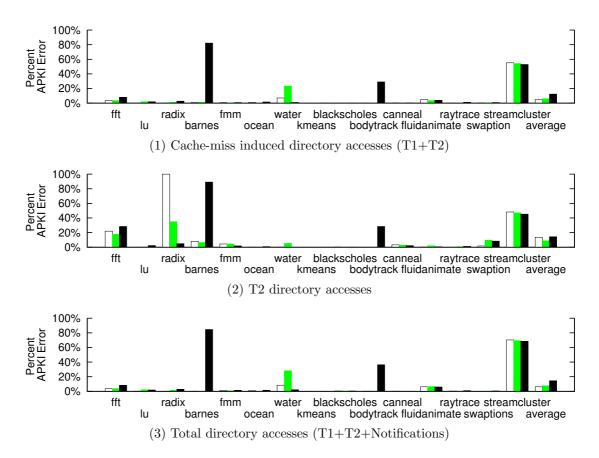

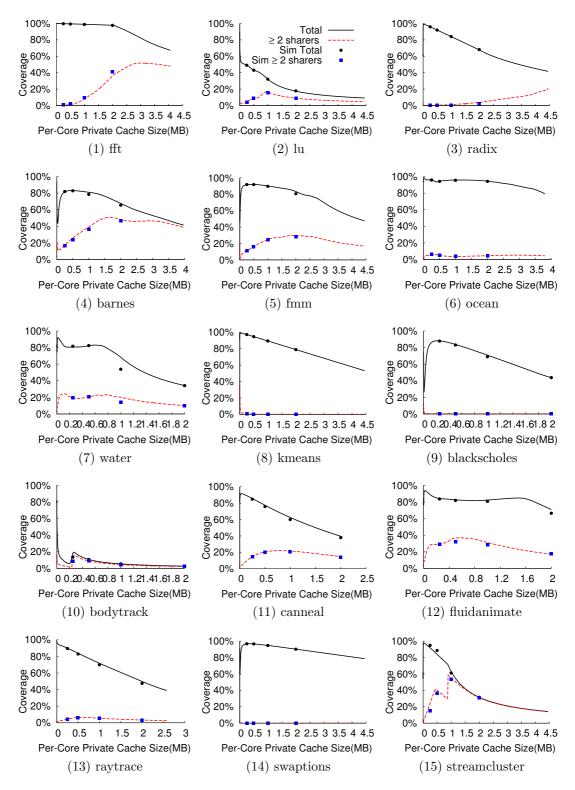

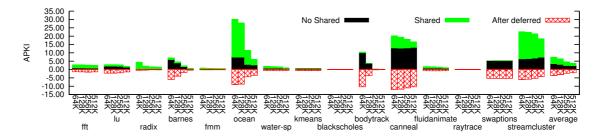

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.5 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \end{array}$ | Breakdown of directory APKI vs. private data cache size for 64-core<br>CPUs | 57<br>62<br>64<br>70<br>72<br>73<br>74<br>76<br>80<br>82<br>83 |

| <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ol>                                                  | Breakdown of directory APKI vs. private data cache size for 64-core<br>CPUs | 87<br>88<br>90<br>92                                           |

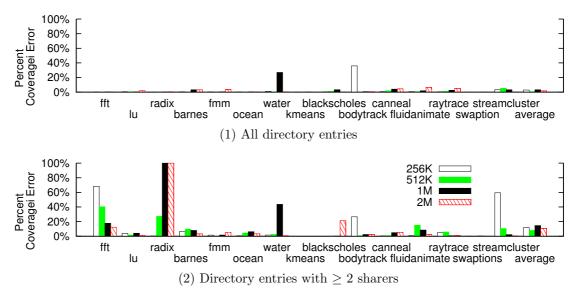

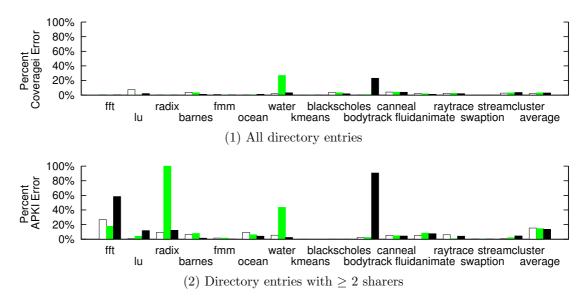

| 7.5 | Percent coverage error                                                                              |

|-----|-----------------------------------------------------------------------------------------------------|

| 7.6 | Percent coverage error for 16, 64, 256 cores                                                        |

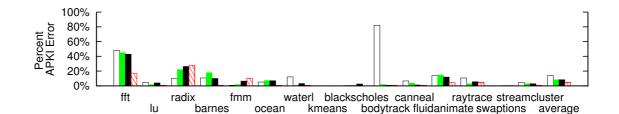

| 7.7 | Distribution access during their lifetimes                                                          |

| 7.8 | Percentage of entries with $\geq 3$ accesses $\ldots \ldots \ldots \ldots \ldots \ldots \ldots $ 97 |

| 7.9 | Percentage of entries with $\geq 3$ accesses for 16, 64, 256 cores $\dots \dots 97$                 |

| 8.1 | Minimum Cuckoo coverage for 1% eviction rate                                                        |

| 8.2 | DGD with 64 cores                                                                                   |

| 8.3 | SCD with 256 cores                                                                                  |

| 8.4 | Multi-level directory cache implementations                                                         |

| 8.5 | Hit and miss rates for T1 and T2 lookups at different levels of the                                 |

|     | directory cache for different private cache sizes                                                   |

| 8.6 | L2 directory cache read APKI for different private cache sizes 118                                  |

| 8.7 | L2 directory cache write APKI for different private cache sizes 118                                 |

| 8.8 | Latency critical L2 directory cache access APKI with or without                                     |

|     | shared caches and deferred                                                                          |

#### Chapter 1: Introduction

High-performance microprocessors are integrating an increasing number of cores on chip. Today, CPUs with 8–10 state-of-the-art cores or 10s of smaller cores [1,2] are in the market. For example, Knights Landing announced by Intel will be built using up to 72 Airmont (Atom) cores with four threads per core [3]. CPUs with 100s of cores–*i.e.*, large-scale chip multiprocessors (LCMPs) [4,5]–will be possible in the near future. This offers enormous potential performance improvement for programs with thread-level parallelism.

At the same time, new memory technologies have been adopted to provide more storage close to the cores, thus keeping up with the compute scaling. For example, Knights Landing employs on-package eDRAM [3]. There are also studies on Phase-Change RAM [6], Spin Transfer Torque RAM [7] and Resistive RAM [8]. These new technologies will provide the potential for much larger amounts of cache on chip.

While LCMPs are growing with more cores and larger on-chip caches, to fully utilize them, computer architects face huge challenges in scalability. Among these challenges, one of the most critical is cache coherence. Snooping protocols, which send cache coherence operations through a bus, only work for small-scale systems. When scaling beyond 16 or 32 cores, a directory-based protocol is required. Directory-based protocols keep a separate directory that stores the state and sharers of the cache blocks it tracks for coherence, enabling point-to point protocols that are more scalable than snooping protocols. But scaling this directory beyond hundreds of cores and hundreds of megabytes of cache is a key problem.

Ideally, a directory should consume small area and power, and incur low latency overhead when scaling to large core count and cache size. A directory's area, latency overhead and power can be tuned via a few design parameters. First, the area of a directory is determined by its capacity. Second, the latency overhead of a directory can be calculated by latency per access times its access frequency. Lastly, power dissipation of a directory is composed of static power, which is determined by its capacity, and dynamic power, which can be calculated by the energy per access times access frequency. In addition, both latency per access and energy per access of the directory are affected by the directory's capacity and architecture, while the access frequency of the directory is mostly decided by the data cache capacity. Therefore tuning *directory capacity* and *directory architecture* can change the balance between area, latency and power in the directory.

Many directory architectures have been proposed to make different trade-offs in balancing these three design parameters. Duplicate tag directories [9] are areaefficient, but require high associativity as CPUs scale. This architecture incurs large overhead in access latency and energy per access, thus becoming not scalable with a large number of cores. Sparse directories [10], on the other hand, are more scalable, because they store the sharer list per cache tag in a cache with low associativity. Unfortunately, the sparse directory architecture can become very big, as its size scales with both core count and cache size. When the cache size increases, there are more tags that need to be stored in the directory, whereas when the core count increases, there are more sharers that need to be tracked by each directory entry. For example, a full-map sparse directory for a 256-core CPU (assuming 64-byte cache blocks) will be half the size of its associated cache. Moreover, sparse directories require over-provisioning the number of tags to avoid conflicts due to their low associativity, further worsening the area and power requirement of a sparse directory as cache capacity scales.

Researchers have developed many approaches to improve the capacity scaling of directories. One approach is to reduce the sharer lists, such as using alternative sharing representations [10–15], or hierarchical directories [16–18]. Another approach is to reduce conflicts [18–20]. There are also approaches exploiting private data [20–23]. However, these techniques do not come without a price; many of them increase the complexity of the directory and/or access to the directory, complicating the directory design.

The balance among area, power and performance is not only affected by the directory techniques, but it is also affected by directory behavior, such as the access frequency to the directory and the content of the directory. Therefore, to complete the picture of the effectiveness and trade-off of different directory techniques, directory behavior needs to be studied–specifically, the *directory access patterns* and *directory content characteristics*. *Directory access patterns* include the read/write access frequency, as well as access distribution over different directory entries. This

information helps designers to understand the cost of each technique. *Directory* content characteristics include the total number of entries in the directory, as well as the degree of sharing for each entry. They also include the type of sharing-read vs. write. This information helps designers to determine how much the directory can be compressed.

These two important factors are impacted by how applications exercise the directory. For example, sharing is inherently an application behavior, with any sharing that occurs in the directory traceable to the interaction between application threads. Also, the directory access streams are dependent upon the memory access streams, which are decided by applications too.

But in addition to applications, directory content and access patterns are also highly sensitive to architecture. For example, varying *core count* usually changes the number of application threads, directly affecting the amount and frequency of sharing, thus changing the content of the directory. Also, varying the *data cache hierarchy* affects directory access streams because the directory access streams are cache-filtered versions of the memory access streams. Therefore, the cache size will affect the directory behavior by changing directory access streams.

On the other hand, the data cache hierarchy can also alter the sharing captured by the directory. This is because only the sharing that occurs in the private caches is visible to the directory, while the sharing that occurs in the shared cache or main memory is not visible. And the data cache size affects where the sharing happens. For example, the sharing that happens between two application threads may occur far apart in time. When the data cache is small, it is possible that the data block is evicted from the private cache before the second access happens. In this case, the sharing of the data block does not go through the private cache, thus it is invisible to the directory. But if the data cache is large enough to retain the data block, then the sharing of this data block happens in the private cache, and the directory is needed to provide coherence information. Therefore, the data cache size affects the directory behavior by changing the sharing pattern as well.

Given the importance of memory coherence to multicore scalability, it is crucial to study different directory techniques and their application and architecture dependencies. Traditionally, computer architects have used architectural simulation alone to study directory effects. Simulators can model memory behavior accurately, but simulating CPUs with 100s of cores is extremely slow. Moreover, one simulation only represents one individual architecture configuration and input problem. Simulation sweeps are usually required to gain deep insights. But with increasing number of cores and more complex cache hierarchies, the design space for the directory is growing exponentially large. Therefore, many researchers only vary the application, *i.e.*, by running entire benchmark suites, but they do not vary the cache configuration when studying directory techniques. There are only a few studies that have simulated different core counts or cache sizes [19, 22, 24]. And even in their cases, they only look at a small number of configurations.

One of the tools that can help architects evaluate multicore caches is *reuse* distance (RD) analysis [25–30]. RD analysis evaluates cache hierarchies using RDprofiles, which capture program-level locality. Recently, private-stack reuse distance (PRD) profiling [27–30] has been proposed to model the interaction in private data caches using per-thread coherent LRU stacks.

RD profiles are *architecture independent* across cache scaling, *i.e.*, a few profiles can reveal cache behavior across a large number of CPU configurations. Studies also show that PRD profiles for programs with symmetric threads are essentially architecture independent across cache size scaling as well [26, 27, 30, 31].

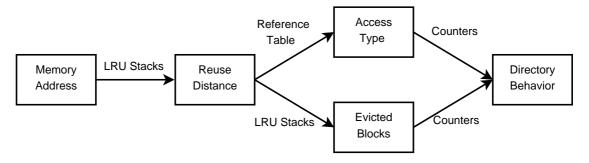

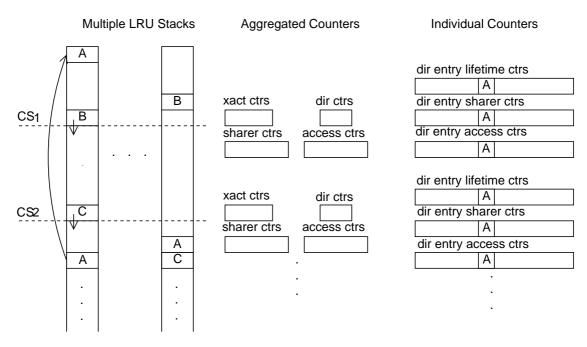

In light of this, this thesis applies multicore RD analysis to study the directory behavior. As explained above, the directory behaviors as well as the trade-off of different directory techniques are architecture dependent. This thesis extended RD analysis to provide a fast way to study the directory behavior across different CPU configurations, giving insights into the directory scalability problem, similar to what RD analysis has provided for the data cache. A framework is proposed based on PRD stacks that can extract the directory access and sharing information. In particular, *relative reuse distance between sharers* is proposed in this thesis. Relative reuse distance quantifies the sharing distance between accesses, identifies the sharing that occurs in the private cache, and thus directory, and enables the capacity-sensitive directory behavior analysis. Then, insights of directory access and sharing patterns are used to study the effectiveness and trade-off of directory techniques when core count and/or cache size scale.

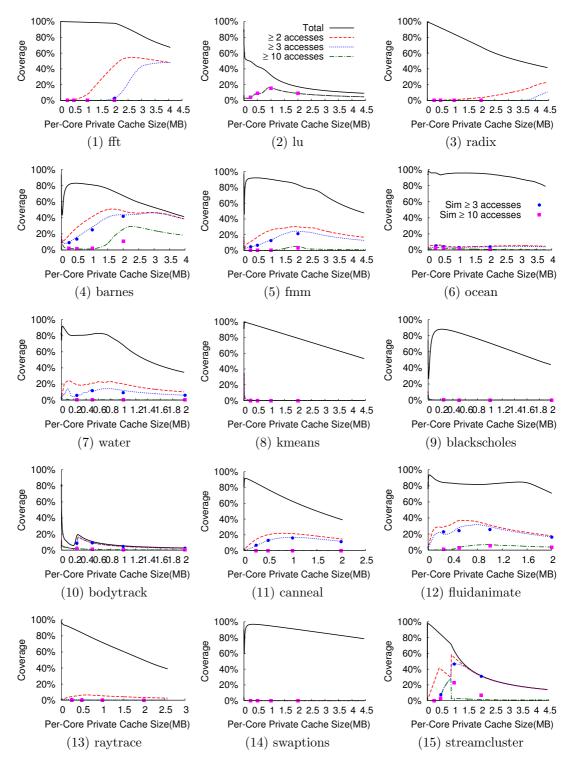

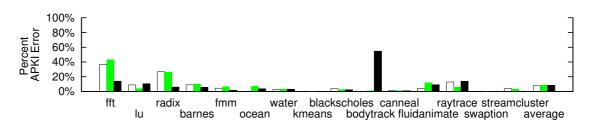

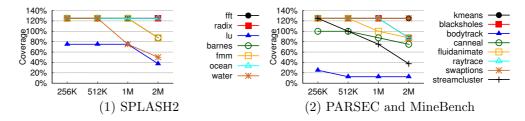

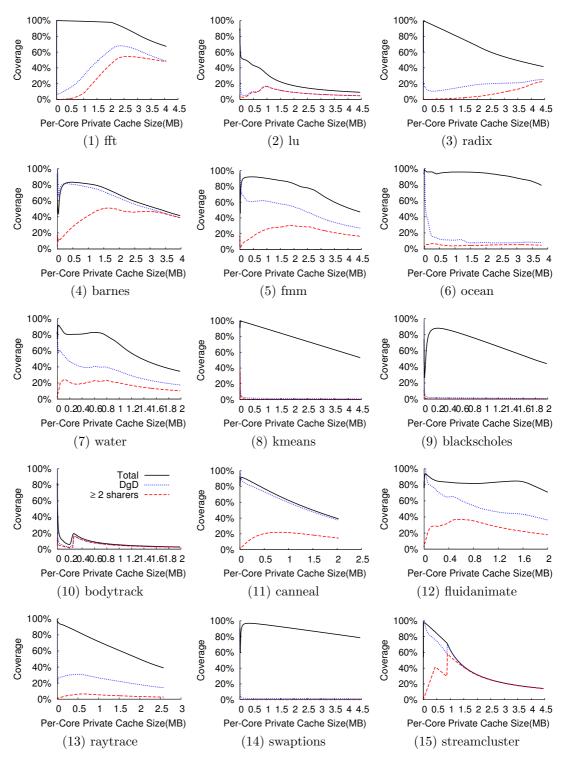

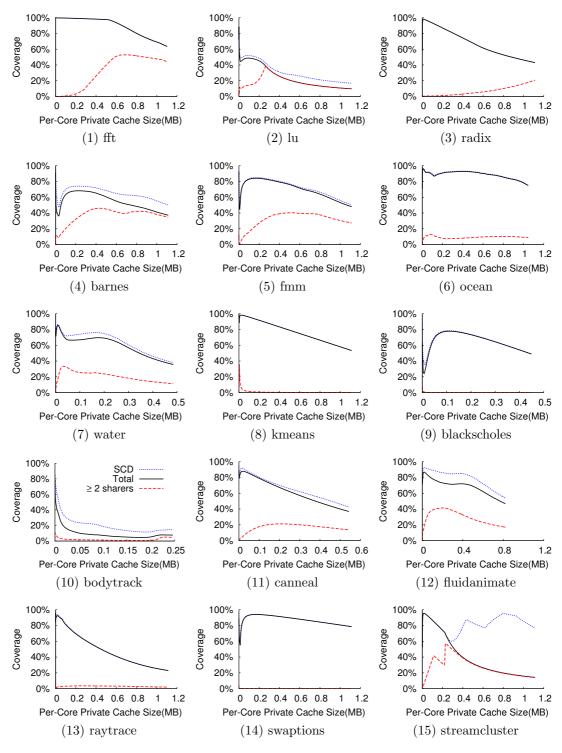

The analysis is implemented in a PIN-based profiler [32] to study directory behavior when scaling cache size and core count. Three aspects of the directory behavior are studied in this thesis: directory access frequency, directory contents and directory access distribution. For directory access frequency, the profiling results show a 3.5x drop in total accesses when increasing cache sizes from 16KB to 1MB, despite an increase in sharing-based directory accesses. For directory contents, the results show an increase in number of shared entries and a reduction in private entries when scaling cache sizes, enabling an reduction in total number of directory entries. The results show that directory size can be reduced by 53.3% in terms of coverage. For directory access distribution, the results show that at 1MB, 23.0% of the entries receive 37.8% of the total directory accesses and 82.7% of the sharing-based directory accesses. The profiling results also show that core count scaling has a much smaller effect on directory than cache size scaling. With 64MB total cache, the directory accesses increases by 38% and the directory size increase by 2.3% despite a 16x increase in core count.

To validate the profiling results, cache simulations are performed in this thesis to compare against profiling results. The validation results show the profiled directory accesses are within 8.6% of simulation on average across cache size scaling, and within 12.2% of simulation on average across core count scaling. Moreover, the profiled directory coverage results are within 11.2% of simulation on average across cache size scaling, and within 14.5% of simulation on average across core count scaling. In addition, the error of profiled directory access distribution results is 8.7% on average across cache size scaling, and 8.1% on average across core count scaling.

This thesis also discusses the implications of the profiling results for current directory techniques. First, the fraction of on-chip memory for directory varies with cache size scaling. Experiments show that for most benchmarks, a Cuckoo directory only needs to provide entries for 37.5–87.5% of the cache blocks in the private caches. Second, the fraction of shared entries increases with cache size scaling. Experiments

show that the average reduction for DGD technique compared to a regular directory decreases from 49.6% to 26.7% with cache size scaling. Third, most entries exhibit a limited sharing degree even with cache size scaling. Experiments show that on average, the increase in directory entries for the SCD technique is within 7.2%. Fourth, a small fraction of the directory receives a large portion of the directory accesses. Experiments show that in a multi-level directory, the first level that only covers 18.75% of the cache blocks in the private caches receives 83–91% of the latency critical directory accesses. Lastly, there are more opportunities to trade off directory access latency for directory size with cache size scaling, indicating the overheads for the above techniques reduce with cache size scaling.

The rest of this thesis is organized as follows. Chapter 2 provides the background on cache coherence structures, directory and the current directory techniques. Chapter 3 provides the background on sequential and multicore reuse distance analysis, and previous work studying cache sharing behavior using RD analysis. Chapter 4 discusses how reuse distance is used in analyzing directory behavior. Chapter 5 discusses the detailed implementation of the analysis framework. Chapter 6 reports profiling results while chapter 7 validates the profile results with cache simulations. Chapter 8 discusses implications and the case studies. Finally, chapter 9 concludes the thesis.

#### Chapter 2: Background on Directory

### 2.1 Cache Coherence and Directory

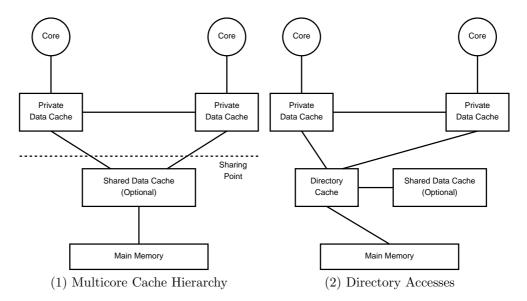

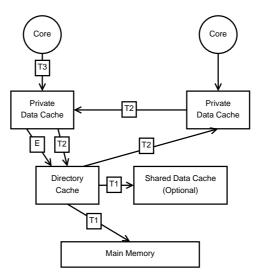

The memory hierarchy of a typical multicore usually consists of multiple levels of private caches, an optional shared cache, and a shared main memory, as illustrated in Figure 2.1(1). Cores and their private data caches sit at the top of the hierarchy, with multiple levels of private cache per core. Off-chip memory sits below the cache hierarchy.

Caching shared data in the private caches introduces a cache coherence problem. This is because the cores see memory through their local private caches, and without precautions, they can see different value of same memory location in their respective caches [33].

Hennessy and Patterson discussed the three aspects of cache coherence in the book *Computer Architecture, Fourth Edition: A Quantitative Approach* [33].

- Preserving program order. After a write by core C to memory location X, a read by C always returns the value written by C, if there is no writes to X by another core between the write and the read by C.

- 2. Cores should not continuously read an old data value. After a write by one

Figure 2.1: Directory Accesses in a Multicore Cache Hierarchy

core to memory location X, a read by another core to location X should return the written value, if the read and write are sufficiently separated in time and no other writes to X occurs between the two accesses.

3. Writes to the same memory location are serialized. That is, if value 1 and then 2 are written to one location, cores can never read the value of location as 2 and then later read it as 1.

Also as explained above, cache coherence is only relevant to the private caches, not the shared structure. Therefore this thesis defines the line between last level private caches and the first shared structure (either shared cache or main memory) as the CPU's *sharing point*. Cache coherence has to be maintained above the *sharing point* while there is no coherence issue below the *sharing point*.

#### 2.1.1 Directory

The protocols to maintain coherence for multiple processors are called cache coherence protocols. The cache coherence protocol keeps track of the state of any sharing of a data block, *e.g.*, whether the block is shared or private, and if the former, the cores that are sharing the data block. Traditionally, there are two ways to maintain cache coherence between multiple cores.

One is the snooping protocol, which sends cache coherence operations through some broadcast medium, such as a bus. In snooping protocols, each cache that has a copy of the data also has the sharing status of the block, but there is no centralized structure for this information. The request of a cache block is sent to the broadcast medium and the broadcast medium is snooped by the cache controller of each core, to determine if the core has a copy of the data that is being requested.

Snooping protocols are simple and do not require significant hardware support, because they rely on a single point of serialization: the broadcast bus. But they are very message intensive. When the number of cores increases, snooping protocols will generate too many messages for the bus to handle. Therefore the snooping protocol has limited scalability.

The alternative to snooping protocols is to keep a directory. A directory-based protocol keeps a separate directory that stores the state of the block it tracks for coherence. Each entry contains sharing information of a memory block, such as whether the block is dirty or which caches have a copy of this block. The use of a directory structure can reduce the bandwidth demands, as memory requests only need to go to the directory, not to every other core in the CPU.

One simple directory implementation is to attach each memory block with the directory entry that is in the shared structure, either shared data cache (assuming inclusive) or main memory. This is taking advantage of the shared structure as one single point for accesses to be serialized. It is also called an in-cache directory if the directory is implemented in the shared cache. In such an implementation, the amount of the information is proportional to the size of the shared structure.

An in-cache directory can be very costly in terms of area. Because the shared cache is usually much bigger than the last level private cache, not all the cache blocks in the shared cache are cached in the last level private cache. These blocks that are not cached by the private caches need neither coherence nor directory entries. Therefore, when the directory is integrated with shared cache, it contains many empty entries, wasting precious on-chip area. For example, modern day Intel microprocessors (like the Intel Core i7 processor) implement inclusive last level shared caches, and these are 8x the size of the cores' private caches [34]. If an in-cache directory is implemented, then at least 87.5% of the directory entries are not in use at any given time.

On the other hand, for a directory that is implemented in main memory, the overhead is not only the area, but also the long access latency. Because many directory accesses involve the data that are already on chip, accessing main memory before proceeding greatly increases the access latency of such accesses.

To reduce the area overhead, some approaches try to only track the active cache blocks that are resident in the private data caches and put this smaller directory cache on chip. One of the approaches is duplicate-tag-based directory [9, 35]. A duplicate-tag-based directory uses the existing tags in the private cache and stores all of them in central place, usually sitting at the CPU's sharing point. Therefore, the state for a block can be determined by examining the directory to find out all the copies of the tag in every possible cache.

Duplicate-tag-based directory is simple to implement and requires low area cost. However, its associativity increases proportional to the core count, which makes it not scalable. To illustrate, with a 64-core CPU, the directory needs to contain the tags for all 64 possible cache locations. And if each cache is 16-way set associative, then the aggregate associativity of the directory is 1024 ways.

Another approach is using a sparse directory [10]. The sparse directory organizes the cache coherence information as a cache. Each entry of the sparse directory is indexed by the tag of the blocks that are active in the private cache, and the entry contains the sharing information. Similarly, a sparse directory also sits at the CPU's sharing point. Figure 2.1(2) illustrates a directory cache with the on-chip cache hierarchy.

Because the sparse directory is implemented in a similar way as a cache, the architect is free to decide the associativity of the directory, making it more scalable. However, there is area overhead associated with the sparse directory. One of them is over-prevision. Theoretically, the directory cache size can be the same as the total number of private cache blocks, but a sparse directory is usually over-provisioned by 2x to 4x to reduce the probability of conflicts in the directory, in case the memory access pattern is skewed to load one directory set more heavily than the others [10]. With increasing size of the private data cache, the over-prevision of the directory can cost a lot of on-chip area.

Moreover, a straightforward way to implement a directory entry is to use a bit vector with one bit per core, also known as a full map entry. Therefore, a system with N cores requires N bits per entry. The directory entry scales linearly with the core count. As the core count increases, full map can incur significant area overhead too. To illustrate, a 256-core CPU needs 256 bits (32 bytes) for every directory entry. And if the directory is over-provisioned by 4x, for each 64-byte cache entry, 128-byte directory capacity is needed to maintain the coherence, making the directory larger than the caches. The huge area requirement for high core count makes sparse directory unscalable too. Therefore, many researchers have proposed to reduce the directory size and thus improve the scalability. This thesis discusses various techniques in detail in Section 2.2.

#### 2.1.2 Cache Coherence Protocol

To maintain the coherence requirements discussed above, a read should always see the value of the most recently write. Hennessy and Patterson discussed the two types of protocols to maintain the cache coherence in the book *Computer Architecture, Fourth Edition: A Quantitative Approach* [33]. One is write update protocol. The write update protocol updates all cached copies of a data block when the data is written to. However, because such protocols have to multicast the writes to all existing copies, the bandwidth requirement for this protocol is huge. Therefore, this protocol is not as widely used as the alternative protocol, the write invalidate protocol.

The write invalidate protocol invalidates copies of a data block when a write happens, so that the core that issues the write has exclusive access to the data before it writes to the data. This protocol is the most common protocol for directory-based schemes, so this thesis will focus on write invalidate protocols.

In addition to invalidating all the other copies of a cache block that is being written to, a cache miss should always find the most recent value of the data. There are two types of cache regarding write policy, write through and write back. In a write-back cache, the most recent copy is in the cache, but not in the memory. Therefore, the directory has to provide the information of where the most recent copy is. Because write-back cache requires less memory bandwidth, it is widely used in multicore CPU, so this thesis will focus on write invalidate protocols with write-back caches.

#### 2.1.2.1 MESI protocol

The MESI protocol is a widely used cache coherence protocol developed by the University of Illinois at Urbana-Champaign [36]. This section explains the protocol in detail because the analysis in this thesis focuses on MESI protocols.

MESI identifies the four states in which a cache block can be in:

• Modified state. This indicates that the block has been modified in the cache. Therefore the data in the cache is the most recent copy and is inconsistent

|   | Mode | Hit or Miss          | State                    | Directory Access       | Comment                  |

|---|------|----------------------|--------------------------|------------------------|--------------------------|

| 1 | R    | miss                 | I -> E                   | Create Directory Entry | Data From Next Level     |

| 2 | R    | miss                 | $M,E,S \rightarrow S$    | Directory Entry Access | Data Forwarding          |

| 3 | R    | hit                  | $_{\mathrm{M,E,S}}$      | No Directory Access    | Data Cache Hit           |

| 4 | W    | ${ m miss}$          | $I \rightarrow M$        | Create Directory Entry | Data From Next Level     |

| 5 | W    | ${ m miss}$          | $M,E,S \rightarrow M$    | Directory Entry Access | Data Forwarding, Invali- |

|   |      |                      |                          |                        | dations                  |

| 6 | W    | $\operatorname{hit}$ | $S \rightarrow M$        | Directory Entry Access | Invalidations            |

| 7 | W    | hit                  | ${\rm M,E}$ -> ${\rm M}$ | No Directory Access    | Data Cache Hit           |

Table 2.1: Access mode, cache hit or miss, cache block state, directory access and comments for MESI protocol.

to the data below the sharing point. Also the core which owns this data has exclusive access to it. The eviction of this block will cause a write back to the memory.

- Exclusive state. This indicates that the block is only in one is cache, but unmodified. This state can be changed into Shared state in response to a read request, or changed into Modified state when being written to. The Exclusive to Modified change can be done locally without notifying the directory.

- Shared state. This indicates that the block is unmodified and exists in more than one private cache. The block cannot be written to in this state. Also the eviction of this block does not need a write back to the memory.

- Invalid state. This indicates that the block is not in any of the private caches.

Table 2.1 shows cache coherence mechanism based on the access mode, hit or miss and the state of the cache block. For example, a cache block starts out in with invalid state, and a read miss or write miss will bring the cache block into the private cache, and create a new directory entry for it. A read miss puts the block into exclusive state, while the write miss puts the block into modified state. While the block is valid in the private cache, a transition to shared state from modified or exclusive state is triggered by a read miss from another core. This read miss will update the directory and also write back the data to the next level. On the other hand, a transition to the modified state from shared state is triggered by a write. This write will access the directory to send out invalidation messages.

As Table 2.1 shows, different cache transactions can trigger different directory accesses. Section 4.2 will discuss this information can be used to study the behavior of the directory in detail.

# 2.1.2.2 MSI protocol

The MSI is a basic cache coherence protocol. Compared to the MESI protocol, the MSI protocol does not have an Exclusive state. In the MSI protocol, shared state indicates the block is unmodified and exists in *one or more* private caches. Therefore, the exclusive state in MESI protocol is a special case of shared state in MSI protocol.

Having exclusive state helps to reduce one type of directory access, the transition form exclusive state to modified state. In MSI protocol, such transition is from shared state to modified state, and incurs a directory access. Therefore the MSI protocol requires more memory bandwidth than the MESI protocol.

#### 2.1.2.3 MOESI protocol

The MOESI protocol is another popular cache coherence protocol proposed by Sweazey and Smith [37]. In addition to the four states in the MESI protocol, MOESI adds an Owned state.

• Owned state. This indicates that the block is both modified and shared. This state is triggered when another core issues a data request to a block in modified state. Instead of changing to shared state and writing back the data as in the MESI protocol, the data is forwarded to the requesting core, changes into owned state without writing back to the next level.

The owned state avoids the need to write back a modified data to next level before sharing it. Therefore, the write-back is deferred and in some cases, multiple write-back can be combined into one write-back, thus saving memory bandwidth.

Therefore, depending on the cache coherence protocol, the access frequency to the directory and the behavior of the directory can be different. Section 4.4 discusses how different cache coherence protocols change the directory behavior.

#### 2.1.2.4 Protocol Variation in Evictions

Apart from different cache coherence protocols, another important part of the directory protocol implementation is how the eviction of data is handled. In a write-back cache, when a modified block is evicted from the data cache, it will write back to the next level memory structure. And naturally, the directory needs to be notified

because the location of the most recent copy of this data is changed. However, for a evicted data block that is clean, it is unclear whether the directory needs to be notified. Notifing the directory will cause extra traffic on chip, but this also enables the directory to update the sharing information. For example, in a sparse directory, by enabling clean eviction notification, a directory entry knows the exact number of existing copies of the corresponding data in the private caches and can be evicted if the number goes down to zero.

The difference in handling the data eviction in different directory techniques affects the analysis in this thesis, and will be explained in Section 4.4.

### 2.2 Previous Directory Techniques

As explained in Section 2.1.1, the size of the sparse directory is the major problem in scalability. A number of prior works have explored many ways to reduce the size of directories, and this thesis studies the characterization of directory behavior and evaluates the effectiveness and the cost of prior works.

Several works have focused on reducing sharer lists. One way is to use a compressed but inexact encoding for each entry. Gupta et al. proposed the coarse vector technique, which uses N/K bits, where a bit is set if any of the sharers in a K-sharer group caches the block [10]. Acacio et al. proposed sharing code based on multilayer clustering approach [38]. It constructs the nodes logically in a tree structure and the sharing code is the level of the root of the minimal sub-tree that contains the home node and all the sharers.

Another approach is to maintain the exact sharer lists. IEEE Standard Scalable Coherent Interface (SCI) [39] proposed chained directory protocol. Each directory entry contains a chain of pointers to all the sharers. Nilsson and Stenstrom proposed a balanced tree structure instead of a link list for each entry [40] and Chang and Bhuyan improved it by maintaining multiple trees for each entry [41]. A hierarchical directory is also proposed to implement multiple levels of directory cache, in which each first-level directory encodes the sharers of a subset of caches, and the higher level tracks the directory of lower level caches [16–18,42]. Recently, Zhao et al. observed that many memory locations have the same sharer list and thus proposed SPACE [15]. SPACE encodes sharing patterns in the directory entry and has a separate table to decode the pattern into bit-vectors.

Moreover, one observation is that in many benchmarks, only a few memory blocks are widely shared among all cores. This has enabled researchers to propose a directory entry format that only tracks a few sharers. Agarwal et al. evaluate the schemes of limited pointers, in which a smaller number of pointers is used to identify the sharers [11]. Choi and Park proposed the segment directory, a hybrid of limited pointers and bit-vector, to further reduce the entry size [12]. Each directory entry is of size  $K+\log_2 N/K$  and can track at most K sharers. The problem of the limited pointer technique is sharer overflow, when the number of pointers is not enough to track all the sharers. Agarwal et al. evaluated the broadcasting policy as well as the no-broadcast policy in which extra sharers get invalidated [11]. Chaiken et al. proposed a software fallback, where the software emulates a full map directory when overflow happens [14]. Researchers have also combined limited pointers with various techniques mentioned above. Gupta et al. proposed switching to coarse representation [10] and Chen proposed using chained pointers when directory entries overflow [13]. Sanchez et al. proposed SCD [18] to scale up to a thousand cores or more. For cache blocks with narrow sharing, SCD uses pointers in entries, while for blocks with wide sharing, it uses a hierarchy of multiple directory entries.

The capacity reduction of these techniques is dependent upon how the directory entry is encoded, but the overhead is related to directory behavior. When the techniques employ complex directory protocol, they usually require multiple lookups per directory access, increasing the directory access latency. This thesis analyzes the directory access frequency, thus it can estimate the cost of such techniques.

Apart from reducing the directory entry size, there are techniques that focus on reducing the number of entries. One is to reduce the over-provisioning by *reducing conflicts*. Ferdman et al. proposed the Cuckoo Directory [19] to reduce conflict misses using Cuckoo Hashing [43]. ZCache-style replacement [44] is also used to reduce the conflicts in SCD [18] and DGD [20]. The directory content studied in this thesis shows a minimum number of directory entries needed in these techniques assuming full associativity; therefore, it gives a lower bound on the directory capacity when designing a directory cache using these techniques. On the other hand, these techniques combine sophisticated hashing schemes and re-insertions, increasing the cost of directory accesses unevenly. This thesis studies the accesses frequency for different types of directory accesses, thus it can help determine the cost of these techniques.

There are also approaches focusing on exploiting private data to reduce the

number of entries. Cuesta et al. use the operating system to detect private pages and omit tracking cache blocks in those private pages [23, 45]. Valls et al. proposed PS-Dir [21], which stores shared cache entries in regular SRAM, while keeping private entries in slower eDRAM. SCT [22] and DGD [20] recognize private data accessed by each core tend to occur in large contiguous regions. Hence, they coalesce consecutive privately accessed cache blocks, and track them as a single coherence unit. The directory content analysis in this thesis can determine the number of shared entries in the directory, thus giving a lower bound of these techniques. The analysis can also be performed assuming different cache block sizes, giving an estimate of their capacity reduction. In addition, these techniques require complicated directory operation, therefore the directory access pattern analysis in this work can be helpful in analyzing the cost of such techniques.

The tagless coherence directory [46] proposed by Zebchuk et al uses bloom filters to track which blocks are in the private cache. This approach significantly reduces directory storage requirements because the tags are not stored, so the capacity of the directory purely depends on the number of bloom filters. However, the approach uses multiple hash functions, and access energy can be very high. The directory access frequency analysis in this thesis can help determine whether it is energy-scalable.

Finally, the last technique is to exploit the locality of coherence operation. The thesis shows that not all entries in the directory are equally important. Some directory entries are accessed much more frequently than other directory entries WayPoint [24] proposed a two-level directory. It evicts infrequently accessed entries that do not fit in the on-chip directory, and stores them in off-chip DRAM. The access distribution analysis in this thesis can help analyze this kind of non-uniform access distribution across directory entries. Chapter 3: Background on Reuse Distance Analysis

### 3.1 Reuse Distance Profile

Reuse distance (RD) analysis is a tool to characterize cache behavior by analyzing program locality. It is initially developed for uniprocessor to study the locality of the program. The analysis measures an *RD profile*, which records RD values for all memory references.

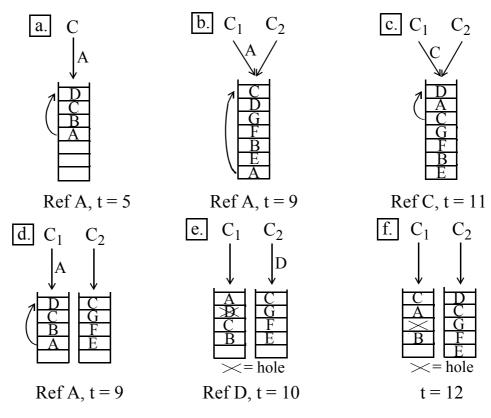

An RD value is defined as the number of unique data blocks referenced since the last reference to the same data block. To illustrate, Figure 3.1(a) shows a memory access stream for uniprocessor accessing seven memory blocks, A - G. At t = 5, block A is accessed, the RD value for this access is 3 because there are three unique references between this access and the previous access to block A at t = 1.

An LRU stack is used to obtain the RD values. The stack contains the program's memory blocks, and is maintained like a cache with LRU ordering among the blocks. When a memory access is performed, the LRU stack is searched to find a. Time: 1 2 3 4 5 6 7 8 9 10 11 b. Time: 1 3 4 5 6 7 8 9 10 11 2 Core: A B C D A C E F G C D Core C1: A В С D Α С F G Core C2: Е С D (w) (w)

Figure 3.1: memory reference streams for uniprocessor and multicore

Figure 3.2: LRU stacks for RD, CRD, and PRD

the memory block and the stack depth of the block is its RD value. Then the entry for this memory block is moved to the top of the stack. To illustrate, Figure 3.2(a) shows the state of the LRU stack at t = 5, the stack depth of block A is 3, which is the RD value for this access.

Moreover, assuming LRU and full associativity, a cache of size CS can satisfy any reference with RD < CS; therefore the cache miss count for this cache is the sum of all references in the RD profile with RD  $\geq CS$ . To illustrate, Figure 3.2(a) shows the state of the LRU stack at t = 5, and shows the RD value for this access to block A. Therefore, this access will be a hit in a cache with 4 or more entries, but a miss in a cache with less than 4 entries.

In sequential programs, the RD profiles are architecture independent, because

the memory access stream is fixed once the binary of the program is produced. Each program produces one memory access stream results in one RD profile. With this profile, it is possible to predict the misses for any cache size CS, and evaluate cache performance at any cache size CS. Therefore RD profiles allow fast analysis along the cache capacity dimension.

In recent years, RD analysis is extended for multicore processors by modeling inter-thread interactions. The memory hierarchy in multicore processor usually contains two different cache architecture, shared cache and private cache. To evaluate shared cache, *Concurrent reuse distance (CRD) analysis* [25–31] is developed. It uses one global LRU stack to model the reuse across thread-interleaved memory references. To evaluate private cache, *private-stack reuse distance (PRD) analy*sis [27–30] is developed. It models multiple LRU stacks, one stack per core, and the memory references are accessed on its local stack while the coherence is maintained among all stacks.

RD analysis for multicore CPUs is more complex compared to the sequential RD analysis because the locality in parallel programs involves both per-thread reuse and memory reference interaction between simultaneous threads. For example, in a shared cache, inter-thread memory reference interleaving leads to *interference*. While in private caches, *data sharing* leads to replications and communications.

Moreover, memory interleaving caused by inter-thread interactions depends on timings. Therefore RD analysis for multicores become sensitive to how the memory accesses are interleaved, *i.e.*, *architecture dependent*. CRD/PRD profile measured on one architecture might not be valid for another architecture if the per-thread timing changes substantially, unable to reflect the locality for the cache accurately.

However, studies show that in programs whose threads execute similar codes, e.g., programs that exploit *loop-based* parallelism, the memory interleaving is regular [26, 27, 30, 31]. Because these threads tend to speedup or slow down by similar amounts with different architectural configuration. Therefore CRD/PRD profiles for these programs are stable across different architecture, and thus essentially architecture independent and can provide accurate analysis.

As multicore RD analysis is a great tool to study cache size scaling, there are also researches that extended reuse distance to study core count and problem size scaling. Researches shows that CRD and PRD profiles for symmetric threads change in a systematic fashion when scaling core count and problem size. For core count scaling, memory interleaving from the threads are increased, but with similar locality characteristics [29–31]. For problem scaling, the computation structure, such as loops, and the data structure are increased proportionally [30, 47]. Therefore the shift in CRD and PRD profiles preserve the shape and are highly predictable.

Therefore researchers proposed using simple prediction algorithms to predict the profiles with different core counts and problem sizes. Reference groups [47] was proposed to predict shape-preserving profile shift. The technique creates groups of reference and measure the shift rates for each group by comparing two profiles. Then apply the scaled shift rates to form a scaled-up profiles. The technique is first used to predict RD profiles across problem size scaling [47]. It is then extend to predict CRD and PRD profiles across problem size and core count scaling, and researches show the technique is very accurate [29, 30, 47].

#### 3.2 Multicore Reuse Distance Profile

## 3.2.1 CRD Profile

As explained in Section 3.1, *Concurrent reuse distance* or CRD, is used to capture locality information in a shared cache, by measuring the reuse distance of thread-interleaved memory reference stream that access one shared cache. CRD values are measured on a global shared LRU stack [25–31].

To illustrate, Figure 3.1(b) shows a interleaving of memory references from two cores,  $C_1$  and  $C_2$ . In this memory access stream, all memory references are read expect the reference to block D at t = 10, as indicated by (w) in the figure. This memory access stream is constructed from the memory access stream in Figure 3.1(a), by distributing and interleaving the memory accesses among two cores. Figure 3.2(b) and (c) shows the global LRU stacks for CRD profile. In particular, Figure 3.2(b) shows the state of the global LRU stack at t = 9, when core  $C_1$  references block A. There are six blocks above A in this global LRU stack, thus the CRD for this access is 6, indicating this access is a hit for any shared cache with 7 or more entries, but a miss for any shared cache with less than 7 entries.

However, the RD for the accesses belong to core  $C_1$ , also know as intra-thread RD, is 3, while CRD for this access is 6. In this case, CRD > RD, because of the memory interleaving. The accesses from  $C_2$  is different from accesses from  $C_1$ , and cause *dilation* of intra-thread reuse distance. Therefore the private data in the threads will cause CRD to increase compared to its intra-thread RD. On the other hand, the shared data in the threads can offset the dilation effect. First effect is the overlapping reference. For example, Figure 3.1(b) shows  $C_2$ 's access to block C at t = 8 interleaves with  $C_1$ 's reuse of block A at t = 9, but it does not increase A's CRD, because  $C_1$  already accesses block C at t = 5 in this reuse interval. Second effect is the *intercept*. To illustrate, Figure 3.2(c) shows the state of the global LRU stack at t = 11, when core  $C_1$  is referencing block C. The intra-thread RD for this access is 2, while the CRD for this access is also 2. This is because core  $C_2$  accesses the same block C in this reuse interval, causing the CRD to decrease.

## 3.2.2 PRD Profile

As explained in Section 3.1, *Private-stack reuse distance* or PRD, is used to capture locality information in private caches, by measuring reuse distance across per-thread memory reference streams that access coherent private caches. PRD values are measured on multiple private LRU stacks that are kept coherent with individual threads' memory reference streams [27–30].

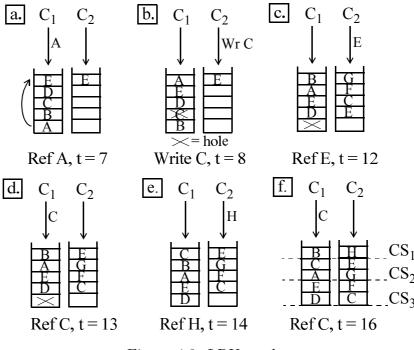

Similar to sequential RD profiles, PRD profiles capture the reuse within each LRU stack, or intra-thread reuse, which can be used to predict the private cache misses. Figure 4.3(d)-(f) shows the LRU stacks for PRD profiles. In particular, Figure 4.3(d) shows the intra-thread reuse at t = 9. In Figure 4.3(d), Core C<sub>1</sub> references A. There are three blocks above A in the LRU stack of core C<sub>1</sub>, so its PRD = 3. This access is a hit in a cache of size 4 or more, but a miss in a smaller

cache. But the private stacks are multiplied, so the total private cache size should be the aggregate capacity of all private cache. Therefore in this case, the private cache has to be size 8 or more for this access to be a hit.

Other than intra-thread reuse, PRD profiling captures inter-thread interactions as well, *e.g.*, sharing. When read sharing occurs, in which one data block is accessed by multiple cores; replicas of the block show up in multiple stacks. These replicas in the stacks increase the capacity pressure because more cache is needed to satisfy the cores' accesses. For example, in Figure 4.2,  $C_1$  accesses c at t = 5 and  $C_2$  accesses C at at t = 8. Figure 4.3(d) shows data block C is replicated in both stacks.

In addition to read sharing, PRD also captures write sharing by maintaining coherence via write invalidation between LRU stacks. To illustrate,  $C_2$ 's reference to D at t = 10 in Figure 4.2 is a write, then invalidation will occur in  $C_1$ 's stack as in Figure 4.3(e). The invalidation has two consequences. One is that a "hole" is created when a block is invalidated to prevent promotion of blocks further down the LRU stack [27]. When a data block below the hole is referenced, the hole moves to the position of that block, to preserve the stack depth of the blocks below. For example, in Figure 4.3(f) shows the state of the private LRU stack at t = 12, after the rereferences of C by  $C_1$  at t = 11. Comparing to Figure 4.3(e), Figure 4.3(f) shows, the reference of C cause block A to be pushed down and the hole move to depth (C's old position). The other consequence is the coherence miss, which is a miss caused by the write invalidation. For example, in Figure 4.3(f), after invalidation, if  $C_1$  re-reference block D again, then this access will always miss, regardless of the cache capacity.

## 3.3 Cache Sharing Behavior

In previous studies [29,30], researchers studies the sharing in the caches using reuse distance analysis, in particular the difference between CRD and PRD profiles. This thesis studies the directory behavior using an extension of reuse distance analysis. Since the sharing in cache is closely related to the directory behavior, this section reviews how CRD and PRD profiles reveal the sharing in caches.

As explained in Section 3.2, PRD profile and CRD profile are used to study private cache and shared cache respectively. If there is no sharing between the threads, the profiles for private cache and shared cache are similar, as shown in previous studies [29, 31]. But sharing will cause PRD profile to have more misses than CRD profile. There are two sources of the extra misses.

One is the extra misses due to the replication. To illustrate, Figure 4.3(d) shows the core  $C_1$  re-referencing block A at t = 9. Figure 4.3(d) also shows data block C is replicated in both stacks and this replication puts pressure to the cache. And as explained in Section 3.2.2, for access A to be a hit, the private cache must be size 8 or more. But Figure 4.3(b) shows the same access for shared cache, and as explained above, for this access A to be a hit, the shared cache only need to be size 7 or more. The difference in capacity requirement comes from the replication of block C. Therefore, for same capacity, the private cache will suffer more misses than shared cache due to replications.

Figure 3.3: CRD and PRD profiles for benchmark ocean

The other source of extra misses is the coherence miss from the invalidations. Coherence miss can only happens in private cache. To illustrate, in Figure 4.3(f), after invalidation of block D at t = 10, if C<sub>1</sub> re-reference block D again, then this access will always miss, regardless of the cache capacity. While in Figure 4.3(c), the write to block D at t = 10 will not cause any invalidation. After the access of block C at t = 11, if C<sub>1</sub> re-reference block D, it will still hit if the cache is large enough. In another word, coherence miss will never happen in CRD profile because there is no write invalidation in a shared cache. Therefore, the private cache will suffer more cache misses than shared cache due to invalidations.

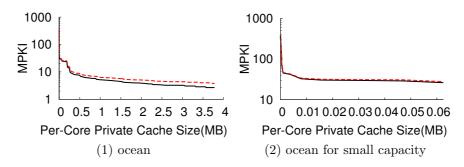

To illustrate the difference between CRD and PRD profiles, Figure 3.3 plots the MPKI corresponding to the CRD and PRD profiles for ocean from SPAHSH2 benchmark suites [48] following the method in the previous study [29, 30]. Figure 3.3(1) shows the two complete profiles and Figure 3.3(2) shows the two profiles for small capacity.

As Figure 3.3(2) shows, the PRD and CRD profiles are almost identical at small capacity, indicating the absence of sharing effects, both replications and invalidations. This shows at small capacity, the most data in the cache are private data.

Figure 3.4: PRD profiles for benchmark ocean for 16-, 64-, 256-cores

While figure 3.3(1) shows in larger capacity, there is a gap between PRD and CRD profiles, which is called "sharing-based degradation" in previous study [30]. This shows the sharing only begin to manifest itself in a larger cache.

This is because the parallelization scheme, such as blocking, usually have high sharing distance. Traditionally, programmers try to avoid frequency sharing in the benchmarks to minimize the communication and getting better performance. Therefore, the sharing distance for benchmarks are usually high and thus the sharing is only observable in a larger cache.

### 3.4 Core Count Scaling Behavior

In previous studies [29, 30], researches also study how PRD profiles changes with core count scaling. This thesis also studies how directory behavior changes with core count scaling. Therefore this section reviews the core count scaling effects on PRD profiles.

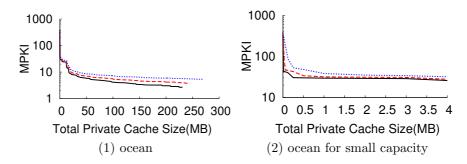

Figure 3.4 plots the MPKI corresponding to the PRD profiles for ocean from SPAHSH2 benchmark suites [48] for 16-, 64- and 256-cores, following the method in the previous study [29, 30]. Figure 3.4(1) shows the three complete profiles and

Figure 3.4(2) shows the three profiles for small capacity.

As Figure 3.4(2) shows, at small capacity, the PRD profile exhibits a shift with the increasing core count. In fact the shift is proportional to the number of cores. This is because the core count scaling increases the interference between the threads. In loop-based parallel programs, the parallelization is done by breaking the loop into multiple parts and execute them on multiple cores, as Figure 3.1 shows. Therefore, with more cores, more interleaved memory locations are referenced between reuses. And the increased PRD value shifts the PRD profiles towards higher capacity.

While as Figure 3.4(1) shows, at larger capacity, the shift in PRD profile becomes smaller and not proportional to the number of cores. This is because of the limited scope of the interference. In loop-based parallel programs, though the distance of reuse within a loop is increased due to more core count, the distance of reuse between the loops are mostly constant. Therefore, at larger core count the shift is very insignificant.

On the other hand, Figure 3.4(1) shows the non-shifting parts of PRD also increases with core count. This is due to the increase of sharing with core count scaling. With more cores, there are more replications and invalidations, causing PRD to increase with core counts.

#### Chapter 4: Analysis Framework

This chapter explains the how reuse distance framework is adapted for analyzing directory cache. Section 4.1 discusses how to study the directory behavior through the data cache transactions information. Section 4.2 and 4.3 explain using reuse distance analysis framework to study the directory access and content. Section 4.4 discusses the sensitivity of the analysis framework to coherence protocol.

## 4.1 Characterization of Directory Behavior

A directory cache access is performed when a core performs a memory operation that cannot be satisfied from the core's local private cache hierarchy, requiring memory transactions that involve other remote caches or main memory. Therefore the behavior of a directory cache can be studied through data cache transactions. To illustrate, Figure 4.1 groups cache transactions into 3 categories, labeled T1–T3.

T1 represents a cache transaction that misses all the way to the sharing point, either to shared cache or main memory. The directory is accessed, to create an entry to track future coherence information. Moreover, the directory access that caused by T1 transaction is usually latency tolerant, because T1 transaction incurs access below the sharing points, often off-chip, and much higher access latency than

Figure 4.1: Directory Accesses in a Multicore Cache Hierarchy

directory access. Though directory still need be to accessed to determine that the data is not chip, it can be overlapped with the memory access because only memory address is needed to proceed.

T2 represents a cache transaction that requires information from remote cores. These "sharing-based" transaction accesses directory too, to determine the coherence action and the sharers involved. Comparing to T1 transaction, the directory access that caused by T2 transaction is usually latency critical, because the directory information is essential to either the correctness of the program or getting the data, the directory access has to done before getting the data block.

T3 represents a cache transaction that hit in local private data cache and can be satisfied by it, such as read hit or write hit to a modified block. T3 transaction will not generate directory access.

Finally, E represents a notification to the directory when when a cache block is evicted from the private cache. This thesis assumes all eviction, dirty or clean will notify the directory, so that the directory is synchronized with the cache.

Therefore, by examining the data cache transactions and data cache eviction, one can get the access information to the directory cache. This includes the access frequency to the whole directory, as well as the how the access distributed across directory entries.

Apart from directory cache access frequency and distribution, the access to the directory also change the content of the directory. In order to analyze the directory cache content, the concept of *directory entry lifetime* is introduced. *Directory entry lifetime* is defined as the period that the entry resides in the directory.

When T1 transaction is performed, a new data block is brought into the private cache. This creates a new directory entry with a single sharer in the directory cache, and starts a new directory entry lifetime.

During its lifetime, T2 transaction access modifies the sharer list of the directory entry. A T2 read transaction adds a sharer to the entry's sharer list, while a T2 write transaction reduces the sharer list to a single sharer (assuming invalidation on writes). And a eviction notification also subtract one sharer from the sharer list.

Finally, the lifetime of a directory entry ends when the directory is notified that all copies of its associated data blocks have been evicted from the private caches. And the directory entry can be deallocated to provide space for other entries.

Therefore, by examining the data cache transactions and data cache eviction, one can get the content information to the directory cache. This includes total number of entries in the directory as well as the sharing degree of each entry.

Here, the T1-T3 and E transactions in Figure 4.1 are determined by the private

data cache. The data cache size affects the hit and miss of a data transaction and the number of private caches (*i.e.*, cores) will affect the sharing between each caches, thus affect the balance and frequency of T1, T2, T3 and E transactions. As discussed above, this not only changes the access pattern but also affects the content of the directory by changing the lifetimes and the sharer lists of a directory entry. The goal of this thesis is to fully characterize the dependence of directory's accesses and contents on the private data cache hierarchy.

### 4.2 Directory Access Analysis

| Time:                 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8   | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|-----------------------|---|---|---|---|---|---|---|-----|---|----|----|----|----|----|----|----|

| Core C <sub>1</sub> : | А | В | С |   | D | Е | А |     |   | В  |    |    | С  |    | В  | С  |

| Core C <sub>2</sub> : |   |   |   | Е |   |   |   | С   | F |    | G  | Е  |    | Η  |    |    |

|                       |   |   |   |   |   |   |   | (w) |   |    |    |    |    |    |    |    |

Figure 4.2: Two interleaved memory reference streams

As explained in Chapter 3, RD analysis is a great tool to study the cache behavior with cache scaling, because one profile can provide the cache information across all cache size. This section discusses how to extend multicore RD analysis to analyze directory caches. As discussed in Section 4.1, the directory's accesses are closely related to data cache misses. In particular, a major part of the directory's accesses come from cache misses, because when a cache miss occurs, the directory is accessed to determine if the requested cache block is in other private caches.

Figure 4.2 shows a interleaving of memory references from two cores,  $C_1$  and  $C_2$ . In this memory access stream, all memory references are read expect the reference to block C at t = 8, as indicated by (w) in the figure. For example, when

Figure 4.3: LRU stacks

$C_1$  re-references block A at t = 7 in Figure 4.3(a), if the local private cache is large enough to capture this reuse (PRD < CS), then the reference is a read hit. Otherwise (PRD  $\geq CS$ ), the reference is a miss and generates a directory access. Therefore, looking at PRD already provides a major part of the directory access information.

However, PRD profile only provide local cache information, and this information alone is not enough. The problem is revealing the sharing in the cache. For example, PRD profiles cannot identify if a write hit is performed on a shared cache, nor can they distinguish whether a directory access is a shared access (T2). As discussed in Chapter 1, although sharing is an application-level property, whether the sharing in the program is exposed to the directory depends on the size of the data cache. Therefore, the *relative reuse distance* between sharers is essential to determine if the sharing happens in the cache.

Relative reuse distance is proposed to evaluate the difference of stack depths for the same block across multiple stacks. Because the stacks are organized in LRU fashion, the difference in stack depths indicates how far apart in time the sharing happens. For example, if the two accesses to the same block from different cores happen close in time, then a small cache is sufficient to retain the data block when the second access happens. On the other hand, if the two accesses happen far apart in time, the data block is possibly evicted from the cache before the second access happens if the cache is too small. The sharing is only exposed given a bigger cache.

In order to analyze the relative reuse distance, remote reuse distance, or  $PRD_{remote}$ , is introduced.  $PRD_{remote}$  is the minimum stack depth across all remote PRD stacks for a memory reference. Relative reuse distance can be calculated by comparing PRD and  $PRD_{remote}$ , thus obtaining the sharing information.

There are three possible outcomes for  $\text{PRD}_{remote} < CS, \geq CS$  and  $\infty$ . When  $\text{PRD}_{remote} = \infty$ , there is only one copy of the data block regardless of cache size, and it resides in the local LRU stack. Thus, this data block is "truly private."  $\text{PRD}_{remote} \geq CS$  suggests there is no other copy of this data block within the limited time window captured by CS. The data block is classified as "temporally private" [22]. Lastly,  $\text{PRD}_{remote} < CS$  shows there are other copies in the remote LRU stacks, and there is sharing going on in the private caches.

To illustrate, Figure 4.3(f) shows  $C_1$  re-references data block C at t = 16. Data block C exists in both LRU stacks, but at different depths, hence the directory access behavior depends on the private cache size. Figure 4.3(f) shows three cases, labeled  $CS_1-CS_3$ . If the cache size is  $CS_1$ , then  $PRD \ge CS_1$  and  $PRD_{remote} \ge CS_1$ , so neither copy is on chip. Thus,  $C_1$ 's reference is a miss and generates a T1 directory access. If the cache size is  $CS_2$ , then  $PRD < CS_2$  and  $PRD_{remote} \ge CS_2$ , and only  $C_1$ 's copy is on chip. The block C is "temporally private." So  $C_1$ 's reference is a T3 access regardless of access mode, and does not generate a directory access. Lastly, if the cache size is  $CS_3$ , then  $PRD < CS_3$  and  $PRD_{remote} < CS_3$ , and both copies are on-chip. If the access is a read, this is a read hit and a T3 access, so there is no access to the directory. But if the access is a write, then this is a write hit to a shared block, so a T2 directory access is generated.

The above example shows a few combinations of access mode, PRD and  $PRD_{remote}$ , and how they affect the access to the directory. Table 4.1 lists the 18 possible different cache transactions, depending on the access mode (read or write),  $PRD/PRD_{remote}$  outcomes discussed above, and also how these transactions are related to MESI protocol in Table 2.1. Table 4.1 reports them in terms of the T1–T3 categories.