## ABSTRACT

Title of Document:

### SILICON ON INSULATOR BIPOLAR JUNCTION TRANSISTORS FOR FLEXIBLE MICROWAVE APPLICATIONS

John McGoldrick Bavier, Doctor of Philosophy 2014

Directed By:

Professor John Cumings, Department of Materials Science and Engineering

Microwave frequency flexible electronic devices require a high quality semiconducting material and a set of fabrication techniques that are compatible with device integration onto flexible polymer substrates. Over the past ten years, monocrystalline silicon nanomembranes (SiNMs) have been studied as a flexible semiconducting material that is compatible with industrial Si processing. Fabricated from commercial silicon on insulator (SOI) wafers, SiNMs can be transferred to flexible substrates using a variety of techniques. Due to their high carrier mobilities, SiNMs are a promising candidate for flexible microwave frequency devices.

This dissertation presents fabrication techniques for flexible SiNM devices in general, as well as the progress made towards the development of a microwave frequency SiNM bipolar junction transistor (BJT). In order to overcome previous limitations associated with adhesion, novel methods for transfer printing of metal films and SiNMs are presented. These techniques enable transfer printing of a range of metal films and improve the alignment of small transfer printed SiNM devices. Work towards the development of a microwave frequency BJT on SOI for SiNM devices is also described. Utilizing a self-aligned polysilicon sidewall spacer technique, a BJT with an ultra-narrow base region is fabricated and tested.

Two regimes of operation are identified and characterized under DC conditions. At low base currents, devices exhibited forward current gain as high as  $\beta_F = 900$ . At higher base current values, a transconductance of 59 mS was observed. Microwave scattering parameters were obtained for the BJTs under both biasing conditions and compared to unbiased measurements. Microwave frequency gain was not observed. Instead, bias-dependent non-reciprocal behavior was observed and examined. Limitations associated with the microwave impedance-matched electrode configuration are presented. High current densities in the narrow electrodes cause localized heating, which leads to electrode material damage and ultimately dopant diffusion in the BJT.

Finally, device design improvements are proposed to address the problem of localized heating and increase device lifetime under testing conditions. High values for DC current gain suggest that future modifications should improve microwave frequency performance and measurement reproducibility.

## SILICON ON INSULATOR BIPOLAR JUNCTION TRANSISTORS FOR FLEXIBLE MICROWAVE APPLICATIONS

By

John McGoldrick Bavier

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2014

Advisory Committee: Professor John Cumings, Chair Professor Liangbing Hu Professor Manfred Wuttig Dr. Vince Ballarotto Professor Min Ouyang, Dean's Representative © Copyright by John McGoldrick Bavier 2014

# Dedication

To my father, Richard Bavier, for always encouraging me to pursue that which is worthy of my effort.

## Acknowledgements

There are many without whose help I could not be writing this thesis. It's truly a humbling experience to try to account for all of the support I've received from friends, family, and colleagues over my graduate career. While I don't have the space to thank everyone here, I am forever indebted to those who have helped and I aspire to their generosity as I continue my career.

First I must thank my academic advisor, John Cumings, for giving me the opportunity to work on this project. He has always been a source of good advice, technical or otherwise, and always found a way to be available when I needed him to be. Special thanks as well to my sponsor at LPS, Vince Ballarotto. Vince has always helped me to keep perspective when things don't go as planned, and to appreciate and acknowledge the little victories along the way. It's a great feeling to work for people who are also your supporters and advocates, and I am grateful to Vince and John for that.

I owe much of my fabrication ability to Dan Hines, who taught me many of the cleanroom skills used extensively in this work. Dan also helped me get my first publication, for which I will always be grateful. I'd like to thank Andrew Tunnell for setting a graceful example of how to go through the process of being (and ultimately ceasing to be) a graduate student. Thanks to Jia Huang for introducing me to the basics of SiNM processing. While she didn't contribute directly, I thank Merintje Bronsgeest for friendly lab conversation and baked goods when she was late to meetings. Thanks to Da Song and Colin Preston for their help and good company in my last years at Maryland. It's been a pleasure working alongside you both.

iii

Finally, thanks to my family. To my wife Heather, for putting up with the late nights and dirty dishes. And for always believing that I would do well, even when I had my doubts. To my mother Mary, for unconditional support and friendship, and for encouraging me to reach out of my comfort zone and pursue bigger things. To my brother and all-time favorite guitar player Andy, for giving someone to look up to as an academic and as a man.

# Table of Contents

| i |

|---|

| i |

| V |

| i |

| i |

| X |

| 1 |

| 2 |

| 4 |

| 4 |

| 4 |

| 2 |

| 3 |

| 3 |

| 3 |

| 5 |

| 5 |

| 7 |

| 0 |

| 0 |

| 7 |

| 7 |

| 4 |

| 3 |

|   |

# List of Tables

| Table 1.1 – BJT modes of operation                          | 19 |

|-------------------------------------------------------------|----|

| Table 2.1 – Contact angle data for parylene C               |    |

| Table 2.2 – Pre- and post-transfer resistivity measurements |    |

# List of Figures

| Figure 1.1 – Three layer configuration for nanomembrane fabrication [2]         | 4  |

|---------------------------------------------------------------------------------|----|

| Figure 1.2 – Generic SiNM transfer process                                      | 5  |

| Figure 1.3 - Si conduction band in the reciprocal lattice [5]                   | 6  |

| Figure 1.4 - Elastically relaxed strain sharing membrane transfer [7]           | 8  |

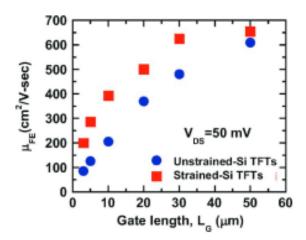

| Figure 1.5 - Field effect mobility for strained and unstrained SiNM MOSFETs [7] | 8  |

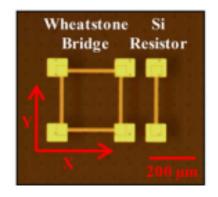

| Figure 1.6 - Piezoresistive SiNM strain sensor [8]                              |    |

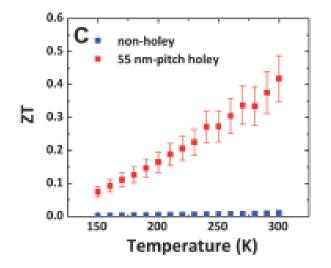

| Figure 1.7- ZT for "holey" and "non-holey" SiNMs                                |    |

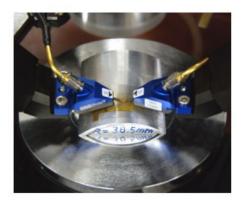

| Figure 1.8 – Measurement of strained SiNM PIN diodes                            |    |

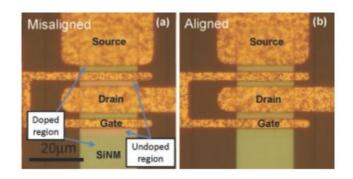

| Figure 1.9 – Alignment of microwave frequency SiNM FET [21]                     |    |

| Figure 1.10 – PN junction                                                       |    |

| Figure 1.11 – Forward biased PN junction [22]                                   |    |

| Figure 1.12 – Shockley diode IV characteristic [23]                             |    |

| Figure 1.13 – BJT, forward active mode                                          |    |

| Figure 1.14 – Quiescent point on DC IV curve [24]                               |    |

| Figure 1.15 – Two-port network [25]                                             |    |

| Figure 1.16 – The Smith Chart [27].                                             |    |

| Figure 1.17 – Coplanar waveguide                                                |    |

| Figure 1.18 – Tapered CPW design                                                |    |

| Figure 1.19 – Shorted electrode configuration                                   |    |

| Figure 1.20- HFSS simulation results for signal transmission and reflection     |    |

| Figure 1.21 - S-parameter measurements for tapered CPW                          |    |

| Figure 2.1 - Linear regression to determine $\gamma_s^{P}$ and $\gamma_s^{D}$   |    |

| Figure 2.2 – Fabrication and transfer process                                   |    |

| Figure 2.3 – Successfully transferred metal films                               |    |

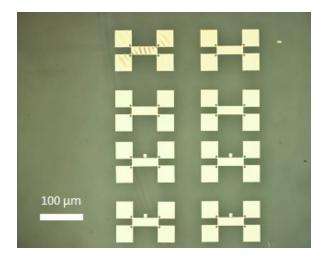

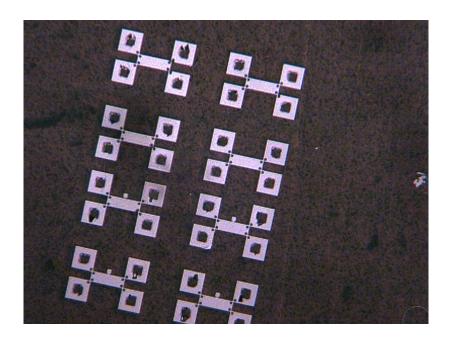

| Figure 2.4 – Partially etched top Si layer                                      |    |

| Figure 2.5 – Perforated Si sheet                                                |    |

| Figure 2.6 – Diagram of HF solution undercut                                    |    |

| Figure 2.7 – Partially undercut Si feature                                      |    |

| Figure 2.8 – Completely released SiNM.                                          | 56 |

| Figure 2.9 Stamp assisted SiNM transfer [49]                                    |    |

| Figure 2.10- The flip-transfer process [7]                                      | 58 |

| Figure 2.11 – Large area, flip-transferred SiNM                                 | 59 |

| Figure 2.12 – Shifting during flip-transfer                                     | 60 |

| Figure 2.13 – Successful transfer                                               |    |

| Figure 2.14 – Partially released SiNMs                                          | 61 |

| Figure 2.15 – Transferred aligned SiNMs on kapton                               | 62 |

| Figure 2.16 – Au electrodes on transferred SiNMs                                |    |

| Figure 2.17 – Etched SiNM on kapton                                             | 63 |

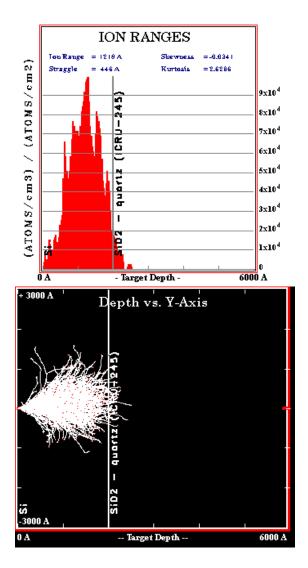

| Figure 3.1- Output from SRIM simulation                                         |    |

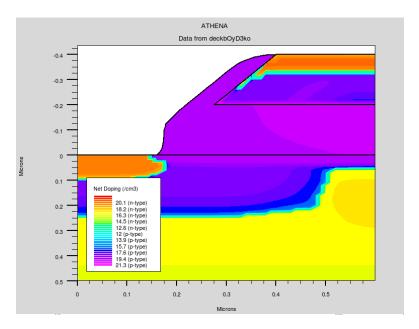

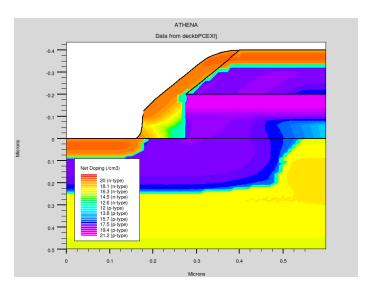

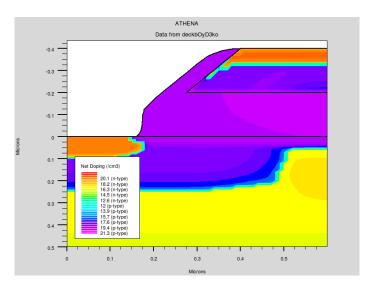

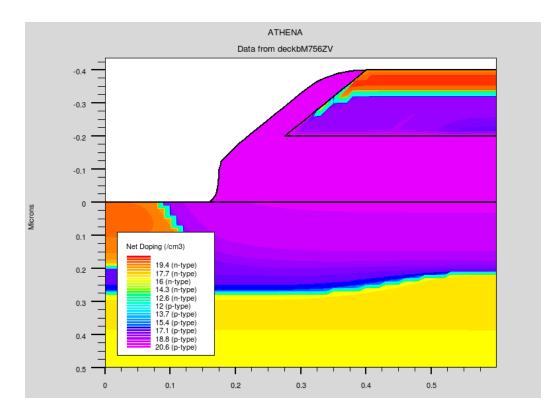

| Figure 3.2 - ATHENA two-dimensional doping profile                              |    |

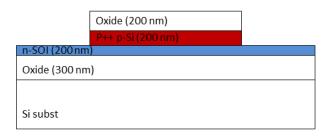

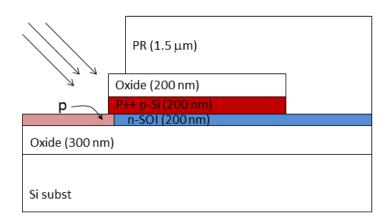

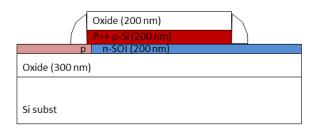

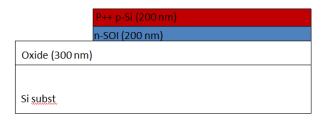

| Figure 3.3 – N-type SOI                                                         |    |

| Figure 3.4 - Poly-Si extrinsic base layer                                       |    |

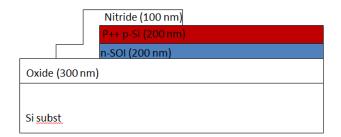

| Figure 3.5 – Protective SiO <sub>2</sub> layer                                  | 72 |

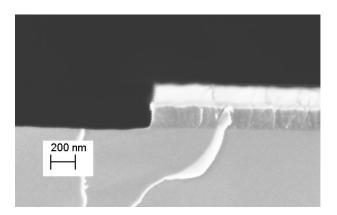

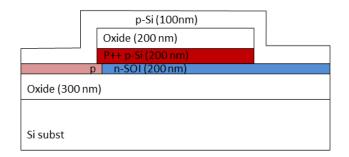

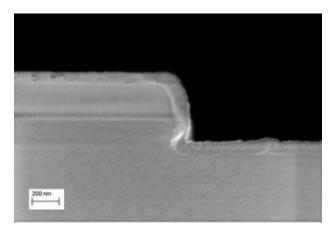

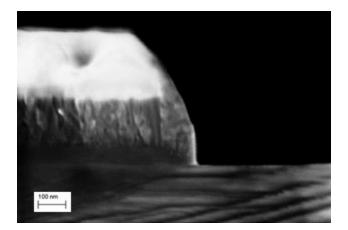

| Figure 3.6 – Vertical step etch, diagram and SEM image                             | . 73 |

|------------------------------------------------------------------------------------|------|

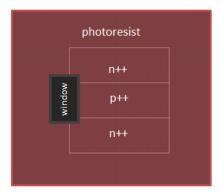

| Figure 3.7 – Angled ion implant                                                    | . 74 |

| Figure 3.8 – Conformal poly-Si deposition                                          | . 75 |

| Figure 3.9 – Poly-Si sidewall spacer                                               | . 76 |

| Figure 3.10- Simulated dopant distribution before annealing                        | . 77 |

| Figure 3.11 – Simulated dopant distribution after annealing                        | . 77 |

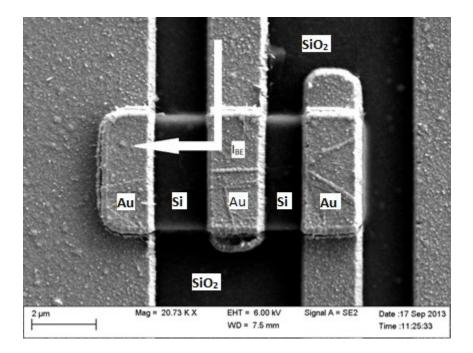

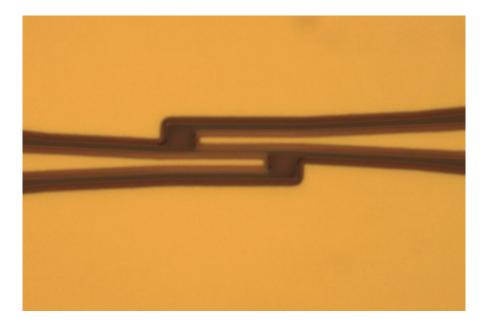

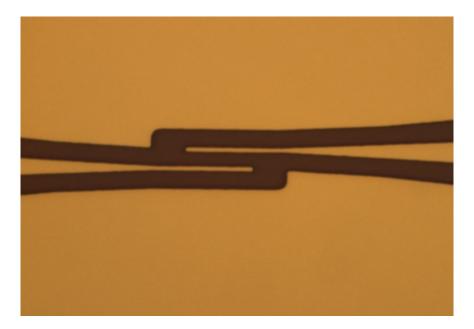

| Figure 3.12 – Top view of Si device                                                | . 78 |

| Figure 3.13 – Cross-section of step                                                | . 78 |

| Figure 3.14 – Nitride patch window                                                 | . 79 |

| Figure 3.15 – Cross-section of step with protective nitride                        | . 79 |

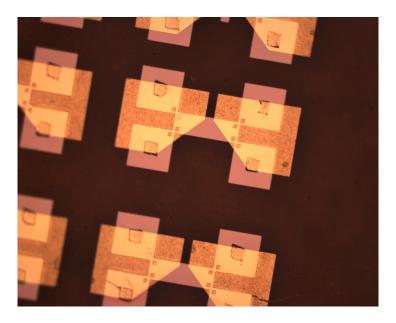

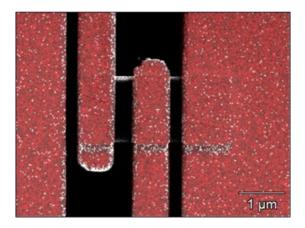

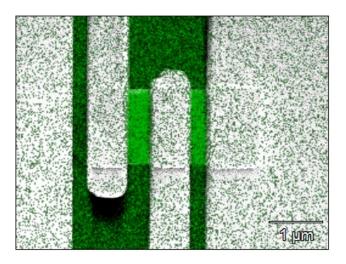

| Figure 3.16 – Patterned metal electrodes                                           | . 81 |

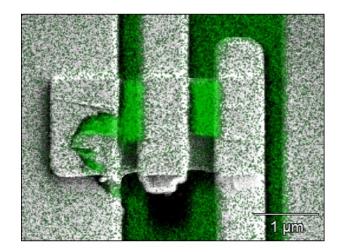

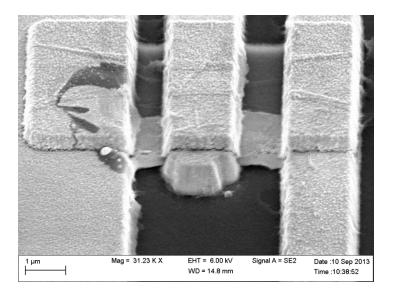

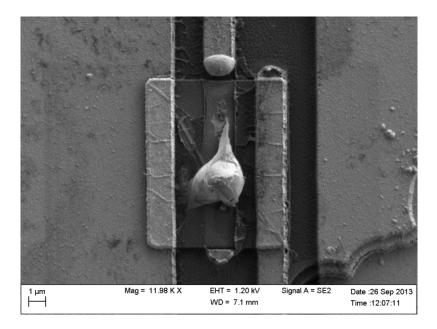

| Figure 3.17 – Ti/Au device failure                                                 | . 82 |

| Figure 3.18 – EDX Au overlay before failure                                        | . 83 |

| Figure 3.19 – EDX Si overlay before failure                                        |      |

| Figure 3.20 – EDX Au overlay after failure                                         | . 84 |

| Figure 3.21 – EDX Si overlay after failure                                         | . 85 |

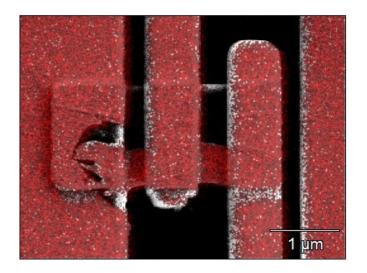

| Figure 3.22 – Tilted SEM image of electrodes after failure                         |      |

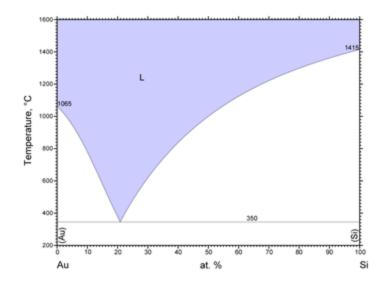

| Figure 3.23 – Au-Si binary phase diagram [57]                                      |      |

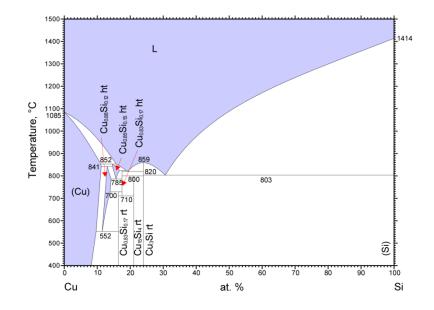

| Figure 3.24 – Cu-Si binary phase diagram [58]                                      |      |

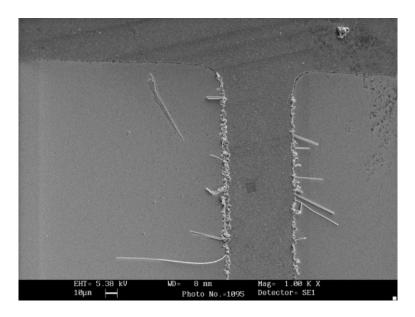

| Figure 3.25 – Ti/Cu device failure                                                 |      |

| Figure 3.26 – SEM image of melted Ti/Cu electrode                                  |      |

| Figure 3.27 – Whisker electromigration pattern [61]                                |      |

| Figure 3.28 – Voids caused by electromigration [61]                                |      |

| Figure 3.29 – Fully etched W film before resist removal                            |      |

| Figure 3.30 – Etched W electrodes using isotropic W etch                           |      |

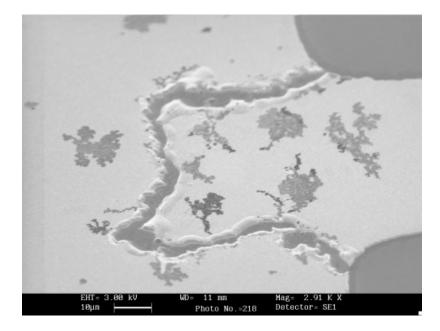

| Figure 3.31 – Effect of annealing at 1100°C for 45 seconds                         |      |

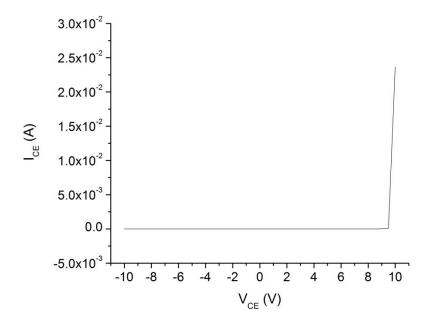

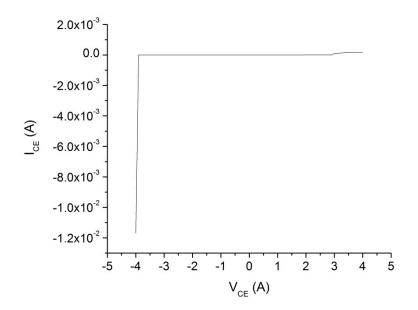

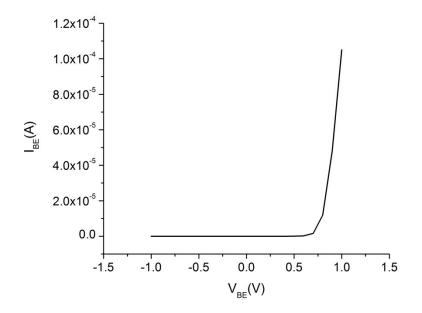

| Figure 4.1 – I-V characteristics of the base-emitter junction                      |      |

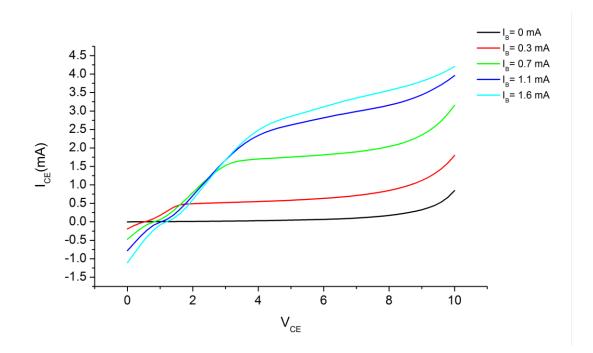

| Figure 4.2 – Preliminary I-V data                                                  |      |

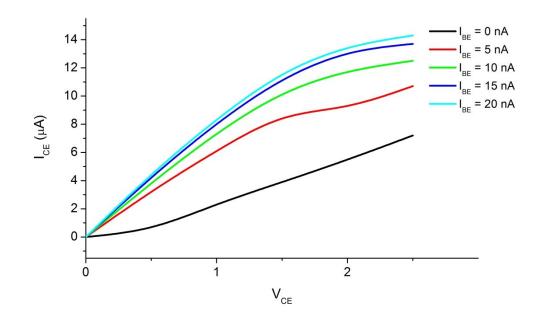

| Figure 4.3 – Low base current I-V characteristics                                  |      |

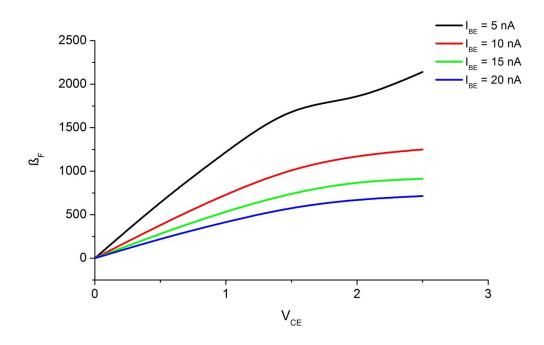

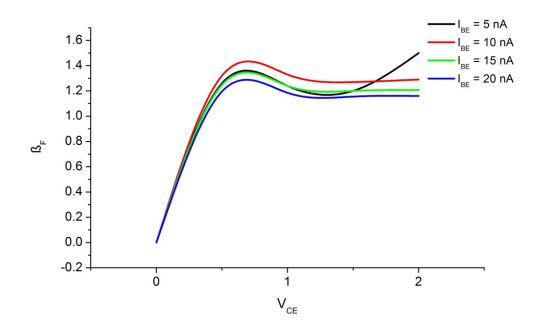

| Figure 4.4 - $\beta_F$ including ohmic current                                     | 101  |

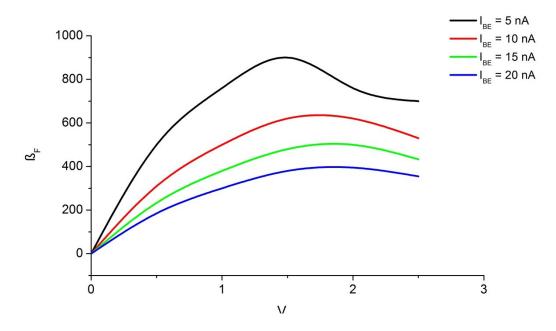

| Figure $4.5 - \beta_F$ with ohmic current subtracted                               |      |

| Figure 4.6 - $\beta_F$ after two minutes under test                                |      |

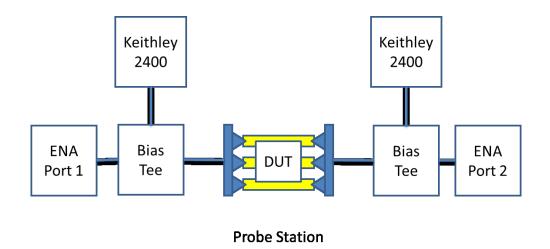

| Figure 4.7 – Experimental setup for S-parameter measurements                       |      |

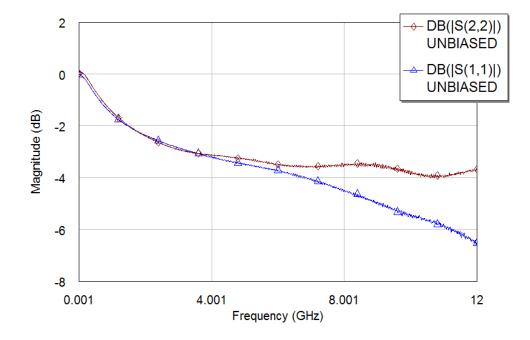

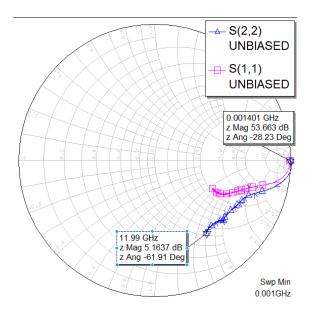

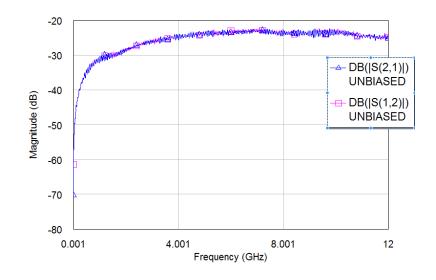

| Figure $4.8 - S_{11}$ and $S_{22}$ for an unbiased BJT                             |      |

| Figure 4.9 - Smith chart of $S_{11}$ and $S_{22}$ for an unbiased BJT              |      |

| Figure $4.10 - S_{21}$ and $S_{12}$ of an unbiased BJT                             |      |

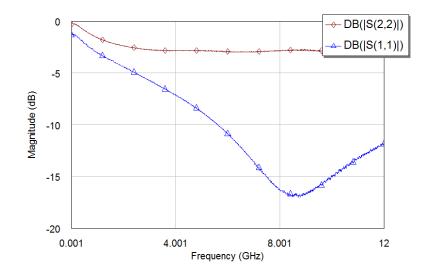

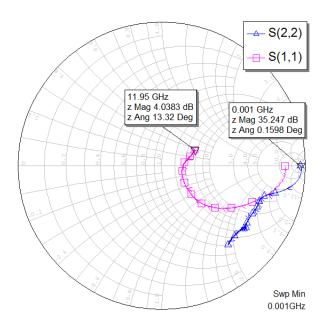

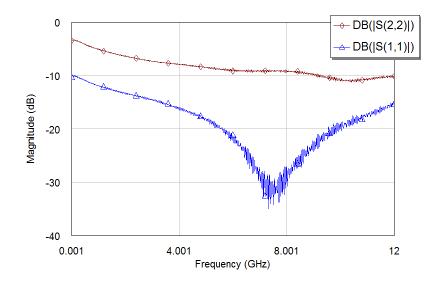

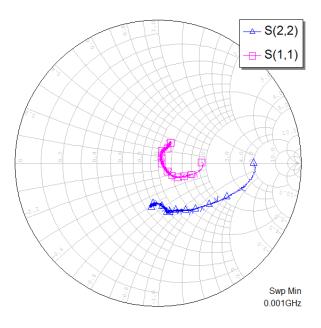

| Figure 4.11- $S_{11}$ and $S_{22}$ for an "ON – $g_m$ " biased BJT                 | 108  |

| Figure 4.12 – Smith chart of $S_{11}$ and $S_{22}$ for an "ON – $g_m$ " biased BJT |      |

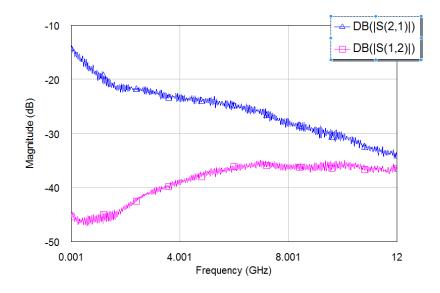

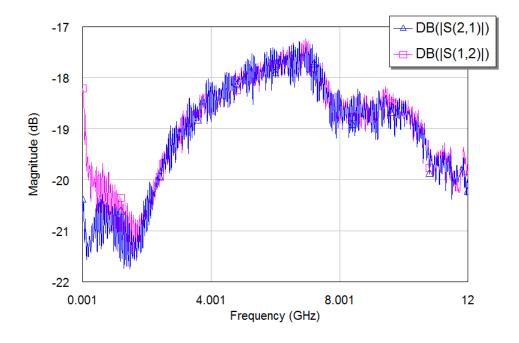

| Figure $4.13 - S_{21}$ and $S_{12}$ for and "ON - $g_m$ " biased BJT               |      |

| Figure 4.14 - $S_{11}$ and $S_{22}$ for an "ON- $\beta_F$ " biased BJT             |      |

| Figure 4.15 - Smith chart for an "ON- $\beta_F$ " biased BJT                       |      |

| Figure 4.16 - $S_{21}$ and $S_{12}$ for an "ON- $\beta_F$ " biased BJT             |      |

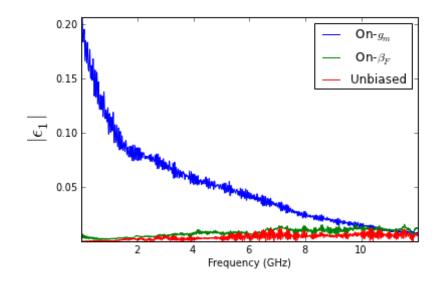

| Figure 4.17 - $\epsilon_1$ for the three biasing regimes                           |      |

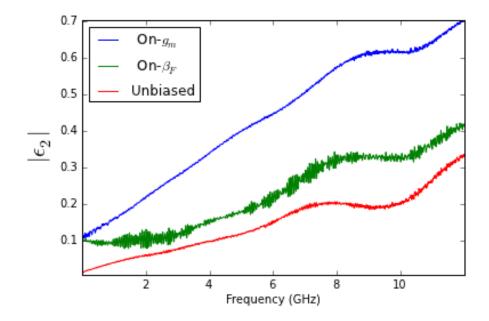

| Figure 4.18 - $\epsilon_2$ for the three biasing regimes                           |      |

| 0                                                                                  |      |

# List of Abbreviations

- AC alternating current

- BJT bipolar junction transistor

- BOX buried oxide layer

- CMOS complementary metal-oxide-semiconductor

- CPW coplanar waveguide

- DC direct current

- EDX energy dispersive x-ray microscopy

- FTDS 1H,1H,2H,2H-perfluorodecyltrichlorosilane

- HF hydrofluoric acid

- HFSS High Frequency Structure Simulator

- LPCVD low-pressure chemical vapor deposition

- LPS Laboratory for Physical Sciences, University of Maryland

- MOSFET metal-oxide-semiconductor field effect transistor

- OTS octadecyltrichlorosilane

- PECVD plasma-enhanced chemical vapor deposition

- poly-Si polycrystalline silicon

- RIE reactive ion etching

- SAM self-assembled monolayer

- SFTP surface functionalized transfer printing

- SiNM silicon nanomembrane

SOI – silicon on insulator

# Chapter 1: Introduction and Background

The focus of this project has been to develop techniques and devices for use in the growing field of flexible electronics. Flexible electronics are a class of devices that can conform to non-planar surfaces and operate under bending conditions. Due to their flexibility, they are able to operate in environments previously inaccessible to rigid chip-based electronics. This work will present new techniques for the transfer of high-quality electronic materials to flexible substrates and describe the performance and limitations of a transistor in development for flexible microwave applications.

There are a variety of methods and materials for the fabrication of electronic devices on flexible substrates. In this study we use transfer printing, due to its scalability and the high quality of films that it is capable of producing. Whereas transfer printing of metals had previously been limited to gold films, this work presents a technique that enables transfer printing of a range of metals. A previously unreported technique for transfer of aligned monocrystalline silicon nanomembranes (SiNMs) will also be presented.

The availability of high quality metal and semiconductor films on flexible substrates has led to recent research into microwave frequency flexible electronic devices. The addition of microwave frequency devices to existing flexible technology will enable a range of new capabilities like fast, low power communication and wireless energy transfer. In this study, we present progress on the development of the first flexible microwave silicon nanomembrane bipolar junction transistor.

The second and third chapters of this thesis provide background that will be useful in the discussion of the progress we've made. The fourth chapter will describe our work in the transfer printing of metals and SiNMs. In the fifth chapter, the design and fabrication of bipolar junction transistors (BJTs) for flexible applications will be presented. This chapter will also describe the primary limitation of this device design, the effects of localized Joule heating. The sixth chapter will describe direct current and microwave electrical characterization. Finally, chapter 7 will provide conclusions based on current work and an outlook on directions for future studies.

### 1.1 Silicon Nanomembrane Background

In order to achieve microwave frequency performance on flexible substrates, a high quality flexible semiconducting material is required. SiNMs are chosen due to their high carrier mobility, flexibility, and compatibility with established complementary metal-oxide-semiconductor (CMOS) processing techniques. Previous work has demonstrated microwave frequency operation of SiNM devices, indicating that they should be a suitable material for microwave BJTs.

The flexibility of a material is a function of both material properties and geometry. Thick aluminum stock is very difficult to bend and quickly deforms plastically if bent. aluminum foil, on the other hand, is flexible can be bent easily and many times before failure. Monocrystalline silicon is similarly rigid at thicknesses above 100  $\mu$ m, and will cleave along crystalline planes when bent. At thicknesses between 1 nm and 1  $\mu$ m, however, Si is highly flexible. For instance, a SiNM with 7 nm thickness has been shown to have a bending stiffness of 8.86 MPa\* $\mu$ m<sup>4</sup>, seven orders of magnitude lower than if it were 1.5  $\mu$ m thick [1].

Over the past ten years, SiNMs have been studied as the active semiconductor in high-performance flexible devices. They consist of freestanding thin monocrystalline Si films that can be transferred to any properly prepared adhesive substrate. Once transferred, the mechanical properties of the overall device are dominated by the (much thicker) substrate, allowing for flexible monocrystalline Si devices.

SiNMs have a combination of properties that make them uniquely suited to high performance flexible electronics. They can be mechanically and epitaxially strained, which alters their band structure and conductivity. Due to their thinness, they can be patterned at the nanoscale to alter their thermal properties. Finally, their combination of high carrier mobility and flexibility make them well suited to bio-implantable and high frequency flexible devices.

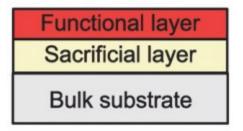

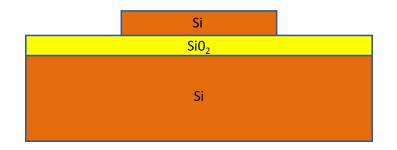

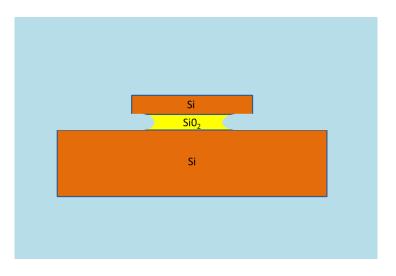

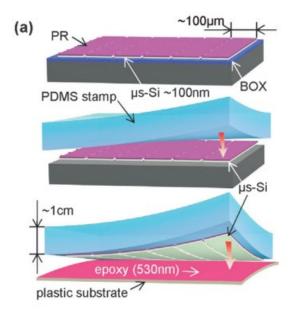

The typical method for creating freestanding nanomembranes utilizes a three-layer configuration wherein a functional layer is separated from the bulk substrate by a sacrificial layer (Figure 1.1). The sacrificial layer is then etched, decoupling the

functional layer from the bulk substrate, leaving a freestanding functional film. This technique requires a selective etch process that will completely remove the sacrificial layer but not damage the functional layer.

Figure 1.1 – Three layer configuration for nanomembrane fabrication [2]

The three-layer configuration of choice for SiNMs has been the silicon-on-insulator (SOI) wafer. In the case of SOI, both the functional layer and bulk substrate are monocrystalline Si and the sacrificial layer is  $SiO_2$ . SOI has the advantage that it is already widely used in the semiconductor industry and is commercially available.  $SiO_2$  is also a convenient sacrificial layer, because it can be selectively etched by hydrofluoric acid (HF) solutions, which have a very low etch rate for Si [3].

SOI also has the significant advantage that it can withstand high temperatures and solvent treatment which would otherwise be incompatible with most polymers. After ion-implantation, Si must be annealed to temperatures above 900 °C in order to repair crystalline damage and to move interstitial dopant species into lattice sites. Standard e-beam deposition and lift-off requires the sample to be submerged in acetone for an extended period of time. The ability to perform these processing steps on SOI and

then transfer to a flexible substrate gives SiNMs an advantage over directly-deposited semiconductors.

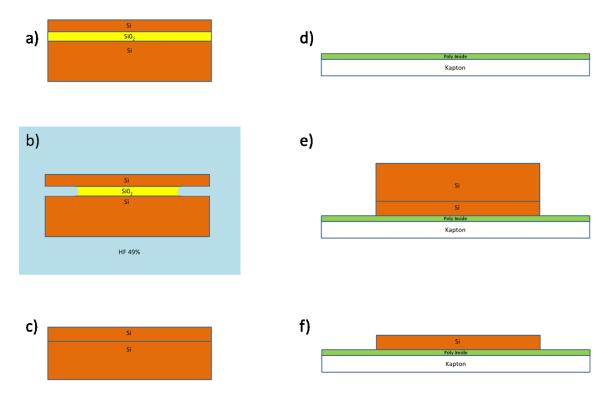

The basic SiNM transfer process is shown in figure 1.2. The functional top Si layer is partially etched to expose the underlying buried oxide (BOX) layer to the HF solution. It is then submerged in HF, which undercuts the top Si layer and releases it (Figure 1.2b, 1.2c). The weakly coupled SiNM is then brought into contact with an adhesive substrate and is transferred (Figure 1.2d-1.2f).

Figure 1.2 – Generic SiNM transfer process

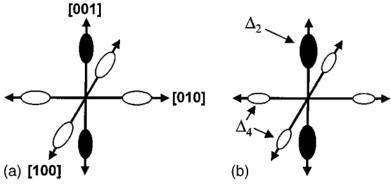

A more specific description of SiNM transfer methods will be given in chapter 2. This section will describe some of the interesting properties of SiNMs as well as their applications in medicine and high frequency flexible electronics. The first significant outcome of transferring SiNM devices to flexible substrates is the ability to apply strain. Because it is an indirect band-gap semiconductor, the conduction band of Si forms six symmetrical ellipsoids in the reciprocal lattice, two on each axis (Figure 1.3). It is well known that strain on the Si crystal lattice breaks the six-fold symmetry of the conduction band, reducing inter-valley phonon scattering. Furthermore, the shape of the ellipsoids is distorted, lowering the effective mass of electrons in the conduction band in the direction of tensile strain. These two effects combine to increase the mobility of electrons in the conduction band. This increased mobility decreases switching time, and strained Si is widely used in the microprocessor industry [4].

Figure 1.3 - Si conduction band in the reciprocal lattice [5]

A typical method for introducing strain to the Si lattice is to introduce germanium (Ge) to the Si during growth. Ge atoms have the same valence state as Si, but are larger and introduce an isotropic tensile strain to the lattice. This type of strain can be achieved by adding Ge during wafer fabrication, as well as during epitaxy. Using this

method, electron mobility can be enhanced to more than double that of unstrained Si [6].

In the case of SiNMs, however, strain can also be applied mechanically, through the bending or stretching of a flexible substrate. When SiNMs are transferred, the overall mechanical properties of the device are dominated by the new substrate. By bending or straining the substrate, local strain at its surface is transferred to the SiNM, altering its electrical properties.

The effects of strain can be exploited in order to increase device performance. Three layer epitaxial Si/SiGe/Si membranes are, when released, under strain even while elastically relaxed. Before membrane release the SiGe layer is under compressive strain, due to the larger Ge atoms. Once released, the stress due to compression in the SiGe layer introduces tensile strain to the two Si layers, and strain is shared between all three layers (Figure 1.4). Metal-oxide-semiconductor field-effect transistors (MOSFETs) made from this strained heterostructure exhibit significantly higher field-effect mobility than identical devices fabricated from Si alone (Figure 1.5) [7].

Figure 1.4 - Elastically relaxed strain sharing membrane transfer [7]

Figure 1.5 - Field effect mobility for strained and unstrained SiNM MOSFETs [7]

The effect of strain on SiNMs has been exploited to create piezoresistive flexible strain sensors (Figure 1.6) [8]. The heterogeneous system including the Si device and flexible substrate was shown to have a gauge factor (ratio of percent change in electrical resistance to mechanical strain) of approximately 43. The devices were

found to be mechanically robust with no appreciable change in operation after 1000 cycles at bending radii as small as 12mm.

Figure 1.6 - Piezoresistive SiNM strain sensor [8]

In addition to altering the electrical properties of SiNMs using strain, their thermal properties can be altered using advanced nanopatterning techniques. By introducing scattering sites for phonons, the thermal conductivity can be suppressed. This low thermal conductivity (combined with high electrical conductivity due to heavy doping) could lead to the use of Si as a thermoelectric material.

The figure of merit for thermoelectric materials is ZT.

$$ZT = \frac{\sigma S^2 T}{\lambda}$$

Eq. 1.1

It is proportional to electrical conductivity  $\sigma$  and inversely proportional to thermal conductivity  $\lambda$ . Monocrystalline Si can be doped to achieve high electrical

conductivity, but its relatively high thermal conductivity (1.3  $Wcm^{-1} \circ C^{-1}$ ) has prevented its use an efficient thermoelectric material.

Using block copolymer lithography, however, holes can be etched into the SiNM at a size and spacing that is on the order of a phonon's mean free path but larger than the mean free path of an electron. This creates preferential phonon scattering, reducing thermal conductivity by a factor of 25 without degrading electrical conductivity [9].

The thermoelectric figure of merit ZT of these "holey" SiNMs was measured to be as high as 0.4 at room temperature (Figure 1.7), better than non-patterned Si by a factor of nearly 50. This ZT value also brings Si within an order of magnitude of the highest performing telluride thermoelectric materials which have a room temperature ZT between 2 and 2.5 [10].

Figure 1.7- ZT for "holey" and "non-holey" SiNMs

Silicon has a significant advantage over Te based thermoelectric materials in that it is naturally abundant and non-toxic. A significant limitation to SiNMs' adoption as a thermoelectric material is also related to their nanoscale thickness. Because they are so thin, the overall power density of a SiNM thermoelectric device is limited. It has been theorized that bulk 3D Si with nanopores of comparable size and pitch could have similar thermoelectric properties to holey SiNMs [11]. The ability to manufacture nanoporous Si on an industrial scale could lead to the use of Si and a thermoelectric material.

Over the past five years, SiNMs have been investigated for possible integration into bio-implantable devices. SiNMs can conform to the surface of skin and organs without inhibiting their electrical performance. They can be patterned into serpentine shapes and applied to pre-strained substrates so that they stretch as well as bend [12]. Si is nontoxic in the quantities present in SiNM devices and will dissolve into the body on the timescale of days. Coatings have been developed that can provide stable device performance for months, with rapid transience thereafter [13].

SiNM-based biological sensors have been demonstrated to be effective in several animal trials, and have begun human medical testing [14]. High resolution SiNM sensor arrays were applied directly to the brains of cats and oscillatory sleep signals were observed at a spatial resolution below that of conventional subdural electrodes [15]. Large area sensors on pigs' hearts were able to detect the propagation of electrical signals as the heart beats, possibly leading to a new way of diagnosing arrhythmia [16]. High spatial resolution sensors were also used to monitor the temperature of the surrounding tissue during rf and cryo-ablation, which could minimize tissue damage during those procedures in the future. Most recently, a human medical trial was performed where SiNM based devices were placed on the skin to monitor temperature, moisture and other data during the healing of surgical wounds [14].

Flexible implantable devices have shown great promise for minimally invasive monitoring, but previously reported devices all require a physical connection to the outside world for power and communications. These devices would benefit greatly from wireless communication and charging. Microwave frequency transmission between these devices and the outside world could potentially overcome both of these challenges and enable truly non-invasive monitoring and treatment.

Passive and active microwave frequency SiNM devices have been demonstrated. The microwave performance of flexible PIN diodes has been measured under conditions of strain (Figure 1.8) [17]. A 10% reduction in internal parasitic impedance was shown at a strain of 0.4% while in the ON state. Isolation in the OFF state was not shown to degrade under strain conditions.

Figure 1.8 – Measurement of strained SiNM PIN diodes

The first active high-frequency SiNM device was a field-effect transistor with a maximum oscillation frequency ( $f_{MAX}$ ) of 515 MHz [18]. These devices were doped using phosphorous diffusion at high temperature. This design was improved upon by a subsequent study that used ion implantation as the doping method. Ion implantation gives better lateral and vertical spatial resolution to doped regions than diffusion does, and these devices reported a  $f_{MAX}$  of 3.1 GHz [19]. Improvements in gate alignment lead to FETs with reported  $f_{MAX}$  values of 7.8 GHz [20] and most recently 12 GHz [21] (Figure 1.9).

Figure 1.9 – Alignment of microwave frequency SiNM FET [21]

All previously reported active SiNM devices have been FETs. While passive PIN devices have been studied, there have been no reports of the active NPN or PNP BJT configuration at any frequency. While FETs are the most common configuration in use today, BJTs are still preferred for certain applications like high frequency switching and amplification. The addition of BJTs to existing FET based SiNM technology would also pave the way for SiNM based bipolar-CMOS (BiCMOS) technology, which exploits the advantages of both types of transistor in a single device.

In conclusion, SiNM technology has shown promise in a wide range of applications. Previous work has shown that SiNM based devices can exhibit microwave frequency performance. Due to their flexibility, high mobility, and compatibility with standard Si processing techniques SiNMs were chosen as the semiconducting material for this project. In this work, we fabricate SiNMs using an established method as well as demonstrate a previously unreported SiNM transfer technique. We also design, fabricate, and characterize BJTs on SOI for integration into SiNM technology.

### 1.2 Theoretical Background

### 1.2.1 Bipolar Junction Transistors

The device chosen for development in this project is the BJT. Previously reported SiNM microwave devices in the MOSFET configuration indicate that it should be possible to fabricate microwave SiNM BJTs. While less common than MOSFETS, BJTs are preferred for certain applications such as fast switching and signal amplification.

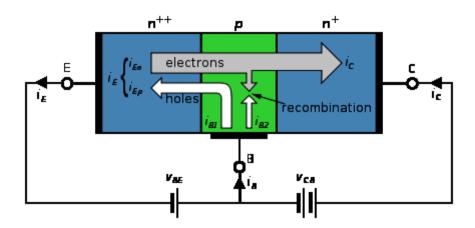

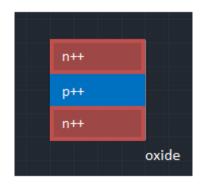

BJTs are an electrical device consisting of three regions of alternating semiconductor type. An NPN BJT consists of two n-type semiconductors separated by a thin p-type semiconductor, and a PNP consists of two p-type semiconductors separated by a narrow n-type region. The interfaces of the semiconductor regions form PN junctions, whose properties determine the operation conditions of the device. Direct current (DC) device performance is described using the Ebers-Moll model and DC output conditions are used to bias the device for alternating current (AC) signal gain.

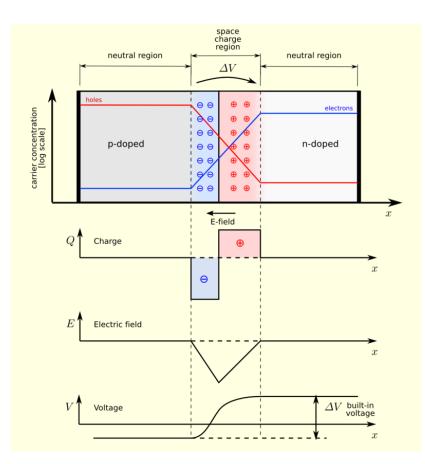

The fundamental constituent of the BJT is the PN junction (Figure 1.10). When a ptype semiconductor comes into contact with an n-type semiconductor, free electrons diffuse into the p-type material and free holes diffuse into the n-type material. These minority carriers leave behind ionized donor and acceptor atoms and then recombine with carriers of the opposite type. The result is a region on either side of the junction that is depleted of free charge carriers called the depletion region. In this region, the space charge from the ionized donors creates an electric field in the opposite direction of carrier diffusion. In equilibrium the force of this electric field prevents further diffusion of charge carriers. This field also creates a built-in potential across the interface.

Figure 1.10 – PN junction

When a PN junction is reverse biased, the applied potential adds to the built-in voltage and the depletion region widens. Under reverse bias conditions, only a very small current flows due to thermal diffusion of free carriers into the depletion region. This current is called the reverse saturation current and is roughly independent of the reverse bias.

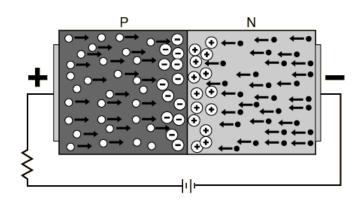

If the PN junction is forward biased at a value higher than the built-in potential, electrons move freely across the junction and become minority carriers in the p type material. These minority carriers then diffuse some distance before recombining with holes. Simultaneously, holes diffuse into the n type material and recombine with electrons. The net effect of this diffusion and recombination is forward current flow (Figure 1.11). The average distance a carrier will travel before recombination is called the minority carrier diffusion length.

Figure 1.11 – Forward biased PN junction [22]

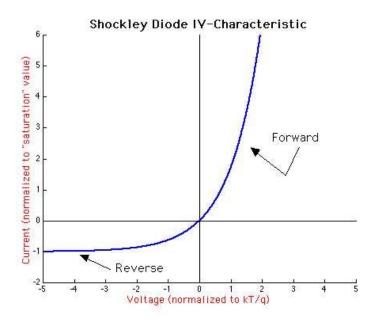

The flow of current under forward bias but not under reverse is the defining property of a PN junction. The current flowing across a PN junction is given by the Shockley diode equation

$$I = I_S \left( \frac{qV_D}{nkT} - 1 \right)$$

Eq. 1.2

Where I is the diode current,  $I_S$  is the reverse saturation current, q is the charge of the electron,  $V_D$  is the applied diode voltage, k is Boltzmann's constant, T is the temperature and n is an ideality factor with n=1 being an ideal PN junction. The current-voltage output of an ideal PN junction is shown in Figure 1.12.

Figure 1.12 – Shockley diode IV characteristic [23]

A BJT is a three terminal device consisting of two PN junctions, with each terminal connecting to one of the three NPN or PNP regions. The configuration chosen for this project is NPN, so further treatment will describe this configuration. The three terminals are called the emitter, base, and collector.

There are four modes of operation depending on the relative biasing of each of the PN junctions: forward active, reverse active, saturation, and cutoff. The biasing of the two junctions in each of these modes is given in Table 1.1. Among these, the highest DC current gain and AC signal gain can be achieved in forward active mode. A schematic of a BJT in forward active mode is given in Figure 1.13.

| Base-Emitter Bias | Base-Collector Bias | Mode           |

|-------------------|---------------------|----------------|

| Forward           | Forward             | Saturation     |

| Reverse           | Reverse             | Cutoff         |

| Reverse           | Forward             | Reverse active |

| Forward           | Reverse             | Forward active |

Table 1.1 – BJT modes of operation

Figure 1.13 – BJT, forward active mode

In forward active mode, the base-emitter junction is forward biased and the base collector junction is reverse biased. A small current going into the base region controls a large current between the emitter and collector.

In the limit of a very wide base region, the presence of a reverse biased base-collector junction would prevent any current from flowing between the collector and emitter. Majority carriers in both the base and collector are not able to cross the base-collector depletion region. This behavior will be observed in chapter 5 when we observe the effects of Joule heating on devices. Current will only flow if a BJT's base region is narrow compared to the minority carrier diffusion length.

When the base-emitter junction is forward biased and current flows from the base into the emitter, electrons are able to diffuse into the base region as minority carriers. Some then recombine with holes to constitute the base current. Others will diffuse across to the base-collector depletion region and are swept into the collector by the built-in electric field of the base-collector PN junction. This diffusion across the base region is the source of current gain. In order to maximize the number of electrons that diffuse across to the base-collector depletion region, the dopant concentration in the emitter is typically several orders higher than that of the base. The base region is also designed to be very narrow, typically a small fraction of the minority carrier diffusion length.

With the proper geometry and dopant concentrations, it is possible to design a BJT such that the current due to electrons diffusing across the base region is many times larger than the current used to forward bias the base-emitter junction. This ratio is called the forward common emitter current gain,  $\beta_F$  and is an important figure of merit for BJTs.

$$\beta_F = \frac{I_C}{I_B}$$

Eq. 1.3

For modern Si BJTs  $\beta_F$  has a typical value of 100-300, but can be as high as 1000. The other important figure of merit for this study is transconductance. Transconductance,  $g_m$  is defined as the change in collector current divided by the change in base voltage.

$$g_m = \frac{\partial I_{CE}}{\partial V_{BE}} = \frac{I_{CE}}{V_T}$$

Eq. 1.4

where  $V_T$  is the thermal voltage, approximately 26 mV at room temperature. Current gain and transconductance will play an important role when biasing our BJTs for AC signal gain.

The DC output characteristics of a BJT can be described using the Ebers-Moll model. This model extends the Shockley diode equation to include the currents at all three terminals. The full Ebers-Moll model states that

$$i_{c} = I_{s} \left( e^{\frac{qV_{BE}}{nkT}} - e^{\frac{qV_{BC}}{nkT}} \right) - \frac{I_{s}}{\beta_{R}} \left( e^{\frac{qV_{BC}}{nkT}} - 1 \right)$$

Eq. 1.5

$$i_B = \frac{I_S}{\beta_F} \left( e^{\frac{qV_{BE}}{nkT}} - 1 \right) + \frac{I_S}{\beta_R} \left( e^{\frac{qV_{BC}}{nkT}} - 1 \right)$$

Eq. 1.6

$$i_E = I_S \left( e^{\frac{qV_{BE}}{nkT}} - e^{\frac{qV_{BC}}{nkT}} \right) + \frac{I_S}{\beta_F} \left( e^{\frac{qV_{BE}}{nkT}} - 1 \right)$$

Eq. 1.7

where  $i_C$  is the collector current,  $i_B$  is the base current,  $i_E$  is the emitter current, n is an ideality factor and  $\beta_R$  is the reverse common emitter current gain. In forward active mode, we can use the approximation:

$$V_{BC} < 0, \quad \frac{qV_{BC}}{nkT} \sim 1$$

Eq. 1.8

The Ebers-Moll equations then become

$$i_{c} = I_{s} \left( e^{\frac{q V_{BE}}{n k T}} - 1 \right)$$

Eq. 1.9

$$i_B = \frac{I_S}{\beta_F} \left( e^{\frac{qV_{BE}}{nkT}} - 1 \right) = \frac{i_C}{\beta_F}$$

Eq. 1.10

$$i_E = I_s \frac{\beta_F + 1}{\beta_F} \left( e^{\frac{qV_{BE}}{nkT}} - 1 \right) = \frac{\beta_F + 1}{\beta_F} i_C$$

Eq. 1.11

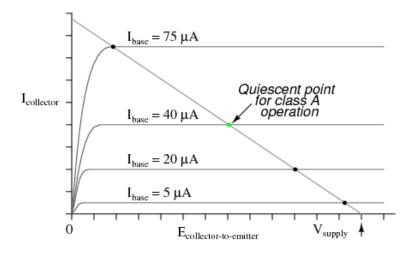

Proper biasing for AC signal gain is usually determined from the BJT's currentvoltage output characteristics (Figure 1.14).  $i_C$  is measured as  $V_{CE}$  is swept while  $i_B$  is held constant. This process is repeated for different values of  $i_B$ . In forward active mode  $i_C$  is nearly independent of  $V_{CE}$  but strongly dependent on  $i_B$ . For this reason, a BJT in forward active operation is considered a current controlled current source.

The biasing conditions for AC signal gain are usually chosen somewhere in the middle of the forward active region, so that small changes in  $i_B$  and  $V_{CE}$  do not take the device out of forward active mode.

Figure 1.14 – Quiescent point on DC IV curve [24]

The biasing conditions for AC operation are obtained from the quiescent point, which is chosen to be in a biasing region of linear response. The value of  $V_{CE}$  during AC operation is equal to the value of  $V_{CE}$  at the quiescent point. The value of  $i_B$  under AC operation is the  $i_B$  value of the curve that intersects the quiescent point. In Figure 1.14, that value is  $i_B = 40 \ \mu$ A. In order to determine the DC bias for  $V_{BE}$  given a value for  $i_B$ , a current-voltage sweep of the base-emitter junction is taken, and the corresponding  $V_{BE}$  is obtained.

In summary, BJTs use the properties of PN junctions along with minority carrier diffusion to create gain. When in forward active mode they operate as a current controlled current source. BJT behavior under DC conditions is described using the Ebers-Moll model. DC current-voltage data can be used to obtain biasing conditions for AC signal gain.

#### 1.2.2 Microwave Frequency Electronics

Existing flexible device technology stands to benefit significantly from microwave frequency technology. Low-power directional microwave communication and wireless inductive energy transfer could have applications from implantable medical devices to space exploration. At microwave frequencies, the standard lumped-element model starts to become invalid and a new set of concepts is necessary to describe microwave networks. In order to develop flexible microwave devices, it is necessary to have an understanding of some basic principles of microwave engineering.

Microwave electronics are used extensively in telecommunications, the military, and increasingly in consumer electronics. Microwave signals can transmit data at high speed using directional, low power antennas. The microwave regime is also the point at which the wavelength of the electromagnetic signal becomes comparable to the size of practical devices. As a consequence, microwave signals behave and must be treated differently than lower frequency AC signals. In this section we will review some relevant microwave frequency concepts that will be used in device analysis.

All electromagnetic signals obey the Maxwell equations. Because it is not feasible in practice to obtain solutions to Maxwell's equations at all points in space and time, electrical models are employed that give approximate solutions for the equations based on key assumptions. For DC and lower frequency AC signals, the lumped element model is used. This model treats components as discrete units, with

properties of resistance, capacitance, and inductance. A key assumption of this model, however, is that the phase of the AC signal is the same at all points in a discrete element. In other words, the unit is much smaller than the signal's wavelength.

As the wavelength of an electromagnetic signal becomes comparable with the size of the device, the phase of the signal will vary appreciably from one end of the device to the other. At this point the assumption of constant phase is no longer valid, and the lumped element model no longer applies.

In order to understand signal propagation through devices and along transmission lines, a set of microwave engineering concepts has been developed. In this section we will establish some new definitions for impedance and signal transmission and reflection, as well as scattering parameters and the Smith chart. In doing so we will follow the formalism used in *Microwave Transistor Amplifiers* by Guillermo González [25].

A sinusoidal signal in both voltage and current can be described as the real part of its complex exponential function

$$v(x,t) = Re[V(x)e^{-i\omega t}]$$

$$i(x,t) = Re[I(x)e^{-i\omega t}]$$

Eq. 1.13

In a lossless medium, these two signals satisfy the wave equation

$$\frac{d^2 V(x)}{dx^2} - \gamma^2 V(x) = 0$$

Eq. 1.14

$$\frac{d^2 I(x)}{dx^2} - \gamma^2 I(x) = 0$$

Eq. 1.15

where  $\gamma = \alpha + i\beta$  and  $\alpha$  and  $\beta$  are the attenuation and propagation constants. For a lossless transmission line,  $\alpha = 0$ .

At every point along this line, there is a ratio between the amplitude of the voltage and that of the current. We define this ratio as the point's characteristic impedance.

$$Z(x) = \frac{V(x)}{I(x)}$$

Eq. 1.16

And for uniform transmission, this value is constant.

$$Z(x) = Z_0$$

Eq. 1.17

We will see the effects of a non-uniform characteristic impedance below. The general solutions to the wave equations then become

$V(x) = Ae^{-\gamma x} + Be^{\gamma x}$ Eq. 1.18

$$I(x) = \frac{A}{Z_0} e^{-\gamma x} - \frac{B}{Z_0} e^{\gamma x}$$

Eq. 1.19

In order to understand the effects of a change of characteristic impedance, imagine that an incident wave travelling in the forward direction terminates at an interface. Some fraction will then be transmitted through the interface and the rest will be reflected. We define  $\Gamma_0$  as the reflection coefficient, which is equal to the ratio of the amplitude of the reflected wave to the amplitude of the transmitted wave.

$$\Gamma_0 = \frac{B}{A}$$

Eq. 1.20

The general solutions at this interface are then

$$V(x) = A(e^{-\gamma x} + \Gamma_0 e^{\gamma x})$$

Eq. 1.21

$$I(x) = \frac{A}{Z_0} e^{-\gamma x} - \frac{B}{Z_0} e^{\gamma x}$$

Eq. 1.22

We can then define the characteristic impedance at the interface the same way we did at points along the transmission line.

$$Z_{L} = \frac{V(x)}{I(x)} = Z_{0} \frac{e^{-\gamma x} + \Gamma_{0} e^{\gamma x}}{e^{-\gamma x} - \Gamma_{0} e^{\gamma x}} = Z_{0} \frac{1 + \Gamma_{0}}{1 - \Gamma_{0}}$$

Eq. 1.23

Or, solving for  $\Gamma_0$

$$\Gamma_0 = \frac{Z_L - Z_0}{Z_L + Z_0}$$

Eq. 1.24

The reflection at an interface is directly proportional to the difference in characteristic impedance on either side. The reflection coefficient approaches unity (total reflection) as the load impedance approaches infinity. It also approaches negative unity as the load impedance approaches zero. This situation corresponds to a total reflection with a phase shift of 180°.

Maximum transmission of a signal across an interface occurs when the characteristic impedance must be the same on both sides. This corresponds to a reflection coefficient of  $\Gamma_0 = 0$  and 100 percent transmission. In microwave electronics, if two components have the same characteristic impedance they are said to be "impedance matched" and no signal is reflected when passing from one to the other. This concept will be used in the design of our coplanar waveguide electrodes.

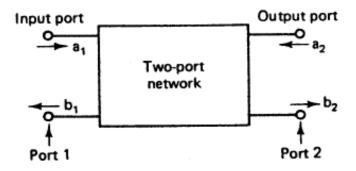

In microwave electronics, a transistor is modeled as a two-port network (Figure 1.15). A two-port network has an input port (Port 1) and an output port (Port 2). The incident signals on port 1 and 2 are  $a_1$  and  $a_2$ , and the reflected signals at port 1 and 2 are  $b_1$  and  $b_2$ , respectively.

Figure 1.15 – Two-port network [25]

A BJT is a three terminal device, and in order to treat it as a two-port network one terminal must be shared between two ports. The common-emitter configuration was chosen for this project because it generally gives the highest signal gain. In this configuration, the emitter is connected to the ground for both port 1 and port 2.

Two port networks can be characterized by their scattering (S) parameters. These parameters are defined as the ratios between the different incident and reflected signals at the two ports.

$$S_{11} = \frac{b_1}{a_1}\Big|_{a_2=0} \qquad S_{21} = \frac{b_2}{a_1}\Big|_{a_2=0} \qquad \text{Eqs. 1.25, 1.26}$$

$$S_{12} = \frac{b_1}{a_2}\Big|_{a_2=0} \qquad S_{22} = \frac{b_2}{a_2}\Big|_{a_2=0} \qquad \text{Eqs. 1.27, 1.28}$$

$S_{11}$  is the reflection coefficient ( $\Gamma_0$ ) for an incident signal on port 1.  $S_{22}$  is the reflection coefficient for an incident signal on port 2. For an impedance matched

network,  $S_{11}$  and  $S_{22}$  will be small and for a poorly matched network they are close to 1.  $S_{21}$  is the forward signal gain of the device and  $S_{12}$  is the reverse signal gain. For impedance matched networks,  $S_{21}$  and  $S_{12}$  are close to 1, for mismatched networks they are low and for active devices with signal gain they are greater than 1.

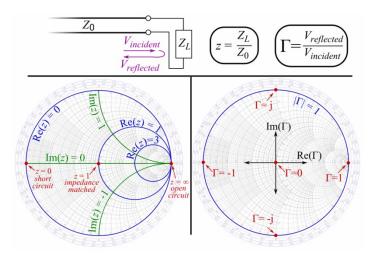

S-parameters are often displayed visually using a Smith Chart (Figure 1.16) [26].

Figure 1.16 – The Smith Chart [27]

The Smith chart can be read quickly to obtain both complex impedance and complex reflection coefficient. Set in a complex plane, the x axis of the Smith chart represents real impedance (resistance). Impedance is scaled so that the origin corresponds to the real impedance of a matched system (for our case 50  $\Omega$ ). The left end of the real axis corresponds to an impedance of zero and the right end corresponds to an impedance of infinity.

The vertical axis corresponds to imaginary impedance or reactance. The top of the vertical axis represents an infinite inductive load and the bottom represents an infinite

capacitive load. The center of the vertical axis represents zero net imaginary impedance.

Circles of constant normalized real and imaginary impedance are shown in Figure 2. A point's real and imaginary impedance can easily be determined visually by the two circles it intersects.

The real and imaginary components of the complex reflection coefficient are simply the Cartesian coordinates on the Smith chart. The magnitude of the reflection coefficient is its radial distance from the center. Networks with well-matched impedance will appear near the center of the Smith chart and networks with poorly matched impedance will appear toward the edges.

The behavior of microwave networks requires a different set of concepts than is used at lower frequencies. In our characterization of microwave devices, we will use the concepts of characteristic impedance, signal reflection and transmission, and Sparameters. In order to show the real and imaginary components of the S-parameters, it will be useful to view them on a Smith chart. The design of our electrode configuration will be based on the concept of impedance matching, in order to maximize signal transmission and minimize reflection. For our BJT devices, S-parameters will be examined to show transmission and reflection at both biased and unbiased conditions.

## 1.2.3 Tapered Coplanar Waveguide Electrodes

We saw, in Section 1.2.2, how characteristic impedance affects the transmission of microwave signals across an interface. In order to characterize a device's microwave performance, all components connected to it must be impedance matched, including the on-chip electrodes. At lower frequencies, any geometrical layout with suitably low resistance, capacitance and inductance is suitable to transmit AC signal to a device. At microwave frequencies, however, the characteristic impedance of an electrode depends critically on its geometry.

We require an electrode configuration that is impedance matched to our test equipment, which has a characteristic impedance of 50  $\Omega$ . Because we are depositing metals onto a flat surface, a planar structure is additionally required. There are a number of planar structures capable of transmitting microwave signals such as microstrips, slotlines, and coplanar strips. The configuration chosen for this project was the coplanar waveguide (CPW). A CPW is compatible with the BJT's three terminal geometry and with the resolution of our photolithography process.

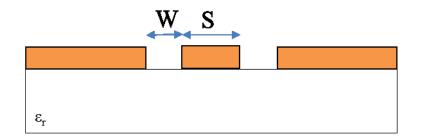

A CPW consists of three metal strips on top of a dielectric substrate (Figure 1.17). The two outer strips constitute the ground plane and in practice are much wider than the center strip. An ideal coplanar waveguide has an infinitely thick substrate and infinitely wide ground planes.

Figure 1.17 – Coplanar waveguide

The characteristic impedance of an ideal CPW is given by the expression [28]

$$Z_0 = \frac{1}{Cv_{ph}} = \frac{30\pi}{\sqrt{\epsilon_{re}}} \frac{K'(S/(S+2W))}{K(S/(S+2W))}$$

Eq. 1.29

where S is the half-width of the center strip and W is the width of the gap, K(x) is the complete elliptic integral of the first kind and

$$K'(x) = K\left(\sqrt{1 - x^2}\right)$$

Eq. 1.30

The characteristic impedance of an ideal CPW depends only on the center trace width, gap spacing and dielectric constant of the substrate. In practice, CPWs must have finite dielectric thickness and a constant ground plane width. Additionally, CPWs on SOI have two dielectric layers with different dielectric constants corresponding to the thin buried oxide layer and the thick Si handle wafer. These non-ideal properties of a CPW must be taken into account when designing CPW electrodes. The first non-ideal characteristic is that the ground planes must have a finite width and the dielectric must have a finite thickness. The characteristic impedance of a CPW with finite width ground planes and a single dielectric layer of finite thickness has been approximated using the conformal mapping method [28]. It is given by

$$Z_0 = \frac{30\pi}{\sqrt{\epsilon_{\rm re}}} \frac{K'(k_2)}{K(k_2)}$$

Eq. 1.31

where

$$k_2 = \frac{a}{b} \sqrt{\frac{1 - b^2/c_0^2}{1 - a^2/c_0^2}}$$

Eq. 1.32

$$\epsilon_{re} = 1 + \frac{\epsilon_r - 1}{2} \frac{\mathrm{K}(k_3)}{\mathrm{K}'(k_3)} \frac{\mathrm{K}'(k_2)}{\mathrm{K}(k_3)}$$

Eq. 1.33

$$k_{3} = \frac{\sinh(\frac{\pi a}{2h})}{\sinh(\frac{\pi b}{2h})} \sqrt{\frac{1 - \sinh^{2}(\frac{\pi a}{2h})/\sinh^{2}(\frac{\pi c_{0}}{2h})}{1 - \sinh^{2}(\frac{\pi b}{2h})/\sinh^{2}(\frac{\pi c_{0}}{2h})}}$$

Eq. 1.34

a is equal to half of the center trace width (S/2 in Figure 1), b is equal to the distance from the center of the CPW to the ground plane (S/2+W in Figure 1),  $c_0$  is the width of the ground plane, h is the thickness of the substrate and  $\epsilon_r$  is the relative dielectric constant of the substrate.

This value approaches the ideal approximation as ground plane width and dielectric thickness approach infinity. The method to account for the presence of a two-layer

dielectric has been previously reported for the case of infinite ground planes [29]. In this method, a fill factor is included in the expression for effective relative dielectric constant ( $\epsilon_{rs}$ ) to account for the two layers' thicknesses and dielectric constants. This same method can be applied to the above equations to give the impedance of a CPW with finite ground planes and a two-layer finite dielectric thickness. The new expression for  $\epsilon_{rs}$  is

$$\epsilon_{re} = 1 + \frac{\epsilon_{r1} - \epsilon_{r2}}{2} \frac{K(k_4)}{K'(k_4)} \frac{K'(k_2)}{K(k_2)} + \frac{\epsilon_{r2} - 1}{2} \frac{K(k_5)}{K'(k_5)} \frac{K'(k_2)}{K(k_2)}$$

Eq. 1.35

where

$$\begin{aligned} k_{4} &= \frac{\sinh(\frac{\pi a}{2h_{1}})}{\sinh(\frac{\pi b}{2h_{1}})} \sqrt{\frac{1 - \sinh^{2}(\frac{\pi a}{2h_{1}})/\sinh^{2}(\frac{\pi c_{0}}{2h_{1}})}{1 - \sinh^{2}(\frac{\pi b}{2h_{1}})/\sinh^{2}(\frac{\pi c_{0}}{2h_{1}})}} \end{aligned}$$

Eq. 1.36

$$k_{5} &= \frac{\sinh(\frac{\pi a}{2(h_{1} + h_{2})})}{\sinh(\frac{\pi b}{2(h_{1} + h_{2})})} \sqrt{\frac{1 - \sinh^{2}(\frac{\pi a}{2(h_{1} + h_{2})})/\sinh^{2}(\frac{\pi c_{0}}{2(h_{1} + h_{2})})}{1 - \sinh^{2}(\frac{\pi b}{2(h_{1} + h_{2})})/\sinh^{2}(\frac{\pi c_{0}}{2(h_{1} + h_{2})})}}$$

Eq. 1.36

$h_1$  and  $h_2$  are the thicknesses of the two dielectric layers and  $\epsilon_{r1}$  and  $\epsilon_{r2}$  are their relative dielectric constants.

Using the above expressions along with the known dielectric constants of Si and SiO<sub>2</sub> it is possible to calculate the characteristic impedance of a CPW on SOI of any geometry. Alternatively, the impedance can be set at 50  $\Omega$  and a gap spacing (b-a)

can be calculated for a given trace width (2a) and ground plane thickness ( $c_0$ ). Using this method, an impedance matched CPW can be calculated for any arbitrary trace width. Due to the presence of elliptic integrals, the above expressions must be solved numerically.

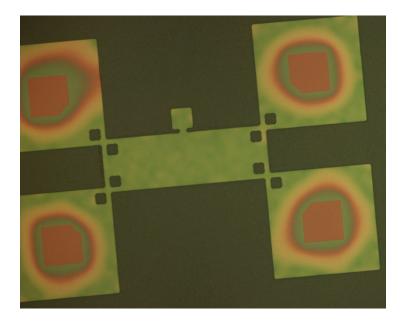

The final important consideration in the design of the CPW electrode is the size disparity between the microwave probes and the device under test. In order to minimize internal parasitic resistance in our devices, they were designed to be as small as the photolithography tool at LPS could reliably produce. The resulting total device width was 8  $\mu$ m, with contact metal traces separated by approximately 1.5  $\mu$ m. The ground-signal-ground test probes on our probe station have a much larger separation, 150  $\mu$ m between probes. While smaller probes can be purchased, the smallest commercially available probes have a 50  $\mu$ m spacing. Even if suitably spaced probes could be obtained, the probe station does not accommodate alignment at the 1.5  $\mu$ m scale.

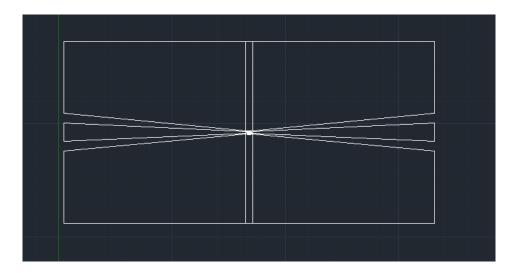

Due to these considerations, it is necessary to employ a tapered CPW electrode configuration (Figure 1.18). The probes make contact at the ends where the center trace width is 50  $\mu$ m, well within the alignment capabilities of the probe station. The device is in the center, where the center trace width is 1.7  $\mu$ m. As the center trace narrows, the spacing must also be adjusted in order to maintain a characteristic impedance of 50  $\Omega$ .

Figure 1.18 – Tapered CPW design

In order to maintain the correct spacing at all points along the waveguide, a Python script was written to calculate the characteristic impedance at every point along the taper. The script uses Newton's method to solve for W given a trace width S, and a characteristic impedance  $Z_0 = 50 \Omega$ . The output is an Autocad macro that draws the taper with the correct spacing. The resulting Autocad shape was then used in the photomask design file.

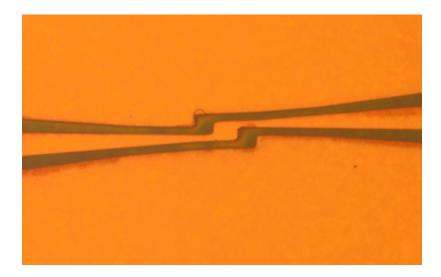

In order to use this tapered CPW design with confidence, the electrode configuration is also characterized. The structure used for electrode testing is shorted where the device would otherwise be (Figure 1.19). This allows us to test the CPW itself, independent of the effects of the Si BJT.

Figure 1.19 – Shorted electrode configuration

This "shorted" configuration was chosen because it better represents the final device than an electrode that passes straight through. The taper coming in from the left will contact a different device region than the one coming in from the right. In the center region, the spacing of the CPW is interrupted, due to the shift associated with making contact to two different terminals of the Si device. This interruption will necessarily cause some impedance mismatch. High frequency modeling and electrode fabrication and testing were performed to determine if the reflection due to this interruption is suitably low.

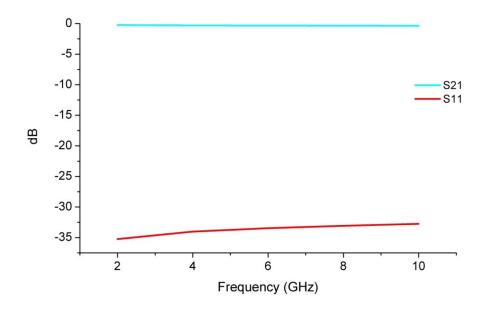

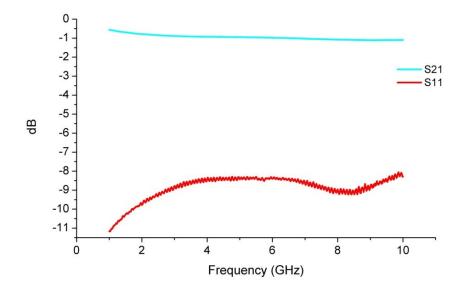

The structure is imported into the Ansys High Frequency Structure Simulator (HFSS). Port 1 is placed along the left end of the taper, with the signal along the center trace and the outer planes set at ground and Port 2 is placed along the right end. A frequency sweep is performed and S-parameters were obtained from the software. The simulation result shows very high transmission of the signal through the taper (Figure 1.20). Approximately 96% of the signal is transmitted, and only 2% is reflected. Signal reflection is attributed to a small impedance mismatch at the center of the taper, where the shorted electrodes are located. The remaining 2% signal loss can be attributed to losses in the substrate and the metal itself.

Figure 1.20- HFSS simulation results for signal transmission and reflection

The simulation results are consistent with expectations. Some reflection is present, but it is low enough to be considered acceptable. Based on the results of this simulation, a photomask was ordered and a shorted CPW was fabricated on SOI.

In order to best replicate the conditions of the final devices, test electrodes were fabricated on SOI with the top Si layer completely etched. Standard photolithography is performed to pattern the region of metal deposition. 30 nm of Ti is deposited as an adhesion layer, on top of which 700 nm of Au is deposited. Lift-off is performed in

acetone. S-parameters are measured using an Agilent E5071C network parameter analyzer. The test probes were Picoprobe model 40A-GSG-150-P.

S-parameter measurements show qualitatively similar performance, but less ideal than simulation (Figure 1.21). Approximately 80 percent of the signal is transmitted, and approximately 11 percent reflected.

Figure 1.21 - S-parameter measurements for tapered CPW

This higher level of reflection could be due to a number of factors. Whereas the simulation assumes 100 percent transmission into the CPW itself, it's possible that one source of reflection is the interface between the probes and the metal. Factors in the fabrication process like resist shrinkage or overexposure could affect critical spacing and cause an impedance mismatch. Additionally, there could be coupling with other devices on the same chip.

After reviewing the measurement results, it was determined that a loss of -1 dB through the measurement apparatus is sufficient and a signal reflection -8.5 dB is low enough to be acceptable. Enough signal is transmitted through the test structure that we are confident we should see the effects of the BJT. Based on the HFSS model and the shorted electrode test data, we decided to use the tapered CPW electrode structure for BJT devices.

In conclusion, a tapered CPW electrode has been designed to meet the on-chip measurement needs for our Si BJT. Established methods are used to calculate the impedance of a CPW on a two-layer dielectric with a finite ground plane, and a Python script is used to solve for the spacing of the CPW as a function of the trace width. This script was then used to calculate the spacing at all points along a taper going from the widely spaced probe to the small contact regions on a Si BJT.

High frequency modeling shows that the structure is well matched to a 50  $\Omega$  transmission line. A test electrode structure was fabricated and measured. While the real-world measurement shows higher signal reflection and loss than the simulation, the high level of signal transmission is sufficient for microwave frequency measurements.

# Chapter 2: Transfer Printing

### 2.1 Transfer Printing of Patterned Metal Films

The integration of flexible devices into complex circuits requires metal interconnects and electrodes. The first project presented in this dissertation is a technique for transfer printing of metal films. This work was carried out in parallel with the development and fabrication of BJTs, with the goal of enabling fully transfer printed microwave devices in the future.

There are several techniques for creating metal interconnects on metal substrates. Ink-jet printing and soft lithography techniques exist, but these often suffer from low resolution and poor film quality. Using transfer printing, high quality films can be fabricated on a Si wafer and then transferred to a flexible substrate.

Earlier work has described successful transfer printing of Au films [30], but transfer printing of other metal films has not been achieved previous to this study. Without surface modification, evaporated metal films adhere too strongly to bare Si substrates and cannot be transferred using conventional methods. In this study, we develop a method for transfer printing of five different metals by pre-coating the deposition substrate with parylene C in order to reduce adhesion and enable the transfer process [31].

Transfer printing is based on the principle of differential adhesion. If a material is weakly bound to one substrate and brought into contact with another, more adhesive substrate, it will transfer to the target substrate when the two are separated. If a substrate can be made adhesive through surface treatments such as adhesive coatings or plasma treatment is a suitable target (post-transfer) substrate material for transfer printing. Conversely any substrate whose adhesion can be made sufficiently low is a candidate for pre-transfer processing.

Adhesion can be caused by chemical bonding, electrostatic forces, mechanical interlocking of materials, diffusion, polar interaction, and dispersive forces (wetting). Among these, polar and dispersive adhesion are the primary forces in evaporated metal films. By controlling polar and dispersive adhesion, we can fabricate substrates that have desirable characteristics for transfer printing. The combination of polar and dispersive contributions to a substrate's adhesion is the substrate's surface energy.

Surface energy is a measure of the energetic disruption of molecular bonds that arises due to the formation of a surface. Liquids and vapor on a surface with high surface energy will more readily wet the surface and adhere more strongly to it. Total surface energy is simply the sum of the polar and dispersive contributions.

Surface energy is typically measured by contact angle measurements with various liquids of known polar and dispersive properties [32]. This technique, described in

44

detail later, is used in this study as a measure of the polar and dispersive adhesive properties of substrate surface treatments.

A range of metals deposition techniques has been developed to accommodate the needs of flexible electronics. Ink printing has been demonstrated [33] but faces challenges. An ink containing conducting or semiconducting material can be deposited directly onto a target substrate. Typically, this ink must be sintered at high temperature after deposition in order to remove solvents and obtain useful conductivity values. Ink rheology and drying time have a significant effect on film quality as well as adhesion. These challenges have limited the reported resolution of ink-based printing technology to tens of microns [34]. The use of solvents, variable film quality and resolution, and need for high-temperature processing makes ink based material deposition incompatible with many flexible substrates and applications.

Soft lithography transfer methods have been developed for transfer of deposited material from one substrate to another [35]. These typically employ an elastomeric stamp with raised features corresponding to the final patterned film. The stamp is designed to have low adhesion to the deposited film, and when brought into contact with a target substrate, the film transfers over. Soft lithography can be performed as an additive process, producing a minimum of waste material, and once a template has been fabricated, it can be reused many times. Flexible stamps can also be applied to non-planar surfaces. Flexible stamps, however, are susceptible to distortions. Strain

from the printing process can deform the stamp causing pairing and sagging, as well as swelling and shrinking of features [36]. The resolution, while better than inkbased printing is typically no less than one micron [37].

Transfer printing offers advantages over ink and soft-lithography based techniques [38]. Resulting films can consist of high quality materials at very high resolution on a wide range of substrates. Materials are fabricated and patterned on a host substrate of choice, and then transferred via differential adhesion to a target substrate. The host substrate can be chosen such that it is able to withstand harsh processing steps. Some examples include carbon nanotubes that have been grown on SiO<sub>2</sub> substrates at 800°C, temperatures above organic semiconductors deposited onto octadecyltrichlorosilane (OTS) treated SiO<sub>2</sub> substrates, and graphene deposited at temperatures above 900°C [30]. All have been successfully transferred to alternate substrates using surface functionalized transfer printing (SFTP). The only requirement for the transfer of these and other high-quality materials to alternate substrates is the ability to establish differential adhesion between the host and target substrates. In addition to high quality materials, SFTP allows for resolutions limited only by lithography technique. In combination with e-beam lithography, SFTP can achieve resolutions much lower than one micron.

Prior to this study, Au was the metal of choice for transfer printing. Au exhibits relatively low adhesion to Si substrates when deposited via e-beam evaporation. This low adhesion to the host substrate facilitates transfer to a variety of target substrates.

Other metals, however, typically exhibit stronger adhesion to Si substrates, limiting their utility for transfer printing.

One attempt at lowering the adhesion of deposited metal films onto Si substrates has been the formation of self-assembled monolayers (SAMs) on the substrate before metals deposition [39]. Any surface treatment candidate for use in transfer printing must meet three main requirements:

- 1. The adhesion of the deposited film to the treated substrate must be high enough for the film to survive pre-transfer processing, usually photolithography, metals deposition and liftoff.

- 2. The same adhesion must not be higher than that of the metal film to the target transfer substrate, which would prevent successful transfer.

- 3. The surface treatment must survive the entire transfer process without significant damage, which could degrade its adhesion-lowering properties.

1H,1H,2H,2H-perfluorodecyltrichlorosilane (FDTS) has been used as a release layer to lower the adhesion of nanoimprint lithography templates to polymer films [40]. FTDS has been reported to significantly lower the surface energy of Si surfaces. Janssen has reported a surface energy of 16.14 mJ/m<sup>2</sup> for an FTDS coated Si wafer, as compared to 71.91 mJ/m<sup>2</sup> for bare Si surfaces. This creates a very low adhesion between the deoposited film and deposition substrate. However, metal films with feature sizes less than ~100  $\mu$ m have not been found to survive photolithographic processing. Typically, deposited films are washed away during lift-off indicating that the adhesion between the films and substrate is too low and our first requirement is not met [41].

OTS had previously been used to lower the surface energy of SiO<sub>2</sub> substrates in order to improve the crystallinity of organic films [42]. OTS treated Si has a reported surface energy of 25.38 mJ/m<sup>2</sup> which is higher than FTDS, but still well below that of bare Si. While OTS treated samples do survive pre-transfer processing, films do not release completely during transfer. Previous studies have reported degradation of OTS films beginning around 180 °C [43] which is below the temperatures experienced during the transfer process. The high pressure and elevated temperature of the transfer process, therefore, likely damages the OTS monolayer, which would indicate that OTS treatment does not satisfy our third requirement.

In this study, we develop a surface treatment for transfer printing of metals that satisfies all three requirements. Parylene C is a polymer commonly used as a moisture-proof coating in medicine and electronics. It is compatible with all solvents and developers used in our photolithography process and has a reported dissociation temperature of 290 °C, [44] which is well above the temperature of transfer printing which we set at 175 °C. We use parylene C as a surface treatment that has a suitable surface energy (and corresponding adhesion) and which remains stable throughout the fabrication and transfer process.

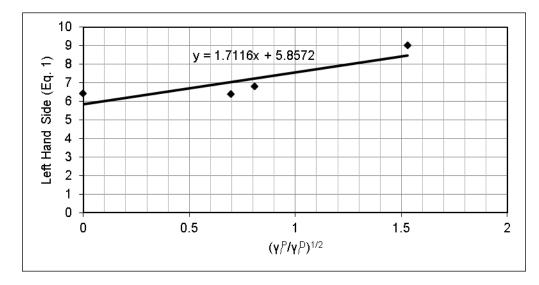

In order to determine the surface energy of parylene C, contact angle measurements were performed using a Ramé-Hart contact angle goniometer. A liquid droplet was dispensed onto the surface of a given solid substrate and the angle of the liquid formed at the surface of the solid substrate was measured. This was done using 4 different liquids (water, ethylene glycol, formamide and diiodomethane) with five angle measurements averaged together for each liquid on a given surface. The total, dispersive and polar components of the surface energy of the solid substrate surface can then be calculated using Equations 2.1 and 2.2 [32]:

$$(1+\cos\theta)/2)(\gamma_l^{T}/\gamma_l^{D})^{1/2} = (\gamma_s^{P})^{1/2} (\gamma_l^{P}/\gamma_l^{D})^{1/2} + (\gamma_s^{D})^{1/2}$$

Eq. 2.1

$$\gamma_s^{T} = \gamma_s^{D} + \gamma_s^{P}$$

Eq. 2.2

where  $\theta$  is the measured contact angle and  $\gamma_l^{T}$ ,  $\gamma_l^{D}$ ,  $\gamma_l^{P}$  are the known values of the total, dispersive and polar components of the test liquids, respectively.

| Liquid             | Contact Angle | $\gamma_l^{\rm D} ({\rm mJ/m^2})$ | $\gamma_l^{\rm p} ({\rm mJ/m^2})$ |

|--------------------|---------------|-----------------------------------|-----------------------------------|

| Water              | 81.04°        | 21.8                              | 51.0                              |

| Formamide          | 68.12°        | 34.0                              | 30.0                              |

| Ethylene<br>Glycol | 58.04°        | 29.0                              | 19.0                              |

| Diiodomethane      | 36.54°        | 50.8                              | 0.0                               |

Table 2.1 – Contact angle data for parylene C

A plot of the (known) left hand side of Eq. 1 vs.  $(\gamma_l^{P}/\gamma_l^{D})^{1/2}$  is therefore linear, with a slope of  $(\gamma_s^{P})^{1/2}$  and a y intercept of  $(\gamma_s^{D})^{1/2}$  (Figure 2.1).

**Figure 2.1** - Linear regression to determine  $\gamma_s^{P}$  and  $\gamma_s^{D}$

A linear regression shows the slope to be  $1.71 \pm 0.72$  and the intercept to be  $5.87 \pm 0.68$ . This corresponds to a  $\gamma_s^{P}$  value of 2.93 mJ/m<sup>2</sup>  $\pm 3.02/-1.96$  mJ/m<sup>2</sup> and a  $\gamma_s^{D}$  value of 34.31 mJ/m<sup>2</sup>  $\pm 8.63/-7.36$  mJ/m<sup>2</sup> for a total surface energy of 37.23 mJ/m<sup>2</sup>  $\pm 9.14/-7.61$  mJ/m<sup>2</sup>. The measured value of surface energy for parylene C falls in the range between SAM surface treatment (OTS, FTDS) and the surface energy of bare Si. Based on surface energy measurements, it is determined that parylene C has the adhesive properties needed for transfer printing of metal films.

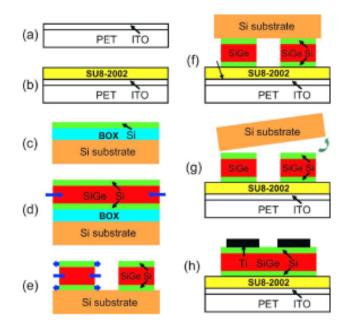

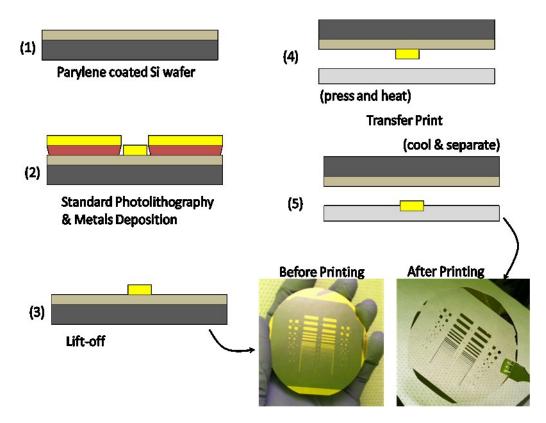

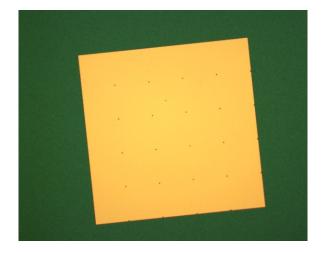

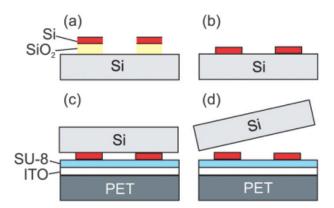

The processing steps for the fabrication of patterned metal films onto parylene C coated Si wafers (Figure 2.2, 1 - 3) and the transfer printing of the patterned metal films onto a plastic substrate (Figure 2.2, 4 & 5) are shown in Figure 2.2.

Figure 2.2 – Fabrication and transfer process

Three inch diameter Si wafers were purchased from Silicon Quest International and used as received. The wafers are coated with a 25 µm thick parylene C film by Specialty Coating Systems. Wafers are coated on both sides, with the parylene film continuous over the edge from one side to the other. This two-sided coating prevents delamination of the parylene film during processing. If the wafer is diced, the film will no longer be continuous over the edge, and delamination is likely. Therefore, only full 3" wafers are used in this study. No adhesion promoters are applied to the Si wafer prior to parylene deposition. (Figure 2.2, 1). Standard photolithography, vacuum deposition of metals and lift-off is performed on the surface of the parylene coated wafer (Figure 2.2, 2 & 3) resulting in a patterned metal film as seen in the optical image (left image) in Figure 2.2. An oxygen plasma treatment using a

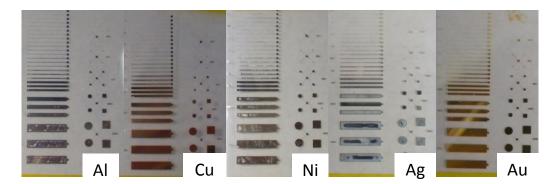

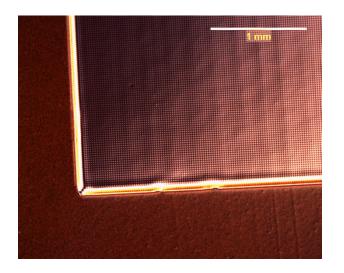

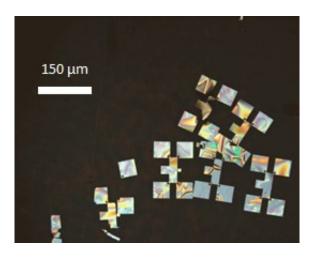

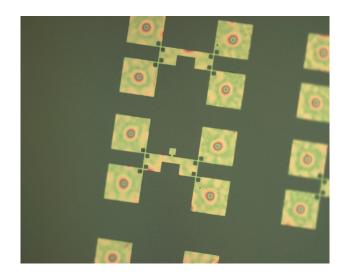

PlasmaStar Axic system at 100 SCCM and 200 Watts is performed for 1 minute on the surface of a polyethylene naphthalene (PEN) plastic substrate. The plasma treated PEN surface is placed in contact with the patterned metal surface of the parylene coated Si wafer and the two substrates are then placed together in a Nanonex NX2500 imprinter machine for transfer printing. Transfer printing is performed in the NX2500 chamber at approximately 175 °C and 500 psi for 3 minutes (Figure 2.2, 4). The substrates are then removed from the chamber and separated (Figure 2.2, 5). The resulting successfully transfer printed metal films are shown in the optical image (right image) in Fig. 2.2 and in the optical images in Fig. 2.3 for Al, Cu, Ni, Ag and Au (from left to right).

Figure 2.3 – Successfully transferred metal films

Thickness measurements are taken before transfer using a Tencor Alpha-step 200 profilometer. Resistance measurements are taken with a handheld Fluke multimeter at the ends of 1 cm long bars of varying widths (as shown in Fig. 1). Pre- and post-transfer resistivity measurements are shown in Table 2.2.

| Metal | Pre-transfer Resistivity | Post-transfer Resistivity |

|-------|--------------------------|---------------------------|

| Al    | 41.7 nΩm                 | 37.5 nΩm                  |

| Ag    | 13.9 nΩm                 | 17.6 nΩm                  |

| Cu    | 15.6 nΩm                 | 15 nΩm                    |

| Ni    | 80.1 nΩm                 | 81.0 nΩm                  |

| Au    | 21.8 nΩm                 | 20.7 nΩm                  |

Table 2.2 – Pre- and post-transfer resistivity measurements

Resistivities are comparable to bulk values for each metal, indicating that the films are of high quality. Additionally, post-transfer resistivity values are not significantly reduced due to the transfer process. This indicates that the films are not damaged during transfer.