## ABSTRACT

VEHICLES

Directed By:

Title of Document:

Professor Alireza Khaligh Department of Electrical and Computer Engineering

HIGHLY EFFICIENT SIC BASED ONBOARD

CHARGERS FOR PLUG-IN ELECTRIC

Haoyu Wang, Doctor of Philosophy, 2014

Grid-enabled plug-in electrified vehicles (PEVs) are deemed as one of the most sustainable solutions to profoundly reduce both oil consumption and greenhouse gas emissions. One of the most important realities, which will facilitate the adoption of PEVs is the method by which these vehicles will be charged. This dissertation focuses on the research of highly efficient onboard charging solutions for next generation PEVs.

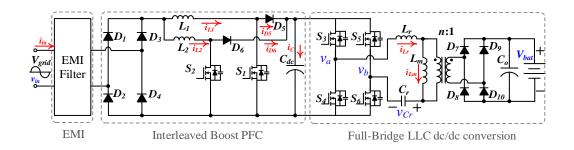

This dissertation designs a two-stage onboard battery charger to charge a 360 V lithium-ion battery pack. An interleaved boost topology is employed in the first stage for power factor correction (PFC) and to reduce total harmonic distortion (THD). In the second stage, a full bridge inductor-inductor-capacitor (LLC) multi-resonant converter is adopted for galvanic isolation and dc/dc conversion. Design considerations focusing on reducing the charger volume, and optimizing the conversion efficiency over the wide battery pack voltage range are investigated. The

designed 1 kW Silicon based charger prototype is able to charge the battery with an output voltage range of 320 V to 420 V from 110 V, 60 Hz single-phase grid. Unity power factor, low THD, and high peak conversion efficiency have been demonstrated experimentally.

This dissertation proposes a new technique to track the maximum efficiency point of LLC converter over a wide battery state-of-charge range. With the proposed variable dc link control approach, dc link voltage follows the battery pack voltage. The operating point of the LLC converter is always constrained to the proximity of the primary resonant frequency, so that the circulating losses and the turning off losses are minimized. The proposed variable dc link voltage methodology, demonstrates efficiency improvement across the wide state-of-charge range. An efficiency improvement of 2.1% at the heaviest load condition and 9.1% at the lightest load condition for LLC conversion stage are demonstrated experimentally.

This dissertation proposes a novel PEV charger based on single-ended primary-inductor converter (SEPIC) and the maximum efficiency point tracking technique of an LLC converter. The proposed charger architecture demonstrates attracting features such as (1) compatible with universal grid inputs; (2) able to charge the fully depleted battery pack; (3) pulse width modulation and simplified control algorithm; and (4) the advantages of Silicon Carbide MOSFETs can be fully manifested. A 3.3 kW all Silicon Carbide based PEV charger prototype is designed to validate the proposed idea.

# HIGHLY EFFICIENT SIC BASED ONBOARD CHARGERS FOR PLUG-IN ELECTRIC VEHICLES

By

Haoyu Wang

## Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2014

Advisory Committee: Professor Alireza Khaligh, Chair/Advisor Professor Robert Newcomb Professor Neil Goldsman Professor Isaak Mayergoyz Professor Patrick McCluskey, Dean's representative © Copyright by Haoyu Wang 2014 Dedication

To my parents and my wife.

## Acknowledgements

First of all, I would like to thank my advisor, Prof. Alireza Khaligh, for his supervision, tolerance, and support. He introduced me to the realm of power electronics, where I found my genuine research interest. He provided me resources and constructive advices to broad the vision of my research. I would never forget that he helped to revise my very first manuscript word by word. He taught me not only the methodology of becoming a good researcher, but also the life philosophy of being a mature man. His enthusiasm, passion, and ambition towards career will continue to inspire me in the rest of my life.

I would also like to acknowledge my dissertation committee members. I appreciate Prof. Robert Newcomb, my academic advisor during the first two years of my Ph.D. study, for his unselfish guidance and encouragement. He passed to me not only knowledge, but also the optimism to life. I am truly grateful to Prof. Isaak Mayergoyz, who was also a committee member at my doctoral proposal exam. His comments and suggestions are very useful and helped me to improve the quality of my work. I would also like to thank Prof. Neil Goldsman, for his support and guidance over the Maryland Industrial Partnerships (MIPS) project, which is a key part of my dissertation. My appreciation also goes to Prof. Patrick McCluskey for his kindness in serving on my dissertation committee as the dean's representative.

This thesis would not be finished without the valuable inputs from my brilliant colleagues in the Power Electronics, Energy Harvesting, and Renewable Energies Laboratory. I would like to express my gratitude to Serkan Dusmez, Yichao Tang, Seshadri Raghavan, Dr. Amin Hasanzadeh, Junyi Shen, and Chuan Shi for their kind assistance and profitable discussions.

My special thanks also goes to CoolCAD Electronics, LLC, for their support and help in my project, especially Dr. Akin Akturk and Dr. Siddharth Potbhare. I would like to acknowledge Dr. Fariborz Musavi from CUI, INC, and Dr. Zhong Nie from Chrysler Group LLC, for their technical advices. I would like to thank Bryan Quinn, Joe Kselman, and Shayam Mehrotra for their technical support. Many thanks to Melanie Prange, Maria Hoo, Vivian Lu, Victoria Berry, Heather Stewart, Kristin Little, Carrie Hilmer, Wei Shi, and all the staff members in the Department of Electrical and Computer Engineering for their service and support.

I would also like to acknowledge all the friends I met during this unforgettable journey in the United Sates. It is them who made my Ph.D. life colorful and enjoyable.

In the end, I would like to thank my father Meng Wang, my mother Lijuan Yan, my wife Jingke He, and every member of my family, for their continuous love and support. To them I dedicate this thesis.

## Table of Contents

| Dedication                                                                      | . ii |

|---------------------------------------------------------------------------------|------|

| Acknowledgements                                                                | iii  |

| Table of Contents                                                               | . v  |

| List of Tables                                                                  | 'iii |

| List of Figures                                                                 | ix   |

| Chapter 1 Introduction                                                          | . 1  |

| 1.1. Background                                                                 | . 1  |

| 1.2. Charging Infrastructures and Charging Profile of Li-ion Battery            | . 3  |

| 1.2.1 Charging Power Levels                                                     |      |

| 1.2.2 Battery Swapping                                                          | . 5  |

| 1.2.3 Battery Charging Profile                                                  | . 5  |

| 1.3. Typical Energy Storage and Power Conversion Interfaces of EVs              | . 9  |

| 1.4. Typical Circuit Configurations of Onboard Charger                          | 11   |

| 1.5. Challenges in Onboard Charger Design                                       | 13   |

| 1.6. Silicon Carbide Power Devices                                              | 17   |

| 1.7. Intellectual Merit and List of Contributions                               | 22   |

| 1.8. Outline of Dissertation                                                    |      |

| Chapter 2 State of The Art Isolated Battery Chargers                            | 27   |

| 2.1 Introduction                                                                | 27   |

| 2.2 Review of Front End ac/dc PFC Topologies                                    | 28   |

| 2.2.1 Conventional Boost PFC Converter                                          |      |

| 2.2.2 Bridgeless Boost PFC Converter                                            | 29   |

| 2.2.3 Interleaved Boost PFC Converter                                           |      |

| 2.3 Review of Second Stage Isolated dc/dc Topologies                            | 31   |

| 2.3.1 Full Bridge Isolated PWM Buck Converter                                   |      |

| 2.3.2 Full Bridge Phase-shift PWM Converter                                     |      |

| 2.3.3 Full Bridge Series Resonant Converter                                     |      |

| 2.3.4 Full Bridge LLC Resonant Converter                                        |      |

| 2.4 Summary                                                                     |      |

| Chapter 3 Comprehensive Topological Analyses of Isolated Resonant Converters in | L    |

| PEV Battery Charging Applications                                               |      |

| 3.1 Introduction                                                                |      |

| 3.2 Circuit Modeling and Analyses of Resonant Converters                        | 40   |

| 3.2.1 Circuit Modeling                                                          |      |

| 3.2.2 Dc Voltage and Current Characteristics                                    | 42   |

| 3.2.3 Capacitive and Inductive Operations                                       |      |

| 3.3 Charging Profile of Li-ion Battery                                          | 46   |

| 3.4 Basic Design and Comparison Considerations                                  |      |

| 3.5 Comparison of Resonant Converters in PEV Battery Charging Application       |      |

| 50                                                                              |      |

| 3.5.1 Series Resonant Charger                                                   | 50   |

| 3.5.2 Parallel Resonant Charger                                                 | 52   |

| 3.5.3 LCC Series-parallel Charger                                             | 54  |

|-------------------------------------------------------------------------------|-----|

| 3.5.4 LLC Series-parallel Charger                                             | 57  |

| 3.6 Summary                                                                   | 60  |

| Chapter 4 Design and Analysis of a Full Bridge LLC Based PEV Charger Optimiz  | zed |

| for Wide Battery Voltage Range                                                |     |

| 4.1 Introduction                                                              | 61  |

| 4.2 General Boost Converter                                                   | 63  |

| 4.3 Interleaved Boost Converter                                               | 66  |

| 4.3.1 Interleaving Effect on Input Ripple Current                             | 67  |

| 4.3.2 Interleaving Effect on Magnetic Volume Reduction                        | 69  |

| 4.3.3 Interleaving Effect on Output Capacitor                                 | 69  |

| 4.4 Full Bridge LLC Converter                                                 |     |

| 4.4.1 Operation Analysis with $f < f_s/2$                                     | 73  |

| 4.4.2 Operation Analysis with $f_s/2 < f < f_s$                               |     |

| 4.4.3 Operation Analysis with $f_s < f < f_p$ (f close to $f_s$ )             |     |

| 4.4.4 Operation Analysis with $f_s < f < f_p$ (f close to $f_p$ )             | 83  |

| 4.4.5 Operation Analysis with $f > f_p$                                       |     |

| 4.4.6 Summary of Switching Conditions                                         | 88  |

| 4.4.7 Modeling with First Harmonic Approximation                              | 89  |

| 4.4.8 Steady State Operating Characteristics                                  | 92  |

| 4.5 Designing a 1 kW PEV Charger Prototype                                    |     |

| 4.5.1 Charging Profile of 1 kW Li-ion Battery                                 | 95  |

| 4.5.2 Interleaved Boost PFC Converter Design                                  |     |

| 4.6 Full-Bridge Series LLC Converter Design                                   | 98  |

| 4.7 Optimization of the LLC Magnetic Components                               | 102 |

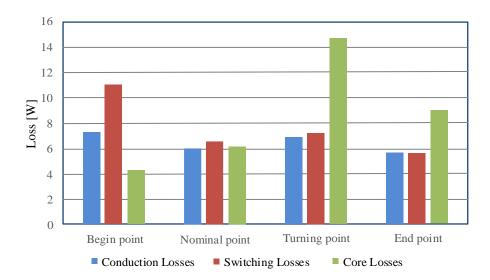

| 4.8 Loss Analysis of the Full-Bridge LLC Converter                            | 107 |

| 4.8.1 Conduction Losses                                                       | 107 |

| 4.8.2 Switching Losses                                                        | 108 |

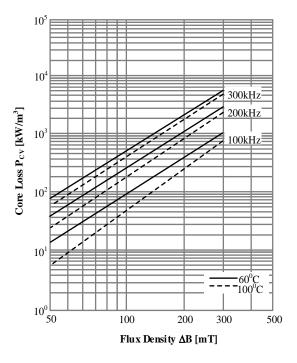

| 4.8.3 Core Losses                                                             | 109 |

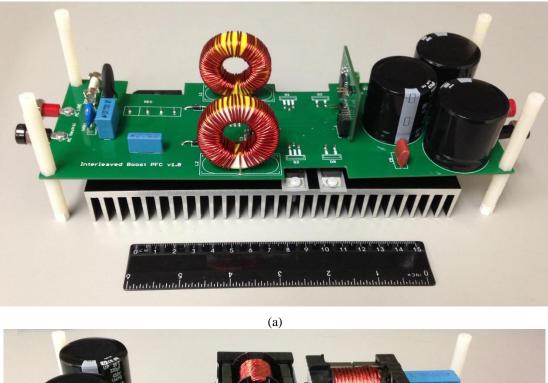

| 4.9 Experiment Results                                                        | 110 |

| 4.10 Summary                                                                  | 118 |

| Chapter 5 Minimizing the Circulating Energy and Tracking the Maximum Efficien | ncy |

| Point of LLC Converter                                                        |     |

| 5.1 Introduction                                                              | 119 |

| 5.2 Proposed Maximum Efficiency Point Tracking of LLC Converter               | 122 |

| 5.2.1 DC Voltage Characteristics of LLC PEV Battery Charger with Fixed        | Dc  |

| Link Voltage                                                                  | 122 |

| 5.2.2 Operating Modes in ZVS Region 1                                         | 124 |

| 5.2.3 Operating Modes in ZVS Region 2                                         | 125 |

| 5.2.4 Operating Modes in Primary Resonant Frequency                           | 126 |

| 5.2.5 Proposed Maximum Efficiency Point Tracking Technique                    | 128 |

| 5.3 Circuit Modeling and Loss Analysis at Maximum Efficiency Point            |     |

| 5.3.1 Circuit Modeling at Maximum Efficiency Point                            |     |

| 5.3.2 Loss Analysis at Maximum Efficiency Point                               | 133 |

| 5.4 Design Considerations                                                     |     |

| 5.5 Control Strategy                                                          | 139 |

| 5.6 Simulation Results                                                    | 40 |

|---------------------------------------------------------------------------|----|

| 5.7 Experiment Results 14                                                 | 43 |

| 5.8 Performance Comparison                                                | 48 |

| 5.9 Summary                                                               | 52 |

| Chapter 6 A Novel Approach to Design EV Battery Chargers Using SEPIC PFC  |    |

| Stage and Optimal Operating Point Tracking Technique for LLC Converter 15 | 54 |

| 6.1 Introduction15                                                        |    |

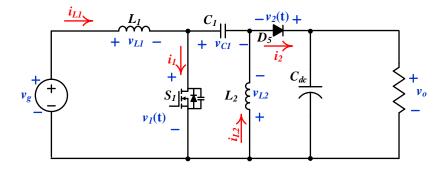

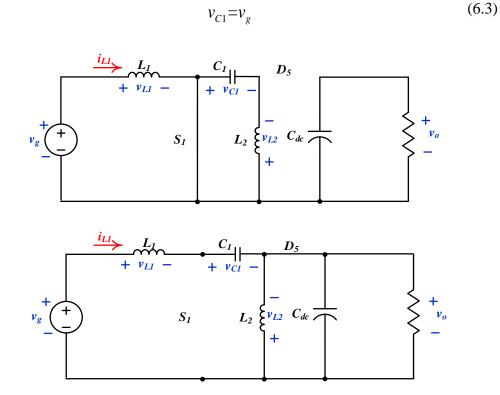

| 6.2 Review of SEPIC Converter                                             | 57 |

| 6.3 Circuit Modeling                                                      | 51 |

| 6.3.1 Small Signal Modeling16                                             |    |

| 6.3.2 Current Loop Analysis                                               | 55 |

| 6.3.3 Voltage Loop Analysis17                                             |    |

| 6.4 Design Considerations                                                 |    |

| 6.4.1 Continuous Conduction Mode17                                        | 76 |

| 6.4.2 Capacitor Voltage Ripple17                                          | 79 |

| 6.5 Simulation Results                                                    |    |

| 6.5.1 Simulation Results of the SEPIC PFC Stage                           |    |

| 6.5.2 Simulation Results of the LLC dc/dc Stage                           |    |

| 6.6 Experiment Results                                                    |    |

| 6.6.1 Experiment Results of the SEPIC PFC Stage                           | 91 |

| 6.6.2 Experiment Results of the SEPIC PFC Stage                           | 98 |

| 6.7 Summary                                                               |    |

| Chapter 7 Conclusions and Future Work                                     |    |

| 7.1 Conclusions                                                           | 96 |

| 7.2 Future Work                                                           |    |

| Bibliography                                                              | 15 |

## List of Tables

| Table 1-1   | Charging power levels                                             | 3   |

|-------------|-------------------------------------------------------------------|-----|

| Table 1-2   | Charging characteristics and infrastructures of some manufactured |     |

| PHEVs and E | Vs                                                                | 6   |

| Table 1-3   | DOE technical targets on onboard charger                          | .14 |

| Table 1-4   | Electric properties of semiconductors                             | .18 |

| Table 1-5   | Comparison of diodes parameters                                   | .20 |

| Table 1-6   | Comparison of MOSFETs parameters                                  | .21 |

| Table 2-1   | Comparison of ac/dc PFC topologies for PEV battery charging       | .31 |

| Table 2-2   | Comparison of isolated converters in PEV charging applications    | .37 |

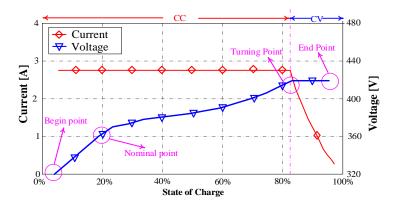

| Table 3-1   | Key points in the 3.3 kW charging profile of the PEV battery pack | .48 |

| Table 3-2   | Parameters of designed resonant chargers                          | .50 |

| Table 3-3   | Comparison of resonant converters in PEV charging applications    | .59 |

| Table 4-1   | Switching conditions of LLC converter                             | .89 |

| Table 4-2   | Key points in the charging profile of the PEV battery pack        | .96 |

| Table 4-3   | Critical parameters of magnetic components                        | 108 |

| Table 4-4   | Design of an interleaved full-bridge LLC onboard charger          | 112 |

| Table 5-1   | Comparison of LLC converter at different operating points         | 129 |

| Table 5-2   | Design of a 1 kW LLC onboard charger                              | 140 |

| Table 5-3   | Design of a conventional 1 kW LLC onboard charger                 | 148 |

| Table 6-1   | Designed parameters of the SEPIC PFC rectifier                    | 182 |

| Table 6-2   | Designed parameters of the 3.3 kW LLC converter                   | 198 |

# List of Figures

| Fig. 1.1       | Weekly U.S. regular conventional retail gasoline prices               | 1  |

|----------------|-----------------------------------------------------------------------|----|

| Fig. 1.2       | Li-ion pricing and energy density (1991-2006)                         | 2  |

| Fig. 1.3       | Annual sales of light-duty electric vehicles worldwide (2011-2017).   | 3  |

| Fig. 1.4       | The Li-ion battery charging techniques                                | 8  |

| Fig. 1.5       | Advanced fast charging techniques                                     | 9  |

| Fig. 1.6       | General power architecture of an EV                                   | 10 |

| Fig. 1.7       | Typical block diagram of ac/dc PFC stage and equivalent circuit       |    |

| model          |                                                                       | 11 |

| Fig. 1.8       | Typical configuration of isolated dc/dc topology                      | 12 |

| Fig. 1.9       | Common switching networks                                             | 12 |

| Fig. 1.10      | Common rectifier networks                                             | 13 |

| Fig. 1.11      | An arbitrary transformer primary voltage waveforms, illustrating the  |    |

| volt-seconds a | pplied during the positive portion of the cycle                       | 15 |

| Fig. 2.1       | Single phase boost PFC converter                                      | 28 |

| Fig. 2.2       | Bridgeless PFC boost converter                                        | 30 |

| Fig. 2.3       | Interleaved PFC boost converter                                       | 30 |

| Fig. 2.4       | Full bridge isolated PWM buck converter                               | 31 |

| Fig. 2.5       | Waveforms of full bridge isolated buck converter                      |    |

| Fig. 2.6       | Full bridge phase-shift PWM converter                                 |    |

| Fig. 2.7       | Waveforms of full bridge phase-shift converter                        |    |

| Fig. 2.8       | Full bridge SRC PFM converter                                         |    |

| Fig. 2.9       | Full bridge LLC PFC converter                                         |    |

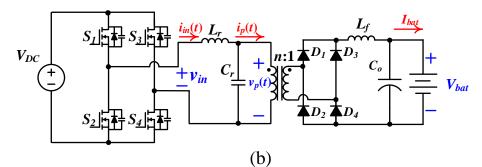

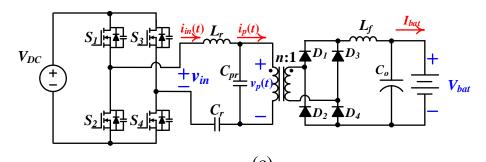

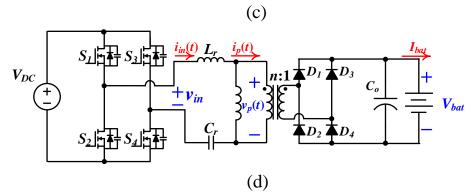

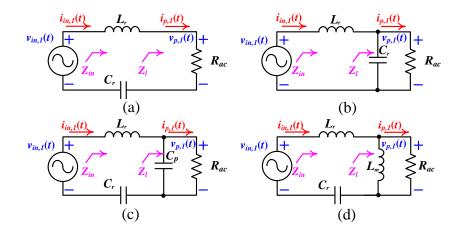

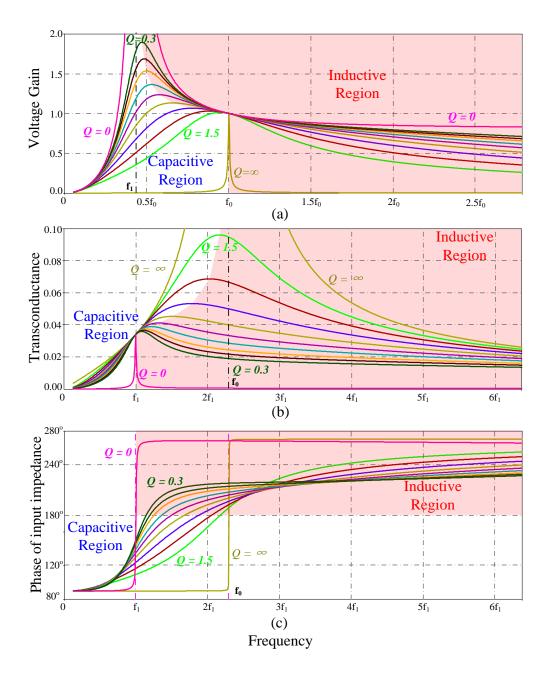

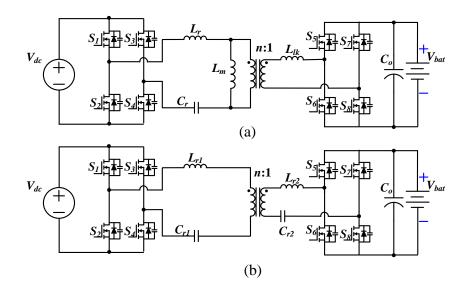

| Fig. 3.1       | Isolated resonant topologies in battery charging applications         | 39 |

| Fig. 3.2       | Ac equivalent models of resonant converters                           |    |

| Fig. 3.3       | Switching output waveforms in continuous conduction mode for          |    |

| resonant conve | erters with (a) capacitive $Z_{in}$ , and (b) inductive $Z_{in}$      | 44 |

| Fig. 3.4       | Charging characteristics of a Li-ion battery cell                     | 47 |

| Fig. 3.5       | Charging profile of a 360 V Li-ion battery pack rated at 3.2 kW       | 47 |

| Fig. 3.6       | Dc voltage and current characteristics of the SRC charger             | 51 |

| Fig. 3.7       | Dc voltage and current characteristics of the PRC charger             | 53 |

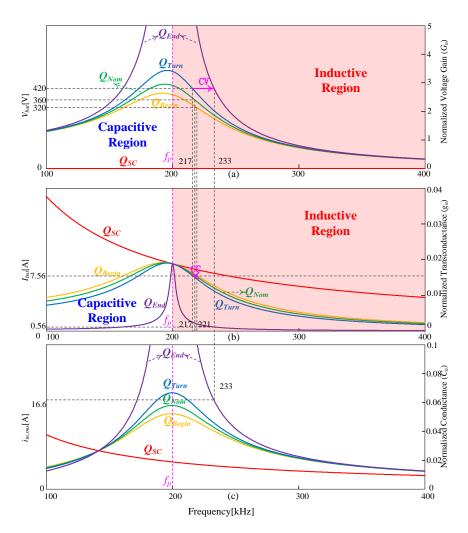

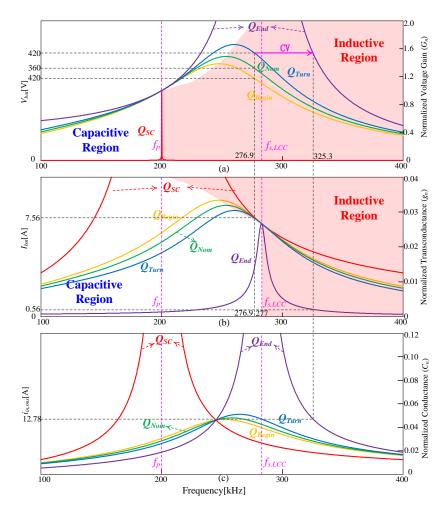

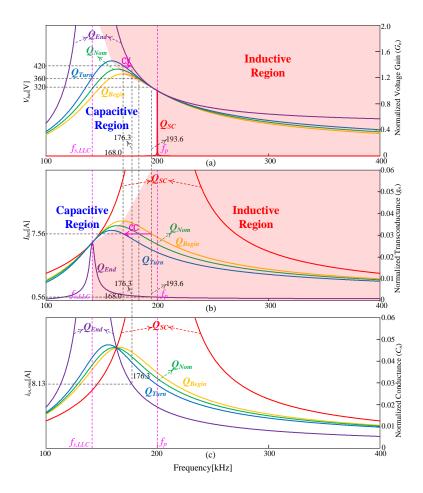

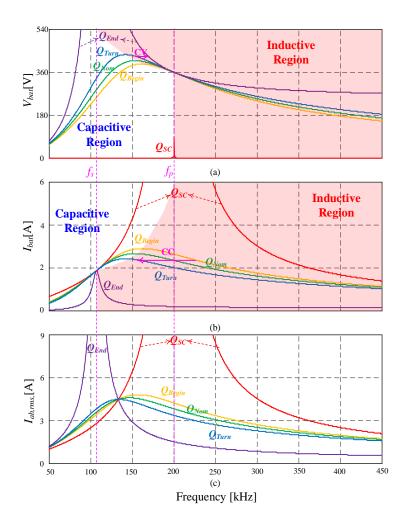

| Fig. 3.8       | Dc voltage and current characteristics of the LCC charger             | 55 |

| Fig. 3.9       | Dc voltage and current characteristics of the LLC charger             | 58 |

| Fig. 4.1       | General system architecture of a battery charger                      | 61 |

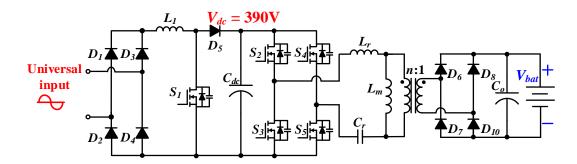

| Fig. 4.2       | Schematic of proposed interleaved level 2 isolated onboard charger    |    |

| Fig. 4.3       | Schematic of general boost converter                                  | 63 |

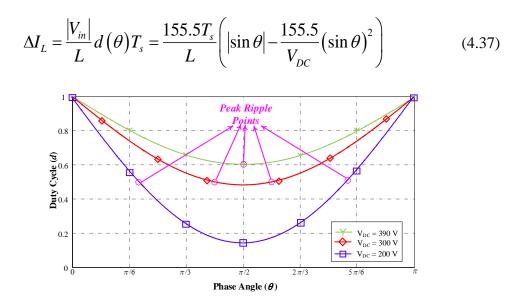

| Fig. 4.4       | Simulated waveforms of the general boost converter                    | 64 |

| Fig. 4.5       | Schematic of two phase interleaved boost converter                    | 67 |

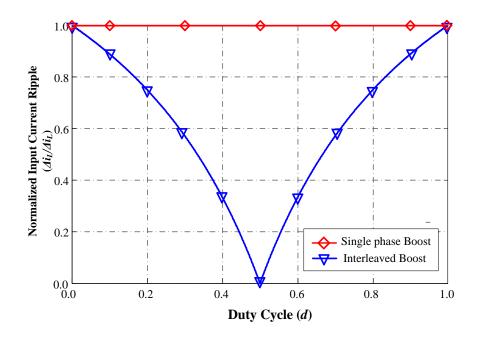

| Fig. 4.7       | Effectiveness of input ripple cancellation for interleaved converters | 69 |

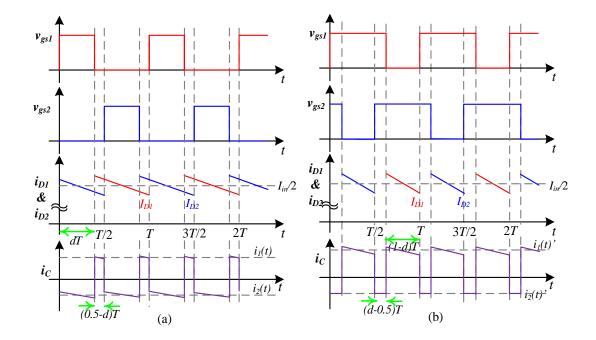

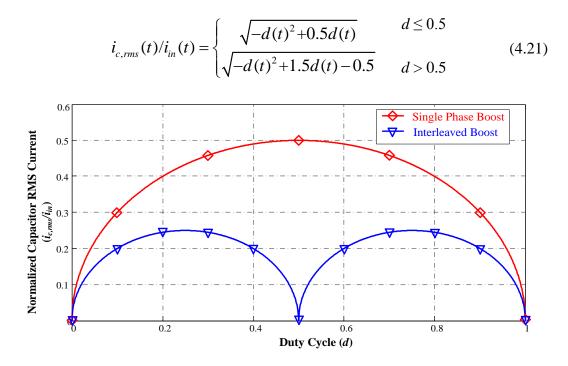

| Fig. 4.8       | Output capacitor current ripple of the 2 phase interleaved boost      |    |

| converter      |                                                                       | 71 |

| Fig. 4.9       | Effectiveness capacitor rms current reduction for interleaved         |    |

| converters     | -                                                                     | 72 |

|                |                                                                       |    |

1

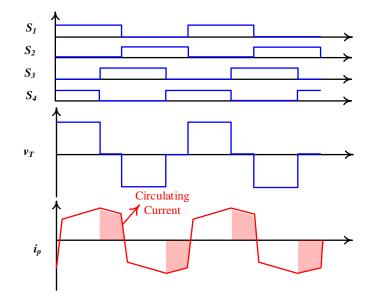

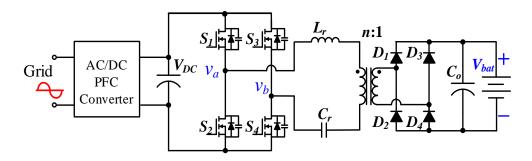

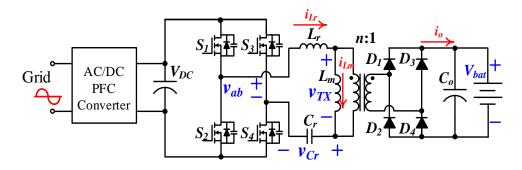

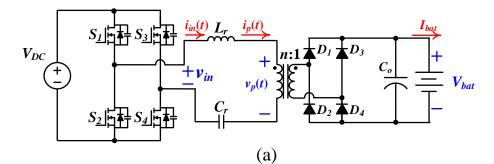

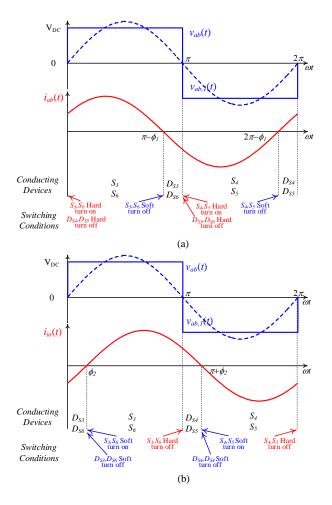

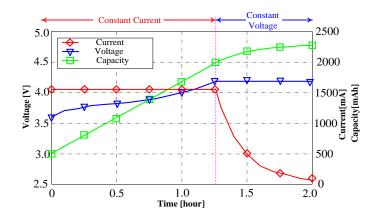

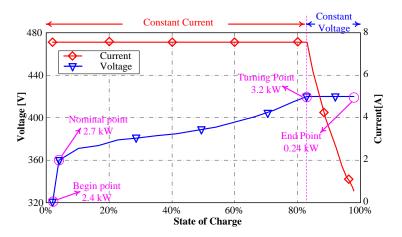

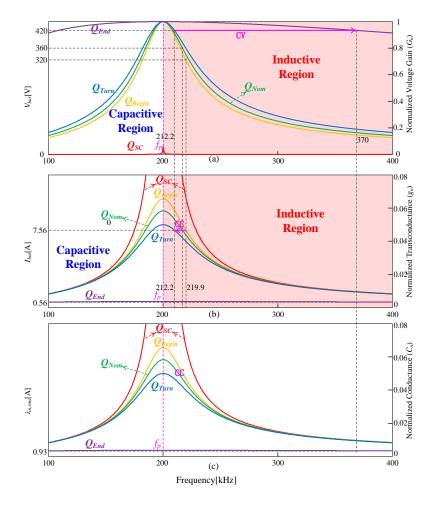

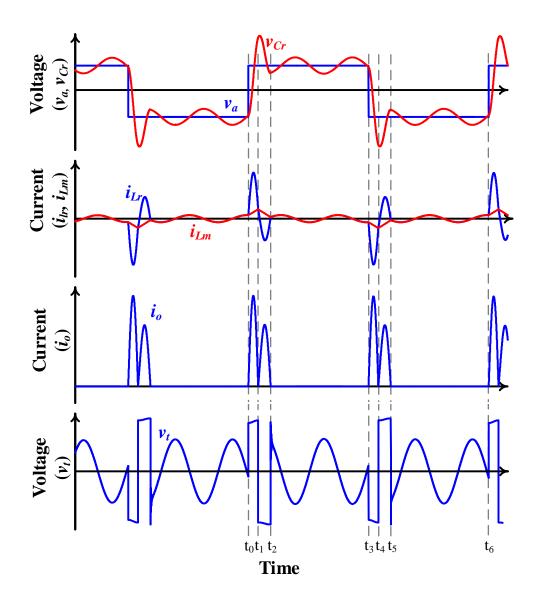

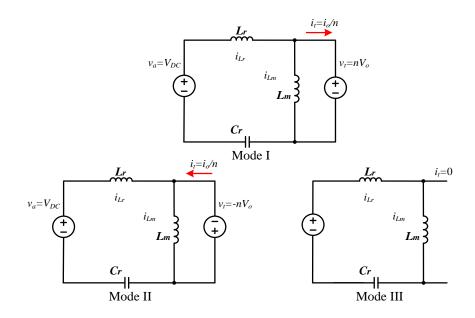

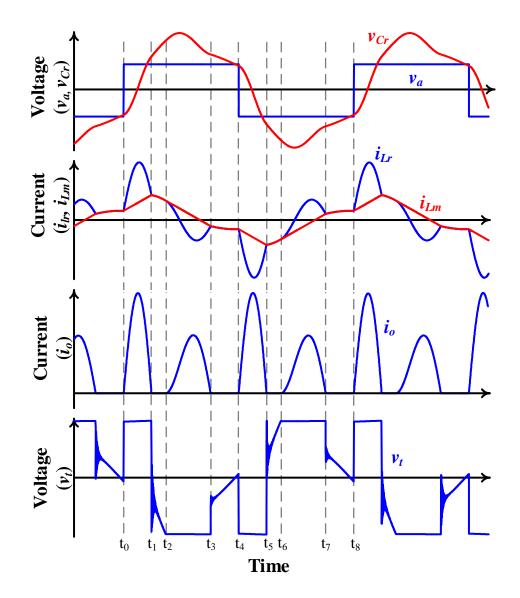

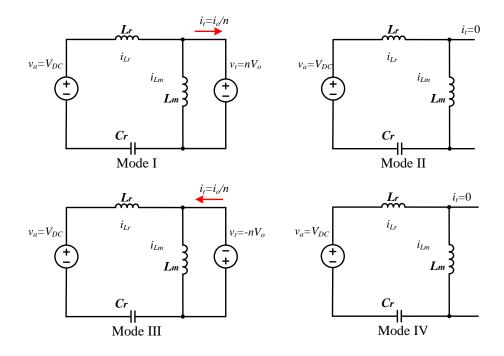

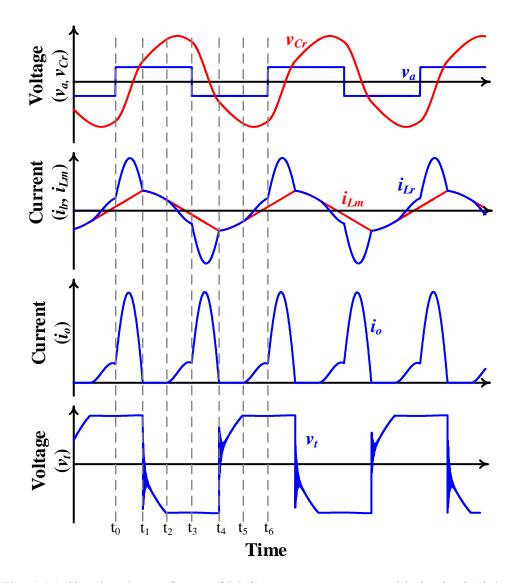

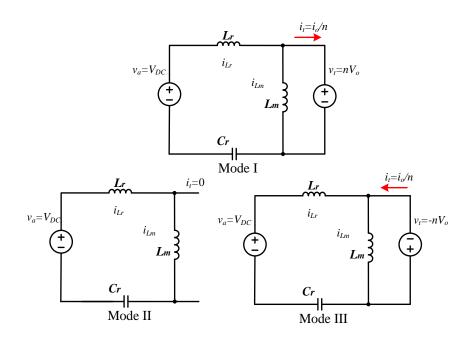

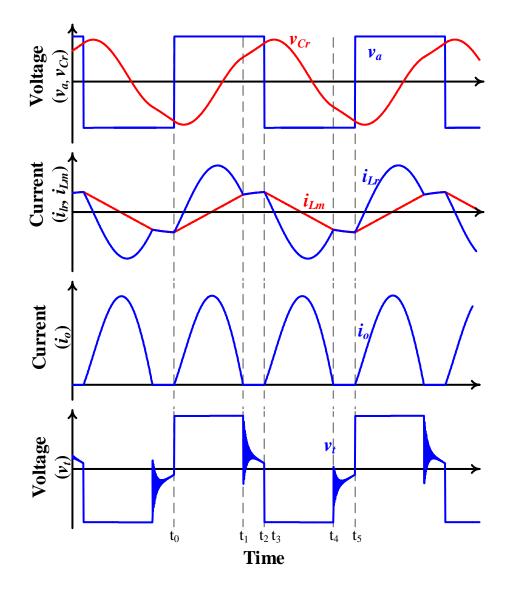

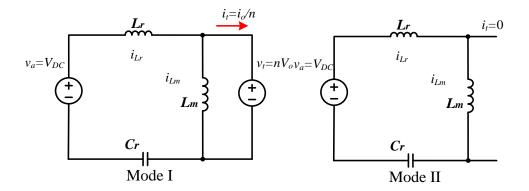

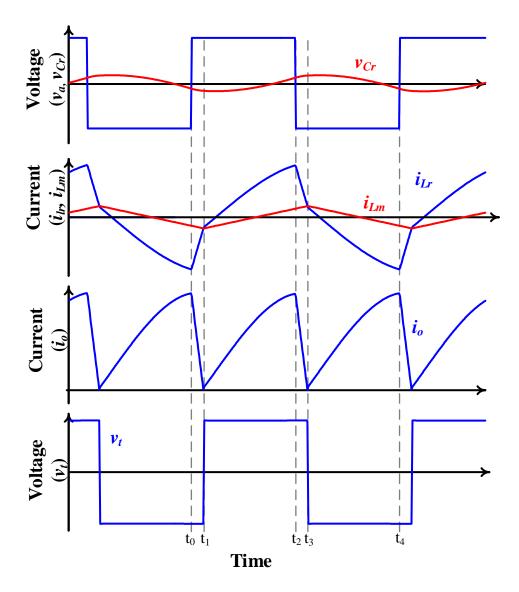

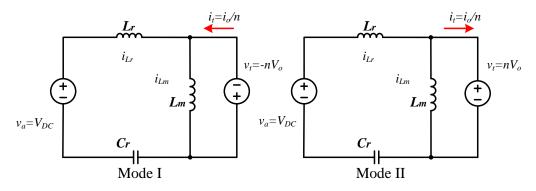

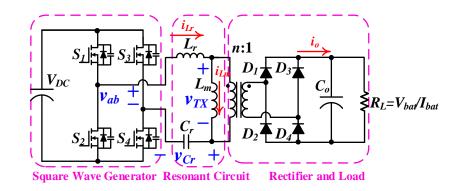

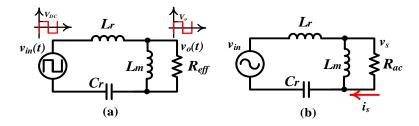

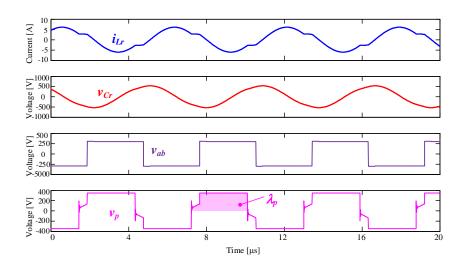

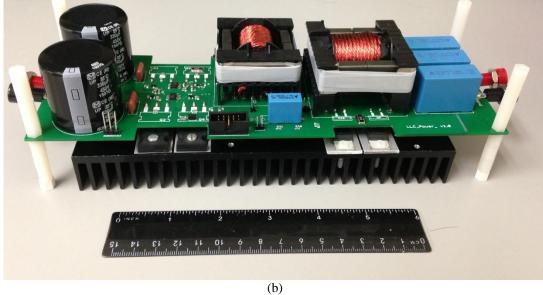

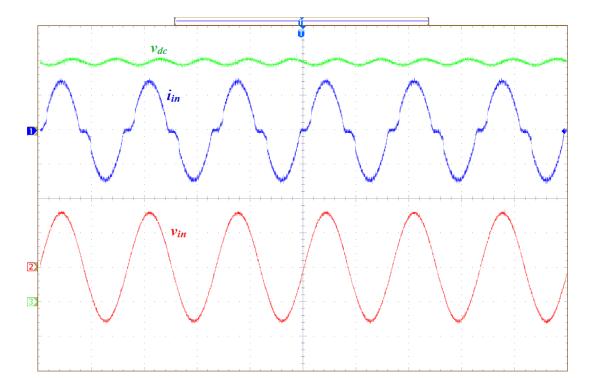

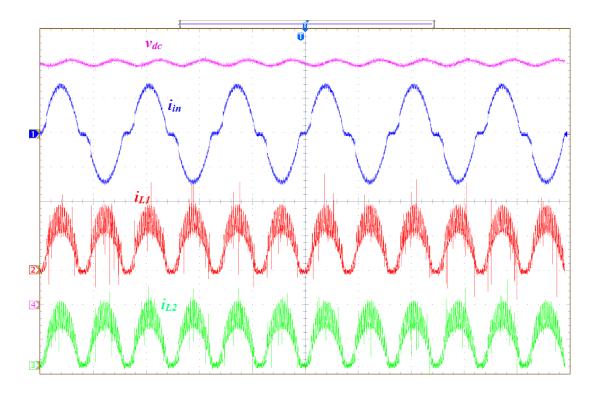

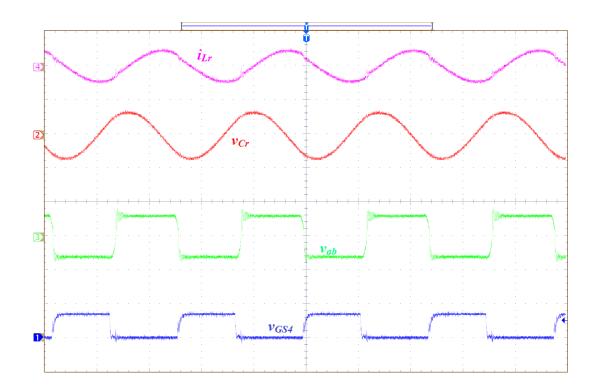

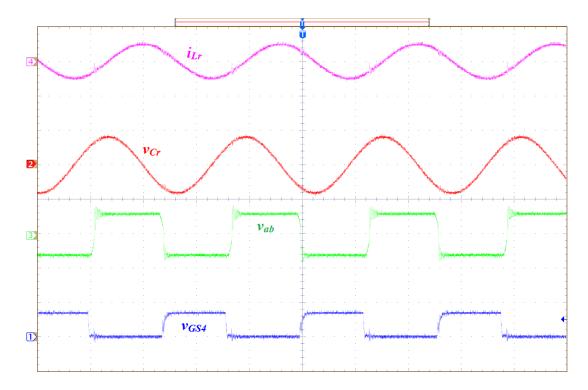

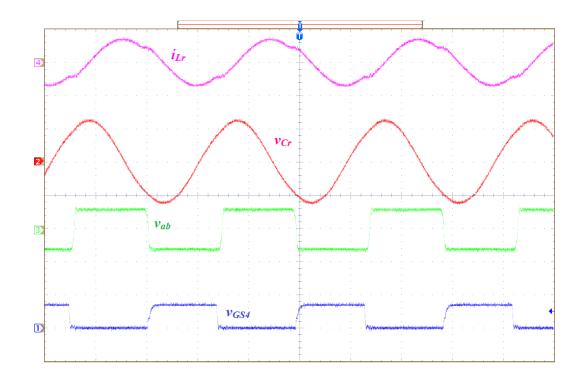

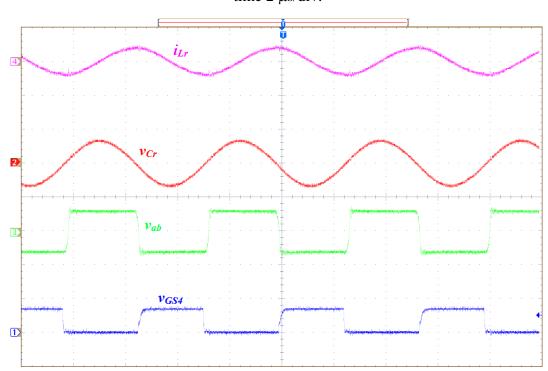

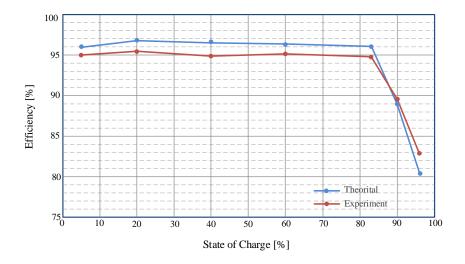

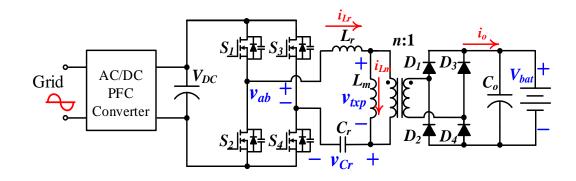

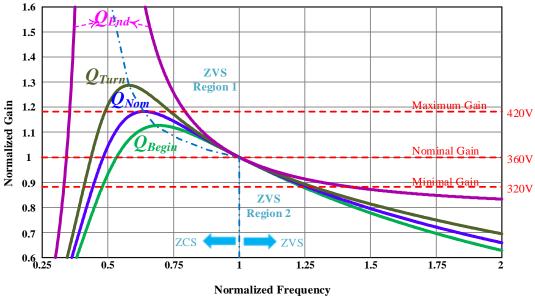

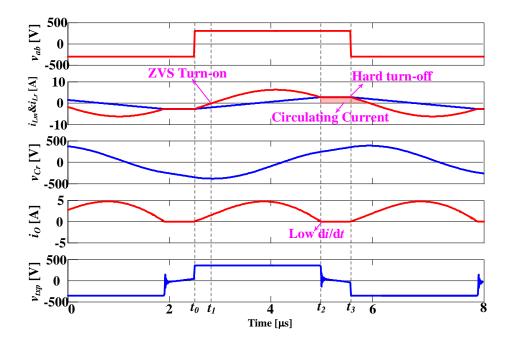

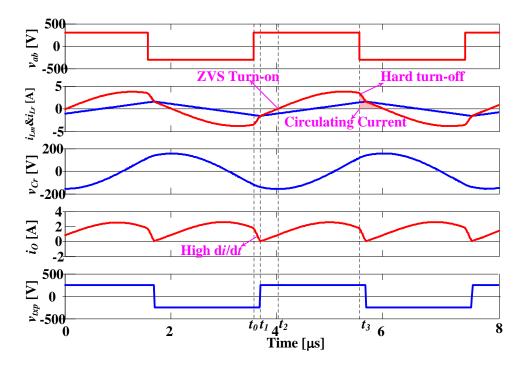

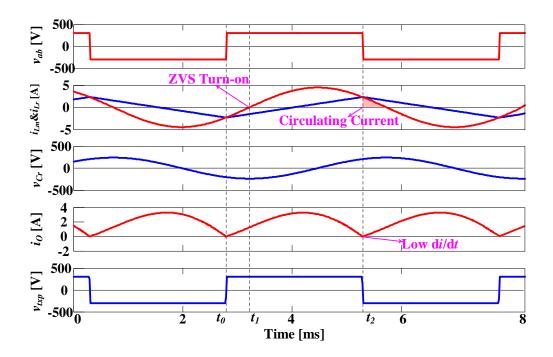

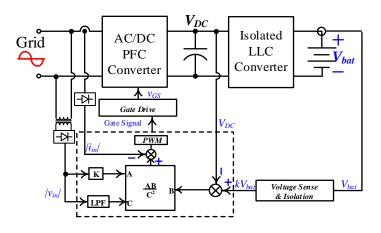

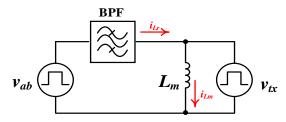

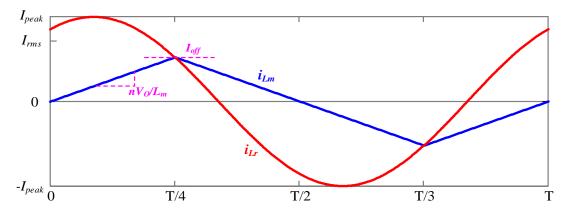

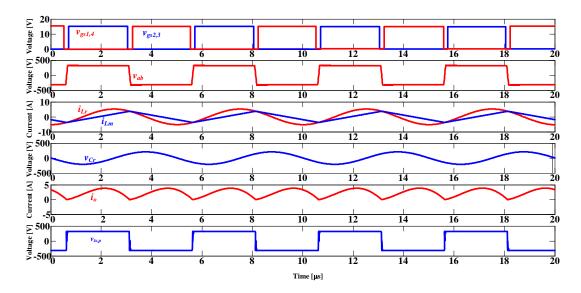

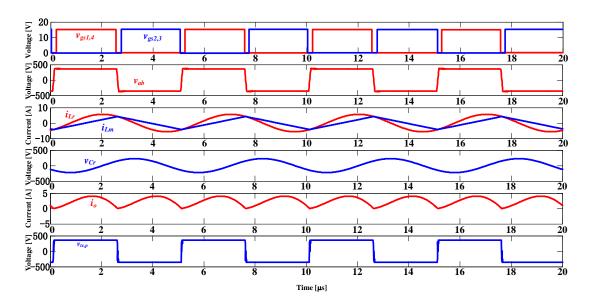

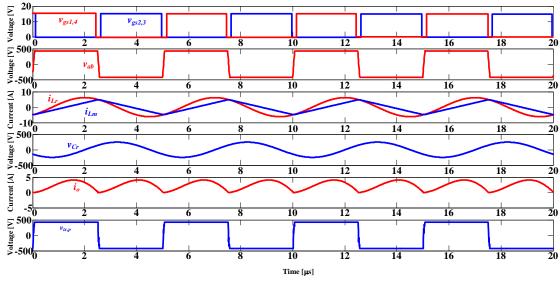

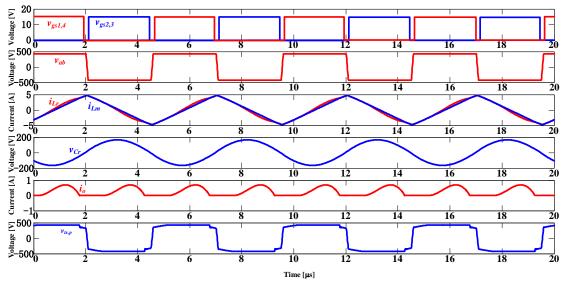

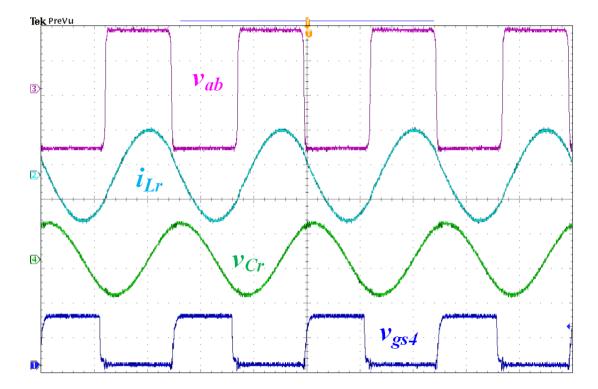

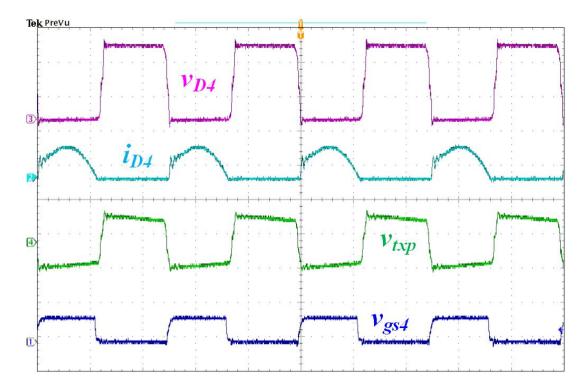

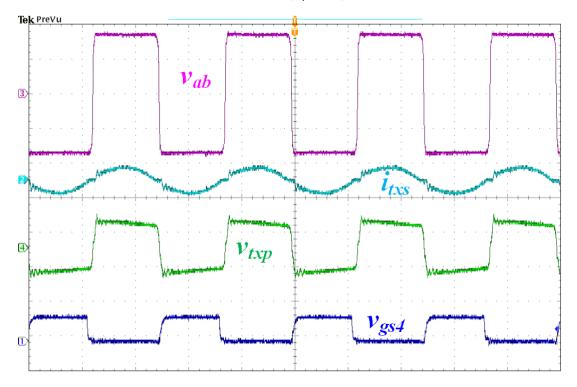

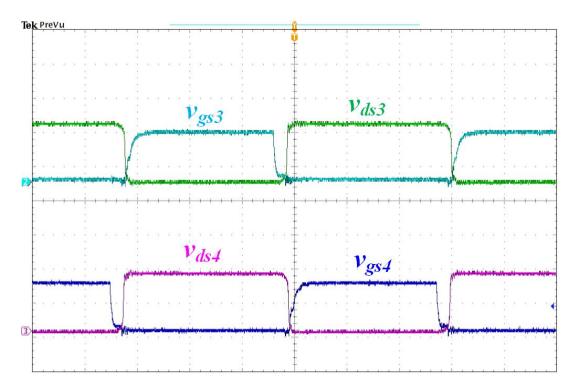

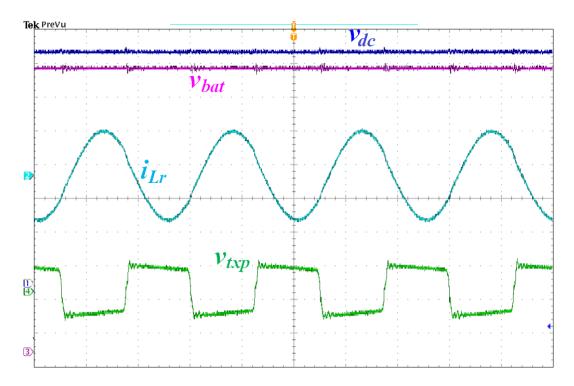

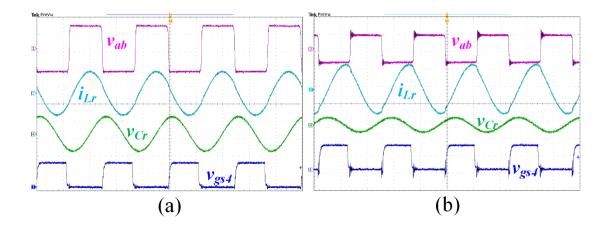

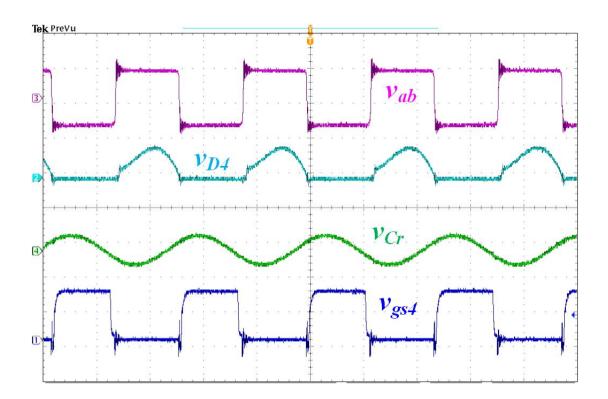

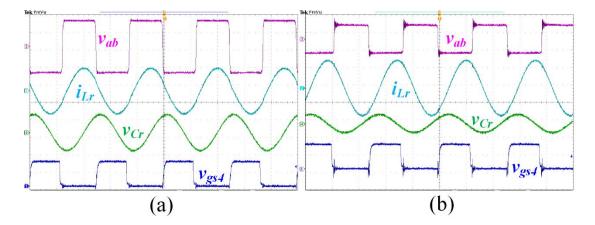

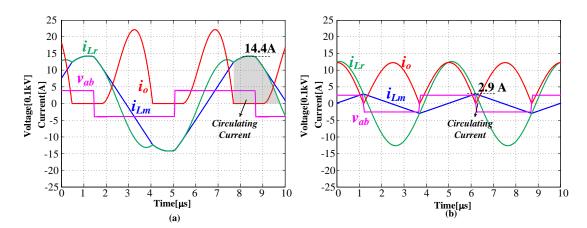

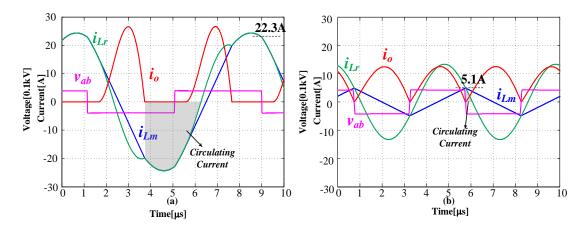

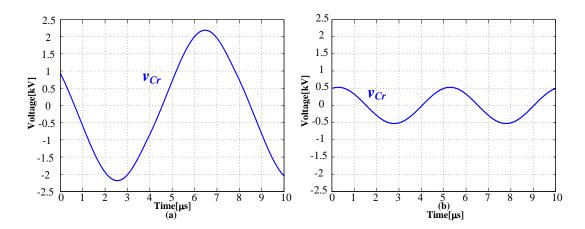

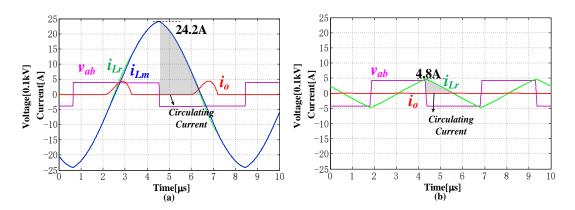

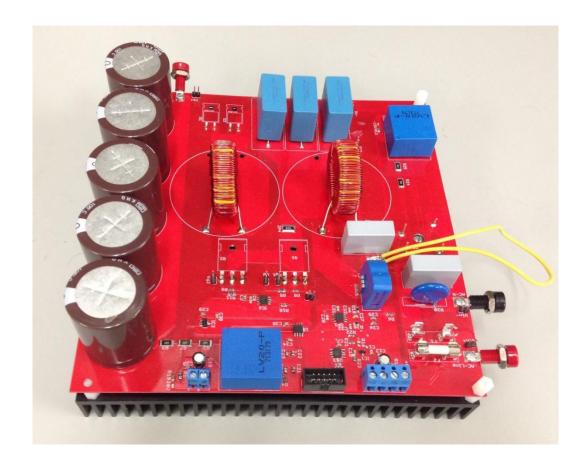

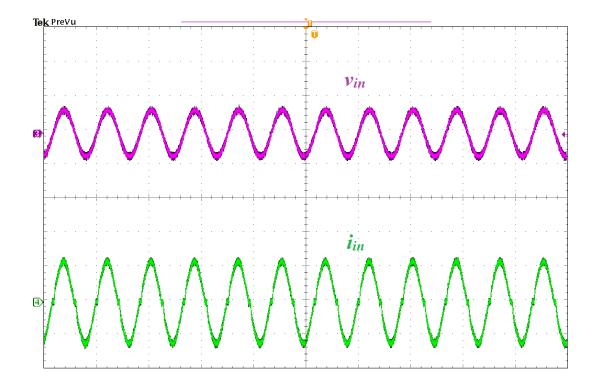

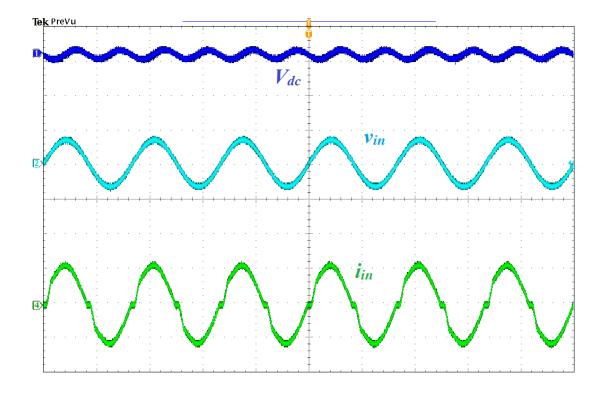

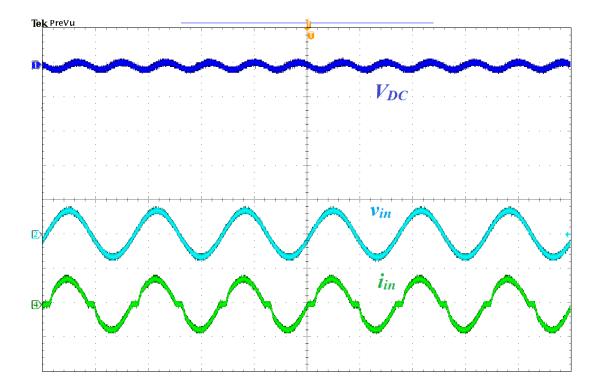

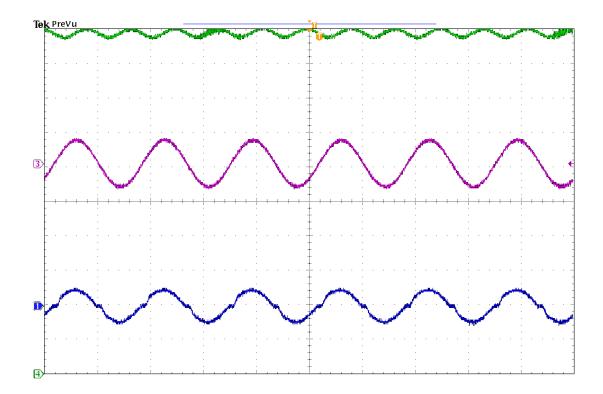

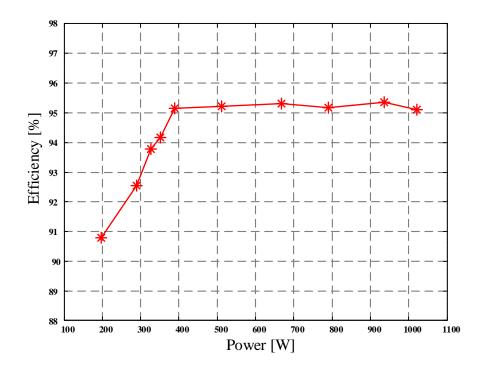

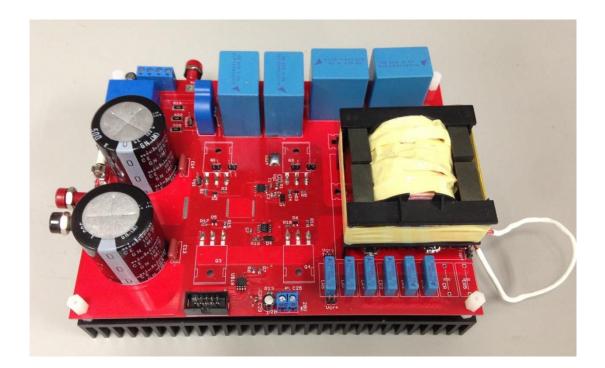

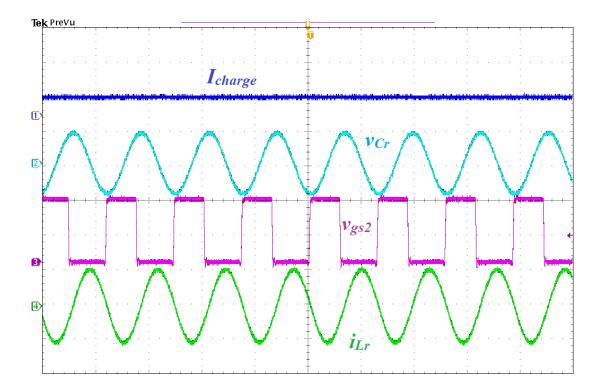

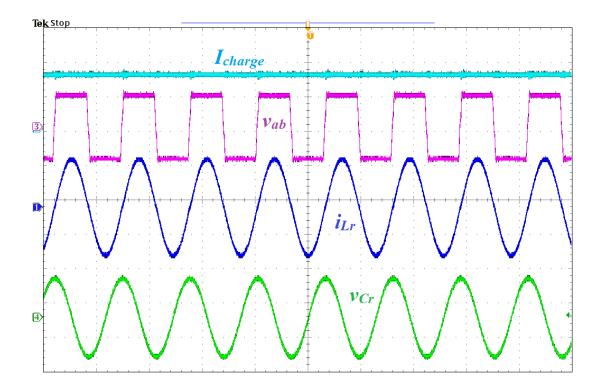

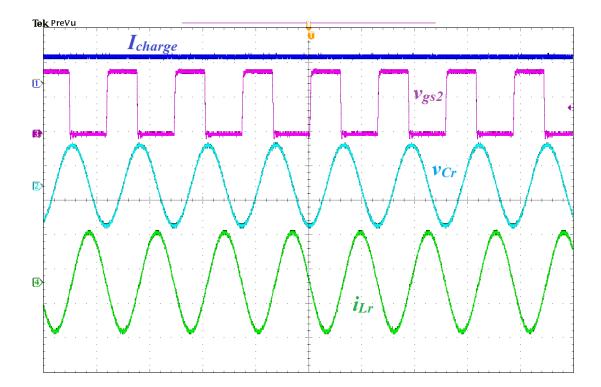

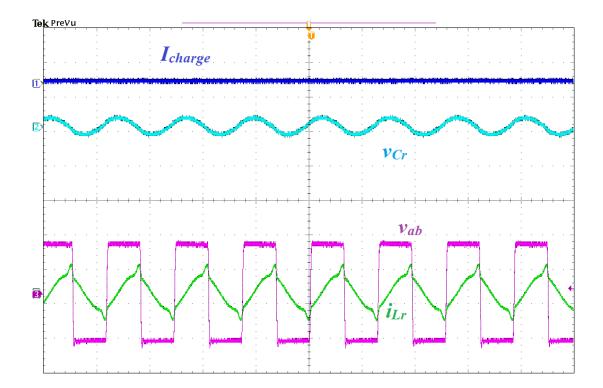

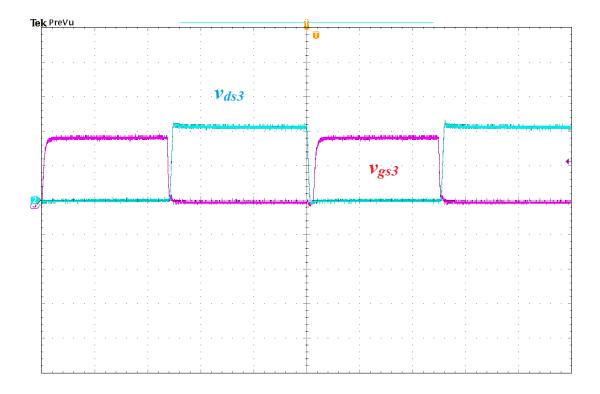

Fig. 4.10 Fig. 4.11 Simulated waveforms of LLC resonant converter in ZCS operation Fig. 4.12 Operating modes of LLC resonant converter in ZCS operation with f <Simulated waveforms of LLC resonant converter with  $f_s/2 < f < f_s.....79$ Fig. 4.13 Fig. 4.14 Operating modes of LLC resonant converter with  $f_s/2 < f < f_s$ ......80 Simulated waveforms of LLC resonant converter with  $f_s < f < f_p$  (f Fig. 4.15 Fig. 4.16 Operating modes of LLC resonant converter with  $f_s < f < f_p$  (f close to Simulated waveforms of LLC resonant converter  $f_s < f < f_p$  (*f* close to Fig. 4.17 Fig. 4.18 Operating modes of LLC resonant converter  $f_s < f < f_p$  (f close to  $f_p$ )..85 Fig. 4.19 Fig. 4.20 Three stage configuration of full bridge LLC resonant converter.....90 Fig. 4.21 Simplified full bridge LLC converter circuit and circuit model under Fig. 4.22 first harmonic approximation (FHA)......91 Frequency characteristics of LLC resonant converter......94 Fig. 4.23 Charging profile of a 360 V Li-ion battery pack rated at 1 kW......96 Fig. 4.24 Fig. 4.25 Duty cycles corresponding to 390 V, 300 V, and 200 V dc link voltages.. Dc characteristics of the designed 1 kW LLC converter......102 Fig. 4.26 Fig. 4.27 Simulated LLC results at the turning point......104 Typical core loss chart for PC47 ferrite......110 Fig. 4.28 Fig. 4.29 A 1 kW PEV charger prototype......112 Fig. 4.30 Fig. 4.31 Waveforms of interleaved boost PFC converter operating at 1 kW..... Inductors waveforms of interleaved boost PFC converter operating at Fig. 4.32 Fig. 4.33 LLC converter operating at nominal point......116 Fig. 4.34 Fig. 4.35 LLC converter operating at turning point......117 Fig. 4.36 Efficiency of the designed LLC converter versus stage of charge of Fig. 4.37 The block diagram of the conventional LLC charger structure......123 Fig. 5.1 Fig. 5.2 Dc voltage characteristics of LLC charger......124 Simulated waveforms of LLC converter operating in ZVS region 1.125 Fig. 5.3 Simulated waveforms of LLC converter operating in ZVS region 2.127 Fig. 5.4 Simulated waveforms of LLC converter operating in primary resonant Fig. 5.5 frequency..... Diagram of proposed maximum efficiency tracking technique......131 Fig. 5.6 Fig. 5.7 Equivalent circuit model of LLC converter at resonant frequency....131

| Fig. 5.8       | Resonant tank current waveform at resonant frequency                             | 132  |

|----------------|----------------------------------------------------------------------------------|------|

| Fig. 5.9       | Equivalent circuit of <i>v</i> <sub>ab</sub> transition                          | 137  |

| Fig. 5.10      | ZVS boundary waveform: MOSFETs output capacitors are charged                     |      |

| and discharged | d in the deadband                                                                | 138  |

| Fig. 5.11      | Control schema of the proposed maximum efficiency point tracking                 | g of |

| LLC charger.   |                                                                                  |      |

| Fig. 5.12      | Simulated result of LLC converter operating at begin point                       | 142  |

| Fig. 5.13      | Simulated result of LLC converter operating at nominal point                     | 142  |

| Fig. 5.14      | Simulated result of LLC converter operating at turning point                     | 143  |

| Fig. 5.15      | Simulated result of LLC converter operating at end point                         | 143  |

| Fig. 5.16      | Experiment result of LLC converter operating at rated power                      | 144  |

| Fig. 5.17      | ZCS operation of secondary diode at rated power                                  | 145  |

| Fig. 5.18      | Transformer secondary current at rated point                                     | 145  |

| Fig. 5.19      | ZVS operations of primary MOSFETs at rated power                                 |      |

| Fig. 5.20      | Input voltage and output voltage waveforms at rated power                        |      |

| Fig. 5.21      | LLC converter performance comparison at the begin point                          | 149  |

| Fig. 5.22      | Diode turning-off of designed converter using conventional fixed                 | dc   |

| link voltage   | ·                                                                                | 149  |

| Fig. 5.23      | LLC converter performance comparison at the nominal point                        |      |

| Fig. 5.24      | LLC converter performance comparison at the turning point                        |      |

| Fig. 5.25      | LLC converter performance comparison at the end point                            | 151  |

| Fig. 5.26      | Efficiencies of the designed LLC converters versus stage of charge               | e of |

| battery pack   | ·                                                                                | 152  |

| Fig. 6.1       | Charging profile of Li-ion battery                                               | 155  |

| Fig. 6.2       | Conventional two stage isolated charger based on boost PFC and                   | full |

| bridge LLC to  | opologies                                                                        | 156  |

| Fig. 6.3       | Proposed two stage isolated charger based on SEPIC and full brid                 | dge  |

| LLC topologi   |                                                                                  |      |

| Fig. 6.4       | Schematic of SEPIC converter                                                     |      |

| Fig. 6.5       | Operation modes of SEPIC converter                                               |      |

| Fig. 6.6       | Duty cycle of SEPIC converter in PFC application                                 | 161  |

| Fig. 6.7       | Averaged switch model of SEPIC converter                                         | 162  |

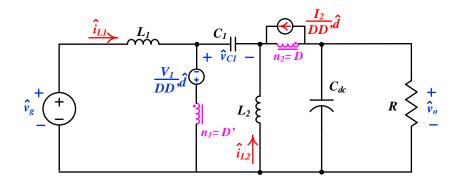

| Fig. 6.8       | Averaged dc model of the switch network                                          | 163  |

| Fig. 6.9       | Linearized small signal ac model of the switch network                           | 164  |

| Fig. 6.10      | Small signal model of SEPIC converter                                            |      |

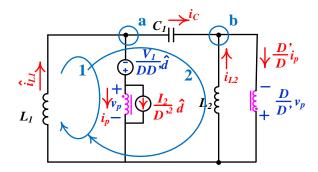

| Fig. 6.11      | Small signal model of SEPIC converter to calculate <i>G</i> <sub><i>id</i></sub> | 166  |

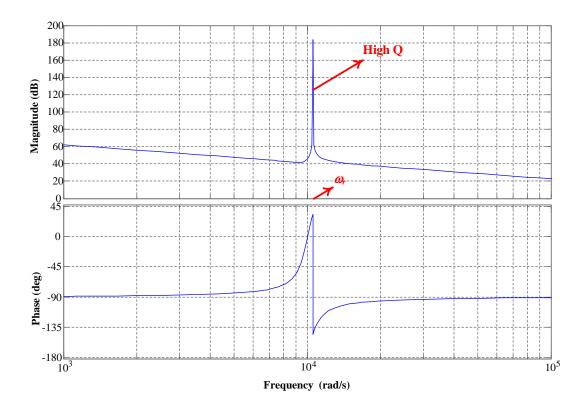

| Fig. 6.12      | Bode plot of $G_{id}$ with line phase angle = $\pi/2$                            | 168  |

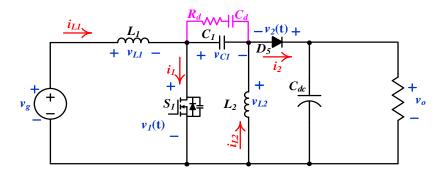

| Fig. 6.13      | Modified SEPIC converter with the damping R-C network                            |      |

| Fig. 6.14      | Bode plot of $G_{id}$ with $R_d$ - $C_d$ damping network                         | 170  |

| Fig. 6.15      | Schematic of the current loop controller with the small-signal                   |      |

| model          | · · · · · · · · · · · · · · · · · · ·                                            | 170  |

| Fig. 6.16      | Small signal model of SEPIC converter to calculate <i>G</i> <sub>vd</sub>        | 171  |

| Fig. 6.17      | Bode plot of $G_{vd}$ with $R_d$ - $C_d$ damping network                         |      |

| Fig. 6.18      | Schematic of the voltage loop controller with the small-signal                   |      |

| model          |                                                                                  | 175  |

| Fig. 6.19      | Inductor current $i_{L1}$ at boundary conduction conduction                      | 177  |

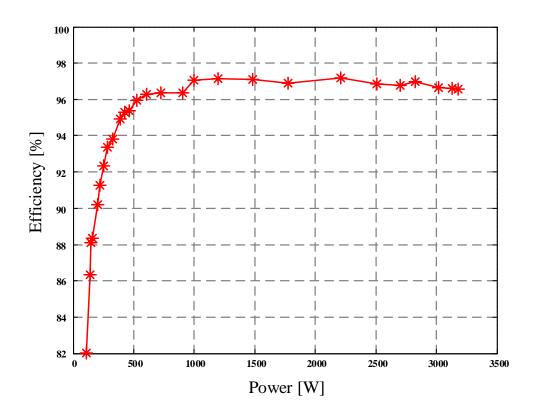

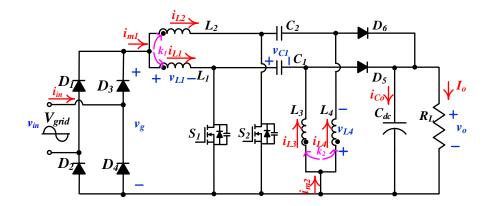

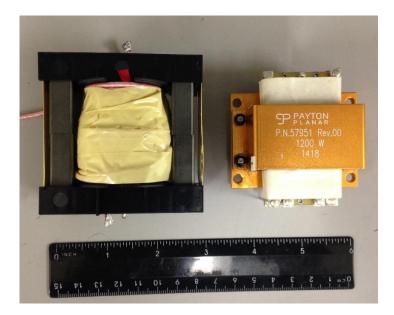

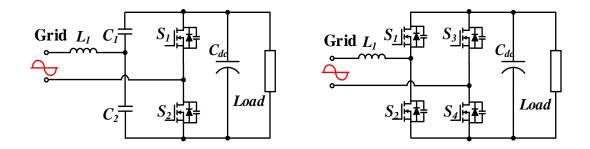

Fig. 6.20 Fig. 6.22 Fig. 6.23 Simulation results of the input voltage and input current at 1 kW...183 Fig. 6.24 Simulation results of the input current and output voltage ripple with  $V_{out} = 420 \text{V}.$  184 Fast Fourier transform analysis of input current at rated power with Fig. 6.25  $V_{out} = 420 \text{V} \dots 184$ Fig. 6.26 Simulation results of the input voltage and SEPIC capacitor voltage at Fig. 6.27 Simulation results of the input current and output voltage at Simulation results of the input current and output voltage at Fig. 6.28  $V_{out} = 100 \text{V}.....187$ Fig. 6.29 LLC converter performance comparison at the operating point A....189 Fig. 6.30 LLC converter performance comparison at the operating point B...189 Fig. 6.31 Fig. 6.32 LLC converter performance comparison at the operating point C....190 Resonant capacitor voltage stress comparison at the operating point Fig. 6.33 C..... LLC converter performance comparison at the operating point D...191 Fig. 6.34 Fig. 6.35 Designed ac/dc SEPIC PFC converter prototype......192 TMS320F28335 DSP development board......192 Fig. 6.36 Experimental results of the input voltage and the input current ( $V_{in}$  = Fig. 6.37 Experimental results of the output voltage, input voltage and the input Fig. 6.38 Experimental results of the input voltage, and the SEPIC capacitor Fig. 6.39 Experimental results of the output voltage input voltage, and the input Fig. 6.40 Experimental results of the output voltage, input voltage, and the input Fig. 6.41 Efficiency versus output power of the designed SEPIC converter...198 Fig. 6.42 Fig. 6.43 Experimental results of the LLC charger operating at point A......200 Fig. 6.44 Fig. 6.45 Experimental results of the LLC charger operating at point B......200 Fig. 6.46 Experimental results of the LLC charger operating at point C......201 Experimental results of the LLC charger operating at point D......202 Fig. 6.47 Fig. 6.48 Zero voltage switching of power MOSFET......203 Fig. 6.49 Schematic of interleaved SEPIC PFC converter suing coupled Fig. 7.1 inductors..... Fig. 7.2 PFC inductors switched at 100 kHz, 500 kHz, and MHz......210 LLC transformers switched at 200 kHz and MHz......211 Fig. 7.3 Fig. 7.4 Fig. 7.5

## Chapter 1 Introduction

## 1.1. Background

The gasoline price has kept on increasing since early 1990s. According to the Energy Information Administration (EIA) survey studies from 1990 to 2013, Fig. 1.1, the gasoline price has tripled since 1990. The rise of gas price increases the cost of conventional transportation.

Fig. 1.1. Weekly U.S. regular conventional retail gasoline prices.

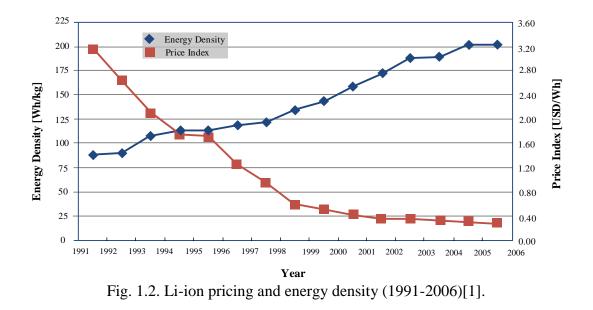

On the other hand, with the evolvement of material science and battery manufacturing technology, the price of a battery is decreasing gradually, and the corresponding energy density is increasing annually. This is demonstrated in Fig. 1.2 [1]. These trends are propelling the transition of transportation from conventional internal combustion engine (ICE) to the next generation electrified drive train systems. Consequently, more and more efforts are being involved into developing advanced electric vehicle (EV) and plug-in hybrid electric vehicle (PHEV) technologies.

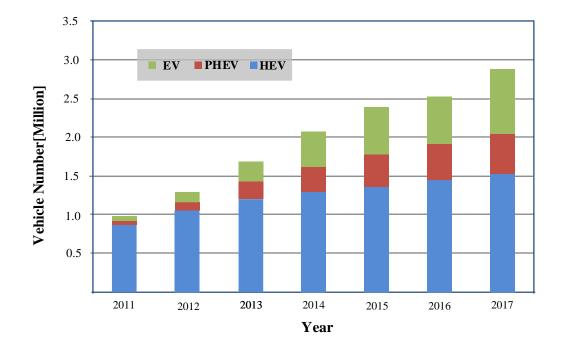

In the United States, an official domestic goal of putting one million electric vehicles on the road by 2015 has been established [2]. Different public policies have been implemented by governments to encourage the electrification of transportation system [3]. Fig. 1.3 demonstrates the projected annual light-duty electric vehicles sales worldwide. In this chart, In comparison with 2011, the sale of electric vehicles (EV) is predicted to increase by 46 times by 2017.

With the reduction of battery price, the price gap between conventional ICE vehicles and electric vehicles would become narrower. Electric vehicles are becoming more affordable. However, increasing the charging speed or reducing the charging time become one of the major concerns of ordinary consumers. Conventional ICE vehicles take 3 to 5 minutes to refuel the tank, while electric vehicles take a much

longer time to recharge the battery pack. Moreover, the lack of charging facilities also prevents the widespread adoption of electric vehicles [4].

Fig. 1.3. Annual sales of light-duty electric vehicles worldwide (2011-2017) [5].

## 1.2. Charging Infrastructures and Charging Profile of Li-ion Battery

|         |              |             | Cost of        | Miles of                 | Chargir | ng Time  |  |

|---------|--------------|-------------|----------------|--------------------------|---------|----------|--|

| Chargin | Power        | Charging    | charging       | Range for 1              |         |          |  |

| g level | supply       | Power       | infrastructure | hour of                  | EV      | PHEV     |  |

|         |              |             |                | charge                   |         |          |  |

| Level 1 | 120 VAC      | 1.4 kW @ 12 | \$500-\$800    | 3~4 miles                | ~17     | ~7 hrs   |  |

| Level I | Single Phase | amp         | Ψ300-Φ000      | J <sup>10</sup> 4 IIIICS | hrs     | ~ / 1115 |  |

| Level 2 | 240 VAC      | 3.3 kW      |                | 8~10 miles               | ~7 hrs  | ~3 hrs   |  |

|         | Single Phase | (onboard)   | \$3,150-       | o~10 lilles              | ~7 ms   | ~5 1115  |  |

| Level 2 | (Up to 80    | 6.6 kW      | \$5,100        | 17~20 miles              | ~3.5    | ~1.4     |  |

|         | amps)        | (onboard)   |                | $17\sim 20$ miles        | hrs     | hrs      |  |

|         | 3 phase 208  |             |                | 50~60 miles              |         |          |  |

| Level 3 | VAC          | >50 kW      | \$30,000-      |                          | 30~45   | ~10      |  |

|         | or 200 ~ 450 | (off board) | \$160,000      | (80% per 0.5             | mins    | mins     |  |

|         | VDC          |             |                | hour charge)             |         |          |  |

Table 1-1 Charging power levels (Based in part on [6])

| (~200 |  |  |  |

|-------|--|--|--|

| amps) |  |  |  |

Depending on the power-level and the required charging facilities, charging of EVs and PHEVs can be classified into 3 different levels (as summarized in Table 1-1).

### 1.2.1 Charging Power Levels

In the United States, level 1 charging is adopted for single phase 120 V/12 A, 60 Hz grid outlet. Level 1 charger is easy to be integrated onboard. The installation cost of level 1 charging infrastructure is estimated to be \$500 to \$800 [7], [8]. The relative low price makes level 1 applicable to home charging. However, the low charging power increases the charging time of battery pack (up to 17 hours) to charge a typical 25 kWh battery pack from 20% state of charge (SOC) to full SOC.

Level 2 charging requires 240 V power outlet, which is available at the majority of house garages as well as public facilities. In comparison with level 1, without compromising the convenience of accessibility, the level 2 charging time is much less. The cost of installation including the residential electric vehicle supply equipment (EVSE) unit is expected to be \$3,150 to \$5,100 [9]. Consequently, level 2 charging is expected to be the dominant charging method available in majority of private and public facilities [3].

Level 3 or DC fast charging extends the charging power to a much higher level (excess of 50 kW). Consequently, the charging time is significantly reduced. The level 3 charging stations are expected to charge EV to 50% SOC in 20 minutes. One of the frontier EV companies, Tesla, targets at 5 minutes fully charging its EVs in the foreseeable future using its supercharging stations [10], [11]. However, level 3 charging comes with its extremely high costs, which includes the installation cost, infrastructure cost, as well as the maintenance cost [12], [13]. Besides, delivering power to a battery pack very rapidly can cause overheat and potential damage to the battery cells. Moreover, drawing ultra-high power from the grid increases the demand from the grid and might incur overload problem of local distribution facilities [14]–[16]. Consequently, level 3 charging is mainly intended for commercial and public charging stations [17]–[19].

#### 1.2.2 Battery Swapping

Instead of charging the battery pack overnight at home, the depleted battery pack could be replaced with a fully charged one in a short time, so that the driver is able to get back onto the road fast. This is where the concept of battery swapping comes from. 90 second battery swapping time, which is less time than it takes to fill up a traditional car at the gas station, has been reported by Tesla in 2013 [20]. Battery swapping is deemed as a proposing technique, which makes up the drawbacks of relative slow battery charging speed [21], [22]. However, current battery swapping technique is too specific to be applied to different models of electric vehicles and battery types. Universal battery swapping codes or standards must be composed and implemented before spreading this technique into the commercial market.

#### 1.2.3 Battery Charging Profile

Table 1-2 lists the charging characteristics and infrastructures of the popular

EVs and PHEVs available in the market. All listed EVs and PHEVs are equipped with onboard chargers applicable to level 1 and level 2 charging. All EVs and PHEVs except Tesla Model S, utilize universal charge connector, which is defined by SAE J1772 standard.

| Vehicle          | EV<br>type | Price         | Batter<br>y           | Onboard<br>Charger | E-<br>Range | Connector<br>Type           |                | rging<br>me<br>Level |

|------------------|------------|---------------|-----------------------|--------------------|-------------|-----------------------------|----------------|----------------------|

| Nissan<br>leaf   | EV         | \$35,2<br>00  | 24<br>kWh<br>Li-ion   | 3.3 kW<br>OBC      | 100<br>mi   | SAE J1772<br>JARI/TEP<br>CO | 1<br>22<br>hrs | 2<br>8 hrs           |

| BWM<br>ActiveE   | EV         | Lease<br>only | 32<br>kWh<br>Li-ion   | 7.2 kW<br>OBC      | 100<br>mi   | SAE J1772                   | 8-10<br>hrs    | 4-5<br>hrs           |

| Ford<br>Focus    | EV         | \$39,2<br>00  | 23<br>kWh<br>Li-ion   | 6.6 kW<br>OBC      | 76 mi       | SAE J1772                   | 20<br>hrs      | 3-4<br>hrs           |

| Mitsubis<br>hi I | EV         | \$29,1<br>25  | 16<br>kWh<br>Li-ion   | 3.3 kW<br>OBC      | 62 mi       | SAE J1772<br>JARI/TEP<br>CO | 13<br>hrs      | 4~5<br>hrs           |

| Honda<br>Fit     | EV         | Lease<br>only | 20<br>kWh<br>Li-ion   | 3.3 kW<br>OBC      | 76 mi       | SAE J1772                   | 6 hrs          | 3 hrs                |

| Toyota<br>Prius  | PHE<br>V   | \$32,0<br>00  | 4.4<br>kWh<br>Li-ion  | 3.3 kW<br>OBC      | 15 mi       | SAE J1772                   | 3 hrs          | 1.5<br>hrs           |

| Chevy<br>Volt    | PHE<br>V   | \$39,1<br>45  | 16<br>kWh<br>Li-ion   | 3.3 kW<br>OBC      | 35 mi       | SAE J1772                   | 10<br>hrs      | 4 hrs                |

| Cadillac<br>ELR  | PHE<br>V   | n/a           | 16.5<br>kWh<br>Li-ion | 3.3 kW<br>OBC      | 35mi        | SAE J1772                   | n/a            | 4.5<br>hrs           |

| Tesla<br>Model S | EV         | \$95,4<br>00  | 85<br>kWh<br>Li-ion   | 10 kW<br>OBC       | 265         | Mobile<br>Connector         | 34             | 14                   |

Table 1-2 Charging characteristics and infrastructures of some manufactured

PHEVs and EVs

| mi | hrs | hrs |

|----|-----|-----|

|----|-----|-----|

\*Specification data is based on public information and is subject to change.

Li-ion cell has much higher energy density than other battery chemistries, such as lead acid cell, nickel cadmium cell, as well as Ni-metal hydride cell [23]. In EVs and PHEVs, energy density and the weight of the battery are two of the most critical parameters that determine the electric range of vehicle. Consequently, Li-ion cell has dominated the market of EVs and PHEVs. This could be observed from Table 1-2, as all the listed EVs and PHEVs are equipped with a Li-ion battery pack. It should be noted that, although extended life cycles, increased energy density, and slight cost reduction have been achieved with the evolutions of battery technology [4], Li-ion battery pack is still the most expensive and heaviest component in EVs and PHEVs.

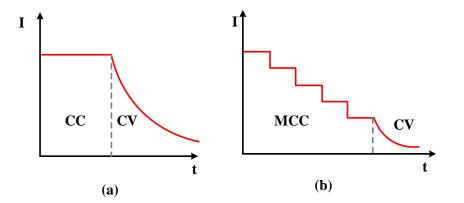

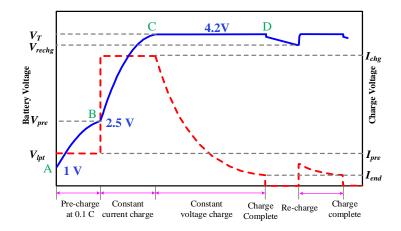

Various methods can be adopted to safely charge the Li-ion batteries. It is not only the battery chemistry which determines the power level at which a cell can accept a charge, but also the method used to charge the battery. The method shown in Fig. 1.4(a) is called constant current - constant voltage (CC-CV), which is a common charging technique. The basic idea behind this technique is that the battery is charged with a constant maximum current, typically defined by the cell manufacturer, up to the cut-off voltage. Then, it is voltage is kept fixed and it is charged at this constant voltage until the current draw decreases to around one tenth of the peak current or less, which represents a full charge [24]. To increase the charge acceptance rate of the battery, multi-stage constant current - constant voltage (MCC-CV) has been proposed [25]. The principle is nearly the same as CC-CV. However, instead of providing the battery with one constant current level, several current steps are applied up to the cutoff voltage as shown in Fig. 1.4(b).

Fig. 1.4. The Li-ion battery charging techniques, (a) constant current-constant voltage, (b) multistage constant current-constant voltage.

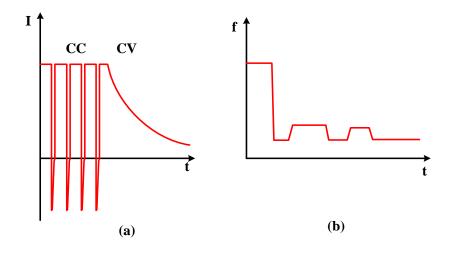

The above-described charging methods have limited transfer power capability due to polarization, which include ohm polarization, consistency polarization, and electrochemical polarization. New charging methods, which reduce the influence of polarization, and therefore increase the charge acceptance rate, are still being actively investigated and pursued. One approach which discharges the battery at specific time intervals during charging to increase the charging acceptance is proposed in [22]. This approach can be applied to both CC-CV and MCC-CV techniques in order to yield a better performance. A simplified example of the CC-CV method with negative pulses is represented in Fig. 1.5(a). Another approach proposed in [26] utilizes a variable pulse charge strategy. In this approach, the optimal pulse charge frequency is continuously determined to distribute ions in the electrolyte evenly. Between pulses, a variable rest period is applied to neutralize and diffuse the ions. This rest period is defined by a maximum power point tracker to determine the maximum level of current acceptance for a given SOC in real time. A typical waveform of the variable frequency associated with pulse charging is shown in Fig. 1.5(b). Using this method charge rate can be increased In comparison with conventional CC-CV and fixed frequency pulse charging methods.

Fig. 1.5. Advanced fast charging techniques, (a) constant current –constant voltage with negative pulse, (b) variable frequency pulse charge [27].

## 1.3. <u>Typical Energy Storage and Power Conversion Interfaces of EVs</u>

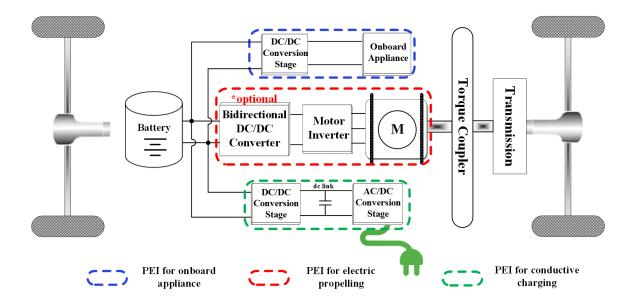

The typical power architecture of an EV is shown in Fig. 1.6. A high voltage (300 V~400 V) and high energy (tens of kWh) battery pack is installed onboard and functions as the energy storage unit. Besides, there are three main power electronic interfaces (PEIs), which are in charge of the power conversions. They are a) PEI for electric propelling, b) PEI for onboard appliances, and c) PEI for onboard charging.

Fig. 1.6. General power architecture of an EV.

The PEI for electric propelling primarily consists of a motor inverter and a bidirectional dc/dc converter. Two operation modes, propelling mode and regenerative braking mode, are associated with this interface. In propelling mode, energy is transferred from the battery pack to the electric machine. In regenerative braking mode, the electric machine functions as a generator. The retrieved power from braking is transferred back to the battery pack. The motor inverter operates as a rectifier. The optional bidirectional dc/dc converter is used to obtain control over charging and discharging of the battery as port of the PEI for electric propulsion [28].

The PEI for onboard appliances is mainly a dc/dc converter. The dc/dc converter steps down the high voltage from battery pack (300 V~400 V) to 12 V to provide power to the onboard electric appliances, such as air conditioning, headlights, stereo systems, and etc. This converter must incorporate galvanic isolation to protect the low voltage electronic system from the potentially hazardous high voltage [29].

Energy flow in this PEI is unidirectional.

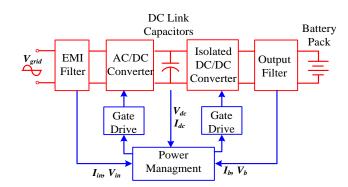

The PEI for onboard charger is used to transfer power from the grid to charge the battery pack. Typically, this onboard charger consist of two stages: 1) first stage for ac/dc conversion and power factor correction; 2) second stage for dc/dc conversion and galvanic isolation [3]. Currently, all commercialized onboard chargers have unidirectional power flow from grid to vehicle. However, since most vehicles are parked an average of 95 percent of the time, it is claimed that batteries could be used to let power flow from the vehicle to the power lines and back [30]. In this emerging vehicle-to-grid (V2G) technology, onboard chargers are required to have bidirectional power flows capability. When the vehicle is in idle mode, the battery can feed power back to the grid [31]–[34].

### 1.4. Typical Circuit Configurations of Onboard Charger

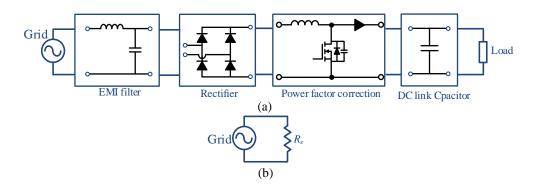

Fig. 1.7. (a) Typical block diagram of ac/dc PFC stage, (b) equivalent circuit model.

The first stage ac/dc PFC converter typically consists of an EMI filter, rectifier, PFC converter, as well as a DC link capacitor [see Fig. 1.7(a)]. The PFC converter is controlled by a high frequency signal to regulate the ac line current to follow the ac line voltage and frequency. Ideally, the ac/dc PFC stage could be

equivalent to a resistive load, as shown in Fig. 1.7(b), to eliminate the total harmonic distortion, and to maximize the power transfer.

Fig. 1.8. Typical configuration of isolated dc/dc topology.

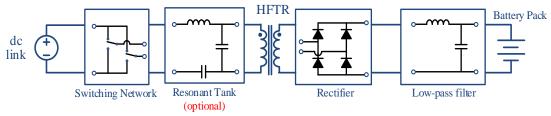

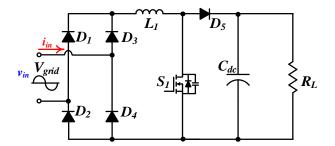

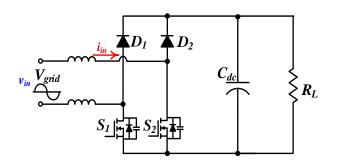

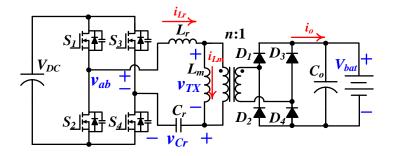

A typical second stage isolated dc/dc converter consists of a switching network, high frequency transformer, rectifier, and a low pass filter (see Fig. 1.8). For frequency modulated resonant converters, an additional resonant tank between switching network and high frequency is required.

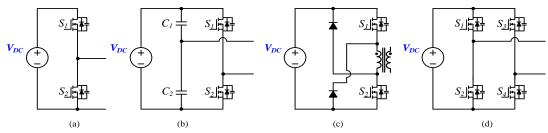

Four different switching networks are shown in Fig. 1.9. With the same dc link voltage and switch ratings, root mean square (RMS) output voltage of full bridge is twice of that of half bridge configuration. Therefore, the full bridge topology with the same switch ratings can be designed and utilized with two times higher output power capability. In order to achieve shorter charging time, higher power level is always desirable for onboard battery chargers. Consequently, only full-bridge configurations are considered in this dissertation.

Fig. 1.9. Common switching networks, (a) half bridge, (b) half bridge with split

capacitor, (c) two switch forward, (d) full bridge.

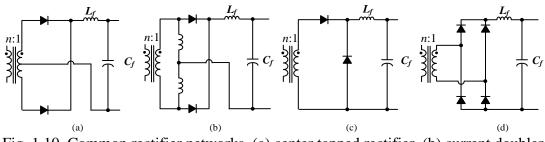

Four different rectifier networks are shown in Fig. 1.10. Half wave rectifier only utilizes half of the input voltage cycle, and does not provide a high power density. Current doubler rectifier and center-tapped rectifier are more suitable for low voltage and high current applications, respectively. The voltage rating of rectifier diodes must be higher than twice of the output voltage. However, onboard battery charging is associated with high battery pack voltage and relatively low charging current, where full bridge rectifier is more suitable. Consequently, only full-bridge rectifier configurations are considered in this dissertation.

Fig. 1.10. Common rectifier networks, (a) center tapped rectifier, (b) current doubler rectifier, (c) half wave rectifier, (d) full bridge rectifier [35].

## 1.5. Challenges in Onboard Charger Design

Typically, front-end ac/dc PFC stage is universal to different applications. While the second-stage isolated dc/dc converter is in charge of regulating the charger's output voltage and current to fit the different SOCs of battery. This dissertation focuses on the research of both the front-end ac/dc conversion and the second stage isolated dc/dc conversion.

The U.S. Department of Energy (DOE)'s technical targets on 3.3 kW level 2

onboard chargers is summarized in Table 1-3.

| 3.3 kW Charger                   |               |            |         |        |  |  |  |  |

|----------------------------------|---------------|------------|---------|--------|--|--|--|--|

| Year Cost Size Weight Efficiency |               |            |         |        |  |  |  |  |

| 2010                             | \$900-\$1,000 | 6-9 liters | 9-12 kg | 90-92% |  |  |  |  |

| 2015                             | \$600         | 4 liters   | 4 kg    | 93%    |  |  |  |  |

| 2022                             | \$330         | 3.5 liters | 3.5 kg  | 94%    |  |  |  |  |

Table 1-3 DOE technical targets on onboard charger[36]

In order to design an ultra-compact, and highly efficient onboard charging interface, following considerations must be taken into account:

1) High switching frequency is desired to reduce the volume and weight;

2) Both step-down and step-up operations should be realized to satisfy the wide output voltage range requirements;

3) Zero-voltage-switching (ZVS) feature is desired to reduce the switching losses as well as high frequency electro-magnetic interference (EMI);

4) A high-frequency transformer must be integrated to achieve galvanic isolation without compromising the size and weight;

5) Conversion efficiency must be optimized across the full battery voltage ranges as well as different load conditions.

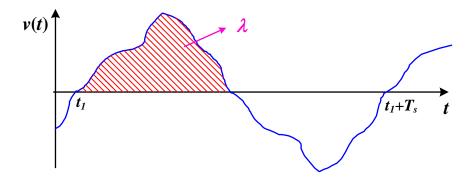

However, it is a challenging task to satisfy all above-mentioned considerations simultaneously. As shown in Fig. 1.11, higher switching frequency is associated with smaller volt-second applied to the magnetic component. According to Eq. (1.1), the flux variation is also smaller. So the corresponding core losses are reduced. However,

core loss and the switching loss increases with the increase of frequency. With higher switching frequency, the conversion efficiency will degrade.

Fig. 1.11. An arbitrary transformer primary voltage waveforms, illustrating the voltseconds applied during the positive portion of the cycle [37].

$$\Delta B = \frac{\lambda}{2nA_e} \tag{1.1}$$

where  $\lambda$  is the voltage second applied to the primary side of transformer; *n* is the number of primary turns;  $A_e$  is the effective cross section area of the magnetic core.

In high switching frequency applications, MOSFET is preferred due to its fast switching speed and no tail current. In hard switching topologies, higher switching frequencies would lead to high stress and high EMI noise. Thus, soft switching techniques, which include zero voltage switching (ZVS) and zero current switching (ZCS), are desired. For MOSFETs, ZVS is more suitable due to the fact that operation with ZVS eliminates both body diode reverse recovery and semiconductor output capacitances from inducing switching loss in MOSFETs [37]. However, ZVS technique could lead to high circulating current and increased conduction losses. Moreover, in some specific topologies, such as phase shift full bridge converter, even though ZVS operation is achievable in full loads; however, MOSFETs in the lagging leg might lose ZVS features in light load conditions.

Another challenge comes from the wide voltage variation of the high voltage battery pack in the EV. Corresponding to the depleted SOC and full SOC, the voltage of battery pack varies from the cut off voltage to the charge voltage (e.g. 320V to 420V). This means the dc/dc conversion stage must be able to be adapted to this wide voltage range. The pulse-width-modulation (PWM) topologies have the advantages of easy regulation of the output voltage in a wide range. However, they also have the disadvantages of incomplete ZVS range. Frequency modulated resonant topologies have a full ZVS range. However, the efficiency of resonant topologies can be only optimized in some specific output voltage.

To overcome those challenges and to develop an ultra-compact, highly efficient onboard charging system, following components and technologies need to be addressed:

1) Advanced magnetics material: The size of the magnetic component is constrained by the core loss associated with high switching frequency. In order to solve this problem, more advanced magnetics material with smaller core loss in higher switching frequencies must be adopted.

2) Advanced packaging technique: Packaging is directly relevant to the size of the onboard charging system. Packaging techniques help to improve the space utilization and heat dissipation.

16

3) Advanced cooling technique: Heat sinks take a large portion of the charging system volume. The size of the heat sink is directly determined by the cooling technique. Generally, active cooling is better than passive cooling. The liquid cooling is preferred in the case of conventional Silicon based power electronic interfaces.

4) Advanced switching power devices: Power losses from switching power devices such as MOSFETs and diodes take a large portion of the total system losses. Advanced power devices with low on resistances, high voltage ratings, faster switching speeds, and high operating temperature help reduce the power losses and the thermal stress.

5) Advanced converter topologies and control methods: The converter topology determines the circuit performances such as ZVS feature, EMI, circulating current, conduction losses, and switching losses. An optimized circuit topology and control method would help optimize the overall circuit performance over the wide battery SOC range.

This dissertation will mainly focus on the research of advanced converter topologies as well as control strategies using SiC power devices to optimize the overall power density and efficiency of the onboard charging system over the wide battery SOC range.

#### 1.6. <u>Silicon Carbide Power Devices</u>

As the power density, volume, and weight specifications of power electronic

systems become more stringent, topological configurations and control methods alone is not sufficient to fulfill the performance targets [27]. Wide bandgap power devices are expected to open up new markets for power conversion in high-power, hightemperature, and high-frequency applications where silicon (Si) technology is approaching its theoretical power limits [38]. Majority of industries including automotive and semiconductor device manufacturers are exploring the usage of wide band gap Silicon Carbide (SiC) and Gallium Nitride (GaN) power devices for power electronic based applications [39], [40].

The electric properties of various semiconductors power devices are summarized in Table 1-4. The bandgap of SiC is approximately three times higher than Si. This increases the energy needed for an electron jumping from valence band to conduction band. Thus, the number of electron-hole pairs created due to temperature rise is significantly reduced. This makes SiC devices much more stable in high temperature and more suitable for high-temperature applications. Moreover, the thermal conductivity of SiC devices is much better than Si devices, which facilities heat dissipation and the heat sink size can be significantly reduced.

| Property                                                        | Si   | GaAs | 3C-<br>SiC | 6H-<br>SiC | 4H-<br>SiC | 2H-<br>GaN | Diamond |

|-----------------------------------------------------------------|------|------|------------|------------|------------|------------|---------|

| Bandgap, $E_g$ (eV)                                             | 1.12 | 1.43 | 2.4        | 3.0        | 3.2        | 3.4        | 5.5     |

| Electric<br>Breakdown<br>Field, <i>E<sub>c</sub></i><br>(MV/cm) | 0.25 | 0.3  | 2.0        | 2.5        | 2.2        | 3.0        | 5.0     |

| Saturated<br>Electron<br>Drift Velocity,                        | 1.0  | 1.0  | 2.5        | 2.0        | 2.0        | 2.5        | 2.7     |

Table 1-4 Electric properties of semiconductors

| $v_{sat} (10^7 \text{cm}^2/\text{s})$                         |      |      |      |      |      |     |      |

|---------------------------------------------------------------|------|------|------|------|------|-----|------|

| Electron<br>Mobility $\mu_n$<br>(cm <sup>2</sup> /V·s)        | 1350 | 8500 | 1000 | 500  | 950  | 440 | n/a  |

| Hole Mobility,<br>$\mu_p (\text{cm}^2/\text{V}\cdot\text{s})$ | 480  | 400  | 40   | 80   | 120  | 30  | 1600 |

| Relative<br>dielectric<br>constant, <i>ɛ</i> r                | 11.9 | 13.0 | 9.7  | 10.0 | 10.0 | 9.5 | 5.0  |

| Thermal<br>Conductivity<br>(W/cm·K)                           | 1.5  | 0.5  | 5.0  | 5.0  | 5.0  | 1.3 | 20.0 |

| Direct/Indirect<br>Bandgap                                    | Ι    | D    | Ι    | Ι    | Ι    | D   | Ι    |

Another advantage of SiC devices is their higher electric breakdown field. As shown in Table 1-4, 4H-SiC has an order of magnitude higher breakdown field and higher temperature capability than conventional Si. This means for the same blocking layer dopant density, SiC device has over an order of magnitude higher voltage blocking capability. High voltage blocking capability brings the benefit of reduced leakage current and associated leakage losses. On the other hand, for a desired breakdown voltage, SiC device has an order of magnitude lower blocking layer thickness [41]. Schottky didoes and MOSFETs are majority carries power devices. The on resistance of majority carrier power devices is inversely proportional to the blocking layer thickness, and proportional to the doping concentration. The reduced blocking layer thickness with increased doping concentration yield a SiC majority carrier devices much smaller on resistance compared to that of Si majority carrier devices[42]. Low on resistance brings the benefit of reduced conduction losses.

As shown in Table 1-4, GaN has higher bandgap and breakdown field than SiC. This brings GaN power devices the benefits of good high temperature performance, high breakdown voltage, and low on resistance. However, GaN power devices are not commercially available at over 200V, 12A power ratings, which makes them not commercially ready to be used in designing onboard chargers for the automotive industry. This dissertation will mainly focuses on design and optimization of onboard charger based on Si and SiC power devices.

The parameters of three 600 V and 8 A power diodes are presented in Table 1-5. In comparison with Si Schottky diode, the forward voltage drop of SiC Schottky diode is improved by 31%. The leakage current of SiC Schottky diode (50  $\mu$ A) is comparable with that of PiN Si diode (30  $\mu$ A), while significantly improved in comparison with Si Schottky diode (250  $\mu$ A). This improvement brings the benefit of reduced leakage losses. The most attracting feature of SiC Schottky diode is its zero reverse recovery. This eliminates the turning-off losses of the SiC Shottky diodes. The SiC diodes are the optimal options for ultra-high switching frequency applications. Specifically, applying SiC Schottky diodes in boost PFC stage results in zero reverse recovery losses and significantly reduced EMI.

| Part Number                           | ETX0806 | QH08TZ600 | C3D08060A |

|---------------------------------------|---------|-----------|-----------|

| Material                              | Si      | Si        | SiC       |

| Technology                            | PiN     | Schottky  | Schottky  |

| Breakdown voltage (V)                 | 600     | 600       | 600       |

| Average forward current $I_F(A)$      | 8       | 8         | 8         |

| Forward voltage at $I_F$ , $V_F$ (V)  | 3.4     | 2.6       | 1.8       |

| Maximum Reverse current, $I_R(\mu A)$ | 30      | 250       | 50        |

| Junction Capacitance, $C_T(pF)$       | 6       | 25        | 39        |

| Reverse Recovery time, $t_{rr}$ (ns)  | 14      | 11.1      | 0         |

| Price, (USD)                          | 1.12    | 2.86      | 3.86      |

Table 1-5 Comparison of diodes parameters

\*Price data is based on digikey as of July 2013 and is subject to change.

The parameters of three 24 A power MOSFETs are summarized in Table 1-4. Super junction technology allows the thick drift region of a power MOSFET to be heavily doped. Therefore, the on resistance could be reduced without compromising the breakdown voltage [43]. As shown in the table, SiC power MOSFET has comparable on resistance with the Si super junction MOSFET. However, the voltage rating of SiC power MOSFET is twice of its Si counterpart.

In comparison with regular 1.2 kV Si power MOSFET, the on resistance, input capacitance, and output capacitance of SiC MOSFET are reduced by 68%, 88.9%, and 89.7%, respectively. Reduced on resistance, input capacitance and output capacitance bring the benefits of reduced conduction losses, gate driving losses and switching losses, respectively. The reverse recovery time and charge of body diode of SiC MOSFETs are reduced by 89.1%. Moreover, the fall time is reduced by 50%. This means faster switching speed can be achieved with SiC power MOSFET with the same voltage rating. The disadvantage of SiC power MOSFETs mainly comes from its high diode forward voltage drop. As shown in the table, the body diode of SiC MOSFET has three times higher forward voltage than Si MOSFET. This increases the conduction losses from the body diodes. Generally, the body diodes should be avoided to reduce the associated conduction losses.

| Part Number                               | IPB60R160C6            | APT24M120L                   | CMF10120D |

|-------------------------------------------|------------------------|------------------------------|-----------|

| Material                                  | Si                     | Si                           | SiC       |

| Technology                                | CoolMOS super junction | POWER<br>MOS 8 <sup>TM</sup> | Z-FET     |

| Drain-source voltage, $V_{DS}(V)$         | 650                    | 1200                         | 1200      |

| Drain current at $25^{\circ}$ C $I_D$ (A) | 24                     | 24                           | 24        |

| Static drain-source on resistance         | 0.16                   | 0.50                         | 0.16      |

Table 1-6 Comparison of MOSFETs parameters

| $R_{ON}\left( \Omega ight)$                         |           |        |         |

|-----------------------------------------------------|-----------|--------|---------|

| Input capacitance, <i>C</i> <sub>iss</sub> (pF)     | 1660      | 8370   | 928     |

| Output capacitance, $C_{oss}$ (pF)                  | 314       | 615    | 63      |

| Fall time, $t_f(ns)$                                | 8         | 42     | 21      |

| Rise time, <i>t<sub>rise</sub></i> (ns)             | 13        | 27     | 34      |

| Body diode forward voltage, $V_F$ (V)               | 0.9@11.3A | 1V@12A | 3.5V@5A |

| Body diode reverse recovery time, $t_{rr}(ns)$      | 460       | 1270   | 138     |

| Body diode reverse recovery charge, <i>Qrr</i> (nC) | 8200      | 30000  | 97      |

| Price, (USD)                                        | 4.61      | 20.2   | 16.67   |

\*Price data is based on digikey as of July 2013 and is subject to change.

#### 1.7. Intellectual Merit and List of Contributions

This dissertation focuses on how to achieve both the efficiency optimization over the wide voltage range and the capability to charge the deeply depleted battery packs simultaneously. We mainly concentrated on the perspectives of power electronics topologies, and control methodologies using SiC power semiconductors. The proposed efficiency enhancement technique can be extended to higher power level and will have a profound impact on the deployment of next generation PEVs.

The contributions of this work are listed as below.

1) We conducted a comprehensive literature review on the PEV onboard charging.

2) We proposed a new methodology to effectively evaluate the charging performances of resonant topologies.

3) We proposed and developed a Si based level 1 onboard charger based on

interleaved Boost PFC and full bridge LLC topologies.

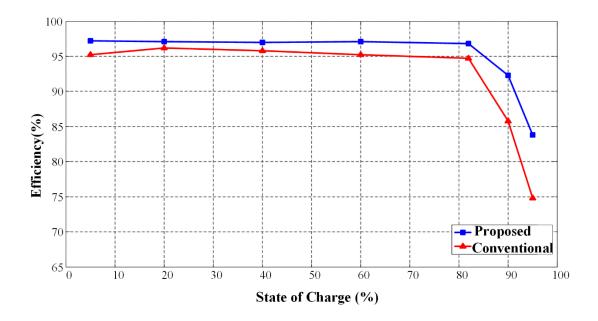

4) We proposed a novel maximum efficiency point tracking technique for LLC based chargers. Using this proposed technique, we make the dc link voltage follow the battery voltage, so that the LLC converter is always operating in the vicinity of its resonant frequency, where the circuit losses are minimized. An efficiency improvement of 2.1% at the heaviest load condition and 9.1% at the lightest load condition for LLC conversion stage are demonstrated experimentally. This is the main engineering contribution of this work.

5) We proposed and developed a novel SiC based level 2 charger based on SEPIC PFC stage and maximum efficiency point tracking technique for LLC converter. For the first time, we achieved both the efficiency optimization over the wide voltage range and the capability to charge the deeply depleted battery pack simultaneously. The developed loss evaluation methodology, control technique, and design philosophy are modeled and validated mathematically. This is the main theoretical contribution of this work.

## 1.8. <u>Outline of Dissertation</u>

This dissertation consists of eight chapters.

Chapter 1 is the introduction.

In chapter 2, states of the art of isolated charger topologies are reviewed and compared. Three different boost type converters (conventional boost, bridgeless boost, and interleaved boost) are discussed and compared comprehensively for the front-end ac/dc PFC applications. For the second stage dc/dc conversion, different isolated dc/dc topologies are investigated for PEV battery charging applications. A comprehensive comparison is made between conventional full bridge isolated PWM buck converter, full bridge phase-shift PWM converter, full bridge series resonant pulse-frequency-modulation (PFM) converter, and full bridge LLC series parallel PFM converter.

In chapter 3, a methodology is proposed to effectively evaluate the circuit performance of resonant topologies in battery charging applications. This methodology includes evaluating the battery voltage, charging current, as well as the input root mean square (RMS) current characteristics to design the resonant chargers and to compare the chargers' performance. Using the proposed method, four full-bridge isolated resonant chargers, which are rated at 3.2 kW and used to charge a 360 V Li-ion battery pack, are designed and evaluated. Based on the analytical results, it is shown that the LLC charger takes the advantages of LCC and PRC chargers, while avoiding the drawbacks of SRC chargers. LLC can maintain better efficiency, voltage regulation, as well as short circuit protection performance over the full range of battery SOC. Thus, LLC could be chosen as a suitable candidate for PEV battery charging applications.

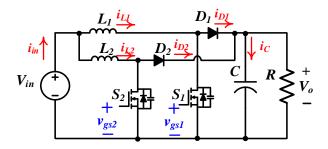

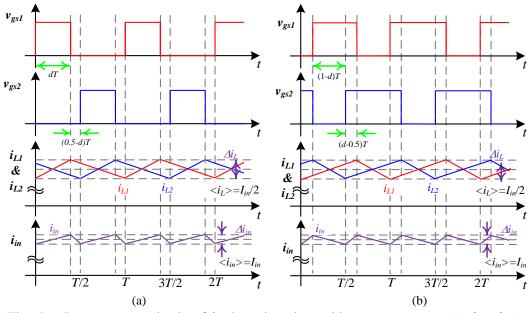

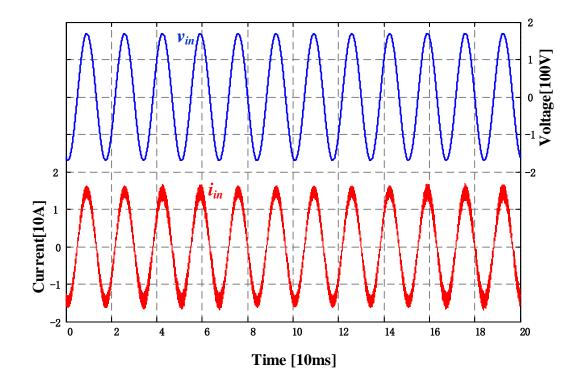

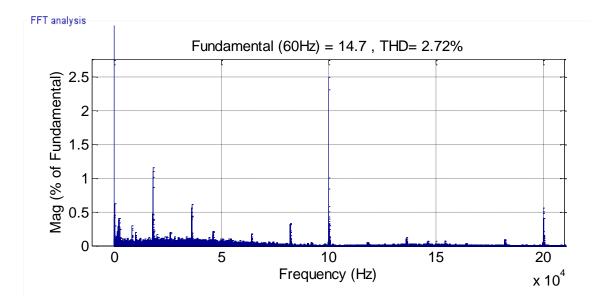

In chapter 4, a level 2 onboard PEV battery charger is proposed. Interleaved boost topology is used in the first stage for PFC and THD reduction while reducing volume of the magnetic components. In the second stage, a full bridge LLC resonant converter is employed to achieve high conversion efficiency over the full voltage range of the battery pack. The suitability and advantages of the proposed converter are discussed and design guidelines are provided through theoretical analyses for both interleaved boost and full bridge LLC topologies. As a case study, design considerations for a 1 kW level 2 charger, which converts 110 V, 60 Hz ac to battery voltage range of 320 V to 420 V are provided.

The experimental results are presented for validation of simulations and analytical studies. The first stage interleaved boost converter demonstrates unity power factor operation at the rated power and achieves THD less than 4%. In the second stage LLC converter, the switching losses and conduction losses are optimized through operating the converter close to resonance frequency of the resonant tank.

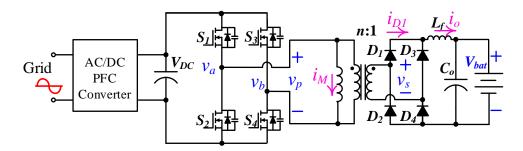

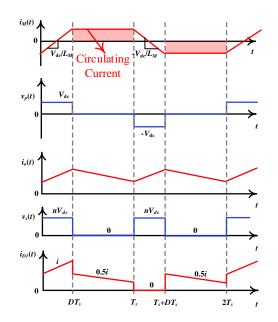

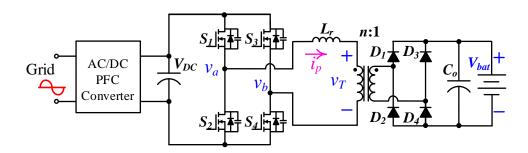

In chapter 5, a novel maximum efficiency point tracking technique is proposed for LLC based plug-in electric vehicle battery chargers. With this proposed technique, dc link voltage always follows the change of battery pack voltage; which ensures that an LLC converter is always operating at the primary resonant frequency. Detail modeling and losses analysis are provided for an LLC converter operating at the resonant frequency. According to the theoretical analysis, a guideline is detailed to design LLC converters operating at maximum efficiency point. The designed LLC converter is simulated, and the simulation results show that an LLC converter is able to provide 2.5% efficiency improvement at the heaviest load condition and 8.9% efficiency improvement in the lightest load condition.

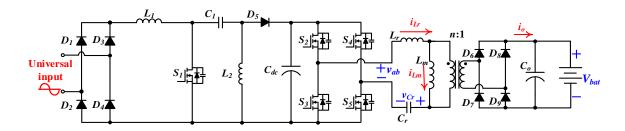

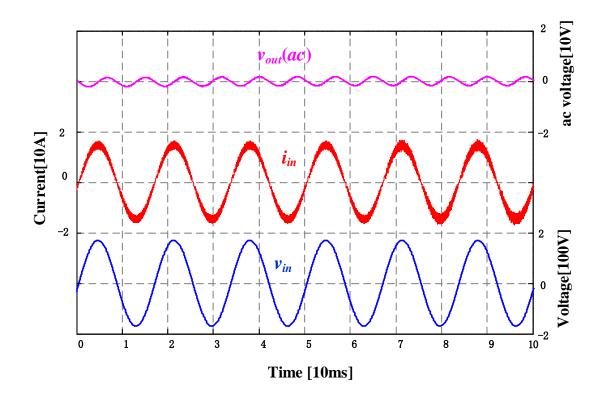

In chapter 6, an onboard PEV battery charger based on a SEPIC PFC stage

and an LLC topology is proposed. Proposed topology combination is able to charge the deeply depleted battery packs, whose voltage might goes down to 100 V. The maximum efficiency point tracking technique for the LLC topology is utilized to optimize the conversion efficiency of the charger. Since SEPIC topology owns the features of both boosting the input voltage and chopping the input voltage, it is utilized in the front-end power factor correction stage. A 3.3 kW charger prototype, which includes both the ac/dc and the isolated dc/dc stages, is designed to validate the proof of concept. Simulation results and experimental results demonstrate that the designed charger is able to maintain a wide dc link voltage range (100V-420V) while keeping the LLC converter operating at its maximum efficiency point.

Chapter 7 concludes this dissertation. Contributions of this work are summarized in this chapter. The future work is also discussed. The future efforts would focus on three aspects. 1) Implement the interleaved SEPIC PFC converter using coupled inductors, so that the power level of the PFC stage can be increased. 2) Boost the switching frequency from around one hundred kilo Hz to higher than Mega Hz. So that the size of the passive components is able to be further reduced. 3) Modify the circuit topology so that the power flow can be bidirectional.

## Chapter 2 State of The Art Isolated Battery Chargers

## 2.1 <u>Introduction</u>

In plug-in electric vehicles (PEVs), an ultra-compact, highly efficient onboard charger is desired. In order to achieve those targets, the converter topologies must be optimized for high voltage PEV battery charging applications.

In PEV battery charging applications, the battery voltage and load condition vary in a wide range depending on the different state of charge (SOC) of the battery, as well as different battery types [44], [45]. Therefore, operating with maximum efficiency through reducing the conduction and switching losses over the full output voltage and load ranges is a challenging issue in PEV charger design.

In comparison with conventional pulse width modulation (PWM) converters, frequency modulated resonant converters exhibit advantages such as (a) reduced switching losses and thus higher conversion efficiency, (b) capability to operate at higher switching frequency, which helps to reduce the size of magnetic components and thus to improve the power density, and (c) zero voltage switching feature, which can eliminate some sources of electromagnetic interference [37], [46]. Consequently, resonant dc/dc converters are deemed as a good candidate for front-end dc/dc conversion applications, which requires a constant output voltage [35], [47], [48].

In this chapter, state of the art ac/dc PFC and isolated dc/dc topologies are reviewed for PEV battery charging applications. This chapter is organized as follows; Section 2.2 compares the performance of conventional boost, bridgeless boost, as well as interleaved boost topologies in the power level of level 2 charging. In section 2.3, four different isolated full bridge dc/dc topologies are analyzed, discussed, and compared for PEV battery charging applications. Finally, Section 2.4 summarizes the study and features the benefits based on the achieved results.

## 2.2 <u>Review of Front End ac/dc PFC Topologies</u>

Front end ac/dc converter is a critical component of PEV charger. Proper selection of the topology is essential to meet the regulatory requirements for input current harmonics, output voltage regulation and implementation of power factor correction [49]–[52].

Boost topology and its derivatives are widely used for ac/dc PFC purposes [53]. In comparison with operation in continuous conduction mode (CCM), boost converter operating in discontinuous mode (DCM) would have smaller switching losses. However, for high power level, operation in DCM means large current stress to circuit components. Therefore, only CCM is considered for high power PEV battery charging applications. Conventional boost topology, bridgeless boost topology, as well as interleaved boost topology are reviewed for application in ac/dc PFC stage for PEV battery charging applications.

#### 2.2.1 Conventional Boost PFC Converter

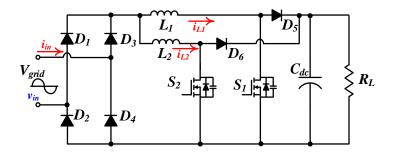

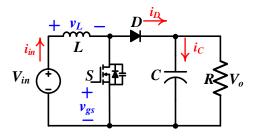

Fig. 2.1. Single phase boost PFC converter.

Fig. 2.1 shows the schematic of a single phase boost PFC converter. A diode bridge is utilized to rectify the ac voltage from the grid to dc; a boost converter is followed to correct the power factor. In comparison with interleaved topology, the ripple current of the filter capacitor is pretty high [54]. The main limitation of conventional boost PFC converter is the high conduction losses due to the current flow through the semiconductor devices [27]. The high frequency operation makes the reverse recovery losses from the boost diode a big concern. Utilizing SiC Schottky diodes could alleviate the reverse recovery problems to some extent. However, this also increase the total cost. Moreover, in high power level, the high peak current of the inductor in DCM is associated with bulky magnetic component.

2.2.2 Bridgeless Boost PFC Converter

#### Fig. 2.2. Bridgeless PFC boost converter.

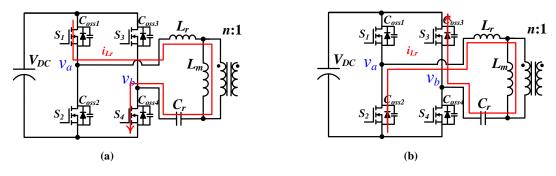

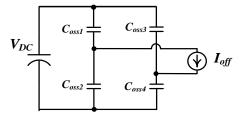

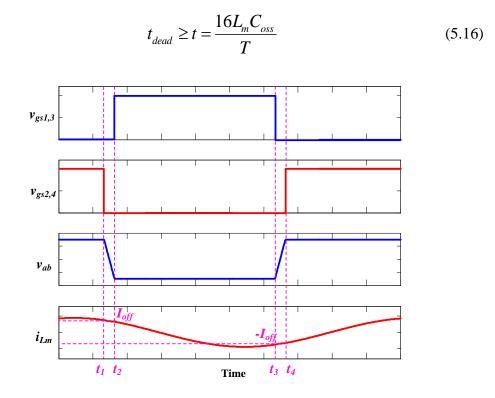

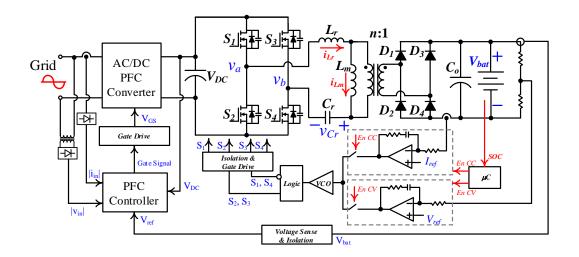

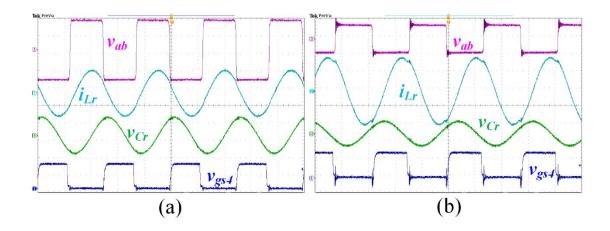

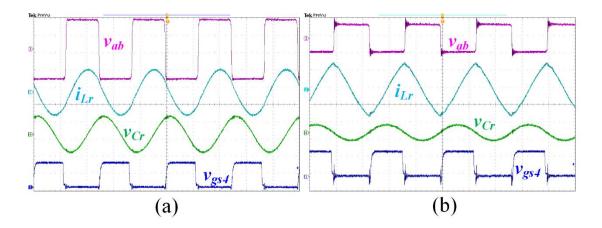

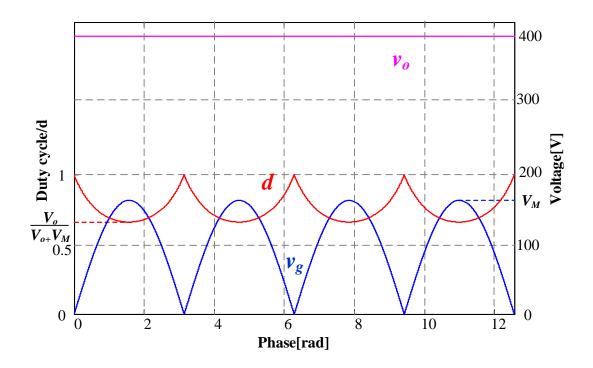

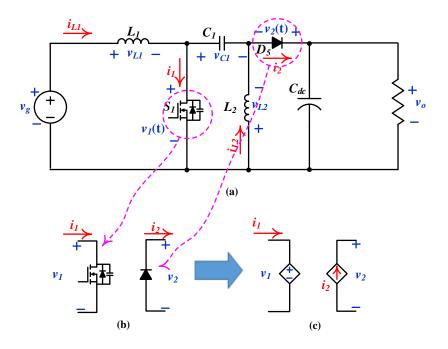

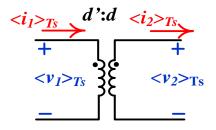

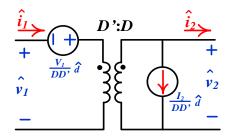

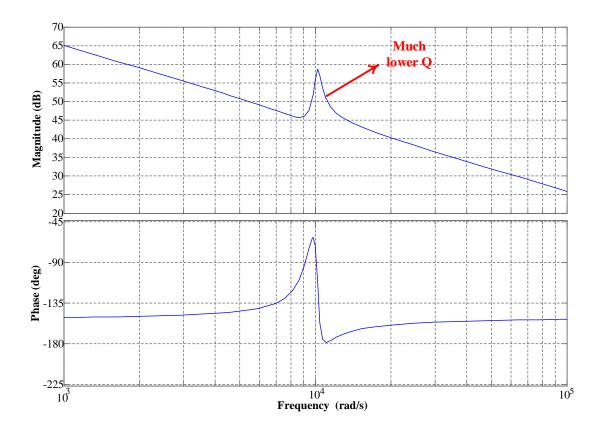

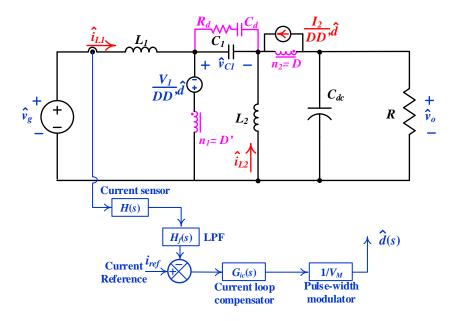

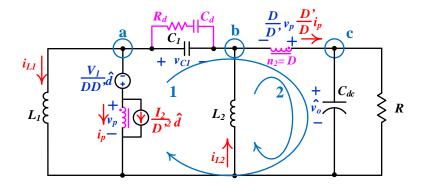

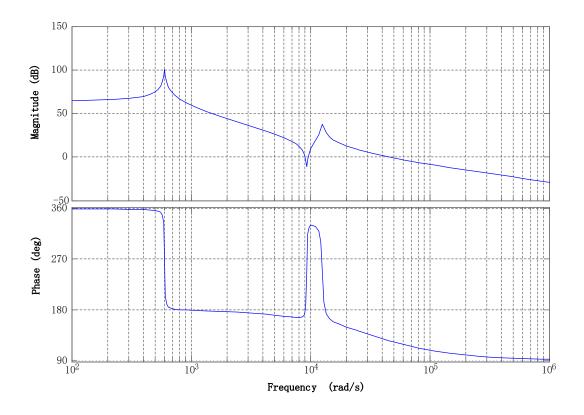

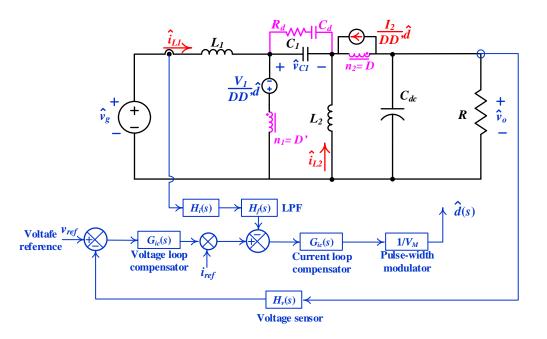

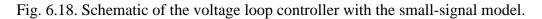

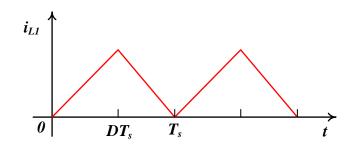

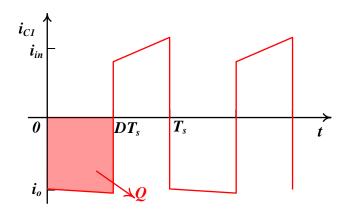

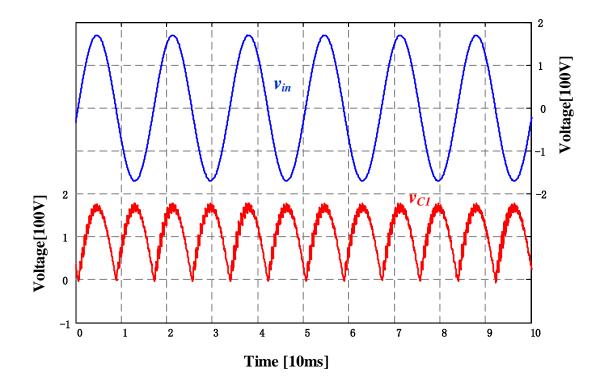

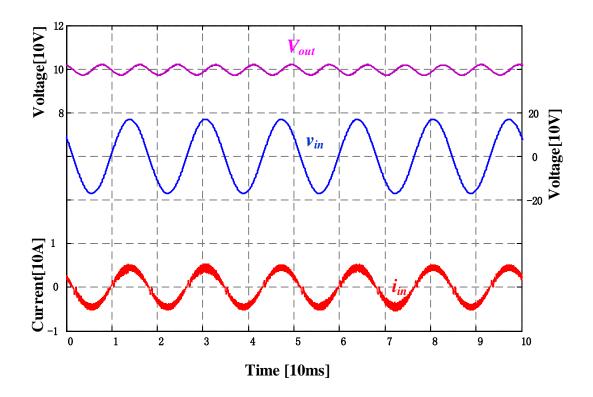

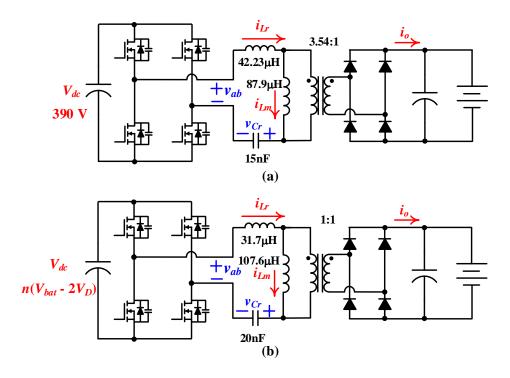

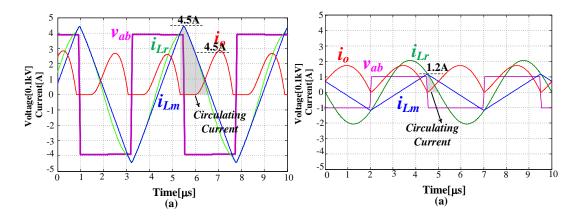

Fig. 2.2 shows the schematic of bridgeless PFC boost converter. In comparison with conventional boost PFC converter, bridgeless topology gets rid of the diode bridge while keep the boost feature. Consequently, the loss associated with diode rectifier bridge is reduced, which makes it suitable to be applied to higher power level. However, bridgeless configuration brings problems of high EMI [55], [56]. Besides, the floating input line makes it impossible to sense the input voltage without a low frequency transformer or an optical coupler. In order to sense the input current, complex circuit is necessary to sense the current in the MOSFET and diode separately [52], [57]. Moreover, in high power level, the high peak current of the inductor is also associated with bulky magnetic components.