#### ABSTRACT

| Title of dissertation:    | CHAOTIC OSCILLATIONS<br>IN CMOS INTEGRATED CIRCUITS                                                                                                                          |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Myunghwan Park, Doctor of Philosophy, 2013                                                                                                                                   |

| Dissertation directed by: | Professor Daniel P. Lathrop<br>Department of Physics<br>Department of Electrical and Computer<br>Engineering<br>Institute for Research in Electronics and<br>Applied Physics |

|                           | Doctor John C. Rodgers<br>Institute for Research in Electronics and                                                                                                          |

**Applied Physics**

Chaos is a purely mathematical term, describing a signal that is aperiodic and sensitive to initial conditions, but deterministic. Yet, engineers usually see it as an undesirable effect to be avoided in electronics. The first part of the dissertation deals with chaotic oscillation in complementary metal-oxide-semiconductor integrated circuits (CMOS ICs) as an effect behavior due to high power microwave or directed electromagnetic energy source. When the circuit is exposed to external electromagnetic sources, it has long been conjectured that spurious oscillation is generated in the circuits. In the first part of this work, we experimentally and numerically demonstrate that these spurious oscillations, or out-of-band oscillations are in fact chaotic oscillations. In the second part of the thesis, we exploit a CMOS chaotic oscillator in building a cryptographic source, a random number generator.

We first demonstrate the presence of chaotic oscillation in standard CMOS circuits. At radio frequencies, ordinary digital circuits can show unexpected nonlinear responses. We evaluate a CMOS inverter coupled with electrostatic discharging (ESD) protection circuits, designed with  $0.5\mu m$  CMOS technology, for their chaotic oscillations. As the circuit is driven by a direct radio frequency injection, it exhibits a chaotic dynamics, when the input frequency is higher than the typical maximum operating frequency of the CMOS inverter. We observe an aperiodic signal, a broadband spectrum, and various bifurcations in the experimental results. We analytically discuss the nonlinear physical effects in the given circuit : ESD diode rectification, DC bias shift due to a non-quasi static regime operation of the ESD PN-junction diode, and a nonlinear resonant feedback current path. In order to predict these chaotic dynamics, we use a transistor-based model, and compare the model's performance with the experimental results. In order to verify the presence of chaotic oscillations mathematically, we build on an ordinary differential equation model with the circuit-related nonlinearities. We then calculate the largest Lyapunov exponents to verify the chaotic dynamics. The importance of this work lies in investigating chaotic dynamics of standard CMOS ICs that has long been conjectured. In doing so, we experimentally and numerically give evidences for the presence of chaotic oscillations.

We then report on a random number generator design, in which randomness derives from a Boolean chaotic oscillator, designed and fabricated as an integrated circuit. The underlying physics of the chaotic dynamics in the Boolean chaotic oscillator is given by the Boolean delay equation. According to numerical analysis of the Boolean delay equation, a single node network generates chaotic oscillations when two delay inputs are incommensurate numbers and the transition time is fast. To test this hypothesis physically, a discrete Boolean chaotic oscillator is implemented. Using a CMOS 0.5  $\mu$ m process, we design and fabricate a CMOS Boolean chaotic oscillator which consists of a core chaotic oscillator and a source follower buffer. Chaotic dynamics are verified using time and frequency domain analysis, and the largest Lyapunov exponents are calculated. The measured bit sequences do make a suitable randomness source, as determined via National Institute of Standards and Technology (NIST) standard statistical tests version 2.1.

### CHAOTIC OSCILLATIONS IN CMOS INTEGRATED CIRCUITS

by

Myunghwan Park

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2013

Advisory Committee: Professor Daniel P. Lathrop, Chair/Advisor Doctor John C. Rodgers, Co-Advisor Professor Steve M. Anlage Professor Robert W. Newcomb Professor Thomas M. Antonsen © Copyright by Myunghwan Park 2013

## Dedication

To my parents Jonghwa Park and Sookwon Kim for all their support, love, sacrifices, and prayers.

#### Acknowledgments

I would like to give special thanks to my two greatest advisors, Professor Daniel Lathrop and Doctor John Rodgers. My long journey has started from Summer of 2009, when I was introduced to unknown fields of chaos. I would like to express my gratefulness to Professor Daniel Lathrop for giving me an invaluable opportunity to work this challenging and interesting projects. He has always encouraged me in every positive ways and showed boundless enthusiasm. I also give my special appreciations to Doctor John Rodgers who is a great engineer and scientist. I am forever grateful to his dedications to the projects. I will cherish the opportunity I had to work with him and always remember his valuable discussions, lessons, and times.

I would like to thank Professor Steve Anlage, Professor Robert Newcomb, and Professor Thomas Antonsen for agreeing to serve my thesis committee and for giving inputs in the dissertation.

My colleagues at the IREAP have enriched my life in University of Maryland in many ways. I would like thank Dr. Zeynep Dilli and Hien Dao for insightful discussions we had on our research. Many thanks go to many colleagues, David Meichle, Matthew Adams, Barbara Brawn-Cinani, Hansen Nordsiek, and Dan Zimmerman who have continuously given supports over my work. It was great privilege to work with these smart and wonderful people and friends.

This graduate school life would have not been made this far without my wife, Ena Kim. I would never forget her love, support, prayers, and endurance and I promise to return all for the rest of our lives. Last, but not the least, I would not be where I am now, without the supports, prayers, and sacrifices from my parents. I truly appreciate for everything that my parents have done for me.

In the end, I would like thank both Office of Naval Research and Air Force Office of Scientific Research for their support of this work.

## Table of Contents

| Lis | st of '    | Tables         |                                                               | vii      |

|-----|------------|----------------|---------------------------------------------------------------|----------|

| Lis | st of ]    | Figures        |                                                               | viii     |

| 1   | Intro      | oductior       | 1                                                             | 1        |

|     | 1.1        | Motiva         | tion                                                          | 1        |

|     | 1.2        | Theore         | etical Background                                             | 4        |

|     |            | 1.2.1          | Chaotic Circuits in Nonlinear Dynamics                        | 4        |

|     |            | 1.2.2          | Examples of Electromagnetic Interference Effects              |          |

|     | 1.3        | Organi         | zation of the Thesis                                          | 18       |

|     | 1.4        | List of        | Contributions                                                 | 19       |

| 2   | Exp        |                | al Chaotic Oscillation in CMOS Digital Circuits               | 22       |

|     | 2.1        |                | ew                                                            |          |

|     | 2.2        |                | ircuit Overview                                               |          |

|     | 2.3        | Design         | of CMOS Inverter Chain and Electrostatic Discharging Circuits |          |

|     |            | 2.3.1          | CMOS Inverter                                                 |          |

|     |            | 2.3.2          | Cascaded Output Buffer                                        |          |

|     |            | 2.3.3          | Electrostatic Discharging Protection Circuit                  |          |

|     | 2.4        | -              | mental Demonstration of Chaotic Oscillation                   |          |

|     |            | 2.4.1          | Experimental Setup                                            |          |

|     |            | 2.4.2          | Packaging and Printed Circuit Board Design                    |          |

|     |            | 2.4.3          | Experimental Results under Microwave Excitation               |          |

|     | ~ <b>-</b> | 2.4.4          | Calculation of Lyapunov Exponents                             |          |

|     | 2.5        |                | sion : Theoretical Background of Nonlinear Sources            |          |

|     |            | 2.5.1          | ESD-to-RFI Rectification                                      |          |

|     |            | 2.5.2          | Non-Quasi Static Analysis in PN-junction                      |          |

|     | 0.0        | 2.5.3          | Low Frequency LC Resonant Current                             |          |

|     | 2.6        | Conclu         | sions                                                         | 51       |

| 3   |            | 0              | Chaotic Oscillation in CMOS Digital Circuits                  | 53       |

|     | 3.1        | Overvı         | ew                                                            | 53       |

|     | 3.2        |                | stor-Based Simulation : Compact Modeling                      |          |

|     |            | 3.2.1          | Non-Quasi Static features in the BSIM model                   | 54       |

|     |            | 3.2.2          | Simulation Results                                            | 57       |

|     | 3.3        |                | ry Differential Equations : Numerical Modeling                | 63       |

|     |            | 3.3.1          | Nonlinear Sub-Functions in ODEs                               | 63<br>70 |

|     |            | 3.3.2          | Simulation Results                                            | 70<br>72 |

|     | <u>م</u>   | 3.3.3<br>Summe | Calculation of Lyapunov Exponents                             | 72       |

|     | 3.4        | Summa          | ary                                                           | 73       |

| 4  | Desi   | o i r                                                                                                                                      | 75 |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 4.1    | Overview                                                                                                                                   | 75 |

|    | 4.2    | Numerical Analysis of Boolean Chaos                                                                                                        | 77 |

|    | 4.3    | Discrete Boolean Chaotic Oscillator                                                                                                        | 80 |

|    | 4.4    | IC realization of the CMOS Boolean Chaotic Oscillator                                                                                      | 84 |

|    |        |                                                                                                                                            | 84 |

|    |        | 0                                                                                                                                          | 87 |

|    | 4.5    |                                                                                                                                            | 92 |

| 5  | Cry    | ptographic Physical Random Number Generator                                                                                                | 93 |

|    | 5.1    | Overview                                                                                                                                   | 93 |

|    | 5.2    | Random Number Generation                                                                                                                   | 95 |

|    | 5.3    | Statistical Tests                                                                                                                          | 99 |

|    | 5.4    | Summary                                                                                                                                    | 01 |

| 6  | Con    | clusions and Future Research 10                                                                                                            | 04 |

|    | 6.1    | Conclusions                                                                                                                                | 04 |

|    |        | 6.1.1 Chaotic Oscillation as HPM effect in CMOS ICs                                                                                        | 04 |

|    |        | 6.1.2 Chaotic Oscillation in Cryptographic Random Number Gen-                                                                              |    |

|    |        | $eration \ldots 10$ | 06 |

|    | 6.2    | Future Directions                                                                                                                          |    |

|    | 6.3    | Closing Remarks                                                                                                                            |    |

|    | DOU    |                                                                                                                                            |    |

| А  | BSI    | M Parameters 1                                                                                                                             | 10 |

| В  | Cod    | le for Numerical Models 1                                                                                                                  | 14 |

|    | B.1    | Main Function                                                                                                                              | 15 |

|    | B.2    | Subfunctions                                                                                                                               |    |

| Bi | bliogi | raphy 1                                                                                                                                    | 18 |

## List of Tables

| 2.1 | Physical dimensions of the designed circuit             | 27  |

|-----|---------------------------------------------------------|-----|

| 2.2 | Switching Characteristics of CMOS inverter              | 31  |

| 5.1 | Comparison of different random number generator sources | 95  |

| 5.2 | Type I and II error in Statistical hypothesis testing   | 100 |

| 5.3 | Results of NIST statistical test $\alpha = 0.01$        | 103 |

# List of Figures

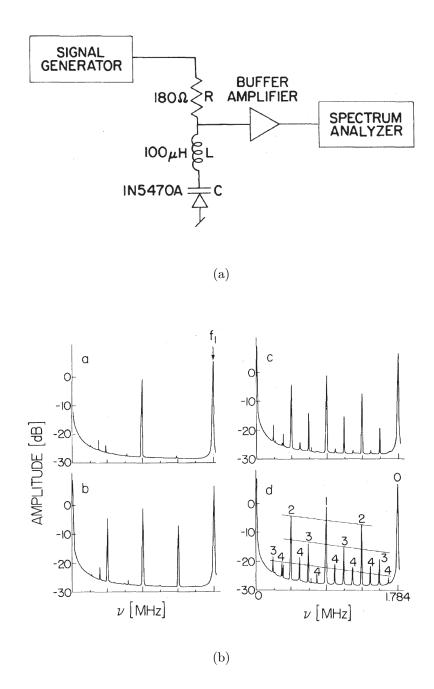

| 1.1 | (a) Circuit diagram of driven anharmonic oscillator. This circuit con-                     |          |

|-----|--------------------------------------------------------------------------------------------|----------|

|     | sists of a nonlinear capacitor, a resistor, and an inductor [1]. (b)                       |          |

|     | Voltage spectrums as RF amplitudes change, driving circuits from                           | 7        |

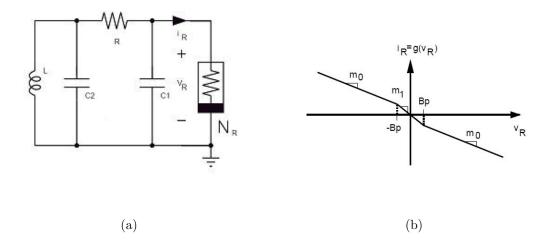

| 1.2 | <ul><li>(a) Circuit diagram of Chua chaotic circuit.</li><li>(b) Current-voltage</li></ul> | 1        |

| 1.2 | transfer characteristics of Chua diode [19]                                                | 8        |

| 19  |                                                                                            | 0        |

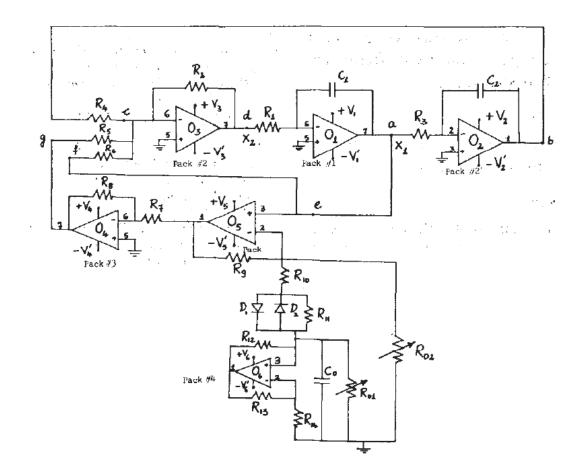

| 1.3 | Circuit diagram of an RC Op-Amp chaos generator using a hysteresis                         | 9        |

| 1 / | <ul><li>[21]</li></ul>                                                                     | 9        |

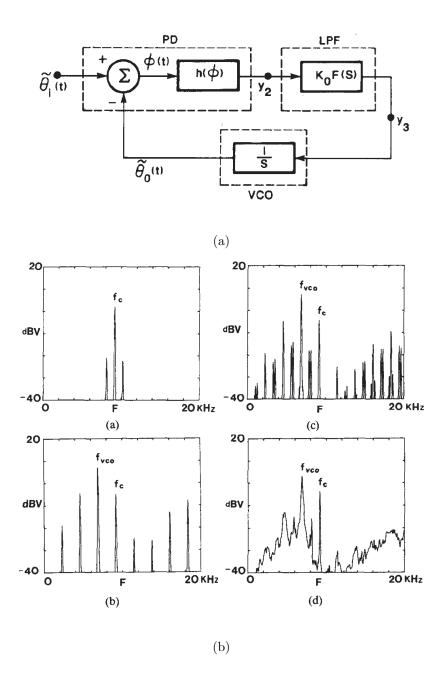

| 1.4 |                                                                                            | 11       |

| 15  |                                                                                            | 11<br>10 |

| 1.5 |                                                                                            | 12       |

| 1.6 | Example of Boolean chaos circuit, which consists of one NAND gate                          | 19       |

| 17  | 0                                                                                          | 13       |

| 1.7 | Classes of core chaotic oscillators. (a) sinusoidal oscillator with a                      |          |

|     | parallel RC, (b) using diode inductor composite, and (c) with FET                          | 14       |

| 1.8 | and capacitor composite [33]                                                               | 14       |

| 1.0 | verse field creates the multiplications of free electrons by impact ion-                   |          |

|     | izations. (b) Scanning electron microscopy image of a junction break-                      |          |

|     |                                                                                            | 16       |

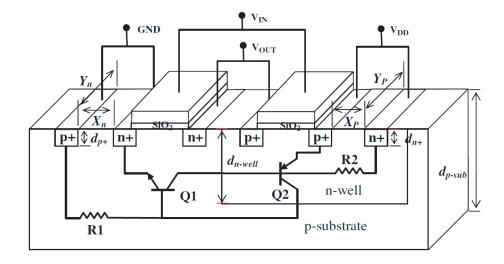

| 1.9 | Schematic diagram of CMOS inverter showing two parasitic bipolar                           | 10       |

| 1.0 | junction transistors $Q_1$ and $Q_2$ . Latch-up effects are due to the BJT                 |          |

|     | • • • •                                                                                    | 17       |

|     |                                                                                            | 11       |

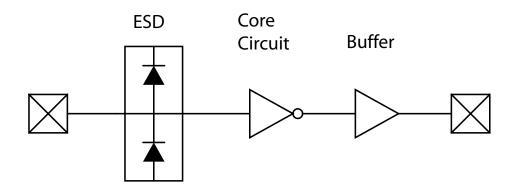

| 2.1 | Schematic diagram and basic elements in modern CMOS digital ICs.                           | 25       |

| 2.2 | Basic components of CMOS digital circuit, consisting of electrostatic                      |          |

|     | discharging (ESD) protection circuit, core circuit, and output buffer.                     | 26       |

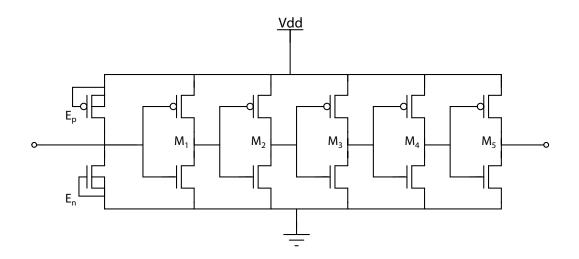

| 2.3 | (a) Circuit diagram of a CMOS inverter designed using On-Semiconductor                     | •        |

|     | $0.5\mu$ m process technology. This circuit resembles the simplest digital                 |          |

|     | circuit. The circuit consists of ggNMOS and gcPMOS ESD protec-                             |          |

|     | tion circuits at the input $(E_p \text{ and } E_n)$ . The inverter functions at M1         |          |

|     | and output buffers M2, M3, M4, and M5 are designed to drive enough                         |          |

|     | current at the capacitive load. (b) Picture of device-under-test (DUT)                     |          |

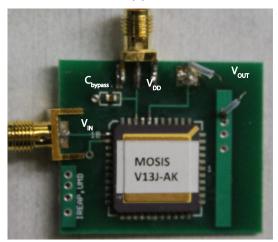

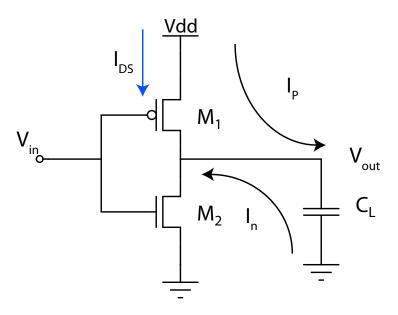

|     | 1                                                                                          | 28       |

| 2.4 | Circuit diagram of a CMOS inverter. The switching current is the                           |          |

|     | 0 1                                                                                        | 29       |

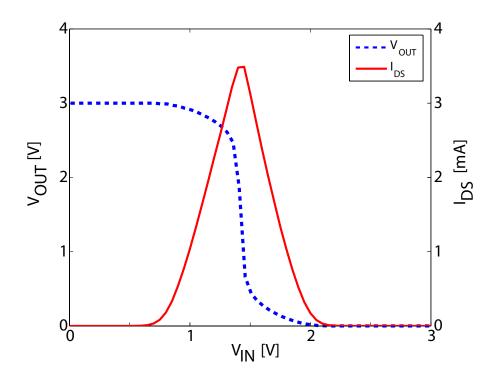

| 2.5 | Experimental results of DC transfer characteristics and short cur-                         |          |

|     | rent of CMOS inverter in DC condition. Peak current of 3.5 mA is                           |          |

|     | 1 0                                                                                        | 30       |

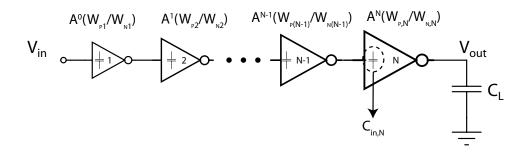

| 2.6 | Schematic diagram of a cascaded scale-up buffer. The number of                             |          |

|     | stages N should be an even number, and A is a scale ratio for the                          |          |

|     | widths of transistors                                                                      | 32       |

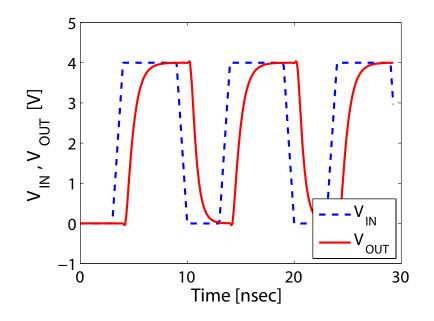

| 2.7  | Time evolution of input and output voltage of the designed buffer.<br>The simulated results show that the output of buffer has only a small                                                                                                                                                                                                                 |   |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

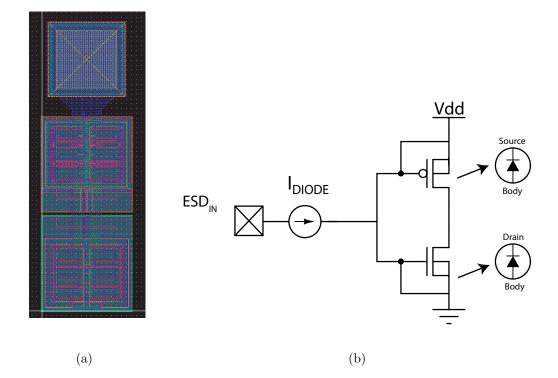

| 2.8  | <ul><li>(a) Layout of ESD protection circuits. The topmost square repre-</li></ul>                                                                                                                                                                                                                                                                          | • | 33 |

|      | sents a pad design, and the two bottom squares represent several ESD MOSFETs, connected as back-to-back diode. (b) ESD event occurring at the input of CMOS digital circuits. $V_{DD}$ is biased at 4V,                                                                                                                                                     |   |    |

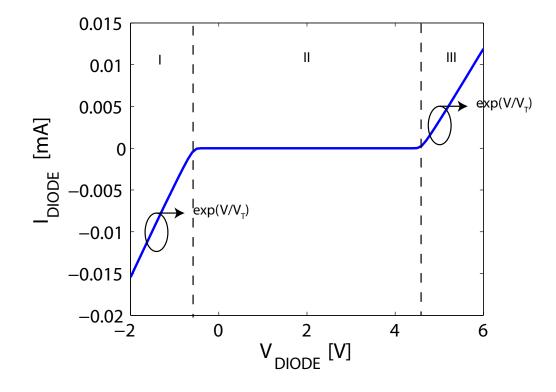

| 2.9  | and $I_{DIODE}$ is measured at the input                                                                                                                                                                                                                                                                                                                    |   | 35 |

|      | Current-voltage transfer curves in Region I and III follows the Shock-<br>ley diode equations.                                                                                                                                                                                                                                                              | _ | 36 |

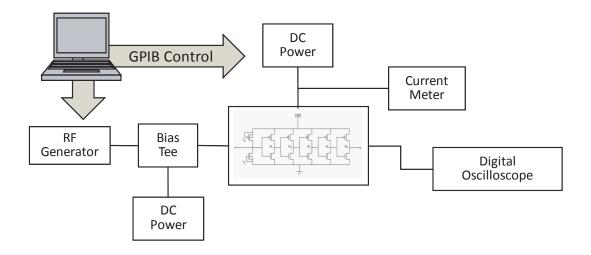

| 2.10 | Experimental setup for measuring output voltage, supply current,<br>and input rectified voltage. RF signal is directly injected at the input<br>of device-under-test (DUT), mounted on the PCB, with varying RF<br>power and frequency. The digital oscilloscope has a high sampling<br>rate to measure the real time input and output voltages, and the DC |   |    |

|      | supply current is measured with a current meter.                                                                                                                                                                                                                                                                                                            | • | 38 |

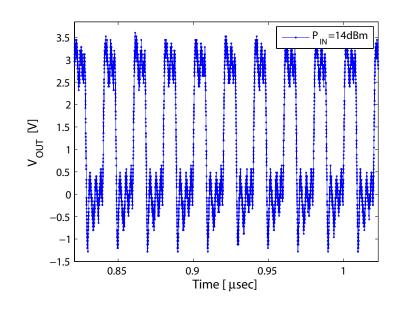

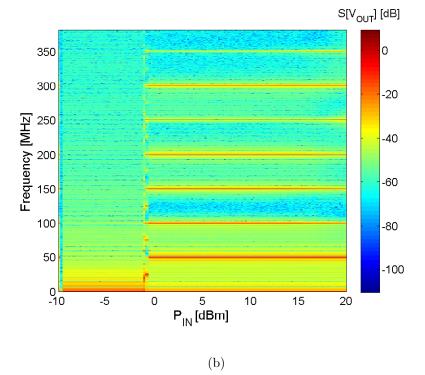

| 2.11 | of 14 dBm and frequency of 100 MHz (b) Spectrogram of output voltage as input RF power is varied. Only the superharmonics are                                                                                                                                                                                                                               |   |    |

| 2.12 | <ul><li>observed</li></ul>                                                                                                                                                                                                                                                                                                                                  | • | 41 |

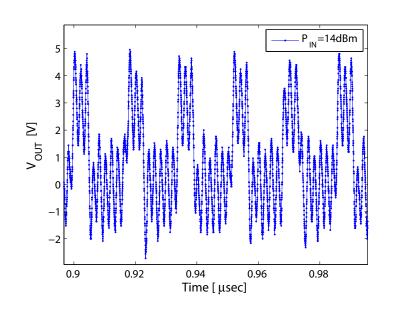

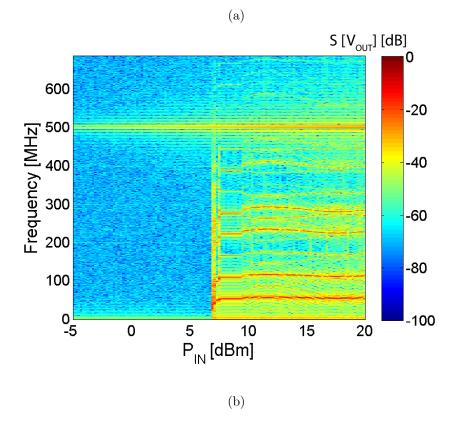

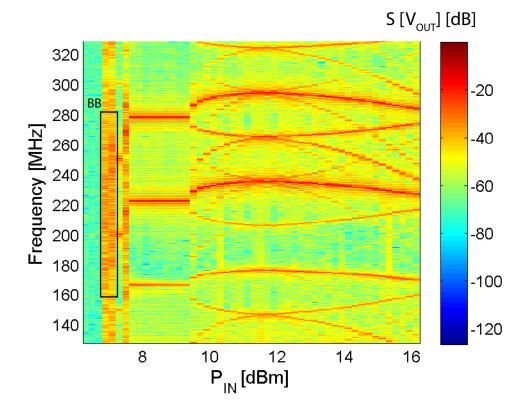

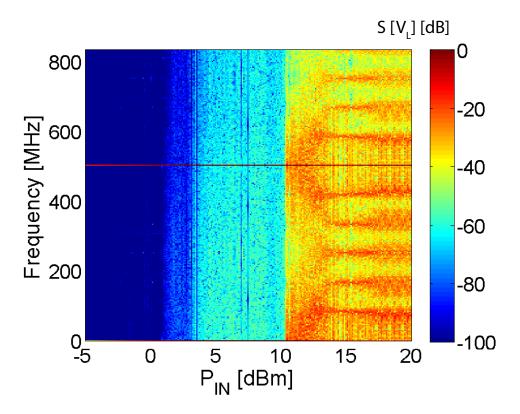

|      | of 14 dBm and frequency of 500 MHz (b) Spectrogram of output voltage as input RF power is varied.                                                                                                                                                                                                                                                           |   | 42 |

| 2.13 | Evidence of chaotic oscillation such as complex spectrum and broad-                                                                                                                                                                                                                                                                                         |   | 43 |

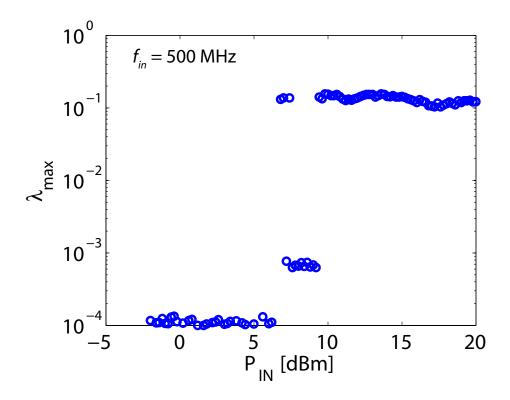

| 2.14 | band spectrum (BB)                                                                                                                                                                                                                                                                                                                                          | • | 40 |

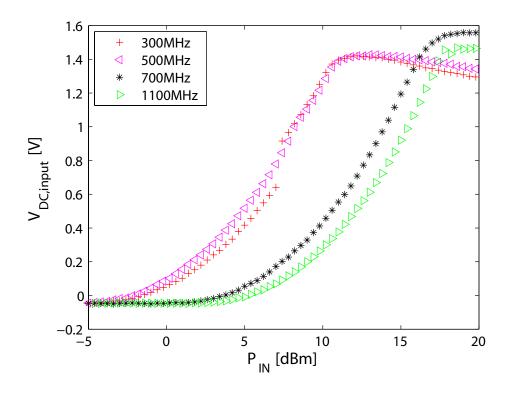

| 2.15 | input RF signal with a frequency of 500 MHz, as in Fig. 2.12(b) Experimental results of rectified DC input voltage (time-average values). Input voltage is measured across a large resistance connected at the bias tee. Input voltage is rectified at 1.4 V due to the rectification                                                                       |   | 44 |

|      | of ESD diodes, resulting in a DC offset at the circuit input                                                                                                                                                                                                                                                                                                | • | 46 |

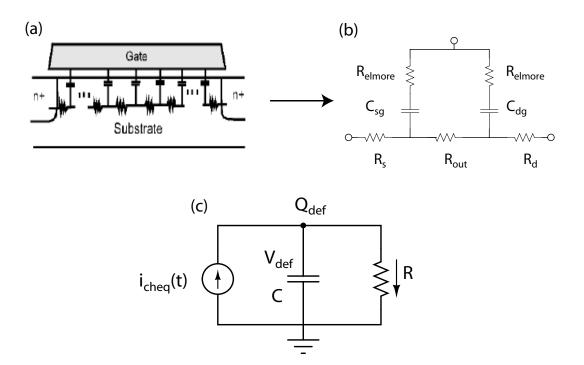

| 3.1  | (a) Diagram of charge-deficit Non-Quasi-Static model. (b) Diagram shows an equivalent network for the channel of MOSFET. (c) NQS sub-circuit for transient analysis.                                                                                                                                                                                        |   | 56 |

| 3.2  | Diagram for Berkeley Short-channel IGFET Model 4 substrate resis-<br>tance network, which models non-quasi static region. This resembles<br>a reverse recovery time of ESD junction diodes during switching                                                                                                                                                 |   | 57 |

|      | J                                                                                                                                                                                                                                                                                                                                                           |   |    |

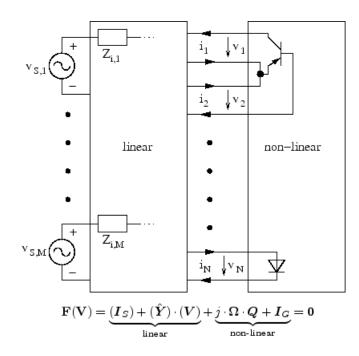

| 3.3  | Schematic diagram explaining how the harmonic balance simulation<br>operates. $F(V)$ solves the nonlinear and linear parts separately. Y<br>is the transadmittance matrix for the linear parts, and Q and $I_G$ are                                                                                                                                                                                                                                                                                                                                                                                               |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

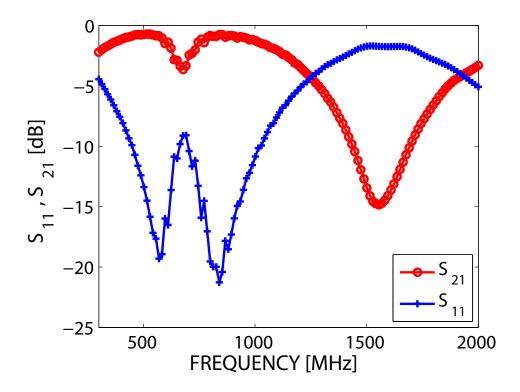

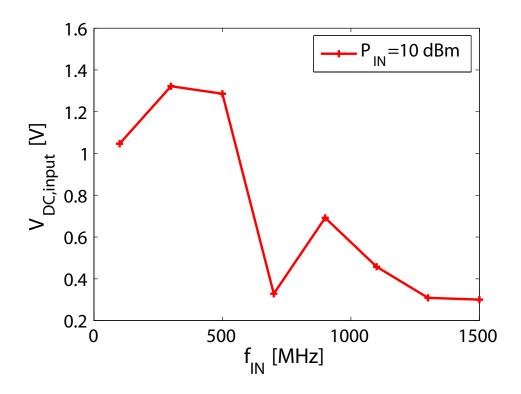

| 3.4  | Forward transmission coefficient $S_{21}$ (red) and forward reflection co-<br>efficient $S_{11}$ (blue). Notice there is a 4dB decrease in $S_{21}$ , meaning<br>less than half of input power is transmitted at the frequency around                                                                                                                                                                                                                                                                                                                                                                             | 59 |

| 3.5  | DC detected input voltage as frequency of input is changing and RF amplitude is fixed at 10 dBm. The trough around 700 MHz corresponds with the decline of forward transmission coefficient in                                                                                                                                                                                                                                                                                                                                                                                                                    | 50 |

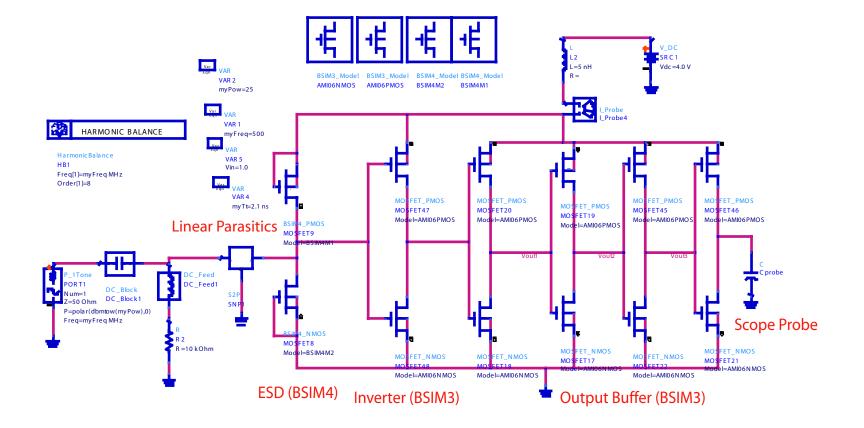

| 3.6  | A complete schematic created with ADS software. The BSIM 4 model<br>is included as well as the input parasitic model. The BSIM SPICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51 |

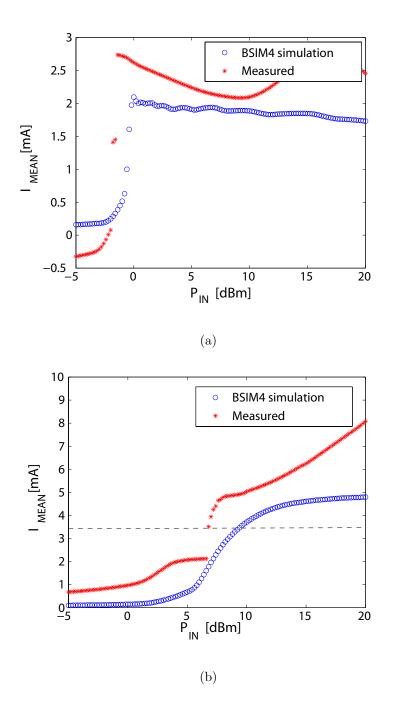

| 3.7  | parameters are extracted from test results provided from the foundry. Comparison of experimental and simulation results of time-averaged DC supply current as RF power is varied for input drive frequency of (a) 100 MHz (Linear regime) and (b) 500 MHz (NQS regime). The simulation accounts for the BSIM4 NQS feature and reflective impedance. Notice the jumps at 7 dBm appears both in experiment and simulation. Supply current never exceeds DC peak current 3.5 mA (dotted line) for (a) but supply current exceeds DC peak current as it enters the chaotic region in (b). Such comparison can also be | 52 |

| 3.8  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34 |

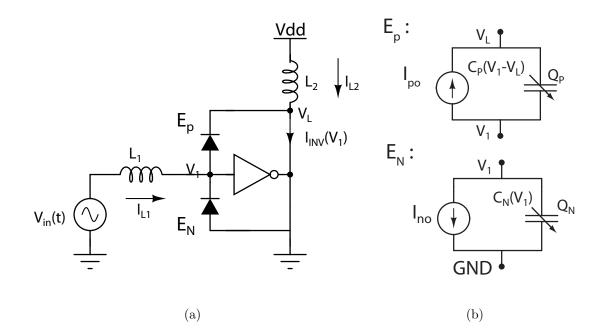

| 3.9  | Flowchart for numerical modeling. The system of ODE is solved<br>using 4th order Runge-Kutta method with the nonlinear source listed,<br>such as nonlinear diode equations, nonlinear transconductance of the                                                                                                                                                                                                                                                                                                                                                                                                     | 56 |

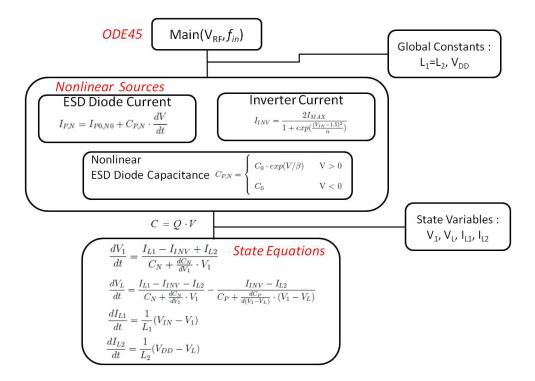

| 3.10 | inverter, and nonlinear ESD diode capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57 |

| 3.11 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71 |

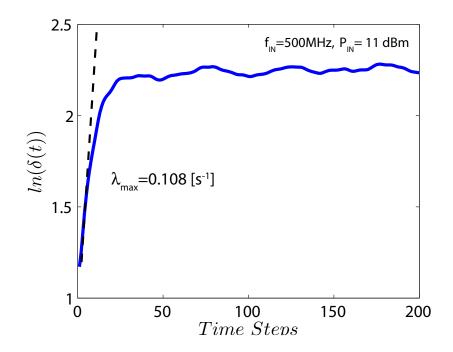

| 3.12 | Average logarithmic distance between trajectories corresponding to Fig. 3.10(b). The initial positive slope (the positive largest Lyapunov                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72 |

|      | exponent) and a long time saturation of the average distance indicate chaotic dynamics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74 |

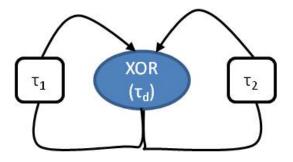

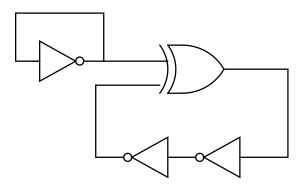

| 4.1 | Example of Boolean Chaos. Two delays $(\tau_1 \text{ and } \tau_2)$ are inputs of XOR with response time $(\tau_d)$ .                                                                                                                                                                                                                                                                                                                                                                    | 77  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

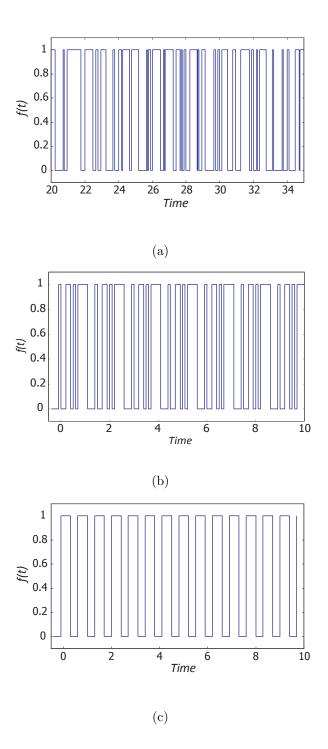

| 4.2 | Numerical results from XOR (a) when $\tau_1$ and $\tau_2$ is incommensurate,<br>and $\tau_d$ is 0 (Boolean chaos), (b) when $\tau_1$ and $\tau_2$ is incommensurate,<br>and $\tau_d$ is 0.1 (period 4), and (c) when $\tau_1$ and $\tau_2$ is commensurate, and<br>$\tau_d$ is 0 (period 1). Boolean chaotic oscillation is observed when state<br>transition occurs with no response time and two incommensurate de-<br>lays inputs. When two delays are commensurate and response time | 11  |

| 4.0 | of XOR is large, periodic transition is observed                                                                                                                                                                                                                                                                                                                                                                                                                                         | 79  |

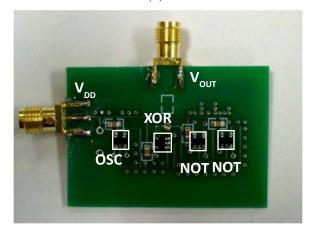

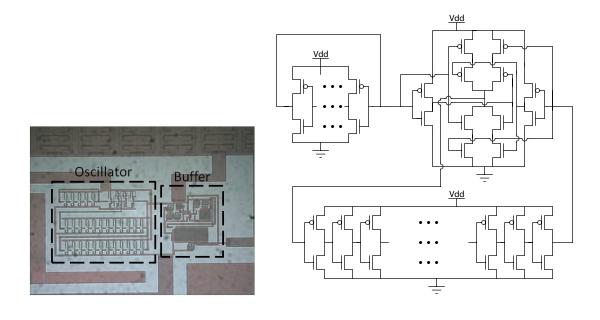

| 4.3 | (a) Diagram of circuit which generates Boolean chaotic oscillation.<br>This circuit consists of an $XOR(\tau_d)$ , a ring oscillator( $\tau_1$ ), and a delay( $\tau_2$ )<br>(b) Picture of the circuit implemented on printed circuit board (PCB),                                                                                                                                                                                                                                      |     |

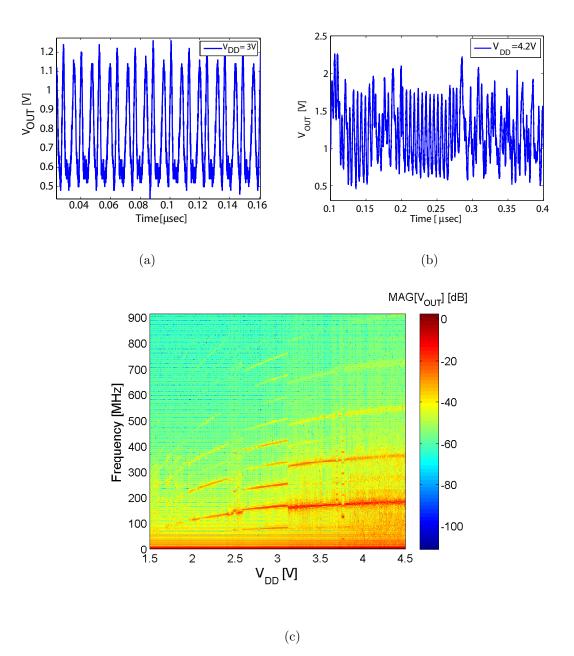

| 4.4 | consisting of commercial logic gates                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81  |

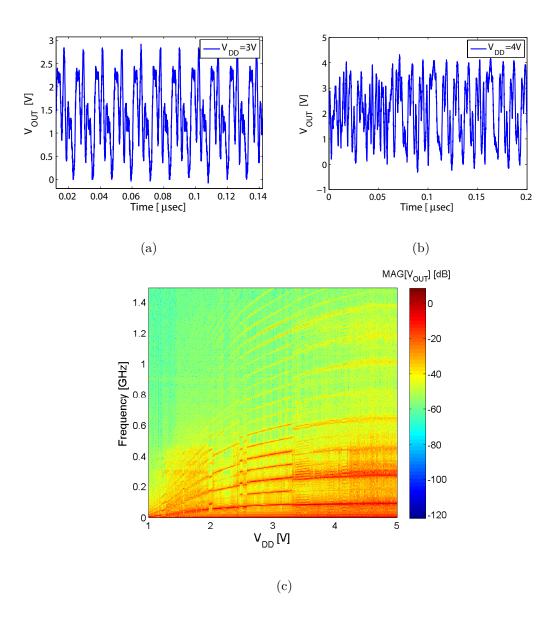

| 1.1 | at 3V. (b) Time evolution of chaotic oscillations when the circuit is biased at 4V. (c) Frequency spectrum of output voltage signal with                                                                                                                                                                                                                                                                                                                                                 |     |

|     | varying $V_{DD}$ . A broad spectrum with numerous subharmonics is observed, reaching from DC to 500 MHz.                                                                                                                                                                                                                                                                                                                                                                                 | 82  |

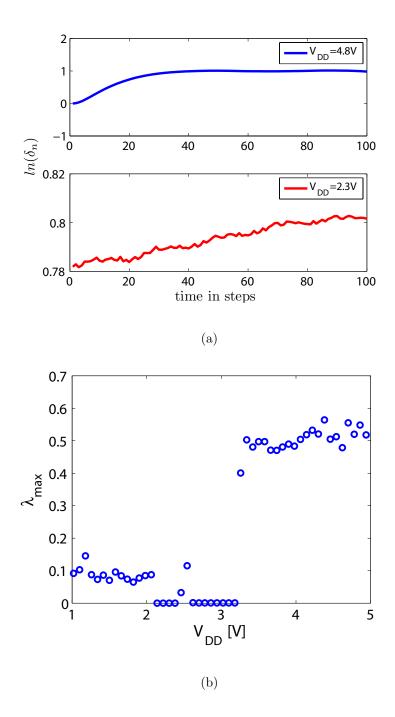

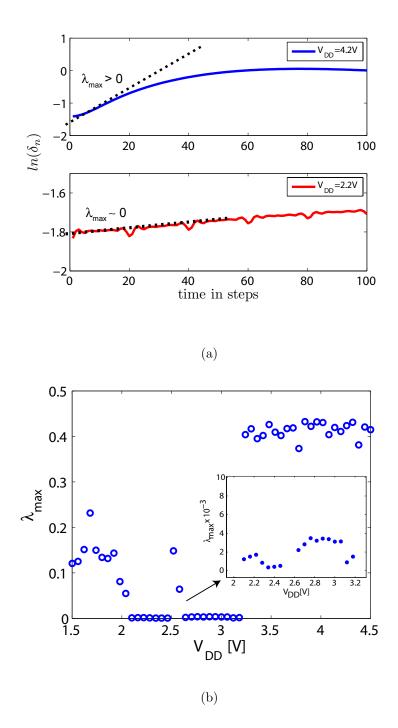

| 4.5 | (a) Average logarithmic distance between trajectories when $V_{DD}$ is 4.8V (top) and 2.3V (bottom). Top figure shows a positive slope                                                                                                                                                                                                                                                                                                                                                   |     |

|     | while the bottom has a slope close to zero. (b) Maximum Lyapunov<br>exponents $(\lambda_{max})$ with varying $V_{DD}$ as the measured data for each<br>$V_{DD}$ are calculated for $\lambda_{max}$ . After $V_{DD}$ reaches 3.3V, the circuit                                                                                                                                                                                                                                            | 0.0 |

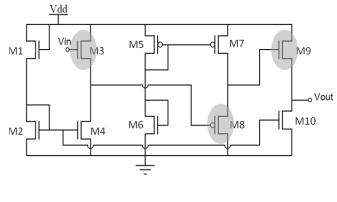

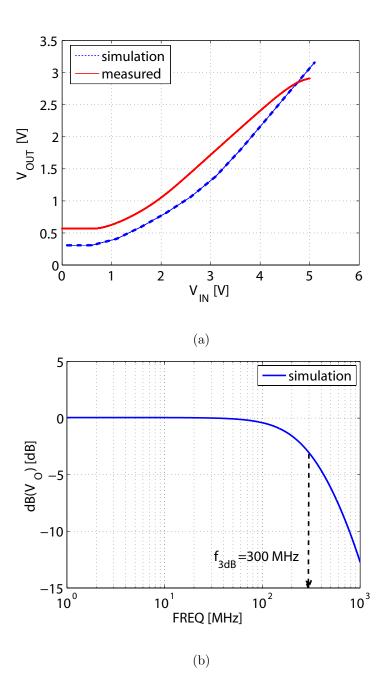

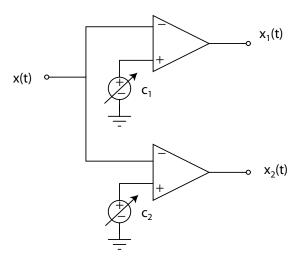

| 4.6 | enters chaotic region, resulting in positive $\lambda_{max}$                                                                                                                                                                                                                                                                                                                                                                                                                             | 83  |

| 47  | either sourced or sinked                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 85  |

| 4.7 | ulation. (b) Bode plot of simulated output voltage of buffer. This<br>buffer is capable of 3dB cut-off frequency of 300 MHz and has wide<br>input ranges for unity gain. The cutoff frequency of the buffer is de-                                                                                                                                                                                                                                                                       |     |

| 4.8 | termined from the amount of current flowing through amplifiers and<br>loading capacitance                                                                                                                                                                                                                                                                                                                                                                                                | 88  |

|     | from DC to 300 MHz, is observed.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 89  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4.9 | (a) Average logarithmic distance between trajectories when $V_{DD}$ is<br>4.2V (top) and 2.2V (bottom). Top figure shows a positive slope<br>while the bottom has a slope close to zero. (b) Maximum Lyapunov<br>exponents ( $\lambda_{max}$ ) with varying $V_{DD}$ as the measured data for each<br>$V_{DD}$ are calculated for $\lambda_{max}$ . After $V_{DD}$ reaches 3.3V, the circuit |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | enters chaotic region, resulting positive $\lambda_{max}$ . An inset in (b) indicates                                                                                                                                                                                                                                                                                                        |     |

|     | near-zero $\lambda_{max}$ for periodic oscillation.                                                                                                                                                                                                                                                                                                                                          | 91  |

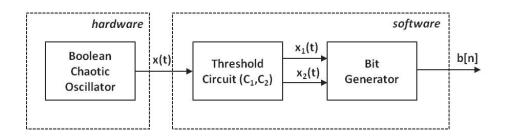

| 5.1 | Schematic diagram of random number generation using CMOS boolean                                                                                                                                                                                                                                                                                                                             | 0.0 |

|     | chaotic oscillator.                                                                                                                                                                                                                                                                                                                                                                          |     |

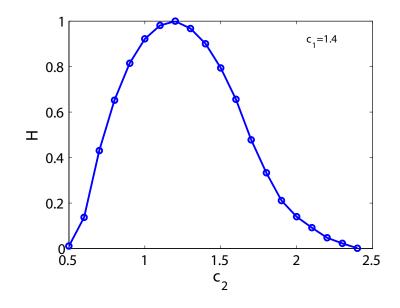

| 5.2 | Diagram of circuit for generating binary sequences                                                                                                                                                                                                                                                                                                                                           | 97  |

| 5.3 | Calculated entropy as a function of threshold $C_2$ . We evaluated the binary sequence of $C_2 = 1.2$ for statistical properties of random pro-                                                                                                                                                                                                                                              |     |

|     | cesses using the NIST statistical test.                                                                                                                                                                                                                                                                                                                                                      | 98  |

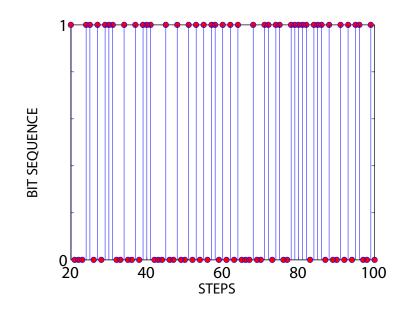

| 5.4 | Bit sequence generated after post-processing. The closed circles rep-                                                                                                                                                                                                                                                                                                                        |     |

|     | resent the actual bits                                                                                                                                                                                                                                                                                                                                                                       | 98  |

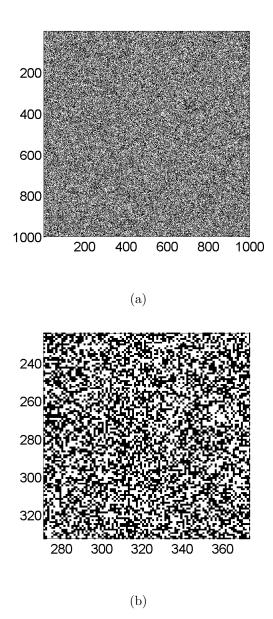

| 5.5 | (a) Grayscale plot for output bit sequence after converting to square matrix. (b) Inset of (a). Black pixels represent 1, and white pixels                                                                                                                                                                                                                                                   |     |

|     | respresent 0                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

#### Chapter 1

#### Introduction

#### 1.1 Motivation

Chaotic dynamics describe a signal that is aperiodic, and sensitive to initial conditions, yet deterministic. Chaotic oscillations have long been studied as an intriguing mathematical phenomenon, yet engineers usually see it as an undesirable effect to be avoided in designed systems. However, a new view has recently emerged, and researchers now recognize that chaos may offer substantial benefits to a number of engineering applications, including communications, remote sensing, and cryptography. This change in perspective was prompted by two important discoveries: (1) chaotic systems are easily controlled [2] and (2) multiple chaotic systems can synchronize [3]. These discoveries have shown that the unpredictable instability of chaos may be transformed into natural versatility and flexibility. Consequently, much theoretical and experimental research has advanced this new area of chaos engineering.

Many chaotic systems require chaotic circuits or chaotic oscillators as core parts. The design of chaotic oscillators has been a field of increasing interest during the past few decades. After the first thrust of chaotic circuits in the early 1980s, the development of chaotic circuits has taken interesting paths in unique directions [1]. The main design goal in chaotic circuits has been to develop new chaotic circuits, and to study the nonlinear dynamics responsible for chaos generation. The study of chaotic circuit design has been more popular ever since scientists and engineers began to find applications of these chaotic circuits in fields such as communication and cryptography [4, 5].

Most of the present chaotic circuits are developed through careful modeling of nonlinear dynamics and are purposely designed to operate in the chaotic regions. We would like to introduce a new *paradigm* of generating chaotic oscillations that utilize the chaotic oscillations present in standard CMOS circuit design. In this thesis, we study the chaotic dynamics observed in a practical integrated circuit (IC). This is, to the author's knowledge, the first work demonstrating chaotic oscillations in a generic CMOS integrated circuit.

Not only does chaotic oscillation in standard CMOS circuits provide an opportunity to develop chaotic circuits in the simplest structures, it can also motivate a better understanding of the stability of electronics when are exposed to high power microwave sources. Especially in the operation of radio frequency CMOS integrated circuits, we observe various forms of instability and other effects. As a consequence of such high power microwave signals coupling to the circuits, many forms of destructive and non-destructive effects occur and are reported [6]. Examples of destructive effects include junction and dielectric breakdown, which are merely physical damages of systems. As examples of non-destructive effects, researchers have identified some low-order nonlinear effects, usually categorized as a single bit error [7], a latch-up [8], or even a relaxation oscillation [9]. Yet, there have been no reported observations of higher-order effects like chaotic oscillation in generic CMOS circuits when a given circuit is excited by electromagnetic interference. In many different contexts, as ways to characterize nonlinear behaviors of radio frequency power amplifier design, many studies suggest high-order instability [10], or spurious oscillation [11], or parametric subharmonic oscillation [12], but none have analyzed this effect further in the context of nonlinear dynamics. The importance of understanding chaotic oscillation lies in the fact that, unlike a low-order instability, this chaotic oscillation can actually drive the system into a temporary reset or failure. This is of interest to people studying high power microwave (HPM) effects. The effect under exposure to HPM sources is the concern, and if a large RF signal can drive the system into a chaotic state, then this could bring new ways to destroy or upset the system without physically damaging the system.

Another topic in this thesis is the use of CMOS chaotic circuits in the design of random number generators, which is key in the fields of hardware cryptography. A random number generator in hardware cryptography is used mainly for the security and privacy of users. Building a successful cryptographic solution relies heavily on the outcomes of randomness in the system. Among many candidates for random sources, the chaotic oscillator has gained popularity over many non-deterministic sources like thermal noise and stray radio frequency waves. In building a random number generator to be more compatible with CMOS technology, we examine an important class of generating chaotic oscillations, that is, *Boolean Chaos*. In this way, we have successfully built a CMOS Boolean chaotic oscillator which is feasible for generating random numbers. The NIST statistical test version 2.1 is perform to check its feasibility [13].

#### 1.2 Theoretical Background

To demonstrate the presence of chaotic dynamics in electronics, at the fundamental stages, we need to study circuits in the nonlinear dynamics context. In this sense, it is important to look at previous studies regarding chaotic circuit development. For background, many terms, characterizations, and the structure of generic chaotic circuits are reviewed.

Many HPM effects and directed electromagnetic source effects have been reported. We review several examples of these effects, and categorize them as either non-destructive and destructive effects.

#### 1.2.1 Chaotic Circuits in Nonlinear Dynamics

Chaos theory describes the behavior of a dynamical system that is aperiodic, and sensitive to initial conditions, yet deterministic. Chaotic systems are encountered in a wide variety of fields including chemistry [14], biology [15], optics [16], and electronics [17]. This definition of chaos is generally an accepted one throughout a broad community, including mathematics, pure and applied physics, and engineering.

At first, study of chaotic circuits has generally been purely for academic and theoretical reasons. Chaotic circuits were built as physical tools to study the nonlinear dynamics described by a set of governing equations. Mathematicians and theoretical physicists built chaotic circuits to explain the dynamics of complex systems. Lately, research in chaotic circuits has been extended to actual applications in communication and cryptography. New types of chaotic oscillators are increasingly being introduced to meet the needs in such fields. Here, we would like to summarize the work and research trends in chaotic circuits, along with introducing the important works.

At this point, it is interesting to note an important finding in developments of chaotic circuits: chaos synchronization. Since chaotic signals are hard to control and predict, many engineers have neglected or underestimated their use in engineering systems [3]. Due to the discovery of the interesting phenomenon that chaotic signals can synchronize, chaos research has expanded to the engineering fields as well. Likewise, chaotic circuits play central roles in the physical implementation of chaotic systems. As an active research topic, new types of chaotic circuits are introduced to meet the needs of system. We will introduce a few important chaotic circuits, and will categorize numerous chaotic circuits by the method of chaotic oscillation generation.

- Chaotic circuits, from nonlinear nature of semiconductor device parameters [1] and [18].

- Chaotic circuits, from piecewise-linear negative resistance [19] and [20]

- Chaotic circuits, from hysteresis [21] and [22].

- Chaotic circuits, for high speed operation [23], [24], and [25].

At first, chaotic circuits were developed as a tool to validate nonlinear dynamics theory. Famous attractors named after Poincare, Lorenz, and Rossler have all been subjects of study in mathematical modeling of complex nature. An attractor is a set of points that is used to describe a system towards which the system evolves. Scientists have built chaotic circuits to validate their models. One of the early examples of chaotic circuits is the "Linsay circuit," or RLD circuit, made of a nonlinear diode, a resistor, and an inductor with a non-autonomous signal excitation. The first electronic circuit implementations appeared in the mid-1980s with the driven anharmonic oscillator [1]. Fig. 1.1(a) shows the diagram of this chaotic circuit. Its nonlinear element in this chaotic circuit is a nonlinear p-n junction diode whose capacitance varies as the voltage across the junction changes. As the circuit is driven by a signal generator and its magnitude changes, period doubling as well as period tripling and quintupling, and other subharmonic generations are observed, as shown in Fig. 1.1(b). Further study on these driven RLD chaotic circuits revealed important nonlinear dynamics. Ref. [26] explains the universal behavior of chaotic oscillation seen in this type of circuit including important features of chaotic dynamics such as intermittency, crises, period doubling, and coupled oscillator behavior. The junction capacitance was identified as the source of chaotic oscillation. The capacitance varies with applied voltage as well as applied signal frequency. Another interesting work relies on the chaos found in a driven diode-terminated transmission line, with the transmission line impedance mismatched with that of the source [18]. Ref. [18] discusses the relationship of reverse recovery time of the junction diode with the generated chaos.

Another class of chaotic circuits is based on a piecewise-linear resistance, usually implemented with operational transconductance amplifiers. One of the most

Figure 1.1: (a) Circuit diagram of driven anharmonic oscillator. This circuit consists of a nonlinear capacitor, a resistor, and an inductor [1]. (b) Voltage spectrums as RF amplitudes change, driving circuits from periodic oscillation to chaotic oscillation.

famous chaotic circuits is probably Chua's circuit, shown in Fig. 1.2(a) [19]. This circuit consists of linear capacitors, inductors, and a diode with negative resistance whose current and voltage relation is shown in Fig. 1.2(b). For chaotic oscillation, the DC load line has to generate two unstable equilibrium points in the transfer curve of the Chua diode. In other words, we need at least two unstable equilibrium points, one to provide stretching dynamics and the other to provide folding dynamics. Nearby trajectories of a dynamical system are repeatedly diverged exponentially and converged back together in phase space. The operating principle of

Figure 1.2: (a) Circuit diagram of Chua chaotic circuit. (b) Current-voltage transfer characteristics of Chua diode [19].

this circuit is that the DC equilibrium points are given by the intersection between  $v_R$ - $i_R$  characteristics of the nonlinear element and the load line 1/R. For the general double scroll strange attractor, the circuit has three DC equilibrium points or three intersections. One of them is at the origin and the other two are usually located at

the second and fourth quadrants. These two latter points act as the fixed points in the attractor. There are many different versions of Chua's circuit as the Chua diode, or the negative resistance function can be implemented with various kinds of forms. This work [27] is the first monolithic realization of the nonlinear element in Chua's circuit.

While Chua's circuit relies on the nonlinearity of Chua's diode, the circuit first introduced in [21] generates chaotic oscillation via hysteresis. This circuit, shown in Fig.1.3, consists of op-amps which produce a type of hysteresis. The basic idea

Figure 1.3: Circuit diagram of an RC Op-Amp chaos generator using a hysteresis [21].

is to begin with second-order ordinary differential equations whose nonlinearity is mainly from a type of bent hysteresis. The modification is made so that each cycle of the dynamical system produces the hysteresis to a different point of its loop which eventually causes chaotic oscillation [28]. In Fig. 1.3, the circuits with  $O_1$ ,  $O_2$ , and  $O_3$  form a dynamical system and  $O_3$ ,  $O_4$ ,  $O_5$ , and  $O_6$  form a bent hysteresis nonlinearity.

Another important class of chaotic oscillators aims at the generation of a high frequency chaotic signal. Due to an increasing need for high frequency chaotic oscillators, various types of chaotic oscillators have been developed. However, most of the important attempts in designing high frequency chaotic oscillators involve the adaptation of nonlinear radio frequency components, such as the phase-locked loop, the oscillator, and the power amplifier. A phase-locked loop (PLL) is a functional device, widely used to synthesize and convert the frequency, and is used as a frequency-modulated demodulator. The basic configuration of a PLL consists of a phase detector, a low-pass filter, and a voltage controlled oscillator, as shown in Fig. 1.4 [23]. Chaotic oscillation is observed when the maximum angular frequency deviation exceeds some critical value. This critical value is chosen so that the frequency difference between the free-running frequency and the input carrier frequency is slightly greater than the pull-in frequency in order to realize the outof-lock condition.

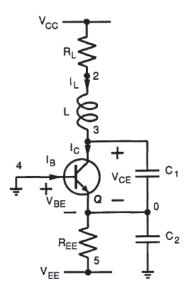

The Colpitts oscillator [24] which is shown in Fig. 1.5, consists of a single bipolar junction transistor with the feedback network from an inductor L with a series resistance  $R_L$ , and a capacitive divider from  $C_1$  and  $C_2$ . The complex dynamics

Figure 1.4: (a) Block digram of a phase-lock loop (PLL). (b) The bottom right figure shows a broad chaotic spectrum [23].

of the oscillator may be understood by having two equilibrium points, one in the forward active region and one in the cutoff region, resulting in asymmetric driving point characteristics [29].

Figure 1.5: Circuit diagram of a bipolar junction transistor Colpitts oscillator [24].

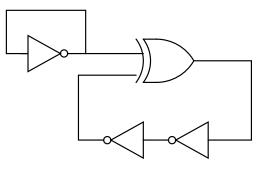

Another important class of chaotic circuits make use of so-called "Boolean chaos". Boolean chaos [25] is a phenomenon in an autonomous network which shows high dimensional chaotic oscillation, exponential sensitivity to initial conditions, and has a broad power spectrum. This unique behavior was first described by a group of mathematicians, using a Boolean delay equation [30]. The circuit node includes Boolean-like state transitions with a fast transition time, and a feedback loop with incommensurate delay inputs that lead to Boolean chaotic oscillation. Fig. 1.6 depicts an example of a Boolean chaotic circuit, which consists of digital circuit elements. The bandwidth of the chaotic oscillation depends on the propagation delay time as well as the power supply of the system.

Another research approach to chaotic circuits would be to study the necessary and sufficient mathematical conditions for chaos generation. While there is an ever-

Figure 1.6: Example of Boolean chaos circuit, which consists of one NAND gate with three NOT gates.

increasing number of chaotic circuits, the necessary and sufficient mathematical conditions for chaos generation are unknown. The purpose of this kind of work is to find the simplest mathematical function that gives rise to chaos and to find general classes of oscillators that exhibit chaos. Researchers looked for the simplest "jerk" functions which result in positive Lyapunov exponents [31][32]. A system that has received considerable attention is

$$\ddot{x} = J(\ddot{x}, \dot{x}, x) \tag{1.1}$$

"jerk function" means a function J such that the third-order ODE can be written in the form of (1.1). The computational model considers systems of the form

$$\ddot{x} = a_1 \ddot{x} + a_2 \varphi(\ddot{x}) + a_3 \dot{x} + a_4 \varphi(\dot{x}) + a_5 x + a_6 \varphi(x) + a_7$$

(1.2)

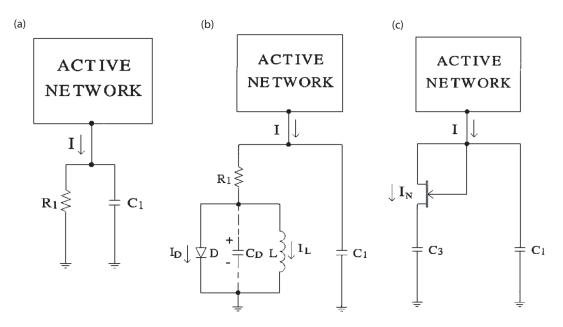

where  $\varphi(x)$  is a simple nonlinear function chosen to permit electronic implementation with diodes and operational amplifiers. The procedure for finding the jerk function is to run a 4th-order Runge-Kutta algorithm to solve the equations with randomly chosen coefficients  $a_1$ - $a_7$ , and a selected nonlinear function  $\varphi(x)$ . Next, there was an attempt to find a design methodology for building chaotic oscillators [33].This paper explains the three important classes of core oscillators that are necessary to generate chaotic oscillation. The active networks in Fig. 1.7 are usually voltage controlled current sources.

Figure 1.7: Classes of core chaotic oscillators. (a) sinusoidal oscillator with a parallel RC, (b) using diode inductor composite, and (c) with FET and capacitor composite [33].

#### 1.2.2 Examples of Electromagnetic Interference Effects

Electromagnetic emission is of concern to many circuit designers. This concern has become more important as improvement in chip technology has led to a higher density of circuits inside a single chip, and a decrease in the operation wavelength of the circuit. When high power microwave sources are coupled to a circuit, various kinds of effects can occur. Examples of external electromagnetic sources are the signals from radars and high power microwave weapons that are usually intentionally designed to bring high power RF outputs.

Microwave signals interference with electronic systems is not an entirely new concern. Although this may not be exactly fit into the scenario of HPM effects in the CMOS ICs, the following story is a good example of electromagnetic interference in our daily lives. We are reminded of the importance of EMI compliance whenever we take off or land in an airplane, and are requested to refrain from using all electronic devices. This request suggests that electromagnetic energy emitted from our laptops and personal devices might induce noise in the communication between airplanes and control towers. In any case, the importance of keeping electronic systems from interfering with others is recognized by all designers.

Previous studies have shown that various physical mechanisms result in instabilities when a circuit is excited by microwave signals. The first observation is the rectification of radio frequency (RF) signals in bipolar junction transistors and fieldeffect transistors. When a microwave signal is injected into the base of the BJT, qualitatively speaking, the AC signal is rectified to a DC value by the nonlinearity of the emitter-base junction characteristics, and may shift the quiescent point of operation. Many studies [34, 35] have reported the experimental observation as well as the mathematical proof of this effect. Low frequency rectification is often within the operating passband of the circuit, and may have unintended effects on the entire circuit. Similar behaviors are also observed in junction field-effect transistors [36]. The model in this literature, from a small signal viewpoint, demonstrates that the effect is caused by device nonlinearity, especially the nonlinear transconductance of

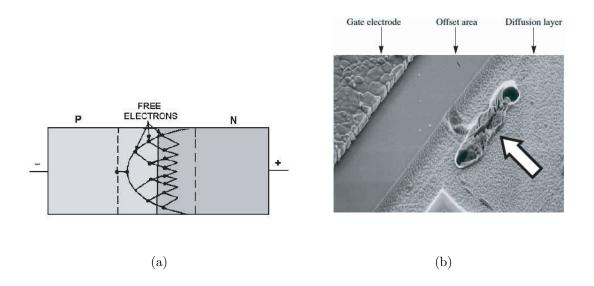

Figure 1.8: (a) Diagram of PN-junction in the Avalanche breakdown. High reverse field creates the multiplications of free electrons by impact ionizations. (b) Scanning electron microscopy image of a junction breakdown. The arrow region shows a physical PN-junction damage.

the field-effect transistors.

Effects can be grouped into two non-destructive and destructive effect, depending on the degree of damage. First, many PN-junction exist inside the CMOS structure, and due to high reverse biasing of these PN-junctions, these junctions can experience breakdowns, as shown in Fig. 1.8. In a high reverse bias state, the electrons cause impact ionization, resulting in the freeing multiple electrons. This is called the avalanche breakdown. Eventually, the high reverse fields even break the bondings of the donors or acceptors, resulting in a sudden current spike. This is called the Zener breakdown [37]. Another destructive effect is a dielectric breakdown. Most CMOS ICs have dielectrics as insulating layers, and when they are shorted due to high RF signal coupling, the circuit no longer functions. Gate oxide

Figure 1.9: Schematic diagram of CMOS inverter showing two parasitic bipolar junction transistors  $Q_1$  and  $Q_2$ . Latch-up effects are due to the BJT action.

breakdown can cause a conduction path between the metal gate and the channel. These two destructive effects are well known in the start-of-art CMOS technology, and this damage requires replacement of the parts.

Next, we give a reported example of non-destructive effects. This is a transientinduced latch-up. Latch-up can occur when the parasitic bipolar transistor action in the body is turned on, resulting in conduction through the body, rather than through the channel of the MOSFET device. Fig. 1.9 shows that parasitic BJTs are present inside a CMOS inverter. This nonlinear mechanism results in overshoot and undershoot voltage spikes at the outputs and inputs, and most latch-ups occur as a result of high power pulse electromagnetic interference and electrostatic discharging [8, 38].

There is no doubt that these examples are harmful in building reliable CMOS

electronics. However, on the other hand, these effects in standard CMOS circuits could be targets for researchers developing electromagnetic weapons (EMP) [39].

#### 1.3 Organization of the Thesis

The material presented in this thesis is organized into four chapters. The first half of the work focuses on the chaotic oscillation found in generic CMOS circuits, and the second half talks about the specific design of the CMOS Boolean chaotic oscillator.

Chapter 2 is devoted to an experimental demonstration of chaotic oscillation in a CMOS inverter design under microwave signal excitation. We present the design details of the CMOS inverter coupled with electrostatic discharging (ESD) circuits using On-Semiconductor 0.5  $\mu m$  technology. We also describe how the experiment is performed. We give some experimental observations which suggests ch aotic dynamics. We also give a qualitative analysis of the nonlinear sources.

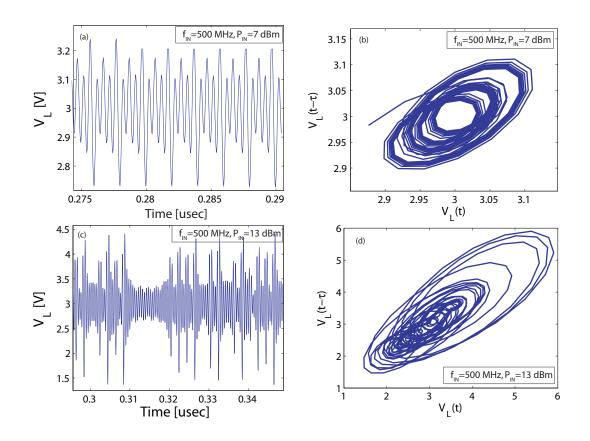

In Chapter 3, we focus on modeling the chaotic oscillation events demonstrated in Chapter 2. We present a transistor-based simulation, using BSIM 4 SPICE parameters and a lumped-element model, and also numerical modeling, built with sets of ordinary differential equations. We also compute the largest Lyapunov exponents for the outputs generated from the numerical models to verify the existence of chaotic oscillation.

In Chapter 4, we present a new class of chaotic oscillator, the Boolean chaotic oscillator. Based on the Boolean delay equation, we verify the presence of chaos in

such networks. We then test our hypothesis generated with the numerical models by building a Boolean chaotic oscillator with discrete commercial parts. Using CMOS  $0.5 \ \mu m$  technology, we build an on-chip CMOS Boolean chaotic oscillator.

Chapter 5 is devoted to a test of the applicability of the designed Boolean chaotic oscillator in cryptographic random number generation. With proper post-processing of the analog signal, we design a random number generator using our integrated circuit. Moreover, a statistical analysis of the random number generation, the NIST test suite, is performed to test the feasibility of our circuit as a random number generation source.

Chapter 6 provides a summary to the thesis and discusses future work.

#### 1.4 List of Contributions

Chaotic oscillation has long been conjectured or observed as an effect of high power microwave signals or directed electromagnetic signals; however, there has been no study or thorough proof of the phenomenon. This becomes more problematic when chaotic oscillation is found in our state-art-technology like CMOS.

One of main reasons that this issue has been overlooked is the divergent research fields involved. As stated, chaotic dynamics in circuits should be studied in the context of nonlinear dynamics; nonlinear dynamics researchers traditionally characterize chaotic oscillation or circuits via a set of governing mathematical equations. Period doubling, intermittency, and positive Lyapunov exponents are important tools in nonlinear dynamics theory for investigating the chaotic nature of the various systems. However, chaotic oscillation is not a primary concern for RF circuit designers, as long as the circuit is classified as unstable.

In this thesis, we investigate the chaotic dynamics in the CMOS integrated circuits, and validate the presence of chaotic oscillation, when the circuit is under a direct microwave injection.

In second part of the thesis, we exploit chaotic oscillation in building a random number generator. Here, we use a new paradigm of chaos generation: Boolean chaos. We are able to build CMOS on-chip Boolean chaotic oscillators. This type of chaotic oscillator is well-suited to building a cryptographic random number generator.

The contributions of this thesis can be listed in the following points:

## Investigation of chaotic oscillation in standard CMOS digital ICs as new class of high power microwave effects. (Chapter 2 and chapter 3)

- 1. Design of Test CMOS ICs: CMOS Inverter coupling with ESD protection circuits using On-Semiconductor 0.35  $\mu$ m technology.

- 2. Direct RF injection experiment on the CMOS IC. Experimental results that shows evidences of chaotic oscillation.

- 3. Characterization and analytical discussion of the nonlinearity.

- 4. Transistor-based circuit modeling based on BSIM4 and numerical modeling to verify the presence of chaotic oscillation by computing positive largest Lyapunov exponents.

# Design of Random Number Generator using CMOS Boolean Chaotic Oscillator (Chapter 4 and Chapter 5)

- 1. Numerical analysis of a new chaos generation called Boolean chaos.

- 2. Design of CMOS Boolean chaotic oscillator using On-Semiconductor 0.35  $\mu$ m technology, whose bandwidth reaches from DC to 300 MHz.

- NIST statistical tests about the random number generation using our CMOS Boolean chaotic oscillator.

## Chapter 2

# Experimental Chaotic Oscillation in CMOS Digital Circuits

# 2.1 Overview

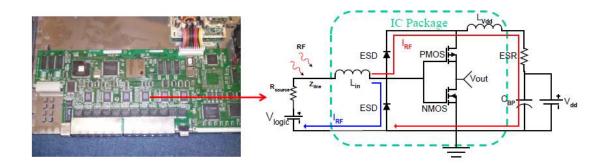

Here, we study the effect of electromagnetic sources, especially high power microwave (HPM) signals, such as those from radars and directed microwave sources, on the operation of CMOS integrated circuits. The term "effect" is used to study the behavior of the circuit, when high power electromagnetic sources are coupled into the circuit.

Previous study on the "effect" has focused on the behavior of commercial components. While CMOS has been a start-of-art technology over the last several decades, little research was done on electromagnetic source effects in CMOS ICs. As the technology has developed, the device switching rate has gotten higher and scaling of the devices becomes smaller, making the dielectric of CMOS even thinner. These devices, in turn, become highly vulnerable to HPM signals, thus causing some disruptions to the entire system.

In addition, when the circuit is operating in radio frequency range, signal wavelength is comparable to the dimension of passive components. In this regime, printed circuit board traces, packaging, bond-wire, and other passive parasitics all become important to consider. Also, due to high frequency HPM signals, the operating speed of CMOS IC nearly reaches the maximum operating speed of the design circuit, which brings more nonlinear effects to the dynamics of the circuit.

Some reported circuit effects of HPM signals can be categorized as non-destructive or destructive effects. Destructive effects are caused by large electromagnetic sources which can permanently damage a system. The damaged components have to be replaced for the system to function. Some examples of these permanent damages are junction breakdown and dielectric breakdown. Non-destructive effects generate undesirable results, causing disruption to normal behavior. This requires less electromagnetic energy and effects are temporary. For a system to function again, the system only requires reset. One example is latch-up, which is caused by turning on parasitic bipolar junction transistors inside CMOS structure. The details are explained in Chapter 1.

Another kind of effect is chaotic oscillation. As mentioned, chaos is defined by aperiodicity and sensitiveness to initial conditions, but is deterministic. Researchers have long conjectured and observed a high dimensional instability, referring to it as spurious oscillations, or unstable oscillations [11][12]. This instability is also encountered in high power amplifier stability study. Highly nonlinear power amplifiers are often exposed to these phenomenon, when they are driven under large RF signal [10]. Confirming the existence of chaotic dynamics in the circuit requires some nonlinear dynamics background.

Our approach in solving this problem is purely based on investigating the nonlinear dynamic nature of the designed circuit, because the presence of chaos can only be proven by in context of nonlinear dynamics. Therefore, the work focuses on investigating and observing evidences in experiment and numerical analysis. In Section 2.2, we give a brief overview of the test circuit and a motivation of the work with the CMOS technology.

In Section 2.3, we show the design details of CMOS digital ICs, which consist of a CMOS inverter, a cascade output buffer, and electrostatic discharging (ESD) protection circuits. The test circuit was designed using Cadence Virtuoso layout tools and was fabricated using the On-Semiconductor 0.5 um process. Basic DC and transient test results are given.

In Section 2.4, we present experimental results of the designed circuit under a direct microwave excitation. We introduce a general experimental procedure and a test-board design. We suggest some evidences of chaotic oscillation through experimental observations.

In Section 2.5, we include the device physics characterization of nonlinear sources present in the circuit. We give qualitative and quantitative analysis of these nonlinear behaviors. Using Lyapunov exponents, we quantify chaotic oscillation in the experimental results.

# 2.2 Test Circuit Overview

As stated, previous study has involved mainly commercial devices, and has used basic models to describe very simple behaviors. On top of this, it is hard to look inside the physical layouts of circuits due to proprietary restrictions. For these reasons, we design our circuit in house, starting from layouts to PCB soldering. In this manner, all of our circuit parameters are known. In addition, all the SPICE

Figure 2.1: Schematic diagram and basic elements in modern CMOS digital ICs.