## ABSTRACT

| Title of dissertation:    | REUSE DISTANCE ANALYSIS FOR<br>LARGE-SCALE CHIP MULTIPROCESSORS             |

|---------------------------|-----------------------------------------------------------------------------|

|                           | Meng-Ju Wu, Doctor of Philosophy, 2012                                      |

| Dissertation directed by: | Professor Donald Yeung<br>Department of Electrical and Computer Engineering |

Multicore Reuse Distance (RD) analysis is a powerful tool that can potentially provide a parallel program's detailed memory behavior. Concurrent Reuse Distance (CRD) and Private-stack Reuse Distance (PRD) measure RD across threadinterleaved memory reference streams, addressing shared and private caches. Sensitivity to memory interleaving makes CRD and PRD profiles architecture dependent, preventing them from analyzing different processor configurations. However such instability is minimal when all threads exhibit similar data-locality patterns. For loop-based parallel programs, interleaving threads are symmetric. CRD and PRD profiles are stable across cache size scaling, and exhibit predictable *coherent movement* across core count scaling. Hence, multicore RD analysis can provide accurate analysis for different processor configurations. Due to the prevalence of parallel loops, RD analysis will be valuable to multicore designers.

This dissertation uses RD analysis to analyze multicore cache performance for loop-based parallel programs. First, we study the impacts of core count scaling and problem size scaling on CRD and PRD profiles. Two application parameters with architectural implications are identified:  $C_{core}$  and  $C_{share}$ . Core count scaling only impacts cache performance significantly below  $C_{core}$  in shared caches, and  $C_{share}$  is the capacity at which shared caches begin to outperform private caches in terms of data locality. Then, we develop techniques, in particular employing reference groups, to predict the coherent movement of CRD and PRD profiles due to scaling, and achieve accuracy of 80%–96%. After comparing our prediction techniques against profile sampling, we find that the prediction achieves higher speedup and accuracy, especially when the design space is large. Moreover, we evaluate the accuracy of using CRD and PRD profile predictions to estimate multicore cache performance, especially MPKI. When combined with the existing problem scaling prediction, our techniques can predict shared LLC (private L2 cache) MPKI to within 12% (14%) of simulation across 1,728 (1,440) configurations using only 36 measured CRD (PRD) profiles. Lastly, we propose a new framework based on RD analysis to optimize multicore cache hierarchies. Our study not only reveals several new insights, but it also demonstrates that RD analysis can help computer architects improve multicore designs.

## Reuse Distance Analysis for Large-Scale Chip Multiprocessors

by

Meng-Ju Wu

## Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2012

Advisory Committee: Professor Donald Yeung, Chair/Advisor Professor Bruce Jacob Professor Manoj Franklin Professor Rajeev Barua Professor Chau-Wen Tseng © Copyright by Meng-Ju Wu 2012

#### Acknowledgments

I owe my gratitude to all the people who have made this thesis possible. First I would like to thank my advisor, Professor Donald Yeung for his unwavering support as I worked at this challenging and fruitful topic. The thinking process which I learned from him is the best treasure of the entire research.

I would also like to thank Professor Bruce Jacob, Professor Manoj Franklin, Professor Rajeev Barua, and Professor Chau-Wen Tseng for agreeing to serve on my thesis committee and for sparing their invaluable time reviewing this manuscript.

My colleagues at the University of Maryland have enriched my graduate life in many ways and deserve a special mention. Hameed, Xuanhua, Wanli, Xu, Inseok, Minshu, and Cheng-Han gave me wonderful help and discussion. I would also like to thank my friends for enriching my graduate life in many ways.

I owe my deepest thanks to my family, my mother and father, my sister and brother-in-law, and my little nieces. Although they are in Taiwan and far away from me, their love, encouragement, and guidance have supported me throughout my whole life. Words cannot express the gratitude I owe them. And finally, to my dearest wife, Yung-Ching, whom I love very much. More than anything, she has continuously motivated me and given me confidence through this journey. Without her love and support, I could not complete my dissertation, and life will be tasteless.

# Table of Contents

| Lis | st of '                    | Tables                                                                                        | v                                            |

|-----|----------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------|

| Lis | st of l                    | Figures                                                                                       | vi                                           |

| 1   | Intro<br>1.1<br>1.2<br>1.3 | Contributions                                                                                 | 1<br>5<br>10                                 |

| 2   | Back<br>2.1<br>2.2         | Multicore Reuse Distance                                                                      | 12<br>12<br>13<br>15<br>17<br>18<br>19<br>20 |

| 3   | Mul <sup>-</sup><br>3.1    | Quantifying Thread Interactions                                                               | 22<br>23<br>23<br>25                         |

|     | 3.2                        | Thread Interactions Analysis at a Fixed Core Count and Problem Size3.2.1Private-data Profiles |                                              |

|     | 3.3                        | 3.3.1 Private-data Profiles                                                                   | 33<br>35<br>38                               |

|     | 3.4<br>3.5                 | Architectural Implications3.5.1Core Count Scaling3.5.2Problem Size Scaling                    | 42<br>46<br>46<br>54<br>55                   |

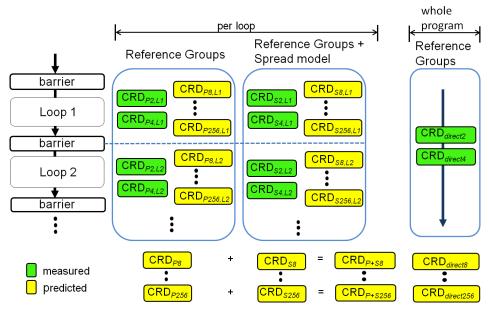

| 4   | Mul <sup>*</sup><br>4.1    | Prediction Techniques                                                                         | 56<br>56<br>57<br>59                         |

|     | 4.2                        | Prediction Methodology                                                                        | 60<br>61                                     |

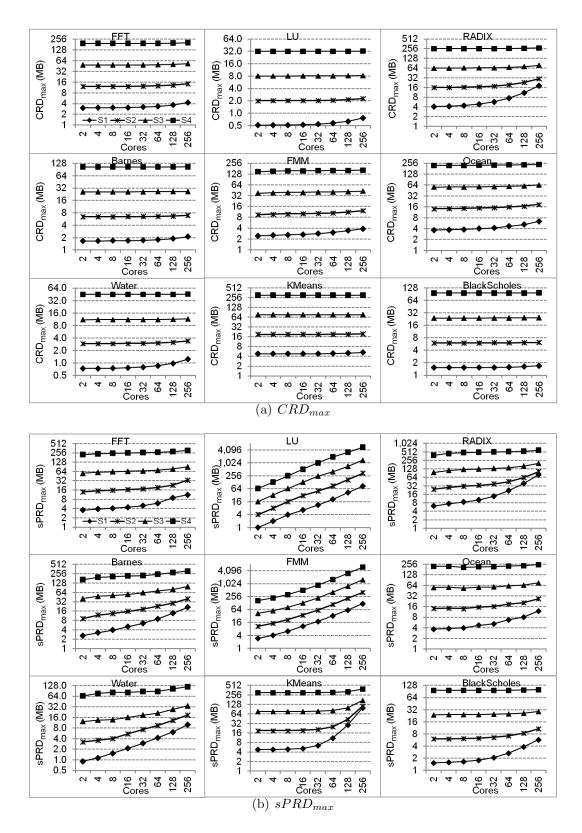

|     | 4.3                        | Prediction Accuracy Results for Core Count Scaling                                            | 63<br>64<br>65                               |

|         | 4.3.2    | PRD Profiles                                                | . 70  |

|---------|----------|-------------------------------------------------------------|-------|

| 4.4     | Predic   | ction Accuracy Results for Problem Size Scaling             | . 75  |

|         | 4.4.1    | CRD Profiles                                                |       |

|         | 4.4.2    | PRD Profiles                                                | . 80  |

| 4.5     | Predic   | ction Accuracy Results for Core-Problem Scaling             | . 84  |

|         | 4.5.1    | CRD Profiles                                                |       |

|         | 4.5.2    | PRD Profiles                                                |       |

| 5 Mul   | ticore ( | Cache Performance Prediction                                | 90    |

| 5.1     | Archit   | tecture Assumptions                                         | . 90  |

| 5.2     | Profile  | e Stability                                                 | . 93  |

|         | 5.2.1    | CRD Profiles                                                | . 94  |

|         | 5.2.2    | PRD Profiles                                                |       |

| 5.3     | MPK      | I Prediction Accuracy                                       | . 99  |

|         | 5.3.1    | Prediction Approach                                         |       |

|         | 5.3.2    | Shared LLC MPKI Prediction Accuracy                         | . 101 |

|         | 5.3.3    | Private L2 Cache MPKI Prediction Accuracy                   |       |

|         | 5.3.4    | Sensitivity to Cache Associativity                          | . 109 |

| 6 Opt   | imizing  | g Multicore Cache Hierarchies Using Reuse Distance Analysis | 113   |

| 6.1     |          | mance Models                                                |       |

| 6.2     |          | rmance Analysis                                             |       |

| 0       | 6.2.1    | Private vs. Shared LLCs                                     |       |

|         | 6.2.2    | Scaling Private-vs-Shared LLCs                              |       |

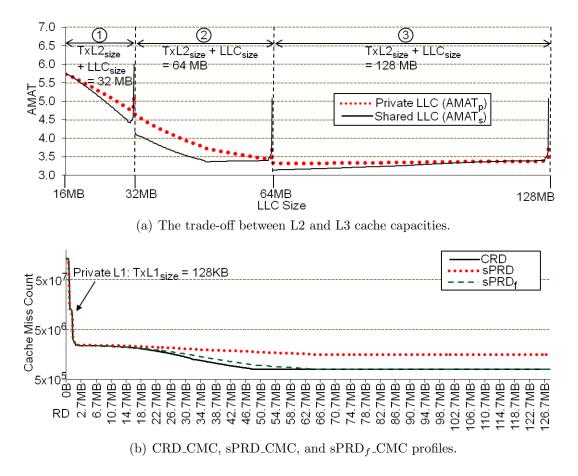

|         | 6.2.3    | Trade-off Between L2 and LLC Capacities                     |       |

|         |          |                                                             |       |

|         |          | versus Sampling                                             | 138   |

| 7.1     |          | core Reuse Distance Sampling                                |       |

| 7.2     |          | ling Accuracy and Performance                               |       |

| 7.3     | Comp     | pare with Prediction                                        | . 148 |

| 8 Rela  | ated Wo  | ork                                                         | 151   |

| 8.1     | Reuse    | e Distance Analysis                                         | . 151 |

| 8.2     | Design   | n Space Exploration                                         | . 156 |

| 9 Con   | clusion  | and Future Work                                             | 161   |

| 9.1     | Summ     | nary                                                        | . 161 |

| 9.2     | Futur    | e Directions                                                | . 164 |

| Bibliog | raphy    |                                                             | 167   |

|         |          |                                                             |       |

## List of Tables

| 2.1 | Parallel benchmarks used in our study                                                           | 20  |

|-----|-------------------------------------------------------------------------------------------------|-----|

| 3.1 | $C_{core}, C_{share}, CRD_{max}, sPRD_{max}, \Delta M_a$ , and $\Delta M_m$ for our benchmarks. | 52  |

|     | Simulator parameters used in the shared cache performance experi-<br>ments                      |     |

| 7.1 | Accuracy and speedup comparison between the sampling technique and the prediction technique.    | 149 |

# List of Figures

| $2.1 \\ 2.2$ | Multicore cache hierarchy                                                                                                                                                      | 13              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|              | lap, and intercept among inter-thread memory references in the shared cache.                                                                                                   | 14              |

| 2.3          | Two memory reference streams, illustrating replication, invalidation, and hole in the private caches.                                                                          | 16              |

| 2.4          | Thread interleaving mechanism.                                                                                                                                                 | 19              |

| 2.5          | Multi-dimensional architecture-application design space (AADS)                                                                                                                 | 21              |

| 3.1          | Acquiring $\operatorname{CRD}_P$ , $\operatorname{CRD}_S$ , $\operatorname{CRD}_{PC}$ , and $\operatorname{CRD}_{SC}$ profiles                                                 | 24              |

| $3.2 \\ 3.3$ | Acquiring $PRD_P$ , $PRD_S$ , $PRD_{PR}$ , and $PRD_{SR}$ profiles Barnes' locality profiles for the most important parallel region running on 16 cores at the S2 problem size | 26<br>28        |

| 3.4          | FFT's locality profiles for the most important parallel region running<br>on 16 cores at the S2 problem size.                                                                  | 20<br>29        |

| 3.5          | Quantifying individual thread interaction effects.                                                                                                                             | $\frac{-6}{32}$ |

| 3.6          | A simple example showing how CRD and PRD shift with core count scaling. Each cache block contains 4 elements.                                                                  | 34              |

| 3.7          | Barnes' private-data locality profiles running on 4 cores and 16 cores at the S2 problem size.                                                                                 | 36              |

| 3.8          | FFT's private-data locality profiles running on 4 cores and 16 cores                                                                                                           |                 |

| 2.0          | at the S2 problem size.                                                                                                                                                        | 37              |

| 3.9          | Barnes' shared-data locality profiles running on 4 cores and 16 cores at the S2 problem size.                                                                                  | 40              |

| 3.10         | FFT's shared-data locality profiles running on 4 cores and 16 cores at the S2 problem size.                                                                                    | 41              |

| 3.11         | A simple example showing how CRD and PRD shift with problem size scaling. Each cache block contains 4 elements.                                                                | 43              |

| 3.12         | FFT's private-data locality profiles running on 16 cores at the S1 and                                                                                                         |                 |

| 3.13         | S2 problem sizes                                                                                                                                                               | 44              |

| 3.14         | S2 problem sizes                                                                                                                                                               | 45              |

| 0.15         | size                                                                                                                                                                           | 47              |

|              | $C_{core}$ and $C_{share}$ across core counts and problem sizes                                                                                                                |                 |

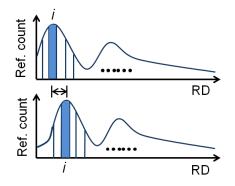

| 4.1          | Detecting alignment and shifting using reference groups                                                                                                                        | 57              |

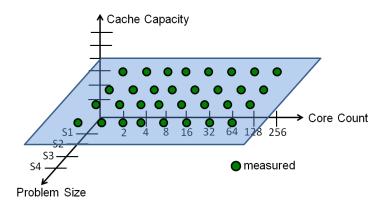

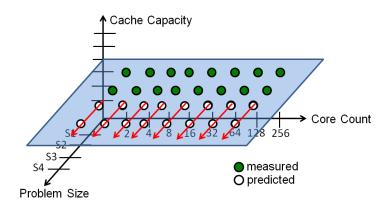

| 4.2          | Design space across 8 core counts and 4 problem sizes                                                                                                                          | 61              |

| 4.3          | Acquiring and predicting profiles                                                                                                                                              |                 |

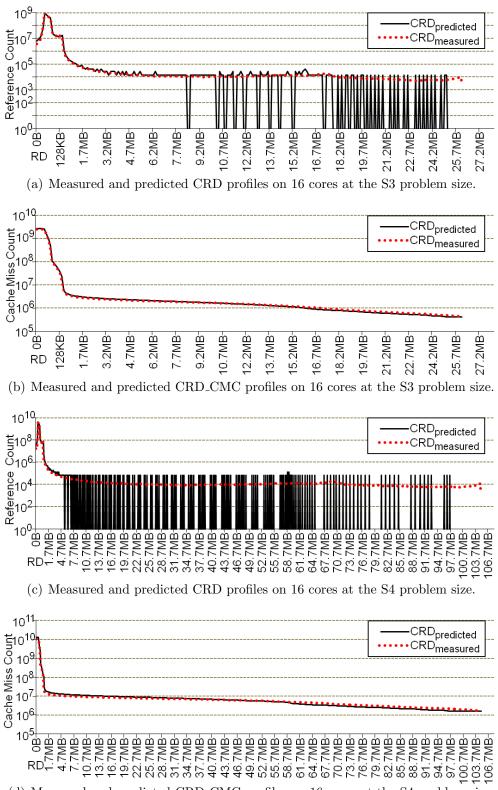

| $4.4 \\ 4.5$ | Profile prediction for core count scaling. $\dots \dots \dots \dots \dots \dots$<br>Examples for measured and predicted $CRD_{direct}$ profiles with core                      | 65              |

| ч.Ј          | count scaling                                                                                                                                                                  | 66              |

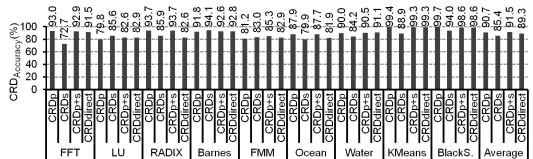

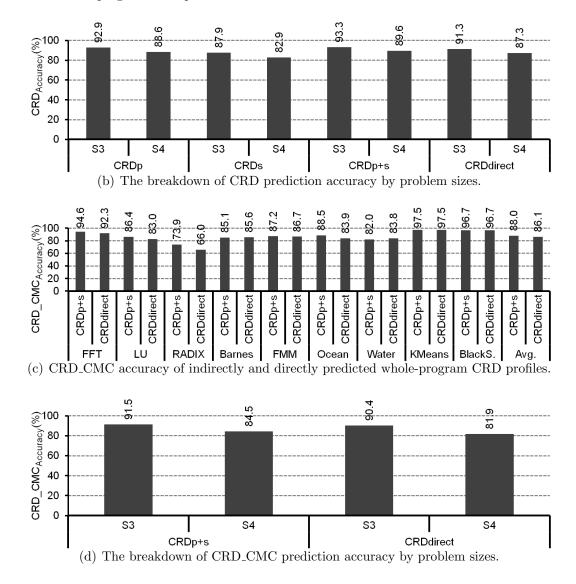

| 4.6   | CRD profile prediction accuracy for core count scaling.                                                     |   | 68         |

|-------|-------------------------------------------------------------------------------------------------------------|---|------------|

| 4.7   | Examples for measured and predicted $PRD_{direct}$ profiles with core                                       |   | <b>P</b> 1 |

| 1.0   | count scaling.                                                                                              |   | 71         |

| 4.8   | PRD profile prediction accuracy for core count scaling                                                      |   | 73         |

| 4.9   | Profile prediction for problem size scaling.                                                                | • | 75         |

| 4.10  | Examples for measured and predicted $CRD_{direct}$ profiles with problem                                    |   |            |

|       | size scaling.                                                                                               |   | 77         |

|       | CRD profile prediction accuracy for problem size scaling                                                    | • | 78         |

| 4.12  | Examples for measured and predicted $PRD_{direct}$ profiles with problem                                    |   |            |

|       | size scaling.                                                                                               |   | 81         |

|       | PRD profile prediction accuracy for problem size scaling                                                    |   | 82         |

|       | Profile prediction for core-problem scaling.                                                                | • | 84         |

| 4.15  | CRD profile prediction accuracy for scaling core count and problem                                          |   |            |

|       | size together.                                                                                              | • | 85         |

| 4.16  | PRD profile prediction accuracy for scaling core count and problem                                          |   |            |

|       | size together.                                                                                              | • | 88         |

| 5.1   | Tiled CMP.                                                                                                  |   | 91         |

| 5.2   | CRD profiles from the FFT benchmark running on 64 cores at the                                              | • | 01         |

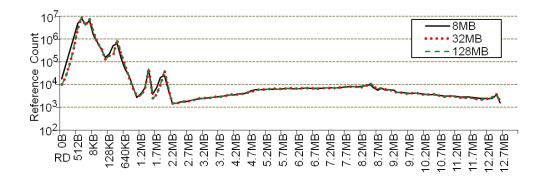

| 0.2   | S2 problem size across 8M, 32M, and 128M LLC capacity                                                       |   | 95         |

| 5.3   | Stability measurement of CRD profiles and CRD_CMC profiles                                                  |   | 96         |

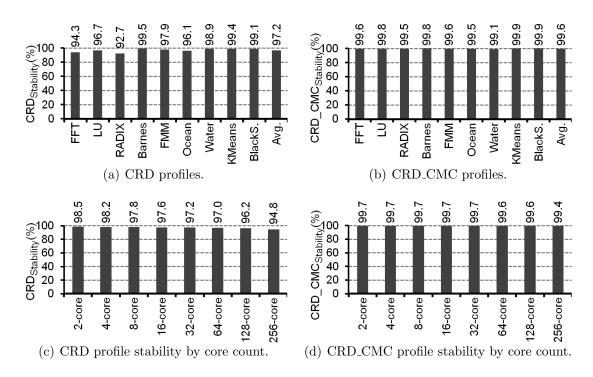

| 5.4   | PRD profiles from the FFT benchmark running on 64 cores at the S2                                           | · | 50         |

| 0.1   | problem size across 32K, 64K, and 128K per-core L2 capacity                                                 |   | 97         |

| 5.5   | Stability measurement of PRD profiles and PRD_CMC profiles                                                  |   | 98         |

| 5.6   | Architecture-application design space.                                                                      |   | 99         |

| 5.7   | Percent shared LLC MPKI prediction error with 0.05 offset.                                                  |   |            |

| 5.8   | MPKI prediction error for S4 and 4–16MB shared LLCs.                                                        |   | 102<br>104 |

| 5.9   | Prediction error for S4 and 4–16MB shared LLCs by core count.                                               |   |            |

| 5.10  | FFT's predicted LLC MPKI curves for No-Pred, C-Pred, and CP-                                                | · | 104        |

| 0.10  | Pred at the S4 problem size.                                                                                |   | 105        |

| 5 11  | MPKI difference for shared LLC MPKI prediction.                                                             |   |            |

|       | Percent private L2 MPKI prediction error with 1.0 offset.                                                   |   |            |

|       | Prediction error by core count.                                                                             |   |            |

|       | FFT's predicted L2 MPKI curves for No-Pred, C-Pred, and CP-Pred                                             | • | 107        |

| 0.14  | at the S4 problem size.                                                                                     |   | 108        |

| 5 1 5 | MPKI difference for private L2 MPKI prediction.                                                             |   |            |

|       | Shared LLC MPKI difference between 32-way and 16-way set asso-                                              | • | 109        |

| 5.10  | ciative LLCs by core count and cache capacity.                                                              |   | 110        |

| 517   |                                                                                                             | · | 110        |

| 0.17  | MPKI prediction error for S2 and 4–128MB 16-way/32-way set asso-<br>ciptive LLCa                            |   | 111        |

|       | ciative LLCs                                                                                                | · | 111        |

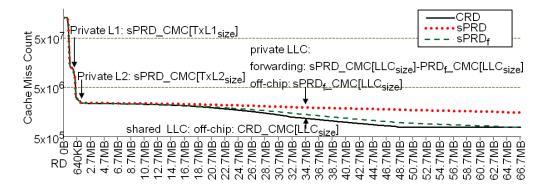

| 6.1   | CRD_CMC, sPRD_CMC, and sPRD_ $f$ -CMC profiles for FFT running                                              |   |            |

|       | on 16 cores at the S3 problem size.                                                                         |   | 114        |

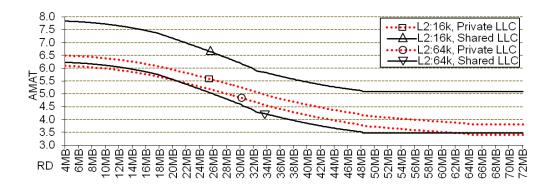

| 6.2   | FFT's AMAT <sub><math>p</math></sub> and AMAT <sub><math>s</math></sub> for different L2 and LLC capacities |   |            |

|       | r                                                                                                           |   |            |

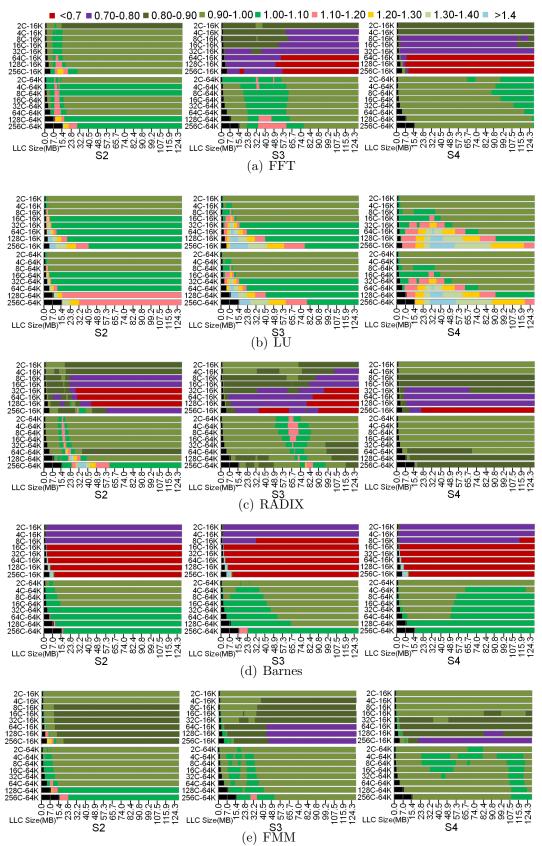

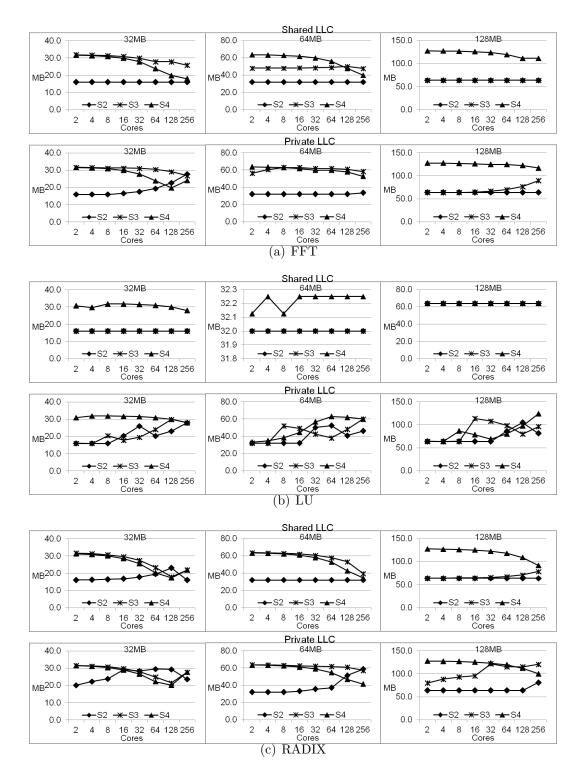

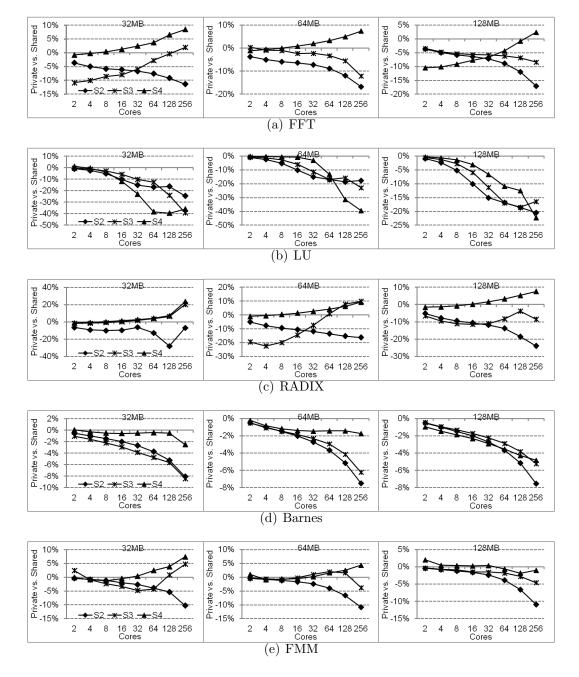

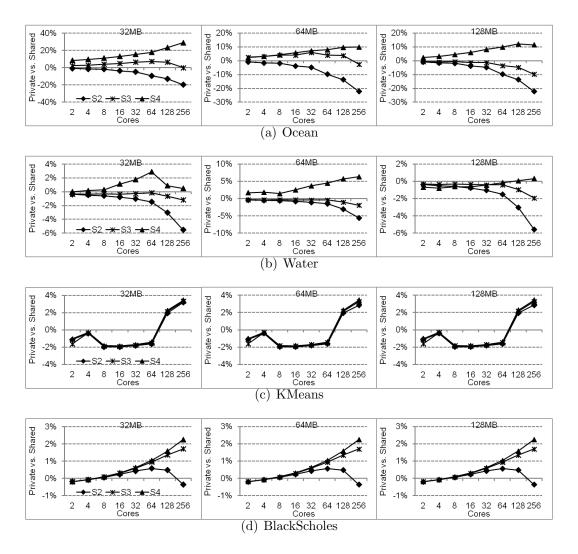

| 6.3        | Private vs. shared LLC performance across L2 capacity, LLC capac-                                                                                           |     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | ity, core count, and problem size for FFT, LU, RADIX, Barnes, and                                                                                           |     |

|            | FMM                                                                                                                                                         | 120 |

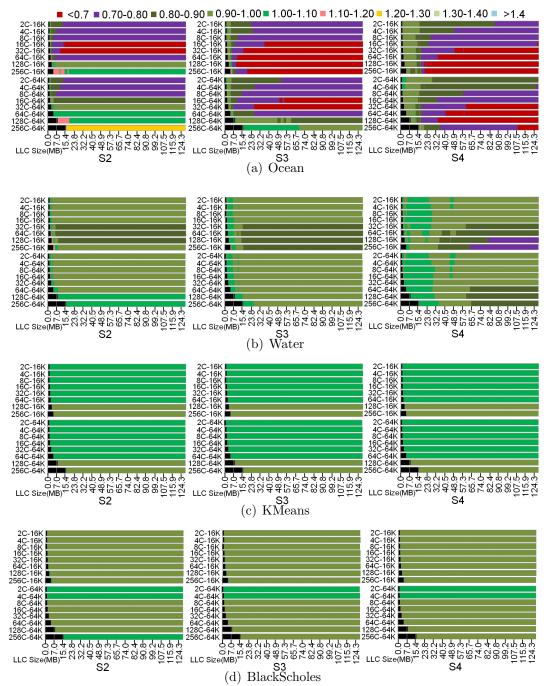

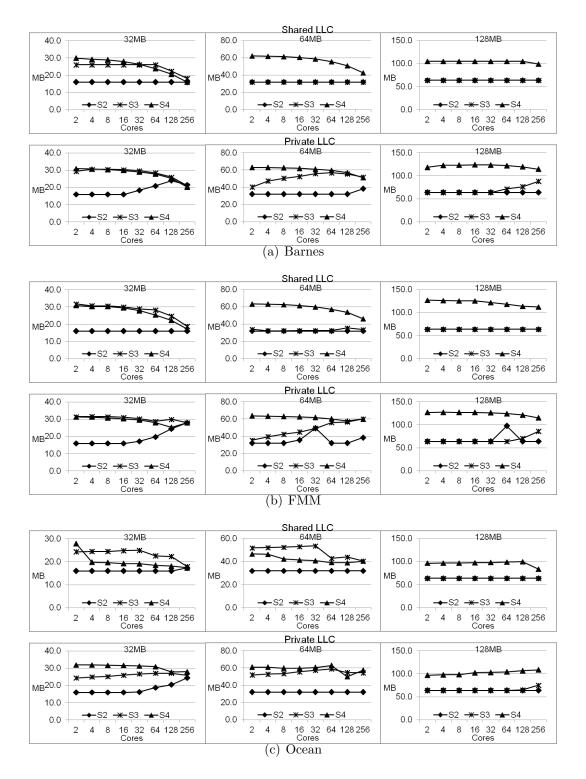

| 6.4        | Private vs. shared LLC performance across L2 capacity, LLC capac-                                                                                           |     |

|            | ity, core count, and problem size for Ocean, Water, KMeans, and                                                                                             |     |

|            | BlackScholes.                                                                                                                                               | 121 |

| 6.5        | The trade-off between $L2_{size}$ and $LLC_{size}$ for FFT running on 16 cores                                                                              |     |

|            | at the S3 problem size.                                                                                                                                     | 126 |

| 6.6        | Optimal $LLC_{size}$ at different problem sizes (S2-S4), total cache sizes                                                                                  |     |

|            | (32M-128M), and the number of cores for FFT, LU, and RADIX 1                                                                                                | 128 |

| 6.7        | Optimal $LLC_{size}$ at different problem sizes (S2-S4), total cache sizes                                                                                  |     |

|            | (32M-128M), and the number of cores for Barnes, FMM, and Ocean.                                                                                             | 129 |

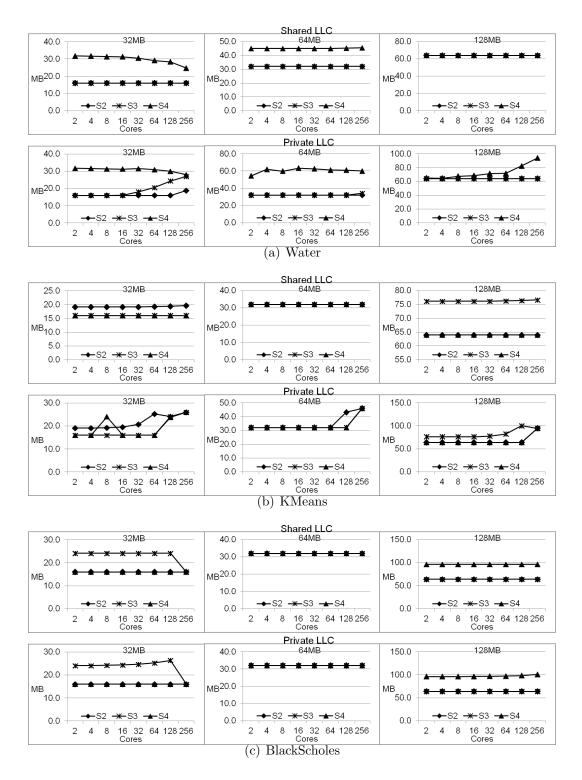

| 6.8        | Optimal $LLC_{size}$ at different problem sizes (S2-S4), total cache sizes                                                                                  |     |

|            | (32M-128M), and the number of cores for Water, KMeans, and BlackSc-                                                                                         |     |

|            | holes.                                                                                                                                                      | 130 |

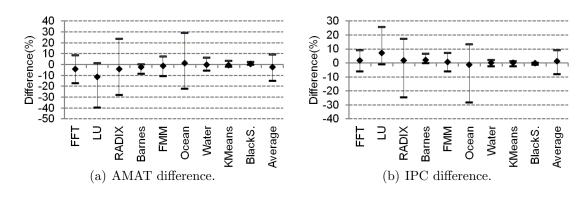

| 6.9        | AMAT difference between the highest and the lowest AMAT                                                                                                     | 133 |

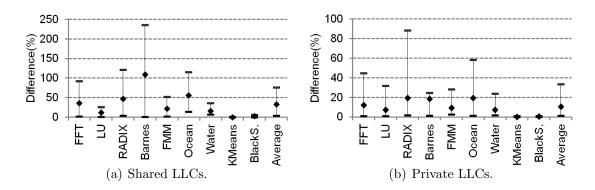

| 6.10       | AMAT difference between private and shared LLCs at $LLC_{size.opt}$ for                                                                                     |     |

|            | FFT, LU, RADIX, Barnes, and FMM.                                                                                                                            | 136 |

| 6.11       | AMAT difference between private and shared LLCs at $LLC_{size,opt}$ for                                                                                     |     |

|            | Ocean, Water, KMeans, and BlackScholes.                                                                                                                     | 137 |

| 6.12       | AMAT and IPC difference between private and shared LLCs at the                                                                                              |     |

|            |                                                                                                                                                             | 137 |

| <b>_</b> . |                                                                                                                                                             |     |

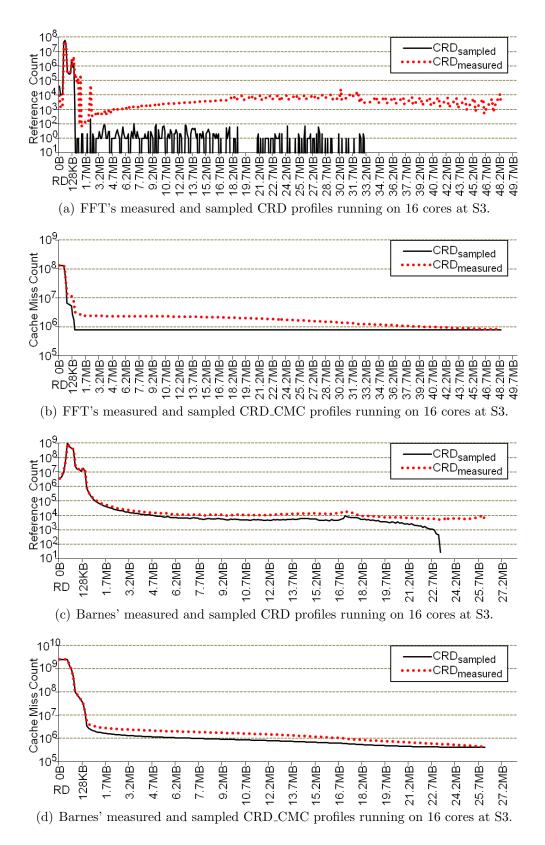

| 7.1        | Measured and sampled $CRD_{direct}$ profiles with $R_{sampling} = 0.1$ and                                                                                  |     |

|            | prairing                                                                                                                                                    | 142 |

| 7.2        | Measured and sampled $PRD_{direct}$ profiles with $R_{sampling} = 0.1$ and                                                                                  |     |

|            | $\mathbf{R}_{pruning} = 0.99. \qquad \dots \qquad $ | 143 |

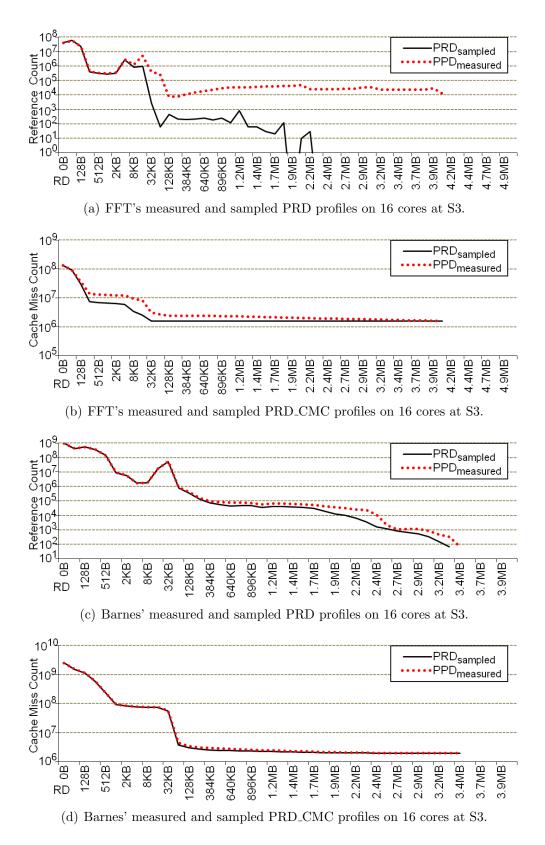

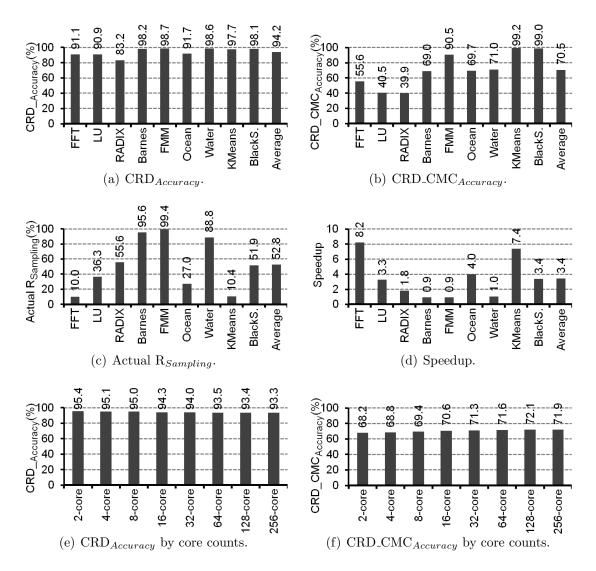

| 7.3        | Accuracy and performance of the sampling technique with $R_{Sampling} =$                                                                                    |     |

|            | 0.1 and $R_{Pruning} = 0.99$ for CRD profiles                                                                                                               | 144 |

| 7.4        | Accuracy of the sampling technique with $R_{Sampling} = 0.1$ and $R_{Pruning} =$                                                                            |     |

|            | 1                                                                                                                                                           | 146 |

| 7.5        | Accuracy and performance of the sampling technique with $R_{Sampling} =$                                                                                    |     |

|            | 0.01 and $R_{Pruning} = 0.90$ for CRD and PRD profiles                                                                                                      | 147 |

## Chapter 1

### Introduction

## 1.1 Motivation

In recent years, chip multiprocessors (CMPs) dominate design trends as chip manufacturers strive to achieve greater performance and power efficiency. CMPs with one hundred cores are already in the market, and CMPs with more than one hundred cores and more than one hundred MBs of on-chip cache will be available in the near future. On multicore processors, parallel programs can use multiple cores in parallel to solve problems more quickly. One key factor determining a multicore processor's performance and power consumption is how effectively programs can utilize the on-chip cache hierarchy.

Memory performance depends on the physical characteristics of the cache system and the parallel application's intra-thread locality and inter-thread interactions in the cache hierarchy. For example, data sharing may reduce the aggregate working set size in shared caches, decreasing the cache capacity pressure. However, shared caches have longer average access latency. In contrast, data sharing may cause replication and communication in private caches, reducing the effective cache capacity and inducing coherence misses. However, private caches keep data locally and have shorter average access latency.

To understand these complex effects, simulation is the de facto method for

studying multicore cache hierarchies [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11]. These studies simulate processors with varying *core count* and *cache capacity* to quantify how different designs impact memory performance. However, the number of configurations in terms of core count, cache hierarchy, and problem size is very large. Worse yet, detailed simulations will become more complex and time consuming as processors and problem sizes scale to the large-scale chip multiprocessor (LCMP) level. Hence, using detailed simulations to study this large design space becomes difficult due to the multi-dimensional nature of the design space.

To study future CMPs, computer architects need new tools to gain deeper insights into multicore memory performance. Reuse Distance (RD) analysis [12] is a good potential candidate to tackle this multi-dimensional design space problem. Recently, researchers have developed multicore RD analysis to analyze multicore cache performance for shared caches and private caches. To address interference and data sharing effects between threads in shared caches, *Concurrent Reuse Distance* (CRD) [13, 14, 15, 16, 17] uses a global stack to measure RD across thread-interleaved memory reference streams. On the other hand, to address data replication and communication in private caches, *Private-stack Reuse Distance* (PRD) [15, 16, 17] uses per-thread coherent stacks to measure RD separately for individual threads. For multicore processors, we can use CRD and PRD profiles together to evaluate an application's memory performance for different cache hierarchies quickly. But most importantly, it provides rich insights into how an application's inter-thread interactions impact its data locality.

A major problem with multicore RD analysis is that CRD and PRD profiles

are sensitive to how inter-thread memory references interleave. For example, the number of interleaved memory streams increases as core count scales. Hence, an application's CRD and PRD profiles are not valid at different core counts. Even at the same core count, the relative execution speed between threads may change across different cache sizes, and this may change the interleaving of memory references. As a result, the CRD and PRD profiles measured on one cache size may not be valid for another cache size. So, strictly speaking, CRD and PRD profiles are *architecture dependent*. Such profile's instability defeats the benefits of multicore RD analysis.

Previous multicore RD research has revolved around developing techniques for acquiring profiles and verifying accuracy. Researchers have investigated constructing multicore RD profiles by using trace-based analyses [13, 14] for shared caches. Unfortunately, these techniques are complex because they need to take into account all the possible ways that memory references can interleave. Moreover, these techniques usually require at-scale profiling. Hence, they are impractical for large core counts and problem sizes.

In this dissertation, we will show that the complexity of analyzing memory interleaving depends on how programs are parallelized. *Task-level parallelism* and *loop-level parallelism* are two of the major parallelization techniques. In task-level parallel programs, threads are often doing different computations, and they have different locality characteristics. When the cache size changes, the relative speed between threads may change, causing irregular memory interleaving and complex thread interference. In contrast, in a loop-based parallel program, threads from the same parallel loop are doing very similar computations. These threads have almost identical locality characteristics. When the cache size changes, these threads all either speed up or slow down, but by the same amount. So roughly speaking, the interleaving does not change. In this case, CRD and PRD profiles are highly stable across different cache sizes and can provide accurate analysis. We also find that core count scaling makes CRD and PRD profiles shift *coherently* in a shape-preserving way. The coherent movement suggests predictability. When combined with the existing problem scaling prediction [20], we can study the entire design space from a small number of samples very quickly, and enable practical RD analysis for LCMPscale systems.

In this work, we focus on loop-based parallel programs. Although this is one restriction of our work, loop-based parallel programs are pervasive in many domains, for example, scientific, multimedia, data-mining, and bioinformatics applications. A lot of data-parallel applications have symmetric threads. One of the most popular programming models, OpenMP, also provides a pragma to parallelize loops. In addition, loop-based parallel programs can provide large amounts of parallelism simply by increasing the problem size, so they are highly scalable. For future CMPs, loop-based parallel programs will be very important workloads. For these reasons, multicore RD analysis for loop-based parallel programs will be very valuable to multicore designers, compilers, and programmers.

#### 1.2 Contributions

This dissertation presents a thorough investigation of multicore RD analysis. The challenges lie in developing an efficient multicore RD analysis framework to analyze the CRD and PRD profiles for different scaling dimensions (core count and problem size) and different cache hierarchies (multi-level private and shared caches). This dissertation addresses these challenges and makes the following six contributions.

#### (1) In-depth Analysis on CRD and PRD Profiles

We provide an in-depth analysis on inter-thread interactions in both shared and private caches, and we show how CRD and PRD profiles capture them. We isolate these different effects by creating several new locality profiles to analyze their relative contributions.

First, memory reference streams are interleaved in shared caches, and the interleaving degrades intra-thread's data locality. When data sharing happens, it can reduce the memory reference's reuse distance and improve data locality in shared caches. Because our benchmarks tend to share data across distant iterations, data sharing usually impacts CRD profiles at large RD values in our benchmarks. Depending on where data sharing happens, inter-thread shared memory references also tend to spread and distort the CRD profile. However, we find that this effect is not significant in our benchmarks.

Second, read-shared data causes replication in private caches, reducing the effective cache capacity. On the other hand, write-shared data causes invalidation in private caches. While invalidations cause coherence misses for the reuses of victimized data blocks, they can also improve locality because the holes they leave behind can absorb stack demotions. PRD profiles can capture these effects. In CMPs, multiple private stacks contribute to increased cache capacity. To capture this effect, we compute the *scaled PRD*, or sPRD, which equals  $T \times PRD$ , where Tis the number of threads. Because both CRD and sPRD reflect total cache capacity, we can compare the cache performance between shared and private caches across different sizes by comparing CRD and sPRD profiles directly.

Our analysis quantify these effects, and help researchers better understand how inter-thread interactions impact an application's memory behavior.

#### (2) The Impact of Core Count Scaling

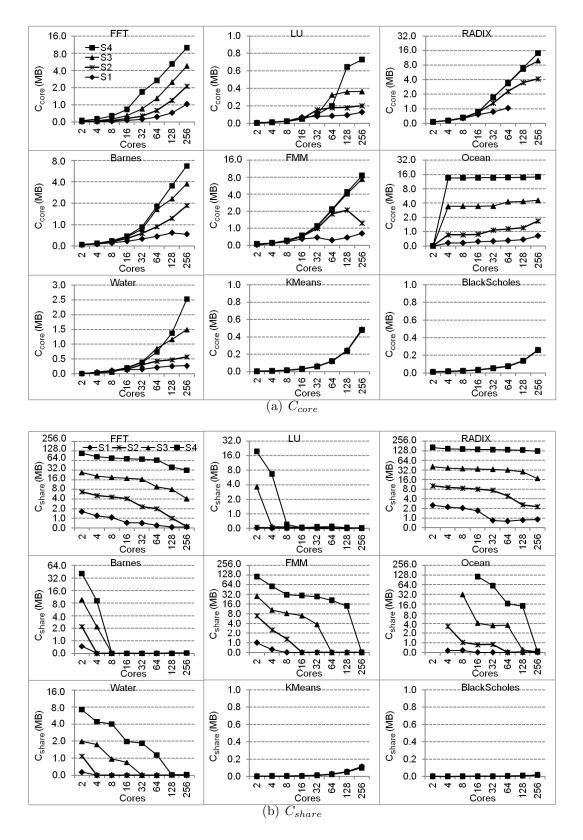

We use RD analysis to study the impact of core count scaling on an application's memory behavior, showing how CRD and PRD profiles evolve at different core counts. For core count scaling, we find CRD profiles shift *coherently* to larger RD values in a shape-preserving way. Shifting slows down and eventually stops at a certain RD value, and we define this point as  $C_{core}$ . Core count scaling only impacts cache performance significantly below this stopping point in shared caches.

Core count scaling also causes sPRD profiles to shift to larger RD values in a shape-preserving way. However, replications and coherence misses also grow as core count scales. As a result, there is no  $C_{core}$  in sPRD profiles, and data locality degradation happens across all RD values.

#### (3) Architectural Implications

We also explore the architectural implications of our data sharing insights.

This dissertation defines  $C_{share}$  to be the cache capacity at which the data sharing of a given application becomes noticeable. Beyond this point, shared caches show locality advantage (lower cache misses) over private caches. We also find that the degree of data sharing is not a fixed characteristic of a given application, but rather is a function of RD value. So the selection between private and shared caches also depends on cache capacities.

When considering the scaling impact, we find that  $C_{core}$  shifts to larger RD values and  $C_{share}$  shifts to smaller RD values with core count scaling. This suggests that the cache capacity at which shared caches begin to outperform private caches decreases as core count scales. But this benefit must be weighted against the higher access latency of shared caches which also grows as core count scales.

Problem size scaling increases the working set size, and CRD and sPRD profiles shift to larger RD values. We also find that both  $C_{core}$  and  $C_{share}$  shift to larger RD values. As a result, problem size scaling may reduce the benefit of using shared caches at a fixed cache capacity.

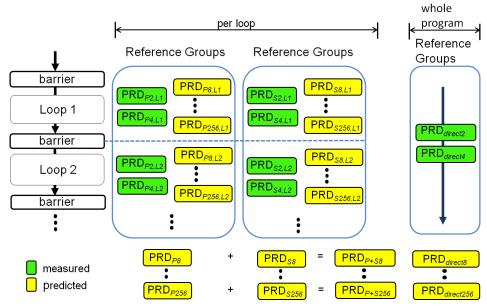

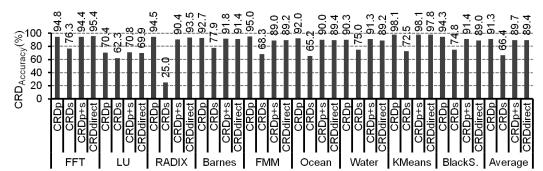

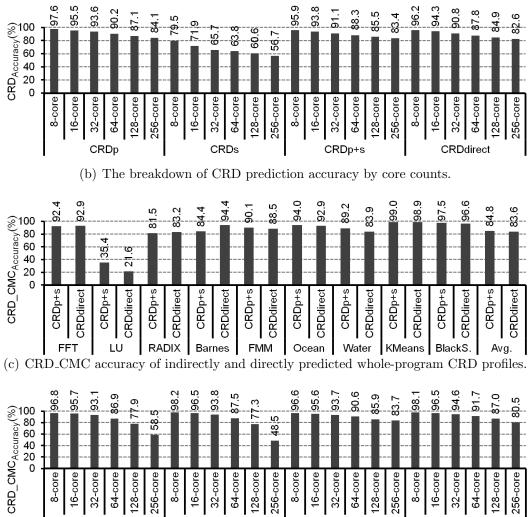

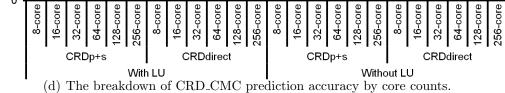

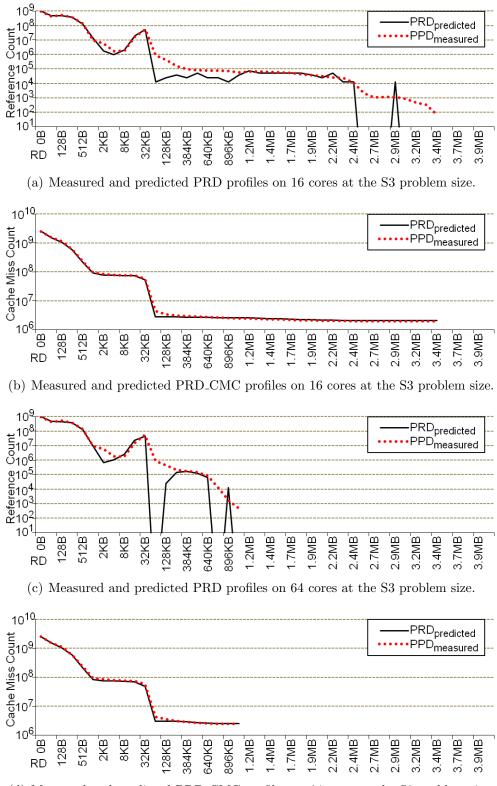

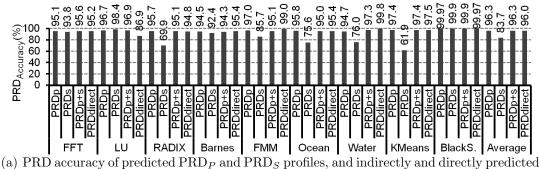

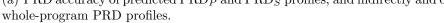

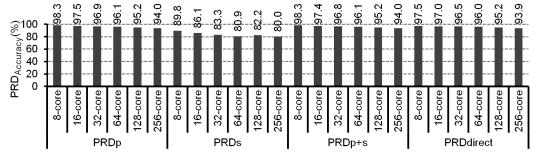

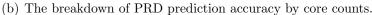

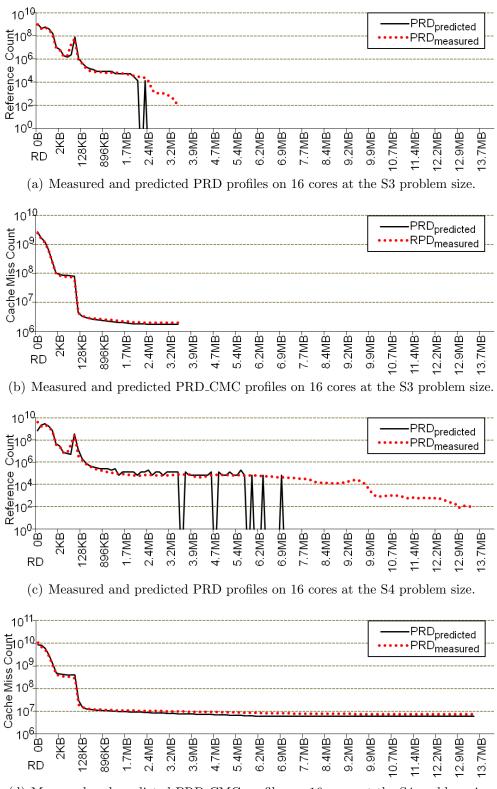

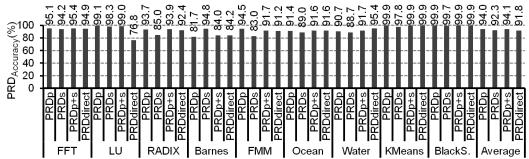

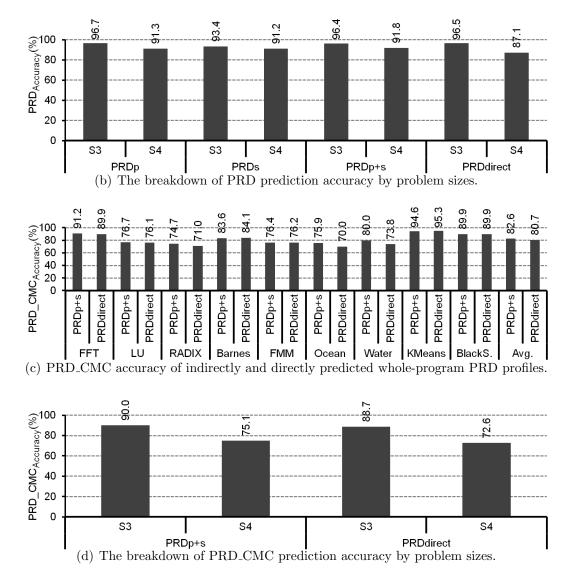

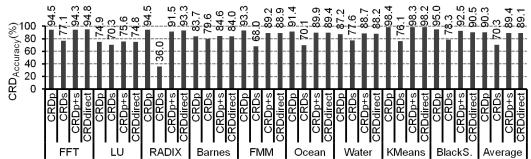

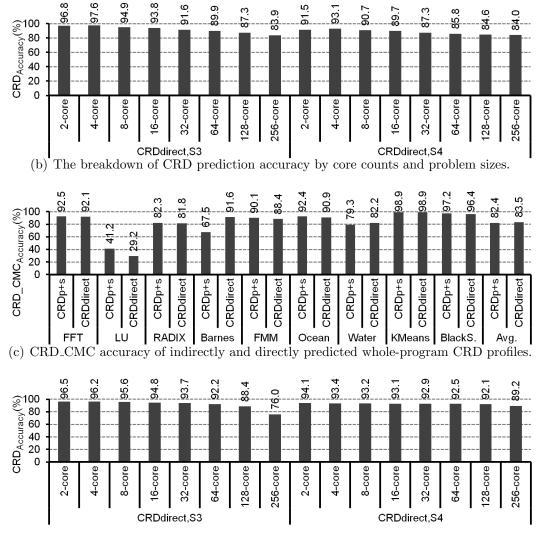

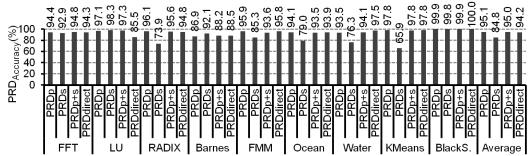

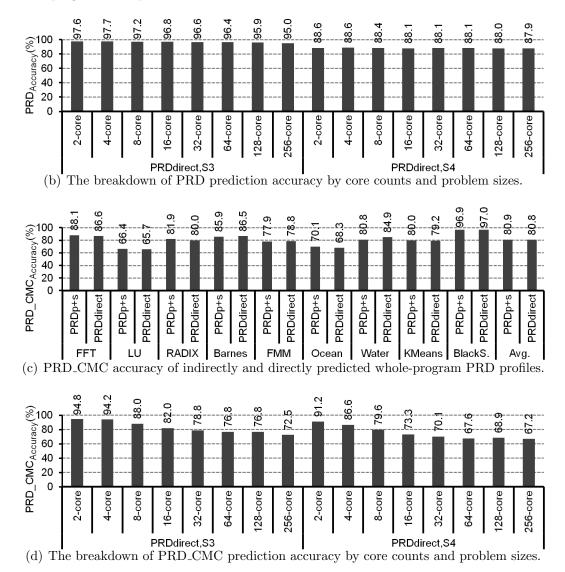

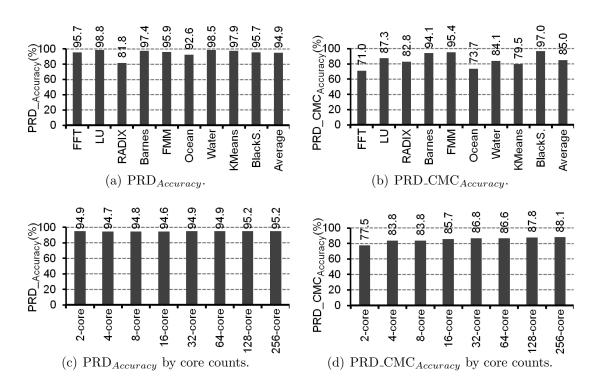

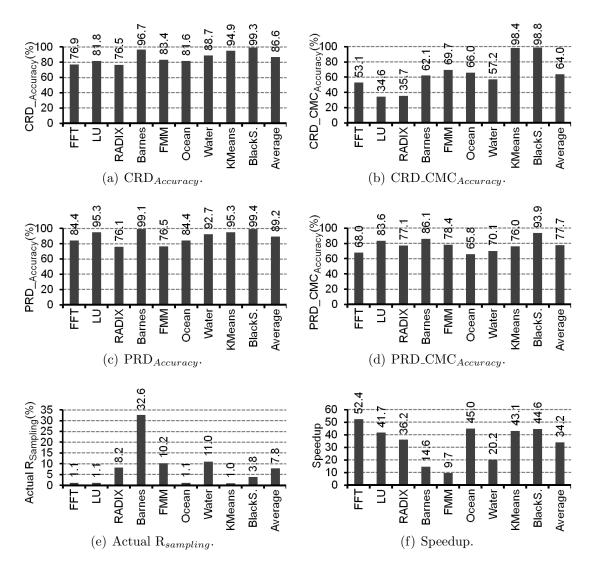

#### (4)Profile Prediction

The CRD and PRD profiles of loop-based parallel programs show coherent shifting with core count scaling and problem size scaling, and we develop techniques to predict the coherent movement of CRD and PRD profiles. Reference groups [20] is previously used to predict a sequential program's RD profiles across problem size scaling. We employ this technique to predict CRD and PRD profiles across core count scaling. Because data sharing also causes spreading, we propose uniformly distributing the portion of CRD profiles, which is associated with shared references. We investigate the prediction accuracy of CRD and PRD profiles under three scaling schemes, core count scaling, problem size scaling, and core-problem scaling. To evaluate the prediction accuracy between measured and predicted profiles, we use two metrics,  $RD_{Accuracy}$  and  $RD_{CMC_{Accuracy}}$ . The former represents the normalized absolute difference, and the latter reflects the difference in cache performance. The average  $RD_{Accuracy}$  and  $RD_{CMC_{Accuracy}}$  for CRD (PRD) profiles are between 82.4% (80.7%) and 91.5% (96.3%). We also find that the prediction accuracy decreases as the prediction horizon increases.

Lastly, we compare our prediction technique against the RD sampling technique, which can also accelerate the acquisition of profiles. The prediction technique and the sampling technique have similar average accuracy. However, the sampling technique needs to collect profiles at every configuration. In contrast, the prediction technique can predict any configuration from a small number of measurements. The benefit of prediction becomes more significant for core-problem scaling. As a result, our prediction technique can outperform the RD sampling technique.

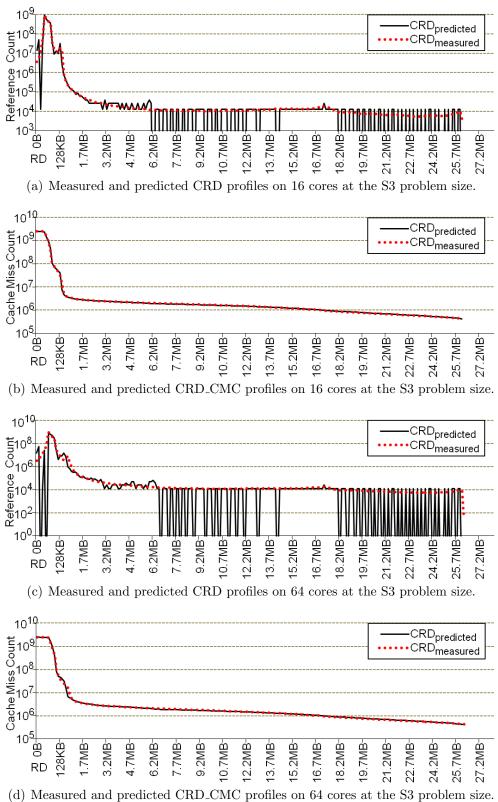

#### (5) Profile Stability and Cache Performance Validation via Simulation

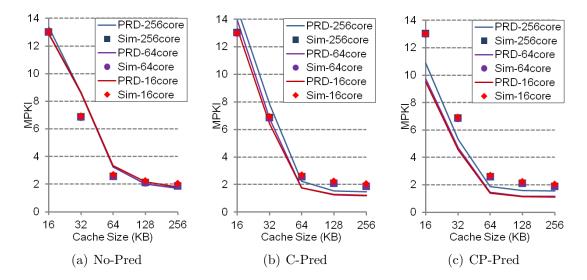

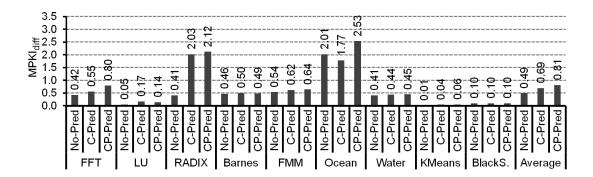

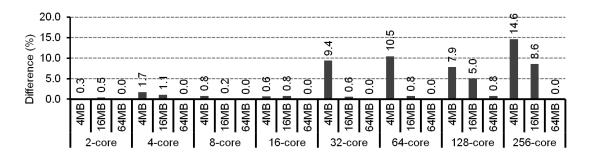

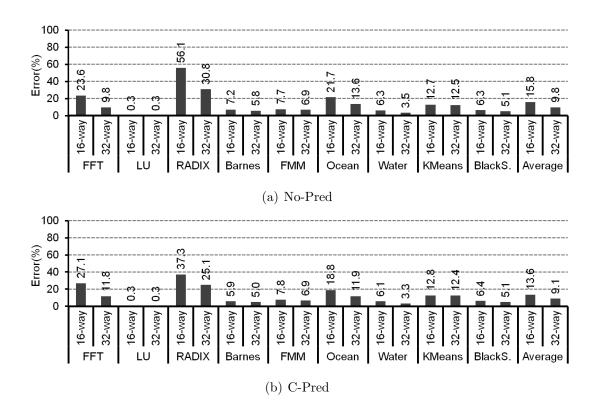

We quantify the CRD and PRD profiles' dependence on cache capacity, and we also validate the cache performance provided by CRD and PRD profile predictions against detailed simulations. We use the M5 simulator to model tiled CMPs and simulate our benchmarks on processors with 2–256 cores. For shared last level caches (LLCs), we simulate the cache capacity from 4MB to 128MB. For private L2 caches, we simulate the per-core L2 cache capacity from 16KB to 256KB. In total, we simulate 3,168 configurations.

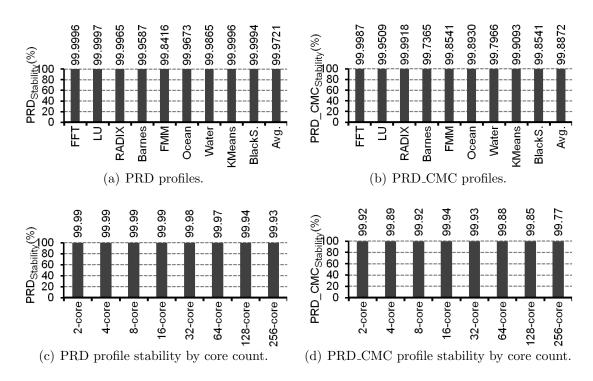

Two stability metrics,  $\text{RD}_{Stability}$  and  $\text{RD}_{CMC}_{Stability}$ , are used to evaluate profile stability. The average  $\text{RD}_{Stability}$  and  $\text{RD}_{CMC}_{Stability}$  for CRD (PRD) profiles are 97.2% (99.97%) and 99.6% (99.89%), respectively. The results confirm that CRD and PRD profiles are minimally cache-capacity dependent in our loop-based parallel programs.

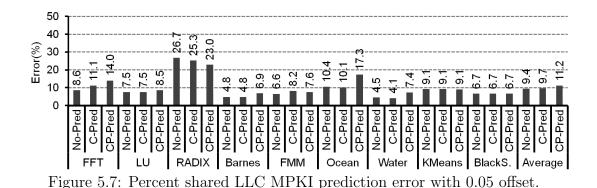

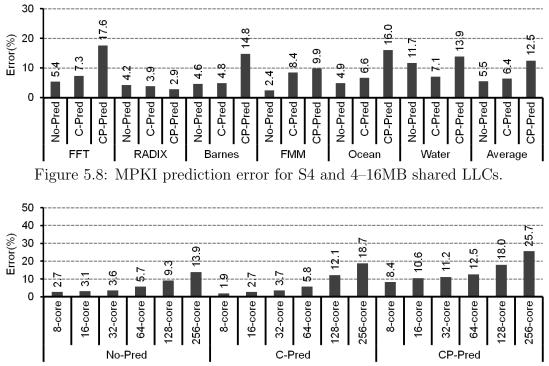

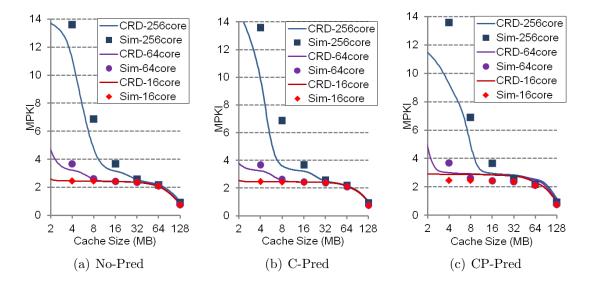

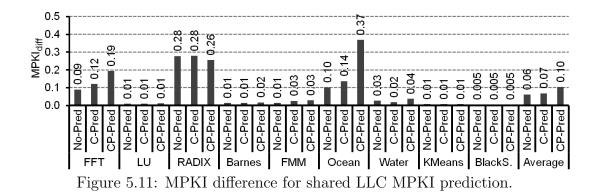

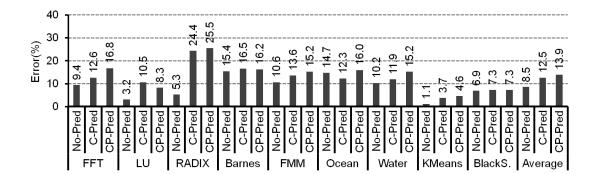

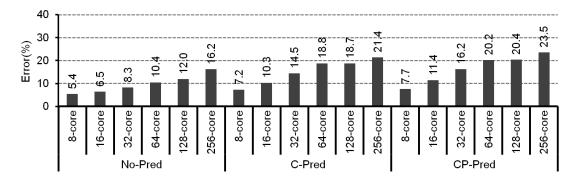

Lastly, our core count prediction techniques can predict shared LLC (private L2 cache) MPKI to within 10% (13%) of simulation across 1,728 (1,440) configurations using 72 measured CRD (PRD) profiles. When combined with the existing prediction technique for problem size scaling, we can predict shared LLC (private L2 cache) MPKI to within 12% (14%) of simulation using 36 measured CRD (PRD) profiles. The results show that our prediction technique can help explore a large design space efficiently.

#### (6) Multicore Cache Hierarchy Optimization

Lastly, we propose a novel framework for identifying optimal multicore cache hierarchies for loop-based parallel programs by using reuse distance analysis. Our framework can analyze and quantify the performance difference for different cache hierarchies easily, providing several new insights. In this work, we focus on tiled-CMPs.

The key to optimizing multicore cache hierarchies lies in *balancing the total* on-chip and off-chip memory stalls. To achieve good performance, the capacity of the last private cache above the last level cache must exceed the region in the PRD profile where significant data locality degradation happens. Shared LLCs can outperform private LLCs when the total off-chip memory stall saved in shared LLCs is larger than the total on-chip memory stall saved in private LLCs. At the optimal LLC size, the average performance (AMAT) difference between private and shared LLCs can reach as high as 15%, but it is smaller than the performance difference caused by L2/LLC capacity partition (76% in shared LLCs, and 33% in private LLCs). This suggests that the physical data locality is very important for multicore cache systems.

## 1.3 Roadmap

The rest of this dissertation is organized as follows. Chapter 2 provides the background for our study on multicore RD analysis, and explains the methodology used to acquire CRD and PRD profiles. Chapter 3 discusses the impact of data sharing on CRD and PRD profiles by breaking down CRD and PRD profiles into several profiles to explain how different effects change the application's data locality. We also explore the architectural implications of CRD and PRD profiles across core count scaling and problem size scaling. The coherent movement in CRD and PRD profiles due to different scaling schemes suggests the predictability of profiles. Chapter 4 develops techniques to predict CRD and PRD profiles, and it evaluates the prediction accuracy. Then, Chapter 5 validates the profile stability, and it also demonstrates our technique's ability to accelerate cache performance evaluation. To study the multicore cache system design, Chapter 6 proposes a novel framework based on multicore RD analysis for studying cache hierarchy optimization. Chapter 7 compares our prediction technique against the RD sampling technique. Finally, Chapters 8 lists the prior work related to this research, and Chapter 9 concludes this dissertation and suggests future research directions.

#### Chapter 2

### Background and Methodology

This chapter describes the essential concept of multicore reuse distance (RD) analysis and the methodology used to acquire profiles. Section 2.1 introduces multicore reuse distance. Section 2.2 presents our modified Intel Pin tool, which we use to profile loop-based parallel programs. Then, we introduce the 9 benchmarks and the architecture-application design space used to drive this work.

## 2.1 Multicore Reuse Distance

In 1970, Mattson et al. [12] introduced reuse distance (RD) to model different storage configurations on virtual memory pages in one pass. Later, researchers applied RD analysis to study uniprocessor cache performance.

Reuse distance measures the number of unique data blocks referenced between two references to the same data block in the LRU stack. When a new data block appears in the memory reference stream, this data block is pushed onto the stack. When a previously-accessed data block appears, the stack is searched. The reuse distance is the depth between the referenced data block and the top of the stack. The histogram of RD values for all references in a program is the RD profile. For an LRU cache with capacity C, the number of cache misses is the sum of all references counts with reuse distance  $\geq C$  in the RD profile. For sequential programs, RD

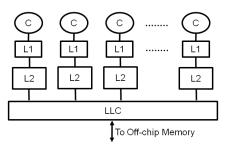

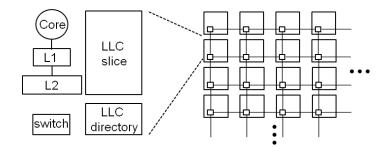

Figure 2.1: Multicore cache hierarchy.

profiles are *architecture independent*. They can be acquired on one machine, and then used to predict cache misses at different cache sizes without additional runs.

Multicore processors often contain both shared and private caches. For example, Figure 2.1 illustrates a typical multicore processor consisting of 2 levels of private cache backed by a shared last-level cache. Threads interact very differently in each type of cache, requiring separate locality profiles. For example, data sharing may reduce the aggregate working set size in shared caches, reducing cache capacity pressure. In contrast, data sharing may cause replication and communication across private caches, reducing the effective cache capacity and inducing coherence misses. To model shared caches and private caches, we use *Concurrent Reuse Distance (CRD)* and *Private-stack Reuse Distance (PRD)* profiles, respectively.

## 2.1.1 Concurrent Reuse Distance

RD analysis can be extended for shared caches by computing reuse distance across the interleaved memory streams from all cores on a single LRU stack–i.e., the concurrent reuse distance (CRD) [13, 14, 15, 16, 17]. Data locality in shared caches is affected by several different inter-thread interactions. Figure 2.2 illustrates CRD

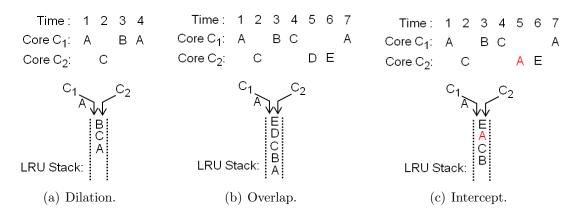

Figure 2.2: Two interleaved memory reference streams, illustrating dilation, overlap, and intercept among inter-thread memory references in the shared cache.

for a sequence of interleaved memory references from two cores, showing dilation, overlap, and intercept among inter-thread memory references in the shared cache.

In Figure 2.2(a), Core 1 accesses data blocks A and B at time 1 and 3, while Core 2 accesses data block C at time 2. When Core 1 accesses A at time 4, Core 1's reuse of A has RD = 1, but its CRD = 2. In this case, CRD is larger than RD, because Core 2 brings in one unique reference, C. Hence, the interleaving causes CRD dilation.

In many multithreaded programs, threads share data. Data sharing can reduce dilation in two ways. First, data sharing can introduce *overlapping references*, which happens when data sharing occurs inside the reuse interval of referenced data. In Figure 2.2(b), both Core 1 and Core 2 access block C at time 2 and time 4. So there are only 4 unique references between the reuse of A, instead of 5, due to the overlap. Second, data sharing can introduce *intercepts*, which occur when data sharing happens on the reused data itself. For example, in Figure 2.2(c), Core 2 references A instead of D at time 5, which causes Core 1's reuse of A to exhibit CRD = 1, so CRD actually becomes less than RD.

In Chapter 3, we investigate dilation, overlap, and intercept in CRD profiles. Then we study their effects as core count and problem size scale.

#### 2.1.2 Private-stack Reuse Distance

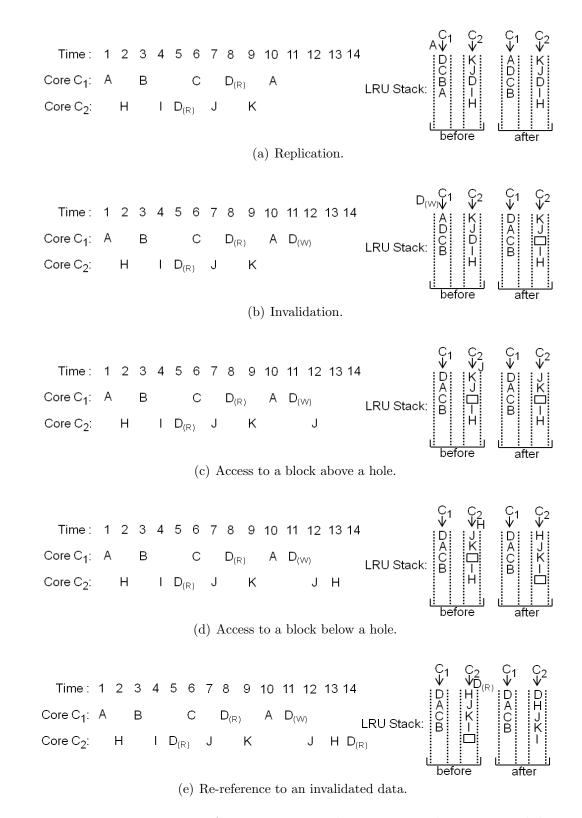

Private-stack Reuse Distance (PRD) profiles are measured by applying each thread's memory reference stream onto its own LRU stack while maintaining coherence across per-thread stacks [15, 16, 17]. To maintain data coherence in private caches, write invalidation is a common mechanism. In the absence of writes, there are not any inter-thread interactions across private stacks. For example, Figure 2.3(a) shows the PRD stacks from two cores before and after the memory access to A at time 10. Both Core 1 and Core 2 have read data block D by this time. Readsharing causes duplication of D in the private stacks. Hence, replications reduce the effective cache capacity in private caches.

When a write happens, only one data block is kept in the private stacks, as the cache coherence protocol invalidates all other copies. In Figure 2.3(b), Core 1 writes D at time 11, and Core 1's reuse of D has PRD = RD = 1. Core 2's block D is invalidated. To prevent invalidations from promoting blocks further down the LRU stack, invalidated blocks become holes [15, 16, 17].

The depth of the hole is unaffected when referencing blocks above the hole. In Figure 2.3(c), Core 2 accesses block J at time 12. Block J moves to the top of the stack, and it pushes K down. The hole remains at the same position. However, when

Figure 2.3: Two memory reference streams, illustrating replication, invalidation, and hole in the private caches.

Core 2 accesses H, which is below the hole, H is brought to the top of the stack. Then the hole moves to the former depth of block H, as shown in Figure 2.3(d). So, blocks which are deeper than H remain at the same depths in the stack.

When a new block or an invalidated block is accessed, all the data blocks above the topmost hole are pushed down and fill the topmost hole. Figure 2.3(e) shows an example. When Core 2 re-references invalidated block D, it causes a miss in Core 2's private cache. Data block I - H are pushed down and fill the hole.

Invalidations always cause the reuse of a victimized data block to be a cache miss, and these are known as coherence misses. However, invalidations may also improve data locality because the holes they leave behind eventually absorb stack demotions. For example, if Core 2 first accesses a new data block L instead of H in Figure 2.3(d), the hole will be filled, and the depth of H is still 4. Next when Core 2 accesses block H, the reuse of block H has PRD = 4, instead of 5. We call this effect *demotion absorption*. Hence, if victimized data blocks are not re-referenced frequently, invalidations may actually relieve capacity pressure and improve data locality.

In Chapter 3, we will investigate replication and invalidation in PRD profiles. Then we will study their effects as core count and problem size scale.

#### 2.2 Methodology

To provide an in-depth analysis on how data sharing and interleaving impact CRD and PRD profiles for loop-based parallel programs, we develop a profiling tool based on the Intel Pin infrastructure to acquire CRD and PRD profiles across 9 benchmarks running 4 different problem sizes on 2–256 cores. In this section, we first introduce our Pin-based tool. Then we present the benchmarks and the design space that are used in this research.

#### 2.2.1 Pin-based Profiling Tool

Intel's Pin [21] is a dynamic binary instrumentation tool that can capture very detailed program behavior. The instrumented binary runs natively on the hardware, so it provides much higher performance and compatibility than simulators. Hence, we develop our own Pin tool to acquire CRD and PRD profiles.

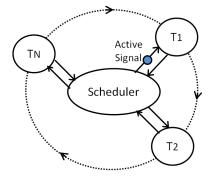

One challenge in acquiring multicore RD profiles by using Pin is to ensure the accurate modeling of inter-thread interactions. We need to control the context switch in the OS scheduler to simulate simultaneous thread execution, which is faithful to how a CMP would execute the threads. Therefore, we adopt the finegrain context switch method proposed by McCurdy and Fischer [22], as illustrated in Figure 2.4. In the McCurdy and Fischer's method, a centralized scheduler controls which thread is active. Only one thread can be active at a time. The other threads are waiting for the active signal from the scheduler. The active signal is passed in round-robin order, so the memory accesses are interleaved in a consistent order across all threads. The scheduler also simulates the synchronization mechanism of Pthreads.

When we acquire CRD and PRD profiles, we make several assumptions. First,

Figure 2.4: Thread interleaving mechanism.

our Pin tool performs functional execution only, context switching between threads every memory reference. Hence, the memory references from each thread are interleaved uniformly in time. Second, in our memory interleaving model, we don't simulate a particular cache hierarchy or CMP architecture. So, there are no timingrelated interferences in CRD and PRD profiles. As we will show in our stability study (Section 5.2), this assumption of uniform memory interleaving is accurate enough to acquire profiles for loop-based parallel programs. Third, we also assume the application is the only load on the system. The OS does not interrupt threads. Finally, we assume 64-byte memory blocks.

#### 2.2.2 Benchmarks

Table 2.1 lists our benchmarks used in this research: FFT, LU, Radix, Barnes, FMM, Water, and Ocean from the SPLASH2 suite [23], KMeans from MineBench [24], and BlackScholes from PARSEC [25]. For each benchmark, we employ 4 problem sizes, S1–S4 ( $2^{nd}$  column of Table 2.1). We run initialization code on a single core, optionally simulate the beginning of the parallel region, and then turn on CRD and

| Benchmark    | Problem Sizes(S1/S2/S3/S4)                         | Insts Profiled (M)(S1/S2/S3/S4) | Profiled Region |

|--------------|----------------------------------------------------|---------------------------------|-----------------|

| FFT          | $2^{16}/2^{18}/2^{20}/2^{22}$ elements             | 29/129/560/2,420                | whole program   |

| LU           | $256^2/512^2/1024^2/2048^2$ elements               | 43/344/2,752/22,007             | whole program   |

| RADIX        | $2^{18}/2^{20}/2^{22}/2^{24}$ keys                 | 53/211/843/3,372                | whole program   |

| Barnes       | $2^{13}/2^{15}/2^{17}/2^{19}$ particles            | 214/1,015/4,438/19,145          | 1 timestep      |

| FMM          | $2^{13}/2^{15}/2^{17}/2^{19}$ particles            | 235/1,006/4,109/16,570          | 1 timestep      |

| Ocean        | $130^2/258^2/514^2/1026^2$ grid                    | 30/107/420/1,636                | 1 timestep      |

| Water        | $10^3/16^3/25^3/40^3$ molecules                    | 43/143/553/2,099                | 1 timestep      |

| KMeans       | $2^{16}/2^{18}/2^{20}/2^{22}$ objects, 18 features | 186/742/2,967/11,874            | 1 timestep      |

| BlackScholes | $2^{16}/2^{18}/2^{20}/2^{22}$ options              | 60/242/967/3,867                | 1 timestep      |

Table 2.1: Parallel benchmarks used in our study.

PRD profiling and continue parallel region simulation for some number of instructions ( $3^{rd}$  column of Table 2.1). In FFT, LU, and Radix, profiles are acquired for the entire program. For the other benchmarks, profiles are acquired for only 1 timestep of the algorithm, so we skip the  $1^{st}$  timestep and profile the  $2^{nd}$  timestep.

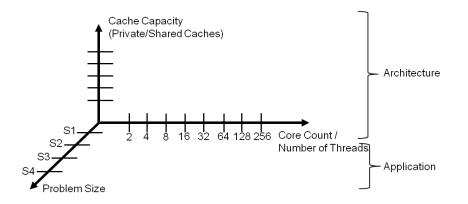

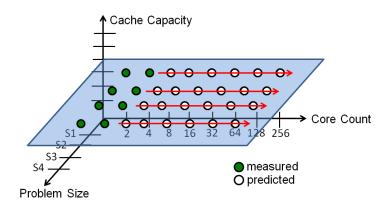

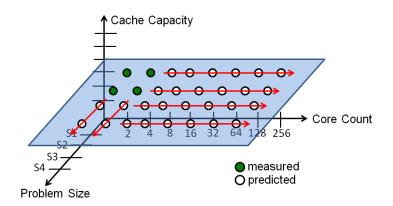

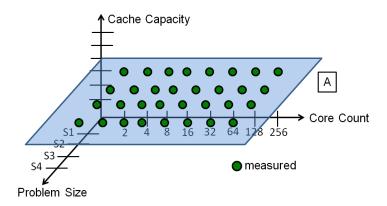

#### 2.2.3 Architecture-Application Design Space

Processor scaling defines a design space consisting of multicore processors with varied core counts and cache organizations with different capacities. These are architecture design parameters. As processors scale to large core counts and cache capacities, problem size scales, too. Hence, our work also considers the problem size as an independent parameter that can be varied as well. The number of threads and problem sizes are application parameters. Together, these scaling dimensions of architecture and application form a multi-dimensional designed space, as illustrated in Figure 2.5. We call this architecture-application design space (AADS).

In this research, each benchmark has 4 problem sizes running on 8 core counts

Figure 2.5: Multi-dimensional architecture-application design space (AADS).

from 2 to 256 cores. We also study private and shared caches with varying cache capacities. By comparing CRD (PRD) profiles along any axis, we can characterize profile sensitivity to the corresponding type of scaling.

In our profile prediction study, each benchmark has 32 configurations, and we have a total of 288 configurations across our 9 benchmarks. When we evaluate the accuracy of using CRD and PRD profile predictions to estimate the multicore cache performance (MPKI), we simulate 6 different shared LLC sizes and 5 different private L2 cache sizes. In this case, the design space has a total of 3,168 configurations.

## Chapter 3

#### Multicore Reuse Distance Analysis

The memory behavior on multicore cache systems is the result of intra-thread data locality and inter-thread interferences. In Section 2.1, we review different thread interactions in private and shared caches, and we show how CRD and PRD capture them. In Section 3.1, we further separately quantify these effects by creating several new locality profiles that isolate these thread interactions. This analysis provides rich information about how inter-thread interactions impact an application's memory behavior in private and shared caches.

In Section 3.2–Section 3.4, we study three sources of inter-thread interaction perturbation. The first one is cache capacity scaling; for this, we present our interaction insights at a fixed core count and problem size. The second one is core count scaling, which increases the number of interleaving memory reference streams. The third one is problem size scaling, which increases the memory footprint.

The impact of core count scaling and problem size scaling on CRD and PRD profiles has implications for multicore cache performance. In Section 3.5, we identify two important cache capacities,  $C_{core}$  and  $C_{share}$ . Then we study their architectural implications.

#### 3.1 Quantifying Thread Interactions

For shared caches, inter-thread interactions cause dilation, overlap, and intercept in CRD profiles. On the other hand, for private caches, inter-thread interactions cause replication and invalidation in PRD profiles. To study inter-thread interactions, we isolate these different effects by creating several new locality profiles. To further separate the different locality characteristics of each parallel region in a program, our Pin tool records profiles in between every pair of barrier calls–*i.e.*, per parallel region. Although there might be several parallel loops in the same parallel region, per-parallel region profiling is sufficient for our study.

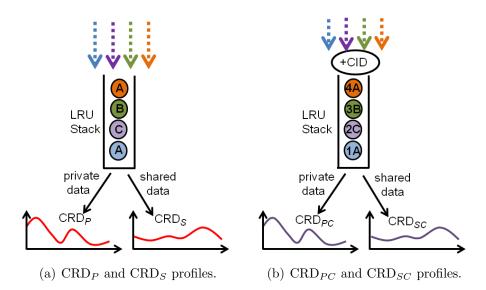

## 3.1.1 CRD profiles

Within each parallel region, we acquire CRD profiles for mostly private data and mostly shared data separately. We call the former profiles "private-date CRD (CRD<sub>P</sub>) profiles", and we call the latter profiles "shared-data CRD (CRD<sub>S</sub>) profiles". We employ a single global LRU stack for computing CRD<sub>P</sub> and CRD<sub>S</sub>, as illustrated in Figure 3.1(a).

To separate private and shared data blocks, we record each memory block's CRD values separately and the number of times the block is referenced by each core. In our benchmarks, because individual memory blocks tend to exhibit a small number of distinct CRD values, this bookkeeping does not increase storage appreciably. After a parallel region completes, we use a fixed threshold to determine each memory block's sharing status. If a single core is responsible for 90% or more of

Figure 3.1: Acquiring  $CRD_P$ ,  $CRD_S$ ,  $CRD_{PC}$ , and  $CRD_{SC}$  profiles.

a memory block's references, the block is private; otherwise, it is shared. Then we accumulate all memory blocks' CRD counts into either the  $CRD_P$  profile or  $CRD_S$  profile based on each block's sharing status.

As mentioned in section 2.1.1, data sharing introduces overlapping references and reduces the dilation. Although the  $\text{CRD}_P$  profile only has the mostly private data, data sharing still occurs in between data reuses. This is because we measure CRD values from the same stack. Hence, the  $\text{CRD}_P$  profile represents the combined effect of dilation and overlap, and the amount of intercepts is small. The  $\text{CRD}_S$ profile also captures data sharing that happens on the reuse data itself. As a result, the  $\text{CRD}_S$  profile not only contains the dilation and overlap effects, but it also has the intercept effect.

Next, we isolate the sharing-based interactions. We maintain a second global LRU stack, and we prepend every memory block's address with the ID of the core (CID) that performs this memory access, as illustrated in Figure 3.1(b). We call

the profiles acquired on this CID-extended stack  $\text{CRD}_{PC}$  and  $\text{CRD}_{SC}$  profiles. In these two profiles, inter-thread references are always unique. Comparing  $\text{CRD}_{PC}$ and  $\text{CRD}_P$  profiles shows the impact of overlap. Similarly, the effect of intercepts due to shared data is also removed. Comparing  $\text{CRD}_{SC}$  and  $\text{CRD}_S$  profiles shows the combined impact of overlap and intercept.

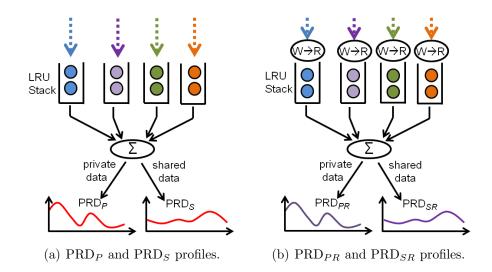

## 3.1.2 PRD profiles

For PRD profiles, each core has its own private LRU stack, and the coherent mechanism mentioned in Section 2.1.2 is implemented. We acquire PRD profiles for mostly private data and mostly shared data separately within each parallel region. We call the former profiles "private-data PRD (PRD<sub>P</sub>) profiles", and we call the latter profiles "shared-data PRD (PRD<sub>S</sub>) profiles". After a parallel region completes, we sum up these per-thread PRD<sub>P</sub> profiles to create a single PRD<sub>P</sub> profile, and we sum up these per-thread PRD<sub>S</sub> profiles to create a single PRD<sub>S</sub> profile, as illustrated in Figure 3.2(a). These two profiles represent overall per-thread memory behavior for mostly private data and mostly shared data.

As mentioned in section 2.1.2, read-shared data causes replications, and writeshared data causes invalidations in private stacks. Both  $PRD_P$  and  $PRD_S$  profiles contain the combined effect of replication and invalidation because we measure PRD values on the same per-core stack. The re-reference of invalidated data causes cache misses. These "coherence misses" appear at the infinite PRD value.

Next, we remove write-sharing to isolate hole-related interactions. This is done

Figure 3.2: Acquiring  $PRD_P$ ,  $PRD_S$ ,  $PRD_{PR}$ , and  $PRD_{SR}$  profiles.

by converting writes to reads, as illustrated in Figure 3.2(b). The only effect left in profiles is replication. Profiles acquired on read-conversion stacks are called  $PRD_{PR}$  and  $PRD_{SR}$  profiles. Comparing  $PRD_P$  with  $PRD_{PR}$  profiles shows the absorption impact due to holes. Comparing  $PRD_S$  and  $PRD_{SR}$  profiles shows the impact of holes and coherence misses.

# 3.2 Thread Interactions Analysis at a Fixed Core Count and Problem Size

This section applies the isolation techniques introduced in Section 3.1 to the study of inter-thread interactions. We analyze two specific benchmarks, FFT and Barnes. Although each benchmark has different interactions, all parallel regions exhibit very similar behavior. The insights gathered from FFT and Barnes can generally represent inter-thread interactions for our benchmarks.

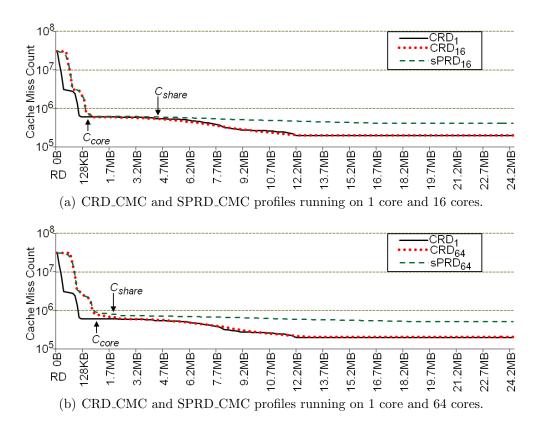

Although PRD profiles are based on per-core stacks, the multiple private stacks

still contribute to increased cache capacity on multicore processors. To capture this effect, we compute the *scaled PRD*, or sPRD, which equals  $T \times PRD$ , where T is the number of threads. Because both CRD and sPRD reflect total cache capacity, we can compare the cache performance between shared and private caches across different cache sizes by comparing CRD and sPRD profiles directly.

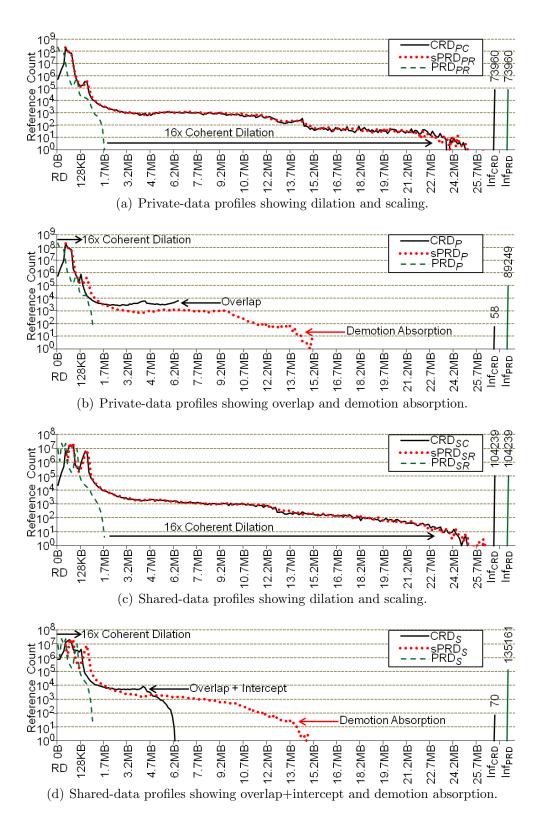

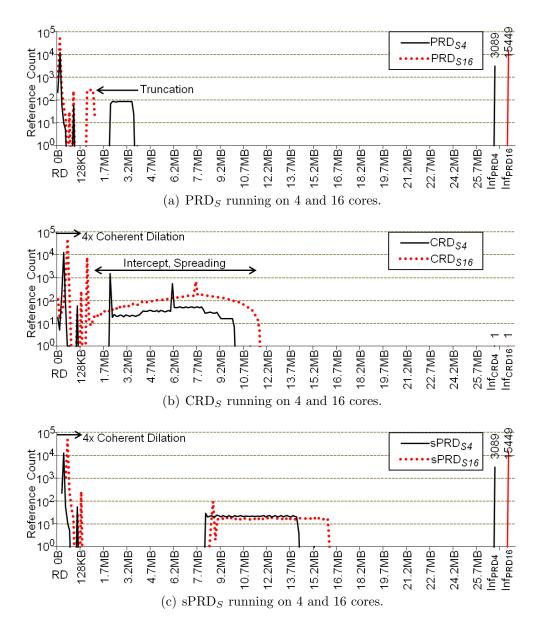

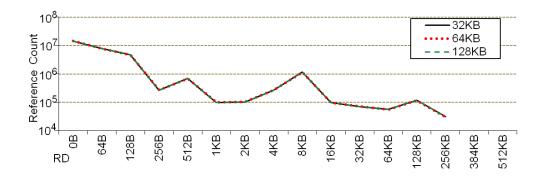

Figure 3.3 and Figure 3.4 shows different CRD and PRD profiles for the most important parallel region in Barnes and FFT running on 16 cores at the S2 problem size. In each graph, the Y-axis is the reference count in log10 scale, and the X-axis is the RD value in terms of cache capacity. This is done by multiplying RD values by the cache block size, 64 bytes. In this study, for each profile, reference counts from multiple adjacent RD values are summed into a single RD bin, and plotted as a single Y value. For capacities 0–128KB, bin size grows logarithmically; beyond 128KB, all bins are 128KB each.

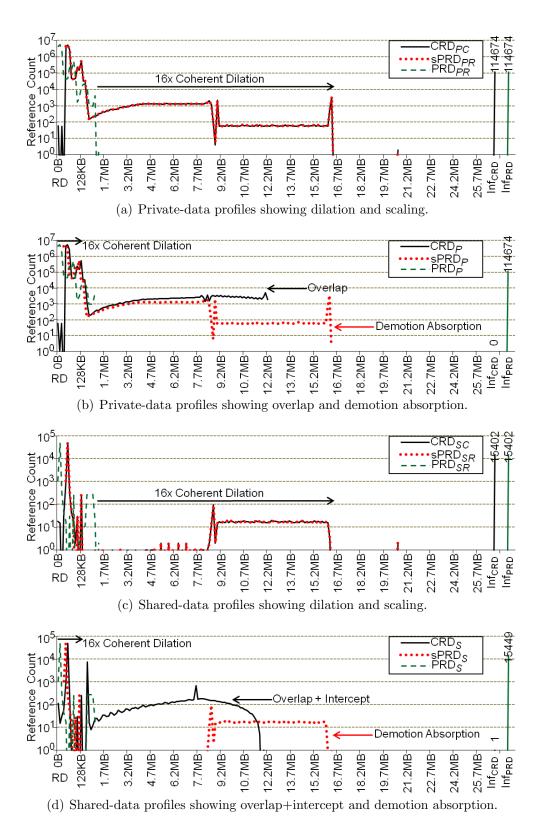

#### 3.2.1 Private-data Profiles

Figure 3.3(a) and Figure 3.4(a) plot  $CRD_{PC}$  and  $sPRD_{PR}$  profiles along with  $PRD_{PR}$  profile. As described in Section 3.1, there are no sharing-induced interactions in  $CRD_{PC}$  and  $sPRD_{PR}$  profiles. Comparing  $CRD_{PC}$  and  $PRD_{PR}$  profiles shows the dilation effect, and comparing  $sPRD_{PR}$  and  $PRD_{PR}$  profiles shows the scaling effect.

In Figure 3.3(a) and Figure 3.4(a), the  $sPRD_{PR}$  profile is a 16x scaling of the  $PRD_{PR}$  profile. This is because sPRD profiles are the scaled versions of PRD

Figure 3.3: Barnes' locality profiles for the most important parallel region running on 16 cores at the S2 problem size.

Figure 3.4: FFT's locality profiles for the most important parallel region running on 16 cores at the S2 problem size.

profiles. An interesting observation is that the  $\text{CRD}_{PC}$  profile is almost identical to the sPRD<sub>PR</sub> profile, and the  $\text{CRD}_{PC}$  profile is also a 16x scaling of the PRD<sub>PR</sub> profile. This is because symmetric threads are interleaved systematically in the same parallel region. In the shared cache, the intra-thread data reuse at a particular RD is interleaved by the same amount of RD from each of the other simultaneous threads. This effect is called *dilation*. In this example, the dilation is by exactly a factor of 16x. As a result, scaling and dilation both shift the PRD<sub>PR</sub> profile in a shapepreserving way and degrade data locality at the same rate, *i.e.*, linear with the number of threads.

When there is no data sharing, shared and private caches show the same data locality behavior. However, when data sharing happens, shared and private caches have different sharing-related interactions. Figure 3.3(b) and Figure 3.4(b) illustrates the  $CRD_P$ ,  $sPRD_P$ , and  $PRD_P$  profiles of Barnes and FFT, respectively. As described in Section3.1, comparing  $CRD_{PC}$  and  $CRD_P$  profiles shows the impact of overlapping references, and comparing  $sPRD_{PR}$  ( $PRD_{PR}$ ) and  $sPRD_P$  ( $PRD_P$ ) profiles shows the impact of invalidated references.

$CRD_P$  profiles terminate before  $CRD_{PC}$  profiles. As discussed in Section 3.1, data sharing introduces overlap that reduces dilation in CRD profiles, and the amount of reduction depends on the degree of data sharing.  $CRD_P$  and  $CRD_{PC}$ profiles are almost identical at small RD values. As RD value increases, the  $CRD_P$ profile exhibits less shift. In our benchmarks, programmers tend to share data across distant loop iterations, so data sharing tends to happen at large reuse windows only. As a result, overlapping references rarely happen in small reuse distance windows for CRD profiles.

Data sharing introduces demotion absorption in sPRD profiles. At small RD values,  $sPRD_P$  and  $sPRD_{PR}$  profiles are almost identical. This is because invalidated references rarely happen in small reuse windows for sPRD profiles. As RD value increases,  $sPRD_P$  profiles exhibit less shift and terminate before  $sPRD_{PR}$  profiles. When there are few invalidations as in FFT,  $sPRD_{PR}$  and  $sPRD_P$  are practically identical, even at large RD values. However, when there are more invalidations, as in Barnes, the holes reduce the shift significantly.

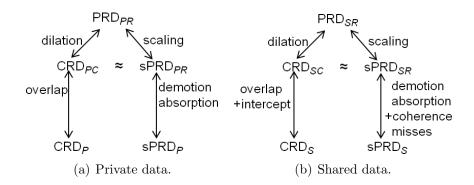

Lastly, the amount of contraction in  $\text{CRD}_P$  and  $\text{sPRD}_P$  profiles varies with reuse distance. Because the contraction comes from the inter-thread interactions of sharing data, its presence or absence along  $\text{CRD}_P$  and  $\text{sPRD}_P$  profiles permits assessing the degree of data sharing as a function of reuse distance. As illustrated in Figure 3.3(b) and Figure 3.4(b),  $\text{CRD}_P$  and  $\text{sPRD}_P$  profiles are almost identical at small RD values. Then data sharing begins to affect  $\text{CRD}_P$  and  $\text{sPRD}_P$  profiles. The contraction increases as RD value grows, and finally causes the different termination of  $\text{CRD}_P$  and  $\text{sPRD}_P$  profiles.  $\text{CRD}_P$  profiles end earlier than  $\text{sPRD}_P$  profiles. Although invalidations create holes and reduce the reuse distance, this absorption effect is smaller than the overlap effect. The is because write-shared data makes up only a portion of the total shared data, and replications caused by read-shared data also degrades data locality in private caches. Figure 3.5(a) illustrates the relationship between profiles for private data.

Figure 3.5: Quantifying individual thread interaction effects.

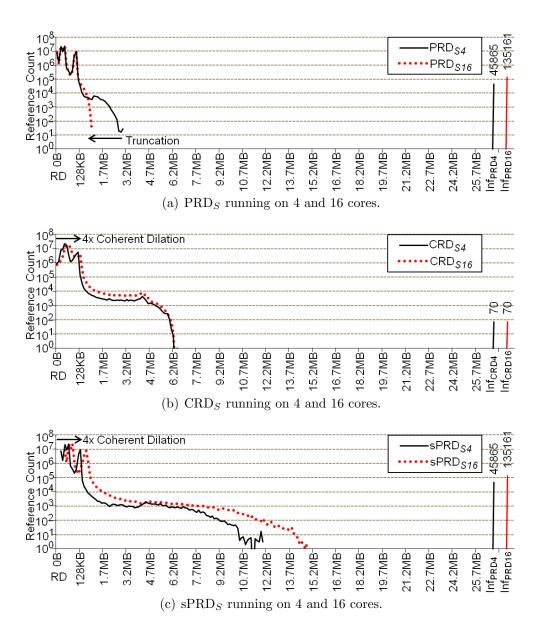

### 3.2.2 Shared-data Profiles

Figure 3.3(c)-(d) and Figure 3.4(c)-(d) plot the shared-data profiles of Barnes and FFT. The shared-data profiles exhibit behavior very similar to the corresponding private-data profiles. First, the dilation and scaling are equivalent for parallel loops in the absence of data sharing. As a result,  $\text{CRD}_{SC}$  and  $\text{sPRD}_{SR}$  profiles are almost identical, and both show the coherent shift by a factor of 16x in a shape preserving way with respect to the  $\text{PRD}_{SR}$  profile. The  $\text{CRD}_S$  profile has the effect of overlap, and the  $\text{sPRD}_S$  profile has the effect of demotion absorption. Both profiles show contraction, but the  $\text{CRD}_S$  profile shrinks more than the  $\text{sPRD}_S$  profile. The reasons are described in Section 3.2.1.

Figure 3.3(d) and Figure 3.4(d) also show the effect of intercepts in  $\text{CRD}_S$  profiles, and the effect of invalidations in  $\text{sPRD}_S$  profiles. As described in Section 2.1.1, the intercept splits intra-thread reuse windows, with the resulting CRD value depending on the intercepted location. Because intercepts can happen randomly at any location, the CRD values of intercepted data blocks can be any value between 0 and the max CRD value. In our benchmarks, because data sharing usually happens at large reuse windows, intercept tends to spread the reference counts at large RD values in  $CRD_S$  profiles. This effect is visible clearly in FFT.

Invalidations create holes in private stacks, and the consequent references to the already-invalidated blocks have infinite reuse distance. So the increasing cache misses at infinite reuse distance show the cache performance degradation due to coherence misses. Another important observation is that the holes have the same impact on  $\text{sPRD}_S$  and  $\text{sPRD}_P$  profiles, because holes reduce the depth for both shared and private data in stacks. Figure 3.5(b) summarizes the relationship between profiles for shared data.

Lastly, in our benchmarks, we find private-data profiles dominate shared-data profiles. For example, the amount of private references is 6x and 259x more than the amount of shared references in Barnes and FFT, respectively. As a result, dilation and overlap in CRD profiles along with scaling and demotion absorption in sPRD profiles determine overall shared/private cache performance.

## 3.3 Thread Interactions Analysis for Core Count Scaling

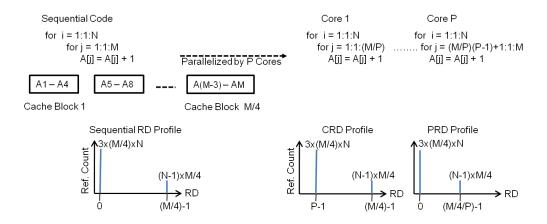

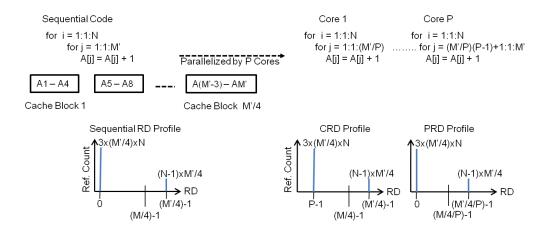

When core count increases but problem size stays fixed (*i.e.*, strong scaling), core count scaling reduces each thread's working set size. More threads also increase inter-thread interactions. Figure 3.6 depicts a simple example which parallelizes a vector operation for P cores. In the sequential program, each cache block contains four data elements, so there are a total of M/4 cache blocks. Each cache block is referenced four times (re-referenced three times) before the inner for-loop advances

Figure 3.6: A simple example showing how CRD and PRD shift with core count scaling. Each cache block contains 4 elements.

to the next cache block. The outer for-loop re-accesses each cache block with reuse distance (M/4) - 1, and there are N - 1 re-references for each block.

In the parallel program, the inner loop is partitioned into P chunks, and each core has M/P elements. For the CRD profile, the uniform interleaving causes the RD value of re-references at the inner-loop to move to P-1. However, the re-references at the outer-loop stay at the same RD value, (M/4) - 1. This is because core count scaling does not increase the total amount of global data, so the theoretical max RD value doesn't change. As a result, when core count increases, the references at small RD values move to larger RD values. However, the CRD profiles of different core counts eventually end at the same RD value.

In contrast, PRD profiles truncate as core count increases. The references at small RD values do not move due to the absence of interleaving. However, the re-references at the outer-loop move to smaller RD values due to the reduction of perthread working set size. In this example, the max RD value of the PRD profile moves from (M/4) - 1 to (M/4/P)/-1. As a result, when core count increases, the PRD profile truncates. This simple example shows the major inter-thread interactions as core count scales. In the following sections, we conduct a detailed study to understand how core count scaling impacts CRD and PRD profiles.

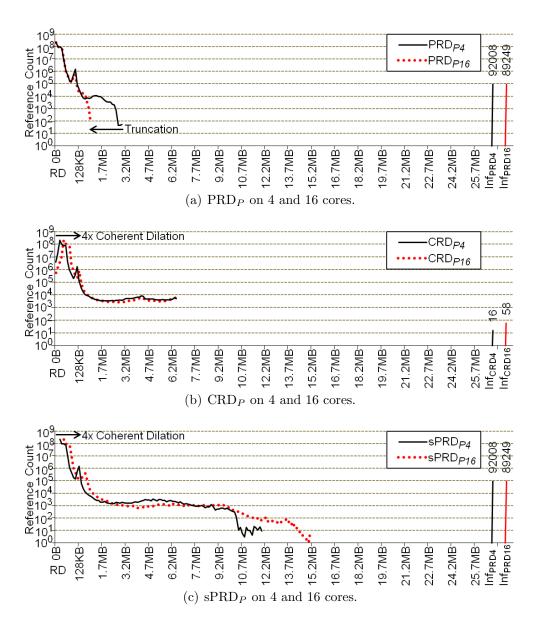

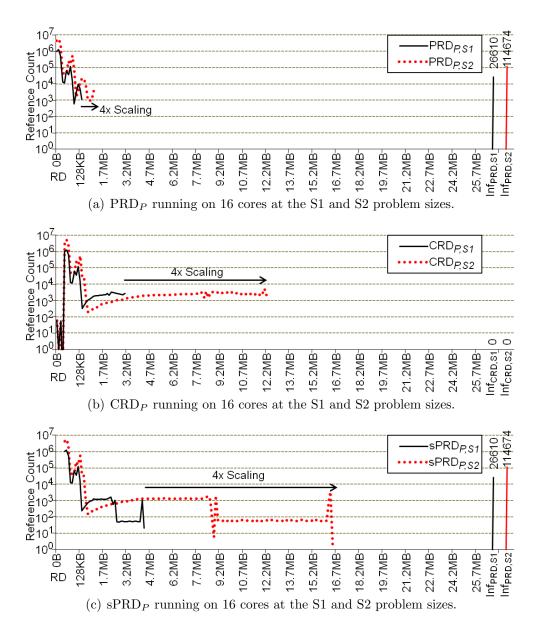

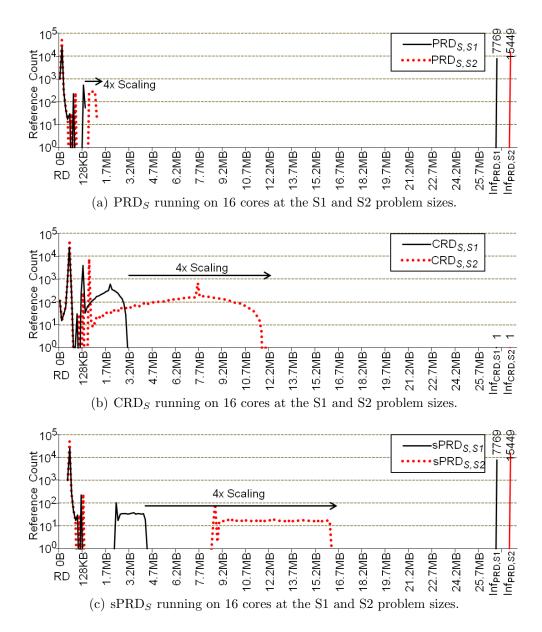

#### 3.3.1 Private-data Profiles

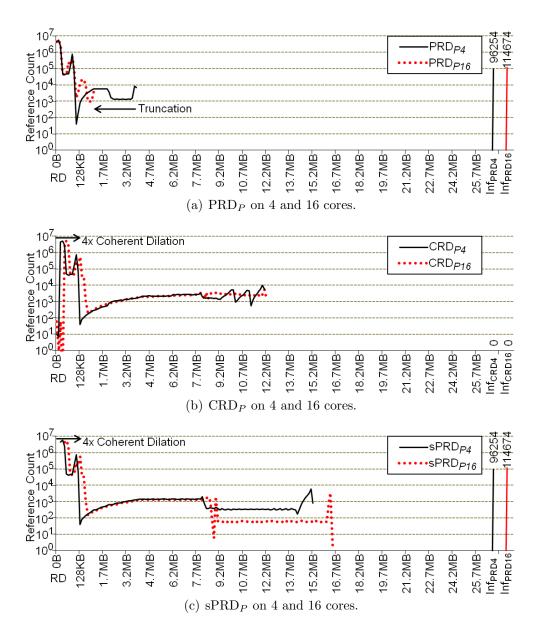

Figure 3.7 and Figure 3.8 illustrate the private-data profiles for the most important parallel region in Barnes and FFT running on 4 cores and 16 cores at the S2 problem size. First, we compare  $PRD_{P4}$  and  $PRD_{P16}$  profiles to study the perthread locality impact due to core count scaling. In Figure 3.7(a) and Figure 3.8(a),  $PRD_{P4}$  and  $PRD_{P16}$  profiles exhibit very similar shapes because threads on 4 and 16 cores execute the same code. At small RD values,  $PRD_{P4}$  and  $PRD_{P16}$  profiles are almost identical. This is because this region reflects memory references executed within contemporaneous computation. So core count scaling doesn't affect the locality. Then  $PRD_{P4}$  and  $PRD_{P16}$  profiles split at a certain RD value, and finally the  $PRD_{P16}$  profile ends earlier than the  $PRD_{P4}$  profile due to the reduction of per-thread working set size.

This truncation, along with overlapping references at large RD values, almost perfectly cancel the dilation due to core count scaling in CRD profiles, as illustrated in Figure 3.7(b) and Figure 3.8(b). Because symmetric threads are interleaved systematically, the  $\text{CRD}_{P16}$  profile is not only a coherent shift of the  $\text{PRD}_{P16}$  profile, but it is also a coherent shift of the  $\text{PRD}_{P4}$  profile and the  $\text{CRD}_{P4}$  profile. At small RD values, the  $\text{CRD}_{P16}$  profile coherently scales the  $\text{CRD}_{P4}$  profile by a factor of

Figure 3.7: Barnes' private-data locality profiles running on 4 cores and 16 cores at the S2 problem size.

Figure 3.8: FFT's private-data locality profiles running on 4 cores and 16 cores at the S2 problem size.

4x. At large RD values, shifting slows down and eventually stops due to the effects of truncation and overlap. So  $CRD_{P16}$  and  $CRD_{P4}$  profiles merge, and end at about the same RD value. This makes sense: because core count scaling does not change the amount of global data, the theoretical maximum RD value is roughly the same. This analysis shows core count scaling degrades data locality for shared caches, but its impact is limited to small capacities. We will discuss this further in Section 3.5.1.