## ABSTRACT

| Title of dissertation:    | INFORMATION POWER EFFICIENCY<br>TRADEOFFS IN MIXED SIGNAL<br>CMOS CIRCUITS       |

|---------------------------|----------------------------------------------------------------------------------|

|                           | Nicole McFarlane, Doctor of Philosophy, 2010                                     |

| Dissertation directed by: | Professor Pamela Abshire<br>Department of Electrical<br>and Computer Engineering |

Increasingly sensors for biological applications are implemented using mixed signal CMOS technologies. As feature sizes in modern technologies decrease with each generation, the power supply voltage also decreases, but the intrinsic noise level increases or remains the same. The performance of any sensor is quantified by the weakest detectable signal, and noise limits the ability of a sensor to detect the signal. In order to explore the trade-offs among incoming signal, the intrinsic physical noise of the circuit, and the available power resources, we apply basic concepts from information theory to CMOS circuits. In this work the circuits are modeled as communication channels with additive colored Gaussian noise and the signal transfer characteristics and noise properties are used to determine the classical Shannon capacity of the system. The waterfilling algorithm is applied to these circuits to obtain the information rate and the bit energy is subsequently calculated.

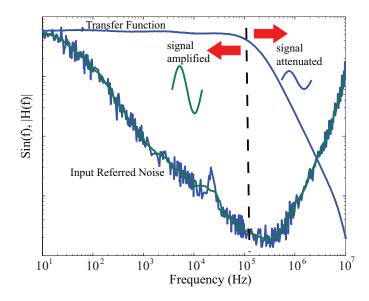

In this dissertation we restricted our attention to operational transconductance amplifiers, a basic building block for many circuits and sensors and oftentimes a major source of noise in a sensor system. It is shown that for typical amplifiers the maximum information rate occurs at bandwidths above the dominant pole of the amplifier where the intrinsic physical circuit noise is diminished, but at the same time the output signal is attenuated. Thus these techniques suggest a methodology for the optimal use of the amplifier, but in many cases it is not practical to use an amplifier in this manner, that is at frequencies above its 3dB cutoff. Further, a direct consequence of applying the classic waterfilling algorithm leads to the idea of using modulation techniques to optimize system performance by shifting signals internally to higher frequencies, providing a practical means to achieve the information rates predicted by waterfilling and at the same time maintaining the real world application of these amplifiers. In addition, the information rates and bit energy for basic CMOS amplifier configurations are studied and compared across configurations and processes. Further the additional design constraints formed by adding the information rate and the bit energy to traditional design characteristics is explored.

## INFORMATION POWER EFFICIENCY TRADEOFFS IN MIXED SIGNAL CMOS CIRCUITS

by

Nicole McFarlane

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2010

Advisory Committee: Professor Pamela Abshire, Chair/Advisor Professor Prakash Narayan Professor Martin Peckerar Professor Timothy Horiuchi Professor Peter Sandborn © Copyright by Nicole McFarlane 2010

## Acknowledgments

This work was possible only with the support of a number of people. I would like to thank my advisor Pamela Abshire for her guidance through the PhD process. My office mate for the past 2 years Marc, thanks for all the lunches and encouragements. Those who have already graduated, Som, Honghao, Peng, Eric you set the bar for the rest of us. David, Anshu, Babak, Eric, Timir thank you. I have enjoyed spending time with all of you past and present. The members of the 2006 408D group A. Banes, P. Hurtado, E. Arvelo, S. Sahand and Z. Bekka. thank you choosing to work on your project. The other committee members, Dr Narayan, Dr Peckerar, Dr Horiuchi and Dr Sandborn, thank you for taking the time to serve. My friends at Howard, Crawford, William, Tony, James, even though I have left it was like I never left. Dr Harris thank your for supporting my goals. Rhonda, Kizi thank you for letting me talk and always being there. Marcia, Angela without you I would never have made it this far. Ora, Nerle, Philo wish you were able to be here today. The rest of my friends and family, thank you. Dianne, Lester, Narissa, Dederick for knowing you are there no matter what. Bari, I look forward to life.

## Table of Contents

| Lis | List of Tables v                         |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                |

|-----|------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Lis | st of ]                                  | Figures                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | vi                                                                                             |

| 1   | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Impac<br>Appro<br>Reseau                                                                | n<br>ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $     \begin{array}{c}       1 \\       2 \\       5 \\       10 \\       11     \end{array} $ |

| 2   | Nois<br>2.1<br>2.2                       | Funda<br>2.1.1<br>2.1.2<br>2.1.3                                                        | MOS Circuits         mental Noise Concepts         Stochastic Process         Power Spectral Density         System Models         FET Noise Models         Thermal Noise                                                                                                                                                                                                                                                                                                                        | 12<br>12<br>12<br>14<br>15<br>16<br>18                                                         |

|     |                                          | 2.2.2<br>2.2.3                                                                          | Shot NoiseThermal Noise?2.2.2.1Shot Noise = Thermal Noise?2.2.2.2Gate Leakage Noise due to Shot NoiseInduced Gate Current Noise2.2.3.1A Short Discussion of Shot Noise and Thermal Noise                                                                                                                                                                                                                                                                                                         | 20<br>22<br>22<br>23                                                                           |

|     | 2.3                                      |                                                                                         | PhysicsFlicker Noise2.2.4.1Issues with Flicker Noise in the LiteratureParameter Extraction Methodology                                                                                                                                                                                                                                                                                                                                                                                           | 24<br>25<br>28<br>30                                                                           |

|     |                                          | 2.3.1                                                                                   | Extracted Noise Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32                                                                                             |

| 3   | Corr<br>3.1<br>3.2<br>3.3                | Ampli<br>Inform<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8 | ve Analysis of Amplifier Topologies         fier Configurations         nation Power Tradeoffs for Basic Topologies         Information Rate Using a First Order Model         Information Rate as Function of Bias Current         Noise Efficiency Factor         Bit Energy         Other Considerations         Experimental Measurements on Single Transistor Amplifiers         Experimental Measurements on OTAs         Information Rate of Amplifiers Fabricated in Different Processes | 34<br>34<br>37<br>39<br>47<br>48<br>50<br>53<br>54<br>55<br>70<br>71                           |

|     | J.J                                      | Unapt                                                                                   | er Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11                                                                                             |

| 4  | Trac   | leoffs in a Single Amplifier Design                                 | 74 |  |

|----|--------|---------------------------------------------------------------------|----|--|

|    | 4.1    | Design Constraints on a Simple OTA Topology                         | 74 |  |

|    | 4.2    | Tradeoffs in a Simple OTA                                           | 79 |  |

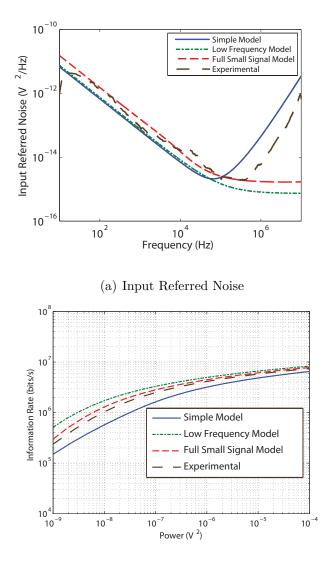

|    | 4.3    | Model Accuracy                                                      | 80 |  |

|    | 4.4    | Fitting Information Rate and Bit Energy into Current Design Method- |    |  |

|    |        | ologies                                                             | 89 |  |

|    | 4.5    | Information Rate assuming White Noise Only                          | 91 |  |

|    | 4.6    | Chapter Summary                                                     | 95 |  |

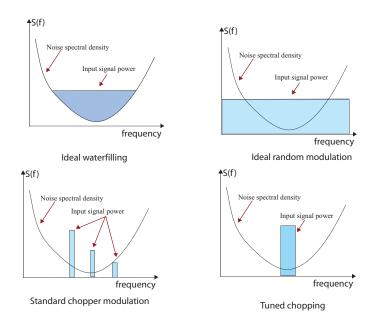

| 5  | Achi   | ieving Increased Information Rate                                   | 97 |  |

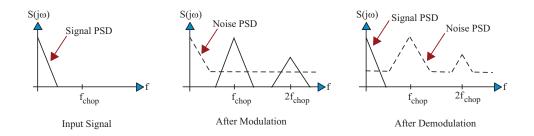

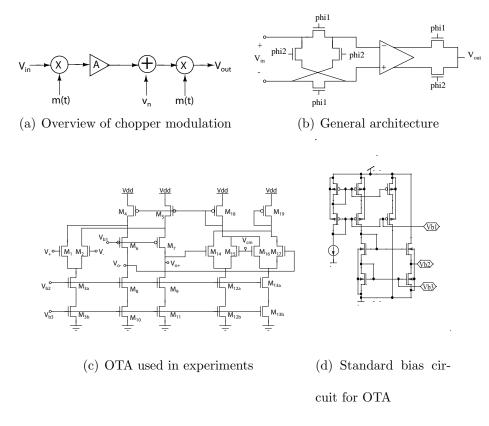

|    | 5.1    | Standard Chopper Modulation                                         | 99 |  |

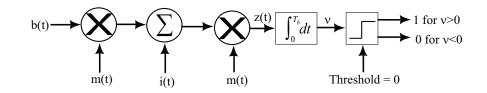

|    | 5.2    | Random Modulation                                                   | 09 |  |

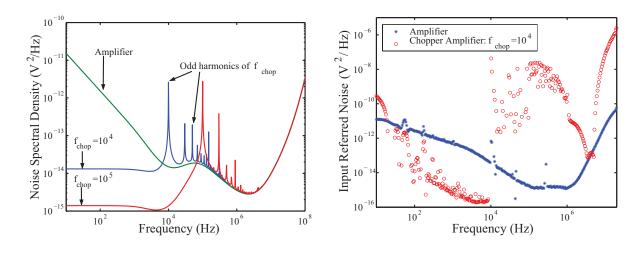

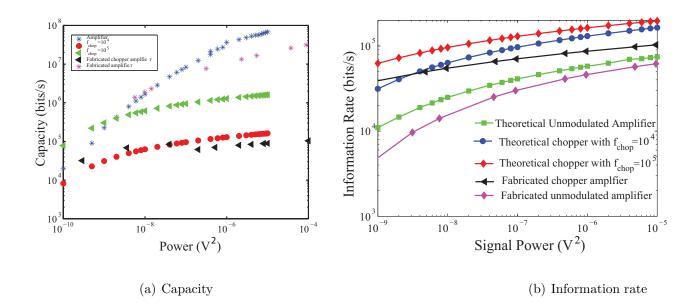

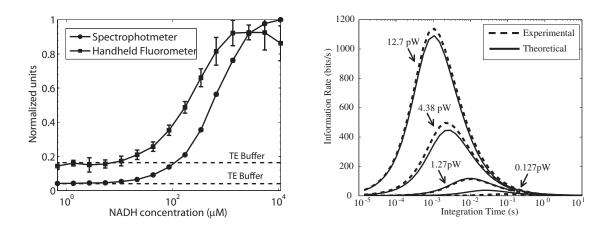

|    | 5.3    | Theoretical and Experimental Results and Discussion                 | 10 |  |

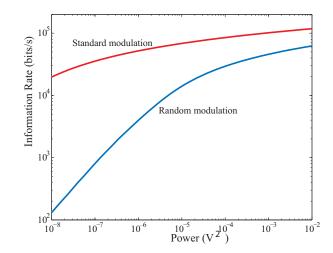

|    | 5.4    | Bit Energy of Modulation Schemes                                    | 21 |  |

|    | 5.5    | Modulation as an Optimisation Technique                             | 23 |  |

|    | 5.6    | Chapter Summary and Discussion                                      | 23 |  |

| 6  | Con    | clusions 1                                                          | 29 |  |

| Bi | bliogr | Bibliography 133                                                    |    |  |

# List of Tables

| 3.1 | Summary of Amplifier Configurations                 | 37 |

|-----|-----------------------------------------------------|----|

| 3.2 | Noise Efficiency Factor of different configurations | 50 |

| 4.1 | Summary of Trends with Design Parameters            | 92 |

# List of Figures

| 1.1  | MOSFET transistor                                                                                | 6  |

|------|--------------------------------------------------------------------------------------------------|----|

| 1.2  | Gaussian channel                                                                                 | 8  |

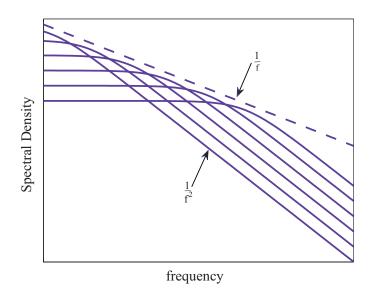

| 1.3  | Waterfilling in the spectral domain                                                              | 9  |

| 1.4  | Communication System                                                                             | 10 |

| 2.1  | Transformations used to determine equivalent noise                                               | 16 |

| 2.2  | MOSFET Noise Sources and Models                                                                  | 17 |

| 2.3  | Channel is modeled as linear resistor for thermal noise calculations                             | 18 |

| 2.4  | Sources of shot noise.                                                                           | 21 |

| 2.5  | Induced Gate Current Noise.                                                                      | 23 |

| 2.6  | Flicker noise caused by traps at the Si-Oxide interface. $\ldots$ . $\ldots$ .                   | 25 |

| 2.7  | Random telegraph signal: change in current over time                                             | 26 |

| 2.8  | Superposition of all RTS gives rise to 1/f spectrum                                              | 27 |

| 2.9  | Noise parameter extraction setup.                                                                | 31 |

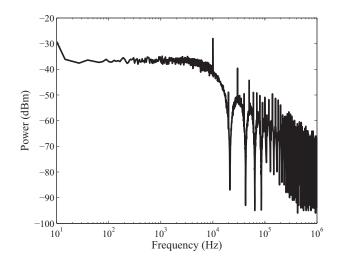

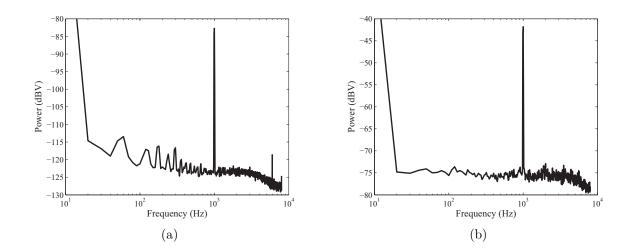

| 2.10 | Experimental noise of $6/2$ NMOS transistor $\ldots \ldots \ldots \ldots \ldots$                 | 33 |

| 2.11 | Experimental noise of 25/5 NMOS transistor                                                       | 33 |

| 3.1  | Amplifier configurations                                                                         | 38 |

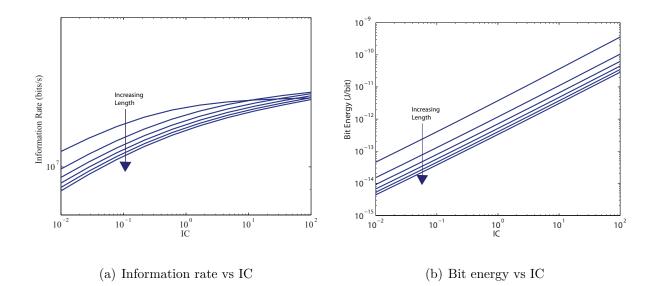

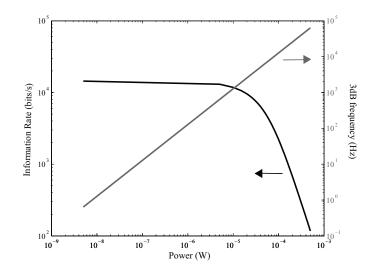

| 3.2  | Input referred noise spectral density and information rate assuming first order characteristics. | 45 |

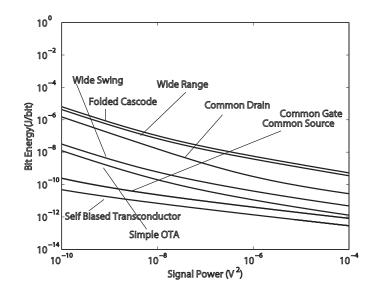

| 3.3  | Theoretical information rate for power level of $10^{-4}$ and $10^{-10}$                         | 46 |

| 3.4  | Theoretical input referred noise assuming $W/L=25/5$ and using the simple model                  | 48 |

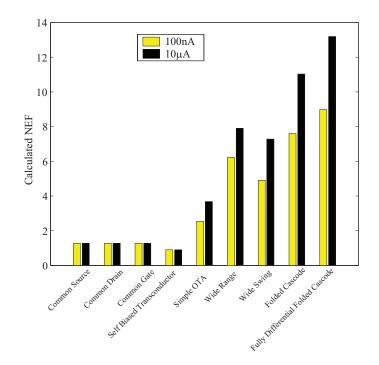

| 3.5  | Noise efficiency factor of OTAs                                                                  | 51 |

| 3.6  | Bit energy assuming first order characteristics of amplifiers from Table 3.1                     | 52 |

| 3.7  | Theoretical bit energy for for two bias currents at a power level of $10^{-4}$ and $10^{-10}$ .                  | 53 |

|------|------------------------------------------------------------------------------------------------------------------|----|

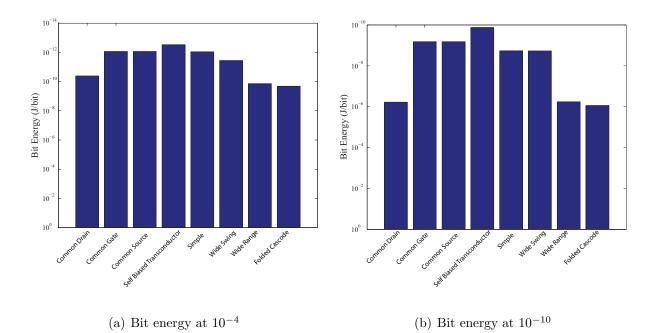

| 3.8  | Experimental noise and transfer functions for single transistor con-<br>figurations                              | 56 |

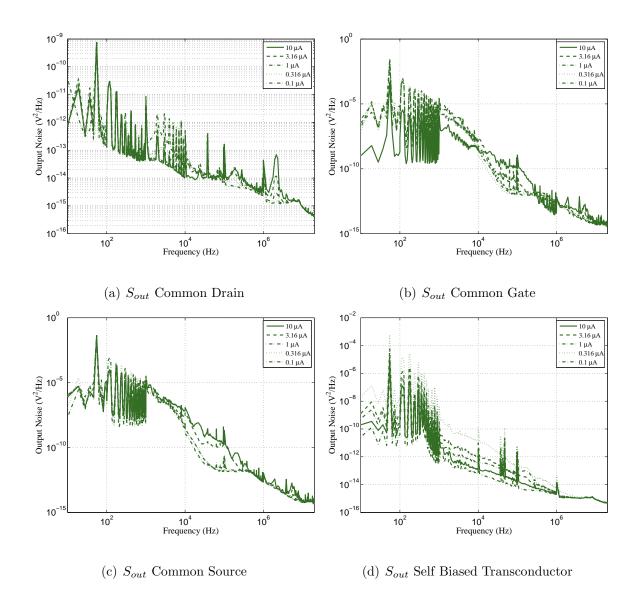

| 3.9  | Measured output noise for different single transistor topologies at varying bias conditions.                     | 57 |

| 3.10 | Transfer function for single transistor topologies at varying bias con-<br>ditions.                              | 58 |

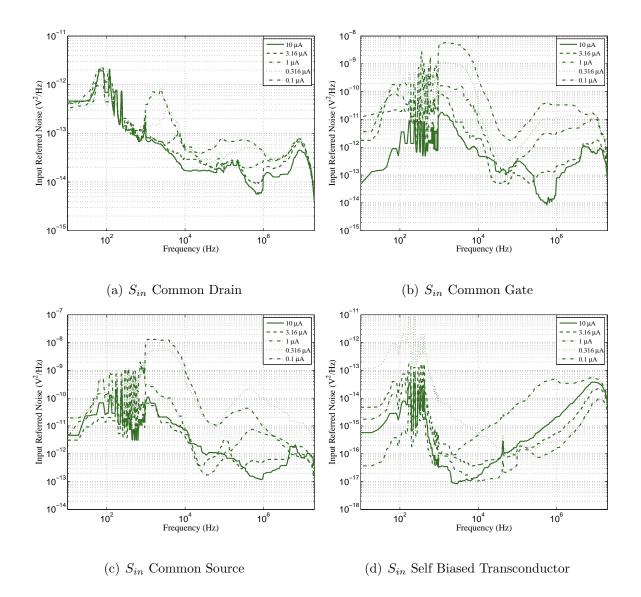

| 3.11 | Experimentally derived input referred noise for single transistor topolo-<br>gies at varying bias current.       | 59 |

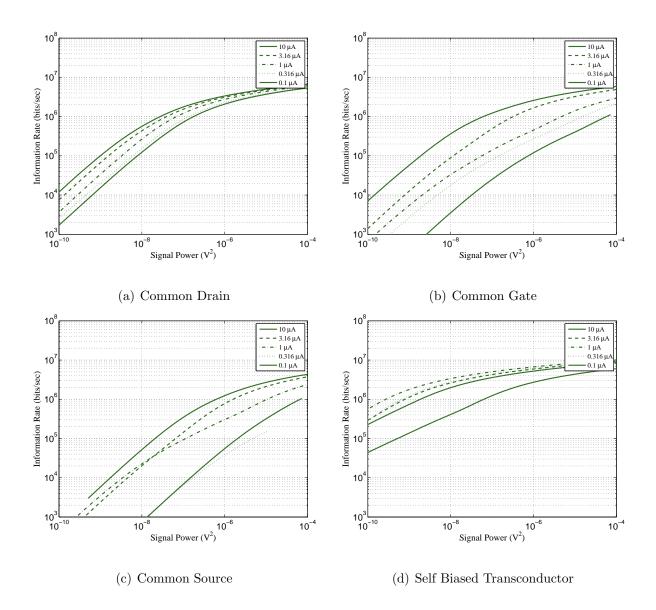

| 3.12 | Experimentally derived information rate at different bias conditions for single transistor configurations.       | 60 |

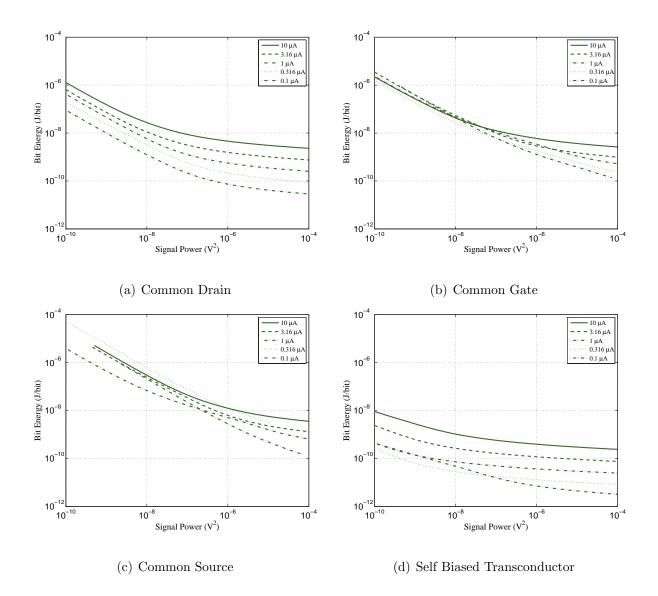

| 3.13 | Experimentally derived bit energy at different bias conditions for sin-<br>gle transistor configurations.        | 61 |

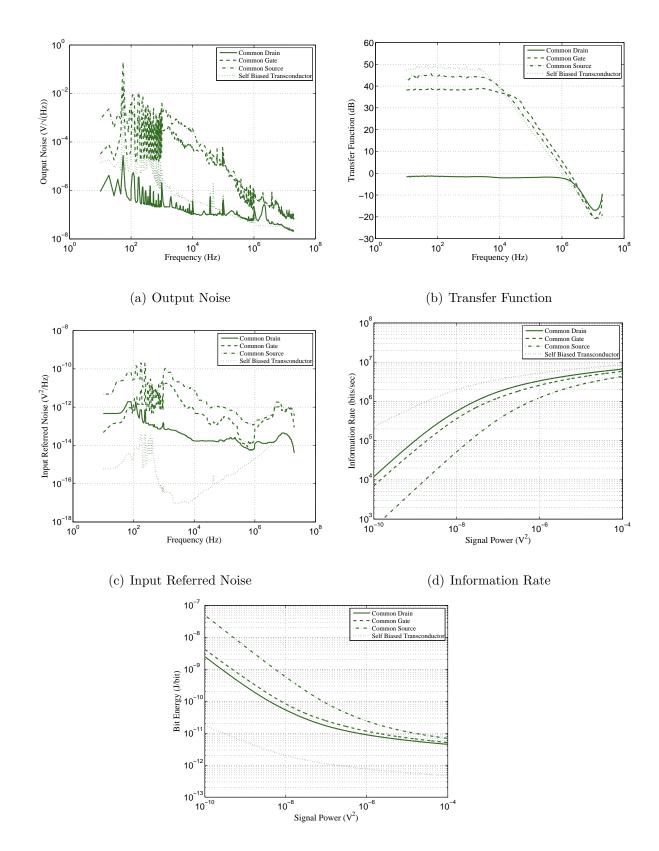

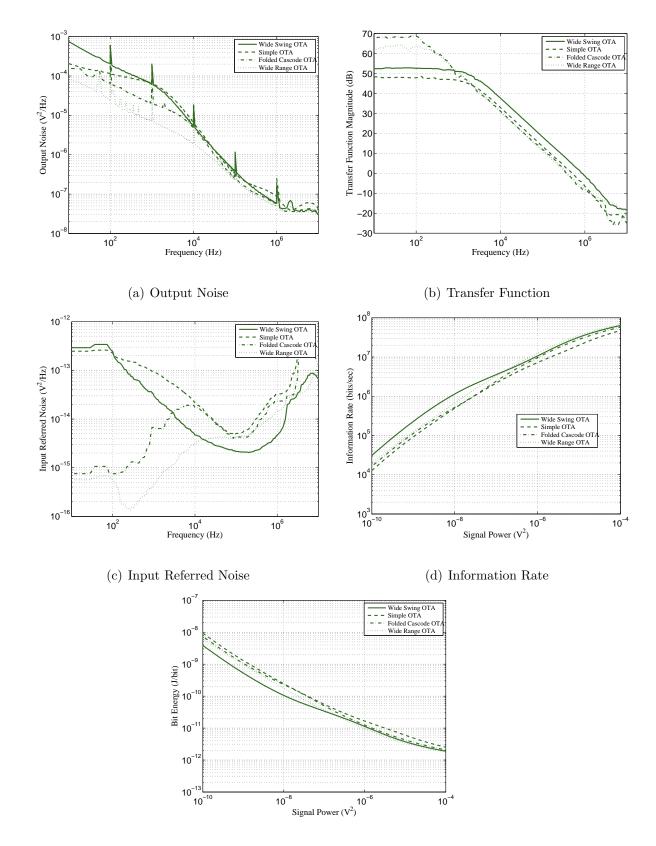

| 3.14 | Experimental noise and transfer functions for all four OTAs with bias current of 10 $\mu$ A.                     | 63 |

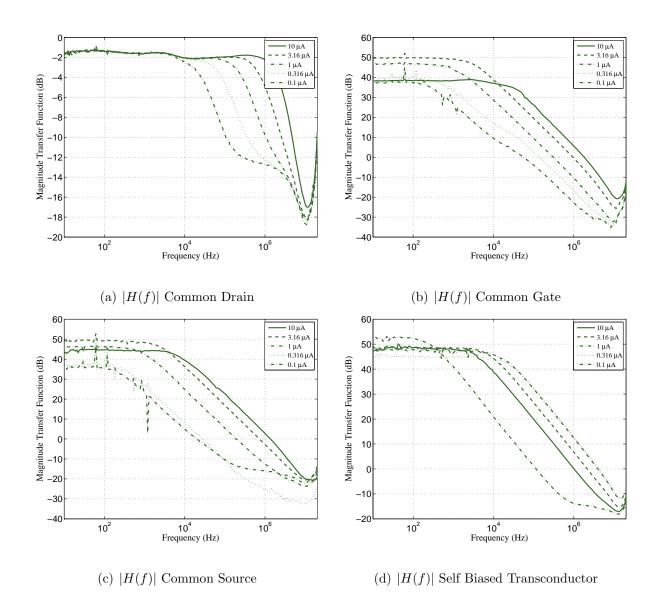

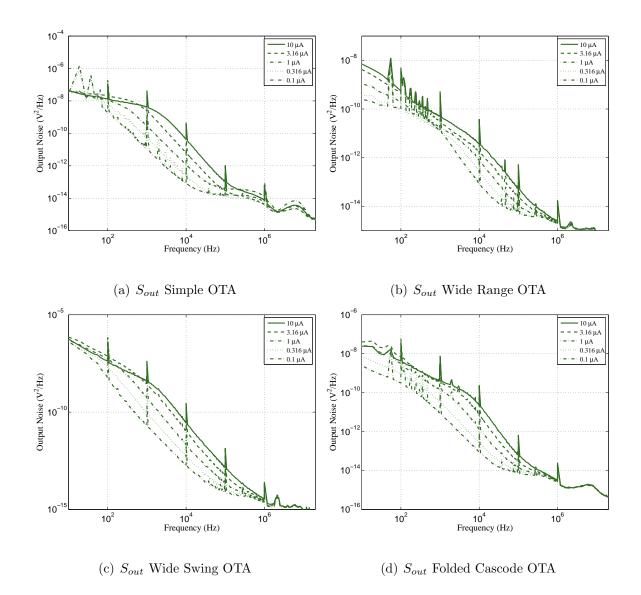

| 3.15 | Measured output noise for different OTA topologies at varying bias conditions.                                   | 64 |

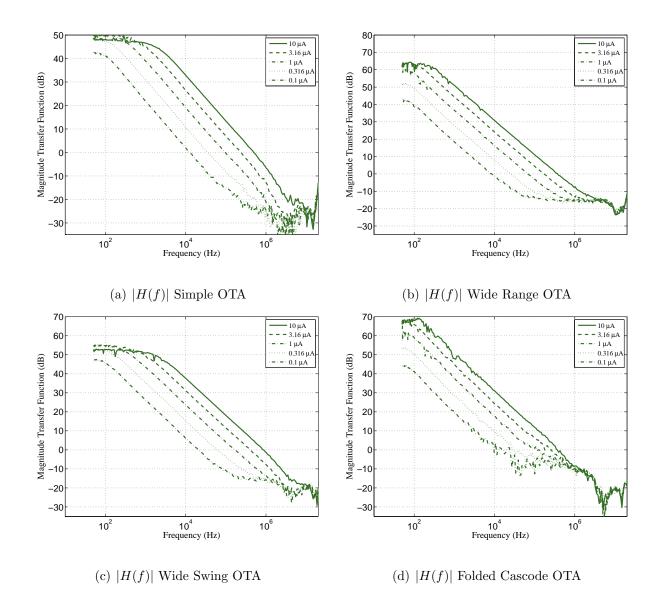

| 3.16 | Transfer function for OTA topologies at varying bias conditions                                                  | 65 |

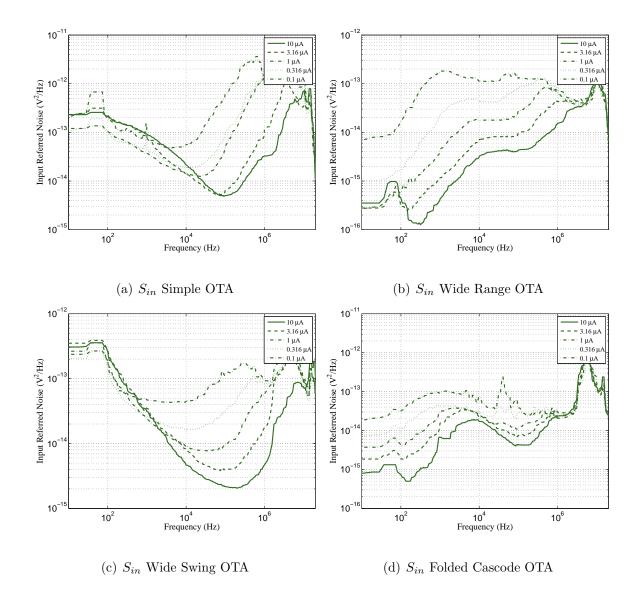

| 3.17 | Experimentally derived input referred noise for OTA topologies at varying bias current.                          | 66 |

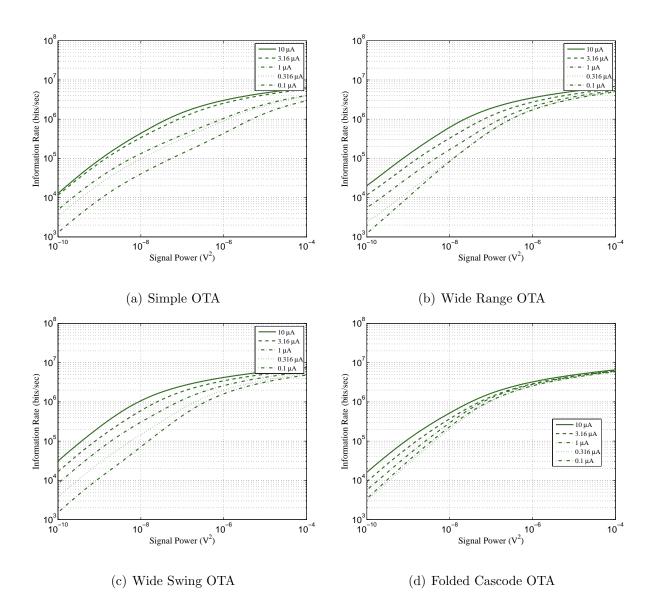

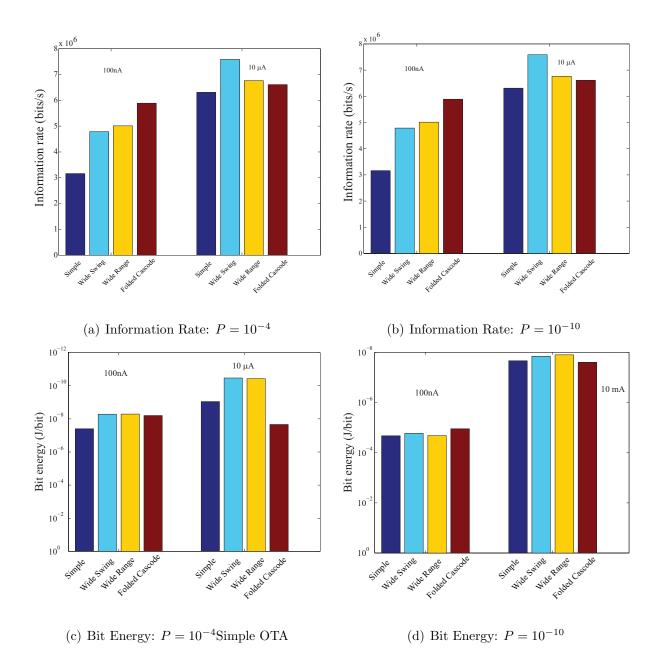

| 3.18 | Experimentally derived information rate at different bias conditions.                                            | 67 |

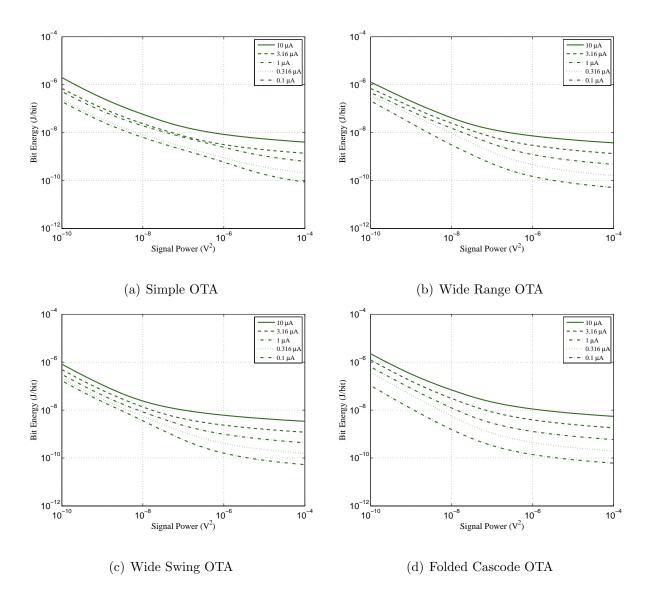

| 3.19 | Experimentally derived bit energy at different bias conditions                                                   | 68 |

| 3.20 | Experimentally derived information rate for bias currents 10 $\mu$ A and 100 $\mu$ A for the OTA configurations. | 69 |

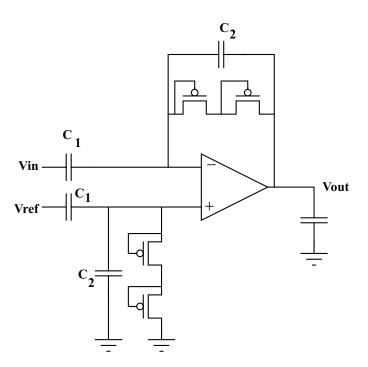

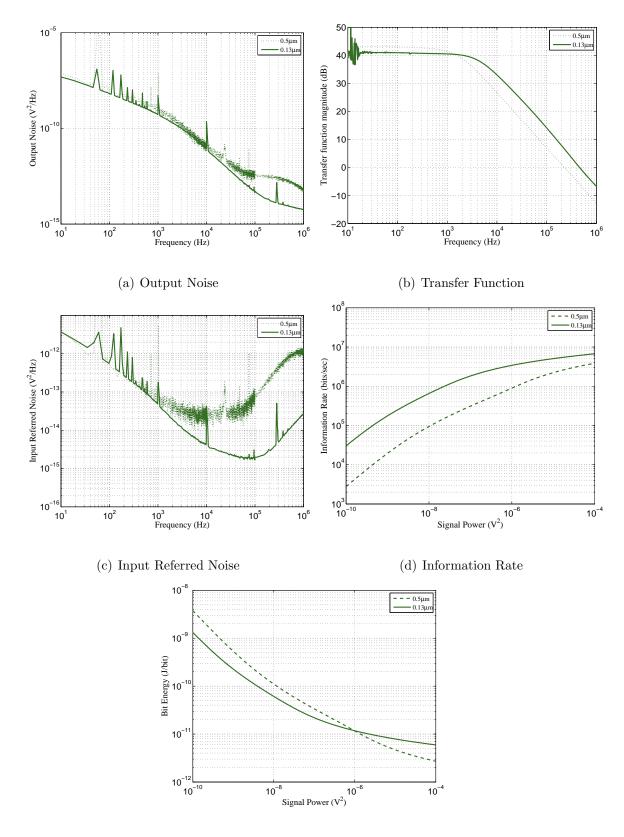

| 3.21 | Bioamplifier based on Harrison design.                                                                           | 71 |

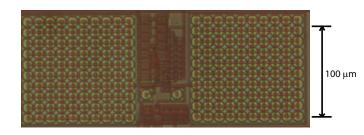

| 3.22 | Experimental 0.5 $\mu$ m and 0.13 $\mu$ m process. Sizes are different but characteristics are the same.         | 72 |

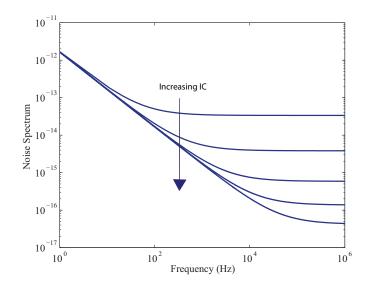

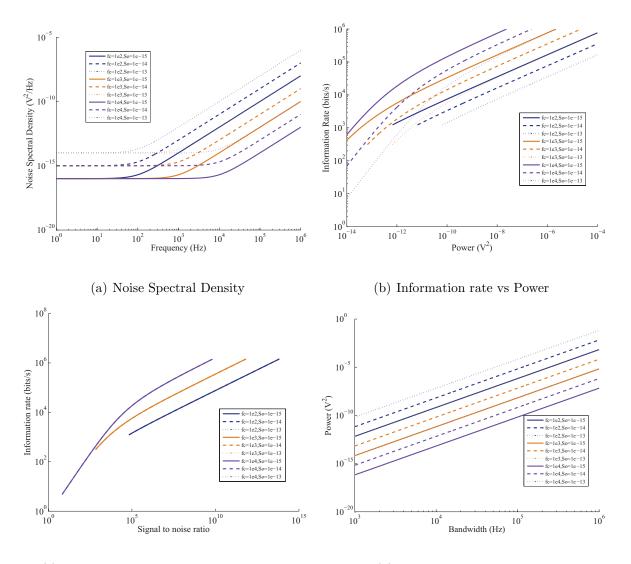

| 4.1  | Input Referred Noise $(Sin(f))$ for different inversion coefficients                                             | 80 |

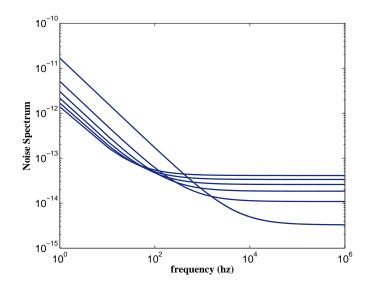

| 4.2  | Input Referred Noise $(Sin(f))$ for different transistor lengths                                                 | 81 |

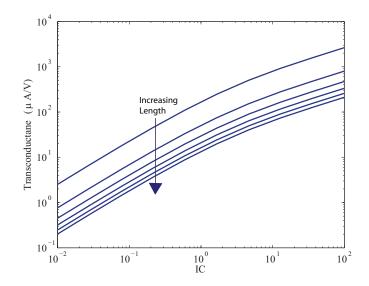

| 4.3 Transconductance for different inversion coefficients                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

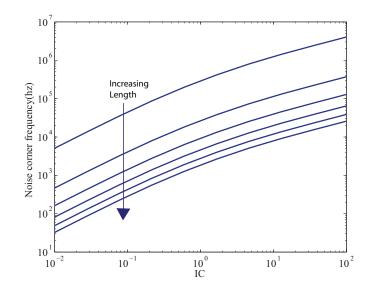

| 4.4 Noise corner frequency for different inversion coefficients                                                                               |

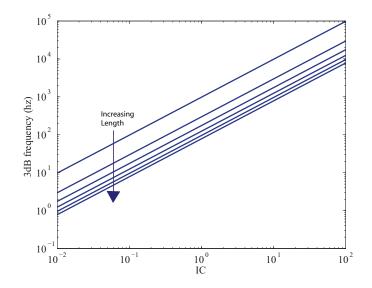

| 4.5 3dB frequency for different inversion coefficients                                                                                        |

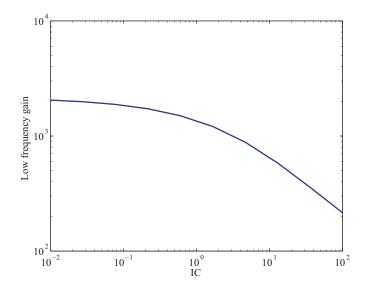

| 4.6 Low frequency gain for different inversion coefficients                                                                                   |

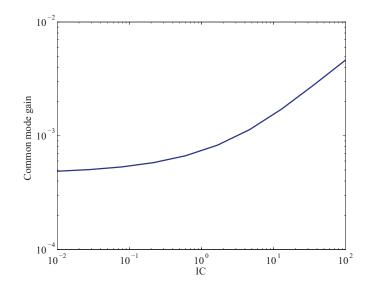

| 4.7 Common mode gain for different inversion coefficients                                                                                     |

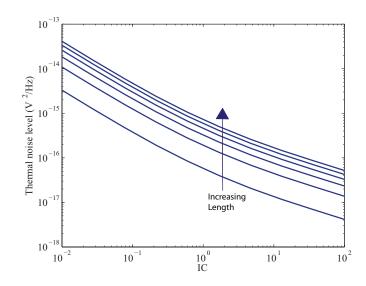

| 4.8 Thermal noise level for different inversion coeffciencts                                                                                  |

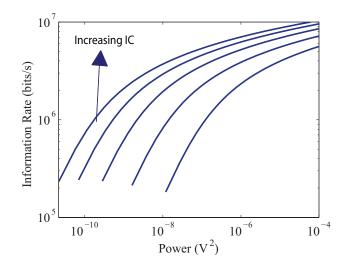

| 4.9 Information rate for different inversion coefficients                                                                                     |

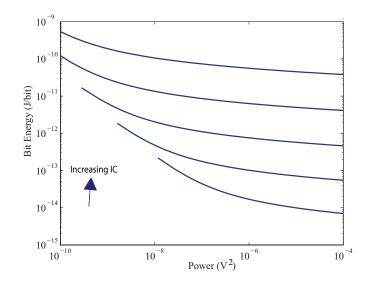

| 4.10 Bit Energy for different inversion coefficients                                                                                          |

| 4.11 Information rate and bit energy vs IC for a power level of $10^{-4}$ 85                                                                  |

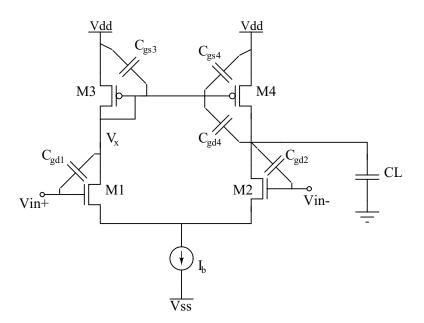

| 4.12 Simple OTA showing the parasitic capacitancees                                                                                           |

| 4.13 Input referred noise and information rate for the simple OTA $\ldots$ 90                                                                 |

| 4.14 Theoretical results for information rate with white noise only with low pass filter                                                      |

| 4.15 Theoretical results for information rate and 3dB frequency vs System<br>Power with white noise only with low pass filter                 |

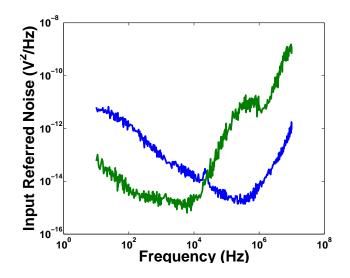

| 5.1 Input referred noise for two different OTAs                                                                                               |

| 5.2 Typical input referred noise and transfer function                                                                                        |

| 5.3 Basic principle of chopper modulation                                                                                                     |

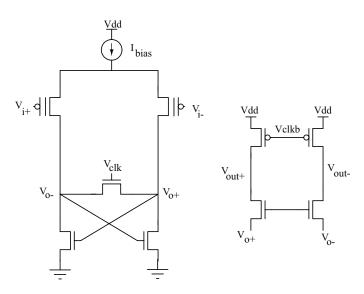

| 5.4 Chopper modulated amplifier                                                                                                               |

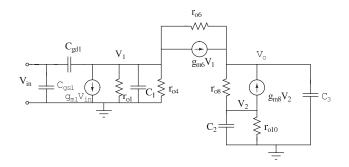

| 5.5 $$ Simplified small signal model for the fully differential folded cascode . 104 $$                                                       |

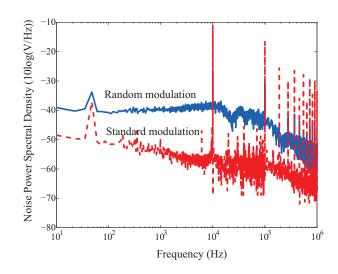

| 5.6 Theoretical and experimental input referred noise of OTA and chop-<br>per modulated OTA                                                   |

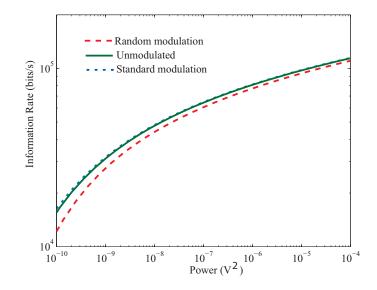

| 5.7 Capacity and information rate chopper modulated and unmodulated folded cascode OTA                                                        |

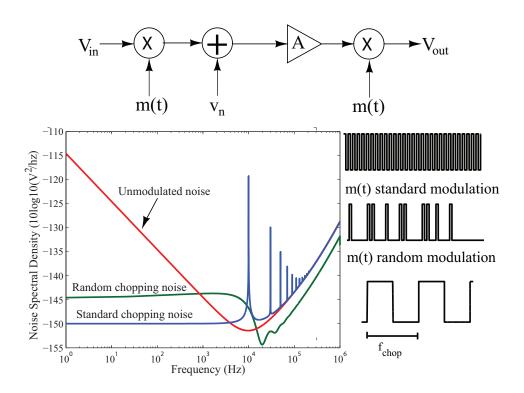

| 5.8 Overall system diagram, showing random and regular modulation signals, along with the input-referred noise for each modulation scheme.111 |

| 5.9  | Input-referred noise for unmodulated,) Standard chopping and ran-<br>dom chopping schemes |

|------|-------------------------------------------------------------------------------------------|

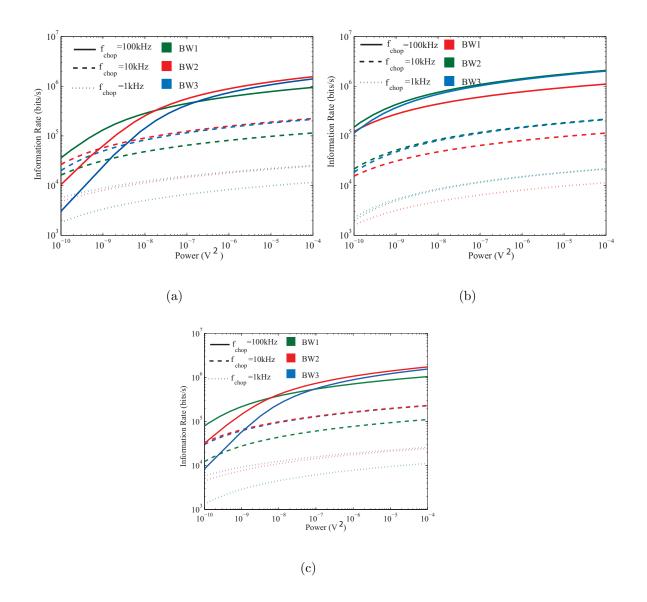

| 5.10 | Information rate for unmodulated, standard chopping and random chopping schemes           |

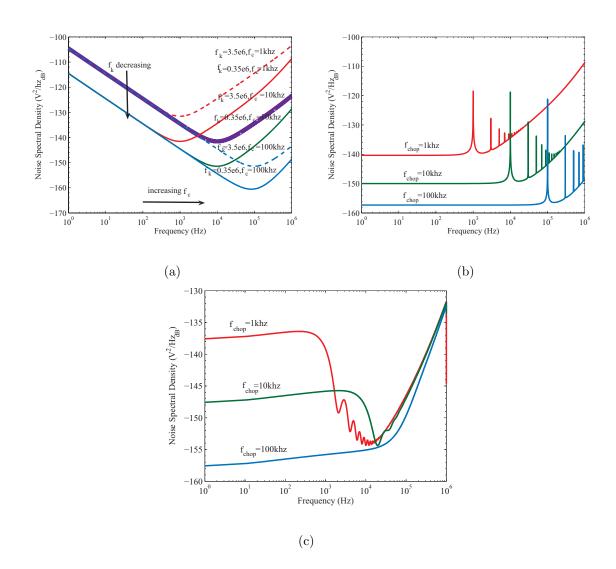

| 5.11 | Information rate for the noise models shown in Figure 5.9(a) $\ldots$ 114                 |

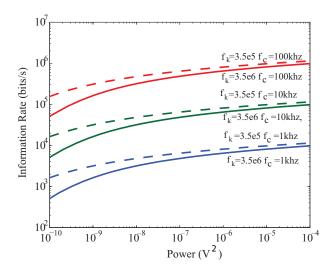

| 5.12 | Theoretical information rate of amplifier using different modulation schemes              |

| 5.13 | Measured output noise of circuit                                                          |

| 5.14 | Experimentally derived capacity of noise                                                  |

| 5.15 | Random number generator used in experiments                                               |

| 5.16 | Experimentally measured clock spectrum with frequency of 10 kHz. $$ . 120 $$              |

| 5.17 | Photomicrograph of implemented chopper bioamp                                             |

| 5.18 | Different methods of frquency allocation of the input signal 122                          |

| 5.19 | Ideal Spread Spectrum System                                                              |

| 5.20 | Signal spectrum                                                                           |

| 6.1  | Information rate for a active pixel sensor                                                |

## Chapter 1

## Introduction

## 1.1 Motivation

In recent years there has been a substantial amount of research into designing biosensors for particular applications. These sensors may include electrical activity sensors, such as to amplify weak extracellular signals of cells, capacitive sensors to monitor the motility and health of cells or fluorescence sensors which can be used for a wide variety of applications in biology including imaging and analyte detection and quantification. These sensors have general applicability in drug screening, explosives detection and clinical diagnosis just to name a few [1–8].

In these applications, however, one of the greatest concerns is with being able to detect signals that are very small. This implies that the power level of the input signal is an important factor to be considered. In addition each biosensor, particularly if implemented using integrated circuits, has a substantial intrinsic physical noise associated with it in addition to the environmental noise. This may change from process to process and is very much dependent on physical design parameters.

Finally many of these biosensors are meant to be used in portable and/or labon-a-chip applications. In these types of applications the available power resources are typically extremely limited. There therefore exists the need to consider these three factors (input signal level, noise and available power resources) when designing biosensors. Studying the trade-offs between these three will give valuable insight into creating or improving design methodologies for more efficient sensors. To accomplish this the information rate was used to give a measure of trade-offs involved with the input signal power level and the physical noise of the channel, where the channel is the portion of the sensor that accomplishes the transduction of the signal of interest into a form that can be further analyzed or stored. Additionally the concept of bit energy, which is defined as the ratio of the system power to the information rate, is employed to incorporate a measure of the available power resources.

## 1.2 Impact of this work in Mixed Signal Design

In today's world many portable and lab-on-chip biosensors are implemented using a CMOS technology platform due to the low cost and the maturity of the technology. The trend in current CMOS processes is to scale down in size to get more transistors in a given area. This comes with a corresponding decrease in the power supply, but the intrinsic noise remains the same. This causes an increase in the overall signal to noise ratio. Understanding the trade-offs between the input signal of interest, the available power and the noise is the driving force of this work. When designing an application specific system, designers have many options to choose from to optimize a particular design. These options are typically specific to the application of the system, for example an amplifier which amplifies neural signal recordings has a different set of optimization goals than an imager whose task it is to perform signal processing on a captured image. A typical design cycle progresses in such a way that a few parameters must be chosen at the outset, and these parameters are then used to find other parameters and system characteristics. The design is then simulated and manually adjusted to obtain what one hopes is the optimum design.

In pure digital design there are many optimization tools available which allow one to optimize for power, area and other factors. There also exists many synthesis tools which can aid the designer in the circuit design. No such tools currently exist in general analog design (at least for a wide range of applications), and designing analog and mixed signal circuits tend to be somewhat of an art rather than rigorous implementations of specific design rules that are can be repeatedly followed. There is also very little understanding of how to optimize for trade offs in mixed signal design, for example in OTA design one's goal may be to achieve the maximum open loop gain, while at the same time attempting to minimize noise, and also ensuring that the amplifier is stable. But while CMRR, CMR, PSRR and other constraints are usually calculated they are usually calculated after the design has already been chosen.

In order to bring the analog and mixed signal world closer to having a similar set of design tools as in pure digital design, this dissertation explores how to use principles of information theory and apply them to mixed signal circuits in order to optimize the energy efficiency of the design. As stated before, the mixed signal VLSI designer has many options and constraints while creating a design. Often they must critically consider power consumption and noise characteristics of the intended system. To date there is no standard figure of merit that considers an optimum balance among input signal power level, power consumed by the circuit, and intrinsic noise characteristics, especially when considering different processes and topologies. It has been recently proposed that by applying the principles of information theory circuits can be treated as Gaussian channels with additive noise and a measure of signal power to noise level efficiency can be computed. By further considering the cost of using the circuit (power consumption) we can obtain a figure of merit which encompasses both noise sources and power considerations [9, 10].

As fabrication processes allow the use of smaller and smaller transistors, intrinsic MOSFET noise becomes one of the most important limiting factors for circuit design. This can be especially important in sensor design. For any circuit, and for amplifiers in particular, noise places important limits on the input signal. This can be especially important in neural amplifier applications where the sensed input is in the  $\mu V$  range. In all circuits there are two classes of noise sources present. First there is noise due to physical processes such as thermal, shot and flicker noise, the second is the noise due to process variations. Both of these have an effect on the circuit. This work focuses on studying a specific class of amplifiers known as operational transconductance amplifiers (OTA) that are typical subcomponents used in sensor design.

Traditional analog design considerations include gain, bandwidth and stability. However optimizations of most of these factors are typically applied in a somewhat ad hoc manner. This mean that there is some need for a rigorous methodology in mixed signal design.

Traditional design considerations for an OTA usually derive from wanting it

to be low noise and high open loop gain. There is not usually an area consideration for an OTA since it is usually relatively small. If feedback is used, however, then area can become a limiting factor for certain applications as passive components require significant area resources in most integrated circuit technologies.

In this work we consider the introduction of additional design considerations which are intended to allow the design to achieve higher energy efficiency. Capacity, measured in bits/s, is well known in the information theory field. In the following section a background summary on information capacity is given and the rationale for applying it to analog circuit design is explained.

## 1.3 Approach

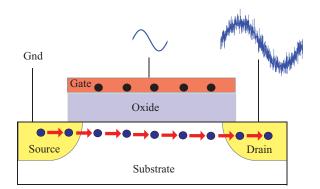

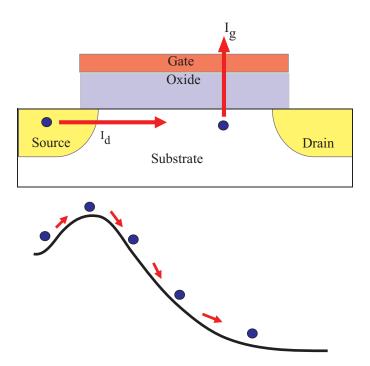

Physically a transistor takes an input signal and through physical mechanisms of potential fields and current flow it gives rise to an output signal that is corrupted by the intrinsic noise of the transistor (figure 1.1). A passive noiseless resistor is assumed at the drain terminal. Assuming the input signal is noiseless, a MOSFET generates a field induced current between its source and drain terminals that can then be read either as a voltage (as shown at the drain terminal in the figure 1.1) or a current. The current in the channel is not a perfect replica of the input signal voltage as there will be an additional unwanted random signal due to extra charges being randomly *added* or *subtracted* to it due to the noise processes related to the operation of the device. This noise appears as fluctuations in the current through the device or fluctuation of the voltage or charge on a node. The parameters that determine

Figure 1.1: MOSFET transistor: output signal is corrupted by the physical noise sources which randomly affect the flow of charges from the source to drain terminals

the noise are derived from the physical structure. Therefore a reasonable model is that a transistor can be considered to be an information processing transformation channel in the presence of noise. [9]. This idea can be extended to circuits that are made up of multiple transistors such as amplifiers, analog to digital converters (ADC), digital to analog converters (DAC) and other practical systems. In many cases the noise sources are due to fundamental physical effects such as thermal, shot and 1/f noise in continuous time channels such as an amplifier (see chapter 2), or the noise may be due to sources such as to switching and quantization effects in ADCs and DACs. Stationary noise may also be introduced because of process variations such as in an imager where fixed pattern noise exists. In this work the focus is on amplifiers used in sensor circuits which physically transform an input voltage to an amplified representation of itself. An interpretation of the maximum information rate in this context then is that it quantifies the ability of the channel to transduce the incoming input signal efficiently. The mathematical framework to quantify information transmission in a channel has already been developed in the information theory field by Shannon [11, 12]. Entropy (similar in some ways to the entropy defined in classical thermodynamics taught in college physics and chemistry) is a measure of the average uncertainty in a random variable and is given by ([13])

$$h(X) = -\int_{S} f(x)\log_2 f(x)dx \tag{1.1}$$

where f(x) is a probability distribution function and S is the support set of the random variable X. X in this case represents the input signal to a sensor. Mutual information is defined as the reduction in uncertainty of one random variable due to another random variable, and is a measure of dependence between the two variables.

$$I(X;Y) = h(X) - h(X/Y)$$

(1.2)

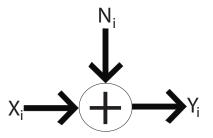

A communication channel can be defined as an entity which takes an input and provides a correlated output which is probabilistically dependent on the input. The channel may be corrupted by noise, which can itself be a probabilistic process. A Gaussian channel is one which has an output that is corrupted by a noise source that is Gaussian in nature. A Gaussian channel is described by

$$Y_i = X_i + N_i \tag{1.3}$$

where X, Y and N are the input, output and noise of the channel, at time i, respectively (figure 1.2). The noise is considered to be independent of the input signal and is drawn i.i.d. (independently and identically distributed) from a Gaussian

Figure 1.2: Gaussian channel: the output signal Y is composed of the original signal X as well as the noise associated with the channel.

distribution. The capacity of the channel is found by maximizing the mutual information which leads to an unlimited capacity when no constraints are specified. However under an average signal power constraint, P, the capacity of a Gaussian channel [11–13]

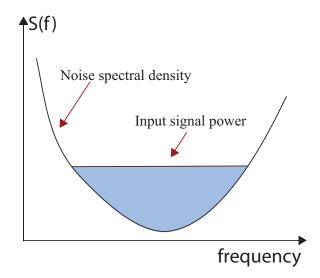

$$C = \frac{1}{2} \int \log_2 \left( 1 + \frac{(\nu - N(f))^+}{N(f)} \right) df$$

(1.4)

where

$$P = \int (\nu - N(f))^{+} df$$

(1.5)

where  $\nu$  and N(f) are a constant and noise spectrum respectively. This solution is known as waterfilling, since the input signal power (assumed to be a Gaussian process) is allocated to spectral areas where the noise spectral density is lowest (figure 1.3).

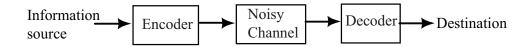

Information theory has always been closely associated with digital circuits where bits are a natural unit of measure as there are only two states possible for any input or output signal. Within that framework the usual objective is to encode the input signal to achieve maximum information rate and to decode the signal after it has been transmitted through the channel (figure 1.4). Usual methods to

Figure 1.3: Waterfilling in the spectral domain: For maximum information rate the input signal power is placed at frequencies where the noise is lowest first before spilling over to the parts of the spectrum where the noise is higher.

incorporate this into the design of the digital communication system is to determine the best or most appropriate coding scheme to transmit a sequence of ones and zeroes over a noisy channel. In this case the noise is caused by clock jitter, thermal noise and interfering signals (crosstalk). In the analysis in this work we consider a continuous time signal where, for the purposes of the theoretical calculation, the signal is a sampled representation of itself. In this dissertation the implications of information theory and waterfilling in particular is taken as a guide to formulating a methodology for amplifier design and this work is not approached as a source coding or channel coding problem, but rather a problem of how to design a better circuit.

In this dissertation information rate is considered as an analogy of the circuit as a communication channel and information rates are determined because logically these sensory circuits essentially transmit information to the user about the input

Figure 1.4: A communications channel from the standard information theoretic point of view.

signal. In today's world of lab-on-chip applications the cost of transmitting this information is at a premium due to the weak signals and low power requirement of many sensors. In this sense the cost of using the channel is the energy to transmit the information (signal) over the channel. It is also worth noting that in the traditional sense capacity is the rate beyond which there exists some error in the received signal as it is impossible to transmit above this rate with arbitrarily small error. The actual capacity may not be achievable.

### 1.4 Research Contributions of this work

The capacity is defined as the maximum rate at which a channel can transmit information with arbitrarily small error. Information rate has been previously analyzed for silicon photoreceptors and systems with feedback [10, 14]. However these results only assumed white noise processes, thermal noise for transistors or shot noise for photodiodes. In this work the implications of the maximum information rate and bit energy on analog circuits is more fully investigated by considering colored Gaussian noise sources in addition to the white noise sources. In addition, in order to better aid the mixed signal designer, the information efficiency trade-offs in analog and mixed signal circuits using the information rate and bit energy are explored by studying different circuit topologies. We also focus on trade-offs for an example circuit in order to understand how they can affect existing design methodologies. Finally, the implications of the approach, including the suggestion for using chopper modulation to achieve information rate, are outlined.

## 1.5 Dissertation Outline

Background material on the physical sources of noise and their accompanying models for MOSFETs is outlined in chapter 2. Using simple models, a comparative analysis of the information rate and the energy required to transmit one bit of information with basic operational transconductance amplifiers was performed and experimentally verified in chapter 3. The information rate for circuits fabricated in two different technologies was also explored. Chapter 4 explores the accuracy of the models used and determines how the information rate and bit energy for amplifiers fit within an existing design methodology. As mentioned above, the natural conclusion of applying waterfilling to OTAs is chopper modulation, a technique that is explored in chapter 5. Finally, chapter 6 concludes this work with a summary of the findings and their possible impact on the world of analog design.

## Chapter 2

## Noise in CMOS Circuits

## 2.1 Fundamental Noise Concepts

Noise is, in general, an undesirable random signal. Various sources of noise may be present in the output signals and these noise signals can severely distort the desired output signals. Before going into detail about specific noise models some fundamentals about stochastic processes are first briefly reviewed.

## 2.1.1 Stochastic Process

As noise is usually random, it cannot be analyzed using standard signal processing techniques such as the Fourier transform and spectrograms. The analysis and theory of noise are dealt with using the concept of stochastic processes. A stochastic process is one in which a time function is assigned to every outcome in the sample space. The ensemble of all possible functions that can be realized is a stochastic process [15].

To start assume there is a stochastic process defined by X(t). This stochastic process is considered stationary if it has time independent statistical properties and is considered to be wide sense stationary if

$$E[X(t)] = constant$$

(2.1)

$$E[X(t)X(t+\tau)] = R_{XX}(\tau)$$

(2.2)

where  $R_{XX}$  is the autocorrelation function which is the expectation of the product of two random variables at times  $t_1 = t$  and  $t_2 = t + \tau$ . If a process is wide sense stationary and satisfies

$$A[X(t)] = E[X(t)]$$

(2.3)

$$A[X(t)X(t+\tau)] = R_{XX}(\tau)$$

(2.4)

where

$$A[X(t)] = \lim_{T \to \infty} \frac{1}{2T} \int_{-T}^{T} x(t) dt$$

(2.5)

then it is an ergodic process. If a process is ergodic, then it is possible to interpret what the parameters of the process mean in a physical sense. If a random signal can be modeled as an ergodic process, then its mean (E[X]) is the DC component of the signal, the squared mean value is related to the DC component's power and the mean squared value is related to the signal's average power and the variance is proportional to the AC power. The variance is the difference between the squared mean and the mean squared that is  $\sigma_X^2 = E[X^2] - (E[X])^2$ .

Most noise processes are modeled as Gaussian processes. A Gaussian random variable has a probability density function given by

$$f_X(x) = \frac{1}{\sigma_X \sqrt{2\pi}} \exp\left[-\frac{\left(x - \overline{X}\right)^2}{2\sigma_X^2}\right].$$

(2.6)

where  $\sigma^2$  is the variance and  $\overline{X}$  is the mean. Gaussian stochastic processes are completely described by their mean and auto-correlation function, that is no additional parameters are needed to completely specify the process.

## 2.1.2 Power Spectral Density

Noise is a random signal, therefore the Fourier transform does not exist. The power spectrum of the process is instead used to represent information about the frequency domain characteristics. The power spectrum is the Fourier transform of the autocorrelation function  $(R_{XX})$  which is defined as

$$R_{XX}(t,t+\tau) = E[X(t)X(t+\tau)]$$

(2.7)

$$S_{XX}(\omega) = \int_{-\infty}^{\infty} R_{XX}(\tau) \exp(-j\omega\tau) d\tau \qquad (2.8)$$

This implies that the integral of  $S_{XX}$  over  $\omega$  is the expectation of the square of the random variable or the power of the process. It is then simple to move from the time domain to the frequency domain. If a process is modulated in the time domain this corresponds to a convolution in the frequency domain. If the process undergoes linear time invariant filtering this corresponds to multiplying the spectrum by the squared magnitude of the transfer function [15]. Use of the spectral density makes evaluation of noise in circuits using small signal analysis (for transistor circuits) possible. It allows placement of sources (either voltage or current) into the circuit to represent the noise source. The noise seen at various points in the circuit can then be evaluated using standard circuit techniques [15, 16].

## 2.1.3 System Models

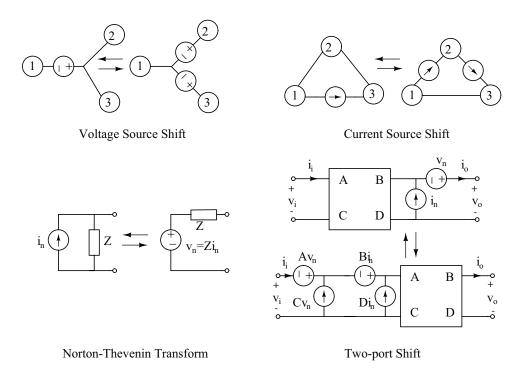

Any noisy circuit may be modeled as a noise free multi-port network that is connected to independent noise sources that represent various noise sources from different components. They may also be equivalently modeled as a noise free circuit with equivalent sources at the input or the output. There are four basic transforms that may be used manipulate each separate noise source within a circuit and turn it into the equivalent source at another node within the circuit (figure 2.1). The first way is a voltage source shift in which the noise voltage sources are moved through the circuit without changing the KVL (Kirchoff's Voltage Law) equations. The second way is a current source shift where the noise current sources are moved through the circuit without changing the KCL (Kirchoff's Current Law) equations. The third method is a Norton-Thevenin transformation where the noise current source is changed into a noise voltage source or the noise voltage source is transformed into a noise current source. The fourth method involves two-port shifts where the output noise and current sources are transformed into input current and noise sources via the equations

$$\left(\begin{array}{c} v_{it} \\ i_{it} \end{array}\right) = \left(\begin{array}{c} A & B \\ C & D \end{array}\right) \left(\begin{array}{c} v_{ot} \\ i_{ot} \end{array}\right)$$

where the noise voltages are as shown in figure 2.1. Note that the voltage and current noise sources are fully correlated [17]. It should also be noted that introducing feedback does not affect the equivalent input or output noise of the amplifier (assuming feedback elements are perfectly noiseless), thus noise generators may be moved outside of a feedback loop [18]. Noise is a fluctuation that can either be positive or

Figure 2.1: Transformations used to determine equivalent noise

negative, therefore when drawing as a current or voltage source in a circuit diagram any direction may be chosen for the source. Typically the direction is chosen that makes any subsequent calculations or manipulations easier.

## 2.2 MOSFET Noise Models

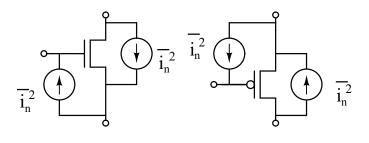

There are four types main sources of noise in MOSFETs: flicker noise, thermal noise, gate leakage noise and shot noise. We consider each of these sources in detail in the following sections. In this work only flicker and thermal noise are considered to be dominant, and both are modeled as a noise current source across the source and drain (figure 2.2). As CMOS devices scale down we expect these noise sources to increase, thus noise considerations are critical to any design.

(b) Small Signal Model

Figure 2.2: MOSFET Noise Sources. (a)NMOS and PMOS transistors showing noise current sources between the drain and source and into the gate (b)Flicker and thermal noise are modeled as current sources between the drain and the source. Gate current noise is modeled as a current source from the gate to the channel. Note that direction is shown on these figures to identify as the sources as current sources, the arrow may be drawn in the direction most suitable for the calculation.

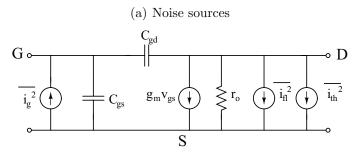

Figure 2.3: Channel is modeled as linear resistor for thermal noise calculations.

## 2.2.1 Thermal Noise

Thermal noise is present in a multitude of devices and is due to random thermal motion of electrons in the channel as depicted in figure 2.3. It is unaffected by direct current, as thermal electron velocities are much larger than drift current velocities.

A thermal noise model along with experimental results for conductors was first developed in papers by Nyquist and Johnson in 1928 [19, 20]. This model has since been applied to MOSFETs by assuming a linear channel resistance (figure 2.3) given by the transconductance,  $g_m$ . Van der Ziel derives the thermal noise for FETs as [21]

$$S_{I_D}(0) = \gamma 4kTg_{d0} \tag{2.9}$$

where  $\gamma$  is related to the drain and gate voltage, and thus the mode of operation of the device.  $\gamma$  has a value of 2/3 in the saturation region, and  $g_{d0}$  is the ratio of the conductance per unit length at the source (at zero drain bias) and the length of the device. For a MOSFET in above threshold saturation  $g_{d0} = g_m$  and the thermal noise is more commonly written as:

$$S_{I_D}(0) = \gamma 4kTg_m \tag{2.10}$$

where

$$g_m = \frac{\mu W C_{ox}}{L} \left( V_{gs} - V_{th} \right).$$

(2.11)

Equation (2.10) is the noise at zero frequency, but is expected to be accurate up to relatively high frequencies. In weak inversion the value of  $\gamma$  is usually assumed to be 1/2. Van der Ziel's derivation for thermal noise at weak inversion arrives, after some manipulations, at the following expression

$$S_{I_d}(f) = 2qI_{sat}(1 + exp(-\beta V_d))$$

(2.12)

which is the accepted form of a shot noise model for  $I_{sat}$ . Sarpeshkar also makes the apparent connection between shot and thermal noise in subthreshold operation, however there is no doubt that the noise process is thermal in nature [22]. It was shown by Coram and Wyatt that the extended Nyquist-Johnson model is only thermodynamically valid for operating regions where the resistor is linear [23]. The form of the thermal noise as shot noise developed for subthreshold operation is thermodynamically valid and may thus acceptable for use. In saturation clearly  $g_m$ is nonlinear and depends on the gate voltage, however for small ranges of the gate voltage it can be assumed that the transconductance does not change much. Thus equation (2.10) is widely used in practice for transistors operating in the saturation region despite the fact that it is inconsistent with thermodynamic principles. At best (2.10) is a bound on the thermal noise of the transistor. In recent years thermal noise models have been improved, mainly for RF design where thermal noise is the most important noise source. Experiments have shown that the noise given by equation (2.10) is smaller than that experimentally measured in submicron devices [24]. It has been shown that previous models use a carrier temperature model that is inconsistent with the mobility model, leading to a wrong value for  $\gamma$  (hot electron effects) [24].

It has been assumed in most works that only the term  $\gamma$  changes in subthreshold operation, where it is assumed to be 1/2. However a more accurate thermal noise model for subthreshold is

$$S_{I_d}(f) = \frac{kT}{2\kappa} \tag{2.13}$$

where  $\kappa$  is the subtreshold slope [25]. Note that all these thermal noise equations are actually derived under equilibrium conditions.

## 2.2.2 Shot Noise

Shot noise arises each time current flows across a potential barrier, therefore there are a few possible sources for shot noise in a MOSFET, the source to drain current across the p-n junction in subthreshold, the current across the p-n junction to the substrate and the gate current in all regions of operation (figure 2.4). There is no shot noise for the source to drain current under strong inversion as the potential barrier which the current flows across is decreased. All shot noise is related to the direct current flow across the barrier and at any time instant the current can be thought of as comprising a number of random independent pulses. A current pulse

Figure 2.4: Sources of shot noise.

at any time  $\tau_k$  can be written as

$$X(t) = \sum_{k=-\infty}^{\infty} h(t+\tau_k).$$

(2.14)

For the drain current this leads to a noise spectral density of

$$S_{I_d} = 2qI_d \tag{2.15}$$

where the amplitude of this noise current has a Gaussian distribution.

The substrate current is typically assumed to be negligible and therefore this source of shot noise is ignored.

#### 2.2.2.1 Shot Noise = Thermal Noise?

It has been proposed that in the subthreshold region that shot and thermal noise, traditionally thought to be separate processes, are actually the same process [22]. This was primarily achieved through a mathematical manipulation that assumes linearity of the conductance and that Einstein's relationship holds. This is not necessarily true and there is some debate about the validity of this approach. One method to prove or disprove this result would be to perform noise measurements at low temperatures in an attempt to separate the contributions due to thermal and shot noise. However the actual case may be that what we call shot noise and thermal noise are actually limiting cases for a more general noise mechanism with high temperature causing the thermal contribution to dominate and low temperature causing the shot noise to dominate. If the transmission of carriers is treated as a quantum mechanical phenomenon, it can be shown that both noise terms are limiting cases of the same physical model [21,22,26–28]. Therefore in this work shot noise is ignored as a source of significant MOSFET drain current noise.

## 2.2.2.2 Gate Leakage Noise due to Shot Noise

The shot noise due to gate leakage current can be written as

$$S_{I_q} = 2qI_g \tag{2.16}$$

Since  $I_g$  is typically very small, this term is usually insignificant, and is not considered in most calculations. The noise source is represented in the model as a noise current source at the gate of the transistor.

Figure 2.5: Induced Gate Current Noise.

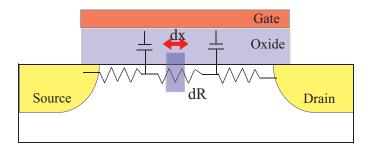

## 2.2.3 Induced Gate Current Noise

The thermal noise in the channel induces fluctuations in the gate-channel voltage at arbitrary points along the channel. There exists a distributed RC network along the channel where the distributed resistance is the channel itself and there is a capacitance between the gate and the channel  $(C_{gs})$  (figure 2.5) [18, 21]. This gives rise to a corresponding gate current noise that is correlated with the channel thermal noise and is given by (for long channel transistors)

$$S_{I_g} = \frac{16}{15} kT \omega^2 C_{gs}^2 \tag{2.17}$$

where  $C_{gs} = 2/3C_{ox}WL$ . The correlation factor between the induced gate noise and the thermal noise is 0.395 [18, 21]. For short channel transistors the noise is increased due to hot electrons (this is true for thermal noise as well). This noise source is more important at higher frequencies and for the purposes of this work it is ignored.

#### 2.2.3.1 A Short Discussion of Shot Noise and Thermal Noise Physics

Shot noise and thermal noise in conductors were first referenced in papers by Johnson, Nyquist and Schottky [19, 20, 29]. Callegaro derives expressions for both thermal and shot noise [27]. Fundamentally thermal noise is typically understood to be fluctuations in the position of the charged carriers. This uncertainty in position gives rise to fluctuations around the mean of the current (voltage) measured. Shot noise on the other hand is related to the quantization of the carriers and thus the uncertainty is related to the exact energy of the carriers. This is therefor related to the number of carriers which contribute the direct current. As such both thermal and shot noise are classically thought to arise from two different physical process and are usually considered to be independent. Based on the models for the two noise sources at absolute zero (or as close as one can get to it) there should be almost zero thermal noise, but the noise due to shot noise should still exists as long as there is a current flow. In addition as the temperature decreases the shot noise should remain the same. Note however that this explanation assumes that the device current is completely independent of temperature. It is also clear that the temperature will have some effect on the amount of uncertainty in the energy states. It is nevertheless widely accepted that one should not count both shot and thermal noise at the same time for MOSFETs. In addition in some quantum mechanical treatments both noise sources (thermal and shot) are attributed to the same physical mechanism [26,30,31].

Figure 2.6: Flicker noise caused by traps at the Si-Oxide interface.

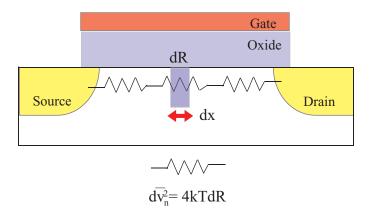

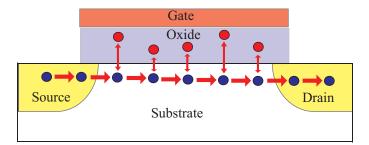

## 2.2.4 Flicker Noise

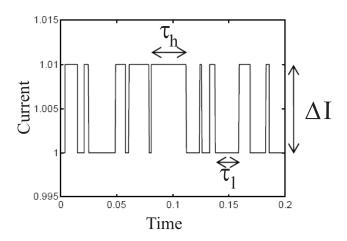

Flicker noise can be observed in many systems. This includes but is not limited to transistors, traffic flow rate, nerve membrane voltages and loudness and pitch of music. It is thus considered by some researchers to be ubiquitous [32]. It is the dominant noise source in transistors up to relatively high frequencies (process dependent). The most predominant theory on flicker noise holds that it is a superposition of several random telegraph signals (discrete modulation of the source to drain channel conductance, RTS) which are caused by single inversion carriers at the silicon - oxide interface being trapped and emitted from the interface traps (figure 2.6). This trapping-detrapping process results in fluctuations in the number of mobile carriers. Along with the carrier number fluctuation there is an associated channel mobility fluctuation due to the traps themselves being Couloumbic scattering sites. Thus there is an associated fluctuation in the channel mobility. A single RTS is shown in figure 2.7; the times between the high and low current states are exponentially distributed, that is the switching is a Poisson process. By evaluating the autocorrelation function it is found that each RTS fluctuation has a Lorentzian

Figure 2.7: Random telegraph signal: change in current over time.

power spectral density. Superimposing a number of these RTS's gives rise to a 1/f spectrum (figure 2.8). The trapping-detrapping process depends on the operating region of the transistor and can occur by thermally activated processes and tunneling. If an exponential relationship between the capture and release rates and the depth of the trap in the oxide is assumed and the traps are assumed to be uniformly distributed (spatially and energy wise), then the spectral density of the oxide traps is [33, 34]

$$S_{N\prime_{ot}} = \frac{N_{ot}}{WL} \frac{1}{f} \tag{2.18}$$

where  $N'_{ot}$  is the number of occupied traps, L and W are the length and width of the gate respectively and  $N_{ot}$  is the density of oxide traps per unit area. Under the assumption that the inversion charge and the gate voltage are linearly related for all operating regions, a physical model for flicker noise can be obtained and is given

Figure 2.8: Superposition of all RTS gives rise to 1/f spectrum.

by [35, 36]

$$S_{I_d} = \begin{cases} \frac{q^2}{C_{ox}^2} \left(\frac{I_d}{V_g - V_t}\right)^2 \frac{N_{ot}}{WL} \frac{1}{f}, & \text{strong inversion, linear} \\ \frac{q^2}{C_{ox}} \frac{N_{ot}}{L^2} \frac{I_d}{f}, & \text{strong inversion, saturation} \\ \frac{C_{inv}^2}{(C_{ox} + C_d)^4} \frac{q^4}{(kT)}^2 I_d^2 \frac{N_{ot}}{WLf}, & \text{weak inversion, below threshold} \end{cases}$$

(2.19)

The above equations can be fitted to a generic semi-empirical form given by

$$S_{I_d} = \frac{K_f I_d^{A_f}}{C_{ox}^2 W L f^{E_f}}$$

(2.20)

where  $K_f$  is a constant that varies depending on the region of operation. However, for each operating region of the transistor, simple spice models can be derived,

$$S_{vg} = \begin{cases} \frac{K_f I_d}{C_{ox}^2 L_{eff}^2 f}, & \text{strong inversion, saturation} \\ \frac{K_f I_d}{C_{ox}^2 W L f}, & \text{strong inversion, triode} \\ \frac{K_f I_d^2}{C_{ox}^2 W L f^{E_f}}, & \text{subthreshold} \end{cases}$$

(2.21)

where  $K_f$  is a process dependent parameter that is voltage dependent since it reflects the density of oxide traps.  $A_f$  and  $E_f$  are experimentally determined process parameters which usually have a value of approximately 1. These are the simplest models that an analog designer can use and are generally considered to be extremely oversimplified; however they provide a bound on the expected noise of any circuit. Another simple model commonly used in practice, assumes the voltage noise source is independent of the bias current [18]

$$S_v = \frac{K}{WLC_{ox}f} \tag{2.22}$$

where K is a process dependent parameter.

More complex models are available (specifically the BSIM 3.3 or 4.0 model) which contains 4 different parameters which must be fitted experimentally. The equations given above are usually used for hand calculations and in most SPICE programs (HSPICE, PSPICE, TSPICE), although most implementations require the user to manually change the noise model as appropriate to the region of operation.

## 2.2.4.1 Issues with Flicker Noise in the Literature

While the description described in the previous section is adequate for most designers, one should also be aware of the some of the controversy and misconceptions that surround flicker noise. One of the first questions asked is: "what is the flicker noise at zero frequency?" or "what is it's cutoff frequency?" since the integral of 1/f from zero to some frequency results in an infinite power. However this is easily resolved by considering that zero frequency means infinite time and hence infinite power, and that zero frequency does not really exist mathematically. Also the autocorrelation function of flicker noise is constant, which implies that flicker noise arises from a process with time independent memory which is associated with the long occupation time constants of the interface traps [32, 37, 38].

The physical cause of flicker noise was also a subject for much controversy in the past, as it was thought that it could be caused by mobility fluctuations or carrier number fluctuations. It is now generally accepted that it is a fluctuation in the number of carriers, with each fluctuation having a Lorentzian spectra, which then gives rise to a mobility fluctuation. As already stated, the models given in the previous section are simplified models useful for hand calculations. The BSIM4 models do a slightly more accurate modeling of the noise parameters across different regions of operations but are still relatively inaccurate when compared to experimental data. This is because they do not take into account the bias history of the device which can affect the present noise data [33, 36, 39–43].

Another important question, particularly for this work given the approach outlined in Chapter 1, is whether flicker noise is Gaussian and also if it is stationary. Surprisingly, these are not always addressed in discussions about flicker noise. A survey of the literature shows that there are conflicting views. Some experimental results have shown that the amplitude distribution of flicker noise is Gaussian, however there are some view that oppose this. Brophy found that the process was stationary [44], while Brophy and Greenstein found it to be nonstationary [45]. Stoisiek and Wolf found that the statistical properties of flicker noise were consistent with the assumption of stationarity [46]. If the spectrum for 1/f noise (band pass filtered) is [47]

$$S_X = \begin{cases} \frac{C}{2\pi\omega} & \omega_1 < \omega < \omega_2 \\ 0 & otherwise \end{cases}$$

then the autocorrelation function is

$$R_X = \frac{C}{2\pi} (C_i(\omega_2 \tau) - C_i(\omega_1 \tau)]$$

(2.23)

$$C_i(Z) = \int_{-\infty}^{Z} \frac{\cos y}{y} dy$$

(2.24)

This leads to

$$R_X(\tau \to 0) = \frac{C}{2\pi} ln \frac{f_2}{f_1}$$

(2.25)

This is independent of the time and is thus stationary. However, as mentioned previously, there is some question as to whether this low frequency actually exists. Flicker noise has been measured down to  $10^{-6.3}$ s ([37]) and the spectrum keeps increasing. If this lower cutoff does not exist then the process is not stationary. Since this cutoff cannot be experimentally measured (such measurements would take an infinitely long time) [37], it may or may not exist. Therefore flicker noise may or may not be stationary. It is therefore assumed for this work that flicker noise is both stationary and Gaussian in nature.

#### 2.3 Noise Parameter Extraction Methodology

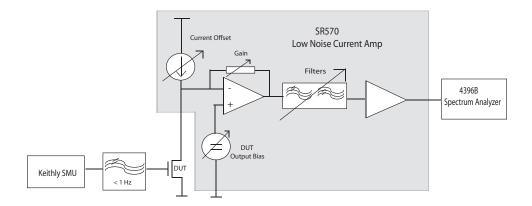

The process dependent parameters for flicker noise  $(K_f, A_f, E_f)$  were experimentally measured and extracted for a commercial  $0.5\mu m$  3-metal, 2-poly process. Figure 2.9 shows the experimental setup [48,49]. Measurements were performed in a Faraday cage to suppress environmental noise. The gate was biased using a battery

Figure 2.9: Noise parameter extraction setup.

and voltage regulator to provide a constant noiseless bias gate voltage. The SR570 is a low noise current preamplifier that can provide a bias current to the transistor, it also has the advantage of being battery powered. Keithley 236 source measure units were used to experimentally extract  $g_m$  and other parameters at varying bias currents. The output of the current preamp was connected to the input of the spectrum analyzer. Since the SR570 is a programmable transresistance amplifier, it allows the measurement of the noise voltage which can be easily converted back to the current noise. By using a log-log plot the parameter  $K_f$  can be extracted. Alternatively the noise voltage at the drain can be measured using a resistor to set the transistor drain current. In this configuration the noise of the resistor (assumed to be only thermal noise) needs to be taken into account.

For amplifier measurements, the output noise voltage is measured directly (through a low noise buffer). The output noise voltage is related to the output noise current by

$$S_{V_{out}} = Z_{out}^2 S_{I_{out}} \tag{2.26}$$

where  $Z_{out}$  is the output impedance of the amplifier together with its load, and may not be purely resistive.

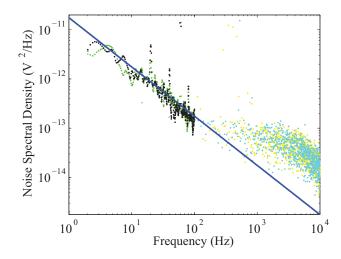

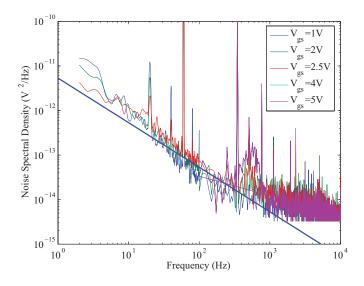

## 2.3.1 Extracted Noise Parameters

Figure 2.10 shows the measured experimental noise for a 6/2 NMOS transistor in a standard 0.5  $\mu$ m process. Figure 2.11 shows the measured experimental noise at different bias currents (for above threshold saturation operation) for a 25/5 transistor in the same process. Here the aspect ratio is given in terms of lambda based designs where  $\lambda = 0.35\mu$ m. Using this noise spectrum measurement the noise parameter  $K_f$  is  $\approx 10^{-26}$ . The parameters  $A_f$  and  $E_f$  are extracted to be 1. It should be noted that although this is measured data, the actual  $K_f$  can vary from wafer to wafer and can also vary depending on which part of the wafer the chips have originated. This means that even though the parameters have been experimentally extracted they will not necessarily always match the experimental measurements for subsequent circuit designs, however they should be adequate to determine the noise before tape-out and are still useful as a design check.

Figure 2.10: Experimental noise of 6/2 NMOS transistor: solid line is calculated noise with  $K_f = 10^{-26}$ . (Multiple lines reflect different measurement ranges during the same experiment).

Figure 2.11: Experimental noise of 25/5 NMOS transistor: solid line is calculated noise with  $K_f = 10^{-26}$ . (The large peaks reflect 60Hz noise and its harmonics).

## Chapter 3

## Comparative Analysis of Amplifier Topologies

OTAs and single transistor amplifiers are ubiquitous components in analog and mixed signal design, we therefore choose to begin exploring the idea of informations rates for circuits by focusing on how to determine the information rate for an amplifier and the implied characteristics of a particular design. Amplifiers are generally used to boost the absolute value of a signal. They are therefore used to amplify weak signals, in filter designs, in comparator designs, as buffers and are found in some form in almost any design which contains significant analog processing. In accordance with the theory outlined in the first chapter, each amplifier can be treated as a channel which transduces a weak signal into an amplified version of itself which can then be stored or further processed by other circuitry. To this end one of the first questions in investigating this approach is to ask the following: what does the information rate say about choosing a configuration for a particular task?

## 3.1 Amplifier Configurations

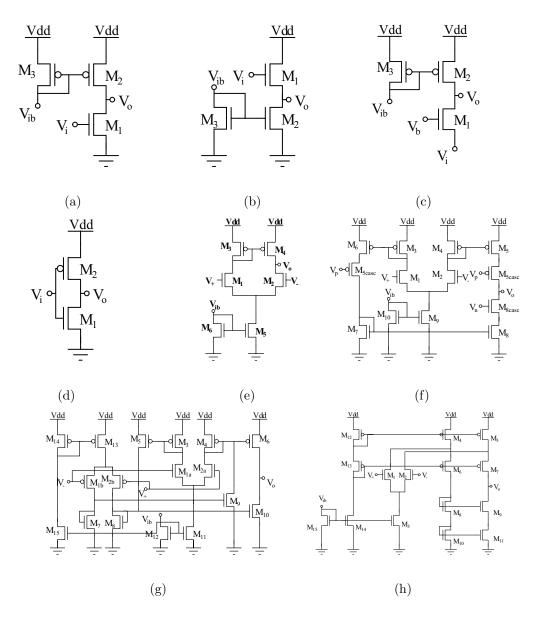

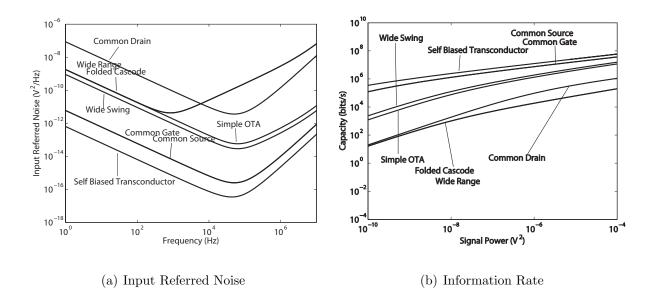

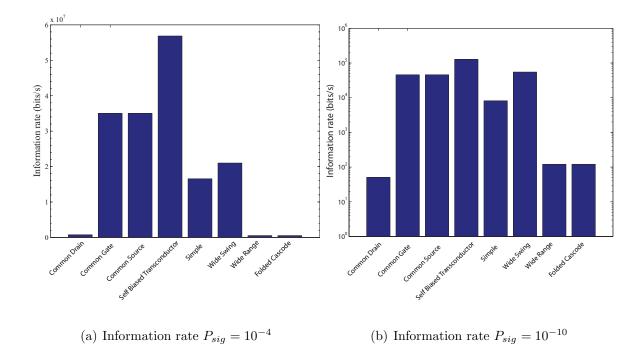

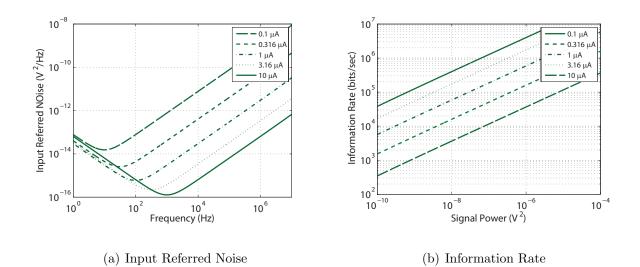

For this study, we limit the choices to the basic configurations upon which more complicated designs are based. The configurations studied are: the single transistor amplifiers: common source, common gate and common drain, all with active loads. In addition the self biased transconductor, as well as a variety of OTA's are also studied. The OTA's studied were the simple OTA, wide range OTA, wide swing OTA and folded cascode OTA (figure 3.1). Understanding the efficiency of these configurations will allow a designer to select the option most suited to the desired application.

These amplifiers reflect differences or improvements in gain, output resistance, common mode range, common mode rejection ratio and power supply rejection ratio. For a given fixed aspect ratio (W/L), the folded cascode has the highest gain, while the source follower has the lowest (gain  $\approx 1$ ). The common gate is better suited to a current buffering application. Differential amplifiers are better suited to applications in which the environmental noise is expected to be high. There is an increase in gain from the simple to the wide range to the wide swing to the folded cascode. And of course the wide swing has the best common mode range of all the OTA's, while the folded cascode has the best power supply rejection ratio. The OTAs all have better power supply rejection and common mode rejection than the single transistor amplifiers. A fully differential amplifier (such as that to be seen in Chapter 5) would have improved noise immunity over the single ended versions, however we restrict this portion of the study to only single ended amplifiers.

The important properties of these amplifiers, specifically the low frequency gain, location of the dominant pole and power consumption, are summarized in Table 3.1. To apply the waterfilling approach, the noise spectrum of the channel is required and we start by determining the input referred noise of the amplifier. To begin a simplified noise model for the amplifier is assumed.

The noise for each transistor in an amplifier may be modeled according to

simple flicker noise and thermal models introduced in the Chapter 2. The output current noise spectral density for each transistor is given by

$$S_{I_d} = \gamma 4 KT g_m + \frac{K_f I_d^{A_f}}{f^{E_f} C_{ox} L_{eff}^2}$$

$$(3.1)$$

where  $K_f \approx 10^{-26}$  (for NMOS),  $A_f \approx 1$  and  $E_f \approx 1$  are process dependent constants and  $\gamma$  depends on the region of operation (2/3 for above threshold and 1/2 for subthreshold operation). The noise of the PMOS is an order of magnitude lower than the NMOS. The input referred noise of each amplifier is determined by first finding the output voltage noise, which can be related to the current noise (at low frequencies) as

$$S_{out_v} = S_{I_d} Z_{out}^2 \tag{3.2}$$

The input referred voltage noise is then the ratio of the output voltage noise and the differential gain of the amplifier. As stated in Chapter 2 while this is just one method to determine the input referred noise, and all valid methods should lead to the same answer. The noise of the current mirrors which provide the bias current are neglected in a simple model since ideally it adds into both sides of the differential amplifier equally and should not affect the output noise voltage. The noise of the current mirrors is considered in the single amp stages.

For more accurate noise modeling the full small signal model should be considered to properly take into account the frequency effects. The output voltage noise of each transistor is considered, and then the amplification of each noise source from its position in the circuit to the output is considered. The input referred noise is the sum of all these noise sources divided by the gain of the amplifier. This more

| Configuration                        | Low Frequency<br>Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1/Dominant Pole                                                  | Power Dissipation      |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------|

| Common Source                        | $-g_{m1}(r_{o1}  r_{o2})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $(r_{o1}  r_{o2})\left(C_{gd2}+C_L\right)$                       | $I_{bias}(Vdd+Vss)$    |