#### **ABSTRACT**

Title of Document: CARBON NANOTUBE THIN FILM AS AN

**ELECTRONIC MATERIAL**

Vinod Kumar Sangwan, Doctor of Philosophy,

2009

Directed By: Professor Ellen D. Williams and

Associate Professor Michael S. Fuhrer,

Department of Physics

Carbon nanotubes (CNT) are potential candidates for next-generation nanoelectronics devices. An individual CNT possesses excellent electrical properties, but it has been extremely challenging to integrate them on a large-scale.

Alternatively, CNT thin films have shown great potential as electronic materials in low cost, large area transparent and flexible electronics.

The primary focus of this dissertation is patterning, assembling, characterization and assessment of CNT thin films as electronic material. Since a CNT thin film contains both metallic and semiconducting CNTs, it can be used as an active layer as well as an electrode material by controlling the growth density and device geometry. The growth density is controlled by chemical vapor deposition and airbrushing methods. The device geometry is controlled by employing a transfer printing method to assemble CNT thin film transistors (TFT) on plastic substrates. Electrical transport properties of CNT TFTs are characterized by their conductance,

transconductance and on/off ratio. Optimized device performance of CNT TFTs is realized by controlling percolation effects in a random network.

Transport properties of CNTs are affected by the local environment. To study the intrinsic properties of CNTs, the environmental effects, such as those due to contact with the dielectric layer and processing chemicals, need to be eliminated. A facile fabrication method is used to mass produce as-grown suspended CNTs to study the transport properties of CNTs with minimal effects from the local environment. Transport and low-frequency noise measurements are conducted to probe the intrinsic properties of CNTs.

Lastly, the unique contrast mechanism of the photoelectron emission microscopy (PEEM) is used to characterize the electric field effects in a CNT field effect transistor (FET). The voltage contrast mechanism in PEEM is first characterized by comparing measurements with simulations of a model system. Then the voltage contrast is used to probe the local field effects on a single CNT and a CNT thin film. This real-time imaging method is assessed for potential applications in testing of micron sized devices integrated in large scale.

#### CARBON NANOTUBE THIN FILM AS AN ELECTRONIC MATERIAL

By

### Vinod Kumar Sangwan

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2009

Advisory Committee:

Professor Ellen D. Williams, Chair

Professor Romel D. Gomez

Associate Professor Michael S. Fuhrer

Associate Professor Ian Appelbaum

Dr. Vincent W. Ballarotto

© Copyright by Vinod Kumar Sangwan 2009

# Dedication

To my parents, Ved Kaur and Dharam Singh

### Acknowledgements

This dissertation would not have been possible without the support of people mentioned here; especially my adviser Professor Ellen D. Williams. Roughly six years back, I knocked on Ellen's door without an appointment and asked if I could work in her group. Since then it has been a great learning experience working with her. She taught me to remain focused while working on multiple projects at the same time; she has been very patient while I was getting nowhere in trying different fabrication methods; and she provided crucial help in designing experiments and analyzing the data, at the same time letting me learn to think like an experimentalist. Her lucid and concise writing style also helped me in developing much-needed writing skills.

I would also like to acknowledge Professor Michael S. Fuhrer for helping me analyze the results and letting me use the facilities in his lab. Regular meetings with Michael inspired me to balance my fabrication work with more fundamental physics experiments. I benefitted a lot from his feedback based on his vast experience and knowledge of electronic transport in carbon nanotubes.

I cannot thank enough Dr. Vincent W. Ballarotto for helping me on most of my projects. Vince trained me to use photoelectron emission microscope and introduced me to ultra-high vacuum systems. I could always knock on his door for help in my experiments, in preparing for talks, or in writing papers. Our (heated) discussions about our experiments and science in general were important part of my

development as a scientist. He has also been a good friend and cheered me up when projects were not going at expected pace.

I would like to thank Dr. Daniel R. Hines for teaching me most of the fabrication techniques that I used in this dissertation. He has always been around whenever I needed his help in preparation of samples or in getting ready for conference presentations. His long experience and knowledge of material science saved me a lot of time when I was making my way through trials and errors of experiments during initial stage of my graduate study.

Working with Tracy Moore and Andrew Tunnell in LPS was very helpful for me. Tracy Moore was always ready to offer a hand in fabrication and measurements. I generously used CNT growth recipes, LabVIEW programs and photoetch masks designed my Andrew Tunnell. His sense of humor made LPS a lively place. Thanks to Dr. Mihaela Ballarotto for contributing to the organic semiconductor project. Dr. Karen Siegrist happily provided her PEEM data for my simulations. I would also like to extend my gratitude to the staff at LPS; especially, Laurence C. Olver, Steve Brown, Lisa Lucas, Dan Hinkel, Victor Yun and Scott Horst for providing indispensible help in the clean room.

Parts of my experiments were conducted in the physics department building, and both, Ellen's and Michael's group members have been very nice to me. Dr. Adrian E. Southard spent hours helping me set up experiments in the probe stations. Dr. Brad R. Conrad introduced me to noise measurements. Alexandra Curtin helped me in taking EFM images. Thanks to Sungjae Cho for helping me in a side project on

graphene. Also thanks to Enrique Cobas that I could always turn to him for troubleshooting the CVD growth system. Working with Dr. David Tobias and Professor Christopher Lobb during the first year of my PhD introduced me to some general concepts in experimental physics that proved to be quite useful later on. Special thanks to them. I would also like to thank Professor Ted Einstein for providing useful feedbacks during talk practices. I apologize for not being able to list everyone here, but I would like to extend my deep appreciation to the rest of the group members who have helped me in one way or other.

I would like to extend my gratitude to all the Physics Department and MRSEC staff. I would like to specifically mention Margaret Lukomska, Donna Hammer, Linda O'Hara and Jane Hessing who enrolled me in the courses so many times after the deadline had passed.

Lastly, I would like to thank all my friends at University of Maryland for putting up with me and enriching my graduate school experience. I would also like to mention my parents, Dharam Singh and Ved Kaur, and my wife, Pratibha Choudhary for their love and support.

# Table of Contents

| Dedication                                                        | ii   |

|-------------------------------------------------------------------|------|

| Acknowledgements                                                  | iii  |

| Table of Contents                                                 | vi   |

| List of Tables                                                    | viii |

| List of Figures                                                   | ix   |

| Chapter 1: Introduction                                           | 1    |

| 1.1 Historical Background of Carbon Nanotubes                     | 1    |

| 1.2 Structure and Properties of Carbon Nanotubes                  | 1    |

| 1.3 Why Carbon Nanotube Thin Films Devices?                       |      |

| 1.4 Overview of the Thesis                                        | 11   |

| Chapter 2: Transfer Printing                                      | 14   |

| 2.1 Introduction to Transfer Printing                             | 15   |

| 2.2 Preparation of the Metal Electrodes                           | 18   |

| 2.3 Surface Treatments to enhance Differential Adhesion           | 21   |

| Chapter 3: Growth and Patterning of Carbon Nanotubes              | 25   |

| 3.1 Carbon Nanotube Growth by Chemical Vapor Deposition           |      |

| 3.2 Controlling the Density Carbon Nanotubes                      |      |

| 3.3 Techniques for Patterning Carbon Nanotube Thin Films          | 34   |

| 3.3.1 Photolithographic Patterning of CVD grown CNTs              | 34   |

| 3.3.2 Pre-patterning of the Catalyst                              |      |

| 3.2.3 Patterning CNT Thin Films using Transfer Printing           | 45   |

| 3.4 Comparison of Patterning Methods                              |      |

| Chapter 4: Transport and 1/f Noise in Suspended Carbon Nanotubes  | 52   |

| 4.1 Fabrication of the Devices                                    | 53   |

| 4.2 Versatility of the Fabrication Method                         | 57   |

| 4.3 Transport Measurements                                        | 60   |

| 4.4 Introduction to 1/f Noise                                     | 64   |

| 4.5 1/f Noise in CNTs                                             | 65   |

| 4.6 Conclusions                                                   | 77   |

| Chapter 5: Carbon Nanotube Thin Film as a Semiconducting Material | 78   |

| 5.1 Percolation Theory of 2D Random Conducting Sticks             |      |

| 5.2 Percolation Theory for CNT Thin Films                         |      |

| 5.3 CNT Thin Film Devices                                         | 83   |

| 5.4 Optimization of the Device Performance                        |      |

| 5.5 CNT Thin Film Devices on Flexible Substrates                  | 96   |

| 5.5.1 Bottom Gate Devices                                         | 96   |

| 5.5.2 Top Gate Devices                                            | 99   |

| 5.5.3 Control Devices                                             |      |

| 5.5.4 Transport Properties of Transfer Printed Devices            | 103  |

| 5.6 Conclusions                                                   |      |

| Chapter 6 · Carbon Nanotube Thin film as an Electrode Material    |      |

| 6.1 Airbrushing CNT Thin Films                                                | 110  |

|-------------------------------------------------------------------------------|------|

| 6.2 Transfer Printing CNT Electrode Sub-assemblies                            | 117  |

| 6.3 Characterization of the Dielectric Layer                                  |      |

| 6.4 All-Carbon Nanotube Thin film Transistors                                 | 124  |

| 6.5 Flexibility of CNT Thin Films                                             | 129  |

| 6.6 CNT Thin Film Electrodes in Organic Complementary Circuits                | 130  |

| 6.7 Conclusions                                                               |      |

| Chapter 7: Voltage Contrast in Photoelectron Emission Microscopy              | 139  |

| 7.1 Photoelectron Emission Microscope                                         | 140  |

| 7.2 Optics of Image Formation in PEEM                                         |      |

| 7.3 Fabrication of the Devices                                                |      |

| 7.4 Measurement and Image Analysis                                            | 147  |

| 7.5 Contrast Mechanisms in PEEM                                               |      |

| 7.5.1 Topography Contrast                                                     | 148  |

| 7.5.2 Voltage Contrast                                                        |      |

| 7.6 Numerical Model                                                           |      |

| 7.7 Analytical Model                                                          | 155  |

| 7.8 Results and Discussion                                                    | 158  |

| 7.9 Conclusions                                                               | 168  |

| Chapter 8: Characterizing Carbon Nanotube Devices using Photoelectron Emis    | sion |

| Microscopy                                                                    | 170  |

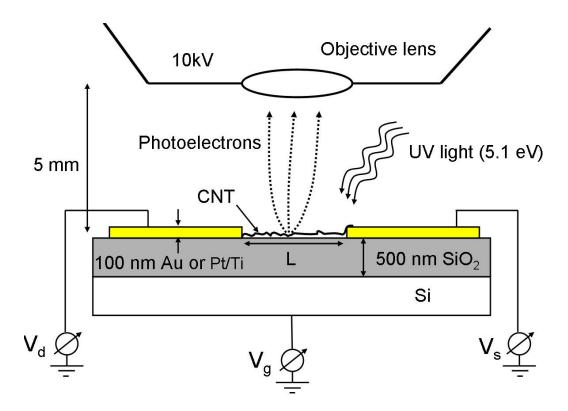

| 8.1 Device Fabrication and Experimental Set-up                                |      |

| 8.2 Voltage Contrast in a Single CNT                                          |      |

| 8.3 Image Formation Mechanism of CNT on SiO <sub>2</sub>                      |      |

| 8.4 Probing Local Potential in CNT Devices                                    | 181  |

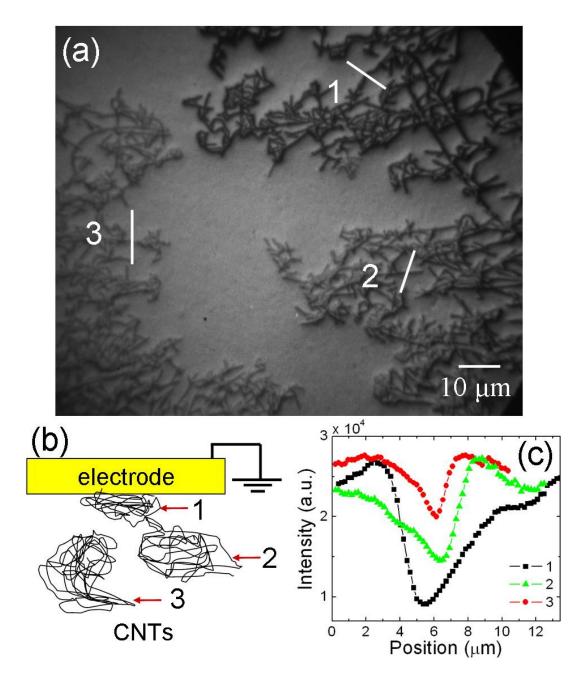

| 8.5 Imaging Contrast and CNT Network Connectivity                             | 185  |

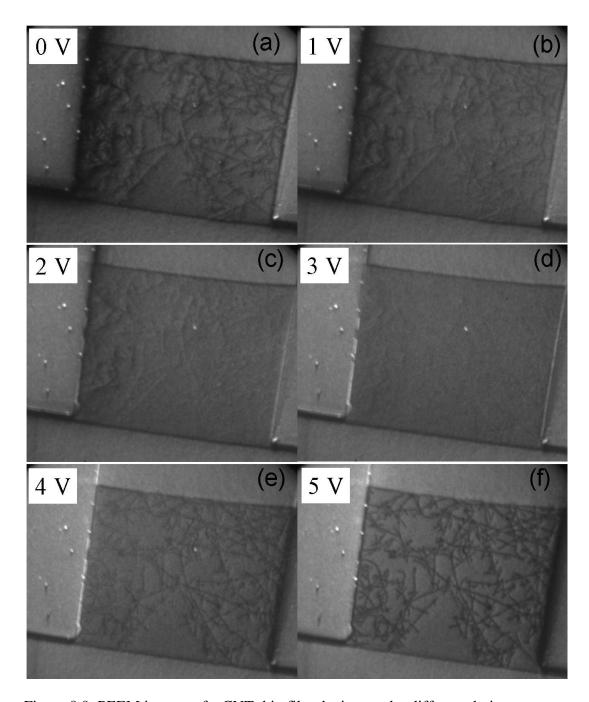

| 8.6 Probing Percolation Effects in CNT Thin Film Devices                      | 186  |

| Conclusions                                                                   | 189  |

| Chapter 9 : Summary                                                           | 190  |

| Appendix A: Abbreviations used in the Thesis                                  | 194  |

| Appendix B: Effects of Chemical Processing on Electrical Properties of Carbon | 1    |

| Nanotube Thin Films Devices                                                   |      |

| Appendix C: Simulation of Electric Fields using POISSON-SUPERFISH             | 209  |

| Appendix D: IDL 6.1 Codes for PEEM Image Processing                           |      |

| Appendix E: MATLAB Codes for Analysis of Electron Trajectory Data             | 217  |

| Bibliography:                                                                 | 228  |

## List of Tables

| Table 3.1 | Growth procedure of CNTs using CVD.                                | 28 |

|-----------|--------------------------------------------------------------------|----|

| Table 3.2 | A comparison of various CNT thin film patterning methods discussed | 51 |

# List of Figures

| Figure 1.1 a) The honeycomb lattice structure of unrolled CNT (graphene)                           |

|----------------------------------------------------------------------------------------------------|

| Figure 1.2 Schematic of band structure of 2-dminesional graphene                                   |

| Figure 1.3 The band structure of the CNT can be obtained by applying the                           |

| Figure 2.1 Schematic of transfer printing method used to transfer multiple                         |

| Figure 2.2 a) PDMS stamps are treated with release layer on Si substrate                           |

| Figure 3.1 Chemical Vapor Deposition (CVD) set up for CNT growth                                   |

| Figure 3.2 AFM images of CNT thin film grown by CVD using a) ferric nitrate, 29                    |

| Figure 3.3 a) An SEM image of CNT thin film grown by 40% H <sub>2</sub> and 60% CH <sub>4</sub> 32 |

| Figure 3.4 a) Average density of CNT network (p) is plotted against the                            |

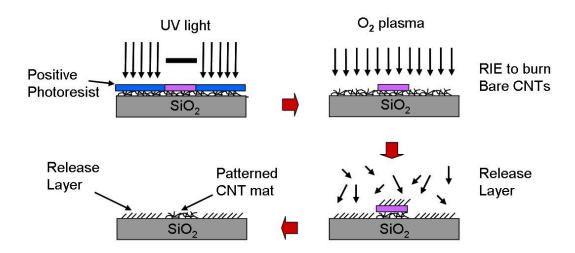

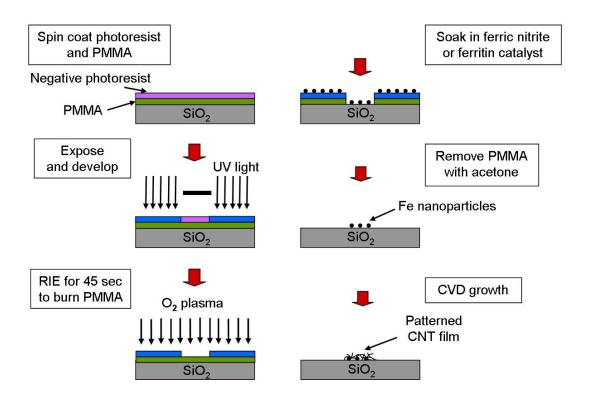

| Figure 3.5 Photolithography and reactive ion etching are used to pattern a CNT 36                  |

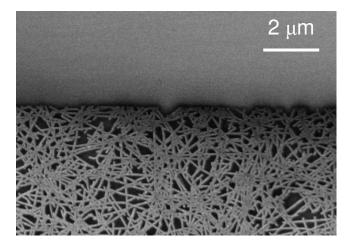

| Figure 3.6 SEM micrograph of the edge of a CNT thin film patterned by                              |

| Figure 3.7 Photolithography is used to pattern the ferritin catalyst before CNTs 38                |

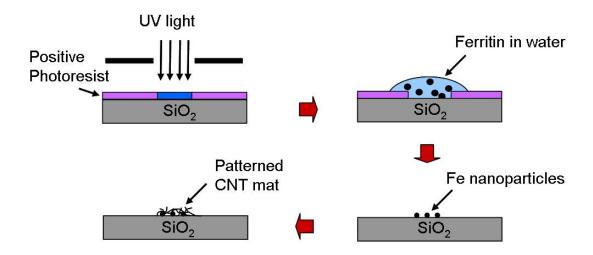

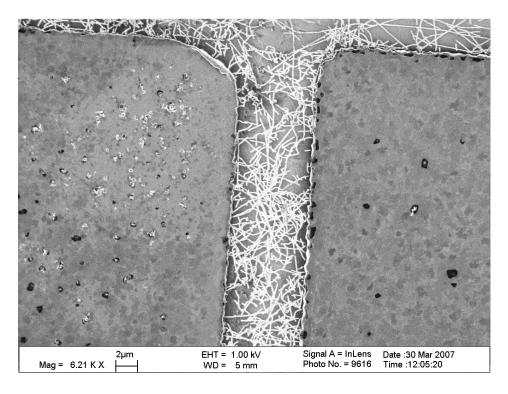

| Figure 3.8 An SEM image of the edge of a CNT thin film patterned by                                |

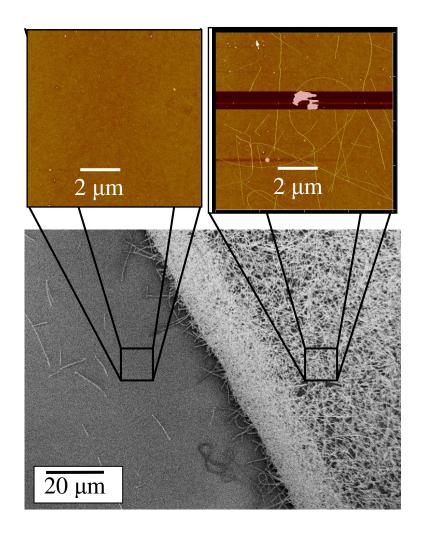

| Figure 3.9 Schematic of the photolithography steps to synthesize patterned 41                      |

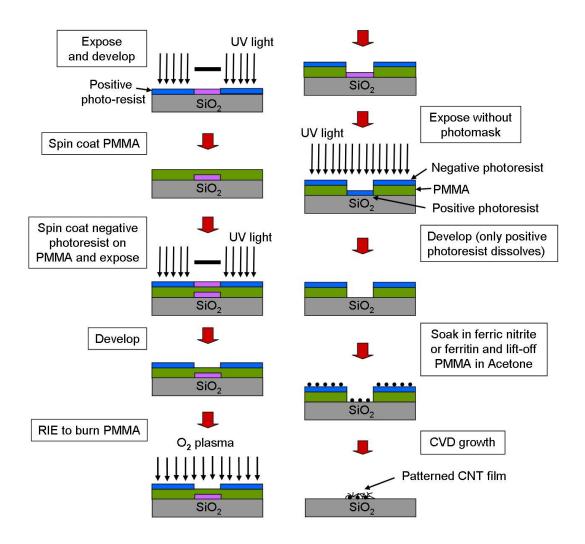

| Figure 3.10 Schematic of the photolithography steps to grow patterned CNT 43                       |

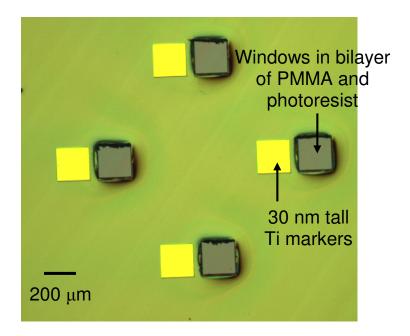

| Figure 3.11 An optical image of a patterned bilayer of the photoresist and PMMA. 44                |

| Figure 3.12 SEM image of a CNT thin film device fabricated by growing CNTs 45                      |

| Figure 3.13 Illustration of steps for patterning CNT films using transfer printing 47              |

| Figure 3.14 a) Height profile of a master 16 µm tall Si stamp. b) Comparison 49                    |

| Figure 3.15 a) Profile of the PET stamps made from two master Si stamps                            |

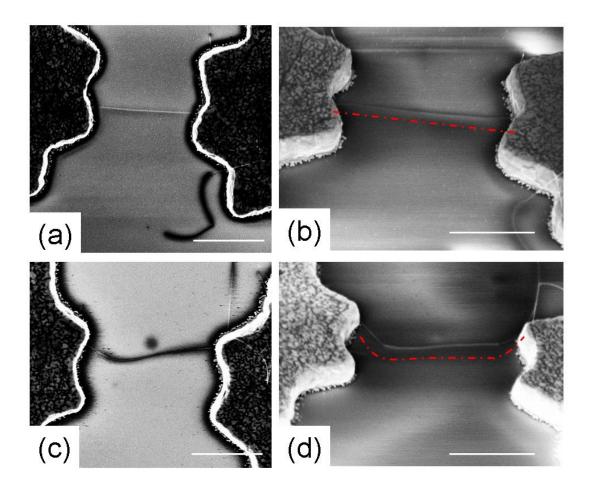

| Figure 4.1 a) CNT covered substrate is pressed against electrodes at 300 psi, 55                   |

| Figure 4.2 a) SEM image of a suspended CNT device. Suspended CNT shows 56                          |

| Figure 4.3 a) An SEM image of a single suspended CNT printed from a CNT 59                         |

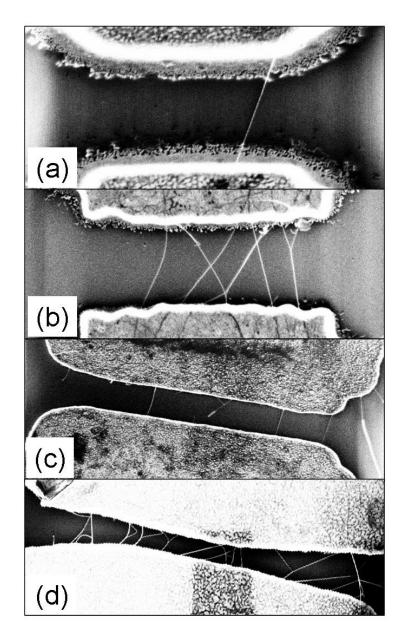

| Figure 4.4 a) An optical image of a chip containing 51 electrode pairs                             |

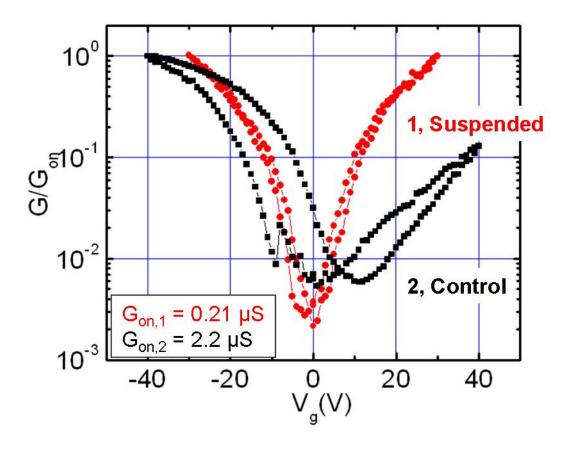

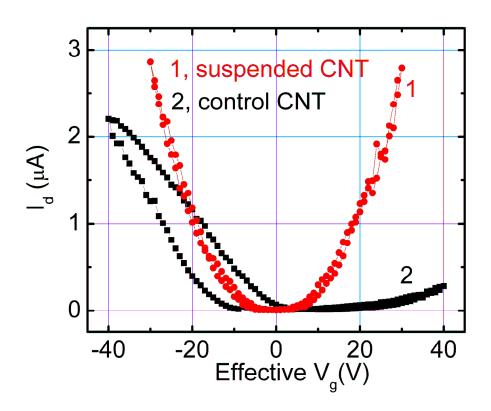

| Figure 4.5 Transfer characteristics of a suspended CNT-FET (1) is compared 62                      |

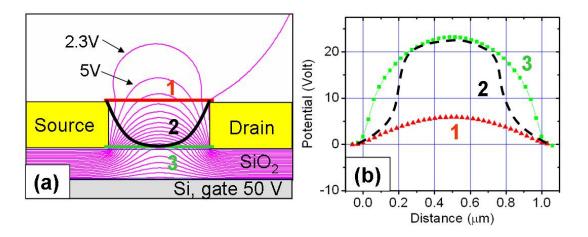

| Figure 4.6 a) Simulations of equi-potential lines using Poisson-Superfish                          |

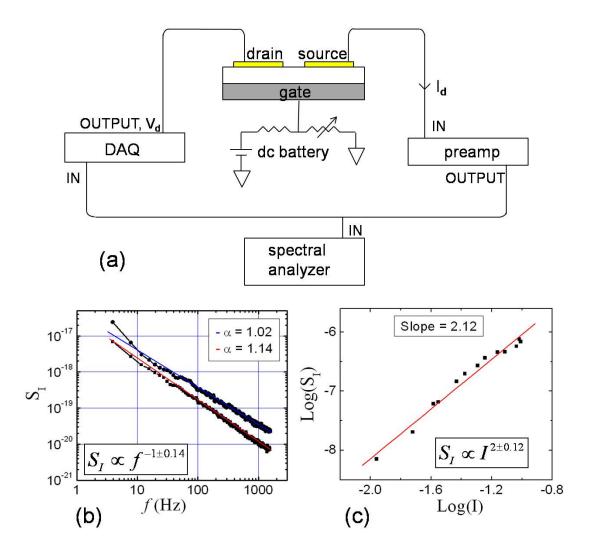

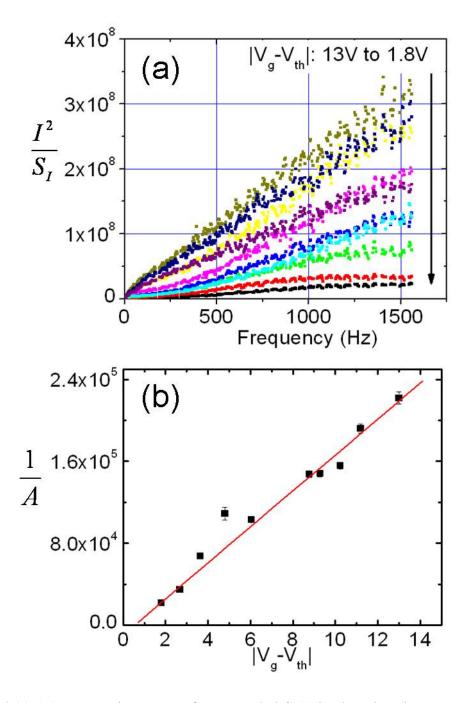

| Figure 4.7 a) Schematic of noise measurement set-up. b) Noise spectral 67                          |

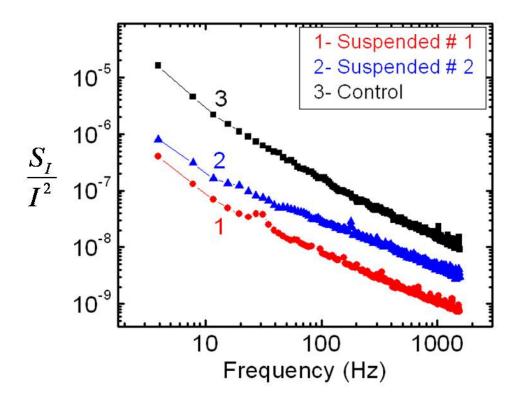

| Figure 4.8 Noise power as a function of frequency for a control device and                         |

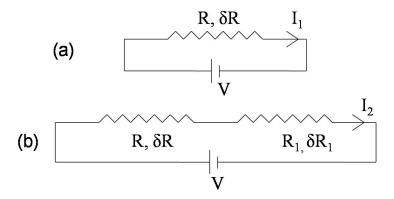

| Figure 4.9 a) Circuit diagram of a device with resistance R with resistance                        |

| Figure 4.10 Transfer curves of suspended and control CNTs where drain                              |

| Figure 4.11 a) Inverse noise power of a suspended CNT is plotted against                           |

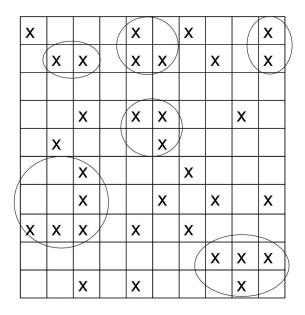

| Figure 5.1 A square lattice consisting randomly distributed occupied sites                         |

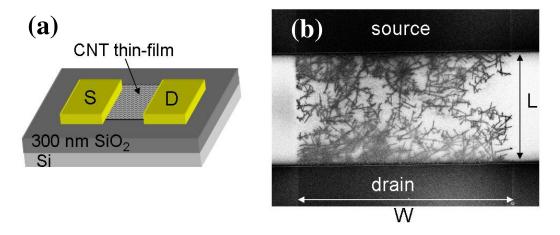

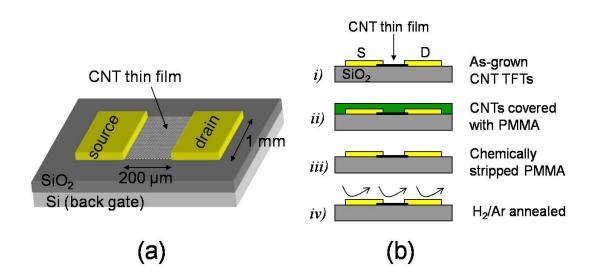

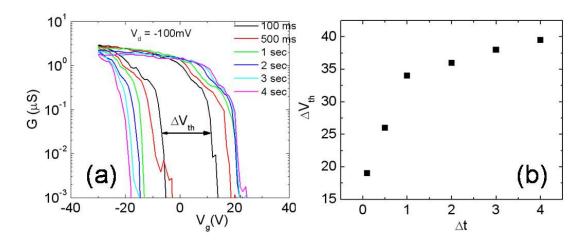

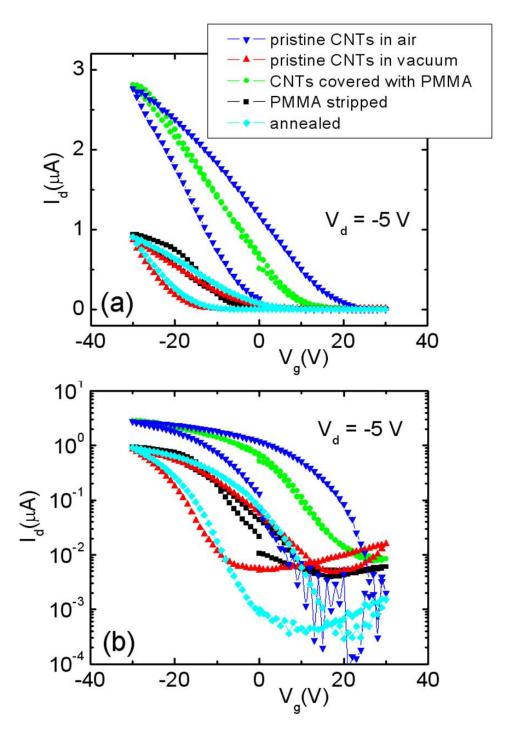

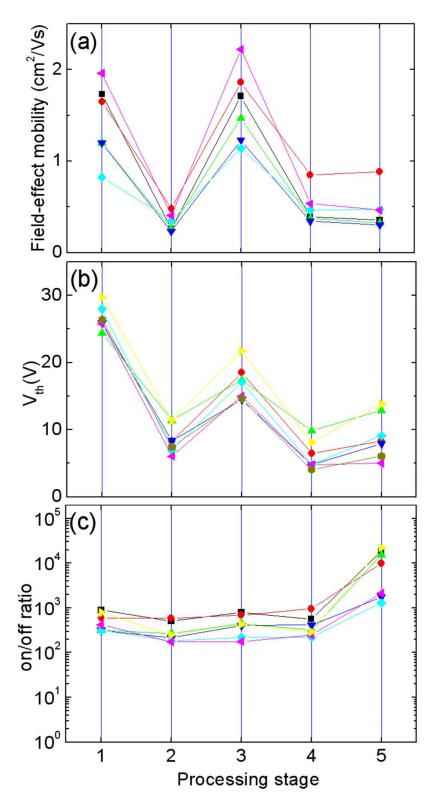

| Figure 5.2 a) Schematic of a CNT thin-film device on a 300 nm thick                                |

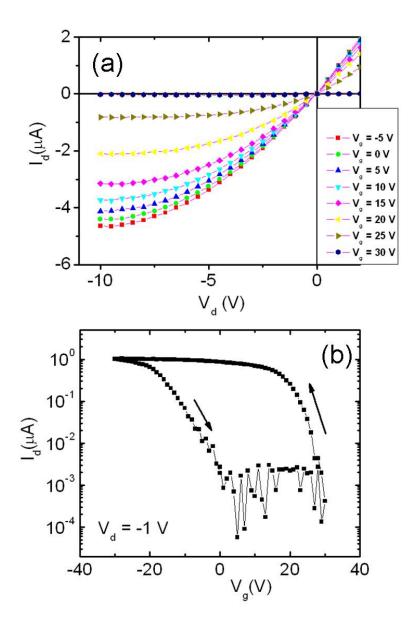

| Figure 5.3 a) Output characteristic of a CNT thin-film transistor with $W = 50 \mu m 87$           |

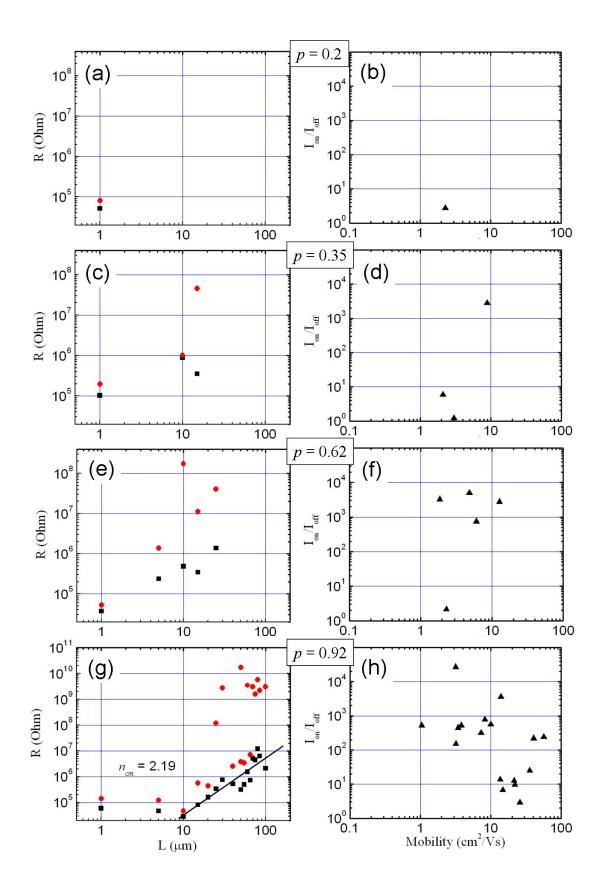

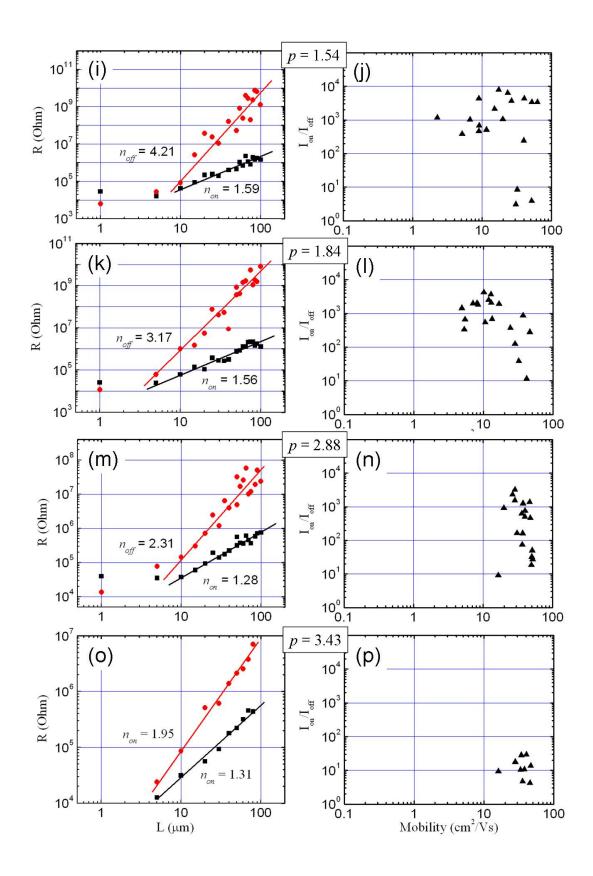

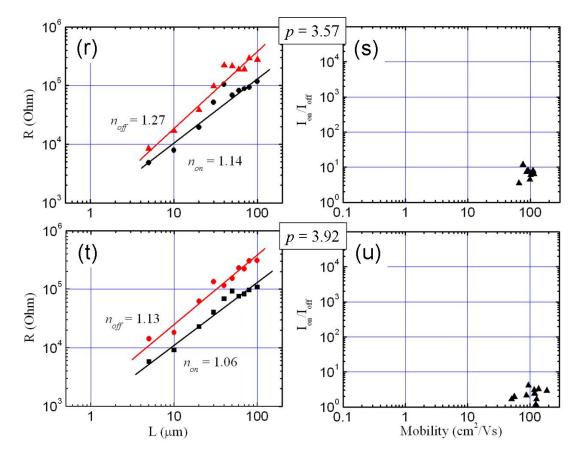

| Figure 5.4 Left column from (a) to (t): Device resistance in on-(black squares 91                  |

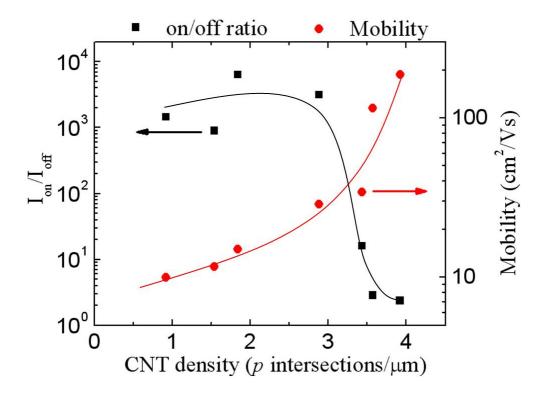

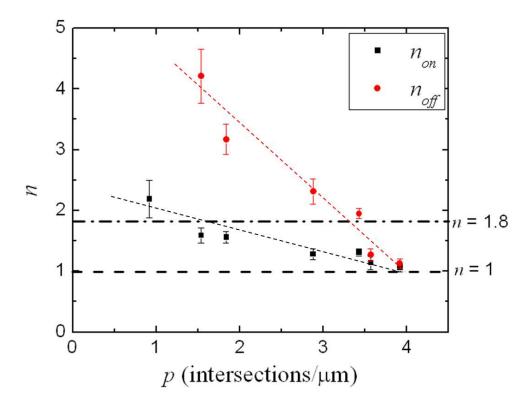

| Figure 5.5 On/off ratio and field-effect mobility versus density of CNTs in                        |

| Figure 5.6 Power law exponents from length dependence of 'on' and 'off'94                          |

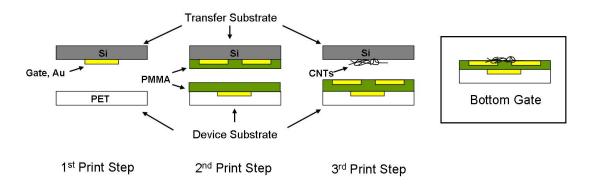

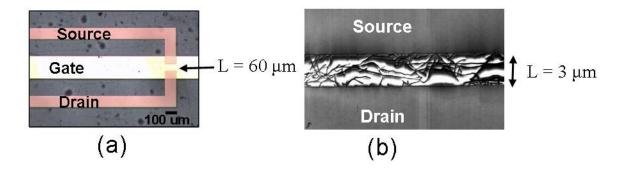

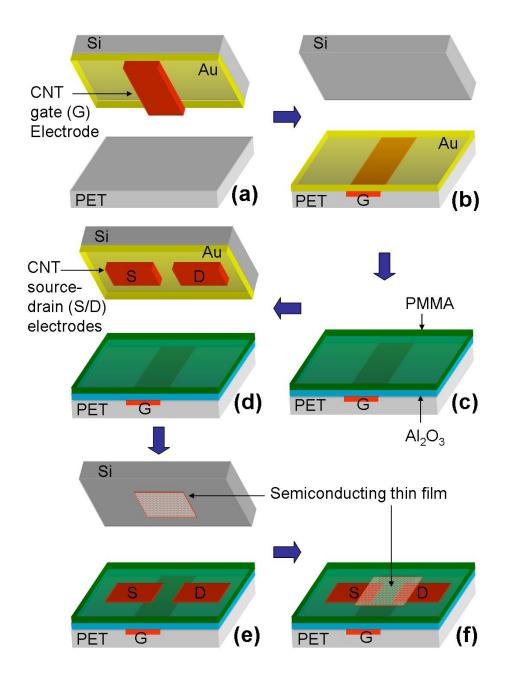

| Figure 5.7 Schematic of printing steps involved in fabrication of bottom gate 98                   |

| Figure 5.8 a) An optical image of a bottom gate device with $L = 60 \mu m$                         |

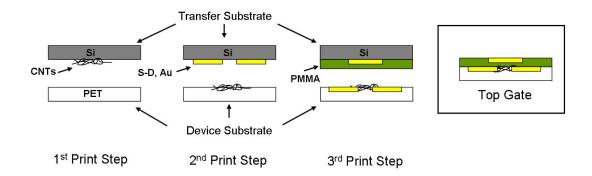

| Figure 5.9 Schematic of printing steps involved in assembling a top gate 100                       |

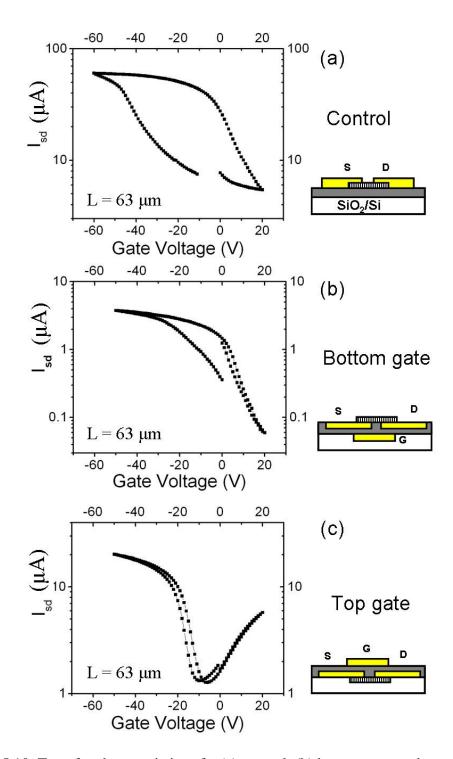

| Figure 5.10 Transfer characteristics of a (a) control, (b) bottom gate and 102                     |

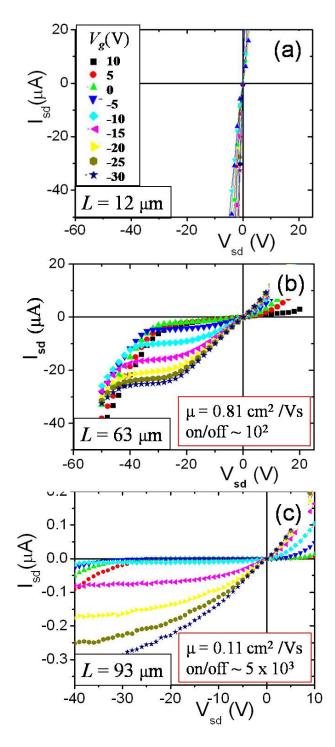

| Figure 5.11 a), b), c) Output characteristics of top gate devices with $W = 100 \mu m$ 104         |

| Figure 6.1 Schematic of the experimental set-up for airbrushing CNT solution 112                    |

|-----------------------------------------------------------------------------------------------------|

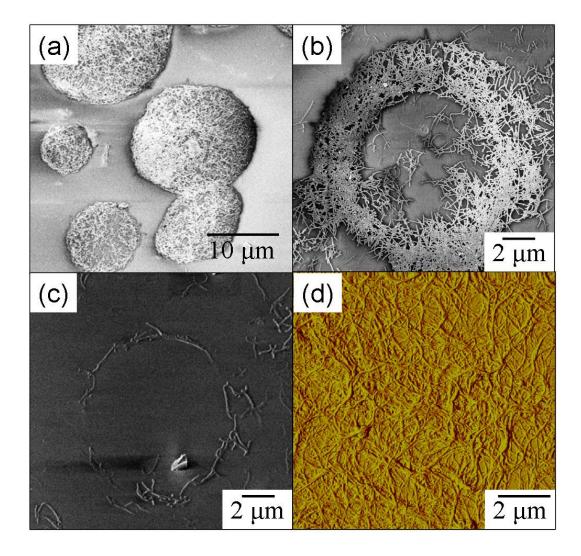

| Figure 6.2 a) A SEM image of CNTs in dried droplets of 3 mg/ml solution 114                         |

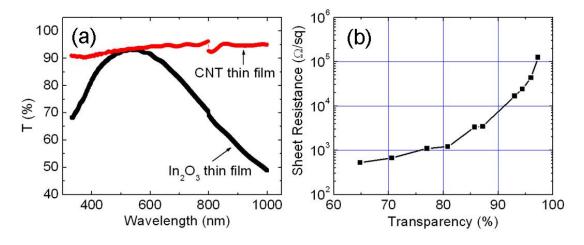

| Figure 6.3 a) Transparency of a CNT thin film (sheet resistance $\sim 10 \text{ k}\Omega$ ) and 115 |

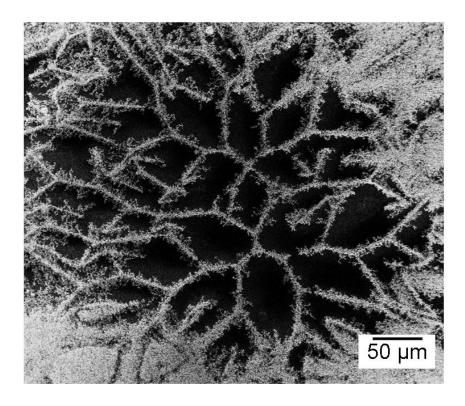

| Figure 6.4 CNT thin film flowers obtained after lift-off of a negative photoresist . 117            |

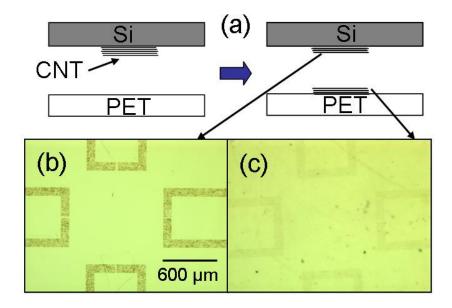

| Figure 6.5 a) Schematic of transfer printing an airbrushed CNT thin film                            |

| Figure 6.6 Schematic of different transfer printing steps used to fabricate                         |

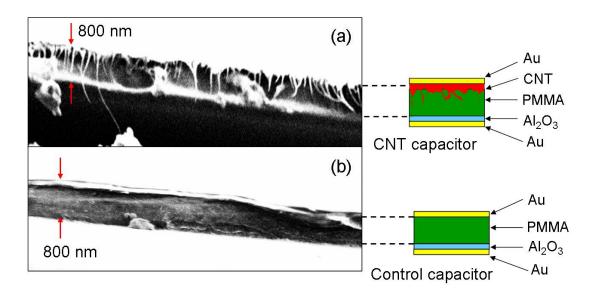

| Figure 6.7 a) A SEM image of cross-section of a CNT thin-film capacitor reveals 123                 |

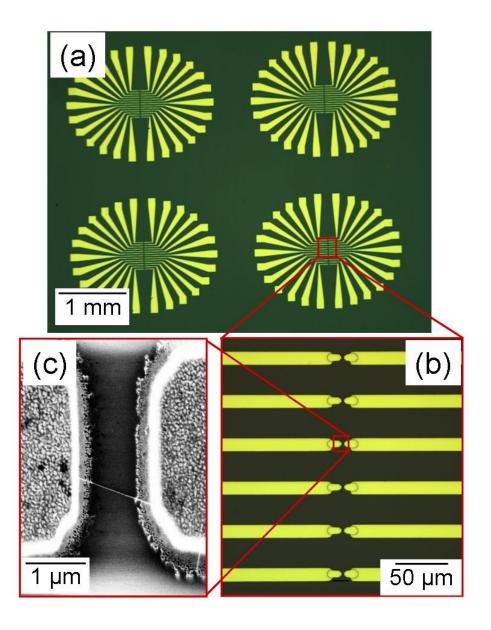

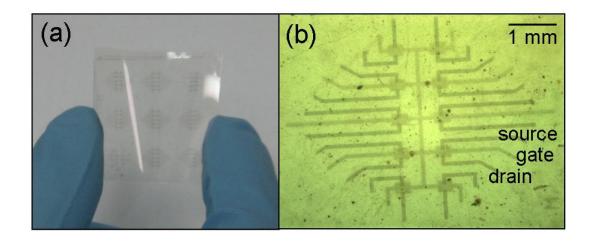

| Figure 6.8 a) An optical image of a one inch square PET substrate with 90 CNT 125                   |

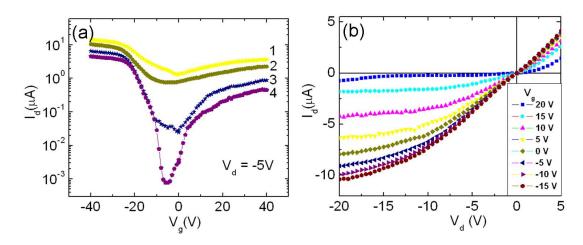

| Figure 6.9 a) Transfer characteristics of an all-CNT device ( $L = 60 \mu m$ ) at 126               |

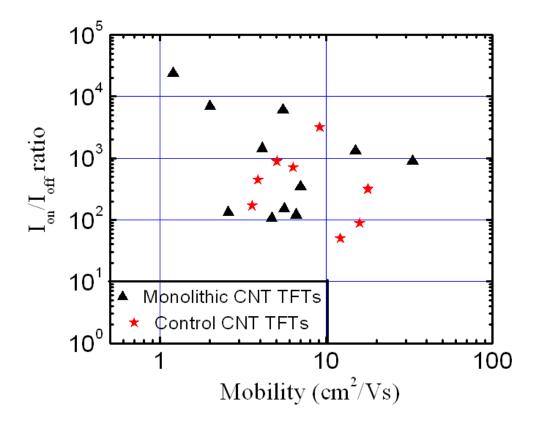

| Figure 6.10 On/off ratio is plotted as a function of mobility for all-CNT 127                       |

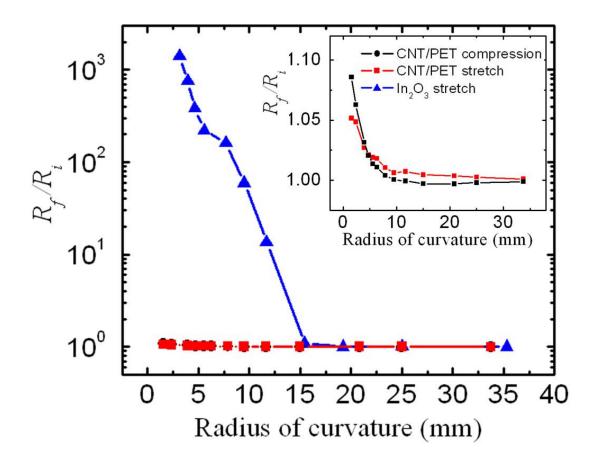

| Figure 6.11 Ratio of the sheet resistances, $R_f/R_i$ , before and after bending as a 130           |

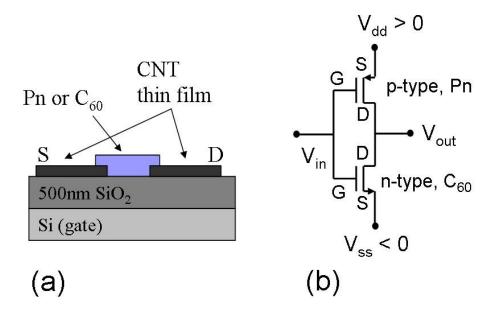

| Figure 6.12 a) Schematic of pentacene and C60 TFTs used for complementary 132                       |

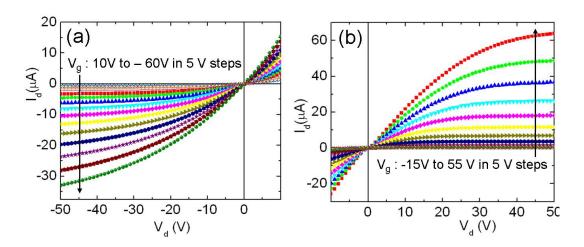

| Figure 6.13 a) Output characteristics of a p-type pentacene device ( $L = 30 \mu m$ ) 133           |

| Figure 6.14 a) Transfer characteristics of C60 and pentacene TFTs are compared 134                  |

| Figure 6.15 a) Input-output voltage transfer characteristic of a pentacene-C <sub>60</sub> 136      |

| Figure 7.1 Schematic of the PEEM systems with all major components labeled 141                      |

| Figure 7.2 a) A picture of sample holder in the PEEM sample region which acts a 143                 |

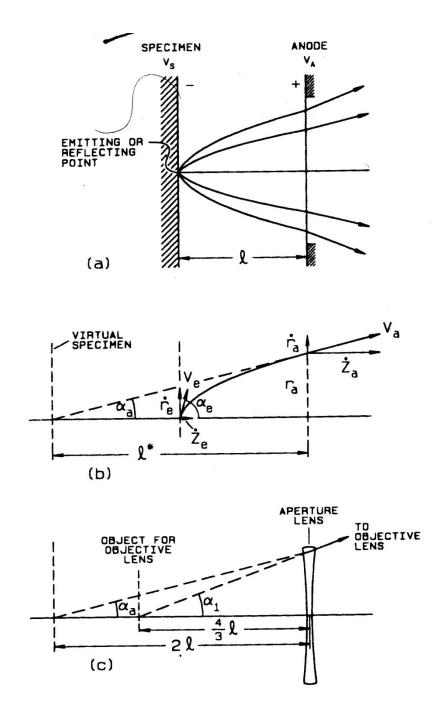

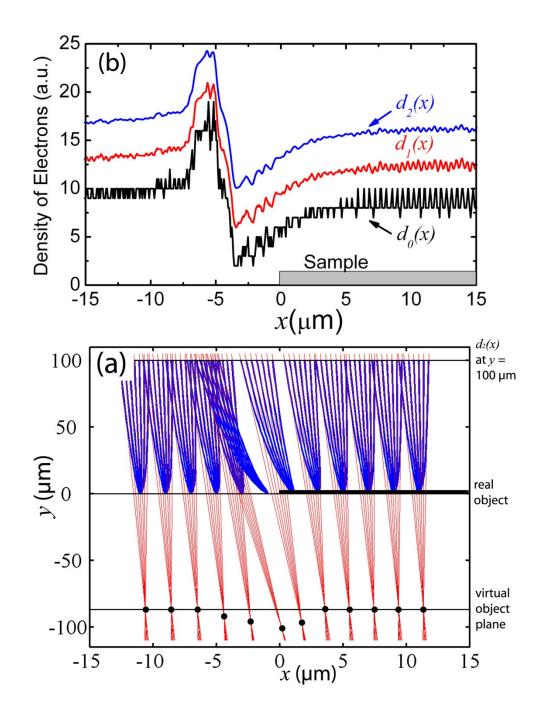

| Figure 7.3 a) Trajectories of electrons emitted from a flat surface follow                          |

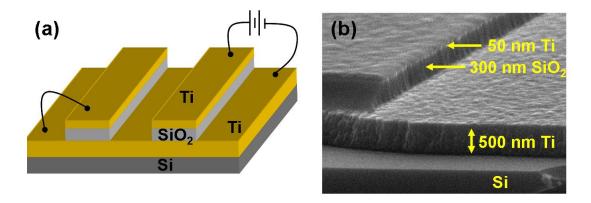

| Figure 7.4 (a) Schematic of a tri-layered sample for voltage contrast                               |

| Figure 7.5 a) Electrostatic simulations show perturbation of the electric field 149                 |

| Figure 7.6 a) A PEEM image of a sample showing the effect of bias on imaging 150                    |

| Figure 7.7 a) Electron trajectories simulated using SIMION 7 when the sample 153                    |

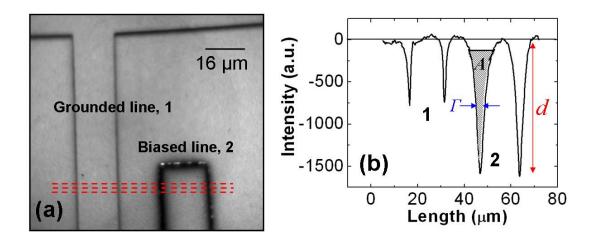

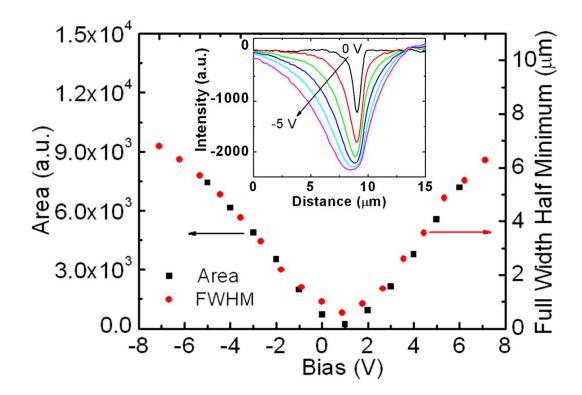

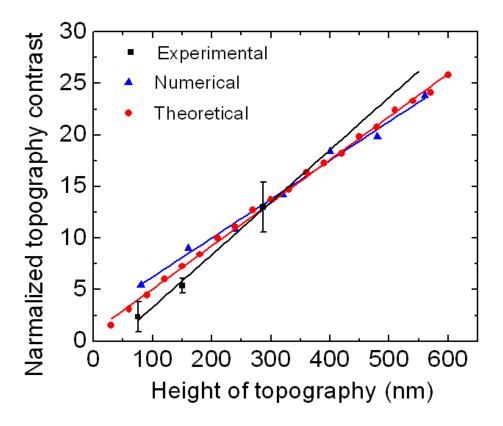

| Figure 7.8 The area under the curve A and the full width half minimum $\Gamma$ as a 159             |

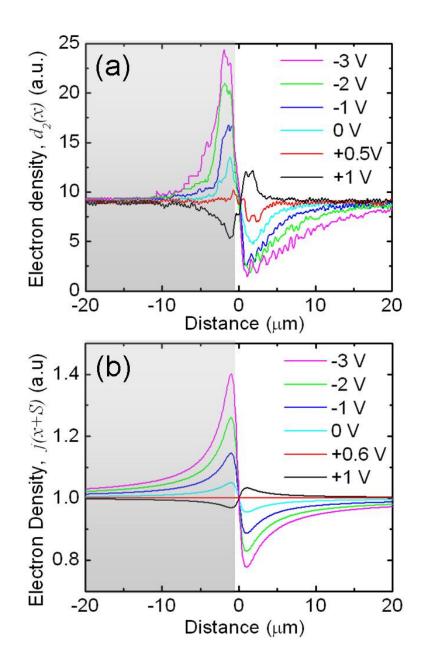

| Figure 7.9 a) Electron distribution $d_2(x)$ obtained from the numerical method 161                 |

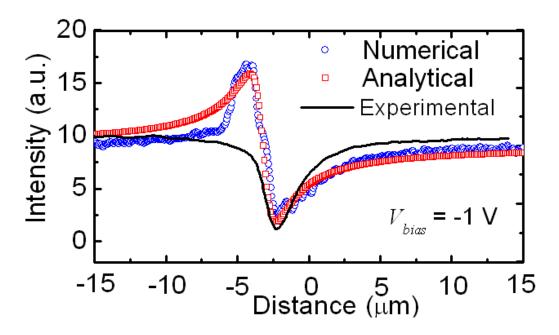

| Figure 7.10 Intensity profiles obtained from two analyses (blue and red curves 162                  |

| Figure 7.11 The area under the intensity dips from measured and calculated 163                      |

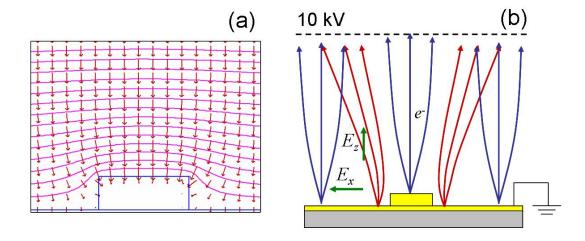

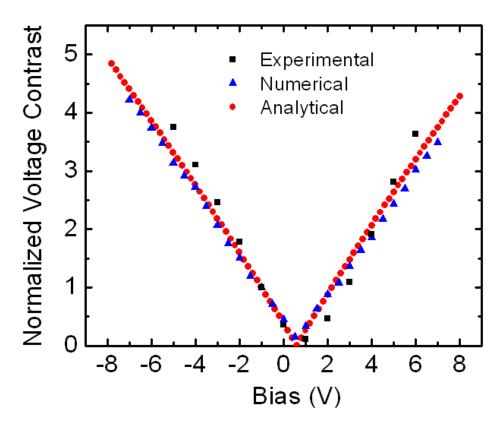

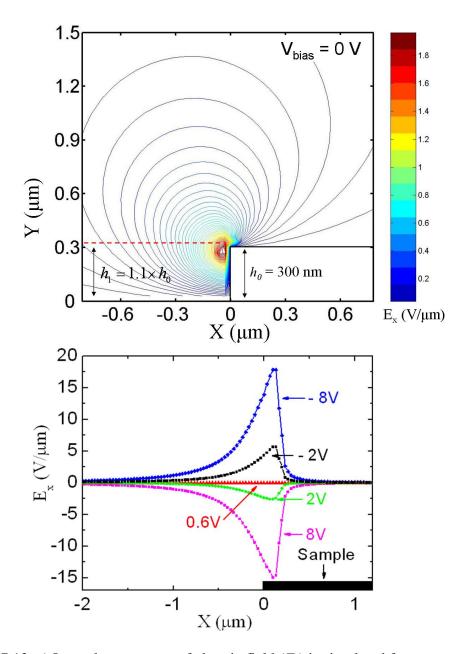

| Figure 7.12 a) Lateral component of electric field ( $E_x$ ) is simulated for a                     |

| Figure 7.13 The area under the intensity dips for measured and calculated 168                       |

| Figure 8.1 Schematic of a CNT device in the PEEM chamber                                            |

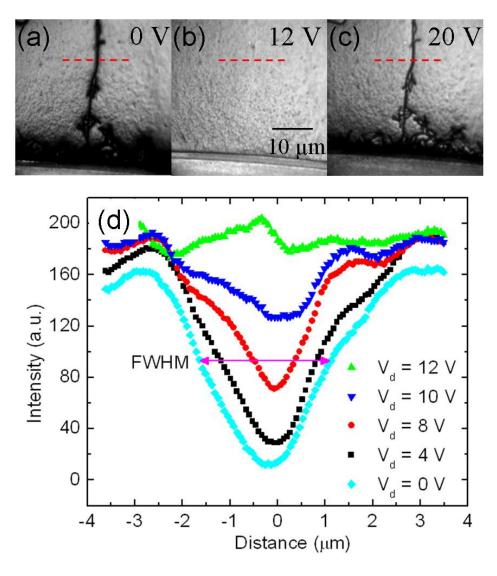

| Figure 8.2 a), b), c) PEEM images of a CNT at $V_{\text{bias}} = 0 \text{ V}$ , 12 V and 20 V,      |

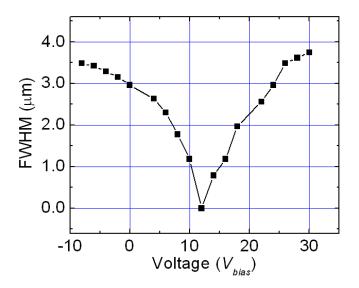

| Figure 8.3 Apparent diameter of CNT (FWHM as shown in Fig. 8.2) as a                                |

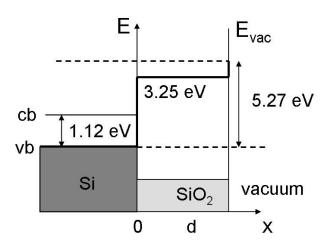

| Figure 8.4 Band diagram of the Si/SiO2 interface. The energy required for an 176                    |

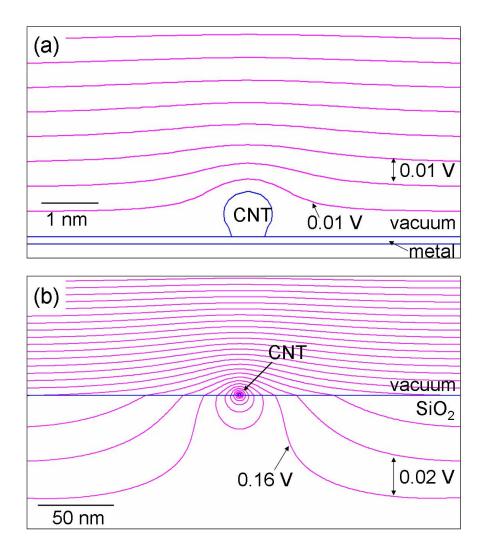

| Figure 8.5 Electric field simulations were done using Poisson-Superfish                             |

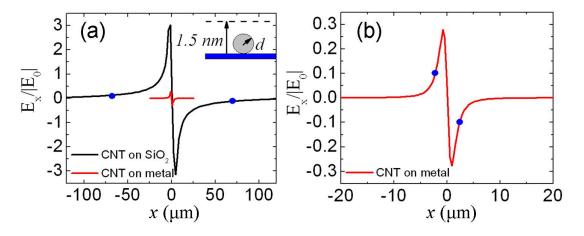

| Figure 8.6 a) The ratio $E_x/ E_0 $ is plotted along a line 0.5 nm above a CNT                      |

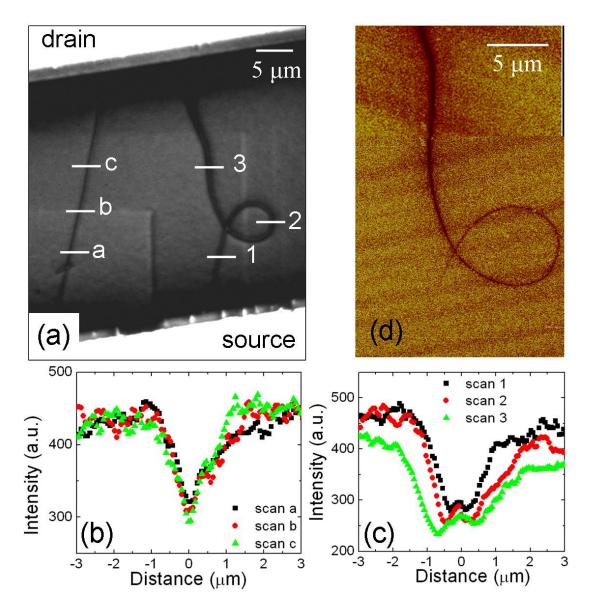

| Figure 8.7 a) PEEM image of a CNT FET containing two CNTs. The drain 183                            |

| Figure 8.8 a) PEEM image of three different segments of a thin film of well 184                     |

| Figure 8.9 PEEM images of a CNT thin film devices under different drain 188                         |

Chapter 1: Introduction

#### 1.1 Historical Background of Carbon Nanotubes

Carbon is found in a wide variety of compounds due to its unique capacity for diverse orbital hybridizations (sp, sp<sup>2</sup> and sp<sup>3</sup>). However, till last century, pure elemental compounds of carbon were thought to be limited to diamond, graphite and amorphous carbon. In the beginning of the 20<sup>th</sup> century, the first carbon fiber was discovered and used in early prototypes of light bulbs by Thomas A. Edison [1]. After WW II, research in carbon fibers was further stimulated by the needs of the space and aircraft industries for strong and lightweight composite materials. However, the smallest diameter achievable for a carbon fiber was reported to be ~ 100 A [2]. The existence of smaller diameter carbon fibers was seriously reconsidered after the discovery of a new allotrope of carbon, buckminsterfullerene (buckyballs) by Kroto and Smalley in 1985 [3]. Buckyballs are hollow spherical molecules consisting of sp<sup>2</sup> hybridized carbons and they triggered speculation about the existence of hollow cylindrical forms of carbon [4-6]. Soon after, the first carbon nanotube was observed by Iijima [7] using transmission electron microscopy in 1991. Since then carbon nanotubes have been extensively studied by scientists around the world.

#### 1.2 Structure and Properties of Carbon Nanotubes

Carbon nanotubes are hollow cylindrical sheets of graphite seamlessly rolled in diameters ranging from 0.7 to 10 nm [8, 9]. A single- (multi-) walled nanotube

results from rolling a single (multiple) graphene sheet(s). Most single-walled nanotubes (SWNT) have diameters less than 2 nm. The two hemispherical ends of CNTs can be neglected for all the properties and applications discussed in this work. Thus the large aspect ratio ( $> 10^4$ ) makes CNTs essentially one-dimensional nanostructures. To understand the structure and properties of SWNTs, I first consider a honeycomb graphene sheet.

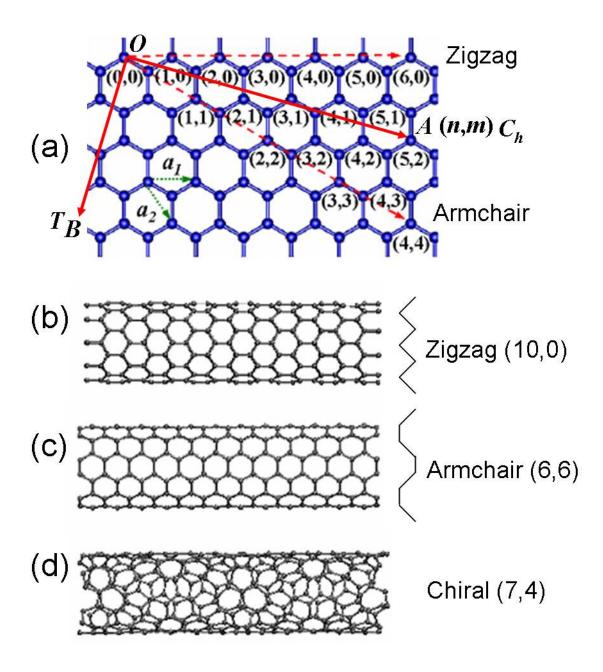

Graphene is a two dimensional hexagonal lattice of sp<sup>2</sup> hybridized carbon atoms (Fig. 1.1) with a basis containing two carbon atoms [9]. Interestingly, a CNT can be obtained by rolling a graphene sheet without distortion in countless many ways. The structure and properties of a CNT depends on the direction in which graphene is folded. For the purpose of completeness, let me introduce the classification system for CNTs. The structure of a nanotube is specified by a vector  $\overrightarrow{OA}$ , connecting the lattice point A(n, m) with the origin O(0, 0), see Fig. 1.1(a). The vector  $\overrightarrow{OA}$ , also called the chiral vector ( $C_h$ ), can be written as  $C_h = na_1 + ma_2$ , where  $a_1$  and  $a_2$  are two unit vectors (Fig. 1.1), and n and m integers such that  $0 \le |m| \le n$ . The vector  $C_h$  lies along the circumference of the nanotube designated as (n, m), and a translational vector (T, perpendicular to  $C_h$ ) defines the axis of the nanotube.

Figure 1.1 a) The honeycomb lattice structure of unrolled CNT (graphene). The unit vectors are denoted by  $a_1$  and  $a_2$ . A CNT designated by (n,m) is obtained by connecting the lattice point (n,m) with the origin. The chiral vector  $(C_h)$ , connecting (n,m) and (0,0), defines the circumference of the CNT. The translation vector (T) is perpendicular to  $C_h$ , and is parallel to the axis to the CNT. b), c) and d) The structure of a zigzag, an armchair and a chiral CNT is shown, respectively. (Courtesy of Prof. Susan Sinnott, UFL).

All possible nanotubes can be classified as achiral or chiral. An achiral nanotube is identical to its mirror image where a chiral nanotube is not. There are only two possible achiral nanotubes; zigzag and armchair nanotubes. A zigzag nanotube (Fig. 1.1(b)) is obtained by connecting a lattice point (n,0) with the origin (horizontal dashed line in Fig. 1.1(a)). An armchair nanotube (Fig. 1.1(c)) is obtained by connecting a lattice point (n, n) with the origin (slanted dashed line in Fig. 1.1(a)). The names zigzag and armchair come from the shape of the cross-sectional rings of the CNTs, as shown on the right side of Fig. 1.1(b) and (c). Connecting any other point (n, m) with the origin will result in a chiral CNT (Fig. 1.1(d)). Note that all the possible chiralities of CNTs in the graphene sheet in Fig. 1.1 correspond to the lattice points in between the two dashed lines. Connecting the origin with lattice points from outside the two dashed lines does not produce a different chirality. The diameter of a CNT resulting from a chiral vector (n, m) is given by [9]

$$d = a\sqrt{n^2 + m^2 + nm} \,, \tag{1.1}$$

where d is the diameter and a = 2.49 A is the lattice constant of the honeycomb lattice. Though the diameter of three CNTs in Fig. 1.1(a), (b) and (c) (10a, 10.4a and 9.64a, respectively) are almost the same, they show very different electrical properties. Now we will discuss the effect of chirality the CNT on electrical properties of the CNT.

The band structure of CNTs can be simply derived from that of graphene.

The tight binding solution of graphene was by derived by P. R. Wallace in 1947 [10].

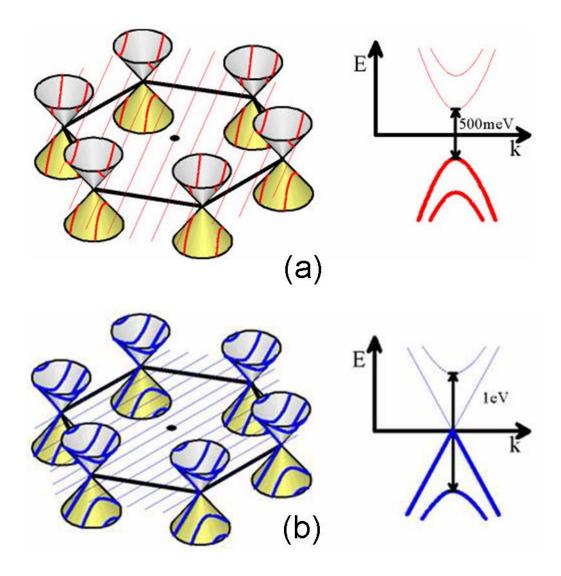

The band structure near the band edges is shown in Fig. 1.2, where the third dimension (vertical axis) represents energy. One can imagine six pairs of cones and

inverted cones meeting at six corners of a hexagon (i.e. K points). Thus, graphene can be called a zero-gap semiconductor. The energy dispersion relation at low energies near the band edge is given by [9]

$$E(k_x, k_y) = \pm \gamma_0 \sqrt{1 + 4\cos(\frac{\sqrt{3}k_x a}{2})\cos(\frac{k_y a}{2}) + 4\cos^2(\frac{k_y a}{2})},$$

1.2

where  $k_x$  and  $k_y$  are wavevectors,  $\gamma_0$  is a transfer integral, and a is the lattice constant.

When graphene is rolled into a (n, m) CNT the lattice points (n, m) and the origin correspond to the same carbon atom. Since the wavefunction is single-valued at the origin, a periodic boundary condition is imposed on the wavevector along the circumference of the CNT. Therefore, the wavevector associated with the  $C_h$ becomes quantized, while the wavevector associated with T remains unchanged for a long CNT. The boundary condition is expressed as  $k.C_h = 2\pi q$ , where q is an integer. This condition defines a set of allowed wavevectors k parallel to  $C_h$ . Thus, the energy bands consist of a set of one-dimensional energy dispersion relations. These wavevectors can be thought of as regularly spaced vertical planes in the band diagram of graphene in Fig. 1.2. The energy bands of CNTs can be obtained from crosssections of these vertical planes with the cone-shaped band structure. Intersection of a plane with a cone produces either a pair of straight lines (if sliced through origin) or a hyperbola (if slices miss the origin). If the vertical planes are aligned such that they do not intersect with the K points, all the sub-bands are hyperbolic with a finite bandgap (Fig. 1.3(a)). These CNTs are semiconducting with a direct band-gap. However, if some of the vertical planes intersect with the K points of the hexagon, the resulting first sub-band is linear with zero band-gap and all other sub-bands are hyperbolic (Fig. 1.3(b)). These CNTs are zero-gap semiconductors but they exhibit metallic

conduction at finite temperature because an infinitesimal energy is needed to excite carriers into the conduction band.

Figure 1.2 Schematic of band structure of 2-dminesional graphene.

CNTs can be divided in three different categories; metallic, semi-metallic, and semiconducting. The chirality  $C_h = (n, m)$  of a CNT can uniquely determine the category of the CNT. For the sake of completeness I will state classification conditions without deriving them (the full derivation can be seen in Ref. [9]). A CNT is semiconducting if the quantity (n - m) is not a multiple of 3. If (n - m) is a multiple of 3, two cases arise depending on whether or not (n - m) is also a multiple of 3p, where p is the highest common divisor of n and m. In case (n - m) is a multiple of 3 but not of 3p, the resulting CNT is metallic. When (n - m) is a multiple of both 3 and 3p, the resulting CNTs are semi-metallic or small-gap semiconducting. Semi-metallic CNTs are expected to be metallic from this simple analysis of band structure

but a small band gap (~ 10 meV) exists because of the curvature of the CNT. It has been observed that from an ensemble of CNTs, approximately 1/3 of CNTs are metallic or small-gap semiconducting and the remaining 2/3 of CNTs are semiconducting.

Within this simple analysis, the band gap of semiconducting CNTs  $(E_g)$  varies inversely with the diameter of CNTs [11, 12],  $E_g = \frac{2\gamma_0 a_1}{d}$ , where  $\gamma_0$  is a transfer integral,  $a_I$  is the nearest neighbor C-C distance in the graphene sheet, and d is the diameter of the CNT. Interestingly, to the first order, the band gap of a semiconducting CNT depends only on its diameter, not on its chirality. However, as we just discussed, CNTs of the same diameter can be either metallic or semiconducting depending on the chirality. Now I will briefly discuss the application of electric properties of CNTs in electronic devices.

Carbon nanotubes possess many remarkable properties. Instead of writing an exhaustive review, I will briefly mention some of the most outstanding and relevant properties. CNTs have been claimed to be one of the strongest and stiffest materials discovered so far. The Young's modulus of SWNTs along the axial direction has been reported to be as high as ~ 2 TPa [11-18] (compare with that of steel ~ 200 GPa). The absence of any dangling bonds makes CNTs stable at high temperatures and compatible with different chemical environments [19]. However, since all the atoms in a CNT are on the surface, they are free to interact with the environment. This property can be useful by functionalizing CNTs for sensing applications [20].

Figure 1.3 The band structure of the CNT can be obtained by applying the boundary conditions on the band structure of graphene. Slices represent the chiral vector of resulting CNTs. a) When slices (red lines) do not pass through any K point, the resulting sub-bands are hyperbolic with a finite bandgap, and a. semiconducting CNT is obtained. b) When slices (blue lines) pass through a K point, the resulting first subband is linear with zero bandgap, and a metallic CNT is obtained. (Courtesy of Prof Michael Fuhrer, UMD)

Defect-free CNTs have long mean free paths of for phonons ( $\sim 1.5 \, \mu m$  [21, 22]) and electron transport ( $\sim 1 \, \mu m$  [23-25]). Due to the first fact, CNTs, like graphite, are very good heat conductors. The thermal conductivity of CNTs at the room temperature is predicted to be as large as 6000 W/m-K (compare with that of

copper, 385 W/m-K). Long mean free paths of electrons makes CNTs excellent 1-dimensional materials to study various quantum phenomena. Ballistic transport has been observed in up to micron long metallic [23, 25] as well as semiconducting CNTs [24]. Even in the diffusive regime, the current densities as high as 10<sup>9</sup>A/cm<sup>2</sup> have been observed in both metallic [26] and semiconducting SWNTs [27].

Semiconducting CNTs have been studied extensively in a field effect transistor (FET) geometry [28-32]. In a CNT FET, the CNT is contacted by two metal electrodes (the source and the drain) forming a 1-dimensional device channel in between them. The third electrode (the gate) is separated from the device channel by a dielectric layer. One of the most common materials to make CNT FET with is a Si substrate with a thermally oxidized layer (SiO<sub>2</sub>, ~ few 100 nm thick). In a bottom gate FET geometry, the underlying conducting substrate (Si) is used as a gate electrode. In a top gate geometry, an additional metal electrode can also be deposited (separated by a dielectric) on the top of the CNT. Depending on the requirements of specific experiments, several other variations can be introduced in this basic FET geometry. To characterize a material in a FET, the response of gate bias on the device current is monitored. From this, the velocity and mobility of the charge carriers can be calculated. In a semiconducting CNT, the density of carrier in the conduction band can be modulated by the gate bias. These FETs show gate dependent device current. In contrast, the device current in a metallic CNT is independent of the gate bias. SWNTs have exceptionally large room temperature field-effect mobility ( $\sim 10^5 \text{ cm}^2/\text{Vs}$  [29]) and saturation carrier velocity ( $\sim 2 \times 10^7$ cm/s [27]). Semiconducting CNT, can also be turned off (~ nA) by controlling the

gate bias, thus producing a high on/off ratio of the devices. These properties make CNT very interesting nanoelectronics materials.

#### 1.3 Why Carbon Nanotube Thin Films Devices?

As discussed in the previous section, an individual semiconducting, single-walled CNT is an excellent semiconducting material with field-effect mobility as large as 10<sup>5</sup> cm<sup>2</sup>/Vs [29]. High quality FETs [28, 29, 31, 33] and circuits consisting of individual CNTs have been demonstrated [34]. However, it is difficult to fabricate devices and integrated circuits based on individual CNTs. Techniques such as "find and wire" [29, 35], AFM manipulation [36], mechanical transferring [37], self-assembly [38, 39] or electrophoresis [40] have been employed in the manipulation of individual CNTs and the fabrication of CNT devices. These techniques, however, are labor intensive and difficult to integrate into large-scale fabrication processes.

Additionally, the electronic characteristics of single CNTs are dependent on CNT chirality [8]. No known growth mechanism produces CNTs of precisely controlled chirality, even though success has been recently reported in controlled separation or growth of CNTs with desired characteristics. For example, CNTs of uniform diameter have been purified with potential scalability [41]; metallic CNTs in a FET geometry have been burned at high bias [42, 43]; metallic CNTs in a thin film have been etched by reactive ion etching [44]; and semiconducting CNTs have been selectively grown by a CVD method [45]. However, it remains difficult to incorporate individual CNTs with uniform characteristics in large-scale electronics. Therefore, a thin film of CNTs [46] presents an interesting alternative to single CNTs

as it avoids the difficulties of manipulating individual nanotubes. A CNT thin film also averages out the non-uniformities resulting from nanotube geometry variations.

In applications such as large area, flexible panel displays [47], disposable electronics (e.g. radio frequency identification (RFID)) [48, 49], biocompatible electronics and chemical sensors, the field-effect mobility of the device can be sacrificed for cost and ease of fabrication. Many organic semiconducting materials such as Pn and P3HT have been suggested as potential candidates in these applications. However, CNT thin films not only have better field-effect mobility [50], but they also exhibit the added advantages of environmental stability and large flexibility [51]. Thus, it is worthwhile to incorporate CNT thin films in large area flexible electronics on transparent substrates. Random networks of CNTs [46, 52] as well as aligned CNTs [39, 53-55] have been demonstrated as the potential component in such devices. While aligned CNTs can have the advantage of large channel current they are expected to have a poor on/off ratio due to the presence of metallic CNTs. In contrast, in random networks, the role of metallic CNTs could be more effectively subdued (using percolative effects) to obtain better on/off ratios [52].

#### 1.4 Overview of the Thesis

This thesis explores the scope of using CNT thin films as electronic materials.

This research involved a wide variety of fabrication and characterization techniques, which will be introduced in detail where they are first encountered in this thesis.

Most of the fabrication steps can be carried out in a moderately equipped clean-room. However, some procedures required very specific tools such as a nano-imprint

machine for transfer printing. Most of the characterization methods will also be familiar to someone with a basic knowledge of MOSFET engineering. However, some characterization tools, such as the photoelectron emission microscope, may be new to some readers. Ample discussion is dedicated to such tools and methods. This research also involved several kinds of simulations carried out by commercially available software packages. Major themes of the thesis can be divided into the following four sections:

#### a. Controlled growth and patterning of CNTs

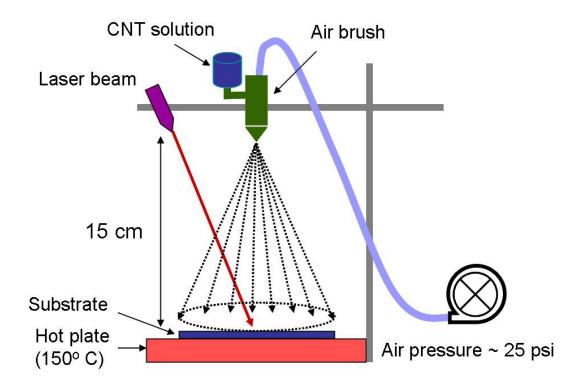

We primarily employed chemical vapor deposition (CVD) and airbrushing commercially obtained CNT solutions to obtain CNT thin films. Controlled growth of CNTs by CVD is discussed in Chapter 3. I will also describe and compare different techniques to pattern CNTs in Chapter 3. Chapter 6 discusses the methods of airbrushing CNT thin films and patterning airbrushed CNTs. A novel technique to pattern suspended CNTs is discussed in Chapter 4. These devices were used to study intrinsic properties of individual CNTs.

#### b. Assembling devices

In this research, I use transfer printing methods extensively to assemble various device geometries on plastic substrates. Transfer printing is used to pattern CNT thin films in Chapter 3, to assemble CNT thin film transistors (TFTs) in Chapter 4 and Chapter 6, and to fabricate suspended CNTs in Chapter 4. Thus, I will introduce the concept of transfer printing in Chapter 2 before anything else in this

thesis. Since photolithography is used in almost all the chapters, it is also introduced in Chapter 2.

#### c. Assessment of CNTs in electronics applications

The scope of CNT thin films as semiconducting materials is discussed in Chapter 5. The percolation effects in a CVD grown random network of CNTs are studies to optimize the device performance. This experiment is carried out keeping in mind the low-cost large electronic applications in mind and CNT thin films stand out as a potential candidate. The potential of using CNT thin films as electrode materials is discussed in Chapter 6. Airbrushed CNTs are used for this purpose. I also demonstrate all-carbon devices in Chapter 6, where the active layers as well as the electrodes are made from CNTs. The effect of the environment and dielectric layer in CNT devices is assessed in Chapter 4. This experiment involves electronic transport and low frequency noise measurements in pristine suspended CNTs.

#### d. Unique characterization of CNTs using PEEM

Finally, I will introduce a novel method to characterize the local field effects in CNT devices using PEEM in Chapter 8. This method also has the potential of being used to probe percolative effects in CNT thin film devices. Before that, I will introduce PEEM and its contrast mechanisms in Chapter 7. The voltage contrast of PEEM will also be characterized by studying a model system in Chapter 7.

In the next chapter, I will introduce the concept and procedure of transfer printing.

### Chapter 2: Transfer Printing

Since its inception in the 1950's, semiconductor integrated circuit technology, largely based on processing using photolithography, has dominated solid-state electronics. Photolithography is an expensive method that involves high temperature processes, is limited by optical resolution, and it is restricted by photoresist chemistry and inorganic semiconducting materials. Recently, alternative fabrication methods have been developed to meet requirements of new materials, device geometries and applications. Such techniques include ink-jet printing [56], soft-lithography (e.g. micro-contact printing [57, 58], replica molding [59]), nanoimprint lithography (NIL) [60] and transfer printing (TP) [61, 62]. These methods are compatible with organic as well as conventional inorganic electronic materials. Moreover, these methods have potential to incorporate a wide variety of device configurations.

Here, transfer printing is of particular interest. Transfer printing does not involve chemical processing and is scalable to high volume manufacturing processes (such as roll-to-roll printing [63]) on large areas of flexible substrates. It is important to understand that transfer printing is not a form of lithography but rather is used in conjunction with patterning techniques. Transfer printing offers sequential assembly of lithographically prepared device components incorporating a wide variety of materials. As a result, different components of the device can be independently fabricated on different substrates using different, even otherwise mutually incompatible, processing techniques. Most of the device components such as metal electrodes, CNT thin-films and organic semiconductor layers can be prepared

independently on inorganic substrates. Transfer printing allows sequential incorporation of the device components onto polymer and plastic substrates without affecting the quality of the original device components.

For logic circuits, it may be desirable to encapsulate the active layer in order to isolate any sensitive component from the environment. However, for sensors the active layer needs to be in communication with the environment. Therefore, both top and bottom gate CNT devices have been fabricated here by sequential assembly of components (electrodes, dielectric layer and patterned CNT thin films) by a transfer printing method. In this chapter I will first discuss general concepts and the scope of transfer printing methods. Then, I will describe some commonly used photolithography recipes to fabricate metal electrodes. These recipes will be frequently referred to in subsequent chapters.

#### 2.1 Introduction to Transfer Printing

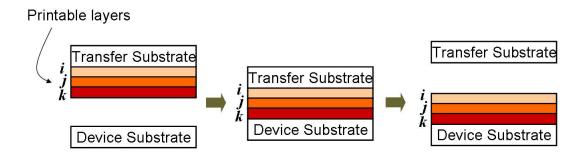

Transfer printing works on the simple principle of differential adhesion [61, 62]. The work of adhesion,  $W_A$  (cohesion,  $W_C$ ) is defined as the reversible energy gained in bringing together unit areas of two different (similar) materials from infinity to interfacial contact, in vacuum. For a successful transfer printing the following requirements need to be fulfilled:

1. When a uniform un-patterned printable layer is to be printed onto a device substrate from a transfer substrate the work of adhesion  $(W_A)$  at the interfaces between the printable layer (PL) and the device substrate (DS) needs to be larger than that between the printable layer and the transfer

substrate (TS). This condition can be written as:

$$W_A(PL/DS) > W_A(PL/TS)$$

2. The work of cohesion of a material is required to be higher than the work of adhesion for at least one of its two interfaces with other materials. If this fails, the material will be torn and fractions of material will be transferred to both substrates during a printing attempt. This condition applies to all the materials involved in the transfer printing and can be expressed as:

$$\begin{split} &W_C(TS) > W_A(TS / PL) \\ &W_C(PL) > W_A(TS / PL) \text{ or } W_C(PL) > W_A(DS / PL) \\ &W_C(DS) > W_A(DS / PL) \end{split}$$

3. Transfer printing can also be used to print stacked assemblies of multiple printable layers. In this case, in addition to the previous conditions mentioned above, the work of adhesion between the transfer substrate and the topmost printable layer must also be smaller than the work of cohesion of all the printable layers and the work of adhesion of all the interfaces between them:

$$W_A(TS/i) < W_C(i), W_C(j), W_C(k), W_A(i/j), W_A(j/k), W_A(k/DS)$$

4. To make a device in a useful geometry, the printable layer usually needs to be patterned. In that case, the transfer substrate and the device substrate also come in to contact during transfer printing. The work of adhesion between the two substrates must be less than the work of cohesion of both substrates to avoid mechanical damage when they are separated after transfer printing:

$$W_A(TS/DS) < W_C(DS), W_C(TS)$$

Finally, the transfer printing should not deteriorate the electronic,

mechanical and other relevant characteristics of the device components.

Fig. 4.1 shows a schematic of a transfer printing process when a stack of multiple printable layers is transferred to a device substrate. When the desired necessary works of adhesion and cohesion are optimized, the printable layers are transferred to the device substrate upon separation of the transfer and the device substrates. Multiple layered devices can also be fabricated by sequential transfer printing of one or a few printable layers at a time, thereby reducing some (but not all) constraints on sequential printing.

Figure 2.1 Schematic of transfer printing method used to transfer multiple printable layers from the transfer substrate to the device substrate.

Irrespective of the technology used, the transfer printing process should depend only on the above conditions. Since the substrate materials used in flexible electronics are polymeric, temperature (above the glass transition temperature,  $T_g$ ) combined with pressure is an efficient way to establish the differential adhesion. We

use a Nanonex 2500 imprint machine to achieve this. This machine uses a gas medium to control the pressure (up to 600 psi) and three 500 W tungsten halogen lamps as the heat source to control the temperature (up to 300 °C). The transfer substrate containing the printable layer is placed on the top of the device substrate with the printable player sandwiched between them. If required, the Nanonex 2500 manual contact aligner can be used to align the printable layer onto the device substrate prior to this step. Two silicone rubber sheets are used to hold the substrates together during transfer printing. The chamber is first evacuated to -14 psig for 3 minutes to create a vacuum between the rubber sheets, which are then mechanically sealed from the chamber throughout the subsequent steps. Then, the chamber is pressurized by N<sub>2</sub> gas and lamps are turned on to heat up the chamber. The temperature of the chamber is monitored by a thermocouple placed under the bottom rubber sheet, and is controlled by using a PID algorithm. The control unit also supports programming the sequence in which pressure and temperature are varied. For most of the applications discussed, the chamber is fully pressurized before turning on the lamps. But for some applications, it is desired to reach an intermediate pre-pressure before turning on the lamps and then attaining the final desired pressure. After transfer printing, the device substrate and the transfer substrate are gently separated.

#### 2.2 Preparation of the Metal Electrodes

The gate and the source and drain electrodes are patterned on Si transfer substrates using photolithography. The Au electrode material is incorporated with either addition of material by e-beam evaporation or subtraction of material using Au

etchant. The material additive technique is described first below, followed by a description of the additive layer.

The Si wafer piece is first cleaned with 1,1,2 trichloroethylene (TCE), acetone, methanol and isopropanol (IPA), followed by baking in a dry oven at 120 °C for 10 min. A negative photoresist (NR7 1500 PY) is spin coated at 4000 rpm for 1 min to produce 1.5 µm thick layer and then prebaked at 120 °C for 1 min. The photoresist is then exposed to UV light (12 mW/cm<sup>2</sup>) through an optical mask for 16 sec. The photoresist is post-baked at 120 °C for 1 min to accelerate the chain reactions that polymerize the exposed resist. The photoresist is developed in resist developer (RD6) for 15 sec. A Au film of the desired thickness (usually 100 nm) is then deposited by e-beam evaporation at 2 x 10<sup>-6</sup> Torr. The Au layer is exposed to reactive ion etching (RIE) using O<sub>2</sub> plasma for 5 min. This increases the surface roughness of the Au electrodes to improve their adhesion to polymeric substrates in transfer printing. Finally, the photoresist lift-off is carried out by a gently stirred resist remover (RR2) heated at 85 °C. Negative photoresist produces an under-cut in the side walls which is essential to the lift-off. Au is found to have very weak adhesion to the Si surface, possibly due to a thin water layer absorbed on the native oxide surface. In standard practice, a thin film of wetting layer (Cr or Ti) is deposited before Au deposition to improve adhesion. However, for this application, the wetting layer increases the work of adhesion such that the electrodes could not be printed to any of device substrates. Without the wetting layer, extra care is needed for the fragile Au electrodes to survive the lift-off. The minimum feature size achievable by the additive method is 1  $\mu$ m.

A subtractive approach has also been used to fabricate Au electrodes and successfully incorporate them into transfer printing. First, a Au film is deposited on a clean Si wafer piece by e-beam evaporation followed by exposure to  $O_2$  plasma to produce a rougher top surface. Then, a positive photoresist (OiR 908 35) is spin coated at 4000 rpm for 1 min to produce a 3.5 µm thick layer. The photoresist is prebaked at 90 °C and exposed to UV through a photomask. The photoresist is developed in OPR 6242 for 1 min. Then, the Au film, exposed through the windows in the photoresist layer, is etched away by Au etchant GE-1848 (Transene Company, Inc). Finally, the photoresist is removed by soaking in acetone for 5 min. Here, the photoresist does not and need not have an undercut in side walls since it does not involve a lift-off step. Moreover, the surface of the Si substrate can be treated with release layer before depositing the Au film, to further decrease the adhesion of Au to the Si substrate to promote the transfer printing. This is a robust technique to produce a high through-put of Au electrodes. However, since chemical etching is an isotropic process, the minimum feature size of electrodes must be larger than the thickness of the film. The minimum feature size achievable for 100 nm thick electrodes is 1 μm. If precise and smooth features of electrodes are not required, Au electrodes can also be directly deposited on a Si substrate (clean or RL treated) using a shadow mask. The minimum feature size achievable in this case is 100 μm.

We primarily use poly (methyl methacrylate) (PMMA) as the dielectric layer in transfer printed devices, but several other polymeric materials have been incorporated as proof-of-concept dielectric layers (Chapter 5). The solution of PMMA (MicroChem, molecular weight 950,000) in anisole with different

concentrations (4% and 7%) is spin-coated at different speeds (from 1500 to 4000 rpm) on a substrate to obtain dielectric layers of desired thickness (varying from 0.2 to 1.0 µm). The PMMA film is then baked on a hot plate (from 90 - 150 °C) to evaporate the solvent. Several polymeric device substrates have been successfully incorporated in transfer printing, but we primarily focused on a polyethylene terephthalate (PET) (Dupont Mulinex 453/700) substrate for flexible and transparent CNT devices. We purchased the PET film with a special surface treatment to enhance adhesion. The active area for CNT devices consisting of random network CNTs was patterned by various methods discussed in Chapter 2. Since the CNT films are not optically visible, 30 nm thick Ti alignment markers were fabricated on the SiO<sub>2</sub>/Si substrate using photolithography before CNT growth. These markers are used to align the CNT thin film to the device substrate in subsequent printing steps using a manual contact aligner.

#### 2.3 Surface Treatments to enhance Differential Adhesion

As-made device components may not have the necessary differential adhesion required for transfer printing. Therefore, we developed some techniques to control the work of adhesion of the printable layers and the substrates. The surface energy of a material can be enhanced by increasing the surface roughness and/or by modifying the surface chemically. We found that a Au electrode with the top surface exposed to O<sub>2</sub> plasma for 5 min resulted in more robust transfer printing to PET. Similarly, an untreated Au electrode did not print to an untreated PET surface very well, but transferred to an as-obtained pretreated PET film. We also employed a corona discharge technique to further improve the adhesion of PET films. Corona discharge,

however, makes the PET surface so adhesive that it also becomes irreversibly bonded to a Si transfer substrate during printing. Additional surface treatments can be done to the Si surface to avoid this problem. Such bonding problems were avoided by using fluorinated silane self-assembled monolayers (SAMs). We used a (tridecafluoro-1,1,2,2-tetrahydrooctyl) trichlorosilane SAM for this purpose. The silane end of the SAM attaches to the Si or SiO<sub>2</sub> surface and the fluorinated part of the SAM acts as a release layer for other materials. The SAM can be deposited on a surface either by vapor phase deposition or liquid phase deposition using microcontact printing. In the first case, the SAM was deposited by exposing the Si substrate to the vapors of the fluorinated silane. To mask the Au electrodes on the Si substrate from the vapors of the fluorinated silane, the Au surface was first treated with a thiol- terminated SAM (benzyl mercaptan). The thiol group attaches to the Au surface but not to the Si surface.

The procedure for adhesion modification is as follows: The Si substrate containing Au electrodes is placed in a home-made chamber, and evacuated to 50 mTorr. Then, benzyl mercaptan vapors are introduced to the chamber for 2 hours. The substrate is rinsed with IPA, and then the release layer is deposited in the same manner using another similar chamber. It was found that excessive exposure (more than 5 min) of the Si surface to fluorinated silane decreased the surface adhesion so much that even dielectric polymers such as PMMA could not be spin-coated. However, exposure for 2 min results in successful spin-coating of polymer as well as useful differential adhesion for transfer printing. Treated substrates are stored in a dry  $N_2$  box because the silane SAM is known to deteriorate in air.

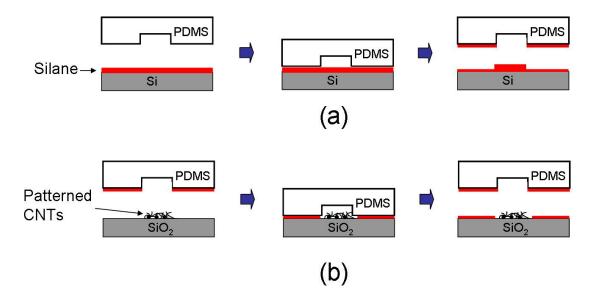

Figure 2.2 a) PDMS stamps are treated with release layer on Si substrate for 15 minutes. b) The PDMS stamps are aligned over patterned CNT thin films and release layer treatment is done on the area outside the CNT patterns by micro-contact printing.

A release layer treatment was also used on SiO<sub>2</sub> substrates containing CNT thin films. When CNT thin films are patterned by photolithography, the surface treatment is done by vapor phase deposition before removing the photoresist covering the patterned CNTs (see details in Chapter 3). In other patterning techniques, where CNTs are not covered by a photoresist, the release layer is patterned onto the Si substrate by micro-contact printing using polydimethylsiloxane (PDMS) stamps. PDMS stamps have been extensively used in similar applications in soft-lithography [57, 58].

The procedure for patterning the release layer by PDMS stamps is as follows: First, a 10 mM solution of (tridecafluoro-1,1,2,2-tetrahydrooctyl) trichlorosilane is prepared in anhydrous ethanol. PDMS stamps are made from the same master Si

stamp as used in Section 3.2.3 to make PET templates. A Slygard 184 silicone elastomer base is mixed with its curing agent by stirring vigorously for 5 min, creating air bubbles in the elastomer paste. To remove the bubbles, the paste was kept in a chamber that is slowly evacuated to approximately 100 mTorr. The elastomer is then poured onto the master Si stamp, placed in an oven and heated at 120 °C. The oven is slowly evacuated to remove the bubbles introduced during the pouring step. After curing the stamps in the oven for 1 hour, the master Si stamp and its PDMS negative are carefully separated. In parallel, the fluorinated silane solution is spread over a blank Si substrate in a dry N<sub>2</sub> chamber. After the solvent evaporates, the PDMS stamp is kept on the Si substrate for 15 minutes to treat the protruding parts of the stamp with silane, as illustrated in Fig. 2.2(a). The PDMS stamp is then aligned and brought into contact with the SiO<sub>2</sub>/Si substrate containing the patterned CNT thin films, such that the CNT patterns lie under the trenches in the stamp, as shown in Fig. 2.2(b). Since the same master stamp is used to make both the PET stamp to pattern the CNTs and the PDMS stamp to pattern the release layer, only the area outside the patterned CNTs is treated with the release layer. Therefore, the CNTs remain pristine. This step exposes the silane-treated stamp to air so the time involved in this step should be minimized. After 15 minutes of contact, the stamp and the substrate are separated and stored in dry  $N_2$  box till further use.

### Chapter 3 : Growth and Patterning of Carbon Nanotubes

In this chapter we describe the CNT growth process and fabrication techniques to pattern CNT thin films. Some of the commonly used techniques to synthesize CNTs are arc discharge [7], laser ablation [64], high pressure decomposition of carbon monoxide (HiPCO process) [65] and chemical vapor deposition (CVD) [66-71]. The CVD process has been shown to produce large quantities [72] of long single walled nanotubes [30, 73] with fewer defects [74]. CVD can also be used to control the average length of CNTs, the areal density of CNT thin films, and the distribution of CNT diameters by varying the growth duration, the density and the size of the catalytic particles. We used CVD grown CNT thin films as the active layer in CNT thin film transistors (TFTs). For the fabrication of CNT TFTs, it is desirable to pattern the CNT thin films to isolate the devices that are in close proximity to each other. Various fabrication techniques to pattern CVD-grown as well as airbrushed CNT thin films will be described in this chapter.

### 3.1 Carbon Nanotube Growth by Chemical Vapor Deposition

CNT thin films can be grown by CVD using many catalytic materials such as Fe, Ni, Co, Mo etc. [75]. We use iron nanoparticles on thermally oxidized Si (300 nm or 500 nm thick SiO<sub>2</sub>) substrates to grow CNTs. Iron catalytic particles can be dispersed on the growth substrate in various ways such as using supported catalyst [70], using ferric nitrate nanoparticles in isopropyl alcohol (IPA) [36], and using

ferritin encapsulated iron nanoparticles in de-ionized water (DI) [76, 77]. We used the last two methods to obtain iron nanoparticles.

The process for dispersing catalyst particles on a growth substrate is as follows: Anhydrous ferric nitrate is dissolved in IPA (70 µg/ml) and mixed well by stirring the solution overnight. Pieces of thermally oxidized Si (500nm SiO<sub>2</sub>) wafer pieces were cleaned with solvents (acetone, methanol and IPA) and dipped in the catalyst solution for 10 seconds. Then they were dipped in a hexane solution (mixture of 5% cyclo-hexane and 95% n-hexane) for 10 seconds. The hexane solution helps ferric nitrate nanoparticles to precipitate and stick to the SiO<sub>2</sub> surface. The resulting samples are ready for CVD growth. Ferritin catalyst solution was purchased from Atomate Corporation and stored at 2° to 8° C. Ferritin protein molecules have a spherical structure with a cavity inside, in which the iron nanoparticles are stored [77]. The concentration of the ferritin was diluted from 51 mg per ml aqueous solution (0.003 molar, as purchased) to 0.1 - 0.5 mg per ml by adding de-ionized water (DI). Wafer pieces of the growth substrates (thermally oxidized Si or quartz) were soaked in ferritin solution for 8 minutes. After drying the SiO<sub>2</sub> surface with nitrogen gas, the wafer pieces are ready for CVD growth as described below.

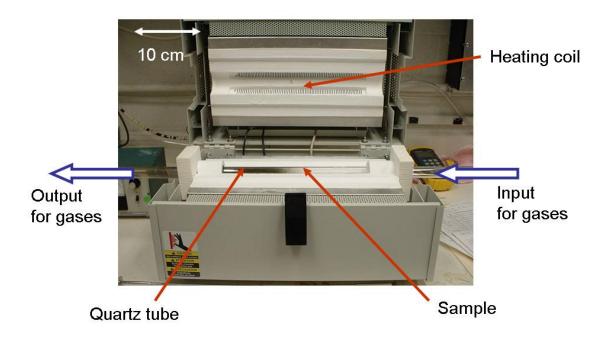

Ferrin nitrate soaked chips (roughly 0.5 cm x 0.5 cm) were put in a quartz boat and set in a single zone Lindberg/BlueM tube furnace with a 1 inch quartz glass tube, Fig. 3.1. O<sub>2</sub> was flushed out of the quartz tube before introducing the explosive gases. This is done by flowing argon gas for 10 minutes with the flow rate of 730 ml/min (Table 3.1). Then O<sub>2</sub> was purged out of the flammable gas lines by flowing

CH<sub>4</sub>, H<sub>2</sub> and C<sub>2</sub>H<sub>4</sub> for 3 minutes with a flow rate of 1000 ml/min. The furnace was then heated up to 850°C gradually through several ramping and soaking steps using an Omega CN4431 PID-temperature controller. The oven was soaked for 5 minutes at each of 3 intermediate temperatures (600 °C, 750 °C, 825 °C) to stabilize the temperature. Ar gas was kept flowing (730 ml/min) during heating. At 850 °C, CNTs were grown by flowing CH<sub>4</sub>, H<sub>2</sub> and C<sub>2</sub>H<sub>4</sub> in the furnace at the flow rates of 1900 ml/min, 1300 ml/min and 10 ml/min, respectively. The growth parameters are shown in Table 3.1. These flow rates have been reported to produce optimized long single walled nanotubes [30]. H<sub>2</sub> is believed to reduce iron nanoparticles whereas CH<sub>4</sub> and C<sub>2</sub>H<sub>4</sub> act as carbon feed-stock for CNT growth. The growth was done for 8 to 10 min and then the furnace was purged with Ar and simultaneously cooled down to room temperature. The resulting film is expected to have mostly single-walled CNTs with a ratio of one-third metallic CNTs to two-thirds semiconducting CNTs [30]. When using ferritin catalyst, an additional calcinations step is required to burn the ferritin covering off the iron nanoparticles. For that purpose the samples were initially heated up in air keeping both ends of the tube open at 850°C for 10 minutes before the growth. The furnace was cooled down to room temperature. Then, the procedure for the growth of CNTs is exactly same as described above, and shown in Table 3.1.

Figure 3.1 Chemical Vapor Deposition (CVD) set up for CNT growth.

| Action | Gas  | Flow        | Temperature     | Duration |

|--------|------|-------------|-----------------|----------|

| Purge  | Ar   | 729 ml/min  | RT              | 10 min   |

| Heat   | Ar   | 729 ml/min  | RT – 600° C     | 10 min   |

|        | Ar   | 729 ml/min  | 600° C – 750° C | 5 min    |

|        | Ar   | 729 ml/min  | 750° C – 825° C | 5 min    |

|        | Ar   | 729 ml/min  | 825° C – 850° C | 10 min   |

| Grow   | H2   | 1900 ml/min | 0500 C          | 8-10 min |

|        | CH4  | 1300 ml/min | 850° C          |          |

|        | C2H4 | 10 ml/min   |                 |          |

| Cool   | Ar   | 729 ml/min  | 850° C - RT     | ~2 hours |

Table 3.1 Growth procedure of CNTs using CVD.

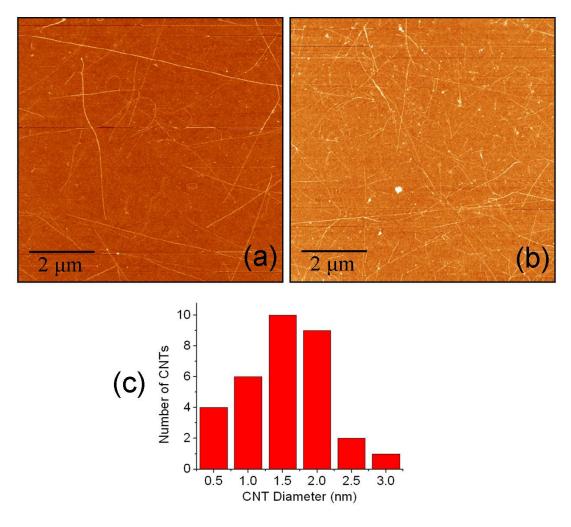

Figure 3.2 AFM images of CNT thin film grown by CVD using a) ferric nitrate, and b) ferritin catalyst. c) Diameter histogram of CNT grown using ferric nitrate.

Fig. 3.2(a) and (b) show AFM pictures of CNT thin films grown from ferric nitrate and ferritin catalyst, respectively. CNT thin films grown from ferritin catalyst tend be slightly denser than those from ferric nitrate for the above mentioned concentrations. The band gap of a semiconducting CNT is known to depend on its diameter [11, 12] and smaller diameter CNTs are reported to higher energy band-gap leading to larger on/off ratio of the devices. So, it is desirable for our purpose to have CNTs within a narrow range of small diameter. The diameter of a CNT is known to

correlate with the diameter of the catalyst particle [77-81]. Since ferritin protein cavities restrict the size of iron nanoparticles, the resulting catalyst particles are expected to have smaller and more consistent size [82]. Ferric nitrate catalyst has also been shown to produce mostly single walled CNTs. The diameter of the CNTs was obtained from the height profile in AFM images. A histogram of the diameter of 35 CNTs (grown from ferric nitrate) shows a peak around 1.5 nm, see Fig. 3.2(c). This diameter distribution suggests that most of the CNTs are single walled. The average diameter of the CNTs grown by ferritin was found to be 1.4 nm from analysis of AFM images (Fig. 3.2(c)).

### 3.2 Controlling the Density Carbon Nanotubes

The density of the CNTs is expected to depend on the growth time, flow rate of feed gases and the concentration of the catalyst solution. A direct linear correlation was not observed between the density of CNTs and the growth time. It has been suggested that CNTs stop growing after some time and gas flow for longer duration has less and less effect on CNT density. Most of the CNT thin films reported in this thesis were prepared by 8 to 10 min growth. The density of CNTs in a thin film was controlled by two methods: by varying the ratio of feed gases and by varying the concentration of the catalyst. Controlling the density of CNTs by varying the concentration of ferritin catalyst was difficult, due to solution to solution variability and handling issues. Therefore, ferric nitrate catalyst was used in both methods.

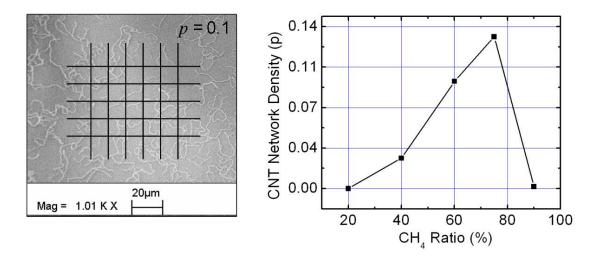

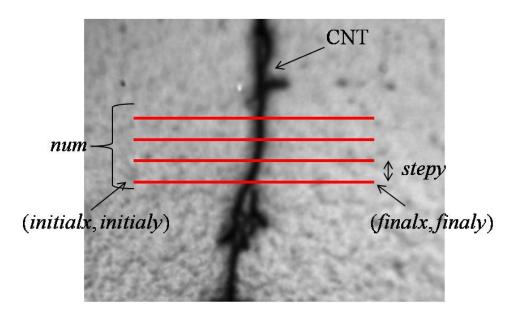

It is usually difficult and unreliable to characterize the density of CNTs by counting the number of CNTs per unit area. Thus, we employ here a grid method to determine the density of nanotubes. A two dimensional grid of lines was overlaid on SEM images of CNTs as shown in Fig. 3.3(a). The density of the CNT network is characterized by an average density of intersecting points, p (the number of intersections per unit gridline length) between CNTs and the grid. We simulated random networks in Interactive Data Language (IDL 6.0) to confirm that the parameter p correctly characterizes the density (number of lines per unit area). The average density of intersections between the grid and a network of random lines (generated by IDL) varied linearly with the density of the network. The grid spanned over an area (100  $\mu$ m x 100  $\mu$ m) larger than average length of CNTs (7  $\mu$ m). The total length of grid lines was also chosen sufficiently large,  $\sim$  1.2 mm. The average density parameter p was obtained from grid analysis at two opposite corners of each sample.

In the first method, the density of CNTs thin films was controlled by relative composition of the gases  $H_2$  and  $CH_4$  (no  $C_2H_4$ ) [76] while keeping the total gas flow constant at 2000 ml/min. The concentration of ferric nitrate was kept 70 µg/ml. The parameter p is plotted against ratio of  $CH_4$  to the total gas (in absence of  $C_2H_4$ ) flow rate in Fig. 3.3(b). The highest density of CNTs (p = 0.13, i.e. roughly 50 CNT/100 µm²) was achieved at 65%  $CH_4$  after which the yield of CNTs exhibited a sudden drop, probably due to poisoning of the catalyst by excessive carbonation [76]. A small amount of  $C_2H_4$  (3 ml/min) could be introduced in the furnace to obtain denser CNT films.

Figure 3.3 a) An SEM image of CNT thin film grown by 40%  $H_2$  and 60%  $CH_4$  with total gas flow of 2000 ml/min. Overlaying grids is used to characterize the density of CNT mat. The image has p=0.1 intersections/ $\mu$ m, which corresponds to roughly 40 CNTs/100  $\mu$ m<sup>2</sup>. b) CNT network density as a function of ratio of  $CH_4$  to total gas feed.

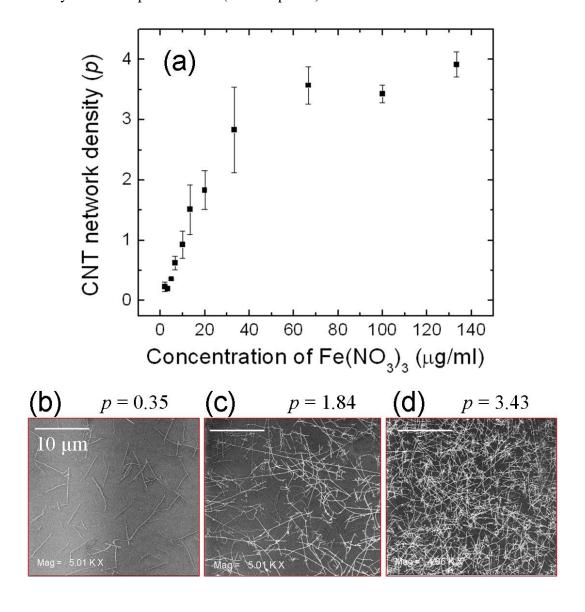

In the second method, the density of CNT was controlled by varying the concentration of the ferric nitrate solutions. The gas flow rate of CH<sub>4</sub>, H<sub>2</sub> and C<sub>2</sub>H<sub>4</sub> was kept at 1900 ml/min, 1300 ml/min and 8 ml/min, respectively. Ferric nitrate solutions of ten different concentrations (varying from 2  $\mu$ g/ml to 133  $\mu$ g/ml) were prepared and dispersed on different growth substrates. CNTs were grown for 10 min on all the substrates. Fig. 3.4(a) shows the variation in the average density of CNTs (*p*) as a function of concentration of the catalyst. Fig. 3.4(b), (c) and (d) show SEM images of CNT thin films obtained from catalyst concentration of 2  $\mu$ g/ml, 20  $\mu$ g/ml and 66  $\mu$ g/ml, respectively. It is interesting to note that CNT density initially increases rapidly with the concentration and then becomes almost constant for concentrations higher than 66  $\mu$ g/ml. The maximum density of CNTs achievable from the first method was 0.14 intersections/ $\mu$ m. (We found that CNTs with density higher density is needed for high quality CNT thin film devices (see Chapter 4)) This

method was used to produce CNT thin films with densities in a broad range varying from p = 0.35 intersections/ $\mu$ m (Fig. 3.4(b)) to p = 3.43 intersections/ $\mu$ m (Fig. 3.4(d)). These CNT thin films were used in an experiment to study the effect of the CNT density on device performance (see Chapter 4).

Figure 3.4 a) Average density of CNT network (p) is plotted against the concentration of ferric nitrate solution. The error bars correspond to the difference in the density of CNTs at two opposite corners of a growth substrate. b), c) and d) SEM image of CNT thin film with p=0.35, 1.84 and 3.43 intersection/ $\mu$ m, respectively. The scale bar in all the images is 10  $\mu$ m.

### 3.3 Techniques for Patterning Carbon Nanotube Thin Films

It is essential to pattern CNT thin films to make useful arrays of devices. Even when study of a single device is intended, patterning the CNT film is important. For example, when wafer pieces are immersed in catalyst solution, the CNTs are expected to grow everywhere on the SiO<sub>2</sub> surface, including the edges. It was observed that the percolating network of CNTs makes a conducting path to the Si back gate. Thus, it is undesirable to make CNT thin film transistors directly on the growth substrate without patterning the CNT thin film. Patterning the CNT thin films is also needed to define geometrical parameters of the device, such as the channel length and the channel width. Various techniques to pattern CNT thin films will be discussed in this section.

### 3.3.1 Photolithographic Patterning of CVD grown CNTs

Photolithography offers a straightforward way to pattern CNT films. Since the CNT thin films are not sufficiently optically visible for using a contact aligner, prior to CNT growth 30 nm thick Ti alignment markers were fabricated on the SiO<sub>2</sub>/Si substrate by photolithography. To pattern the CNT thin film, a photoresist (positive toned OiR 908 35, Fujifilm or negative toned NR7 1500 PY, Futurrex Inc.) was spin coated over the SiO<sub>2</sub>/Si substrate surface containing the CNT thin film. The photoresist was exposed to UV light (12 mW/cm<sup>2</sup>) through a photomask to define desired shape and size (e.g. 200 μm square areas) using a Karl Suss Mask Aligner. After developing the photoresist, the film area to be retained was protected by the remaining photoresist. The CNTs outside the covered area were burned by reactive

ion etching (RIE) using an  $O_2$  plasma (power = 100 W, pressure = 200 mTorr, PlasmaTherm 790 Series) for 1 min. Now the photoresist can be removed by acetone and we get a patterned CNT film. Schematic of this procedure are shown in the first two steps in Fig. 3.5.

The as-patterned CNT film can be used to make devices on the SiO<sub>2</sub> substrate. However, to make patterned CNT films compatible with the transfer printing process (see Chapter 2) we need to do a surface treatment to the SiO<sub>2</sub> substrate. Before removing the remaining photoresist that covered the patterned film, the exposed SiO<sub>2</sub>/Si surface was treated with a (tridecafluoro-1,1,2,2-tetrahydrooctyl) trichlorosilane self-assembled monolayer (SAM). This SAM treatment creates a release layer to decrease the work of adhesion of the SiO<sub>2</sub> surface to establish a desirable differential adhesion against device substrates [61] (see Section 2.3 for details). Finally, the remaining photoresist was washed away with acetone and the resulting CNT film is ready to be transfer printed. A schematic of this process is shown in the last two steps in Fig. 3.5.

A possible disadvantage of this patterning technique is that the CNTs have been exposed to various chemical treatments. The effect of chemical processing on transport properties of CNT TFTs is discussed in Appendix B. Moreover, the SAM layer on the SiO<sub>2</sub>/Si surface is not compatible with the annealing process to remove possible surface contaminants [83]. Therefore, patterning processes that do not expose the CNT film to resist processing chemicals have been developed. Two such patterning methods are (1) CVD-grown CNT films from pre-patterned catalyst and

(2) transfer printing of CVD grown CNTs to polymer stamps. These techniques have the advantage that no chemicals come in contact with the CNTs during the patterning.

Figure 3.5 Photolithography and reactive ion etching are used to pattern a CNT thin film after grown of CNTs where a release layer is applied prior to lift-off to aid transfer printing.

Figure 3.6 SEM micrograph of the edge of a CNT thin film patterned by photolithography.

### 3.3.2 Pre-patterning of the Catalyst

As stated above, it is desirable to develop a patterning technique by which CNTs are not left with residues of resist-processing chemicals. This can be achieved by patterning catalyst nanoparticles prior to CNT growth. Isolated CNTs have been grown by using patterned catalysts [71, 84]. Here we wish to grow a patterned CNT thin film using a similar process. We used different processing chemicals here.

### 3.3.2.1 Pre-patterning the Catalyst using a Photoresist

In this case, CNT films were grown using pre-patterned ferritin catalyst. A positive photoresist (OiR-908 35) was spin coated onto a SiO<sub>2</sub>/Si substrate. The photoresist was exposed through a photomask containing 500 µm square features. After developing the photoresist, the ferritin was deposited onto the patterned SiO<sub>2</sub>/Si substrate by soaking in an aqueous solution of ferritin (0.5mg/ml) for 8 minutes. CNTs were then grown by CVD as described earlier in this chapter. This patterning process is shown schematically in Fig. 3.7.

Fig. 3.8 shows AFM and SEM images of the patterned CNT thin films. A continuous and uniform CNT thin film can be seen in the patterned area. There is, however, a dense strip of CNTs on the edge of the patterned area, possibly due to excessive deposition of the catalyst near the edge of patterned photoresist. There are also some CNTs grown outside the patterned area because during the lift-off step some ferritin molecules can stick back to the substrate. The density of the CNTs outside the pattern is reduced by facing the substrate down and slowly moving it up during lift-off. CNTs outside the patterned area are too sparse to make any

37

percolative network. Thus, multiple devices fabricated on a substrate are still electrically isolated from each other.

Figure 3.7 Photolithography is used to pattern the ferritin catalyst before CNTs are grown.

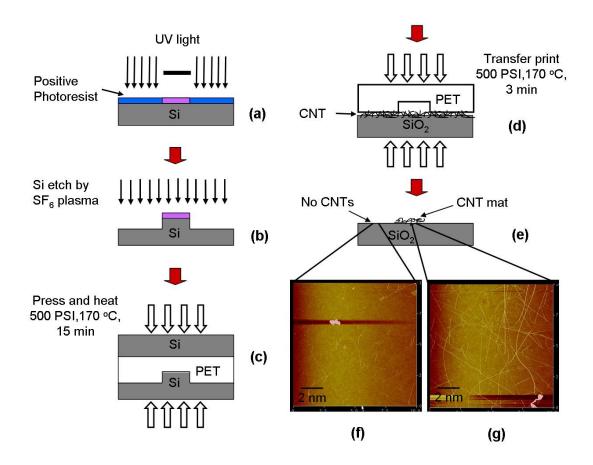

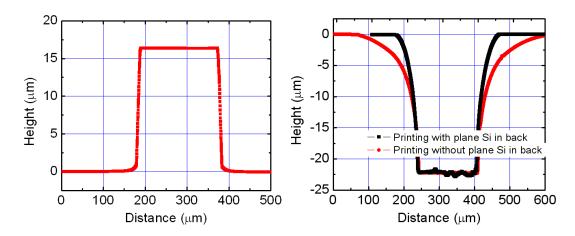

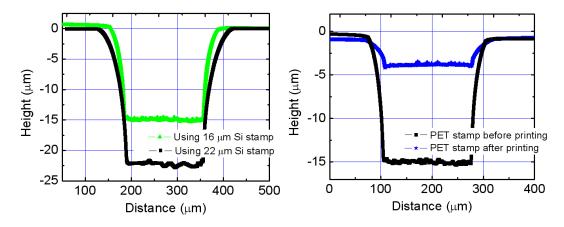

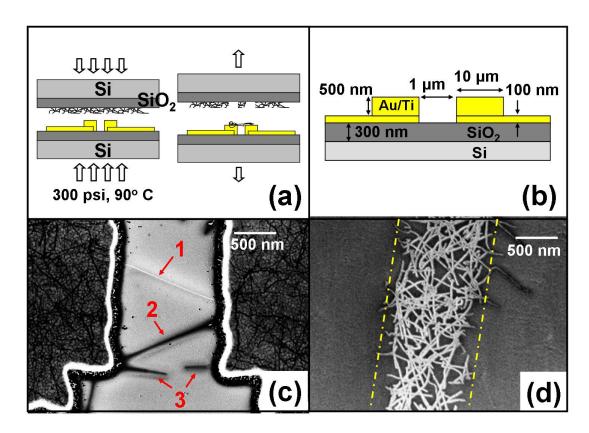

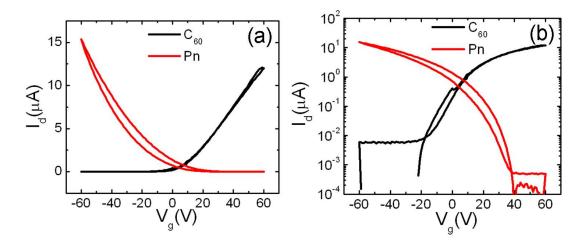

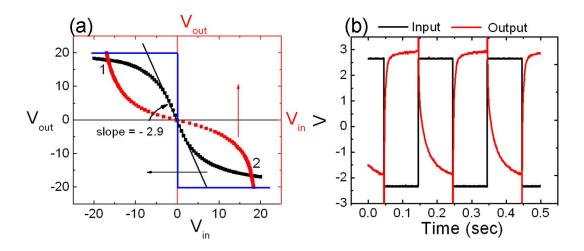

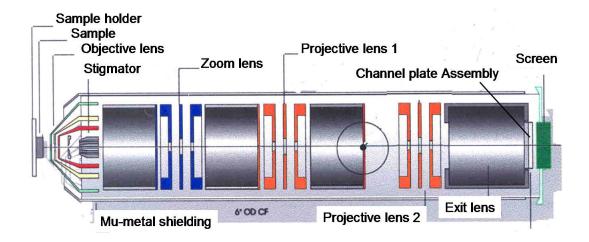

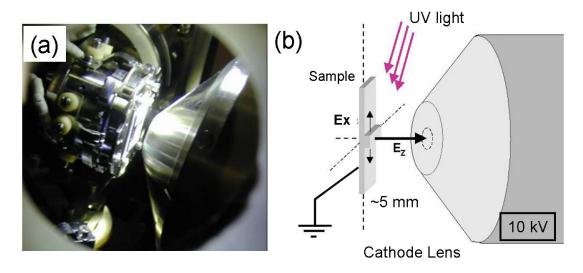

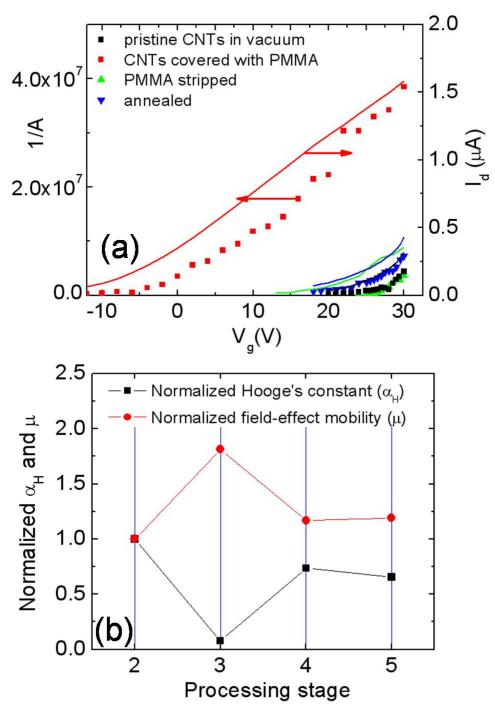

Here, we cannot treat the SiO<sub>2</sub> surface with the release layer in gaseous phase because the CNTs would also get exposed. CNT thin films on untreated SiO<sub>2</sub> substrate are not compatible with a reliable and complete transfer printing process (CNTs do transfer print to PET partially). However, the surface treatment on these patterned CNT thin films can be carried out by micro-contact printing of the release layer using elastomeric templates. This process is explained in detail in Section 2.3.