#### ABSTRACT

| Title of dissertation:    | HARDWARE DESIGN, PROTOTYPING<br>AND STUDIES OF THE EXPLICIT<br>MULTI-THREADING (XMT) PARADIGM |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

|                           | Xingzhi Wen<br>Doctor of Philosophy, 2008                                                     |  |  |  |

| Dissertation directed by: | Professor Uzi Vishkin                                                                         |  |  |  |

Department of Electrical and Computer Engineering

With the end of exponential performance improvements in sequential computers, parallel computers, dubbed "chip multiprocessor", "multicore", or "manycore", has been introduced. Unfortunately, programming current parallel computers tends to be far more difficult than programming sequential computers. The Parallel Random Access Model (PRAM) is known to be an easy-to-program parallel computer model and has been widely used by theorists to develop parallel algorithms because it abstracts away architecture details and allows algorithm designers to focus on critical issues. The eXplicit Multi-Threading (XMT) PRAM-On-Chip project seeks to build an easy-to-program on-chip parallel processor by supporting a PRAM-like programming (performance) model. This dissertation focuses on the design, study of the micro-architecture of the XMT processor as well as performance optimization.

The main contributions are:(1) Presented a scalable micro-architecture of the XMT based on high level description of the architecture. (2) Designed a synthesizable Verilog HDL (hardware design language) description of XMT, which lead

to the first commitment to the silicon of the XMT processor, a 75 MHz XMT FPGA computer. With the same design, we expect to see the first XMT ASIC processor using IBM 90nm technology. (3) Proposed and implemented some architecture upgrades to the XMT: (i)value broadcasting, (ii)hardware/software comanaged prefetch buffers and (iii) hardware/software co-managed read-only buffers. (4) Quantitatively studied the performance of XMT using non-trivial application kernels with the 75 MHz XMT FPGA computer, in addition, the performance of a 800MHz XMT processor is projected. (5) The choice of not having local private caches in the XMT architecture is studied by comparing current architecture with an alternative one that includes conventional coherent private caches.

# HARDWARE DESIGN, PROTOTYPING AND STUDIES OF THE EXPLICIT MULTI-THREADING (XMT) PARADIGM

by

# Xingzhi Wen

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2008

Advisory Committee: Professor Uzi Vishkin, Chair/Advisor Professor Joseph F. JaJa Associate Professor Manoj Franklin Associate Professor Clyde Kruskal Assistant Professor Tali Moreshet © Copyright by Xingzhi Wen 2008

# Dedication

To my wife, Lihua, my daughter, Annie and my parents.

#### Acknowledgements

I would like to express my gratitude to my advisor, Professor Uzi Vishkin, for his guidance and support throughout my doctoral studies. I greatly appreciate the research opportunity he provided to me. Dr. Jacob and Dr. Franklin provided many good suggestions for the research. Dr. Yeung and Dr. Qu also gave me very helpful comments about my work and Dr. Moreshet provided many valuable comments on an earlier version of this dissertation.

Michael Horak graciously found the time to help with English editing in spite of being extremely busy with finalizing his own M.S. thesis. I also want to thank Aydin Balkan, George Caragea, Fuat Keceli, Mary Kiemb, and Alexandros Tzannes as well as other members of the XMT team.

I would like to thank my wife, Lihua and my parents for their patience and encouraging words. Without their support, I would not have finished this long journey.

# Table of Contents

| Li | List of Figures ix                |                                                             |                                                                                                                                  |                                                                             |  |

|----|-----------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| Li | st of .                           | Abbrev                                                      | iations                                                                                                                          | xii                                                                         |  |

| 1  | Intro<br>1.1<br>1.2<br>1.3<br>1.4 | What<br>Chip                                                | n<br>el Computing                                                                                                                | 4<br>5<br>8<br>8                                                            |  |

| 2  | Arch 2.1                          | Micro<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6 | re of the XMT Processor<br>-architecture of the XMT Processor                                                                    | 18<br>19<br>20<br>22<br>24<br>26                                            |  |

|    |                                   | $2.2.1 \\ 2.2.2 \\ 2.2.3$                                   | SPMD Programming ModelParallel and Serial Mode SwitchObservation on Synchronization Needs of Nested Spawn (sspawn)Implementation | 27                                                                          |  |

|    | 2.3                               | Featur<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5         | res of the XMT Processor Memory Hierarchy                                                                                        | 33<br>33<br>34<br>36<br>38                                                  |  |

|    | 2.4                               | Macro<br>2.4.1<br>2.4.2                                     | <ul> <li>architecture of the XMT Processor</li></ul>                                                                             | $\begin{array}{c} 41 \\ 43 \\ 43 \\ 44 \\ 46 \\ 47 \\ 48 \\ 49 \end{array}$ |  |

| 3 | XM                              | T FPG   | A Prototype and Performance Evaluation                                                                                                 | 52       |  |  |  |

|---|---------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|   | 3.1                             | Specif  | fications of the XMT FPGA Prototype                                                                                                    | 52       |  |  |  |

|   |                                 | 3.1.1   | Partitioning the XMT Processor                                                                                                         | 52       |  |  |  |

|   |                                 | 3.1.2   | Specification of the XMT FPGA Prototype                                                                                                | 53       |  |  |  |

|   |                                 | 3.1.3   | Envisioned XMT Processor                                                                                                               | 59       |  |  |  |

|   | 3.2                             | ımarks  | 61                                                                                                                                     |          |  |  |  |

|   |                                 | 3.2.1   | Matrix Multiplication (mmul)                                                                                                           | 62       |  |  |  |

|   |                                 | 3.2.2   |                                                                                                                                        | 62       |  |  |  |

|   |                                 | 3.2.3   | Breadth-First Search (BFS)                                                                                                             | 63       |  |  |  |

|   |                                 | 3.2.4   |                                                                                                                                        | 64       |  |  |  |

|   |                                 | 3.2.5   | Array Summation (add)                                                                                                                  | 65       |  |  |  |

|   |                                 | 3.2.6   |                                                                                                                                        | 65       |  |  |  |

|   |                                 | 3.2.7   | $Convolution (conv) \dots \dots$ | 66       |  |  |  |

|   |                                 | 3.2.8   |                                                                                                                                        | 66       |  |  |  |

|   | 3.3                             | Perfor  | mance Analysis                                                                                                                         | 67       |  |  |  |

|   |                                 | 3.3.1   | Speedup relative to Serial Execution on MTCU and AMD                                                                                   |          |  |  |  |

|   |                                 |         | Opteron                                                                                                                                | 67       |  |  |  |

|   |                                 | 3.3.2   | What is Happening inside the XMT Processor?                                                                                            | 71       |  |  |  |

|   |                                 |         | 3.3.2.1 Bandwidth Utilization in Memory Access                                                                                         | 71       |  |  |  |

|   |                                 |         | 3.3.2.2 Breakdown of Execution Cycles                                                                                                  | 74       |  |  |  |

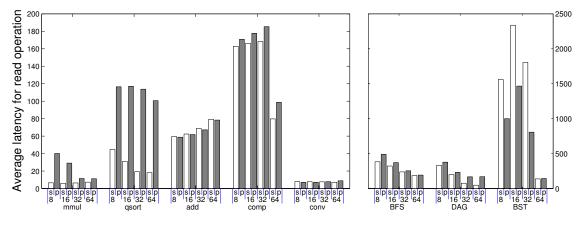

|   |                                 |         | 3.3.2.3 Average Latency for Read Operations                                                                                            | 76       |  |  |  |

|   |                                 | 3.3.3   | Wall Clock Time Comparison between Projected XMT Pro-                                                                                  |          |  |  |  |

|   |                                 |         | cessor and AMD Opteron                                                                                                                 | 79       |  |  |  |

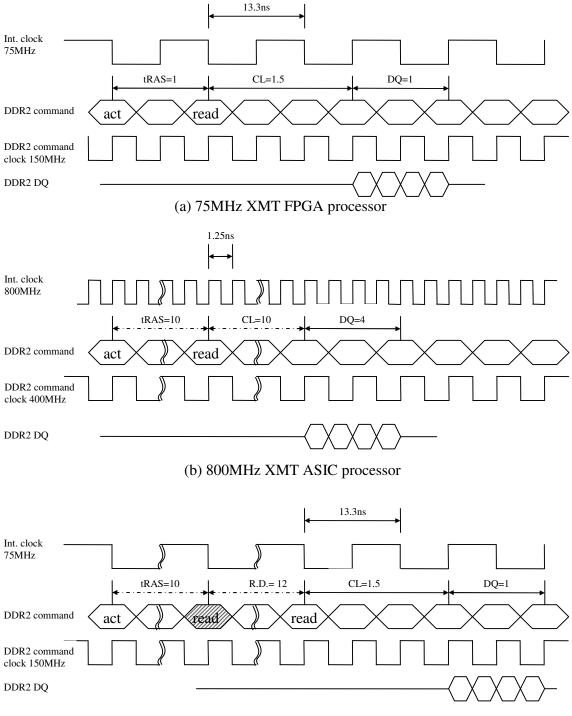

|   |                                 |         | 3.3.3.1 DDR2 SDRAM Basics                                                                                                              | 81       |  |  |  |

|   |                                 |         | 3.3.3.2 Slowing Down the DDR2 SDRAM                                                                                                    | 82       |  |  |  |

|   |                                 |         | 3.3.3.3 Validation of the Projection                                                                                                   | 86       |  |  |  |

|   |                                 |         | 3.3.3.4 Envisioned Performance of XMT ASIC 800MHz with                                                                                 |          |  |  |  |

|   |                                 |         | DDR2-800                                                                                                                               | 87       |  |  |  |

| 4 | т                               | 101     |                                                                                                                                        | 00       |  |  |  |

| 4 |                                 |         | es vs Shared Caches in XMT                                                                                                             | 89<br>89 |  |  |  |

|   | 4.1 Why Not Use Private Caches? |         |                                                                                                                                        |          |  |  |  |

|   | 4.2                             |         |                                                                                                                                        | 91       |  |  |  |

|   |                                 | 4.2.1   | Directory                                                                                                                              |          |  |  |  |

|   | 4.0                             | 4.2.2   |                                                                                                                                        | 95       |  |  |  |

|   | 4.3                             |         |                                                                                                                                        | 98       |  |  |  |

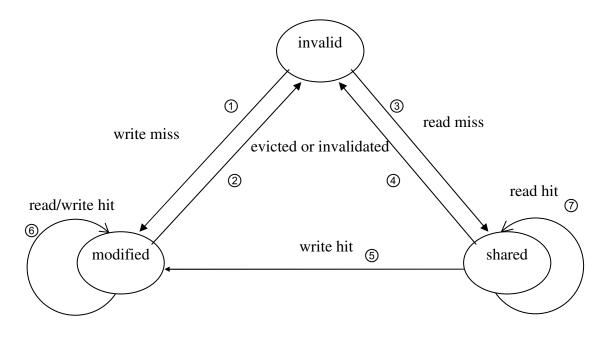

|   |                                 | 4.3.1   | Program Execution Cycle Count and Speedups 1                                                                                           |          |  |  |  |

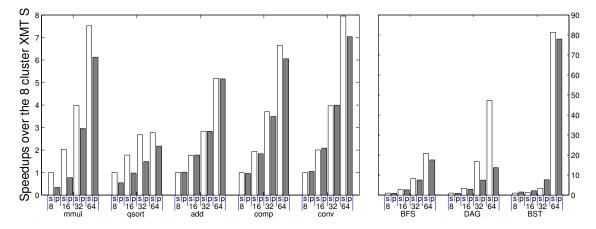

|   |                                 | 4.3.2   | Traffic Volume in the Interconnection Network                                                                                          |          |  |  |  |

|   |                                 | 4.3.3   | Average Latency for Read Operation                                                                                                     |          |  |  |  |

|   |                                 | 4.3.4   | Summary of XMT P and S                                                                                                                 | 107      |  |  |  |

| 5 | Con                             | clusion | and Future Work                                                                                                                        | 109      |  |  |  |

| 0 | 5.1                             |         |                                                                                                                                        | 105      |  |  |  |

|   | $5.1 \\ 5.2$                    |         | e Work                                                                                                                                 |          |  |  |  |

|   | 0.2                             | I dout  |                                                                                                                                        |          |  |  |  |

| А | Intro      | oductio  | n to the Verilog Model of the XMT Prototype | 113   |

|---|------------|----------|---------------------------------------------|-------|

|   | A.1        | Cluste   | rs                                          | . 113 |

|   | A.2        | Maste    | r Cluster                                   | . 115 |

|   | A.3        | Interco  | onnection Network                           | . 116 |

|   | A.4        | Cache    | Module                                      | . 116 |

|   | A.5        | Interfa  | ace of XMT Processor                        | . 117 |

|   | A.6        | Differe  | ences in XMT ASIC and XMT FPGA              | . 117 |

| - | 07         |          |                                             |       |

| В | Clus       |          |                                             | 118   |

|   | B.1        |          | iew                                         |       |

|   | <b>D</b> a |          | Interface of Cluster                        |       |

|   | B.2        |          | ction Buffer                                |       |

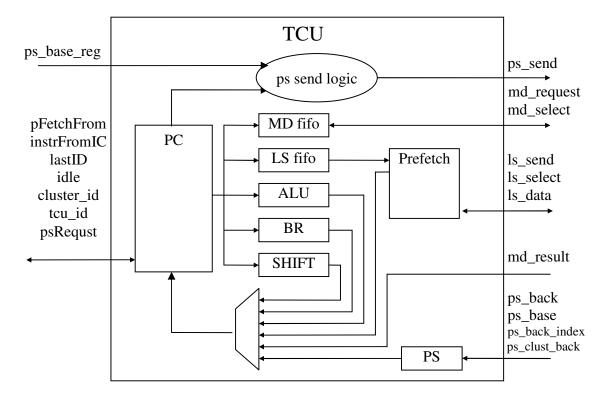

|   | B.3        |          | d Control Unit (TCU)                        |       |

|   |            |          | Interface of the TCUs                       |       |

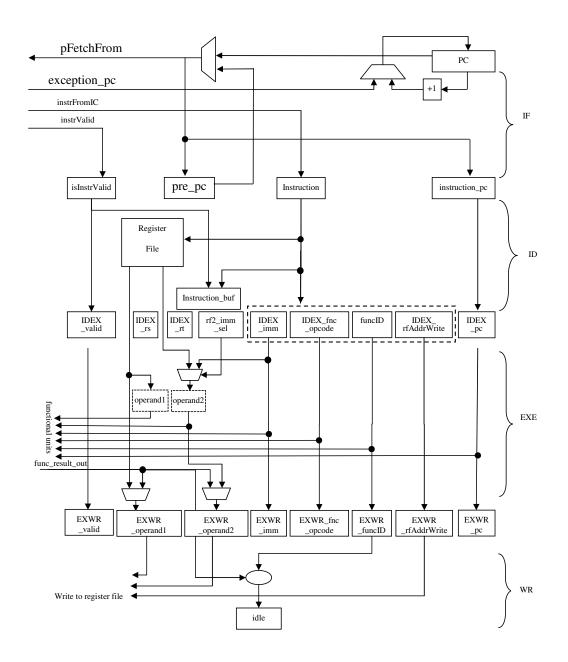

|   |            | B.3.2    | Program Counter (PC)                        |       |

|   |            | B.3.3    | Performance Counter Register Files          |       |

|   |            |          | B.3.3.1 How to use PCRFs?                   |       |

|   | B.4        | Arbite   | PTS                                         |       |

|   |            | B.4.1    | Basic Arbiter                               |       |

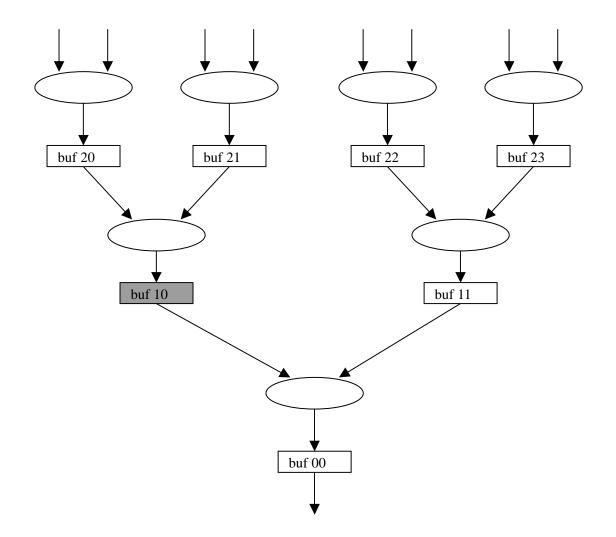

|   |            | B.4.2    | Basic Arbiter Tree                          |       |

|   | B.5        | Memo     | ry Address Hashing                          | . 139 |

|   | B.6        | Functi   | onal Units                                  |       |

|   |            | B.6.1    | ALU                                         | . 143 |

|   |            |          | B.6.1.1 Instructions Executed by ALU        | . 144 |

|   |            | B.6.2    | Shift Functional Unit(SFT)                  | . 145 |

|   |            |          | B.6.2.1 Instructions Executed by SFT        | . 146 |

|   |            | B.6.3    | Branch Functional Unit(BR)                  | . 147 |

|   |            |          | B.6.3.1 Instructions Executed by BR         | . 147 |

|   |            |          | B.6.3.2 Behavioral Description of BR        | . 148 |

|   |            | B.6.4    | Multiplication/Division Functional Unit(MD) | . 148 |

|   |            |          | B.6.4.1 Instructions Executed by MD         | . 149 |

|   |            |          | B.6.4.2 Behavioral Description of MD        | . 150 |

|   |            | B.6.5    | Prefix-sum                                  |       |

|   |            | B.6.6    | Load/Store                                  |       |

|   | B.7        | Four B   | Enhancements                                |       |

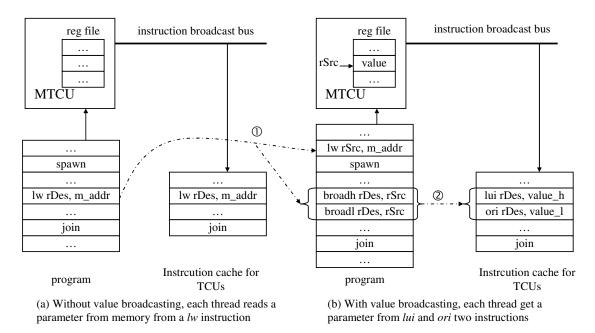

|   |            | B.7.1    | Broadcasting                                | . 152 |

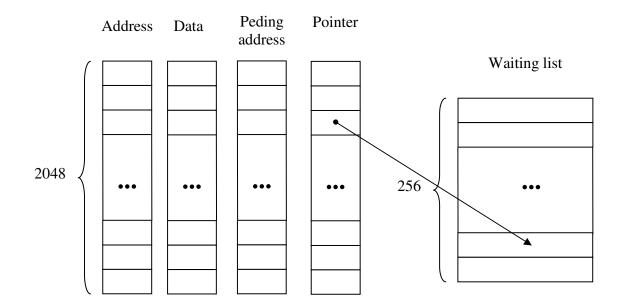

|   |            | B.7.2    | Prefetch Buffer                             |       |

|   |            | B.7.3    | Read-Only Buffer                            | . 155 |

|   |            | B.7.4    | Non-Blocking Store                          |       |

|   |            |          |                                             | -     |

| С |            | ter Clus |                                             | 162   |

|   | C.1        | Maste    | r TCU                                       |       |

|   |            | C.1.1    | Spawn/join Functional Unit(SJ)              |       |

|   |            |          | C.1.1.1 Behavioral Description of SJ        |       |

|   |            | C.1.2    | Local private cache for MTCU                | . 167 |

|   |       | C.1.3 Instruction Broadcasting                                            | 169 |

|---|-------|---------------------------------------------------------------------------|-----|

|   | C.2   | Global Register File (GRF)                                                | 170 |

|   |       | C.2.1 Interface of the GRF                                                | 170 |

|   |       | C.2.2 Serial Mode                                                         | 171 |

|   |       | C.2.3 Parallel Mode                                                       | 171 |

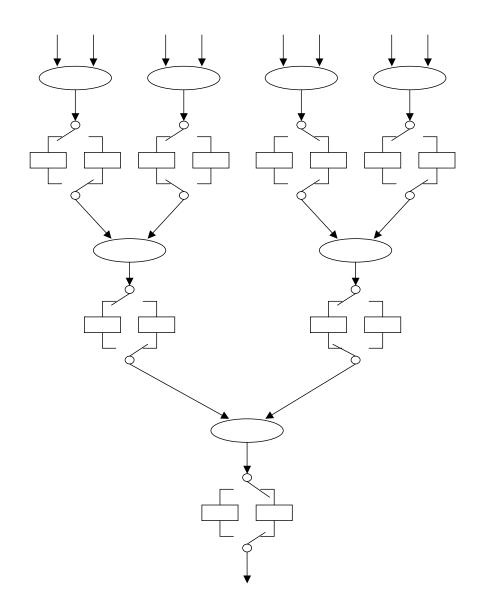

|   | C.3   | Prefix-sum Unit                                                           | 171 |

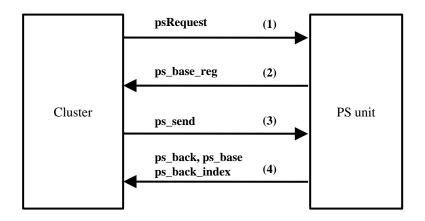

|   |       | C.3.1 Interface between Cluster and PS Unit                               |     |

|   |       | C.3.2 Interface of PS Unit                                                | 173 |

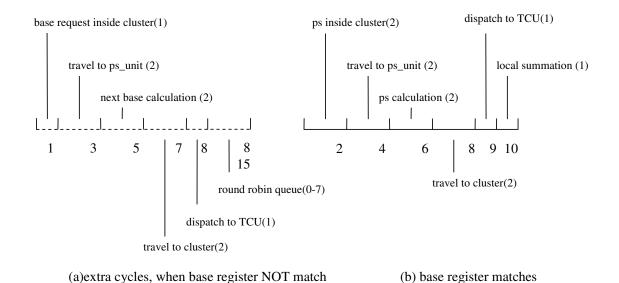

|   |       | C.3.3 Base Register Selection                                             |     |

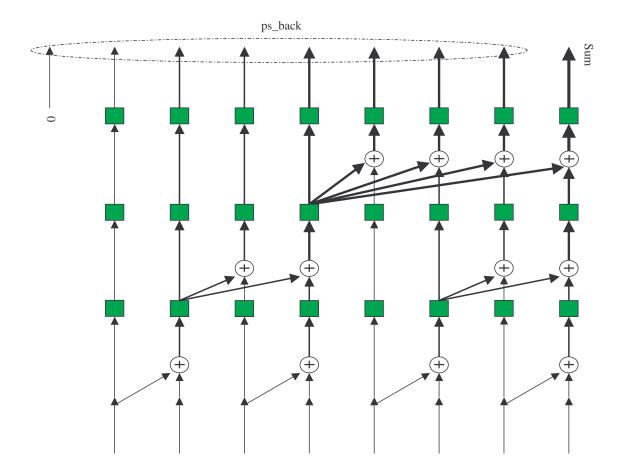

|   |       | C.3.4 Zero-base Prefix-sum Computation                                    |     |

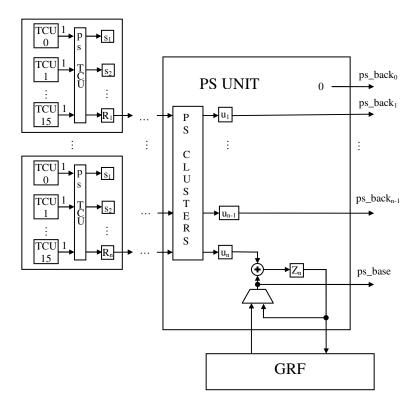

|   |       | C.3.5 Putting it All Together                                             |     |

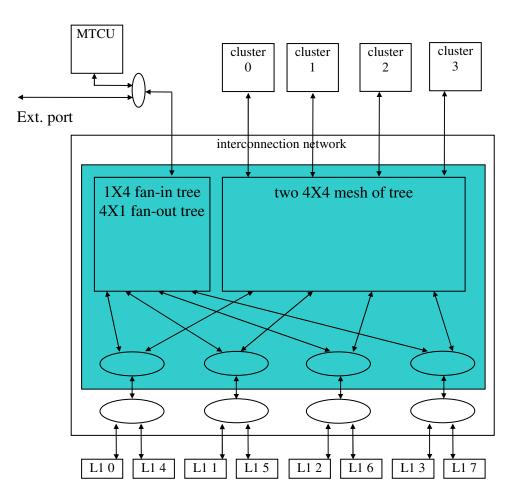

| D | Inter | rconnection Network                                                       | 180 |

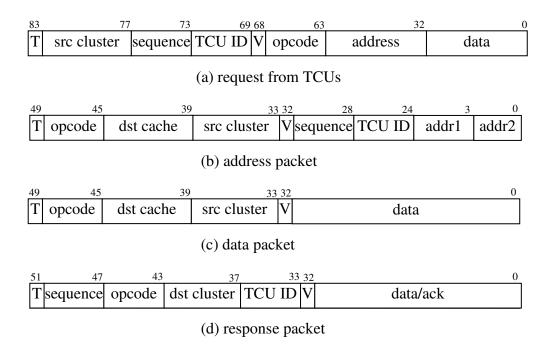

|   | D.1   | Interface of the interconnection network                                  | 181 |

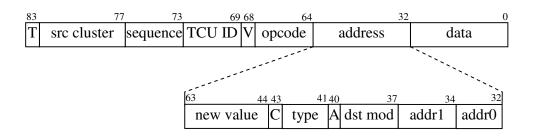

|   | D.2   | Packet formats                                                            | 182 |

| Е | On-o  | chip Cache                                                                | 186 |

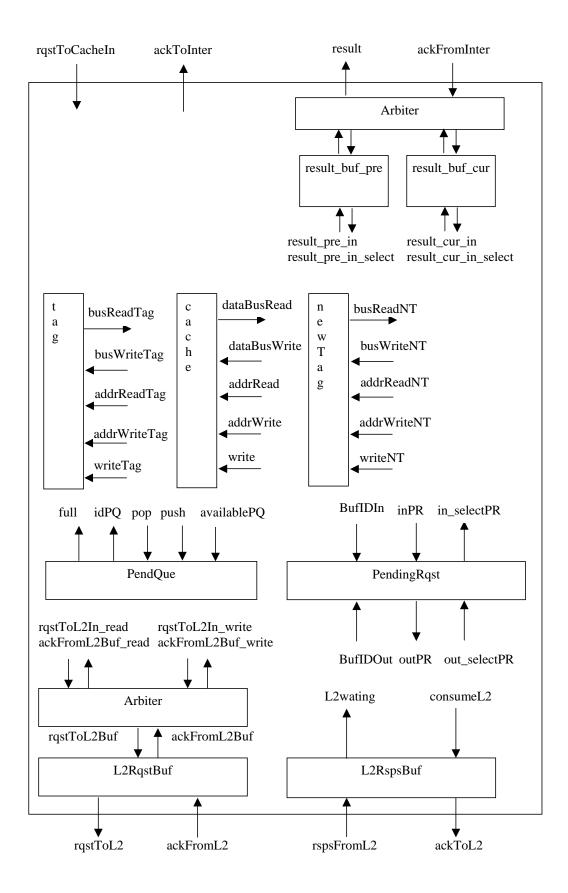

|   | E.1   | Overview of the Cache Hierarchy in the XMT Prototype                      | 187 |

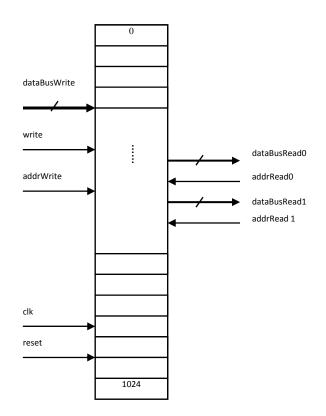

|   | E.2   | Interface of a Cache Module                                               | 187 |

|   | E.3   | Components of a Cache Module                                              | 189 |

|   |       | E.3.1 Tag                                                                 | 191 |

|   |       | E.3.2 NewTag                                                              | 192 |

|   |       | E.3.3 Data Array                                                          | 192 |

|   |       | E.3.4 Pending Requests                                                    | 194 |

|   |       | E.3.5 Pending Queue                                                       | 194 |

|   |       | E.3.6 FIFOs and Arbiters                                                  | 197 |

|   |       | E.3.6.1 MC Request and Response Buffers                                   | 197 |

|   |       | E.3.6.2 Result Arbiter and FIFOs                                          | 197 |

|   | E.4   | How a Cache Module Works                                                  | 197 |

|   |       | E.4.1 The Life-Cycle of a Cache Hit                                       | 199 |

|   |       | E.4.2 The Life-Cycle of a Cache Miss                                      |     |

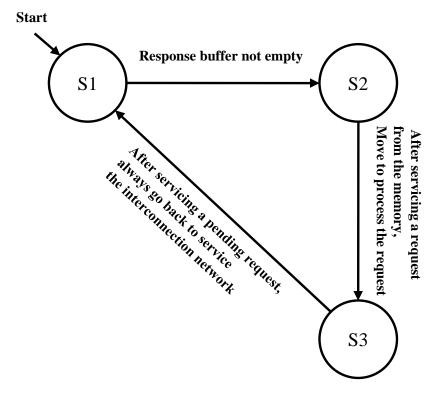

|   |       | E.4.3 Cache Module Status                                                 | 202 |

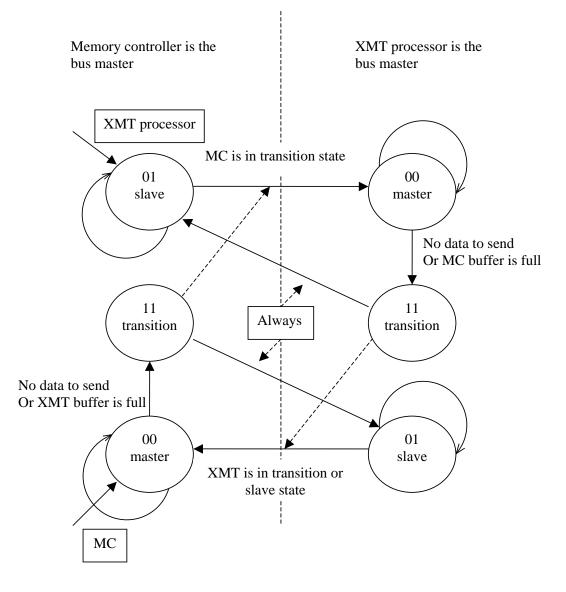

|   | E.5   | Sharing a Memory Controller Channel                                       | 203 |

|   | E.6   | Performance Counter and Special Registers                                 | 206 |

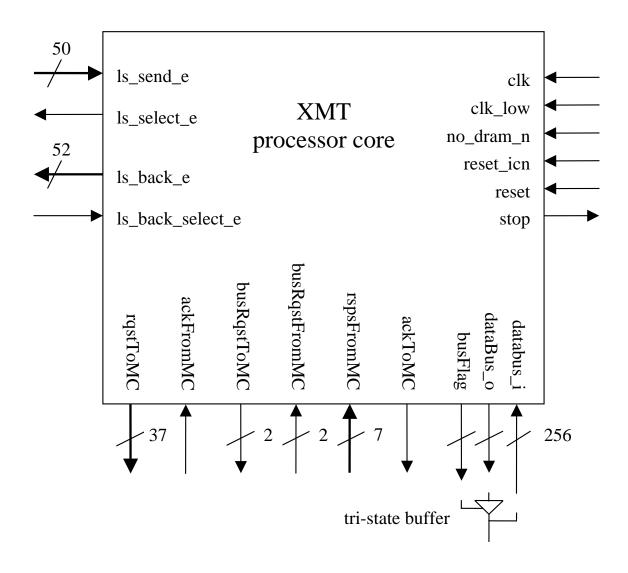

| F | Inter | rface of XMT Prototype                                                    | 212 |

|   | F.1   | clock, reset, stop and no_dram_n                                          | 213 |

|   | F.2   | External Memory Access Port                                               | 214 |

|   | F.3   | Interface to an Off-chip Memory Controller                                | 215 |

| G |       |                                                                           | 220 |

|   | G.1   | PCI Interface Module                                                      |     |

|   |       | G.1.1 Interface of pci_if Module                                          | 221 |

|   |       | G.1.2 How does the pci_if Module Work?                                    | 223 |

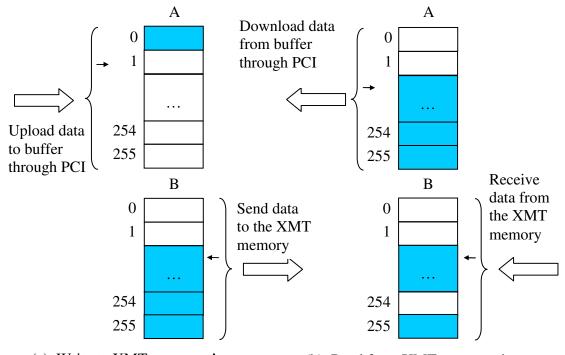

|   |       | G.1.2.1 Two Buffers in pci_if Module $\ldots \ldots \ldots \ldots \ldots$ | 223 |

| G.1.2.              | 2 Address Mapping for the Host Computer                             | 225   |

|---------------------|---------------------------------------------------------------------|-------|

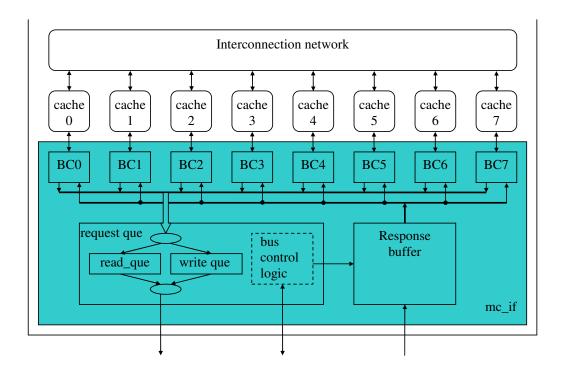

| G.2 Memory Con      | troller                                                             | 228   |

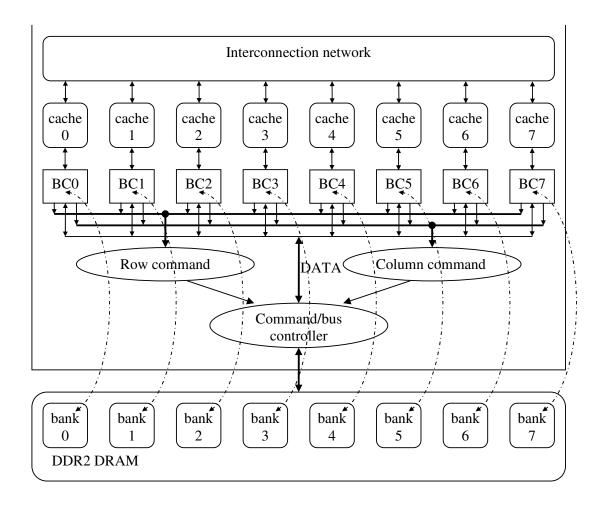

| G.2.1 DRAM          | A Architecture and Organization                                     | 229   |

| G.2.2 Bank          | Controller (BC) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$  | 230   |

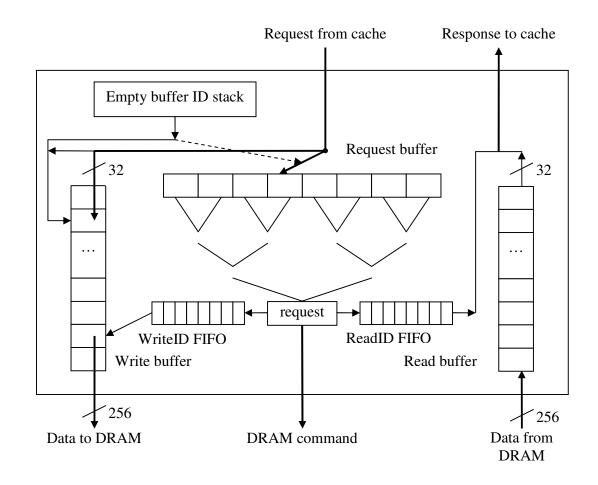

|                     | and and Bus Controller(CBC)                                         |       |

| G.2.3.              | 1 Interface of the CBC $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 237   |

| G.2.3.              | 2 How Does the CBC Work?                                            | 240   |

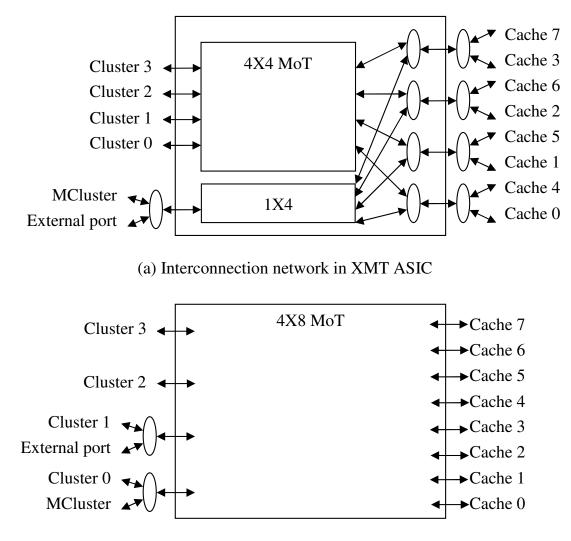

| G.3 Other Differe   | nces in XMT FPGA Prototype                                          | 242   |

|                     |                                                                     |       |

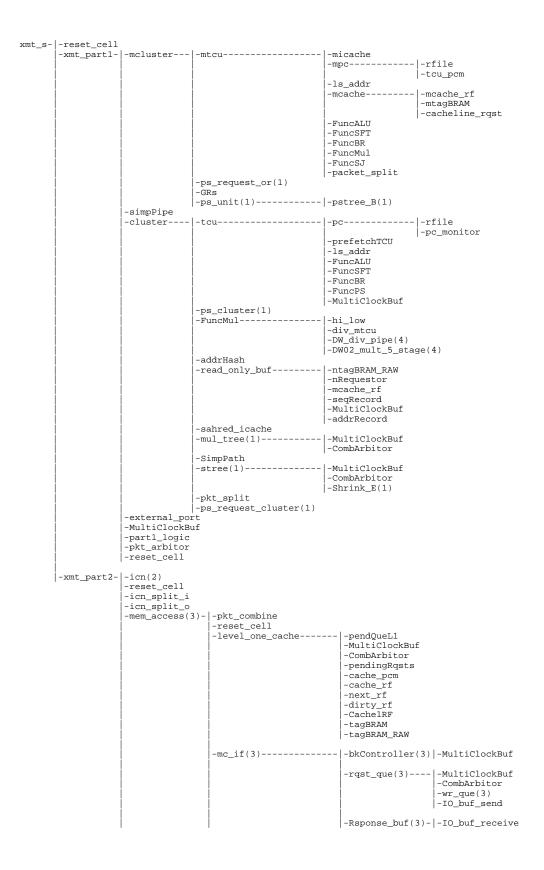

| H Verilog Module Hi | erarchy                                                             | 244   |

|                     |                                                                     | 0.4.0 |

| I XMT ISA           |                                                                     | 246   |

| Bibliography        |                                                                     | 250   |

| Dibitography        |                                                                     | 200   |

# List of Figures

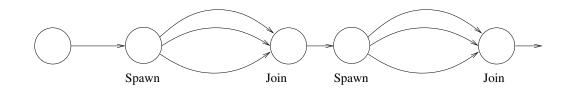

| 1.1  | Serial and parallel execution modes                                                                                                                                      | 9  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | XMT execution model $\ldots$                                                                                                                                             | 11 |

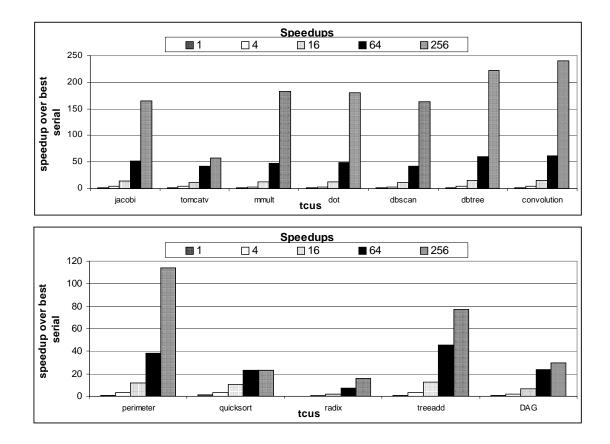

| 1.3  | Speedups on XMT simulator                                                                                                                                                | 15 |

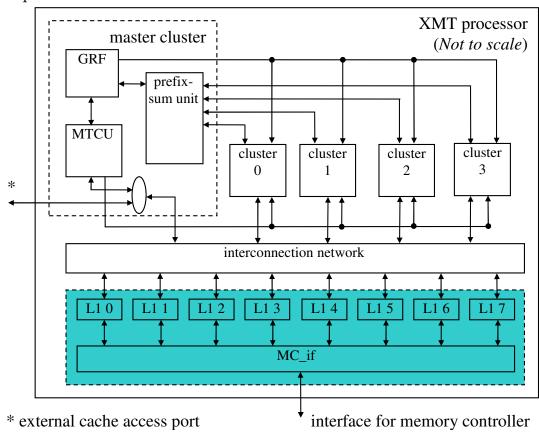

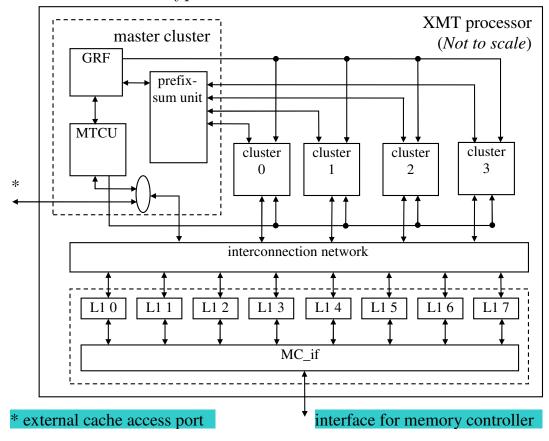

| 2.1  | Block diagram of the XMT processor                                                                                                                                       | 19 |

| 2.2  | Cluster and TCUs                                                                                                                                                         | 21 |

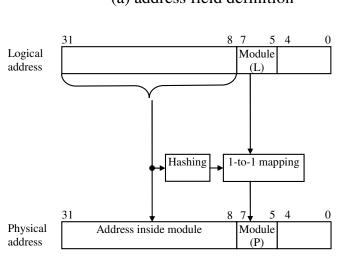

| 2.3  | Physical address calculation with hashing                                                                                                                                | 25 |

| 2.4  | Single Spawn (sspawn)                                                                                                                                                    | 28 |

| 2.5  | Transitions between serial and parallel modes with sspawn $\ . \ . \ .$ .                                                                                                | 30 |

| 2.6  | Broadcasting a value to virtual threads                                                                                                                                  | 35 |

| 2.7  | Illustration of the need for a blocking store                                                                                                                            | 37 |

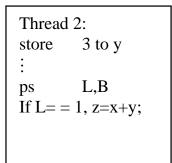

| 2.8  | Develop a PRAM-On-Chip program from work-depth paradigm $\ . \ .$ .                                                                                                      | 42 |

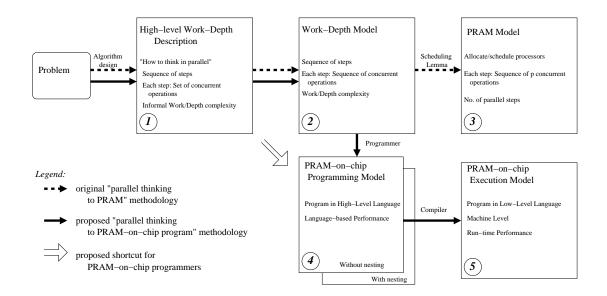

| 3.1  | Partitioning of the XMT processor for 3 FPGAs                                                                                                                            | 54 |

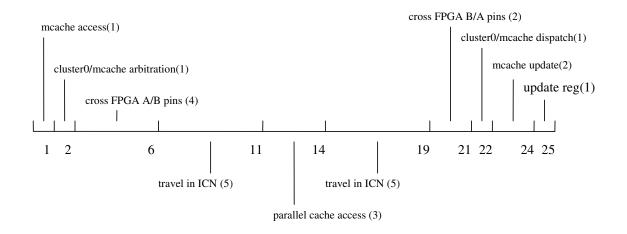

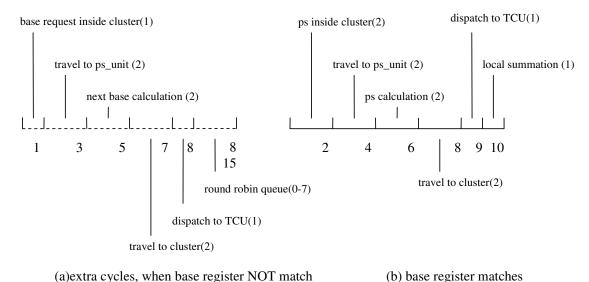

| 3.2  | Decomposition of MTCU cache miss penalty                                                                                                                                 | 55 |

| 3.3  | Decomposition of shared cache miss penalty                                                                                                                               | 57 |

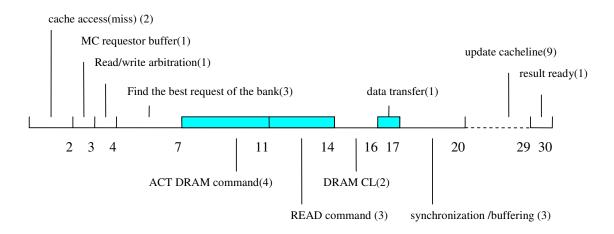

| 3.4  | Prefix-sum operation                                                                                                                                                     | 59 |

| 3.5  | An envisioned XMT processor                                                                                                                                              | 61 |

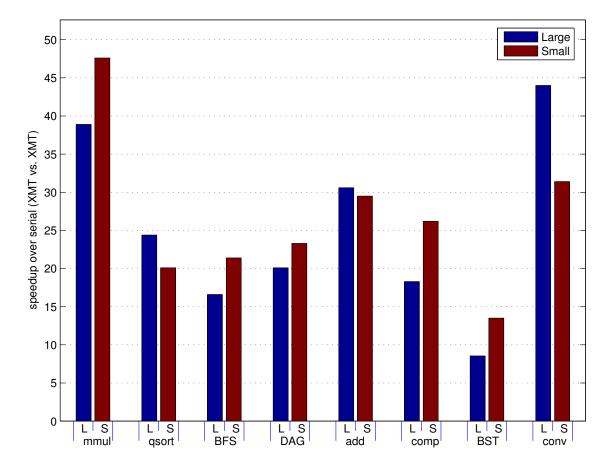

| 3.6  | Speedups of the benchmarks (parallel Vs. serial in XMT)                                                                                                                  | 69 |

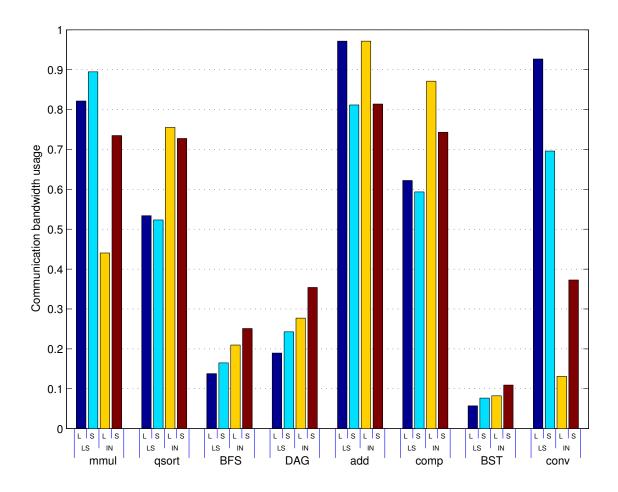

| 3.7  | Normalized throughput of the LS unit and interconnection network .                                                                                                       | 73 |

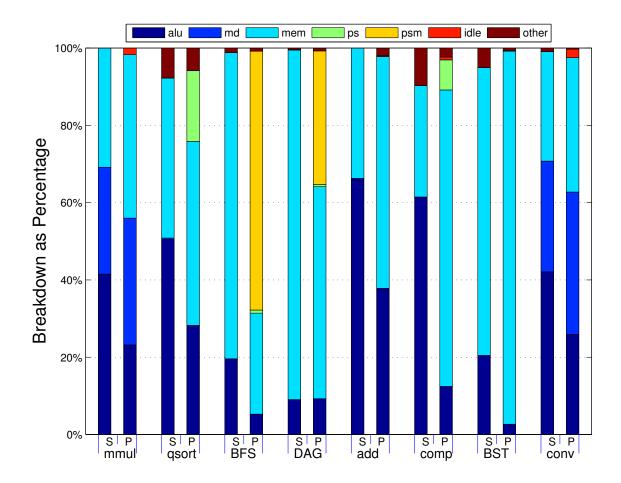

| 3.8  | Breakdown of serial and parallel execution time in XMT FPGA pro-<br>totype. For each benchmark, left bar is for serial execution and right<br>bar is parallel execution. | 75 |

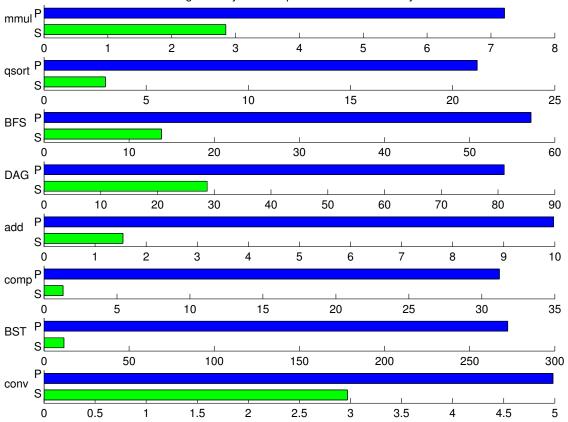

| 3.9  | Average latency of read operations in the serial and parallel program<br>in number of cycles                                                                             | 77 |

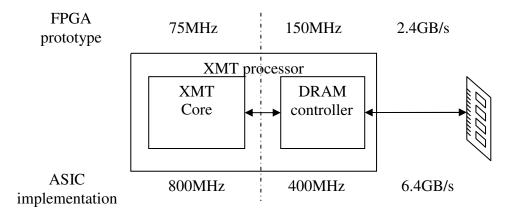

| 3.10 | The differences in the FPGA and ASIC implementation                                                                                                                      | 80 |

| 3.1         | 1 Cycle-accurate read timing                                                                                                              |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1         | 2 Normalized execution cycle                                                                                                              |

| 4.1         | Two XMT processors side by side: (a) XMT S processor, without local cache; (b) XMT P processor with local private cache                   |

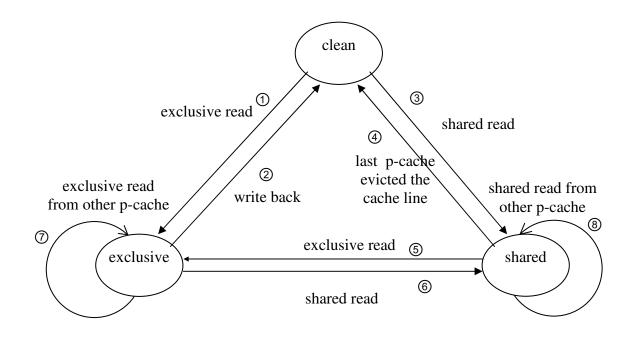

| 4.2         | State transition diagram of a cache line in directory                                                                                     |

| 4.3         | State transition diagram of a cache line in private cache 96                                                                              |

| 4.4         | Speedup over 8-cluster XMT S                                                                                                              |

| 4.5         | Traffic volume in 8-cluster XMT S                                                                                                         |

| 4.6         | Average latency of the read operations in cycles                                                                                          |

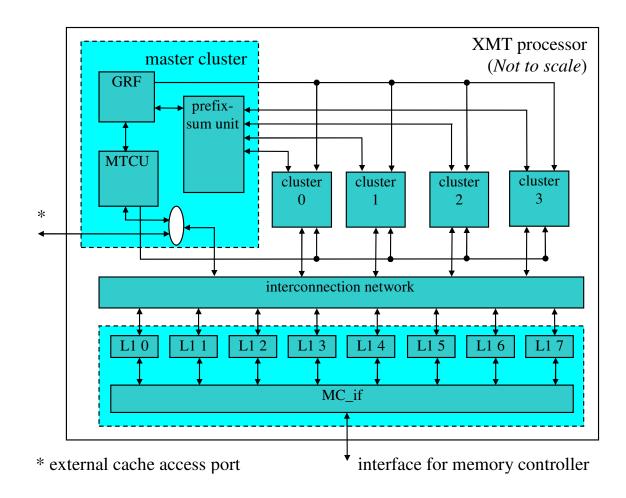

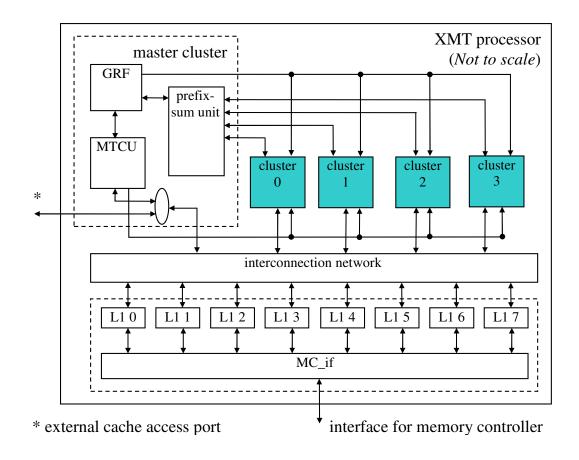

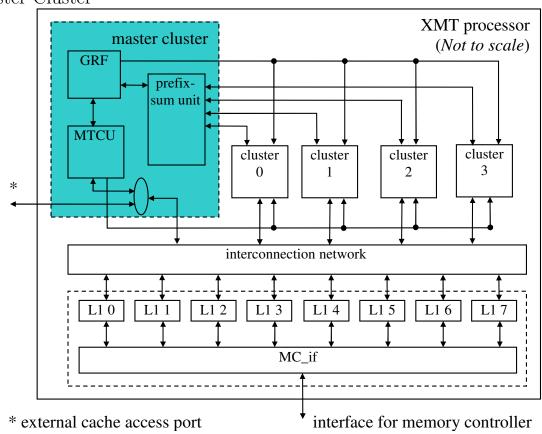

| A.1         | XMT block diagram                                                                                                                         |

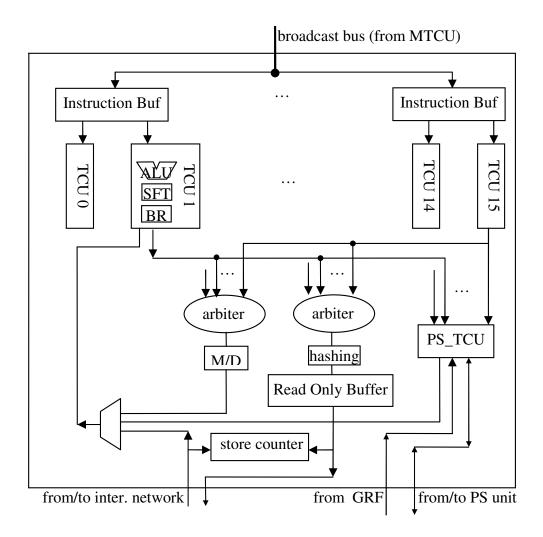

| B.1         | Clusters                                                                                                                                  |

| B.2         | 2 Instruction cache $\ldots \ldots 122$ |

| В.З         | B Block diagram of a Thread Control Unit (TCU)                                                                                            |

| <b>B.</b> 4 | Structure of the TCUs                                                                                                                     |

| В.5         | 6 One buffer arbiter tree                                                                                                                 |

| В.6         | 3 Two entry buffer arbiter tree                                                                                                           |

| В.7         | <sup>7</sup> Memory address hashing                                                                                                       |

| В.8         | Value broadcasting                                                                                                                        |

| B.9         | Using pointer in ROB for waiting list                                                                                                     |

| C.1         | Interface between clusters and PS unit                                                                                                    |

| C.2         | 2 Prefix-sum tree for 8 inputs                                                                                                            |

| С.З         | B PS unit and clusters                                                                                                                    |

| C.4         | Prefix-sum operation                                                                                                                      |

| D.1 | interconnection network                                              |

|-----|----------------------------------------------------------------------|

| D.2 | Packet bit definition                                                |

| E.1 | Components of an L1 Cache Module                                     |

| E.2 | State transition diagram for L1 shared cache                         |

| E.3 | Eight cache modules share one memory controller interface 205        |

| E.4 | Cache PCRF/SR access request                                         |

| F.1 | Interface of an XMT processor core                                   |

| F.2 | State transition diagram of XMT processor and MC                     |

| G.1 | Access the memory space of the XMT processor through the PCI bus 224 |

| G.2 | Memory modules                                                       |

| G.3 | Bank controller                                                      |

| G.4 | Interconnection network topology                                     |

| H.1 | Verilog Module Hierarchy                                             |

# List of Abbreviations

- ALU Arithmetic Logic Unit

- ASIC Application Specific Integrated Circuit

- BFS Breath First Search

- BST Binary Search Tree

- CMP Chip MultiProcessor

- CRCW Concurrent Read Concurrent Write

- DAG Directed Acyclic Graph

- FPGA Field Programmable Gate Array

- GR Global Register

- GRF Global Register File

- HDL Hardware Description Language

- ILP Instruction level parallelism

- IOS Independence of Order Semantics

- LSRTM Length of Sequence of Round Trips to Memory

- MTCU Master Thread Control Unit

- MC Memory Controller

- MSI Modified Shared Invalid

- OS Operating System

- PRAM Parallel Random Access Machine(Model)

- PS Prefix Sum (to register)

- PSM Prefix Sum to Memory

- QRQW Queue-Read Queue-Write

- SIMD Single Instruction Multiple Data

- SMP Symetric multi-processor

- SMT Simultaneous multi-threading

- SPMD Single Program Multiple Data

- TCU Thread Control Unit

- TLP Thread level parallelism

- XMT eXplicit Multi-Threading

- XMT P XMT with coherent Private caches

- XMT S XMT Shared caches only (without private caches )

#### Chapter 1

#### Introduction

Micro-processor performance has been improved continuously over the past decades, primarily because an increasing number of faster transistors are available on-chip, thanks to the development of the semiconductor industry. Processors can operate at a higher clock rate with faster transistors and more transistors enabled designers to implement various optimizations in hardware, namely targeting extraction of instruction level parallelism (ILP) in hardware, parallelizing execution of serial code.

However, the extensive power consumption in high density chips became a new challenge for further improvement of processor performance with the traditional techniques. For example, clock rates increase with shrinking transistor sizes, but since faster clocks are the major contributor to the increasing power consumption, they are unlikely to increase as they used to.

On top of that, ILP has reached its diminishing return stage. As the finestgrain parallelism, ILP techniques attempt to exploit parallelism among instructions in serial programs. To increase the amount of parallelism, researchers have studied a variety of techniques such as: dynamic scheduling, multi-instruction issue, branch prediction, and register renaming. However, the parallelism available in a serial program is inherently limited [49, 39]. The new trend in processor industry is turning to multi-core processors, as the name indicates, consisting of multiple processor cores in a single chip. These processors are also referred to as CMPs (chip multi-processor). This is a natural choice since it is no longer cost effective to improve the performance of a single core due to design complexity, increased power consumption and diminishing performance increase. In a typical multi-core processor, cores are quite independent of each other since their sharing are limited to lower levels of a memory hierarchy. These multi-core processors are used in the symmetric multi-processor (SMP) systems and each core is scheduled by an operating system (OS) independently.

The XMT (explicit multi-threading) platform attempts to take advantage of the fast-growing number of transistors available on a chip in a different way from simply replicating advanced serial processor cores as in the CMP. The XMT processor is designed to support thread level parallelism using thread-aware hardware, targeting shortened single task completion time. More importantly, XMT is a parallel algorithmic architecture that efficiently executes PRAM (parallel random access machine/model) algorithms.

#### 1.1 Parallel Computing

Although On-chip parallel computing is relatively new, parallel computing based on multiple processors(chips) have been around for many decades [2, 3]. Shared memory and message passing are the two main parallel programming models. In a shared memory parallel computer architecture, multiple processors share the same memory address space and the communication between processors is done through the shared memory implicitly. Programmers do not need to know the physical location of the data. Message passing is an explicit communication method, since processors have to exchange messages to communicate with each other. Generally, it is believed that programming in shared memory is easier than in message passing. With hardware and software support, the combination of shared memory and message passing can be implemented[37, 14].

Communication bandwidth and latency are among the most important measurements of any parallel computer system. Until recently, all parallel computers were built from multiple chips and communications between processors had to cross chip boundary and rely on an off-chip interconnection network. The communication overhead in such a system is very expensive due to the long latencies and low bandwidth. Caches are used in multiprocessors to reduce the latencies, but it has also introduced the coherence problem, resulting from possible multiple copies of a single memory location. Bus snooping and directory based protocols are used to address the cache coherence problem. Bus snooping is simple but it is limited to a small scale of the parallel computer due to the limited bus bandwidth. The directory base cache coherence protocol is scalable, but it needs extra storage space for directories and its hardware implementation is very complicated. It is well known that cache coherence protocols are inefficient for some data access patterns, typically those using extremely fine-grained parallelism. As a result, caches in parallel computers are not as effective as in uniprocessors in providing low-latency, high-bandwidth memory accesses for certain types of programs.

Programming in parallel computing is quite challenging [5]. First, it is difficult to develop a correct parallel program, because of asynchronous events and potential deadlocks from many possible execution paths. It is more difficult for programmers to reason about a multithreaded program than a single-thread program. Second, it is difficult to develop a high performance parallel program, since programmers need to know the details of the targeted parallel computer. The communication overhead in parallel computing is quite difficult to estimate. Indeed, the challenges of parallel programming has been preventing it from broad application for many decades.

#### 1.2 What is PRAM?

The abstract model for serial computing is RAM (Random Access Machine/-Model) and PRAM (Parallel Random Access Machine/Model) is its counterpart in parallel computing. The main assumption of the PRAM is that the latency for an arbitrary number of memory accesses is the same as for one access. PRAM was extensively used in 1980s and 1990s for the theorists to develop and study parallel algorithms for various applications. With PRAM, algorithm designers can concentrate on the problem itself and they are freed from dealing with the details of a specific architecture. However, because of the abstraction, PRAM underestimates the communication overhead that is not negligible in real multi-chip parallel computers. In 1993, Culler et al. published a paper [13] that pointed out that PRAM is an oversimplified model and proposed a new parallel machine model. From the mid-1990s, PRAM was deemed useless and research about PRAM faltered because most researchers abandoned it.

Researchers have tried to approximate the theoretical performance of the PRAM using multi-chip parallel computing, like NYU-Ultracomputer [20] in the 1980s and the SB-PRAM [6, 16, 38] in the 1990s. However, the paper [13] and the later book [14] explain why the high latency, and even more importantly the limited bandwidth among the processors, make it hard to accomplish.

The XMT PRAM-On-Chip project at the University of Maryland is based on the observation that the fast growing number of transistors will make it possible to build a PRAM on a single chip. When multiple cores reside on the same chip, they can be connected with a very high-bandwidth, low-latency network, and the communication overhead among them can be significantly reduced compared to the multi-chip parallel computers. Before we jump into the the details of the XMT, representative CMPs will be reviewed, since both CMP [24, 23] and XMT are singlechip multi-threaded architecture.

# 1.3 Chip Multi-Processor(CMP))

The first example of CMP, a dual-core processor, was introduced by IBM [28] and now both Intel and AMD deliver quad-core processors. As the name indicates, two or four processors are placed on one chip. The cores in these chips are rather independent and powerful, while they share some chip-wide resources such as a lower-level cache. OS considers these cores as independent processors when assigning a thread or process to them. A CMP system can improve overall throughput of a chip and execute parallel programs like in SMP, but it also has similar programming challenges as SMP.

Recent research[32, 4] on CMP shows that a heterogeneous architecture performs better than a homogeneous one under the same power and area constraints. The advanced serial processors typically apply many microarchitecture optimization techniques to achieve a better single-thread performance, e.g. out-of-order execution, branch prediction, and pipelining. These techniques generally are not cost effective in terms of performance-per-transistor and performance-per-watt. The hardware support of fine-grained parallelism is a desirable feature for future multi-core processors [30].

The CELL[26, 52] processor designed by Sony, Toshiba and IBM is an architecture that is radically different from conventional multi-core processors. The CELL uses a high performance PowerPC core that controls eight relatively simple SIMD cores, called Synergistic Processing Elements (SPE). The processor is designed for the Sony PS3 game console, but it is also considered to be a good building block of high performance scientific computing solutions[52]. Each SPE in CELL has its own local storage and the data transfers from local storage to the global storage need to be taken care of by the programmer explicitly, which makes programming for CELL quite challenging.

The Niagara processor[17, 29] from SUN is a multi-core multi-threaded processor, which is targeted for server applications. The latest generation of Niagara 2 has 8 cores and each core can execute up to 8 threads. The threads are switched to utilize processors better by hiding latencies from cache miss, branch misprediction and exceptions. The power consumption per thread is extremely low, slightly more than 2 Watts per thread. The processor is designed to achieve better throughput with less power consumption, but it is not designed for shortening single task completion time as XMT.

Tile-based architectures, such as MITs Raw [43], Stanfords Smart Memories [33] and UT-Austins TRIPS [41], also expect to scale to high levels of parallelism. The XMT, unlike Raw, Smart Memories and TRIPS, provides hardware support for efficient load balancing and better support for a shared-memory model, both of which are critical for many irregular applications.

Amdahl's law states that the overall speedup a parallel program can provide is limited by the serial portion of the program. Therefore it is reasonable to use a more powerful processor for the serial portion while using many simple in-order RISC processors for parallel execution, which are efficient both in power and area. In the XMT system, we propose to have one powerful MTCU(Master Thread Control Unit) for the serial part, which applies various optimizations for single-thread execution, and have as many as 1024 relatively simple, in-order execution TCUs (Thread Control Units) for the parallel part to achieve better overall area and power utilization. It is also possible for an XMT processor to have multiple MTCUs to support multiple OS threads, where the parallel processors are dynamically assigned to the MTCUs.

Although both CMP and XMT are trying to take advantage of an increasing number of transistors and high on-chip communication bandwidth available, the XMT architecture addresses the long standing challenge: programmability. It does so by natively supporting thread level parallelism in hardware, specifically supporting fine-grained parallelism from PRAM algorithms.

# 1.4 eXplicit Multi-Threading (XMT)

The XMT project attempts to design an architecture that executes PRAMstyle programs efficiently by taking advantage of the low-latency and high-bandwidth communication network available on a single chip. Load balancing that needs to be carefully handled in other parallel computers is naturally achieved in the XMT by a dynamic task assigning scheme. The programming model of the XMT is simple, and there are plenty of PRAM algorithms available which are easy to implement on the XMT. The multi-operand prefix-sum operation, a special instruction introduced in XMT, further lowers the latency of the synchronization among multiple threads and reduces the overhead of generating new threads.

#### 1.4.1 Background review

Early papers on the XMT presented the fine-grained programming model, architectural features and some initial performance results [48, 36, 15, 11, 34, 35, 46, 45, 44].

#### XMT Programming Model

The programming model underlying the XMT framework is the SPMD (Single Program Multiple Data) programming model that has two executing modes: serial

Figure 1.1: Serial and parallel execution modes

and parallel. The *spawn* and *join*, instructions specify the beginning and end of a parallel section (executed in parallel), respectively. See figure 1.1.

An arbitrary number of virtual threads, initiated by a *spawn* and terminated by a *join*, share the same code. The memory access model of the XMT processor is a hybrid of so-called arbitrary CRCW (Concurrent Read Concurrent Write) and QRQW (Queue Read Queue Write) [18]. The arbitrary CRCW aspect dictates that concurrent writes to the same memory location result in one arbitrary write committing. No assumption needs to be made beforehand about which will succeed. An algorithm designed with this property in mind permits each thread to progress at its own speed from its initiating *spawn* to its terminating *join*, without ever having to wait for other threads; that is, no thread busy-waits for another thread. We call this "independence of order semantics" (IOS).

An advantage of using this easier to implement SPMD model is that it is also an extension of the classical PRAM model, for which a vast body of parallel algorithms is available in the literature [25, 27]. The programming model also incorporates the prefix-sum statement. The prefix-sum operates on a base variable, B, and an increment variable, R. The result of a prefix-sum (similar to an atomic fetch-and-increment [20]) is that B gets the value B + R, while the return value is the initial value of B. The primitive is especially useful when several threads simultaneously perform a prefix-sum against a common base, because multiple prefix-sum operations can be combined by the hardware to form a very fast multi-operand prefix-sum operation. Because each prefix-sum is atomic, each thread will receive a different return value. This way, the parallel prefix-sum command can be used for implementing efficient and scalable inter-thread synchronization, by arbitrating an ordering between the threads.

# The XMT Architecture

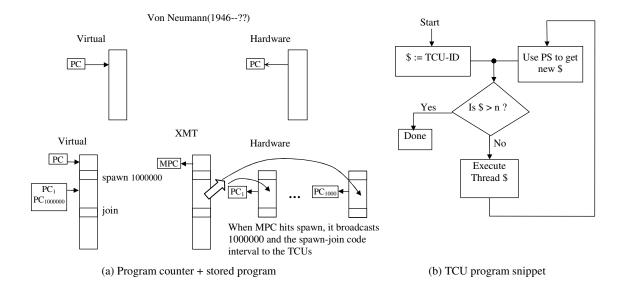

Perhaps the most important distinguishing characteristics of an XMT architecture are low-overhead mechanisms for the management of parallelism. New elements not present in standard microprocessor design are introduced for the purpose of supporting the parallel programming model. The XMT programming model allows programmers to specify an arbitrary degree of parallelism in their code. Clearly, real hardware has finite execution resources, so in general all threads cannot execute simultaneously. In an XMT machine, a thread control unit (TCU) executes an individual virtual thread. Upon termination of a virtual thread, the TCU performs a prefix-sum operation in order to receive a new (virtual) thread ID. The TCU will then execute the thread with that new ID. All TCUs repeat the process until all the virtual threads have been completed. A Master Thread Control Unit (MTCU) orchestrates the TCUs. Figure 1.2 illustrates this: (i) through a comparison with the von Neumann stored program and program counter apparatus (1.2 (a)), and (ii)

through a snippet of the program of a TCU (1.2 (b)).

Figure 1.2: XMT execution model

We begin with Figure 1.2 (a). Its upper part, entitled "von Neumann (1946– ??)," illustrates the program counter apparatus in serial machines, which has dominated general-purpose computing since 1946; it is not yet clear whether and when its reign will end. The right hand side (of the upper part of Figure 1.2 (a)) depicts the hardware apparatus, where one command at a time is brought to the program counter. The left hand side (of the upper part of Figure 1.2 (a)) demonstrates how the programmer is often educated to think about this apparatus–"the virtual outlook". Here the program counter is the one to move; it moves from one location of the memory to another, perhaps like a "book analogy", where the finger of a reader advances from one line of the book to another. The fact that this von Neumann apparatus has survived orders of magnitude improvements in speed since the 1940s makes it a remarkable "Darwinistic success story". For this reason we sought to upgrade, rather than replace in a disruptive manner, this successful apparatus.

The lower part of Figure 1.2 (a), entitled "XMT", illustrates the new apparatus. The left hand side (of the lower part of Figure 1.2 (a)) depicts the virtual description. There is still one computer program as in the von Neumann apparatus. In the above book analogy, one finger (marked as PC, for program counter) moves from one line of the book to another, until it reaches a special command called spawn. The spawn command specifies a number of "threads" which can be performed in parallel. Since we discuss now the virtual side, any number of threads can be specified. Figure 1.2 (a) mentions 1,000,000 threads. The virtual threads, initiated by a *spawn* and terminated by a *join*, share the same code. At run-time, different threads may have different lengths, based on individual control flow decisions. The programmer's understanding will be that each of the threads can progress (guided by one finger per thread) from the *spawn* command to a subsequent *join* command at its own speed. At the join, the thread expires. Once all the virtual threads expire, the finger marked PC continues. The main difference in the hardware description on the right-hand-side (of the lower part of Figure 1.2 (a)), is that the number of program counters is fixed (the figure mentions 1,000), and does not change as a function of the *spawn* command at hand. The program counter of the MTCU (denoted MPC) executes the serial code, prior to the spawn command. The program counter of the MTCU executes a *spawn* command and then broadcasts the following instructions until a *join* instruction to the other program counters. The program counters start by executing the first 1,000 among the 1,000,000 threads, one thread each. When a program counter completes its thread, it starts executing one of the yet-to-be-executed threads. This is done until all of the 1,000,000 threads finish.

Figure 1.2 (b) illustrates the program of a TCU. Suppose that n = 1,000,000 threads are to be executed as a result of a *spawn* command. The figure assumes that n and the SPMD code were broadcast to all TCUs. TCU i starts by executing the respective virtual thread i, but only if i is not larger than n. Upon finishing the execution of a virtual thread, the TCU uses a prefix-sum computation to obtain the ID of the next virtual thread it should execute, and proceeds to execute it if that ID is not larger than n. Note that the only communication among TCUs is through the prefix-sum computation. An extension of the architecture that allows some nesting of *spawn* commands (using an *sspawn* command, noted later) is not reviewed here.

#### Expected Performance of XMT

Previous papers on XMT have presented simulation results of the performance of the XMT. The work reported in [48] is the speedup of several parallel algorithms based on hand-coded assembly programs (see table 1.1). The DAGs problem aims to find the longest path leading to each vertex in the directed acyclic graphs. Integer sorting uses bin-sort iterations to sort an array. List ranking finds for each element in the list its total distance from the end of the list, given that each element has a pointer pointing to its successor. Detailed information about these problems and algorithms can be found in [48].

The XMTC compiler made it possible to evaluate the performance of the XMT

|              |                | Number of TCUs |       |       |       |        |        |

|--------------|----------------|----------------|-------|-------|-------|--------|--------|

| Problem      | Input Size     | 20             | 50    | 100   | 200   | 500    | 1000   |

| DAGs         | graph4         | 4.17           | 7.59  | 10.71 | 13.78 | 16.45  | 17.72  |

|              | graph6         | 5.79           | 14.02 | 26.69 | 43.97 | 100.46 | 159.69 |

| Integer sort | $5 \cdot 10^3$ | 3.61           | 7.71  | 13.21 | 21.84 | 40.15  | 60.88  |

| List ranking | $10^{3}$       | 2.68           | 5.29  | 7.83  | 12.81 | 23.47  | 32.49  |

|              | $5 \cdot 10^3$ | 3.09           | 7.62  | 14.89 | 28.53 | 63.30  | 106.6  |

Table 1.1: Empirical performance result

on more complex applications. Figure 1.3 shows the speedup results reported in [34].

The XMT showed good performance on applications which have either small input size or exhibit irregular behavior, for which traditional parallel computing cannot employ a simple static scheme because of potential high load-imbalance or communication overhead. From previous work[48, 36, 34, 35], the speedup of the XMT is about one magnitude order lower than the hardware cost, which is much better than multiprocessor parallel computing[48].

XMT speedups exceeding 100-fold for a standard VHDL gate-level simulation benchmark suite relative to serial were reported in [22].

Figure 1.3: Speedups on XMT simulator

# 1.4.2 Overview of Thesis

This dissertation presents the first hardware implementation of the XMT architecture, which is extended from the high level description and software simulator of the XMT architecture presented in early papers. The performance of the XMT architecture is also studied with an FPGA-based prototype [51, 50].

Following this introduction, the XMT architecture is presented. The components of the XMT processor, transitions between parallel and serial modes, instruction and value broadcasting, software/hardware co-managed prefetch buffer, and the read-only buffer are explained in detail. The overview of the XMT framework is also discussed in this chapter for better understanding of a broad concept of XMT.

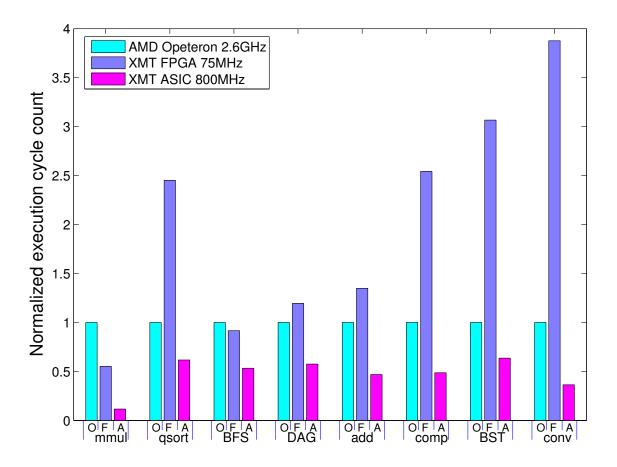

In chapter 3, the performance of the XMT processor is studied from different aspects with the XMT FPGA prototype. The execution time of a parallel implementation over the best serial program in the prototype is reported. The absolute execution time (wall-clock time) is compared with a commodity 2.6GHz AMD Opteron processor. The performance of an envisioned XMT ASIC 800MHz processor is projected using the XMT FPGA prototype as a cycle-accurate emulator by slowing down the DRAM.

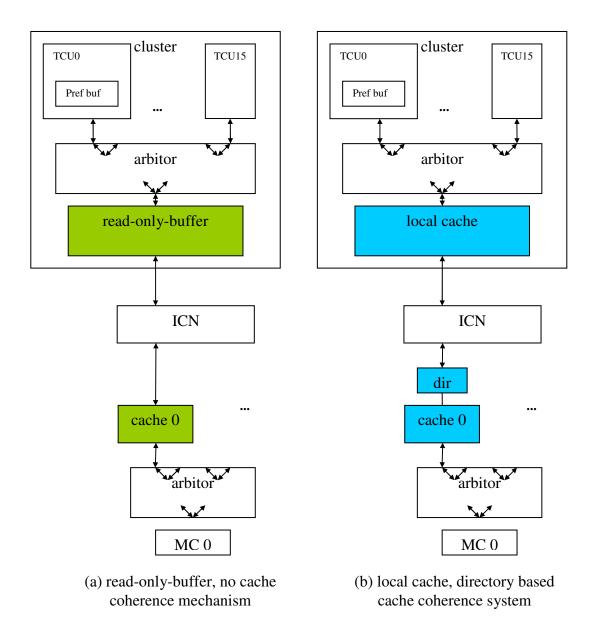

In chapter 4, the choice of not having coherent private caches is studied. An imaginary system that includes conventional coherent private caches is simulated and its performance is compared to the preferred default configuration: XMT without coherent private caches. The two systems are compared in execution time, traffic in the interconnection network, and average latency for read operations. The simulation results suggest that coherent private caches do not have an advantage in the context of the XMT system, which is designed to support fine-grained, PRAM-based algorithms efficiently.

Chapter 5 concludes this thesis by summarizing the results from this study and briefly discusses the future work towards a complete XMT processor.

The description of the Verilog model of the two XMT prototypes: ASIC and FPGA versions are presented in the appendices. Following an overview of the XMT Verilog model, each chapter of the appendices describes a component of the XMT in great detail. Since the XMT processor is still under development, the description of modules is only valid for the current snapshot. The XMT ASIC prototype is

discussed as the default, and the differences between ASIC and FPGA versions are presented in the last chapter of the appendices.

# Chapter 2

## Architecture of the XMT Processor

In this chapter, the micro-architecture of the XMT will be presented in great detail.

## 2.1 Micro-architecture of the XMT Processor

## 2.1.1 Overview

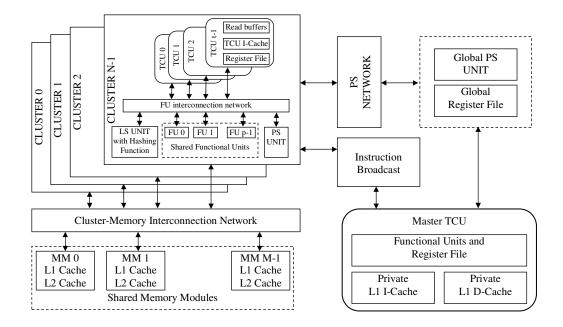

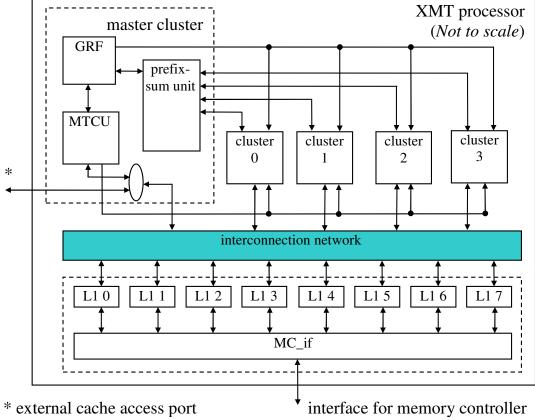

The XMT processor includes a MTCU (Master Thread Control Unit), clusters comprising of TCUs (Thread Control Units) and functional units, an interconnection network, shared on-chip cache modules, memory controllers (MC), a global register file (GRF) and a prefix-sum unit.

Figure 2.1 depicts the block diagram of the XMT processor. The MTCU executes the serial portion of the program and clusters of TCUs execute the parallel sections. MTCU and clusters of TCUs access shared memory space through an interconnection network. The memory space is partitioned into multiple memory modules, which can be independently accessed. The prefix-sum unit can execute common base prefix-sum operations from multiple TCUs in a unit time, which will provide low overhead for extremely fine-grained parallelism.

Figure 2.1: Block diagram of the XMT processor

# 2.1.2 Master TCU

The master TCU is the only TCU active in serial mode. Similar to advanced serial microprocessors, the master TCU can incorporate standard techniques related to ILP, such as branch prediction, out-of-order execution, and register renaming. The main difference between the MTCU and a serial microprocessor is its support of special XMT instructions such as *spawn* and *join*. When the XMT processor switches to parallel mode, the MTCU broadcasts the instructions in the parallel section to all clusters where they are copied to a local instruction buffer and later fetched by TCUs inside clusters. After all instructions in the parallel section have been broadcast, the MTCU waits for TCUs to finish the execution of the parallel section.

The Master TCU has its own cache, L0, that is only active during serial mode

and applies write-through. Whenever the local cache in MTCU is written, the shared cache is also updated with the new value. When the XMT processor enters parallel mode, the Master TCU discards its local cache. The overhead of the flushing L0 cache is trivial since write-through mechanism is chosen. The MTCU will have compulsory misses when XMT switches back to serial mode, but it can be solved by advanced hardware/software prefetch. The other option is to apply a hardware cache coherence protocol between shared cache modules and MTCU local cache. If a memory location cached in MTCU local cache is updated by a TCU, it can either update or invalidate the cache line in the MTCU local cache. When XMT operates in serial mode, L0 cache is the first level cache of the MTCU and multiple shared memory modules provide the lower level of the memory hierarchy (similar to a serial processor). With this memory hierarchy, the MTCU mainly relies on L0 in serial mode, instead of shared caches.

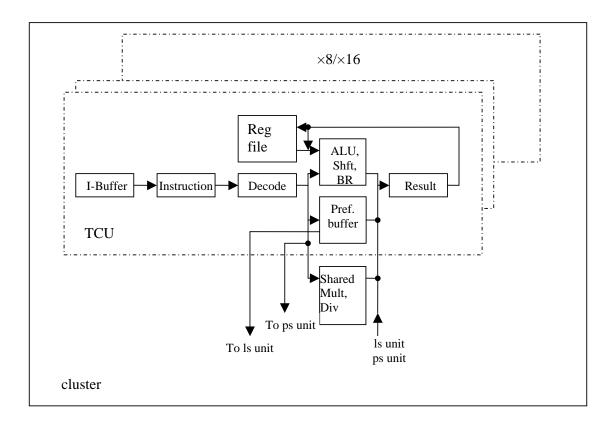

#### 2.1.3 TCUs and Clusters

A TCU can execute a thread in parallel mode. TCUs have their own local registers and they incorporate simple in-order pipelines including fetch, decode, execute/memory access and write-back stages. The TCUs have a very simple structure and do not aggressively pursue maximum performance. Given the limited chip area, the overall performance of the XMT is likely better when it has more simple TCUs rather than fewer, but more advanced, TCUs because of the well-known diminishing

Figure 2.2: Cluster and TCUs

return of many ILP techniques. However, XMT does not prevent TCUs from introducing any advanced techniques, since the TLP (Thread Level Parallelism), which XMT is taking advantage of, is orthogonal to that. A TCU is an in-order processor that only issues a new instruction when the previous instruction has been executed, so there is only one instruction from a TCU being executed by functional units at any moment. A cluster is a group of 16 TCUs and accompanying functional units. TCUs share some functional units with several other TCUs in the same cluster; this is similar to an SMT (Simultaneous Multi-Threading) processor. For complicated and time-consuming operations, such as multiplication and division, multiple TCUs are assigned to one functional unit. Some simple functional units are not shared, because the overhead of sharing is comparable with that of replicating them and it may be intensively used by TCUs. If several TCUs assigned to a functional unit try to access it, proper arbitration is used to queue all requests. Each cluster has one load/store port to the interconnection network, which is shared by all TCUs inside the cluster. Prefix-sum requests from TCUs are combined in the cluster and sent to the prefix-sum unit. Figure 2.2 shows the block diagram of the cluster.

### 2.1.4 Prefix Sum Unit and Global Register File

ps R, B, an individual prefix-sum, indicates the following atomic operations.

$R \leq B$ , R will get the old value of B.

$B \le B + R$ , B will get the sum of B and R.

B is called base register

A series of individual prefix-sum instructions,  $ps R_0, B, ps R_1, B \cdots$ , will result in

$B \leq = B + R_0 + R_1 + R_2 + \cdots$  $R_0 \leq = B$  $R_1 \leq = B + R_0$  $R_2 \leq = B + R_0 + R_1$  $\vdots$

In XMT, the common base prefix-sum instructions from different threads can be executed by the prefix-sum unit simultaneously. In this case, the result of the execution of these prefix-sum instructions are the same as executed in serial mode at an arbitrary order, but the execution will take a constant time on XMT, regardless of how many threads participate. Due to the hardware implementation challenges, the incremental values are limited to 0 or 1. There is no limit on the base register and the result of a ps operations is 32-bit value. This hardware implemented multioperands prefix-sum operation can be used in efficient inter-thread synchronization by arbitrating an ordering between threads.

TCUs send 1 bit input for a ps operation request and get the prefix-sum results in local registers. The prefix-sum unit is based on binary tree implementation. After the prefix-sum unit finishes calculation, each TCU gets its own value (prefix-sum of inputs with initial value of 0 in base register) and the base value broadcast from the prefix sum unit; then, the final results are the sum of these two numbers which is calculated locally by TCUs. The registers in GRF are used for base registers of the prefix-sum operations. The master TCU can access these registers directly, but regular TCUs can only access them through a prefix-sum operation. There is only one prefix-sum unit, but the global register file has multiple registers, so a proper sharing mechanism is needed. At any cycle, the inputs of the prefix-sum unit will handle only one base register. Requests to other base registers have to wait their turn. The base register number for a particular clock cycle is determined by the requests from all TCUs. Each TCU has multi-bit output, where each bit represents a base register, and assert 1 at a proper bit when there is a request for a ps operation. In other words, there is a decoder for the ps operation. The bit-wise logic OR of all these outputs of the decoders from TCUs are used to determine the next base

register. The base registers are chosen in a round-robin fashion among those who actually have a request. This may introduce some delays in the beginning of a prefix-sum operation for a new base register, but not for the following operations.

### 2.1.5 Memory Modules and Hashing

To provide better bandwidth, XMT uses multiple memory modules, which operate independently. Clusters and memory modules are connected by an interconnection network. The memory address space is evenly divided among these memory modules. The shared caches are used for instructions only by the MTCU, not for TCUs, since the instructions for TCUs are broadcast by the MTCU and buffered in the instruction buffer. Within each memory module, the order of operations to the same location is preserved and a store operation can be acknowledged as soon as the cache module accepts the request, regardless if it results in a cache hit or miss. Each memory module also has an adder to support a fetch-and-add operation for any value of increment, unlike the ps instruction that can only support a binary input, 0 or 1. Resembling the NYU-Ultracomputer fetch-and-add, the prefix-sum-to-memory (psm) instruction is executed on cache modules and they are executed one after the other (in contrast to the ps instruction that processes requests concurrently).

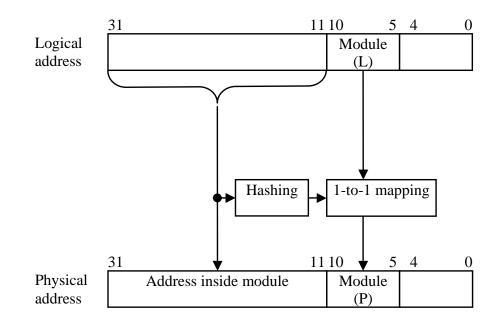

The memory space is divided evenly among memory modules. Each memory request will be dispatched from a cluster to one of those memory modules. In our

Figure 2.3: Physical address calculation with hashing

implementation, we assumed that the address is 32 bits and cache line is 32 bytes, which is the base element of mapping. One possible implementation of the allocation of memory addresses to memory modules is outlined below. Some bit fields of the address can be used to determine the cache module, such as the Module(L) (L means logical address) field consisting of bits 5 through 10 (4:0 is used as offset inside a cache line), as shown in figure 2.3. Bits 5 through 10 are chosen to have the smallest granuality, a cache line, in distributing to different cache modules. But then code exhibiting certain regularities could result in an imbalance among the number of accesses to different memory modules. The basic idea that has been used in the literature for coping with such imbalance is to employ the concept of hashing. This thesis does not claim that the problem of how best to use hashing for reducing imbalance, as well as for achieving the best overall performance, has been resolved. We only present a straw man solution for this fundamental problem, as we plan to thoroughly investigate it in the future. For a group of addresses that share the same upper field with different Module(L), a 1-to-1 mapping is used to map the natural module index (Module(L)) to the module index (Module(P), P means physical address), as in figure 2.3, so that they are always distributed to 64 memory modules. The hashed value is used to choose different 1-to-1 maps for different groups. Note that there are 64! 1-to-1 mappings of the set  $0,1,\dots,63$  onto itself.

## 2.1.6 Interconnection Network

Since an efficient interconnection network is so important to the XMT processor, we decided to custom design it and study its performance carefully. The behavioral description was incorporated into the current verilog HDL description to allow simulation of applications. The network has uniform delays for any sourcedestination pairs and it is designed to have zero interference between traffic for different destinations unless the network is heavily loaded or extremely unbalanced. More detailed description of the interconnection network appears in [8, 9, 7, 10].

# 2.2 Program Execution Flow

## 2.2.1 SPMD Programming Model

The XMT uses fine-grained SPMD (Single Program Multiple Data) programming model. The actual performance model is a hybrid of so-called arbitrary CRCW (Concurrent Read, Concurrent Write) and QRQW (Queue-Read, Queue-Write) [18]. XMT program starts with serial mode and it changes to parallel mode when a *spawn* instruction is executed. The spawn instruction carries two parameters: *low* and *high*, meaning the parallel thread id ranges between *low* and *high* inclusively. After all parallel threads finish, the MTCU executes *join* instruction and the processor changes back to serial mode. See figure 1.1 on page 9. When the *spawn* instruction is executed, the *low* and *high* are copied to global registers, GR-LOW and GR-HIGH respectively. GR-LOW is used as the base of prefix-sum operation, that assigns new thread IDs to the new available TCUs. GR-HIGH is used to store the upper bound of the valid thread ID and TCUs can generate a new thread during parallel mode by increasing GR-HIGH through *sspawn*, a prefix-sum operation to GR-HIGH with incremental value of one.

## 2.2.2 Parallel and Serial Mode Switch

The one important difference between the XMT and CMP is who manages the parallel threads. In CMP, normally the the OS (Operating System) is aware of the existence of the parallel threads and OS is responsible for the scheduling of the threads on the available processors. In the XMT, the parallel threads are not OS threads. All parallel threads are managed by hardware, this includes TCU assignment, termination of threads and completion of all parallel threads.

The change from serial to parallel mode is simpler than the reverse. When the MTCU encounters a *spawn* instruction, it initializes both GR-LOW and GR- HIGH and the XMT processor enters parallel mode. The MTCU also starts the broadcasting of instructions in the parallel section through the instruction bus at the beginning of parallel mode.

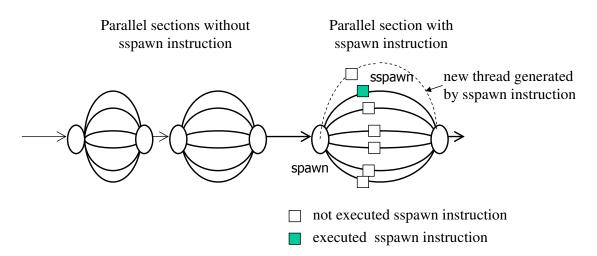

The transition from parallel to serial mode is more involved because of the *sspawn* instruction that can increase the GR-HIGH dynamically (see figure 2.4. The *sspawn* instruction is a prefix-sum operation with GR-HIGH as the base register and incremental value of one (1). The differences between *spawn* and *sspawn* instructions are listed in table 2.1.

Figure 2.4: Single Spawn (sspawn). A parallel thread can generate a new thread by increasing GR-HIGH. The figure shows that not all threads executed the sspawn instruction in a parallel section because of different execution paths

When the XMT processor enters parallel mode, GR-LOW and GR-HIGH, two designated global registers, are loaded with the low and high bounds of thread IDs and the value of GR-HIGH is broadcast to all TCUs. The spawn instruction prompts the master TCU to broadcast the instructions between the spawn and join

|                             | spawn       | sspawn        |

|-----------------------------|-------------|---------------|

| executed by                 | MTCU        | TCU           |

| executed in                 | serial mode | parallel mode |

| number of generated threads | any         | 1             |

Table 2.1: Comparison between spawn and sspawn instruction

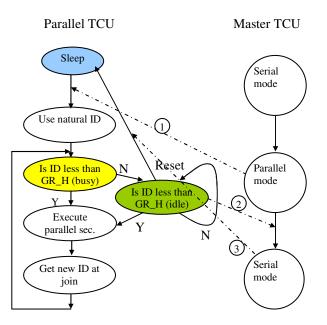

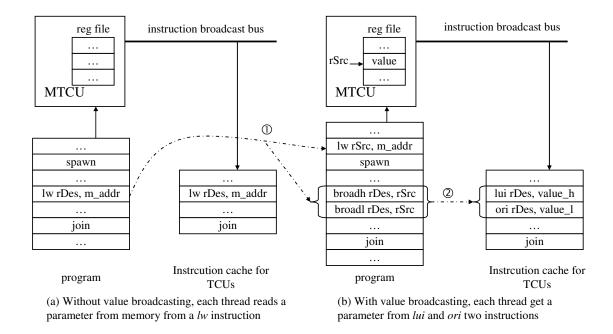

instructions and then wait for completion of the parallel execution. Clusters, groups of TCUs, are activated by broadcasting the instructions (link ① in Figure 2.5). The broadcasted instructions are saved to local instruction buffers at clusters. Such broadcasting is more efficient than having the TCUs fetch instructions from main memory and load the memory system with intensive read requests. However, the number of instructions that can be stored in the instruction buffers is limited and TCUs have to fetch instructions from shared caches through the interconnection network for larger parallel sections.

A TCU executes one virtual thread at a time. TCU i starts by executing virtual thread i (its natural ID). When the number of virtual threads exceed the number of TCUs in the XMT processor, a TCU may serially execute multiple threads. A TCU obtains a new virtual thread whenever it finishes executing the previous one. Unlike the assignment of the virtual thread IDs to the TCUs for the first virtual thread they execute, more effort is needed for later ID assignments. This is done using dedicated prefix-sum hardware with GR-LOW as the base. Upon reaching a join

Figure 2.5: Transitions between serial and parallel modes with sspawn

instruction, a TCU gets a new virtual thread ID from the ps operation and jumps to the beginning of the parallel section. The TCU either enters an idle state when its allocated ID exceeds GR-HIGH (namely, it is beyond the scope of the current spawn command), or executes the parallel section with the valid thread ID.

It is possible that an allocated thread ID that exceeds GR-HIGH at a certain point of time becomes valid later, after GR-HIGH increases. To handle this case, TCUs in idle state will keep comparing its ID with GR-HIGH. If the ID becomes valid due to an *sspawn* in another TCU, the TCU will execute the virtual thread immediately. The MTCU is capable of detecting when all TCUs are in their idle state by checking the logic AND of all idle flags as this will signal that the execution of the current parallel section has been completed. Then the MTCU would change execution mode back to serial mode and continue (link 2) in Figure 2.5). The Master TCU resets all clusters after it changes back to serial mode (link ③ in Figure 2.5).

# 2.2.3 Observation on Synchronization Needs of Nested Spawn (sspawn) Implementation

In the current XMT processor model, nesting of parallel sections is allowed through the use of a *sspawn* instruction. The basic mechanism of increasing the number of virtual threads that need to be executed by a prefix-sum to register GR-HIGH was noted before. But, should the programmer use nested spawn commands, and have the compiler translate them to *sspawn* commands, or use *sspawn* commands directly? This question is beyond the scope of the thesis. However, regardless of how this question is resolved, proper management of the *sspawn* instruction is necessary to prevent potential explosion in the number of new virtual threads (and possibly the memory that will be needed for storing initialization data). Quite a few studies, including Leiserson's MIT Cilk project [12], have considered ways for coping with the memory explosion possibility, and we do not have anything new to add to it. Below, we chose to highlight one new subtle observation with respect to the initialization data. The observation appears to be fundamental and could be of wider interest beyond just the XMT platform.

An attractive feature of XMT is its so-called independence of order semantics (IOS). While applicable in different ways to different levels of abstraction, IOS means that a parallel thread can advance to the end of a parallel section (i.e., until it reaches a *join* command) without ever needing to wait for any other thread. In general,

IOS greatly reduces (though it does not always completely eliminate, as the new observation below shows) busy-wait (or spin-wait) between parallel threads. (As an example for IOS, consider use of a ps command to GR-HIGH by a thread executing a *sspawn* command. The relevant point is that this parent thread needs only wait for the feedback from the ps functional units but not on any other thread.) However, the observation presented below will lead to the conclusion that the introduction of *sspawn* instruction makes some synchronization between the parent thread and child thread inevitable.

The busy-wait inevitability observation: Suppose that the parent thread is responsible for: (i) initializing input data for the child thread, and (ii) declaring it (through an *sspawn* command). Then the child thread must busy-wait at least once on its parent thread.