#### ABSTRACT

Title of dissertation: HIGH-SPEED ANALOG-TO-DIGITAL

CONVERTERS FOR MODERN SATELLITE RECEIVERS: DESIGN VERIFICATION

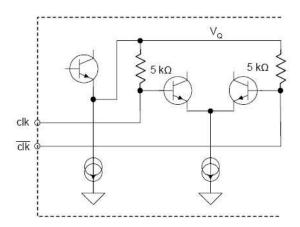

TEST AND SENSITIVITY ANALYSIS

Seokjin Kim

Doctor of Philosophy, 2008

Dissertation directed by: Dr. Martin Peckerar

Department of Electrical and Computer

Engineering

Mixed-signal System-on-chip devices such as analog-to-digital converters (ADC) have become increasingly prevalent in the semiconductor industry. Since the complexity and applications are different for each device, complex testing and characterization methods are required. Specifically, signal integrity in I/O interfaces requires that standard RF design and test techniques must be integrated into mixed signal processes. While such techniques may be difficult to implement, on-chip test-vehicles and RF circuitry offer the possibility of wireless approaches to chip testing. This would eliminate expensive wafer probing solution to verify the design of high-speed ADC functionality currently required for high-speed product evaluation.

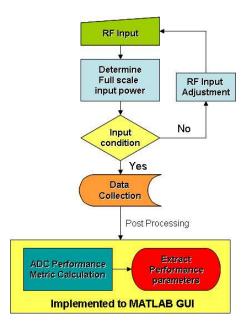

This thesis describes a new high-speed analog-to-digital converter test methodology. The target systems used on-chip digital de-multiplexing and clock distribution. A detail sequence of performance testing operations is presented. Digital outputs are post processed and fed into a computer-aided ADC performance characterization tool which is custom-developed in a MATLAB GUI. The problems of high sampling rate ADC testing are described. The test methodologies described reduce test costs and overcome many test hardware limitations. As our focus is on satellite receiver systems, we emphasize the measurement of inter-modulation distortion and effective resolution bandwidth. As a primary characterization component, Fourier analysis is used and we address the issue of sample window adjustment to eliminate spectral leakage and false spur generation. A 6-bit 800 MSamples/sec dual channel SiGe-based ADC is used as a target example and investigated on the corner lot process variations to determine the impact of process variations and the sensitivity of the ADCs to critical process parameter variations.

## HIGH-SPEED ANALOG-TO-DIGITAL CONVERTERS FOR MODERN SATELLITE RECEIVERS: DESIGN VERIFICATION TEST AND SENSITIVITY ANALYSIS

by

## Seokjin Kim

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2008

Advisory Committee:

Professor Martin Peckerar, Chair/Advisor

Professor Neil Goldsman

Professor Pamela Abshire

Professor Kristine M. Rosfjord

Professor Aristos Christou

© Copyright by Seokjin Kim 2008

## Preface

This work is about the design verification and production test methodologies for high-speed analog-to digital converters(ADCs), which is an example of system-on-chip devices. It came to our attention that there are few references available to enlighten the design/test engineer on the concepts of design verification and production testing of high-speed ADC system-on-a-chip (SoC) devices. The research intention developed here is to link RF design and test concepts to mixed-signal SoC testing for developing high-speed ADCs.

Throughout this research, we define any system whose operation requires a 100 MHz or faster system clock as a "high-speed" or "high-sampling" system. In the digital output of ADCs, we refer to any system requiring greater than or equal to 8-bits as "high-accuracy." Under the topic of high-speed ADCs, there are three major categories of both analog and digital: design, testability, and sensitivity. ADC design and testability is closely related to ADC input and output interface configurations. ADC sensitivities are more related to a semiconductor process technology and to design maturity.

Indeed, many component descriptions presented here are based on the conventional ADC characterization and ADC design. We extend these to the more capable ADC design verification methodologies for a modern satellite receiver that are the subject of the dissertation. These research topics are taken two steps further:

- Describing a new cost effective dynamic test methodology;

- Explaining how to implement design verification and production testing solutions for high-sampling rate ADCs.

Test and measurement are both unique and exceptionally important to the development of modern electronics technology. Tests and measurements of RF/mixed-signal and SoC devices are routine bench-top activities in laboratories, but design verification and production tests add more complexities and constraints to perform those tests and measurements while maintaining the same level of quality. It is erroneously thought that testing is a "low technology" arena that is well understood. Current day integrated circuits (ICs) must merge analog and digital function and operate in the millimeter wave regime. RF design techniques must be brought to bear at all levels of design. Simply getting test signals into such systems is a challenge and to recover the circuit response without distortion is more of a challenge. In the past, most effort was devoted to chip design and fabrication. The result was a product that was not factory testable - a guaranteed failure in the field.

This work merges high-speed ADC design approaches with "design for testability." It is a primal target to provide a test stand capable of evaluating analog-to-digital converter systems designed to sample at a rate near a giga-sample per second or faster. Exploring the limits of performance of high sampling rate ADC (high-speed mixed signal ICs) is also a part of the work. Throughout this work, novel test

methodologies are highlighted. This research is intended to show the step-by-step approach to high-speed ADC design verification and production tests to help many of ADC design engineer in both industry and academia.

Seokjin Kim

Analog & Mixed-signal System Design Lab.

University of Maryland, College Park

## Dedication

To my loving parents for being the best parents that any son could wish for.

I would be lost without their love and guidance.

To my wise brother and beautiful sisters, who define strength and determinations.

You always believe in me.

$I\ love\ you\ all$  and

Thank you to teach me how to appreciate all that my life hands to me.

## Acknowledgements

I would like to thank to my best and most trusted, respectful academic advisor and mentor, Dr. Martin M. Peckerar, for his kind advice and timeless encouragement. More than words can ever describe for his tremendous amount of support and friendship I depend on. Throughout my Ph.D. research, his great enthusiasm for innovation and engineering is truly inspirational with his open-mind personality. I also give my special appreciations to all committee members, Dr. Neil Goldsman, Dr. Pamela Abshire, Dr. Kristine M. Rosfjord, and Dr. Aristos Christou. Without their guidance and collaborations, the RF/mixed-signal device and system characterizing test laboratory could not be established in the University of Maryland, College Park.

As a member of Analog and Mixed-signal System Design Laboratory, University of Maryland, College Park, I would like to also thank my colleagues: Kwangsik Choi, Yves Ngu, Keir Lauritzen, Jimmy Wienke, Jeff Allnut, Po-Hsin Chen, Hsinche Chang, Scott Baumann, and Sanaz Adl. I appreciate all their help, support, interest and valuable discussions.

I would like to express my gratitude to Dr. Keith Perkins from US Naval Research Laboratory (Washington, D.C.). Initial stage of the my research work for high-speed mixed-signal SoCs testing could excel with his friendly advice and collaboration.

I am bound to express my gratefulness to Hughes Network Systems (Germantown, MD). While collaborating with HNS, I had been exposed to a robust industrial engineering and product development environment that culture is testing the ASIC, a part of the SPACEWAY program. I would like to thank Jovan Preradovic and Richard Thompson for their technical assistance in configuring laboratory test equipment and test preparations. I acknowledge the administrative support and access to the HNS SPACEWAVE program offered me by Thomas Jackson, Bala Subramaniam and Mallik Moturi. I am deeply indebted to Radmil Elkis and Lam-Vien Nguyen (Thales Communications Systems) for assistance evaluating and bench-marking the high-speed analog-to-digital converter verification programs (VTS suite) I developed in the cause of my thesis work.

Personally, I would like to send my special thank to Diktys Stratakis in the University of Maryland, College Park and Jorge A. Ruiz Cruz who is now a professor in the Universidad Autonoma de Madrid, Spain for their trustful friendships throughout my Maryland life - Thanks buddies!

There are many people who I could not include in this short acknowledgement.

I really thank to all those who gave me the possibility to complete this thesis.

Seokjin Kim

Analog & Mixed-signal System Design Lab.

University of Maryland, College Park

# Table of Contents

| Li | st of             | Tables                                                             | xii |

|----|-------------------|--------------------------------------------------------------------|-----|

| Li | st of             | Figures                                                            | xiv |

| Li | st of.            | Abbreviations                                                      | XX  |

| 1  | Intr              | oduction                                                           | 1   |

|    | 1.1               | Overview                                                           | 1   |

|    | 1.2               | General philosophy                                                 | 2   |

|    | 1.3               | Motivation and objective                                           |     |

|    | 1.4               | Outline of thesis                                                  |     |

|    | 1.5               | Contributions                                                      |     |

|    | 1.6               | Glossary of terms                                                  |     |

| 2  | An                | Overview of ADCs and ADC Test Procedures                           | 19  |

|    | 2.1               | Overview                                                           | 19  |

|    | 2.2               | ADC architectures                                                  |     |

|    |                   | 2.2.1 Flash ADC                                                    | 21  |

|    |                   | 2.2.2 Integrating ADC                                              |     |

|    |                   | 2.2.3 Pipelined ADC                                                |     |

|    |                   | 2.2.4 Successive-approximation-resister(SAR) ADC                   |     |

|    |                   | 2.2.5 Sigma Delta $(\Sigma - \Delta)$ ADC                          |     |

|    |                   | 2.2.6 Two-step ADC                                                 |     |

|    | 2.3               | ADC architecture tradeoffs                                         |     |

|    | 2.4               | ADCs as mixed-signal SoCs for modern satellite communications      |     |

|    | 2.5               | Design verification tests: From component characterization to pro- |     |

|    |                   | duction testing                                                    | 40  |

|    | 2.6               | Capital expensive items for design verification tests              |     |

|    | $\frac{2.7}{2.7}$ | Conduct a design verification test                                 |     |

|   |      | 2.7.1   | Process of a design verification test              |

|---|------|---------|----------------------------------------------------|

|   |      |         | 2.7.1.1 DVT-1                                      |

|   |      |         | 2.7.1.2 DVT-2                                      |

|   |      | 2.7.2   | DVT plan and hardware verification test (HVT) 47   |

|   | 2.8  | Produ   | ct development process                             |

|   | 2.9  | Summ    | uary                                               |

| 3 | Higł | n-speed | ADC Characterization: New Results 51               |

|   | 3.1  | Overv   | <mark>iew</mark>                                   |

|   |      | 3.1.1   | The test specification process                     |

|   |      | 3.1.2   | A test design example:                             |

|   | 3.2  | High-s  | speed ADC functionality                            |

|   |      | 3.2.1   |                                                    |

|   |      | 3.2.2   | Digital output timing                              |

|   |      | 3.2.3   | Latency                                            |

|   |      | 3.2.4   | Track-and-Hold requirements                        |

|   | 3.3  | Differe | ential I/O designation                             |

|   | 3.4  |         | level definitions                                  |

|   | 3.5  |         | ge                                                 |

|   | 3.6  | Interfa | ace                                                |

|   |      | 3.6.1   | I/O designation                                    |

|   |      | 3.6.2   | I/O description                                    |

|   |      | 3.6.3   | Power supply                                       |

|   |      | 3.6.4   | Analog inputs                                      |

|   |      | 3.6.5   | Digital inputs                                     |

|   |      |         | 3.6.5.1 Clock-cycle                                |

|   |      | 3.6.6   | Logic outputs: LVDS                                |

|   |      | 3.6.7   | Miscellaneous I/O                                  |

|   | 3.7  | Electr  | ostatic-discharge(ESD) protection                  |

|   | 3.8  |         | nary                                               |

| 4 | Test | Fixtur  | re and Design Verification Test Setup 94           |

|   | 4.1  |         | iew                                                |

|   | 4.2  | Test fi | exture and periphery subsystem design for speed 95 |

|   |      | 4.2.1   | The ADC socket                                     |

|   |      | 4.2.2   | Sub-system design for I/Os                         |

|   |      | 4.2.3   | Power supply decoupling                            |

|   |      | 4.2.4   | Device interface board (DIB) design                |

|   | 4.3  | Test s  | etup and equipment suite                           |

|   | 44   | Summ    | 125<br>125                                         |

| 5 | AD(  | C Design Verification Software and Test Methodologies  | 127   |

|---|------|--------------------------------------------------------|-------|

|   | 5.1  | Overview                                               | . 127 |

|   | 5.2  | ADC DVT and characterization                           | . 128 |

|   |      | 5.2.1 Linear ADC                                       | . 130 |

|   |      | 5.2.2 Compressing ADC                                  | . 152 |

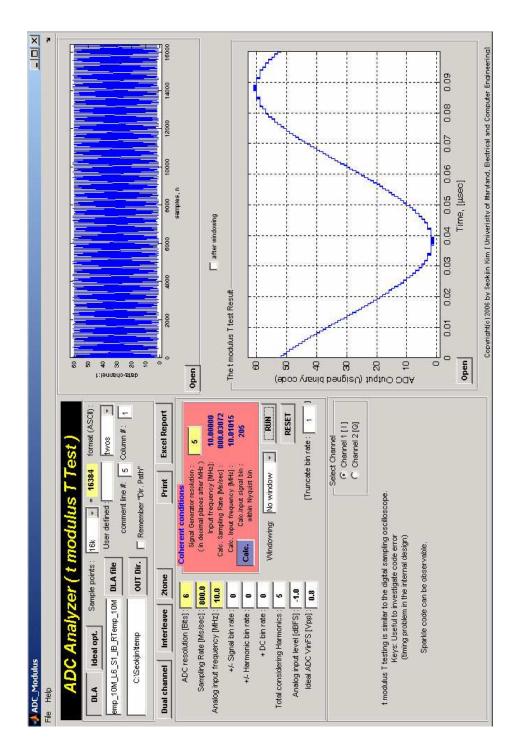

|   | 5.3  | A verification test software (VTS)                     | . 159 |

|   |      | 5.3.1 VTS features                                     | . 164 |

|   |      | 5.3.2 Why the VTS is unique?                           | . 164 |

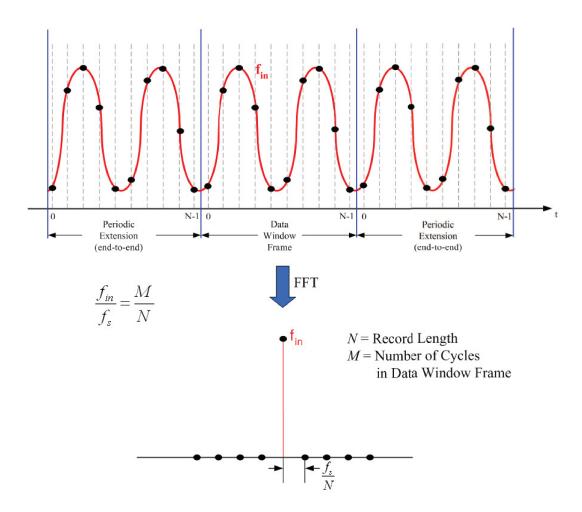

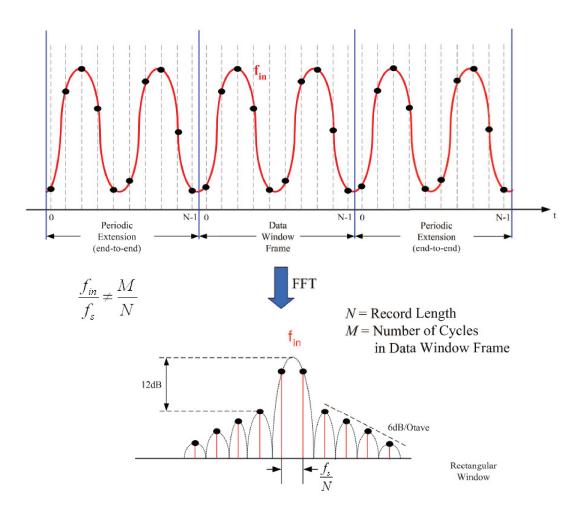

|   |      | 5.3.3 Spectral leakage and windowing                   | . 165 |

|   | 5.4  | High-speed ADC DVT methodology                         | . 171 |

|   |      | 5.4.1 Operations                                       | . 172 |

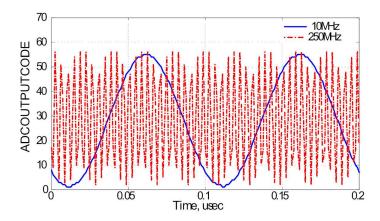

|   |      | 5.4.2 Sine wave reconstruction test                    | . 182 |

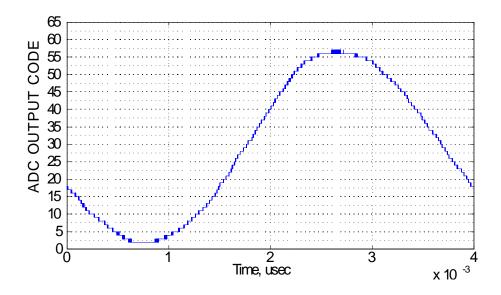

|   |      | 5.4.3 Sine wave code error test                        | . 182 |

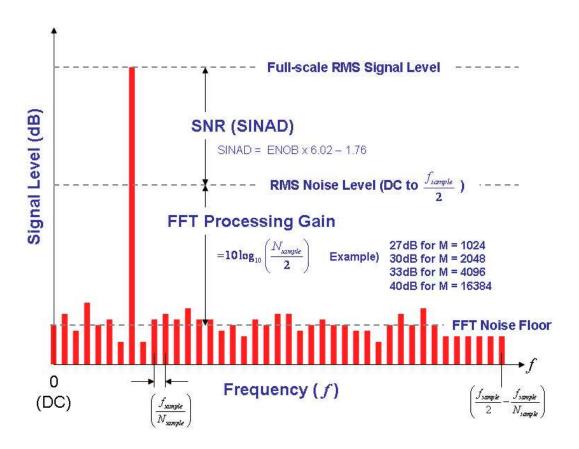

|   |      | 5.4.4 The fast Fourier transform                       | . 183 |

|   |      | 5.4.5 Sine wave histogram test and linearity           | . 189 |

|   |      | 5.4.5.1 Differential nonlinearity (DNL)                | . 194 |

|   |      | 5.4.5.2 Integral nonlinearity (INL)                    | . 195 |

|   |      | 5.4.6 Effective resolution bandwidth test              | . 197 |

|   |      | 5.4.7 Two-tone sine wave intermodulation test          | . 197 |

|   |      | 5.4.7.1 IMD <sub>3</sub> and IP <sub>3</sub>           | . 198 |

|   |      | 5.4.8 Analog power test and dynamic range              | . 200 |

|   |      | 5.4.9 Testing in the temperature extremes              | . 203 |

|   | 5.5  | Production tests                                       | . 208 |

|   |      | 5.5.1 Continuity( $I_{DDQ}$ ) test                     | . 209 |

|   | 5.6  | Test result summary                                    | . 210 |

| 6 | Sens | sitivity Analysis on High-speed ADCs: Corner Lot Study | 214   |

|   | 6.1  | Overview                                               |       |

|   | 6.2  | Process variations                                     |       |

|   |      | 6.2.1 Global variations                                |       |

|   |      | 6.2.2 Mismatch variations                              |       |

|   |      | 6.2.3 Corner lot definition                            | . 218 |

|   | 6.3  | Thames ASIC corner lot study                           | . 219 |

|   | 6.4  | Test description                                       |       |

|   |      | 6.4.1 Test requirements and setup                      |       |

|   | 6.5  | Test results                                           |       |

|   |      | 6.5.1 DC Test                                          | . 227 |

|   |      | 6.5.2 Dynamic performance test                         | . 228 |

|   | 6.6  | Test results and discussion                            | . 230 |

|   | 6.7  | Summary                                                | . 236 |

| 7  | Cond   | clusions |                                                                    | 237 |

|----|--------|----------|--------------------------------------------------------------------|-----|

|    | 7.1    | Summa    | ary                                                                | 237 |

|    | 7.2    |          | butions                                                            |     |

|    | 7.3    | Future   | work                                                               | 241 |

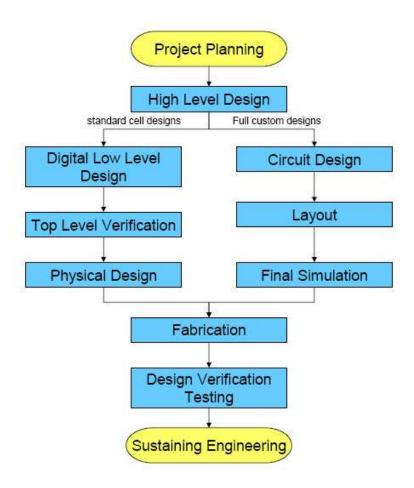

| Ap | pend   | ix A: V  | LSI design procedure                                               | 243 |

|    | A.1    | Quality  | y policy and objectives                                            | 244 |

|    | A.2    | Project  | $ m t \; flow \; \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 246 |

|    |        | A.2.1    | Project planning                                                   | 248 |

|    |        | A.2.2    | High level design                                                  | 248 |

|    |        | A.2.3    | Digital low level design                                           | 251 |

|    |        | A.2.4    | Top level verification                                             | 252 |

|    |        | A.2.5    | Physical design                                                    | 254 |

|    |        | A.2.6    | Circuit design                                                     | 255 |

|    |        | A.2.7    | Layout                                                             | 256 |

|    |        | A.2.8    | Final simulation                                                   | 256 |

|    |        | A.2.9    | Fabrication                                                        | 258 |

|    |        | A.2.10   | Design verification testing                                        | 258 |

|    |        | A.2.11   | Sustaining engineering                                             | 260 |

| Bi | bliogr | aphy     |                                                                    | 263 |

## List of Tables

| 2.1  | Hardware design physical testing summary                                  | 47  |

|------|---------------------------------------------------------------------------|-----|

| 3.1  | HNS <i>Thames</i> ASIC high-speed ADC logic-level definition              | 64  |

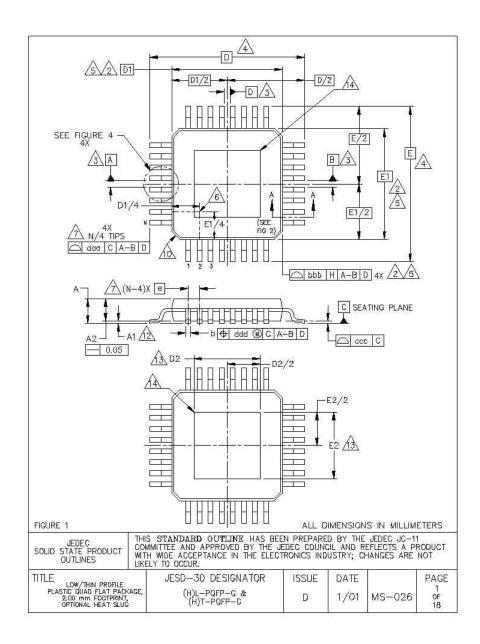

| 3.2  | HNS <i>Thames</i> ASIC high-speed ADC Package dimensions                  | 68  |

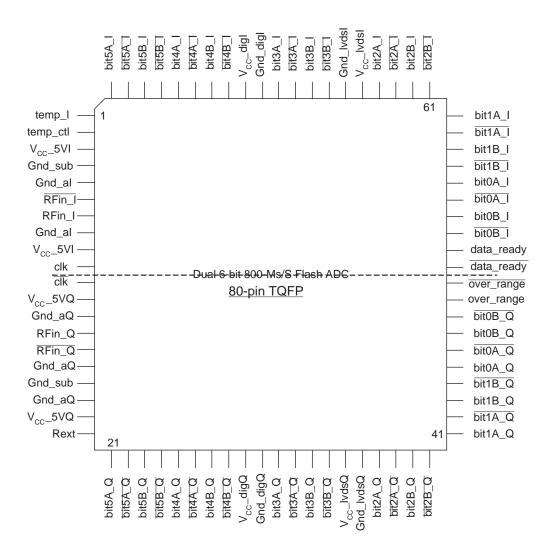

| 3.3  | High-speed ADC I/O pin description                                        | 71  |

| 3.4  | Thames ASIC I/O summary                                                   | 75  |

| 3.5  | High-speed ADC ASIC pin connections designated to ground                  | 76  |

| 3.6  | High-speed ADC ASIC supply voltage                                        | 76  |

| 3.7  | Electrical parameters for custom differential clock inputs                | 80  |

| 3.8  | Electrical parameters for LVDS output drivers                             | 81  |

| 3.9  | Digital output code                                                       | 83  |

| 3.10 | HNS $Thames$ ASIC high-speed ADC ESD diode connections                    | 87  |

| 5.1  | Popular ADC input window functions and figures of merit                   | 171 |

| 5.2  | High-speed ADC tests - wafer and final production                         |     |

|      |                                                                           | 200 |

| 5.3  | Summary of HNS 6-bit Dual Channel ADC at room temperature $(25^{\circ}C)$ | 211 |

| 5.4 | VTS suite vs. other program                                                |

|-----|----------------------------------------------------------------------------|

| 6.1 | Thames ASIC corner lot process variation condition                         |

| 6.2 | HNS Thames ASIC corner lot split, designation, and variation condition 223 |

| 6.3 | Thames measured analog 5V supply current                                   |

| 6.4 | Thames measured LVDS 5V supply current                                     |

| 6.5 | Thames measured digital and LVDS 3V supply current                         |

| 6.6 | Thames measured bias voltages                                              |

| 6.7 | Thames Dynamic results summary - I channel at Room temperature 229         |

| 6.8 | Thames Dynamic results summary - Q channel at Room temperature 230         |

# List of Figures

| 2.1  | ADC architectures, applications, resolution and sampling rates            | 20 |

|------|---------------------------------------------------------------------------|----|

| 2.2  | Typical flash ADC Architecture                                            | 22 |

| 2.3  | Interpolation scheme in a flash ADC                                       | 23 |

| 2.4  | Single-slope ADC Architecture                                             | 25 |

| 2.5  | Typical dual-slope ADC Architecture                                       | 27 |

| 2.6  | A pipeline ADC block diagram                                              | 28 |

| 2.7  | Successive-approximation-resister (SAR) ADC                               | 30 |

| 2.8  | Second order sigma-delta ADC                                              | 32 |

| 2.9  | Two-step ADC architecture                                                 | 33 |

| 2.10 | ADC architecture tradeoffs                                                | 35 |

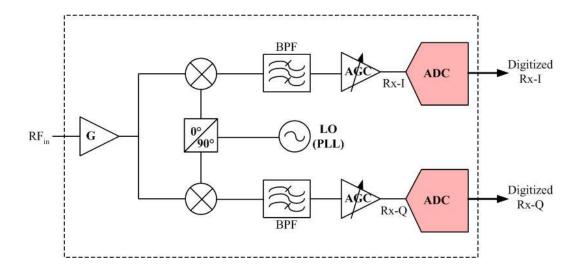

| 2.11 | Typical satellite receiver function block                                 | 37 |

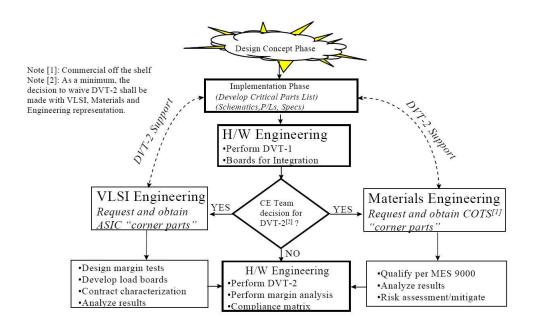

| 2.12 | Design verification process outline                                       | 44 |

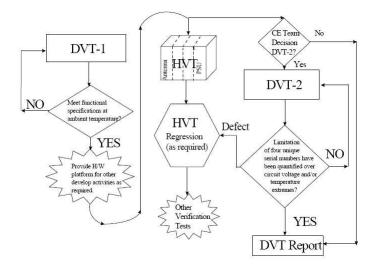

| 2.13 | Over all flow of the 2 phased DVT and the relationship to HVT $$          | 48 |

|      |                                                                           |    |

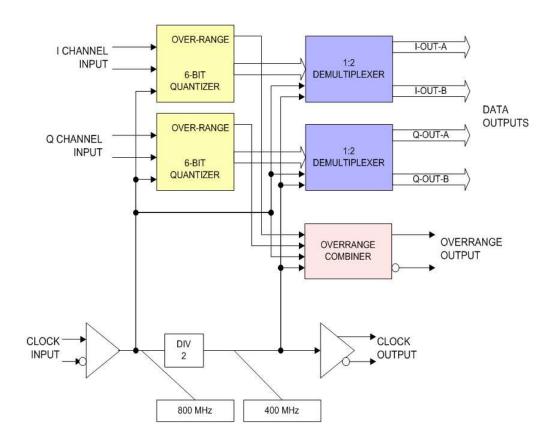

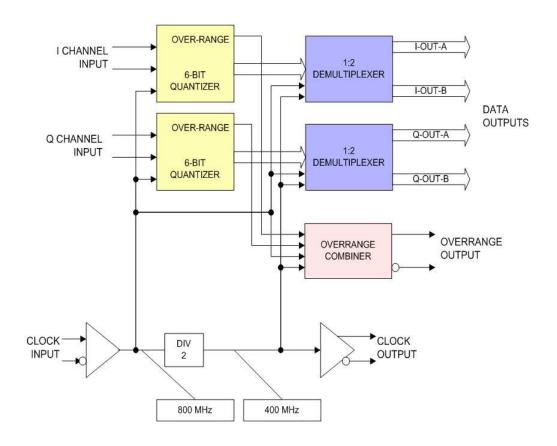

| 3.1  | Top level functional block for the HNS $\mathit{SPACEWAY}$ high-speed ADC | 55 |

| 3.2  | HNS SPACEWAY high-speed ADC ASIC block diagram                            | 57 |

|      |                                                                           |    |

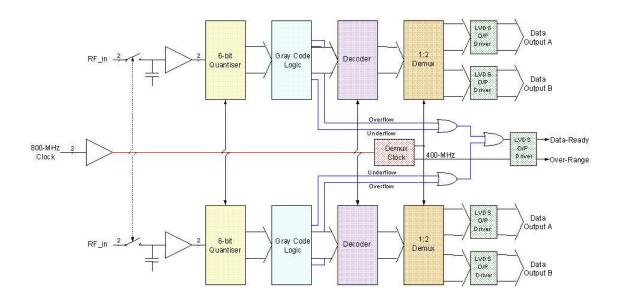

| 3.3  | HNS SPACEWAY high-speed ADC ASIC block diagram for design verification tests              | 59  |

|------|-------------------------------------------------------------------------------------------|-----|

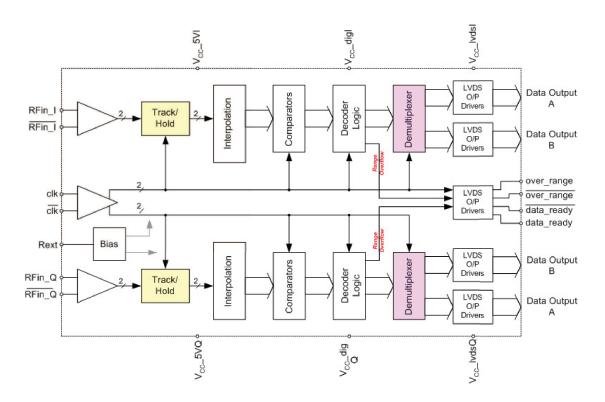

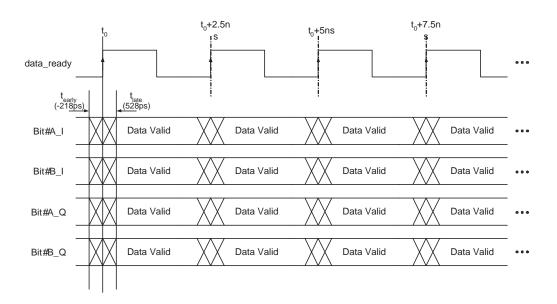

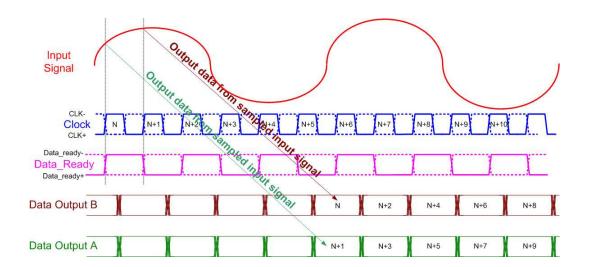

| 3.4  | HNS SPACEWAY Thames high-speed ADC ASIC data output timing relationship                   | 61  |

| 3.5  | HNS SPACEWAY Thames high-speed ADC latency                                                | 62  |

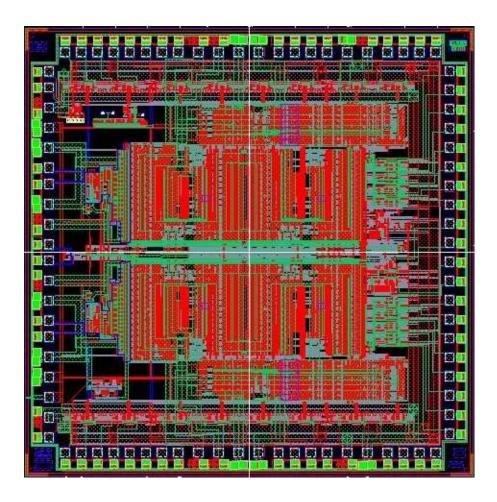

| 3.6  | Thames ASIC layout view                                                                   | 65  |

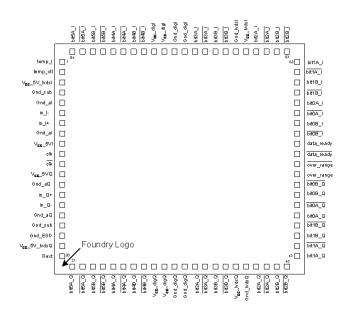

| 3.7  | High-speed ADC ASIC bond pad designation                                                  | 66  |

| 3.8  | Thames ASIC bonding diagram for 80-pin TQFP                                               | 66  |

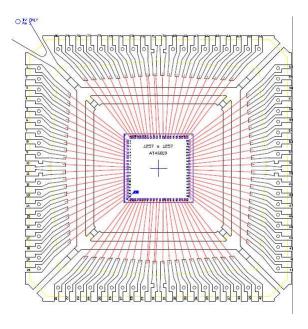

| 3.9  | HNS SPACEWAY Thames ASIC Package outline                                                  | 67  |

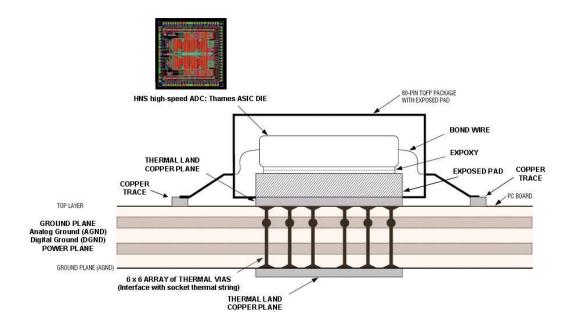

| 3.10 | High speed dual channel 6-bit TQFN packaged ADC thermal management                        | 69  |

| 3.11 | High-speed ADC I/O Designation for 80-pin TQFP                                            | 70  |

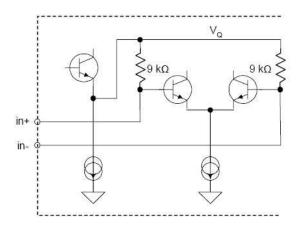

| 3.12 | High-speed ADC RF input equivalent circuit                                                | 78  |

| 3.13 | High-speed ADC RF input equivalent circuit for sampling clock input                       | 79  |

| 3.14 | LVDS output voltage levels                                                                | 82  |

| 3.15 | LVDS digital output signals and LVDS offsets                                              | 82  |

| 3.16 | LVDS output driver termination                                                            | 84  |

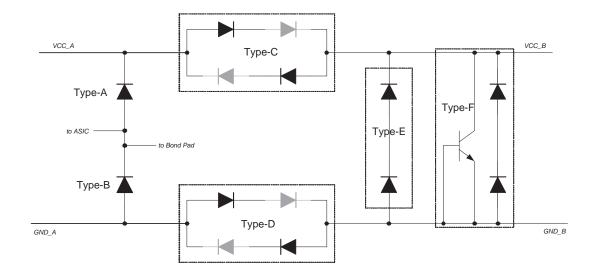

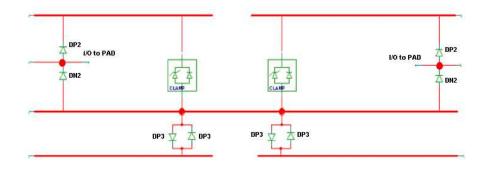

| 3.17 | ESD diode structure types                                                                 | 85  |

| 3.18 | General configuration of multi-supply clamp and input protection scheme                   | 86  |

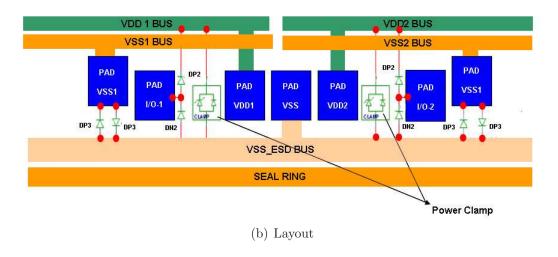

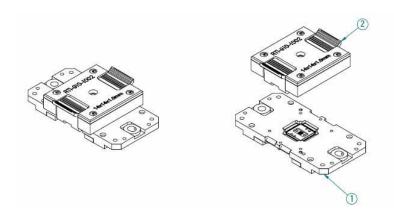

| 4.1  | High speed dual channel 6-bit ADC test fixture with a mounting socket                     | 97  |

| 4.2  | High speed dual channel 6-bit ADC (TQFN packaged) mounting socket                         | 99  |

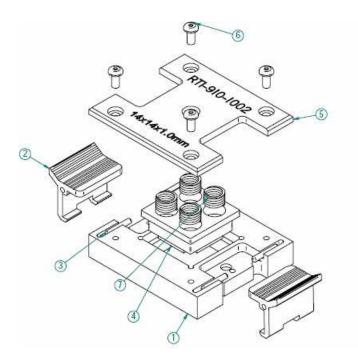

| 4.3  | High speed dual channel 6-bit ADC (TQFN packaged) mounting socket dual latch lid assembly | 100 |

| 4.4  | High speed dual channel 6-bit ADC (TQFN packaged) mounting socket assembly (bottom)       | 101 |

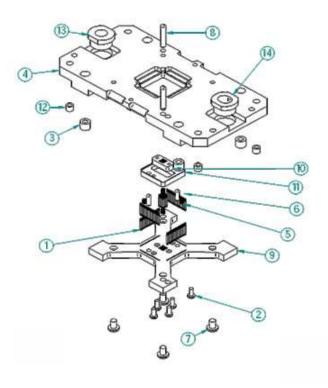

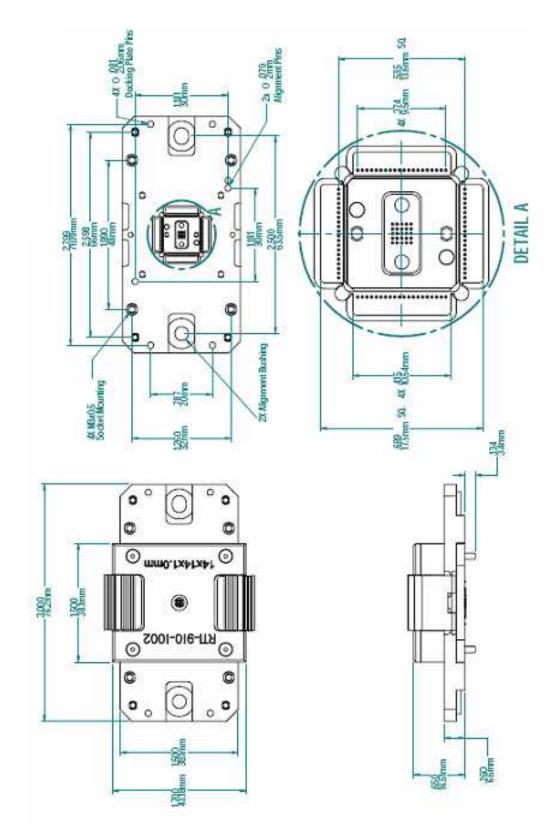

| 4.5  | High speed dual channel 6-bit ADC (TQFN packaged) mounting socket mechanical drawing                         |

|------|--------------------------------------------------------------------------------------------------------------|

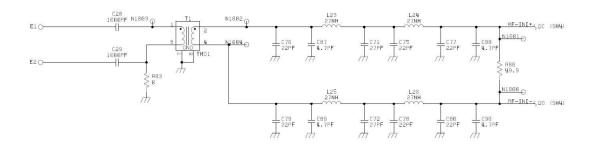

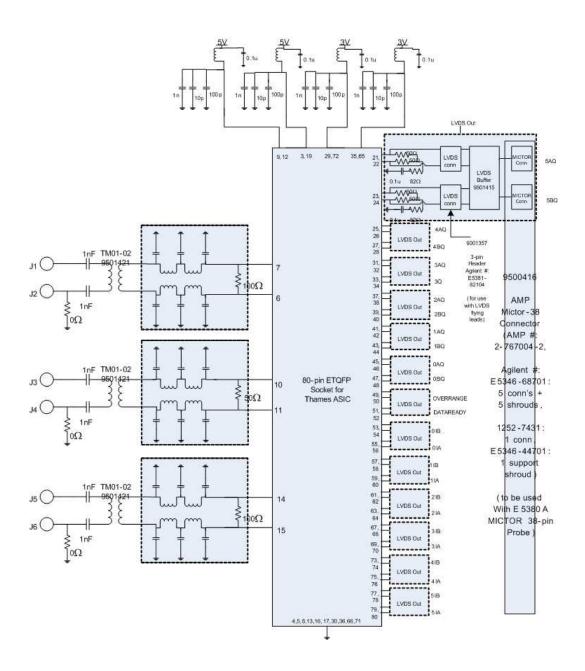

| 4.6  | Thames RF input for I-channel                                                                                |

| 4.7  | Thames RF input for clock                                                                                    |

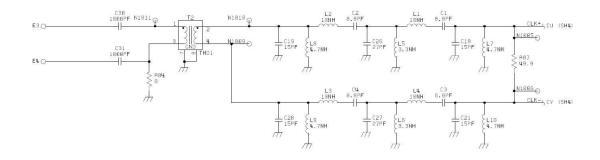

| 4.8  | Thames Power supply decoupling schematic capture                                                             |

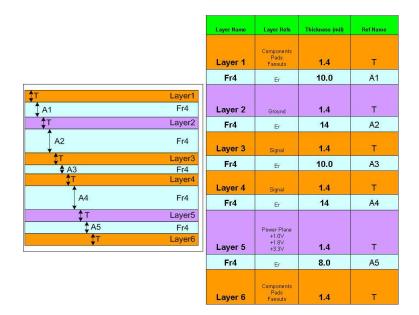

| 4.9  | High speed dual channel 6-bit ADC test device interface board (DIB) layer stack-up information               |

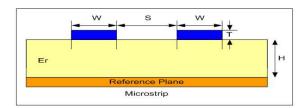

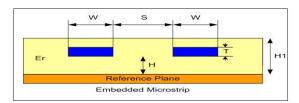

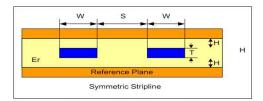

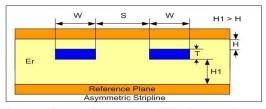

| 4.10 | Microstriplines impedance calculation chart                                                                  |

| 4.11 | Striplines impedance calculation chart                                                                       |

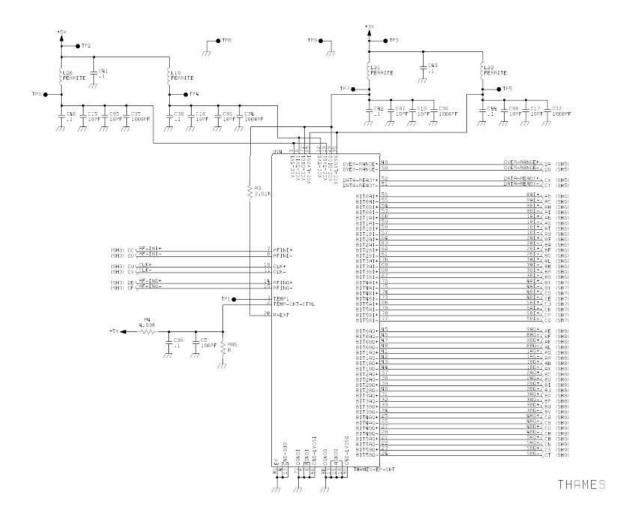

| 4.12 | High speed dual channel 6-bit ADC test fixture DIB total schematic design                                    |

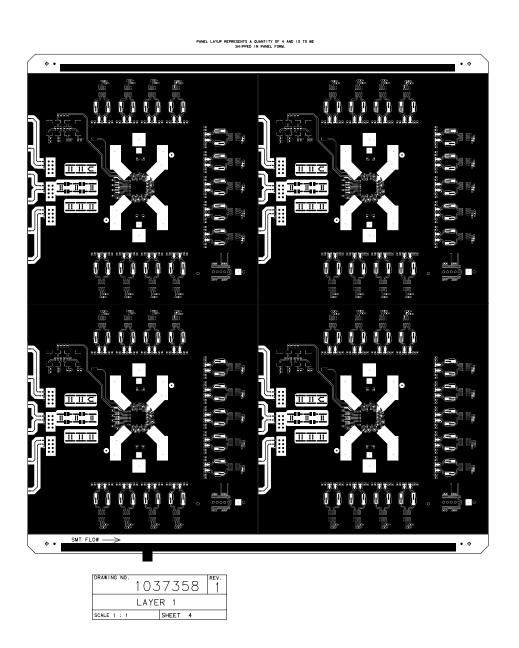

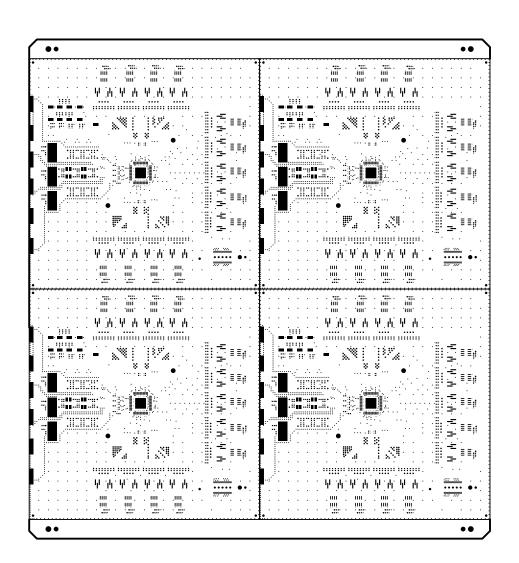

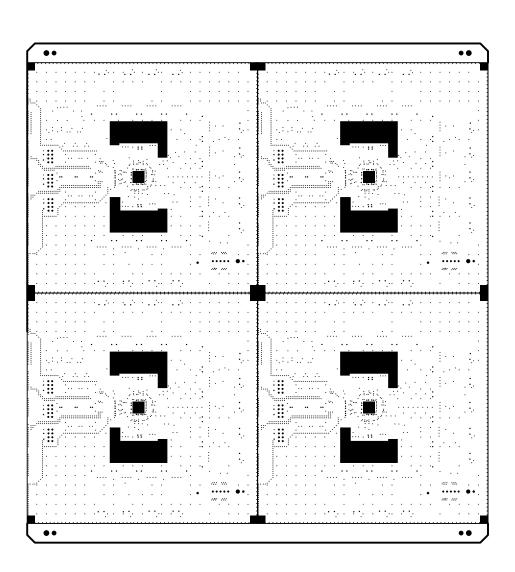

| 4.13 | High speed dual channel 6-bit ADC test fixture DIB Layer 1 112                                               |

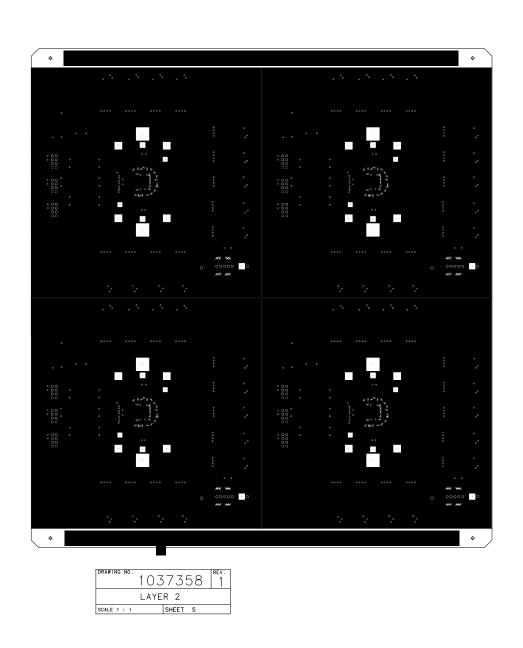

| 4.14 | High speed dual channel 6-bit ADC test fixture DIB Layer 2 113                                               |

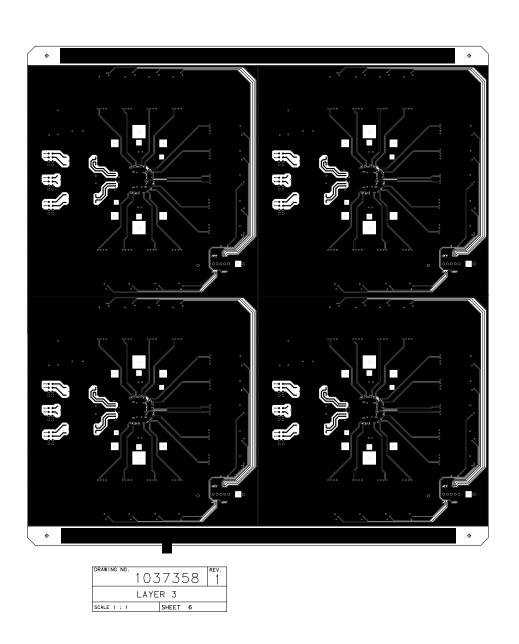

| 4.15 | High speed dual channel 6-bit ADC test fixture DIB Layer 3 114                                               |

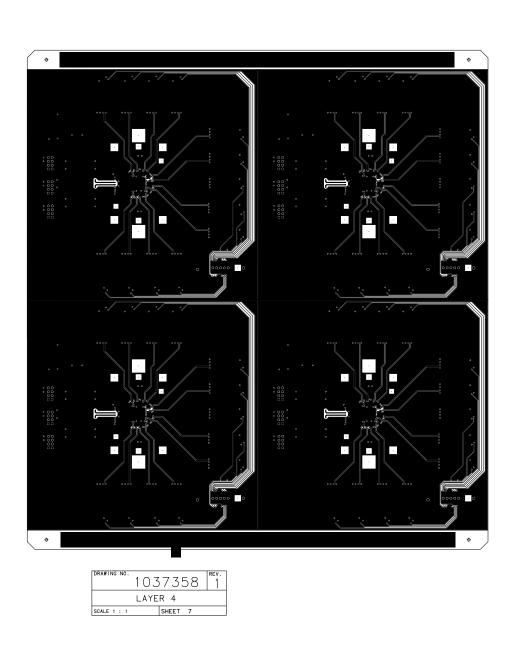

| 4.16 | High speed dual channel 6-bit ADC test fixture DIB Layer 4 115                                               |

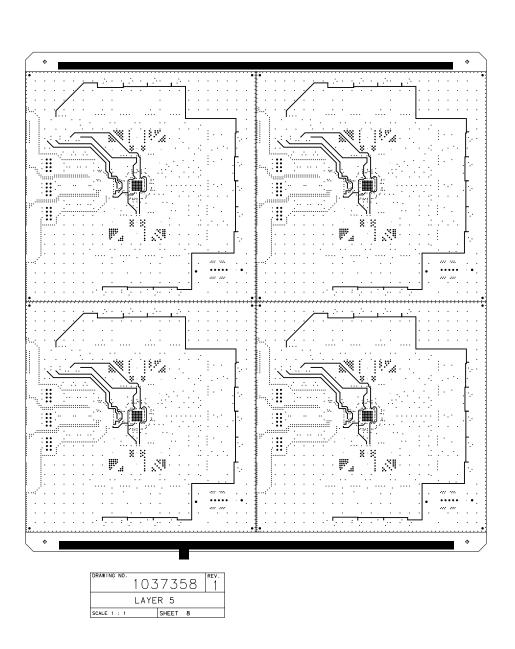

| 4.17 | High speed dual channel 6-bit ADC test fixture DIB Layer 5 116                                               |

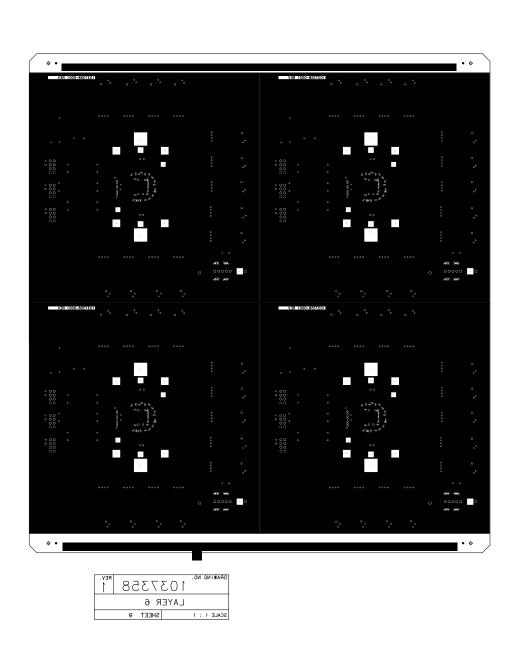

| 4.18 | High speed dual channel 6-bit ADC test fixture DIB Layer 6 117                                               |

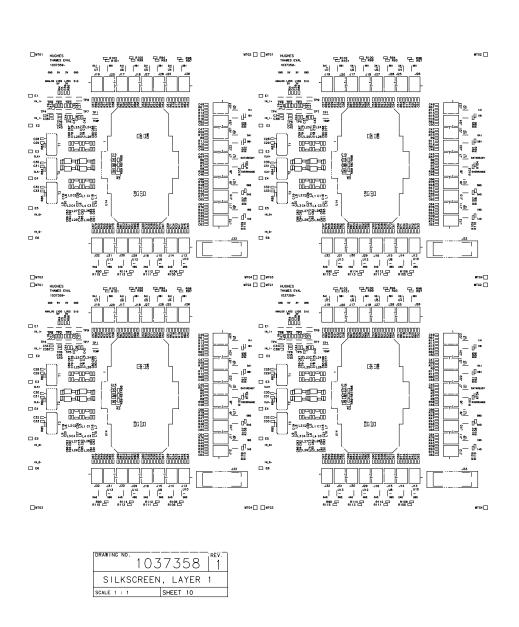

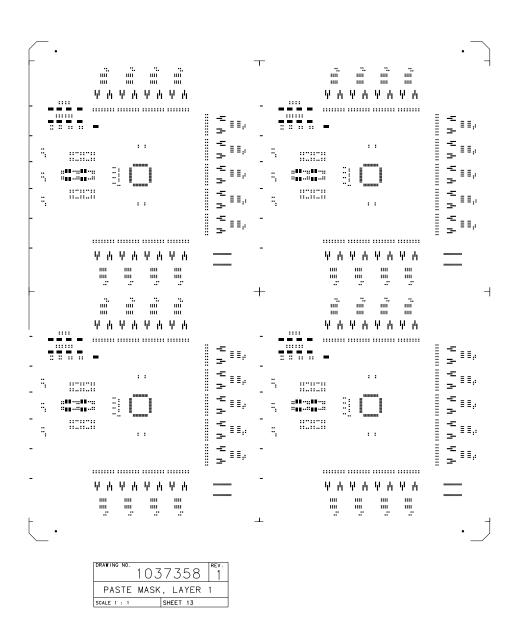

| 4.19 | High speed dual channel 6-bit ADC test fixture DIB Layer 1 silkscreen118                                     |

| 4.20 | High speed dual channel 6-bit ADC test fixture DIB Layer 1 soldermask119                                     |

| 4.21 | High speed dual channel 6-bit ADC test fixture DIB Layer 1 pastemask $120$                                   |

| 4.22 | $\label{thm:eq:high-speed} \mbox{High speed dual channel 6-bit ADC test fixture DIB Layer 6 soldermask 121}$ |

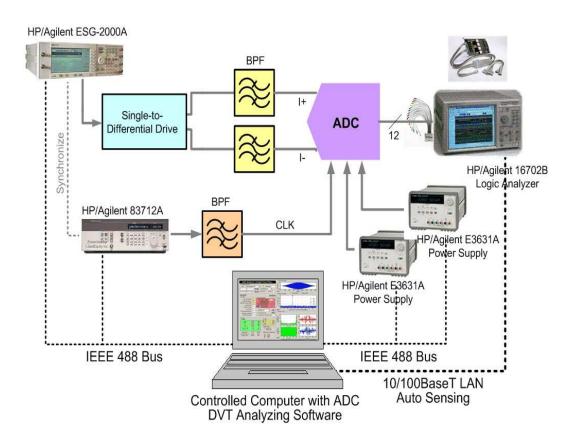

| 4.23 | Single channel differential ADC dynamic testing configuration 123                                            |

| 4.24 | Thames ASIC test bench setup photograph                                                                      |

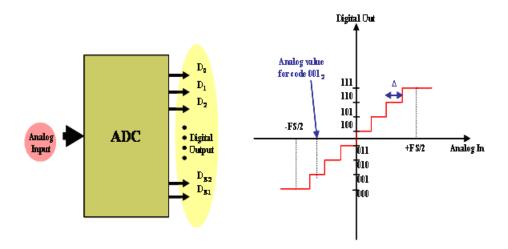

| 5.1  | Flash ADC basic architecture                                                                                 |

| 5.2  | General ADC and 3-bit ADC transfer function                                                         |

|------|-----------------------------------------------------------------------------------------------------|

| 5.3  | ADC static ramp testing                                                                             |

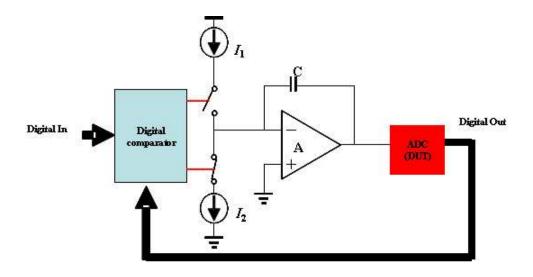

| 5.4  | ADC static test - servo loop testing                                                                |

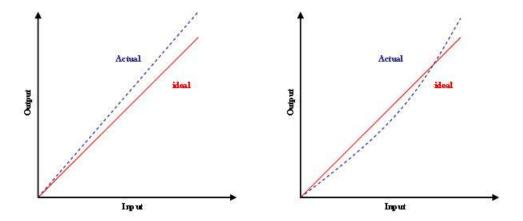

| 5.5  | Gain errors of ADC                                                                                  |

| 5.6  | ADC transfer function and non-linearity                                                             |

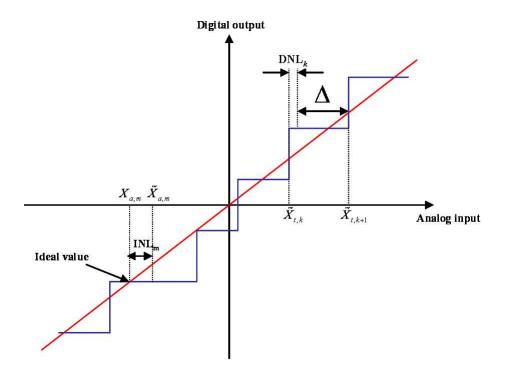

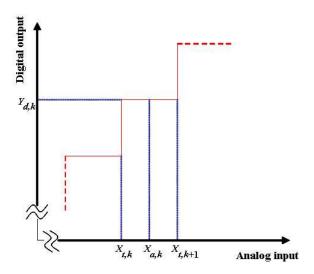

| 5.7  | Non-ideal ADC transfer function with INL and DNL errors                                             |

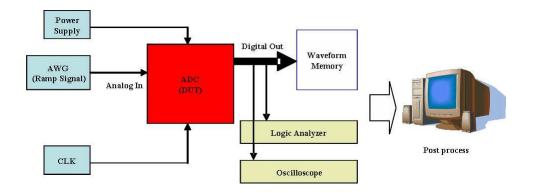

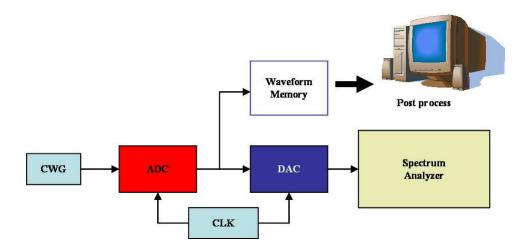

| 5.8  | ADC dynamic test setup                                                                              |

| 5.9  | MAXIM MAX1148 (80 MS/s 10-bit ADC) FFT spectrum                                                     |

| 5.10 | Signal-to-noise-and-distortion vs. input power                                                      |

| 5.11 | Effective resolution bandwidth of ADC                                                               |

| 5.12 | Intermodulation distortions of ADC                                                                  |

| 5.13 | Block diagram of the characterized compressing ADC                                                  |

| 5.14 | A compressing flash ADC architecture                                                                |

| 5.15 | 3-bit compressing ADC transfer function                                                             |

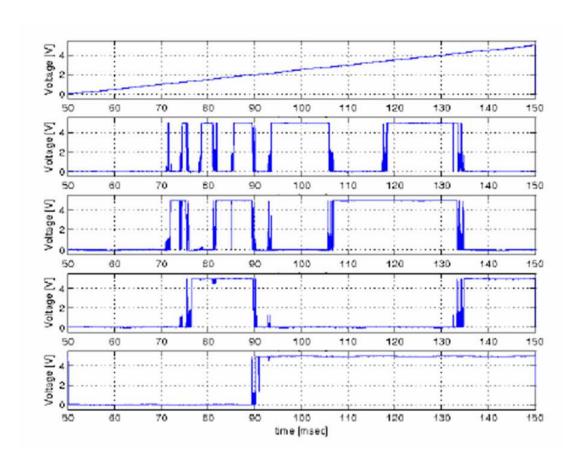

| 5.16 | 3-bit compressing ADC bitwise digital output waveforms ( $V_{ref} = 100 \text{ mV}$ )               |

| 5.17 | Characterized 4-bit 80 MS/s compressing ADC digital outputs $157$                                   |

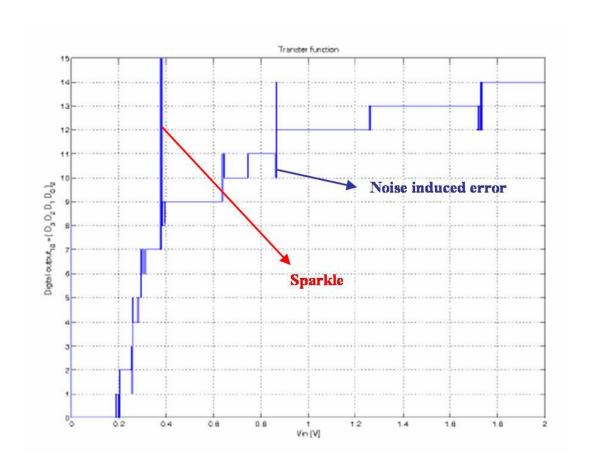

| 5.18 | Measured static transfer function for 4-bit 80 MS/s compressing ADC 158                             |

| 5.19 | Dynamic performance I of a 4-bit 80MS/s compressing ADC 160                                         |

| 5.20 | Dynamic performance II of a 4-bit 80MS/s compressing ADC 161                                        |

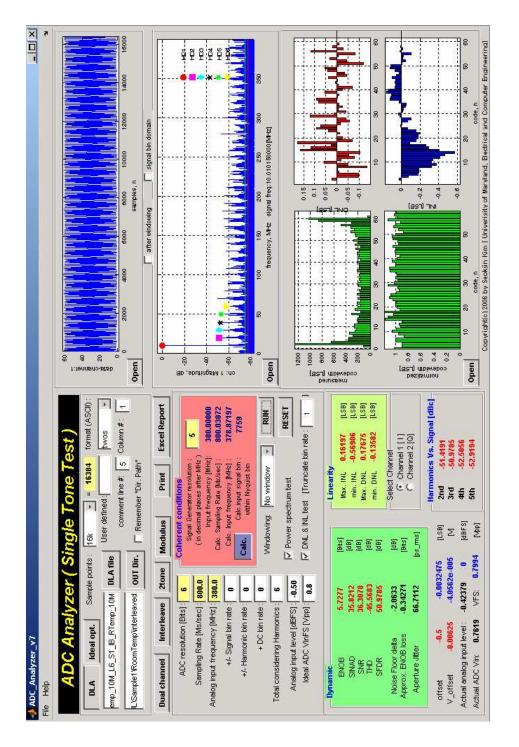

| 5.21 | High-speed ADC design verification test software main frame interface 163                           |

| 5.22 | FFT representation of pure sine wave having integral number of cycles in a sampling data window     |

| 5.23 | FFT representation of pure sine wave having non-integral number of cycles in a sampling data window |

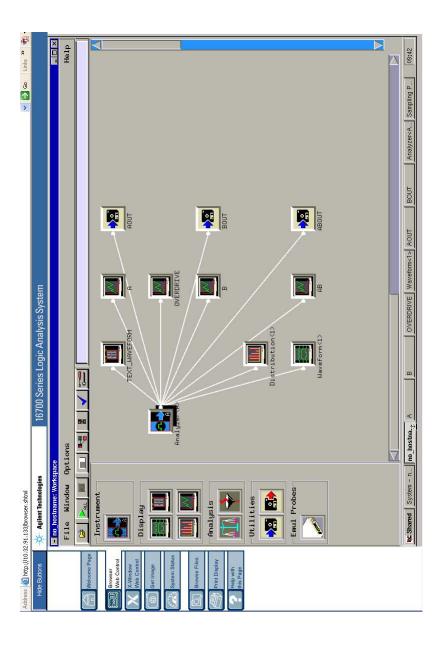

| 5.24 | High-speed ADC DVT operations with VTS                                                    |

|------|-------------------------------------------------------------------------------------------|

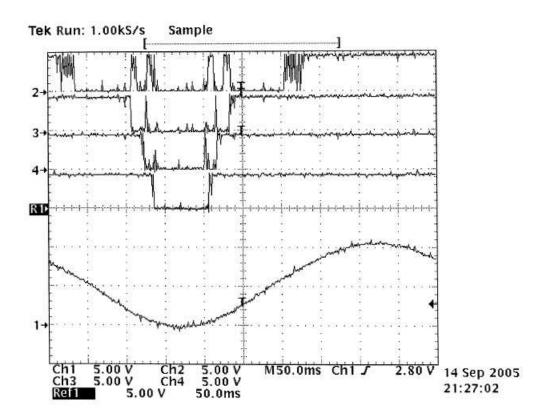

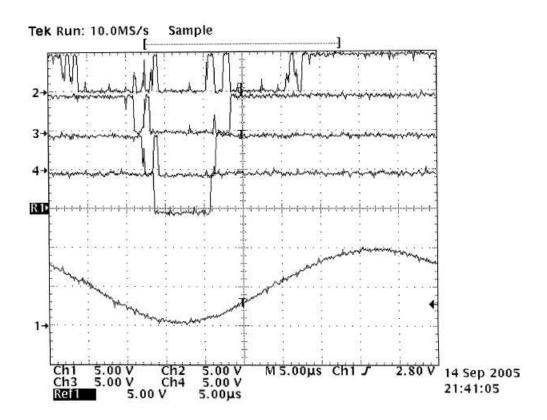

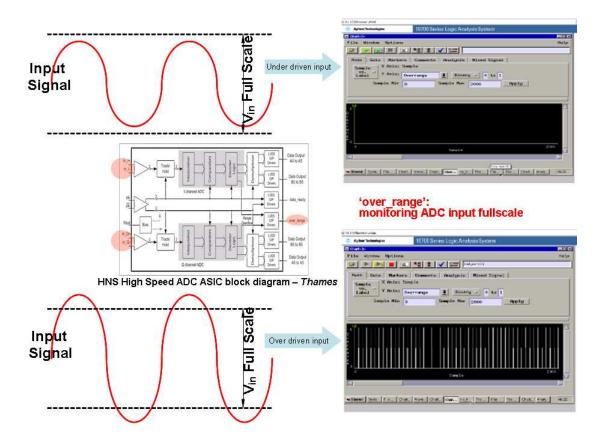

| 5.25 | Thames ADC DVT DLA setup configuration                                                    |

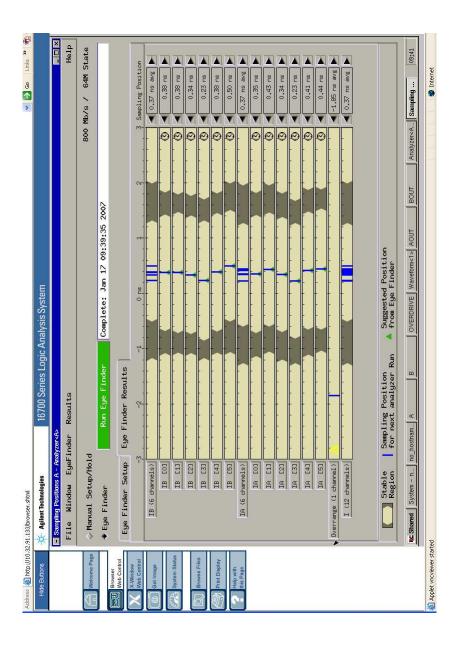

| 5.26 | Thames ADC demultiplexed digital output channel DLA eye analysis for triggering           |

| 5.27 | Thames ADC demultiplexed digital output channel A data successful acquiring using the DLA |

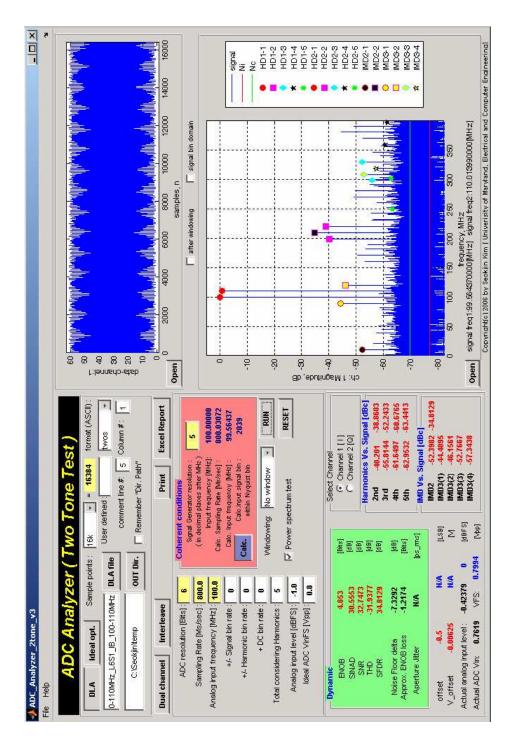

| 5.28 | High-speed ADC DVT VTS suite two-tone testing module GUI $$ 180                           |

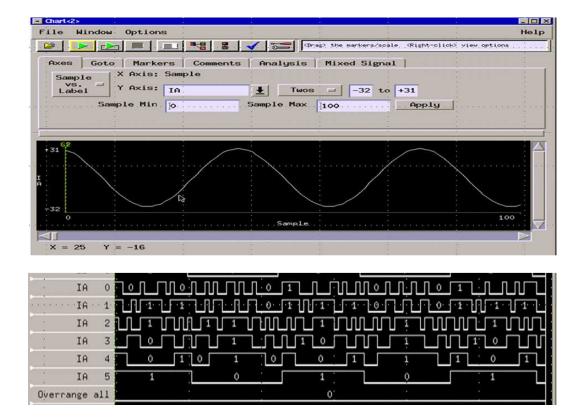

| 5.29 | VTS time-domain analysis tool: code-error testing module 181                              |

| 5.30 | Sine wave reconstruction test result                                                      |

| 5.31 | Sine wave code error test result                                                          |

| 5.32 | FFT output with effects of processing gain                                                |

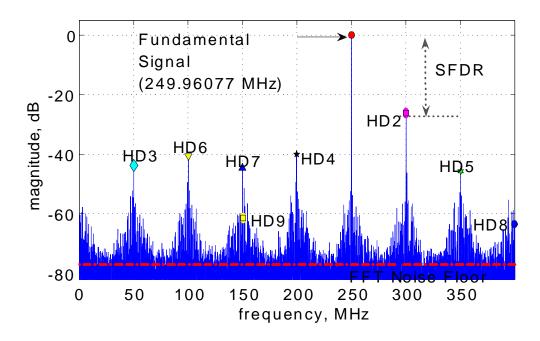

| 5.33 | Power spectrum of <i>Thames</i> ASIC ADC with 250 MHz Sine wave sampled at 800 MS/s rate  |

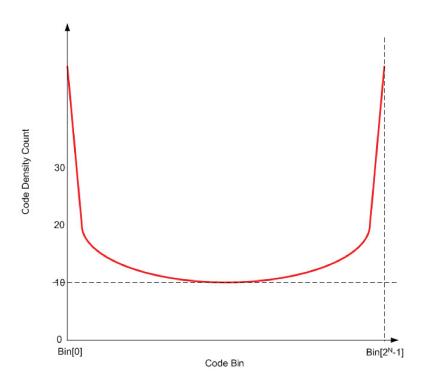

| 5.34 | ADC Histogram Sine wave input                                                             |

| 5.35 | Code probability distribution of a sine wave                                              |

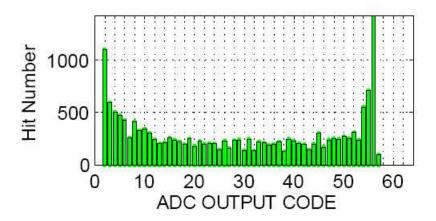

| 5.36 | Histogram test result based on a code density test                                        |

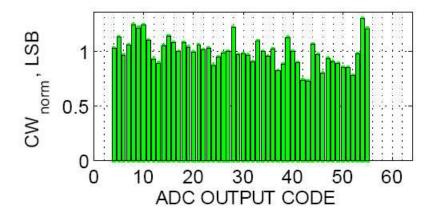

| 5.37 | Normalized codewidth LSB result from Figure 5.36 193                                      |

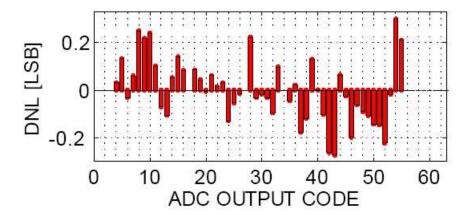

| 5.38 | Differential nonlinearity result                                                          |

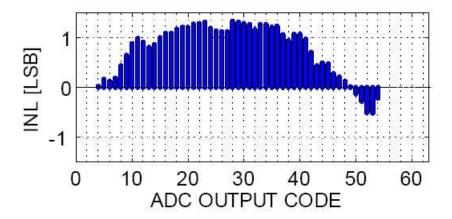

| 5.39 | Integral nonlinearity result                                                              |

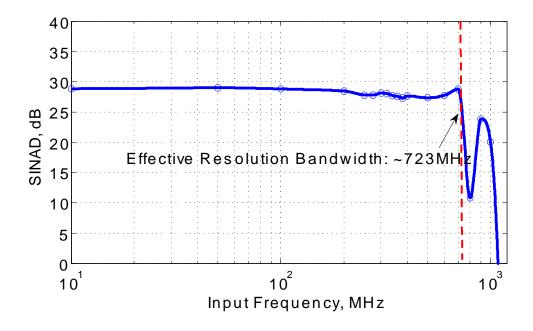

| 5.40 | Effective resolution bandwidth under 800 MS/s sampling rate 198                           |

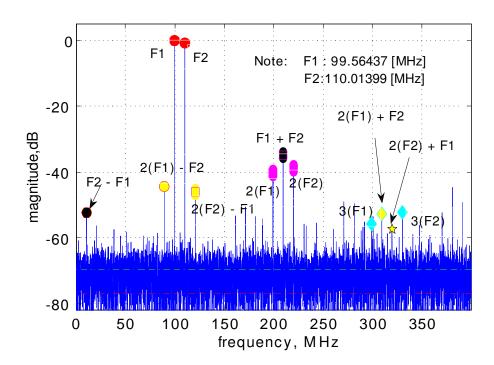

| 5.41 | Two-tone sine wave IMD product test result                                                |

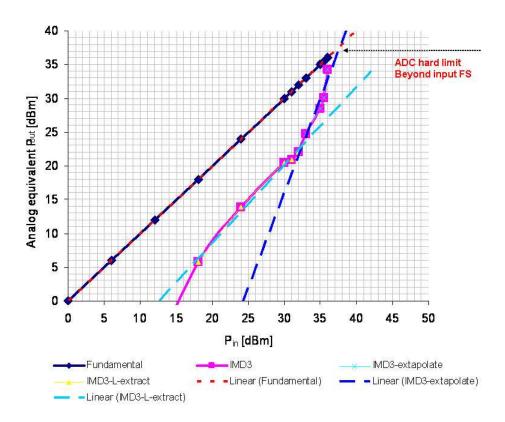

| 5.42 | Intercept points for <i>Thames</i> ASIC ADC                                               |

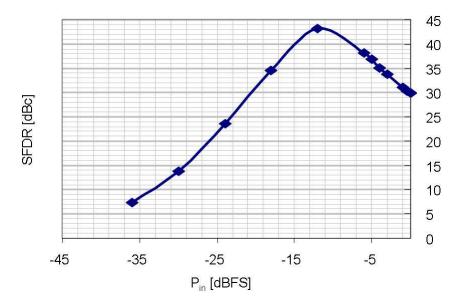

| 5.43 | Two-tone spurious free dynamic range characteristics for $\it Thames  ASIC202$            |

| 5.44 | Thames ASIC ADC analog power testing calibration                                          |

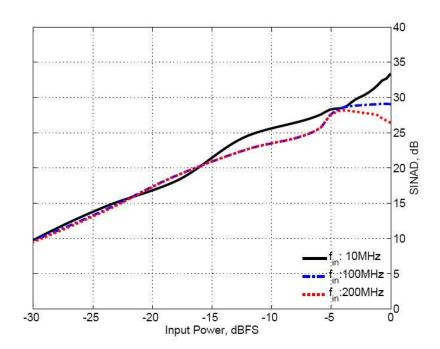

| 5.45 | Signal-to-noise-and-distortion (SINAD) to ADC analog input power . 205                    |

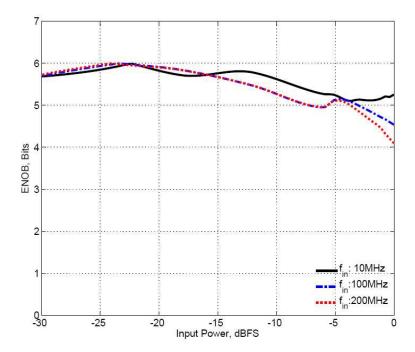

| 5.46 | Effective-numbers-of-bit (ENOB) to ADC analog input power 206                                 |

|------|-----------------------------------------------------------------------------------------------|

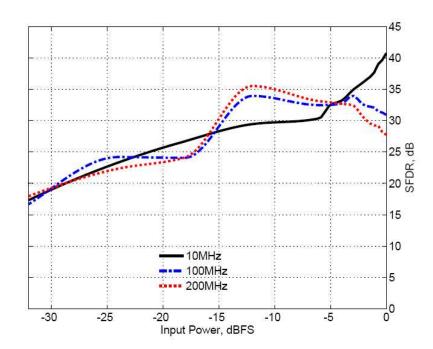

| 5.47 | Spurious free dynamic range (SFDR) characteristics for <i>Thames</i> ASIC analog input levels |

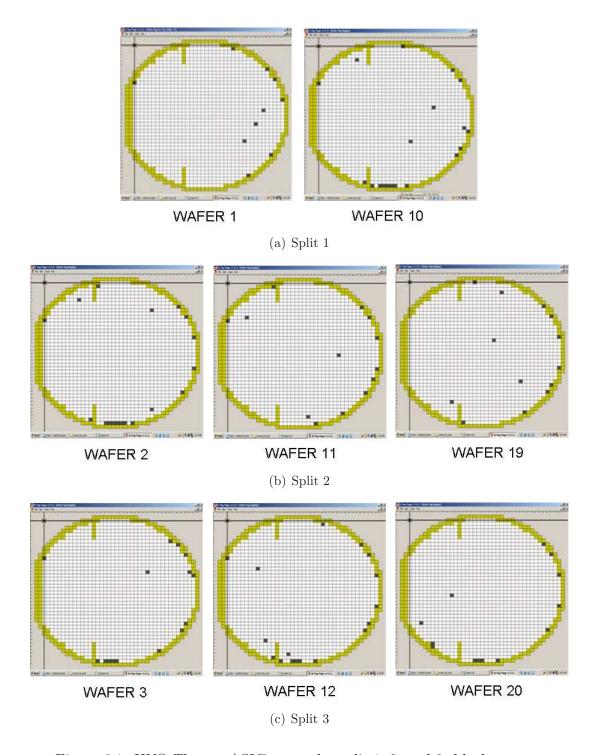

| 6.1  | HNS <i>Thames</i> ASIC corner lot split 1, 2, and 3                                           |

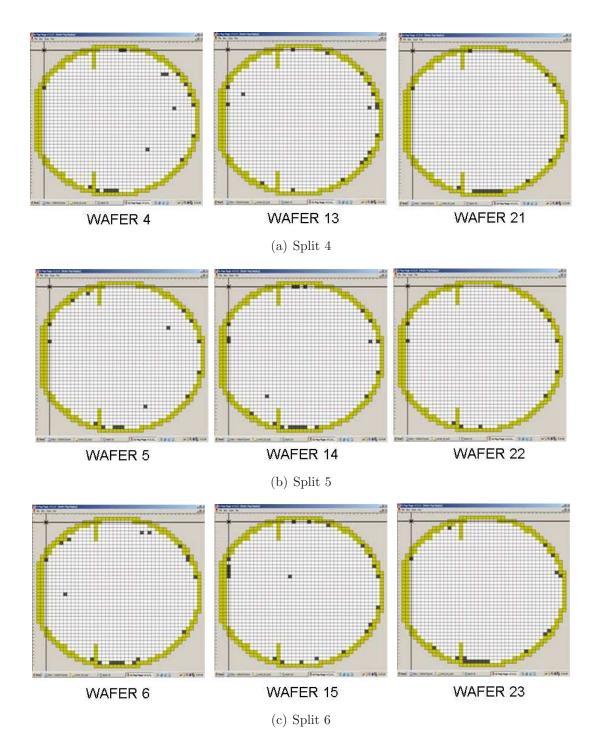

| 6.2  | HNS Thames ASIC corner lot split 4, 5 and 6                                                   |

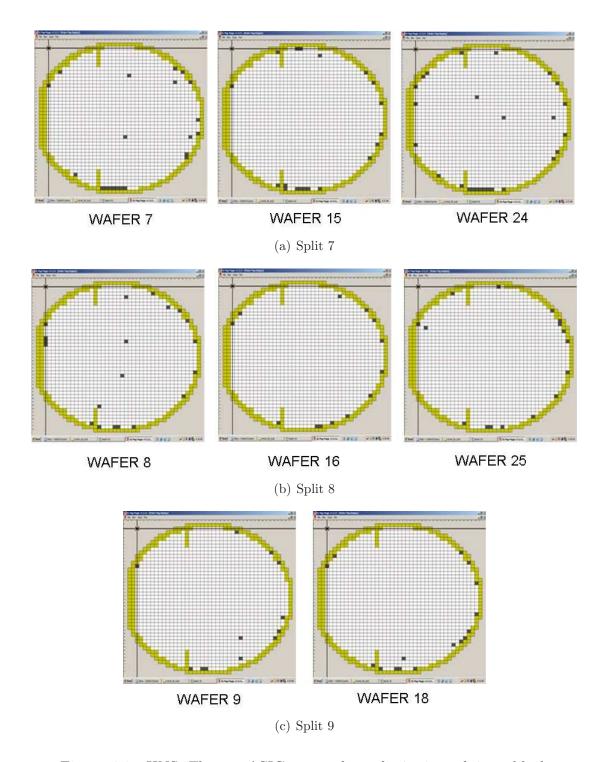

| 6.3  | HNS Thames ASIC corner lot split 7, 8 and 9                                                   |

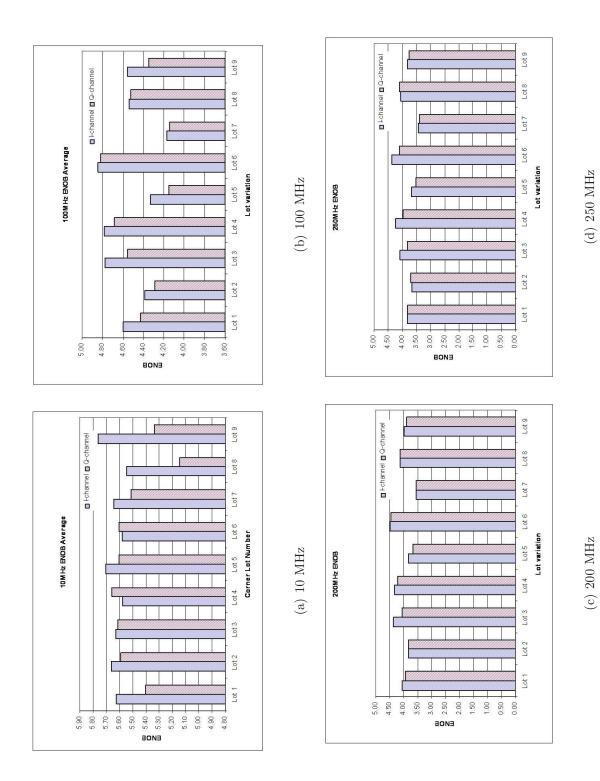

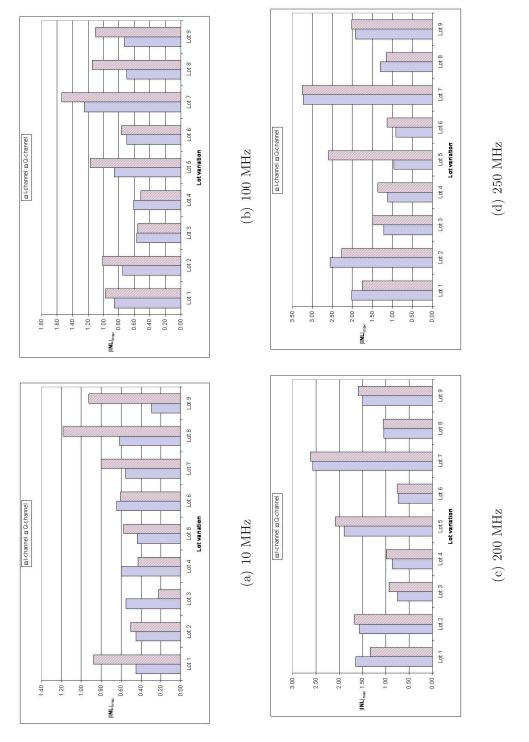

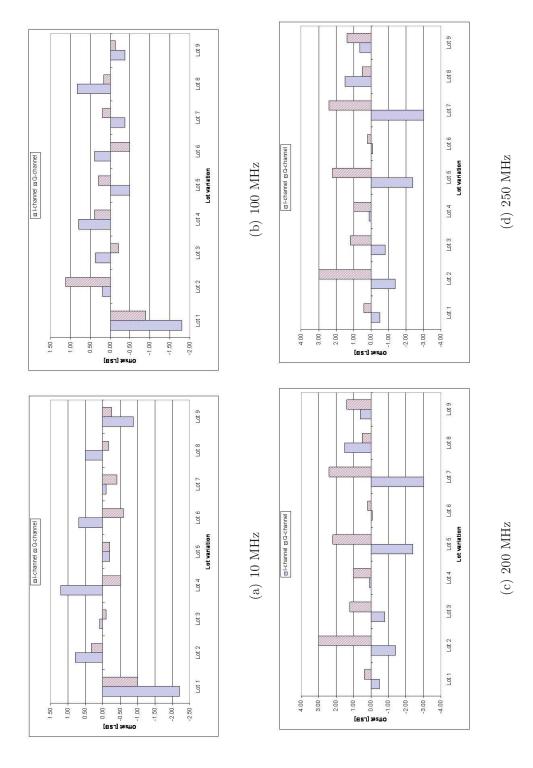

| 6.4  | HNS <i>Thames</i> ASIC ADC ENOB for each corner lot split 232                                 |

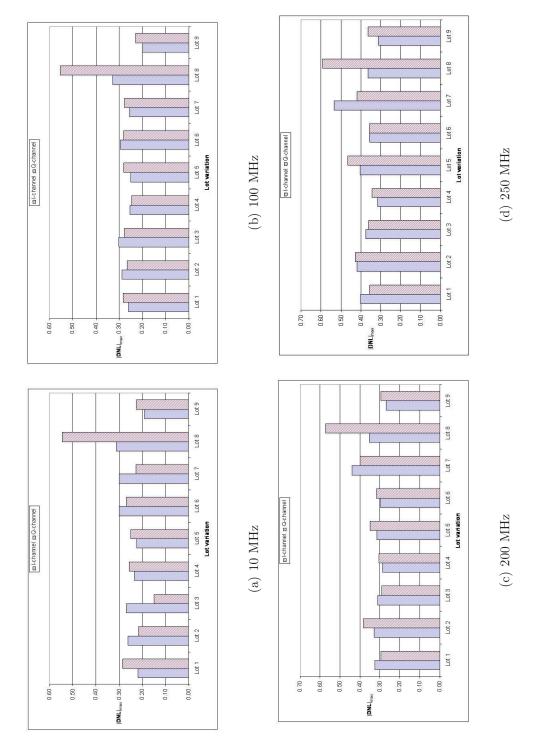

| 6.5  | HNS Thames ASIC ADC DNL for each corner lot split                                             |

| 6.6  | HNS Thames ASIC ADC INL for each corner lot split                                             |

| 6.7  | HNS Thames ASIC ADC offset voltage for each corner lot split 235                              |

| A.1  | VLSI Process Phase                                                                            |

| A.2  | Example of planning and design phase high level design functional block: high-speed ADC       |

## List of Abbreviations

ADC

Analog-to-digital converter

AGC Automatic Gain Controller ASIC Application Specific Integrated Circuit ATE Automated Test Equipment **AWG** Arbitrary Waveform Generator BJTBipolar Junction Transistor BER Bit Error Rate **BIST** Built-in Self Test BPF Bandpass Filter CDMCharge Distribution Model CEConcurrent Engineering CLKClock CMLCurrent Mode Logic COTS Commercial Off The Shelf CWContinuous Wave DAC Digital-to-analog converter dBmdB refereed 1 milli-Watt (mW) dBFS dB referred full-scale (0 dBFS is assigned to the maximum possible level) DETS Defect and Enhancement Tracking Systems DFT Discrete Fourier Transform DfT Design-for-Test DIB Device Interface Board

DIV Divider

DLA Digital Logic Analyzer

DNL Differential Non-linearity

DRC Design Rule Checking

DSP Digital signal processing

DSO Digital Storage Oscilloscope

DUT Device Under Test

DVT Design Verification Test

ECN Engineering Change Notice

ENOB Effective Number of Bits

EOC End-of-conversion

EOS Electrical Over Stress

ERB Effective resolution bandwidth

ESD Electrostatic Discharge

EVM Error vector magnitude

FFT Fast Fourier Transform

FSO Final-sign-off

GND Ground

GS/s Giga-samples per second

GUI Graphical User Interface

HBM Human Body Model

HBT Hetero Junction Transistor

HD Harmonic Distortion

HVT Hardware Verification Test

HLD High level design or discription

HNS Hughes Network Systems, LLC

IEC International Electro-technical Commission

IEEE Institute of Electrical and Electronic Engineers

INL Integral Non-linearity

IMD Intermodulation distortion

IP3  $3^{rd}$  order Intercept point

ISO International Organization for Standardization

JEDEC Joint Electronic Device Engineering Council

LAB Laboratory

LAN Local Area Network

LFPM Linear Feet per Minute

LLD Low level design or description

LPF Lowpass filter

LSB Least significant bit

LVDS Low Voltage Differential Signals LVS Layout versus schematic check

MSB Most significant bit

MS/s Mega-samples per second

PC Personal Computer

PCB Printed Circuit Board

PDF Probability Density Function

PDK Process Design Kit

PDR Preliminary design review

RF Radio frequency

SAR Successive approximation resistor

SiGe Silicon germanium

SINAD Signal-to-noise-and-distortion ratio

SFDR Spurious-free dynamic range

SNR Signal-to-noise ratio

SoC System-on-chip

SPR System problem report

SVT System Verification Test

THD Total harmonic distortion

TQFN Thin Quad Flat Pack

Voffset ADC input offset voltage

VFS Full scale ADC input voltage

VTS Verification Test Software

Chapter 1

Introduction

## 1.1 Overview

This introduction establishes a general philosophy of system verification to serve as a guide for the work presented in the body of the thesis to follow. This is followed by a statement of the unique contributions this thesis makes to the fields of testing and system validation. The introduction concludes with a glossary of the many mysterious and arcane terms used as a jargon in these fields.

# 1.2 General philosophy for the validation of complex integrated systems

A mixed-signal system-on-chip (SoC) device is defined as a group of on-chip integrated subsystems consisting of both digital and analog elements, and their associated components. Generally, validation of complex integrate systems follows basic steps: (1) building prototype - SoC design data produced under the electronic design automation (EDA) or computer aid design (CAD) environment [4, 5]; (2) preparing event based test vectors based on the SoC design data produced in the EDA environment; (3) applying the event based test vectors derived from the SoC design data to the prototype silicon by an event based test system; and (4) evaluating the response output of the prototype silicon; and (5) modifying the event based test vectors to acquire desired response outputs from the silicon prototype; and (6) applying the modified event based test vectors to the EDA environment to modify the design data, thereby correcting design errors in the SoC design. Developing SoC devices or products requires numerous collaborations among design engineers, test engineers, product engineers, and system engineers. To have a fully characterized product for customers or for system applications, system engineers must define and document customer requirements so that the rest of the engineering team can design the product and successfully release their design to production. After the system engineers define the product technical requirements, the design engineers develop the corresponding integrated circuits according to the specified needs.

Test engineers generate hardware and software that will be used to guarantee the performance of each SoC product after fabrication. That is, they assess the safe-operating areas (SOAs) of chip bias and input range. They must also develop the hardware and software approaches necessary to adjust parameters like DC offset and AC gain, or to compensate for manufacturing defects, etc. They are also responsible for reducing the cost of the testing by test time reductions and cost-saving measurements.

We must be careful to state that testing is important from start to finish in the manufacturing of integrated circuits (ICs). First, test consideration is required early in the SoC design cycle. In the low frequency and static regimes of operation, "standard" sub-system parameter evaluations (such as voltage and current off-sets) must be characterized by testing in the design phase. System-specific information, such as linearity, for example, is also necessary for ADCs.

Second, we must provide quick, straight-forward methods for evaluating the functionality of large numbers of parts in the production phase of system development. One of the major problems encountered here is the large number of probes required at wafer-level test. This issue is addressed with the use of on-chip "RF reporting circuits." It must be noted that the testing of packaged chips is also a problem in volume production facilities. Characterizations and modeling of the packaged chips must be carefully conducted in order to reduce down parasitic due to the packages and on-board level systems in the test-vehicles. This thesis does

not address wafer-level probe testing for production in detail. Instead, the thesis concentrates on evaluating packaged chip testing both in the initial design release and production environments.

Nowadays, automated test equipment (ATE) is available from various commercial vendors, such as Teradyne, LTX, Agilent Technologies, and Schlumberger, etc. Common high-end ATE testers usually consist of three major components: a test head, a workstation, and the mainframe tester for production test [6, 7]. Basically, a workstation is the interface between a tester and the user. Test engineers build test programs and debug the programs. The mainframe consists of power supplies, measurement instruments and control computers for these components. Usually, the test head contains the most sensitive measurement electronics. A device interface board (DIB) can be included in the test head and plays an interface role between the ATE tester and the device under test (DUT). Successful SoC diagnosis and characterization depends on the design of electromechanical fixtures and on our ability to eliminate parasitics (such as stray inductance, and capacitance) introduced by the test apparatus.

There are differences between digital testing and mixed-signal testing [6]. Digital circuits can be tested as stand-alone units, but mixed-signal circuits are normally evaluated for their performance in system-level applications. For example, digital circuits such as AND gates, NAND gates, flip-flops, and counters can be tested by their logic levels and digital output. As a comparison, a particular mixed-signal sub-

circuit can be tested with a totally different suite of tests depending on its intended functionality in the system-level application. This thesis explains the detailed test and characterization procedures for full evaluation of a high-speed ADC and a novel compressing ADC as examples of mixed-signal SoCs. The author concentrates on the characterization of high speed data converters for telecommunication applications.

## 1.3 Motivation and objective

Mixed-signal integrated circuit test requirements have grown in complexity due to the expansion of the telecommunications, image-processing industries. Mixed-signal circuits, such as analog-to-digital converters (ADCs), are generally required in many advanced systems. In telecommunications (especially in modern satellite and digital radio receivers such used in ultra-wide-band (UWB) telecommunications) ADCs are used to sample the analog signals and to transfer them to the digital registers for base-band applications in high speed and high-resolution systems. There is much research in design prospects. However, testing high-speed ADCs is still a relatively unknown field compared with high-speed ADC design itself.

While the subjects of digital integrated circuit testing and testability have been covered in many books and references [8, 9, 10, 11], it is difficult, in practice, to find the best testing methods for analog and mixed-signal test and measurement. Testing SoCs for high frequency and wider bandwidth applications is normally a

lengthy, elaborate task. This is mainly because of the limitation of reference signal sources or the difficulty of creating testable circuit or system designs. For example, characterizing and testing ADCs require measurement of a large number of parameters to fully specify the performance of the system. The presence of both analog and digital signals often makes the test and characterization more difficult and challenging.

In addition, test equipment complexity and the breadth of expertise of the test engineer create hidden obstacles to characterizing and testing Mixed-signal SoCs. Demanding custom designed measurement systems are necessary for characterizing ADCs as mixed signal SoCs. It is challenging to come up with a complete characterization system for mixed-signal SoCs such as high speed data converters in modern satellite receiver applications. The performance of characterization equipment is frequently insufficient for the test at hand and the available tool base may differ from test site to test site. In this work, the characterizations and testing techniques are developed in response to limitations on test equipment for a high speed and wide bandwidth ADC and a compressing ADC.

Demystifying testing and characterization techniques for a high speed, broad bandwidth ADCs is the main goal of this thesis, as is merging standard analog and digital test techniques with "design-for-test" (DfT) methodology throughout the life of the ADC development. The thesis also intends to bridge Radio Frequency (RF) and microwave circuit design and test and measurement techniques to validate and

characterize high-speed ADC designs.

It is a primal target to provide a test stand capable of evaluating high-speed ADC systems in a modern satellite receiver. The work is intended to show the step-by-step approach to high-speed ADC design verification and production tests to help many of ADC design engineer in both industry and academia.

## Objective:

To develop full production-ready cost effective design verification test methodology for the high-speed ADC used in modern satellite receivers, the following lists are summarizing what this research provides and accomplishes:

- Case study for a high-speed ADC:

- Design-for-Test (DfT) enhanced approach

- Testability

- Demystify high-speed ADC operation

- Develop concurrent engineering design verification test (DVT) procedures

- Provide a DVT program development (test flow or test plan) to serve as a basis for a verification test suite (VTS)

- Provide Cost-effective ATE solutions

#### 1.4 Outline of thesis

Our main mixed-signal SoC test examples are linear/compressing ADCs (4-bit low-speed compressing ADCs and 8-bit high-speed linear ADCs). In this thesis, we focus on the required test parameter sets for modern satellite receiver applications.

In Chapter 1, general philosophy for validation of complex integrated circuits is introduced with research motivations and objectives to develop high-speed ADC design verification test techniques. Glossary terms for ADCs are also included.

Chapter 2 describes an overview of ADCs and ADC validation test requirements and prerequisite criteria to perform robust and cost-effective design verification tests from the prototype to the full production level testing. Successful product developments are based on concurrent engineering.

Chapter 3 presents the Design-for-Test(DfT) philosophy of high-speed ADC characterization in a modern satellite receiver. A general overview of testing ADC architectures and their operating principles are presented before the verification tests are detailed. Mixed signal circuits to be tested for telecommunication system applications are described.

Chapter 4 addresses the fixture and test bench setup requirements needed to characterize ADC performance. The high-speed ADC verification fixture design and subsystem periphery development are described with cost-effective interface between the ADC and the test equipment. In a high speed ADC prototype design environment, a robust test methodology and the selection of an adequate test fixture and

subsystem are significant parts of the ADC design process enabling mass production.

Chapter 4 shows the test setup and test fixture designs to overcome the limitation for test equipment.

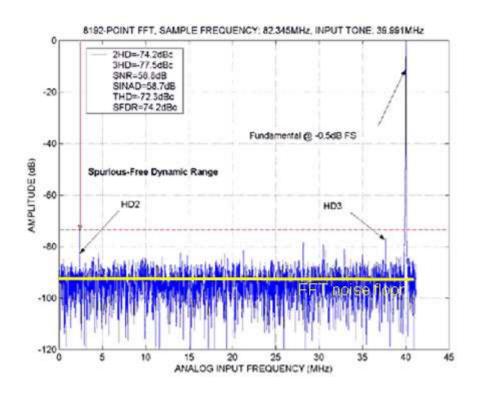

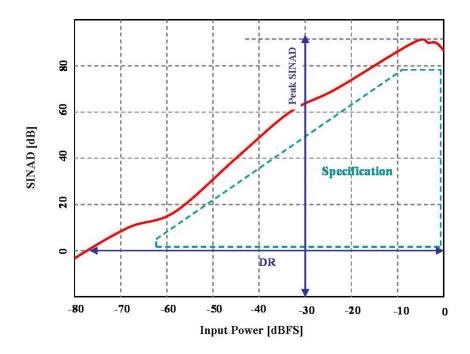

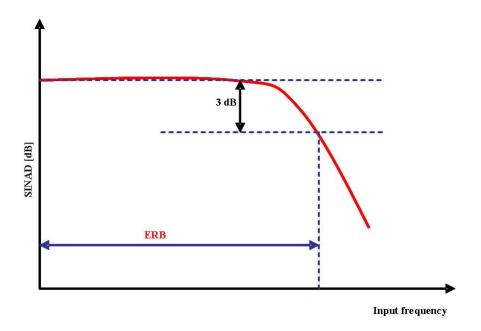

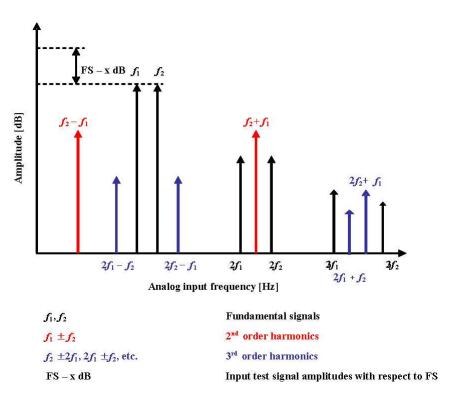

In Chapter 5, Design verification software development and detail test methodologies for high-speed ADCs are discussed. The ADC verification analysis software development is presented along with the test methodology. Testing limitations and difficulties are described. Developed a computer-aided ADC device verification software (VTS) tool consists of four major parts: sine wave power spectrum tests, linearity tests, error code tests and two-tone intermodulation (IMD) tests. The linearity test is described with a sine wave histogram test techniques to provide both the differential nonlinearity (DNL) and the integral nonlinearity (INL). A Fast Fourier transform (FFT) module, which is a workhorse of the sine wave power spectrum tests and the two-tone IMD tests, yields several critical ADC specifications, including the effective resolution bandwidth (ERB), analog power versus spurious free dynamic range (SFDR), effective number of bits (ENOB), and intermodulation destortion (IMD).

In this thesis, a common test setup configuration is used for the entire device verification test (DVT) process and a sine wave is primarily used as the analog input signal due to its easiness of generation and analysis. The advantages of using DSP routines for data analysis are mentioned. The detailed sequence of testing operations necessary for verification testing of high speed ADCs in modern communication systems. These results pave the way for future developments in the field of automated high speed ADC verification methodology. Various aspects such as hardware settings, testing programs, noise and jittering issues are discussed for high speed analog and mixed-signal SoC device testing. Tests and characterizing procedures for dynamic performance of a high speed ADC are proposed and bench test limitations and challenging factors are also discussed.

As ADC characterization routine, both static and dynamic test procedures are described so that ADC systems can be characterized. Both compressing and linear ADC's static and dynamic characterization procedures are described and the test results are shown each.

The production test of the fabricated high-speed ADC is also described in the end of Chapter 5. Test results are summarized as they apply to volume part fabrication. Necessity of system level test and wafer level test vehicle structures are also briefly addressed.

Chapter 6 shows that the sensitivity analysis of the designed high-speed ADC. Dynamic performances of high-speed (800 MS/s) dual channel 6-bit analog-to-digital converters (ADCs) were investigated and reported on the corner lot process variations to determine the impact of process variations. The ADCs sensitivity analysis results to critical process parameter variations provide ADC design limits.

Chapter 7 concludes the work on design verification test for the high-speed analog-to-digital converters in modern satellite receivers. The chapter summarizes

the research works and their achievements and contributions from the developed design verification test methodology and the test program. Future works are also addressed, so that further research can be extended based on the thesis.

#### 1.5 Contributions

The thesis provides a generalized optimal high-speed ADC testing methodology in detail. The methodology is suitable for duplicating the test method and the results for testing reproducibility. Improved test methodology in dynamic performance of ADCs for satellite communications is employed with the device verification test software, VTS suite. The methodology is also developed so that less experienced personnel could perform the rigorous testing needed for proficient verification. Design-for-Test (DfT) concept are applied to succeed in the high-speed ADC design verification tests (DVTs) as a part of process from the design phase to the full productions.

The VTS suite developed in this dissertation has been delivered to Hughes Network Systems [12] and now is in wide spread use to validate their custom ADC ASIC and ADC system development project such as the *Thames* ASIC projects (dual channel 800 MSamples/sec 6-bit ADC ASIC projects).

The corner lot study of *Thames* ASIC projects is also reported for the first time to show the effects of ADC dynamic parameters due to the process variations.

## 1.6 Glossary of terms

The glossary provides a detailed description of AC dynamic performance terms related to high-speed ADCs and their ASIC. It also gives some insight into the test conditions these parameters are specified for.

- ADC Analog-to-Digital Converters, a device or circuit used to convert analog information to digital words.

- Aliasing/Anti-aliasing Conversion of an input frequency to another frequency as a result of the conversion processes. The output frequency of an ADC can not exceed a half of the sampling frequency of the ADC without aliasing. When the input frequency does exceed 1/2 the sampling frequency (Nyquist limit), the signal is folded back (aliasing) or replicated at other frequencies in the frequency spectrum above and below Nyquist (see also Nyquist Frequency). Caused by unwanted signal components above Nyquist, aliasing can be avoided by introducing front-end anti-aliasing filters to attenuate those signals.

- Aperture Delay Aperture delay is the time defined between the rising edge (50% point) of the sampling clock and the instant when an actual sample is taken.

- Aperture Jitter Aperture jitter is the sample-to-sample variation in the time between sampling events.

- Aperture Width Aperture width is the time that a track/hold (T/H) circuit requires to disconnect the hold capacitor from the input circuit (for example, to

turn off the sampling and put the T/H amplifier in hold mode).

- Characteristic Impedance The impedance a transmission line such that, when driven by a circuit with that output impedance, the line appears to be of infinite length such that it will have no standing waves, no reflections from the end and a constant ratio of voltage to current at a given frequency at every point on the line.

- Corner Lots Wafer fabrication where the process is deliberately skewed to produce either fast, or slow wafers so that ASIC performance can be physically evaluated at process extremes.

- DNL Differential Non-Linearity. The measure of the maximum deviation from the ideal step size of 1.00 LSB.

- ENOB Effective Number Of Bits. A specification that helps to quantify dynamic performance. ENOB says that the converter performs as if it were a theoretically perfect converter with a resolution of ENOB. That is, an ENOB of 5.4 says that the converter performs, as far as SINAD is concerned, as if it were a perfectly ideal ADC with a resolution of 5.4 bits (assuming you could have fractional bits). The idea behind ENOB comes from the fact that the absolutely perfect ADC has an SNR that comes only from quantization noise and has absolutely no distortion. When this is the case, SINAD is then equal to SNR. Since SNR of the absolutely perfect ADC is SNR =  $6.02 \times n + 1.76$ ,

where "n" is the number of ADC output data bits, SINAD = SNR for a perfect converter, so SINAD =  $6.02 \times n + 1.76$  and  $n = (SINAD \times 1.76)/6.02$  and we say that ENOB =  $(SINAD \times 1.76)/6.02$ .

- ERB Effective-Resolution-Bandwidth. The ERB is the input frequency point where the SINAD has dropped 3dB (or ENOB 1/2 bit). The signal bandwidth is an important parameter for the ADCs. The ADC bandwidth is limited by the analog bandwidth of the input circuits and the sampling frequency of the ADC.

- FFT Fast Fourier Transform. The FFT is a mathematical operation that converts signals between the time and frequency domains. We generally call the frequency domain (amplitude vs.. frequency) plot an FFT.

- Full-Scale Input Swing The difference between the maximum and minimum input voltages that will produce a valid ADC output without going over- or underrange.

- Gain Error The error in the slope of the ADC transfer characteristic. It is the difference in the actual and ideal full scale input range values.

- IMD Intermodulation Distortion. This is the creation of new spectral components that result from two or more input frequencies modulating each other when the circuit is nonlinear.

- INL Integral Non-Linearity. The maximum departure of the ADC transfer curve from the ideal transfer curve. INL is a measure of how straight is the transfer function curve. There are two popular methods of measuring INL: End Point and Best Fit. The End-Point method is the most conservative, while the Best Fit method gives lower (better-looking) values. National uses the End Point method.

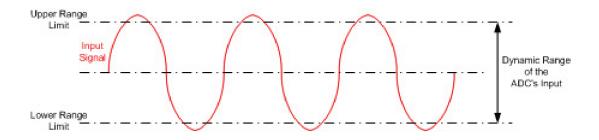

- Input Dynamic Range For an ADC, the range of voltages that can be applied to the input without going under or over range.

- Input Offset The difference between the input value of 1.0 LSB and the input voltage that causes the ADC output code to transition from zero to the first code.

- Input Offset Error The difference between the ideal input value of 0.5 LSB and the input voltage that causes the ADC output code to transition from zero to the first code.

- IP3 3<sup>rd</sup> order intercept point. It is a measure for weakly nonlinear systems and devices, for example receivers, linear amplifiers and mixers. It is based on the idea that the device nonlinearity can be modeled using a low order polynomial, derived by means of Taylor series expansion. The third-order intercept point relates nonlinear products caused by the 3rd order term in the nonlinearity to the linearly amplified signal. The intercept point is a purely mathematical

concept, and does not correspond to a practically occurring physical power level. In many cases, it lies beyond the damage threshold of the device.

LSB - Least Significant Bit. The bit that has the least weight.

Nyquist Rate - The minimum sampling rate (or frequency) needed to prevent frequency aliasing.

Nyquist Frequency - The maximum input frequency beyond which frequency aliasing results.

Offset Error - This is the same as Input Offset Error.

PCB - Printed Circuit Board.

Quantization - The process of dividing a range of analog voltages or currents into smaller range of voltages or currents such that each value is represented by a single digital code.

Quantization Error - The error introduced as a result of the quantization process. The amount of this error is a function of the resolution of the quantizer. By definition, the quantization error of an ADC is 1/2 LSB. Quantization Noise . The noise at the ADC output that is caused by the quantization process. It is defined as  $20*\log(2(n-1)\times\sqrt(6))$ , or about  $6.02\times n+1.76$  dB, where "n" is the number of output bits of the ADC. Quantizer . A circuit that carries out the quantization process. Another name for an Analog-to-Digital Converter.

Reference Voltage . For an ADC, the reference voltage is the voltage against which the analog input or an ADC is compared to determine the ADC output code.

- Resolution A measure of how well the ADC input is resolved, or how well the value of an LSB represents the analog input. Resolution is usually expressed in bits, and then indicates the number of bits available in the ADC output word. The number of discrete output states or values of an ADC can be expressed in the number of digital bits in the output.

- Sampling Noise The inherent noise of an ADC that comes from the steps in the transfer function.

- SFDR Spurious-Free Dynamic Range. A term used to specify ADCs and SFDR is the ratio of the rms amplitude of the carrier frequency (maximum signal component) to the rms value of the next largest noise or harmonic distortion component. SFDR is usually measured in dBc (with respect to the carrier frequency amplitude) or in dBFS (with respect to the ADC's full-scale range).

- SINAD Signal-to-Noise And Distortion ratio. A combination of the SNR and THD specifications, SINAD is defined as the rms value of the fundamental signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c. SINAD can be calculated from SNR and THD. Because it compares all undesired frequency compo-

nents at the output with desired frequency. It is an overall measure of the dynamic performance of the ADC. SINAD is also known as SNDR, S/(N+D) and Signal-to-Noise Plus Distortion. SNR . Signal-to-Noise Ratio. The ratio of the power in the signal to the power in all other spectral components below 1/2 the sampling frequency, excluding harmonics and d.c.

- Spurious Spurious in a spectrum defines as lacking authenticity or validity in essence or origin signal frequency component; not genuine signal or false signal including noise, and harmonics.

- THD Total Harmonic Distortion. The ratio of the rms total of a specified number of harmonic components to the rms value of the output signal. This thesis uses the first nine harmonics ( $f_2$  through  $f_{10}$ ).

- Undersampling Undersampling occurs when the sampling rate of an ADC is much lower ( $f_{\text{SAMPLE}} < 2 \times f_{\text{IN}}$ ) than the applied input frequency, usually resulting in a loss of signal information, thereby causing aliasing (see also Aliasing/Anti-Aliasing). With proper filtering and an adequate input tone and clock frequency selection, the aliased components that contain the signal information can be shifted from a higher-frequency band to a lower-frequency band and converted.

Chapter 2

# An Overview of ADCs and ADC Test

## Procedures

#### 2.1 Overview

An Analog-to-Digital Converter (ADC) is a device or circuit used to convert analog information to digital words. This chapter describes a number of ADC architectures commonly employed in high-performance modern telecommunication systems.

This chapter explores general ADC architectures to study design verification test requirements and prerequisite criteria to perform robust and cost-effective design verification tests from the initial design release phase prototype testing to the full production level testing. Successful product developments are based on concurrent engineering and the chapter guides how concurrently approach the final

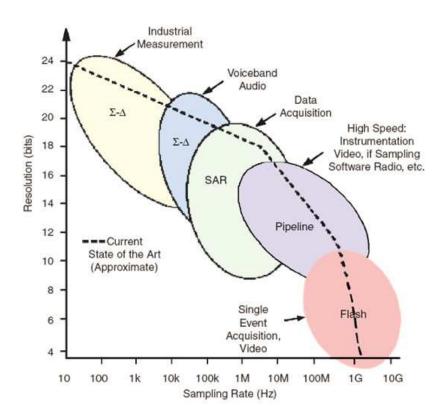

Figure 2.1: ADC architectures, applications, resolution and sampling rates [13] productions.

## 2.2 ADC architectures

There are many ADC architectures commonly employed in high-performance modern electronic systems [14, 15, 16, 17, 18]. Deciding on the correct ADC requires tradeoffs between resolution, channel count, power consumption, size, conversion time, static performance, dynamic performance, and price [19]. System designers or test engineers need to know the key features, and have a basic understanding of the

architectures and their design limitations.

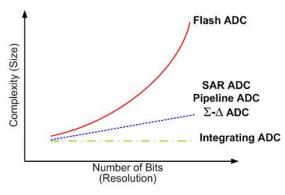

The classification in Figure 2.1 shows, in a general way, how these application segments and the associated typical architectures relate to ADC resolution and sampling rate. The dashed lines represent the approximate state of the art in mid-2005 [20].

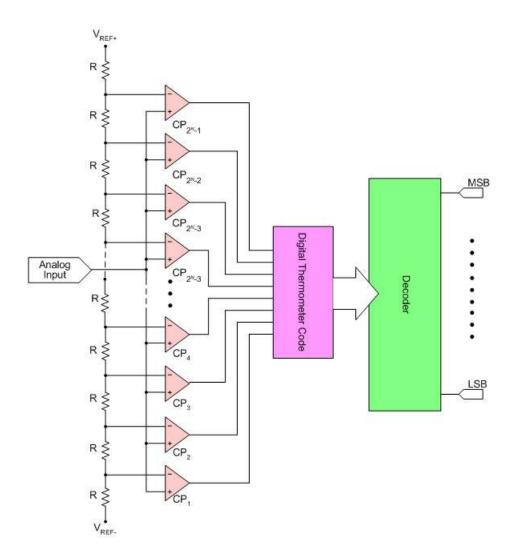

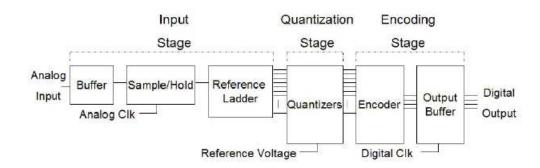

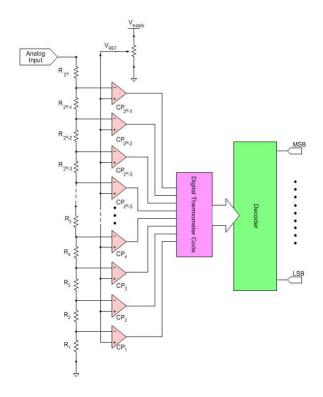

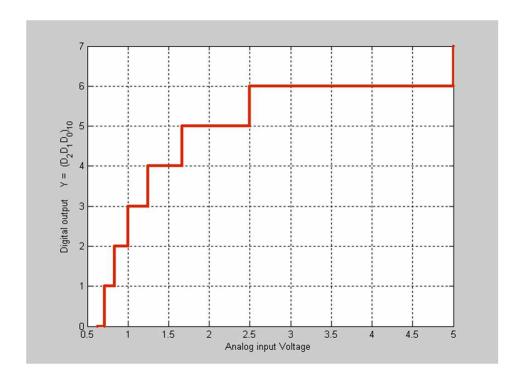

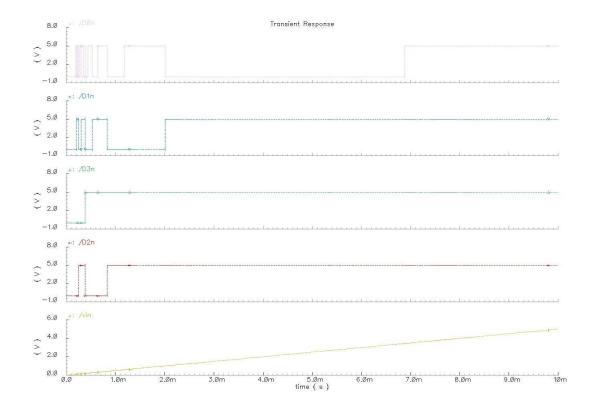

#### 2.2.1 Flash ADC

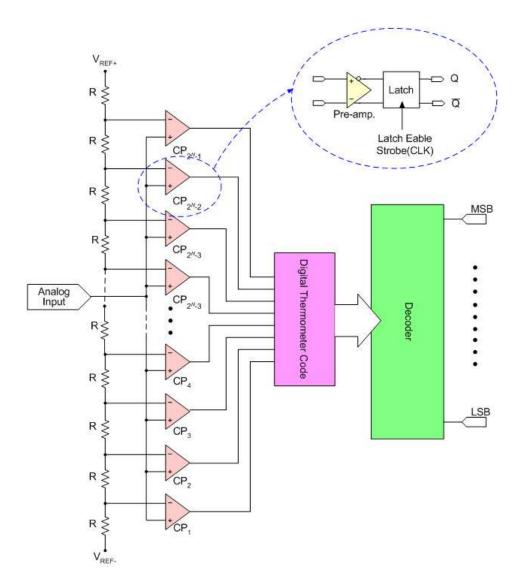

Flash analog-to-digital converters, also known as parallel ADCs, are the fastest way to convert an analog signal to a digital signal. Typical flash ADC is shown in Figure 2.2. They use large numbers of comparators. An N-bit flash ADC consist of  $2^N$  resistor and  $2^N$ -1 comparators. Each comparator has a reference voltage from the resistor ladder string which is 1-LSB step apart between resistors. The outputs from  $2^N$ -1 comparators are a thermometer code and then processed to N-bit binary output by a decoder logic.

Flash ADCs are suitable for applications requiring very large bandwidths. However, flash converters consume a lot of power, have relatively low resolution, and can be quite expensive. This limits them to high frequency applications that typically cannot be addressed any other way. Examples include data acquisition, satellite communication, radar processing, sampling oscilloscopes, and high-density disk drives [20].

The input to a flash ADC is applied to a large number of comparators, which

Figure 2.2: Typical flash ADC Architecture

Figure 2.3: Interpolation scheme in a flash  ${\it ADC}$

have an voltage variable input capacitance, each. Those capacitances are signal-dependent and result in degrading effective-number-of-bits (ENOB) of the converter [16, 20]. They can add distortion for high frequency analog input. A wide bandwidth, low-distortion comparator designs are challenging in a flash ADC design for high frequency operations.

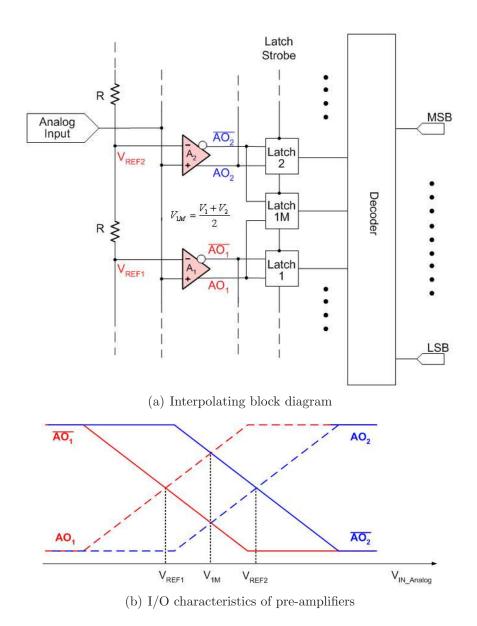

To minimize the number of comparators in typical flash ADCs, an interpolation scheme can be applied [21, 19] as shown in Figure 2.3. In contrast with a simple flash ADC, the interpolating flash ADC scheme halves the number of preamplifiers but maintains the same number of latches. The preamplifier A1 and A2 compare the analog input with the node references,  $V_{REF_1}$  and  $V_{REF_2}$ , respectively. Voltage input/output characteristics of the preamplifiers are shown in Figure 2.3(b). Assuming zero offset for both preamplifiers, we can find that  $V_{\overline{AO_1}} = V_{AO_1}$  when  $V_{IN} = V_{REF_1}$ , and  $V_{\overline{AO_2}} = V_{AO_2}$  when  $V_{IN} = V_{REF_2}$ . If  $V_{AO_2} = V_{\overline{AO_1}}$ , then we can find that  $V_{IN} = V_{IM} = (V_{REF_1} + V_{REF_2})/2$ .

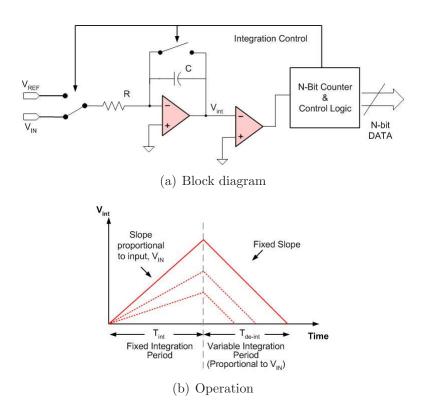

## 2.2.2 Integrating ADC

Integrating analog-to-digital converters (ADCs) provide high resolution analog-to-digital conversions, with good noise rejection [18]. These ADCs are ideal for digitizing low bandwidth signals, and are used in applications such as digital multi-meters and panel meters. They often include LCD or LED drivers and can be used stand alone without a microcontroller host [22].

Figure 2.4: Single-slope ADC Architecture

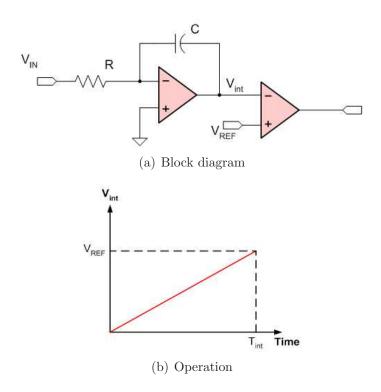

#### A. Single-slope ADC:

A single-slope ADC in Figure 2.4 is the simplest architecture of an integrating ADC. Here, an unknown input voltage ( $V_{IN}$ ) is integrated and the value compared against a known reference value ( $V_{REF}$ ). The time it takes for the integrator to trip the comparator is proportional to the unknown voltage ( $T_{int}/V_{IN}$ ). In this case, the known reference voltage must be stable and accurate to guarantee the accuracy of the measurement.

One drawback to this approach is that the accuracy is also dependent on the tolerances of the integrator's R and C values. Thus, slight differences in each component's value change the conversion result and make measurement repeatability quite difficult to attain in a production environment. To overcome this sensitivity to the component values, the dual-slope integrating architecture is used.

#### B. Dual-slope ADC:

A dual-slope ADC architecture is shown in Figure 2.5. The operation is following: the integrator integrates an unknown input voltage  $(V_{\rm IN})$  for a fixed amount of time  $(T_{\rm int})$ , then "de-integrates" using a known reference voltage  $(V_{\rm REF})$  for a variable amount of time  $(T_{\rm de-int})$ . The operation meets the following condition [20, 13]:

$$T_{\text{de-int}} = T_{\text{int}} \times \frac{V_{\text{IN}}}{V_{\text{REF}}}.$$

(2.1)

The key advantage of this architecture over the single-slope is that the final conversion result is insensitive to errors in the component values. That is, any error introduced by a component value during the integrate cycle will be canceled out during the de-integrate phase [20].

This tradeoff between conversion time and resolution is inherent in this implementation. It is possible to speed up the conversion time for a given resolution with moderate circuit changes. Unfortunately, all improvements shift some of the accuracy to matching, external components, charge injection, etc. In other words, all speed-up techniques have larger error budgets [19].

Even in the single-slope ADC converter in Figure 2.4, there are many potential error sources to consider such as power-supply rejection (PSR), common-mode rejection (CMR), finite gain, over-voltage concerns, integrator saturation, compara-

Figure 2.5: Typical dual-slope ADC Architecture

tor speed, comparator oscillation, capacitor leakage current, parasitic capacitance, charge injection, etc.

Single, dual and multi-slope ADCs can achieve high resolutions (16-bits or more) and are relatively inexpensive and dissipate materially less power versus flash ADCs. These devices support very low conversion rates, typically less than a few hundred samples per second. Most applications are for monitoring DC signals in the instrumentation and industrial markets.

Figure 2.6: A pipeline ADC block diagram [20]

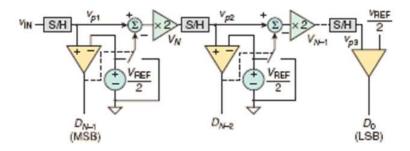

## 2.2.3 Pipelined ADC

The pipelined analog-to-digital converter (ADC) has become the most popular ADC architecture for sampling rates from a few megasamples per second (MS/s) up to 100MS/s or more, with resolutions from 8 to 16 bits [20]. They offer the resolution and sampling rate to cover a wide range of applications, including charge-coupled device (CCD) imaging, ultrasonic medical imaging, digital receiver, base station, digital video (for example, HDTV), xDSL, cable modem, and fast Ethernet.

A pipelined ADC employs a parallel structure in which each stage works on one to a few bits (of successive samples) concurrently as shown in Figure 2.6. The inherent parallelism increases throughput, but at the expense of power consumption and latency. Latency in this case is defined as the difference between the time an analog sample is acquired by the ADC and the time when the digital data is available at the output. For instance, a five-stage pipelined ADC will have at least five clock cycles of latency. In a pipeline converter, a B-bit converter requires only

B comparators, and the output of each comparator is a bit in the final converter output (i.e., no thermometer code) [20].

A pipelined ADC requires accurate amplification in the DACs and interstage amplifiers, and these stages have to settle to the desired linearity level. By contrast, in a flash ADC, the comparator only needs to be low offset and be able to resolve its inputs to a digital level (i.e., there is no linear settling time involved). However, some flash converters require pre-amplifers to drive the comparators. Gain linearity needs to be carefully specified.

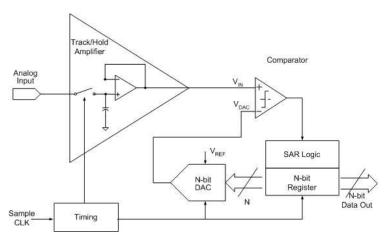

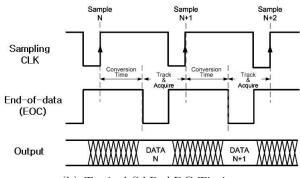

## 2.2.4 Successive-approximation-resister(SAR) ADC

SAR ADCs are frequently the architecture of choice for medium-to-high-resolution applications, typically with sample rates fewer than 5 megasamples per second (Msps). SAR ADCs most commonly range in resolution from 8 to 16 bits and provide low power consumption as well as a small form factor. This combination makes them ideal for a wide variety of applications, such as portable/battery-powered instruments, pen digitizers, industrial controls, and data/signal acquisition [20].

The basic architecture in a SAR ADC is shown in Figure 2.7(a) [16, 19] and the comparator and the N-bit DAC are two critical components in this architecture. The analog input voltage  $(V_{IN})$  is held on a track/hold. To implement the binary search algorithm, the N-bit register is first set to mid-scale (for, 100... .00<sub>2</sub>, where the MSB is set to '1'). This forces the DAC output  $(V_{DAC})$  to be  $V_{REF}/2$ , where

(a) SAR basic building block diagram

(b) Typical SAR ADC Timing

Figure 2.7: Successive-approximation-resister (SAR) ADC

$V_{REF}$  is the reference voltage provided to the ADC. A comparison is then performed to determine if  $V_{DAC}$  is less than or greater than  $V_{DAC}$ . If  $V_{IN}$  is greater than  $V_{DAC}$ , the comparator output is a logic high (or '1') and the MSB of the N-bit register remains at'1'. Conversely, if  $V_{IN}$  is less than  $V_{DAC}$ , the comparator output is a logic low (or '0') and the MSB of the register is cleared to logic '0'. The SAR control logic then moves to the next bit down, forces that bit high, and does another comparison. The sequence continues all the way down to the LSB. Once this is done, the conversion is complete, and the N-bit digital word is available in the register. The fundamental timing diagram is shown in Figure 2.7(b). The end of conversion is generally indicated by an end-of-conversion (EOC).

In a SAR converter, the bits are decided by a single high-speed, high-accuracy comparator one bit at a time (from the MSB down to the LSB), by comparing the analog input with a DAC whose output is updated by previously decided bits and thus successively approximates the analog input [14]. This serial nature of the SAR limits its speed to no more than a few Msps, while flash ADCs exceed giga-sample per second (GS/s) conversion rates.

## 2.2.5 Sigma Delta $(\Sigma - \Delta)$ ADC

$\Sigma$ - $\Delta$  ADCs are used predominately in lower speed applications requiring a trade off of speed for resolution by oversampling, followed by filtering to reduce noise. 24-bit Sigma Delta converters are common in Audio designs, instrumentation and Sonar.

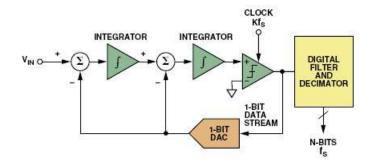

Figure 2.8: Second order Sigma-delta  $(\Sigma - \Delta)$  ADC [20]

Bandwidths are typically less than 1MHz with a range of 12 to 18 bits [13, 23]. A 2nd-order  $\Sigma$ - $\Delta$  ADC basic building block is shown in Figure 2.8. These converters are capable of the highest resolution possible in ADCs. They require simpler antialias filters (if needed) to bandlimit the signal prior to conversion. They trade speed for resolution by oversampling, followed by filtering to reduce noise. However, these devices are not always efficient for multi-channel applications. This architecture can be implemented by using sampled data filters (also known as modulators) or continuous time filters. For higher frequency conversion rates the continuous time architecture is potentially capable of reaching conversion rates in the hundreds of Msps range with low resolution of 6 to 8-bits. This approach is still in the early research and development stage and offers competition to flash alternatives in the lower conversion rate range [24].

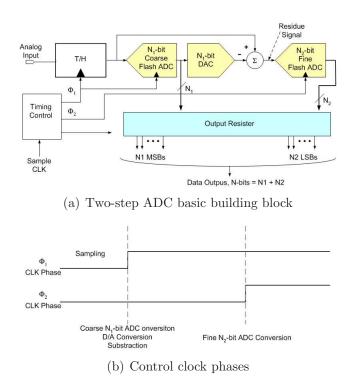

Figure 2.9: Two-step ADC architecture

## 2.2.6 Two-step ADC

Two-step ADCs are also known as subranging converters and sometimes referred to as multi-step or half flash (slower than Flash architecture). This is a cross between a Flash ADC and pipeline ADC. Two-step ADCs can achieve higher resolution or smaller die size and power for a given resolution are needed versus a Flash ADC. This approach combines ideas from successive approximation and flash architectures.

Sub-ranging ADCs reduce the number of bits to be converted into smaller groups, which are then run through a lower resolution flash converter. This approach reduces the number of comparators and reduces the logic complexity, compared to a flash converter [14, 15].

A simplified two-step ADC architecture is shown in Figure 2.9(a). A first conversion is completed with a  $N_1$ -bit converter. A residue is created, where the result of the  $N_1$ -bit conversion is converted back to an analog signal (with an higher resolution  $(2\times N_1$ -bit) accurate DAC) and subtracted from the input signal. This residue is again converted by the  $N_2$ -bit ADC and the results of the first and second pass are combined to provide the N-bit  $(N_1+N_2)$  digital output. As shown in Figure 2.9(b), the coarse ADC and the fine ADC data conversion are controlled by two clock signals,  $\Phi_1$  and  $\Phi_2$ , each by the timing control unit.

### 2.3 ADC architecture tradeoffs

ADCs can be implemented by employing one of architectures in the previous section. ADC's architectural tradeoffs can be addressed in terms of their sampling data conversion time, on-chip device component matching and die size, cost and power [22].

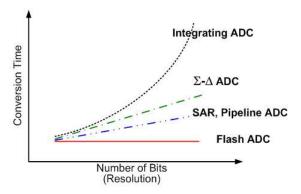

In Figure 2.10(a), the tradeoffs are shown with respect to ADC data conversion time. For flash converters, the conversion time does not change significantly with increased resolution. The conversion time for Successive Approximation Register (SAR) or Pipelined converters increases approximately linearly with an increase in resolution. For integrating ADCs, the conversion time doubles with every bit increase in resolution. The tradeoffs is illustrated in Figure 2.10(a).

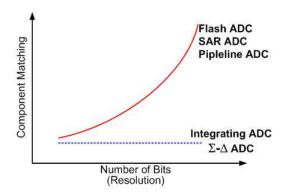

Device matching requirements in on-chip ADC design are shown in Figure 2.10(b).

(a) ADC Conversion time vs. Resolution

(b) Component Matching Vs. Resolution

(c) Complexity Vs. Resolution

Figure 2.10: ADC architecture tradeoffs [19, 22, 20]