## ABSTRACT

| Title of dissertation:    | CMOS N-DIMENSIONAL M-LEVEL<br>HYSTERESIS CIRCUITS<br>AND POSSIBLE APPLICATIONS      |

|---------------------------|-------------------------------------------------------------------------------------|

|                           | Yu Jiang, Doctor of Philosophy, 2007                                                |

| Dissertation directed by: | Professor Robert W. Newcomb<br>Department of Electrical and<br>Computer Engineering |

Hysteresis is a natural phenomenon existing in many systems. Binary hysteresis is the simplest yet important model to study electronically generated hysteresis. Binary hysteresis circuits, the Schmitt trigger being an example, are widely used in reducing noise sensitivity, designing oscillators, generating chaotic signals, etc. A new concept, n-dimensional m-level multi-cell hysteresis is presented. A group of CMOS binary hysteresis circuits with full control which operate in all four quadrants is introduced. CMOS circuits, that give various one-dimensional multi-level hysteresis, in both current mode and voltage mode, are presented. Various combinations of adding forward and reverse binary hysteresis are demonstrated. CMOS circuits, in both current mode and voltage mode, that give two-dimensional multi-level multicell hysteresis, are designed. Further discussion is given on how to extend the results to more dimensions. Two-dimensional hysteresis is used to generate chaotic signals. A couple of areas where multi-cell hysteresis can be useful are suggested.

## CMOS N-DIMENSIONAL M-LEVEL HYSTERESIS CIRCUITS AND POSSIBLE APPLICATIONS

by

## Yu Jiang

## Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2007

Advisory Committee: Professor Robert W. Newcomb, Chair/Advisor Professor James R. Anderson Professor Shuvra S. Bhattacharyya Professor Neil Goldsman Professor Isaak D. Mayergoyz © Copyright by Yu Jiang 2007

# DEDICATION

To my family

## ACKNOWLEDGMENTS

I owe my gratitude to all the people who have made this dissertation possible and because of whom my graduate experience has been one that I will cherish forever.

First and foremost I would like to thank my advisor, Professor Robert W. Newcomb for giving me an invaluable opportunity to work on challenging and extremely interesting projects over the past years. He has always made himself available for help and advice and there has never been an occasion when I have knocked on his door and he has not given me time. It has been a pleasure to work with and learn from such an extraordinary individual.

I would also like to thank my advisory committee: Professor James R. Anderson, Professor Shuvra S. Bhattacharyya, Professor Neil Goldsman, and Professor Isaak D. Mayergoyz for their advise, patience and encouragement.

Thanks to the wonderful staff in the electrical and computer engineering department: Jay Renner, who managed the chip fabrication, Maria Hoo in the graduate office, who handled all my graduate studies forms, Vivian Lu and Olivia Goetz who took care of my financial forms, Dolores Harris and India Tiller in the undergraduate office, who have been always so warm and kind to me. Thanks to Dr. Dan Balón, who used to be the director of graduate academic and student affairs, for always having an open door for the graduate students. Thanks to my greatuncle, Jing Kang, who has always been a mentor for me. Thanks to my parents, Qinxian Kang and Chaomo Jiang, who gave me strength and integrity, and encouraged me pursuing my interests. Thanks to my sister, Peng Jiang, for fulfilling the duty and responsibility for me during difficult times.

Thanks to my long time friend, Zheng Lin, for always believing in me, encouraging me in tough times, and sharing the life experience with me.

Thanks to the many friends I made at the University of Maryland, Song, Ming, Saini, Jianlin, Yin, Xiaohu, Zhihua, Lan, Juan and Xiaobo.

Thanks to my daughter, Felicity, for being such a model baby while I was writing my dissertation.

I owe my deepest thanks to my husband, John Matthews. This dissertation would not be possible without his understanding, patience, and support.

## TABLE OF CONTENTS

| List of                                  | Tables                                                                                                                                                                                                                                                                                                                                                                                                                   | viii                                                                                                                   |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| List of Figures                          |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                        |

| 1 Intro<br>1.1<br>1.2                    | oduction         Multi-Celled Hysteresis         1.1.1       Binary Hysteresis         1.1.2       Multi-Level Hysteresis         1.1.3       Multi-Celled Hysteresis         Contributions of the dissertation                                                                                                                                                                                                          | $     \begin{array}{c}       1 \\       3 \\       5 \\       6 \\       6     \end{array} $                           |

| <ul><li>2 Bina 2.1</li><li>2.2</li></ul> | <ul> <li>2.1.1 CMOS Schmitt Trigger</li></ul>                                                                                                                                                                                                                                                                                                                                                                            | 9<br>11<br>11<br>13<br>15<br>16<br>18<br>18<br>19<br>20                                                                |

| 2.3<br>2.4<br>2.5                        | <ul> <li>2.2.4 Z. Wang's CMOS Two Input Current-Input Voltage-Output<br/>Hysteresis Circuit with Full Control Horizontally</li> <li>2.2.5 Summary</li> <li>2.2.5 Summary</li> <li>2.3.1 Linares-Barronco's CMOS Transconductance Hysteresis Circuit</li> <li>2.3.2 L. Wang's Voltage-Input Current-Output Hysteresis Circuit</li> <li>2.3.3 Summary</li> <li>Current-Input Current-Output Hysteresis Circuits</li> </ul> | <ol> <li>21</li> <li>22</li> <li>23</li> <li>25</li> <li>25</li> <li>28</li> <li>29</li> <li>29</li> <li>31</li> </ol> |

| 3 CM4<br>3.1<br>3.2                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                 | 32<br>32<br>34<br>35<br>40                                                                                             |

|   |      |          | 3.2.2.1   | Schematic and Operation Principle                     | 40  |

|---|------|----------|-----------|-------------------------------------------------------|-----|

|   |      |          | 3.2.2.2   | PSpice Simulations                                    | 42  |

|   |      |          | 3.2.2.3   | CMOS Current-Input Current-Output Reverse Bi-         |     |

|   |      |          |           | nary Hysteresis Circuit                               | 46  |

|   |      | 3.2.3    | Summai    | ry                                                    |     |

|   | 3.3  | CMOS     |           | -Input Voltage-Output Binary Hysteresis Circuits with |     |

|   | 0.0  |          |           | All Four Quadrants                                    | 48  |

|   |      | 3.3.1    |           | tic and Operation Principle                           |     |

|   |      | 3.3.2    |           | Simulations                                           |     |

|   |      | 3.3.3    | -         | Voltage-Input Voltage-Output Forward Binary Hys-      | 50  |

|   |      | 0.0.0    |           | Circuit                                               | 52  |

|   |      | <u> </u> |           |                                                       |     |

|   | 9.4  | 3.3.4    |           |                                                       | 55  |

|   | 3.4  |          | 0         | -Input Current-Output Binary Hysteresis Circuits with | F 4 |

|   |      |          |           | All Four Quadrants                                    |     |

|   |      | 3.4.1    |           | tic and Operation Principle                           |     |

|   |      | 3.4.2    |           | Simulations                                           | 56  |

|   |      | 3.4.3    |           | Voltage-Input Current-Output Reverse Binary Hys-      |     |

|   |      |          | teresis ( | Circuit                                               |     |

|   |      | 3.4.4    | Summar    | ry                                                    | 57  |

|   | 3.5  |          |           | -Input Voltage-Output Binary Hysteresis Circuits with |     |

|   |      | Full C   | ontrol in | All Four Quadrants                                    | 60  |

|   |      | 3.5.1    | Schemat   | tic and Operation Principle                           | 60  |

|   |      | 3.5.2    | PSpice S  | Simulation                                            | 62  |

|   |      | 3.5.3    | CMOS      | Current-Input Voltage-Output Reverse Binary Hys-      |     |

|   |      |          | teresis ( | Circuit                                               | 62  |

|   |      | 3.5.4    |           | ry                                                    |     |

|   | 3.6  | Summ     |           | ·                                                     |     |

|   |      |          |           |                                                       |     |

| 4 | Circ | uits for | Handling  | g Sweeping Signals                                    | 67  |

|   | 4.1  | Overv    | iew       |                                                       | 67  |

|   | 4.2  | Analo    | gue Adde  | ers                                                   | 67  |

|   |      | 4.2.1    | Overvie   |                                                       | 0 - |

|   |      | 4.2.2    | Analogu   | e Current Adder/Subtractor/Sign Inverter Schemat-     |     |

|   |      |          |           | Simulation Results                                    | 69  |

|   |      | 4.2.3    |           | s of Tsay's Voltage Adder/Subtractor/Sign Inverter    | 00  |

|   |      | 1.2.0    |           | rance's Common Mode Rejector                          | 71  |

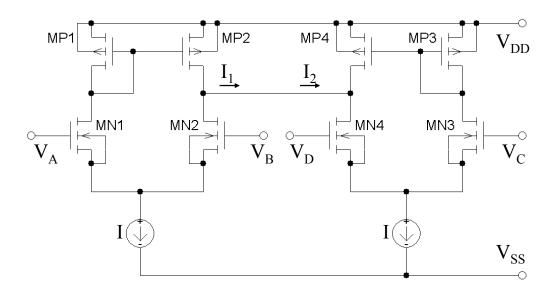

|   |      | 4.2.4    |           | ie Voltage Adder/Subtractor/Sign Inverter Schematic   | 11  |

|   |      | 4.2.4    |           | eration Principles                                    | 73  |

|   |      | 495      | -         | -                                                     | 75  |

|   |      | 4.2.5    | 0         | ue Voltage Adder/Subtractor/Sign Inverter Simulation  |     |

|   |      | 100      |           |                                                       |     |

|   | 4.2  | 4.2.6    |           | ry                                                    |     |

|   | 4.3  |          | ~         | -Quadrant Multipliers                                 |     |

|   |      | 4.3.1    |           | re Review on Four-Quadrant Multipliers                |     |

|   |      |          | 4.3.1.1   | Gilbert-Cell Based Four Quadrant Multipliers          | 80  |

|   |              |        | 4.3.1.2   |                                                          |           |

|---|--------------|--------|-----------|----------------------------------------------------------|-----------|

|   |              |        |           | nique                                                    |           |

|   |              |        | 4.3.1.3   | Quadritail Four Quadrant Multipliers                     |           |

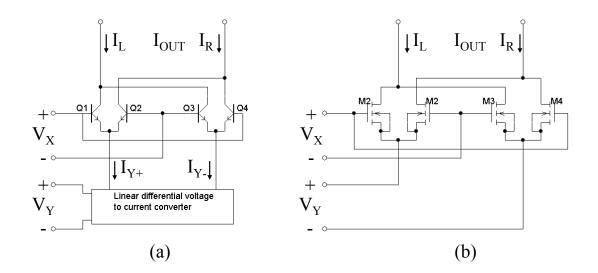

|   |              | 4.3.2  |           | -Input Four-Quadrant Multiplier                          | . 87      |

|   |              |        | 4.3.2.1   | Current-Input Four-Quadrant Multiplier Schematics        | ~ 7       |

|   |              |        | 4999      | and Operation Principles                                 | . 87      |

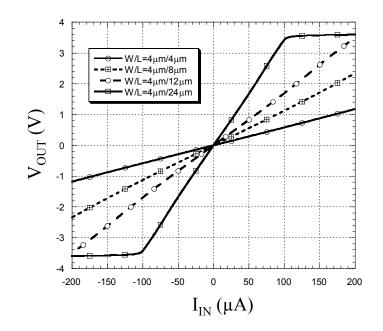

|   |              |        | 4.3.2.2   | Current-Input Four-Quadrant Multiplier Simulation        | . 89      |

|   |              | 4.3.3  | Voltaro   | Results                                                  |           |

|   |              | 4.0.0  | 4.3.3.1   | Voltage-Input Four-Quadrant Multiplier Schematics        | . 95      |

|   |              |        | 1.0.0.1   | and Operation Principles                                 | . 93      |

|   |              |        | 4.3.3.2   | Voltage-Input Four-Quadrant Multiplier Simulation        |           |

|   |              |        |           | Results                                                  | . 95      |

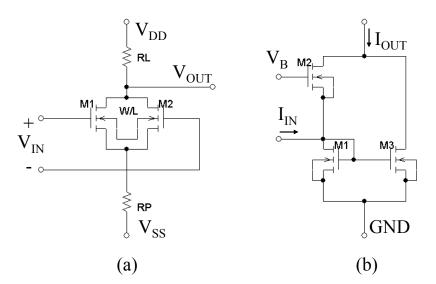

|   | 4.4          | Linear | Voltage-  | Current Converter and Current-Voltage Converter .        | . 100     |

|   |              | 4.4.1  | Linear (  | Current-Voltage Converter                                | . 100     |

|   |              | 4.4.2  | Linear I  | Differential Voltage-Current Converter                   | . 102     |

|   | 4.5          | Summ   | ary       |                                                          | . 105     |

| ۲ | CM           | 20 M1  |           | esternaia Circuit en d'Descible Analisetien en Chees Cor | _         |

| 5 | erati        |        | ы-Сеп ну  | vsteresis Circuit and Possible Application on Chaos Ger  | 1-<br>106 |

|   | 5.1          |        | uction    |                                                          |           |

|   | $5.1 \\ 5.2$ |        |           | s as Building Blocks of Multi-Level Hysteresis and       | . 100     |

|   | 0.2          |        |           | seres is                                                 | 107       |

|   | 5.3          |        | v         | evel Hysteresis Circuits                                 |           |

|   | 0.0          | 5.3.1  |           | Voltage Mode Multi-Level Hysteresis                      |           |

|   |              | 5.3.2  |           | Current Mode Multi-Level Hysteresis                      |           |

|   |              | 5.3.3  |           | y                                                        |           |

|   | 5.4          | CMOS   | 8 Multi-C | ell Hysteresis Circuits                                  | . 118     |

|   |              | 5.4.1  | CMOS '    | Voltage Mode Multi-Cell Hysteresis                       | . 120     |

|   |              | 5.4.2  |           | Current Mode Multi-Cell Hysteresis                       |           |

|   |              | 5.4.3  |           | y                                                        |           |

|   | 5.5          |        |           | ns on Multi-Cell Hysteresis                              | . 129     |

|   | 5.6          |        |           | ation of Multi-Dimensional Hysteresis Cell on Chaos      |           |

|   |              |        |           |                                                          |           |

|   | 5.7          | Summ   | ary       |                                                          | . 145     |

| 6 | Sum          | mary a | nd Open   | Values                                                   | 146       |

| 0 | 6.1          | v      | -         | vanues                                                   | -         |

|   | 6.2          |        | •         | • • • • • • • • • • • • • • • • • • • •                  |           |

|   | 0.2          | 6.2.1  |           | Binary Hysteresis                                        |           |

|   |              | 6.2.2  |           | ell Hysteresis In Neural Networks                        |           |

|   |              |        | 6.2.2.1   | CNN: Cellular Neural Network                             |           |

|   |              |        | 6.2.2.2   | Radial Basis Function Neural Network                     |           |

|   |              |        |           |                                                          |           |

Bibliography

## LIST OF TABLES

| 2.1 | Common names and symbols                                                  |

|-----|---------------------------------------------------------------------------|

| 2.2 | Comparison of the voltage-input voltage-output binary hysteresis circuits |

| 2.3 | Comparison of the current-input voltage-output binary hysteresis circuits |

| 2.4 | Comparison of the voltage-input current-output binary hysteresis circuits |

| 4.1 | Transistor Sizes for Voltage Adder                                        |

| 4.2 | Transistor sizes in current-input multiplier                              |

| 4.3 | Transistor sizes in voltage-input multiplier                              |

| 4.4 | Linear current-voltage converter $V_{OUT}/I_{IN}$ ratios                  |

| 4.5 | Transistor sizes in linear differential voltage-current converter 104     |

| 4.6 |                                                                           |

## LIST OF FIGURES

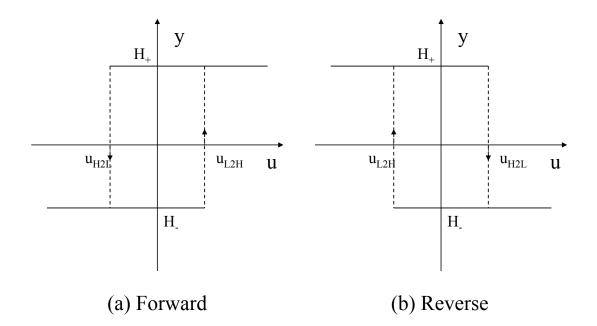

| 1.1 | Binary hysteresis, (a) forward and (b) reverse                                                                                                                                                                | 4  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

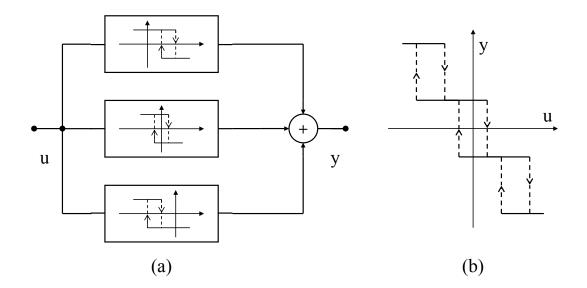

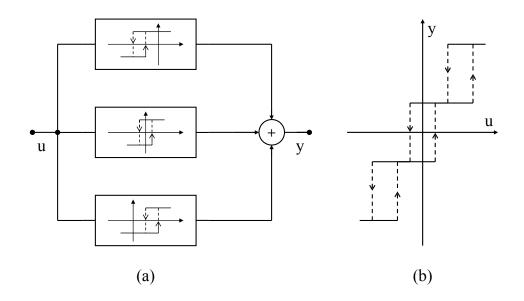

| 1.2 | Generation of 4-level hysteresis by adding 3 binary hysteresis. (a)<br>Schematic. (b) 4-level hysteresis                                                                                                      | 5  |

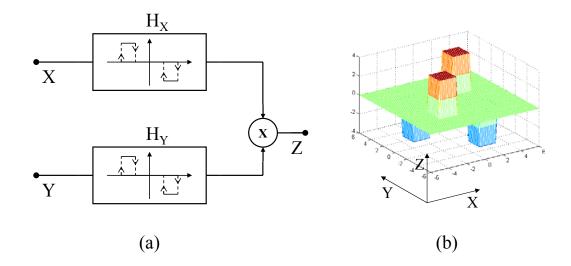

| 1.3 | Generation of 2-dimensional 3-level hysteresis cubes. (a) Schematic.<br>(b) 3-D plot of the hysteresis cubes                                                                                                  | 7  |

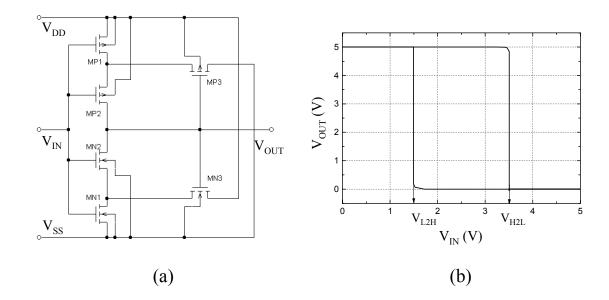

| 2.1 | CMOS Schmitt trigger, a voltage-input voltage-output hysteresis circuit. (a) Schematic used in PSpice simulation. (b) Simulated transfer characteristics, reverse hysteresis. $V_{DD} = 5V$ and $V_{SS} = 0V$ | 12 |

| 2.2 | Pfister's CMOS adjustable Schmitt trigger [41], with external voltage control.                                                                                                                                | 14 |

| 2.3  | Pfister's CMOS adjustable Schmitt trigger [41], with external voltage control simulation results. $V_{DD} = 5V$ and $V_{SS} = 0V$ . (a) $V_{CT} = 0V$ . (b) $V_{CT} = 5V$                                                                                                                                                                                                                                                                                                                                    | 15 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.4  | Kim's adjustable hysteresis using operational transconductance amplifier [23]. (a)Circuit configuration. (b)Transfer characteristic                                                                                                                                                                                                                                                                                                                                                                          | 16 |

| 2.5  | New<br>comb's swept hysteresis hysteresis realization circuits<br>[36].                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17 |

| 2.6  | Newcomb's experimental swept hysteresis results [36]. (a) $V_S$ is a square wave. (b) $V_S$ is a sine wave                                                                                                                                                                                                                                                                                                                                                                                                   | 17 |

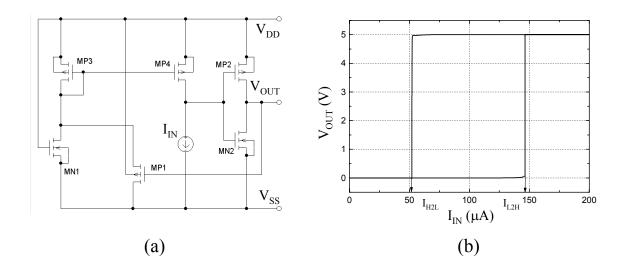

| 2.7  | Liao's CMOS current-input voltage-output hysteresis circuit. [29].<br>(a) Schematic used in PSpice simulation. (b) Simulated transfer char-<br>acteristic, forward hysteresis. $V_{DD} = 5V$ and $V_{SS} = 0V$                                                                                                                                                                                                                                                                                               | 19 |

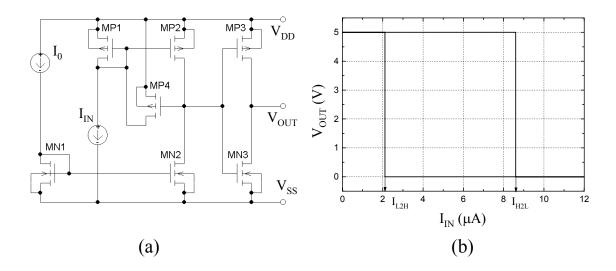

| 2.8  | Z. Wang's CMOS 7-transistor current-input voltage-output hysteresis<br>circuit [59]. (a) Schematic used in PSpice simulation. (b) Simulated<br>transfer characteristic, reverse hysteresis. $V_{DD} = 5V$ , $V_{SS} = 0V$ and<br>$I_0 = 2\mu A$                                                                                                                                                                                                                                                              | 21 |

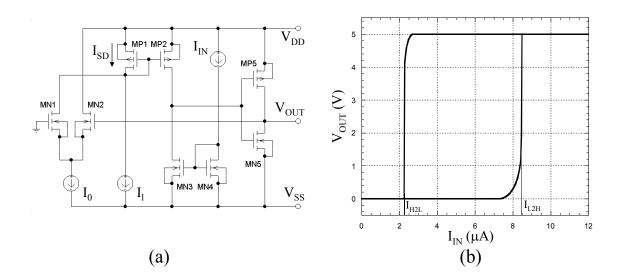

| 2.9  | Z. Wang's CMOS 8-transistor current-input voltage-output hysteresis<br>circuit [60]. (a) Schematic used in PSpice simulation. (b) Simulated<br>transfer characteristic, forward hysteresis. $V_{DD} = 5V$ , $V_{SS} = 0V$ ,<br>$I_0 = 6\mu A$ , and $I_1 = 2\mu A$                                                                                                                                                                                                                                           | 22 |

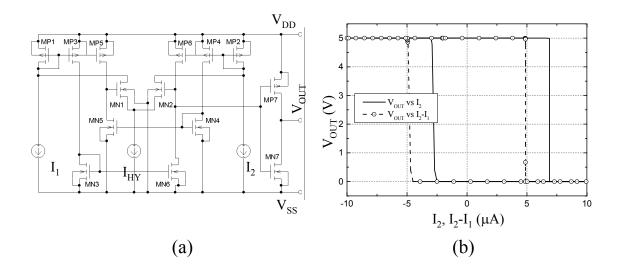

| 2.10 | CMOS two-input current comparator with hysteresis [60]. (a) Schematic used in PSpice simulation. (b)Simulated transfer characteristic, reverse hysteresis. This circuit gives reverse hysteresis; $I_2$ is the input and $I_1$ is the control. $V_{DD} = 5V$ , $V_{SS} = 0V$ , and $I_1 = 2\mu A$                                                                                                                                                                                                            | 24 |

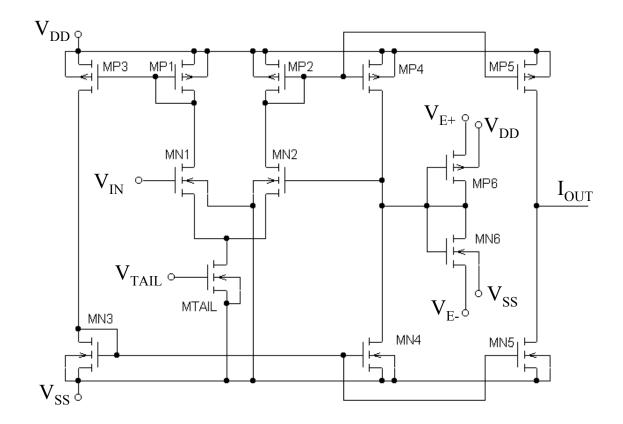

| 2.11 | Schematic of the T-mode hysteresis amplifier [31]                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26 |

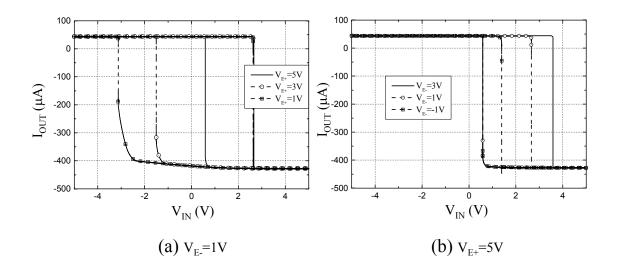

| 2.12 | Simulated transfer characteristics for T-mode hysteresis amplifier.<br>$V_{DD} = 5V$ and $V_{SS} = -5V$ . (a) For $V_{E-} = 1V$ , the solid line, dashed<br>line with centered circles, and dashed line with crossed squares are<br>the output curve when $V_{E+} = 5V$ , $3V$ , and $1V$ , respectively. (b) For<br>$V_{E+} = 5V$ , the solid line, dashed line with centered circles, and dashed<br>line with crossed squares are the output curve when $V_{E-} = 3V$ , $1V$ ,<br>and $-1V$ , respectively | 27 |

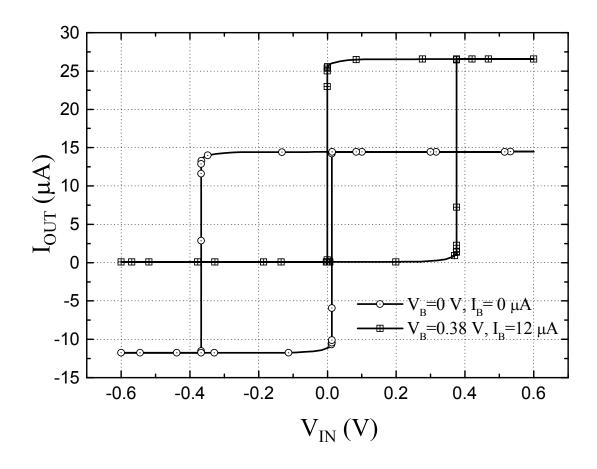

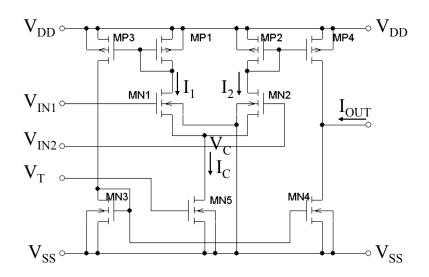

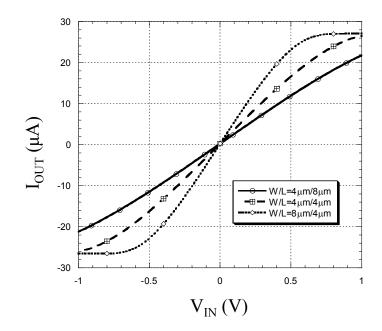

| 2.13 | Schematic of the step-linear voltage-input current-output hysteresis circuit [61].                                                                                                                                                                                                                                                                                                                                                                                                                           | 28 |

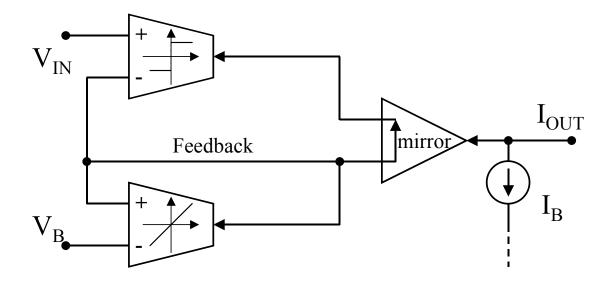

| 2.14 | One simulation example of the voltage-input current-output Hystere-<br>sis for the circuit in Figure 2.13. The solid line with circles is the<br>output when $V_B = 0V$ and $I_B = 0\mu A$ . The solid line with squares is<br>the output when $V_B = 0.38V$ and $I_B = 12\mu A$                                                                                                                                                  | 30 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

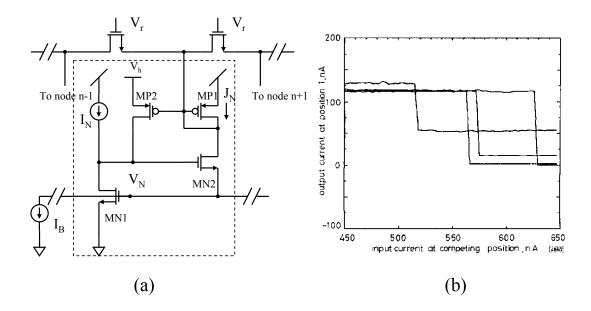

| 2.15 | DeWeerth's winner-take-all(WTA) circuit with distributed hysteresis [13]. (a)Schematic of one element in WTA circuit. (b)Experimental data showing variable hysteretic circuit behavior.                                                                                                                                                                                                                                          | 31 |

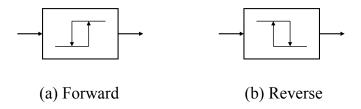

| 3.1  | Binary hysteresis (a) Forward and (b) Reverse [36]                                                                                                                                                                                                                                                                                                                                                                                | 33 |

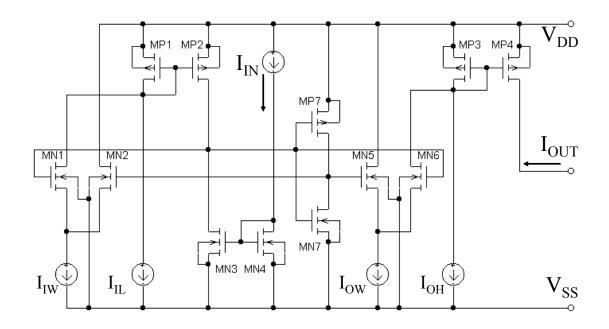

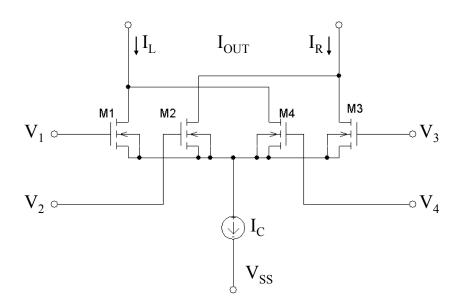

| 3.2  | Schematic of the CMOS current-input current-output hysteresis cir-<br>cuit in fourth quadrant.                                                                                                                                                                                                                                                                                                                                    | 36 |

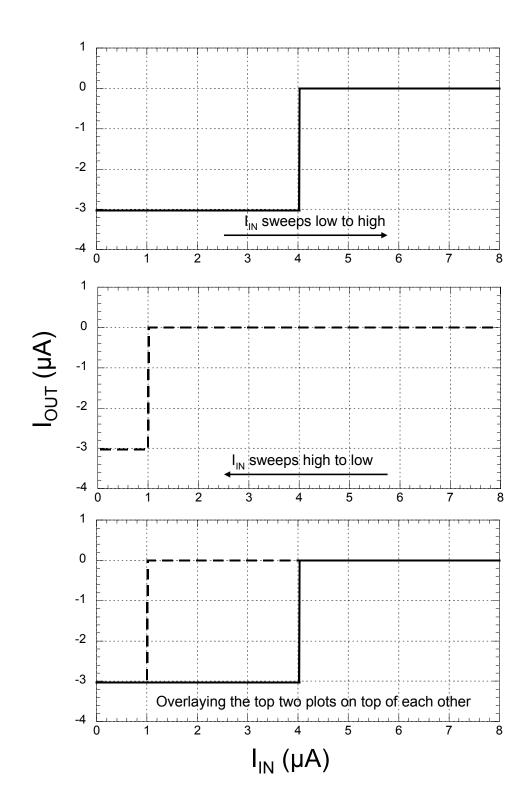

| 3.3  | PSpice simulation results for the current-input current-output hys-<br>teresis circuit in the 4th quadrant, shown in Figure 3.2.                                                                                                                                                                                                                                                                                                  | 38 |

| 3.4  | PSpice simulation results for the current-input current-output hysteresis circuit in the 4th quadrant, shown in Figure 3.2. The solid line with circles is $I_{OUT}$ vs $I_{IN}$ when $I_{IL} = 1\mu A$ , $I_{IW} = 3\mu A$ , $I_{OH} = 0\mu A$ , and $I_{OW} = 3\mu A$ . The dashed line with squares is $I_{OUT}$ vs $I_{IN}$ when $I_{IL} = 3\mu A$ , $I_{IW} = 3\mu A$ , $I_{OH} = 2\mu A$ , and $I_{OW} = 3\mu A$ . $\ldots$ | 39 |

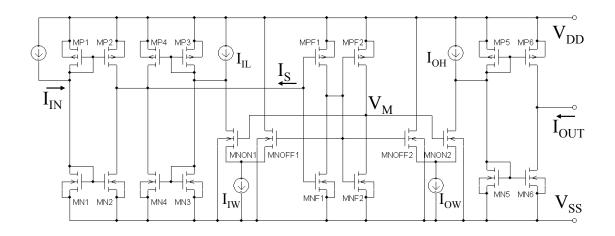

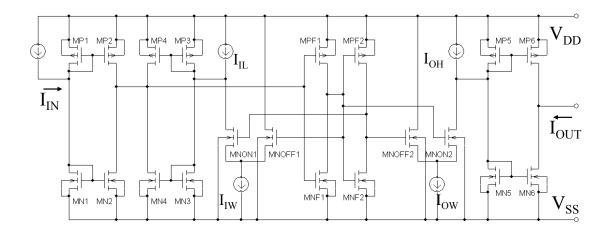

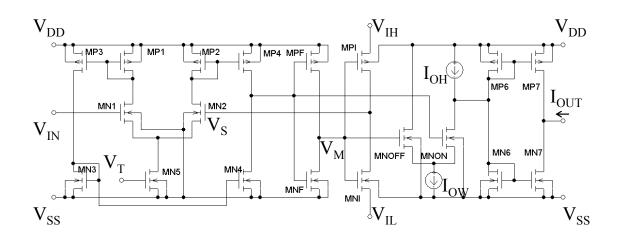

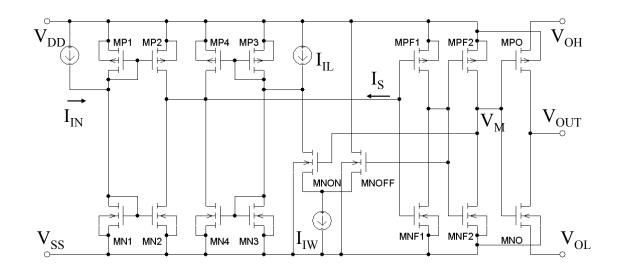

| 3.5  | Schematic of the current-input current-output forward binary hys-<br>teresis circuit working in the full input and output range, all four<br>quadrants                                                                                                                                                                                                                                                                            | 40 |

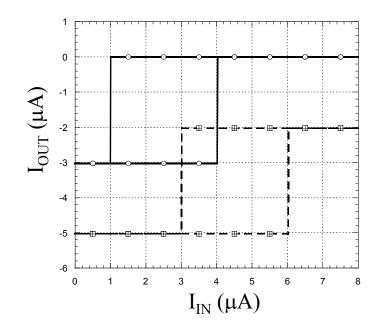

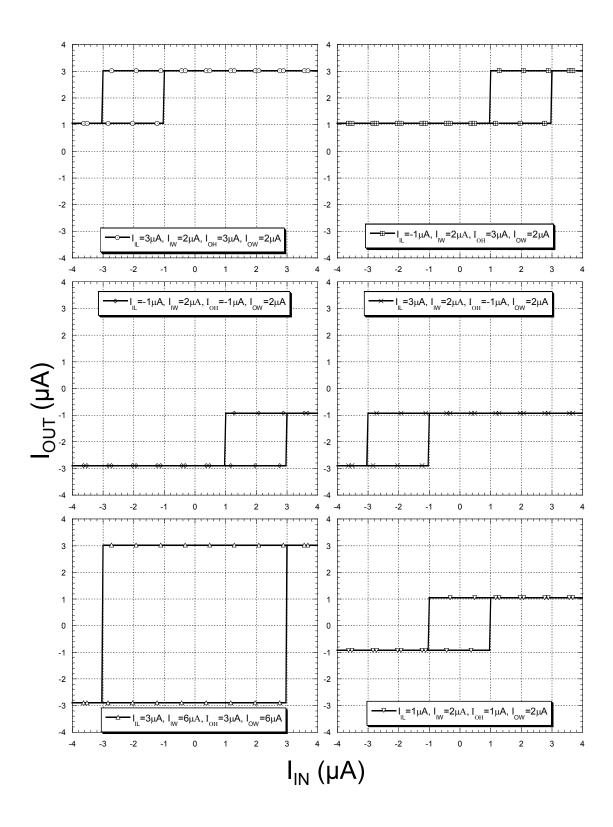

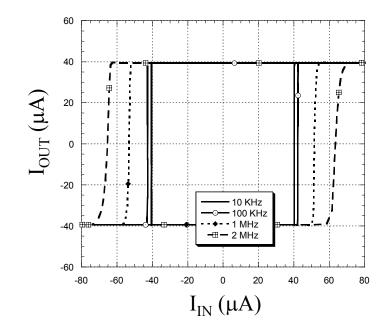

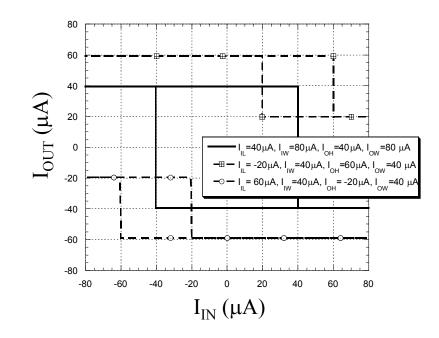

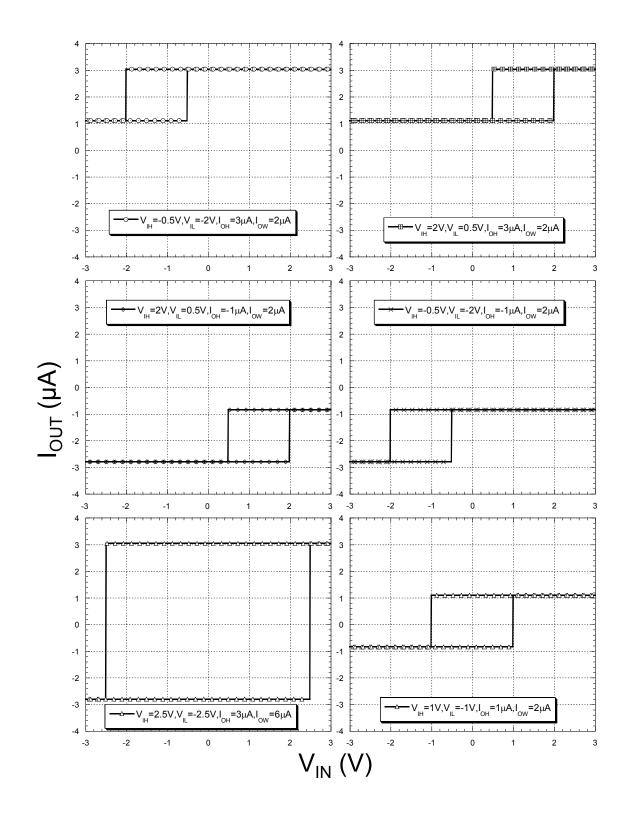

| 3.6  | PSpice simulation results for the current-input current-output for-<br>ward hysteresis circuit with full operating range, shown in Figure 3.5.                                                                                                                                                                                                                                                                                    | 43 |

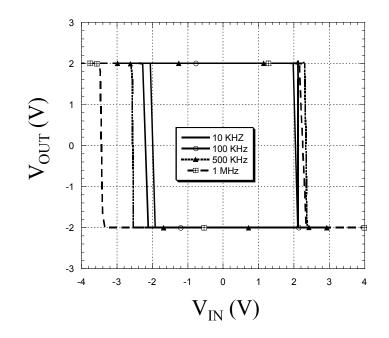

| 3.7  | Frequency response of the current-input current-output forward bi-<br>nary hysteresis circuit shown in Figure 3.5. $I_{IL} = 40\mu A$ , $I_{IW} = 80\mu A$ , $I_{OH} = 40\mu A$ , and $I_{OW} = 80\mu A$ .                                                                                                                                                                                                                        | 45 |

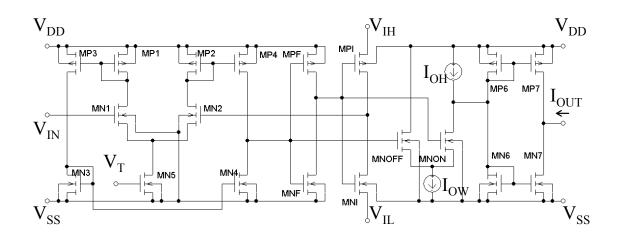

| 3.8  | Schematic of the current-input current-output reverse binary hystere-<br>sis circuit working in the full input and output range, all four quadrants.                                                                                                                                                                                                                                                                              | 46 |

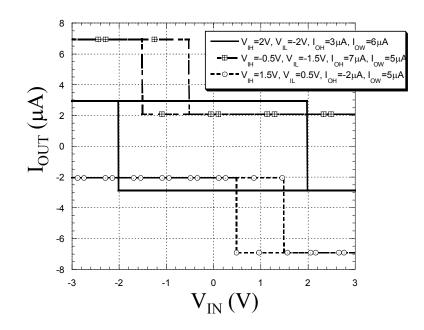

| 3.9  | PSpice simulation results for the current-input current-output reverse<br>binary hysteresis circuit with full operating range, shown in Figure 3.8.                                                                                                                                                                                                                                                                               | 47 |

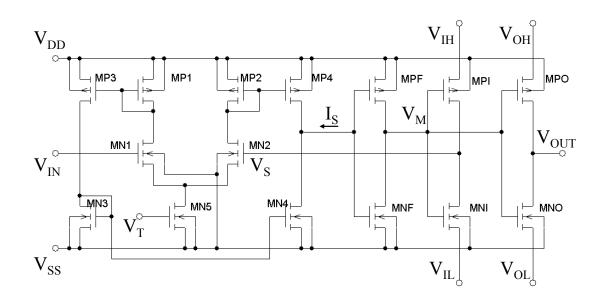

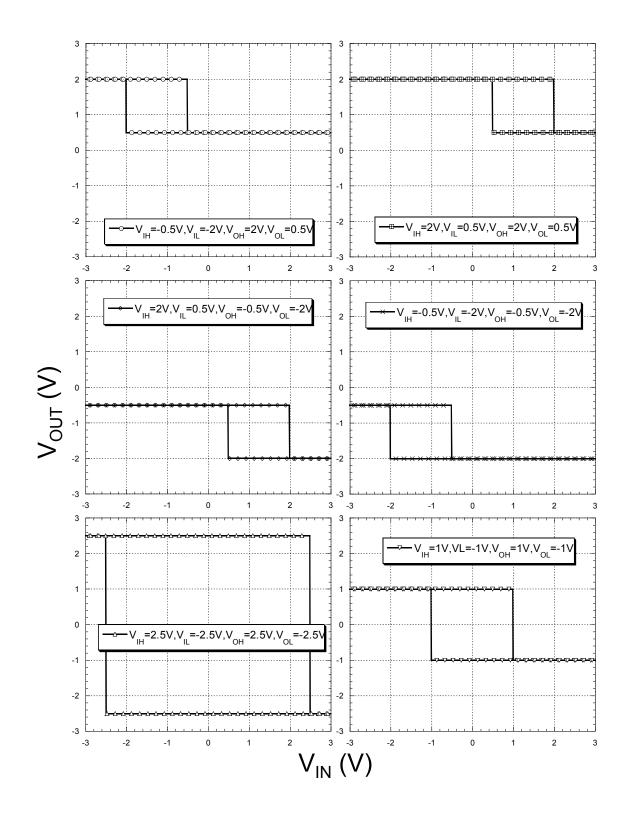

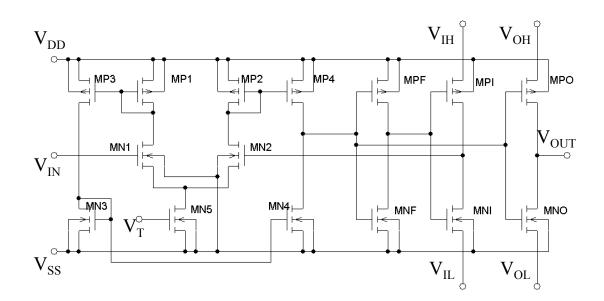

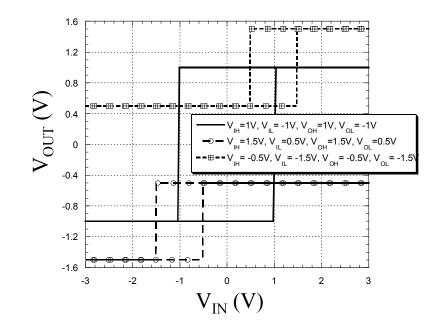

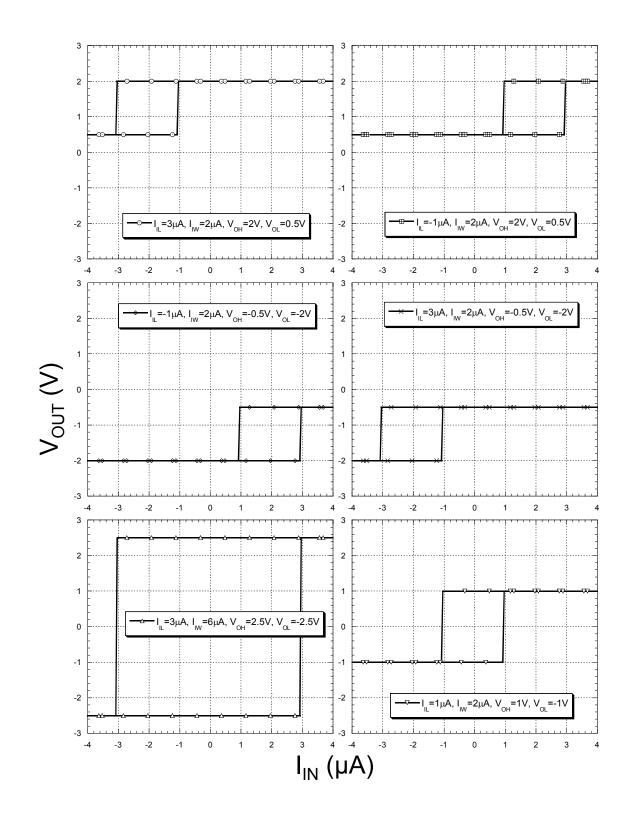

| 3.10 | Schematic of the voltage-input voltage-output reverse binary hystere-<br>sis circuit working in all four quadrants, with full control                                                                                                                                                                                                                                                                                             | 49 |

| 3.11 | PSpice simulation results for the voltage-input voltage-output reverse binary hysteresis circuit with full control, shown in Figure 3.10                                                                                                                                                                                                                                                                                          | 51 |

| 3.12 | Frequency response of the voltage-input voltage-output reverse binary<br>hysteresis circuit shown in Figure 3.10. $V_{IH} = 2V, V_{IL} = -2V,$<br>$V_{OH} = 2V$ , and $V_{OL} = -2V$ . | 52 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13 | Schematic of the voltage-input voltage-output forward binary hys-<br>teresis circuit working in the full input and output range, all four<br>quadrants                                 | 53 |

| 3.14 | PSpice simulation results for the voltage-input voltage-output for-<br>ward binary hysteresis circuit with full operating range, shown in<br>Figure 3.13                               | 54 |

| 3.15 | Schematic of the voltage-input current-output forward binary hys-<br>teresis circuit working in all four quadrants, with full control                                                  | 55 |

| 3.16 | PSpice simulation results for the voltage-input current-output for-<br>ward binary hysteresis circuit with full control, shown in Figure 3.15.                                         | 58 |

| 3.17 | Schematic of the voltage-input current-output reverse binary hystere-<br>sis circuit working in the full input and output range, all four quadrants.                                   | 59 |

| 3.18 | PSpice simulation results for the voltage-input current-output reverse<br>binary hysteresis circuit with full operating range, shown in Figure<br>3.17                                 | 59 |

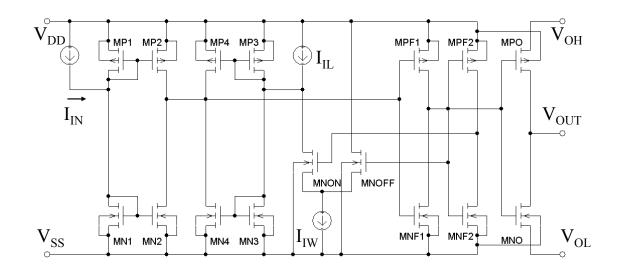

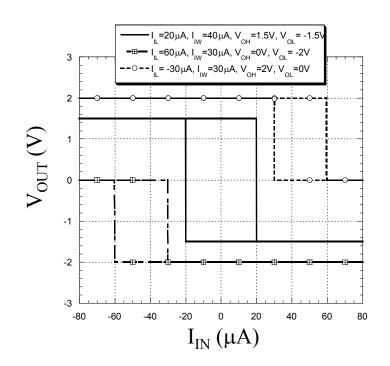

| 3.19 | Schematic of the current-input voltage-output forward binary hys-<br>teresis circuit working in all four quadrants, with full control                                                  | 60 |

| 3.20 | PSpice simulation results for the current-input voltage-output for-<br>ward binary hysteresis circuit with full control, shown in Figure 3.19.                                         | 63 |

| 3.21 | Schematic of the current-input voltage-output reverse binary hystere-<br>sis circuit working in the full input and output range, all four quadrants.                                   | 64 |

| 3.22 | PSpice simulation results for the current-input voltage-output reverse<br>binary hysteresis circuit with full operating range, shown in Figure<br>3.21                                 | 65 |

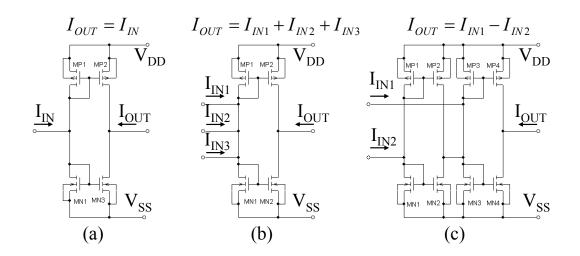

| 4.1  | Schematics of a current sign inverter, a current adder, and a current subtractor. (a) Sign inverter. (b) Adder. (c) Subtractor                                                         | 69 |

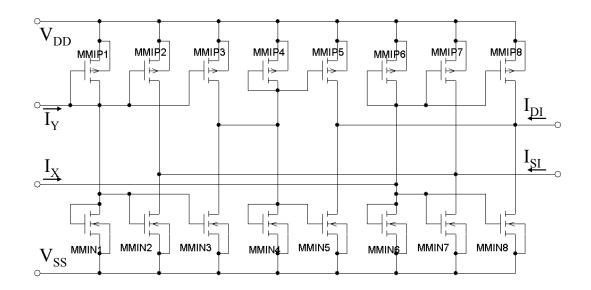

| 4.2  | Schematics of a current a current adder/subtractor with $I_{SI} = I_X + I_Y$<br>and $I_{DI} = I_X - I_Y$                                                                               | 70 |

| 4.3  | Simulation results for the CMOS current adder/subtractor shown in Figure 4.2. $I_X$ sweeps from $-40\mu A$ to $40\mu A$ , and $I_Y$ steps from $-40\mu A$ to $40\mu A$ with $20\mu A$ step. The solid line is $I_{SI}$ , and the dashed line is $I_X + I_Y$ . | 70      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4.4  | Schematic of S. W. Tsay and R. W. Newcomb's [55] adder/subtractor/sig invertor.                                                                                                                                                                               | n<br>72 |

| 4.5  | Schematic of R. R. Torrance's [54] common mode rejection circuit                                                                                                                                                                                              | 72      |

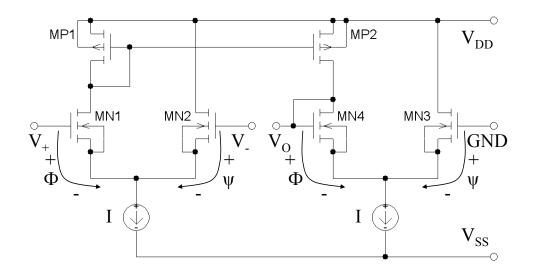

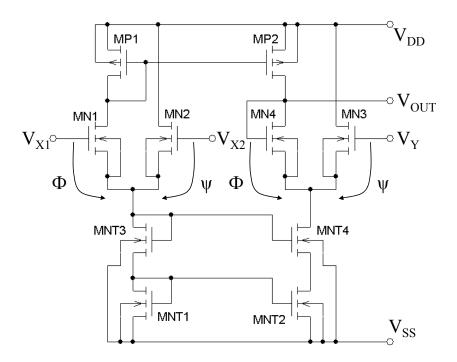

| 4.6  | Schematic of a new CMOS voltage adder/subtractor/sign invertor                                                                                                                                                                                                | 74      |

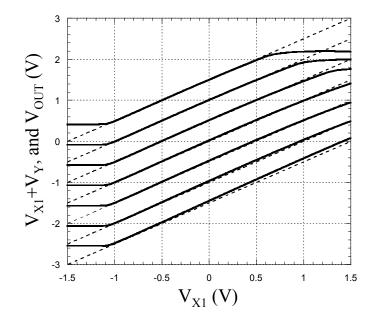

| 4.7  | Simulation results for the voltage adder/subtractor/sign inverter, shown<br>in Figure 4.6, used as a voltage adder, with $V_{OUT} = V_{X1} + V_Y$ . $V_{X1}$<br>sweeps from $-1.5V$ to $1.5V$ and $V_Y$ steps from $-1.5V$ to $1.5V$ with<br>0.5V step        | 76      |

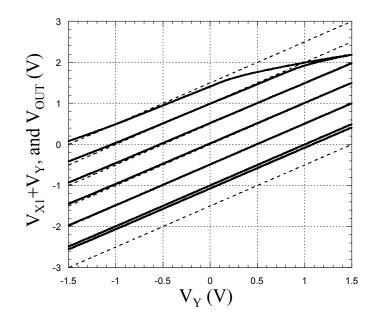

| 4.8  | Simulation results for the voltage adder/subtractor/sign inverter, shown<br>in Figure 4.6, used as a voltage adder, with $V_{OUT} = V_{X1} + V_Y$ . $V_Y$<br>sweeps from $-1.5V$ to $1.5V$ , and $V_{X1}$ steps from $-1.5V$ to $1.5V$ with<br>0.5V step      | 77      |

| 4.9  | Simulation results for the voltage adder/subtractor/sign inverter, shown in Figure 4.6, used as a voltage subtracter, with $V_{OUT} = V_Y - V_{X2}$ .                                                                                                         | 78      |

| 4.10 | Simulation results for the voltage adder/subtractor/sign inverter, shown in Figure 4.6, used as a voltage sign inverter, with $V_{OUT} = -V_{X2}$ .                                                                                                           | 79      |

| 4.11 | Quadritail-Gilbert Cell like Multipliers. (a) BJT Gilbert Cell. (b)<br>CMOS Gilbert cell                                                                                                                                                                      | 81      |

| 4.12 | Squaring circuits. (a)Voltage input [40]. (b) Current input [6], which was further discussed by D. M. W. Leenaerts [28]                                                                                                                                       | 83      |

| 4.13 | Schematic of quadritail multiplication core                                                                                                                                                                                                                   | 85      |

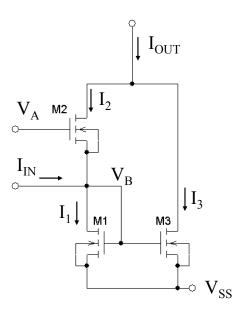

| 4.14 | The schematic of Bult's current squaring circuit [6]                                                                                                                                                                                                          | 88      |

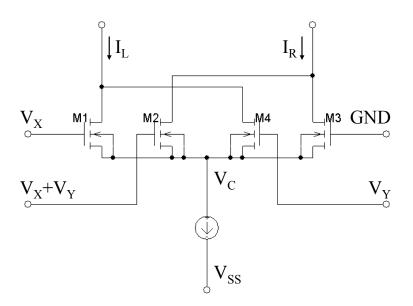

| 4.15 | The schematic of the multiplication core of the current-input multiplier.                                                                                                                                                                                     | 89      |

| 4.16 | The schematic of the CMOS complete four-quadrant current-input multiplier                                                                                                                                                                                     | 90      |

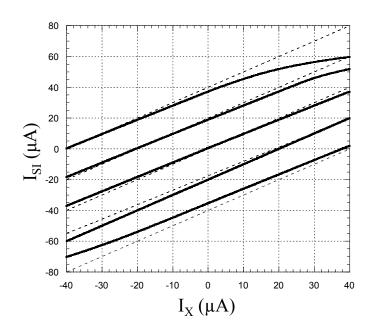

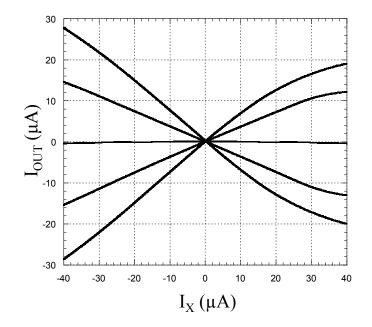

| 4.17 | Simulation results for the CMOS four quadrant current-input current-<br>output multiplier in Figure 4.16. $I_X$ sweeps from $-40\mu A$ to $+40\mu A$ ,<br>and $I_Y$ steps from $-40\mu A$ to $+40\mu A$ with $+20\mu A$ step                                  | 91      |

| 4.18 | Simulation results for the CMOS four quadrant current-input current-<br>output multiplier in Figure 4.16. $I_X$ sweeps from $-20\mu A$ to $+20\mu A$ ,<br>and $I_Y$ steps from $-20\mu A$ to $+20\mu A$ with $+10\mu A$ step              | 92  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

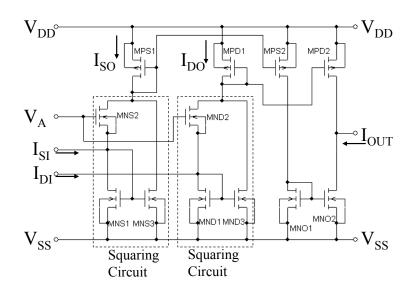

| 4.19 | The schematic of the multiplication core of the voltage-input multiplier–<br>quadritail                                                                                                                                                   | 94  |

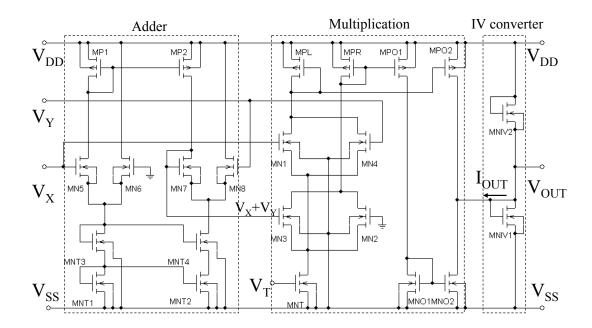

| 4.20 | The schematic of the complete CMOS four quadrant voltage-input multiplier                                                                                                                                                                 | 95  |

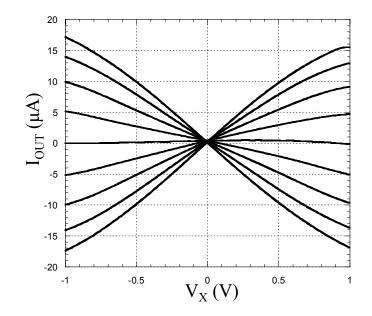

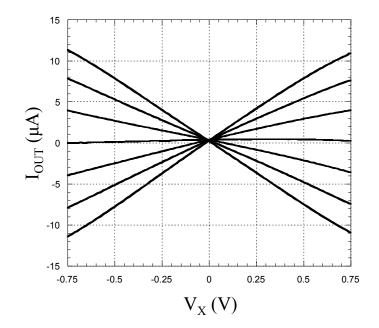

| 4.21 | Simulation results for the CMOS four-quadrant voltage-input multiplier in Figure 4.20, with the current output $I_{OUT}$ . $V_X$ sweeps from $-1V$ to $+1V$ , and $V_Y$ steps from $-1V$ to $+1V$ with $+0.25V$ step                      | 96  |

| 4.22 | Simulation results for the CMOS four-quadrant voltage-input multiplier in Figure 4.20, with the current output $I_{OUT}$ . $V_X$ sweeps from $-0.75V$ to $+0.75V$ , and $V_Y$ steps from $-0.75V$ to $+0.75V$ with $+0.25V$ step.         | 98  |

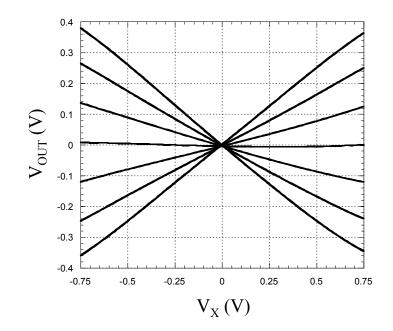

| 4.23 | Simulation results for the CMOS four quadrant voltage-input mul-<br>tiplier in Figure 4.20, with the voltage output $V_{OUT}$ . $V_X$ sweeps<br>from $-0.75V$ to $+0.75V$ , and $V_Y$ steps from $-0.75V$ to $+0.75V$ with<br>+0.25V step | 99  |

| 4.24 | Schematic of the linear current-voltage converter [6]                                                                                                                                                                                     | 100 |

| 4.25 | Simulation results for the linear current voltage converter in Figure 4.24.                                                                                                                                                               | 102 |

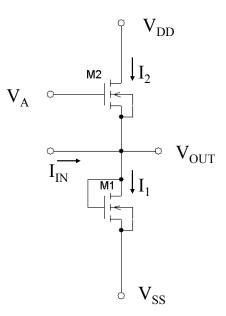

| 4.26 | Schematic of the CMOS linear differential voltage-current converter–<br>differential pair                                                                                                                                                 | 103 |

| 4.27 | Simulation results for the CMOS linear differential voltage-current converter in Figure 4.26.                                                                                                                                             | 105 |

| 5.1  | Block diagrams of binary hysteresis circuits. (a)Forward binary hysteresis. (b) Reverse binary hysteresis.                                                                                                                                | 107 |

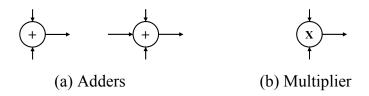

| 5.2  | Block diagrams of adders and multiplier. (a)Two input port adder<br>and three input port adder. (b) Two input port multiplier                                                                                                             | 108 |

| 5.3  | Generation of 4-level hysteresis by adding 3 forward binary hysteresis.<br>(a) Schematic. (b) 4-level hysteresis.                                                                                                                         | 109 |

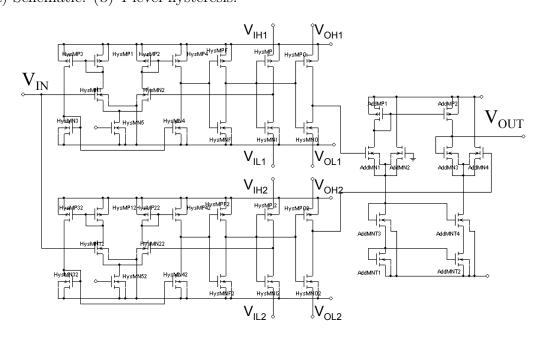

| 5.4  | Schematic of a CMOS voltage mode multi-level hysteresis circuits, with two voltage-input voltage-output binary hysteresis circuits on the left and one analogue voltage adder on the right                                                                                                                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

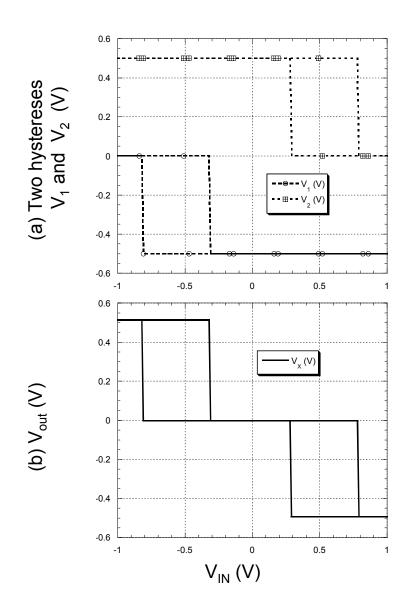

| 5.5  | PSpice simulation results for the generation of a voltage mode 3-level<br>hysteresis. (a) Two reverse binary hysteresis centered $(-0.25V, -0.55V)$<br>and $(0.25V, 0.55V)$ , with the same height of $0.5V$ and width of $0.5V$ .<br>(b) Output voltage $V_{OUT}$ in the unit of Volts. Both plots have $V_{IN}$<br>in the unit of Volts as x-axis                                                          |

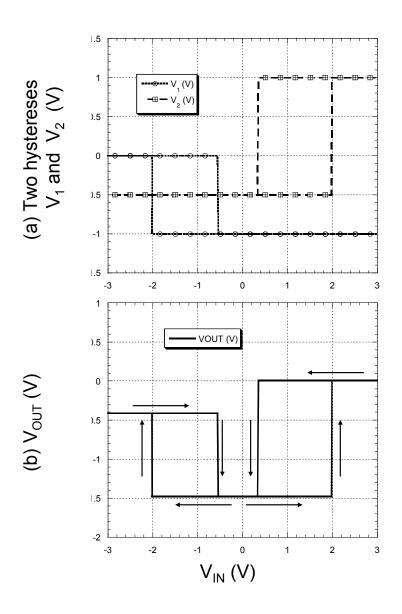

| 5.6  | PSpice simulation results for the generation of a voltage mode 3-level hysteresis. (a) One forward hysteresis centered at $(1.2V, 0.25V)$ with height of $1.5V$ and width of $1.6V$ , and one reverse binary hysteresis centered $(-1.2V, -0)$ with the height of $1V$ and width of $1.6V$ . (b) Output voltage $V_{OUT}$ in the unit of Volts. Both plots have $V_{IN}$ in the unit of Volt as x-axis       |

| 5.7  | Schematic of a CMOS current mode multi-level hysteresis circuit, with three current-input current-output binary hysteresis circuits 113                                                                                                                                                                                                                                                                      |

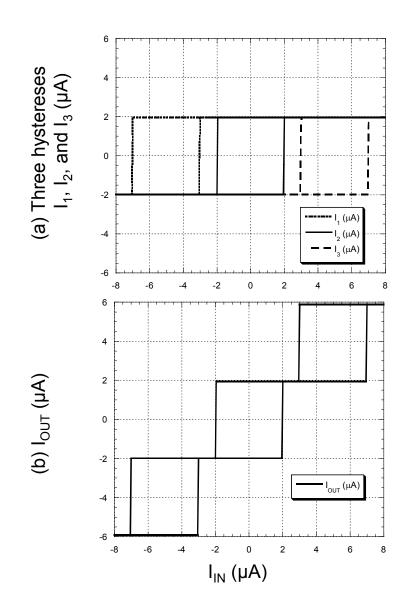

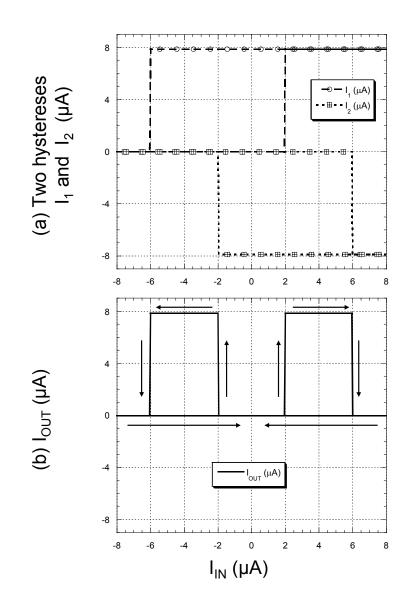

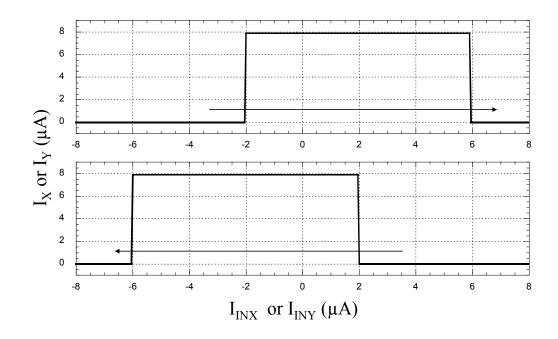

| 5.8  | PSpice simulation results for the generation of a current mode 4-level<br>hysteresis by adding 3 forward binary hystereses. (a) Three binary<br>hystereses are positioned at different locations horizontally without<br>overlapping of the switching points, in the unit of $\mu A$ . (b) Output<br>current $I_{OUT}$ in the unit of $\mu A$ . Both plots have $I_{IN}$ in the unit of<br>$\mu A$ as x-axis |

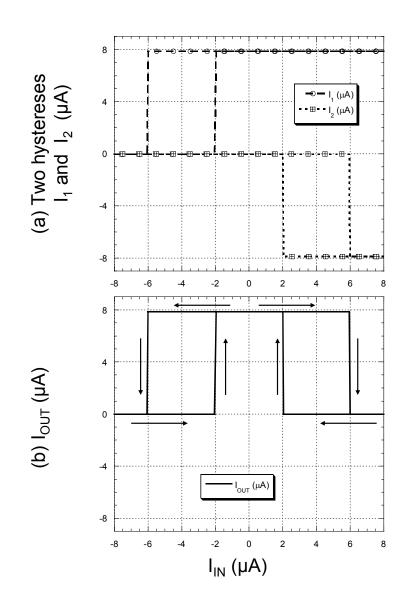

| 5.9  | PSpice simulation results for the generation of a current mode 8-level<br>hysteresis by adding 3 forward binary hysteresis. (a) Three binary<br>hysteresis positioned at same horizontal position with different height<br>and width, in the unit of $\mu A$ . (b) Output current $I_{OUT}$ in the unit of<br>$\mu A$ . Both plots have $I_{IN}$ in the unit of $\mu A$ as x-axis                            |

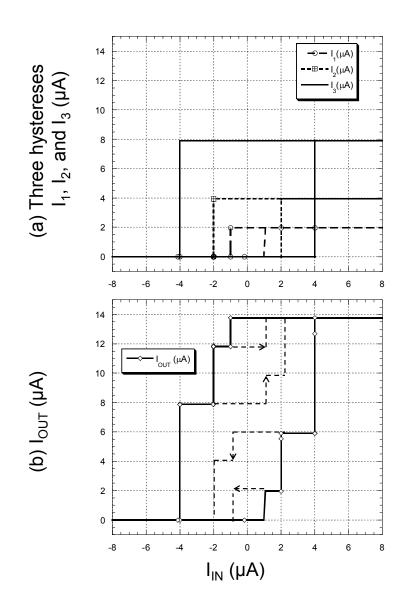

| 5.10 | PSpice simulation results for the generation of a current mode 2-level hysteresis by adding one forward and one reverse binary hysteresis.<br>(a) Two binary hysteresis, one forward, centered at $(-4\mu A, 4\mu A)$ , and one reverse, centered at $(4\mu A, -4\mu A)$ . (b) Output current $I_{OUT}$ in the unit of $\mu A$ . Both plots have $I_{IN}$ in the unit of $\mu A$ as x-axis 117               |

| 5.11 | PSpice simulation results for the generation of a current mode 2-level hysteresis by adding one forward and one reverse binary hysteresis.<br>(a) Two binary hysteresis, one forward, centered at $(-2\mu A, 4\mu A)$ , and one reverse, centered at $(2\mu A, -4\mu A)$ . (b) Output current $I_{OUT}$ in the unit of $\mu A$ . Both plots have $I_{IN}$ in the unit of $\mu A$ as x-axis 119               |

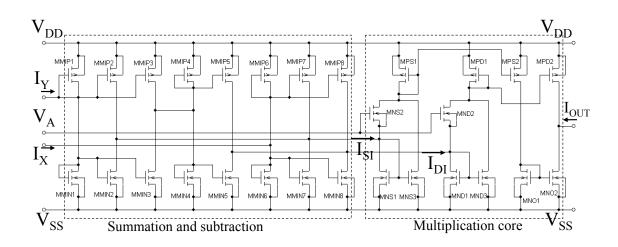

| 5.12 | Generation of 2-dimensional 3-level hysteresis cubes. (a) Schematic.<br>(b) 3-D plot of the hysteresis cubes                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 120 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

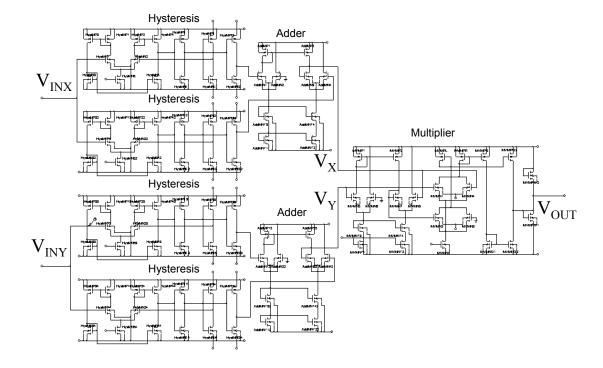

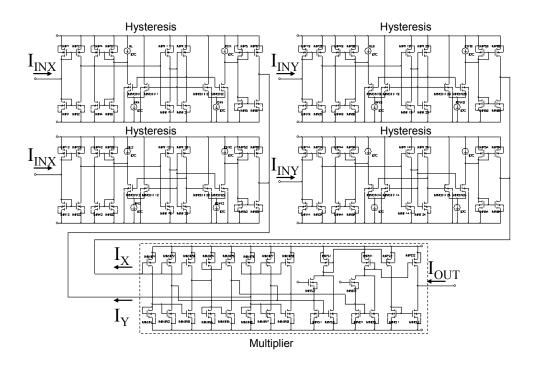

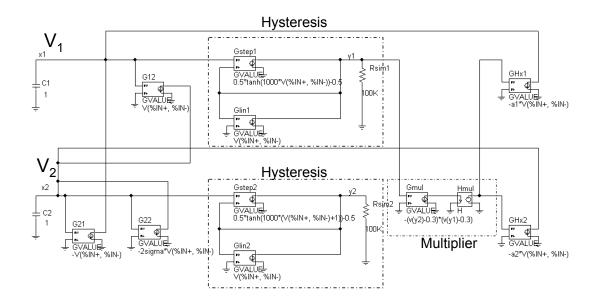

| 5.13 | Schematic of a CMOS voltage mode multi-cell hysteresis circuit, with 4 binary voltage-input voltage-output hysteresis circuits on the left, 2 analogue voltage adders in the middle, and one analogue voltage multiplier on the right.                                                                                                                                                                                                                                                                                                        | . 121 |

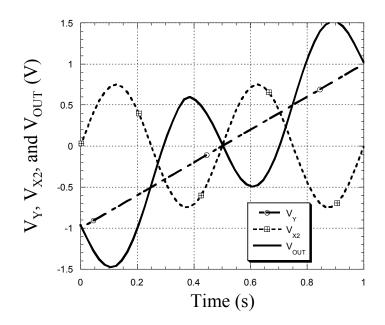

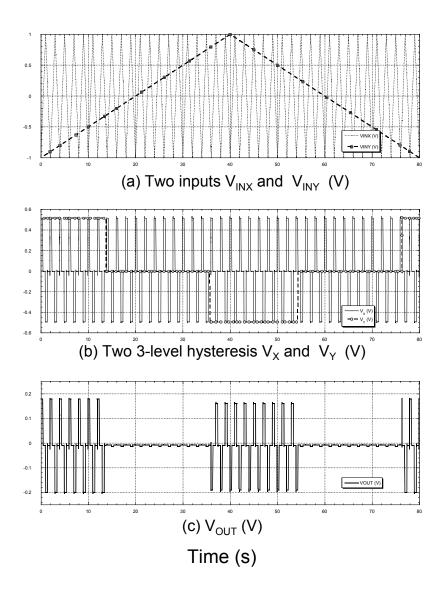

| 5.14 | PSpice simulation results for the CMOS voltage mode multi-cell hys-<br>teresis circuits in Figure 5.13. (a) Two triangular wave inputs: $V_{INX}$<br>with period of 2S, and $V_{INY}$ with period of 80S. (b) Two 3-level hys-<br>teresis, $V_X$ the thin solid line, and $V_Y$ the thick dart line with circles.<br>(c) Output voltage $V_{OUT}$ . All three plots have time as the x-axis with<br>the unit of second                                                                                                                        | . 123 |

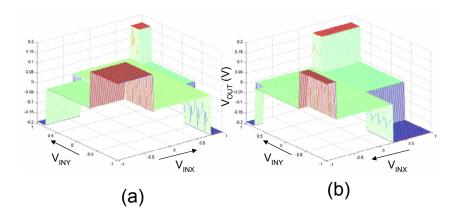

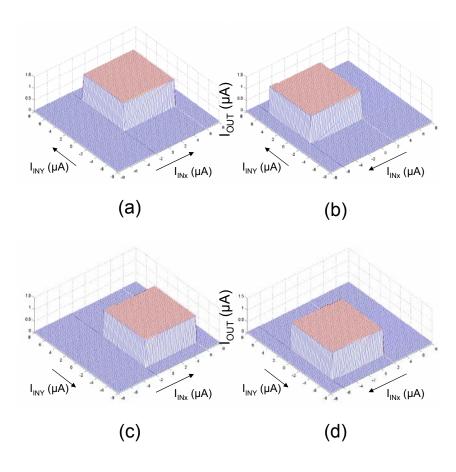

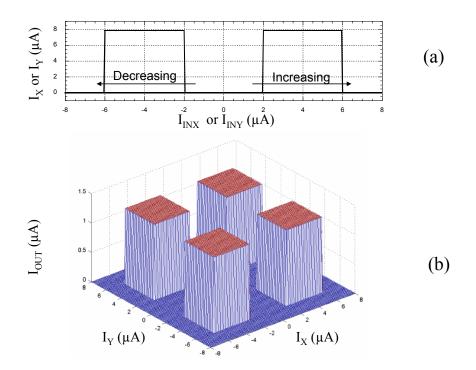

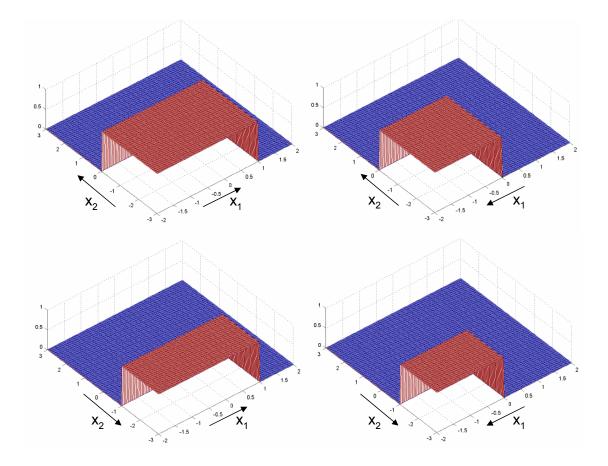

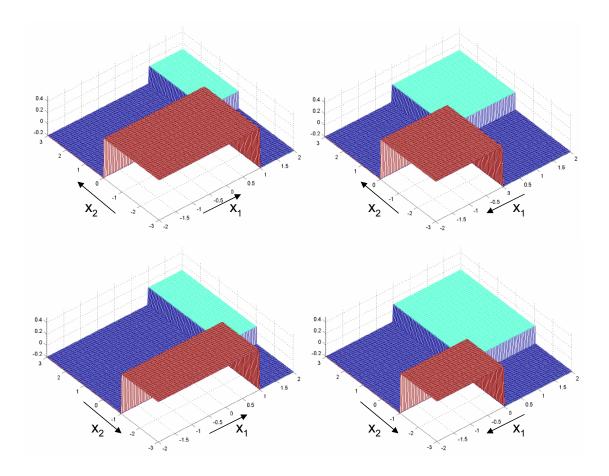

| 5.15 | Voltage mode multi-cell hysteresis, three dimensional plot of $V_{OUT}$ with respect to $V_{INX}$ and $V_{INY}$ . (a) Both $V_{INX}$ and $V_{INY}$ sweep from low to high. (b) $V_{INX}$ sweeps from high to low, and $V_{INY}$ sweeps from low to high. (c) $V_{INX}$ sweeps from low to high, and $V_{INY}$ sweeps from high to low. (d) Both $V_{INX}$ and $V_{INY}$ sweep from high to low                                                                                                                                                | . 124 |

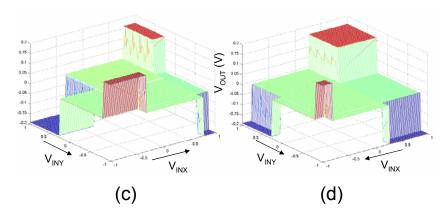

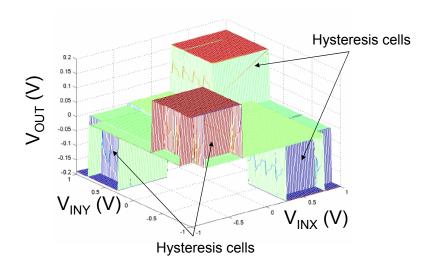

| 5.16 | Voltage mode multi-cell hysteresis, with 4 cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 125 |

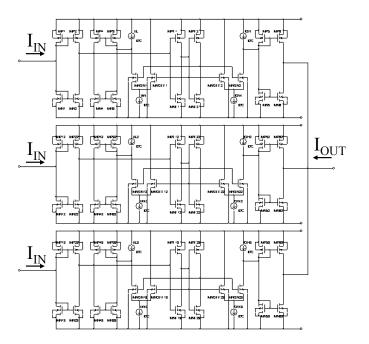

| 5.17 | Schematic of a CMOS current mode multi-cell hysteresis circuit, with 4 binary current-input current-output hysteresis circuits on the top, and one analogue current multiplier on the bottom                                                                                                                                                                                                                                                                                                                                                  | . 125 |

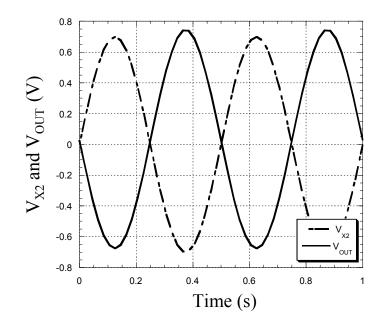

| 5.18 | Multi-level hysteresis signals $V_X$ and $V_Y$ , that is fed to current multiplier to generate current mode multi-cell hysteresis.                                                                                                                                                                                                                                                                                                                                                                                                            | . 126 |

| 5.19 | Current mode multi-cell hysteresis, three dimensional plot of $I_{OUT}$ with respect to $I_{INX}$ and $I_{INY}$ . (a) Both $I_{INX}$ and $I_{INY}$ sweep from low to high. (b) $I_{INX}$ sweeps from high to low, and $I_{INY}$ sweeps from low to high. (c) $I_{INX}$ sweeps from low to high, and $I_{INY}$ sweeps from high to low. (d) Both $I_{INX}$ and $I_{INY}$ sweep from high to low                                                                                                                                                | . 127 |

| 5.20 | Current mode multi-cell hysteresis. (a) $I_X$ or $I_Y$ , with the right rect-<br>angular waveform when $I_{INX}$ or $I_{INY}$ sweeping from low to high, and<br>the left rectangular wave when $I_{INX}$ or $I_{INY}$ sweeping from high to<br>low. (b) $I_{OUT}$ , top most lobe for both $I_{INX}$ and $I_{INY}$ increasing, right<br>most lobe for $I_{INX}$ increasing and $I_{INY}$ decreasing, left most lobe for<br>$I_{INX}$ decreasing and $I_{INY}$ increasing, and bottom most lobe for both<br>$I_{INX}$ and $I_{INY}$ decreasing | . 128 |

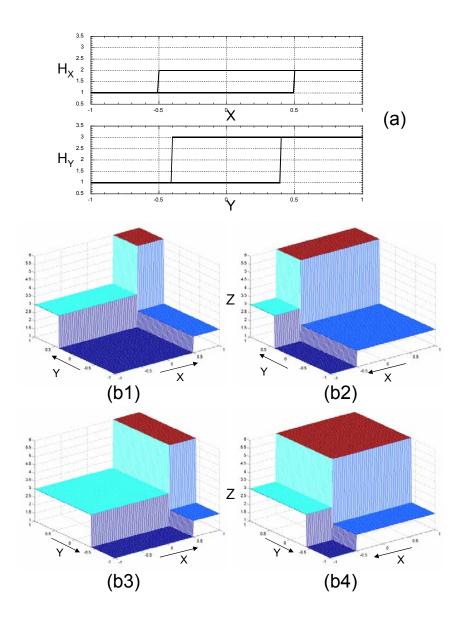

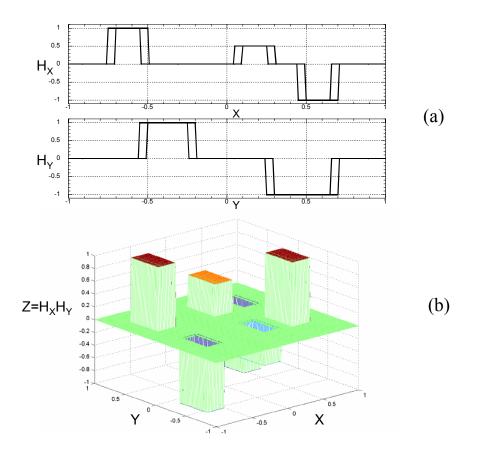

| 5.21 | Multiplication of two binary hysteresis $H_X$ and $H_Y$ . (a) $H_X$ and $H_Y$<br>with respect to X and Y. (b1)~(b2) $Z = H_X H_Y$ with respect to X<br>and Y                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.22 | Generalized case for generating hysteresis cells. (a) Multi-level hysteresis that are the inputs for a multiplier. $H_X$ has three hysteresis sections and $H_Y$ has two hysteresis sections. (b) Multi-cell hysteresis, with six hysteresis cells                                                                                            |

| 5.23 | Schematic for generating chaotic signal using two dimensional hys-<br>teresis cell                                                                                                                                                                                                                                                            |

| 5.24 | Two-dimensional hysteresis $h_1(x_1)h_2(x_2)$ vs $x_1$ and $x_2$ . With different sweeping directions of $x_1$ and $x_2$ , the boundaries are at different locations                                                                                                                                                                          |

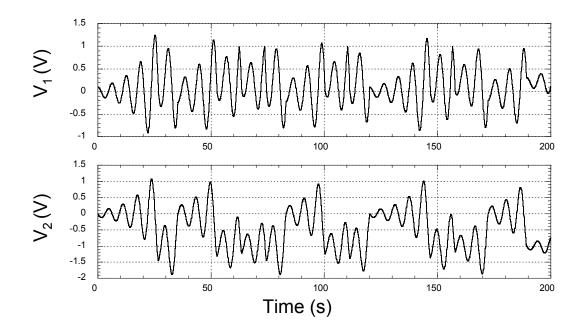

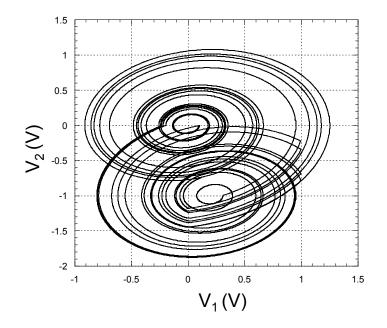

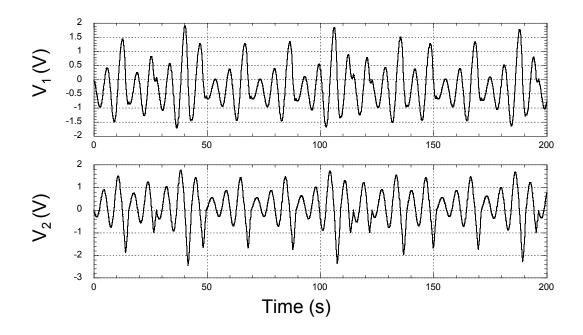

| 5.25 | Time evolution of $V_1$ and $V_2$ , for $a1 = 1$ , $a2 = 0.41$ , $\sigma = -0.1$ with<br>initial condition $V_1 = 0.1$ and $V_2 = 0$ . $h_1$ is a reverse hysteresis with<br>$h_+ = 1$ , $h = 0$ , $u_{H2L} = 1$ , and $u_{L2H} = 0$ , and $h_2$ is also a reverse one<br>with $h_+ = 1$ , $h = 0$ , $u_{H2L} = 0$ , and $u_{L2H} = -1$       |

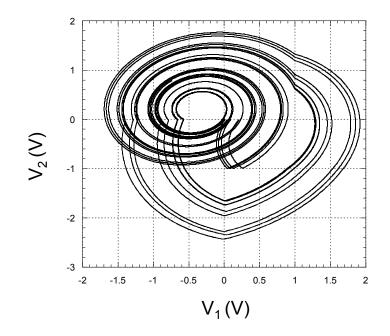

| 5.26 | Phase trajectories of $V_1$ and $V_2$ , for $a1 = 1$ , $a2 = 0.41$ , $\sigma = -0.1$ with<br>initial condition $V_1 = 0.1$ and $V_2 = 0$ . $h_1$ is a reverse hysteresis with<br>$h_+ = 1$ , $h = 0$ , $u_{H2L} = 1$ , and $u_{L2H} = 0$ , and $h_2$ is also a reverse one<br>with $h_+ = 1$ , $h = 0$ , $u_{H2L} = 0$ , and $u_{L2H} = -1$   |

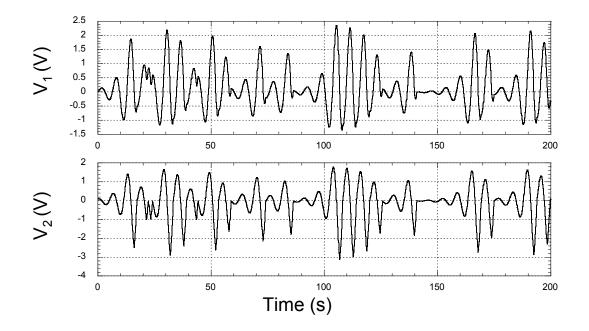

| 5.27 | Time evolution of $V_1$ and $V_2$ , for $a1 = 1$ , $a2 = 2$ , $\sigma = -0.2$ with<br>initial condition $V_1 = 0.1$ and $V_2 = 0$ . $h_1$ is a reverse hysteresis with<br>$h_+ = 1$ , $h = 0$ , $u_{H2L} = 1$ , and $u_{L2L} = 0$ , and $h_2$ is also a reverse one<br>with $h_+ = 1$ , $h = 0$ , $u_{H2L} = 0$ , and $u_{L2H} = -1$          |

| 5.28 | Phase trajectory of $V_1$ and $V_2$ , for $a1 = 1$ , $a2 = 2$ , $\sigma = -0.2$ with<br>initial condition $V_1 = 0.1$ and $V_2 = 0$ . $h_1$ is a reverse hysteresis with<br>$h_+ = 1$ , $h = 0$ , $u_{H2L} = 1$ , and $u_{L2L} = 0$ , and $h_2$ is also a reverse one<br>with $h_+ = 1$ , $h = 0$ , $u_{H2L} = 0$ , and $u_{L2H} = -1$        |

| 5.29 | Two-dimensional hysteresis $h_1(x_1)h_2(x_2)$ vs $x_1$ and $x_2$ . With different sweeping directions of $x_1$ and $x_2$ , the boundaries are at different locations                                                                                                                                                                          |

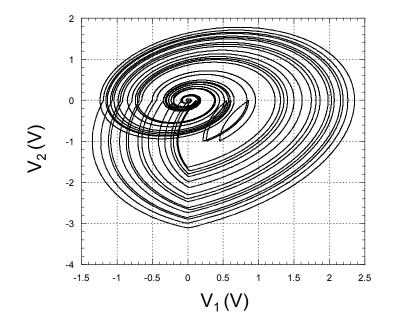

| 5.30 | Time evolution of $V_1$ and $V_2$ , for $a1 = 1$ , $a2 = 2$ , $\sigma = -0.1$ with<br>initial condition $V_1 = 0.1$ and $V_2 = 0$ . $h_1$ is a reverse hysteresis with<br>$h_+ = 0.7$ , $h = -0.3$ , $u_{H2L} = 1$ , and $u_{L2L} = 0$ , and $h_2$ is also a<br>reverse one with $h_+ = 0.7$ , $h = 0.3$ , $u_{H2L} = 0$ , and $u_{L2H} = -1$ |

- 5.31 Phase trajectory of  $V_1$  and  $V_2$ , for a1 = 1, a2 = 2,  $\sigma = -0.1$  with initial condition  $V_1 = 0.1$  and  $V_2 = 0$ .  $h_1$  is a reverse hysteresis with  $h_+ = 0.7$ ,  $h_- = -0.3$ ,  $u_{H2L} = 1$ , and  $u_{L2L} = 0$ , and  $h_2$  is also a reverse one with  $h_+ = 0.7$ ,  $h_- = 0.3$ ,  $u_{H2L} = 0$ , and  $u_{L2H} = -1$ . . . . 144

- 6.1 Binary hysteresis (a) Forward DU (down up). (b) Reverse UD (up down). (c) Forward UD (up down). (d) Reverse DU (down up). . . . 148

| 6.2 | A two-dimensional cellular neural network. The links between cells       |       |

|-----|--------------------------------------------------------------------------|-------|

|     | represent the interaction between cells. The links are different in each |       |

|     | case of definition of neighbors                                          | . 150 |

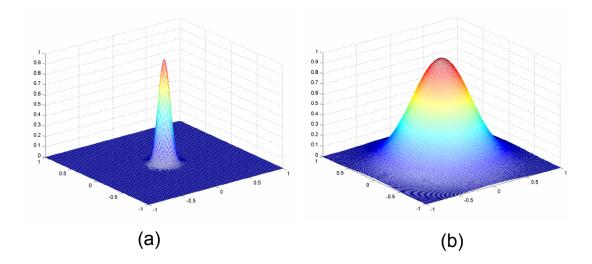

6.3 Radial basis functions with different width  $\eta$ . (a)  $\eta = 0.1$ . (b)  $\eta = 0.5.153$

#### Chapter 1

#### Introduction

According to wikipedia [67], the name of hysteresis has the meaning of "deficiency", or "lagging behind", which was used by Sir James Alfred Ewing, a Scottish physicist and engineer, to described the characteristic hysteresis curve of magnets. The output at one moment of a deterministic system with no hysteresis can be predicted with only the input to the system at that moment and the initial state. Yet for a system with hysteresis characteristics, the output of the system does not only depend on the input to the system at the moment, but also the history of the system. A system with hysteresis is a system with memory. Another important characteristic of hysteresis phenomenon is branching; the definition of hysteresis is given by I. D. Mayergoyz [32] as following: "Consider a transducer that can be characterized by an input u(t) and an output f(t). This transducer is called a hysteresis transducer if its input-output relationship is a multi-branch nonlinearity for which branch-to-branch transitions occur after input extrema." A hysteresis system must be multistable for branching to happen, meaning the system must have multiple equilibrium points for a constant input value. The output while the input is increasing may be different than the output while the input is decreasing [3].

Hysteresis phenomenon was first discovered in magnetics, then later discovered in mechanical hysteresis, ferroelectric hysteresis, and superconductor hysteresis. Hysteresis phenomena not only exist in physics but many disciplines of science: economic systems show signs of hysteresis; cells undergoing cell division have hysteresis behavior in changing states; some neurons do not return to the original state after the removal of stimulus. Hysteresis has been widely studied and mathematical tools and models have been developed to study real life hysteresis systems [10] [32].

In I. Mayergoyz's book [32], hysteresis was categorized into two groups, the rate-independent and rate-dependent. For rate-independent hysteresis output depends on the past value of the input but not the speed of the input. Then rateindependent hysteresis was further divided into two groups, hysteresis with local memories and hysteresis with non local memories. The future output of hysteresis with local memory is uniquely determined by the current output and input. Yet, for hysteresis with non-local memories, the future output not only relies on the current input and output, but also the past extremum values of the input. In I. Mayergoyz's book, extensive studies on the mathematical models of hysteresis and their application are given.

A new concept, n-dimensional m-level multi-cell hysteresis is presented here. This new concept which is the main contribution of this dissertation has not been found in the survey of literatures. Additionally, a significant part of the research work is the CMOS implementation of the n-dimensional m-level multi-celled hysteresis. There are five chapters in the dissertation: Chapter one: Introduction. Chapter two: Binary Hysteresis Circuits, which gives a review on the past job trying to have some control on the binary hysteresis. Chapter three: CMOS Binary Hysteresis Circuits with Full Control. Chapter four: Circuits for Handling Sweeping Signals, that include analogue adders, multipliers, current voltage converters, and voltage current converters. Chapter five: CMOS Multi-Cell Hysteresis Circuit, explains the construction of multi-cell hysteresis.

#### 1.1 Multi-Celled Hysteresis

In this section, the new concept of multi-celled hysteresis is explained. We start with the more familiar concept of binary hysteresis, then proceed to construct multi-level hysteresis using binary hysteresis, and finally reach the construction of multi-celled hysteresis.

#### 1.1.1 Binary Hysteresis

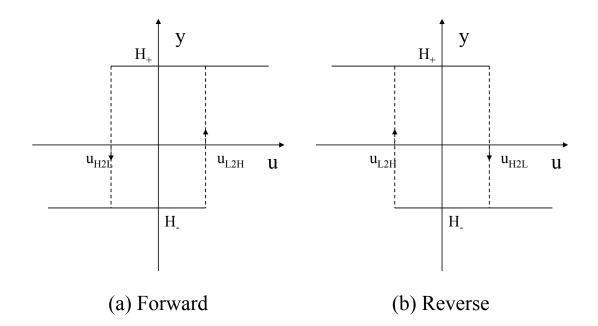

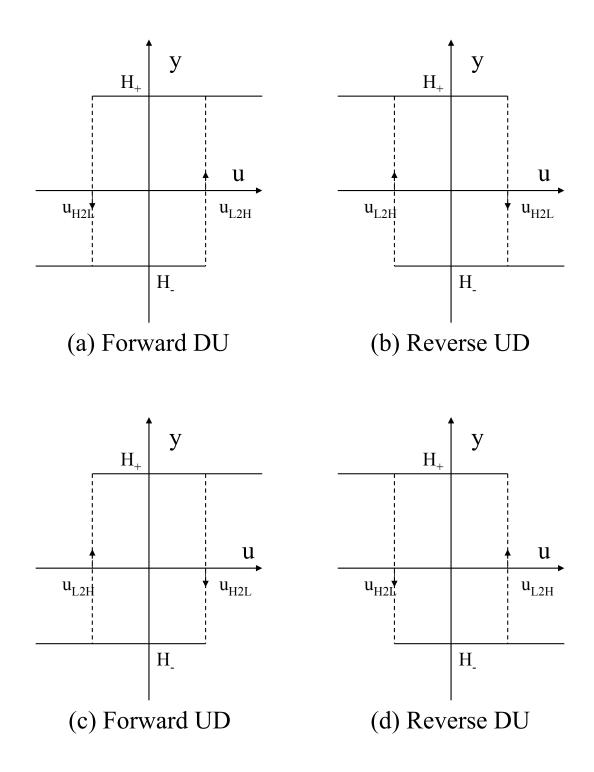

A system is said to exhibit binary hysteresis if it has different switching levels in its input-output transfer characteristics, which make the output signal snap alternately between two stable states (logic low and high). This is illustrated in the hysteresis curves shown in Figure 3.1. For different switching characteristics, binary hysteresis is categorized in two groups, forward binary hysteresis and its reverse, as shown in Figure 3.1, with u as the input and y as the output.

The mathematical description of forward binary hysteresis is contained in Equation (3.1). Here  $H_+$ ,  $H_-$ ,  $u_{H2L}$ , and  $u_{L2H}$  are real parameters characterizing the hysteresis, where  $H_- < H_+$  and  $u_{H2L} < u_{L2H}$  are assumed, and  $y_0$  is the previous value of y. The presence of  $y_0$  in Equation (3.1) ensures that the hysteresis is not multi-valued.

Figure 1.1: Binary hysteresis, (a) forward and (b) reverse.

$$y(u, y_0) = \begin{cases} H_+ & u > u_{L2H}, \text{ for any } y_0 \\ H_+ & u_{H2L} \le u \le u_{L2H}, \text{ if } y_0 = H_+ \\ H_- & u_{H2L} \le u \le u_{L2H}, \text{ if } y_0 = H_- \\ H_- & u < u_{H2L}, \text{ for any } y_0 \end{cases}$$

(1.1)

Reverse hysteresis can be described in a very similar way in Equation (3.2),

where  $H_{-} < H_{+}$  still holds as in the forward hysteresis case, yet  $u_{L2H} < u_{H2L}$ .

$$y(u, y_0) = \begin{cases} H_+ & u < u_{L2H}, \text{ for any } y_0 \\ H_+ & u_{L2H} \le u \le u_{H2L}, \text{ if } y_0 = H_+ \\ H_- & u_{L2H} \le u \le u_{H2L}, \text{ if } y_0 = H_- \\ H_- & u > u_{L2H} \end{cases}$$

(1.2)

Alternate to using  $H_-$ ,  $H_+$ ,  $u_{H2L}$ , and  $u_{L2H}$ , both forward and reverse hysteresis can be characterized by their height  $H_H$ , width  $u_W$ , center position vertically

Figure 1.2: Generation of 4-level hysteresis by adding 3 binary hysteresis. (a) Schematic. (b) 4-level hysteresis

with  $H_C$ , and horizontally with  $u_C$ , as shown in Equations (3.3).

$$H_{H} = H_{+} - H_{-}$$

$$u_{W} = |u_{H2L} - u_{L2H}|$$

$$H_{C} = (H_{+} + H_{-})/2$$

$$u_{C} = (u_{H2L} + u_{L2H})/2$$

(1.3)

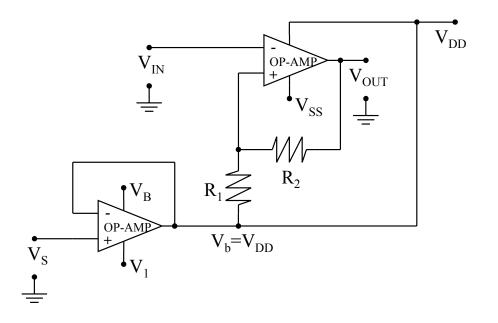

## 1.1.2 Multi-Level Hysteresis

Multi-level hysteresis can be achieved by adding several binary hysteresis curves centered at different positions. In the case where three reverse binary hysteresis curves are added together, they generate 4-level hysteresis, as shown in Figure 1.2, where there are six switching points. The output can take four values, which is why it is referred to as 4-level hysteresis. In the general case, adding (m-1) binary hysteresis generates m-level hysteresis.

#### 1.1.3 Multi-Celled Hysteresis

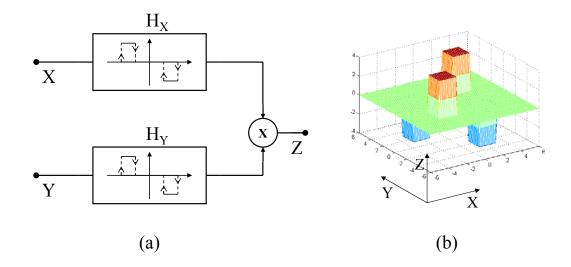

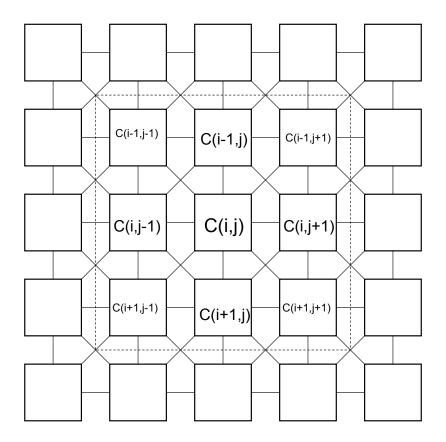

Before embarking on a discussion of the more complicated cases, we start by generating two-dimensional three-level hysteresis cubes. A circuit to generate two-dimensional three-level hysteresis cubes takes two of the three-level hysteresis circuits, as shown in Figure 5.12. The two inputs to the multiplier,  $H_X$  and  $H_Y$ , are both three-level hysteresis signals. The output Z is the product of  $H_X$  and  $H_Y$ . A three-dimensional plot of the two-dimensional three-level hysteresis cells is shown in Figure 5.12 (b). A total of four hysteresis cells are generated in the two input case. This can be generalized in two different ways, both by adding more levels of hysteresis or by increasing the dimensions of the hysteresis. If n 3-level hysteresis signals are used as inputs, then  $2^n$  hysteresis cubes can be generated. It is not difficult to see that  $(m - 1)^n$  hysteresis cubes can be generated by multiplying nm-level hysteresis signals.

### 1.2 Contributions of the dissertation

The main contributions of the dissertation are in the following areas.

- First, the new concept of multi-dimensional multi-level hysteresis is introduced.

- Second, a group of CMOS binary hysteresis circuits with full control which operate in all four quadrants is introduced. These CMOS binary hysteresis cir-

Figure 1.3: Generation of 2-dimensional 3-level hysteresis cubes. (a) Schematic. (b)3-D plot of the hysteresis cubes

cuits include the following four kinds: current-input current-output, voltageinput voltage-output, current-input voltage out, and voltage-input currentoutput. For each kind of binary hysteresis circuit, both forward and reverse hysteresis can be achieved. The position  $(u_C, H_C)$ , the width  $u_W$ , and the height  $H_H$  of each hysteresis can be adjusted independently by external current sources and/or voltage sources. Also, the hysteresis can be put in any of the four quadrants. The detailed discussions on these CMOS binary hysteresis circuits are given in Chapter three. Before that, the historical review of the past means of designing and controlling hysteresis externally are given in Chapter two.

• Thirdly, CMOS circuits, to be combined with the CMOS binary hysteresis circuits, that are also building blocks for multi-dimensional multi-level hysteresis are designed. These circuits include analogue four-quadrant adders, analogue four-quadrant multipliers, in both current and voltage mode, current voltage converters, and voltage current converters. The detailed discussions on the above circuits are given in Chapter four.

- Fourthly, CMOS circuits are designed to give various one-dimensional multilevel hysteresis, in both current mode and voltage mode. Various combinations of adding forward and reverse binary hysteresis are demonstrated. Furthermore, CMOS circuits, in both current mode and voltage mode, that give twodimensional multi-level multi-cell hysteresis are designed. Further discussion on how to extend the results to more dimensions, *n*-D, is given. These are covered in Chapter five.

- Finally, multi-cell hysteresis is suggested to be used in chaotic signal generation, as is covered in section 5.6 of Chapter five. We suggest a couple of areas that multi-cell hysteresis can be useful in Chapter six which gives summaries.

## Chapter 2

#### **Binary Hysteresis Circuits**

To construct multi-cell hysteresis, binary hysteresis circuits are the most important building blocks. In order to place hysteresis cubes at any location in the input-output space, we would like binary hysteresis circuits to possess fully controllable width, height, horizontal and vertical position of the hysteresis. In this chapter, a review of the known binary hysteresis are given.

Binary hysteresis circuits have the feature that the output transfer characteristics have different input thresholds for positive-going and negative-going input signals. The circuits also respond to a slowly changing input waveform with a fast transition time at the output. Former work on binary hysteresis circuits is presented in this Chapter in four Sections: voltage-input voltage-output, current-input voltage-output, voltage-input current-output, and current-input current-output.

If CMOS schematics of the circuits are available in any of the former works in the discussion, similar results are generated by running PSpice simulations with the schematic. MOSIS 1.2  $\mu m$  transistor models (BSIM1, Level 4, and Run n7ab) [37] are used in all the simulations. Also, since some of the names and symbols appear many times in many places, I would like to clarify the definitions and expressions of these names before further discussion. The common names and symbols used often are listed in Table 2.1.

| Symbol               | Definition                             | Expression/Value                                          |

|----------------------|----------------------------------------|-----------------------------------------------------------|

| $\varepsilon_{OX}$   | Dielectric constant of silicon dioxide | $35.1\times 10^{-18}F/\mu m$                              |

| $T_{OX}$             | Gate-oxide Thickness                   | 30.6nm *                                                  |

| $C_{OX}$             | Gate capacitance per unit area         | $C_{OX} = \varepsilon_{OX} / T_{OX}$                      |

| $\mu_n$              | Electron mobility                      | $688.4 \ cm^2/Vs^{*}$                                     |

| $\mu_p$              | Hole mobility                          | $167.4 \ cm^2/Vs$ *                                       |

| $K_N$                | NMOS transconductance parameter        | $K_N = \mu_n C_{OX}$                                      |

| $K_P$                | PMOS transconductance parameter        | $K_P = \mu_p C_{OX}$                                      |

| $W_N \& W_P$         | NMOS & PMOS channel widths             |                                                           |

| $L_N \& L_P$         | NMOS & PMOS channel lengths            |                                                           |

| $\beta_{N,P}$        |                                        | $\beta_{N,P} = \frac{K_{N,P}}{2} \frac{W_{N,P}}{L_{N,P}}$ |

| $V_{THN} \& V_{THP}$ | NMOS & PMOS threshold voltages         | 0.5666V & -0.7996V                                        |

Table 2.1: The definitions and expressions of the common names and symbols.

\* Fabrication process dependant, only valid for BSIM1, Level 4, and Run n7ab.

Since the only large signal current that can run through MOS transistors is either from drain to source for NMOS transistor, or source to drain for PMOS transistors, instead of using either  $I_{DS}$  or  $I_{SD}$ , the symbol I will be used, with substrate normally referring to the name of the transistor that the current is flowing through. For a NMOS transistor, the current can be expressed in Equation (2.1), with  $\beta_N = (K_N W_N / 2L_N)$ . The source to drain current of a PMOS transistor can be described in very similar way, in Equation (2.2),  $\beta_P = (K_P W_P / 2L_P)$ .

$$I = \begin{cases} \beta_N [2(V_{GS} - V_{THN})V_{DS} - V_{DS}^2] & \text{if } V_{GS} \ge V_{THN} \text{ and } 0 \le V_{DS} < V_{GS} - V_{THN} \\ \beta_N (V_{GS} - V_{THN})^2 & \text{if } V_{GS} \ge V_{THN} \text{ and } V_{DS} \ge V_{GS} - V_{THN} \\ 0 & V_{GS} < V_{THN} \end{cases}$$

(2.1)

$$I = \begin{cases} \beta_P [2(V_{SG} + V_{THP})V_{SD} - V_{SD}^2] & \text{if } V_{SG} \ge -V_{THP} \text{ and } 0 \le V_{SD} < V_{SG} + V_{THP} \\ \beta_P (V_{SG} + V_{THP})^2 & \text{if } V_{SG} \ge -V_{THP} \text{ and } V_{SD} \ge V_{SG} - V_{THP} \\ 0 & V_{SG} < -V_{THP} \end{cases}$$

(2.2)

## 2.1 Voltage-Input Voltage-Output Hysteresis Circuits

## 2.1.1 CMOS Schmitt Trigger

The most well known voltage-input voltage-output hysteresis circuit is probably the Schmitt trigger. The Schmitt trigger was invented in the early 20th century by O. H. Schmitt [49] using vacuum tubes for modeling neurons. The basic schematic and the transfer characteristics of a CMOS Schmitt trigger [21] are shown in Figure 2.1.

As the input increases from low to high, the output switches from high to low when the input exceeds  $V_{H2L}$ . As the input decreases, the output can switch back to high again only when the input goes below  $V_{L2H}$ . The circuit can be divided into two parts, depending on whether the output is high or low. If the output is low, then MP3 is on while MN3 is off. At this time, only the p-channel portions are

Figure 2.1: CMOS Schmitt trigger, a voltage-input voltage-output hysteresis circuit. (a) Schematic used in PSpice simulation. (b) Simulated transfer characteristics, reverse hysteresis.  $V_{DD} = 5V$  and  $V_{SS} = 0V$ .

considered in calculating the switching point voltage. If the output is high, then MN3 is on and MP3 is off and only the n-channel portions are considered. With the given  $V_{H2L}$  and  $V_{L2H}$ , the transistor sizes of MN1, MN3, MP1 and MP3 can be decided by Equations (2.3) and (2.4), if  $V_{SS}$  is grounded [2].

$$\frac{\beta_{MN1}}{\beta_{MN2}} = \left[\frac{V_{DD} - V_{H2L}}{V_{H2L} - V_{THN}}\right]^2$$

(2.3)

$$\frac{\beta_{MP1}}{\beta_{MP2}} = \left[\frac{V_{L2H}}{V_{DD} - V_{L2H} - V_{THP}}\right]^2 \tag{2.4}$$

Therefore, we can rearrange Equations (2.3) and (2.4) to solve for switching voltage  $V_{H2L}$  and  $V_{L2H}$  in term of the transistor parameters, as shown in Equations (2.5) and (2.6).

$$V_{H2L} = \frac{V_{DD} + \sqrt{\frac{\beta_{MN1}}{\beta_{MN2}}} \cdot V_{THN}}{1 + \sqrt{\frac{\beta_{MN1}}{\beta_{MN2}}}} = \frac{V_{DD} - V_{THN}}{1 + \sqrt{\frac{\beta_{MN1}}{\beta_{MN2}}}} + V_{THN}$$

(2.5)

$$V_{L2H} = \frac{V_{DD} - V_{THP}}{1 + \sqrt{\frac{\beta_{MP1}}{\beta_{MP2}}}}$$

(2.6)

Equations (2.5) and (2.6) describe the instantaneous switching points of the Schmitt trigger. Detailed study of the transient behavior from one stable state to another can be found in I. M. Filanovsky and H. Baltes's discussions on Schmitt trigger design [14]. For the Schmitt trigger circuit shown in Figure 2.1, the switching voltages and the 2-level output voltages are decided by the transistor parameters and the bias voltages  $V_{DD}$  and  $V_{SS}$ . In other words, the parameters of the hysteresis can not be adjusted externally, except by power supply adjustment, after the design of the circuit is finished.

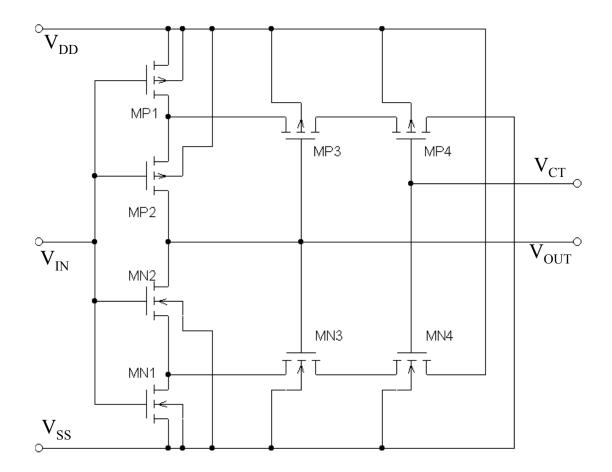

### 2.1.2 Pfister's Schmitt Trigger

There is a slight variation of the Schmitt trigger, due to A. Pfister [41], shown in Figure 2.2. With an additional pair of transistors, MN4 and MP4, at the output stage, the switching voltages of the hysteresis can be adjusted externally by the control voltage, $V_{CT}$ , although the variation is not over a very wide range. One can also notice that the switching from low to high and high to low can not be adjusted independently. There is no control on the output high and output low. The simulation results of Pfister's Schmitt trigger are shown in Figure 2.3.

Figure 2.2: Pfister's CMOS adjustable Schmitt trigger [41], with external voltage control.

Figure 2.3: Pfister's CMOS adjustable Schmitt trigger [41], with external voltage control simulation results.  $V_{DD} = 5V$  and  $V_{SS} = 0V$ . (a) $V_{CT} = 0V$ . (b) $V_{CT} = 5V$ . 2.1.3 Kim's Adjustable Hysteresis Using Operational Transconduc-

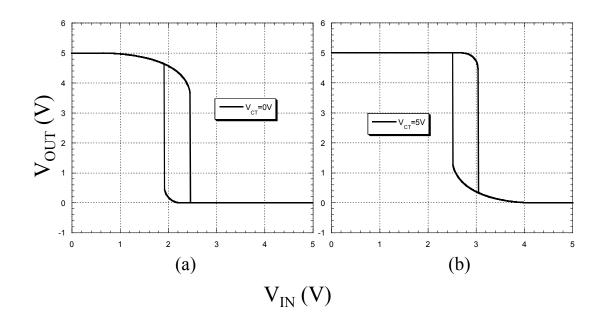

## tance Amplifier

A Schmitt trigger claimed to have fully adjustable hysteresis was implemented using an operational transconductance amplifier (OTA) by K. Kim [23] to give reversed hysteresis. The circuit configuration and the transfer characteristics of Kim's Schmitt trigger are shown in Figure 2.4. The transfer characteristics are directly grabbed from Kim's paper. The two-level output voltages  $V_+$  and  $V_-$  are linearly controlled by the bias current  $I_{B1}$  simultaneously. The switching threshold voltages  $V_{H2L}$  and  $V_{L2H}$  are linearly controlled by a different bias current,  $I_{B2}$ , also simultaneously. For this hysteresis circuit, the height and width of the hysteresis can be adjusted but the position of the hysteresis is fixed, to be symmetric about

Figure 2.4: Kim's adjustable hysteresis using operational transconductance amplifier[23]. (a)Circuit configuration. (b)Transfer characteristic.

the origin. Therefore, Kim's Schmitt trigger is not really fully adjustable.

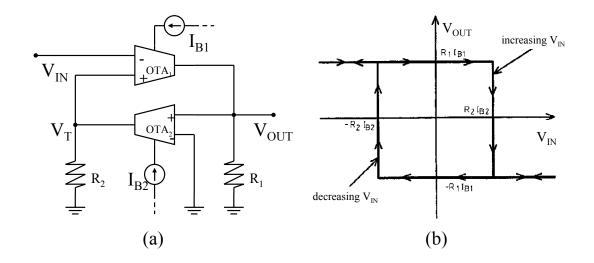

## 2.1.4 Adjustable Hysteresis Using Operational Amplifier

Semistate design theory has been used in the design of hysteresis by R. W. Newcomb [36] to achieve swept binary hysteresis by using operational amplifiers, as shown in Figure 2.5. The hysteresis parameter can be adjusted by the bias voltages  $V_S$  and  $V_B$ . One example of Newcomb's experimental swept hysteresis results are shown in Figure 2.6.

Newcomb's hysteresis has partial tunability, but it is not in CMOS VLSI design.

Figure 2.5: Newcomb's swept hysteresis hysteresis realization circuits [36].

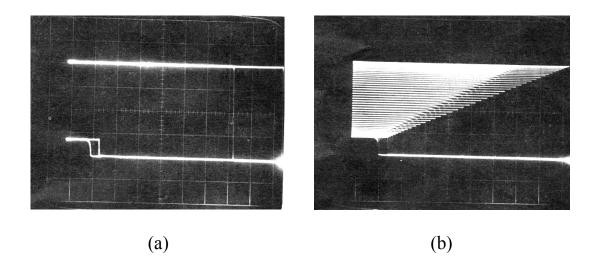

Figure 2.6: Newcomb's experimental swept hysteresis results [36]. (a)  $V_S$  is a square wave. (b)  $V_S$  is a sine wave.

## 2.1.5 Summary

A comparison of the above voltage-input voltage-output hysteresis circuits is given in Table 2.2. None of the listed circuits give complete control of the hysteresis height, width, and position.

|                    | Hysteresis | Horizontal | Vertical |

|--------------------|------------|------------|----------|

| CMOS Schmitt [21]  | Reverse    | None       | None     |

| Pfister's [41]     | Reverse    | Limited    | None     |

| Kim's OTA-R [23]   | Reverse    | Limited    | Limited  |

| Newcomb Swept [36] | Reverse    | Limited    | Limited  |

Table 2.2: Comparison of the voltage-input voltage-output binary hysteresis circuits.

## 2.2 Current-Input Voltage-Output Hysteresis Circuits

Current-input voltage-output hysteresis circuits take currents as inputs and produce voltage as outputs. Often current-input voltage-output hysteresis circuits are referred to as current Schmitt triggers in the literature ([29], [59], and [60]), although they do not operate completely in the current domain. Current-input Schmitt triggers are particularly useful in photodetectors, barcode readers, and optical remote controls.

Figure 2.7: Liao's CMOS current-input voltage-output hysteresis circuit. [29]. (a) Schematic used in PSpice simulation. (b) Simulated transfer characteristic, forward hysteresis.  $V_{DD} = 5V$  and  $V_{SS} = 0V$ .

#### 2.2.1 Liao's CMOS Current-Input Voltage-Output Hysteresis Circuit