**ABSTRACT**

Title of Document: LOW NOISE

PRE-AMPLIFIER/AMPLIFIER CHAIN FOR

HIGH CAPACITANCE SENSORS.

Sanaz Adl, Ph.D., 2007

Directed By: Professor, Martin Peckerar, Electrical and

Computer Engineering

In the past two decades, imaging sensors and detectors have developed tremendously. This technology has found its way into a number of areas, such as space missions, synchrotron light sources, and medical imaging. Nowadays, detectors and custom ICs are routine in high-energy physics applications. Electronic readout circuits have become a key part of every modern detector system. Many sensing circuits in detectors depend upon accumulating charge on a capacitor. The charge uncertainty on the capacitor when it is reset causes a signal error known as reset noise. Therefore, low noise readout circuitry capable of driving high input capacitance is essential for detector systems.

A low noise pre-amplifier/amplifier readout circuitry has been designed and fabricated in 0.13  $\mu m$  IBM CMOS8RF process technology. The pre-amplifier/amplifier chain employs correlated double sampling at the input to suppress the kTC noise without any additional circuitry. In order to increase the signal-to-noise ratio,

capacitive matching is used at the amplifier input. The experimental results of the signal processing chain employing capacitive matching and correlated double sampling show more than 60 times improvement in the signal-to-noise ratio over the same circuit without these improvements.

In this dissertation a novel auto-zeroing technique is introduced as well. This technique uses a nulling point other than the amplifier's input and output to perform the auto-zeroing operation. The auto-zeroing is performed by taking advantage of emitter degeneration in the input transistor pair of the differential pair. For testing purposes this technique is implemented on a telescopic cascode differential amplifier. The auto-zeroed telescopic cascode differential amplifier has also been designed and fabricated in  $0.13 \,\mu m$  IBM CMOS8RF process technology. This auto-zeroing technique reduces the input referred offset noise by an order of magnitude.

# LOW NOISE PRE-AMPLIFIER/AMPLIFIER CHAIN FOR HIGH CAPACITANCE SENSORS.

By

Sanaz Adl

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Ph.D.

2007

Advisory Committee: Professor Martin Peckerar, Chair Pamela Abshire Aris Christou Timothy Horiuchi Kristine Rosfjord © Copyright by Sanaz Adl 2007

# Dedication

To my parents for their unconditional love

## Acknowledgements

I would like to thank my advisor, Professor Martin Peckerar, for his guidance and support during the past three years. His understanding, flexibility, and vision have been truly inspiring. Professor Peckerar allowed me to work independently and explore different ideas, but at the same time he was always available for discussing problems and providing me with valuable insights.

I would also like to thank Professors Pamela Abshire, Aris Christou, Timothy Horiuchi, and Kristin Rosfjord for being on my committee and for providing me with valuable suggestions during my study.

I would like to thank NASA Goddard Space Flight Center for providing the financial assistance for my research.

My warmest thanks go to my colleagues and my friends at UMD and at the ADSL lab at the ECE department. In particular, I would like to convey my gratitude to my friends, Jimmy Wienke, Yves Ngu, and Jeff Allnut. I will deeply miss the long nontechnical and technical conversations with them inside and outside the lab during the past three years. I would like to thank Robert Nagele from the Naval Research Laboratory for providing me with some of the test equipment.

Last but not least, I would like to give my deepest thanks to my parents and my brother for their unconditional love, support, and their belief in me. Certainly, this thesis would have not been possible without their support. I am grateful to my parents, Iraj Adl and Parivash Haeri, for their support and their sacrifice that has helped me reach to this stage. My father's perfectionism and my mother's encouragement has been always a great motivation for me. I thank my brother,

Ahmad Hossein, for his unlimited kindness. I dedicate this thesis to my family as an inadequate but sincere expression of appreciation and love.

# Table of Contents

| Dedication                                                               | ii    |

|--------------------------------------------------------------------------|-------|

| Acknowledgements                                                         | iii   |

| Table of Contents                                                        | v     |

| List of Tables                                                           | vii   |

| List of Figures                                                          | viii  |

| Chapter 1: Introduction                                                  | 1     |

| Chapter 2: Review of VLSI Read out in Detector Systems                   | 4     |

| 2.1 Introduction                                                         |       |

| 2.2 Signal Processing Chain in Radiation Detector Systems                | 4     |

| 2.2.1 Pre-amplifier/Amplifier                                            | 5     |

| 2.2.2 Pulse Shaper                                                       | 8     |

| Chapter 3: Amplifier Architectures                                       | 12    |

| 3.1 Telescopic Cascode Differential Amplifier                            | 12    |

| 3.2 Folded Cascode Differential Amplifier                                | 15    |

| 3.3 Introduction to the concept of Gain Boosting                         |       |

| 3.3.1 Folded Cascode Gain Boosted Amplifier                              | 24    |

| 3.4 Common Mode feedback                                                 |       |

| Chapter 4: Offset                                                        | 34    |

| 4.1 Introduction                                                         | 34    |

| 4.2 DC Offset                                                            | 35    |

| 4.3 Offset Reduction Techniques                                          | 39    |

| 4.3.1 Auto-zeroing and Correlated Double Sampling                        | 39    |

| 4.3.2 Correlated Double Sampling                                         |       |

| 4.3.3 The Chopper Stabilization Technique                                |       |

| 4.4 Implementation Issues and Challenges                                 | 44    |

| 4.4.1 Switches and Their Non-ideal Effects                               | 45    |

| 4.4.2 The Open Loop Offset Cancellation Technique                        | 49    |

| 4.4.3 The Closed-Loop Offset Cancellation Technique                      | 51    |

| 4.4.4 Multistage Offset Storage                                          |       |

| 4.4.5 Closed-Loop Offset Compensation Using an Auxiliary Offset Storage  | 56    |

| 4.4.6 Continuous-Time Auto-zeroing Amplifiers                            |       |

| 4.5 A Novel Auto-zeroing Technique Using Emitter Degeneration            | 73    |

| 4.5.1 Description                                                        | 74    |

| 4.5.2 Simulation Results                                                 | 76    |

| 4.5.3 Experimental Results                                               | 91    |

| 4.5.3.1 Telescopic Cascode Differential Amplifier                        | 91    |

| 4.5.3.2 Telescopic Cascode Amplifier with the Emitter Degeneration Auto- | -     |

| zeroing Technique                                                        | 98    |

| 4.5.3.3 Comparison                                                       | . 106 |

| Chapter 5: Noise Sources in Detector Sensors                             | . 111 |

| 5.1 Introduction                                                         | . 111 |

| 5.2 Noise Sources in Integrated Circuits                                 | 111   |

| 5.2.1 Thermal Noise                                                        | 111    |

|----------------------------------------------------------------------------|--------|

| 5.2.2 Shot Noise                                                           | 112    |

| 5.2.3 Flicker Noise                                                        | 114    |

| 5.2.4 Burst Noise                                                          | 115    |

| 5.2.5 Avalanche Noise                                                      |        |

| 5.3 Noise Models of Integrated Circuits                                    | 117    |

| 5.3.1 Junction Diodes                                                      |        |

| 5.3.2 MOS Transistors                                                      | 118    |

| 5.3.3 Bipolar Junction Transistors                                         | 119    |

| 5.3.4 Resistors                                                            | 120    |

| 5.3.5 Capacitors and Inductors                                             |        |

| 5.4 Noise Analysis in Detector Circuits                                    | 121    |

| 5.4.1 Noise Contributions                                                  | 122    |

| 5.4.1.1 Detector Leakage Current                                           | 122    |

| 5.4.1.2 Parallel Resistance                                                | 124    |

| 5.4.1.3 Series Resistance                                                  |        |

| 5.4.1.4 Amplifier Input Noise                                              | 125    |

| 5.5 Equivalent Noise Charge in the Detector Front End                      | 126    |

| 5.6 Effect of Feedback on Noise Performance                                | 128    |

| Chapter 6: Review of Previously Proposed Techniques for Noise Reduction in |        |

| Sensor Arrays                                                              | 132    |

| 6.1 Introduction                                                           | 132    |

| 6.2 Capacitive Control                                                     | 132    |

| 6.3 Bandwidth Control                                                      | 140    |

| 6.4 Charge Control                                                         | 145    |

| 6.5 Low Noise Pre-amplifier/Amplifier Chain                                |        |

| Chapter 7: A Novel Noise Reduction Technique for High Capacitance Sensor A | Arrays |

|                                                                            | 153    |

| 7.1 Introduction                                                           |        |

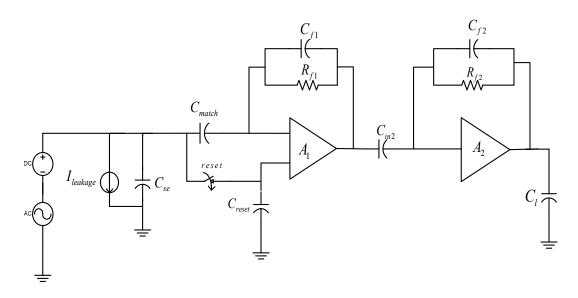

| 7.2 Pre-amplifier/Amplifier Readout Circuitry                              | 155    |

| 7.3 Simulation Results                                                     | 159    |

| 7.4 Experiment Results                                                     |        |

| Chapter 8: Conclusion                                                      | 186    |

| Bibliography                                                               | 190    |

# List of Tables

| ΓABLE 1: TRANSISTOR PARAMETERS FOR THE DIFFERENTIAL TELESCOPIC CASCOD | E   |

|-----------------------------------------------------------------------|-----|

| AMPLIFIER IN FIGURE 47                                                | 78  |

| ΓABLE 2: TRANSISTOR PARAMETERS FOR THE AUTO-ZEROED DIFFERENTIAL       |     |

| TELESCOPIC CASCODE AMPLIFIER IN FIGURE 52                             | 82  |

| ΓABLE 3: CAPACITIVE CONTROL TECHNIQUE CIRCUIT PARAMETERS [41]         | 139 |

| FABLE 4: SIMULATION PARAMETERS FOR THE BANDWIDTH CONTROL TECHNIQUE    |     |

| CIRCUIT [41]                                                          | 144 |

| FABLE 5: COMPONENT PARAMETERS FOR THE CHARGE CONTROL CIRCUIT [41]     | 149 |

| ΓABLE 6: AMPLIFIER CIRCUIT PARMETERS                                  | 157 |

| ΓABLE 7: SUMMARY AND COMPARISON FOR THE LOW NOISE PRE-                |     |

| AMPLIFIER/AMPLIFIER CHAIN                                             | 188 |

| ΓABLE 8: AUTO-ZEROING TECHNIQUE SUMMARY                               | 189 |

# List of Figures

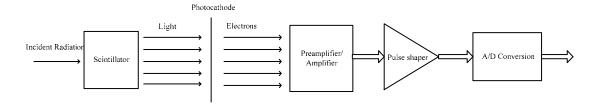

| FIGURE 1: DETECTOR SIGNAL PROCESSING CHAIN                                                                           | 5            |

|----------------------------------------------------------------------------------------------------------------------|--------------|

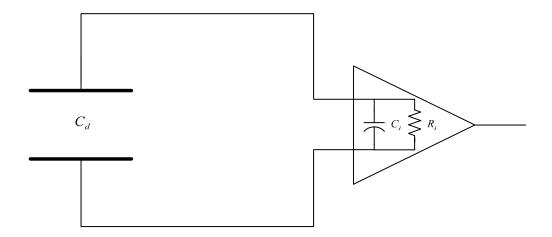

| FIGURE 2: AMPLIFIER AND DETECTOR BLOCK DIAGRAM                                                                       | 5            |

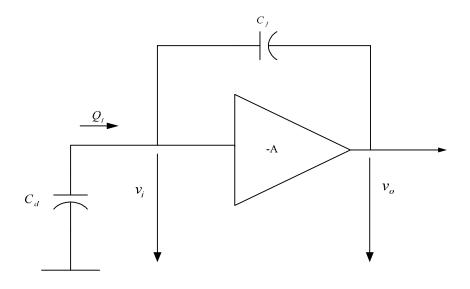

| FIGURE 3: CHARGE SENSITIVE AMPLIFIER CONFIGURATION                                                                   | 6            |

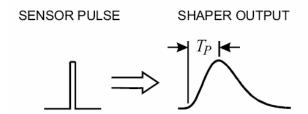

| FIGURE 4: INPUT AND OUTPUT WAVEFORMS OF THE PULSE SHAPER [3]                                                         | 8            |

| FIGURE 5: A SIMPLE PULSE SHAPER USING CR DIFFERENTIATOR AS A HIGH PASS                                               |              |

| FILTER AND A RC INTEGRATOR AS A LOW PASS FILTER                                                                      | 9            |

| FIGURE 6: PULSE SHAPER OUTPUT VS. NUMBER OF INTEGRATORS [3]                                                          |              |

| FIGURE 7: CORRELATED DOUBLE SAMPLING PULSE SHAPER                                                                    |              |

| FIGURE 8: SIMPLE DIFFERENTIAL AMPLIFIER                                                                              |              |

| FIGURE 9: TELESCOPIC CASCODE OPERATIONAL AMPLIFIER                                                                   |              |

| FIGURE 10: TRANSFORMATION OF A TELESCOPIC CASCODE WITH NMOS INPUT TO                                                 |              |

| FOLDED CASCODE                                                                                                       | 15           |

| FIGURE 11: TRANSFORMATION OF A TELESCOPIC CASCODE WITH PMOS INPUT TO A                                               |              |

| FOLDED CASCODE                                                                                                       | 15           |

| FIGURE 12: (A) TELESCOPIC CASCODE OPERATIONAL AMPLIFIER (B) FOLDED CASC                                              |              |

| OPERATIONAL AMPLIFIER                                                                                                |              |

| FIGURE 13: FOLDED CASCODE DIFFERENTIAL AMPLIFIER                                                                     | 17           |

| FIGURE 14: THE EQUIVALENT HALF CIRCUIT FOR THE FOLDED CASCODE                                                        |              |

| DIFFERENTIAL AMPLIFIER                                                                                               | 18           |

| FIGURE 15: HALF CIRCUIT OF THE FOLDED CASCODE DIFFERENTIAL AMPLIFIER US                                              |              |

| TO CALCULATE THE TRANSCONDUCTANCE                                                                                    | 18           |

| FIGURE 16: EQUIVALENT HALF CIRCUIT USED TO CALCULATE THE OVERALL                                                     |              |

| TRANSCONDUCTANCE                                                                                                     | 19           |

| FIGURE 17: EQUIVALENT HALF CIRCUITS USED TO CALCULATE THE OUTPUT                                                     |              |

| RESISTANCE                                                                                                           |              |

| FIGURE 18: (A) GAIN BOOSTED CASCODE AMPLIFIER (B) SMALL SIGNAL MODEL FO                                              |              |

| THE GAIN BOOSTED CASCODE USED TO FIND THE OUTPUT RESISTANCE                                                          |              |

| FIGURE 19: (A) GAIN BOOSTED CASCODE CIRCUIT (B) SMALL SIGNAL EQUIVALENT                                              |              |

| CIRCUIT TO CALCULATE THE OVERALL TRANS-CONDUCTANCE                                                                   | 22           |

| FIGURE 20: GAIN BOOSTING TECHNIQUE APPLIED TO A FOLDED CASCODE                                                       | 2.5          |

| DIFFERENTIAL AMPLIFIER                                                                                               |              |

| FIGURE 21: SINGLE-ENDED GAIN BOOSTING AMPLIFIERS REPLACED BY DIFFERENT                                               |              |

| COUNTERPARTS                                                                                                         |              |

| FIGURE 22: FULLY DIFFERENTIAL AMPLIFIER                                                                              |              |

| FIGURE 23: PMOS BOOSTER SCHEMATIC                                                                                    |              |

| FIGURE 24: COMMON MODE FEEDBACK CIRCUIT APPLIED TO A SIMPLE DIFFERENT                                                |              |

| AMPLIFIERFIGURE 25: COMMON MODE FEEDBACK CIRCUIT REALIZED USING TWO RESISTORS                                        |              |

| FIGURE 26: COMMON MODE FEEDBACK REALIZED BY TWO NMOS TRANSISTORS                                                     |              |

| FIGURE 27: SIMPLE DIFFERENTIAL AMPLIFIER                                                                             |              |

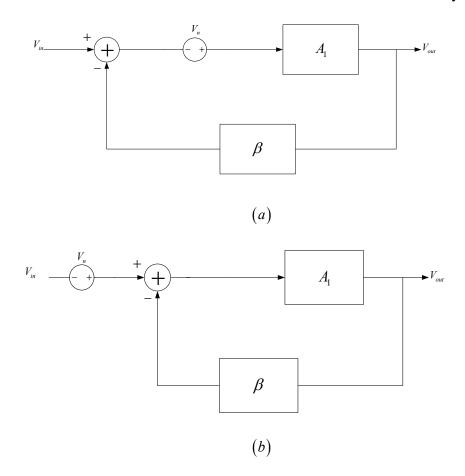

| FIGURE 28: AUTO-ZEROING TECHNIQUE                                                                                    |              |

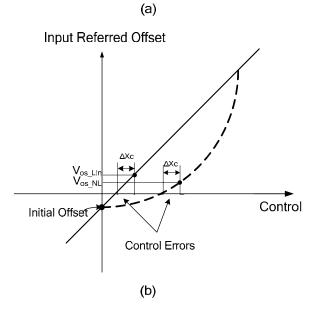

| FIGURE 29: INPUT REFERRED OFFSET VS. THE CONTROL VARIABLE (A) LARGE INIT                                             | 40<br>11 A I |

| OFFSET (B) SMALL INITIAL OFFSET                                                                                      |              |

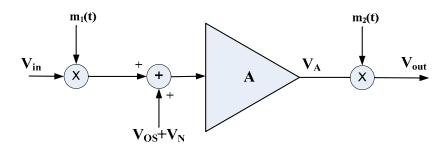

| FIGURE 30: THE CHOPPER STABILIZATION TECHNIQUE                                                                       |              |

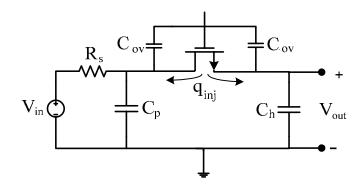

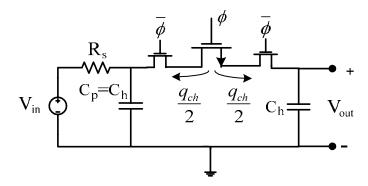

| FIGURE 31: SAMPLE AND HOLD CIRCUIT USED IN AUTO-ZEROING TECHNIQUES                                                   |              |

|                                                                                                                      |              |

| FIGURE 32: SAMPLE AND HOLD CIRCUIT WITH EQUAL CAPACITORS ( $C_{\scriptscriptstyle p}=C_{\scriptscriptstyle h}$ ) ANI |              |

| HALF-SIZED DUMMY SWITCHES                                                                                            |              |

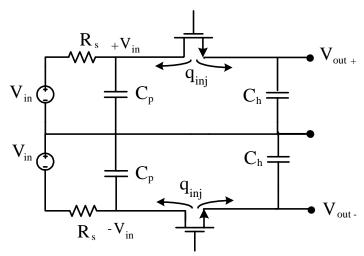

| FIGURE 33: FULLY DIFFERENTIAL STRUCTURE TO CANCEL THE CHARGE INJECTION                                               |              |

| EFFECTS                                                                                                              |              |

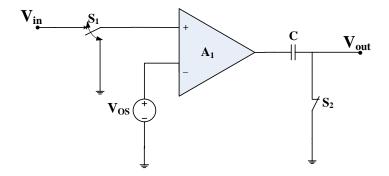

| FIGURE 34: OPEN LOOP OFFSET CANCELL ATION TECHNIQUE                                                                  | 40           |

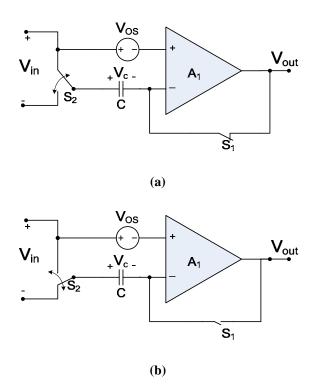

| FIGURE 35: CLOSED LOOP OFFSET CANCELLATION (A) AUTO-ZEROING PHASE (B)                                                    |              |

|--------------------------------------------------------------------------------------------------------------------------|--------------|

| AMPLIFICATION PHASE                                                                                                      | . 51         |

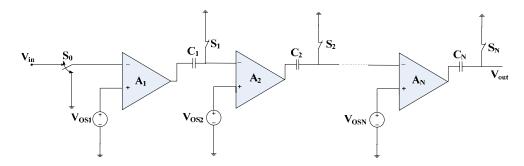

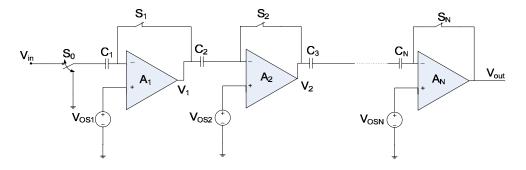

| FIGURE 36: MULTISTAGE OFFSET CANCELLATION USING OPEN-LOOP OFFSET REDUTION IN EACH STAGE                                  | . 53         |

| FIGURE 37: MULTISTAGE OFFSET CANCELLATION USING CLOSED-LOOP OFFSET                                                       |              |

| REDUCTION IN EACH STAGE                                                                                                  | . 53         |

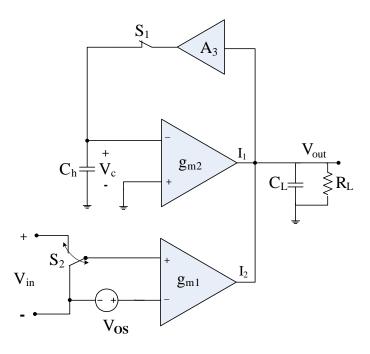

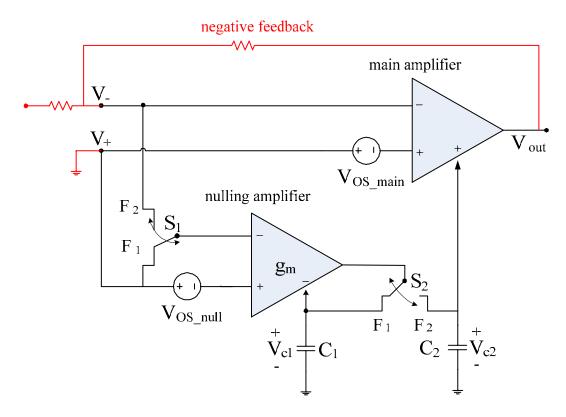

| FIGURE 38: OFFSET REDUCTION USING AN ADDITIONAL AUXILIARY POINT                                                          | . 57         |

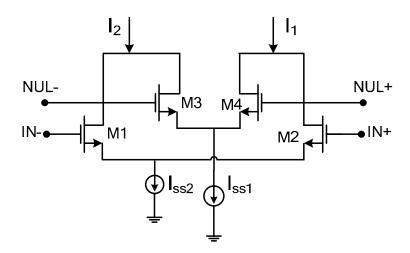

| FIGURE 39: A SIMPLE REALIZATION OF A NULLING POINT IN A DIFFERENTIAL                                                     |              |

| AMPLIFIER                                                                                                                | . 61         |

| FIGURE 40: ACTUAL REALIZATION OF A NULLING POINT IN THE DIFFERENTIAL                                                     |              |

| AMPLIFIER                                                                                                                | . 62         |

| FIGURE 41: REALIZING THE INTERMEDIATE NULLING POINT FOR AUTO-ZEROING                                                     |              |

| USING A CURRENT MIRROR                                                                                                   |              |

| FIGURE 42: CURRENT MIRROR SCHEMATIC                                                                                      |              |

| FIGURE 43: CURRENT MIRROR: LOAD RESISTORS REPLACED WITH TRANSISTOR                                                       |              |

| FIGURE 44: CURRENT MIRROR CURRENT CHANGE VS. THE NULLING VOLTAGE                                                         |              |

| FIGURE 45: CONTINUOUS-TIME AUTO-ZEROING AMPLIFIER                                                                        |              |

| FIGURE 46: AUTO-ZEROING TECHNIQUE USING EMITTER DEGENERATED RESISTORS                                                    |              |

| FOR OFFSET CANCELLATION                                                                                                  | . 74         |

| FIGURE 47: DIFFERENTIAL TELESCOPIC CASCODE AMPLIFIER WITHOUT THE AUTO-                                                   |              |

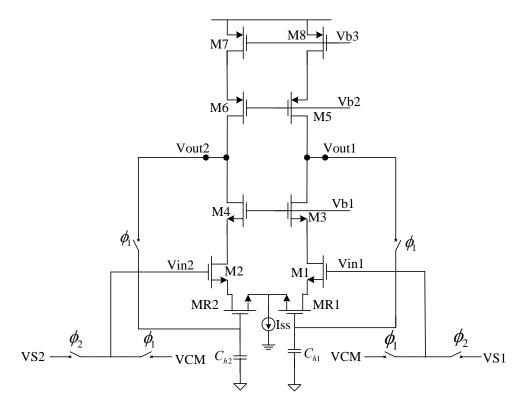

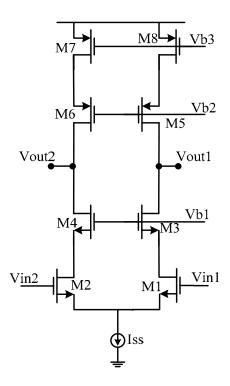

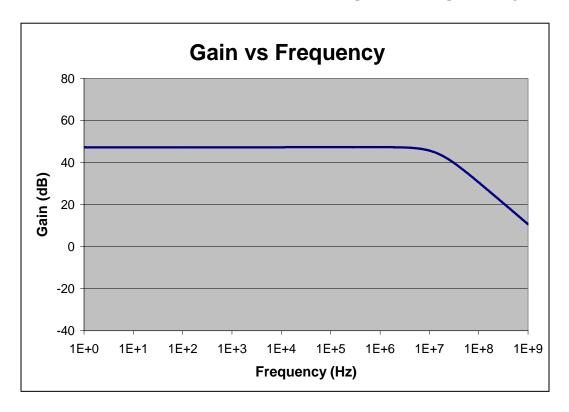

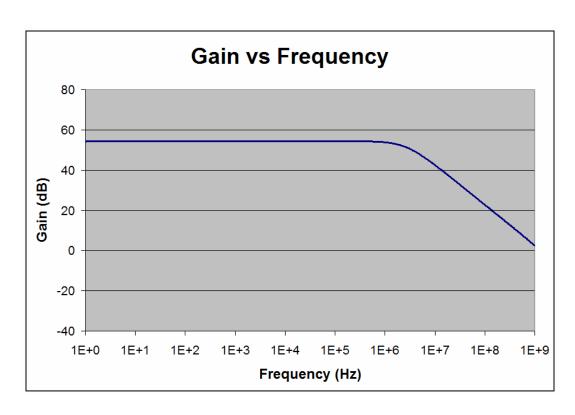

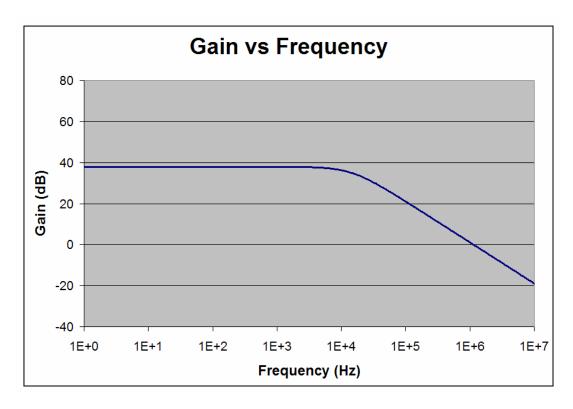

| ZEROING TECHNIQUEFIGURE 48: GAIN VS. FREQUENCY FOR THE TELESCOPIC CASCODE AMPLIFIER IN                                   | . 77         |

| FIGURE 48: GAIN VS. FREQUENCY FOR THE TELESCOPIC CASCODE AMPLIFIER IN                                                    |              |

| FIGURE 47                                                                                                                | . 78         |

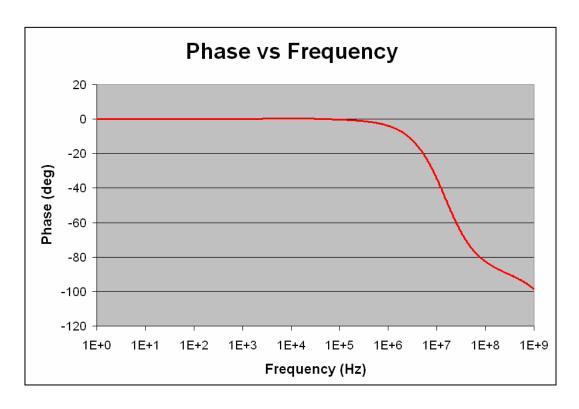

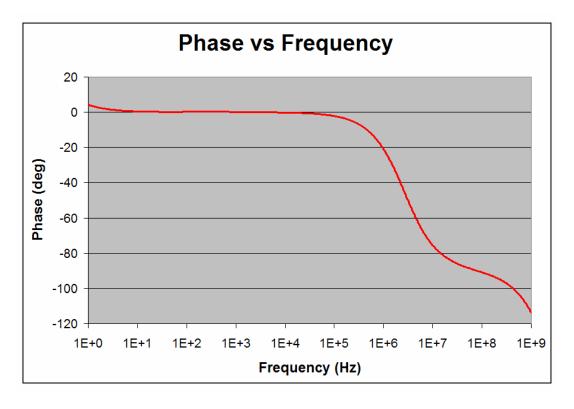

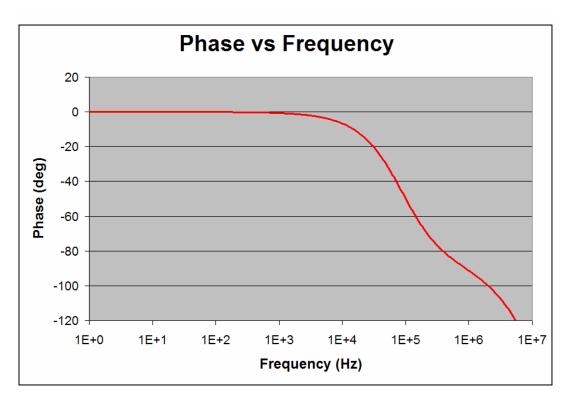

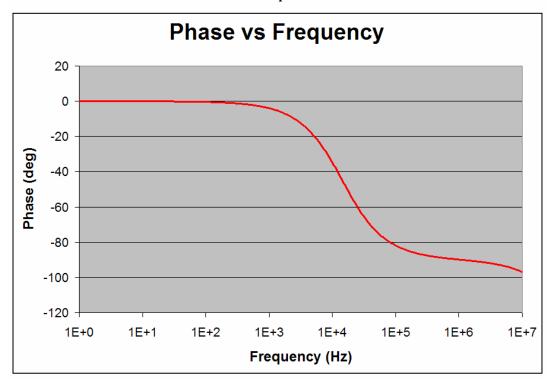

| FIGURE 49: PHASE VS. FREQUENCY FOR THE TELESCOPIC CASCODE AMPLIFIER IN                                                   |              |

| FIGURE 47                                                                                                                | . 79         |

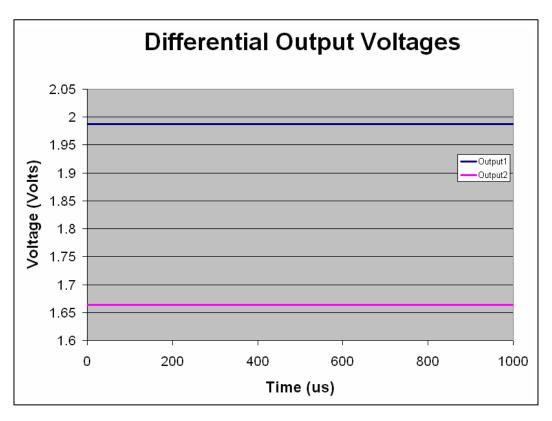

| FIGURE 50: SIMULATED DIFFERENTIAL DC OUTPUT VOLTAGES OF THE TELESCOPIC                                                   | 0.0          |

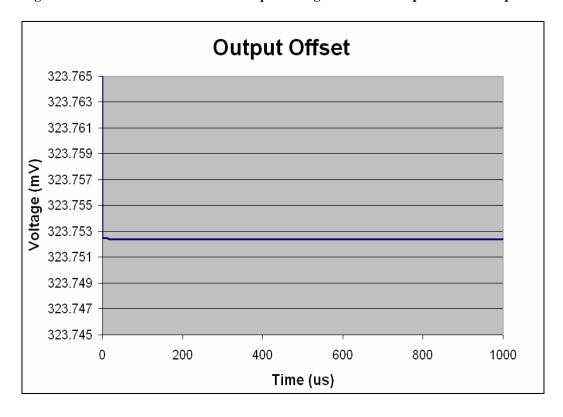

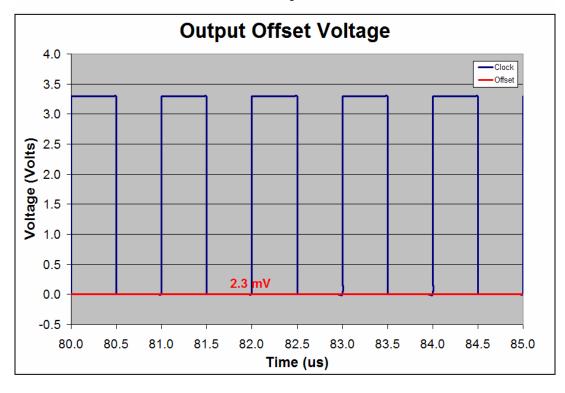

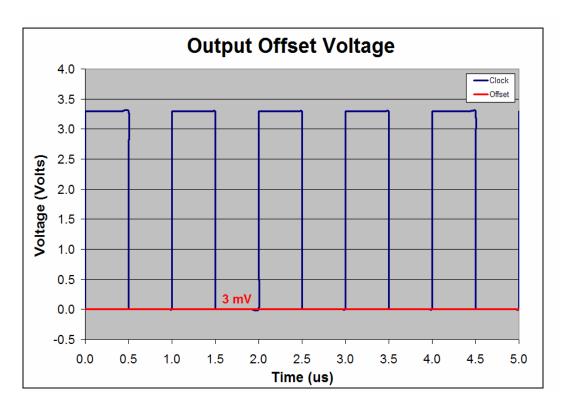

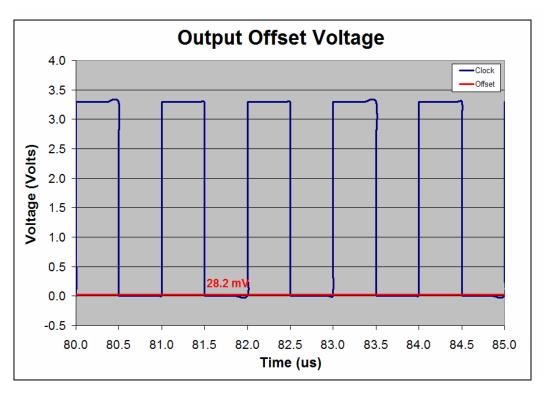

| CASCODE AMPLIFIERFIGURE 51: SIMULATED OUTPUT OFFSET VOLTAGE FOR THE TELESCOPIC CASCODE                                   | . 80         |

| DIFFERENTIAL AMPLIFIER                                                                                                   | 90           |

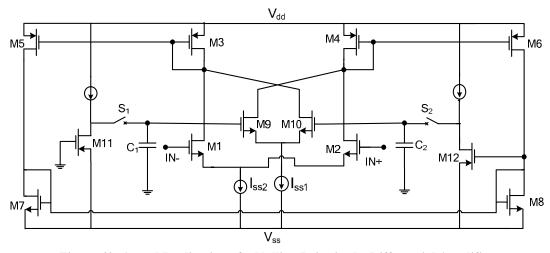

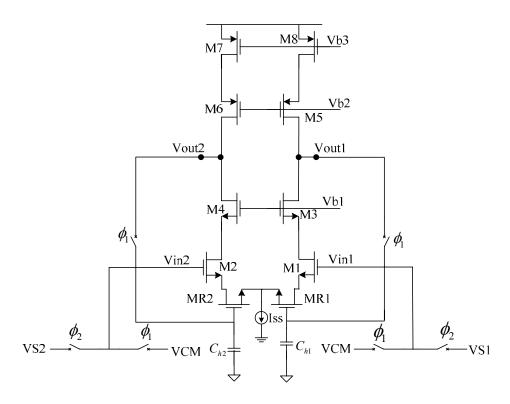

| FIGURE 52: TELESCOPIC CASCODE AMPLIFIER WITH THE EMITTER DEGENERATION                                                    | . 00         |

| AUTO-ZEROING TECHNIQUE                                                                                                   | 82           |

| FIGURE 53: GAIN VS. FREQUENCY FOR THE AUTO-ZEROED TELESCOPIC CASCODE                                                     | . 02         |

| DIFFERENTIAL AMPLIFIER                                                                                                   | 83           |

| FIGURE 54: PHASE VS. FREQUENCY FOR THE AUTO-ZEROED TELESCOPIC CASCODE                                                    | . 02         |

| DIFFERENTIAL AMPLIFIER                                                                                                   | . 83         |

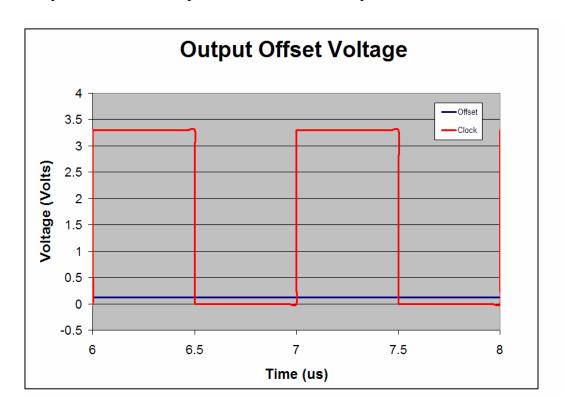

| FIGURE 55: SIMULATED OUTPUT OFFSET VOLTAGE AND CLOCK SIGNAL FOR THE                                                      |              |

| AUTO-ZEROED TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER SHOWN IN                                                           |              |

| FIGURE 52                                                                                                                | . 84         |

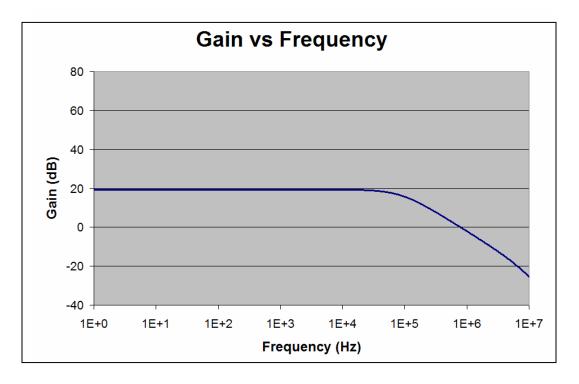

| FIGURE 56: GAIN VS. FREQUENCY FOR THE AUTO-ZEROED TELESCOPIC CASCODE                                                     |              |

| DIFFERENTIAL AMPLIFIER WITH A CLOSED LOOP GAIN OF 10V/V                                                                  | . 85         |

| FIGURE 57: PHASE VS. FREQUENCY FOR THE AUTO-ZEROED TELESCOPIC CASCODE                                                    |              |

| DIFFERENTIAL AMPLIFIER WITH A CLOSED LOOP GAIN OF 10V/V                                                                  | . 86         |

| FIGURE 58: SIMULATED OUTPUT OFFSET VOLTAGE FOR THE AUTO-ZEROED                                                           |              |

| TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A FEEDBACK                                                                |              |

| CONFIGURATION OF 10K/100K                                                                                                | . 86         |

| FIGURE 59: SIMULATED OUTPUT OFFSET VOLTAGE FOR THE AUTO-ZEROED                                                           |              |

| TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A FEEDBACK                                                                |              |

| CONFIGURATION OF 1M/10M                                                                                                  | . 87         |

| FIGURE 60: GAIN VS. FREQUENCY FOR THE AUTO-ZEROED TELESCOPIC CASCODE                                                     | 0.0          |

| DIFFERENTIAL AMPLIFIER WITH A CLOSED LOOP GAIN OF 100V/V                                                                 | . 88         |

| FIGURE 61: PHASE VS. FREQUENCY FOR THE AUTO-ZEROED TELESCOPIC CASCODE                                                    | 0.0          |

| DIFFERENTIAL AMPLIFIER WITH A CLOSED LOOP GAIN OF 100V/V                                                                 | . 88         |

| FIGURE 62: SIMULATED OUTPUT OFFSET VOLTAGE FOR THE AUTO-ZEROED TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A FEEDBACK |              |

| CONFIGURATION OF 10K/1M                                                                                                  | ٩ſ           |

| COLITIOUMTHOU OF TORVIEW                                                                                                 | . <i>)</i> ( |

| FIGURE 63: SIMULATED OUTPUT OFFSET VOLTAGE FOR THE AUTO-ZEROED          |     |

|-------------------------------------------------------------------------|-----|

| TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A FEEDBACK               |     |

| CONFIGURATION OF 100K/10M                                               | 90  |

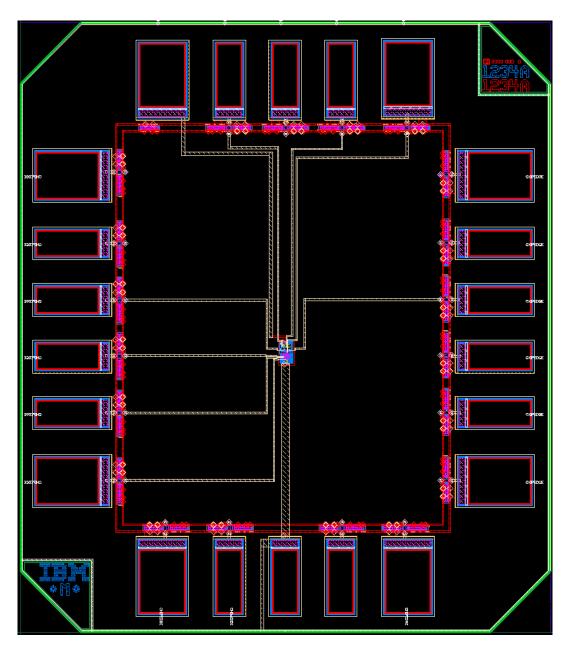

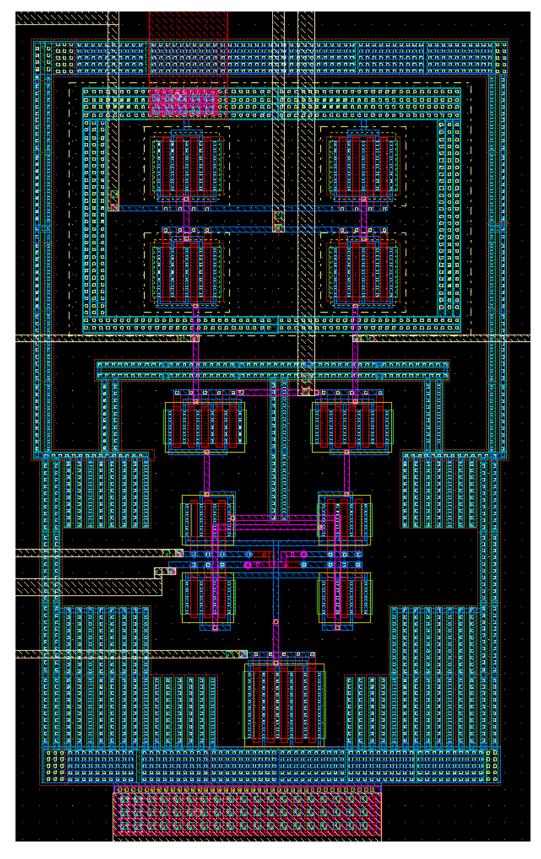

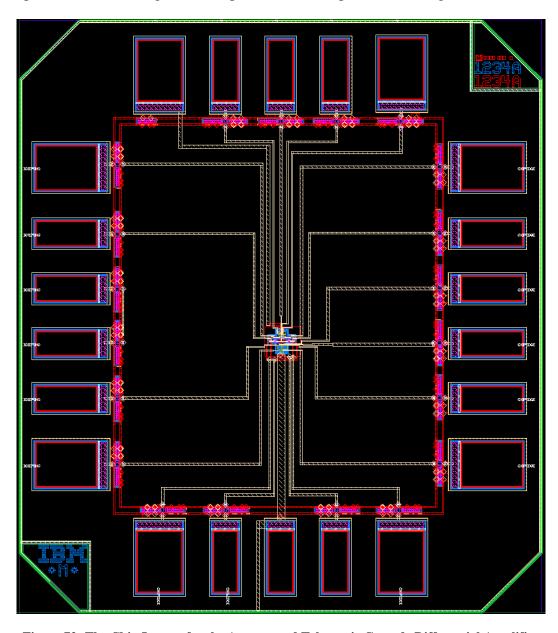

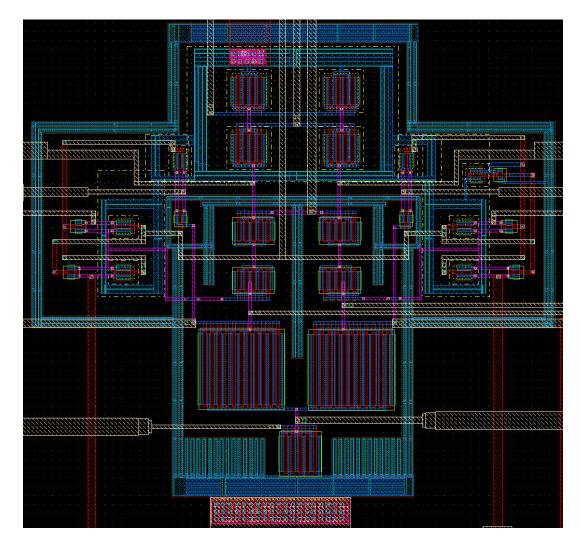

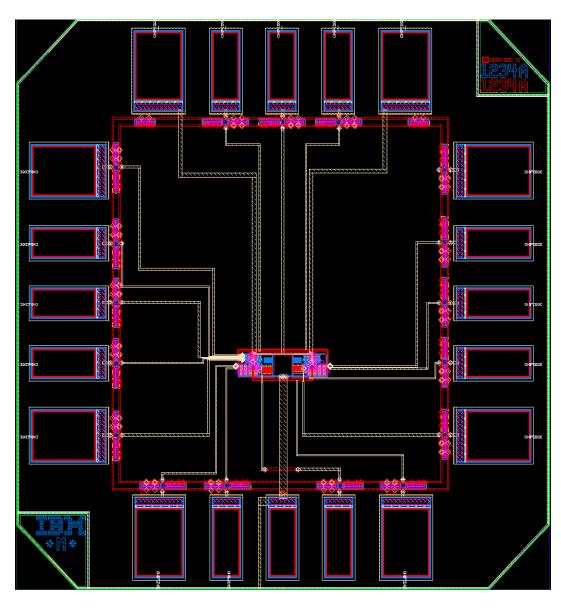

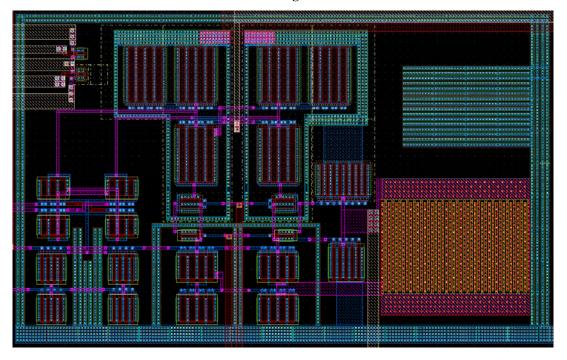

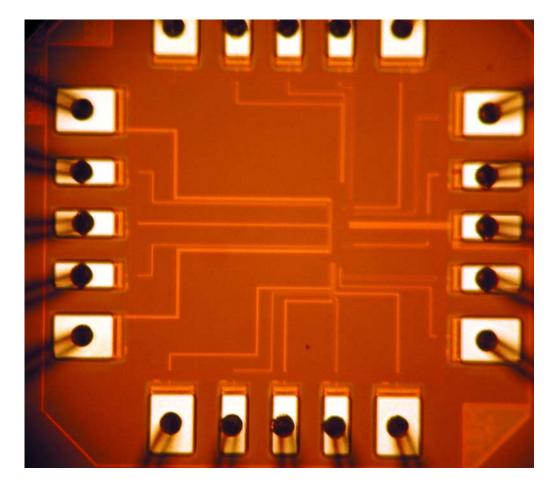

| FIGURE 64: THE CHIP LAYOUT FOR THE TELESCOPIC CASCODE DIFFERENTIAL      |     |

| AMPLIFIER SHOWN IN FIGURE 47                                            | 92  |

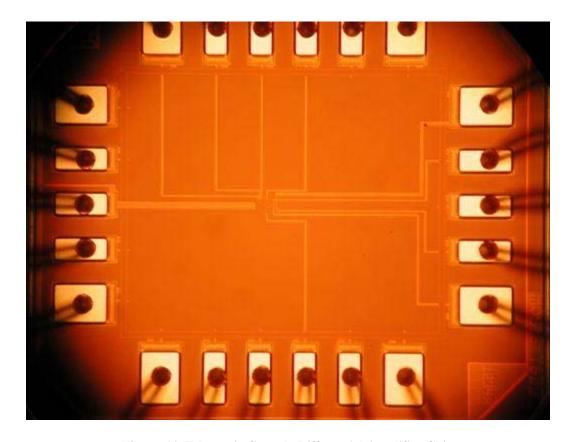

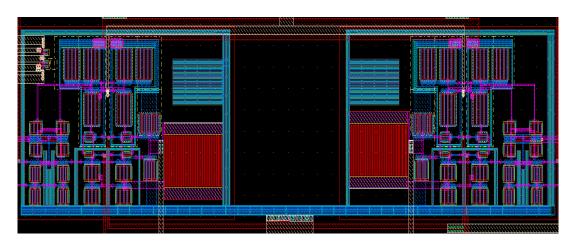

| FIGURE 65: THE TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER LAYOUT         |     |

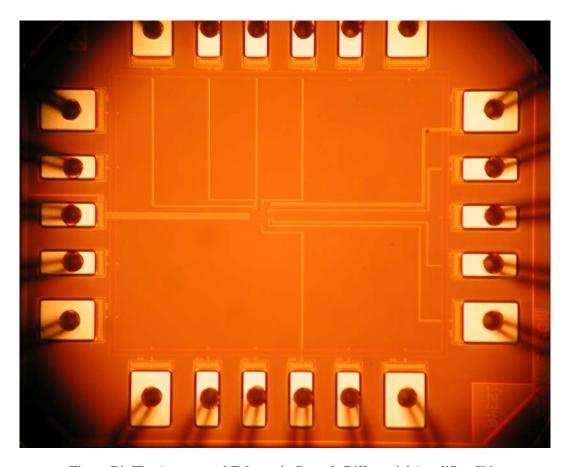

| FIGURE 66: TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER CHIP               |     |

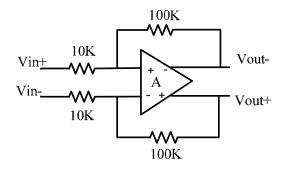

| FIGURE 67: TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER SHOWN IN A FEEDBAC |     |

| CONFIGURATION WITH A CLOSED LOOP GAIN OF 10V/V                          |     |

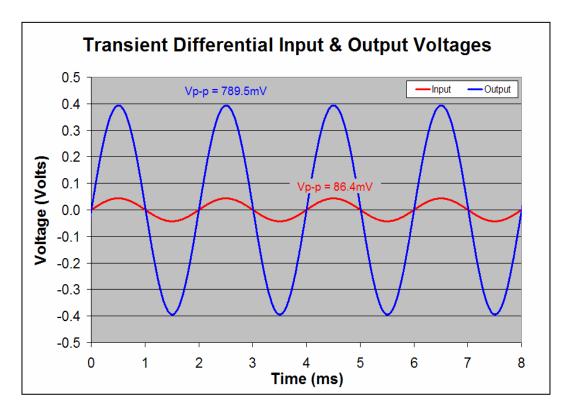

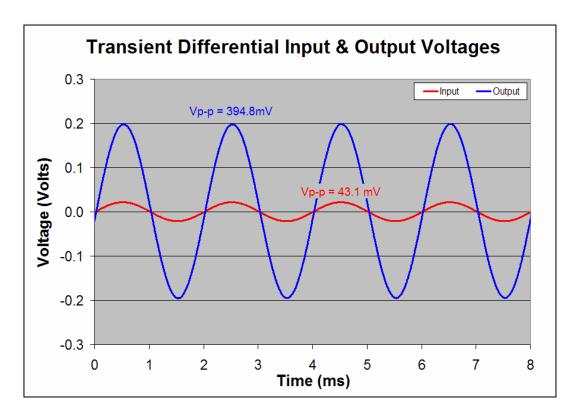

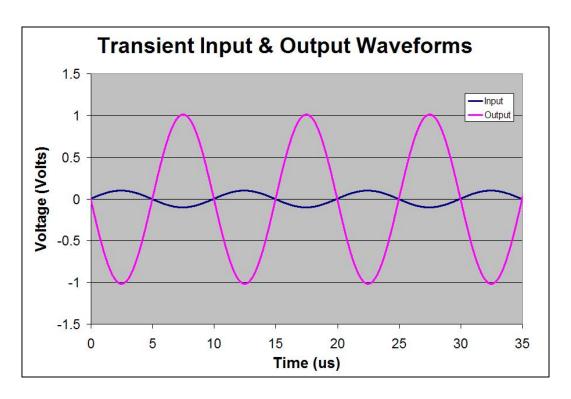

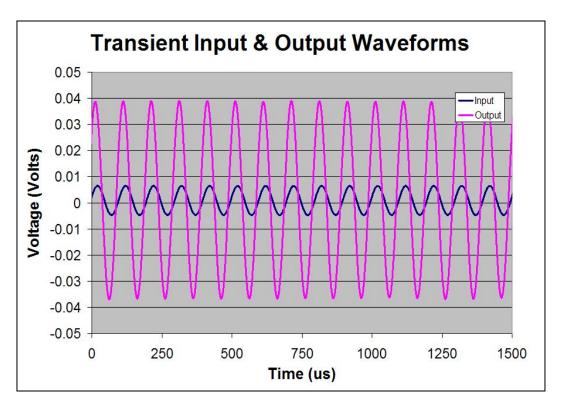

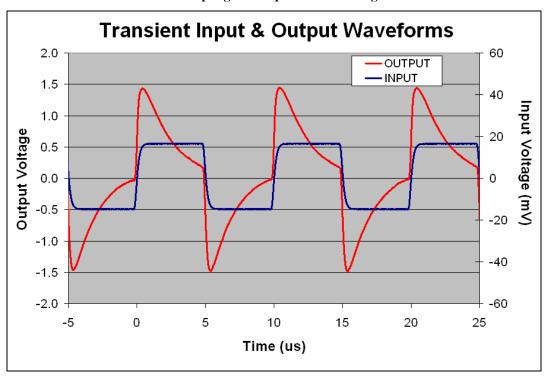

| FIGURE 68: EXPERIMENTAL TRANSIENT INPUT AND OUTPUT WAVEFORMS FOR THE    | )   |

| TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A 10K/100K FEEDBACK      |     |

| RESISTOR CONFIGURATION                                                  |     |

| FIGURE 69: EXPERIMENTAL TRANSIENT INPUT AND OUTPUT WAVEFORMS FOR THE    | )   |

| TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A 1M/10M FEEDBACK        |     |

| RESISTOR CONFIGURATION                                                  | 06  |

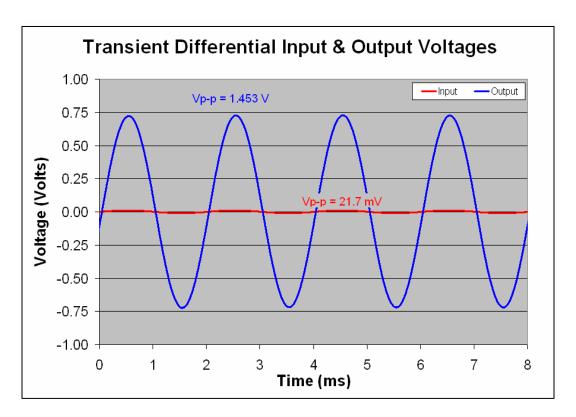

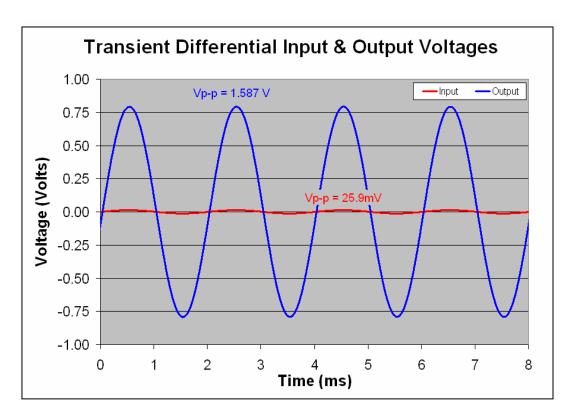

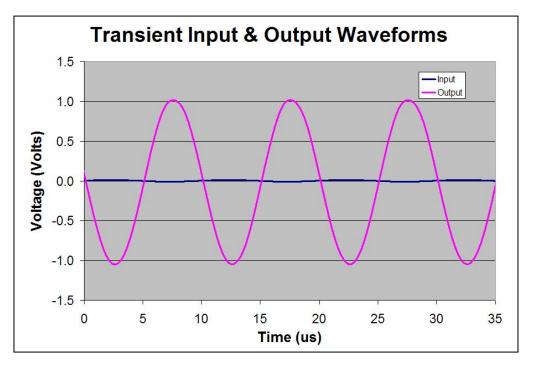

| FIGURE 70: EXPERIMENTAL TRANSIENT INPUT AND OUTPUT WAVEFORMS FOR THE    | 90  |

| TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A 100K/10M FEEDBACK      | ,   |

| RESISTOR CONFIGURATION                                                  |     |

| FIGURE 71: EXPERIMENTAL TRANSIENT INPUT AND OUTPUT WAVEFORMS FOR THE    | 91  |

| TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A 10K/1M FEEDBACK        |     |

| RESISTOR CONFIGURATION                                                  | 00  |

| FIGURE 72: THE CHIP LAYOUT FOR THE AUTO-ZEROED TELESCOPIC CASCODE       | 90  |

| DIFFERENTIAL AMPLIFIER SHOWN IN FIGURE 52                               | 00  |

|                                                                         | 99  |

| FIGURE 73: THE AUTO-ZEROED TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER    | 100 |

| LAYOUT                                                                  |     |

|                                                                         |     |

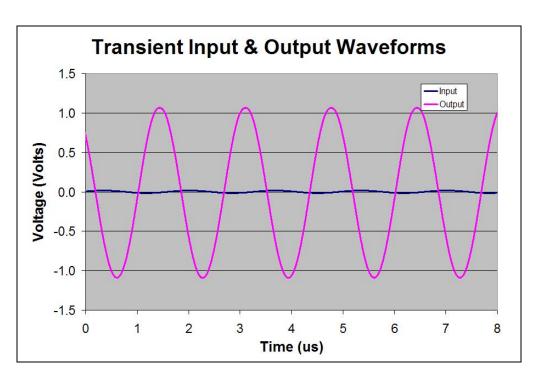

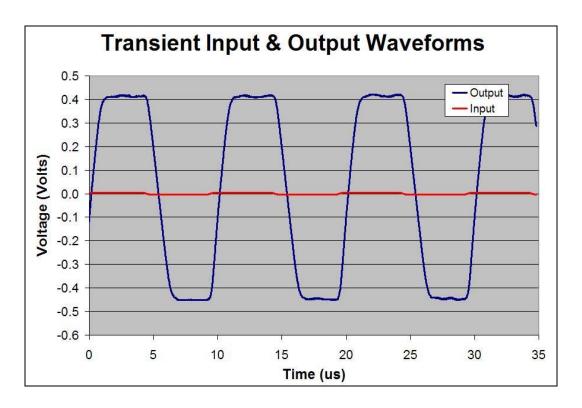

| FIGURE 75: EXPERIMENTAL TRANSIENT INPUT AND OUTPUT WAVEFORMS FOR THE    | ·OI |

|                                                                         |     |

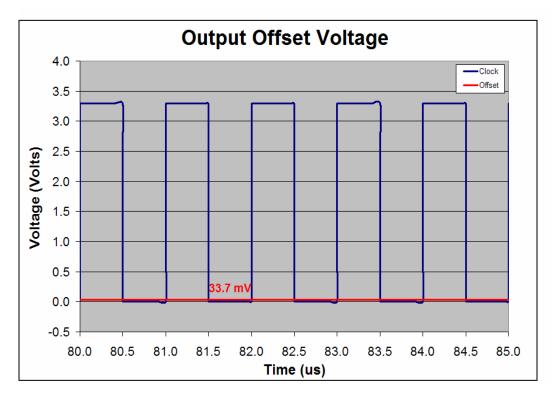

| AUTO-ZEROED TELESCOPIC CASCODE DIFFERENTIAL AMPLIFIER WITH A            | 100 |

| 10K/100K FEEDBACK RESISTOR CONFIGURATION                                |     |

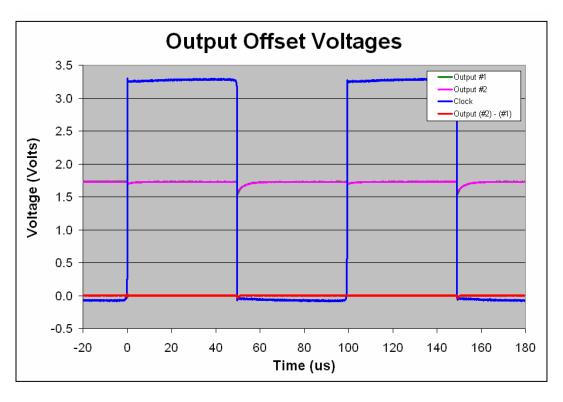

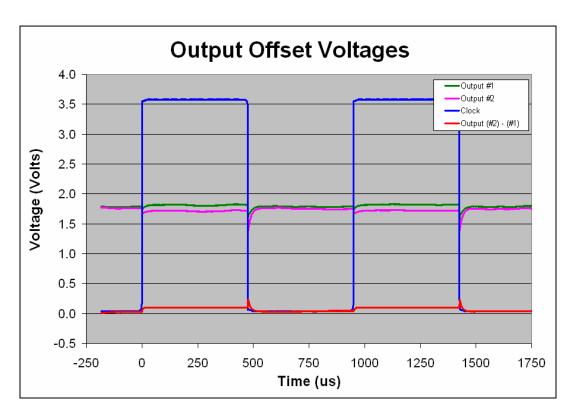

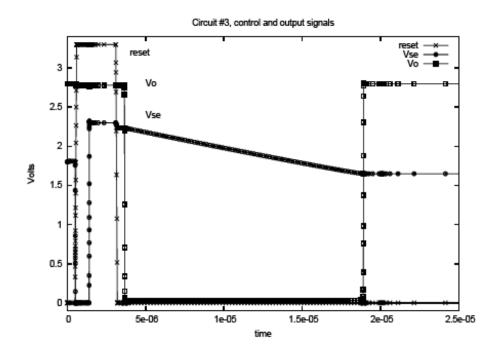

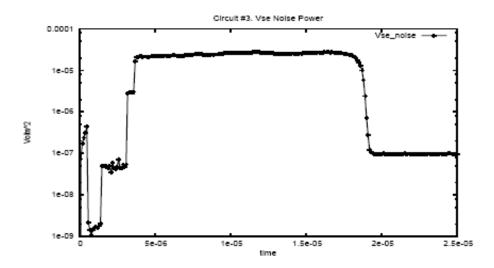

| FIGURE 76: EXPERIMENTAL OUTPUT OFFSET VOLTAGE, OUTPUT VOLTAGES AND THE  | C   |

| CONTROL VOLTAGE VS. TIME FOR THE AUTO-ZEROED TELESCOPIC CASCODE         |     |

| DIFFERENTIAL AMPLIFIER USED WITH A 10K/100K FEEDBACK CONFIGURATION      |     |

| EICUDE 77. EVDEDIMENTAL OUTDUT OFFCET VOLTAGE OUTDUT VOLTAGES AND THE   |     |

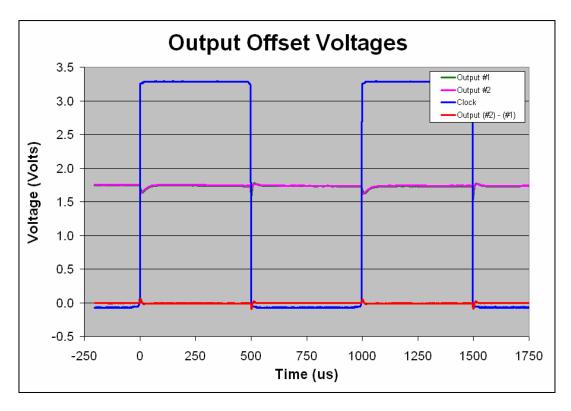

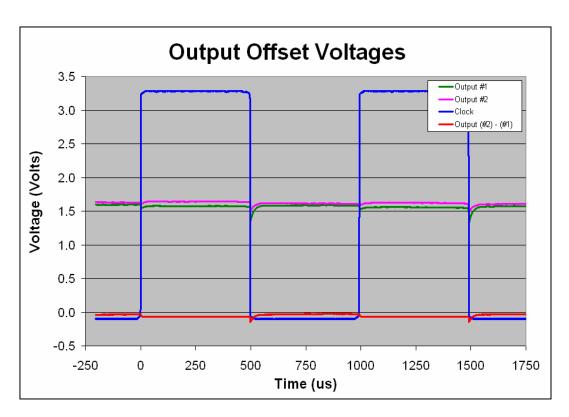

| FIGURE 77: EXPERIMENTAL OUTPUT OFFSET VOLTAGE, OUTPUT VOLTAGES AND THE  | E   |

| CONTROL VOLTAGE VS. TIME FOR THE AUTO-ZEROED TELESCOPIC CASCODE         | 104 |

| AMPLIFIER USED WITH A 1M/10M FEEDBACK CONFIGURATION                     |     |

| FIGURE 78: EXPERIMENTAL OUTPUT OFFSET VOLTAGE, OUTPUT VOLTAGES AND THE  | E   |

| CONTROL VOLTAGE VS. TIME FOR THE AUTO-ZEROED TELESCOPIC CASCODE         |     |

| AMPLIFIER USED WITH A 100K/10M FEEDBACK CONFIGURATION                   |     |

| FIGURE 79: EXPERIMENTAL OUTPUT OFFSET VOLTAGE, OUTPUT VOLTAGES AND THE  | E   |

| CONTROL VOLTAGE VS. TIME FOR THE AUTO-ZEROED TELESCOPIC CASCODE         |     |

| AMPLIFIER USED WITH A 10K/1M FEEDBACK CONFIGURATION                     | .06 |

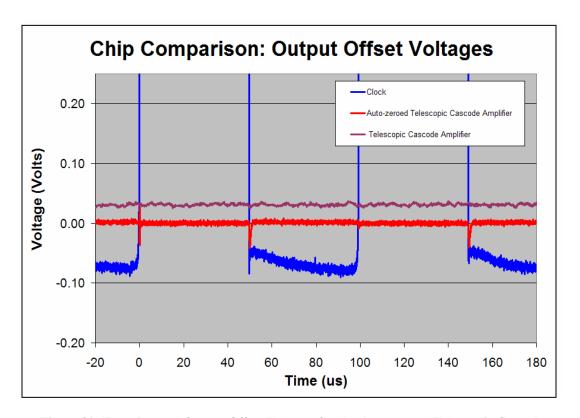

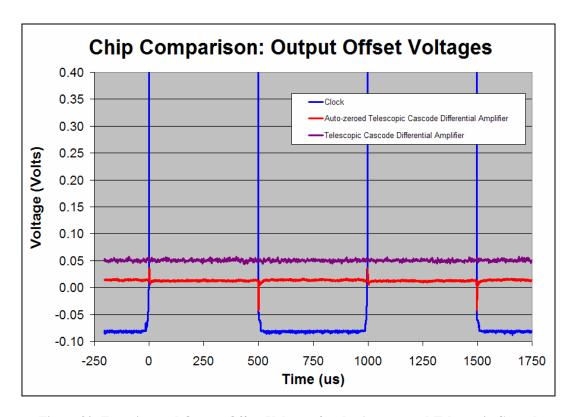

| FIGURE 80: EXPERIMENTAL OUTPUT OFFSET VOLTAGES FOR THE AUTO-ZEROED      |     |

| TELESCOPIC CASCODE AMPLIFIER AND THE TELESCOPIC CASCODE AMPLIFIER       |     |

| USED WITH A 10K/100K FEEDBACK CONFIGURATION 1                           | 107 |

| FIGURE 81: EXPERIMENTAL OUTPUT OFFSET VOLTAGES FOR THE AUTO-ZEROED      |     |

| TELESCOPIC CASCODE AMPLIFIER AND THE TELESCOPIC CASCODE AMPLIFIER       |     |

| USED WITH A 1M/10M FEEDBACK CONFIGURATION 1                             | 108 |

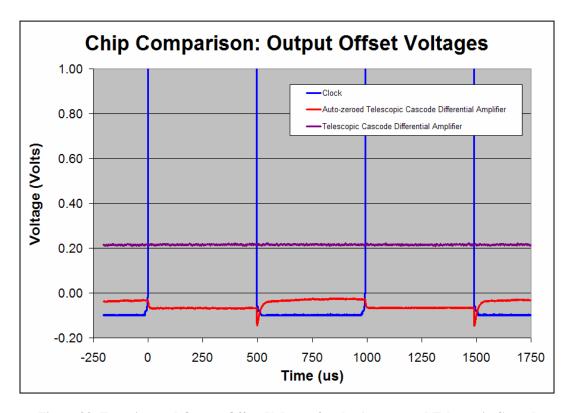

| FIGURE 82: EXPERIMENTAL OUTPUT OFFSET VOLTAGES FOR THE AUTO-ZEROED      |     |

| TELESCOPIC CASCODE AMPLIFIER AND THE TELESCOPIC CASCODE AMPLIFIER       |     |

| USED WITH A 100K/10M FEEDBACK CONFIGURATION 1                           | 09  |

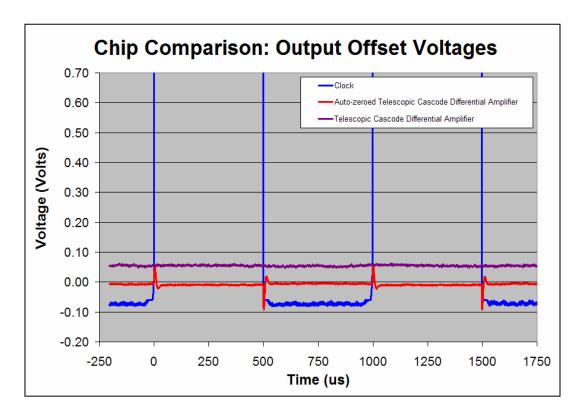

| FIGURE 83: EXPERIMENTAL OUTPUT OFFSET VOLTAGES FOR THE AUTO-ZEROED      |     |

| TELESCOPIC CASCODE AMPLIFIER AND THE TELESCOPIC CASCODE AMPLIFIER       |     |

| USED WITH A 10K/1M FEEDBACK CONFIGURATION 1                             |     |

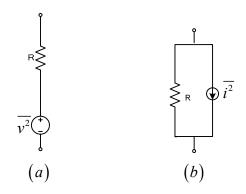

| FIGURE 84: THERMAL NOISE REPRESENTATION                                 | 12  |

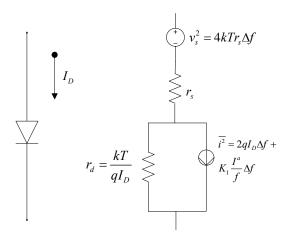

| FIGURE 85: SMALL SIGNAL EQUIVALENT CIRCUIT FOR JUNCTION DIODE 113          |

|----------------------------------------------------------------------------|

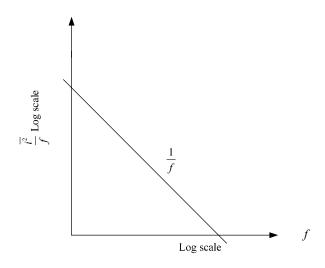

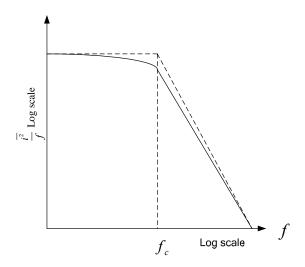

| FIGURE 86: FLICKER NOISE SPECTRUM DENSITY AS A FUNCTION OF FREQUENCY 115   |

| FIGURE 87: BURST NOISE SPECTRAL DENSITY                                    |

| FIGURE 88: NOISE MODEL FOR THE JUNCTION DIODE                              |

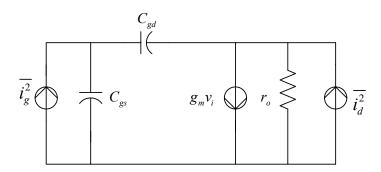

| FIGURE 89: MOSFET SMALL SIGNAL EQUIVALENT CIRCUIT WITH NOISE SOURCES 118   |

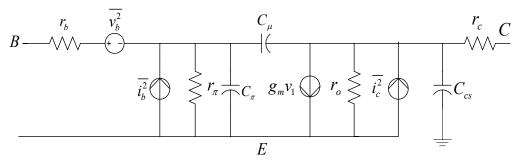

| FIGURE 90: EQUIVALENT BJT MODEL WITH NOISE                                 |

| FIGURE 91: A TYPICAL DETECTOR FRONT END CIRCUIT                            |

| FIGURE 92: EQUIVALENT SMALL SIGNAL CIRCUIT FOR DETECTOR NOISE ANALYSIS 122 |

| FIGURE 93: DETECTOR SHOT NOISE MODEL                                       |

| FIGURE 94: NOISE MODEL FOR THE BIAS RESISTOR 124                           |

| FIGURE 95: EQUIVALENT NOISE CHARGE VS. SHAPING TIME [2]                    |

| FIGURE 96: FEEDBACK IN A NOISY CIRCUIT                                     |

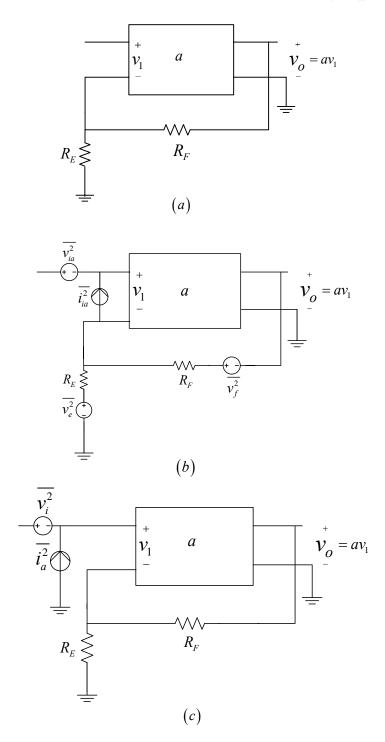

| FIGURE 97: (A) SERIES-SHUNT FEEDBACK CIRCUIT (B) SERIES-SHUNT FEEDBACK     |

| CIRCUIT WITH NOISE SOURCES (C) EQUIVALENT REPRESENTATION OF (D) WITH       |

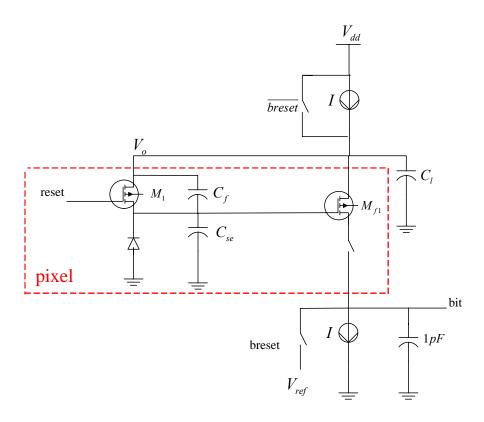

| TWO NOISE SOURCES                                                          |

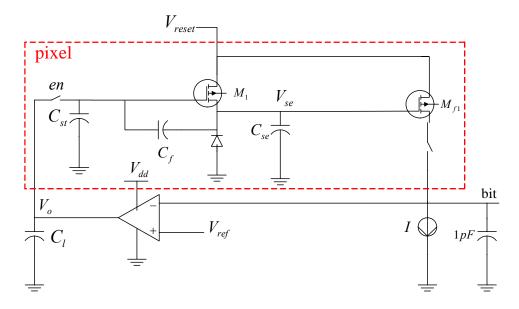

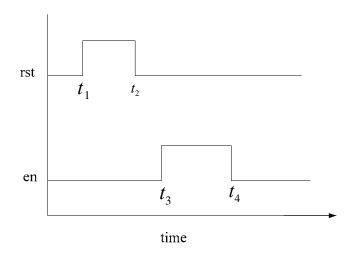

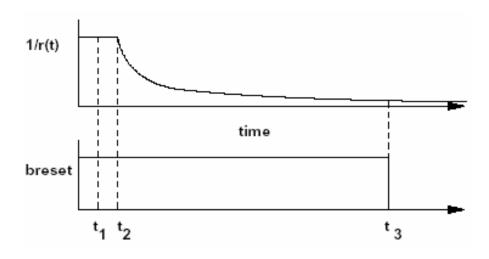

| FIGURE 98: CAPACITIVE CONTROL TECHNIQUE SCHEMATIC                          |

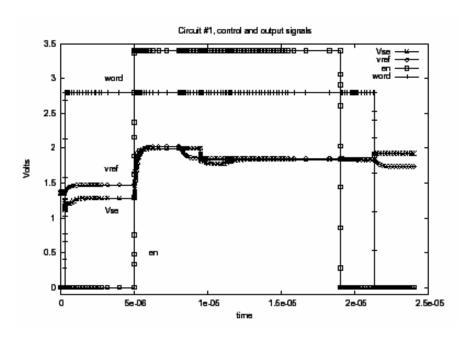

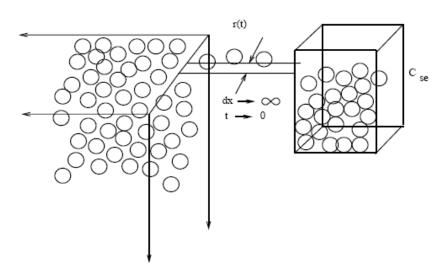

| FIGURE 99: TIMING WAVEFORMS FOR THE CAPACITIVE CONTROL TECHNIQUE 134       |

| FIGURE 100: ANALOGY- HIGH TO LOW POTENTIAL                                 |

| FIGURE 101: ANALOGY- LOW TO HIGH POTENTIAL                                 |

| FIGURE 102: ANALOGY- NO POTENTIAL DIFFERENCE                               |

| FIGURE 103: ANALOGY FOR THE CAPACITIVE CONTROL TECHNIQUE                   |

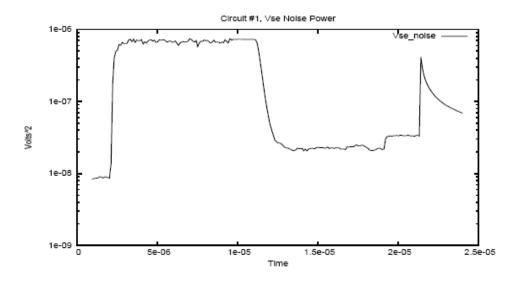

| FIGURE 104: INPUT AND OUTPUT WAVEFORMS FOR THE CAPACITIVE CONTROL          |

| TECHNIOUE CIRCUIT [41]                                                     |

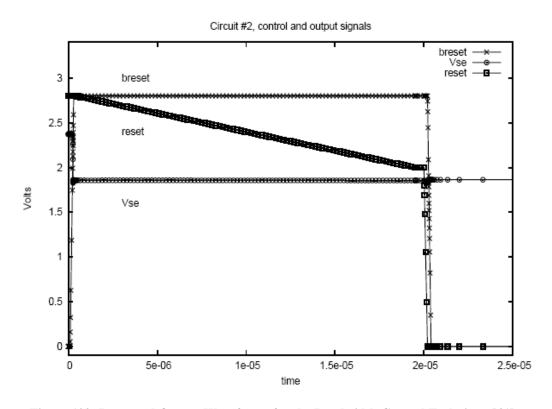

| TECHNIQUE CIRCUIT [41]                                                     |

| TECHNIQUE [41]                                                             |

| FIGURE 106: BANDWIDTH CONTROL TECHNIQUE CIRCUIT SCHEMATIC                  |

| FIGURE 107: TIMING CONTROL TRANSIENT WAVEFORMS [41]                        |

| FIGURE 108: ANALOGY FOR THE BANDWIDTH CONTROL TECHNIQUE                    |

| FIGURE 109: INPUT AND OUTPUT WAVEFORMS FOR THE BANDWIDTH CONTROL           |

| TECHNIQUE [41]                                                             |

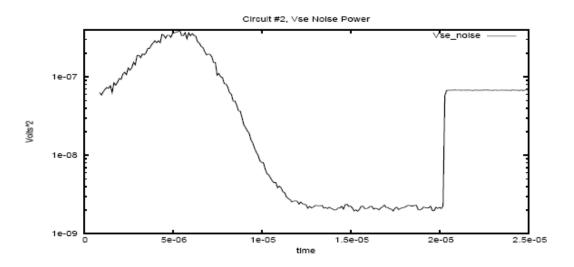

| FIGURE 110: TRANSIENT NOISE WAVEFORMS FOR THE BANDWIDTH CONTROL            |

| TECHNIQUE [41]                                                             |

| FIGURE 111: CHARGE CONTROL TECHNIQUE CIRCUIT SCHEMATIC                     |

| FIGURE 112: ANALOGY FOR THE CHARGE CONTROL NOISE REDUCTION TECHNIQUE 147   |

| FIGURE 113: INPUT AND OUTPUT TRANSIENT WAVEFORMS FOR THE CHARGE            |

| CONTROL TECHNIQUE [41]                                                     |

| FIGURE 114: TRANSIENT NOISE WAVEFORM FOR THE CHARGE CONTROL NOISE          |

| REDUCTION TECHNIQUE [41]148                                                |

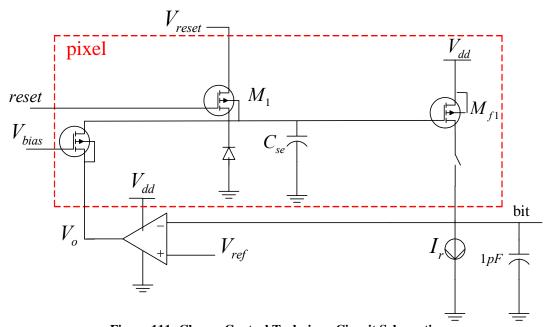

| FIGURE 115: SIMPLIFIED SIGNAL PROCESSING CHAIN SCHEMATIC                   |

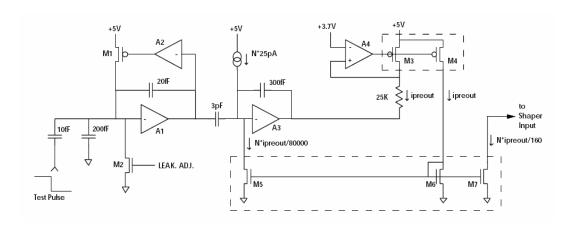

| FIGURE 116: DETAILED SCHEMATIC OF THE PRE-AMPLIFIER/AMPLIFIER SECTION [42] |

| 152                                                                        |

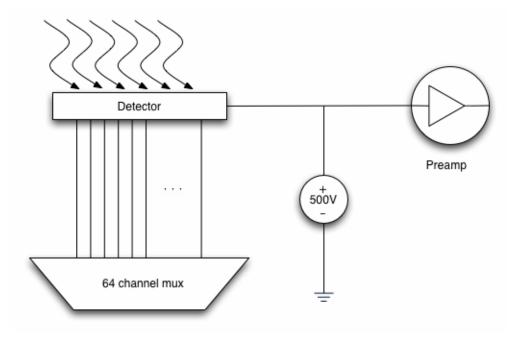

| FIGURE 117: PRE-AMPLIFIER/AMPLIFIER CHAIN USED IN A MULTIPLEXED DETECTOR   |

|                                                                            |

| FIGURE 118: PRE-AMPLIFIER/AMPLIFIER CHAIN BLOCK DIAGRAM                    |

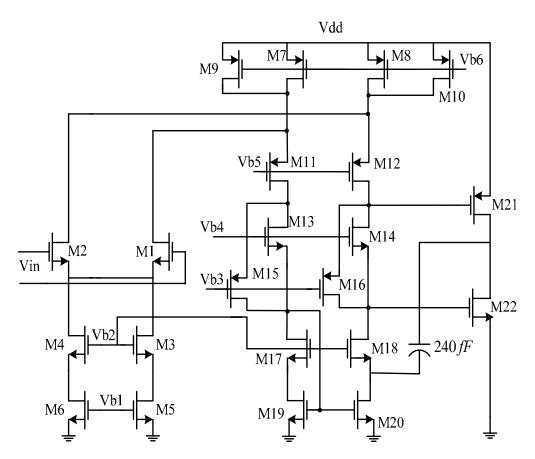

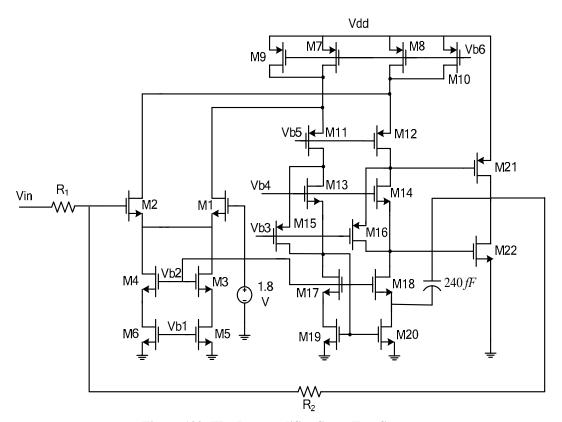

| FIGURE 119: FOLDED CASCODE AMPLIFIER SCHEMATIC FOR EACH STAGE              |

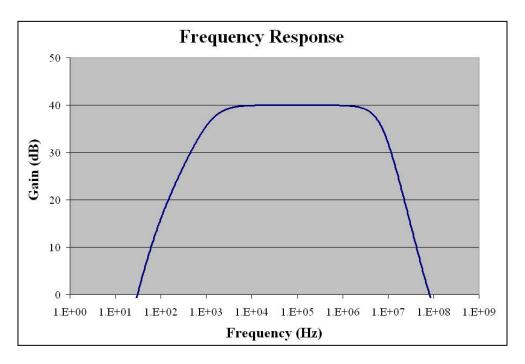

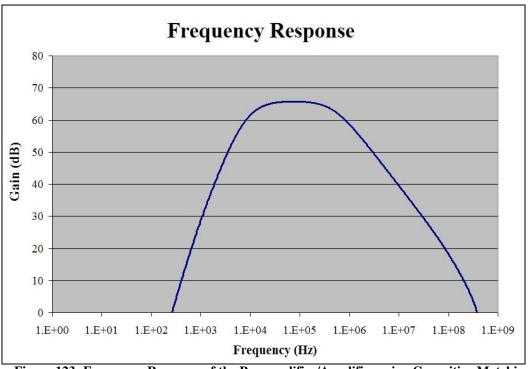

| FIGURE 120: FREQUENCY RESPONSE OF THE PRE-AMPLIFIER/AMPLIFIER EMPLOYING    |

| CORRELATED DOUBLE SAMPLING WITHOUT CAPACITIVE MATCHING                     |

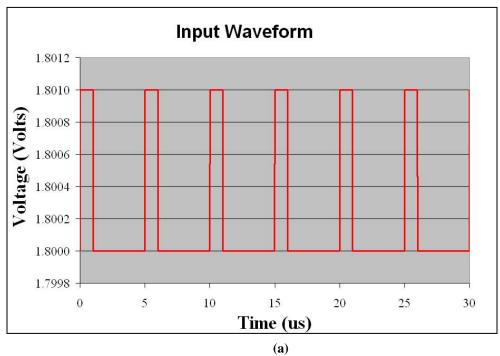

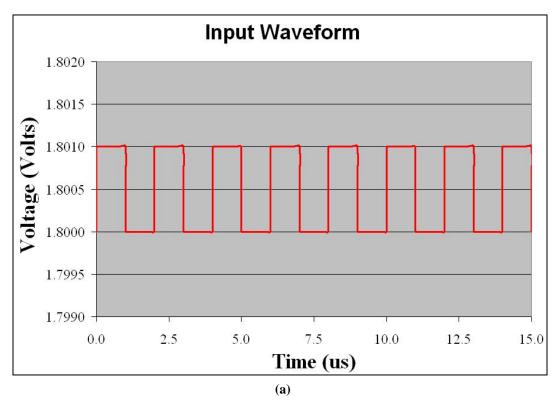

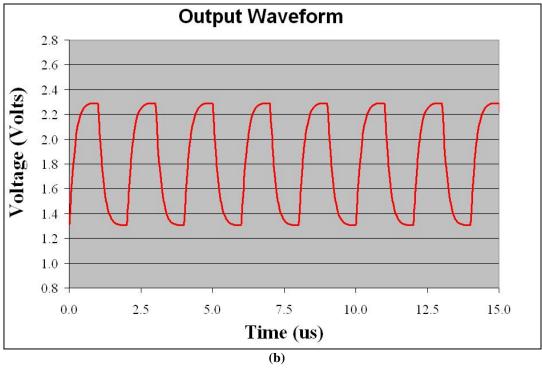

| FIGURE 121: (A) SIMULATED INPUT AND (B) OUTPUT TRANSIENT WAVEFORMS OF THE  |

| PRE-AMPLIFIER/AMPLIFIER READOUT CIRCUITRY EMPLOYING CORRELATED             |

| DOUBLE SAMPLING WITHOUT CAPACITIVE MATCHING                                |

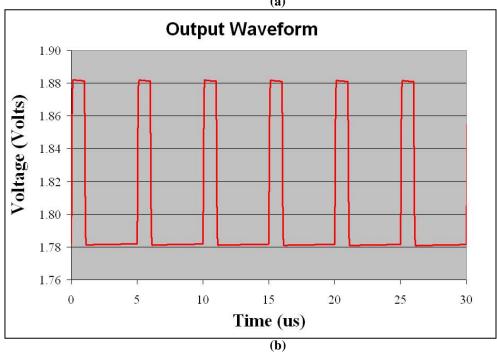

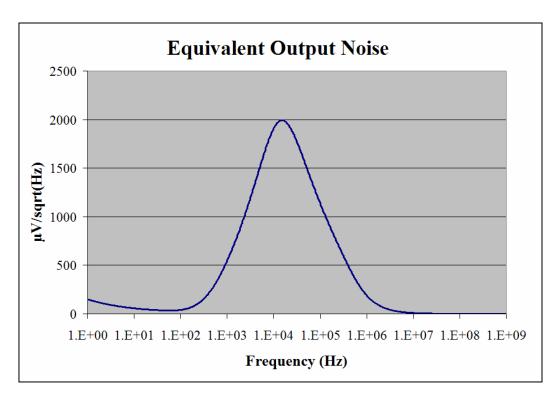

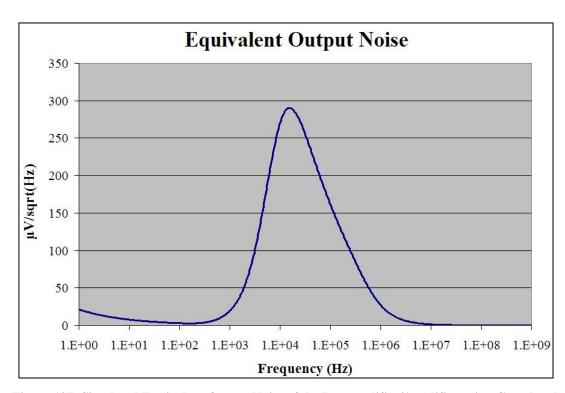

| FIGURE 122: SIMULATED EQUIVALENT OUTPUT NOISE OF THE PRE-                  |

| AMPLIFIER/AMPLIFIER EMPLOYING CORRELATED DOUBLE SAMPLING WITHOUT           |

| CAPACITIVE MATCHING                                                        |

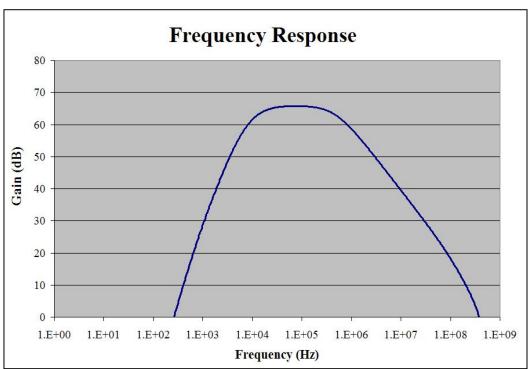

| FIGURE 123: FREQUENCY RESPONSE OF THE PRE-AMPLIFIER /AMPLIFIER USING       |

| CAPACITIVE MATCHING WITHOUT CORRELATED DOUBLE SAMPLING                     |

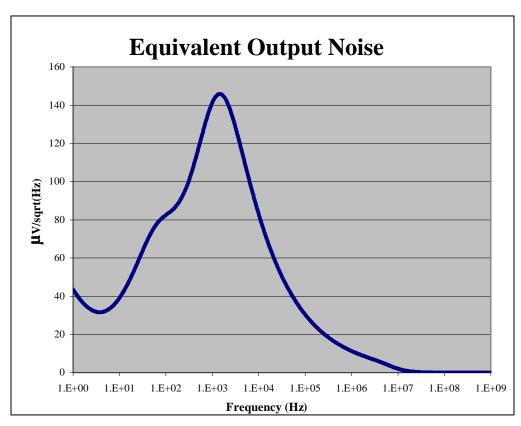

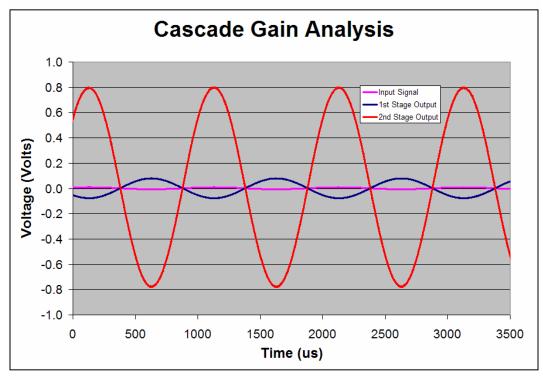

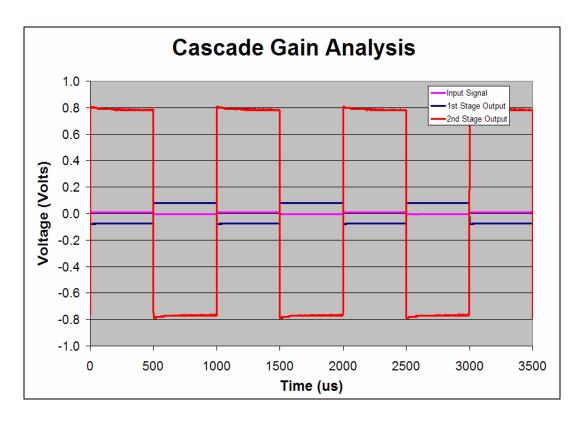

| FIGURE 124: SIMULATED EQUIVALENT OUTPUT NOISE OF THE PRE-                 |

|---------------------------------------------------------------------------|

| AMPLIFIER/AMPLIFIER EMPLOYING CAPACITIVE MATCHING WITHOUT                 |

| CORRELATED DOUBLE SAMPLING164                                             |

| FIGURE 125: FREQUENCY RESPONSE OF THE PRE-AMPLIFIER/AMPLIFIER USING       |

| CORRELATED DOUBLE SAMPLING AND CAPACITIVE MATCHING 165                    |

| FIGURE 126: (A) SIMULATED INPUT AND (B) OUTPUT TRANSIENT WAVEFORMS OF THE |

| PRE-AMPLIFIER/AMPLIFIER READOUT CIRCUITRY USING CORRELATED DOUBLE         |

| SAMPLING AND CAPACITIVE MATCHING 166                                      |

| FIGURE 127: SIMULATED EQUIVALENT OUTPUT NOISE OF THE PRE-                 |

| AMPLIFIER/AMPLIFIER USING CORRELATED DOUBLE SAMPLING AND                  |

| CAPACITIVE MATCHING167                                                    |

| FIGURE 128: THE CHIP LAYOUT FOR THE LOW NOISE PRE-AMPLIFIER/AMPLIFIER     |

| CHAIN SHOWN IN FIGURE 118168                                              |

| FIGURE 129: THE PRE-AMPLIFIER/AMPLIFIER LAYOUT FOR THE LOW NOISE SIGNAL   |

| PROCESSING CHAIN SHOWN IN FIGURE 118 169                                  |

| FIGURE 130: ENHANCED VIEW OF THE LOW NOISE AMPLIFIER                      |

| FIGURE 131: LOW NOISE PRE-AMPLIFIER/AMPLIFIER READOUT CIRCUITRY CHIP 170  |

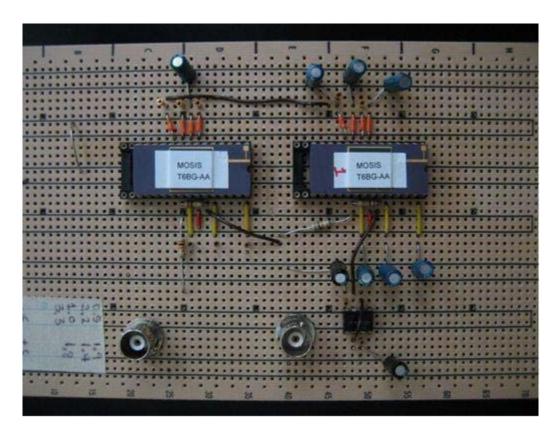

| FIGURE 132: THE PRE-AMPLIFIER STAGE TEST SETUP                            |

| FIGURE 133: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER STAGE WITH A FEEDBACK RESISTOR COMBINATION OF 10K/100K 172      |

| FIGURE 134: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER STAGE WITH A FEEDBACK RESISTOR COMBINATION OF 10K/100K AT       |

| THE 3DB BANDWIDTH FREQUENCY OF 10MHZ                                      |

| FIGURE 135: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER STAGE WITH A FEEDBACK RESISTOR COMBINATION OF 10K/1M 173        |

| FIGURE 136: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER STAGE WITH A FEEDBACK RESISTOR COMBINATION OF 10K/1M AT         |

| THE 3DB BANDWIDTH FREQUENCY OF 600KHZ                                     |

| FIGURE 137: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER STAGE WITH A FEEDBACK RESISTOR COMBINATION OF 10K/1M AT         |

| 10MHZ                                                                     |

| FIGURE 138: TEST SETUP FOR THE PRE-AMPLIFIER/AMPLIFIER READOUT CIRCUITRY  |

| WITHOUT CORRELATED DOUBLE SAMPLING AND CAPACITIVE MATCHING 176            |

| FIGURE 139: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER/AMPLIFIER READOUT CIRCUITRY WITH A CLOSED LOOP GAIN OF          |

| 100V/V                                                                    |

| FIGURE 140: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER/AMPLIFIER READOUT CIRCUITRY WITH A CLOSED LOOP GAIN OF          |

| 100V/V                                                                    |

| FIGURE 141: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER/AMPLIFIER READOUT CIRCUITRY WITHOUT CORRELATED DOUBLE           |

| SAMPLING AND CAPACITIVE MATCHING WITH A CLOSED LOOP GAIN OF 100V/V        |

|                                                                           |

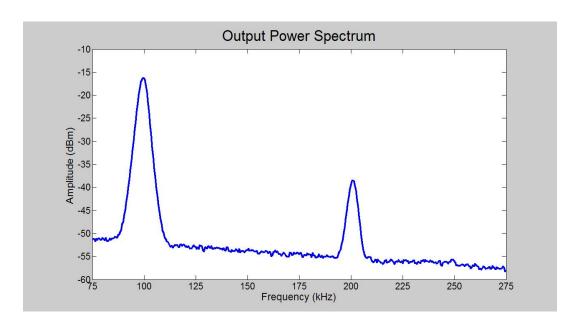

| FIGURE 142: FREQUENCY SPECTRUM FOR THE PRE-AMPLIFIER/AMPLIFIER READOUT    |

|                                                                           |

| CIRCUITRY WITHOUT CORRELATED DOUBLE SAMPLING AND CAPACITIVE               |

| MATCHING WITH A CLOSED LOOP GAIN OF 100V/V                                |

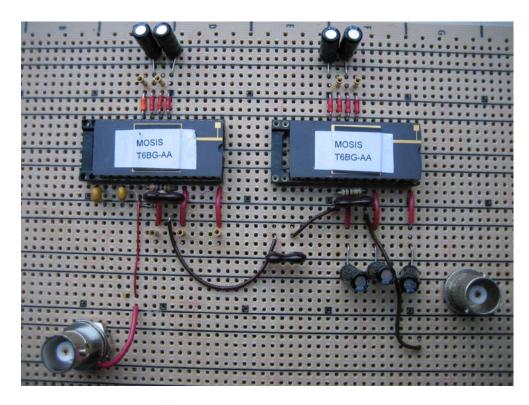

| FIGURE 143: TEST SETUP FOR THE PRE-AMPLIFIER/AMPLIFIER CHAIN EMPLOYING    |

| CORRELATED DOUBLE SAMPLING                                                |

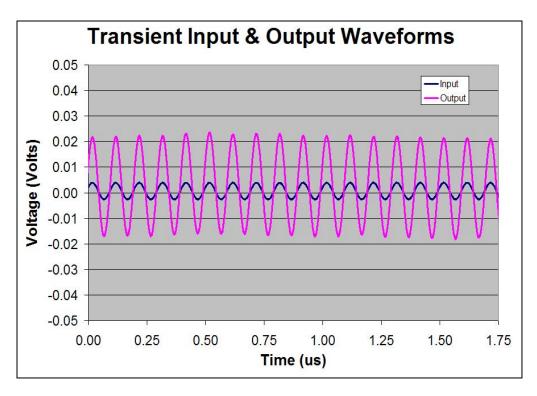

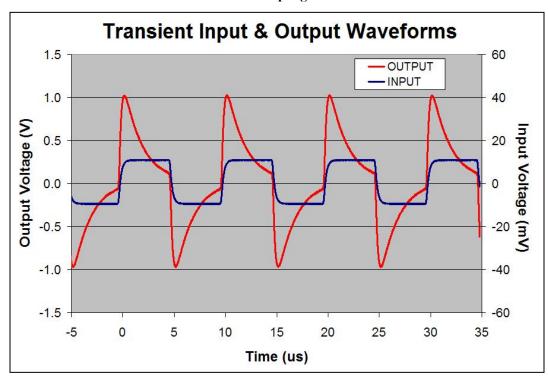

| FIGURE 144: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR THE PRE- |

| AMPLIFIER/AMPLIFIER READOUT CIRCUITRY WITH A CLOSED LOOP GAIN OF          |

| 100V/V                                                                    |

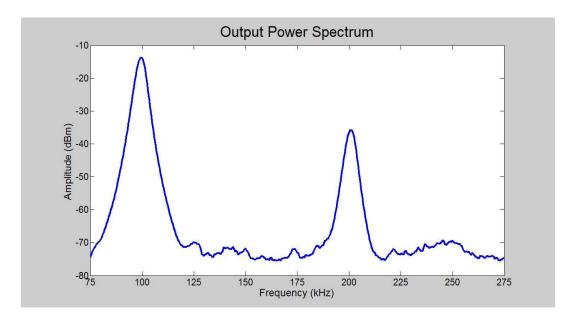

| FIGURE 145: FREQUENCY SPECTRUM FOR THE PRE-AMPLIFIER /AMPLIFIER READOUT   |

| CIRCUITRY EMPLOYING CORRELATED DOUBLE SAMPLING WITH A CLOSED LOOP         |

| GAIN OF 100V/V                                                            |

| FIGURE 146: TEST SETUP FOR THE PRE-AMPLIFIER/AMPLIFIER CHAIN EMPLOYING    |

| CORRELATED DOUBLE SAMPLING AND CAPACITIVE MATCHING 183                    |

| FIGURE 147: EXPERIMENTAL INPUT AND OUTPUT TRANSIENT RESPONSE FOR T | HE PRE- |

|--------------------------------------------------------------------|---------|

| AMPLIFIER/AMPLIFIER READOUT CIRCUITRY EMPLOYING CAPACITIVE         |         |

| MATCHING AND CORRELATED DOUBLE SAMPLING WITH A CLOSED LOOI         | P GAIN  |

| OF 100V/V                                                          | 183     |

| FIGURE 148: FREQUENCY SPECTRUM FOR THE PRE-AMPLIFIER/AMPLIFIER REA | DOUT    |

| CIRCUITRY EMPLOYING CORRELATED DOUBLE SAMPLING AND CAPACIT         | IVE     |

| MATCHING WITH A CLOSED LOOP GAIN OF 100V/V                         | 184     |

# **Chapter 1: Introduction**

In the past two decades, imaging sensors and detectors have developed tremendously. This technology has found its way into a number of areas, such as space missions, synchrotron light sources, and medical imaging. Nowadays, detectors and custom ICs are routine in high-energy physics applications. Electronic readout circuits are a key part of every modern detector system. Although the readout electronics for different experiments may be different, the same basic principles of optimization of signal-to-noise ratio apply to all.

NASA is one of the agencies integrating new sensor technologies for earth resource management surveillance and astronomy. Unique materials used in these new sensors require innovative pre-amplifier/amplifier readout circuitry chains, in order, to fully exploit the potential of these devices. In particular, most detectors exhibit exceptional high output impedance. As a result, standard voltage amplification techniques become difficult, as voltage divider effects "de-magnify" the signal. Additional problems occur when the detectors present large capacitances to the pre-amplifier inputs. This gives rise to charge division which further lowers usable signal. Also, the generated capacitances in conjunction with the resistance are responsible for introducing reset noise in detector systems. So the means to provide low noise readout circuitry which can amplify the signal is essential for detector systems.

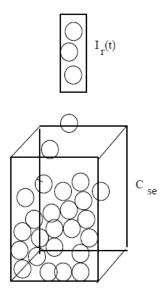

Many sensing circuits in detectors, such as CdZnTe detectors used by NASA for gamma ray detection, depend upon accumulating charge on a capacitor. The charge uncertainty on the capacitor when it is reset to a reference voltage causes noise, reset noise, as a result of shot and thermal processes. Reset noise is enhanced by the sensing capacitor. Therefore, low noise readout circuitry capable of driving a high input capacitance is essential for detector systems. The main goal of this dissertation is to provide a flexible signal processing chain for high capacitance sensors. This innovative signal processing chain is aimed at increasing the signal-to-noise ratio in pixel detectors and sensors. The resulting system can be used in wide variety of detectors with a range of applications such as random access pixel detectors, fully depleted CCDs, hybrid detector systems, and superconducting detector arrays.

In this dissertation, a novel auto-zeroing technique for amplifiers is proposed as well. This novel technique uses a nulling point other than the amplifier's input and output to perform the auto-zeroing operation. The auto-zeroing is performed by taking advantage of emitter degeneration in the input transistor pair of the differential pair to cancel the offset at the output of the amplifier. This technique reduces the input referred offset voltage of the amplifiers by approximately an order of magnitude.

The unique contributions of this dissertation are as follows:

- Developed a low noise pre-amplifier/amplifier chain employing correlated double sampling and capacitive matching

- Implemented correlated double sampling absent of additional circuitry,

using a reset switch

- Designed a readout circuit which includes signal processing at the point of signal reception

- Invented a novel auto-zeroing technique by taking advantage of the emitter degeneration resistors to reduce the input referred offset by an order of magnitude

This dissertation is organized as follows. Chapter 2 reviews the VLSI readout circuitry used in detector systems. Chapter 3 discusses different amplifier architectures and the advantages and disadvantages for each one. Chapter 4 reviews output offset in amplifiers and the techniques used to reduce the input referred offset voltage. This chapter introduces the novel auto-zeroing technique and discusses the test results. Chapter 5 investigates the noise sources which contribute to the noise in sensors. Chapter 6 reviews the previously proposed techniques for noise reduction in sensor arrays. Finally Chapter 7 presents in detail, the novel noise reduction technique for high output capacitance sensor arrays. It discusses the results achieved using the proposed low noise pre-amplifier/amplifier chain. Chapter 8 concludes this dissertation and gives a brief summary of the novel techniques used for auto-zeroing and noise reduction in high output capacitance sensors.

# **Chapter 2: Review of VLSI Read out in Detector Systems**

#### 2.1 Introduction

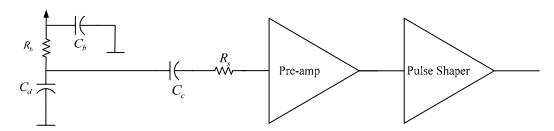

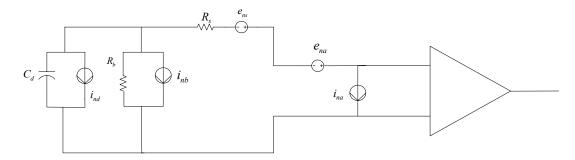

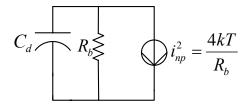

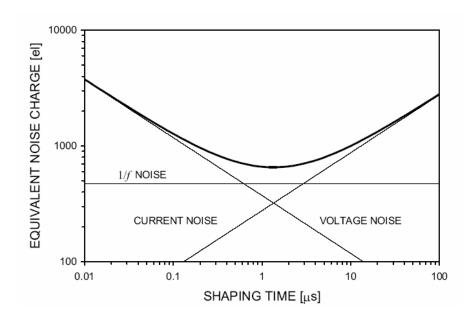

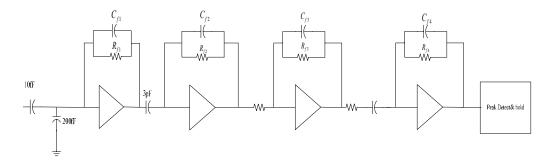

VLSI readout circuitry is a key component in all detector systems [1], [2]. It usually consists of a pre-amplifier/amplifier, pulse shaping section, and detect/hold circuitry. This chapter will mainly focus on the pre-amplifier/amplifier section while providing a brief overview of the pulse shaping. Although the experiments and their associated readout circuitry might have different forms, the basic fundamentals of the readout circuitry are the same.

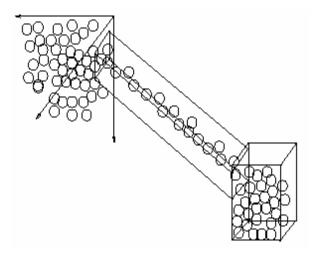

### 2.2 Signal Processing Chain in Radiation Detector Systems

In order to describe the detector signal processing chain, a scintillation detector is used as an example. Figure 1 shows a scintillation detector block diagram. Radiation primarily consisting of Gamma rays, in this example, is absorbed by a scintillating crystal which produces light photons proportional to the absorbed energy. The photocathode absorbs the photons and releases electrons which correspond to the number of photons detected. At this point, the energy absorbed by the scintillation detector is converted into an electrical signal whose charge is proportional to the energy. The pre-amplifier/amplifier increases this charge by a constant factor. The signal is then passed through a pulse shaper which feeds the analog-to-digital converter (ADC). The ADC converts the signal into a digital signal which is used for

digital processing and storage. In the following sections, a brief review of each of the components used in the signal processing chain will be provided.

Figure 1: Detector Signal Processing Chain

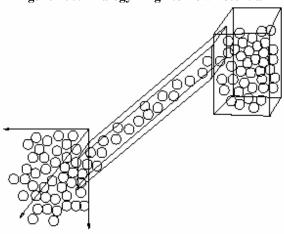

#### 2.2.1 Pre-amplifier/Amplifier

One of the most important building blocks in the readout circuits for radiation detectors is the pre-amplifier/amplifier block. Figure 2 shows an amplifier block connected to a detector. The detector has a capacitor,  $C_d$ , while the amplifier has an input capacitance and resistance,  $C_i$  and  $R_i$  respectively.

Figure 2: Amplifier and Detector Block Diagram

The sensor signal is modeled as a short current pulse. The amplifier detects the sensor signal and integrates it to get the charge signal. If the amplifier has a small

input resistance,  $R_i$ , then the time constant,  $\tau = R_i \left( C_d + C_i \right)$ , for discharging the sensor capacitor is small. As a result, the amplifier will sense the current signal. On the other hand if the amplifier input resistance is large, the input time constant is large compared to the duration of the current pulse. Therefore, the amplifier will sense the voltage stored on the detector capacitance.

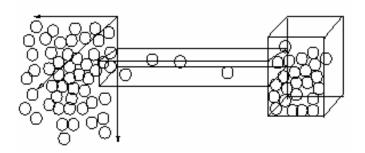

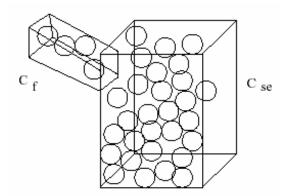

Figure 3 shows a charge sensitive amplifier with a capacitive feedback which performs integration. The amplifier has a gain of A and infinite input impedance. The voltage difference across the feedback capacitor is  $v_f = (A+1)v_i$ , where  $v_i$  is the input signal. The charge deposited on the feedback capacitance becomes  $Q_f = C_f v_f = C_f (A+1)v_i.$  Since no current flows into the amplifier input, all of the signal current must charge up the feedback capacitor so  $Q_i = Q_f$ , and the amplifier dynamic input capacitance is given by equation (2.1).

$$C_i = \frac{Q_i}{v_i} = C_f \left( A + 1 \right) \tag{2.1}$$

**Figure 3: Charge Sensitive Amplifier Configuration**

The output voltage per unit input charge can be represented by equation (2.2) in which it is assumed  $A \gg 1$ .

$$A_{Q} = \frac{dv_{o}}{dQ_{i}} = \frac{Av_{i}}{C_{i}v_{i}} = \frac{A}{C_{i}} = \frac{A}{A+1} \cdot \frac{1}{C_{f}} \approx \frac{1}{C_{f}}$$

(2.2)

Note that the gain declines inversely with the size of the feedback capacitor. The gain is determined by the feedback capacitor which is well defined. In this discussion, the amplifiers are assumed to be infinitely fast. This is not always the case, such as in charge sensitive amplifiers. Charge sensitive amplifiers usually respond more slowly than the time duration of the sensor current signal. However, this does not present a problem since the signal current is first integrated on the sensor capacitor. Then as the amplifier responds, the charge is transferred to the amplifier. The important factor is the amplifier time response. From basic feedback theory, the input impedance of the feedback amplifier is as follows  $Z_i = \frac{Z_f}{A+1} \approx \frac{Z_f}{A}$  for  $A \gg 1$ . At low frequencies, the gain is constant causing the input impedance to be the same as the feedback impedance but reduced by 1/A. At high frequencies beyond the amplifiers 3dB bandwidth,  $f_{\rm 3dB}\,$  , the gain drops linearly with an additional 90 degrees phase shift. Therefore, the following relationship describes the gain of the amplifier:  $A = -j\frac{\omega_o}{\omega}$  in which  $\omega_o$  is the unity gain bandwidth of the amplifier. So the input impedance of the charge sensitive feedback amplifier is represented by equation (2.3).

$$Z_{i} = \frac{1}{j\omega C_{f}} \cdot \frac{1}{-j\frac{\omega_{o}}{\omega}} = \frac{1}{\omega_{o}C_{f}}$$

(2.3)

At frequencies above the 3dB bandwidth of the amplifier  $(f > f_{3dB})$ , the input impedance is resistive. Usually, radiation detector frequencies are above the 3dB bandwidth of the amplifier. This results in resistive input impedance. The sensor capacitance is discharged with the time constant which now can be expressed as  $\tau = R_i C_d = \frac{1}{\omega C_f} C_d$ . The rise time of the charge sensitive amplifier increases with the detector capacitance. Even though the amplifier response time can be longer than the sensor current pulse, it is always required to be faster than the peaking time of the pulse shaper.

#### 2.2.2 Pulse Shaper

The pulse shaper is used to achieve two seemingly conflicting goals. The first goal is to increase the signal-to-noise ratio by restricting the bandwidth. A large bandwidth will increase the noise without increasing the signal. The pulse shaper takes a narrow pulse and turns it into a broader pulse with a gradually rounded peak. Figure 4 shows the input and output waveforms of a pulse shaper.

Figure 4: Input and Output Waveforms of the Pulse Shaper [3]

The pulse shaper transforms a short pulse into a longer pulse with a rounded peak. The pulse shaping is also necessary for the ADC. The input pulse to the ADC cannot be too short, and it should have a gradually rounded peak since the ADC takes

a finite time to acquire the signal. Occasionally the pulse shaper is integrated into the ADC.

The second goal is to limit the pulse width, in order, to measure consecutive signal pulses without pileup or overlap. A tradeoff exists due to the fact that reducing the signal pulse width will increase the signal rate but at the expense of higher noise. It is necessary to find balance between these conflicting goals. Optimum shaping depends on the application. Sometimes, the primary consideration is to reduce noise whereas other times a high signal rate becomes the more important design aspect.

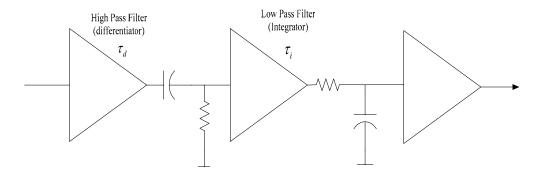

A very simple implementation of the pulse shaper is shown in figure 5. This design consists of a high pass filter (differentiator) followed by a low pass filter (integrator). The high pass filter sets the duration of the pulse by introducing a decay time constant of  $\tau_d$ , while the low pass filter increases the rise time to reduce the noise bandwidth. The key design parameters in this simple pulse shaper implementation are low frequency bound, high frequency bound and signal attenuation.

Figure 5: A Simple Pulse Shaper Using CR Differentiator as a High Pass Filter and a RC Integrator as a Low Pass Filter

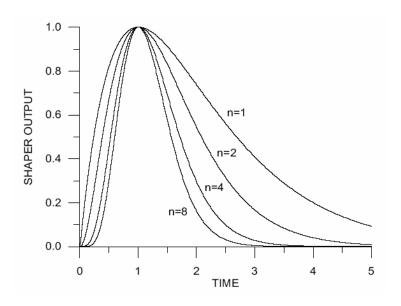

After the output waveform of a simple CR-RC shaper peaks, it returns to baseline very slowly. If the pulse is made more symmetric, higher signal rates for the same peak time can be achieved. A simple way to do this is by increasing the number of integrators causing the integration time to become smaller than the differentiation time with the purpose of keeping the same peaking time. This is illustrated in figure 6. Peaking time is a very important design parameter since it affects the noise bandwidth, and it should also accommodate the sensor response time.

Figure 6: Pulse Shaper Output vs. Number of Integrators [3]

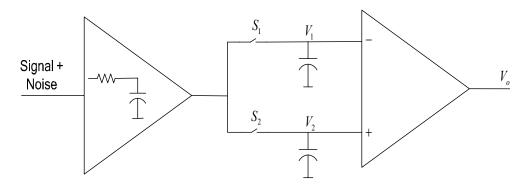

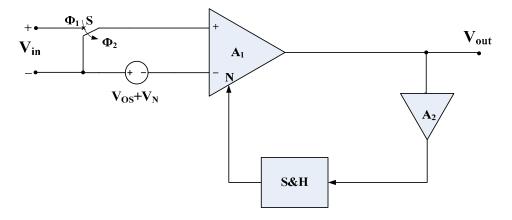

Another type of pulse shaper which is used widely in integrated circuits is the correlated double sampler. This circuit is shown in figure 7. Signals are superimposed on slowly fluctuating baseline noise. To remove the baseline fluctuations, the baseline is sampled before signal. Then, the signal plus baseline is sampled. These two samples are subtracted from each other to give the signal. The pre-filter is necessary to limit the noise bandwidth of the system. Filtering after the

sampler is ineffective since noise fluctuations faster than the sample time will not be removed.

Figure 7: Correlated Double Sampling Pulse Shaper

# **Chapter 3: Amplifier Architectures**

Operational amplifiers are one of the most important building blocks of many different circuits and systems. Different amplifiers are used in a wide range of applications for different purposes such as high speed amplification, filtering, or simply providing a DC bias. This chapter briefly reviews different amplifier architectures such as telescopic cascode differential amplifier, folded cascode differential amplifier and the gain boosted folded cascode amplifier. Emphasis will be on folded cascode and telescopic cascode amplifiers which are used later in this dissertation.

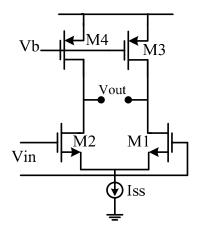

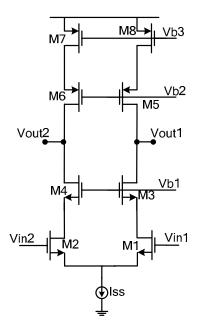

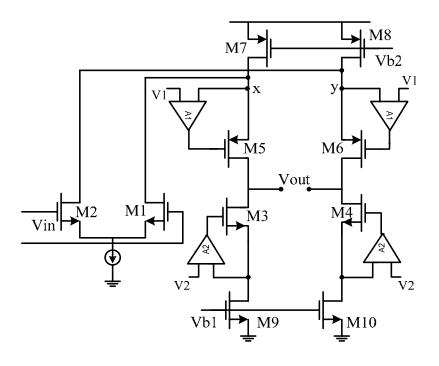

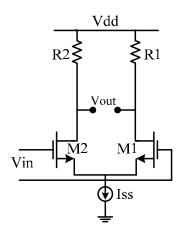

#### 3.1 Telescopic Cascode Differential Amplifier

Telescopic cascode structures are used to increase the gain by stacking transistors [4]-[6]. Consider the simple differential amplifier shown in figure 8. The gain of this circuit is equal to  $g_{m1}(r_{o1}||r_{o3})$ , which is the transconductance of the input transistor times the output resistance of the circuit. The gain of this circuit is relatively low and may not be enough for many applications. To increase the gain the differential cascode topology can be used. Cascoding increases the gain by increasing the output resistance. One way to increase the gain for the simple differential amplifier shown in figure 8 is to increase the output impedance of both NMOS and PMOS devices. This is done by cascoding two NMOS and two PMOS transistors as shown in figure 9. This circuit is called the telescopic cascode

differential amplifier [7] and has a gain equal to  $g_{m1} [(g_{m3}r_{o3}r_{o1})||(g_{m5}r_{o5}r_{o8})]$ , which is the transconductance of the input transistor multiplied by the output impedance of the NMOS cascode in parallel with the output impedance of the PMOS cascode.

Figure 8: Simple Differential Amplifier

Figure 9: Telescopic Cascode Operational Amplifier

This circuit is a good amplifier, exhibiting a moderate gain. The only drawback of this circuit is its limited output swing when it is in the feedback loop. In some applications such as analog to digital converters the output and input are shorted

together during some portion of the operation and the amplifier is in a unity gain feedback. When a unity gain feedback is applied to the differential cascode amplifier shown in figure 9,  $M_1$  and  $M_3$  must be in saturation region in order for the amplifier to function correctly. As we know for an NMOS transistor to be in saturation,  $V_{ds} \geq V_{gs} - V_{th} \text{ or equivalently } V_{gd} \leq V_{th}. \text{ Thus equations (3.1) and (3.2) hold for } M_1 \text{ and } M_3.$

$$V_{in1} \le V_{b1} - V_{gs3} + V_{th1} \tag{3.1}$$

$$V_{out1} \ge V_{b1} - V_{th3} \tag{3.2}$$

The output and input are shorted together when we have unity gain feedback so  $V_{out1} = V_{in1}$ . From the above relations the following relationship is derived.

$$V_{b1} - V_{th3} \le V_{out1} \le V_{b1} - V_{gs3} + V_{th1}$$

(3.3)

As can be seen from equation (3.3) the voltage range is equal to

$V_{\rm max}-V_{\rm min}=V_{th1}-\left(V_{gs3}-V_{th3}\right)$ . This voltage range is less than  $V_{th1}$ . This means that if the output swing is more than this voltage range then  $M_1$  and  $M_3$  will enter the triode region. This is not desired so this circuit is not a good candidate for applications where a large output swing is needed. Even if we have a closed loop gain of larger than one, output swing is still limited.

### 3.2 Folded Cascode Differential Amplifier

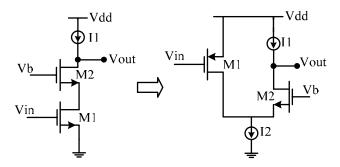

As seen in the previous section telescopic cascode amplifiers have a limited swing specially when used in a unity gain feedback. In order to solve the headroom drawback of the telescopic cascode op amps, folded cascode op amps are used [7]. Figures 10 and 11 show how a telescopic cascode amplifier is transformed into a folded cascode amplifier. The upper PMOS cascode is modeled by a current source as shown in figure 10.

Figure 10: Transformation of a Telescopic Cascode with NMOS Input to a Folded Cascode

Figure 11: Transformation of a Telescopic Cascode with PMOS Input to a Folded Cascode

As mentioned in the previous section, the drawback of the telescopic cascode circuit is that its swing with unity gain feedback is limited. If the output node swings up more than the threshold voltage of the input transistor, the gate voltage of the input transistor will increase by  $V_{th}$  with respect to its drain voltage which is fixed and it

will enter triode region. If the input device is replaced by the opposite type it will still change the input voltage signal to current and inject it to the source of the output device. This time the difference is if output swing is larger than  $V_{th}$ , the input device will not enter triode region.

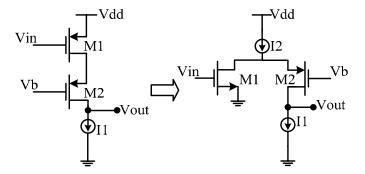

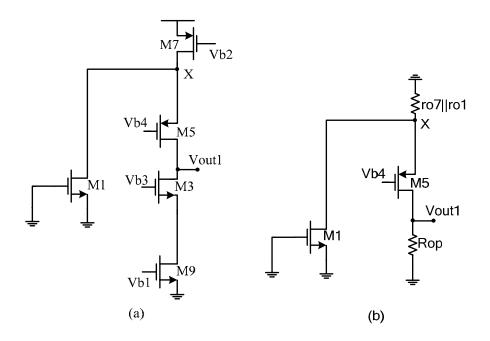

The folding idea can be applied to the telescopic cascode differential pair as can be seen in figure 12. There are no problems in applying a unity gain feedback to the folded cacode differential amplifier. The reason is that in the telescopic cascode in figure 12(a), for  $M_1$  to be in saturation the input common mode level cannot exceed  $V_{b1} - V_{gs3} + V_{th1}$ . We can not short the input to output as it would cause the common mode level to exceed  $V_{b1} - V_{gs3} + V_{th1}$ . But as can be seen in the folded cascode differential amplifier in figure 12(b), for  $M_1$  to be in saturation the input CM level cannot be less than  $V_{b1} - V_{gs3} + \left|V_{thp}\right|$ . Therefore the folded cascode differential amplifier can be designed to allow shorting the input and output together. The differential folded cascode differential amplifier is shown in figure 13.

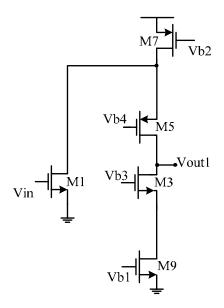

In order to find the gain of the folded cascode amplifier,  $R_{\rm out}$  and  $G_{\rm m}$ , the amplifier's overall output resistance and transconductance, are calculated first. For this purpose consider the half circuit of the folded cascode differential amplifier in figure 13 as shown in figure 14.

Figure 12: (a) Telescopic Cascode Operational Amplifier (b) Folded Cascode Operational Amplifier

Figure 13: Folded Cascode Differential Amplifier

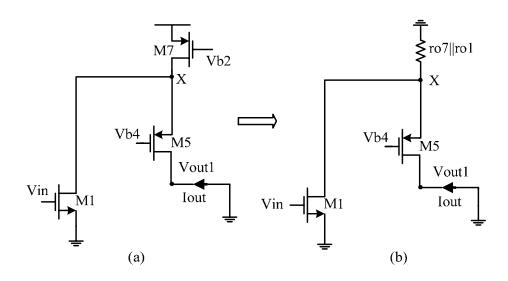

In order to find the overall transconductance,  $G_m$  for the folded cascode differential amplifier, consider the circuit shown in figure 15 in which the output is shorted to ground. As can be seen  $M_3$ ,  $M_9$  are shorted to ground, so the equivalent circuit is as shown in figure 16(a).

Figure 14: The Equivalent Half Circuit for the Folded Cascode Differential Amplifier

Figure 15: Half Circuit of the Folded Cascode Differential Amplifier used to Calculate the Transconductance

The resistance seen looking up at node X is  $r_{\sigma_1} \| r_{\sigma_1}$  as shown in figure 16(b).

The resistance seen looking down at node X is  $\frac{1}{g_{m5}} \| r_{o5}$  which is approximately  $\frac{1}{g_{m5}}$ .

The current entering node X through the drain of  $M_{_1}$  is  $g_{_{m1}}V_{_{in}}$ . This current is split

between the two resistances seen looking up and down at node X. Since the resistance seen at this node looking down,  $\frac{1}{g_{m5}}$  is a lot smaller than the resistance seen at this node looking up,  $r_{o7} \| r_{o1}$ , almost all the current entering this node, enters  $M_5$ . So the output current  $I_{out}$  is approximately equal to  $g_{m1}V_{in}$ . This tells us that the overall trans-conductance of the circuit,  $G_m$  is equal to  $g_{m1}$ , which is the transconductance of  $M_1$ .

Figure 16: Equivalent Half Circuit used to Calculate the Overall Transconductance

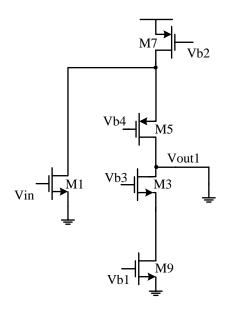

Now in order to calculate the output resistance  $R_{out}$  seen at the output node, consider the circuit shown in figure 17(a) in which the input is shorted. The lower NMOS cascode consisting of transistors  $M_3$  and  $M_9$  is replaced by its equivalent resistance,  $R_{ON} = g_{m3} r_{o3} r_{o9}$  as shown in figure 17(b). The resistance seen at node X looking up is  $r_{o7} \| r_{o1}$  as seen in figure 17(b).

Figure 17: Equivalent Half Circuits used to Calculate the Output Resistance

The output resistance  $R_{out}$  is given by equation (3.4) as follows:

$$R_{out} = R_{OP} \| \left( g_{m5} r_{o5} \left( r_{o1} \| r_{o7} \right) \right) = g_{m3} r_{o3} r_{o9} \| \left( g_{m5} r_{o5} \left( r_{o1} \| r_{o7} \right) \right)$$

(3.4)

Now that both the transconductance and output resistance of the folded cascode differential amplifier are known, the midband gain of the circuit is derived in equations (3.5) and (3.6).

$$A_{v} = G_{m}R_{out} \tag{3.5}$$

$$A_{v} = g_{m1} \left( g_{m3} r_{o3} r_{o9} \left\| \left( g_{m5} r_{o5} \left( r_{o1} \left\| r_{o7} \right) \right) \right) \right)$$

(3.6)

### 3.3 Introduction to the concept of Gain Boosting

In section 3.1, cascoding was discussed as a way to increase the output resistance and hence increase the gain of the operational amplifier. In order to be comprehensive the gain boosting technique is briefly discussed in this section [8]-[12]. We start by calculating the output impedance of the gain boosted cascode circuit.

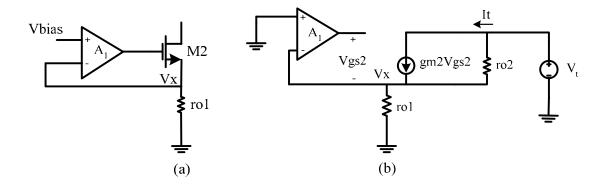

Figure 18(a) shows a gain boosted NMOS cascode in which the lower transistor is replaced by its equivalent output resistance for simplicity.

Figure 18: (a) Gain Boosted Cascode Amplifier (b) Small Signal Model for the Gain Boosted Cascode used to Find the Output Resistance

From the small signal model shown in figure 18(b), it can be verified that  $R_{out}$ , the output resistance after applying the feedback is approximately  $A_1g_{m2}r_{o1}r_{o2}$ . By analyzing the small signal model, we have the following:

$$I_{t} = g_{m_{2}}V_{gs_{2}} + \frac{(V_{t} - V_{x})}{r_{o2}}$$

$$V_{gs_{2}} = -(A_{1} + 1)V_{x}$$

$$V_{x} = I_{t}r_{o1}$$

From these equations the output resistance  $R_{out}$  is given in equation (3.7) and derived as follows:

$$V_{t} = I_{t} r_{o2} \left( 1 + g_{m_{2}} r_{o1} (A+1) + \frac{r_{o1}}{r_{o2}} \right)$$

$$\frac{V_{t}}{I_{t}} = r_{o1} + r_{o2} + g_{m_{2}} r_{o1} r_{o2} (A+1)$$

(3.7)

Since  $A_1 \gg 1$  and  $r_{o1}$ ,  $r_{o2} \ll g_{m_2} r_{o1} r_{o2} A_1$ , equation (3.7) is simplified to equation (3.8).

$$R_{\text{out}} = \frac{V_t}{I_t} = A_1 g_{m2} r_{o1} r_{o2}$$

(3.8)

In other words, the output resistance of the cascode after connecting the booster amplifier is  $A_1$  times that of the cascode without the booster. So adding the booster increases the output resistance of the cascode and multiplies it by the gain of the booster.

At this point the transconductance for the simple gain boosted cascode shown in figure 18 is derived. The circuit and the small signal equivalent model for it are shown in figure 19.

Figure 19: (a) Gain Boosted Cascode Circuit (b) Small Signal Equivalent Circuit to Calculate the Overall Trans-conductance

The transconductance is derived as follows:

$$I_{out} = g_{m1}V_{in} + \frac{V_{X}}{r_{o1}} \Rightarrow V_{X} = r_{o1} \left( I_{out} - g_{m1}V_{in} \right)$$

$$I_{out} = g_{m2}V_{gs2} - \frac{V_{X}}{r_{o2}}$$

$$V_{gs2} = -A_{1}V_{X} - V_{X} = -(A_{1}+1)V_{X}$$

$$I_{out} = -g_{m2} \left( A_{1}+1 \right) V_{X} - \frac{V_{X}}{r_{o2}}$$

$$I_{out} = \left( -g_{m2} \left( A_{1}+1 \right) - \frac{1}{r_{o2}} \right) V_{X} = \left( -g_{m2} \left( A_{1}+1 \right) - \frac{1}{r_{o2}} \right) r_{o1} \left( I_{out} - g_{m1}V_{in} \right)$$

$$I_{out} \left( \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1} + 1 \right) = V_{in}g_{m1} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}$$

$$G_{m} = \frac{I_{out}}{V_{in}} = \frac{g_{m1} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}}{\left( \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1} + 1 \right) - \frac{g_{m1}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} = \frac{g_{m1}}{\left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1} + 1} \right) - \frac{g_{m1}}{r_{o1}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} = \frac{g_{m1}}{r_{o1}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1} + 1 \right) - \frac{g_{m1}}{r_{o1}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} = \frac{g_{m1}}{r_{o1}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} + \frac{g_{m1}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} + \frac{g_{m1}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} + \frac{g_{m1}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} + \frac{g_{m1}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} + \frac{g_{m1}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} + \frac{g_{m1}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} + \frac{g_{m2}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o1}} + \frac{g_{m2}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o2}} + \frac{g_{m2}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o2}} + \frac{g_{m2}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o2}} + \frac{g_{m2}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o2}} + \frac{g_{m2}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o2}} + \frac{g_{m2}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right) + \frac{1}{r_{o2}} \right) r_{o2}} + \frac{g_{m2}}{r_{o2}} \left( g_{m2} \left( A_{1}+1 \right)$$

Equation (3.9) is simplified as follows and the transconductance  $G_m$  is given by equation (3.10).

$$G_{m} = \frac{g_{m1}}{1 + \frac{1}{\left(g_{m2}(A_{1} + 1) + \frac{1}{r_{o2}}\right)r_{o1}}} \approx g_{m1}$$

(3.10)

It can be seen from these calculations that the gain boosting technique increases the output resistance by multiplying it by the booster gain  $A_1$  but it does not change the transconductance of the circuit appreciably.

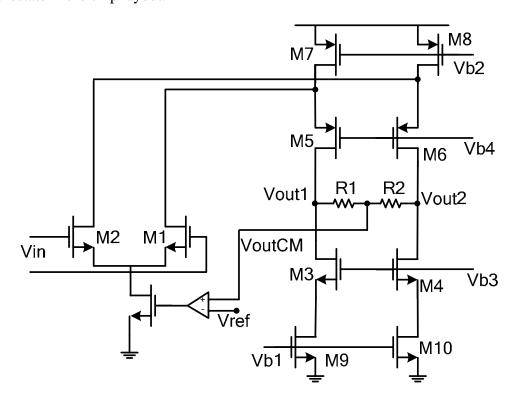

### 3.3.1 Folded Cascode Gain Boosted Amplifier

The gain boosting technique can be incorporated in both differential telescopic and folded cascode circuits to get a high gain from a single stage amplifier [13]. Although this technique is not used in this dissertation, it will be briefly discussed for the sake of completeness. As discussed in section 3.1, by cascoding transistors we can get a higher resistance. There is always a limit to the number of the stages that can be cascoded since it will limit the output swing.

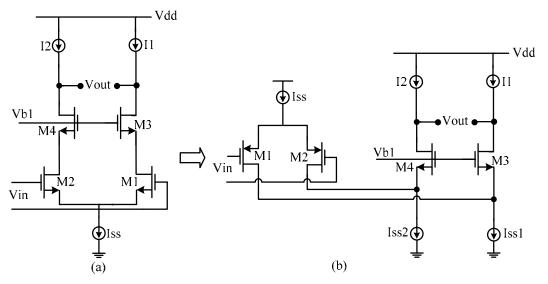

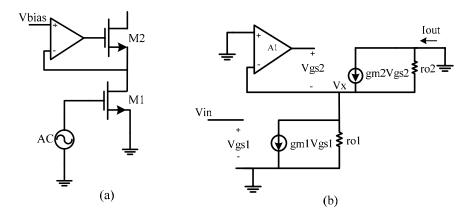

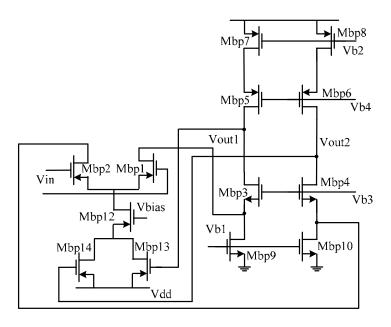

In order to get a higher gain from a one-stage differential folded cascode amplifier, the gain boosting technique can be applied to the amplifier as shown in figure 20. The gain boosting technique is applied to the upper PMOS cascode and the lower NMOS cascode the same way it was applied to the cascode in figure 19(a). Since the signals at the inputs of the two upper and lower gain boosting amplifiers are differential, the upper single ended output amplifiers with the DC gain of  $A_1$  can be replaced by one differential output amplifier with a DC gain of B. The same can be applied to the two lower single ended output gain boosting amplifiers with the DC gain of  $A_2$ . These two single ended amplifiers can be replaced by one differential output amplifier with a DC gain of  $A_2$  as shown in figure 21.

24

Figure 20: Gain Boosting Technique Applied to a Folded Cascode Differential Amplifier

Figure 21: Single-ended Gain Boosting Amplifiers Replaced by Differential Counterparts

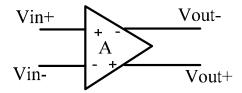

In order to understand this better consider the fully differential amplifier shown in figure 22.

Figure 22: Fully Differential Amplifier

Assuming the voltage at the positive input  $V_{\scriptscriptstyle in+}$  changes by  $\Delta V$  then the voltage at the corresponding output shown by  $V_{\scriptscriptstyle out-}$  changes by  $-A\Delta V$ . Since the input signals to the fully differential amplifiers used as the boosters are differential, if  $V_{\scriptscriptstyle in+}$  changes by  $\Delta V$ , the voltage at the negative input,  $V_{\scriptscriptstyle in-}$  changes by  $-\Delta V$ . Since the input voltage to the negative input is  $-\Delta V$  the corresponding output voltage shown by  $V_{\scriptscriptstyle out+}$  changes by  $+A\Delta V$ . The following relationship holds for the differential input and output voltages as shown below.

$$V_{out} = V_{out+} - V_{out-} = 2A\Delta V$$

$$V_{_{in}}=V_{_{in+}}-V_{_{in-}}=\Delta V-(-\Delta V)=2\Delta V$$

In which  $V_{out}$  is the differential output voltage and  $V_{in}$  is the differential input signal. So the following relationship holds between the input and output and output voltages.  $V_{out} = V_{out+} - V_{out-} = AV_{in} = A(V_{in+} - V_{in-})$

Now in figure 20, assuming the signals at the input of the upper boosters at nodes X and Y are then the signals at the output of the boosters are respectively,  $A_1V_X$  and  $A_1V_Y$ . Since the input signals for the boosters are coming form the fully differential folded cascode amplifier these signals are differential. So if one increases

with the amount of  $\Delta V$  the other decreases with the same amount. Hence, the voltage at the output of the single ended boosters are respectively  $A_1\Delta V$  and  $-A_1\Delta V$ . Comparing these output voltages with the output voltages of the fully differential amplifier shown above, it can be seen that the fully differential amplifier has the same outputs. As a result the two single ended boosters can be replaced with one fully differential booster in order to save space and to reduce the amount of redundant circuitry.

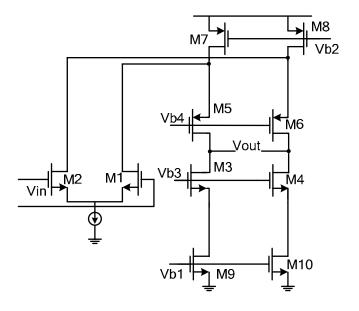

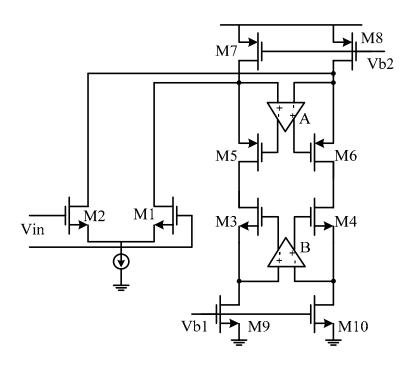

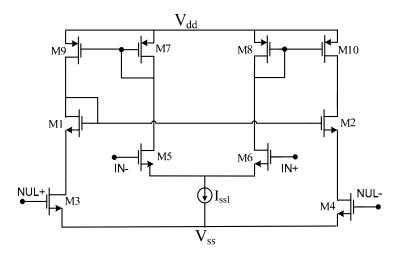

The gain boosted folded cascode amplifier shown in figure 21 consists of a main amplifier and two boosters. Each booster is a differential folded cascode amplifier just like the main amplifier without the boosters. The upper booster, which from now on will be referred to as the NMOS booster is just like the core amplifier. The lower booster will be referred to as the PMOS booster. PMOS input transistors are chosen for the PMOS booster as shown in figure 23. This choice is due to the fact that the input voltages for this booster, the drain voltages of  $M_9$  and  $M_{10}$ , are small and close to the ground voltage. In order to make sure that the input transistors of the boosters are always on PMOS input transistors are chosen for the lower booster and for this reason it is referred to as the PMOS booster.

Figure 23: PMOS Booster Schematic

Using the output resistance and transconductance of the folded cascode differential amplifier calculated in section 3.2, the output resistance and transconductance for the gain boosted folded cascode differential amplifier can be derived. It was shown in section 3.3 that the gain boosting technique multiplies the output resistance by the gain of the gain boosting amplifier and it does not change the transconductance.

The output resistance for the folded cascode differential amplifier is the parallel combination of the resistance seen at the output looking up and down. The resistance seen looking down is  $g_{m3}r_{o3}r_{o9}$  which is the resistance for the lower NMOS cascode. Now that we are boosting the gain of this lower cascode, the output resistance seen looking down is multiplied by the gain of the gain boosting amplifier, B. So the resistance seen looking down is  $g_{m3}r_{o3}r_{o9}B$ .

The resistance seen looking up before applying the gain boosting technique was  $(g_{m5}r_{o5}(r_{o1}||r_{o7}))$ . By applying the gain boosting technique the resistance seen looking up is multiplied by the gain of the booster, A. So the resistance seen looking up is  $(g_{m5}r_{o5}(r_{o1}||r_{o7}))A$ . The output resistance of the gain boosted folded cascode  $R_{out}$  is the parallel combination of the resistance seen looking up and the resistance seen looking down at the output node. The output resistance is given by equation (3.11) while the transconductance is the same as the transconductance of the input transistor and is given by equation (3.12).

$$R_{out} = g_{m3} r_{o3} r_{o9} B \left\| \left( g_{m5} r_{o5} \left( r_{o1} \right\| r_{o7} \right) \right) A$$

(3.11)

$$G_{\scriptscriptstyle m} = g_{\scriptscriptstyle m1} \tag{3.12}$$

The midband gain for the gain boosted folded cascode differential amplifier is shown in equation (3.13).

$$A_{\rm v} = G_{\rm m} R_{\rm out}$$

$$A_{v} = g_{m1} \left( g_{m3} r_{o3} r_{o9} B \left\| \left( g_{m5} r_{o5} \left( r_{o1} \left\| r_{o7} \right) \right) A \right) \right.$$

(3.13)

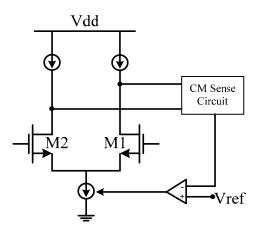

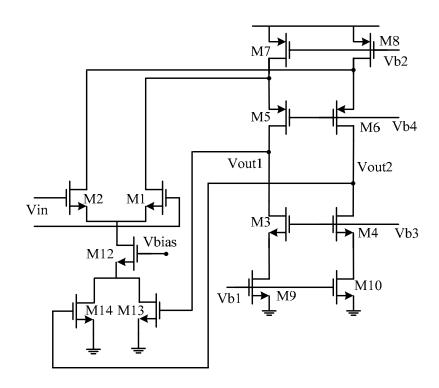

### 3.4 Common Mode feedback

In high gain differential circuits, depending on the load, the output common mode (CM) level may not be well defined. In a differential pair with resistive loads, the output common mode voltage is well defined. If current sources replace the resistive loads then the common mode output voltage is not defined. The reason is that the output node is a node where two drains are connected together, which is like connecting two current sources in series. There is some resistance between the

common node of the two current sources and ground. If these current sources are perfectly matched one of them will source current to the output node and the other will sink the same current and the output bias voltage will be some undefined voltage between  $V_{dd}$  and  $V_{ss}$ , but if they are not matched, the difference between the currents will flow through the output resistance and the output voltage will become very large or very small. A differential feedback circuit can not define the common mode voltage level because it does not detect the common mode level at the output. To solve this problem, a common mode feedback circuit can be used which detects the common mode level of the output, compares it with a reference voltage and returns the error to the bias network to change the current of the tail current source. This ensures that the desired output common mode level is obtained as shown in figure 24.

Figure 24: Common Mode Feedback Circuit Applied to a Simple Differential Amplifier

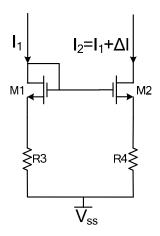

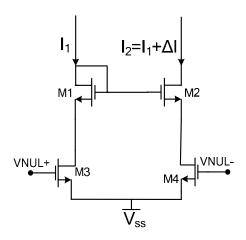

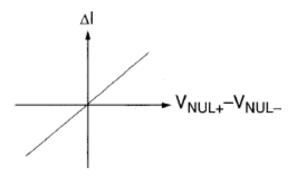

Recall that the common mode output voltage is  $(V_{out1} + V_{out2})/2$ , so the common mode feedback circuit can be two resistors in series [7], [14], [15], which connect the outputs together as shown in figure 25. It can be seen that if  $R_1$  and  $R_2$  have the same value, the voltage of the common node of  $R_1$  and  $R_2$  will be equal to