### ABSTRACT

# Title of Document: GALLIUM NITRIDE NANOWIRE BASED ELECTRONIC AND OPTICAL DEVICES. Abhishek Motayed, Doctor of Philosophy, 2007 Directed By: Professor J. Melngailis, Department of Electrical and Computer Engineering

Gallium nitride nanowires have significant potential for developing nanoscale emitters, detectors, and biological/chemical sensors, as they possess unique material properties such as wide direct bandgap (3.4 eV), high critical breakdown field, radiation hardness, and mechanical/chemical stability. Although few results of individual GaN nanowire devices have been reported so far, most of them often utilize fabrication processes unsuitable for large-scale nanosystems development and do not involve fundamental transport property measurements. Understanding the transport mechanisms and correlating the device properties with the structural characteristics of the nanowires are of great importance for realizing high performance devices.

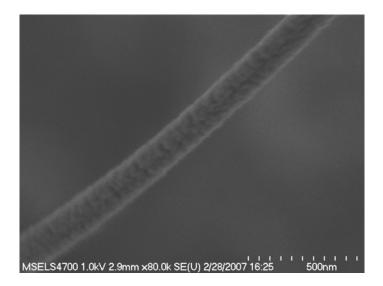

Focused ion beam induced metal deposition was used to make individual GaN nanowire devices, and assessment of their electrical properties was performed. The nanowires were grown by direct reaction of Ga and NH<sub>3</sub>, with diameters ranging from

80 nm to 250 nm and lengths up to 200  $\mu$ m. Dielectrophoretic alignment was used to assemble these nanowires from a suspension on to a large area pre-patterned substrate. A fabrication technique, utilizing only conventional microfabrication processes, has been developed for realizing robust nanowire devices including field effect transistors (FETs), light emitting diodes (LEDs), Schottky diodes, and fourterminal structures. Nanowire FETs with different gate geometries were studied, namely bottom gate, omega-backgate, and omega-plane gate structures. Utilizing omega-backgated FETs, transconductance as high as  $0.34 \times 10^3 \,\mu\text{S mm}^{-1}$  has been obtained. Room temperature field effect electron mobility in excess of 300 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> have been exhibited by a nanowire FET, with a 200 nm diameter nanowire and Si substrate as the backgate. The observed reduction of mobility in the GaN nanowire FETs with decreasing diameter of the nanowire is attributed to the surface scattering. Electron beam backscattered diffraction revealed that the grain boundary scattering is present in some of the nanowires. Temperature dependent mobility measurements indicated that the ionized impurity scattering is the dominant mechanism in the transport in these nanowires. GaN nanoLEDs have been realized by assembling the ntype nanowires on a p-GaN epitaxial layer using dielectrophoresis. The resulting p-n homojunctions exhibited 365 nm electroluminescence with a full width half maximum of 25 nm at 300 K.

# GALLIUM NITRIDE NANOWIRE BASED ELECTRONIC AND OPTICAL DEVICES

By

Abhishek Motayed.

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2007

Advisory Committee: Professor John Melngailis, Chair Professor Thomas E. Murphy Professor Robert W. Newcomb Professor Lourdes Salamanca-Riba Professor. S. Noor Mohammad Dr. Albert V. Davydov © Copyright by Abhishek Motayed 2007

## Preface

This dissertation contains 8 chapters. Most of the results discussed here have been published and presented in numerous referred journals and conferences. Significant details have been added to the chapters 4 and 6, besides the published results. The publications and conference presentations germane to the results are listed chapter wise.

#### Chapter 2: Gallium Nitride Nanowire Growth and Characterization

M. He, **A. Motayed**, and S. N. Mohammad, "Phase separations of single-crystal nanowires grown by self-catalytic chemical vapor deposition method," J. Chem. Phys. 26, 064704 (2007).

#### **Chapter 3: Focused Ion Beam Assisted Fabrication of Nanowire Devices**

-A. Motayed, A. Davydov, M. Vaudin, I. Levin, J. Melngailis, and S. Mohammad, "Fabrication of GaN-based Nanoscale Device Structures Utilizing Focused Ion Beam Induced Pt Deposition," J. Appl. Phys. 100, 024306 (2006).

**-A. Motayed**, A.V. Davydov, M. Vaudin, J. Melngailis, and S. N. Mohammad, "Fabrication and Characterization of Nanoscale Devices from Gallium Nitride Nanowires Utilizing Ion Beam Induced Metal Deposition Techniques," 47<sup>th</sup> Annual Minerals, Metals & Materials Society Electronic Materials Conference, Santa Barbara, CA, USA, 2005.

Chapter 4, 5, and 6: Electric Field Assisted Alignment of Nanowires, Fabrication of Nanowire Devices and Process Optimization, and GaN Based Nanowire Electronic Devices -A. Motayed, M. He, A. V. Davydov, J. Melngailis, and S. N. Mohammad, "Realization of Reliable GaN Nanowire Transistors Utilizing Dielectrophoretic Alignment Technique," J. Appl. Phys. 100, 114310 (2006).

-A. Motayed, A. Davydov, M. He, J. Melngailis, and S. Mohammad, "A Simple Model for Dielectrophoretic Alignment of GaN Nanowires," JVST B. 25, 120 (2007).

-A. Motayed, M. Vaudin, A. V. Davydov, J. Melngailis, M. He, and S. N. Mohammad, "Diameter dependent transport properties of gallium nitride nanowire field effect transistors," Appl. Phys. Lett. 90, 043104 (2007).

-A. Motayed, A. V. Davydov, J. Melngailis, and S. N. Mohammad, "Large Scale Assembly of GaN Nanowires Using Dielectrophoretic Alignment," International Semiconductor Device Research Symposium, Bethesda, MD, USA, 2005.

#### Chapter 7: Gallium Nitride Nanowire-substrate UV Light Emitting Diodes:

**-A. Motayed**, M. Vaudin, A. V. Davydov, J. Melngailis, M. He, and S. N. Mohammad "365 nm Operation of n-GaN nanowire p-GaN substrate homojunction light emitting diodes," Appl. Phys. Lett. 90, 183120 (2007).

-A. Motayed, A. V. Davydov, M. He, J. Melngailis, and S. N. Mohammad, "Dielectrophoretic Alignment and Fabrication Technique for Realizing GaN Nanowire Devices," Materials Research Society Spring Meeting, Boston, MA, USA 2006.

## Dedication

To the memory of my parents, who showed me how to dream,

and

to my wife, Urmi, for being there with me.

## Acknowledgements

During past six years I have had the pleasure of knowing and working with many wonderful and remarkable people. Without their help, guidance, and support, I would not have been able to finish what I started. I would like to thank Dr. John Melngailis for being so supportive of me and my research. His constant encouragement and guidance were truly invaluable. He always made himself available whenever I needed his suggestion or help. I express my sincere gratitude to Dr. S. N. Mohammad, for giving me the very first opportunity to prove myself. Without him, nothing of this would have been possible. His constant inspirations were the most invaluable.

This dissertation would never have been successful without the support of the wonderful people at the National Institute of Standards and Technology. Special thanks go to Dr. Daniel Josell, Dr. William Boettinger, Dr. Frank Gayle, and Dr. Carol Handwerker for giving me such a wonderful opportunity. Working under Dr. Albert Davydov at NIST was such a memorable experience. He has been a wonderful mentor and a friend. He taught me numerous aspects of materials science and many other things, which made this project possible. My appreciation goes to Dr. Norman Sanford, Dr. John Schlager, and Dr. Chris Bertness for their help. Special thanks to Dr. Babak Nikoobakht, Siddarth Sundaresan, and Sandy Clagett for helping me with various things.

My sincere gratitude to my committee members, Dr. Salamanca-Riba, Dr. Newcomb, and Dr. Murphy for their time and valuable suggestions.

My deepest appreciation goes to my wife, Urmi, for supporting me through all these years. She made the most difficult times of my life quite livable. I am thankful to my family, especially my uncle, Asok Motayed, for providing me the much needed support.

I express my gratitude to Mr. John Barry of IREAP for teaching me how to use the FIB tool. University of Maryland administrative officials, especially Dr. Dan Ballon, Maria Hoo, and Nancy L. Gong deserve recognition for helping me with quite a few important things.

## **Table of Contents**

| Preface                                                              | ii  |

|----------------------------------------------------------------------|-----|

| Dedication                                                           | iv  |

| Acknowledgements                                                     | v   |

| List of Tables                                                       | ix  |

| List of Figures                                                      |     |

| Chapter 1: Introduction                                              |     |

| 1.1 Nanowires and Nanotubes                                          |     |

| 1.2 Semiconducting Nanowires and Nanorods                            |     |

| 1.3 Gallium Nitride and Related Alloys                               |     |

| 1.4 Strategies for Developing Nanowire Devices                       |     |

| 1.5 Contributions and Accomplishments                                | 11  |

| Chapter 2: Gallium Nitride Nanowire Growth and Characterization      |     |

| 2.1 Growth of Nitrides                                               |     |

| 2.2 Description of Catalyst Free Nitride Nanowire Growth             |     |

| 2.3 Growth Mechanism.                                                |     |

| 2.4 Characterization of GaN Nanowire                                 |     |

| 2.4.1 Field Emission Scanning Electron Microscopy                    |     |

| 2.4.2 X-ray Diffraction                                              |     |

| 2.4.3 Electron Backscattered Diffraction                             |     |

| 2.4.4 Energy Dispersive X-ray Analysis                               |     |

| 2.4.5 Transmission Electron Microscopy                               |     |

| 2.4.6 Polarization-resolved Photoluminescence Spectroscopy           |     |

| 2.4.7 Cathodoluminescence Spectroscopy                               | 41  |

| Chapter 3: Focused Ion Beam Assisted Fabrication of Nanowire Devices |     |

| 3.1 Focused Ion Beam Induced Metal Deposition Technique              |     |

| 3.2 Experimental Details                                             |     |

| 3.3 Results                                                          |     |

| Chapter 4: Electric Field Assisted Alignment of Nanowires            |     |

| 4.1 Dielectrophoresis – Theoretical Background                       |     |

| 4.2 Designing the Assembly Process                                   |     |

| 4.2.1 Numerical Calculations – Solvent and Frequency Choice          |     |

| 4.2.2 Alignment electrode design – Electrostatic Simulations         |     |

| 4.2.3 Configuration time                                             |     |

| 4.3 Experimental Techniques for Dielectrophoretic Alignment          |     |

| 4.4 Results of Dielectrophoretic Alignment                           | 87  |

| Chapter 5: Fabrication of Nanowire Devices and Process Optimization  |     |

| 5.1 General Fabrication Scheme                                       |     |

| 5.2 Process Optimization                                             |     |

| 5.2.1 Choice of Substrate                                            |     |

| 5.2.2 Alignment Electrode Thickness                                  |     |

| 5.2.3 Metal Contact Schemes                                          |     |

| 5.2.4 Annealing Process                                              |     |

| 5.2.5 Passivation Techniques                                         | 108 |

| Chapter 6: GaN Based Nanowire Electronic Devices                                   | 112 |

|------------------------------------------------------------------------------------|-----|

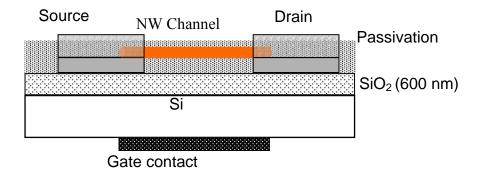

| 6.1 Bottom Gate Devices                                                            | 116 |

| 6.1.1 Back-gated FET Characteristics                                               | 119 |

| 6.1.2 Parameter Extraction                                                         |     |

| 6.1.3 Numerical Simulation of Nanowire-Gate Capacitance                            | 130 |

| 6.1.4 One-Dimensional Modeling                                                     | 137 |

| 6.2 Top Gate Devices                                                               | 150 |

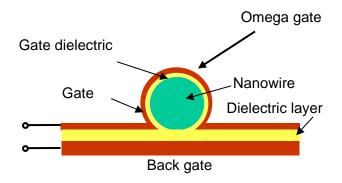

| 6.2.1 Omega-Backgate Geometry                                                      | 151 |

| 6.2.2 Omega-Plane Gate                                                             | 154 |

| 6.3 Four-Terminal Resistivity Structures                                           |     |

| 6.4 Fundamental Transport Properties and Correlation to Structural Characteristics | 6   |

|                                                                                    | 167 |

| Chapter 7: Gallium Nitride Nanowire-substrate UV Light Emitting Diodes             | 172 |

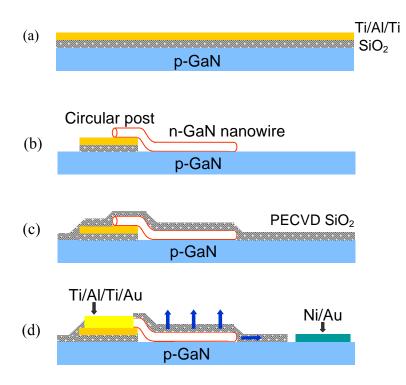

| 7.1 Fabrication Procedure for n-nanowire p-substrate GaN Homojunction              | 174 |

| 7.2 Results                                                                        |     |

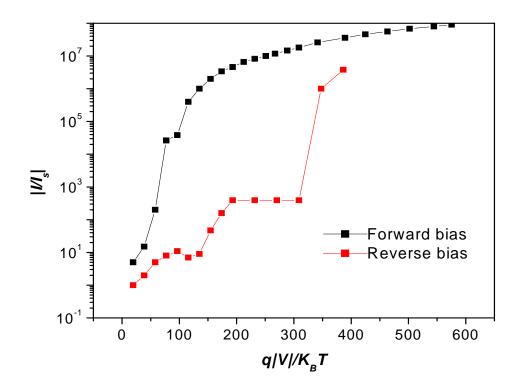

| 7.2.1 Electrical Characteristics                                                   |     |

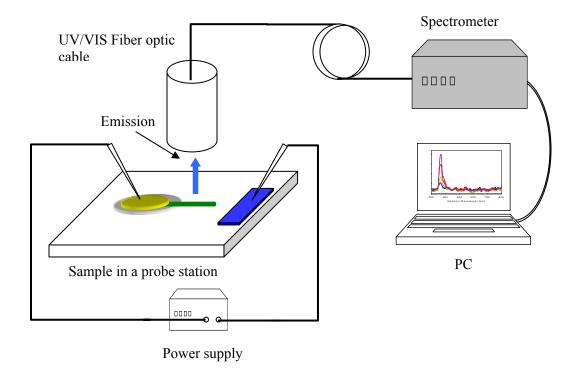

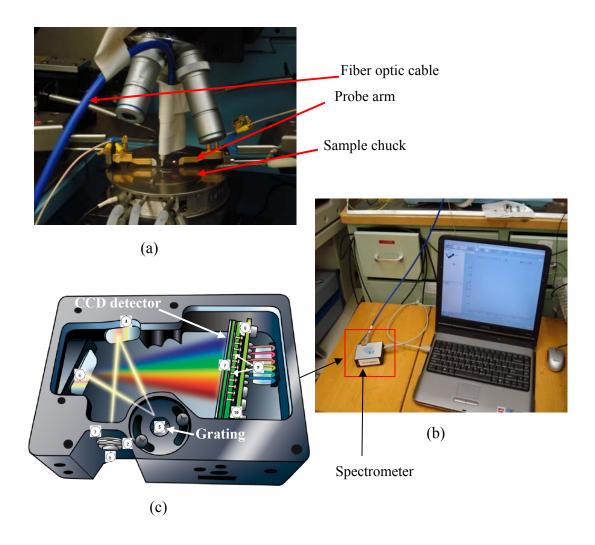

| 7.2.2 Electroluminescence Measurement Setup                                        | 180 |

| 7.2.3 Electroluminescence Characteristics                                          | 182 |

| 7.3 Discussions and Future Directions                                              | 186 |

| Chapter 8: Summary and Conclusions                                                 | 187 |

| 8.1 Concluding Remarks and Future Prospects                                        | 189 |

| Appendices                                                                         |     |

| Appendix A. Standard Cleaning Procedure                                            |     |

| Appendix B. Photolithography Mask Layout                                           |     |

| Appendix C. Photolithography Process Details                                       |     |

| C.1 Dual Resist Lift-off Process                                                   |     |

| C.2 Image Reversal Resist for Mesa Formation                                       |     |

| Appendix D. 1-Dimensional Poisson Solver                                           |     |

| D.1 Gauss Jordan Elimination Technique                                             |     |

| D.2 C++ Implementation of 1-D Poisson Solver                                       |     |

| Bibliography                                                                       | 205 |

## List of Tables

| Table 1.1: Physical properties of Si and other important wide bandgap semiconductors [17].       7                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Table 4.1.</b> Physical parameters used for the calculation of DEP forces for a nanowire in different solvents                                                             |

| <b>Table 5.1</b> : Linear thermal expansion coefficients of different materials.         101                                                                                  |

| <b>Table 5.2</b> : Rise rate for the metal contact annealing, and corresponding device yield.                                                                                 |

| <b>Table 5.3</b> : Deposition parameters for PECVD SiO2                                                                                                                       |

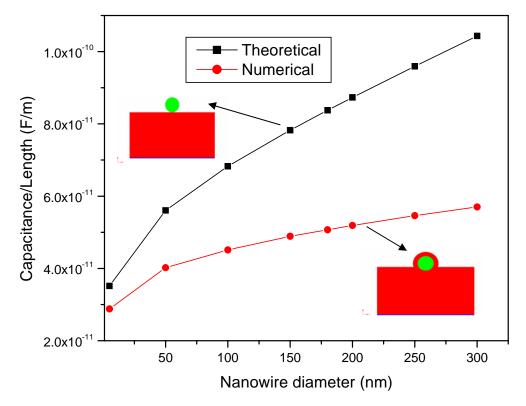

| Table 6.1: Parameters used for capacitance calculations in Maxwell <sup>®</sup>                                                                                               |

| <b>Table 6.2</b> : Comparison of analytical and numerical capacitances for structures shownin Fig. 6.14 and 6.15.136                                                          |

| <b>Table 6.3</b> : Comparison of tranconductances, and normalized transconductances forthe omega-backgate FET, with 200 nm diameter nanowire.154                              |

| <b>Table 6.4</b> : Comparison of FET parameters for convention thin film MOSFETs,Carbon nanowire and Si nanowire FETs, and GaN nanowire FETs obtained in thepresent study.161 |

## List of Figures

| Figure 1.1: Top-down versus bottom-up approach towards nanotechnology                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: An example of hybrid integration – smart, autonomous sensor node. With                                                                   |

| on-board Si processor, chemical/biological sensors realized from nanowires,                                                                          |

| communication components, and photovoltaic cells to generate power, they could                                                                       |

| work without human intervention for indefinite period of time                                                                                        |

| Figure 1.3: Energy band diagram of wurtzite GaN. Direct energy gap is 3.39 eV at                                                                     |

| 300 K                                                                                                                                                |

| Figure 1.4: Lattice constants and bandgap energy for different semiconductors at                                                                     |

| room temperature [18]                                                                                                                                |

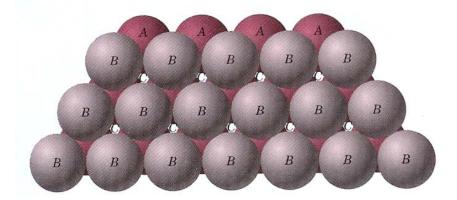

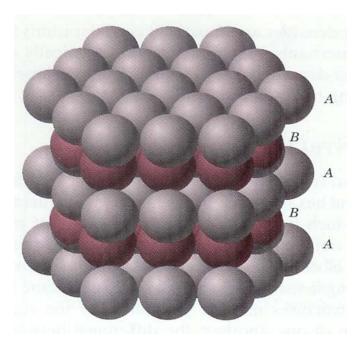

| Figure 2.1: Crystal structure of wurtzite GaN. Basis unit cell is hexagonal closed                                                                   |

| pack (HCP) structure with alternating layers of Ga and N atoms                                                                                       |

| Figure 2.2: Four axes Miller-Bravais coordinate system for HCP structure [19] 15                                                                     |

| Figure 2.3: (a) Different crystallographic direction of the HCP structure. (b)                                                                       |

| Different crystallographic planes for the HCP structure                                                                                              |

| Figure 2.4: The first layer of atoms in a closed packed configuration. A, B, and C                                                                   |

| positions are indicated                                                                                                                              |

| Figure 2.5: The AB stacking sequence for closed-pack atomic planes                                                                                   |

| Figure 2.6: Close-packed plane stacking sequence for HCP structure.         18                                                                       |

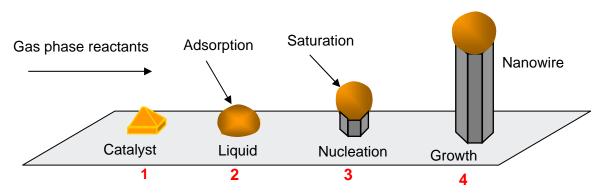

| Figure 2.7: Schematic diagram representing growth steps in VLS growth mechanism.                                                                     |

|                                                                                                                                                      |

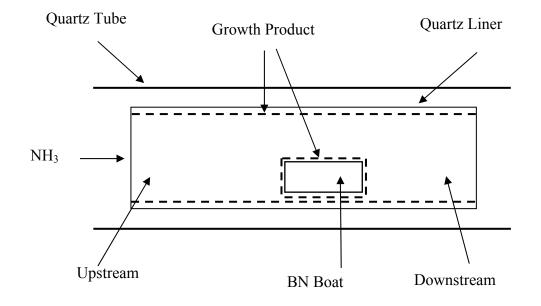

| Figure 2.8: Schematic diagram of the GaN nanowire growth system                                                                                      |

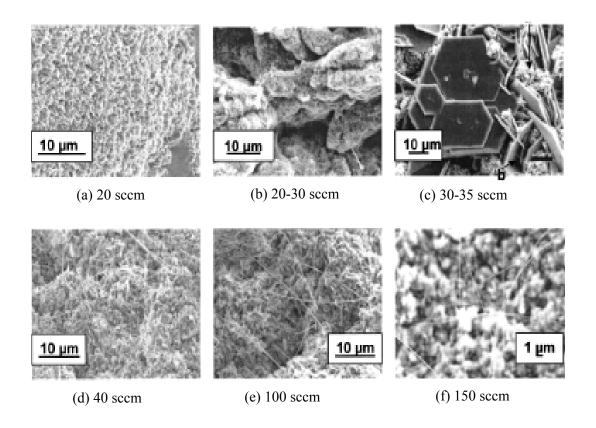

| Figure 2.9: Scanning electron microscope (SEM) images of nanowire growth matrix                                                                      |

| for different ammonia flow rates. (a) 20 sccm, (b) 20-30 sccm, (c) 30-35 sccm, (d) 40                                                                |

| scem, (e) 100 scem, and (f) 150 scem                                                                                                                 |

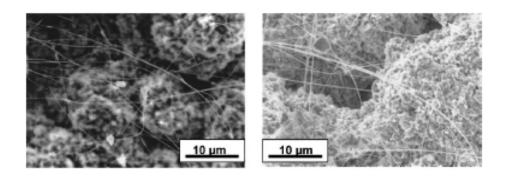

| Figure 2.10: Scanning electron microscope (SEM) images of nanowire growth                                                                            |

| matrix for different growth temperatures. (a) 875 °C, (b) 900 °C, (c) 1000 °C, and (d)                                                               |

| 1100 °C                                                                                                                                              |

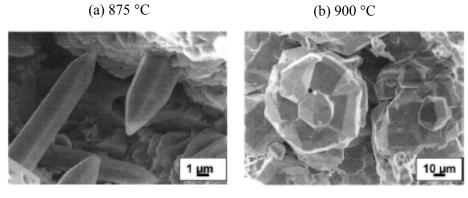

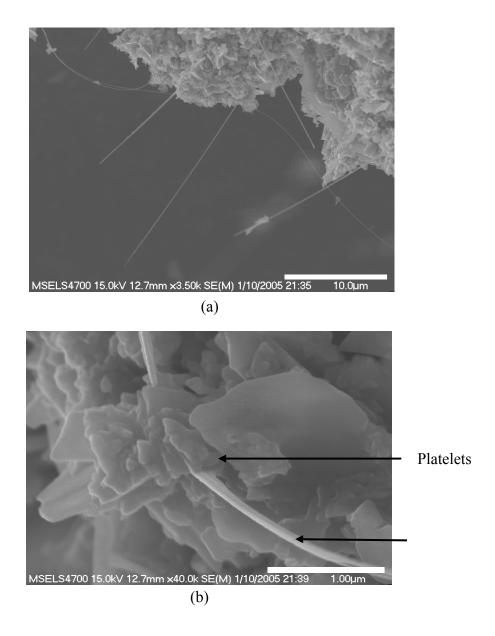

| Figure 2.11: (a) Field emission SEM (FESEM) scans of growth matrix after                                                                             |

| collecting from the growth chamber. (b) FESEM scans of nanowires growing from                                                                        |

| the edges of the GaN platelets. 27                                                                                                                   |

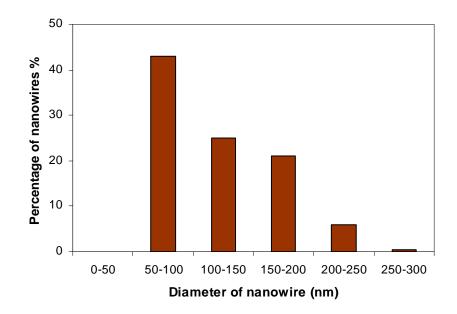

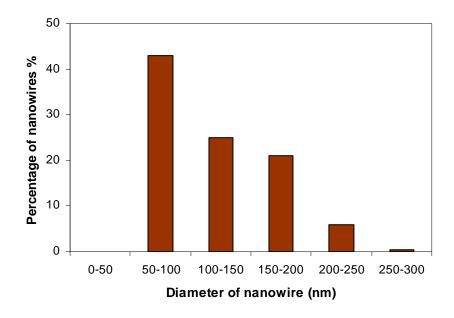

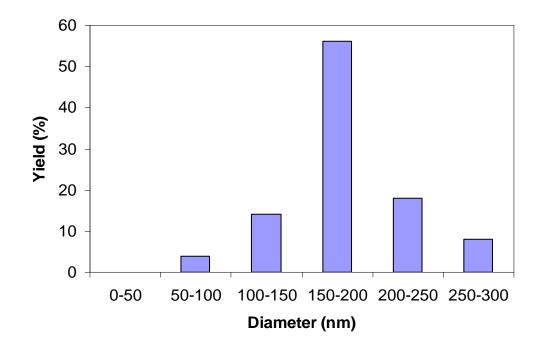

| <b>Figure 2.12:</b> Diameter distribution of nanowires as observed in the growth matrix. 29                                                          |

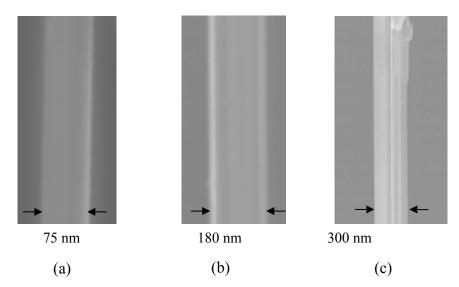

| <b>Figure 2.13:</b> Representative structural characteristics of nanowires observed in different diameter ranges (a) 50 nm $(b)$ 150 nm $(c)$ 250 nm |

| different diameter ranges (a) 50 nm – 100 nm, (b) 150 nm – 200 nm, (c) 250 nm – 300 nm. Diameters of the nanowires are indicated below               |

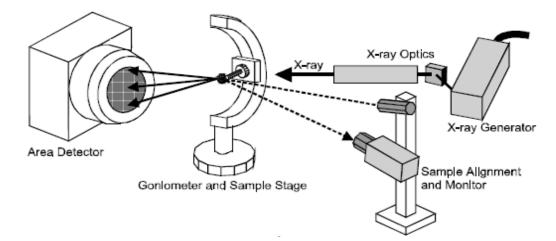

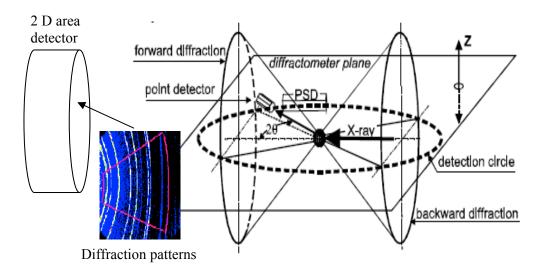

| Figure 2.14: The schematic representation of a typical 2D XRD system                                                                                 |

| Figure 2.14. The schematic representation of a typical 2D ARD system                                                                                 |

| the diffraction cones by the 2 D detector are visible as arc on the detector plane 31                                                                |

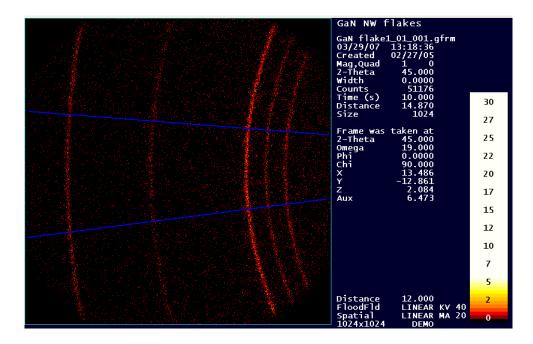

| <b>Figure 2.16:</b> The 2D area diffraction pattern from GaN flake with nanowires on                                                                 |

| Brukeraxs <sup>®</sup> D8 2D diffractometer. The blue lines indicate the chi direction                                                               |

| integration                                                                                                                                          |

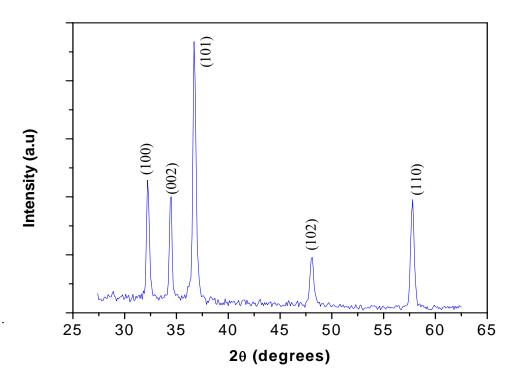

| <b>Figure 2.17:</b> The $\theta$ -2 $\theta$ diffraction of the flake after integrating the 2D spectrum in the                                       |

| chi direction (shown by blue lines in Fig. 2.16)                                                                                                     |

|                                                                                                                                                      |

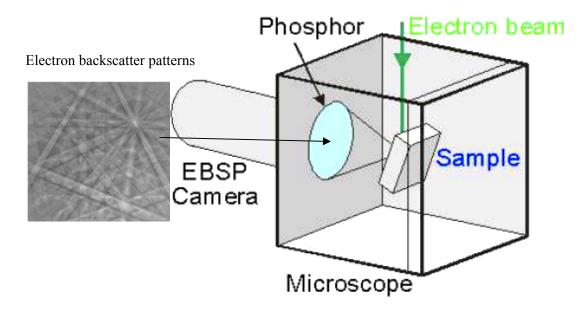

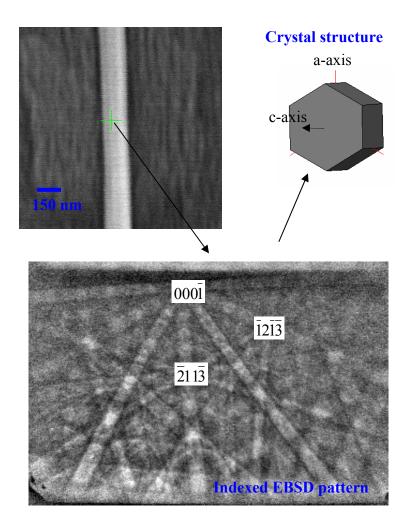

| <b>Figure 2.18:</b> The schematic representation of an EBSD system. The technique is carried out inside an SEM chamber                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

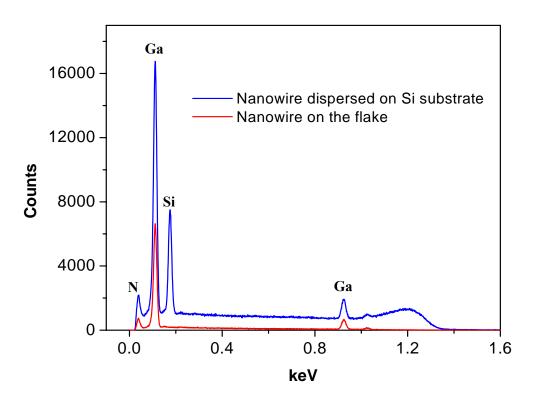

| <b>Figure 2.19:</b> EBSD pattern from a GaN nanowire (shown in the top). Important zone axes are pointed. The crystal structure solution is shown on the right hand side 35<br><b>Figure 2.20:</b> EDX spectra from GaN nanowires. The red curve in from nanowire on the flake and the blue is from nanowire dispersed on a Si substrate |

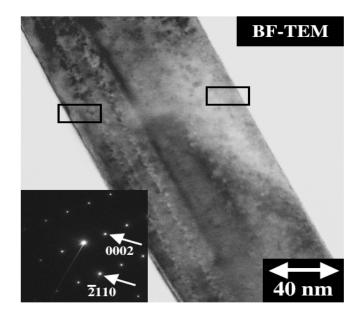

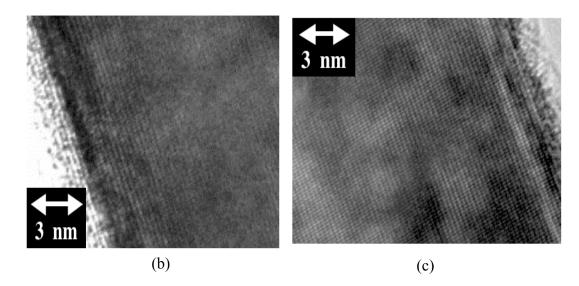

| zone axis, (inset) selected area diffraction (SAD) pattern acquired with an effective aperture of $\sim$ 200nm, (b) and (c) high-resolution lattice images (HR-TEM) acquired of the left and right sides, respectively, of the crystal as marked in (a)                                                                                  |

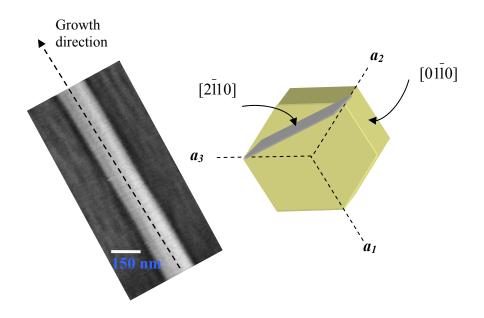

| with c axis pointing out the plane of the paper. The a-plane $(2\overline{1}10)$ is denoted by the                                                                                                                                                                                                                                       |

| gray line, and the nanowires grow normal to that plane                                                                                                                                                                                                                                                                                   |

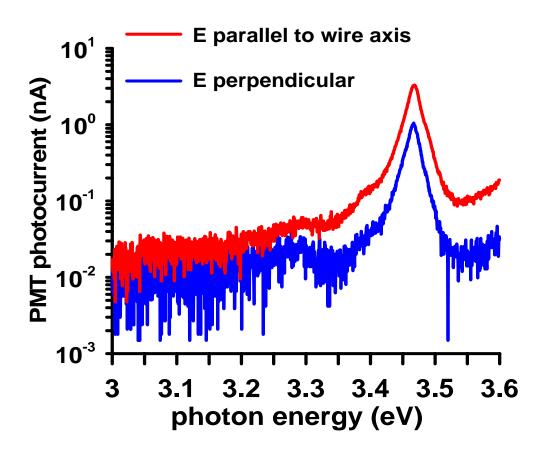

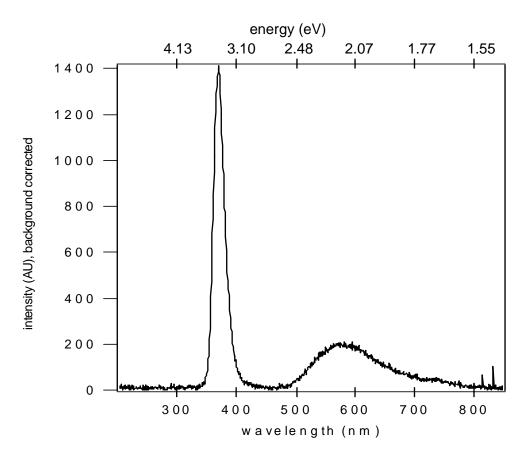

| broader peak centered at 575 nm (2.2 eV) is due to defect-related emission processes.                                                                                                                                                                                                                                                    |

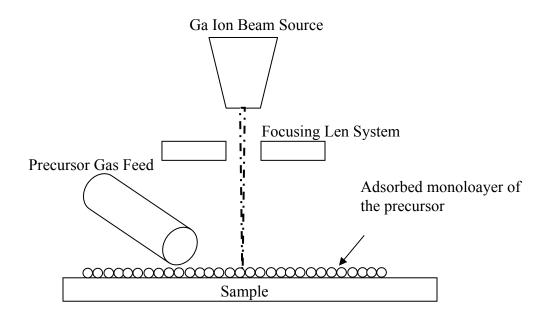

| Figure 3.1: Schematic diagram of focused ion beam (FIB) system                                                                                                                                                                                                                                                                           |

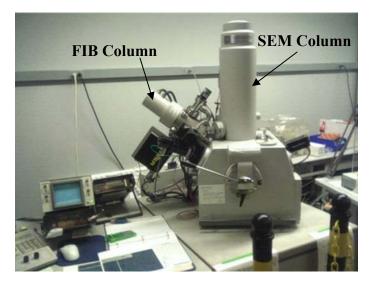

| Figure 3.2: FEI 620 Dual Beam (FIB/SEM) system.    45                                                                                                                                                                                                                                                                                    |

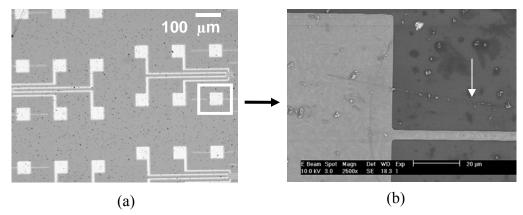

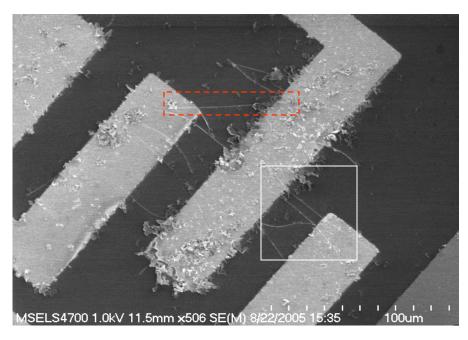

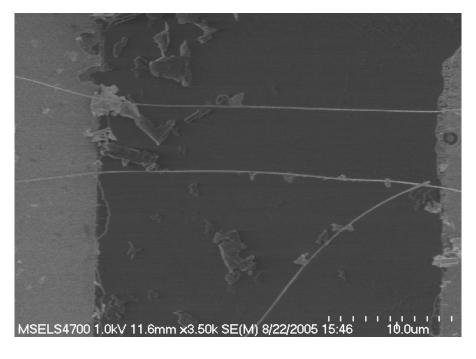

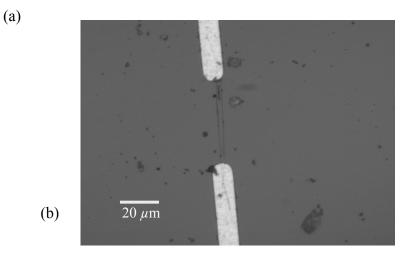

| <b>Figure 3.3:</b> (a) Optical image of pre-patterned substrate with Cr/Au patterns. (b) SEM image of nanowires dispersed close to the pads (indicated with a white arrow).                                                                                                                                                              |

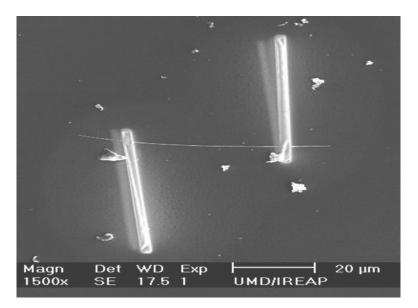

| <b>Figure 3.4:</b> SEM image of a GaN nanowire with FIB deposited Pt metal contacts at the two ends                                                                                                                                                                                                                                      |

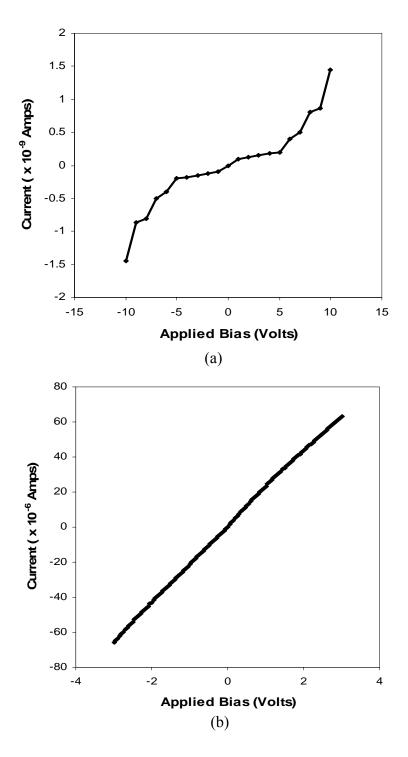

| <b>Figure 3.5:</b> (a) Measured I-V characteristics of GaN nanowire with as-deposited FIB deposited Pt contacts. (b) Measured I-V characteristics of the same nanowire after                                                                                                                                                             |

| annealing the Pt contacts at 500 °C for 30 s in UHP Argon                                                                                                                                                                                                                                                                                |

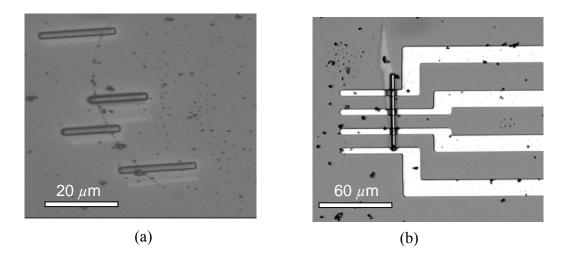

| four-terminal structure. (b) Optical microscope image of a FIB-deposited Pt line on a<br>Cr/Au pre-patterned four-terminal structure                                                                                                                                                                                                     |

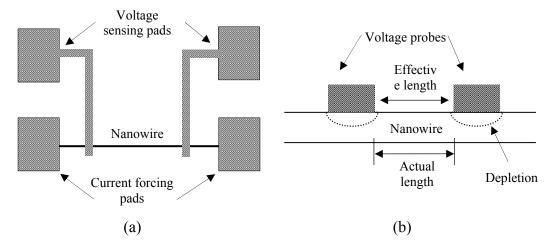

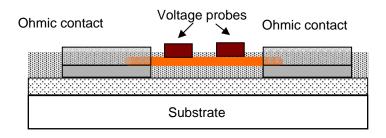

| Figure 3.7: (a) Schematic diagram of the four-terminal structure used to measure the                                                                                                                                                                                                                                                     |

| resistivity of the nanowires. (b) Schematic of the nanowire with the voltage probes,                                                                                                                                                                                                                                                     |

| the depletion region associated with the voltage probes shown by the dashes line 52                                                                                                                                                                                                                                                      |

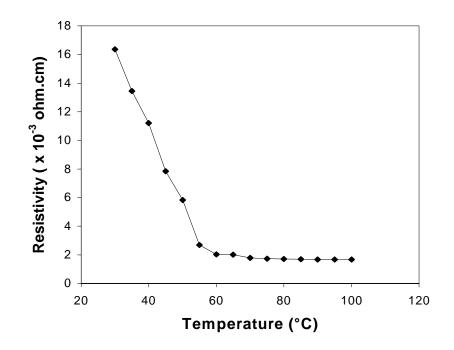

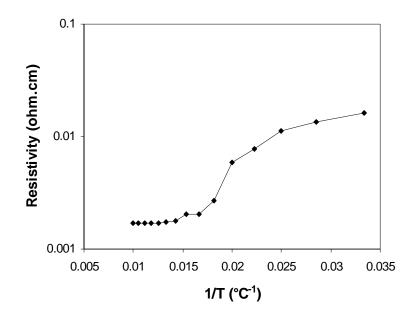

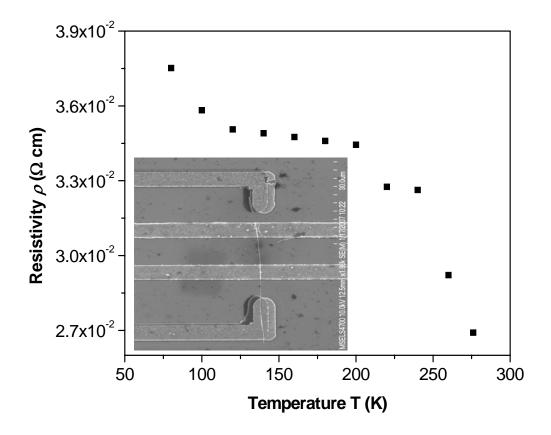

| <b>Figure 3.8:</b> Plot of resistivity (ρ) vs. temperature of a GaN nanowire                                                                                                                                                                                                                                                             |

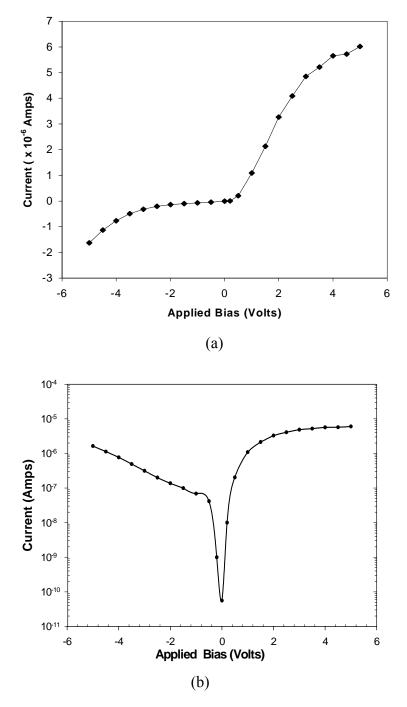

| <b>Figure 3.10:</b> (a) I-V characteristics of FIB-deposited Pt-GaN Schottky diode (b) semi-log plot of I vs. V of the diode                                                                                                                                                                                                             |

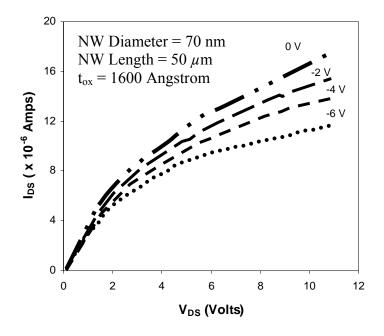

| <b>Figure 3.11:</b> $I_{DS}$ versus. $V_{DS}$ as a function of the gate voltage ( $V_G$ ) applied to the Si backgate. Gate voltage is indicated on each curve. 57                                                                                                                                                                        |

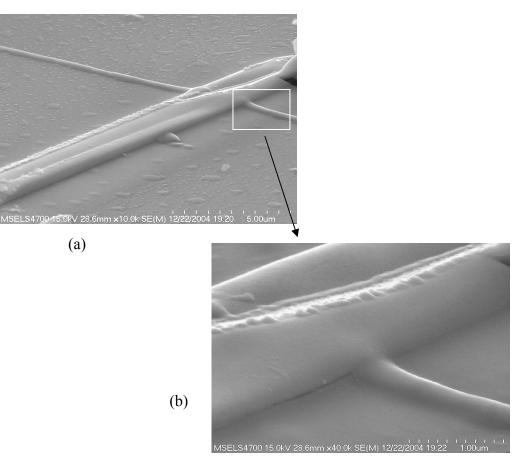

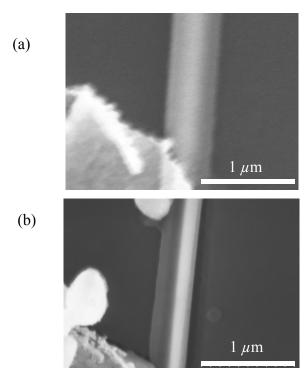

| Figure 3.12: (a) SEM image of a FIB deposited Pt line on GaN showing the volume                                                                                                                                                                                                                                                          |

| swelling underneath the contact region. (b) High resolution SEM scan showing the swelling of the nanowire underneath the contact region                                                                                                                                                                                                  |

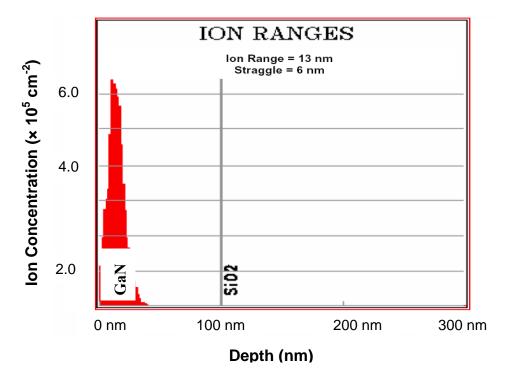

| <b>Figure 3.13:</b> Implantation profile for 30 KeV Ga <sup>+</sup> ions in GaN                                                                                                                                                                                                                                                          |

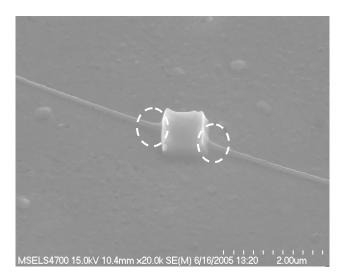

| Figure 3.14: Electron beam induced deposited Pt contact to GaN nanowire. Swelling                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| of the nanowire at the ends of the contacts is indicated by white broken circles 61                                                                                   |

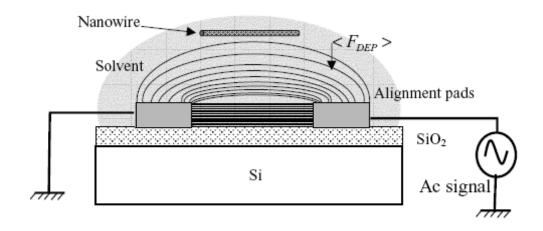

| Figure 4.1: Schematic representation of dielectrophoretic alignment of nanowires                                                                                      |

| using a solvent medium                                                                                                                                                |

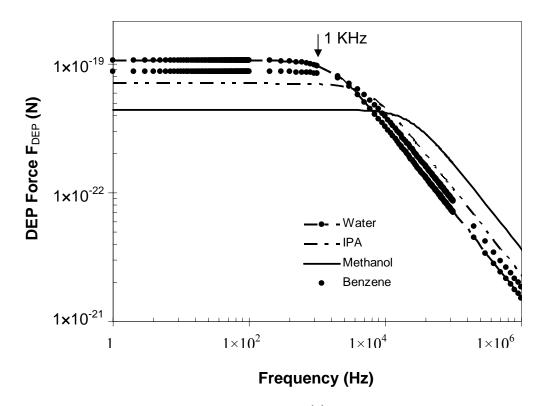

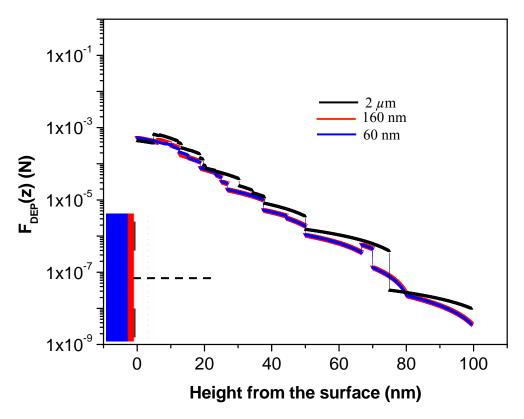

| <b>Figure 4.2:</b> Calculated DEP force experience by a nanowire (100 nm diameter and 50                                                                              |

| $\mu$ m in length) in different dispersing medium as a function of the alignment voltage.                                                                             |

| The drop in the DEP force for different solvents starts around 1 KHz                                                                                                  |

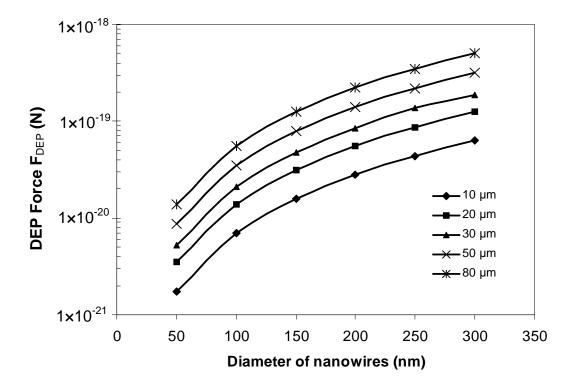

| <b>Figure 4.3:</b> Calculated DEP force variation as a function of nanowire diameter and                                                                              |

| length. The alignment frequency is set to 1 KHz and the dispersing medium is IPA. 69                                                                                  |

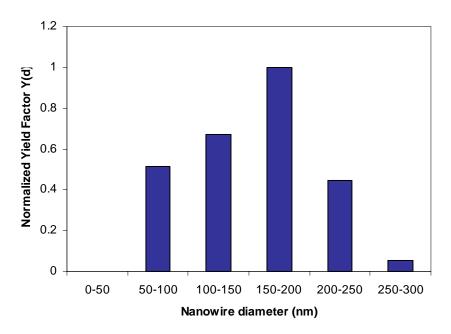

| Figure 4.4: Normalized yield factor as a function of nanowire diameter for DEP                                                                                        |

| process in IPA                                                                                                                                                        |

| <b>Figure 4.5:</b> Diameter distribution of nanowires as observed in the growth matrix71                                                                              |

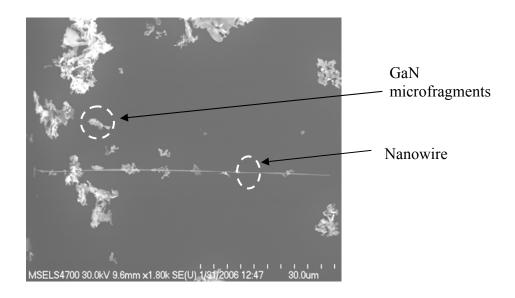

| Figure 4.6: GaN nanowires and platelets as seen on a Si substrate, which is                                                                                           |

| characteristic of the dispersion                                                                                                                                      |

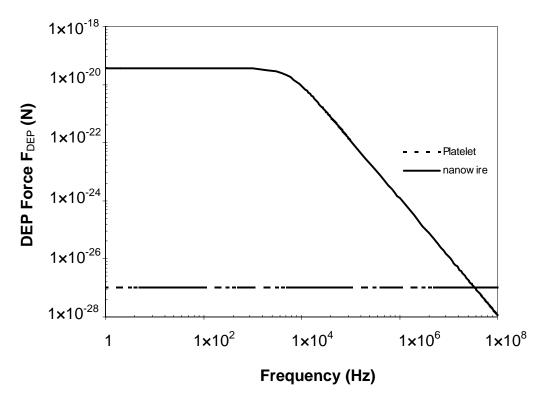

| <b>Figure 4.7:</b> Calculated DEP force experience by a nanowire (100 nm diameter and 50                                                                              |

| $\mu$ m in length) and a spherical fragment (2 $\mu$ m diameter) in IPA with alignment                                                                                |

| frequency at 1 KHz                                                                                                                                                    |

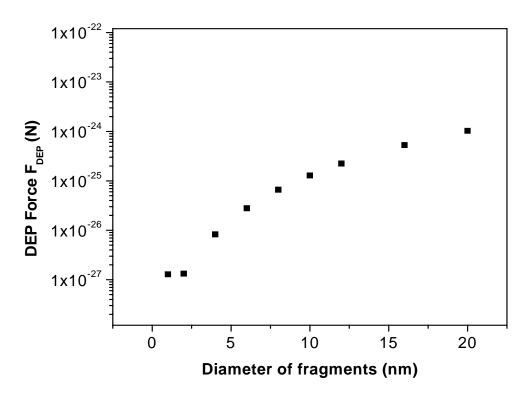

| Figure 4.8: Variations of the DEP force experienced by spherical GaN                                                                                                  |

| microfragments in IPA as a function of their diameters, with alignment frequency set                                                                                  |

| to 1 KHz                                                                                                                                                              |

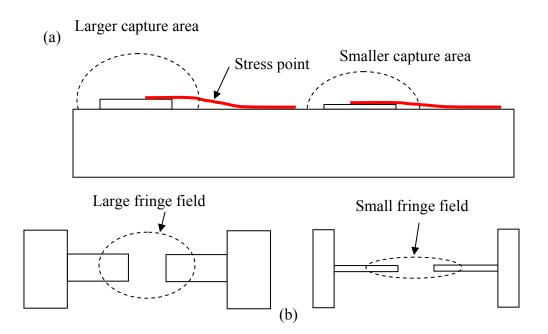

| Figure 4.9: (a) Bending of the nanowire across the edge of the electrode. (b) Large                                                                                   |

| area patterns versus small area patterns                                                                                                                              |

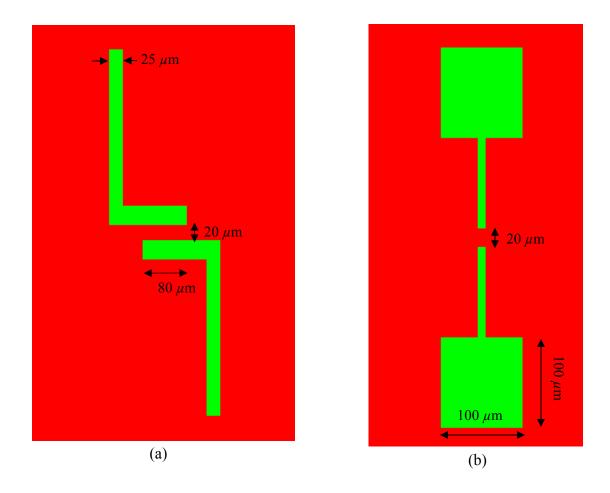

| Figure 4.10: (a) Electrode design 1. (b) Electrode design 2.76                                                                                                        |

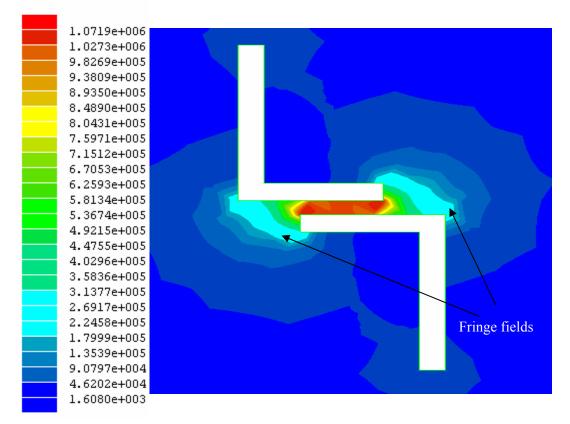

| <b>Figure 4.11:</b> Electric field intensity for design 1 on the substrate plane (x-y plane) for                                                                      |

| +10 V and -10V connected to top and bottom electrode respectively77                                                                                                   |

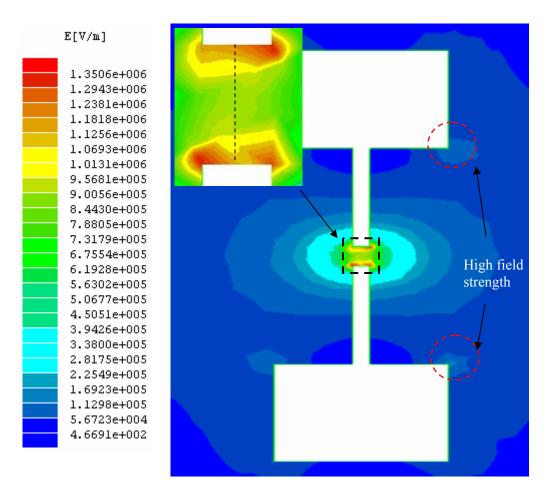

| Figure 4.12: Electric field intensity for design 2 on the substrate plane (x-y plane) for                                                                             |

| +10 V and -10V connected to top and bottom electrode respectively. (inset) Field                                                                                      |

| intensity in the region marked by the black box                                                                                                                       |

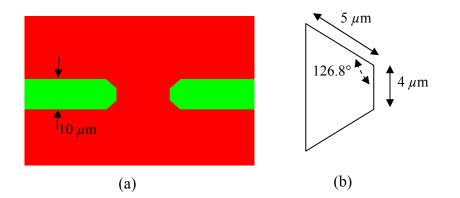

| <b>Figure 4.13:</b> (a) Improved electrode design with beveled edges. (b) Dimensions and angles of the edge                                                           |

|                                                                                                                                                                       |

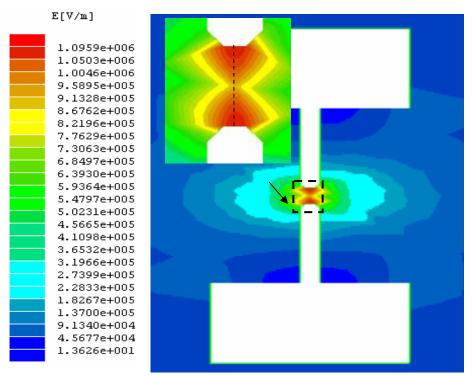

| Figure 4.14: Electric field intensity for beveled edge design. (inset) Field intensity in                                                                             |

| the region marked by the black box                                                                                                                                    |

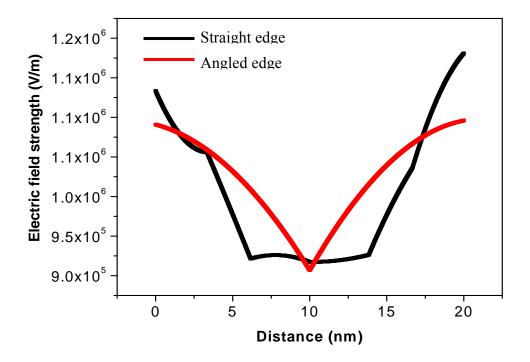

| Figure 4.15: 1D plot of electric field intensity for straight edge and beveled edge                                                                                   |

| design                                                                                                                                                                |

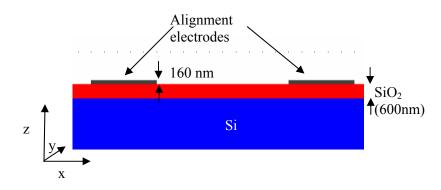

| <b>Figure 4.16:</b> Electrode geometry for field intensity calculation in z direction                                                                                 |

| <b>Figure 4.17:</b> Electric field intensity as a function of the metal pad thickness in the z direction for 20 V bias applied between the pads as shown in the inset |

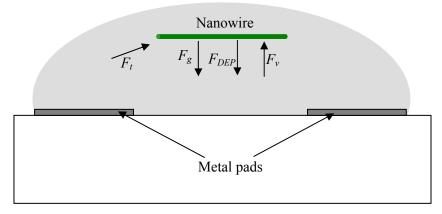

| <b>Figure 4.18:</b> Dominant forces acting on a nanowire floating in a suspension, with                                                                               |

| electric field applied to the alignment pads                                                                                                                          |

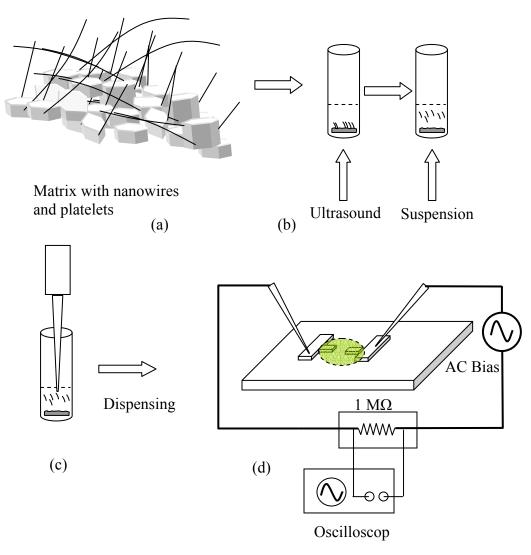

| <b>Figure 4.19:</b> (a) Growth matrix, nanowires and the micro-platelets, (b) formation of                                                                            |

| the suspension through sonication, (c) dispersing the solvent, and (d) setup for DEP                                                                                  |

| alignment                                                                                                                                                             |

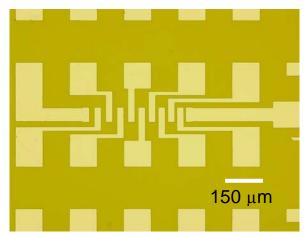

| <b>Figure 4.20:</b> Optical microscope image of interdigitated electrode configuration as in                                                                          |

| design 1                                                                                                                                                              |

| 0                                                                                                                                                                     |

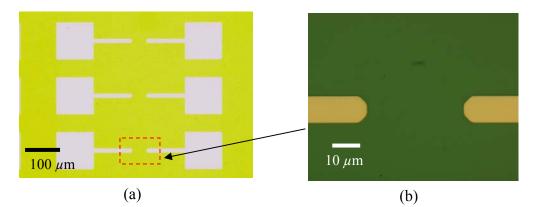

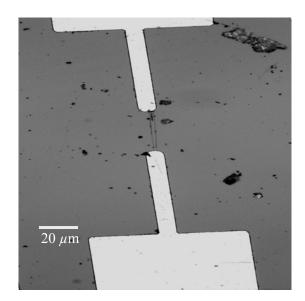

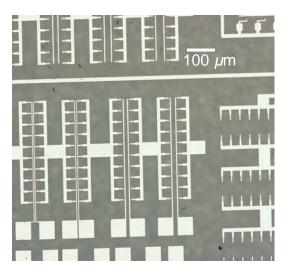

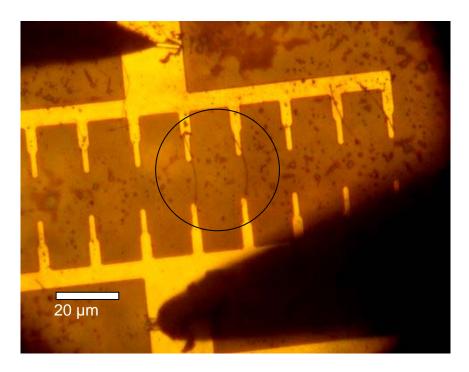

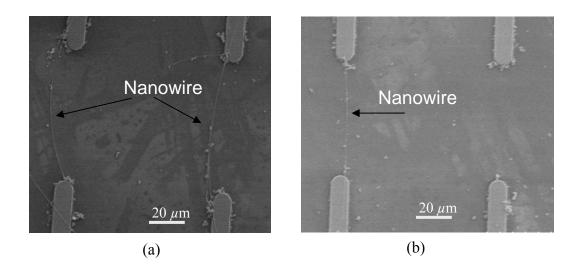

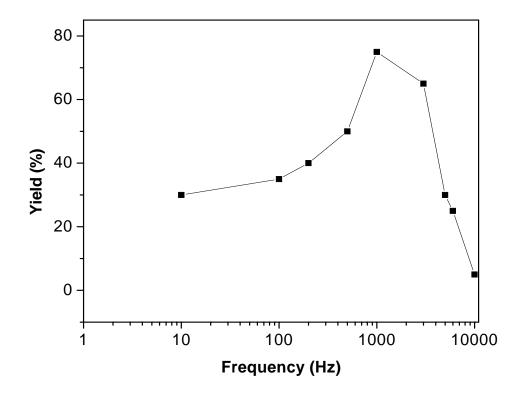

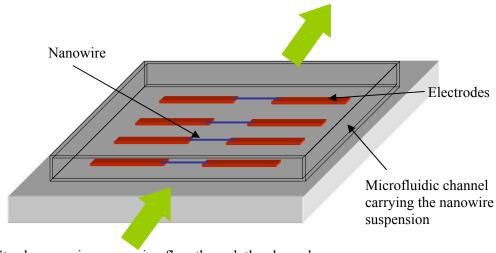

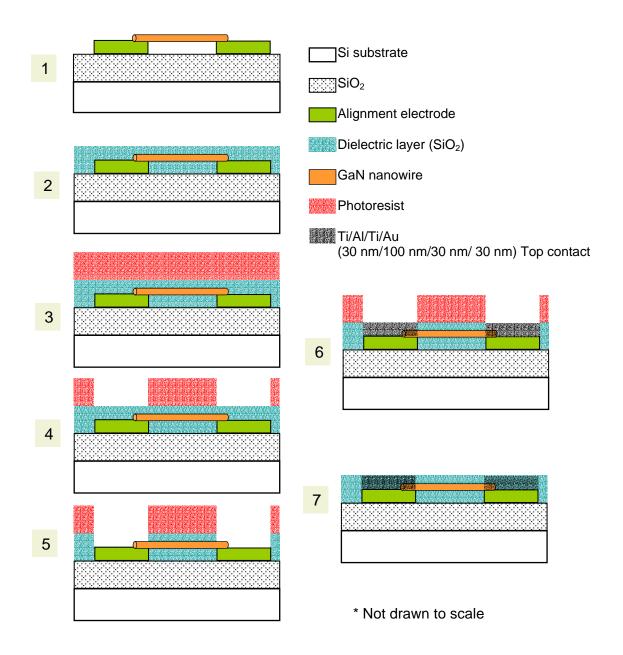

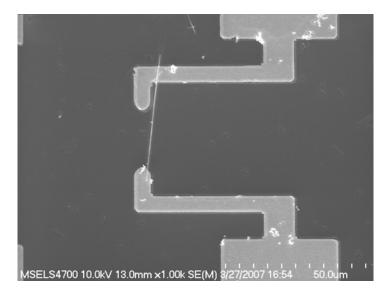

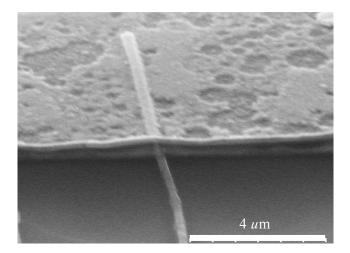

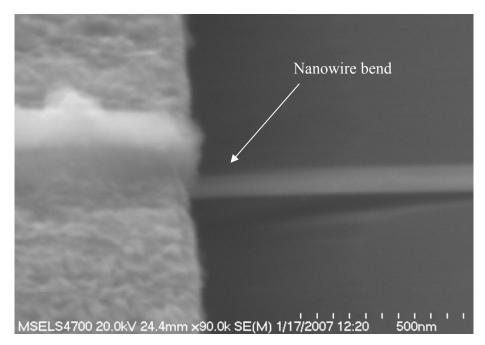

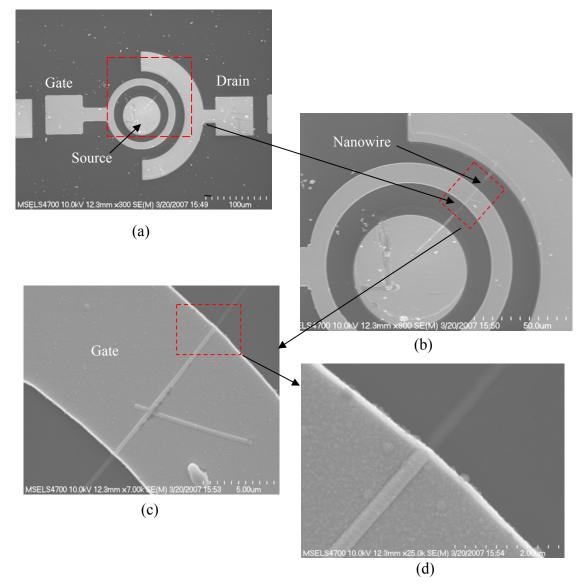

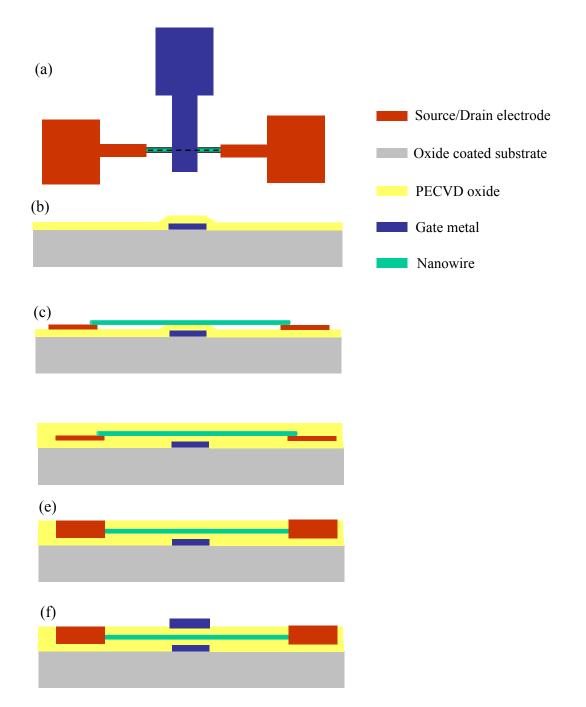

Figure 4.21: FESEM images of GaN nanowires aligned on Ti/Al/Ti pads using DEP force (a) nanowires aligned using 1 KHz 20 volt peak-to-peak ac signal (b) Magnified Figure 4.22: (a) Optical microscope image showing basic structure of the design 2, (b) Magnified image of the area surrounded in (a) with the red box, the beveled edges Figure 4.23: (a) Optical microscope image showing two nanowires captured with 12 V peak to peak ac bias (1 kHz frequency) (b) High magnification of the image in (a). Figure 4.24: (a) Optical microscope image of modified pattern for design 2, (b) Figure 4.25: (a) Optical microscope image of full 2 inch sapphire wafer with alignment electrodes, (b) four-terminal structures, (c) bus lines carrying connecting Figure 4.26: Optical microscope image of nanowires after alignment in a array pattern, the nanowires are seen inside the black circle and the tips of the probes on Figure 4.27: (a) FESEM image of two nanowires captured on two adjacent patterns by applying the same bias to both, (b) FESEM image of nanowire on aligned one pattern, the adjacent pattern was not biased. This clearly demonstrates the effectiveness of the present design in controlled placement of the nanowires. The bias and frequency of the applied voltage used for this process was 12 V peak to peak and Figure 4.28: Plot of experimental yield of alignment as a function of applied bias frequency. The voltage is kept constant at 20 V peak to peak, and the electrode Figure 4.29: Plot of experimental yield of alignment as a function of nanowire diameter. The voltage is kept constant at 20 V peak-to-peak, the electrode separation Figure 4.30: Schematic representation of advanced DEP technique where a microfluidic channel carrying nanowire suspension is placed right over the alignment Figure 5.1: Schematic representation of the complete fabrication process flow for realizing nanowire devices, which are aligned on pre-determined positions on a Figure 5.2: SEM image of complete nanowire device with source and drain contacts. Figure 5.3: SEM image showing a nanowire with both top contact and bottom Figure 5.4: FESEM image of the nanowire with end contacts after annealing of the 2nd metal stack. The break in the nanowire is clearly visible, which is probably caused by the thermal stress during annealing. This nanowire is aligned on a sapphire substrate with no PECVD protective oxide coating. 102 Figure 5.5: FESEM image of a nanowire with top and bottom contacts with a bend

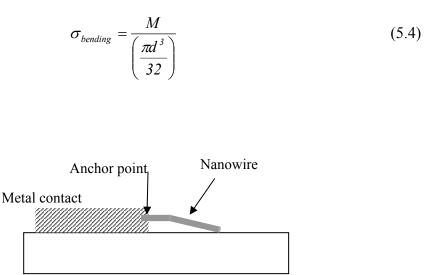

| <b>Figure 5.6:</b> Schematic representation of a nanowire cantilevered from a contact. The                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nanowire is bent at the anchor point                                                                                                                                                       |

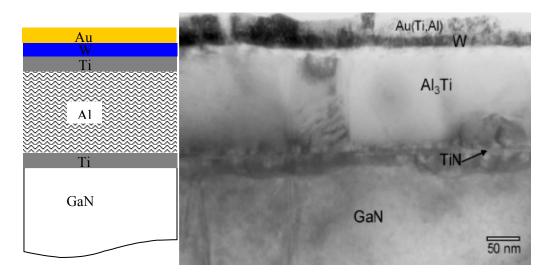

| Ti/Al/Ti/Au metal contact to n-GaN, (b) Cross sectional TEM image of a                                                                                                                     |

| Ti/Al/Ti/W/Au contact to n-GaN, annealed at 750 °C for 30 s in rapid thermal                                                                                                               |

| annealed in argon. The bulk layer is Al <sub>3</sub> Ti which is the reaction product of the                                                                                               |

| Ti/Al/TI layer. In this design an extra barrier metal (W) is incorporated in the                                                                                                           |

| standard metallization. The W layer is clearly seen to be intact after the annealing.                                                                                                      |

| This advanced metallization is capable of withstanding operating temperatures in                                                                                                           |

| excess of 400 °C [71]                                                                                                                                                                      |

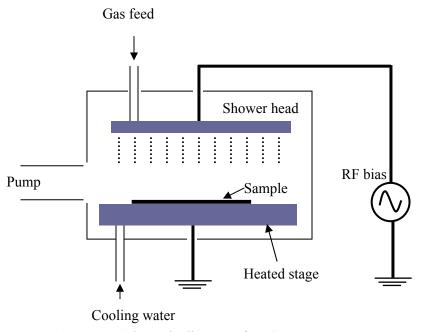

| <b>Figure 5.8:</b> Schematic diagram of PECVD system                                                                                                                                       |

| nanowire with the oxide removed                                                                                                                                                            |

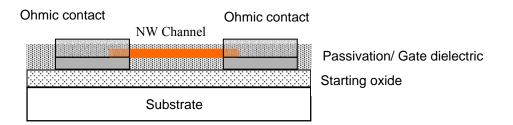

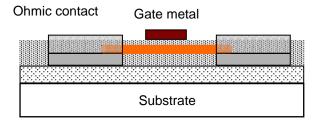

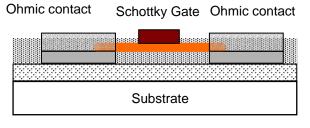

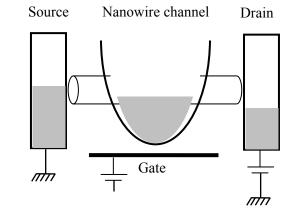

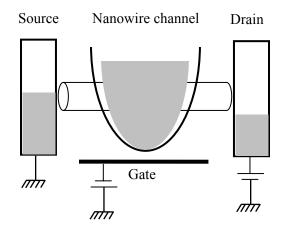

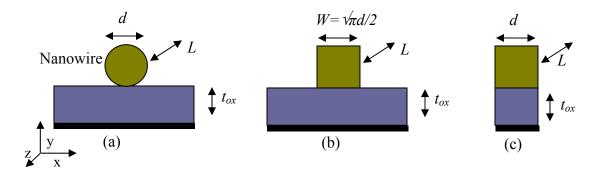

| Fig. 6.1: Basic nanowire device configurations                                                                                                                                             |

| <b>Fig. 6.2:</b> Two-terminal configuration with back-gate                                                                                                                                 |

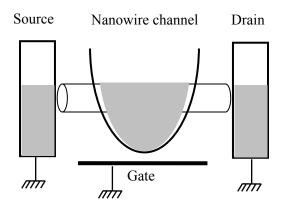

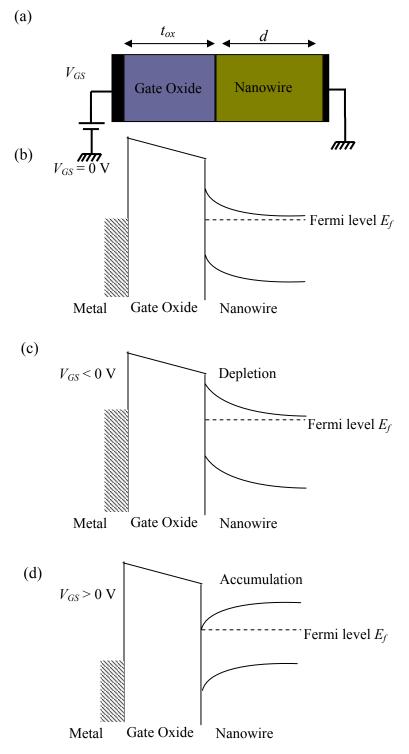

| <b>Fig. 6.3:</b> Schematic representation of the energy band diagram for a nanowire FET                                                                                                    |

| under thermal equilibrium                                                                                                                                                                  |

| Fig. 6.4: Energy band diagram for a nanowire FET under different bias conditions.                                                                                                          |

| (a) $V_{GS} > 0$ , (b) $V_{GS} < 0$ . 118                                                                                                                                                  |

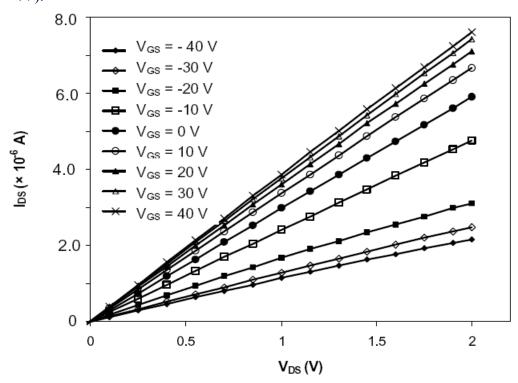

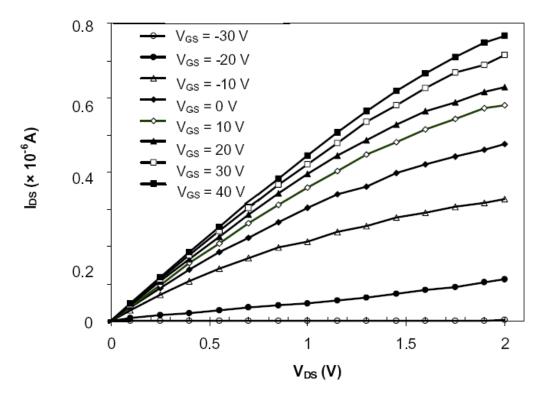

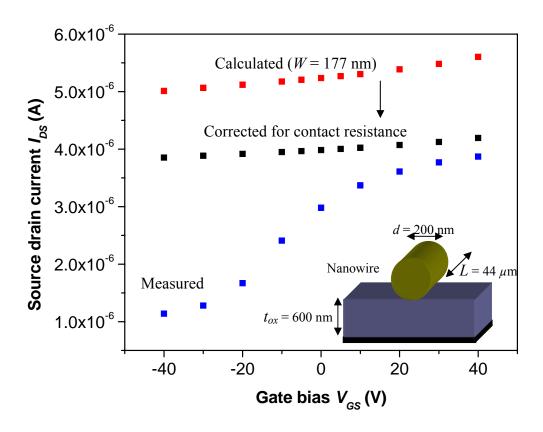

| <b>Fig. 6.5:</b> $I_{DS}$ of vs. $V_{DS}$ plot for a nanowire device of type I (diameter 200 nm, length                                                                                    |

| 44 $\mu$ m) with V <sub>GS</sub> varied from -40 V to + 40 V                                                                                                                               |

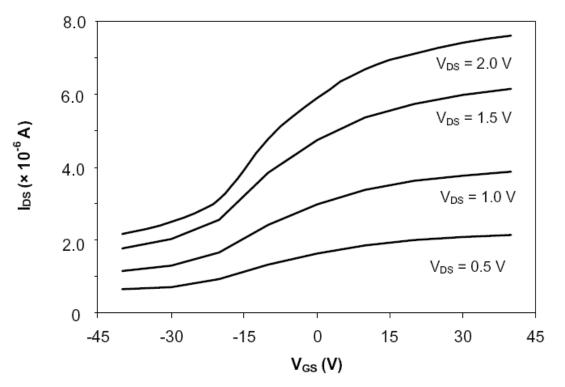

| <b>Fig. 6.6:</b> $I_{DS}$ of vs. $V_{GS}$ plot for the nanowire device of type I (same device as in Fig. 6.5, diameter 200 nm, length 44 $\mu$ m) with $V_{DS}$ varied from 0.5 V to 2.0 V |

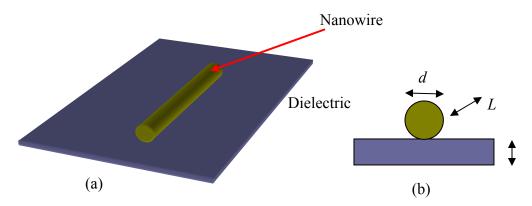

| <b>Fig. 6.7:</b> Plot of $I_{DS}$ vs. $V_{DS}$ of a nanowire device of type II (diameter 95 nm, length                                                                                     |

| $35 \mu\text{m}$ ) with V <sub>GS</sub> varied from $-30 \text{V}$ to $+40 \text{V}$                                                                                                       |

| <b>Fig. 6.8:</b> $I_{DS}$ of vs. $V_{GS}$ plot for the nanowire device of type II (same as in Fig. 6.7,                                                                                    |

| diameter 95 nm, length 35 $\mu$ m) with V <sub>DS</sub> varied from 0.5 V to 2.0 V                                                                                                         |

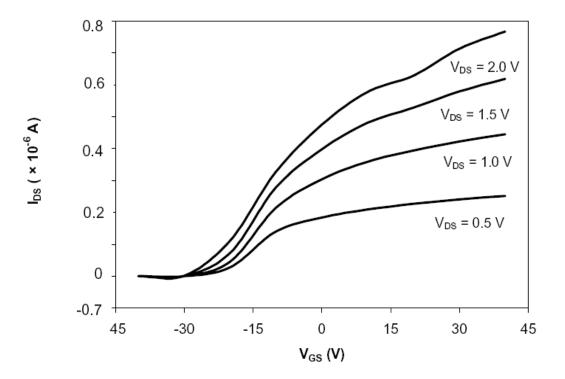

| Fig. 6.9: (a) Normalized transconductance of backgated nanowire FETs with varying                                                                                                          |

| diameters. (b) Semi-log plot of drain current with gate voltage for a 100 nm diameter                                                                                                      |

| nanowire FET. The sub-threshold slope is shown inside the plot                                                                                                                             |

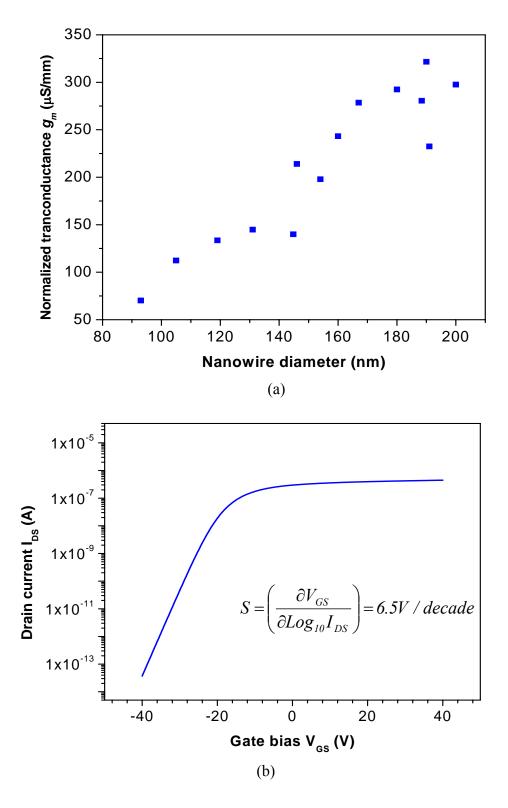

| <b>Fig. 6.10:</b> (a) Cylinder on an infinite dielectric plane model for determining nanowire                                                                                              |

| gate capacitance, (b) Cross section showing the dimensions of the nanowire and the oxide                                                                                                   |

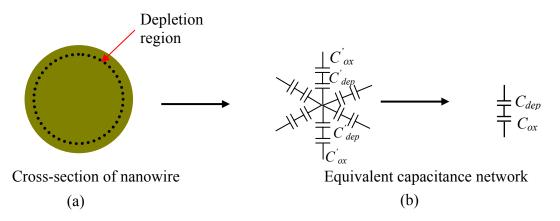

| <b>Fig. 6.11:</b> (a) Nanowire cross-section showing the depletion region, (b) Equivalent                                                                                                  |

| capacitance model for a nanowire cross-section                                                                                                                                             |

| <b>Fig. 6.12:</b> (a) Nanowire geometry used for analytical capacitance expression, (b)                                                                                                    |

| Actual nanowire device geometry used for this study                                                                                                                                        |

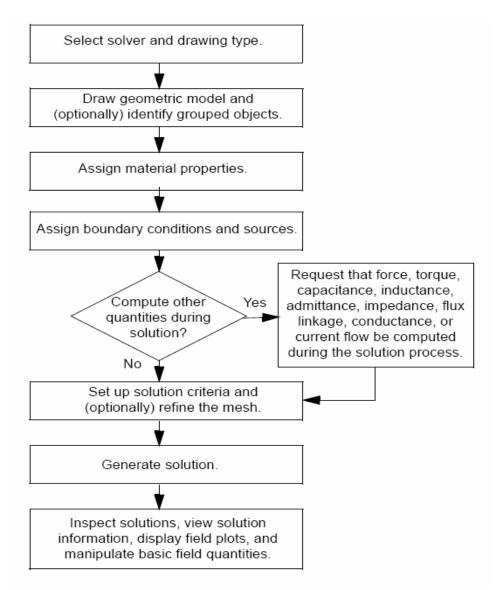

| <b>Fig. 6.13:</b> Flow chart representing the steps for solving a problem in Maxwell <sup>®</sup> 131                                                                                      |

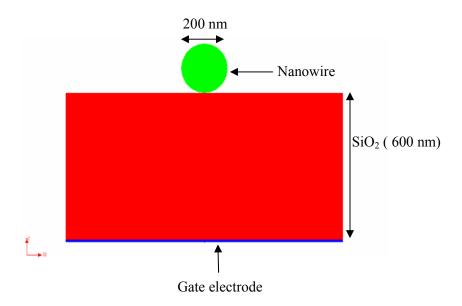

| Fig. 6.14: Simplified geometry used for analytically calculating nanowire-gate                                                                                                             |

| capacitance                                                                                                                                                                                |

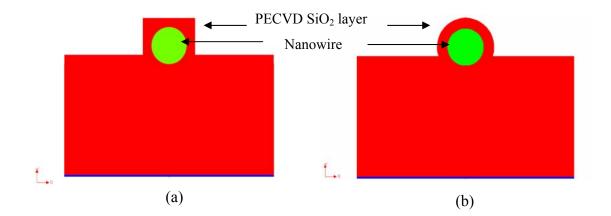

| <b>Fig. 6.15:</b> Simplified geometry of nanowire devices coated with PECVD oxide (a)                                                                                                      |

| assuming a square PECVD SiO <sub>2</sub> profile, (b) a round profile                                                                                                                      |

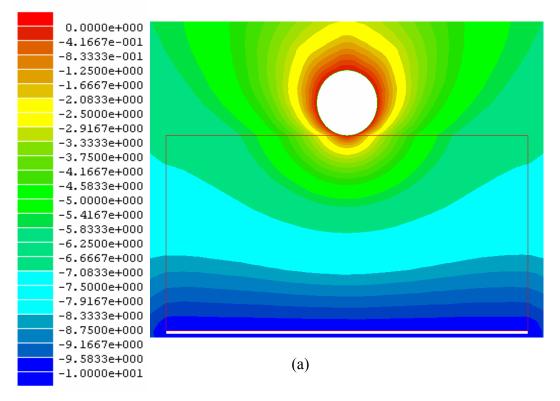

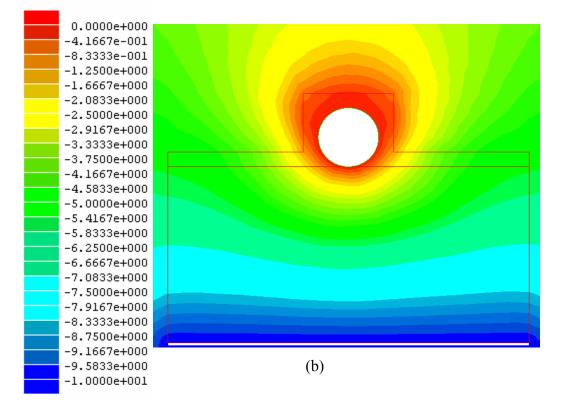

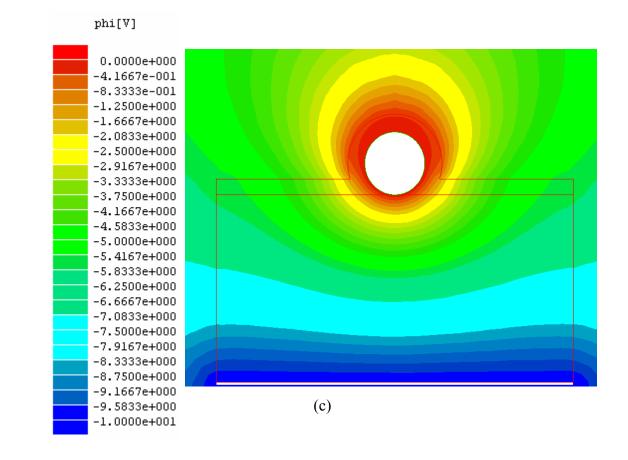

| <b>Fig. 6.16:</b> 2-D plot of voltage (a) bare nanowire, (b) nanowire coated with PECVD oxide with a square profile                                                                        |

| <b>Fig. 6.16:</b> (c) nanowire coated with PECVD oxide with a circular profile                                                                                                             |

|                                                                                                                                                                                            |

| <b>Fig. 6.17:</b> Comparison of numerically and analytically determined capacitances for the structures shown above each plot                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Fig. 6.18:</b> (a) Circular cross-section of a nanowire FET, (b) square cross-section with W scaled to match the surface area of the circular FET, (c) 1-D model neglecting gate in x direction                                                                                                                                                                                               |

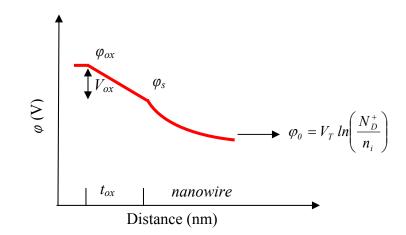

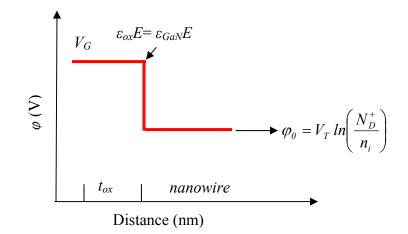

| <b>Fig. 6.19:</b> (a) 1-D MOSFET capacitor (MOS-CAP), (b) energy band diagram for MOS-CAP in thermal equilibrium, (c) for $V_{GS} < 0$ V, and (d) for $V_{GS} > 0$ V 139<br><b>Fig. 6.20:</b> Potential profile for a 1-D MOSFET capacitor with gate bias                                                                                                                                        |

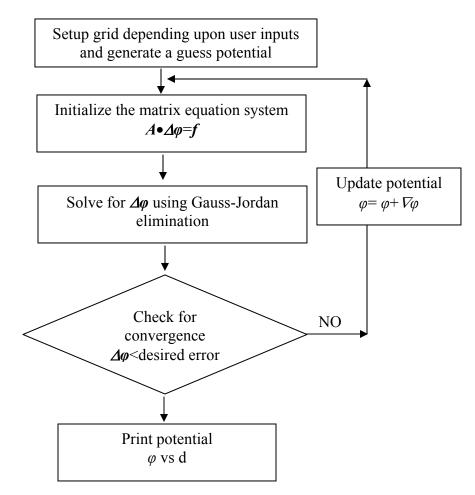

| Fig. 6.22: Flow diagram showing the implementation of the 1-D Poisson solver for MOSCAP.                                                                                                                                                                                                                                                                                                         |

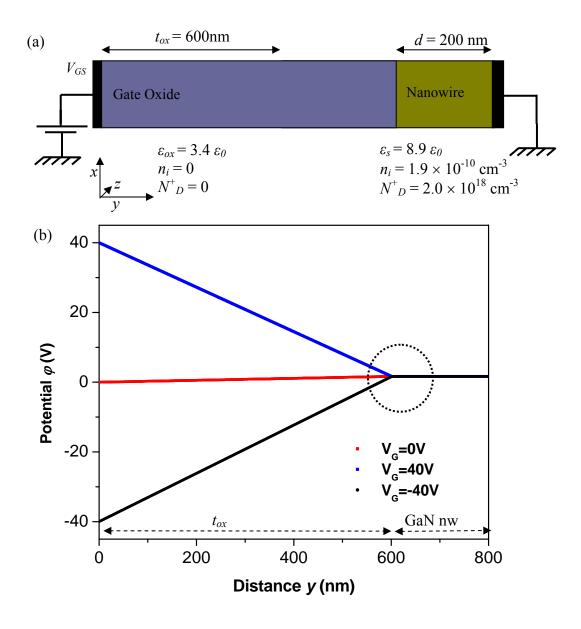

| <b>Fig. 6.23:</b> (a) 1-D nanowire MOSCAP with dimensions as indicated in the figure, (b) numerically calculated potential profiled for the MOSCAP for different gate bias. It can be seen that most of the potential drop occurs in the oxide, which is expected due to its thickness. The potential in the nanowire region, as indicated by the broken black line, is shown in the next figure |

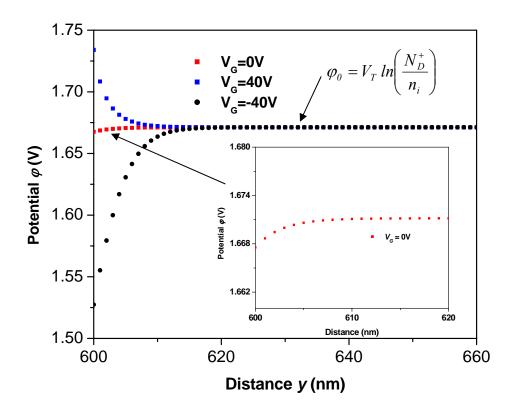

| the potential profile for zero gate bias showing the depletion associated with fermi level alignment through out the system. The thermal equilibrium potential is also shown in the plot                                                                                                                                                                                                         |

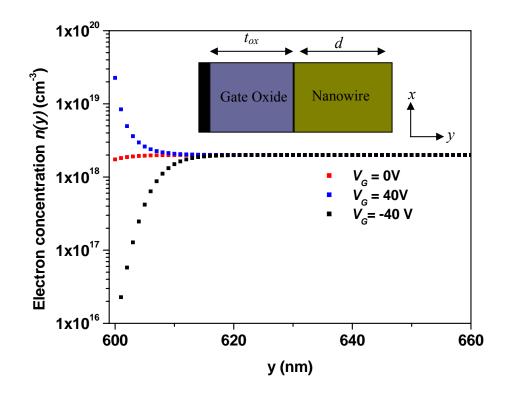

| <b>Fig. 6.25:</b> Electron concentration as a function of distance in y direction for different applied gate bias. Depletion and accumulation for negative and positive gate voltages respectively can be seen in the plot                                                                                                                                                                       |

| <b>Fig. 6.26:</b> Comparison of numerically calculated channel current (red squares) and measured chancel current (blue squares) for a nanowire FET with 1 V $V_{DS}$ . The calculated channel current is also corrected for the contact resistances (black squares).                                                                                                                            |

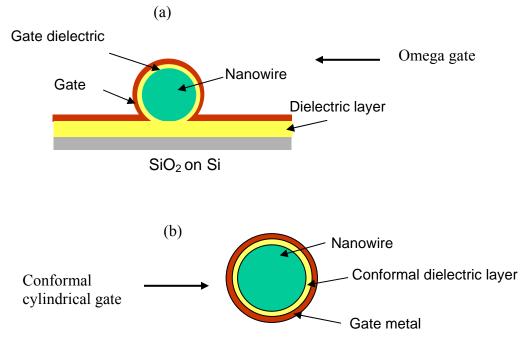

| Fig. 6.27: (a) The omega shaped gate structure, (b) conformal cylindrical gate 151<br>Fig. 6.28: Schematic representation of the omega-backgate structure                                                                                                                                                                                                                                        |

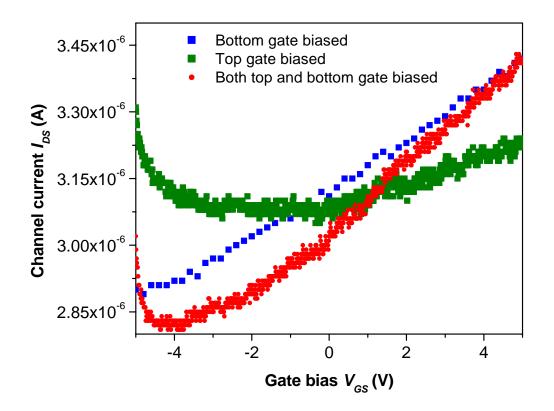

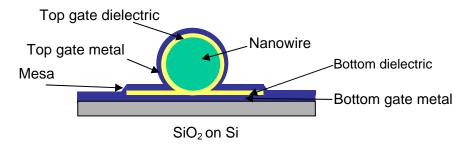

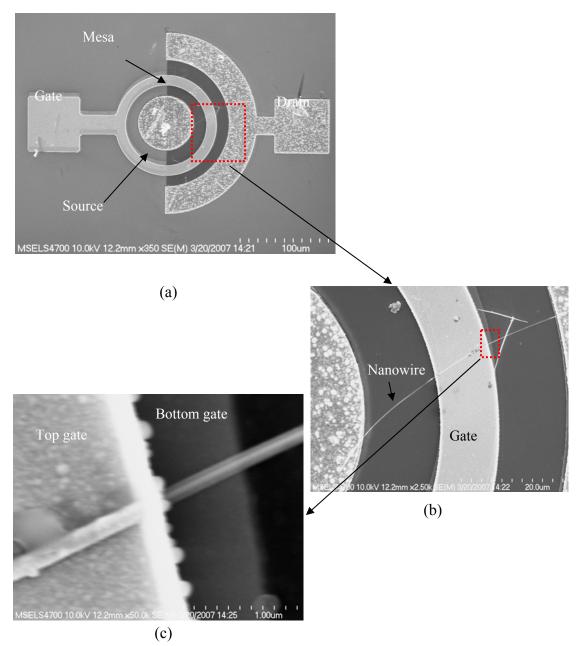

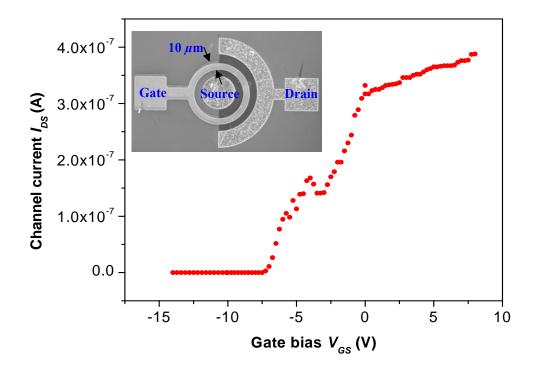

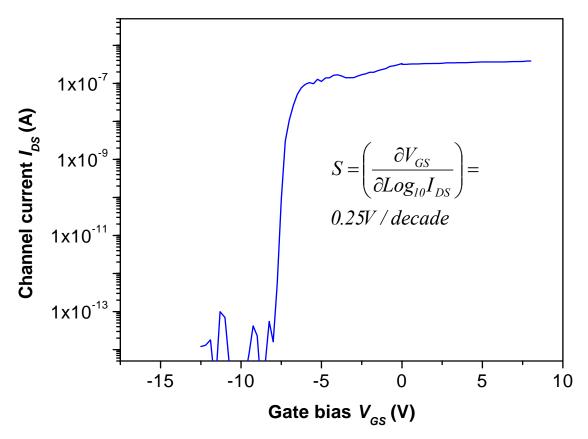

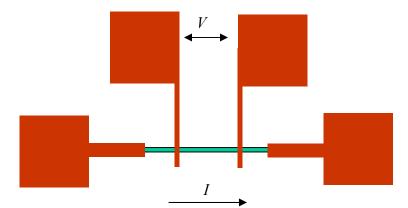

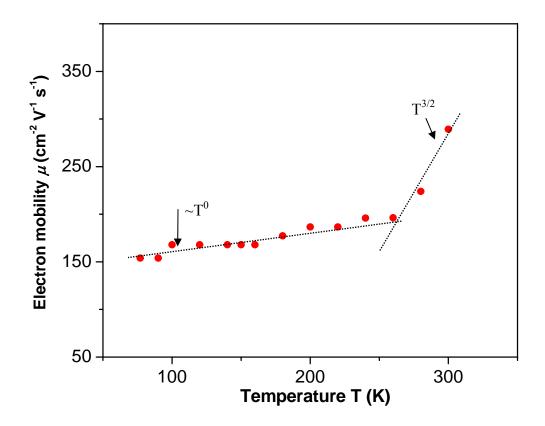

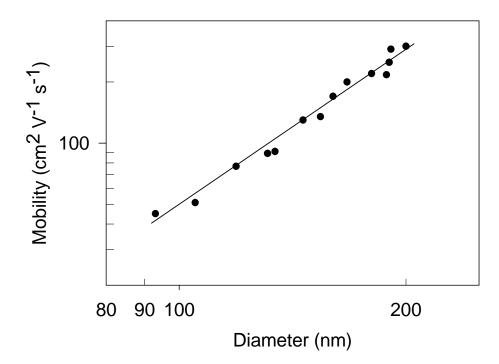

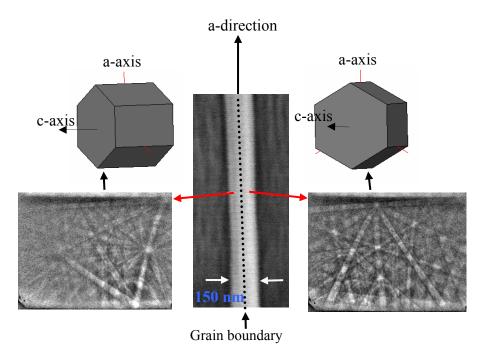

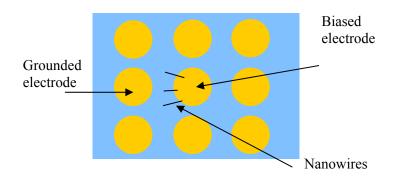

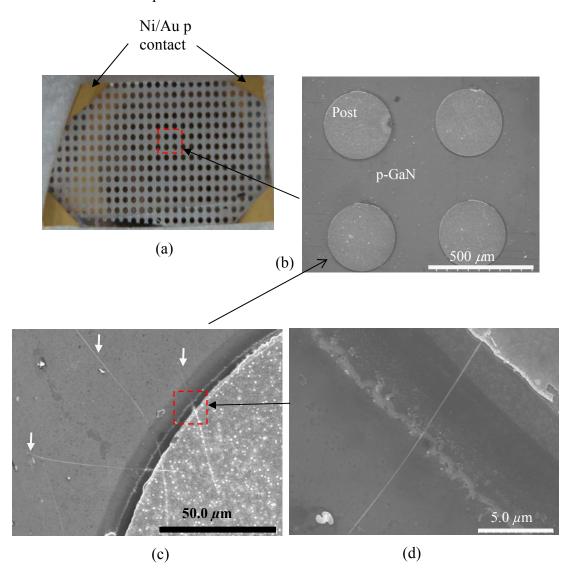

Fig. 6.34: Transconductance plot ( $I_{DS}$  vs  $V_{GS}$ ) of an omega-plane FET with a nanowire of diameter 130 nm and gate length of 10  $\mu$ m. The source drain bias V<sub>DS</sub> is 6 V. (inset) SEM image of the device with source, drain, and gate electrode shown. Figure 6.35: Semi-log plot of the channel current of the omega-plane FET, with the sub-threshold voltage indicated. Transconductance plot of the device is shown in Fig. Fig. 6.36: Pulsed laser deposited Al<sub>2</sub>O<sub>3</sub> on GaN nanowire. The conformal coating of Fig. 6.38: Resistivity of a GaN nanowire as a function of temperature. (inset) SEM Fig. 6.39: Measured field effect electron mobility of a GaN nanowire (diameter 200 nm) as s function of the temperature. Dotted lines represent the non-degenerate and degenerate dependences. 166 Fig. 6.40: Measured field effect electron mobility of GaN nanowires with varying Fig. 6.41: Logarithmic plot of measured mobility vs nanowire diameters with slope of Fig. 6.42: EBSD patterns from two different points on the surface of a 150 nm diameter nanowire. From these patterns, the crystal orientations of the two halves of the bicrystal were determined, as illustrated by the crystal schematics. The a axis of each crystal is parallel to the growth direction but there is a 42° rotation between the c-directions about the common a-axis. The dotted line on the nanowire indicates the Figure 7.1: Schematic representation of the process of aligning and fabricating n-GaN nanowire/p-GaN epilayer LED. 174 Figure 7.2: Schematic representation of the process of aligning n-GaN nanowire on Figure 7.3: (a) Optical image of the p-GaN with the posts with nanowire LEDs, (b) SEM image of insulated posts, (c) nanowires (indicated with the white arrows) aligned from a post, (d) SEM image of a nanowire cantilevered from a post touching the p-GaN substrate. Sidewall of the post is visible in the image. The PECVD SiO<sub>2</sub> is Figure 7.4: Current vs voltage characteristics of a single GaN nanowire/substrate junction LED at room temperature. Blue curve represents the characteristics of the device after annealing at 500 °C for 30 s in argon, and red squares represent the Figure 7.5: Semi-log plot of current vs voltage characteristics of a single GaN nanowire/substrate junction LED at room temperature. The p-n junction is annealed at Figure 7.7: Electroluminescence measurement setup. (a) Probe station with the sample under bias, fiber optic cable is placed right over the sample. (b) UV/VIS spectrometer connected to the computer for data acquisition, and (c) Schematic of the

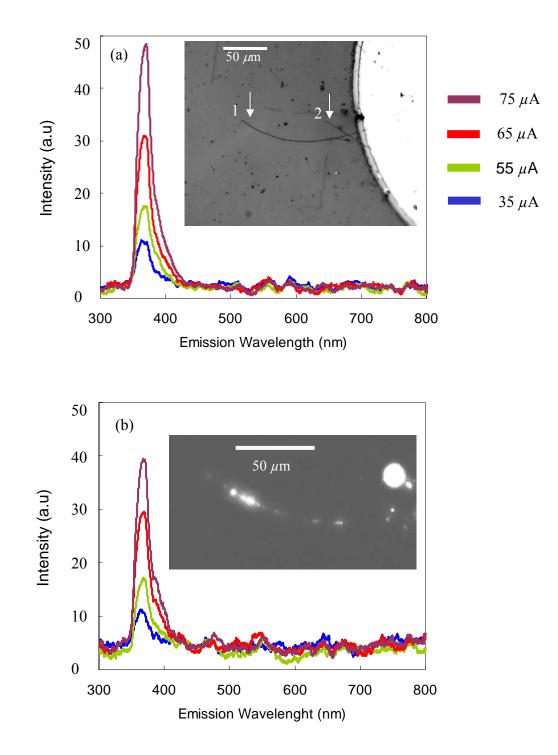

| Figure 7.8: (a) EL of a single nanowire LED after annealing at 500 °C for 30 s in                  |

|----------------------------------------------------------------------------------------------------|

| argon. (inset) Grayscale optical image of a complete nanowire deivce with the end                  |

| contact. A shorter nanowire is visible crossing the longer wire (ends of the two wires             |

| are numbered and indicated with white arrows). (b) EL of the same device after a                   |

| second anneal of 750 °C for 30 s, (inset) Optical image of the same device under                   |

| forward bias with 75 $\mu$ A injection current. Wire 1 and wire 2 had 200 nm and 160 nm            |

| diameters, respectively                                                                            |

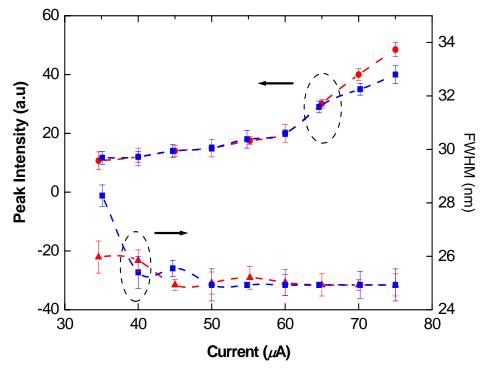

| Figure 7.9: Peak emission intensity and fwhm of nanowire devices under forward                     |

| injection condition. The red curve indicates the characteristics of the devices after 500          |

| $^\circ$ C anneal and the blue curve indicates the trend after a second 750 $^\circ$ C anneal. The |

| error bars represent the standard deviations of the data over 30 nanowire devices with             |

| diameters in the range of 180 nm to 220 nm                                                         |

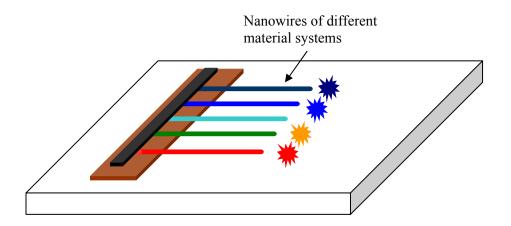

| Figure 7.10: Schematic representation of multi-spectral nanowire emitter array for                 |

| biological detection and chemical sensing applications                                             |

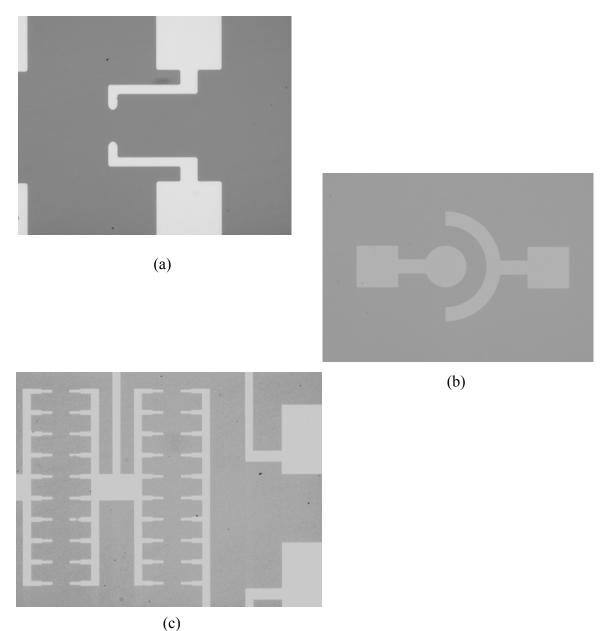

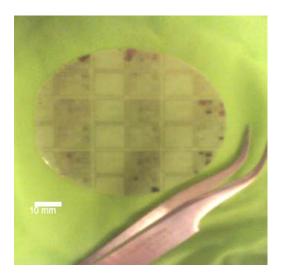

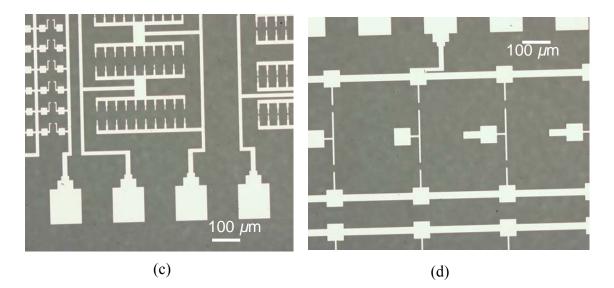

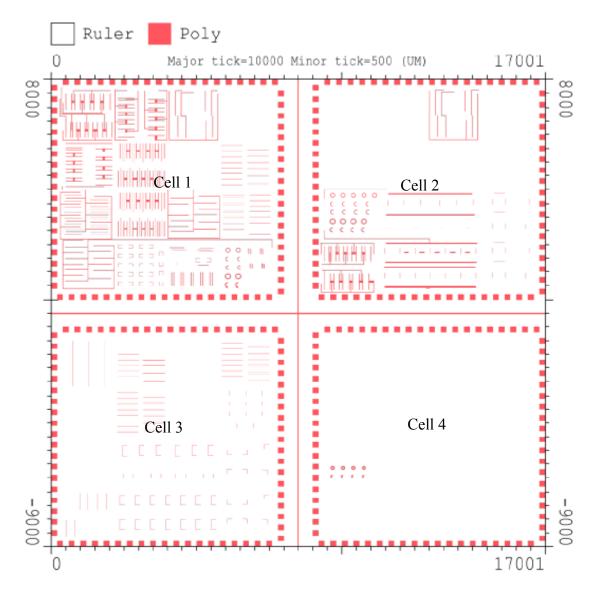

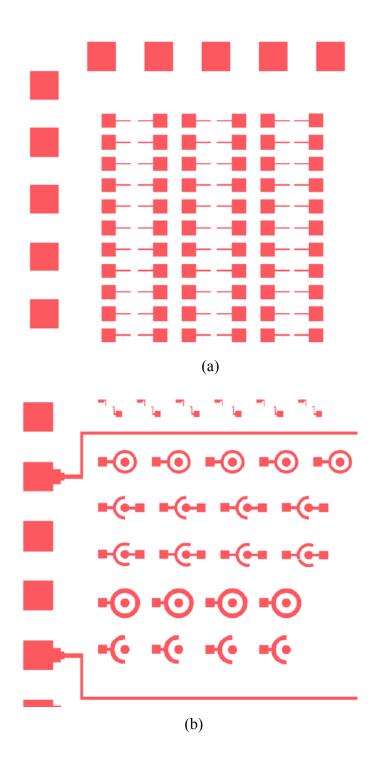

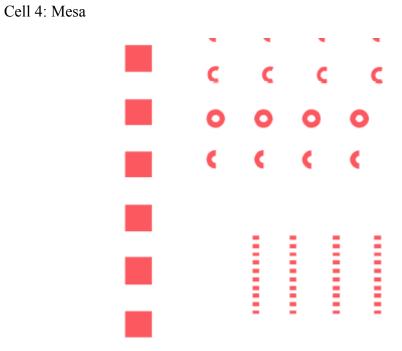

| Figure B.1: Mask layout showing the four-cell design                                               |

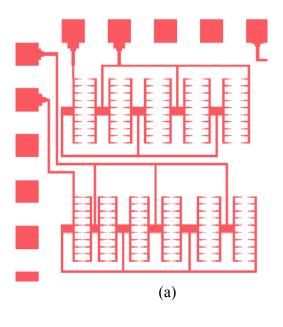

| Figure B.2: (a) Array layout, (b) four-terminal layout                                             |

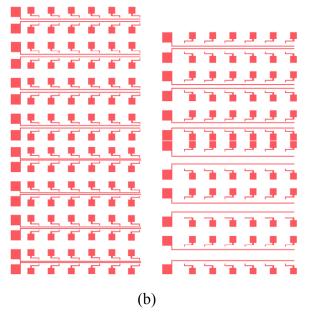

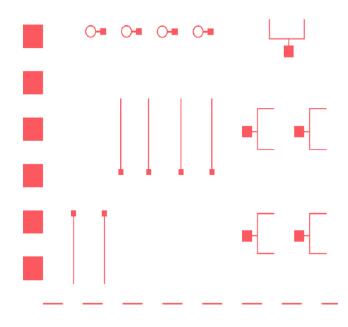

| Figure B.3: (a) Linear source-drain, (b) circular layout                                           |

| Figure B.4: Linear and circular gate designs                                                       |

## **Chapter 1: Introduction**

Nanoscience and nanotechnology is playing the very similar role in shaping the 21<sup>st</sup> century as the advent of printing press played in progressing the human civilization into the renaissance or the invention of steam engine in ushering the industrial revolution. Nanomaterials and nanostructures are defined as having at least one critical dimension of 100 nanometers or less, which is about the size of an average virus. Nanotechnology - the creation, manipulation, and application of materials at the nanoscale involves the ability to fabricate, control, and exploit the unique chemical, physical, and electrical properties of these nanostructures. At the nanoscale levels, the physical, chemical, and biological properties of materials differ in fundamental and quite often valuable ways from the properties of bulk matter [1]. These properties enable development of highly complex and multifunctional materials and systems, which have tremendous potential in improving our lives in numerous ways.

Since 1989, when IBM researchers demonstrated a scientific breakthrough by constructing a 35-atom depiction of the company's logo using a Scanning Tunneling Microscope (STM) [2], the aspiration to control materials at the nanometer level is sweeping industry and academia alike. The power of nanotechnology emerges from the fact that at nanometer scale new and exciting properties emerge in materials that are not possible or not exhibited by those same materials when they have much larger dimensions. These include (but not limited to) optical, electronic, magnetic, chemical, and mechanical properties—depending on the particle, any or all of these can be altered at the nanoscale.

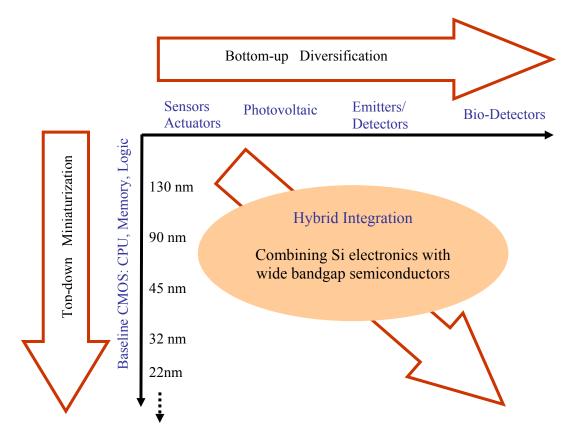

Two different philosophies exist when it comes to realizing these nanostructures: top-down and bottom-up (Fig. 1.1).

Figure 1.1: Top-down versus bottom-up approach towards nanotechnology.

Bottom-up paradigm focuses on the design and synthesis of nanoscale building blocks, elucidation of the fundamental electronic, optical, and other physical properties of these building blocks, and development of methods for hierarchical organization of these building blocks into increasingly complex integrated assemblies. On the other hand, the top-down approach attempts to scale down the dimensions by pushing the limits of conventional micro-manufacturing. Top-down approach has been quite successful in terms of reducing the gate lengths (current state-of-the-art CMOS devices have 65 nm nodes) and packing densities [3]. Topdown techniques work by improving the existing microfabrication processes and innovating new techniques to achieve smaller critical dimensions.

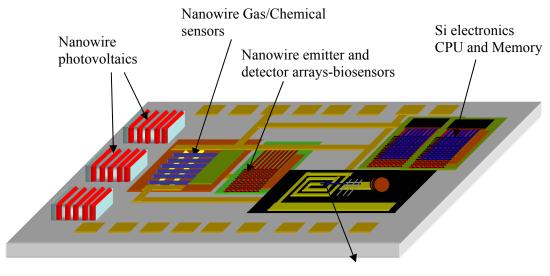

In order to exploit the wide array of material properties and integrate them with existing Si technology, to produce complex and highly functional systems, we have to develop efficient bottom-up techniques. We can consider one scenario where the bottom-up technique has its own advantage. Direct bandgap semiconductors such as gallium nitride (GaN), gallium arsenide (GaAs), and indium phosphide (InP) are often used to realize optical elements (lasers diodes, light-emitting diodes, detectors, etc) due to their efficient recombination and generation properties [4], [5]. To this date, optical elements are either produced as stand-alone devices or integrated with the drive electronics of the same material system. These devices or systems are interfaced with Si microelectronics using off-chip fiber optic connections. Using bottom-up techniques, we can integrate optical nanowire devices directly onto a Si drive electronics chip. This would increase data communication speeds and provide a platform to develop all optical networks. This technique could be extended to integrate nanowires of different material systems, each performing a specific task, with standard Si computing and memory elements. This could eventually lead to highly functional systems such as autonomous sensor clusters (Fig. 1.2) with biological/chemical sensors and RF communication elements integrated with Si electronics, capable of detecting environmental parameters and transmitting the information over a communication link. Integrating nano-photovoltaics will make these systems truly self-sufficient.

3

**RF** components

**Figure 1.2**: An example of hybrid integration – smart, autonomous sensor node. With onboard Si processor, chemical/biological sensors realized from nanowires, communication components, and photovoltaic cells to generate power, they could work without human intervention for indefinite period of time.

## **1.1 Nanowires and Nanotubes**

Nanowires and nanotubes are structures that are cylindrical in shape, with length to diameter ratios often greater than 10<sup>3</sup>. Unlike nanowires, nanotubes are hollow structures with single or multi walls (like carbon nanotubes). Nanowires and nanotubes are highly functional structures with unique properties arising from their low dimensionalities [6]. As they are often grown without any substrates, lattice mismatch and thermal expansion coefficient mismatch problems are not present in these structures. This could mean achieving materials that are free from strain, dislocations, and other structural defects. Due to their high surface to volume ratio, the conduction through these nanowires is strongly affected by the chemical species adsorbed on their surfaces [7]. This would enable us to develop nanoscale, extremely

efficient chemical and biological sensors. Their large surface to volume ratio also enables effective heat removal in these devices. Photo-generation and light extraction are also enhanced due to large surface area in these structures. As nanowires and nanotubes can be placed on any substrate after the growth is completed, they could be integrated with any platforms, including flexible substrates. Once they are placed on pre-determined positions on a substrate, it is relatively simple to apply the conventional fabrication processes to realize electrical and optical devices [8]. This opens up possibilities of integrating exotic III-V compound semiconducting nanowire devices with conventional Si microelectronics. Reduced dimensionality enhances electronic, mechanical, chemical, and optical properties in these nanowires. For nanowires and nanotubes with diameters less than 10 nm, discrete energy levels are formed, which could lead to ballistic transport of electrons through the nanowire [9]. These nanowires and nanotubes are ideal material systems to study fundamental transport properties such as conductance quantization, universal conductance fluctuations, coulomb blockade, etc [10] - [12].

## **1.2 Semiconducting Nanowires and Nanorods**

With all its advantages, carbon nanotubes suffer from one major drawback - lack of control in selective growth of semiconducting and metallic nanowires [13]. A convenient method to separate metallic and semiconducting nanowires does not exist to this date. Also, carbon nanotubes do not allow control of their bandgaps, hence opportunities of making multi-spectral optical elements using carbon nanotubes are limited. Semiconducting nanowires, especially compound semiconductors provide greater flexibility as their bandgaps and doping properties can be controlled by alloy and impurity concentrations, respectively. Heterostructures like core-shell structures can be only formed in semiconducting nanowires, by growing a shell of different bandgap on a nanowire [14], [15]. These kinds of heterostructures are extremely important, as through bandgap engineering we can realize high performance devices such as high electron mobility transistors, resonant tunneling diodes, and laser diodes from these nanowires.

## **1.3 Gallium Nitride and Related Alloys**

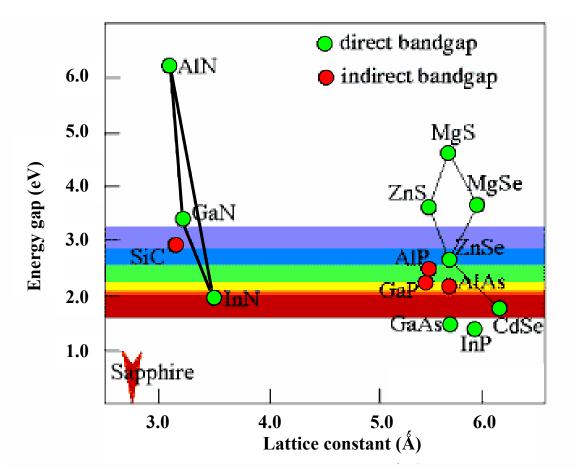

The group III nitrides (AIN, GaN, and InN) and their ternary and quaternary alloys are important class of semiconductors with unique properties such as a direct bandgap spanning the whole solar spectrum (from 0.7 eV for InN to 6.2 eV for AlN), high carrier saturation velocity, high breakdown electric field, and excellent mechanical/thermal stability [16]. As a result nanostructures and nanodevices made from GaN and related nitrides can be utilized to achieve nanoscale ultraviolet (UV)/visible light emitters, detectors, high-speed/high-power transistors and radiation hard, high- temperature electronic devices. Integrating these nitride nanodevices with Si microelectronics could eventually lead to single chip solution for complex optical communication elements, biodetection, chemical sensing systems, etc.

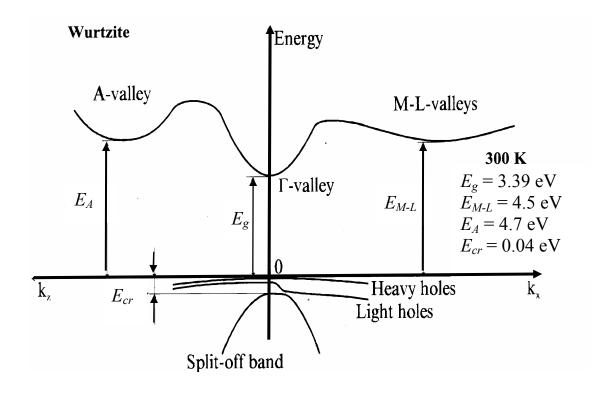

GaN has an energy gap value that approaches 3.4 eV at room temperature (Fig. 1.3) enabling GaN devices to support peak internal electric fields about five times higher than silicon or gallium arsenide (GaAs). Wide bandgap results in lower thermal electron-hole pair generation, hence GaN devices can work at high

temperatures. Due to the larger cohesion energies of its constituent atoms, GaN is chemically robust material, less vulnerable to attack in caustic environments, and more resistant to radiation damage. Various physical properties of different semiconductors in comparison to Si are shown in Table 1.1.

| Property                                                                                      | Si   | GaAs | GaN  | 4H-SiC |  |

|-----------------------------------------------------------------------------------------------|------|------|------|--------|--|

| Band gap, $E_g$<br>(eV) (300K)                                                                | 1.12 | 1.43 | 3.4  | 3.26   |  |

| Dielectric constant, $\varepsilon_r$                                                          | 11.9 | 13.1 | 9    | 10.1   |  |

| Electric<br>breakdownd<br>field, <i>E<sub>c</sub></i><br>(kV/cm)                              | 300  | 400  | 2000 | 2200   |  |

| Electron<br>mobility, $\mu_n$ 1500<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )      |      | 8500 | 1250 | 1000   |  |

| Hole mobility,<br>$\mu_p (\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1})$                         | 600  | 400  | 115  | 850    |  |

| Thermal<br>conductivity, $\lambda$<br>(W cm <sup>-1</sup> K <sup>-1</sup> )                   | 1.5  | 0.46 | 1.3  | 4.9    |  |

| Saturated<br>electron drift<br>velocity, $v_{sat}$<br>(× 10 <sup>7</sup> cm s <sup>-1</sup> ) | 1    | 1    | 2.2  | 2      |  |

| Table                | 1.1: | Physical | properties | of | Si | and | other | important | wide | bandgap |

|----------------------|------|----------|------------|----|----|-----|-------|-----------|------|---------|

| semiconductors [17]. |      |          |            |    |    |     |       |           |      |         |

\* $\varepsilon = \varepsilon_r \cdot \varepsilon_o$  where  $\varepsilon_o = 8.854 \times 10^{-12}$  F m<sup>-1</sup>

Bandgap of the ternary alloy  $Al_xGaN_{1-x}$  can be tuned with varying the mole fraction of Al. This provides means of growing heterostructures with potential wells for carrier confinements. Two-dimensional electron gas can be produced at the interface of GaN and  $Al_xGa_{1-x}N$ , because of their bandgap difference. Separating electrons from the donors increase their mobility and results in increased high frequency operation of the device.

Figure 1.3: Energy band diagram of wurtzite GaN. Direct energy gap is 3.39 eV at 300 K.

Due to its direct bandgap, generation and recombination of electron-hole pairs are efficient. The bandgap of GaN corresponds to an emission wavelength in 360 nm range. This makes the nitride suitable for developing UV/ blue LEDs and Laser diodes.

## 1.4 Strategies for Developing Nanowire Devices

Successful realization of nanowire devices and complex nanosystems would require effective solutions to numerous challenges. Nanowire growth is still at its infancy. Growth methods are not fully understood and often lack dimensionality and orientation control. Also doping issues, both in-situ and ex-situ, have not been addressed in detail for nanowires.

Figure 1.4: Lattice constants and bandgap energy for different semiconductors at room temperature [18].

Characterization techniques (structural, optical, and electrical) normally used to characterize thin film semiconducting materials, are not readily applicable to the nanowires. For example, x-ray diffraction technique which is often used to assess the crystalline qualities of a material cannot give an indication of the individual nanowire properties as it would require focusing of the x-ray beams with spot sizes of 200 nm or less. Thus more time consuming techniques like transmission electron microscopy (TEM) has to be used, which require elaborate sample preparation. Electron backscatter diffraction (EBSD) is a structural characterization technique that provides an easier alternative for individual nanowire structure determination, and as will be shown chapter 2 it can also be used to correlate structural properties with individual nanowire device characteristics.

One of most difficult challenges is developing a reliable assembling technique that is substrate and nanowire material independent. Controlling nanowire placement with reliability and repeatability is the key in producing hierarchical systems. Novel nanowire device designs are essential if we want to fully exploit their enhanced properties. For example, cylindrical-gate nanowire field-effect transistors (FETs), with the gate oxide and gate metal deposited conformally as a shell on the nanowire, will enhance the device performances dramatically. To realize these novel structures, innovative fabrication processes (conformal deposition techniques such as atomic layer deposition, liquid-phase deposition) are required. Device characterization and extraction of material properties (resistivity, mobility, and carrier concentration) are specially challenging for nanowires. Analytical relationships relating the device characteristics with structural properties often does not exist. Simple models and assumptions are generally employed. In order to understand the device properties, fully numerical techniques like finite element analysis are required. Correlating device properties with structural characteristics of these nanowires will ultimately increase our understanding of the transport processes in these nanostructures, which will enable us eventually to realize superior performing nanowire devices. Understanding fundamental carrier transport properties and scattering mechanisms will complete our understanding of these nanostructures.

## **1.5 Contributions and Accomplishments**

This dissertation represents the research which has resulted in numerous publications in referred journals and contributed talks in national and international conferences. The nanowires used for this study was provided by Dr. Maoqi He of Howard University, Washington DC, under a project with joint collaboration between Dr. John Melngailis (University of Maryland, College Park) and Dr. S. N. Mohammad (University of Maryland, College Park). Transmission electron microscopy presented in chapter 2 was performed by Dr. Warren MoberlyChan of Lawrence Livermore National Laboratory (LLNL). The photoluminescence experiments on these nanowires were performed by Dr. Norman Sanford and Dr. John Schlager of National Institute of Standards and Technology (NIST). The cathodoluminescence measurements were performed by Dr. Joseph W. Tringe of LLNL.

Except the above mentioned results, experiments and results presented in this dissertation are obtained solely by the candidate. The significant accomplishments of this research are listed below:

11

- 1.Detailed structural characterizations have been carried out revealing important information about the nature of growth and structural defects in these nanowires.

- Simple nanowire devices were demonstrated using focused-ion beam induced deposition technique, which enabled rapid estimation of the material properties. Interaction of focused-ion beam with GaN nanowire has been studied

- 3. Electric field was used to assemble these nanowires on a pre-patterned substrate. The alignment process has been studied in details, which lead to improved designs of the alignment electrodes and a systematic approach towards the development of the alignment process.

- 4. A general fabrication scheme utilizing only batch fabrication processes has been implemented, which is suitable for any material system. This type of fabrication scheme is quite advantageous over most of the reported methods as it provides a means for integrating nanodevices with conventional silicon microcircuitry.

- 5. We have designed and realized novel nanowire transistors with performances comparable to the state-of-the-art thin film and nanowire devices. This is quite encouraging as it indicates that with improved designs and materials these nanosystems could meet or exceed expectations of the future device or system designers.

- 6.Temperature dependent resistivity measurements indicated that the impurity concentration is quite high in these nanowires, which is possible due to oxygen or other structural defects. Temperature dependent mobility revealed that the

charged impurity scattering is the dominant mechanism in transport through these nanowires. These types of measurements are crucial in understanding the basic conduction processes in the nanowires.

- 7. Diameter-dependent mobility measurement in nanowire transistors indicated the evidence of surface scattering is smaller diameter nanowires. Using reverse engineering and microstructural characterization technique (electron backscattered diffraction), we were able to correlate the structural characteristics of these nanowire devices with their measured electrical properties. To the best of our knowledge, this type of study has not been reported before.

- 8.Ultraviolet nanowire light-emitting diodes (LEDs) have been realized by assembling GaN nanowires on p-GaN substrate, forming mechanical p-n junctions. These LEDs exhibited 365 nm emission with excellent thermal stability. This technique provides a simple technique for realizing wide-area emitting sources and multispectral emitter arrays. Emission from homojunctions of GaN nanowires has not been demonstrated before.

# Chapter 2: Gallium Nitride Nanowire Growth and Characterization

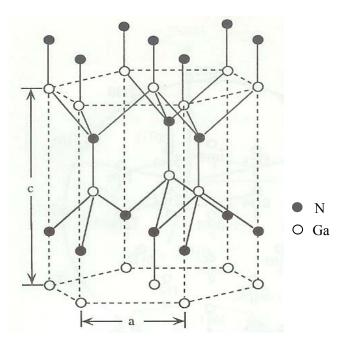

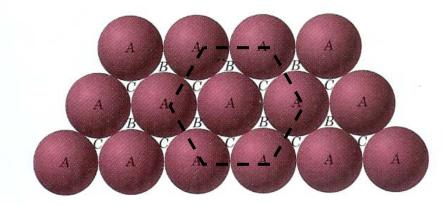

Gallium nitride (GaN) is a compound semiconductor which has a direct bandgap of 3.4 eV at room temperature. GaN and related nitrides have excellent material, optical, and electrical properties. There are three common crystal structures shared by the group-III nitrides: a) wurtzite, b) zincblende, and c) rocksalt structures. Under ambient conditions, the most thermodynamically stable structure is wurtzite for bulk AlN, GaN, and InN. The wurtzite structure has a hexagonal unit cell and thus two lattice constants, c and a. The wurtzite structure consists of two interpenetrating Hexagonal Close Packed (HCP) sublattices, each with one type of atoms, offset along the c axis of 5/8 of the cell height [16].

**Figure 2.1:** Crystal structure of wurtzite GaN. Basis unit cell is hexagonal closed pack (HCP) structure with alternating layers of Ga and N atoms.

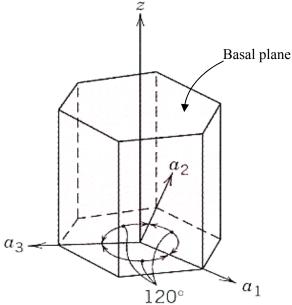

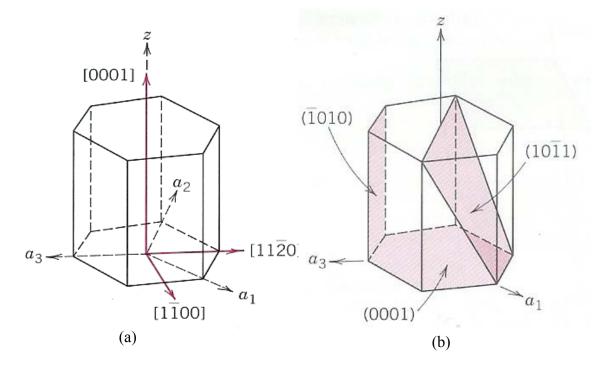

The wurtzite crystal structure of GaN is shown in the Fig. 2.1, where the stacking order of Ga atoms (white) and N atoms (black) can be seen. In order to understand the growth and material properties of a semiconductor it is imperative to have a good understanding of its crystal structure. In order to interpret the results of structural characterization techniques, such as x-ray diffraction, transmission electron microcopy (TEM), and electron backscattered diffraction (EBSD), understanding of the crystal directions and planes is extremely helpful. In order to identify various crystallographic directions in a hexagonal system, a four-axis coordinate system, called Miller-Bravais system, is employed [19]. The three  $a_1$ ,  $a_2$ , and  $a_3$  axis are all contained within a single plane (called basal plane), and at 120° angles to one another (Fig. 2.2).

Figure 2.2: Four axes Miller-Bravais coordinate system for HCP structure [19].