#### ABSTRACT

Title of Document:

#### APPLYING PERCEPTRONS TO SPECULATION IN COMPUTER ARCHITECTURE

Michael David Black, Ph.D., 2007

Directed By:

Professor Manoj Franklin, Electrical and Computer Engineering

Speculation plays an ever-increasing role in optimizing the execution of programs in computer architecture. Speculative decision-makers are typically required to have high speed and small size, thus limiting their complexity and capability. Because of these restrictions, predictors often consider only a small subset of the available data in making decisions, and consequently do not realize their potential accuracy. Perceptrons, or simple neural networks, can be highly useful in speculation for their ability to examine larger quantities of available data, and identify which data lead to accurate results. Recent research has demonstrated that perceptrons can operate successfully within the strict size and latency restrictions of speculation in computer architecture.

This dissertation first studies how perceptrons can be made to predict accurately when they directly replace the traditional pattern table predictor. Several weight training methods and multiple-bit perceptron topologies are modeled and evaluated in their ability to learn data patterns that pattern tables can learn. The effects of interference between past data on perceptrons are evaluated, and different interference reduction strategies are explored. Perceptrons are then applied to two speculative applications: data value prediction and dataflow critical path prediction. Several new perceptron value predictors are proposed that can consider longer or more varied data histories than existing table-based value predictors. These include a global-based local predictor that uses global correlations between data values to predict past local values, a globalbased global predictor that uses global correlations to predict past global values, and a bitwise predictor that can use global correlations to generate new data values. Several new perceptron criticality predictors are proposed that use global correlations between instruction behaviors to accurately determine whether instructions lie on the critical path. These predictors are evaluated against local table-based approaches on a custom cycle-accurate processor simulator, and are shown on average to have both superior accuracy and higher instruction-per-cycle performance.

Finally, the perceptron predictors are simulated using the different weight training approaches and multiple-bit topologies. It is shown that for these applications, perceptron topologies and training approaches must be selected that respond well to highly imbalanced and poorly correlated past data patterns.

### APPLYING PERCEPTRONS TO SPECULATION IN COMPUTER ARCHITECTURE

By

Michael David Black

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2007

Advisory Committee: Professor Manoj Franklin, Chair Professor Donald Yeung Professor Peter Petrov Professor Robert Newcomb Professor Alan Sussman © Copyright by Michael David Black 2007

## Acknowledgements

I need to acknowledge several people without whose help and advice I would not have completed this dissertation.

First and foremost I thank my wife Jennifer. Not only did she provide unlimited love and encouragement through the long process and supported me through six years of graduate school, but she also contributed greatly to the figures and tables, and read through and corrected my work.

I also thank my advisor, Dr. Manoj Franklin, for giving me advice on possible topics, feedback on writing, and generally teaching me how to do computer architecture research. I also thank Dr. Donald Yeung for his suggestion of possible topics and general feedback on my work.

I would like to thank several fellow graduate students who discussed my ideas with me and gave me suggestions on how to proceed with them. Thanks especially to Gregory Bard for his help with analyzing perceptron behavior, and to Nitin Madnani and Sean Leventhal for giving me feedback. Also thanks to other supportive denizens of the SCA Lab, especially Rania Mameesh and Kursad Albayraktaroglu. Finally I need to thank my parents, Ann and Bruce Black, for listening to my ideas and giving me much support and encouragement. I also thank Jennifer's parents, Dick and Linda Koch, for cheering me on.

## Table of Contents

| List of Tables, Figures, and Illustrationsvii                         |

|-----------------------------------------------------------------------|

| Chapter 1: Introduction                                               |

| 1.1. Speculation                                                      |

| 1.2. Dissertation Overview                                            |

| 1.3. Contributions                                                    |

| Chapter 2. Background 11                                              |

| 2.1. The Perceptron                                                   |

| 2.1.1. Rosenblatt's perceptron                                        |

| 2.1.2. Training                                                       |

| 2.1.3. Linear Inseparability                                          |

| 2.1.4. The Perceptron in Hardware                                     |

| 2.1.5. Multilayer Neural Networks                                     |

| 2.2. Perceptron Branch Prediction and Other Architecture Applications |

| 2.2.1. The Two-Level Branch Predictor                                 |

| 2.2.2. Perceptron Branch Prediction                                   |

| 2.2.3. Piecewise Linear Predictor                                     |

| 2.2.4. Other Perceptron Applications in Architecture                  |

| 2.2.4.1. Perceptron-based Confidence Estimation for Branch Prediction |

| 2.2.4.2. Perceptron-based Confidence Estimation for Value Prediction  |

| Chapter 3. Theory                                                     |

| 3.1. Perceptron Learning                                              |

| 3.1.1 Perceptron Context-based Prediction                             |

| 3.1.2 Can a Perceptron Outperform a Table?                            |

| 3.1.3. Perceptron Learning Beyond Context                             |

| 3.1.3.1. Masking                                                      |

| 3.1.3.2. Recognizing new patterns                                     |

| 3.2. Training                                                         |

| 3.2.1. Training Issues                                                |

| 3.2.2. Training using an error value                                  |

| 3.2.3. Training using correlations                                    |

| 3.2.3.1. Without training cutoff                                      |

| 3.2.3.2. With training cutoff                                         |

| 3.2.4. Exponential weight growth                                      |

| 3.2.5 Comparing Training Strategies                                   |

| 3.3. The Multibit Perceptron                                          |

| 3.3.1. Defining the Multibit Perceptron                               |

| 3.3.1.1. Defining Multibit Correlations                               |

| 3.3.1.2. Multibit Perceptron Complexity                               |

| 3.3.2. Multibit Perceptron Topologies                                 |

| 3.3.2.1. The Disjoint Perceptron                                      |

| 3.3.2.2. The Fully Coupled Perceptron                                 |

| 3.3.2.3 Disjoint and Fully Coupled Compared                           |

|   | 3.3.2.4. A Weight for Each Value                       | . 83 |

|---|--------------------------------------------------------|------|

|   | 3.3.2.5. A Set of Weights for Each Target Value        |      |

|   | 3.4. Interference                                      |      |

|   | 3.4.1. Aliasing                                        | . 88 |

|   | 3.4.2. History Interference                            | . 89 |

|   | 3.4.3. History Interference Does Happen                | . 91 |

|   | 3.4.4. Classifying Interference                        |      |

|   | 3.4.5. Interference Effects                            |      |

|   | 3.4.6. History Interference in the Multibit Perceptron | . 98 |

|   | 3.4.7. Coping with History Interference                |      |

|   | 3.4.7.1. "Assigned Seats"                              |      |

|   | 3.4.7.2. Piecewise Linear                              |      |

|   | 3.4.7.3. Ignore the problem                            |      |

| C | hapter 4: Experimental Methodology                     |      |

| - | 4.1. The Simulator                                     |      |

|   | 4.1.1. Mysim overview                                  |      |

|   | 4.1.2. Mysim Core Anatomy                              |      |

|   | 4.1.2.1. Starting simulation                           |      |

|   | 4.1.2.1.1. mymain.c                                    |      |

|   | 4.1.2.1.2. myloader.c                                  |      |

|   | 4.1.2.2. Simulator Support Files                       |      |

|   | 4.1.2.2.1. mymemory.c                                  |      |

|   | 4.1.2.2.2. mysyscall.c.                                |      |

|   | 4.1.2.3. Functional Simulation                         |      |

|   | 4.1.2.4. In-order Pipeline Simulation                  |      |

|   | 4.1.2.5. Superscalar Simulation                        |      |

|   | 4.1.3. Mysim Extensions                                |      |

|   | 4.1.3.1. Cache                                         |      |

|   | 4.1.3.2. Branch Prediction                             |      |

|   | 4.1.3.3. Power Modeling                                |      |

|   | 4.1.4. Mysim Validation and Performance                |      |

|   | 4.2. Simulation Methodology                            |      |

|   | 4.3. Simulating Perceptrons                            |      |

| C | hapter 5: Value Prediction                             |      |

| - | 5.1. Introduction                                      |      |

|   | 5.2. Value Prediction Background                       |      |

|   | 5.2.1. Groundwork and Local Predictors                 |      |

|   | 5.2.2. Global Predictors                               |      |

|   | 5.2.3. Simulating Value Prediction                     |      |

|   | 5.3. Local context-based prediction                    |      |

|   | 5.3.1. The two-level hybrid predictor                  |      |

|   | 5.3.1.1. How it works                                  |      |

|   | 5.3.1.2. What it can and cannot do                     |      |

|   | 5.3.2. Perceptron-based local context predictors       |      |

|   | 5.3.2.1. Why perceptrons?                              |      |

|   | 5.3.2.2. Perceptrons in the Pattern Table              |      |

|   | <b>▲</b>                                               |      |

| 5.3.2.3. Perceptrons in the Value Table                  |     |

|----------------------------------------------------------|-----|

| 5.4. Global context-based prediction                     |     |

| 5.4.1. Why global?                                       |     |

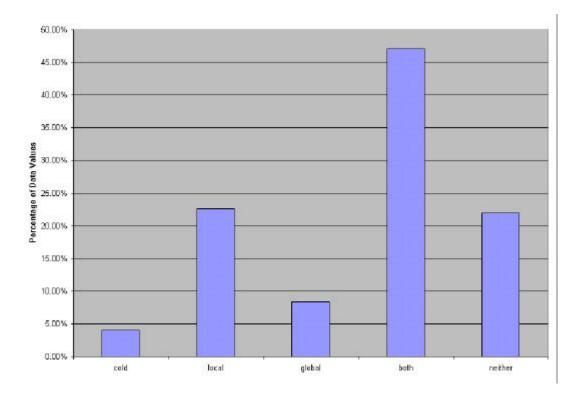

| 5.4.1.1. Values Available Globally                       |     |

| 5.4.1.2. Value Correlations Available Globally           |     |

| 5.4.2. Perceptron Global-based Local                     | 158 |

| 5.4.3. Perceptron Global-based Global                    |     |

| 5.4.3.1. Global-Global Advantages                        |     |

| 5.4.3.2. Global-Global Disadvantages                     |     |

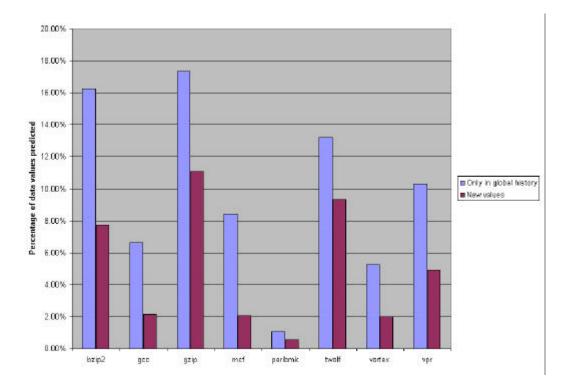

| 5.4.4. Perceptron Bitwise                                |     |

| 5.5. Value Prediction Implementation Details             |     |

| 5.5.1. Simulating Value Predictors                       |     |

| 5.5.2. Global Value History Register                     | 171 |

| 5.6. Experimental Results                                |     |

| 5.6.1. Local Value Predictors                            |     |

| 5.6.2. Global-based Local Predictors                     |     |

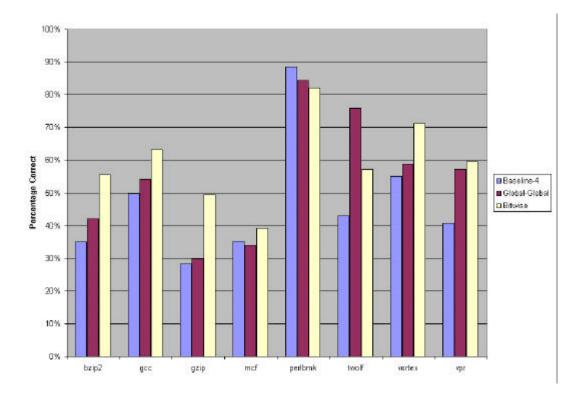

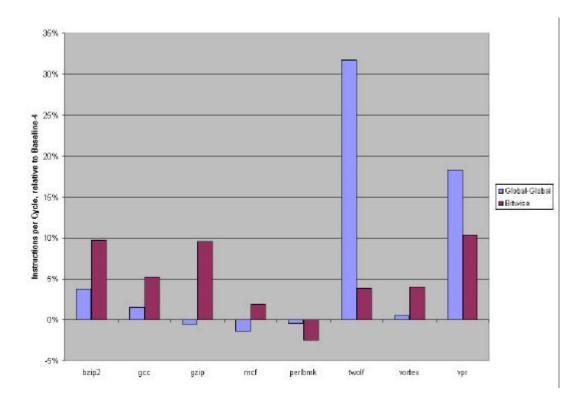

| 5.6.3. Global Value Predictors                           |     |

| 5.6.4. Comparing Physical Size                           |     |

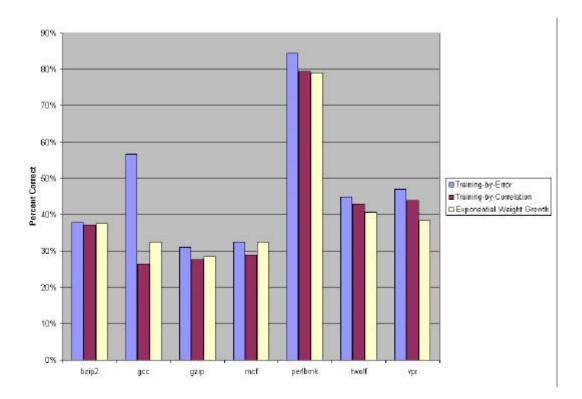

| 5.6.5. Comparing Training Procedures                     |     |

| 5.6.6. Interference                                      |     |

| Chapter 6: Critical Instruction Prediction               | 191 |

| 6.1. Past Work                                           | 193 |

| 6.1.1. Predicting Critical Behavior                      | 193 |

| 6.1.2. Predicting Criticality More Precisely             | 195 |

| 6.1.3. Perceptron Criticality                            | 197 |

| 6.2. Analysis                                            | 199 |

| 6.2.1. Evaluating Criticality                            | 199 |

| 6.2.2. The Critical Behavior Criteria                    | 200 |

| 6.2.3. Global Correlations                               | 203 |

| 6.3. Perceptron Predictor Configurations                 |     |

| 6.3.1. A Perceptron For Each Criterion (PEC)             |     |

| 6.3.2. A Single Perceptron (SP)                          |     |

| 6.3.3. Single Perceptron, Input for Each Criterion (SPC) |     |

| 6.3.4. Training                                          |     |

| 6.4. Experimental Results                                |     |

| 6.4.1. Simulation                                        |     |

| 6.4.2. Baseline                                          |     |

| 6.4.3 Accuracy Results                                   |     |

| 6.4.4. Value Prediction Application                      |     |

| 6.4.5. Physical Size                                     |     |

| 6.4.6. Perceptron Parameters                             |     |

| Chapter 7. Conclusions                                   |     |

| 7.1. Weights                                             |     |

| 7.1.1. Training-by-error                                 |     |

| 7.1.3. Implications                                      | 229 |

| 7.1.4. Lessons                                           |     |

|                                                          |     |

| 7.2. Summary                       |  |

|------------------------------------|--|

| 7.2.1. Perceptron Context Learning |  |

| 7.2.2. Value Prediction            |  |

| 7.2.3. Criticality Prediction      |  |

| 7.2.4. History Interference        |  |

| 7.3 Future Work                    |  |

| References                         |  |

|                                    |  |

# List of Tables, Figures, and Illustrations

| Figure 2.1. Rosenblatt's perceptron                                              |      |

|----------------------------------------------------------------------------------|------|

| Figure 2.2. Basic perceptron                                                     | . 14 |

| Figure 2.3. Linear inseparability                                                | . 18 |

| Figure 2.4. Perceptron modeled in hardware                                       | . 19 |

| Table 2.1. Perceptron delays as reported in [Jim02]                              | . 21 |

| Figure 2.5. Perceptron-based branch predictor block diagram                      | . 25 |

| Figure 2.6. Perceptron-based confidence estimator for value prediction           | . 29 |

| Figure 3.1. Compatible patterns and conflicting patterns                         | . 35 |

| Figure 3.2. Learning incompatible patterns                                       | . 37 |

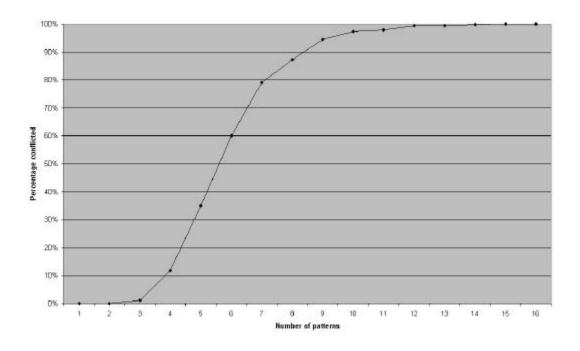

| Figure 3.3. Chance that <i>p</i> patterns will be in conflict                    | . 38 |

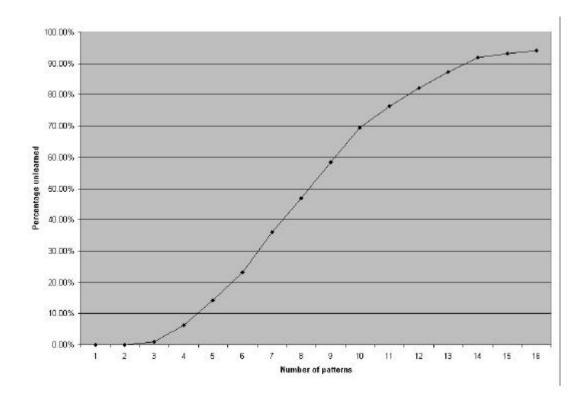

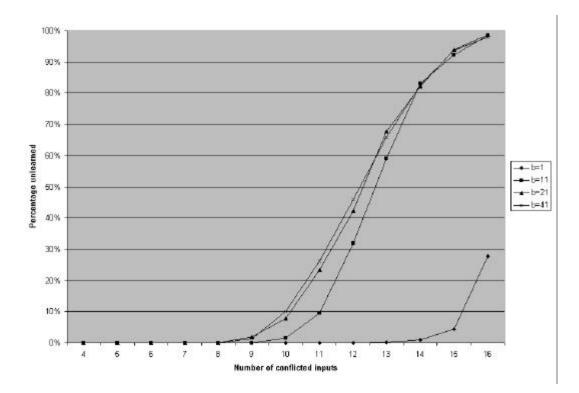

| Figure 3.4. Percentage of the time the perceptron cannot learn <i>p</i> patterns | . 39 |

| Figure 3.5. Effect of imbalance on learning                                      |      |

| Figure 3.6. Unlearnable patterns due to imbalance                                | . 41 |

| Figure 3.7 Imbalanced patterns are learnable with sufficient compatible inputs   | . 42 |

| Figure 3.8: Learnability for 4 patterns                                          | . 44 |

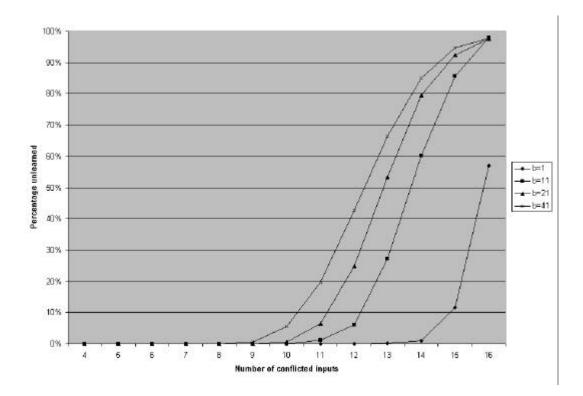

| Figure 3.9: Learnability for 8 patterns                                          | . 45 |

| Figure 3.10: Learnability for 16 patterns                                        | . 45 |

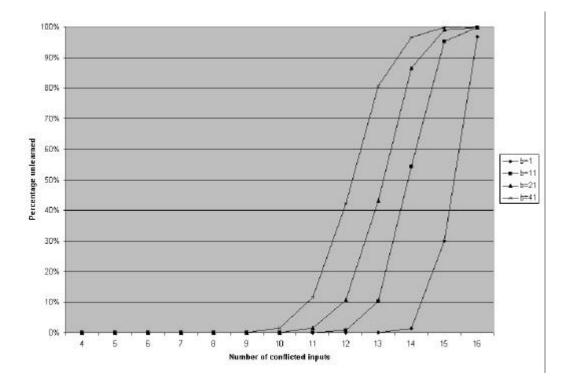

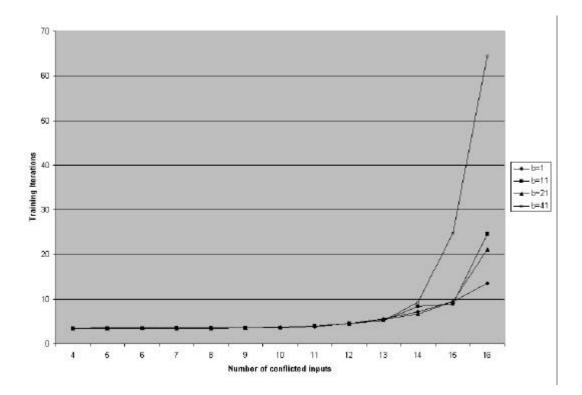

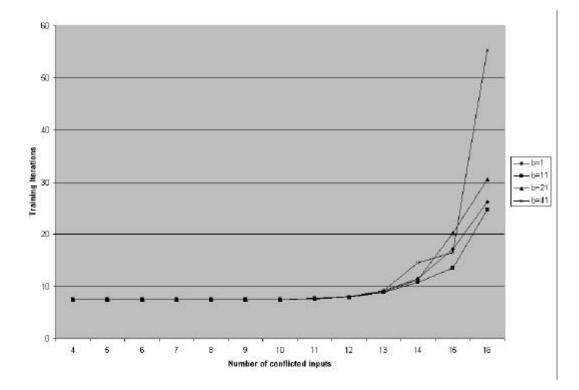

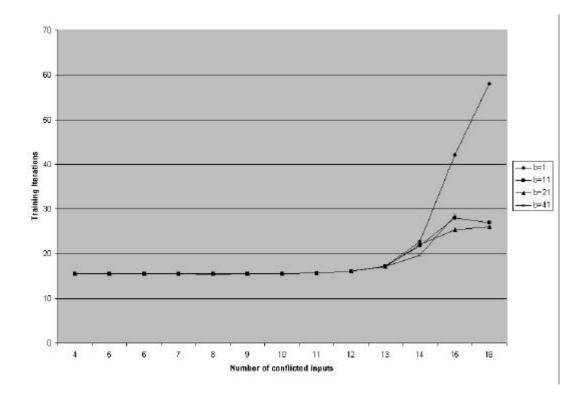

| Figure 3.11: Training time for 4 patterns                                        | . 46 |

| Figure 3.12: Training time for 8 patterns                                        |      |

| Figure 3.13: Training time for 16 patterns                                       |      |

| Figure 3.14. Correlation converted to context patterns                           |      |

| Figure 3.15. A perceptron can learn faster than a table                          |      |

| Figure 3.16. Perceptron masks uncorrelated inputs for a lookup table             | . 51 |

| Figure 3.17. Uncorrelated weight noise can bias a perceptron                     |      |

| Figure 3.18. Training-by-error's handling of false correlations                  | . 61 |

| Figure 3.19. Training-by-error can learn the imbalanced pattern                  | . 62 |

| Figure 3.20. Countering weight noise with exponential growth                     | . 66 |

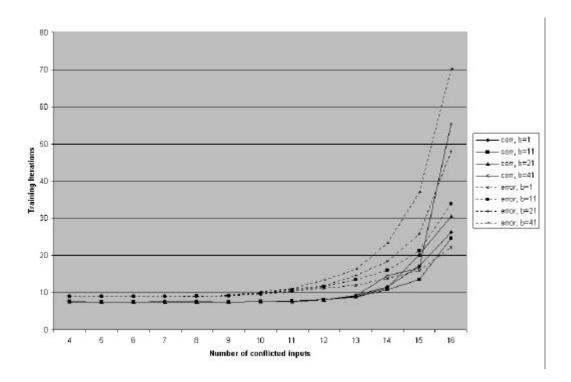

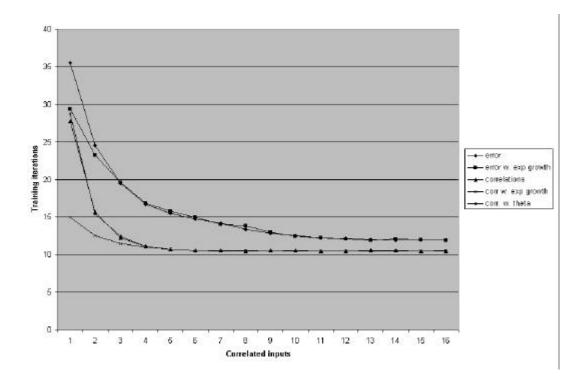

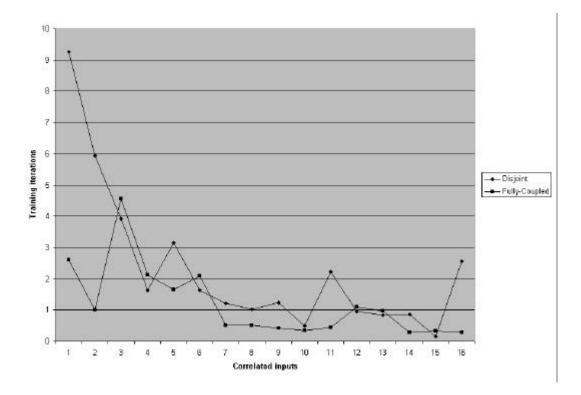

| Figure 3.21. Training time for both training strategies                          | . 68 |

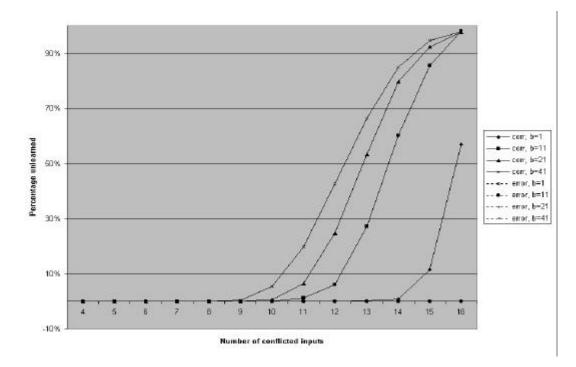

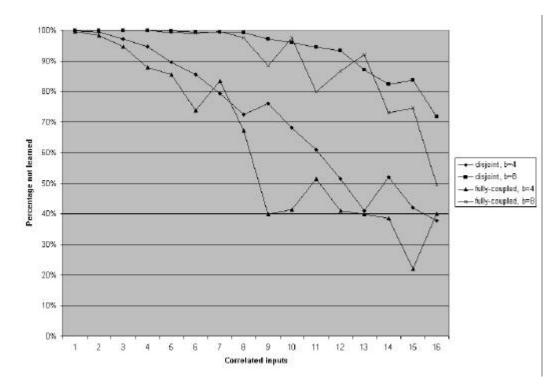

| Figure 3.22. Percentage of patterns unlearned for both training strategies       | . 68 |

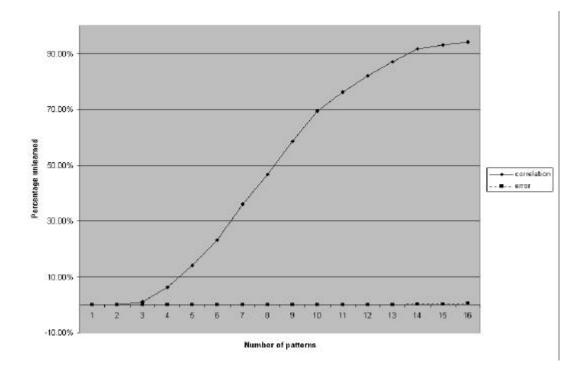

| Figure 3.23. Percentage of the time each training strategy cannot learn          | . 69 |

| Figure 3.24 Training time compared for training strategies                       | . 71 |

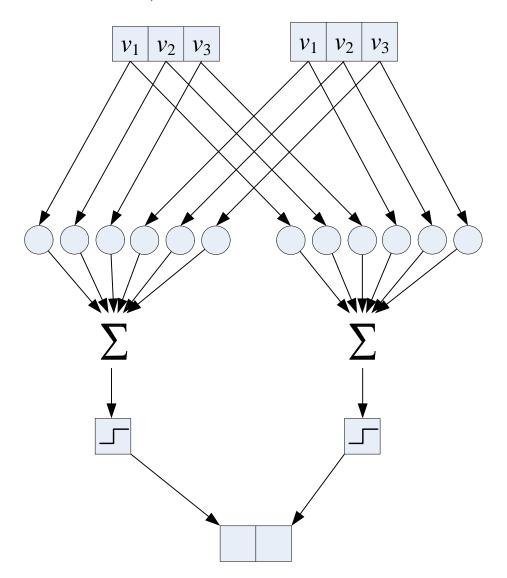

| Figure 3.25. A Multibit Perceptron                                               |      |

| Figure 3.26. Disjoint Perceptron                                                 | . 77 |

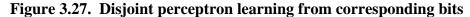

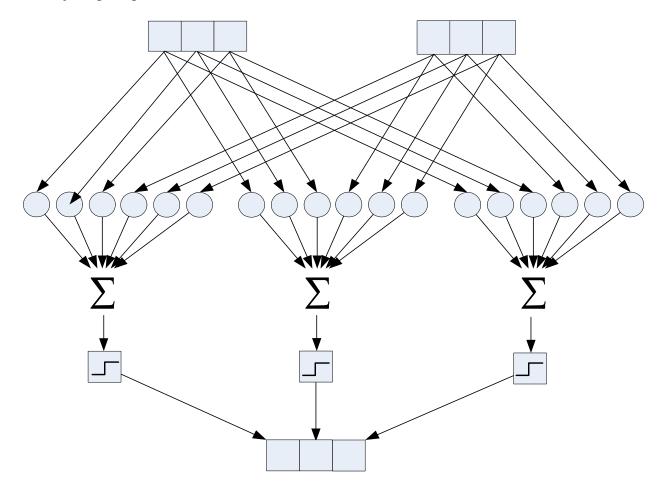

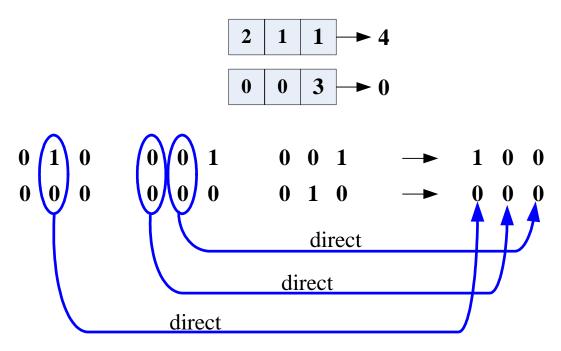

| Figure 3.27. Disjoint perceptron learning from corresponding bits                |      |

| Figure 3.28. Fully-Coupled Perceptron                                            | . 79 |

| Figure 3.29. Disjoint perceptron learning from any bits                          | . 80 |

| Figure 3.30. Learning rates with 2 values per input                              |      |

| Figure 3.31. Learning rates with 4 values per input                              |      |

| Figure 3.32. Training times with 2 values per input and 4 bits                   |      |

| Figure 3.33. Weight-per-value Perceptron                                         |      |

| Figure 3.34. Interference in the branch history                                  | . 90 |

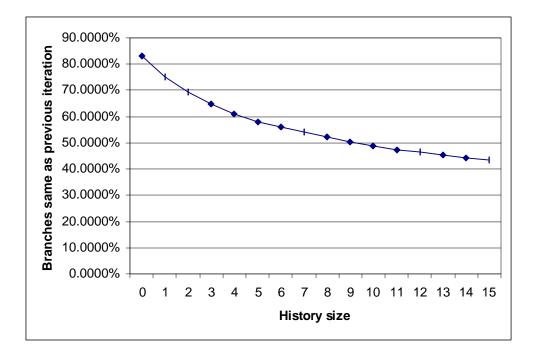

| Figure 3.35. Percentage of branch inputs with the same instruction as the last     |      |

|------------------------------------------------------------------------------------|------|

| iteration                                                                          | . 92 |

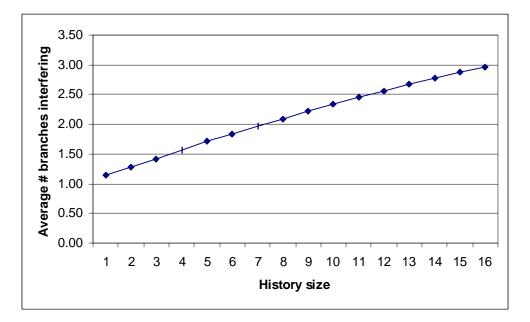

| Figure 3.36. Average number of branches interfering at each input                  | . 92 |

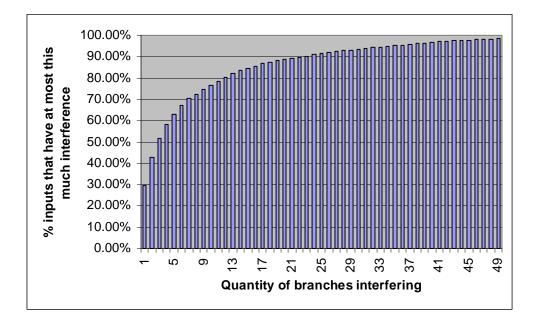

| Figure 3.37. Percentage of inputs suffering from varying interference amounts      | . 93 |

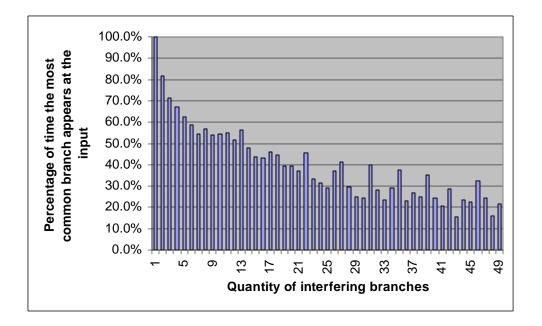

| Figure 3.38. Percentage of the time that a dominating branch is seen at the input  | . 94 |

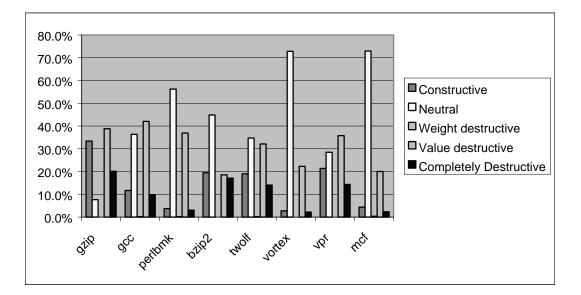

| Figure 3.39. Frequency of each type of branch interference                         | . 97 |

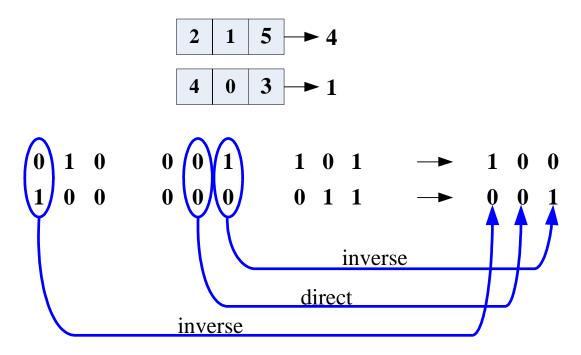

| Figure 3.40. Assigned Seats                                                        | 102  |

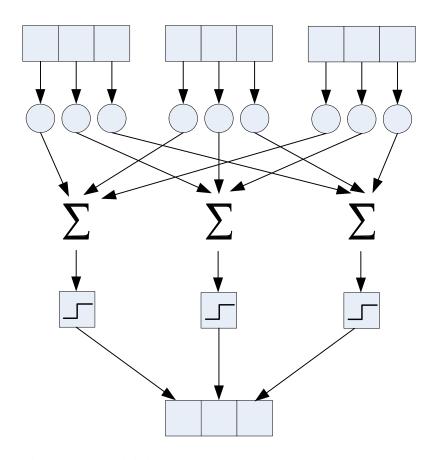

| Figure 3.41. Piecewise Linear Predictor                                            |      |

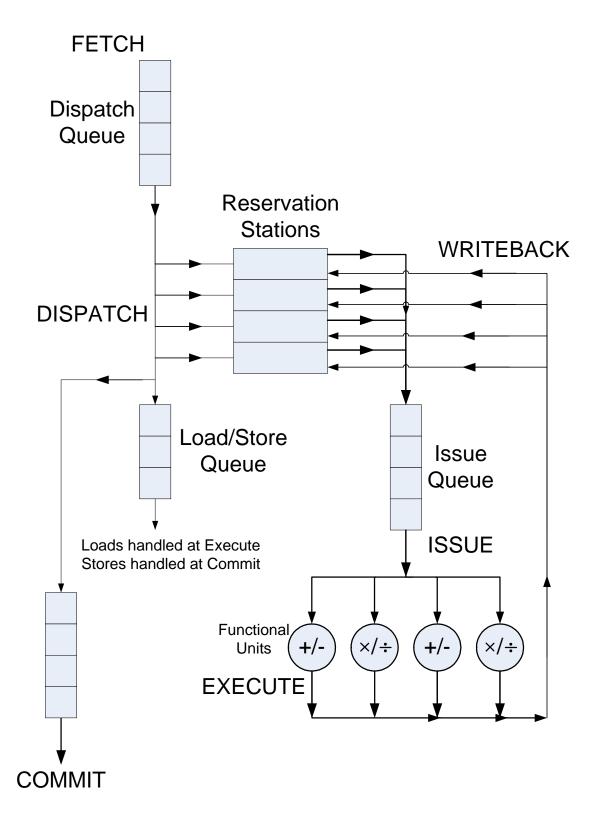

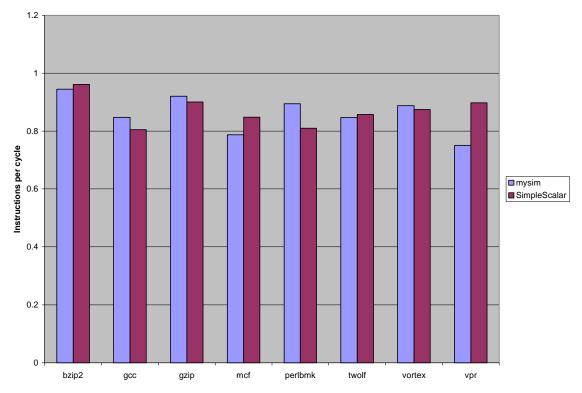

| Figure 4.1. Simulator Block Diagram                                                |      |

| Table 4.1. Benchmarks and parameters                                               | 127  |

| Table 4.2. Relative simulation time of Mysim over Simplescalar                     | 128  |

| Table 4.3. Simulation parameters                                                   | 129  |

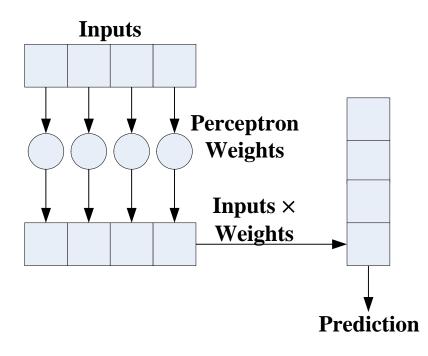

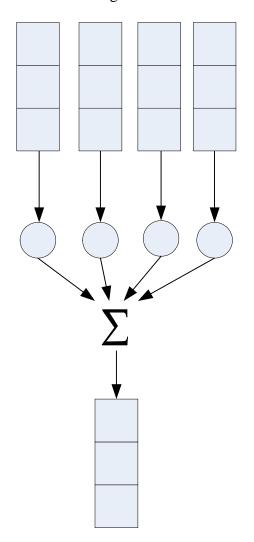

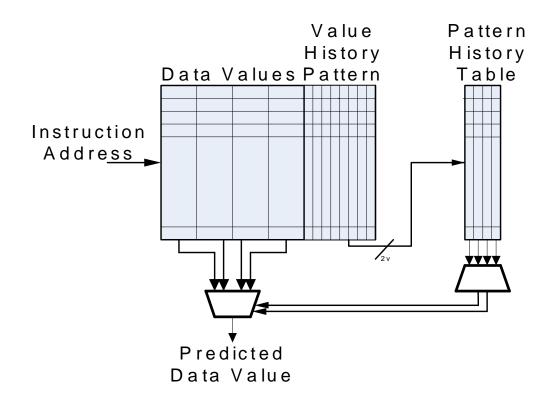

| Figure 5.1. Table-based Value Predictor                                            | 143  |

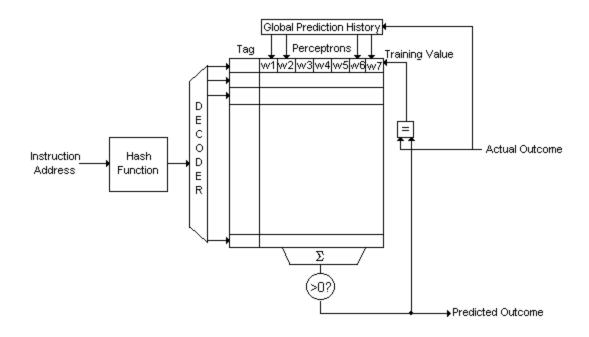

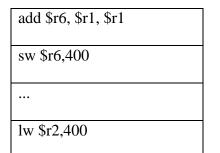

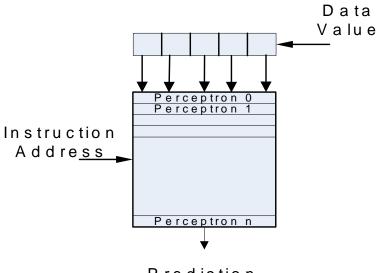

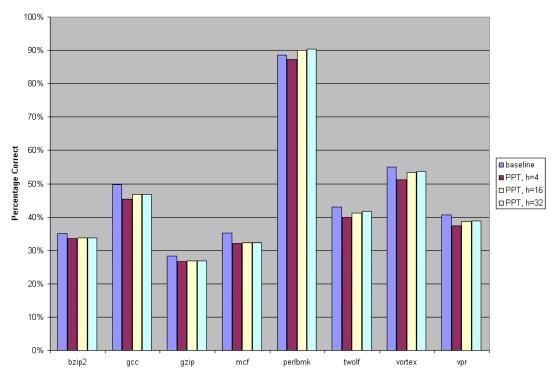

| Figure 5.2: The perceptrons-in-the-pattern-table (PPT) predictor                   | 147  |

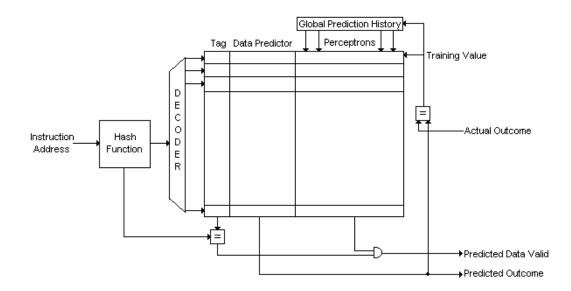

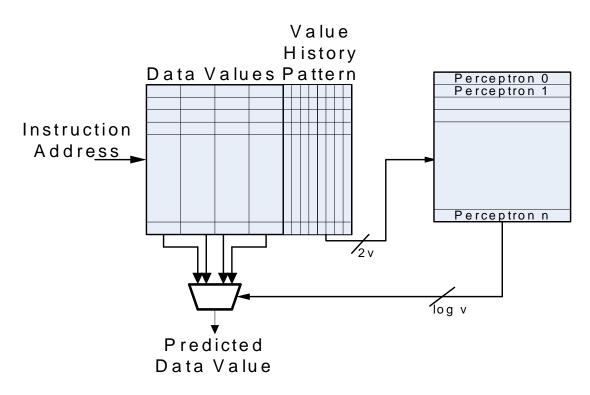

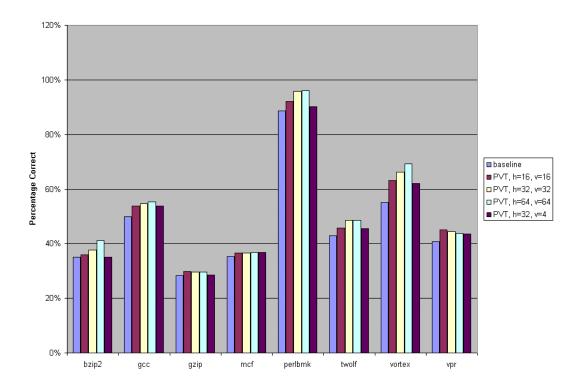

| Figure 5.3. The perceptrons-in-the-value-table (PVT) predictor                     | 151  |

| Figure 5.4. Global value propagation                                               | 153  |

| Figure 5.5. Previous places the current value has been seen                        | 154  |

| Figure 5.6. Global correlations for local values                                   |      |

| Figure 5.7. Global correlations between instructions                               | 156  |

| Table 5.1: Percentage of instructions that repeatedly produce the same 2 values    | 157  |

| Table 5.2. Percentage of instructions globally correlated with a past instruction  | 158  |

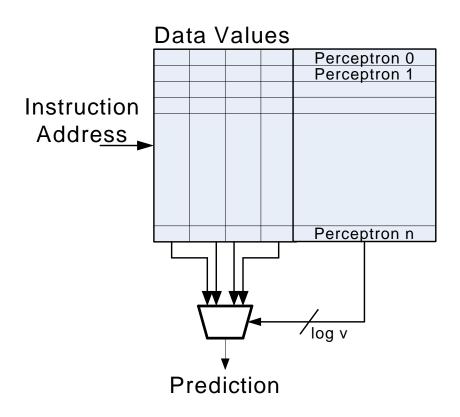

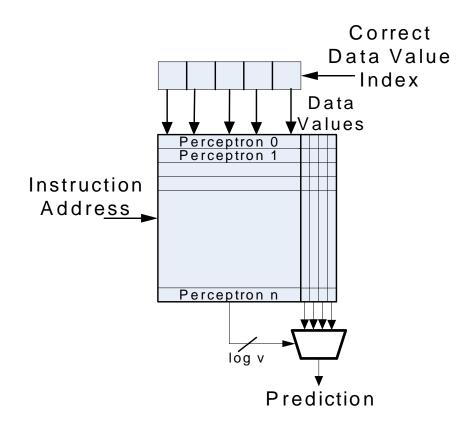

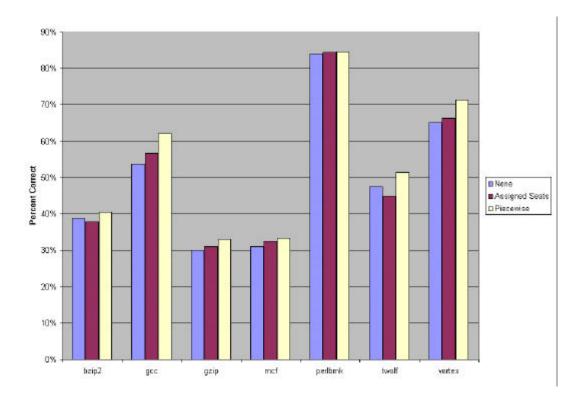

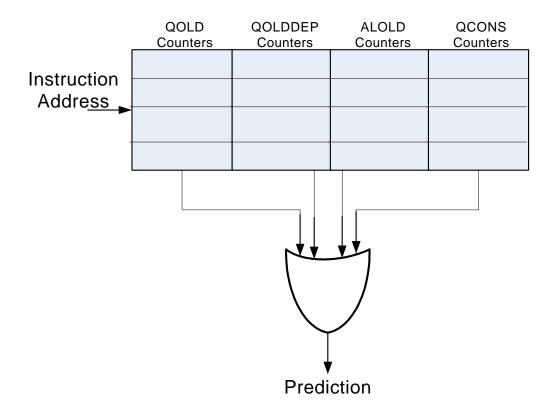

| Figure 5.8. Global-Local Predictor                                                 | 159  |

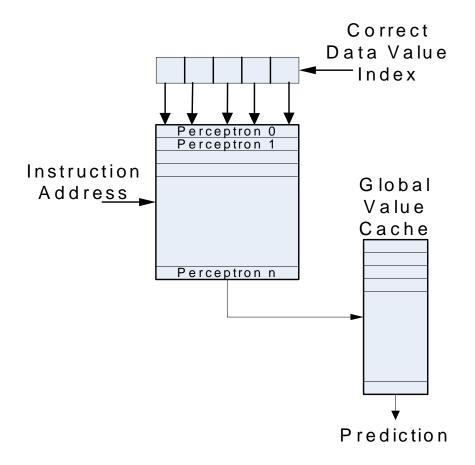

| Figure 5.9. Global-Global Predictor                                                |      |

| Figure 5.10. Bitwise Predictor                                                     |      |

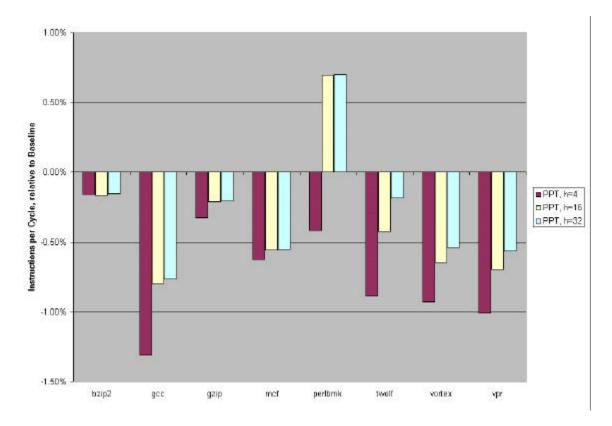

| Figure 5.12. PPT predictor performance                                             |      |

| Figure 5.13. PVT predictor accuracies                                              |      |

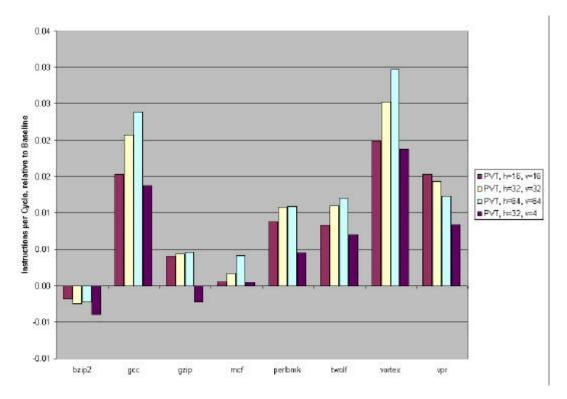

| Figure 5.14. PVT predictor performance                                             |      |

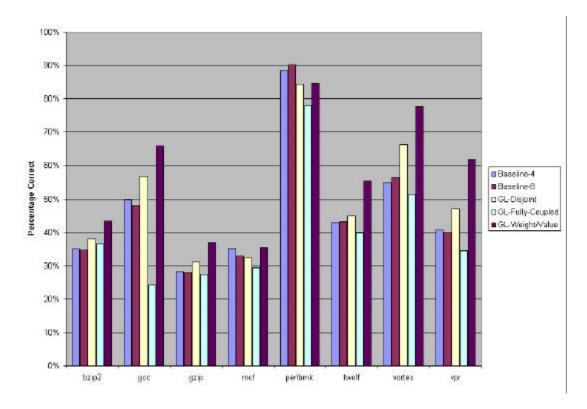

| Figure 5.15. Global-Local Predictor Accuracy for Different Multibit Topologies .   |      |

| Figure 5.16. Global-Local Predictor Performance for Different Topologies           |      |

| Figure 5.20. Correctly predicted data values that have not been produced before    |      |

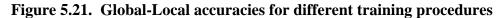

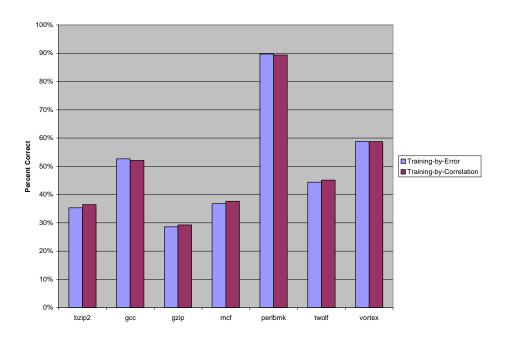

| Figure 5.21. Global-Local accuracies for different training procedures             |      |

| Figure 5.22. PVT accuracies for different training procedures                      |      |

| Table 6.1. Correlation of each criterion with actual criticality                   |      |

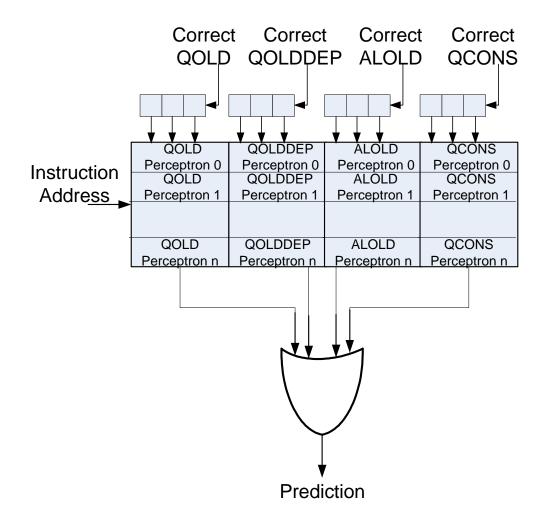

| Figure 6.2: Perceptron for each criterion (PEC) criticality predictor              |      |

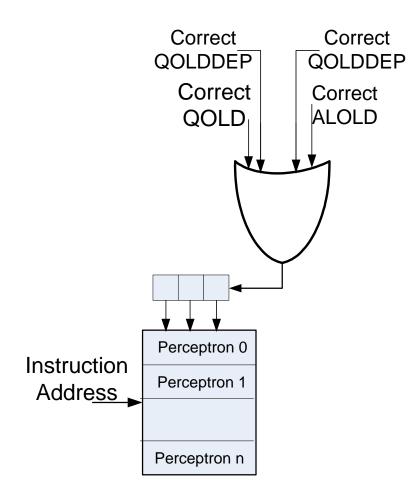

| Figure 6.3. Single perceptron (SP) criticality predictor                           |      |

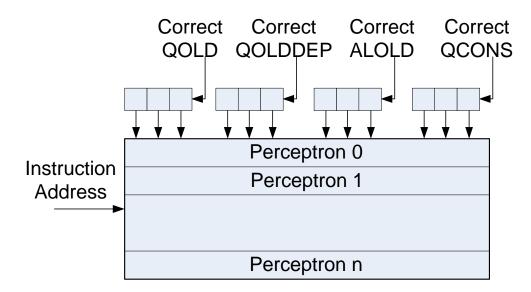

| Figure 6.4. Single perceptron input for each criterion (SPC) criticality predictor | 209  |

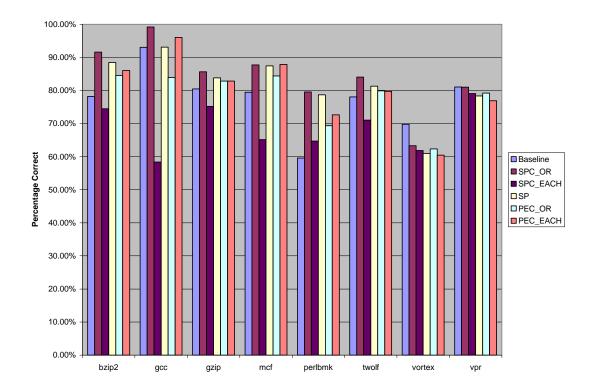

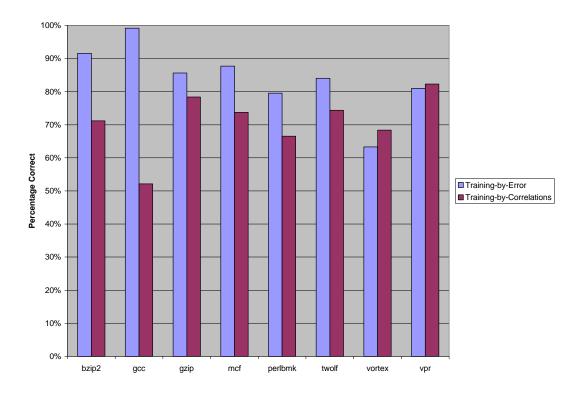

| Figure 6.5. Accuracy of the predictors                                             |      |

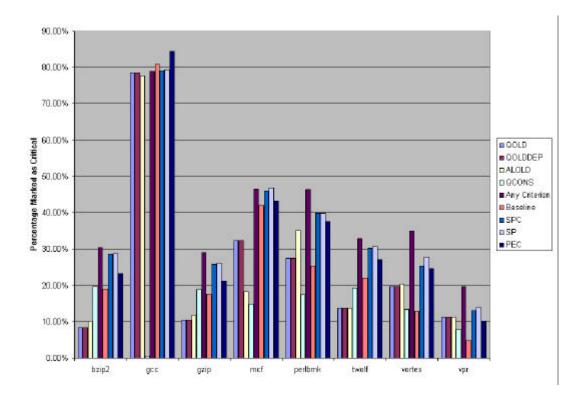

| Figure 6.6. Balance of the predictor results                                       |      |

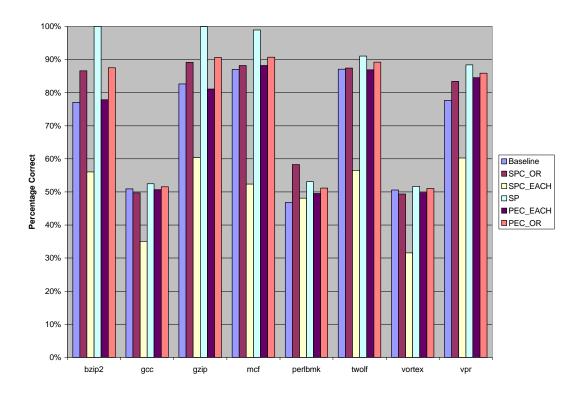

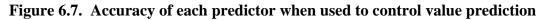

| Figure 6.7. Accuracy of each predictor when used to control value prediction       |      |

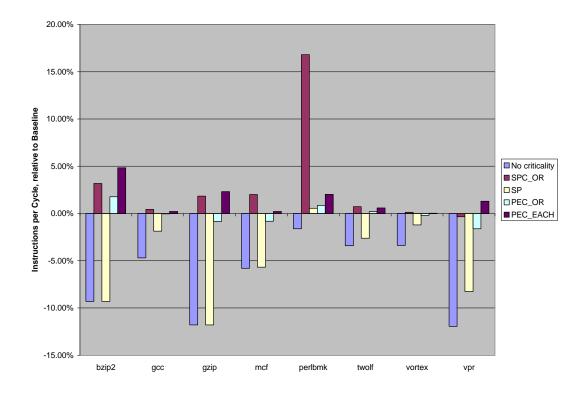

| Figure 6.8. Performance when criticality predictors control value prediction       |      |

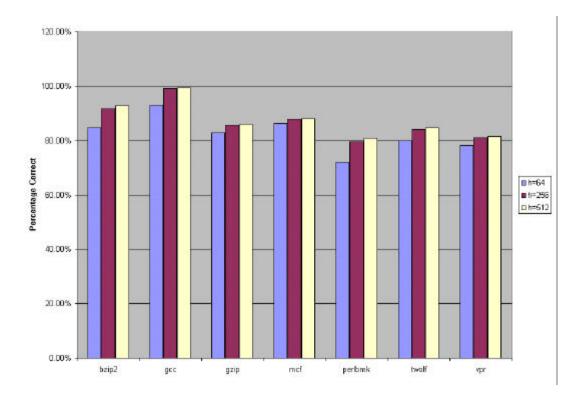

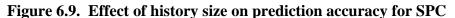

| Figure 6.10. Effect of anti-interference on criticality prediction accuracy        |      |

| Figure 6.11. Effect of training approach on criticality prediction accuracy        |      |

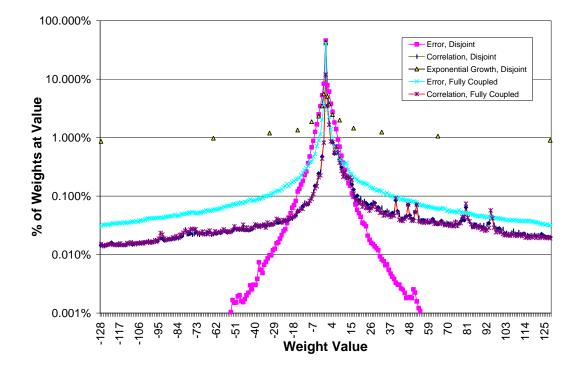

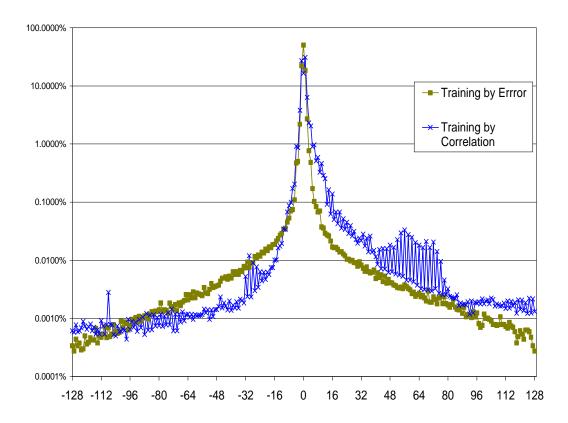

| Figure 7.1. Perceptron weight distribution for the Global-Local predictor          |      |

| Figure 7.2. Perceptron weight distribution for the SPC criticality predictor       |      |

| Figure 7.3. Weight accuracies by final value for the Global-Local predictor        | 228  |

## **Chapter 1: Introduction**

This dissertation studies how perceptrons perform as speculators in microprocessors. I analyze the accuracy and learning capability of perceptron-based predictors and compare them against the more commonly used pattern table-based predictors. I then propose and study perceptron-based predictors in two applications where they have not been widely used before: data value prediction, and dataflow critical-path prediction.

## 1.1. Speculation

Over the last several years, a series of perceptron-based dynamic branch predictors have been proposed, primarily by Daniel Jimenez [Jim00,Jim04,Jim05]. These predictors use very simple single-layer perceptrons to predict the outcome of a branch instruction in a program at runtime. The perceptron is a simple and early form of neural network, of which more complex versions have been widely used in classification and pattern recognition [Sch92,Sch96]. However, up until the work by Jimenez and Lin, neural networks have generally been absent from processor architecture.

Perceptrons, as well as more advanced neural networks, are an artificial intelligence technique meant to mimic the brain. They learn mathematical functions through an iterative process of guessing and training. The neural network is given an input value to a function it is meant to learn. From the function that it has learned so far, it produces an output value based on that input value. The output value is compared to the output value it should have given had the function been accurate, and

the difference is used to adjust the neural network. Over a period of training iterations, the neural network learns the mathematical function without ever being explicitly told what the function is. In fact, the function need not even be known.

At first sight, neural networks seem completely inapplicable to the strict determinism of computer architecture. Computers process data by taking a series of instructions from the programmer and executing them sequentially. An essential characteristic of a computer is its deterministic nature -- for a given set of input data and a given sequence of instructions, the computer will always produce the same output data after executing the instructions. Neural networks, with all their guesswork and approximations, appear to have no place in computer architecture.

However, this is not entirely the case. Modern computer design is very concerned with optimizations. A computer must execute a program correctly, but within that constraint it should run its program quickly, consume little power, be physically small, and cheap to produce. Modern computers must be sensitive to the needs of the application: while a computer running computationally intensive software must execute quickly, a handheld computer should sacrifice speed for low power consumption. An efficient computer processor should be able to adapt its optimization tactics during the execution of a single program and even from one instruction to another.

Speculation plays an increasingly essential role in computer optimization. It is used to create parallelism in sequential programs, to make frequently used data more accessible to the processor, to adjust the speed of computation, and even to determine whether to apply additional speculation [Bur99]. Speculative systems

generally follow the same model. They accumulate information based on earlier program execution. They use the information to make a decision affecting how data is allocated or how the processor executes instructions. The decision can have correct or incorrect results, where a correct result causes an increase in performance, and an incorrect result frequently causes a decrease in performance (as the system has to backtrack and remedy the results of the incorrect decision). In most cases the ideal result, when known, is used to tune the decision maker.

From an intuitive standpoint, neural networks ought to be ideal for making speculative decisions in a computer system. One can imagine a neural network used as follows. Previous execution information can be fed as input to the network. The output can be used as the speculative decision. When the correct result is known later, it can be used to train the network. There are several reasons, however, that have traditionally barred neural networks from microarchitecture. Neural networks suffer from a large hardware complexity. They are slow and training can take many iterations. Additionally, perceptrons suffer from intrinsic limitations that limit what functions they can learn.

This is not to say that neural networks have been completely absent from computer architecture. However, the few previous applications of neural networks in computer architecture have been in situations where slow speed and high physical complexity are permissible, allowing for large multilayer neural networks [Cav97]. High speed speculative problems, particularly those used to increase instruction level parallelism, have until recently been unable to use neural networks.

Branch prediction research, however, has shown that perceptrons' time in computer architecture has come. Single-layer perceptrons do not have the massive size and training time problems of larger neural networks, and the mathematical limitations do not prevent it from performing well in branch prediction. With the shrinking size and cost of hardware removing the barriers, it is time to introduce more intelligent approaches to speculation problems in microarchitecture.

Many speculators in computer architecture tend to use similar prediction approaches. A typical decision-making approach is a hash table of saturating counters, indexed by a history of past data. The value of the selected counter, is compared to a predetermined threshold, and the result relative to that threshold becomes the prediction. The predictor is later trained when the actual result is known by incrementing or decrementing the counter. Such counter based approaches have been proposed for branch prediction [Yeh92], value prediction [Lip96], criticality prediction [Tun01], confidence estimation [Bur99], last touch cache use prediction [Lai00], voltage and frequency scaling [Gov95], and other applications.

The weakness of the saturating counter approach is its physical size. Speculative applications tend to perform better as the past data history size is increased [Yeh92]. However, by using this history size to index the counter table, a single bit increase in history size doubles the size of the table. This exponential growth strictly limits the history size that can be considered. Thus for table-based dynamic branch prediction, a history size of 17 branches was considered a maximum [Yeh93], despite the fact that greater history sizes could further improve the prediction accuracy.

To cope with this limitation, many predictor designs have severely limited the scope of the past data to values that can be most easily used in making predictions. Local predictors were designed, for which only values observed at past instances of the current static instruction were considered in prediction. Because many applications have high local data locality, reasonably good prediction accuracies could be obtained by focusing exclusively on recent local values. This was done, for example, in branch prediction with the PAp predictor [Yeh93], value prediction with the stride and context predictors [Saz97\_2], and criticality prediction with the criteria-based predictors [Tun01]. These table-based predictors obtained fair accuracies while only indexing their tables with a small quantity of past values.

By limiting themselves only to local data, these predictors lose information available globally, or from other instructions, that could allow them to predict more accurately. It has been shown for branch prediction [Yeh93], criticality prediction [Tun02], and confidence estimation [Bla03] that there is information available globally that is not available locally which can improve the accuracy of the predictors. In some studies [Nak99], impractical global predictors were simulated and were shown to substantially outperform the local predictors.

In the perceptron branch predictor, the pattern table indexed by past history is entirely replaced by a perceptron. The advantage of the perceptron is that it grows largely linearly with the past history, not exponentially. The perceptron is thus able to consider significantly longer history sizes than tables and yet remain feasible to implement. Perceptrons are thus able to be used as global predictors. This was the

key factor behind the excellent performance of the perceptron branch predictor [Jim02].

However, the perceptron branch predictor did not perform as well as a global table-based predictor considering an equal size history. The weakness of perceptrons is that they are limited to learning only linearly separable functions. This will be defined in detail in the next chapter. It was found that branch prediction history information often exhibits linearly inseparable functions. The effect of this is that while a perceptron is capable of considering a larger history size than a table, it is typically incapable of extracting as much information from the history as the table.

Despite this learning limitation, the perceptron approach did perform better for branch prediction than other practical predictors. As there are many other speculative applications in which the predictor models are very similar to those in branch prediction, there are other applications that may benefit from a perceptron replacing the pattern-table.

Since the original branch prediction work, perceptrons have been proposed for branch confidence estimation [Akk04] and value prediction confidence estimation [Bla03]. In both of these applications, the table was simply replaced by a perceptron. In some cases, the perceptron performed better. In other cases, it did not [Bla03]. Simply replacing the table with a perceptron without considering the capabilities of the perceptron is likely to produce good predictors only by accident. It is important to understand when and why perceptrons perform better than a table-predictor, what exactly the pattern table learns that they do not learn, and when those unlearnable patterns arise. Knowing this allows a perceptron to be designed that is a good fit for

the application. Perceptrons can be designed with different training procedures or topologies. It is important to understand how to choose the right perceptron for an application.

#### **1.2.** Dissertation Overview

This dissertation has three core parts. In the first part I seek to understand how perceptrons behave and learn in theory when compared to the pattern table. The second and third parts explore different perceptron approaches for data value prediction and critical instruction prediction, respectively.

Why these two applications? Recent past perceptron applications other than branch prediction, such as confidence estimation, use very similar predictor designs to branch prediction. Both confidence estimation and branch prediction use single bit outputs (take/don't take). Both have single bit past inputs. Both can be trained soon after a prediction is made. Value prediction and criticality prediction are interesting because, while being similar to branch prediction in many ways such as latency requirements, each of them pose challenges that branch prediction does not pose.

Value prediction, unlike branch prediction, requires a multiple bit value to be predicted. This raises many challenges. How can a perceptron be best designed to produce multiple bits? Do perceptrons learn the same for multiple bits as for one bit?

Criticality prediction only requires a single bit decision: instruction is on the critical path / instruction is not on the critical path. However, unlike branch prediction, criticality cannot be immediately evaluated for an instruction, even after that instruction commits. How can the predictor be trained? A solution to this is not to train on criticality directly, but to train on whether the instruction exhibits critical

behaviors (or criteria) [Tun01]. However, this introduces additional questions. Which criteria should the perceptron use to train? How should the perceptron train when there are multiple criteria, and multiple correct answers?

My research in this dissertation follows the following methodology. In the theory chapter, I describe different perceptron training approaches and topologies, and determine when one approach works better than another. For both value prediction and criticality, I propose and evaluate many different predictors using different perceptron styles and configurations. These different perceptron predictor configurations are chosen without regard for which theoretically makes the best use of the perceptron for that application. All are evaluated, and through the evaluation it becomes apparent which is the better perceptron approach for that application. Finally, I look at how the perceptrons approaches learned in each application, and analyze why one approach turned out to be a better fit for that application than another.

The dissertation is organized in the following way. The next chapter, Chapter 2, covers the origins and background of perceptrons, and discusses how they are used in branch prediction and confidence estimation.

Chapter 3 contains my theoretical contributions. The chapter first looks at how perceptrons learn relative to how tables learn, and then analyzes several perceptron training approaches. Next it proposes several multibit perceptron topologies, and analyzes how they learn. The chapter finally discusses interference in the history and discusses several ways of overcoming it.

Chapter 4 presents the simulation methodology. It provides a detailed description of the processor simulator I designed for this work. The chapter also provides the simulation parameters used in the subsequent chapter. It finally describes the algorithms used to simulate the perceptrons.

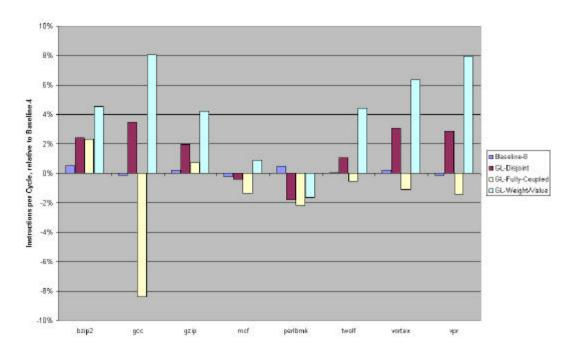

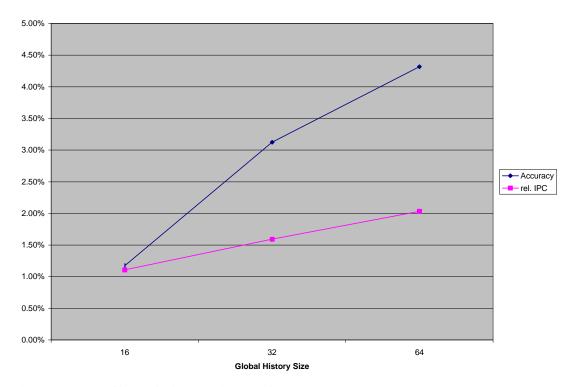

Chapters 5 and 6 respectively propose and evaluate several perceptron value prediction and criticality prediction approaches. Both chapters commence with a background discussing previous work in value prediction and criticality prediction. In Chapter 5 I next propose two perceptron predictors that only consider local value history, a perceptron predictor that considers global history to predict locally available values, a perceptron predictor that predicts past globally available values, and a perceptron predictor that can produce new data values. In Chapter 6 I propose four different configurations for a perceptron criticality predictor. Chapters 5 and 6 conclude by evaluating each perceptron predictor against a standard baseline predictor. In Chapter 5, improvements are shown over the baseline in both prediction accuracy and instruction-per-cycle performance for several of the value predictors. In Chapter 6, improvements are shown over the baseline in predictors. In Chapter 6, improvements are shown over the baseline in predictors. In Several of the criticality predictors. Performance improvement is then demonstrated by using the criticality predictors as confidence estimators for value prediction.

In Chapter 7, which concludes the dissertation, the perceptron weight values and performances for different training styles are used to determine why one perceptron approach works better than another perceptron approach for each application. The chapter concludes by summarizing the dissertation findings and results, and proposes some future areas of study.

## **1.3.** Contributions

The following is a concise list of the contributions of this dissertation: In Chapter 3:

- An analysis of how perceptrons learn context patterns with regard to imbalance between patterns and compatibility between patterns

- An analysis of two perceptron training strategies and their learning rates with regard to the number of correlated inputs

- Three multibit perceptron topologies: disjoint, fully coupled, weight for each input value and an analysis of the number of value correlations each can learn

- An analysis of history interference, its effect on perceptron learning, and two strategies for combating it: assigned seats, piecewise linear

In Chapter 4:

• A completely new execution-driven out-of-order processor simulator

In Chapter 5:

- Two perceptron-based local value predictors: perceptrons in value table, perceptrons in pattern table

- Three perceptron-based local predictors using global information, based on the three multibit topologies.

- A perceptron-based global predictor using a global value cache

- A perceptron-based global predictor using no stored past values (bitwise)

In Chapter 6:

• Three perceptron-based critical criteria prediction approaches

## **Chapter 2. Background**

### 2.1. The Perceptron

The perceptron model used in the recent branch prediction research is possibly the simplest and earliest nontrivial neural network model in existence. It is common for textbooks on neural networks to open with that example before proceeding to more complex neural networks [Rus95]. The reasons for its use in branch prediction, as mentioned previously, are due to strict speed and training latency restrictions.

Modern neural network research has largely forsaken the original perceptron, due to its learning restrictions and simplicity. In fact, a scan of all the papers published in the IEEE Transactions on Neural Networks since 1990 shows only 3 papers that even mention this perceptron model in the title or abstract, and no papers that deal with it exclusively. Besides computer architecture, there would appear to be no major current applications of the basic perceptron. Consequently, to find any analyses of the perceptron, it is necessary to step back 40-50 years to the original work that proposed it.

### 2.1.1. Rosenblatt's perceptron

The earliest form of neural network, the perceptron, was first formally proposed by Frank Rosenblatt in 1957, and was inspired partly from a symbolic logic representation of neuron cells introduced by McCulloch and Pitts in 1943 [Nag91]. Modeled after collections of neurons, the perceptron was among the first so-called "black box" artificial intelligence approaches, which could learn functions and perform tasks without being explicitly told the rules [Rus95]. Although the

perceptron and neural networks were at first supposed to be the key to artificial intelligence, not to mention a tool for understanding the brain, perceptrons have since become generally limited to the role of pattern recognition and classification.

In his book "Principles of Neurodynamics", Rosenblatt defines perceptrons thus: "a set of signal generating units (or "neurons") connected together to form a network. Each of these units, upon receiving a suitable input signal (either from other units in the network or from the environment) responds by generating an output signal, which may be transmitted, through connections, to a selected set of receiving units" [Ros62].

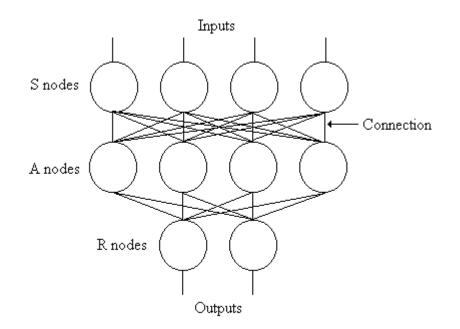

Rosenblatt defined the perceptron in terms of S (sensory) units, A (association) units, and R (response) units, the coupling of which is defined by an interaction matrix. At this time, perceptrons were considered in terms of a computer software model (to be simulated on the Mark I) and the interaction matrix comprised the memory of the neural network. The S units were defined as a "transducer responding to physical energy" which "generates an output signal si=+1 if its input signal exceeds a given threshold, and 0 otherwise." The A unit is "a logical decision element which generates an output signal if the algebraic sum of the input signals alpha is equal or greater than a threshold quantity theta>0. The output signal is equal to 1 if alpha>=theta and 0 otherwise. If alpha=+1, the unit is said to be active." The R unit "emits the output r=+1 is the sum of it input signals is strictly positive, and r=-1 if the sum of the input signals is strictly negative. If the sum of the input signals is zero, the output can be considered equal to zero or indeterminate." The interaction matrix is "the matrix of coupling coefficients for all pairs of units." Each pair has a

value in the matrix; if the value is zero the units are considered unconnected. Rosenblatt defines a "simple perceptron" as a perceptron satisfying five conditions, among them that there is only one R unit with a connection from every A unit, that the perceptron has connections only from S unit to A units and A to R units, the S to A connections have an unchanging unit value, and that the connections are unidirectional. An example of this is shown in Figure 2.1. In modern work, this simple perceptron has become what is meant when the word "perceptron" is used.

#### Figure 2.1. Rosenblatt's perceptron

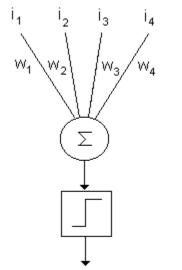

In this dissertation, the units will be called with more modern names. The S units are called "inputs," and always output a value of 1 or -1. In most of the applications discussed, the stimuli are single bits; thus the purpose of the input is to simply convert 0 to -1. The A units, which were later renamed "hidden nodes", are simply dispensed with, and the inputs are directly connected to the R unit. The value

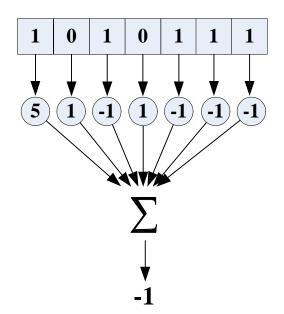

of the connection between each input and the R unit is called a "weight" - these weights comprise the entire storage of the network. Like in Rosenblatt's definitions, the value arriving at the R unit from the inputs is the 1 / -1 input value times the weight. The R unit performs two functions: it sums the weights, and it compares with the threshold to produce the output value. In this dissertation the unit will simply be considered as a sum unit and a threshold unit. Figure 2.2 shows this perceptron. It effectively takes the dot produce of the inputs and the weights, and returns 1 if that dot produce exceeds the threshold, and -1 otherwise. Thus the perceptron basically predicts using:

$$\sum W_{k}I_{k} > 0? \ 1 / -1.$$

Figure 2.2. Basic perceptron

#### 2.1.2. Training

The purpose of the training procedures is to adjust the weights in response to a desired output, so that the perceptron can learn to predict that output for a current set of inputs. Rosenblatt introduces three training procedures: response-controlled

reinforcement, stimulus-controlled reinforcement, and error-corrective reinforcement. Two weight adjustment methods are proposed: "alpha system reinforcement", which adjusts the weights by a constant value *eta*, and "gamma system reinforcement", which adjusts in such a way that the total quantity of all weights is zero. In this dissertation, only alpha system reinforcement is used. Response-controlled reinforcement determines eta entirely from the output value of the perceptron, and adjusts all weights equally. This approach, being highly limited, is not used in this dissertation, and as far as I can tell, has not been seriously considered since Rosenblatt. Stimulus-controlled reinforcement, which I term "training-bycorrelation", has been used in the perceptron branch prediction work. It uses the input values to determine eta for each weight. Error-corrective reinforcement, which I term "training-by-error", adjusts weights only when the perceptron is wrong; it determines an error value using the output value of the perceptron, and uses the input values to determine an eta for each input. The magnitude of eta for alpha system reinforcement is called alpha; in this dissertation, an alpha of 1 is always used.

The objective of the perceptron is to learn correlations between each input value and the output. Each weight determines what and how much effect its input has on the output. A positive weight means that the input has a direct effect on the output, whereas a negative weight means the input has an inverse effect on the output. If the weight is close to zero, the input is found to have little effect on the output; if the weight has a large magnitude it has a strong effect on the output. Thus the perceptron is able to judge which inputs affect the output, and to what degree they do.

The objective of training is to adjust the weight value according to the perceived correlation.

Training-by-correlation works as follows. The weights are adjusted in response to the correlation observed for each input. Thus if an input is the same as the desired output, the weight for that input is incremented; if it is different, the weight is decremented. The prediction output of the perceptron is not taken into account.

Training-by-error only adjusts if the perceptron was wrong. An error value a is computed as a = desired output - predicted output. The perceptron is trained by multiplying a by each input and adding it to the corresponding weight:

$$(w_k = w_k + i_k \boldsymbol{e}).$$

Not yet covered is how the threshold value theta is chosen. One simple approach is to use a constant value, such as 0. However, it is generally considered desirable to dynamically adjust theta in such a way that it reflect the proportion of desired 1 outputs to desired 0 outputs (the more 1's, the lower the theta). This can be accomplished by subtracting the desired output from theta, in training-by-correlation, or the error, in training-by-error. A more easily implemented way, however, which is mathematically equivalent is to have an extra weight "bias weight" connected to an extra input hardwired to 1 [Rus95]. The bias weight is adjusted like any other weight, according to the training policy, and is added to the sum to produce the perceptron output. By including a bias weight, theta can be permanently set to 0.

#### 2.1.3. Linear Inseparability

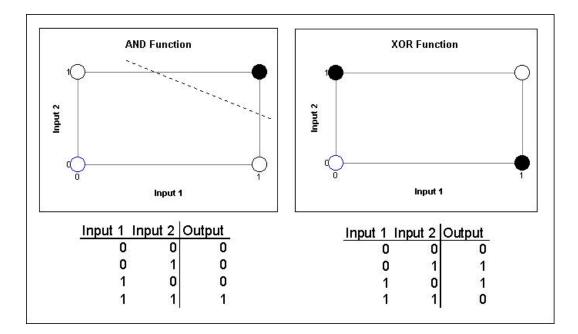

It was originally theorized that neural networks, of unlimited size, could learn all continuous functions. In a 1969 work by Minsky and Papert [Min69], it was shown that this was not the case for perceptrons; that they were in fact limited to learning only functions that are "linearly separable." Minsky's work originally claimed that this was the case for all neural networks, but it was later discovered that linearly inseparable functions can be learned in larger neural networks using hidden layers and more advanced training mechanisms. However, this is still a handicap for the simple single-layered perceptron.

Linear separability is classically pictured geometrically in an *n*-dimensional space, where *n* is the number of inputs. All the possible outputs are placed in the space. If the space can be divided by a plane so that all positive outputs are on one side of the plane and all negative outputs are on the other side, the function is linearly separable [Rus95]. If no plane can be drawn, the function cannot be learned by a perceptron. This is illustrated in Figure 2.3 with the AND function, which is linearly separable, and the XOR function, which is not. This geometrical analysis most likely became popular because image classification was one of the first major applications of neural networks.

#### Figure 2.3. Linear inseparability

Linear separability may be better illustrated for computer architecture applications by looking intuitively at why perceptrons can only learn such functions. In a perceptron, the effect of an input on the output is determined by its weight. As stated before, a positive weight means that the output varies directly with the input, while a negative weight causes the output to vary inversely with the input. Based on its weight, a 1 at a particular input can make the total output more positive or more negative. However, a 1 at a particular input cannot make the total output more positive sometimes and more negative at other times. Functions tend not to be linearly separable if one input's effect on the output relies on another input's effect. The effect of limiting a perceptron to linear separable functions is analyzed in more depth in the next chapter.

#### **2.1.4.** The Perceptron in Hardware

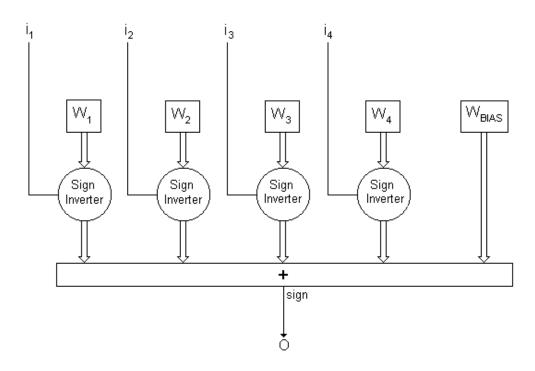

Figure 2.4 shows how a perceptron can be implemented in hardware. The weights are implemented as up-down binary counters that saturate at maximum and minimum values (the minimum has the same magnitude as the maximum and opposite sign). The range of the weights needed to learn effectively is analyzed in Chapter 7; weights with a size ranging from 6 to 9 bits tend to suffice. The analyses in [Jim02] used an 8 bit weight.

#### Figure 2.4. Perceptron modeled in hardware

Because an input bit is interpreted only as -1 or 1, the product between the input bit and its corresponding weight can be implemented simply by using the input bit to choose whether to invert the sign of the weight. These products are summed together, but by using a threshold of 0, only the sign of the total sum is used as the output.

To implement training-by-error, the weights are only adjusted if actual XOR predicted is 1. In this case, the error is 1 if a-p is 2, and -1 if a-p is -2; thus the error is simply a if the weights are adjusted. The weight adjustment, eta, is simply a XOR error (with 0 changed to -1) added to the weights. Because eta is always of magnitude 1, the weights can be simply implemented as a binary counter.

Thus the primary hardware costs are 1) the storage of each weight bit, and 2) the binary adder to sum all the weights, with the remaining logic being of trivial size in comparison. Of these, the storage complexity grows for n inputs at O(n) for the weights, and O(n log n) for the adder [Jim02]. The prediction delay grows at O(log n) for the adder, and is O(1) elsewhere, if a Wallace-Tree adder is used. Training time is O(1). In their analysis, the authors determined that the physical space cost was dominated by the weight storage. In the cost analyses of the various perceptron approach described in this dissertation, the weight storage space for 8-bit weights is used as physical cost of the perceptron.

The hardware latencies were formally analyzed in [Jim02] using HSPICE to model the perceptron and CACTI to model tables of perceptrons. Table 2.1 shows the perceptron delay as a function of perceptron inputs using 180 nm technology as reported in [Jim02]. The delay in indexing a 4096 entry perceptron table was reported as 571 ps. Thus the total latency for making predictions can be determined by adding the two figures. On a 1 GHz processor, a prediction for a perceptron with a 16 bit history takes 1.7 cycles. As processor speeds increase, this number will grow worse, but as transistor technology improves, it should grow better. In this

dissertation, it is assumed that all predictions can be made in 2 cycles or less, and training can be performed in 1 cycle.

| History | Perceptron Delay |

|---------|------------------|

| Size    | (ps)             |

| 4       | 811              |

| 9       | 725              |

| 13      | 1090             |

| 17      | 1170             |

| 23      | 1860             |

#### Table 2.1. Perceptron delays as reported in [Jim02]

This 2 cycle latency was a problem for branch prediction because branch predictions must be made at Fetch. In the other applications analyzed in this dissertation, predictions are not needed until Dispatch, while the information needed to make predictions (the instruction PC) is available at Fetch. Consequently, the prediction latency is not considered as an issue in this work.

## 2.1.5. Multilayer Neural Networks

Most modern neural networks have multiple layers and more elaborate training approaches. A standard approach used for training is backpropagation, which was described in [Rus95]. A three layer neural network employing backpropagation is capable of learning linearly inseparable functions.

Although multilevel neural networks, once trained, might theoretically outperform perceptrons in speculation, there are several problems with employing them. The first problem is the physical size of adding additional layers with additional weights. Adding a hidden layer effectively doubles the size of the network. A more serious problem is the additional latency of performing another summation. Doubling the latency to 4 cycles would have a substantial deleterious effect on neural approaches to the applications discussed here; even making the predictor redundant.

However, the most serious problems relate to training. Backpropagation requires a continuous threshold function because the derivative of the threshold function is used to adjust the weights. The perceptron threshold function is the step function, which cannot be differentiated. Most neural networks employing

$\frac{1}{1+e^{-x}}$  as a threshold function because it approximates the shape and mathematical characteristics of the step function while being continuous (and differentiable). However, using a continuous function requires floating point numbers (or at least large integers), substantially complicating the hardware costs and increasing the latencies. This may be compensated by implementing the neural network as analog components, but it is not clear that analog neural networks yet run at the desired latencies.

The most serious concern is training time. As will be shown in the next chapter, perceptrons can typically be trained in approximately the same number of training iterations as the table-based predictors they replace. Because of the slower learning rate and multiple layers, larger neural networks require substantially more (orders of magnitude higher) training iterations to learn. This makes them slow to predict correctly at first, and slow to adapt to context changes in programs. Thus even if a high latency, implementable multilevel neural network could be implemented, it would be highly unlikely to predict accurately as rapidly as the perceptron, and would consequently almost certainly perform worse.

## **2.2. Perceptron Branch Prediction and Other Architecture Applications**

Branch prediction, being the first successful perceptron application, becomes my template for designing other perceptron predictors. Before discussing other approaches, it is necessary to cover perceptron branch prediction, how it works, and where it evolved from.

#### 2.2.1. The Two-Level Branch Predictor

The two-level branch predictor, proposed by Yeh and Patt in 1992 [Yeh92], became a standard for branch predictor design. The predictor was based off of the original dynamic branch predictor by Smith, which worked by using a table of counters hashed by the branch PC. The Yeh and Patt predictor took this a step further by using information from other branch instructions to make predictions. A shift register holding the history of global branch outcomes was used to hash a second table of counters. Their significantly more accurate two-level predictor captured correlations between the outcomes of different branch instructions. A variation on the two-level predictor that uses a combination of global branch history and branch PC to hash the counter table, McFarling's gshare predictor became widely used as a baseline predictor for performance comparisons.

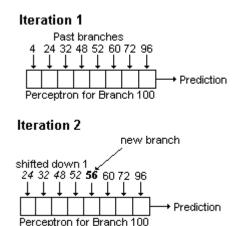

The Yeh and Patt PAg predictor works as follows. A global history of branch directions is stored in a shift register. Branch outcomes are shifted into the table as soon as they are known. A pattern table is selected from a table of pattern tables using the lower bits of the current branch program counter. The concatenated binary branch outcomes form an index to this pattern table, selecting a saturating counter.

This counter value determines whether to take the branch prediction; if it is greater than a threshold, it predicts take, otherwise it predicts to not take.

The problem with this prediction approach is its large size. The pattern table grows exponentially with the number of bits in the history register, and it then must be replicated for each branch instruction in the first level table. Because this predictor was too massive to be practical (it was estimated that the global history size cannot exceed 17 and be practical [Yeh93]), the gshare predictor emerged. It uses a global pattern table, but is indexed by the global branch history XORed with the current branch PC, making a unique index. The gshare predictor was claimed to achieve 97% accuracy for 32k hardware size [McF93]. However, the weakness of the predictor is the aliasing between hashes to the global table. McFarling's own measurements showed a local PAp predictor performing significantly better.

#### **2.2.2. Perceptron Branch Prediction**

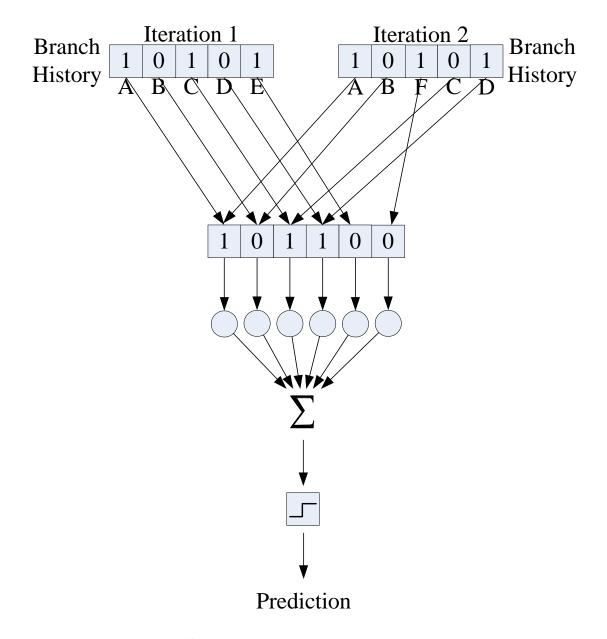

The success of the perceptron branch prediction, proposed by Jimenez and Lin [Jim00], over gshare is partly due to the fact that it is effectively a PAp predictor without the problems of exponential table growth. The aliasing problems of gshare are thus avoided. Figure 2.5 shows a block diagram of this predictor. A global branch history stores the recent branch outcomes. The last bits of the branch instruction address index a table of perceptrons (analogous to the table of pattern tables) and choose a perceptron. Each branch outcome is converted to a 1 or -1 and is fed to a separate perceptron input. The perceptron output is simply the decision of whether to take the branch or not. Training is performed using the training-bycorrelations approach.

#### Figure 2.5. Perceptron-based branch predictor block diagram

In their earliest paper, the authors claimed a 25.6% reduction in relative misprediction rate over gshare at a 128k hardware size, and estimated a 18% increase in program performance [Jim00]. In follow up work the authors increased the misprediction rate to 27% [Jim02]. However, the predictor suffered from a 2 cycle long latency, making it impractical to achieve this rate initially. To compensate for latency issues, the authors used a gshare predictor to make the initial prediction, and then used a perceptron on the next cycle to overturn the gshare prediction if inaccurate [Jim00].

In a more extensive follow-up work that considered latency and hardware size issues, the authors also tried to quantify the branch information that the perceptron could not learn. They determined linearly inseparable branches as sets of branch history patterns that required the perceptron to learn a linearly inseparable function. They found that approximately 3-4% of branches had completely linearly inseparable

functions [Jim02]. They also found that when the history size was increased, the perceptron was more capable of learning the linearly inseparable functions. My analysis and rationale behind this phenomenon is explained in detail in the first part of Chapter 3.

It is important to note that this is not the very first neural branch predictor proposed. Two neural approaches were proposed in a paper by Vintan in 1999 [Vin99]. These predictors were not even close to practical from a hardware standpoint, however, but did manage to achieve accuracies comparable to the tablebased approaches. An even earlier seminar paper in 1996 by Kuvayev [Kuv96] claims to have developed a neural branch predictor; however, the prediction algorithms, predictor topology, and methodology are never mentioned in the paper.

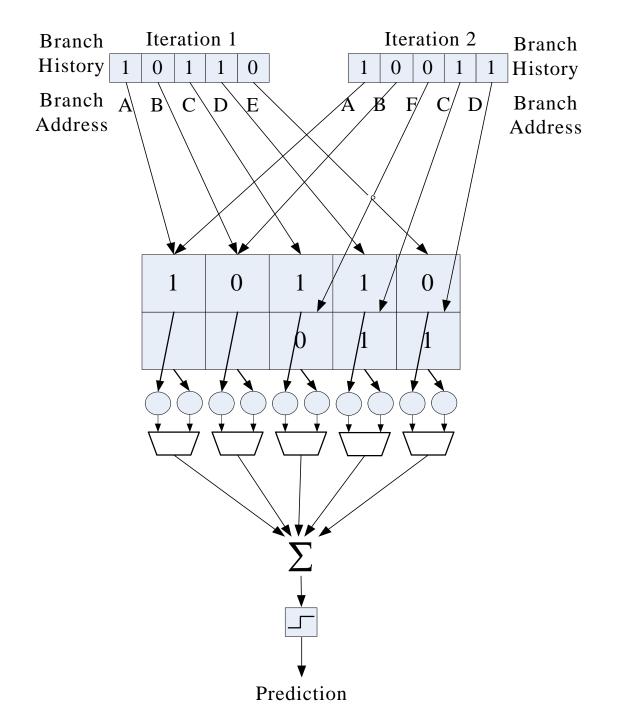

### 2.2.3. Piecewise Linear Predictor

Jimenez refined his predictor in a follow up work [Jim05], which addressed interference problems in the global history table. His piecewise linear predictor maintains the past branch addresses as well as past branch history. Rather than have a single weight for each history entry, an array of weights is maintained, and is selected using the history. This avoids multiple branches from occurring at the same global history entry and interfering with each other. A 3.21% misprediction rate was claimed for this predictor at a history length of over 80. This predictor is discussed in detail at the end of Chapter 3.

#### 2.2.4. Other Perceptron Applications in Architecture

Two additional notable perceptron applications are both in confidence estimation. Branch confidence estimation was explored in [Akk04]. Confidence estimation for value prediction was explored in [Bla03,Bla04,Bla05\_2].

# **2.2.4.1.** Perceptron-based Confidence Estimation for Branch Prediction

Perceptron-based branch confidence estimation, while suggested as a future work by Jimenez [Jim00], was first performed by Akkary et al in 2004 [Akk04]. Confidence estimation for branch prediction has been proposed to limit CPU resources wasted in predicting unpredictable branches. It is practical if the CPU resources dedicated to prediction could be used for other tasks, or if the branch predictor consumes sufficient power so that not predicting can significantly reduce the CPU energy usage. As branch predictors become more complex (the perceptron branch predictor being a case in point), reducing the energy consumption of the branch predictor becomes increasingly useful [Gru98].

The perceptron-based branch confidence estimator is virtually identical to the perceptron branch predictor, with a global branch history and a table of perceptron indexed by the branch instruction address. The key difference is that the accuracy of the branch prediction is stored in the global history rather than the direction of the branch. The authors evaluated their predictor against a preexisting table-based branch confidence estimator that was organized similarly to gshare. The authors claimed a 10% reduction in the number of microoperations performed by the CPU without a loss in performance.

An interesting facet of this branch confidence estimator is that, while it is clearly based on Jimenez's perceptron branch predictor, it uses a training-by-error training strategy rather than the training-by-correlation strategy which Jimenez consistently used in his predictor. Since the reason for the change is not discussed (and in fact the authors even explicitly claim that the training approach is based on Jimenez) it is tempting to assume that the authors were not aware that they were using a different training strategy.

# **2.2.4.2.** Perceptron-based Confidence Estimation for Value Prediction

Confidence estimation for value prediction was introduced by this author in my Master's thesis and is detailed in [Bla03]. Confidence estimation is used to lessen the value prediction misprediction penalty by guessing whether or not to use a value prediction result. The perceptron approach was compared to the local saturating counter approach used by Lipasti's value predictor [Lip97\_2] and in subsequent approaches. The perceptron-based confidence estimator is shown in Figure 2.6 and is structured very similarly to the perceptron-based branch predictor. Past global value prediction accuracies were stored in a global history table. A perceptron was selected from a table of perceptrons by the instruction address, and the global prediction accuracy history was sourced to the inputs of the selected perceptron. The perceptron output decided whether the value prediction would be used. The perceptron was trained using training-by-error.

#### Figure 2.6. Perceptron-based confidence estimator for value prediction

Evaluation was performed using the confidence estimator on three value prediction approaches: stride, last value, and context. The value predictor employing the confidence estimator was evaluated on its prediction accuracy and its coverage, or the percentage of the time that predictions were used. The evaluations showed a coverage improvement of 6% to 10%, and accuracy improvement of 2% to 6%.

An important note about the perceptron confidence estimator is that it replaced a local approach that only used past iterations of the instruction to make a value prediction with a global approach that used the prediction accuracies of past global instructions. While global confidence estimation had been proposed using tables [Cal98], the massive size of the tables made it impractical. By using perceptrons, global value prediction predictability information could be harnessed with suffering the exponential growth of a globally indexed table.

# **Chapter 3.** Theory

Prior to the use of perceptrons, the most accurate branch predictor was the two-level table-based branch predictor. When replacing the table-based predictor with the perceptron, the authors largely mimicked the basic table-based layout [Jim00]. Their perceptron predictor still used the same per-branch-address construction, the same value table, and the same global branch history. The principal differences are that the pattern table is replaced by the perceptron, and the summation of perceptron weights is used to determine the branch prediction, not the value of a saturating counter. The perceptrons are thus given the same information as the table, the same past branch sequences, and are asked to make predictions for the same branch instructions in the same order. In the implementations in this dissertation for value prediction and critical instruction prediction, the perceptron approaches will likewise replace a previously existing table-based predictor. The real question is consequently not how accurately the perceptron predictor predicts in isolation, but how accurately the perceptron predictor predicts when compared to a similarly constructed two-level table predictor incorporating saturating counters. When does the perceptron learn faster than the table? When does the perceptron fail to learn patterns that the table easily grasps?

This chapter explores several facets of how a perceptron behaves when it directly replaces a lookup table. The first topic I examine is under what circumstances a perceptron can learn the same patterns a table can learn. Are there patterns a table can learn that a perceptron cannot learn at all, and what are they?

When can a table learn input data faster than a perceptron, and when could a perceptron learn faster?

The second topic is how the perceptron training strategy affects its learning when the perceptron replaces the lookup table. Past works have used two different training strategies for perceptrons in computer architecture applications. Under what circumstances is one training strategy better than another? What input data characteristics affect the performance of each training approach?

In prior computer architecture work using perceptrons, the applications have all required only a single bit output. Branch prediction and confidence estimation need only a binary "yes/no" decision from their predictors. However, there are many speculative applications that require a multiple bit decision, and lookup tables have been designed for these problems. As the third topic, I examine several ways that perceptrons can be used to predict multiple-bit values. When are perceptrons unable to predict values that lookup tables can predict? Is there any way a multibit perceptron-based predictor can be designed so that it has the same learning power as a multibit table-based predictor?

The last topic I explore is how perceptron predictors cope with interference and aliasing. Because no predictor can be designed that is massive enough to independently consider every single instruction in a program, aliasing between instructions has always reduced table-based predictors' accuracies and learning potential. Perceptron predictors will likewise suffer from interference. Do perceptron predictors respond to interference in the same way as table-based predictors? Is there any way of reducing aliasing's harmful effects in perceptrons?

#### **3.1.** Perceptron Learning

The basic function of a perceptron is to learn correlations between pairs of single-bit data points. The classic perceptron has a single weight for each binary input. The polarity of that weight tells whether that input is directly correlated with the target (a positive weight), or inversely correlated with the target (a negative weight). The magnitude of the weight tells the degree of correlation between the input and the target. A large weight implies that the input is greatly correlated, and always carries the same value relative to the target, while a small weight implies that the input is modestly correlated, and is not necessarily a trustworthy guide for predicting the target. A large weight carries a great degree of influence on the final decision, while a small weight has little influence. Thus training a perceptron for a given target means detecting which inputs are correlated with the target, in what way they are correlated, to what degree they are correlated; and setting a weight appropriately.

The lookup table uses a sequence of past values as input. A hash of the particular value sequence chooses a particular counter which makes the prediction. In contrast to the perceptron, which considers the effect of each input value independently, the table considers the effect of each combination of values. What happens when a perceptron is directly substituted for the lookup table and is asked to learn the effects of combinations of values?

#### **3.1.1 Perceptron Context-based Prediction**

Recall how prediction is performed in the two-level table-based branch predictor. A sequence of past branch results is concatenated to form an index, which

chooses a counter from a pattern table. The prediction is then made from the counter state. While this form of prediction is capable of learning correlations between branches, it is not overtly designed to pick out correlations. Instead, it picks out sequences of branches. It learns that a series of particular branch results is always followed by a particular branch result. This form of prediction can be loosely classified as "context-based prediction", because it uses the context of a specific pattern of branch results to determine the result of the next branch.

Context-based predictors are greatly dependent on the quantity of data points forming their context pattern. A basic first-order context-based predictor learns pairs of data values: value "a" is always followed by value "b", value "c" by value "d". A second-order context-based predictor learns triplets of data values: value sequence "ab" is always followed by "c". The order of the context-based predictor is based on its history size.

Just like table based predictors are designed for context-based learning but can learn individual correlations, perceptrons, while being designed for correlational learning, can pick up some context patterns. There are two important limitations, however: 1) linearly inseparable patterns will be ignored, and 2) all the patterns will need to occur with equal frequency. If the set of patterns conflict with each other, the perceptron will be typically unable to learn all of the patterns in that set. If any pattern occurs significantly more often than another pattern, it can bias the perceptron and prevent it from predicting the less common pattern correctly.

What does it mean for two patterns to conflict? Recall that a perceptron learns by seeking a correlation, either direct or inverse, between each input and the target. If

two patterns contradict each other on an input, one pattern producing a direct correlation for the input, and the other producing an inverse correlation for the input, the two patterns cancel each other out, driving that input's weight to zero. This is acceptable, provided that another input that can be used to predict is not cancelled out. However, if the patterns contradict each other on every input, the perceptron cannot learn both patterns. Thus a set of patterns can be in conflict and cannot be learned by a perceptron. For a set of patterns to be compatible, there has to be at least one input that has the same correlation for every pattern in the set. If there are no inputs that have the same correlation throughout the set, the set of patterns is not compatible.

For example, consider that a third-order perceptron context-based predictor is taught that the sequence 101 is always followed by 1. The perceptron will train its weights accordingly: the first weight will learn a direct correlation, the second an inverse, and the third a direct. Next suppose that the predictor is taught 001 is followed by 0. The perceptron will train its first and second weights to learn a direct correlation, and the third an inverse. There is a conflict on the second input and third inputs; however, because there is no conflict on the first input, the perceptron can learn both patterns. However, suppose that the perceptron is then taught that the sequence 100 is followed by 0. In this case, the perceptron trains the first weight to learn an inverse correlation, and the second and third weights to learn a direct correlation. This 100 pattern conflicts with the 101 pattern on the first and second inputs, and with the 001 pattern on the third input. The three patterns are thus in

conflict with each other, and the perceptron cannot learn them (although it could learn any two of the three patterns).

| Compatible Patterns |             |          |          |   |  |  |  |  |  |

|---------------------|-------------|----------|----------|---|--|--|--|--|--|

| 0                   | 1           | 0        | 1        | 1 |  |  |  |  |  |

| 1                   | 0           | 0        | 1        | 0 |  |  |  |  |  |

| 0                   | 1           | 1        | 0        | 1 |  |  |  |  |  |

|                     |             |          |          |   |  |  |  |  |  |

| inverse             | direct      | conflict | conflict |   |  |  |  |  |  |

| Conflict            | ing Patterr | 18       |          |   |  |  |  |  |  |

| 0                   | 1           | 0        | 1        | 1 |  |  |  |  |  |

| 1                   | 0           | 0        | 1        | 0 |  |  |  |  |  |

| 0                   | 1           | 1        | 0        | 0 |  |  |  |  |  |

|                     |             |          |          |   |  |  |  |  |  |

| conflict            | conflict    | conflict | conflict |   |  |  |  |  |  |

# Figure 3.1. Compatible patterns and conflicting patterns

So what happens when a perceptron context-based predictor is taught conflicting patterns? If there are two patterns in conflict, and they occur equally often, all the perceptron weights will cancelled to zero. The perceptron will thus predict arbitrarily. However, if there are three or more patterns in conflict, some of the perceptron weights may not cancel to zero. When this happens, the perceptron may predict arbitrarily. It may nevertheless learn the patterns.

In the above example, suppose that 101-1, 001-0, and 100-0 occur equally often. For each input, two of the three patterns will bias the weight. Figure 3.2