**ABSTRACT**

Title of dissertation: myCACTI: A NEW CACHE DESIGN TOOL FOR PIPE-

LINED NANOMETER CACHES

Samuel Verzola Rodriguez, Doctor of Philosophy, 2006

Dissertation directed by: Associate Professor Bruce L. Jacob

Department of Electrical and Computer Engineering and Insti-

tute for Advanced Computer Studies University of Maryland, College Park

The presence of caches in microprocessors has always been one of the most important techniques in bridging the memory wall, or the speed gap between the microprocessor and main memory. This importance is continuously increasing especially as we enter the regime of nanometer process technologies (i.e. 90nm and below), as industry has favored investing a larger and larger fraction of a chip's transistor budget to improving the on-chip cache. This is the case in practice, as it has proven to be an efficient way to utilize the increasing number of transistors available with each succeeding technology. Consequently, it becomes even more important to have cache design tools that give accurate representations of designs that exist in actual microprocessors.

The prevalent cache design tools that are the most widely used in academe are CACTI [Wilton1996] and eCACTI [Mamidipaka2004], and these have proven to be very useful tools not just for cache designers, but also for computer architects. This dissertation will show that both CACTI and eCACTI still contain major limitations and even flaws in their design, making them unsuitable for use in very-deep submicron and nanometer caches, especially pipelined designs. These limitations and flaws will be discussed in detail.

This dissertation then introduces a new tool, called myCACTI, that addresses all these limitations and, in addition, introduces major enhancements to the simulation framework. Some of the major enhancements are briefly described as follows:

- Use of SPICE BSIM4.0 equations to accurately characterize device behavior for nanometer process technologies. In contrast, CACTI and, to a major extent, eCACTI simply use hardcoded parameters derived for an obsolete 0.80µm process technology.

- The modeling of a typical explicitly-pipelined cache, which accounts for all the overhead in pipelining that will be present in virtually all industry-level microprocessor caches. In contrast,

CACTI and eCACTI model wave-pipelined cache, something that is not representative of commercial designs.

- Inclusion of more optimal variable stage dynamic logic circuits for the decode hierarchy that

provides the tool more flexibility in finding optimal implementations. In contrast, both CACTI and

eCACTI model a fixed-stage static CMOS decode hierarchy, significantly limiting the optimization

search.

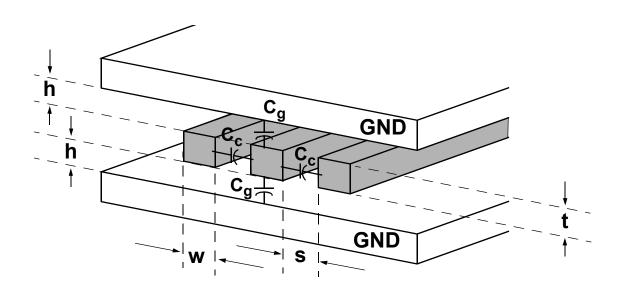

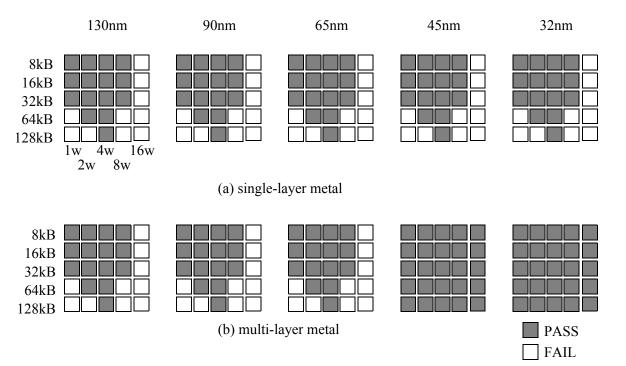

- Inclusion of an accurate model and per-process numbers for a typical BEOL-stack that are representative of nanometer processes. The significance of this is made even more important given the tremendous effect of interconnect parasitics on a cache's behavior.

- Inclusion of a gate leakage tunneling current model for improved handling of static power dissipation.

- Inclusion of a very realistic interconnect model that is representative of the interconnects in a real

nanometer cache. In contrast, both CACTI and eCACTI have an unrealistic model of the

interconnect as they assume the use of interconnect with a single characteristic no matter where it is

located and used in the cache.

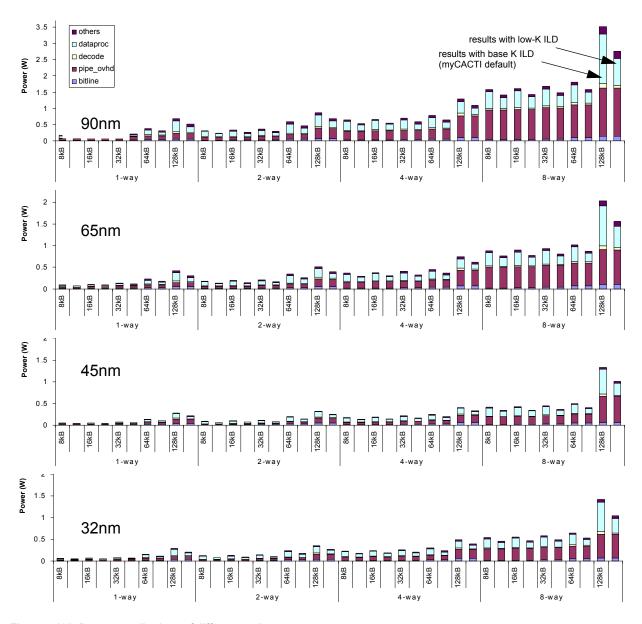

This dissertation then demonstrates the use of myCACTI in the cache design process. Detailed design space explorations are done on multiple cache configurations to produce pareto optimal curves of the caches to show optimal implementations. Detailed studies are also performed to characterize the delay and power dissipation of different cache configurations and implementations. Some of the more important observations, among the many that were found, are as follows:

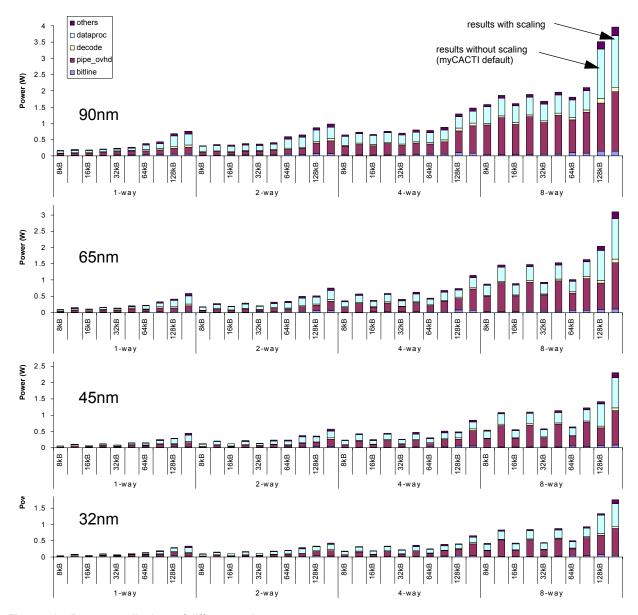

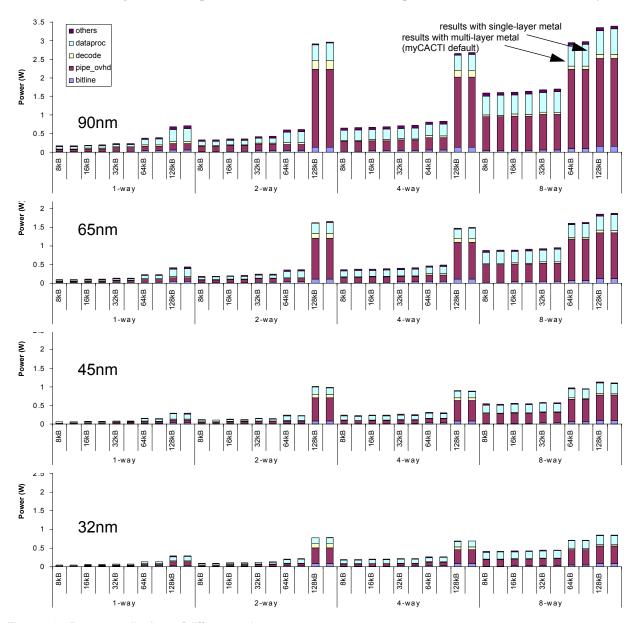

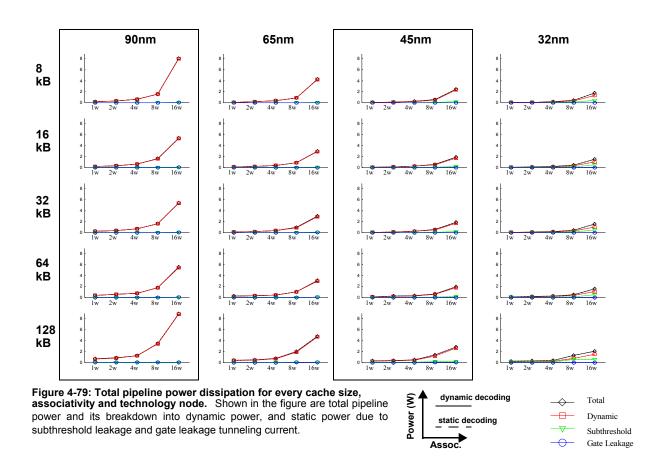

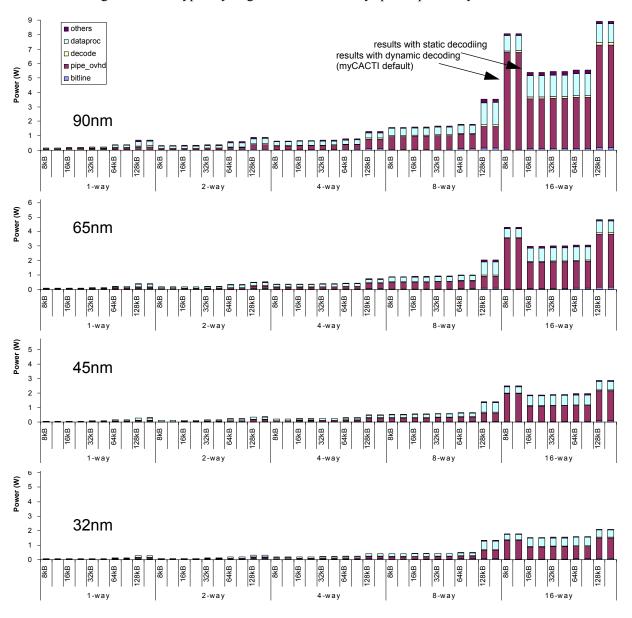

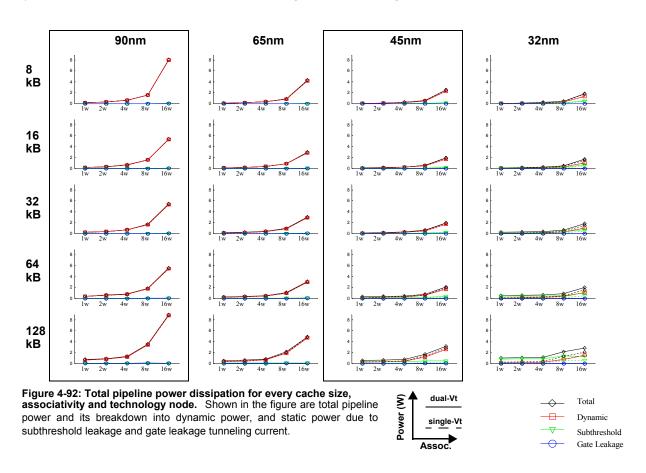

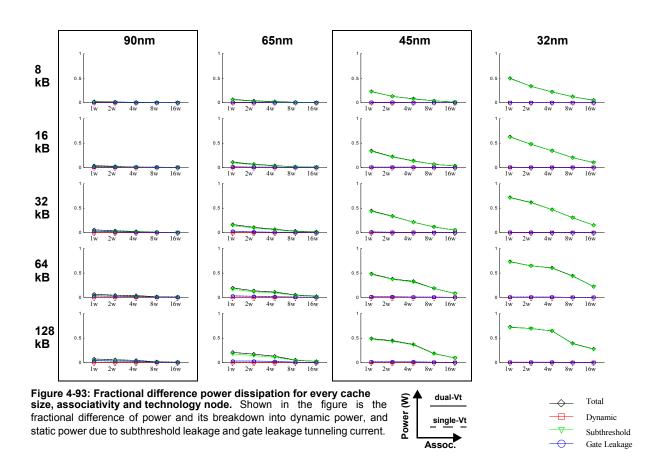

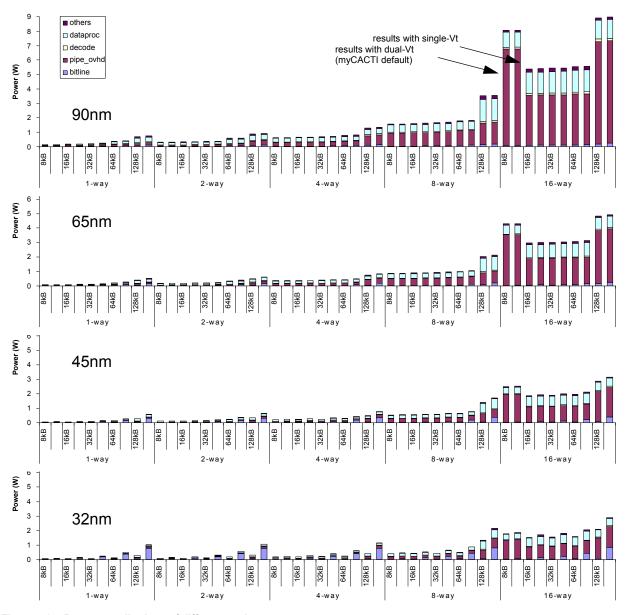

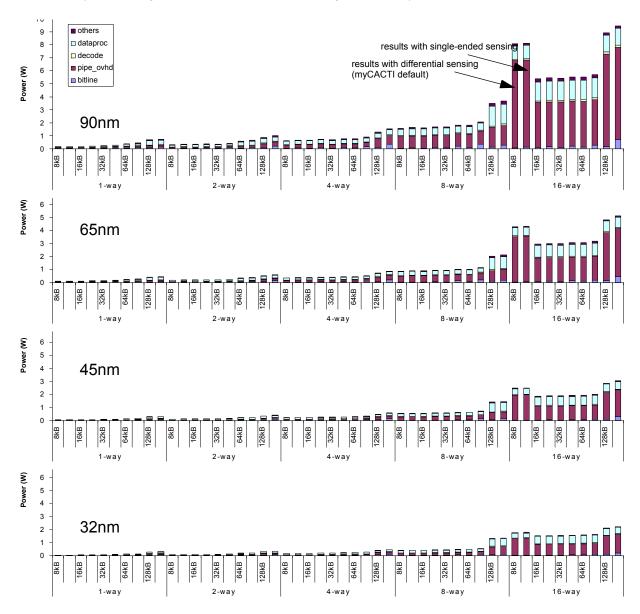

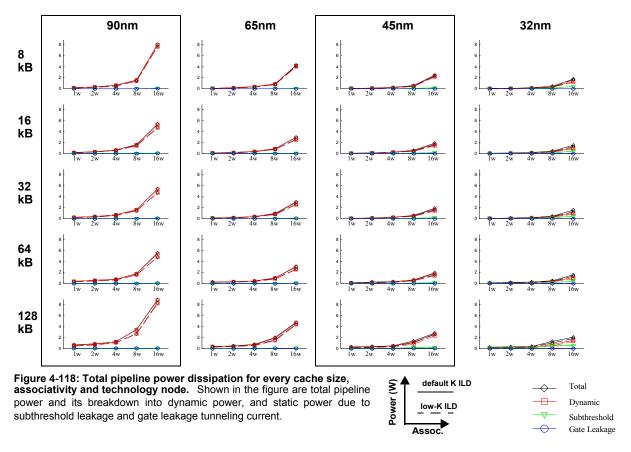

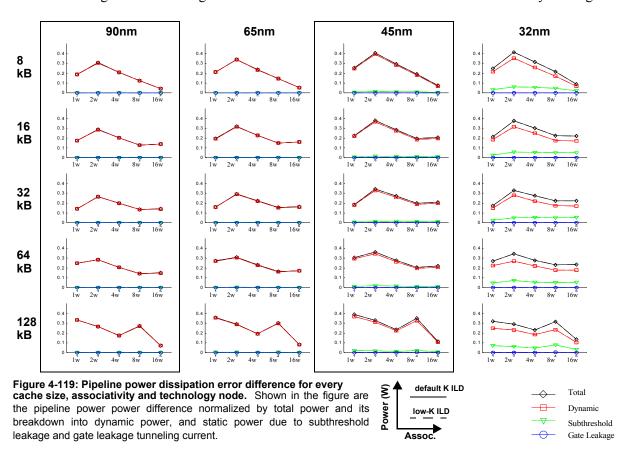

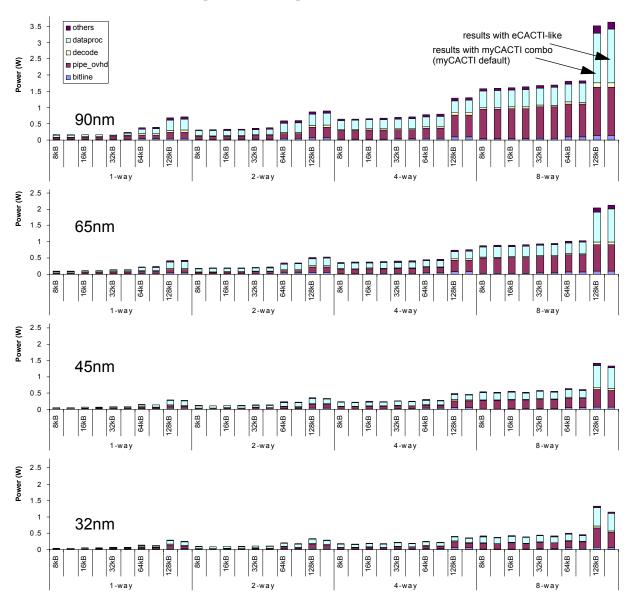

- The pipeline power dissipation overhead is very significant and it typically dominates the total power.

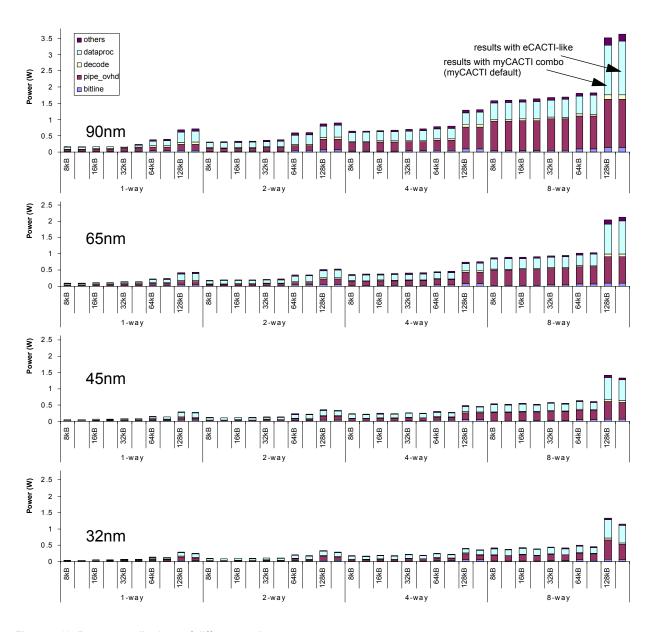

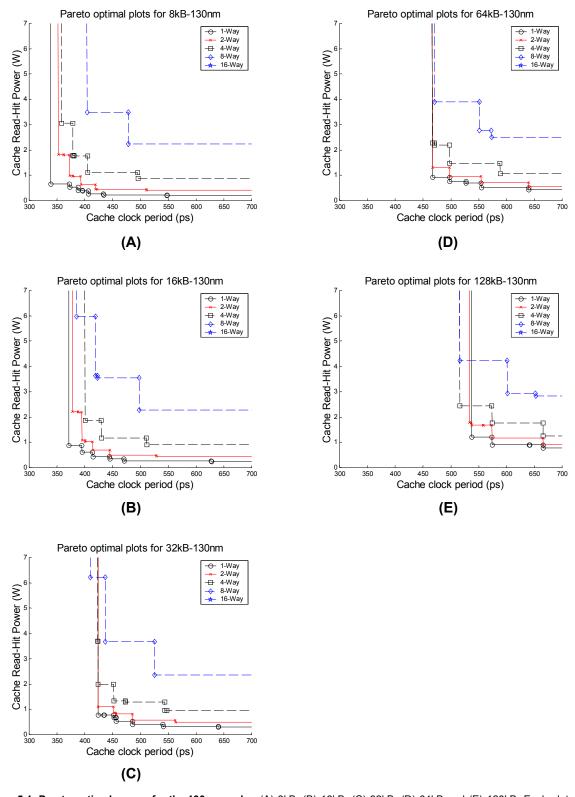

- Interesting non-monotonic behavior with respect to delay and power dissipation for caches with different associativities exist, such that we can conclude that some optimal implementations are definitely superior than other optimal implementations. In other words, overlapping pareto optimal curves result in some optimal points being reconsidered as optimal.

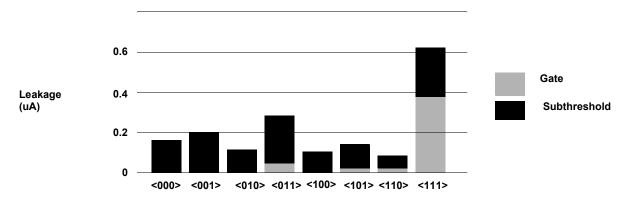

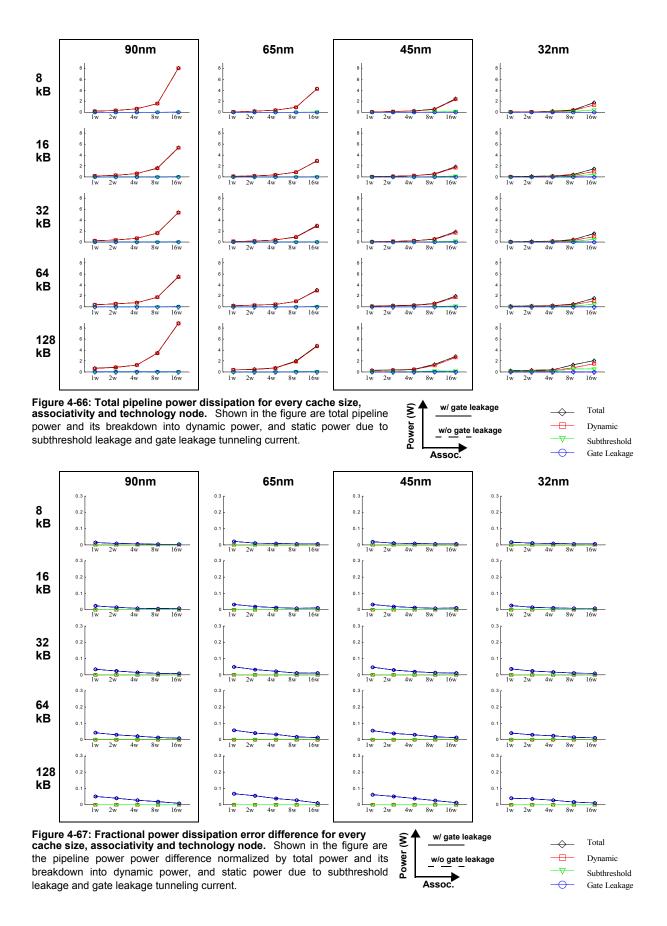

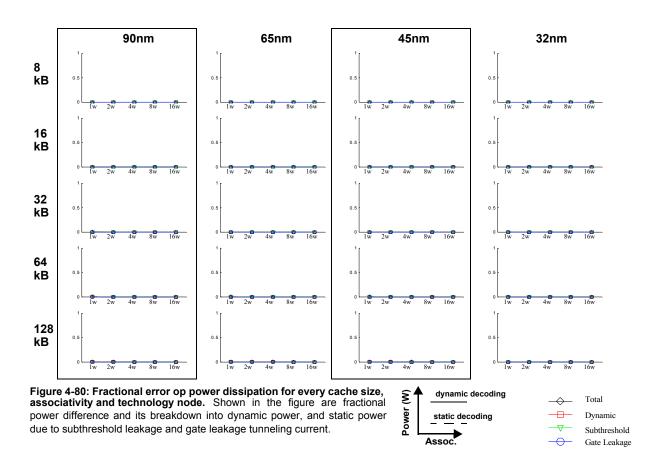

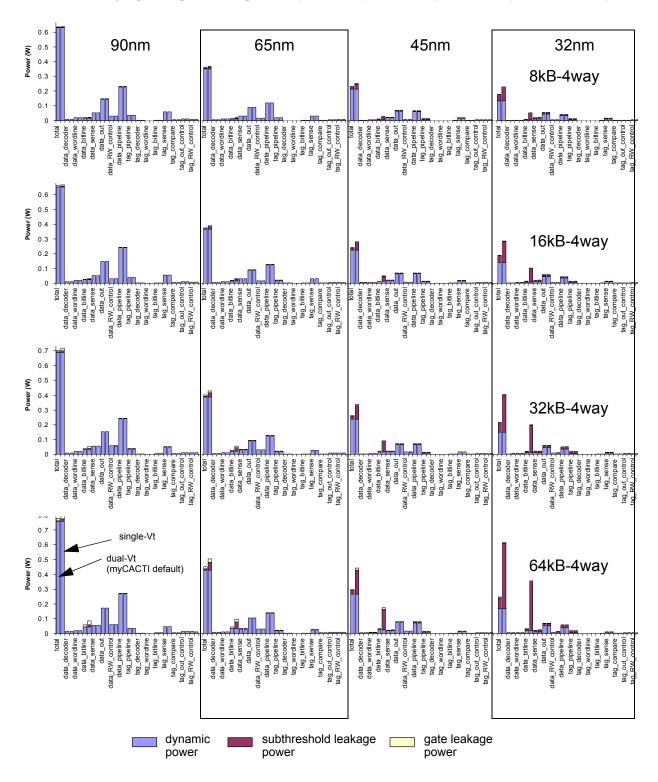

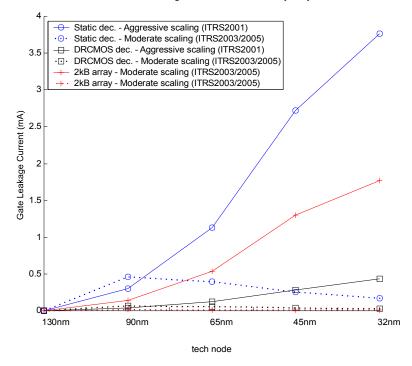

- The power dissipation due to gate leakage tunneling current is surprisingly not as significant as initially expected.

Finally, future directions to the development of myCACTI are identified to show possible ways that the tool can be improved in such a way as to allow even more different kinds of studies to be performed.

## myCACTI: A NEW CACHE DESIGN TOOL FOR PIPELINED NANOMETER CACHES

## by Samuel Verzola Rodriguez

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2006

Advisory Committee:

Associate Professor Bruce L. Jacob, Chair

Associate Professor Gang Qu

Assistant Professor Pamela Abshire

Professor Romel Gomez

Associate Professor Chau-Wen Tseng

© Copyright by

Samuel Verzola Rodriguez

#### ACKNOWLEDGEMENTS

This dissertation would not have been possible without the contribution of scores of people who have helped shape my thesis and my life, either directly or indirectly. First and foremost is my family -- my tatay and nanay, and my siblings Ate Yoyi, LJ and Bads. Their support allowed me to keep my sanity, stay grounded, and above all, remember my pride in being a Filipino. To my advisor, Bruce Jacob -- for all his mentoring and all the help, not to mention the all-important funding, during my stay in Maryland. Going into your office for one of those two-hour talks about anything and everything under the sun was always fun and interesting, to say the least. To Dr. Romel Gomez, I will also always be grateful, for revealing to me the possibilities of grad school, for helping in my admission to Maryland, and for keeping tabs on me the whole time I was there. To the friends I made in College Park -- Xia, Cagdas, Vince, Amol, Tad, Joe, Jimi, Ohm, Ankush, Brinda, Sada, Dave, Jason, Babak and a lot more. Grad school without friends wouldn't be a pretty thing, and I'm glad that even though I'm reticent in getting to know new people, that I had the pleasure of getting to know you guys. To the awesome people at AMD -- I'm grateful to so many of you that I'll have to mention only the guys I had to directly answer to: Rob, Matt, Kathy and Jim. If I name all of you guys, I may end up having to name half of the people at the Boston Design Center. I'm looking forward to renewing acquaintances with you guys once I start working there, and to knowing all of the other people I didn't get a chance to meet. To Leo Tordil and family -- I'll always owe you a favor for providing a roof over my head during the first three months of my stay in the U.S. -- and I offer my apologies for my personality flaw that prevented me from keeping in close touch. To my professors and acquaintances at U.P. -- Gev, Luis, Manuel, Chrd, Marc, CMO, Frank, Eggy, JYG and Chuy, among others -- for encouraging me to go to grad school in the U.S., without which I probably wouldn't have gathered enough courage to start this great and fulfilling journey. To the support guys at Maryland -- Shyam, Jay, To-Anh, Maria, and tons of others. A school is always made by brilliant, hard-working people striving to keep the gears turning. To some of the collegiate sport icons I got to watch at Maryland -- Dixon, Baxter, Blake, Mouton, Wilcox and of course, Vernon Davis -- you made being a Terrapin fun in spite of the weird name -- Go Terps! To my Pisay batchmates who proved that sometimes, it's really a small world by ending up only miles from where I live even though we're eight thousand miles from home -- Toby, Jerry and Andre. Talking with you guys made being alone in the U.S. bearable. Also a very special thanks to Aamer -- a friend, fellow UMD student, research assistant, and the best roommate I ever had. I'll always be eternally grateful to how you put up with me during that awesome but painful, bittersweet six months of 2005. I'm not sure what I would have done without you, and I hope we'll always be friends -- I'll even overlook the fact that you work for Intel. And finally, the person who is the main reason why I strived to do this and to whom this dissertation is dedicated to -- Tats, para sa iyo ito, kahit hindi mo na ako mahal.

# Chapter 1 Introduction 1

| 1.1 | Problem Description                        |                                                              |    |  |  |  |

|-----|--------------------------------------------|--------------------------------------------------------------|----|--|--|--|

| 1.2 | Contributions and Significance             |                                                              |    |  |  |  |

| 1.3 | nization of Dissertation                   | 6                                                            |    |  |  |  |

| C   | hapi                                       | ter 2 Background 8                                           |    |  |  |  |

| 2.1 | Power Dissipation in CMOS Circuits         |                                                              |    |  |  |  |

| 2.2 | Leaka                                      | rage Current Mechanisms                                      |    |  |  |  |

| 2.3 |                                            | RAM and Cache implementation1                                |    |  |  |  |

| 2.4 | Some power solutions and their limitations |                                                              |    |  |  |  |

| 2.4 | 2.4.1                                      | Multi-Vt Solutions                                           |    |  |  |  |

|     | 2.4.1                                      | Forced Stacking                                              |    |  |  |  |

|     | 2.4.2                                      | Input sleep vector                                           |    |  |  |  |

|     | 2.4.4                                      | PMOS-based dynamic domino logic                              |    |  |  |  |

|     | 2.4.5                                      | Body biasing                                                 |    |  |  |  |

|     | 2.4.6                                      | Supply gating                                                |    |  |  |  |

|     | 2.4.7                                      | Other memory-specific techniques                             | 64 |  |  |  |

| 3.1 | •                                          | ter 3 Cache Design Tools 69                                  | 69 |  |  |  |

| 3.2 | CAC                                        | ГІ                                                           | 69 |  |  |  |

|     | 3.2.1                                      | Basic Operation                                              |    |  |  |  |

|     | 3.2.2                                      | CACTI cache structure                                        |    |  |  |  |

|     | 3.2.3                                      | CACTI address decoder                                        | 72 |  |  |  |

|     | 3.2.4                                      | CACTI bitline circuits, tag compare and output drivers       | 75 |  |  |  |

|     | 3.2.5                                      | CACTI program flow                                           | 77 |  |  |  |

| 3.3 | eCACTI                                     |                                                              |    |  |  |  |

|     | 3.3.1                                      | Basic Operation                                              | 78 |  |  |  |

|     | 3.3.2                                      | eCACTI cache structure                                       | 78 |  |  |  |

|     | 3.3.3                                      | eCACTI address decoder                                       | 79 |  |  |  |

|     | 3.3.4                                      | eCACTI bitline circuits, tag compare and output drivers      | 81 |  |  |  |

|     | 3.3.5                                      | Additional eCACTI enhancements                               | 81 |  |  |  |

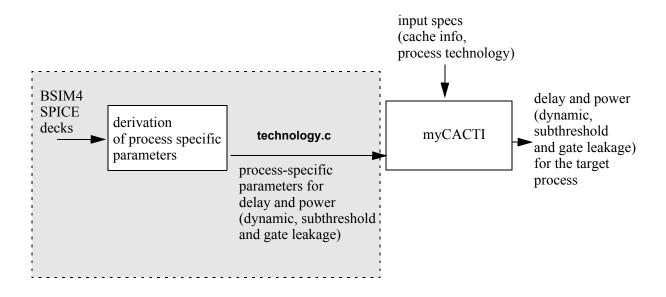

| 3.4 | myCACTI                                    |                                                              |    |  |  |  |

|     | 3.4.1                                      | Basic operation                                              | 81 |  |  |  |

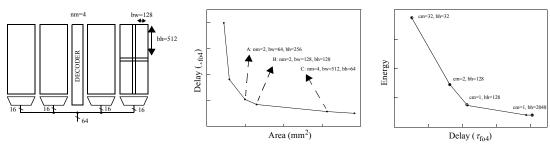

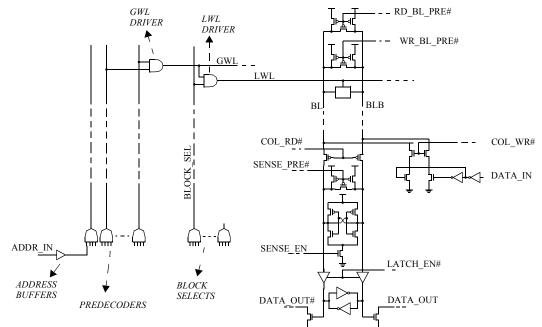

|     | 3.4.2                                      | myCACTI cache structure                                      | 83 |  |  |  |

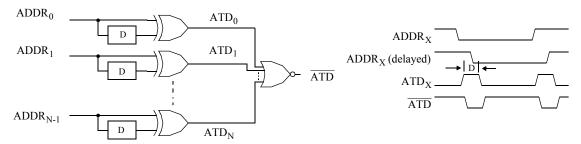

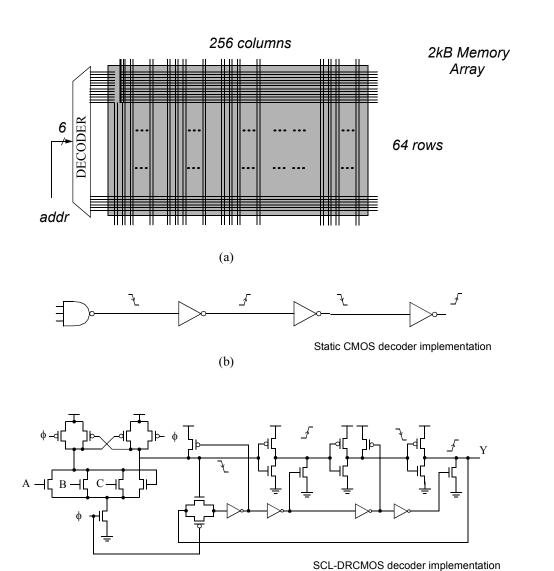

|     | 3.4.3                                      | myCACTI address decoding                                     |    |  |  |  |

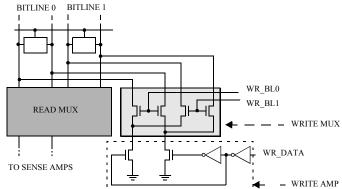

|     | 3.4.4                                      | myCACTI bitline circuits, tag comparators and output drivers | 88 |  |  |  |

|     | 3.4.5   | myCACTI pipelining                             | 88       |

|-----|---------|------------------------------------------------|----------|

|     | 3.4.6   | Gate leakage computation                       |          |

|     | 3.4.7   | Device characterization                        |          |

|     | 3.4.8   | Interconnect characterization                  | 96       |

|     | 3.4.9   | Via parasitic capacitance                      |          |

|     | 3.4.10  | Single-ended sensing                           |          |

|     | 3.4.11  | myCACTI limitations                            |          |

| 2.5 |         | •                                              |          |

| 3.5 | Sullill | nary                                           | 101      |

|     | hant    | er 4 CACTI/eCACTI vs. myC                      | ACTI Con |

|     | _       | •                                              | ACH CON  |

| pa  | rativ   | ve Studies 102                                 |          |

| 4.1 | INTR    | ODUCTION                                       | 102      |

| 4.2 | Backg   | round of Comparisons                           | 102      |

|     | 4.2.1   | Validity of CACTI/eCACTI scaling               |          |

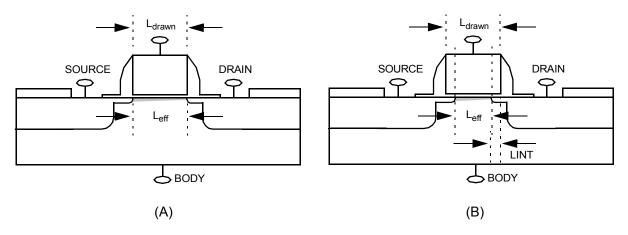

|     | 4.2.2   | Transistor effective length                    |          |

|     | 4.2.3   | Via parasitic capacitance                      |          |

|     | 4.2.4   | Pipelining comparison                          |          |

|     | 4.2.5   | Number of interconnect layers                  |          |

|     | 4.2.6   | Gate leakage                                   |          |

|     | 4.2.7   | Static/dynamic decoding                        |          |

|     | 4.2.8   | Dual-Vt process technologies                   |          |

|     | 4.2.9   | Single-ended sensing                           |          |

|     | 4.2.10  | BEOL low-k study                               |          |

|     | 4.2.11  | Combination of multiple parameters             |          |

| 4.3 | Comp    | arison Methodology                             |          |

| 4.4 | Comp    | arison Results Summary                         | 119      |

| 4.5 | Detail  | ed Comparison Results                          | 120      |

|     | 4.5.1   | Validity of CACTI/eCACTI scaling               | 120      |

|     | 4.5.2   | Transistor effective length                    |          |

|     | 4.5.3   | Via parasitic capacitance                      |          |

|     | 4.5.4   | Pipelining comparison                          |          |

|     | 4.5.5   | Number of interconnect layers                  |          |

|     | 4.5.6   | Gate leakage                                   |          |

|     | 4.5.7   | Static/Dynamic decoding                        |          |

|     | 4.5.8   | Dual-Vt process technologies                   |          |

|     | 4.5.9   | Single-ended sensing                           |          |

|     | 4.5.10  | BEOL low-k study                               |          |

|     | 4.5.11  | Combination of multiple parameters             |          |

|     | 4.5.12  | Direct Output Comparison with CACTI and eCACTI |          |

| 4.6 |         |                                                |          |

| 4.6 | -       | arative study conclusions                      |          |

|     | 4.6.1   | Validity of CACTI/eCACTI scaling               | 231      |

|            | 4.6.2                              | Transistor effective length                                      | 23 |

|------------|------------------------------------|------------------------------------------------------------------|----|

|            | 4.6.3                              | Via parasitic capacitance                                        | 23 |

|            | 4.6.4                              | Pipelining comparison                                            | 23 |

|            | 4.6.5                              | Number of interconnect layers                                    | 23 |

|            | 4.6.6                              | Gate leakage                                                     | 23 |

|            | 4.6.7                              | Static/dynamic decoding                                          | 23 |

|            | 4.6.8                              | Dual-Vt process technologies                                     | 23 |

|            | 4.6.9                              | Single-ended sensing                                             | 23 |

|            | 4.6.10                             | BEOL low-k study                                                 | 23 |

|            | 4.6.11                             | Combination of multiple parameters                               | 23 |

|            | 4.6.12                             | Final summary                                                    | 23 |

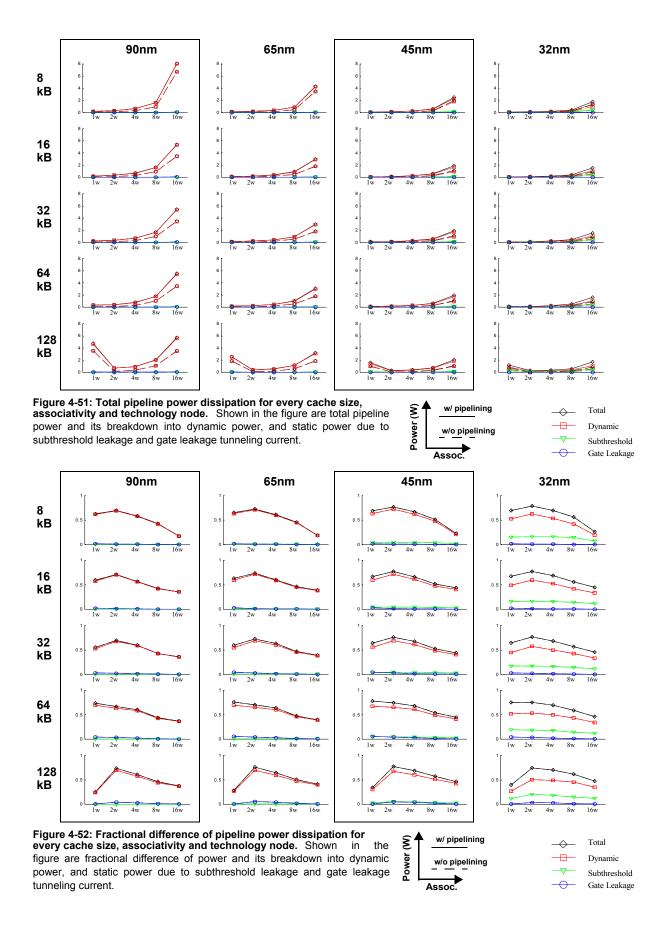

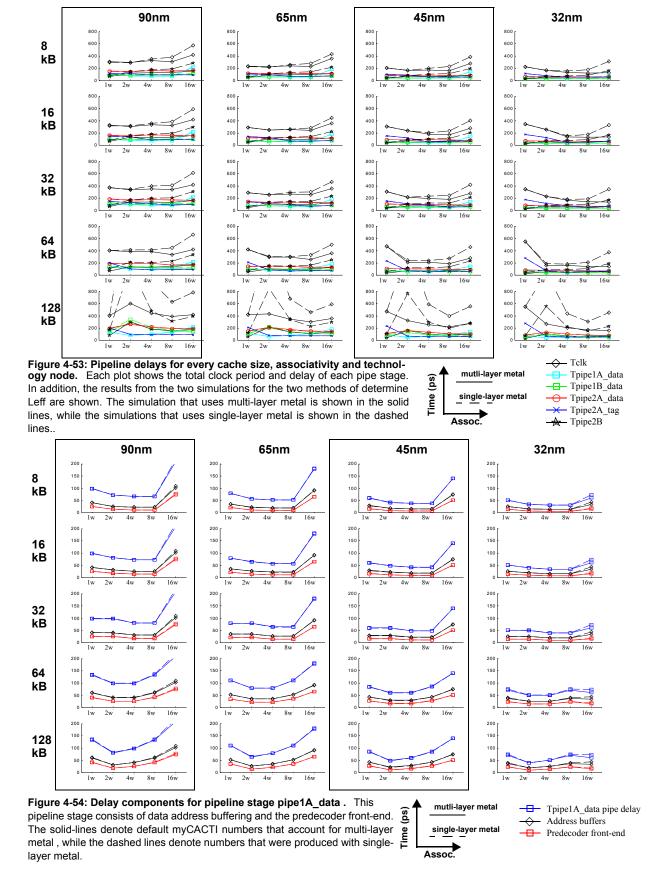

| 5.1<br>5.2 | Introd                             | er 5 myCACTI Detailed Studies  uctional Design Space Exploration | 23 |

| J.L        | 5.2.1                              |                                                                  |    |

|            | 5.2.1                              | 130nm process technology                                         |    |

|            | 5.2.3                              | 90nm process technology 65nm process technology                  |    |

|            | 5.2.4                              | 1                                                                |    |

|            | 5.2.5                              | 45nm process technology                                          |    |

|            | 5.2.6                              | 32nm process technology  Focus on 64kB                           |    |

|            | 5.2.7                              | Summary                                                          |    |

| 5.3        |                                    | ed study of a 64kB 4-way cache                                   |    |

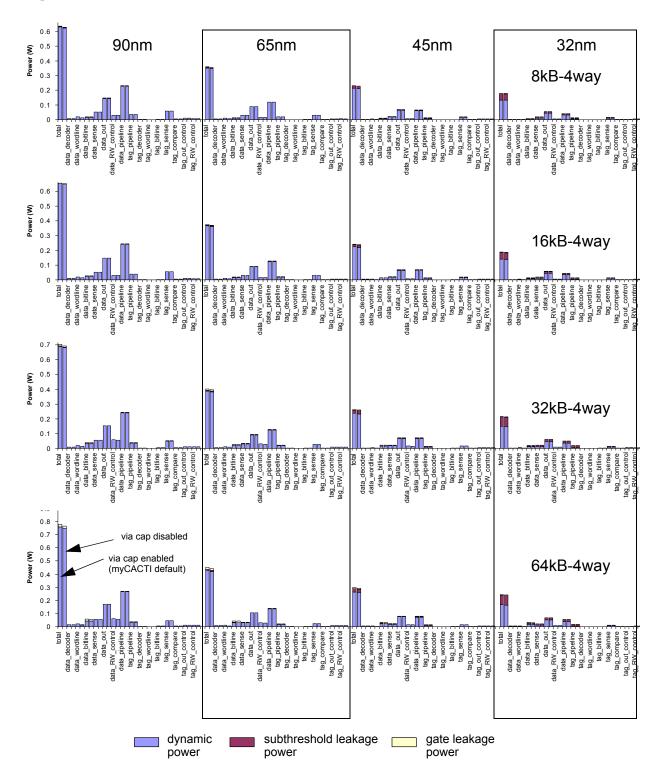

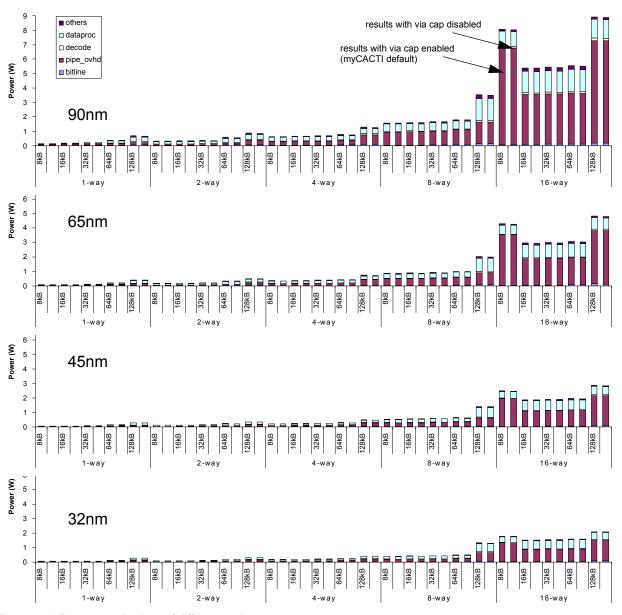

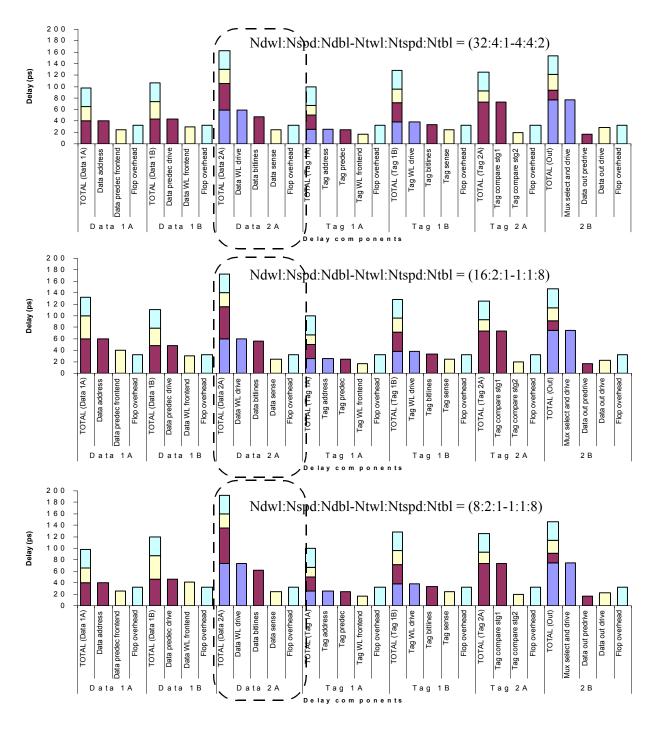

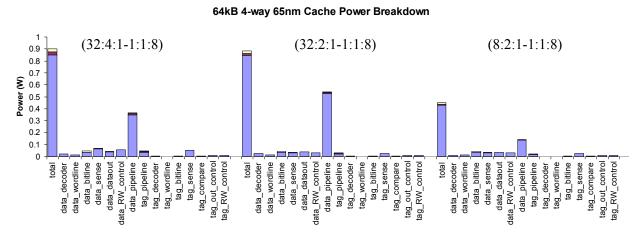

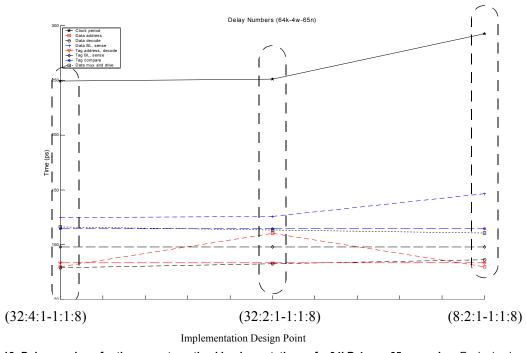

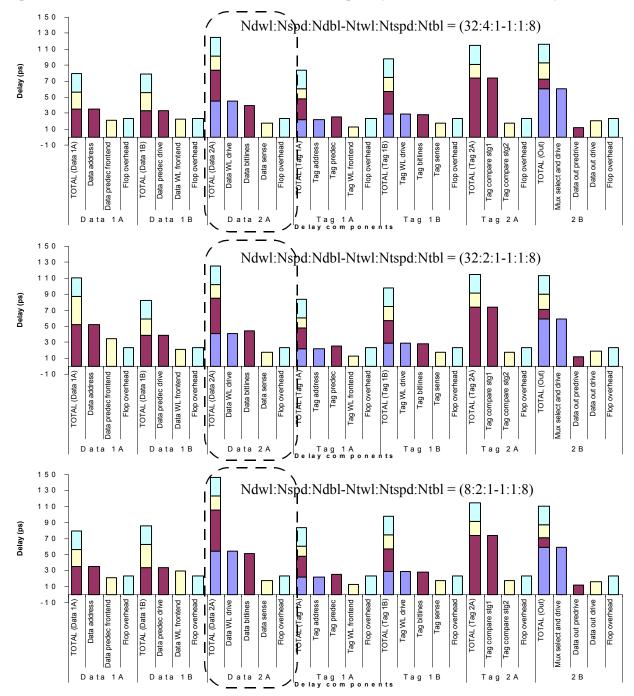

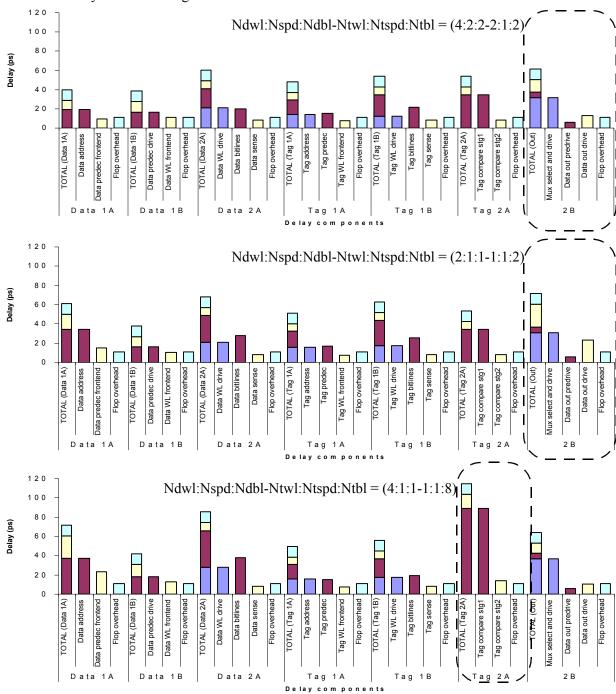

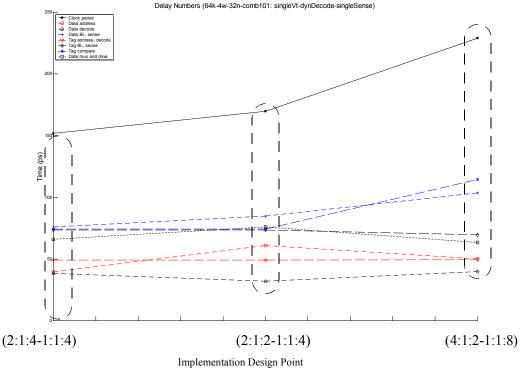

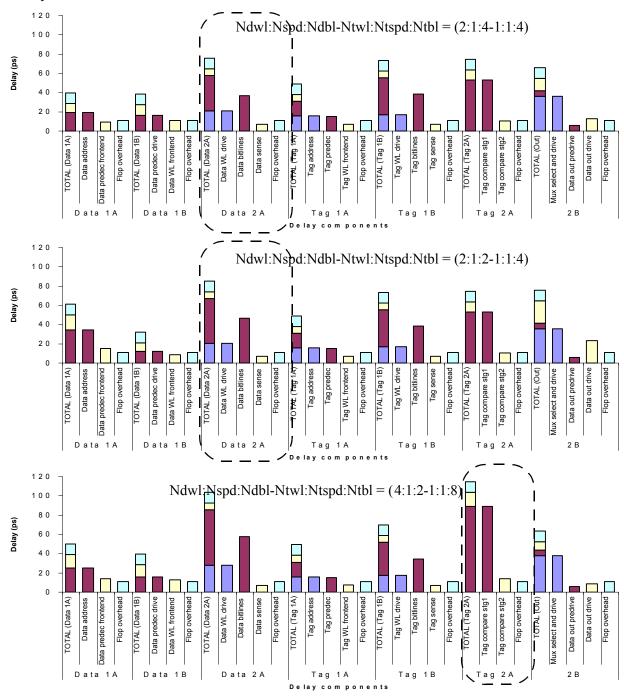

| 5.5        | 5.3.1                              | 90nm 64kB 4-way detailed breakdowns                              |    |

|            | 5.3.2                              | 65nm 64kB 4-way detailed breakdowns                              |    |

|            | 5.3.3                              | 45nm 64kB 4-way detailed breakdowns                              |    |

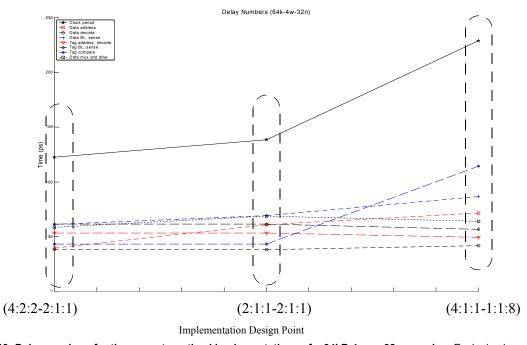

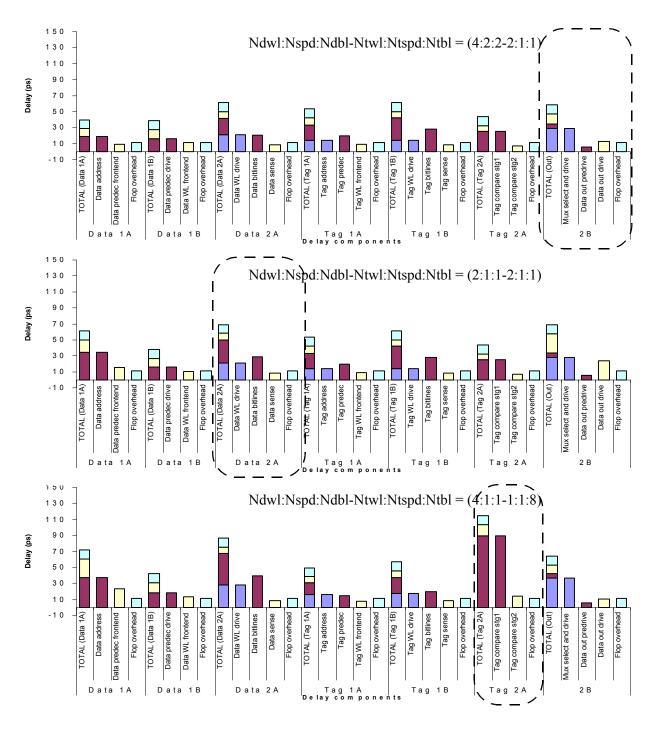

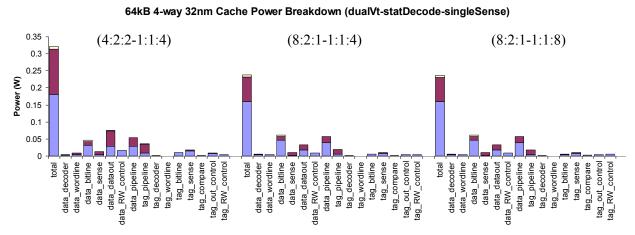

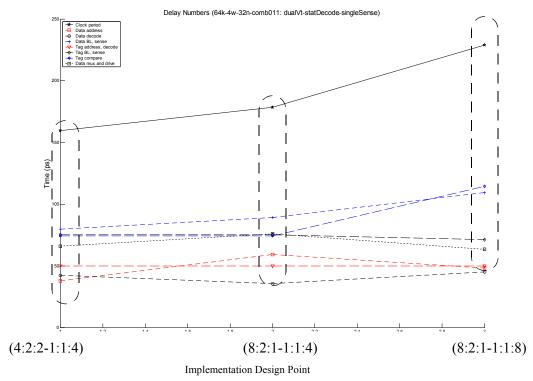

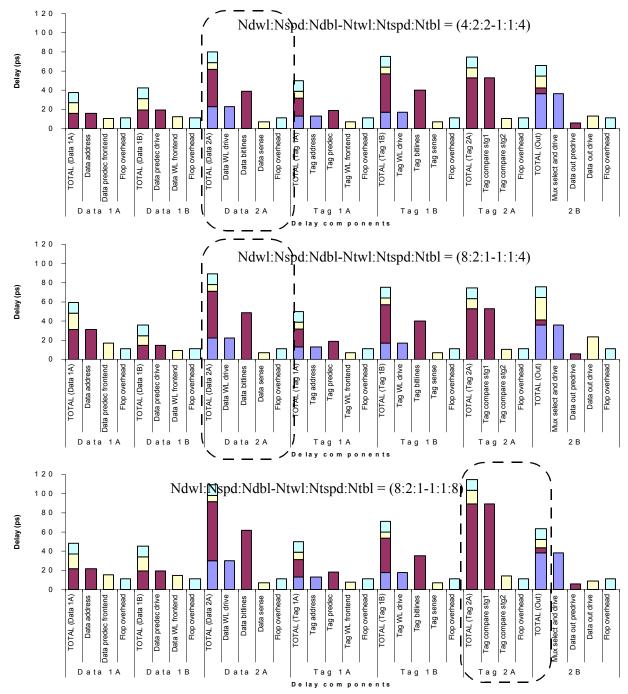

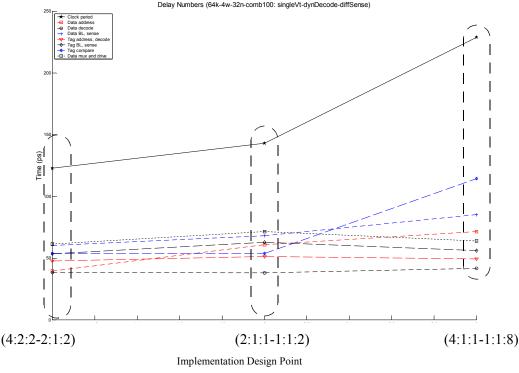

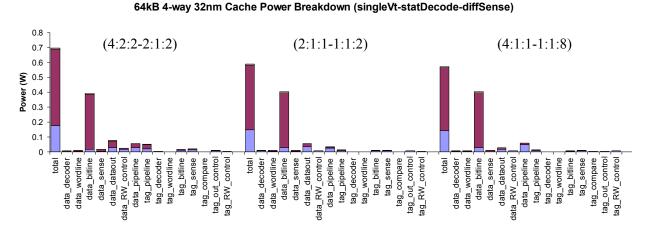

|            | 5.3.4                              | 32nm 64kB 4-way detailed breakdowns                              |    |

|            | 5.3.5                              | Detailed power and delay breakdown summary                       |    |

| 5.4        | Cache design technique comparisons |                                                                  |    |

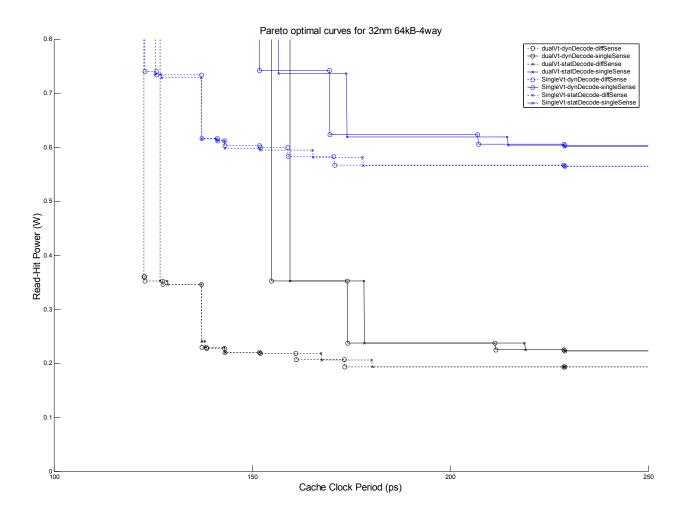

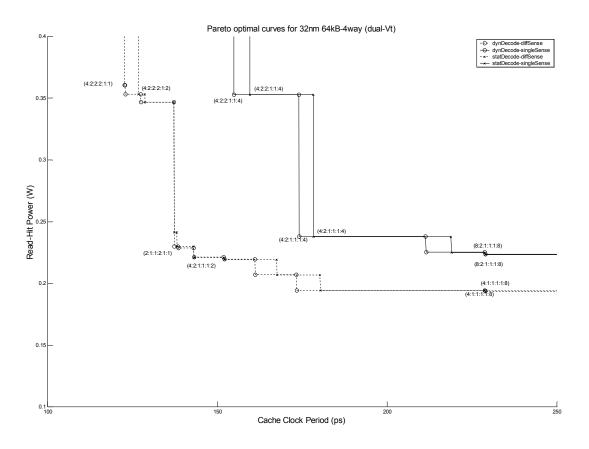

|            | 5.4.1                              | Pareto optimal curves                                            | 26 |

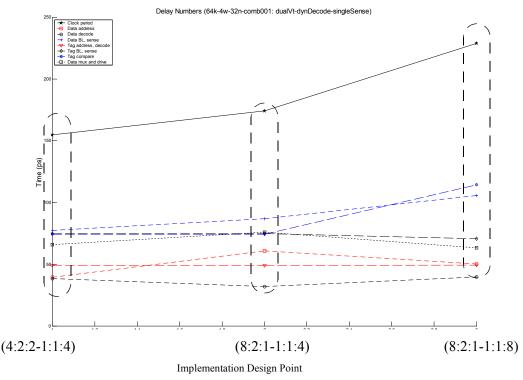

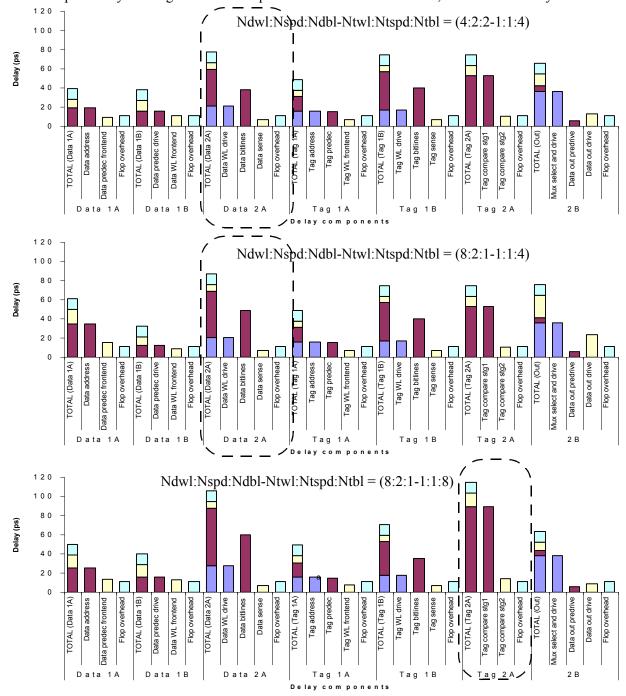

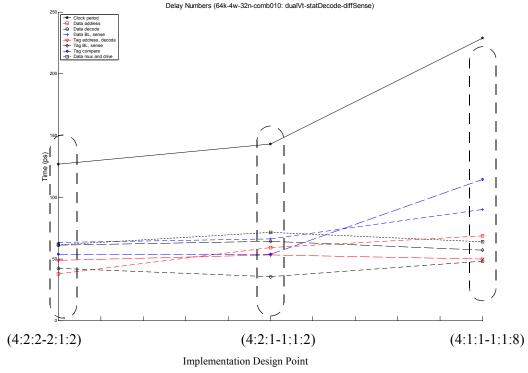

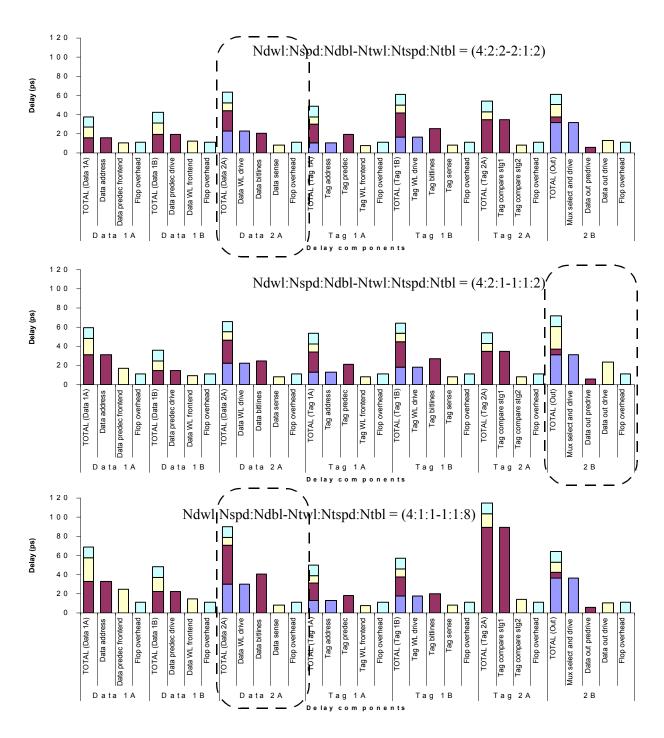

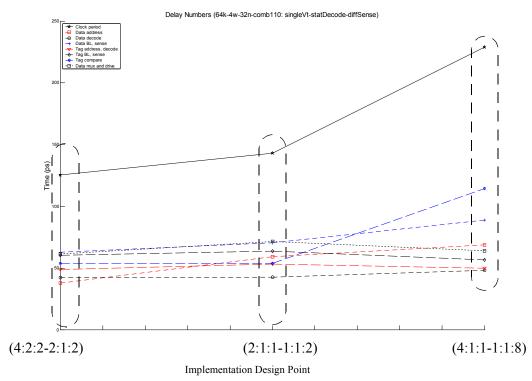

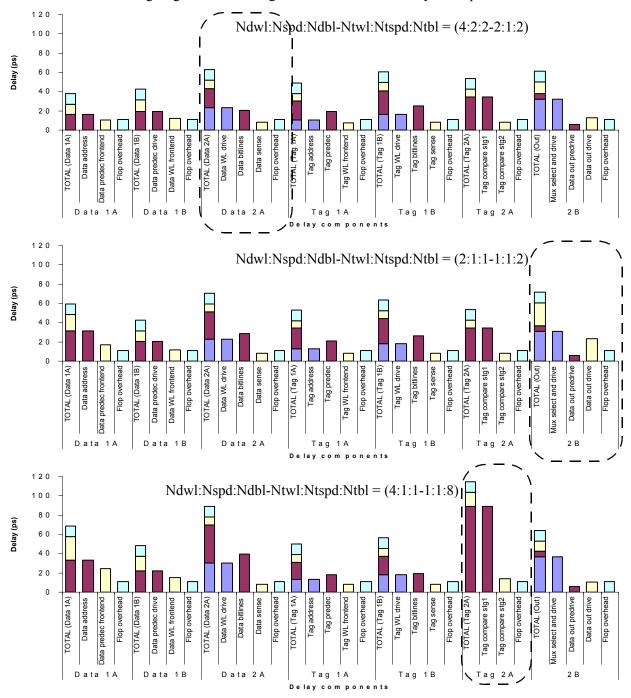

|            | 5.4.2                              | Dual-Vt, Dynamic-Decode and Differential-Sense Implementation    | 27 |

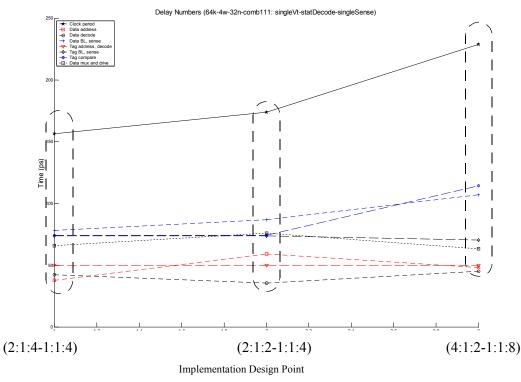

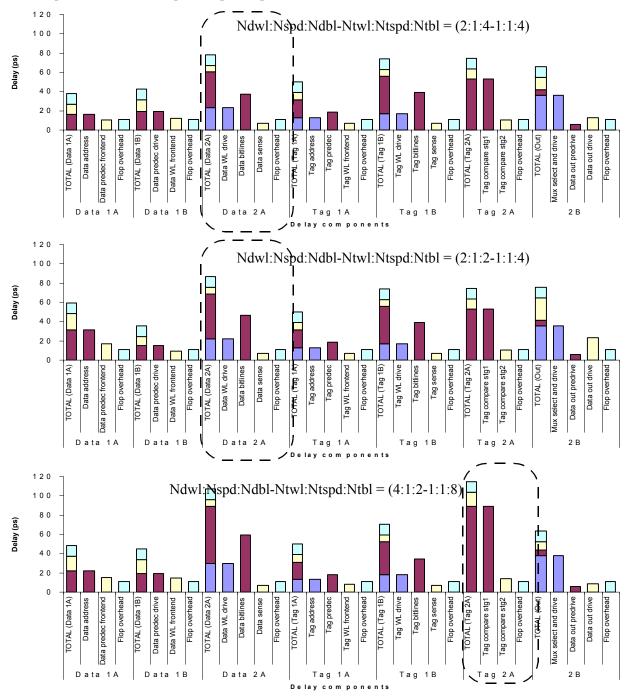

|            | 5.4.3                              | Dual-Vt, Dynamic-Decode, Single-ended-Sense Implementation       | 27 |

|            | 5.4.4                              | Dual-Vt, Static-Decode, Differential-Sense Implementation        | 27 |

|            | 5.4.5                              | Dual-Vt, Static-Decode, Single-ended-Sense Implementation        | 27 |

|            | 5.4.6                              | Single-Vt, Dynamic-Decode, Differential-Sense Implementation     |    |

|            | 5.4.7                              | Single-Vt, Dynamic-Decode, Single-ended-Sense Implementation     | 28 |

|            | 5.4.8                              | Single-Vt, Static-Decode, Differential-Sense Implementation      | 28 |

|            | 5.4.9                              | Single-Vt, Static-Decode, Single-ended-Sense Implementation      | 28 |

|            |                                    |                                                                  |    |

|            | 5.4.10                             | Summary                                                          | 28 |

# Chapter 6 Gate leakage characterization 292

| 6.1     | INTRODUCTION                                                                                                                                                                | 292           |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|

| 6.2     | Background29                                                                                                                                                                |               |  |  |

| 6.3     | EXPERIMENTAL METHODOLOGY                                                                                                                                                    | 293           |  |  |

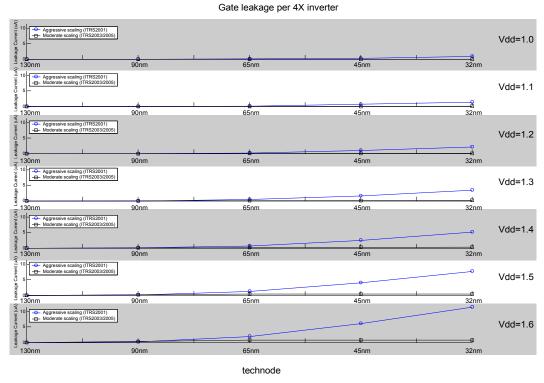

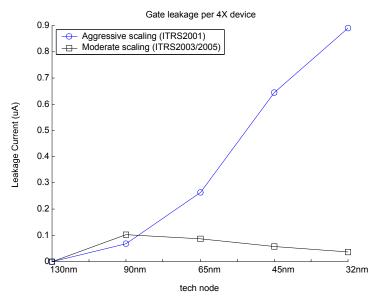

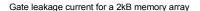

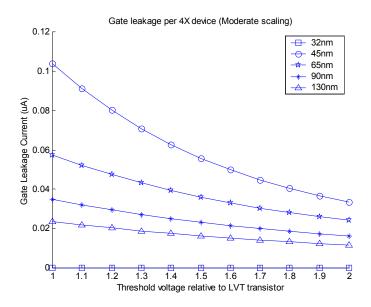

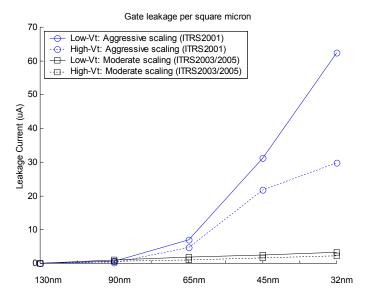

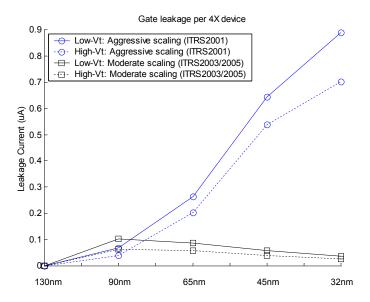

| 6.4     | Main gate leakage factors  6.4.1 Gate leakage current big picture  6.4.2 Vdd scaling  6.4.3 Process parameter scaling  6.4.4 Putting it all together  6.4.5 Circuit example |               |  |  |

| 6.5     | Breakdown of gate leakage current                                                                                                                                           |               |  |  |

| 6.6     | Threshold voltage                                                                                                                                                           |               |  |  |

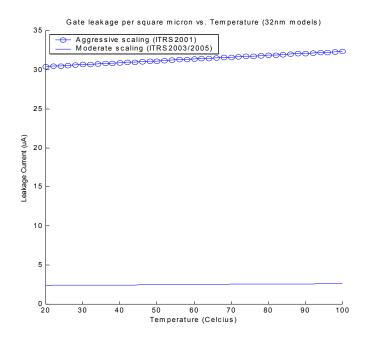

| 6.7     | Temperature effects                                                                                                                                                         | 306           |  |  |

| 6.8     | Discussion                                                                                                                                                                  | 306           |  |  |

| 6.9     | Conclusion                                                                                                                                                                  | 308           |  |  |

| $C_{i}$ | hapter 7 Conclusion 309                                                                                                                                                     |               |  |  |

| 7.1     | Summary and Contributions                                                                                                                                                   | 309           |  |  |

| 7.2     | Limitations                                                                                                                                                                 | 310           |  |  |

| 7.3     | Related Work                                                                                                                                                                | 311           |  |  |

| 7.4     | Future Work                                                                                                                                                                 | 311           |  |  |

| C       | hapter 8 SPICE BSIM4.0 I                                                                                                                                                    | Equations 313 |  |  |

Chapter 9 References 325

## CHAPTER 1 Introduction

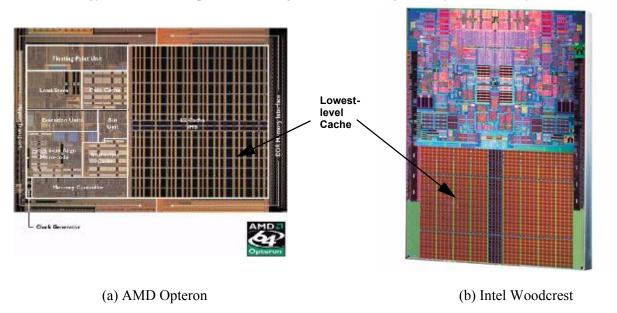

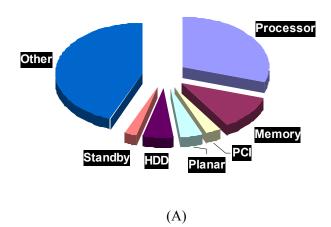

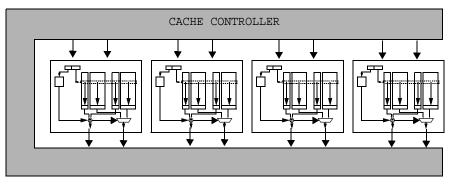

The presence of caches in microprocessors has always been one of the most important techniques in bridging the memory wall, or the speed gap between the microprocessor and main memory. This importance is continuously increasing especially as we enter the regime of nanometer process technologies, as industry has favored investing a larger and larger fraction of a chip's transistor budget to improving the on-chip cache, as it has proven to be an efficient way to utilize the increasing number of transistors available with each succeeding technology. This can be visually seen in the die photos of contemporary processors, as shown in Figure 1-1, where the cache area dominates the total die area. Consequently, it becomes even more important to have cache design tools that give accurate representations of designs that exist in actual microprocessors. The power breakdown in a contemporary Intel-based system is shown in Figure xx [Intel2006], while the power breakdown of a representative processor (Alpha 21264 [Gowan1998]) is shown in Figure xx.

## 1.1 Problem Description

Design tools have always been an integral part of microprocessor design, especially with the onset of VLSI technology that makes it impossible to design, build and debug circuitry the same way it was done

**Figure 1-1: Die photos of contemporary processors showing how cache dominates the total die area.** (a) AMD Opteron. (b) Intel Woodcrest. The lowest-level cache of both processors are pointed to by the arrow.

<sup>1.</sup> Here, we define nanometer process technologies to start from 90nm onwards. All of the studies in this dissertation use process technologies of 90nm, 65nm, 45nm and 32nm, with some studies also containing results for 130nm.

during the small-scale and medium-scale integration era. The use of design tools was important in exploring the available design space and determining optimal implementations given a set of restrictions.

The cache design tool that is the most widely used in academe is CACTI, and it has proven to be a very useful tool not just for cache designers but also computer architects, enabling users to characterize cache behavior without delving too much in some of the more esoteric details of cache design. CACTI, though, was based on assumptions from an obsolete long-channel 0.80µm technology, and with the entry of fabrication process technologies into the submicron and deep-submicron regimes, CACTI results have become aged and may be suspect. eCACTI was written as an enhancement to CACTI and partly updates it to account for some of its limitations, the biggest of which was the inclusion of a subthreshold leakage model to account for the increasing leakage in deep submicron technologies. Even so, both tools still have significant limitations and

## **System Power Consumption**

#### Alpha 21264 PowerConsumption

Figure 1-2: Power breakdowns. (A) Power breakdown in the entire system [Intel2006], and (B) Power breakdown in a representative microprocessor [Gowan1998].

inaccuracies. These inaccuracies may not be overly significant even at deep-submicron technologies, but as we go deeper into very-deep-submicron and eventually nanometer technologies like 90nm, 65nm, 45nm and eventually 32nm, the model limitations of both CACTI and eCACTI, as we will show, will yield inaccurate and misleading results. Some of these major limitations are listed below:

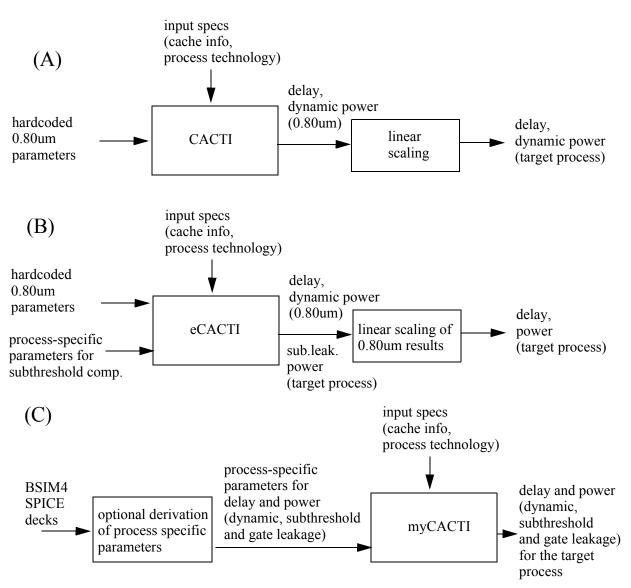

- CACTI and, except for static power computation, eCACTI generate results using a 0.80µm reference technology and then extrapolate it to smaller technologies like present and future nanometer technologies by performing a simple linear scaling of the results, resulting in inaccurate data because many transistor device parameters have not exhibited linear scaling with reference to the 0.80µm process technology.

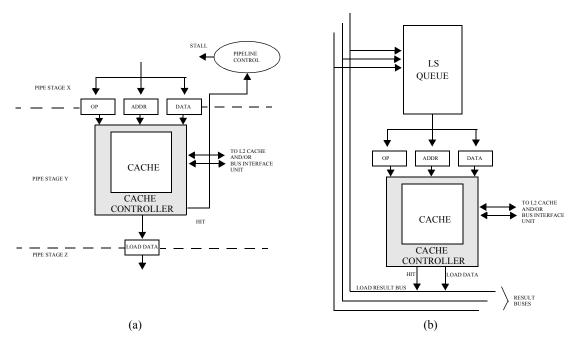

- Both CACTI and eCACTI implicitly handle cache pipelining by using wavepipelining, resulting in severe misrepresentation of the overhead required in explicitly pipelining a cache to properly interface it with a microprocessor. In addition, not all caches produced by CACTI and eCACTI can be wave-pipelined, as this is dependent on the specifics of the optimal implementation found.

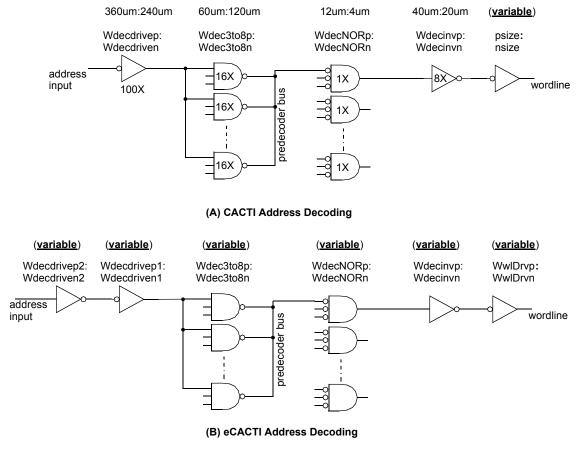

- CACTI and eCACTI have unrealistic assumptions with regards to address decoding circuitry that

severely restrict the search for optimal implementations and in the worst case, produces inaccurately

optimistic data that hides certain circuit delays. Specifically, the assumption of static full-CMOS

logic, along with the use of a fixed-stage decode hierarchy, significantly limits the search for

optimal solutions and in many cases, produces inaccurate results.

- The use of a very limited Back-End-Of-Line<sup>1</sup> (BEOL) stack that does not present an accurate representation of nanometer BEOL stacks, resulting in poor modeling of interconnect parasitics. In addition, significant parasitic effects may be ignored by not accounting for the presence of interconnect vias in the circuit.

- The absence of a gate leakage tunneling current model, which may result in significantly underestimating the power dissipation of the cache.

With these limitations in mind, it becomes necessary to fix these first in order to continue using these cache design tools, especially for the design of pipelined, nanometer caches.

<sup>1.</sup> A BEOL stack refers to all the layers in a process technology fabricated after the active layers. Simply put, it is a description of the interconnect layers in a given process technology.

#### 1.2 Contributions and Significance

The contributions of this dissertation are five-fold. Specifically, these contributions are the following:

- 1. We provide a very detailed tutorial on prevalent static random-access-memory (SRAM) and cache design techniques that are being used in both the industry and academe.

- 2. We enumerate the various limitations and inaccuracies of the cache design tools in prevalent use today, mainly CACTI and eCACTI. These limitations and inaccuracies, as well as impractical assumptions and outright program bugs, are discussed in detail.

- 3. We present a new, vastly enhanced cache design tool that addresses the discussed limitations of both CACTI and eCACTI, and introduces additional enhancements that provide simulation flexibility and ease of use.. We call this new cache design tool myCACTI, which is based on the CACTI and eCACTI infrastructure but introduces radical shifts necessary for nanometer design in both its assumptions and implementation. This dissertation then provides a detailed comparative analysis of myCACTI numbers versus CACTI and eCACTI to demonstrate the inaccuracies that are present with the two existing cache design tools. We show that these inaccuracies are very significant, and could easily lead to false conclusions when these numbers are trusted, especially for cases that may have resulted in hidden impractical implementations during the execution of the program. We describe the major enhancements and improvements of myCACTI over CACTI and eCACTI, namely:

- The use of SPICE BSIM4.0 equations to accurately characterize device behavior for each possible target process instead of using a single reference process and simply scaling the results to the target process (as done by CACTI and eCACTI). In addition, myCACTI provides the ability to support any BSIM4.0 SPICE deck such that it is not constrained to any single set of process parameters and can accomodate any process technology provided by the user. This way, all device parameters that are used by myCACTI is completely transparent to the user, making it easy to verify whether assumptions still hold, especially in future process technologies.

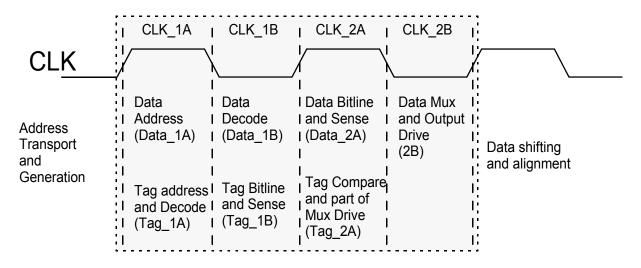

- A detailed description of a typical cache pipeline diagram, along with support for explicit pipelining based on the given timing. This allows the designer to explicitly account for the overhead in pipelining a cache (both in terms of delay, latency and power dissipation), resulting in more accurate numbers and at the same time ensuring easy interfacing with external microprocessor circuitry, as I/O external to the cache simply go in and out through explicit pipeline latches

- Default support for more optimal and more flexible address decoding circuitry. Specifically, the fixed-stage decode hierarchy of CACTI and eCACTI are replaced with a more flexible variable-

stage hierarchy, allowing the simulator tool to accommodate a wider range of loading. In addition, more sophisticated dynamic logic circuits are used to implement these decoders, optimizing both their drive capability and their input load behavior.

- Inclusion of an accurate model and per-process numbers for a typical BEOL-stack that are representative of nanometer processes. The significance of this is made even more important given the tremendous effect of interconnect parasities on a cache's behavior.

- The computation of transistor gate leakage tunneling currents with the use of SPICE BSIM4.0 equations and inclusion of BSIM4.0-compatible SPICE decks.

- Flexible support for multi-Vt process technologies.

- Support for circuit design techniques that may become prevalent in nanometer cache design (like full-swing single-ended sensing)

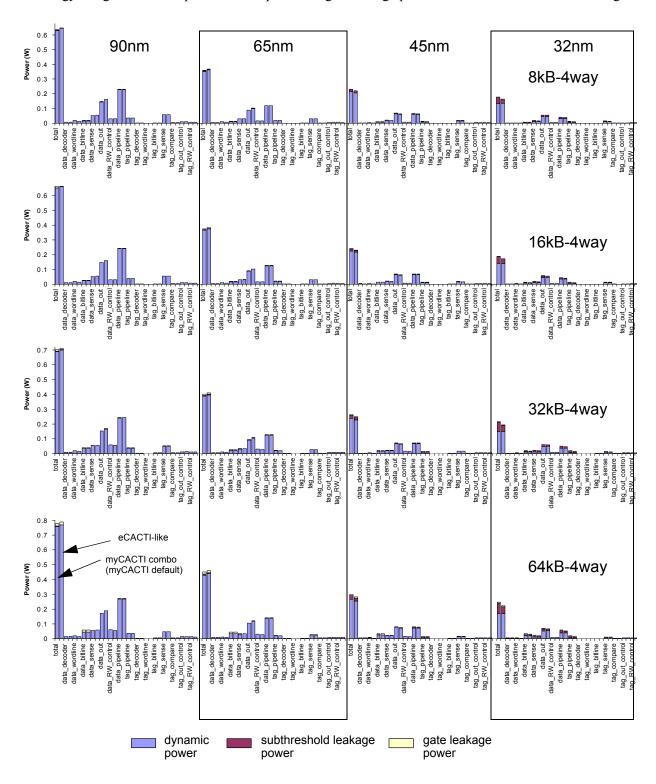

- Generation of more detailed delay and power breakdowns which could be used to study

implementations in more detail by providing additional relevant information that can be used to

justify design tradeoffs.

- More flexible optimization schemes that allow the identification of more than one optimal

implementation. For one thing, this allows the designer to generate pareto optimal curves of the

design, providing more choices to the designer.

- Various bug fixes to CACTI and eCACTI code.

- 4. We use myCACTI to provide more accurate insights into different cache configurations. myCACTI is used to provide detailed design space exploration and power and delay breakdowns of different nanometer caches, resulting in observations like the following:

- The pipeline overhead of a nanometer cache is very significant and in most cases, is one of the dominant contributors to power dissipation. Ignoring this overhead during the design will result in unrealistically optimistic numbers.

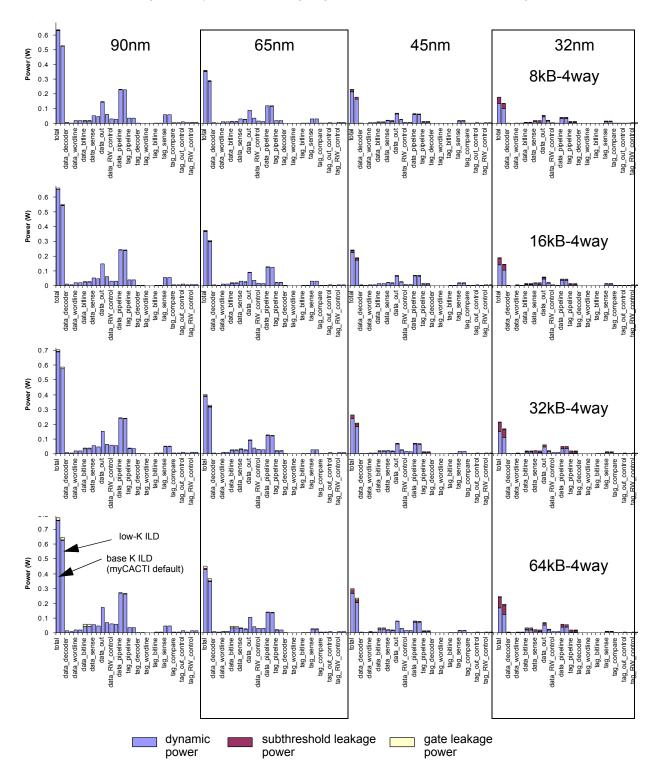

- In deep nanometer nodes, the static power dissipation is very significant, especially in the data bitlines. For single-Vt processes, the static power is typically much more dominant than dynamic power, especially for nodes like 45nm and 32nm, and most of this static power dissipation is due to the bitlines. For dual-Vt processes, the amount of static power is greatly reduced, but is still very significant for the deep nanometer nodes like 45nm and 32nm.

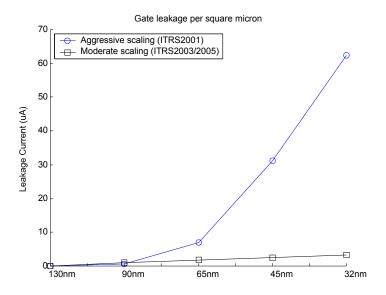

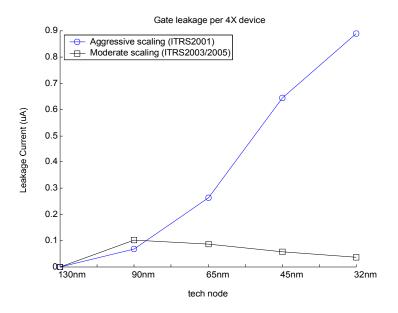

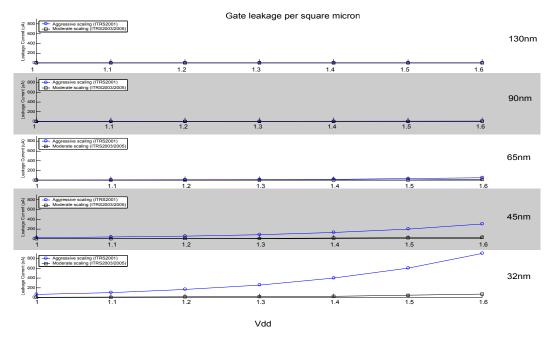

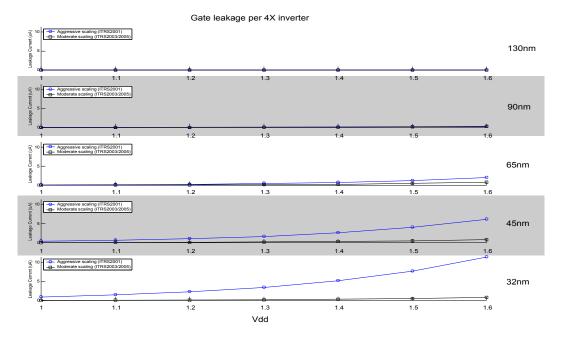

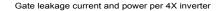

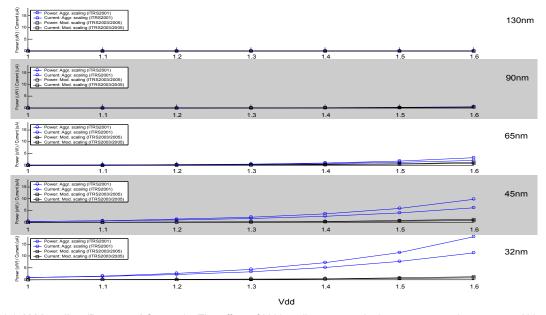

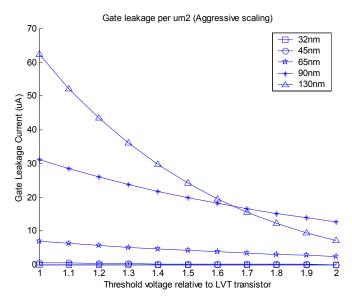

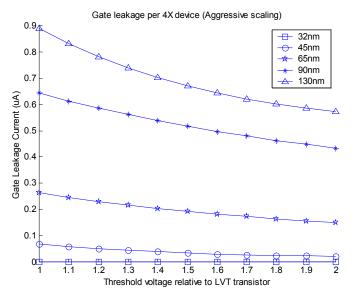

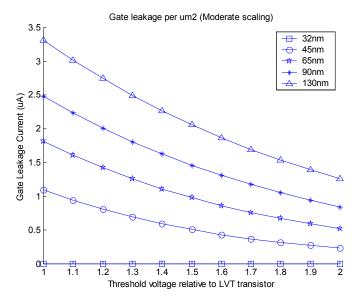

- Gate leakage was found to be surprisingly insignificant, even at deep nanometer nodes. This is mostly due to the fact that the SPICE models we use have been updated to be much less aggressive with regards to oxide scaling, as described by the 2003 and 2005 editions of ITRS.

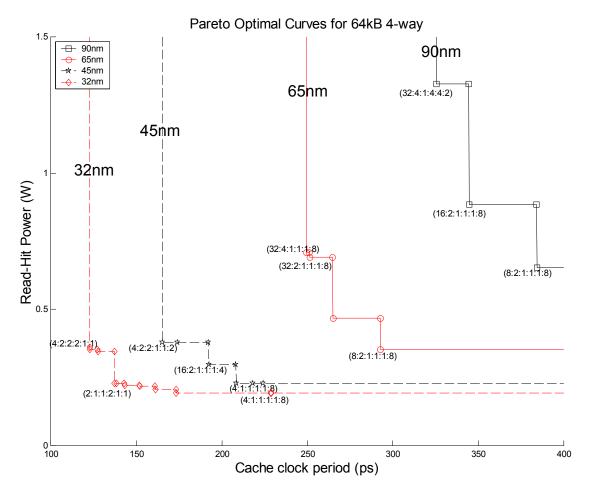

- Pareto optimal curves have demonstrated that some designs are obviously superior than others, and it would make no sense to implement some designs even if they do seem to be optimal. For instance, we have shown that some points in the pareto optimal curves of a 4-way cache is better in both delay and power dissipation compared to a 1-way cache of the same size. Given also that we expect the 4-way cache to result in better processor IPC, this mandates that some design points in the 1-way pareto curves are not good options, as better implementations are possible without any compromise whatsoever.

- The use of full-swing single-ended sensing becomes more and more practical with each succeeding generation, as its disadvantages decreases while the advantages of low-swing differential sensing also decreases.

- 5. Finally, we study the reasons why gate leakage tunneling currents do not seem to be a significant contributor to static power dissipation even for deep nanometer technologies like 45nm and 32nm. We see that the slowing down of aggressive scaling in the past few years because of concerns with power dissipation has significantly slowed down the scaling of gate oxide thicknesses, such that we observe that, on a per device basis, gate leakage tunneling currents actually decrease from one generation to the next.

Finally, future directions to the development of myCACTI are identified to show possible ways that the tool can be improved in such a way as to allow even more different kinds of studies to be performed.

All of these contributions are significant, in that it allows the microprocessor and/or cache designer to better characterize the cache behavior, especially that of present and future pipelined nanometer caches.

## 1.3 Organization of Dissertation

This dissertation aims to provide background on cache design in general, and some cache design tools in particular. A new cache design tool is then demonstrated that provides major additional enhancements compared to existing cache design tools, and the applications of this tool is demonstrated. In this chapter, a brief introduction to the dissertation is given. In chapter 2, a very detailed background on cache design is given to serve as a foundation while discussing the concepts used in cache design tools. In chapter 3, the different cache design tools are discussed. CACTI and eCACTI are discussed in detail. This chapter explores the usage, features and also, the limitations of the two cache design tools. The major enhancements and new features of a

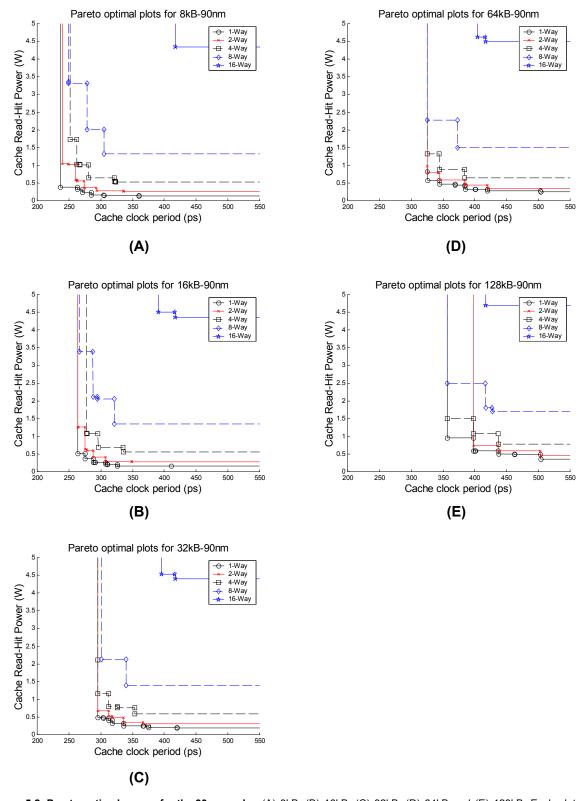

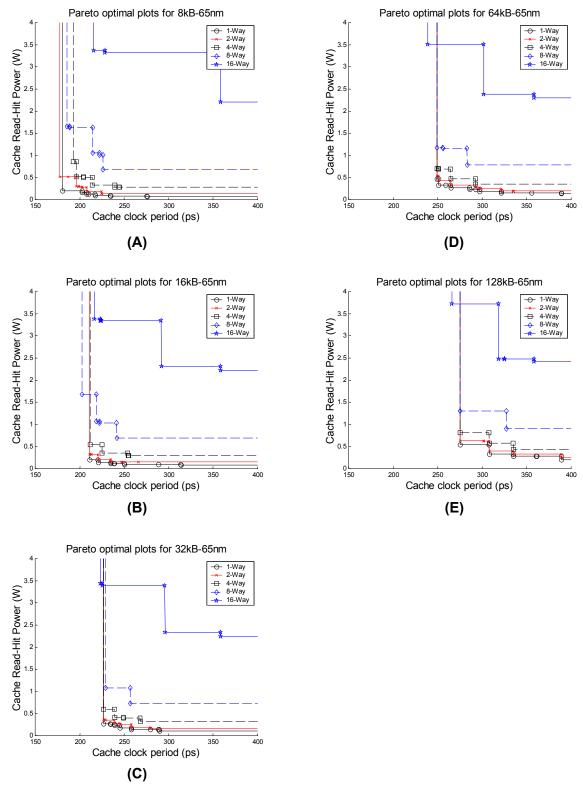

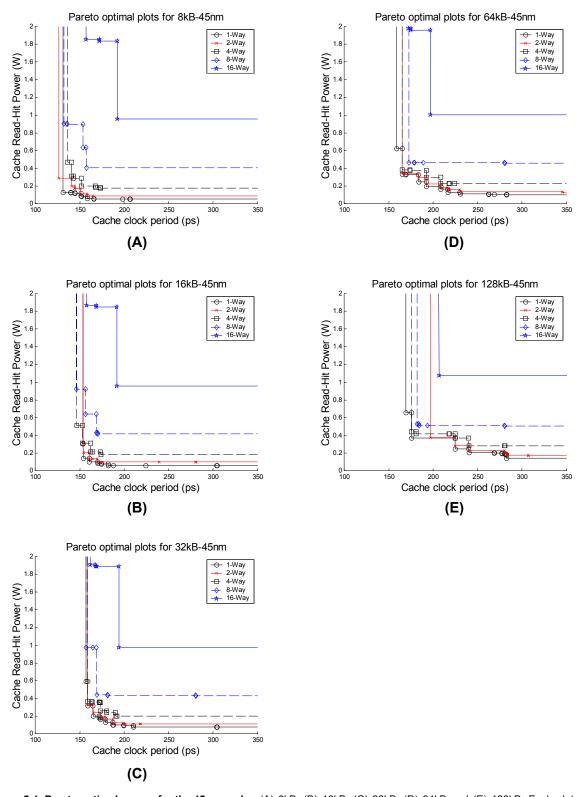

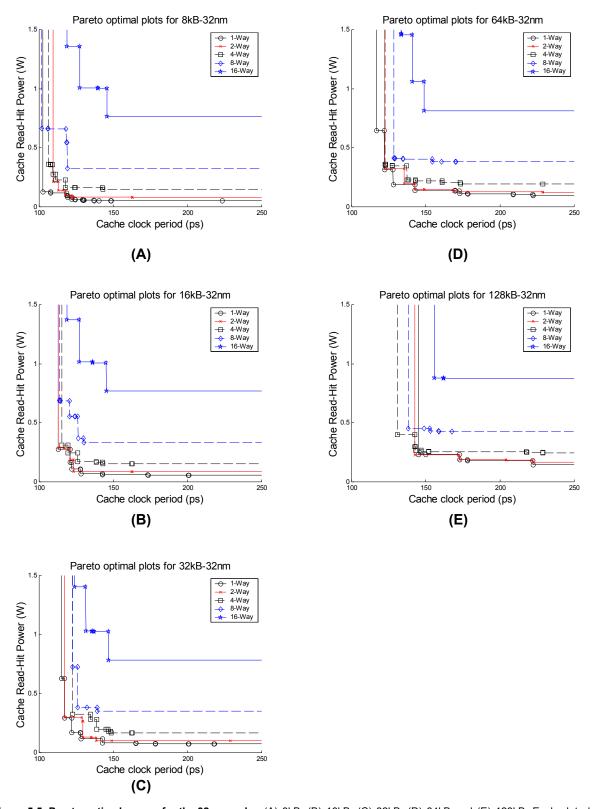

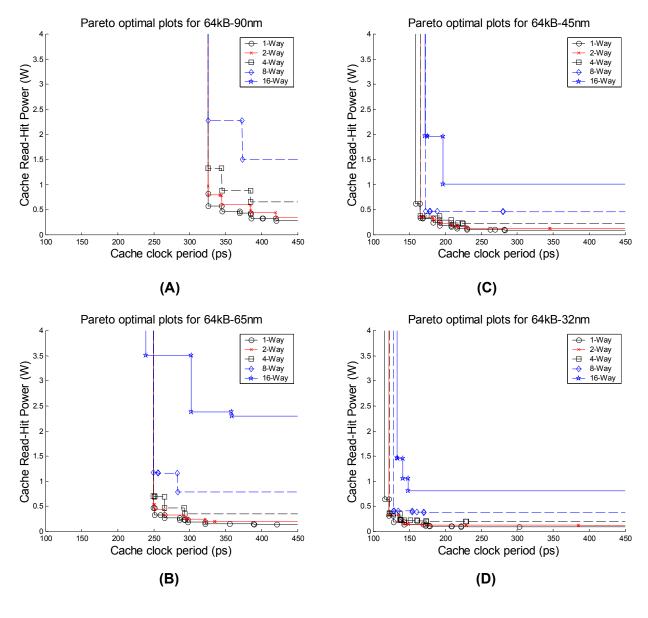

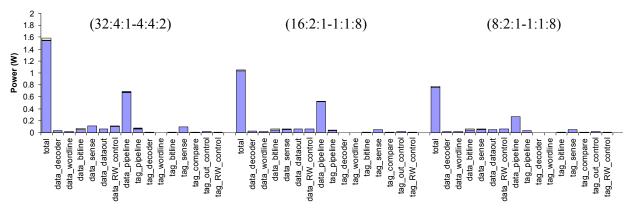

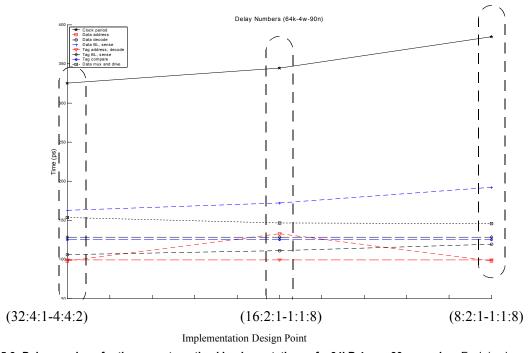

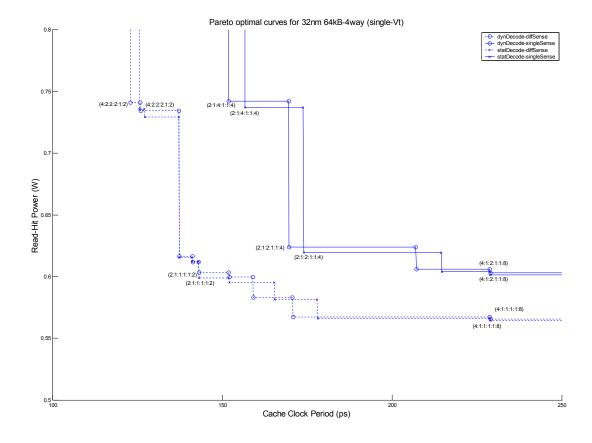

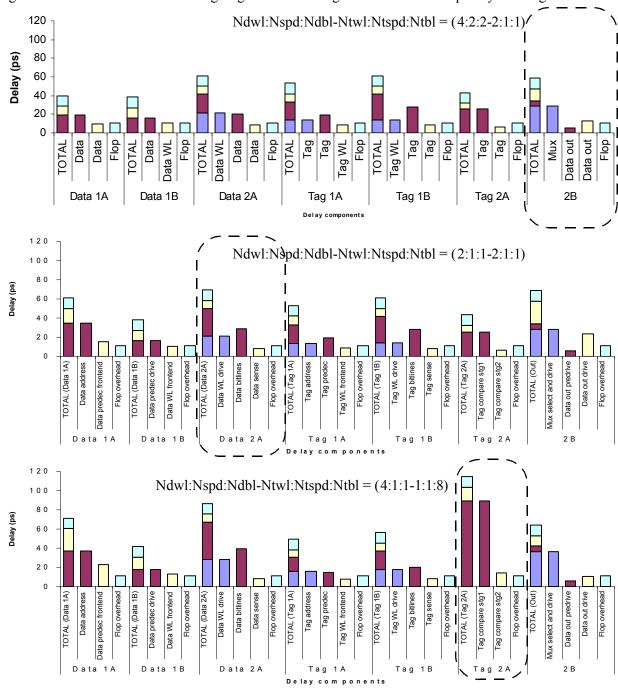

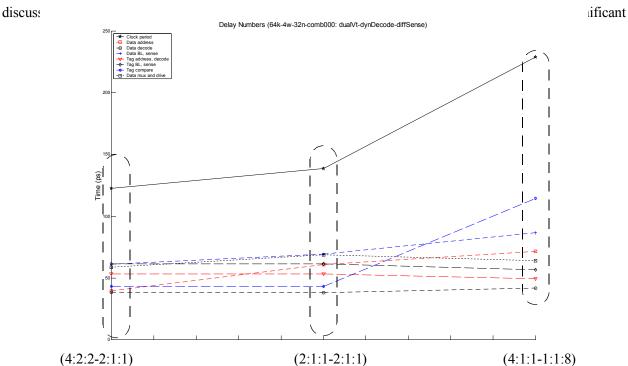

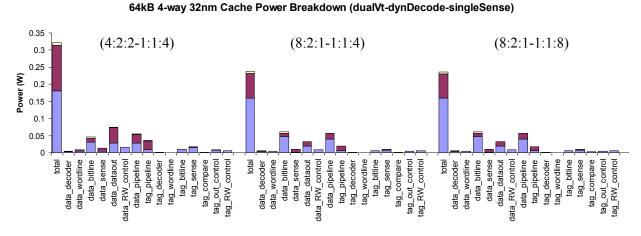

new cache design tool, myCACTI, are then discussed in relation to the existing cache design tools. In chapter 4, detailed comparisons are performed to show the difference in results between CACTI/eCACTI and myCACTI, showing that once the major limitations of CACTI and eCACTI are addressed, the numbers generated by simulation will be significantly different from what they presently would be. This chapter discusses in detail all the different isolated comparative studies that are performed. In addition, the general framework of the comparison is also discussed. In chapter 5, the applications of myCACTI are then demonstrated, starting with detailed design space explorations of a slew of different cache configurations ranging from caches with sizes of 8kB, 16kB, 32kB, 64kB and 128kB; associativities of 1-way, 2-way, 4-way, 8-way and 16-way; and technology nodes of 130nm, 90nm, 65nm, 45nm and 32nm. The output of this study is post-processed to produce pareto optimal plots of the optimal implementations for each cache configuration based on the two criteria of cache read-hit power dissipation and cache clock period. After this general design space exploration is demonstrated, a second set of studies are then performed to show the detailed power dissipation and delay breakdown that myCACTI can provide, and how they can be used by cache designers to identify candidate implementations for further optimization. The study focuses on 64kB 4-way caches and produces detailed data on three of the pareto optimal implementations for each cache configuration. After details of the representative 64kB 4-way cache have been shown, a third set of studies isthen performed, this time to study the effect of three different cache design techniques (mainly single/dual Vt transistors, static/ dynamic decoding and full-swing single-ended/low-swing differential sense amplification) on a 64kB 4-way 32nm cache. During these studies, one of the more important observations is that, contrary to the expectations of the research community, the effects of gate leakage tunneling current with respect to static power dissipation is not significant, even in the very deep nanometer technology nodes like 32nm. Chapter 6 studies this in detail, and shows that precisely because gate leakage tunneling currents are expected to become an even bigger problem than subthreshold leakage currents, the scaling of the gate oxide thickness has been significantly slowed down, and the SPICE models that have been used for the simulations already reflect this. Chapter 7 summarizes this dissertation with concluding remarks.

## CHAPTER 2 Background

### 2.1 Power Dissipation in CMOS Circuits

CMOS circuits were designed to dissipate power only during transitions in state. Once the internal node voltages of a logic gate have been charged or discharged and have reached their steady state, there should exist a very high impedance in between supply and ground such that they are essentially open-circuited.

The dynamic power associated with switching a CMOS gate can be given by:

$$P_{dynamic} = (N \cdot C \cdot V_{DD}^2 \cdot f) + (I_{scc} \cdot V_{DD})$$

The first term is usually the more important because of its omnipresence -- any circuit will always have some internal parasitic capacitance, no matter how small, that has to be charged or discharged in order to change its state and the first term in the equation accounts for the power involved in this capacitive switching process. The second term is due to the so-called short-circuit current, or crowbar current, that exists when the PMOS and NMOS networks are both momentarily active at the same time, presenting a low-impedance path from supply to ground. Although this term may sometimes be significant, careful design of the circuits to ensure reasonable switching edge rates will minimize the time window where the low-impedance Vdd to Vss shorts exist<sup>1</sup>, minimizing the contribution of this crowbar current.

From the equation for dynamic power, many solutions suggest themselves in order to reduce the total power. Reducing any of the four terms (number of devices, device capacitance, supply voltage or system frequency) will result in reduced power consumption. The challenge then becomes the minimization of the negative effects involved in changing these parameters when trying to reduce power.

Static power, on the other hand, is generally expressed as:

$$P_{static} = I_{leak} \cdot V_{DD}$$

This equation simply lumps all the leakage existing in the circuit and uses it in the conventional equation for power.

Power consumption, until recently, has not been a primary concern in designs that were not targeted for specific low-power applications (e.g. portable devices), but with the continuous down-scaling of

<sup>1.</sup> Fast edge rates ensure that the inputs to both the NMOS and PMOS do not linger in an undefined region where it exceeds the threshold of both transistors resulting in a conducting channel where crowbar currents can flow.

technology, the static power dissipation has become increasingly larger. Transistor device channels that were previously considered open circuits are now exhibiting current leakage. Some device structures have become so thin that even though they were designed to be insulators, the very small dimensions involved allow quantum tunneling phenomena to result in significant current flow. Static power dissipation has become a very big problem, and it has greatly contributed to making power consumption a first-order concern even in designs that previously had minimal concern for power at all (e.g. desktop computers).

## 2.2 Leakage Current Mechanisms

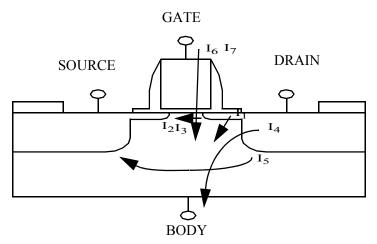

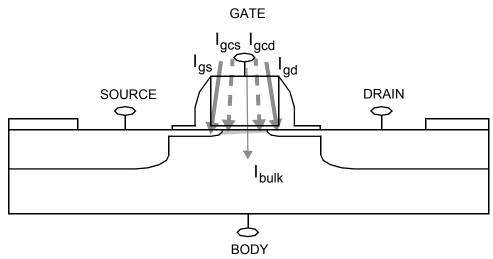

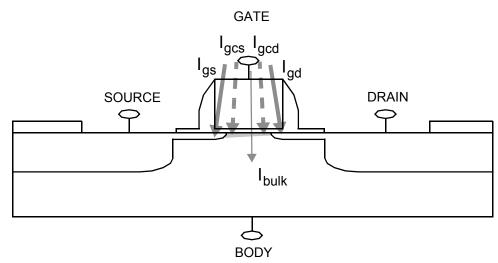

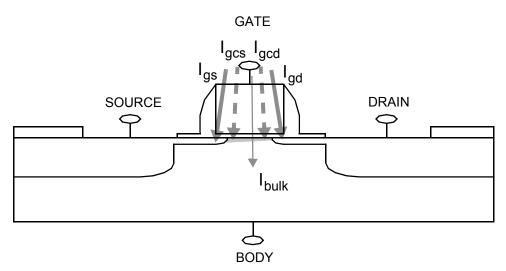

In this section, we provide a brief overview of the leakage mechanisms that are prevalent in a modern MOS transistor. Anis [Anis2003] gives a good overview of these leakage currents, as shown in figure 2-1, and his explanation of these different mechanisms are as follows:

$I_1$  is the reverse bias pn junction leakage. It has two main components: the minority carrier diffusion/drift near the edge of the depletion region, and the electron-hole generation in the depletion region of the reverse bias junction.

I<sub>2</sub> is the weak inversion current or subthreshold conduction current between the source and drain in a MOS transistor; I<sub>2</sub> occurs when the gate voltage is below Vt. the carriers move by diffusion along the surface, and the exponential relation between the driving voltage on the gate and the drain current is a straight line in a semi-log plot.

I<sub>3</sub> represents Drain-Induced Barrier Lowering (DIBL). It occurs when the depletion region of the drain interacts with the source near the channel surface to lower the source potential barrier. The source then injects carriers into the channel surface without the gate playing a role.

Figure 2-1: Typical leakage current mechanisms in a modern MOSFET.

I<sub>4</sub> refers to the Gate-Induced Drain Leakage (GIDL). GIDL current arises in the high electric field under the gate/drain overlap region, causing a deep depletion and effectively thinning out the depletion width of the drain to the well pn junction. Carriers are generated into the substrate and drain from the direct band-to-band tunneling, trap-assisted tunneling, or a combination of thermal emission and tunneling. the thinner oxide thickness Tox and higher Vdd causes a higher potential between the gate and drain which enhances the electric-field dependent GIDL.

$I_5$  is the channel punch-through which occurs when the drain and source depletion regions approach each other and electrically touch deep in the channel. Punch-through is a space-charge condition that allows the channel current to exist deep in the sub-gate region, causing the gate to lose control of the sub-gate channel region.

$I_6$  represents the oxide leakage tunneling. The gate oxide tunneling current Iox which is a function of the electric field Eox can cause direct tunneling through the gate.

$I_7$  is the gate current due to hot carrier injection. Short-channel transistors are more susceptible to the injection of hot carriers (holes and electrons) into the oxide. These charges are a reliability risk and are measurable as gate and substrate currents.

Typically,  $I_2$  and  $I_3$  dominate the off leakage current<sup>1</sup>, and  $I_6$  dominates the gate leakage. A formula for  $I_{off}$  [Chandrakasan1996] is the following:

$$I_{off} = \frac{I_0}{W_0} \cdot W \times 10^{-\frac{(V_{GS} - V_t)}{S}}$$

Where Io/Wo is the saturation current per unit width, and S is the subthreshold slope. For devices with zero gate bias, it can be seen that gate leakage is an exponential function of threshold voltage. For a typical technology with a subthreshold slope of 100mV/decade, each 100mV increase in Vth results in an order of magnitude larger current.

In previous generations, this I<sub>off</sub> has not been a significant problem because of the larger values of Vt involved. But as transistor sizes are scaled down, it often becomes necessary to scale down Vdd correspondingly (i.e. in a constant electric field scaling scheme). Logic gate speeds, as measured by the ability to charge and discharge internal capacitances, are dependent on the gate overdrive voltage Vgs-Vt (where Vgs

<sup>1.</sup> The off leakage current is typically defined as the device drain-to-source current (Ids) with the gate off (i.e., strong inversion has not been reached such that no conducting channel exists between the drain and source terminals. Often, this off current has been associated and is interchanged with the subthreshold current, simply because subthreshold is often the main, dominant factor.

is most often Vdd when provided by another CMOS gate). Decreasing Vdd tends to decrease the speed of the system (even with a decrease in capacitance associated with device scaling) and this is traditionally compensated for by decreasing the threshold voltage to improve the gate overdrive, resulting in an improved current driving capability of the device. Continuing device scaling results in more and more reduction in Vt such that the device off current starts becoming significant, especially when multiplied by the large number of total devices in the entire chip.

Additionally, even in the presence of scaling, a certain amount of device gate to body capacitance needs to be maintained in order to retain control of the inversion channel. With the same dielectric material, this requires reduction of the oxide layer thickness, tox. But as tox goes down below 20 angstroms with continued scaling, the corresponding oxide layer becomes so thin as to allow quantum tunneling effects to start being significant. As such, gate leakage effects are starting to become important, with some sources stating that the rate of increase of gate leakage compared to subthreshold leakage per technology generation is much faster, and gate leakage current may soon become the most dominant mechanism.

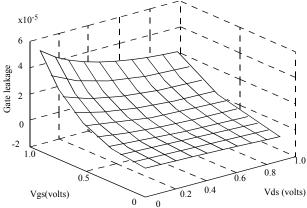

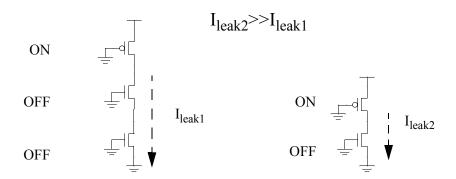

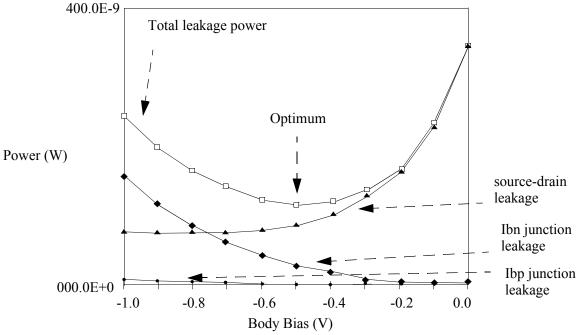

The equation for gate leakage current is more complicated, as given by Clark [Clark2004]. Instead, most techniques that provide solutions for gate leakage instead rely on the characterization of Rao [Rao2003] describing the behavior of gate leakage with respect to its gate-source and drain-source voltage, as shown in figure 2-2. They conclude that for a given gate bias, gate leakage is minimum if the gate-drain voltage (Vgd) is minimum. To minimize gate leakage, we should strive to minimize gate bias (Vgs) and if this is not possible, minimize the gate-drain bias (Vgd).

As a summary, subthreshold leakage are often solved using techniques that increase its threshold voltage, either statically or dynamically. In addition, DIBL effects that contribute to the leakage can be reduced by lowering the drain-source voltage across an off transistor. Gate leakage currents, on the other hand,

Figure 2-2: Gate leakage current for an NMOS as a function of gate-source (Vgs) and drain-source (Vds) voltage (figure from Rao2003). It shows the highest gate leakage when Vgs is max and Vds is zero (making Vgd max also).

are minimized primarily by reducing the gate bias (Vgs) and secondarily, by minimizing the gate-drain bias (Vgd).

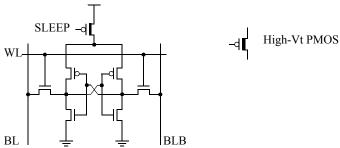

## 2.3 SRAM and Cache implementation

Caches have become an integral part of the operation of modern general-purpose microprocessors. Its importance has become so paramount that its share of the total transistor budget has steadily increased to the point that almost half of microprocessor's die area is allocated to caches. With its increasing total number of devices, caches are becoming a bigger and bigger contributor to a design's static power dissipation. Consequently, it is of utmost importance to develop sound, effective strategies that lower the static power consumption of memory circuits, especially since this will result in a reduction of power consumption during both active and idle modes of the processor. It is therefore necessary to have a detailed knowledge of the design intricacies that are inherent to memory circuits and in particular, SRAMs in order to understand which parts of memory circuits can be modified to reduce leakage currents.

To start things off, we discuss a sample cache operation, a cache read hit, in moderate detail, exposing some of the implementation issues involved in its design.

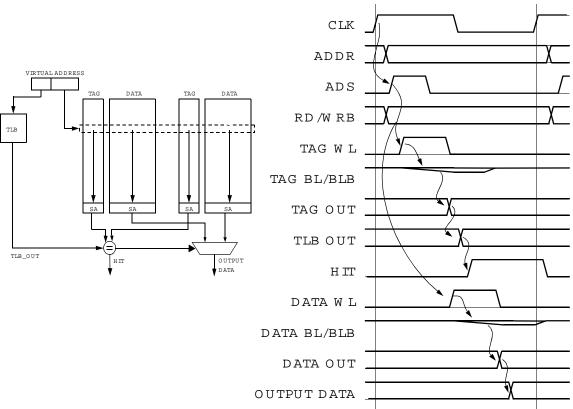

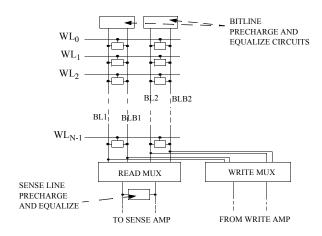

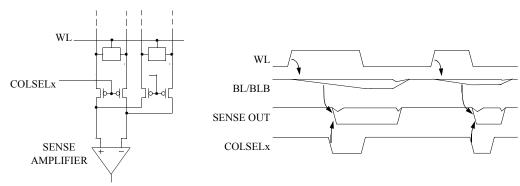

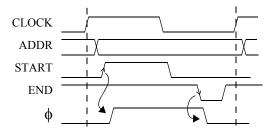

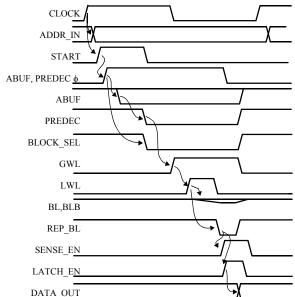

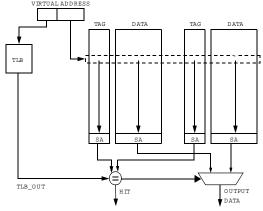

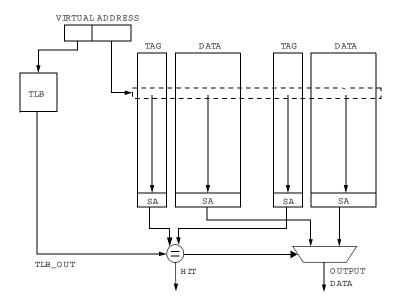

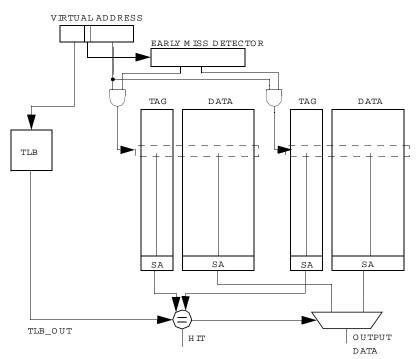

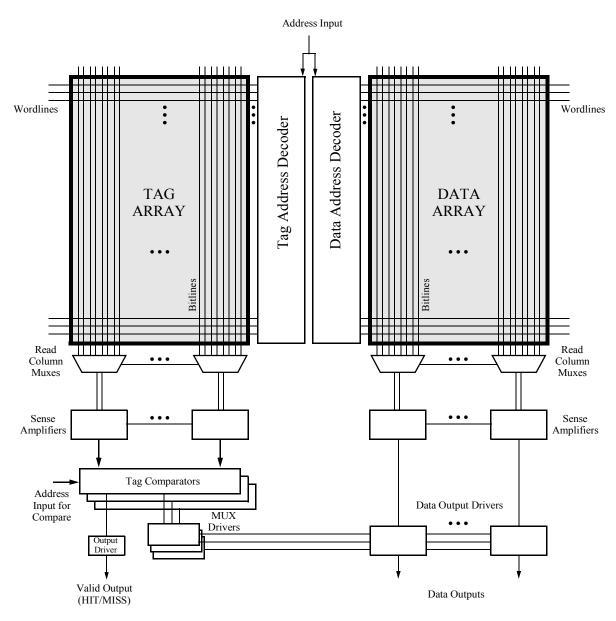

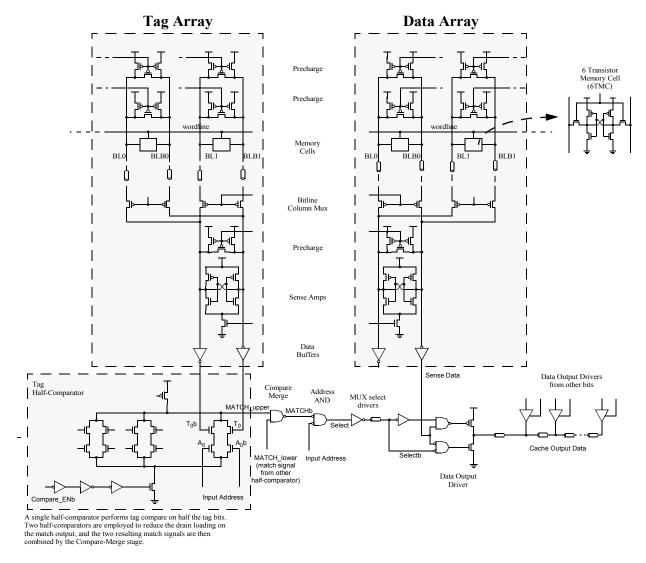

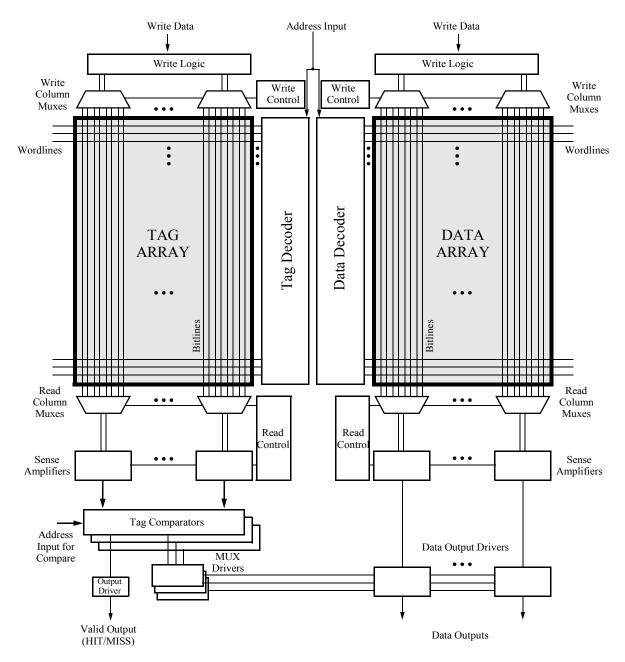

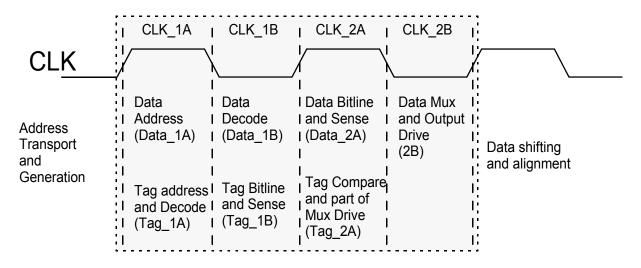

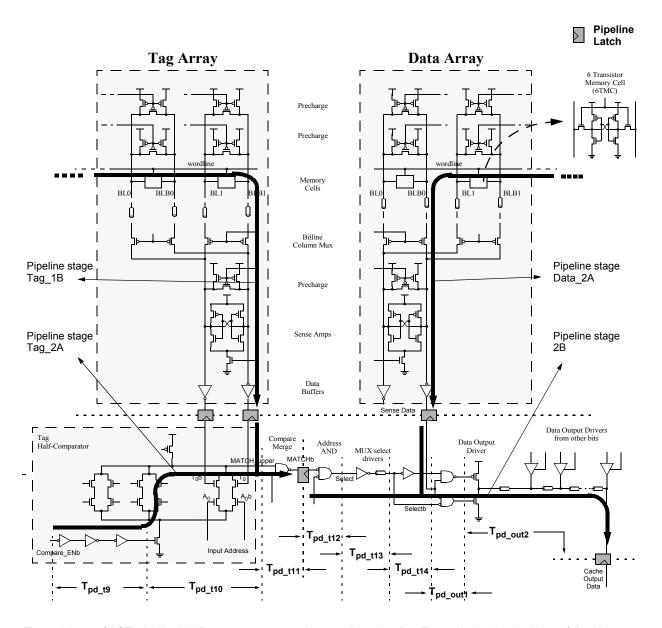

Figure 2-3 shows an example cache organization: a 2-way set associative cache with virtual addressing, along with a timing diagram showing the various events happening in the cache (to be discussed in much more detail in later sections).

Basically, the following steps involve:

- 1. Providing address to the cache, along with an address strobe signal (ADS) confirming the validity of the address. A read/write signal (R/W#) is also sent to specify the operation.

- 2. The index part of the address chooses a word within the tag and data arrays of the 2-way set associative cache (signified by the wordline signal, WL). This in turn causes the internal bitlines to develop a differential, which is amplified by sense amplifiers to produce a full-swing differential output voltage.

- 3. The translated address from the TLB is compared with the output of the tag array to decided if the cache access hit or miss. In case of a hit, the proper data is chosen among the two ways by controlling the output multiplexer and forwarded. A cache miss requires the cache controller to perform a separate operation to retrieve data from external memory (or another level of cache) and perform a write access to the cache.

We have now demonstrated the basic cache read operation and shown some of the blocks used in implementing a cache. In the next sections, we will discuss much more in-depth details, starting with the

implementation of the basic storage structures comprising the tag and data array, then proceeding to how a cache is implemented and how these data arrays are used. Along the way, we also discuss advanced topics that are related to contemporary cache issues like low-leakage operation.

### **SRAM Implementation**

In this section, we discuss the implementation of a static random access memory (SRAM). This is the type of memory used as the building block of most caches because of its superior performance over other memory structures, specifically DRAM. Along with the fact that it uses the same fabrication process as the CPU core, while high-performance DRAM uses a different process that is suboptimal for logic circuits, making it less feasible and less attractive to integrate DRAM-based memory and the processor in one chip.

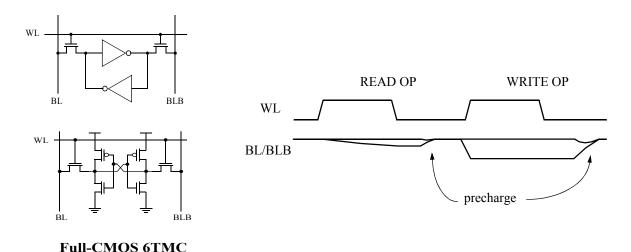

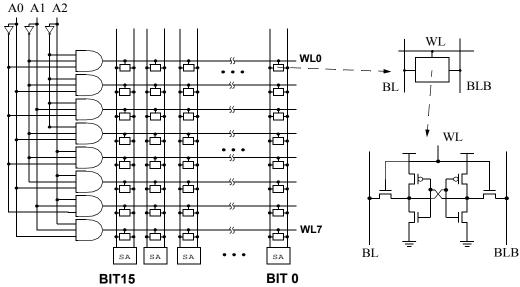

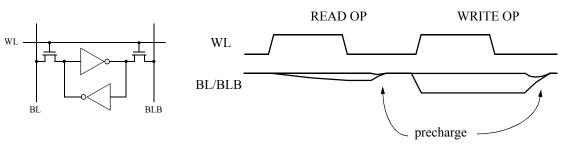

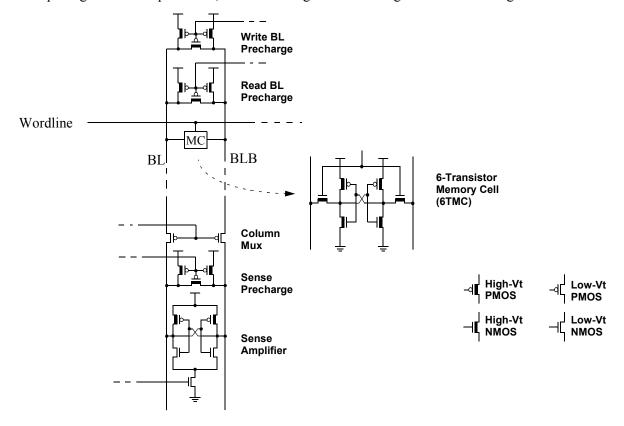

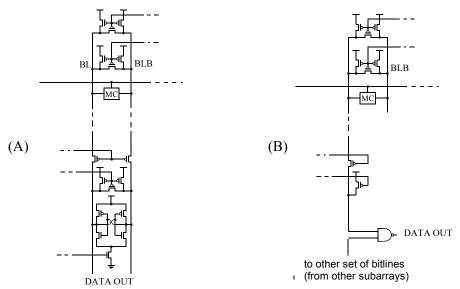

**Basic 1-bit Memory Cell.** This subsection describes how the most basic unit of an SRAM -- a single data bit -- is implemented. For SRAMs, the memory cell is implemented as two cross-coupled inverters accessed using two pass transistors. This topology and its most typical contemporary physical implementation are shown in figure 2-4, along with simple timing diagrams showing the READ and WRITE accesses.

Figure 2-3: Block diagram of a 2-way set associative cache organization, along with the timing diagram showing both internal and external signals for a read operation.

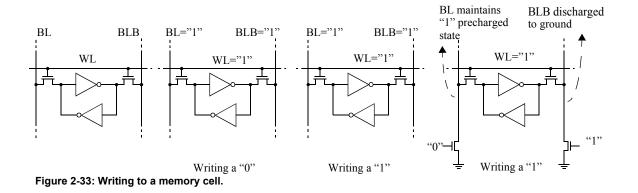

This cross-coupled connection creates regenerative feedback that allows it to indefinitely store a single bit of data. This configuration shows a 1-bit MC with one R/W port that can be used for either a read or a write, but not simulataneously As shown in the figure, the bit is read by asserting WL and detecting the voltage differential between the bitline pair, which are initially precharged to a logic high voltage. The second phase shown in the is a write operation. The bitline is driven with a differential voltage from an external source to force the data onto the memory cell.

One of the assumption of caches, and memory in general, is the ability to store digital data, and we have shown how a single bit can be stored by an SRAM using cross-coupled inverters. This cross-coupled inverter has been implemented in different ways during its evolution. Although we only show the particular implementation that is currently the most practical, numerous implementations have existed over the years, where the main difference has been how the inverter's pullup network is implemented.

Early SRAMs typically used either the full-CMOS or the polysilicon load memory cell configuration. The main advantage then of the poly-load configuration was its smaller area since only four transistors were required for one bit; the pullup was implemented using an additional highly-resistive polysilicon layer such that the load is fabricated on top of the existing transistors, requiring less area. With decrease in feature sizes, the amount of area occupied by the poly-load needed to produce a large enough resistance to overcome leakage currents became too big. Along with its low SER [List86], the poly-load implementation has now become impractical. With the increase in space occupied by the poly-load, it started to be replaced by the poly-PMOS or thin-film-transistor (TFT) PMOS [Minato1987] load configurations, which could still be fabricated on top of the active NMOS but with characteristics superior to the poly-load. With the increasing on-chip integration of caches with microprocessor logic circuits, the additional process complexity required to

Figure 2-4: The basic SRAM cell showing cross-coupled inverters accessed through pass transistors. The state of important signals are also shown during a read and write access. Also shown is the six-transistor implementation of the memory cell (6TMC).

implement the poly-PMOS/TFT-PMOS circuits on the same die as the digital circuits became too cumbersome. An alternative to these circuits, the loadless four transistor cell (LL4T) ompletely removes the pullup load [Noda1998]. Although this scheme results in a smaller area compared to the full-CMOS implementation because only four NMOS transistors are involved, the cell has to be very carefully designed to make sure that leakage currents do not interfere with the latching operation of the cell and its ability to retain data. With continuous technology scaling, the charge stored within the cell decreases, while leakage current increases -- making it more difficult to design reliable LL4T cells, especially if external radiation from alpha particles are taken into account.

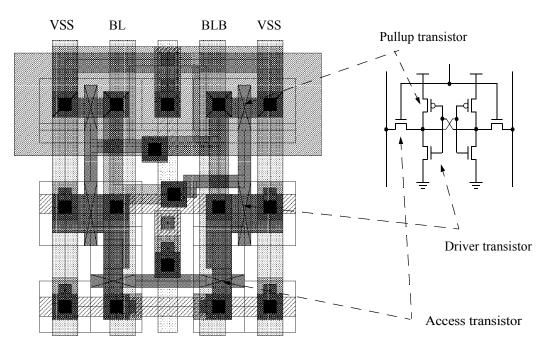

Currently, most conventional designs use the full-CMOS six transistor memory cell (6T MC), with different variations existing based on issues of sizing, physical layout, and transistor threshold voltages for low power (to be discussed in later sections).

The rest of the discussion will be limited only to the 6T MC variant, and an example layout using MOSIS SCMOS rules for a 0.25µm process is shown in Figure 2-5, along with its transistor-level circuit defining the access, driver, and pullup transistors.

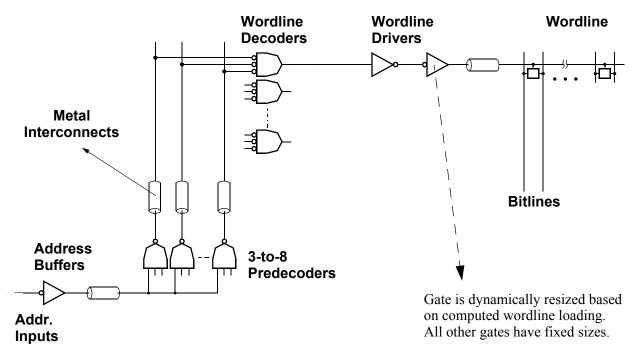

**Address Decoding.** Address decoding is a conceptually simple process of receiving address information and providing signals to initiate and perform the desired operation on the addressed location. At its simplest, it involves feeding an address value into a binary decoder (n to  $2^n$ ) and using the asserted output to activate the

Figure 2-5: Layout of a six transistor memory cell (6T MC) using MOSIS SCMOS rules (SCMOS\_SUBM using TSMC0.25 $\mu$ m). Also shown is the definition of the access, driver and pullup transistors.

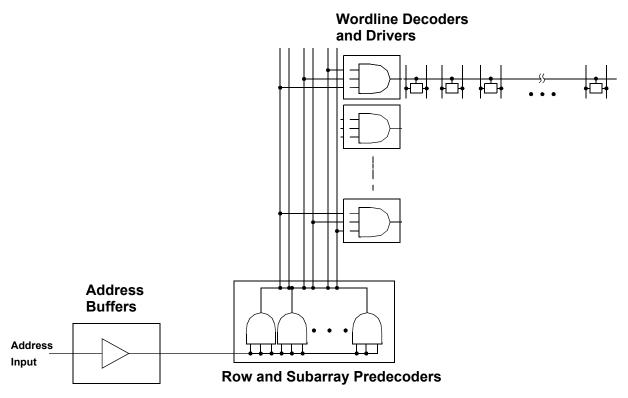

wordline of a subset of memory cells associated with this address. This involves a single AND operation on the input address, with the output connected to memory cell wordlines, as shown in Figure 2-6.

The main concern in address decoding is the large fan-in and fan-out requirements of typical memories because of the number of address bits being decoded and the large amount of cells that have to be driven. This makes the simple one-level AND structure inefficient, and virtually all SRAM designs implement a multi-level decode hierarchy to implement the logic AND function.

In typical designs, the address decoder contributes significantly to the critical path delay and total power consumption, emphasizing the need to optimize the memory array's decode hierarchy implementation **Predecoding.** One of the main usage of a decode hierarchy is to minimize the fan-in of parts of the decode circuit because higher fan-in gates have a large logical effort [Sutherland1991 and Sutherland1999] making them less efficient. Simply put, logical effort expresses how harder it is to drive an arbitrary gate compared to an inverter of the same drive strength. High fan-in static gates typically have high logical efforts and are less efficient to use.

One of the techniques used in minimizing fan-in is a method called predecoding. Predecoding involves using one level of logic to effectively AND subsets of the address. The outputs of these predecoders are then combined by low fan-in gates to produce the final decoder outputs, which are the wordline signals connected to the memory cells. In this way, predecoding simply involves performing the AND operation using multiple levels of logic.

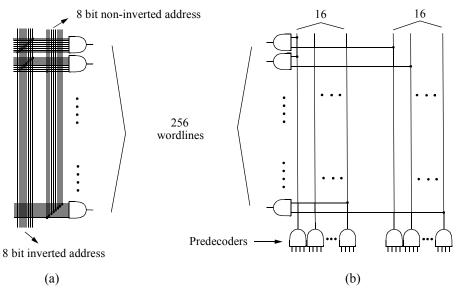

Consider an example where an 8-bit address is to be decoded. A simplistic approach using  $256 (2^8) 8$ -input AND gates are used, as shown in Figure 2-7(a). Although logically correct, these ANDs will have

Figure 2-6: Address decoding shown for a simplistic 8 x 16 bit memory showing 8 3-input AND gates that enable the wordlines of a specific number of cells (16 for one wordline). Also shown are the sense amplifiers that generate logic outputs from the small voltages produced by the cells, and is the internals of a single cell.

significantly higher gate capacitances compared to 2-input ANDs, resulting in larger delays, higher power consumption, and large area.

An alternative decoder implementation using predecoding is shown in Figure 2-7(b). The 8-bit address is divided into two subsets, each with 4 bits. For both subsets, sixteen 4-input ANDs are used to generate all possible combinations of the 4-bit address. The final wordlines are generated using 2-input AND gates to combine one output each from the two subset. In this case, 256 2-input AND gates are used to generate all the 256 wordlines.

Although conceptually simple, predecoding has numerous advantages. Since the final AND gates only have two inputs, they will have significantly less gate capacitance compared to the first implementation. This results in a smaller, faster, lower power circuit that is also more scalable than the original. Although some of the area advantage is offset by requiring the initial high fan-in ANDs, this approach is overall still much better. One main reason that is not immediately obvious is that the possible implementation of the predecoders is more flexible since it can be separated from the memory arrays, and will have less restrictions imposed by the memory array dimensions

With this flexibility, the predecoders can be implemented using sophisticated circuit designs that enable circuits with faster speed, lower power and smaller area. Some of these techniques will be covered in more detail in a later subsection..

The application of these advanced circuit techniques to the first approach is not feasible because of the higher cost involved in applying it to a much larger number of gates (In the example, 256 gates for the simplistic approach and only 32 for the predecoder approach). At the same time, the implementation

Figure 2-7: Sample wordline decoders for an 8-bit address. (a) A simplistic high fan-in AND approach. (b) Decod with predecoding.

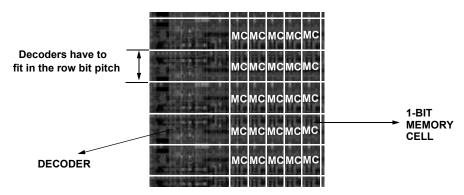

possibilities for gates embedded within the regular structure of the memory array is much more limited since it is affected by other factors including the cell to cell spacing, or pitch, of the memory arrays, as shown in Figure 2-8.

The main disadvantage of predecoding is the need to distribute more wires to propagate all the intermediate predecoder outputs. This is a minor issue, and the advantages of predecoding makes it almost necessary in most SRAM designs.

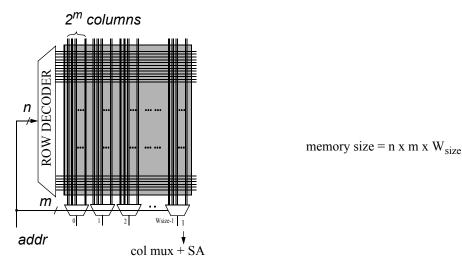

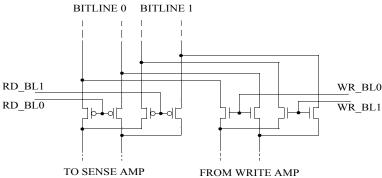

**Row and Column Decoding.** For added flexibility in operation, memory arrays like SRAMs (and in later chapters, DRAMs), typically employ two dimensional decoding, where a subset of the address accesses a single row of the array (the row address), and a separate subset is used to select a fraction of all of the columns accessed within the row, as shown in the sidebar.

In figure 2-9, predecoding for both the row and column addresses are not shown for simplicity, and it is assumed that the row and/or column decoder utilize these predecoder outputs. The multiplexer allows

Figure 2-8: Sample floorplan of the decoders beside the memory array showing the bit pitch limitation.

Figure 2-9: Row and column decoders for a simple SRAM.

multiple bitlines to share a single sense amplifier, saving both power and area. These multiplexers are almost always of the pass transistor variety, allowing it multiplex small-swing voltages in the bitlines. To simplify the figure, only the data read path is shown since address decoding for read and write operations are essentially the same.

**Non-partitioned.** A non-partitioned decode hierarchy refers to a memory organization where all cells in a given row are activated by a single word line output from the row decoder, and the organization of the sample memory system in the previous subsection, as well as the figure in the previous sidebar, are examples of this.

For very small SRAMs (i.e. 1kByte and smaller), this simple non-partitioned approach is sufficient. But as the size of the SRAM increases, several problems start becoming significant:

- 1. As the number of memory cells in an SRAM increases with increasing memory size, more and more transistors from each memory cell are connected to the row's wordlines and the column's bitlines, increasing the total capacitance resulting in an increase in delay and power consumption.

- 2. Increasing the number of memory cells result in a physical lengthening of the SRAM array, increasing the wordline wire length and its parasitic wiring capacitance.

- 3. More power is in the bitlines is wasted during each access because more and more columns are activated by a single wordline even though only a subset of these columns are actually accessed. In a non-partitioned scheme, every column will have an active memory cell, inadvertently discharging the bitlines of the unaccessed columns resulting in wasted power needed to precharge these bitlines back to their original value.

To a certain extent this problem can be mitigated by minimizing the number of columns in an array. For a fixed memory size, this can be done by increasing the number of rows accordingly. This solution is obviously very short-sighted as it will eventually produce its own problems and doesn't solve the original one. Instead, the number of columns (and rows) is used as an additional parameter that can be changed to come up with an optimal memory partitioning and hierarchy, as will be discussed later.

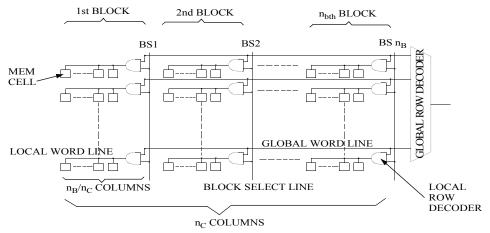

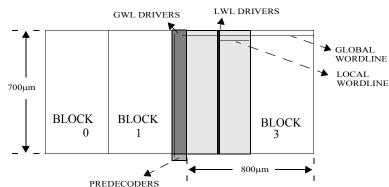

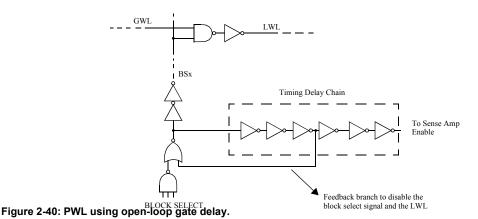

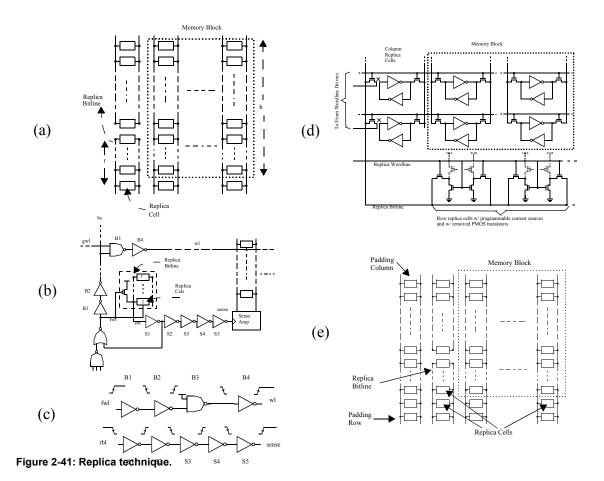

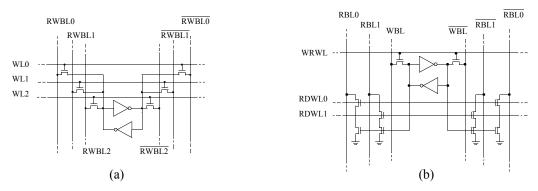

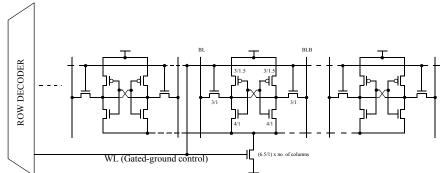

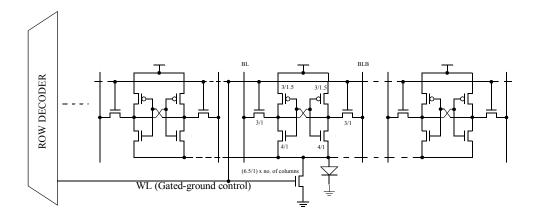

**Divided Wordline (DWL).** To solve the problems of the non-partitioned approach, the divided word line (DWL) technique was introduced by Yoshimoto [Yoshimoto1983] and is now used in virtually all SRAMs because of its usefulness and minimal disadvantages.

DWL involves dividing the memory array along the top level word line (called the global wordline or GWL) into a fixed number of blocks. Instead of enabling all the cells within a row, the global word line is ANDed with a block select signal (derived from another subset of the input address) and asserts a local wordline (LWL). Only cells connected to this asserted local WL are enabled.

This DWL structure is shown in Figure 2-10 where the memory array is divided into  $\eta_B$  blocks. Assuming a total of  $\eta_C$  columns, each block contains  $\eta_C/\eta_B$  columns. Since only a fraction of the total cells (1/ $\eta_B$  to be exact) are connected to an asserted local wordline and consequently activated during an access, the total power consumed in the bitlines is reduced drastically to roughly  $1/\eta_B$  of the original. This value is exactly  $1/\eta_B$  for reads since the nature of wasted power is similar to the power consumed by the bitline read access, while the savings is less for a write access because of the higher power consumed by accessed bitlines during a write.

Additionally, since less cells are connected to the local wordlines, the power and delay will be significantly less. The global wordline also only needs to drive the wire capacitance and the much smaller number of local wordline decoders. The total wordline delay (the sum of the GWL and LWL delays), for the DWL, compared to the non-partitioned implementation, will be much less for moderately sized SRAMs and above.

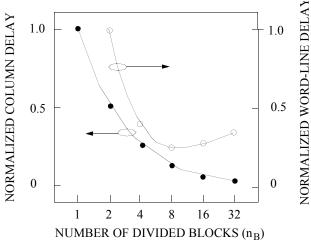

Figure 2-11 shows the effect in column power and wordline delay of changing the number of blocks for an 8k x 8 SRAM. Although this may seem like a small SRAM by today's standards, it is still useful as a basic building block for wide caches. For example, a 128-bit cache can employ sixteen of these small SRAMs resulting in a 128kB cache, which is getting close to the typical size of an L2 cache. The figure shows that even though column power can be continuously reduced by increasing the number of blocks, the benefit to the wordline delay lessens and it reaches a point where it starts to adversely affect the delay.

The implementation of the DWL technique is simple, requiring only additional block select circuits and LWL decoders that can be made simple since they drive less cells. For the 8k x 8 SRAM here, dividing the array into 8 blocks ( $n_B = 8$ ) results in only a 4-6% increase in area while resulting in very significant power (near 800%) and speed (about 300%) gain.

Figure 2-10: An SRAM using the divided word line (DWL) address decoding technique. (Figure taken from Yoshimoto1983).

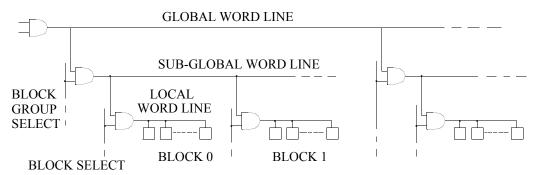

**Hierarchical Word Decoding (HWD).** A logical extension of the DWL scheme is a technique called hierarchical word decoding (HWD) [Hirose1990], and is shown in Figure 2-12.

As the memory size increases, maintaining a DWL structure requires an increase in the number of blocks, which results in an increase in the GWL capacitance since more wordline decoders tap into the GWL. HWD simply introduces additional levels of hierarchy into the decoding scheme to more efficiently distribute capacitances, with the number of levels determined by the total load capacitance of the word decoding path. At 256kB, the difference between DWL and HWD is insignificant, but a 4Mb SRAM using the HWD architecture can reduce delay time by 20% and total load capacitance by 30%.

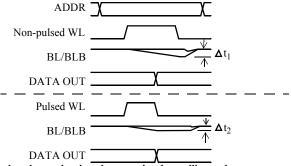

**Pulsed Word Line**. Early SRAM implementations asserted the wordlines for a significant fraction of the cycle time. The wordlines are typically asserted early (after the decode delay) and deasserted late in the access. This method, while functionally correct, is inefficient. [Amrutur1994] For a read access, wordline assertion causes one of the bitline pair to be pulled down, creating a voltage differential across the bitlines. When a sufficient differential exists (the exact value will depend on the process technology and the offset voltage of the sense amplifier), a sense amp is used to amplify this differential and speed up sensing. At this point, any

Figure 2-11: Graph showing effect of the number of blocks, nB, in the memory's column power and word line delay (Graph taken from Yoshimoto1993).

Figure 2-12: Hiearchical word decoding (HWD) architecture showing three levels of decoding. (Picture taken from Hirose1990].

additional differential developed across the bitlines, as a result of the continued assertion of the wordline, will not significantly speed up sensing and will require more power and precharge time.

Most SRAMs now use some kind of pulsed word line, where the wordline is allowed to assert only for a small amount of time necessary to create a sufficient bitline differential voltage after which it is turned off. This technique prevents the development of bitline voltage differential more than is necessary, reducing the power consumed during the precharge process.

The width of the pulsed wordline is controlled either using static delays (where the wordline is turned off after a certain number of delays fixed at design time or fixed by special delay circuitry during built-in self-test), or using some feedback taken from information extracted from the circuits (to be discussed in detail later).

Figure 2-13 shows timing diagrams for a system with and without the pulsed-wordline scheme. As can be seen from the diagram, output data from both systems are produced almost at the same time, but continued assertion of the wordline for non-PWL schemes result in larger differentials developed across the bitline, serving only to consume additional power during precharge.

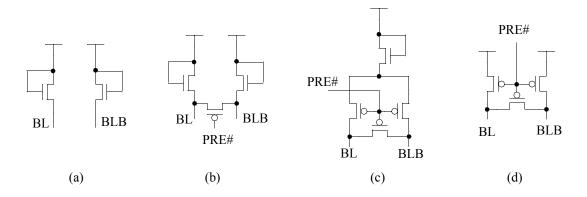

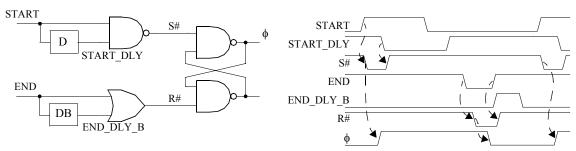

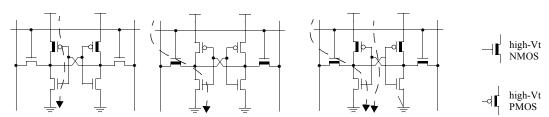

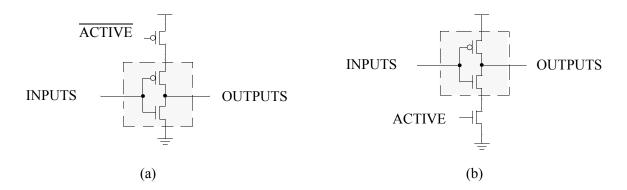

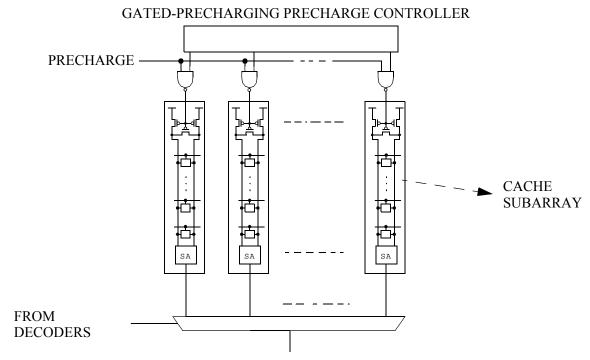

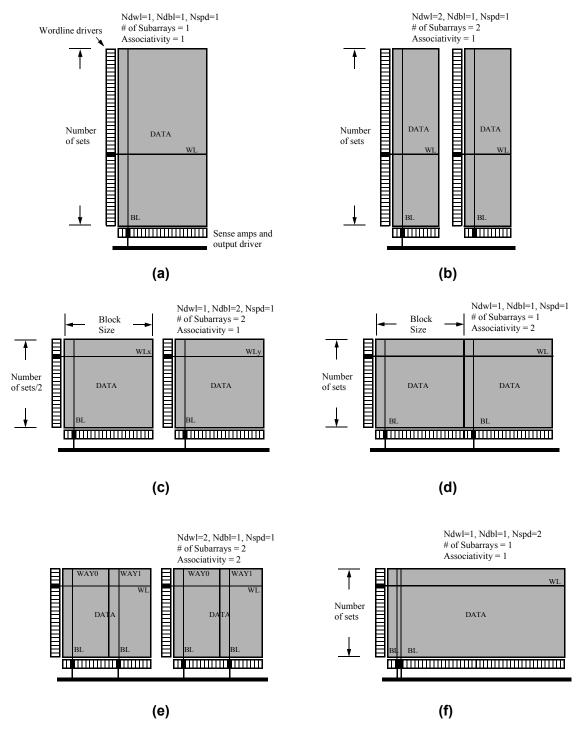

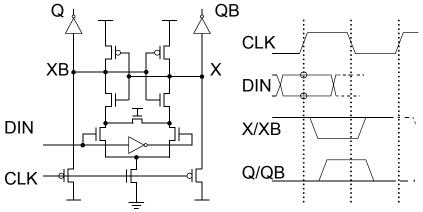

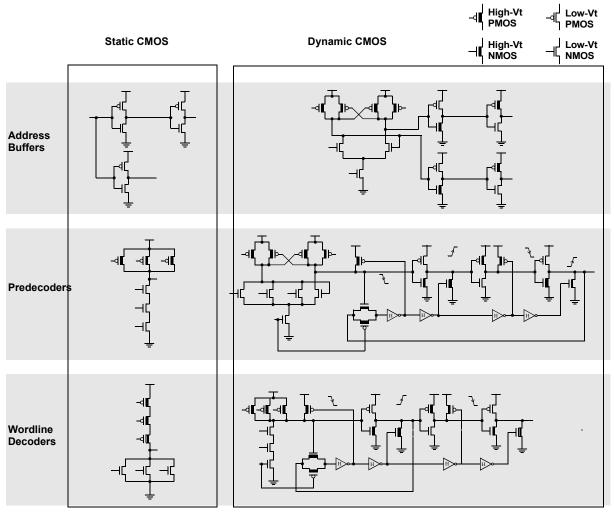

**Physical Decoder Implementation.** With the division of the decoder into multiple levels of hierarchy (i.e. predecoders, global wordline decoders, local wordline decoders, column decoders, block decoders, etc.), different circuit styles and implementations can be used for each decode level depending on different factors including power, speed, area, complexity and layout requirements, among others.

The relative importance of these specifications vary within the decoder hierarchy because of the presence of different constraints. As a quick example, predecoders can use relatively power-hungry circuit styles, which is not true of the local wordline decoders simply because of the much larger number of LWL decoders in the circuit compared to predecoders.

Numerous research have been done to optimize the decoders in the entire hierarchy from the initial predecoder to the final LWL decoder. [Yoshimoto1983, Yamamoto1985, Sasaki1988, Aizaki1990,

Figure 2-13: Timing diagrams showing pulsed and non-pulsed wordline schemes.

Nakamura1997, Mai1998, Nambu1998, Osada2001]. Because of space limitations, only a small (but very relevant and proven optimal) subset of these circuits will be discussed here in detail.

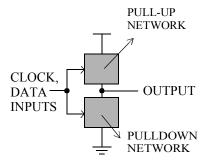

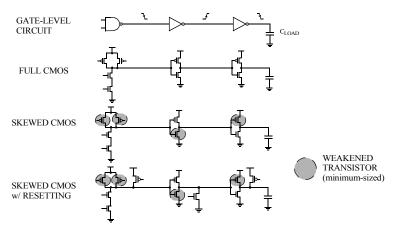

**Digital Logic Styles.** Before proceeding, it is beneficial to discuss different logic circuit styles and where in the decode hierarchy each style is suited to. CMOS logic circuits can be generalized by the circuit shown in figure 2-14. The figure shows an output node connected to Vdd by a pullup network, and to ground by a pulldown network, where both networks are controlled by inputs (e.g. data and/or a clock signal).

The pullup network consists of a combination of PMOS transistors that conditionally connects the output to Vdd, while the pulldown network consists of a combination of NMOS transistors that conditionally connects the output node to ground. Although the inputs and the clock signal are shown to be provided to both the pullup and pulldown networks, they may or may not be utilized depending on the specific implementation.

**Static CMOS.** The first logic style we review are static CMOS or full-CMOS circuits, i.e. at steady state, there will always exist a relatively low-impedance path from the output to either Vdd or ground depending on the logic output. This distinction will be clearer when dynamic CMOS is discussed, where we will see that some logic values depend on the charge stored within parasitic capacitances in the gates themselves.

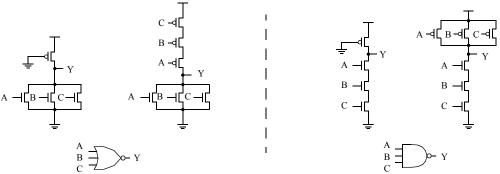

Static CMOS is the easiest and most robust implementation since there are a lot less variations and problems associated with the design. The two variations of the static CMOS style are the static or active load and the full-CMOS styles. 3-input NAND and NOR gates for both styles are shown in Figure 2-15. The main difference of the two styles is the implementation of the pullup net (notice that the pulldown networks are exactly the same). The full-CMOS implementation utilizes a pullup net that is the complement of the pulldown (i.e. parallel connections become series, and vice versa) while the active-load uses an always-on PMOS transistor pulling up the output constantly to Vdd.

The main results of this difference are the following:

- 1. Typically smaller area for the active load because of less transistors.

- 2. The total active-load gate capacitance for each input is typically less than half of the full-CMOS implementation. This results in a smaller logical effort, making this gate easier to drive.

Figure 2-14: Generalized logic circuit.

3. The always-on PMOS will result in significant static power consumption whenever the pulldown net is enabled. In addition, the logic low voltage will not reach the full Vdd value because of the pulling up effect of the PMOS and how it fights the pulldown network. The exact output value will depend on the relative strengths of the transistors.

Speed and power comparisons of these circuits are interesting [Sasaki1988]. Given equal capacitance characteristics, the PMOS-load circuit will produce about 8% more delay than the full-CMOS decoder (because the PMOS-load will tend to fight the pulldown net, producing delay). But the capacitance characteristics of these circuits in practice will usually be different and will tend to make the PMOS-load faster (about 15% faster). In addition, average currents in their decoder (which directly relates to power consumption) show that even though the PMOS-load consumes DC current, there exists a crossover point where cycle times becomes smaller and AC current becomes more dominant. It must be stressed, though, that these current numbers are greatly influenced by the sequencing and control of the gates.

Because of these factors, the speed comparison will be releveant regardless of how the memory is controlled, while the power comparison needs to be studied on a case to case basis to take into account the specific characteristics of a system. For example, a PMOS-load used with pulsed-wordline technique will be active for a smaller amount of time than if a non-PWL technique was used. This makes active-load circuits feasible for use in LWL decoders using PWL since a gain in speed is achieved compared to a full-CMOS system while at the same time not wasting too much power (especially since only a very small fraction of LWL decoders are active at the same time).

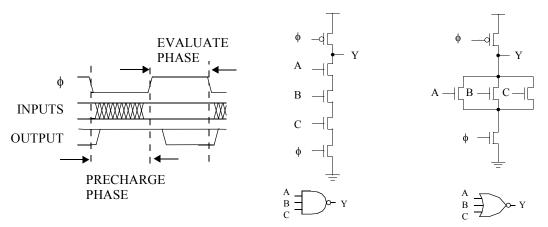

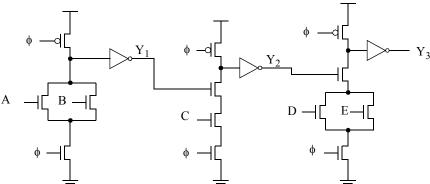

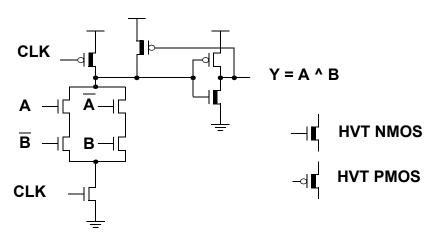

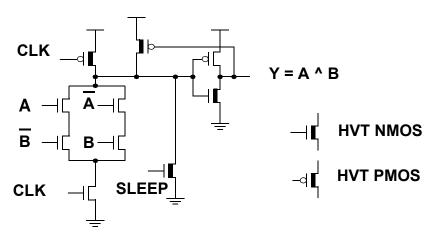

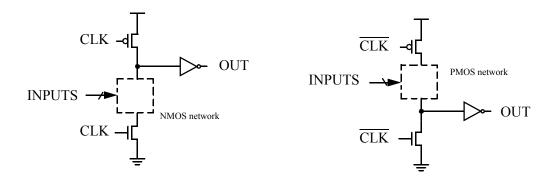

**Dynamic CMOS.** One of the main objectives of dynamic CMOS is to minimize the capacitance of the logic gate inputs. At its simplest, this is done by implementing only either the pulldown or pullup network. Further discussions will involve only dynamic CMOS with pulldown network, as the use of pullup networks are useful only in special applications because of the better characteristics of NMOS transistors compared to their PMOS counterparts.

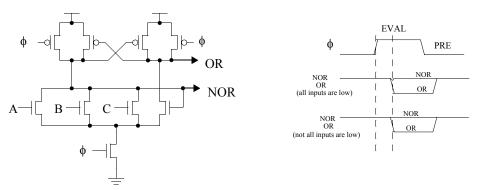

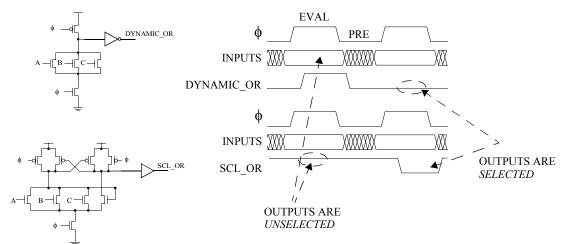

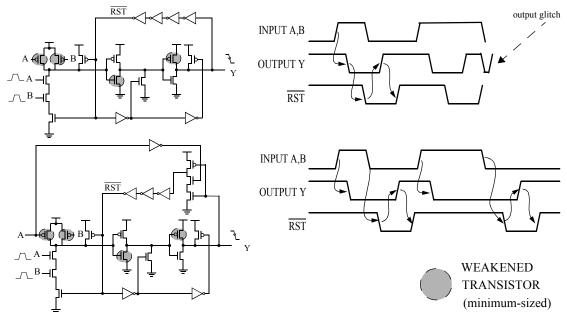

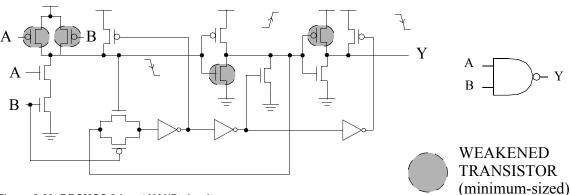

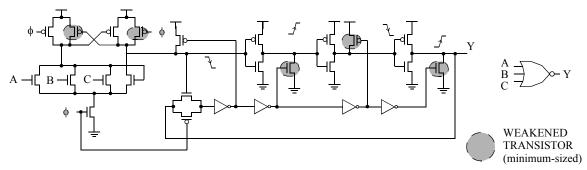

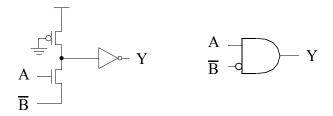

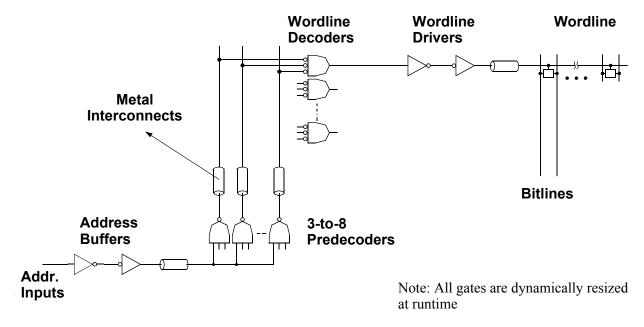

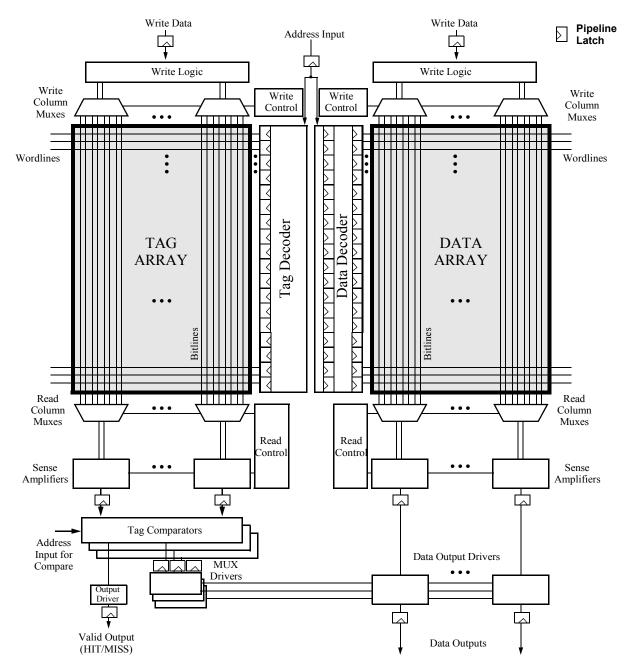

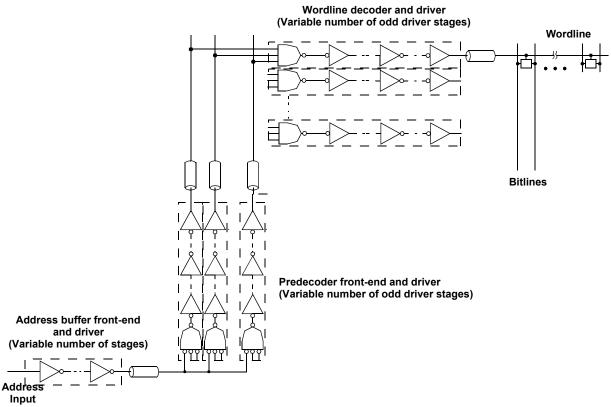

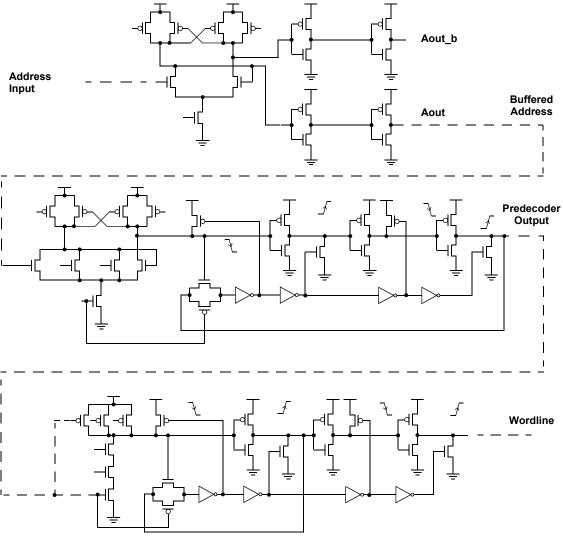

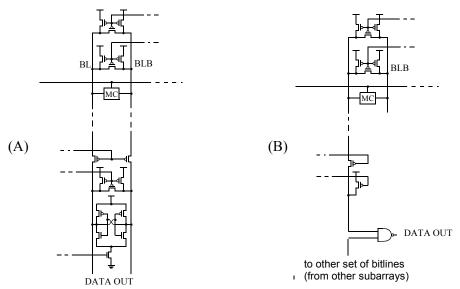

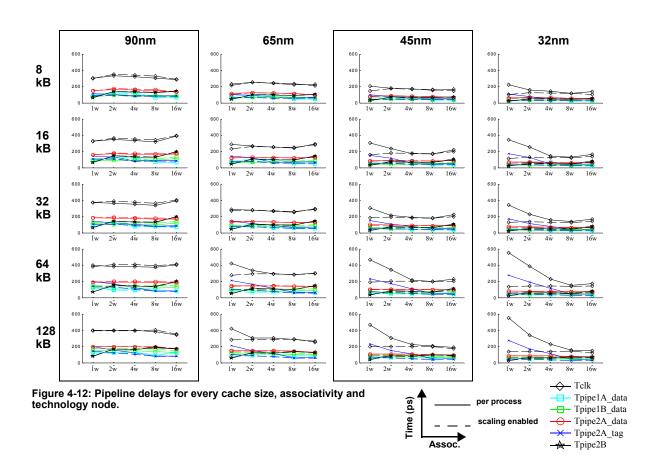

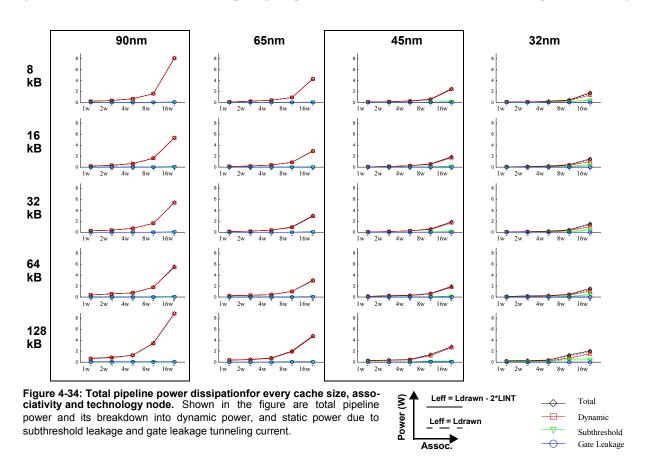

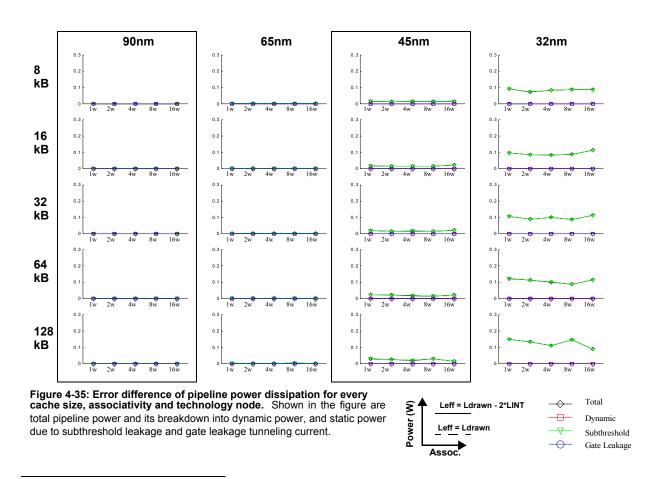

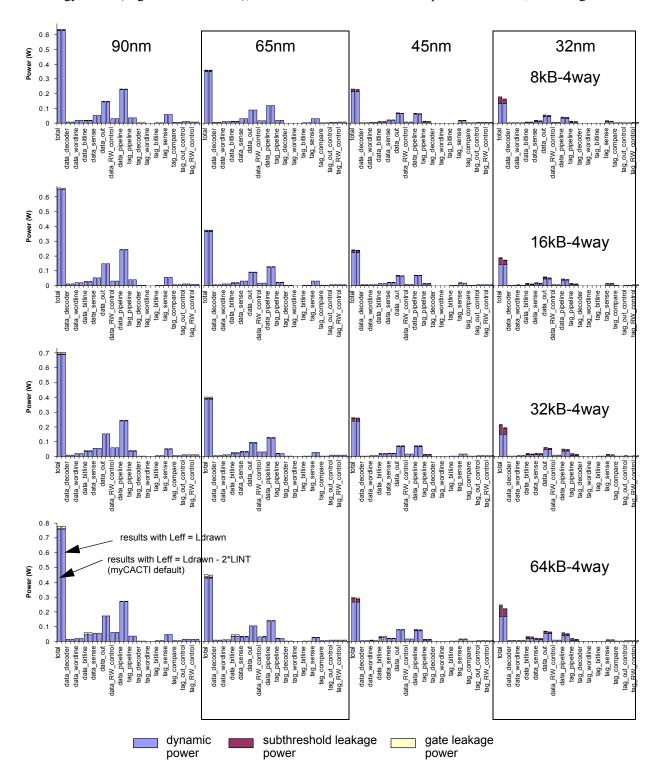

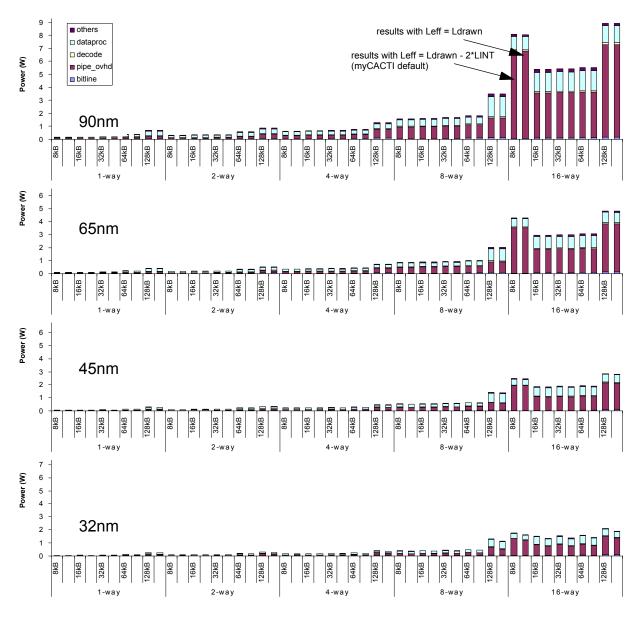

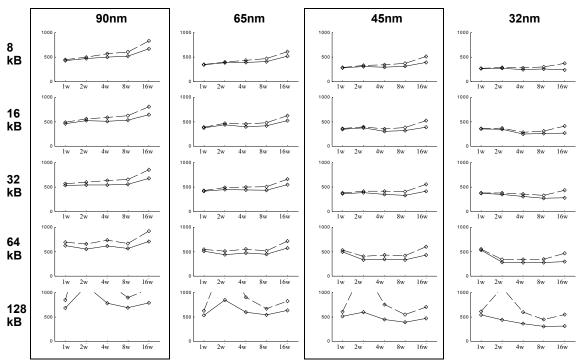

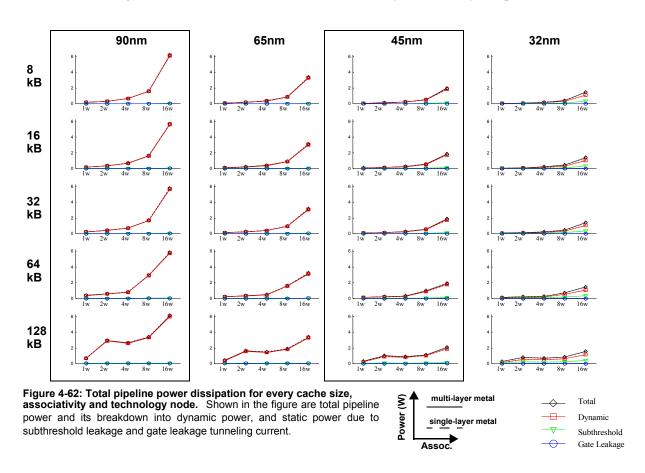

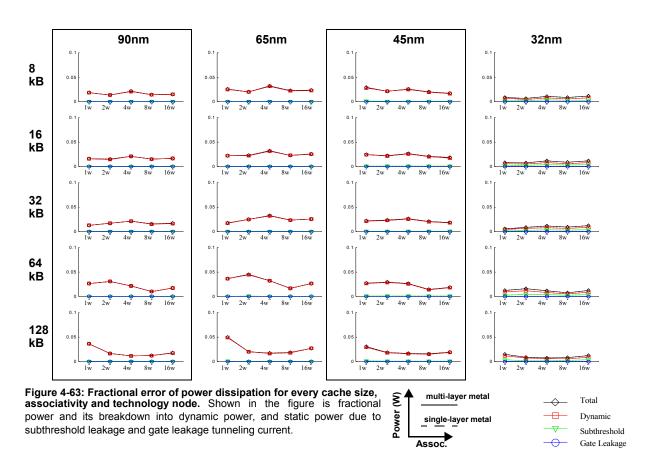

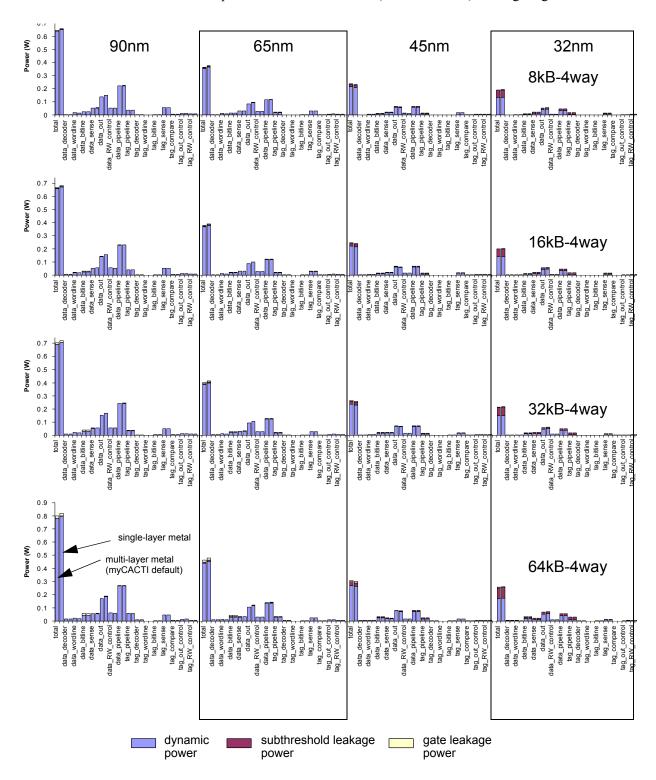

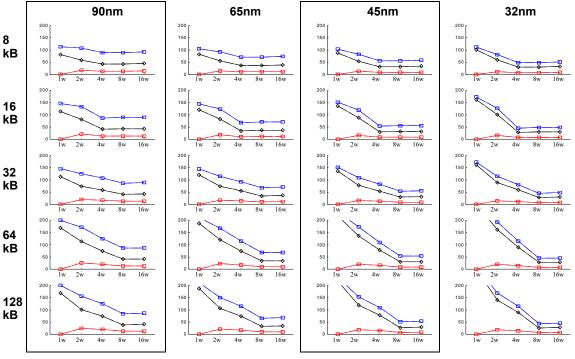

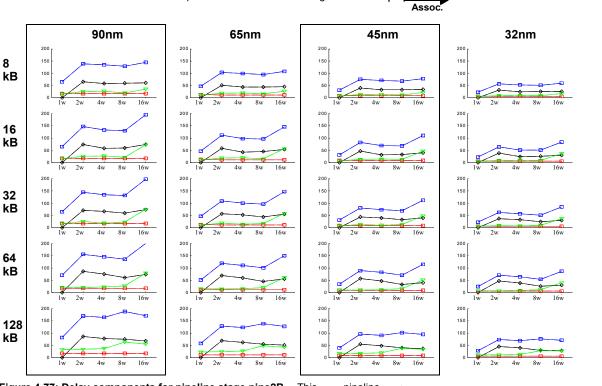

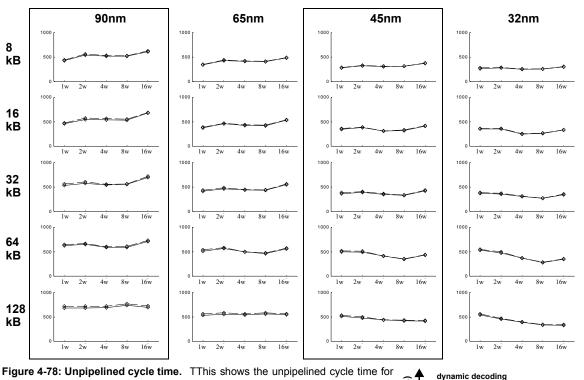

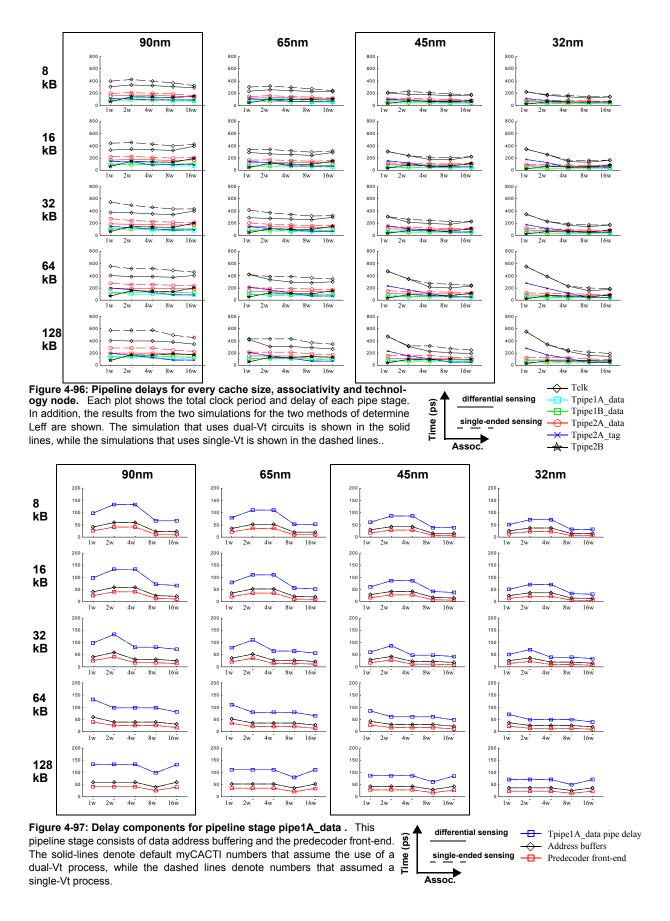

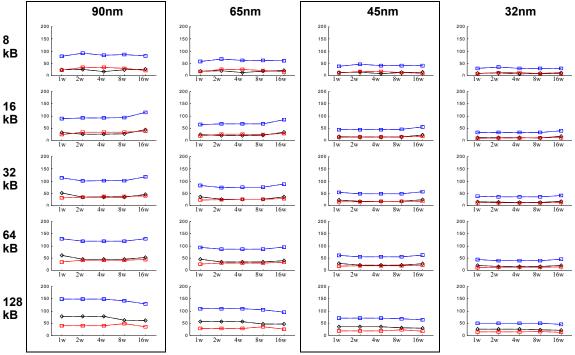

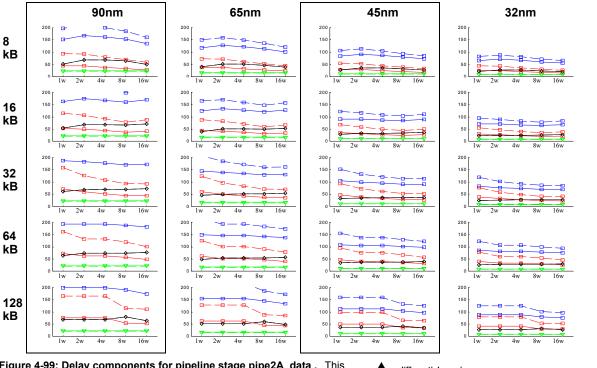

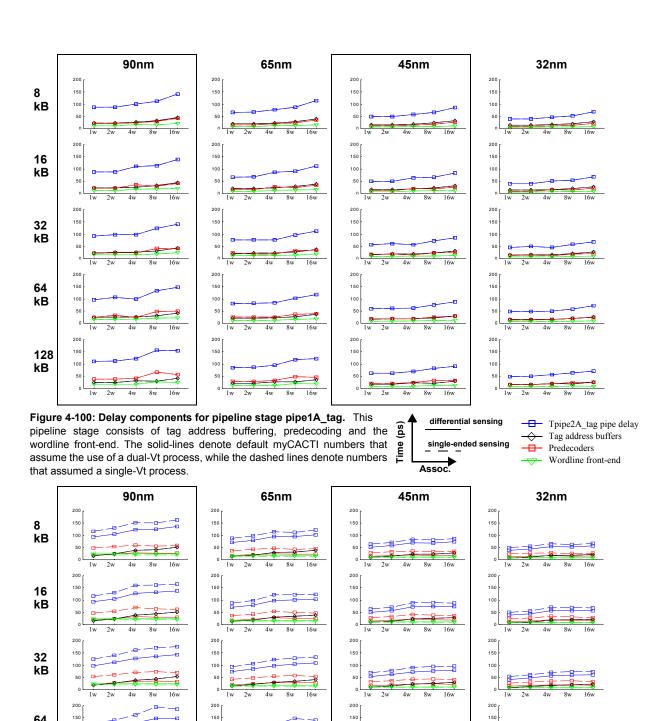

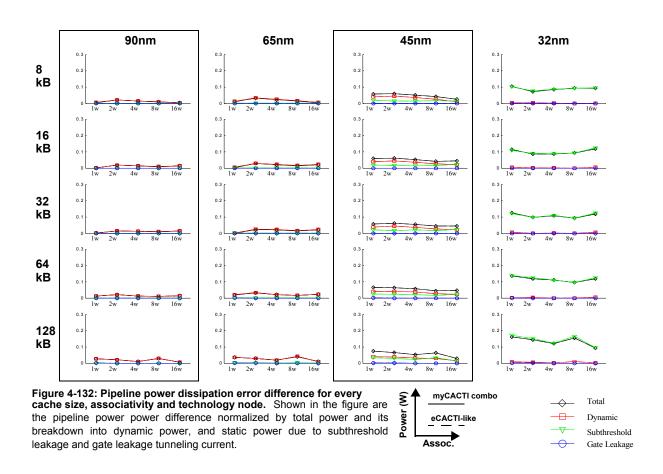

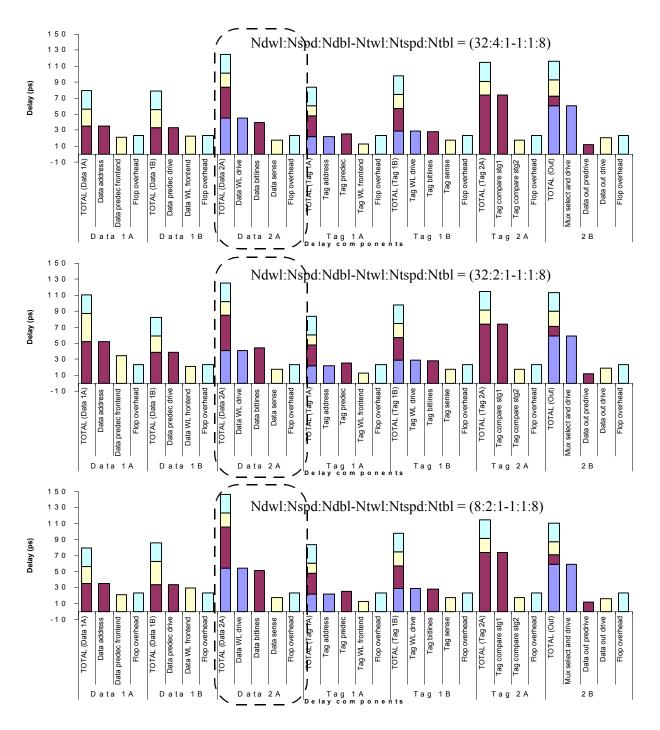

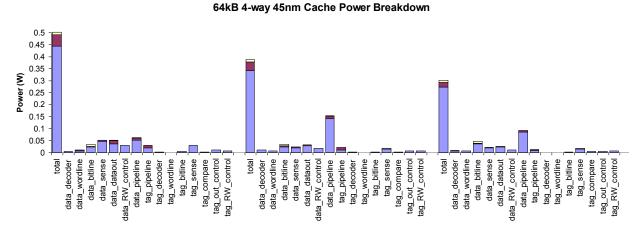

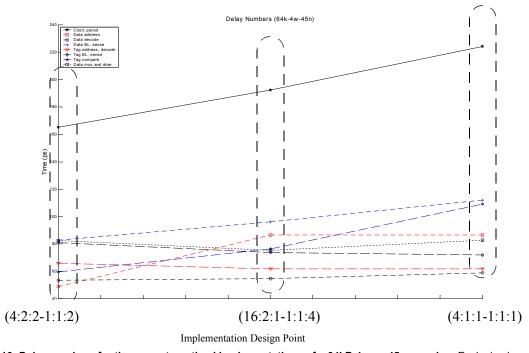

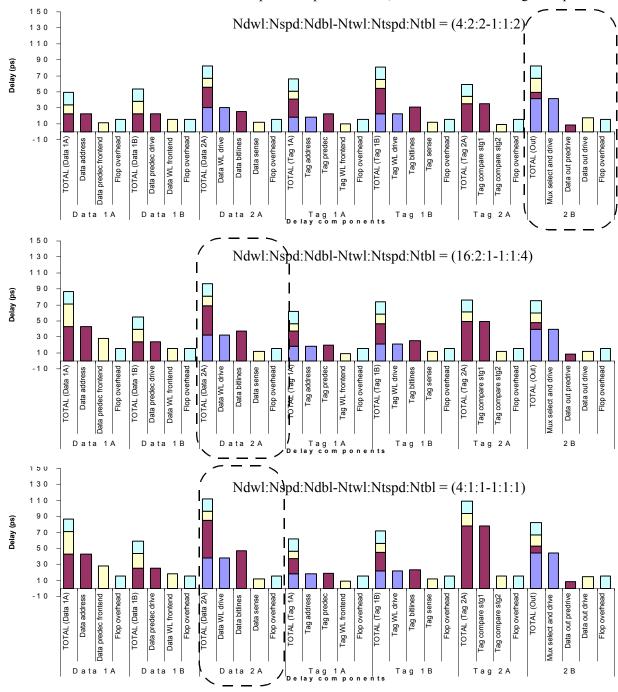

Figure 2-15: Active-load and full-CMOS circuit styles for 3-input NOR and NAND gates.