## ABSTRACT

Title of Document:STUDY OF THE IMPACT OF HARDWARE<br/>FAILURES ON SOFTWARE RELIABILITYBing Huang, Doctor of Philosophy, 2006

Directed By:

Professor Joseph B. Bernstein Professor Carol S. Smidts Reliability Engineering

Software plays an increasingly important role in modern safety-critical systems. Reliable software becomes desirable for all stakeholders. Typical software related failures include software internal failures, input failures, output failures, support failures and multiple interaction failures. This dissertation provides a methodology to study the impact of hardware support failures on software reliability.

The hardware failures we are focusing on in this study are semiconductor device intrinsic failures that are directly related to software execution during device operation. The software execution on hardware devices, in essence, is a series of 0 and 1 signal alternations for the inputs of hardware components. Such signal alternations lead to voltage changes and current flows in the microelectronic hardware device, which serve as electrical stresses on the device and may lead to physical failures. The failure mechanisms include Hot Carrier Injection (HCI), Electromigration (EM), and Time Dependent Dielectric Breakdown (TDDB). During device operation such hardware failures could propagate to circuit level in the form of signal delays, changes of circuit functionality, and signals stuck at a logic value (0 or 1), which could further propagate into the software layer and affect the reliability of the software.

The proposed methodology is divided into three parts: (i) analysis of the manifestations of permanent failures on circuit elements (logic gates, flip-flops, etc.), (ii) development of reliability models for the circuit elements as functions of the software execution, and (iii) calculation of failure probability distributions of the hardware circuit elements under the software execution.

The methodology is applied to a comprehensive case study, targeting all the CPU registers and ALU logic gates of a computer system based on the Z80 microprocessor. About 120 different types of failure manifestations are observed, and more than 250 reliability models for the different types of failure manifestations and circuit elements are developed. Such models allow us to calculate the failure probability distributions of the CPU registers and ALU gates of the Z80 computer system under the software execution. We also extend the methodology and the case study to the consideration of transient failures, also known as Single Event Upsets (SEUs).

## STUDY OF THE IMPACT OF HARDWARE FAILURES ON SOFTWARE RELIABILITY

By

Bing Huang

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2006

Advisory Committee: Professor Joseph B. Bernstein, Co-Chair/Advisor Professor Carol S. Smidts, Co-Chair/Advisor Professor Mohammad Modarres Professor David L. Akin Professor Patrick F. McCluskey © Copyright by Bing Huang 2006

## Dedication

This dissertation is dedicated to my beautiful wife Hui. Her endless support facilitated my work so much during the past six years. Especially in the final stage of my PhD study, while taking care of our newborn son, she made great efforts to make my research as smooth as possible.

I would also like to thank our son Raine, who entered the world while I worked on this dissertation. His smile makes our life so much nicer.

## Acknowledgements

I am grateful for the assistance of so many people in producing this work.

First of all, I would like to thank Dr. Bernstein and Dr. Smidts for their support and guidance during my graduate studies. Their knowledge and wisdom guided me to establish the framework of this dissertation work. Their patience with me when I was struggling with some technical problems gave me great relief. They also taught me a lot of things about everyday life during the past several years.

I would like to thank Dr. Manuel Rodriguez for his inspiring discussions, which led to some important mathematical models in this work. He also worked with me on many details of this dissertation.

I would also like to thank Dr. Ming Li and Dr. Xiaojun Li for their help during the early stages of this work, and their insightful comments, which were invaluable for the completion of this dissertation.

Furthermore, I would like to thank other talented researchers in our group, which include Jin Qin, Xiaohu Zhang, Hu Huang, Yuan Wei, and Dongfeng Zhu, for their help and support to this work.

Finally, I would like to thank Dr. Mohammad Modarres, Dr. David Akin, and Dr. Patrick McCluskey for serving on my dissertation committee.

# Table of Contents

| Dedication                                                                 | . ii       |

|----------------------------------------------------------------------------|------------|

| Acknowledgements                                                           | iii        |

| List of Tables                                                             | vii        |

| List of Figures                                                            | <i>iii</i> |

| Chapter 1 Introduction                                                     | . 1        |

| 1.1 Statement of Problem                                                   | . 1        |

| 1.2 Contents of the Dissertation                                           | 15         |

| 1.3 Summary of Contributions                                               | 17         |

| Chapter 2 Hardware Failures                                                | 19         |

| 2.1 Permanent Physical Failures                                            | 19         |

| 2.1.1 Hot Carrier Injection Failure Mechanism                              | 21         |

| 2.1.2 Electromigration Failure Mechanism                                   | 23         |

| 2.1.3 Time Dependent Dielectric Breakdown Failure Mechanism                | 24         |

| 2.2 Impact on Higher Hardware Levels                                       | 25         |

| Chapter 3 Methodology for the Analysis of Permanent Failure Manifestations | 28         |

| 3.1 Analysis of Failure Manifestations                                     | 30         |

| 3.1.1 Calculation of Failure Rates and Characterization of Stress Patterns | 30         |

| 3.1.2 Identification of Failure Manifestations                             | 39         |

| 3.2 Development of Reliability Models                                      | 49         |

| 3.3 Calculation of Failure Probabilities                                   | 61         |

| 3.3.1     | Calculation of the Hardware Usage Profile                     | 61  |

|-----------|---------------------------------------------------------------|-----|

| 3.3.2     | Calculation of the Hardware Failure Probability Distributions | 64  |

| Chapter 4 | Calculation of Failure Probabilities                          | 67  |

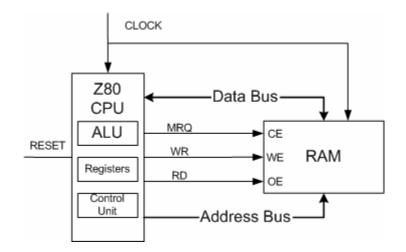

| 4.1 S     | System Description                                            | 67  |

| 4.2 A     | Analysis of Failure Manifestations                            | 70  |

| 4.2.1     | Analysis of the CPU Register Bits                             | 70  |

| 4.2.2     | Analysis of Fault Models for Combinational Logic Elements     | 75  |

| 4.3 L     | ifetime Model Parameters Calculation                          | 80  |

| 4.3.1     | TDDB Lifetime Model Prefactor                                 | 82  |

| 4.3.2     | HCI Lifetime Model Prefactor                                  | 83  |

| 4.3.3     | EM Lifetime Model Prefactor                                   | 84  |

| 4.4 U     | Jsage and Failure Probability Distribution Profiles           | 85  |

| Chapter 5 | Transient Failures and Models                                 | 101 |

| 5.1 T     | ransient Failures                                             | 101 |

| 5.1.1     | Transient Failure Introduction                                | 101 |

| 5.1.2     | Impact on Higher Hardware Levels                              | 102 |

| 5.2 F     | Failure Rate Calculation                                      | 103 |

| 5.2.1     | Heavy Ions Induced SEUs                                       | 103 |

| 5.2.2     | Protons Induced SEUs                                          | 107 |

| 5.2.3     | Neutrons Induced SEUs                                         | 108 |

| 5.3 E     | Extension of Permanent Failure Probability Results            | 111 |

| Chapter 6 | Summary and Future Research                                   | 116 |

| 6.1 S     | Summary                                                       | 116 |

| 6.2       | Conclusions                                | 118   |

|-----------|--------------------------------------------|-------|

| 6.3       | Future Work                                | 120   |

| Appendi   | x A Failure Manifestations for Logic Gates | 121   |

| Glossary  | r                                          | 128   |

| Bibliogra | aphy                                       | . 130 |

# List of Tables

| Table 3.1 Notation of the failure manifestations    47                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.2 Failure rate models of the AND2_1 gate per failure manifestation                                                                                         |

| Table 4.1 Reliability models for the flip-flop circuit element of the Z80 CPU74                                                                                    |

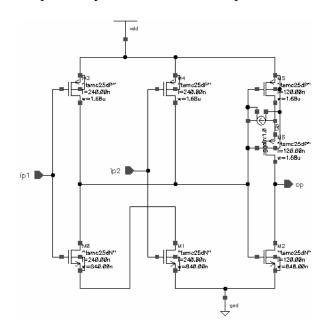

| Table 4.2 Different type of logic gates used in the ALU of the Z80 CPU                                                                                             |

| Table 4.3 Reliability models for logic gates used in the ALU                                                                                                       |

| Table 4.4 Index of user programmable registers    86                                                                                                               |

|                                                                                                                                                                    |

| Table 5.1 Parameters for the calculation of SEU rates for the HEO orbit profile 112                                                                                |

| Table 5.1 Parameters for the calculation of SEU rates for the HEO orbit profile 112Table A.1 Z80 ALU logic gates – Results of SPICE simulations for HCI stress 121 |

| -                                                                                                                                                                  |

# List of Figures

| Figure 2.1 Different abstraction levels of circuit design                         | . 25 |

|-----------------------------------------------------------------------------------|------|

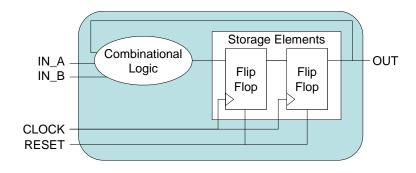

| Figure 2.2 Example of a RTL Design                                                | . 27 |

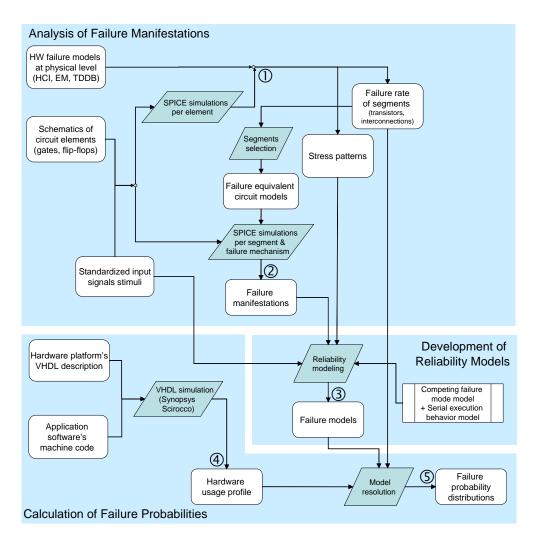

| Figure 3.1 Methodology for the analysis of permanent failure manifestations       | . 30 |

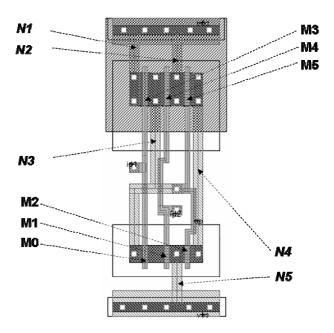

| Figure 3.2 Circuit Layout of an AND2_1 logic gate                                 | . 33 |

| Figure 3.3 Schematic of the AND2_1 logic gate                                     | . 33 |

| Figure 3.4 Asynchronous input signals                                             | . 35 |

| Figure 3.5 Asynchronous and synchronous (clock) input signals                     | . 35 |

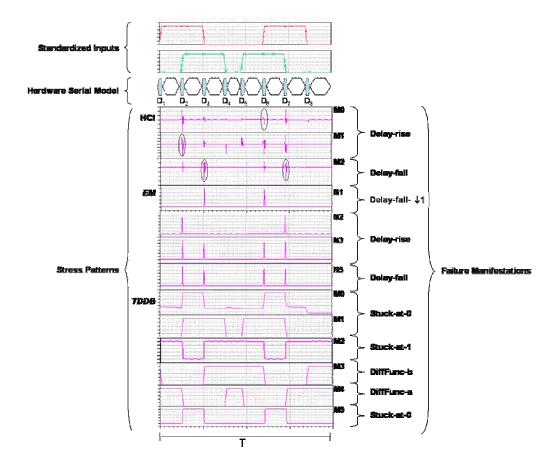

| Figure 3.6 Stress patterns examples for HCI, EM and TDDB in the AND2_1 gate       | . 37 |

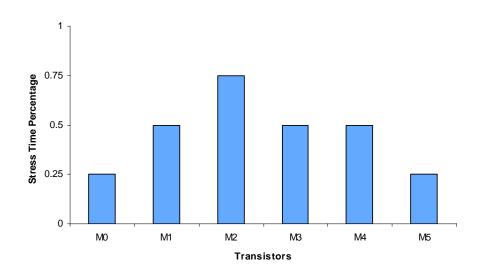

| Figure 3.7 Relative HCI failure rates of transistors                              | . 40 |

| Figure 3.8 Relative EM failure rates of interconnections                          | . 40 |

| Figure 3.9 Percentage of time a transistor suffers from TDDB stress               | . 41 |

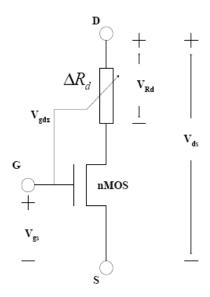

| Figure 3.10 Failure equivalent circuit model for HCI mechanism                    | . 42 |

| Figure 3.11 Failure equivalent circuit model for EM mechanism                     | . 42 |

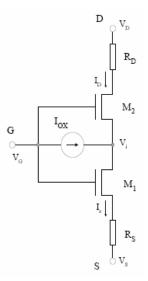

| Figure 3.12 Failure equivalent circuit model for TDDB mechanism                   | . 43 |

| Figure 3.13 AND2_1 layout with transistor M5 replaced by the TDDB failure         |      |

| equivalent circuit model                                                          | . 45 |

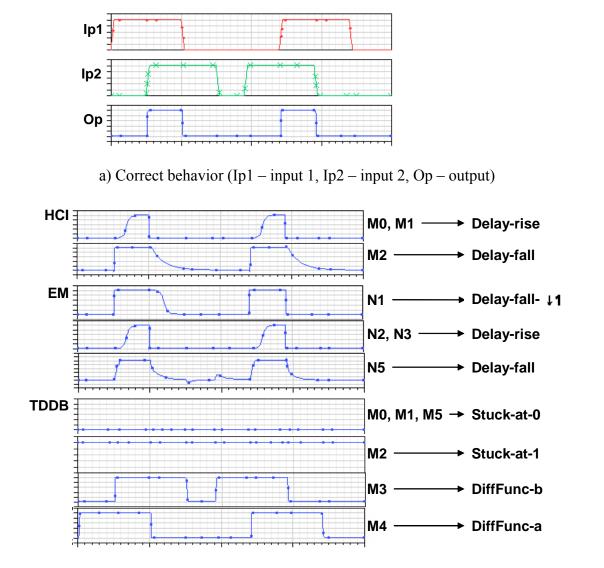

| Figure 3.14 Failure manifestations of the AND2_1 logic gate due to HCI, EM and    |      |

| TDDB stresses in its circuit segments                                             | . 46 |

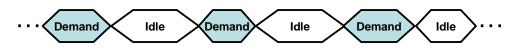

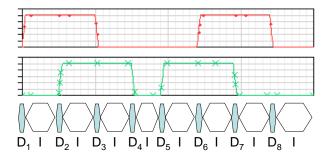

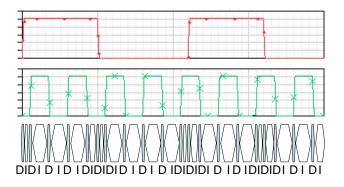

| Figure 3.15 Hardware serial model during software execution                       | . 53 |

| Figure 3.16 Examples of the hardware serial model under a software execution usin | ng   |

| the Standardized Inputs                                                           | . 53 |

| Figure 3.17 Stress patterns using the Standardized Inputs                                | . 55 |

|------------------------------------------------------------------------------------------|------|

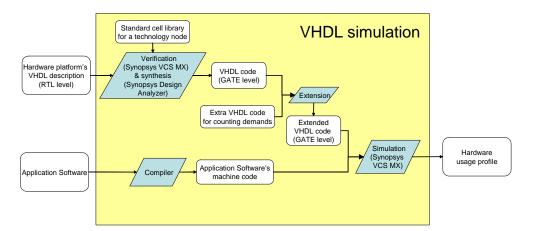

| Figure 3.18 Description of the VHDL simulation step of the methodology                   | . 62 |

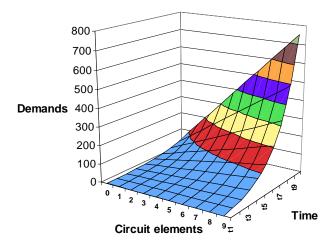

| Figure 3.19 Software-specific hardware usage profile – an example                        | . 64 |

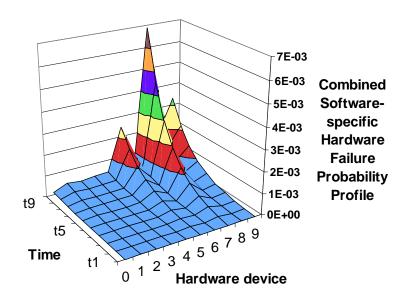

| Figure 3.20 Combined software-specific hardware failure probability profile – an         |      |

| example                                                                                  | . 66 |

| Figure 4.1 The Example Z80 Computer System                                               | . 67 |

| Figure 4.2 Modified Z80 CPU script segment                                               | . 70 |

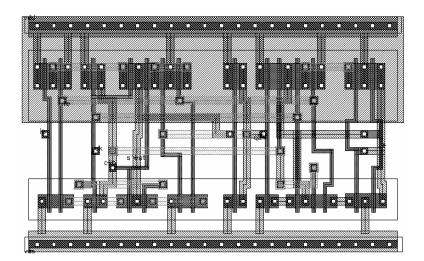

| Figure 4.3 Circuit layout for D flip-flop                                                | . 70 |

| Figure 4.4 Circuit schematic for D flip-flop                                             | . 71 |

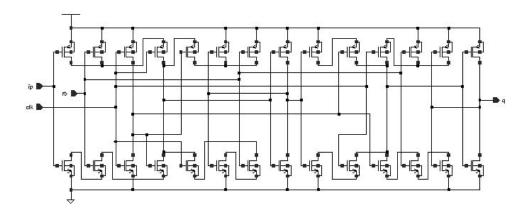

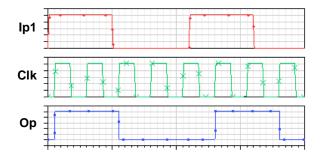

| Figure 4.5 Transient response under normal operation                                     | . 71 |

| Figure 4.6 Z80 registers bits – Results of SPICE simulations.                            | . 73 |

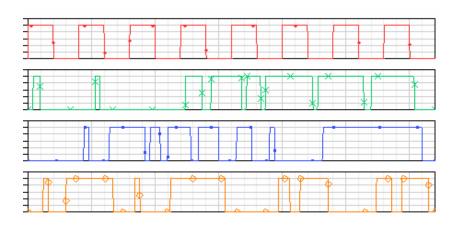

| Figure 4.7 Standardized input signal stimuli for 3-inputs gates                          | . 76 |

| Figure 4.8 Standardized input signal stimuli for 4-inputs gates                          | . 76 |

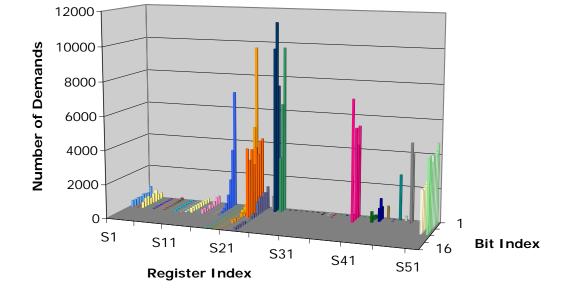

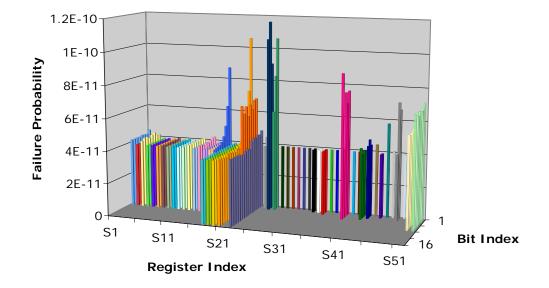

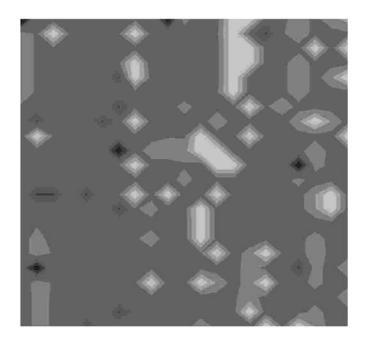

| Figure 4.9 Usage profile for all the CPU registers for the division software program     | n86  |

| Figure 4.10 Failure probability distributions for all the CPU registers for the division | on   |

| software program                                                                         | . 88 |

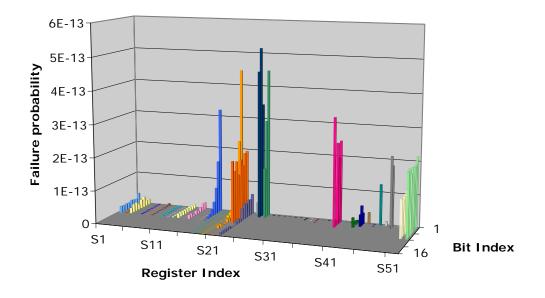

| Figure 4.11 Combined failure probability distribution for all the registers for the      |      |

| division software program                                                                | . 90 |

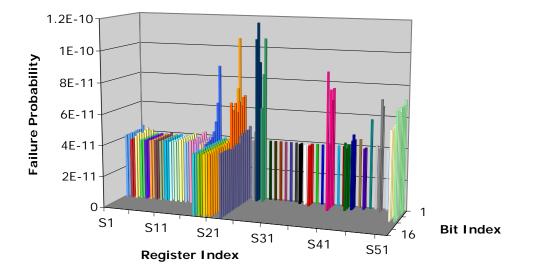

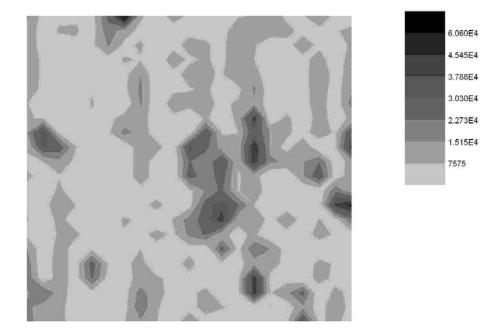

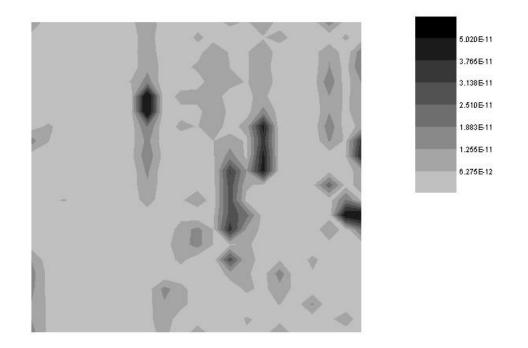

| Figure 4.12 ALU usage map for the division software program                              | . 92 |

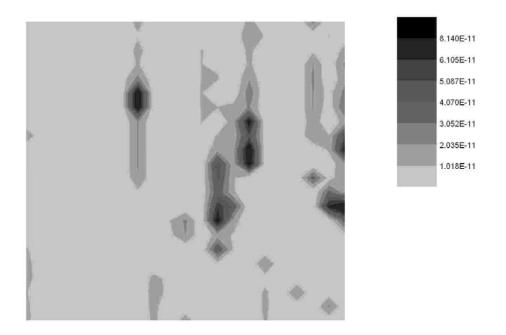

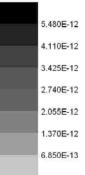

| Figure 4.13 ALU map of probability distributions of different failure manifestation      | IS   |

| for the division program                                                                 | . 93 |

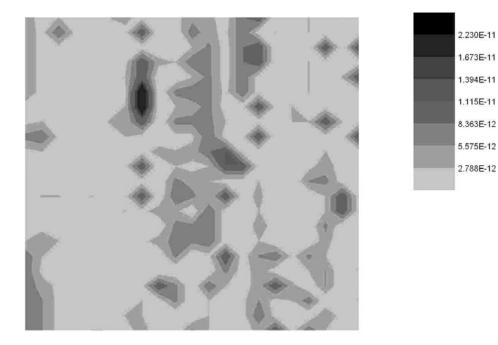

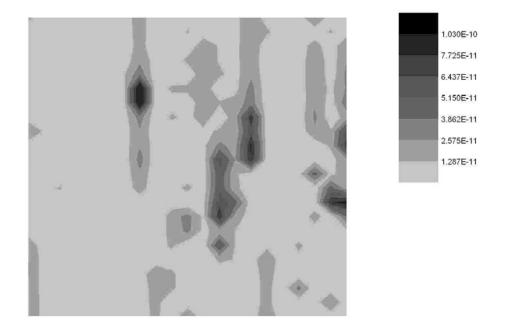

| Figure 4.14 ALU map of combined failure probability distribution for the division        |      |

| program                                                                                  | . 96 |

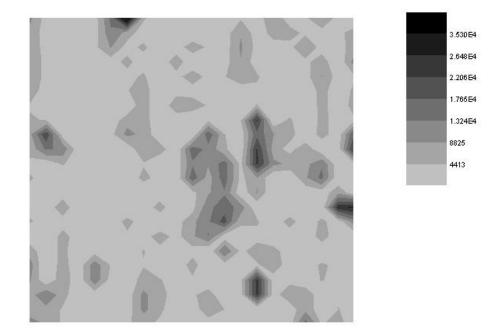

| Figure 4.15 ALU usage map for the bubble sorting program                                |

|-----------------------------------------------------------------------------------------|

| Figure 4.16 ALU map of combined failure probability distribution for the bubble         |

| sorting program                                                                         |

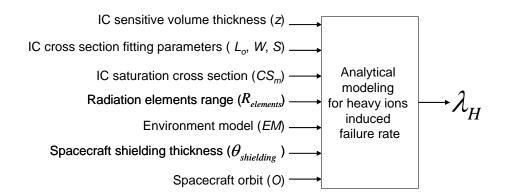

| Figure 5.1 Heavy ions SEU rate calculation                                              |

| Figure 5.2 Analytical modeling for heavy ions induced failure rate 107                  |

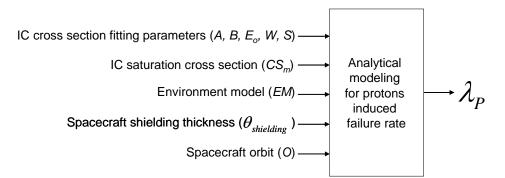

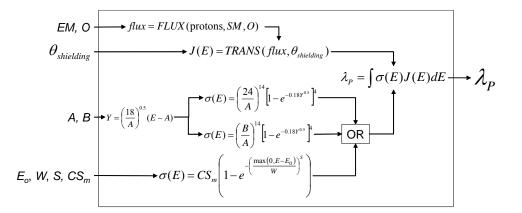

| Figure 5.3 Protons SEU rate calculation                                                 |

| Figure 5.4 Analytical modeling for protons induced failure rate 108                     |

| Figure 5.5 Atmospheric neutron SEU rate calculation                                     |

| Figure 5.6 Spacecraft nuclear reactor neutron SEU rate calculation 109                  |

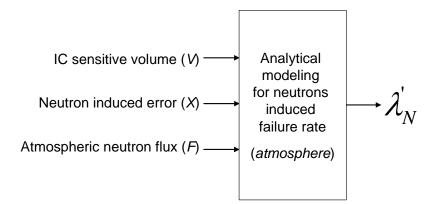

| Figure 5.7 Analytical modeling for atmospheric neutrons induced failure rate 110        |

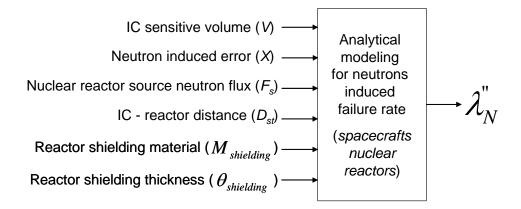

| Figure 5.8 Analytical modeling for spacecraft nuclear reactor neutrons induced failure  |

| rate                                                                                    |

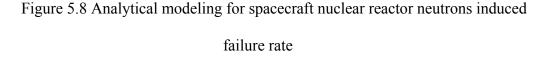

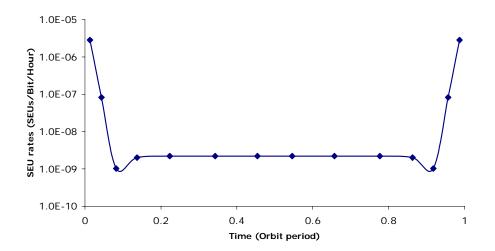

| Figure 5.9 Heavy ions and protons induced SEU rates along the HEO orbit as a            |

| function of time                                                                        |

| Figure 5.10 Total SEU rates along the HEO orbit as a function of time 113               |

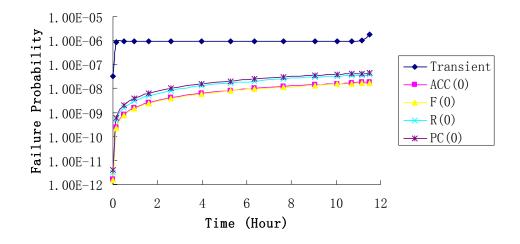

| Figure 5.11 Transient and permanent failure probabilities along the orbit as a function |

| of time                                                                                 |

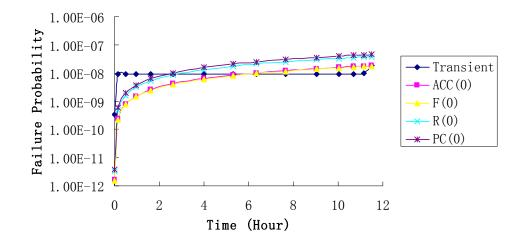

| Figure 5.12 Transient and permanent failure probabilities along the orbit as a function |

| of time, with radiation hardening techniques applied                                    |

## Chapter 1 Introduction

#### 1.1 Statement of Problem

As human technologies advance, software plays an increasingly important role in almost all systems (military, communication, transportation, space, energy, etc), and the development of software and systems that are safe and reliable becomes crucial. Ignoring software risks can lead to catastrophic consequences. About 430 people died in eight fatal accidents (1985-2003) where software was the root cause. A study by the FAA revealed that 40% of the problems in large aircrafts (1984-1994) were software related. In NASA, software has become a major risk factor in space missions and projects. Software failures account for a large percentage of problem reports for NASA projects. For one spacecraft, 33.9% of the total number of failures found during ground testing was software related. This rate was higher than any other category. Other missions, such as Magellan launched in 1989 and Voyager in 1977, experienced software failures as 19-20% of all failures. Other examples of wellknown spacecraft accidents provoked by software malfunction include: the explosion of the Ariane 5 launcher on its maiden flight in 1996, the loss of the Mars Climate Orbiter in 1999, the destruction of the Mars Polar Lander in 2000, the placing of a Milstar satellite in an incorrect and unusable orbit in 1999, and the loss of contact with the Solar Heliospheric Observatory (SOHO) spacecraft in 1998 [1]. The use of reliability methods and techniques can help significantly reduce the risk of these kinds of disasters.

Probabilistic Risk Assessment (PRA) is today the most significant and extended technique from the reliability domain. It aims at assessing, predicting and reducing the risk of failures in large technological systems such as nuclear power plants, chemical plants and aerospace systems. In NASA, PRA is required for all manned missions as well as for all missions with nuclear payload or nuclear fuel (e.g., such as the Crew Exploration Vehicle and other Moon–Mars–Beyond missions). However, current practice in PRA systematically neglects the contribution of software to the risk of failure of the system. The classical PRA methodology accounts for hardware and human interventions but does not account for software. In certain domains (such as nuclear), software has been confined to some extent to non-safety related functions. There also exists a reticence in the software safety community to use quantitative estimates of software failures. It stems essentially from the fact that software is still a new artifact. However, more and more vital functions, which in the past were controlled by human operators or hardware components, are today implemented and controlled by software. Thus, traditional PRA techniques are no longer valid and need to be improved and extended to include software reliability. Ignoring the contribution of software to system risk can lead to catastrophic consequences, such as the examples described above.

Recently, important efforts have been undertaken to incorporate software risks into the PRA technique [2, 3]. The work reported in [3] proposes a taxonomy of software failures as a first step to integrate software risks into PRA. The software is seen as an essential component of a system, which interacts with its environment through input and output interfaces. The software being executed on a computer

platform will take inputs from other subsystems (either software or hardware or humans) and produce outputs that will be used by either humans, other software or hardware. According to this view, a distinction is made between failures occurring within the software component itself and failures occurring due to the interaction between the software and its environment. This leads to the distinction of several software-related failure modes: internal failures, input failures, output failures, support failures and multiple interaction failures. Internal failures are due to the presence of "bugs" within the software code. Input failures are those out-of-bound values sent to the software that may drive correct software to provide incorrect outputs. Output failures are actually the set of out-of-bound software output behaviors that are neither due to out-of-bound input behavior nor due to internal software malfunction. These are failures that occur because of inconsistencies between specifications of the software and its downstream component. Multiple interaction failures are related to synchronization/communication problems between software processes and other system processes (software, hardware or human processes) that execute concurrently. Support failures are those software failures induced by malfunctions in the hardware support platform that the software resides on. They include failures due to competition for computing resources (deadlock, lockout) and computer platform physical failures (CPU failures, memory failures and I/O devices failures). The research work proposed in this dissertation is one component of the current work being done to characterize of this latter type of failure, i.e. computer platform physical failures, also referred to as hardware failures.

That hardware failures may lead to abnormal software behavior has been long recognized. The very first bug report described a bug-related hardware failure (On September 9, 1945, when Mark II, the Aiken Relay Calculator was experiencing problems, an investigation showed that there was a moth trapped between the points of Relay #70) [4]. More recently Iyer and Velardi [5] discovered that 35 percent of software failures in MVS systems were determined to be hardware-failure-related. Fault injection techniques have emerged as the major means to study the hardware failure phenomenon and its impact on the system [6]. Fault injection techniques, as a supplement to traditional software testing, are ideal for revealing the software and system's behaviors under abnormal hardware conditions, which may not be able to be addressed by their counterparts (such as software testing). Fault injection aims at assessing the system behavior in the presence of faults [7-9]. A key concern related to fault injection is the representativeness of the injected faults, i.e., the plausibility of the fault model with respect to actual faults [10]. In the majority of published works, the fault location, the fault type, and the time at which the fault is injected are randomly selected [7, 11]. Such a fault injection profile does not represent the actual hardware conditions in system operation. Therefore software reliability due to hardware support failures cannot be credibly assessed.

The impact of hardware failure on the software and on the system has attracted substantial attention in the field:

Kumar et al. introduced a simulation-based software model for applicationspecific dependability analysis of a system [12]. The model represents an application program by decomposing it into a graph model consisting of a set of nodes, a set of

edges and a mapping of the nodes to memory. The model simulates the execution of the program while faults are injected into the program's memory space. The authors claim that all hardware-related faults can be mapped as memory faults, but do not prove this formally. In addition, the authors do not clearly explain the types of faults injected, and how the injection is accomplished.

Todd Delong et al conducted a similar study to estimate the dependability parameters of computer systems [13]. The system hardware was modeled using a VHDL script. Stuck-at-0 and stuck-at-1 faults were injected into all the visible (programmable) processor registers. This work did not cover bit flipping or transient hardware failures. Nor did it provide the location and frequency distribution of stuckat-0 and stuck-at-1 faults.

Amendola et al conducted a study to investigate the fault behavior of a microprocessor system [14]. They studied the faults located in memory, internal registers of the processor, and busses. Single bit-flipping faults were introduced into the VHDL system model of busses, memory, and CPU. This work demonstrated whether the system could tolerate faults, but could not provide reliability information due to the lack of fault location and distribution information. Choi et al [15] conducted a similar study with identical drawbacks.

D. Gil et al performed a fault injection experiment to analyze the "error syndrome" of a microcomputer system [16]. The system under study was described using VHDL. His experiment considered different types of faults with different durations and injected them into different locations of the microcomputer system.

However there was no prior knowledge of fault frequency or the distribution of fault locations and types.

In these approaches, fault injection is used as an accelerated testing technique to speed up the occurrence of errors and failures (e.g., likely and unlikely faults are given the same probability over location and time), and so do not capture the actual environmental conditions leading to the production of the faults impacting the software. The set of real faults may not be completely covered by the injected faults. More important, reliability estimates on software failures related to a particular operational situation of the system cannot be obtained (e.g., probability that the software of a spacecraft fails due to faults in the microelectronics devices when it will be traveling to Mars following a particular trajectory). In order to use the fault injection technique to calculate reliability estimates of software failures due to hardware malfunction, it is first necessary to characterize the physical operating conditions leading to a hardware malfunction from a probabilistic viewpoint. This problem is related to the development of the so-called *software operational profiles*.

The operational profile (OP) is a quantitative characterization of the way in which a system will be used [17]. It associates a set of probabilities to the system input space, and therefore characterizes the input stimuli of the system in operation. The determination of the OP can help guide managerial and engineering decisions throughout the whole software development lifecycle [17]. For instance, the OP can assist in the allocation of resources and optimization of reviews and code inspections and act as a guideline for software testing. The OP of a system is also a major deciding factor in assessing its reliability. The OP is used to measure software reliability by testing the software in a manner such that the OP represents the system's actual use. It is also used to quantify the propagation of defects (or unreliability) through finite state machine models [2, 3]. However, determining the OP of a system is a difficult part of software reliability assessment in general [18]. The OP is traditionally built by enumerating field inputs and evaluating their occurrence frequencies. Musa pioneered a five-step approach to develop the OP [17]. His approach is based on collecting information on customers and users, identifying the system modes, determining the functional profile and recording the input states and their associated occurrence probabilities experienced in field operation. Expert opinion is normally used to estimate the hardware components-related operational profile due to the lack of field data. Musa's approach has been widely utilized and adapted in the literature to generate the operational profile. Some of these applications are summarized hereafter:

Chruscielski and Tian applied Musa's approach to a Lockheed Martin Tactical Aircraft System's cartridge support system [19]. User surveys which were generated in the format of a Questionnaire for User Interface Satisfaction, were used instead of the field data.

Elbaum and Narla refined Musa's approach by addressing heterogeneous user groups. They discovered that a single operational profile only "averages" the usage and "obscures" the real information about the operational probabilities [20]. They utilized clustering to identify groups of similar customers.

Gittens et al proposed an extended OP model composed of the process profile, structural profile and data profile. The process profile addresses the processes and associated frequencies. The structural profile accounts for the system structure, the configuration or structure of the actual application, while the data profile covers the inputs to the application from different users [21].

Different values of the environment inputs will have major effects on processing. So Musa's [17] recommended approach for identifying the environmental variables is to have several experienced system design engineers identify them by brainstorming a list of those variables that might necessitate the program to respond in different ways. Furthermore, Sandfoss [22] suggests that the estimation of occurrence probabilities could be based on figures obtained from project documentation, engineering, judgment and system development experience. According to Gittens [21], a specific operational profile should include all users and all operating conditions that can affect the system.

Musa's approach and other extended approaches all require either field data or historic usage data. They all use an assumption that field data or historic usage data cover the entire input domain. This assumption is not always true and their approaches are not always successful simply because some input data may not be available, especially for safety critical systems. At least two reasons lead to the unavailability of the entire input data spectrum. First, the system may not be widely used (e.g., a reactor control system of a nuclear power plant). Therefore, very little field and historic usage data can be obtained. Second, the field data does not cover the entire spectrum of the input domain because some conditions may be extremely rare (e.g., unexpected inputs such as hardware failures). Further, many inputs may not be visible (e.g., inputs coming from the hardware platform of the computer system). None of the related research on OP addresses the problem of characterizing the abnormal (or unexpected) software inputs delivered by the hardware devices supporting the software execution. The main contributions of the methodology proposed in this dissertation with respect to the related work on OP are the following:

- Consideration of the hardware platform. The majority of the related research on OP focuses on the characterization of environmental system data from a high-level perspective (e.g., physical data captured by sensors). This means that the boundaries of the OP are external to the computer system executing the software. Our work pushes those boundaries into the computer system itself by considering the contribution of the computer hardware platform to the OP.

- Characterization of unexpected inputs. Available methods and techniques for building the OP normally consider functional software inputs. We focus on nonfunctional inputs based on unexpected (or abnormal) data delivered by the hardware platform to the software. In other words, our interest is in hardware failures that may impact the behavior of the software components of the computer system.

- Use of well-established reliability methods and techniques. Existing approaches rely on expert opinion, field data or historical usage data to build the OP. Our methodology is built from well-known and established reliability methods and techniques from the microelectronics domain.

The proposed methodology thus constitutes a step forward in the OP research field, in the sense that it contributes to the development of comprehensive OP models providing precise estimates of the actual system's operating conditions. Such an OP is referred to as *software-specific hardware failure profile*. For a given system with a computer platform executing a particular application software, the software-specific hardware failure profile is defined by tuple <p, i, f, t> denoting the probability *p* that a hardware device *i* is affected by failure *f* at time *t*. The software-specific hardware failure profile is thus the basis to extend the use of the fault injection technique to the reliability prediction of the impact of hardware failures on software. The development of the software-specific hardware failure profile requires that the mechanisms leading to hardware failures in a computer platform be carefully considered. To calculate the different variables of the software-specific hardware failure profile, we have developed a set of analytical and simulation-based methods that account for the underlying physics and environmental phenomena leading to the production of hardware failures in computer platforms during system operation.

The software execution on hardware devices, in essence, is a series of 0 and 1 signal alternations for the inputs of hardware components. Such signal alternations lead to voltage changes and current flows in the microelectronic hardware device. The voltage and current act as electrical stresses on the device and may lead to physical changes, also referred to as degradations. Failure occurs when degradation reaches the point where the device can no longer perform its intended functions.

Hardware failures created during circuit operation can be categorized into intrinsic and extrinsic failures. Extrinsic failures are the failures not related to the device circuitry itself, but failures extrinsic to the chip, such as open wire bonds in device packaging. Intrinsic failures are caused by intrinsic defects of semiconductor

devices due to limitations of the material properties of the silicon chip or limitations of the manufacturing process. Examples of manufacturing process defects are ion contamination and atom gradients caused by mechanical stresses. Such non-lethal defects can grow into lethal ones when stressed by different failure mechanisms. One type of failure mechanism stresses the device through environmental conditions (e.g. temperature and humidity), which are not related to the software execution during device operation. Typical mechanisms of this type include Temperature Cycling [23, 24] and Corrosion [25, 26], and Stress Migration [27]. The other type of failure mechanism degrades the circuitry during device operation when the device is put under dynamic voltage and current stresses due to software execution. The primary and most studied failure mechanism of this type are Hot Carrier Injection (HCI) [28-31]; Electromigration (EM) [32-36] and Time Dependent Dielectric Breakdown (TDDB) [37-42]. This work examines the hardware intrinsic failures caused by the electronic stresses introduced by the execution of the software during device operation.

During device operation such failure mechanisms could cause shifting of device response parameters, such as voltage, capacitance, and resistance, to the point that they will not meet the designed values. For example, HCI could lead to shifts of threshold voltage, transconductance, mobility and saturation current of MOSFET transistors, while EM could increase the resistance of metal interconnects.

The best way to model the failure mechanisms is from the physics-of-failure point of view. If this can be accomplished, one could have a complete picture of how a device might fail. However, limited knowledge of these failure mechanisms

currently prevents us from completely modeling the physics-of-failure. Without detailed knowledge of the device physics, the best option to represent device failures is through probabilistic statistical models. Such models use observed relationships between failure times and various input parameters, such as voltage and current, to generate probabilistic assessments of when failures may occur [43]. Accelerated Life Testing (ALT) techniques are used to model the relationship between device lifetime and different electrical stresses [44].

Device failures due to such failure mechanisms will result in changes of circuit functionality, which will affect the execution of software running on the hardware platform. To study the impact of the hardware failures on software reliability, we have to investigate the circuit behaviors under the presence of hardware failures caused by these failure mechanisms. The connections between device failure mechanisms and circuit functionality are the failure equivalent circuit models. The underlying concept of the failure equivalent circuit models is to model device degradation with some additional lumped circuit elements (transistors, resistors, dependent current sources, etc.) to capture the behavior of a damaged circuit element in the circuit operation environment. In the past years, several failure equivalent circuit models have been developed for different failure mechanisms [45-51]. Most of these circuit models are based on the SPICE simulation platform, which is the de facto tool in circuit design.

Li et al adopted a one-dimensional HCI transistor degradation model, developed by Leblebici [47], and built a two-transistor HCI degradation model. The model is used to simulate the behavior of some benchmark circuits under the presence of Hot Carrier Injection [52]. The study showed that circuit delays induced by HCI cannot be ignored in submicron devices.

Segura et al investigated the circuit functionality of CMOS gates with damaged gate oxide due to TDDB failure mechanism. The failure equivalent circuit model consists of a series connection of two transistors and a resistance between the gate and the common terminal [53].

The above studies focused on only one particular type of failure mechanism. Most similar works consider different failure mechanisms separately. However, in order to conduct a system wide reliability estimation, all related failure mechanisms should be accounted for.

Srinvasan et al developed an architecture-level microprocessor model that is used to calculate processor lifetime reliability. Multiple failure mechanisms are included in the model to investigate the hardware lifetime with the consideration of some environment stresses (thermal cycling and mechanical stresses). The emphasis of the work is to dynamically provide processor failure rate information under different software applications and environmental stress conditions [54]. The software applications are used to simulate hardware device operation. However, the work does not provide a way to use the hardware reliability information for the evaluation of software reliability due to hardware failures. The main contributions of the methodology proposed in this dissertation with respect to the related work on hardware reliability are the following:

• It systematically calculates the hardware reliability during device operation as a function of the software execution. The interdependencies between

hardware and software in the creation of hardware failures are thus taken into account.

- We have considered all those failure mechanisms (HCI, EM, and TDDB) that are activated as a result of hardware usage induced by software execution. In other words, it accounts for a comprehensive set of hardware device intrinsic failure mechanisms that are directly related to software execution during device operation.

- It not only accounts for the failure probability of the circuit, but also investigates the probability of all possible failure manifestations (delays, stuck-at signals, changes of circuit functionalities, etc.) induced by the different failure mechanisms considered.

- It provides software-specific hardware reliability information, which is the basis for estimating the software reliability induced by hardware support failures.

- Most related research focuses on hardware reliability [47, 52, 53], and does not analyze the impact of hardware failures on software. The study by Srinvasan [54] considers the software only as a means to simulate the hardware operation, without systematic consideration of the influence of the software on hardware failures. Therefore, none of the related work analyzes the interactions and interdependencies between hardware and software with respect to reliability. Thus, this work is a bridge between microelectronic reliability and software reliability.

### 1.2 Contents of the Dissertation

The contents of the dissertation are described as follows.

Chapter 2 analyzes the different types of permanent failures that impact semiconductor devices. The analysis is performed at the different hardware design levels: physical device level, logic level and register transfer level. In particular, we first study permanent failures at the physical level (e.g., intrinsic and extrinsic failures, electrical stress failures, etc.). In this dissertation, we focus on the intrinsic failure induced by HCI, EM, and TDDB failure mechanisms during device operation. Then the way in which the failures propagate and manifest at higher hardware levels (e.g., delay, stuck-at value, different functionality, etc.) is examined.

Chapter 3 describes the methodology proposed for the analysis of the impact of permanent hardware failures on software reliability. The methodology is divided into three parts: (i) analysis of the manifestations of permanent failures on circuit elements (logic gates, flip-flops, etc.), (ii) development of reliability models as functions of the software execution, and (iii) calculation of failure probability distributions of the hardware circuit elements under the software execution. The analysis of the failure manifestation is performed through the use of SPICE simulations and failure equivalent circuit models. The reliability models take into account existing models for the DC stress failure rates, and integrate new models for the corresponding duty factors. These models also consider the way in which software executes through the hardware circuit elements in a computer system. The calculation of the failure probability distributions of the circuit elements is performed using Synopsys VCS MX simulator.

Chapter 4 consists of a comprehensive case study. The methodology is applied to all the CPU registers and ALU logic gates of a computer system based on the Z80 microprocessor. About 120 different types of failure manifestations have been observed, and more than 250 reliability models for the different types of failure manifestation and circuit element developed. Several structures for the reliability models and different notations for the failure manifestations are proposed in order to handle the complexity of the reliability models and obtain a practical and reduced set of models. Such models are used for the calculation of the failure probability distributions of the CPU registers and ALU gates of the Z80 computer system under the software execution.

Chapter 5 extends the methodology and the case study to the consideration of transient failures or SEUs (Single Event Upsets). First, a study of the causes and manifestations of transient failure in semiconductor devices is provided. Then, we develop reliability models for transient failures, which integrate into the same framework a set of well-known analytical models for the failure rate calculation of Single Event Upsets (SEUs). These take into account SEUs induced by cosmic ray particles (heavy ions and protons), neutrons present in the atmosphere, as well as neutrons emitted by nuclear reactors such as the ones that will be used in future nuclear-owered space missions from NASA. The models use design and technology parameters of the IC hardware devices, the operational environment characteristics (radiation particle fluxes) as well as the specifications of the system and mission (e.g., spacecraft shielding and orbit). The case study is then extended to the consideration

of transient failures by calculating the failure probability distributions due to SEUs of the hardware devices of the Z80 based computer system.

Chapter 6 provides the conclusions of the dissertation and proposes future research directions.

1.3 Summary of Contributions

The main contributions of this dissertation are summarized as follows.

It takes into account the influence of the software execution, the operational environment and the semiconductor design and technology in the creation and activation phenomena of hardware failures.

It includes the whole spectrum of hardware failures that can arise during the system operation, i.e. not only Single Event Upsets (SEUs), but also permanent semiconductor device failures due to Hot Carrier Injection, Electromigration, and Oxide Breakdown.

It considers all the possible locations for the hardware failures, i.e. not only sequential logic circuits (registers, memory cells, etc.) but also combinational logic circuits (logic gates)

It analyzes the propagation of failures under particular operational conditions (including the software execution) and precisely determines the form under which each hardware failure manifests (stuck-at-1, stuck-at-0, bit-flip, change of functionality, etc.) at circuit level.

It takes into account the usage of the hardware circuit elements due to software execution during the operational life of the system and provides the failure probability distributions of the circuit elements. This information can facilitate both software and

hardware reliability engineers to improve the system reliability more efficiently by focusing on the most failure-prone circuit elements.

It can be used to extend the use of the fault injection technique to the software reliability prediction under hardware failures and allows for precisely defining representative fault models that can be used in fault injection techniques and tools. It also provides the basis to develop testbeds based on software implemented fault injection (SWIFI) to calculate the final failure probability of the software application. As far as we know, this is the first time that such an extension has been proposed.

## Chapter 2 Hardware Failures

The term "hardware failures" refers to the malfunction of semiconductor devices (Physical Device Level) and their impact (or propagation) on higher hardware levels, namely the Logic Gate Level and the Register Transfer Level (RTL). In this work we also use the term hardware faults as a synonym for hardware failures, since the latter can also be the origin or cause of further errors and failures at higher layers of the system (e.g., software layer). Irrespective of the level considered, hardware failures can be classified according to their duration into permanent (remain indefinitely), transient (have a limited duration) and intermittent (as transients, but manifest repeatedly). In this work, we analyze the mechanisms and events leading to permanent failures at the physical level as well as their impact on the higher hardware levels. Intermittent failures are not addressed because they are produced by the same mechanisms as permanent failures (moreover many of them eventually transform into permanent failures). An analysis of the impact of transient failures on software reliability will be conducted in Chapter 5.

#### 2.1 Permanent Physical Failures

Permanent failures are irreversible physical defects in semiconductor devices introduced during manufacturing or system operation. In general, permanent failures can be divided into intrinsic, extrinsic and electrical stress failures [32].

Intrinsic failures are related to defects of semiconductor devices due to limitations of material properties of the silicon chip or limitations of the manufacturing processes. These defects may be small enough so that they are not lethal (e.g., material impurities), or result in a device being fatally defective (e.g., an open in metal interconnect). Examples of manufacturing processes related defects include ion contamination (Surface Inversion) and atom gradients caused by mechanical stresses (Stress Migration). Semiconductor material properties are stressed by both the environmental conditions (temperature and humidity) and the operational usage (voltage and current). These stressors are called wear-out mechanisms, and may cause non-lethal defects to become lethal. The environmental wear-out mechanisms include Temperature Cycling (mechanical fatigue of the devices due to the temperature) and Corrosion (due to humidity). The wear-out mechanisms related to the operational usage are Hot Carrier Injection (HCI), Electromigration (EM) and Time Dependent Dielectric Breakdown (TDDB) [55].

Extrinsic failures are identified with the interconnection and packaging of the silicon chips. Typical failure mechanisms include die fracture, open bond joints, voids at bonds, etc., which are external to the device circuitry itself.

Electrical stress failures are generally caused by discrete events introduced during device handling in service. These damaging events include Electrostatic Discharge (ESD) and Electrical Overstress (EOS).

The focus of this work is on hardware failures that are directly introduced during the device operation, that is, intrinsic permanent failures due to operational usage (HCI, EM and TDDB). Whenever software executes on hardware platform, the hardware device is stressed by these failure mechanisms. The corresponding failures, in turn, may cause software-execution errors, which means software reliability will be affected. This work focuses on studying the probability of such hardware failures due

to the execution of software. It also provides necessary information to evaluate software reliability induced by these hardware failures.

Intrinsic failures caused by environmental stressors can impact how software executes in a microprocessor. However, they are not induced by the execution of software. For example, corrosion failures occur when the hardware device are in the presence of moisture and contaminants. The lifetime of corrosion failures is expressed as a function of relative humidity and temperature [25, 26]. Stress migration failures are induced when the device is put under mechanical stresses. The lifetime of stress migration failures is expressed as a function of mechanical stress load and temperature [27]. Such environmental stresses are not introduced by software execution, and they could cause hardware failures even when the device is operating. They are not the focus of this work. The impact of such failures on software reliability could be studied in future work.

Similarly, even though extrinsic and electrical stress permanent failures can also impact the system in operation, they are not introduced directly due to software execution. Therefore, these failures are not considered in this study.

#### 2.1.1 Hot Carrier Injection Failure Mechanism

Hot Carrier Injection (HCI) refers to the phenomenon by which carriers (electrons or holes) at the drain end of a MOSFET (Metal-Oxide Semiconductor Field-Effect Transistor) transistor gain sufficient energy to be injected into the gate oxide and cause shifts of some MOSFET parameters, such as threshold voltage, transconductance, mobility and saturation current. This occurs as carriers move along the channel of a MOSFET (the conductivity path between the source and drain of a

field effect transistor) and experience impact ionization near the drain end of the device due to a high lateral electric field. Some high-energy electrons and/or holes produced by the impact ionization are redirected and accelerated to the interface of the oxide and silicon surface. A few of these "lucky" carriers overcome the surface energy barrier, inject into the oxide, and generate interface states and oxide charges. The shifts of threshold voltage and transconductance are proportional to the average density of "traps" (imperfections in a semiconductor material that can capture a free electron or hole), which in turn is inversely proportional to the effective channel length.

Due to the higher mobility and lower energy barrier, hot electrons are much easier to be injected into the oxide than hot holes, which means that nMOSFET transistors are more prone to HCI effects than pMOSFET transistors. Therefore, pMOSFET transistors are seldom a limiting factor in the reliability of a CMOS technology, and can be usually ignored from reliability estimates [28, 56].

The HCI lifetime of a transistor can be determined by:

$$MTTF^{hci} = A_{HCI} \left(\frac{I^{sub}}{W}\right)^{-n} \exp\left(\frac{E_{aHCI}}{\kappa T}\right)$$

(2.1)

where

$A_{HCL}$  the model prefactor determined from life testing

$I^{sub}$  the average substrate current

n a technology related constant

- *W* the transistor channel width

- $E_{aHCI}$  apparent activation energy for HCI

- $\kappa$  Boltzmann's constant

- *T* the absolute temperature

#### 2.1.2 Electromigration Failure Mechanism

Electromigration (EM) is the mass transport of a metal due to the momentum exchange between the conducting electrons that move in the applied electric field and the metal atoms that make up the interconnecting material. It exists wherever electric current flows through metal wires. The EM failure lifetime model of a metal interconnect is characterized as [36]:

$$MTTF^{em} = A_{EM} \left(\frac{I}{A}\right)^{-n} T^{-m} \exp\left(\frac{E_{aEM}}{\kappa T}\right)$$

(2.2)

where

| $A_{EM}$  | the model prefactor                            |

|-----------|------------------------------------------------|

| Ι         | the average current                            |

| A         | the cross section of the interconnects         |

| Т         | the absolute temperature                       |

| $E_{aEM}$ | the activation energy for EM failure mechanism |

| k         | Boltzmann's constant                           |

| n,m       | material and failure mode dependent parameters |

EM decreases the reliability of ICs. In the worst case, it leads to the eventual loss of one or more connections and intermittent failure of the entire circuit. Since the reliability of interconnects is not only of great interest for space travel and military applications but also for civilian applications like the anti-lock braking system of cars, high technological and economic values are attached to this effect.

# 2.1.3 Time Dependent Dielectric Breakdown Failure Mechanism

When an electric field is applied to the dielectric-isolated gate of a MOSFET, the progressive degradation of the dielectric material will result in the formation of conductive paths in the oxide and a shortening of the anode and cathode. When this happens, the continuous stress of the electric field on the gate oxide may lead to excessive energy dissipation, or even thermal runaway, through breakdown paths. The electrical after-effects of oxide breakdown are an abrupt increase in gate current and a loss of gate voltage controllability on device current flowing between drain and source. This kind of failure mechanism is known as Time Dependent Dielectric Breakdown (TDDB) or oxide breakdown, and the degradation process will be accelerated as the thickness of the gate oxide decreases with continued device scaling.

The TDDB lifetime of a transistor is given by [40-42]:

$$MTTF^{tddb} = A_{TDDB} \left(\frac{1}{A}\right)^{\frac{1}{\beta}} V_{gs}^{a+bT} \exp\left(\frac{c}{T} + \frac{d}{T^2}\right)$$

(2.3)

where

$A_{TDDB}$  the model prefactor

a, b, c, d empirically determined constants

- A the device gate oxide area of the transistor, equivalent to W (channel width)  $\times$  L (channel length)

- $V_{gs}$  the gate-to-source voltage

- *T* the absolute temperature

- $\beta$  Weibull distribution slope parameter

# 2.2 Impact on Higher Hardware Levels

Microelectronic hardware circuit design, especially digital IC design, can be divided into four different abstraction levels, as shown in Figure 2.1.

- Behavioral Level: it describes the function (or behavior) components of the system. It specifies the input and output of the component and the function the component carries.

- Register Transfer Level (RTL): a behavioral component is decomposed into combinational logic and storage elements. The storage element (flip flop, latch) is normally controlled by the system clock. The combinational logic provides access control to the storage element.

- Logic Level: the design is represented as a netlist (or combination) with different logic gates (AND, OR, NOT, etc.) and storage elements. The difference between this level and the RTL level is that one can observe the individual gates at this level but only blocks that represent storage and combinational logic at the RTL level.

- Layout Level: this level is the bottom of the hierarchy. This level describes the layout of the actual transistors and their inter-connections.

Figure 2.1 Different abstraction levels of circuit design

In the previous section, the analysis of permanent failures was described at the physical device level of the hardware, that is, with respect to the transistor elements and their physical interconnections, which are the building blocks of the circuit layout. Usually, IC design process starts from the top level (i.e., behavioral level) and goes down step-by-step to the layout level for the targeted semiconductor technology node.

RTL level consists of combinational logic circuits and storage elements, which are further decomposed into discrete logic gates and flip-flops at the logic gate level, as illustrated in an example of RTL design in Figure 2.2.

As explained in Section 2.1, a permanent failure at the physical level that becomes lethal leads to a transistor stuck-on/stuck-off or an open/short in a metal wire. At the logic and RT levels, these physical defects mainly manifest as stuck-at values (the logic voltage of a signal is stuck either at 0 or 1), indeterminate values (the logic voltage of a signal is neither 0 nor 1) and signal delays. Also, the propagation of permanent failures may lead to a functionality change of a combinational logic element, e.g., a transistor stuck-on failure in a NAND gate could change the truth table of the gate, making it behave differently than desired [57]. Besides, permanent failures can also propagate from the combinational logic to the storage elements in the form of bit-flips. Note that stuck-at values are not the only possible manifestations of permanent hardware failures.

Figure 2.2 Example of a RTL Design

# Chapter 3 Methodology for the Analysis of Permanent Failure Manifestations

This chapter describes the methodology for the analysis of permanent hardware failure manifestations. The methodology consists of three phases, which are described as follows.

During the first phase of the methodology (analysis of failure manifestations), SPICE simulation is performed to investigate the behavior of the circuit elements (logic gates and flip-flops) under study with a set of generic input stimuli, which covers all possible combinations of logic levels and transitions of the input signals. This allows for calculating the failure rates of different circuit elements. A set of failure equivalent circuit models for different failure mechanisms, including HCI, EM and TDDB is used to study the circuit failure manifestations under the presence of hardware failures. The main outcome of this phase consists of the set of manifestations of the permanent failures observed in the circuits' output signals (e.g., signal delays, functionality changes or stuck-at failures).

During the second phase of the methodology (development of reliability models), a set of reliability models are built that allow for calculating the occurrence rate of each failure manifestation of a circuit as a function of the software execution profile of a computer system. The models are based not only on existing expressions for the constant stress failure rate of permanent failures, but also on specifically developed models that account for the operational conditions of circuits (e.g., current and voltages) and for the usage of the computer hardware devices as a consequence of the software execution. Different structures and notations are proposed for the reliability models in order to reduce huge numbers of failure manifestations into practical sets of expressions.

During the third phase of the methodology (calculation of failure probability distributions), the reliability models developed in the previous phase are applied to a particular computer platform. The usage of the hardware devices is obtained through VHDL simulations of the computer system under the execution of the software program of interest. This allows for solving the reliability models and calculating the failure probability distributions (per failure manifestation) of the various hardware devices of the computer platform (e.g., ALU gates, CPU registers, memories, etc.).

The methodology is divided into five steps, two steps for the first phase, one for the second phase, and two for the third phase, as illustrated in Figure 3.1. Each step will be described in detail in the following sections.

Figure 3.1 Methodology for the analysis of permanent failure manifestations

## 3.1 Analysis of Failure Manifestations

3.1.1 Calculation of Failure Rates and Characterization of Stress Patterns

This section describes step 1 of Figure 3.1.

As explained in Section 2.1, the hardware failures of interest in this study are intrinsic failures that are directly related to software execution. The execution of the software can be seen as a series of electrical signals based on logic 0s and 1s that activate the circuits of the computer hardware platform following a particular profile.

Of all the intrinsic failure mechanisms, the three most dominant mechanisms are considered in this study. They are Hot Carrier Injection (HCI), Electromigration (EM), and Time Dependent Dielectric Breakdown (TDDB).

Based on the lifetime models (2.1), (2.2) and (2.3) discussed in section 2.1, the corresponding failure rates of a circuit element (transistor or metal interconnection) are calculated as:

$$\lambda_i^{hci} = \frac{1}{MTTF_i^{hci}} \tag{3.1}$$

$$\lambda_i^{em} = \frac{1}{MTTF_i^{em}} \tag{3.2}$$

$$\lambda_i^{tddb} = \frac{1}{MTTF_i^{tddb}}$$

(3.3)

Failure rates expressed in (3.1), (3.2) and (3.3) are referred to as constant (or DC) stress failure rates, since lifetime models (2.1), (2.2) and (2.3) for the reliability evaluation of the different failure mechanisms are obtained from accelerated testing experiments under DC stress conditions. For example, to obtain the HCI lifetime model (equation (2.1)), a series of accelerated life testing experiments are conducted at several substrate current and temperature combinations for the transistors. For a particular combination, the testing is performed by keeping the substrate current and temperature constant during the total testing time. The failure data obtained from testing are then used to extract parameters in the lifetime model by means of maximum likelihood estimation techniques. The models for EM and TDDB (equations (2.2) and (2.3)) are developed in a similar way.

With the lifetime models, the failure rates of all the failure mechanisms can be calculated if we have the device operation conditions, such as the gate to source voltages (Vgs) and substrate currents of the transistors. The device operation condition can be obtained through SPICE simulation.

SPICE stands for Simulation Program with Integrated Circuits Emphasis. It is a general-purpose circuit simulation program for nonlinear dc, nonlinear transient, and linear ac analyses. SPICE provides a detailed analysis of active components including bipolar transistors, field effect transistors, and diodes, as well as lumped components, such as resistors, capacitors and inductors. Note that SPICE is a circuit simulation program, not a logic simulation program. Thus SPICE considers the voltages and currents in a circuit to be continuous quantities, not quantized into high/low values. Other constants, fitting parameters, and activation energies can be extracted from experimental data (e.g., accelerated stress tests or industry data).

SPICE uses as main inputs the schematics of a circuit of the technology under consideration (e.g. Figure 3.3), and the input signal stimuli (e.g., Figure 3.4 and Figure 3.5).

Figure 3.2 Circuit Layout of an AND2\_1 logic gate

Figure 3.3 Schematic of the AND2\_1 logic gate

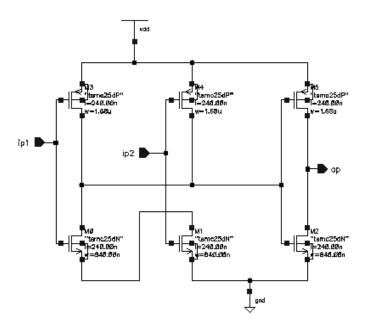

As an example, consider an AND2\_1 logic gate implementing logic operation "And" of two input signals (i.e., given two inputs a and b, the output is  $a \wedge b$ ). The gate belongs to standard cell library vtvtlib25 developed by the Virginia Tech VLSI for Telecommunication (VTVT) Group [58, 59], based on TSMC 0.25  $\mu$ m technology. The physical layout of this gate is shown in Figure 3.2. It is composed of 6 transistors (M0, M1, M2, M3, M4, and M5) and 5 interconnections (N1, N2, N3, N4, N5). The corresponding schematic is shown in Figure 3.3. The AND2\_1 logic gate is used throughout this section to illustrate the methodology.

For the purposes of our analysis, the input signals to a circuit are designed according to the following criteria:

The set of input signals includes all the possible combinations for logic levels (1's and 0's) and transitions (rising and falling edges). We assume that two or more transitions in different lines cannot happen at the same time.

The set of input signals leads to the same duration for every combination of logic levels. The actual duration of a pulse is not important for our analysis, while the value for the duration of a transition period will be given by the particular semiconductor technology under analysis.

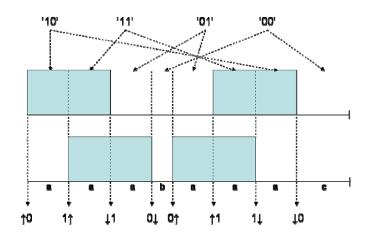

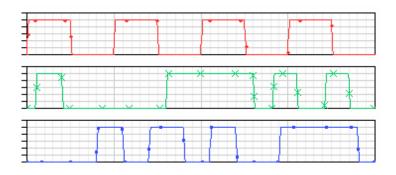

We refer to a set of input signals matching these criteria as Standardized Inputs. Figure 3.4 and Figure 3.5 provide examples of Standardized Inputs.

Figure 3.4 Asynchronous input signals

Figure 3.5 Asynchronous and synchronous (clock) input signals

Consider the 2-asynchronous input signals of Figure 3.4. The first criterion is fulfilled since

- there is a rising transition in the first input when the second input is high or low,

- there is a falling transition in the first input when the second input is high or low,

- there is a rising transition in the second input when the first input is high or low,

- there is a falling transition in the second input when the first input is high or low,

- all logic levels ('00', '01', '10', '11') are present. The second criterion is fulfilled since the percentage of time for each logic combination of the input lines is the same (namely, 2a for combinations '01', '10', '11', and b + c for '00', where 2a = b + c).

It can be shown in a similar way that the two inputs of Figure 3.5 (consisting of an asynchronous signal and the clock line) also fulfill the criteria.

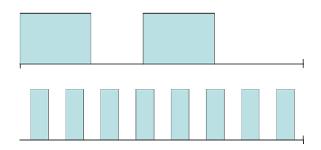

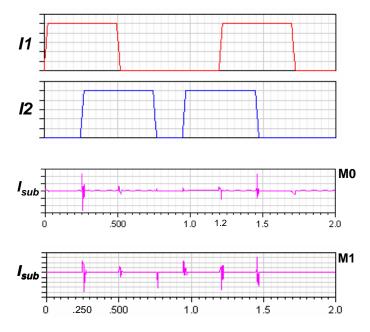

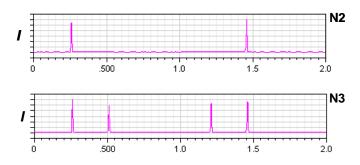

The criteria used for the design of the input signals allow for "capturing" all the different patterns (including their relative time intervals) of the occurrence of the failure mechanisms in a circuit. Indeed, transistors and interconnects suffer from HCI, EM and TDDB stresses only for specific combinations and time intervals of logic levels and transitions of the input signals. We refer to these combinations as stress patterns. This is illustrated in Figure 3.6, where some stress patterns of the AND2\_1 logic gate obtained with SPICE are displayed.

a) HCI effect in transistors M0 (instant  $1.2\mu s$ ) and M1 (instant  $0.250\mu s$ ) in terms

of  $I_{\text{sub}}$

b) EM effect in interconnections N2 and N3 in terms of I

c) TDDB effect in transistor M2 in terms of  $V_{\text{gs}}$

Figure 3.6 Stress patterns examples for HCI, EM and TDDB in the AND2\_1

gate

A transistor suffers from HCI stress only during transition periods, when both gate voltage and drain voltage are high enough and there is current flowing through the channel (parameter  $I_{sub}$  of equation (2.1)). For transistor M0 of the AND2\_1 gate, such conditions appear whenever there is a rising edge (' $\uparrow$ ') in the first input (I1) and the second input (I2) is high ('1') (i.e., instant 1.2µs in Figure 3.6a). For transistor M1, it appears whenever the first input (I1) is high ('1') and there is a rising edge (' $\uparrow$ ') in the second input (I2) (i.e., instant 0.250µs in Figure 3.6a).

A metal wire suffers from EM whenever there is an electric current flowing through it. For CMOS circuits, the current flow in an interconnection is negligible if the circuits are in static condition. However, switching input signals may introduce current pulses in the metal wires leading to EM. As shown in Figure 3.6b, EM arises in interconnect N2 whenever there is a rising transition in input I2 while input I1 is high, or there is a falling transition in input I2 while input I1 is high (i.e., instants 1.25µs and 1.45µs in Figure 3.6b). For interconnect N2, it arises whenever there is a transition in one line while the other is high (i.e., instants 0.25µs, 0.5µs, 1.2µs and 1.45µs in Figure 3.6b).

Unlike HCI, TDDB stresses the gate dielectrics of the transistors even when they are in static state operations. As described in equation (2.3), the transistors lifetime due to TDDB stress strongly depends on the gate to source voltage  $V_{gs}$ . For CMOS circuits, during normal device operation, most of the transistors experience certain periods during which the gate to source voltage  $V_{gs}$  value is equal to the power supply voltage  $V_{dd}$ . The higher the percentage of such periods, the higher the failure rates of the transistors due to the TDDB stress. As shown in Figure 3.6c,  $V_{gs}$  will systematically equal  $V_{dd}$  in transistor *M*2 for logic levels '00', '01', and '10' of inputs I1 and I2 (i.e., time intervals [0, 0.25], [0.5, 1.2] and [1.45, 2.0] in Figure 3.6c), leading to TDDB stress.

3.1.2 Identification of Failure Manifestations

This section describes step 2 of Figure 3.1.

The identification of fault models is divided into the following steps:

- 1) Development of a failure-equivalent-circuit model for the segments,

- Independent simulations of the element by substituting each time one segment by the failure-equivalent-circuit model,

- Observation of the output signal in each simulation and determination of the fault models.

Once the failure rates  $(\lambda_i^{hci}, \lambda_i^{em}, \lambda_i^{tdb})$  are calculated for every transistor Miand interconnection Ni of a circuit element, a selection is made based on the elimination of those segments that are softly or not stressed by the failure mechanisms, so their impact in the global failure probability of the circuit can be neglected. This means that segment *i* under stress *j* will not be given any further consideration in our analysis if  $\lambda_i^j \approx 0$ . This is for instance the case of the pMOSFET transistors of a circuit, which as explained in Section 3.1.1 are barely impacted by the HCI stress.

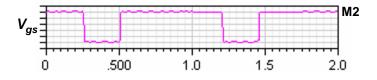

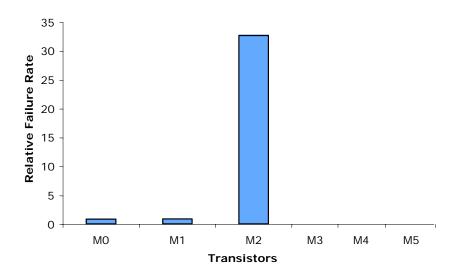

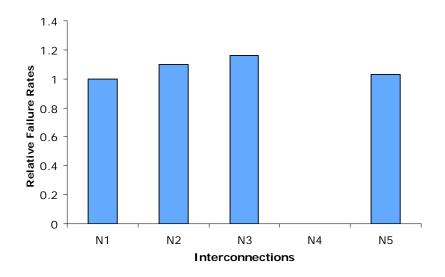

Figure 3.7, Figure 3.8 and Figure 3.9 show an example of a segments selection for the AND2\_1 logic gate.

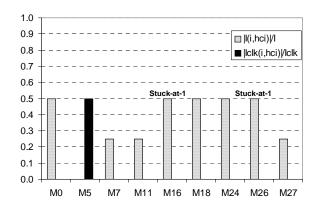

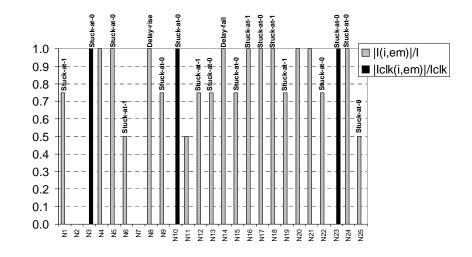

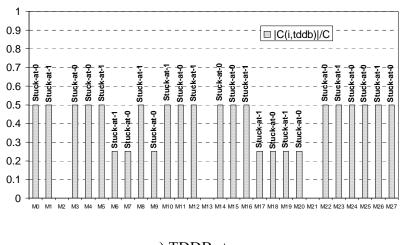

Figure 3.7 Relative HCI failure rates of transistors

Figure 3.8 Relative EM failure rates of interconnections

Figure 3.9 Percentage of time a transistor suffers from TDDB stress

Figure 3.7 shows the relative failure rates of the different transistors for HCI with respect to transistor M0. Figure 3.8 illustrates the relative failure rates of the different metal interconnects for EM with respect to N1. While Figure 3.9 displays the percentage time transistors suffer from TDDB stress. In this case, the segments selection simply leads to the elimination of the pMOSFET transistors under HCI stress (i.e., transistors M3, M4 and M5), and interconnection N4 under EM stress.

In order to account for the effect of different failure mechanisms on circuit functionality, several failure equivalent circuit models [51], one for each failure mechanism, are adopted to obtain circuit level failure manifestations through SPICE simulation (one per segment and failure mechanism). The underlying concept of the failure equivalent circuit models is to model device degradation with some additional lumped circuit elements (resistors, dependent current sources, etc.) to capture the behavior of a damaged circuit element in circuit operation environment. The larger the magnitude of element values, such as the resistance of the lumped resistor, the more severe the damage to circuit functionality. The failure equivalent circuit models are provided in Figure 3.10, Figure 3.11, and Figure 3.12.

Figure 3.10 Failure equivalent circuit model for HCI mechanism

Figure 3.11 Failure equivalent circuit model for EM mechanism

Figure 3.12 Failure equivalent circuit model for TDDB mechanism

The adopted HCI failure equivalent circuit model (Figure 3.10) is the Hot Carrier Induced Series Resistance Enhancement Model (HISREM), also named  $\Delta R_d$ model (proposed by Hwang [48] and improved in [51]). The model is composed of the original nMOSFET transistor connected in series with a voltage dependent drain resistor  $\Delta R_d$ , which reflects the process of hot carrier induced interface trap generation and therefore accounts for the channel mobility reduction and threshold voltage shift. The degree of circuit degradation is reflected by the value of resistor  $\Delta R_d$ . The more severe the HCI damage to the circuit, the higher the resistance value.

The metal conductor used in current submicron CMOS technologies is constructed of a composite layered structure with a refractory metal layer on top and at the bottom of the aluminum alloy core metal. The effect of EM on the composite metal conductor is the increase of line resistance. Usually the failure criteria used in the EM lifetime test is an increase of the line resistance by 10 to 20 %, or a line resistance increase by a fixed value [60]. The EM failure equivalent circuit model for a metal interconnect (Figure 3.11) is a resistor whose resistance value gets higher as the degradation becomes worse.

The TDDB failure equivalent circuit model used (Figure 3.12) corresponds to the Maryland Circuit Reliability Oriented (MaCRO) model [51]. The electrical effect of TDDB is that it provides a conduction path to inject electrons from channel into gate. Therefore, a voltage dependent current source  $I_{ox}$  can be used to connect the gate and channel of the damaged transistor to model the effect of TDDB. The circuit model for nMOSFET is shown in Figure 3.12, in which two split transistors imitate the channel separation by oxide breakdown path, and the voltage-dependent current source  $I_{ox}$  physically represents the conduction mechanism of hard breakdown path across the oxide. The magnitude of  $I_{ox}$  reflects the degree of degradation of the TDDB failure mode. The model can be extended to pMOSFET by properly changing current flowing direction in Figure 3.12.

The relation between the additional lumped circuit elements values used in the failure equivalent circuit models (such as the resistance of the resistors) and the lifetime models of the failure mechanisms (equations (2.1), (2.2) and (2.3)) is beyond the scope of this work. Therefore, the values for the mean time to failure of the circuit are calculated using equations (2.1), (2.2) and (2.3) irrespective of how high it is necessary to increase the value of the lumped circuit elements to readily observe a failure manifestation.

Assuming that the failure of a segment due to HCI, EM and TDDB damage could lead to a circuit functional error, the failure equivalent circuit models are used to replace one segment at a time in the analysis. Each transistor of a circuit is to be replaced by the HCI and TDDB failure equivalent circuit models (Figure 3.10 and Figure 3.12), and each interconnection by the EM failure equivalent circuit model (Figure 3.11). Accordingly, if a circuit contains M transistors and N interconnections, 2M + N mutated versions of the same circuit are produced. A "mutant" is thus a circuit in which a segment (transistor or interconnection) considered to be faulty is replaced by a failure equivalent circuit model. An example of one of such "mutants" for the AND2\_1 gate circuit is provided in Figure 3.13, where transistor M5 is replaced by the TDDB failure equivalent circuit model.

Figure 3.13 AND2\_1 layout with transistor M5 replaced by the TDDB failure equivalent circuit model