## ABSTRACT

| Title of dissertation:    | HILL-CLIMBING SMT PROCESSOR RESOURCE DISTRIBUTION                           |

|---------------------------|-----------------------------------------------------------------------------|

|                           | Seungryul Choi, Doctor of Philosophy, 2006                                  |

| Dissertation directed by: | Professor Donald Yeung<br>Department of Electrical and Computer Engineering |

The key to high performance in SMT processors lies in optimizing the shared resources distribution among simultaneously executing threads. Existing resource distribution techniques optimize performance only indirectly. They infer potential performance bottlenecks by observing indicators, like instruction occupancy or cache miss count, and take actions to try to alleviate them. While the corrective actions are designed to improve performance, their actual performance impact is not known since end performance is never monitored. Consequently, opportunities for performance gains are lost whenever the corrective actions do not effectively address the actual performance bottlenecks occurring in the SMT processor pipeline.

In this dissertation, we propose a different approach to SMT processor resource distribution that optimizes end performance directly. Our approach observes the impact that resource distribution decisions have on performance at runtime, and feeds this information back to the resource distribution mechanisms to improve future decisions. By successively applying and evaluating different resource distributions, our approach tries to *learn* the best distribution over time. Because we perform learning on-line, learning time is crucial. We develop a *hill-climbing SMT processor resource distribution technique* that efficiently learns the best resource distribution by following the performance gradient within the resource distribution space.

This dissertation makes three contributions within the context of learning-based SMT processor resource distribution. First, we characterize and quantify the time-varying performance behavior of SMT processors. This analysis provides understanding of the behavior and guides the design of our hill-climbing algorithm. Second, we present a hillclimbing SMT processor resource distribution technique that performs learning on-line. The performance evaluation of our approach shows a 11.4% gain over ICOUNT, 11.5% gain over FLUSH, and 2.8% gain over DCRA across a large set of 63 multiprogrammed workloads. Third, we compare existing resource distribution techniques to an ideal learningbased technique that performs learning off-line to show the potential performance of the existing techniques. This limit study identifies the performance bottleneck of the existing techniques, showing that the performance of ICOUNT, FLUSH, and DCRA is 13.2%, 13.5%, and 6.6%, respectively, lower than the ideal performance. Our hill-climbing based resource distribution, however, handles most of the bottlenecks of the existing techniques properly, achieving 4.1% lower performance than the ideal case.

# HILL-CLIMBING SMT PROCESSOR RESOURCE DISTRIBUTION

by

Seungryul Choi

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2006

Advisory Committee:

Professor Donald Yeung, Chair/Advisor Professor Chau-Wen Tseng Professor Alan Sussman Professor Manoj Franklin Professor Sung Lee © Copyright by Seungryul Choi 2006

# ACKNOWLEDGMENTS

It is my honor to know so many good people who made my Ph.D. study at the University of Maryland enjoyable. First of all, I really thank my advisor, Dr. Donald Yeung. He not only advised my research but also was a role model in my academic life. In addition, the discussion with him inspired me and made me to aim at higher quality intellectual level. As a result, my graduate study was fun and a meaningful part of my life.

I specially thank my grandmother, father, mother, and brother for their endless love. I was able to finish my long graduate study in Maryland because of their enormous support and endless prayers to God for me. My cousins and cousin-in-laws, Wonsun, Sam, Moonsun, Andrew, and Taewook, always remind me of the meaning of the family. I really appreciate their help since I first came to the USA.

During my stay in Maryland, I was so lucky to have many good people around me. I thank my office mates in the University of Maryland for their help and discussion, and for sharing ideas: Dongkeun, Gautham, Deepak, Hameed, Sumit, Wanli, Xuanhua, Priyanka, Aamer, Sada, Zahran, Anashua, Vinod, Aneesh, Jayanth, Brinda, Renju, Barath, Sumesh, David, Kursad, Mike, Ohm, Sean, and all the other friends in SCA-Lab. I would like to acknowledge the Korean friends and their families in Maryland: Junesong, Jungmin, Kwangoon, Dongin, Eenjun, Hyunsang, Hwansoo, Kyungdong, Sungjoon, Kyongil, Jaejung, Sangwook, Hyunmo, Pyonguk, Bongwon, Changha, Jihwang, Yooah, Seungjoon, Kyungnam, Beomseok, Jinwook, Minho, Bongshin, Jaeyong, Jaeyoon, Sungwook, Bohyung, Hyunook, Woochul, Joonhyuk, Seungjong, Jusub, Dongik, Soobum, and many others. I also appreciate the members of my Ph.D. defense committee: Dr. Manoj Franklin, Dr. Chau-Wen Tseng, Dr. Alan Sussman, and Dr. Sung Lee. In addition, I want to thank Daniel, Timoteo, Joseph, Jennifer, Kwanghoon, Wooyoung, Jaehwa, Jinhyuk, Ilchul, Woochang, and TJ for their religious support and prayers for me. I apologize to those I have inadvertently left out.

Most importantly, I would like to thank my lovely Jiyoun, Andy, and Claire. Andy and Claire have been the source of happiness in my family. Jiyoun has always been the best friend, a great supporter, a trustful advisor as well as a sweet wife.

Lastly, I sincerely thank God for his endless love and care.

# TABLE OF CONTENTS

| Li | of Figures                                                                                                                                                                                                                                                                                             | vii                                                                  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1  | Introduction         1.1       Motivation         1.1.1       Simultaneous Multithreading Processors         1.1.2       Feedback-based SMT processor resource distribution         1.1.3       Hill-Shaped SMT Processor Performance Curve         1.2       Contributions         1.3       Road Map | $1 \\ 1 \\ 2 \\ 4 \\ 7 \\ 10$                                        |

| 2  | 2.1       Single Chip Multi-Threading Processors                                                                                                                                                                                                                                                       | 12<br>12<br>14<br>16                                                 |

| 3  | 3.1 Run-time Hardware Optimization                                                                                                                                                                                                                                                                     | $19\\19\\23$                                                         |

| 4  | 4.1       Performance Curve                                                                                                                                                                                                                                                                            | 26<br>27<br>28<br>31<br>32<br>35<br>35<br>40<br>43<br>43<br>43<br>48 |

| 5  | <ul> <li>5.1 Locality of Performance</li></ul>                                                                                                                                                                                                                                                         | $53 \\ 53 \\ 53 \\ 54 \\ 54 \\ 56 \\ 56 \\ 59 \\ 60 \\ 60$           |

|    | 5.4 Implementation Cost                                                                                                                                                                                                                                                                                |                                                                      |

|   |      | 5.4.1   | Software Implementation                                                                 | 51         |

|---|------|---------|-----------------------------------------------------------------------------------------|------------|

|   |      | 5.4.2   | Hardware Implementation                                                                 | 52         |

|   |      | 5.4.3   | Single-Threaded IPC Computation Overhead                                                | 53         |

| 6 | Perf |         |                                                                                         | 64         |

|   | 6.1  |         |                                                                                         | 64         |

|   |      | 6.1.1   | U U                                                                                     | 35         |

|   |      | 6.1.2   |                                                                                         | 66         |

|   |      | 6.1.3   | 1                                                                                       | 67         |

|   | 6.2  | Qualit  | 0 0                                                                                     | 68         |

|   |      | 6.2.1   | 0 1                                                                                     | <u>5</u> 9 |

|   |      | 6.2.2   |                                                                                         | 70         |

|   | 6.3  | Result  | s of the Limit Study $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ | 72         |

|   |      | 6.3.1   | Performance Opportunities of ICOUNT and FLUSH                                           | 74         |

|   |      | 6.3.2   | Performance Opportunities of DCRA                                                       | 75         |

|   |      | 6.3.3   | Performance Opportunities of Hill-Climbing Resource Distribution . 7                    | 77         |

|   | 6.4  | Perfor  | mance Hazards of the Hill-Climbing Resource Distribution 7                              | 78         |

|   |      | 6.4.1   | Spatial Hazards                                                                         | 30         |

|   |      | 6.4.2   | Temporal Hazards                                                                        | 31         |

| 7 | Perf | ormanc  | e Evaluation of the Hill-Climbing Resource Distribution 8                               | 33         |

|   | 7.1  | Exper   | imental Methodology                                                                     | 33         |

|   | 7.2  | Perfor  | mance Results                                                                           | 34         |

|   |      | 7.2.1   | Baseline Performance Results                                                            | 34         |

|   |      | 7.2.2   | Adaptive Optimization Goals                                                             | 37         |

|   | 7.3  | Impro   | ving Hill-Climbing Resource Distribution                                                | 39         |

|   |      | 7.3.1   | Phase-Based Learning                                                                    | 39         |

|   |      | 7.3.2   | Hill-Climbing with Momentum Term                                                        | 91         |

| 8 | Ove  | rhead A | Analysis And Sensitivity Study 9                                                        | 93         |

|   | 8.1  | Run-t   | ime Overhead Analysis                                                                   | 93         |

|   |      | 8.1.1   | Run-time Stand-Alone IPC Computation Overhead                                           | )3         |

|   |      | 8.1.2   | Resource Distribution Overhead vs. Epoch Size                                           | )5         |

|   | 8.2  | Sensit  | ivity Study                                                                             | )7         |

|   |      | 8.2.1   |                                                                                         | 97         |

|   |      | 8.2.2   | Amount of Processor Resource                                                            | 98         |

|   |      | 8.2.3   | Thread Priority                                                                         | )0         |

| 9 | Cas  | e Study | : Optimizing Multi-Threaded Run-Time System 10                                          | )2         |

|   | 9.1  | Kaffe-  | -Multi-Threaded Run-Time System                                                         | )2         |

|   |      | 9.1.1   | Kaffe                                                                                   | )3         |

|   |      | 9.1.2   | Garbage Collection                                                                      | )4         |

|   | 9.2  | Exper   | imental Methodology                                                                     | )5         |

|   | 9.3  | Result  | ss                                                                                      | )6         |

| 10  | Conclusion                  |  |  |  |  |  |

|-----|-----------------------------|--|--|--|--|--|

|     | 10.1 Summary and Conclusion |  |  |  |  |  |

|     | 10.2 Contributions          |  |  |  |  |  |

|     | 10.3 Future Directions      |  |  |  |  |  |

|     |                             |  |  |  |  |  |

| Bil | pliography 115              |  |  |  |  |  |

# LIST OF FIGURES

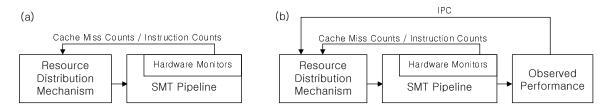

| 1.1 | (a) Existing resource distribution techniques optimize performance indi-<br>rectly by making decisions based on hardware monitors only. (b) Learning-<br>based resource distribution examines actual performance ( <i>e.g.</i> , IPC) to<br>learn the optimal resource distribution.                                                                                                                                                                                                                                                                                                                          | 3  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

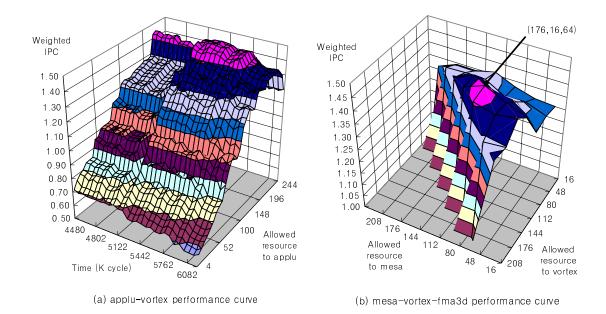

| 1.2 | Performance, measured in weighted IPC metric, of (a) applu and vortex,<br>and (b) mesa, vortex, and fma3d running simultaneously on an SMT pro-<br>cessor, as the fraction of resources allowed to each application is varied. In<br>(a), the Y-axis shows the amount of resources allowed to applu (vortex re-<br>ceives the remaining resources), and the X-axis shows the time. In (b), the<br>X- and Y-axes show the amount of resources allowed to mesa and vortex<br>(fma3d receives the remaining resources). The labeled arrow indicates the<br>resource distribution that achieves peak performance. | 6  |

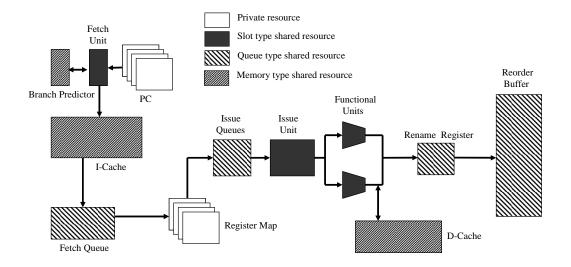

| 2.1 | Block diagram of the SMT processor resources. The shared resources are classified into three types: slot type, queue type, and memory type. White boxes indicate private resources.                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

| 2.2 | Hill-climbing algorithm on discrete domain space (a) and continuous domain space (b). In discrete domain space, the next vertex is picked among the neighboring vertices whose $f$ value is the best (line 4-7). In continuous domain space, the next state is directed by the gradient vector (line 13-16).                                                                                                                                                                                                                                                                                                  | 17 |

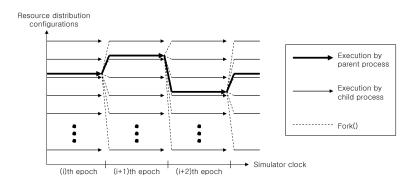

| 4.1 | Probe-based simulation timing diagram. Parent simulator process forks multiple child processes to investigate the various alternatives of the future ( <i>i.e.</i> , the next epoch). Only the parent process is allowed to execute the end-to-end simulation.                                                                                                                                                                                                                                                                                                                                                | 33 |

| 4.2 | Probe-based simulation algorithm pseudo code. Child processes investigate the alternative configurations that the parent process can potentially choose from (line 14).                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33 |

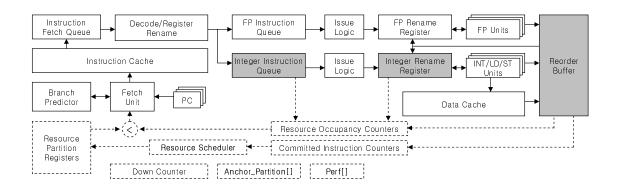

| 4.3 | Block-level diagram of our SMT processor model. Shaded boxes indicate<br>shared hardware structures that are partitioned by the OFF-LINE-Analysis.<br>Dashed boxes indicate additional hardware needed for the implementation<br>of our hill-climbing resource distribution implementation, which we will<br>detail in Section 5.4.                                                                                                                                                                                                                                                                           | 36 |

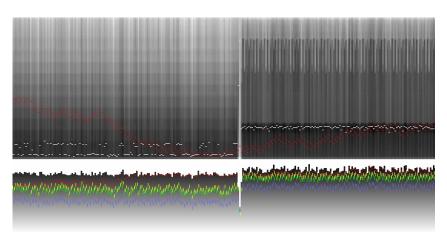

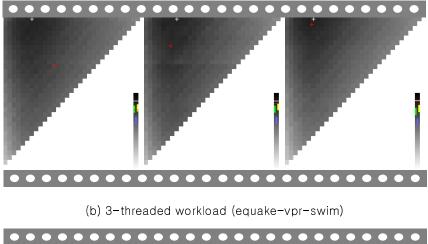

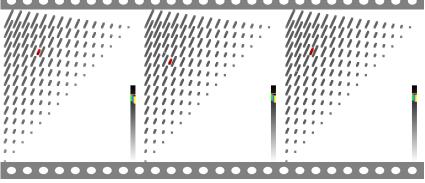

| 4.4 | Snapshot of SMT processor run-time behavior visualization tool for (a) 2-threaded, (b) 3-threaded, and (c) 4-threaded workloads. The run-time behavior of a 2-threaded workload is displayed as a still picture frame, and those of 3- and 4-threaded workload are displayed as motion pictures                                                                                                                                                                                                                                                                                                               | 41 |

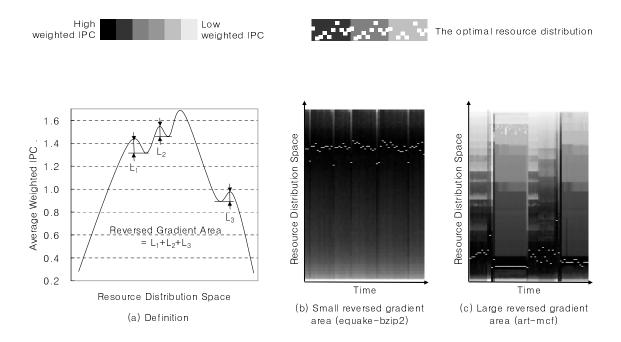

| 4.5 | Reversed gradient area metric measures the amount of local maxima in the performance curve.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45 |

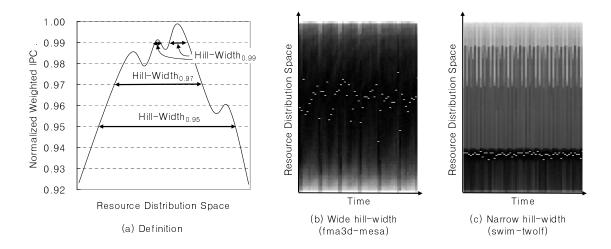

| 4.6  | Hill-width <sub>X</sub> metric measures the fraction of the resource distributions whose performance outcome is better than $X$ of the optimal one                                                                                                                                                                                                                                                                                                                                                                                                      | 45 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

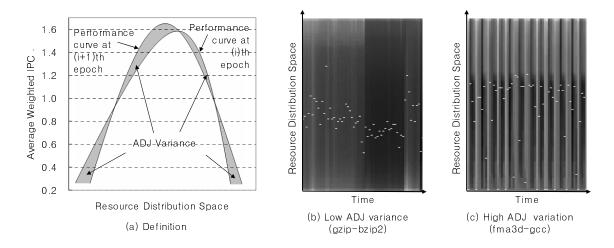

| 4.7  | ADJ variance metric measures the performance difference between two ad-<br>jacent epochs by diff-ing two performance curves.                                                                                                                                                                                                                                                                                                                                                                                                                            | 46 |

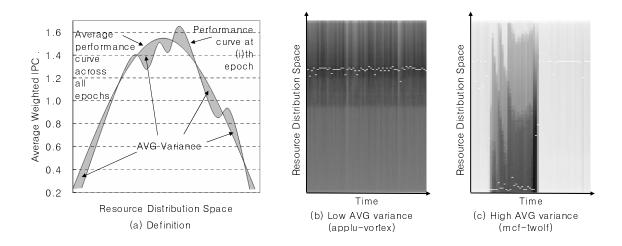

| 4.8  | AVG variance metric measures the performance difference between the current curve and the averaged one.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46 |

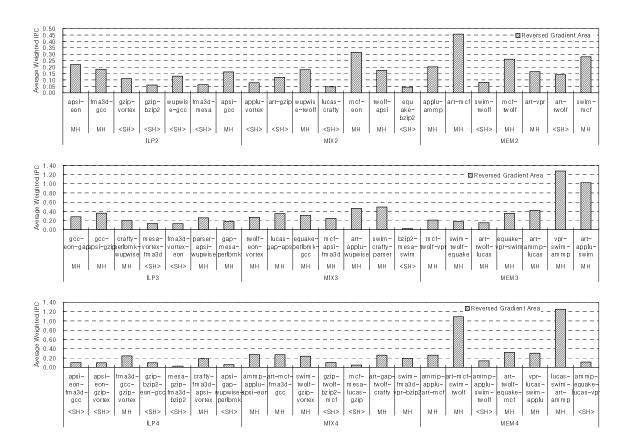

| 4.9  | Reversed gradient area (a local maxima metric for OFF-LINE-Analysis, as illustrated in Figure 4.5) of our 63 workloads. Large reversed gradient area means many local maxima. Based on the condition in Table 4.5, workloads are classified as either single hump (SH) or multiple humps (MH)                                                                                                                                                                                                                                                           | 50 |

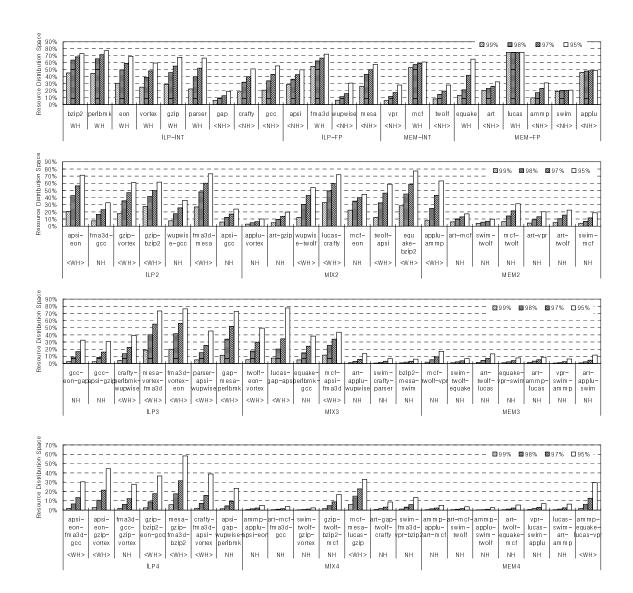

| 4.10 | Hill-width (a metric illustrated in Figure 4.6) of our 63 workloads. Wide hill width means that we can achieve good performance from a wide range of less optimal resource distribution. Based on the condition in Table 4.5, workloads are classified as either wide hill (WH) or narrow hill (NH)                                                                                                                                                                                                                                                     | 51 |

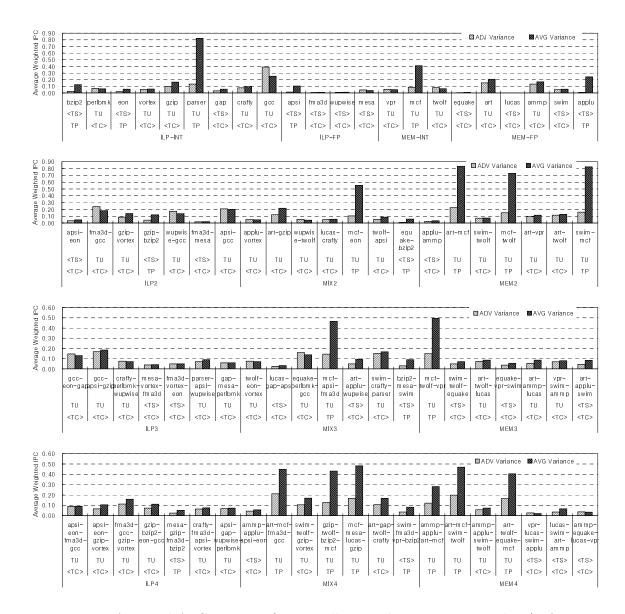

| 4.11 | ADJ and AVG variance (metrics illustrated in Figure 4.7 and 4.8) of our 63 workloads. High ADJ variance means high frequency performance variation over time. Based on the condition in Table 4.5, ADJ variance metric classifies workloads into temporally stable (TS) and temporally unstable (TU). High AVG variance means either high or(and) low frequent performance variation over the execution time. Based on the condition in Table 4.5, AVG variance metric classifies workloads into temporally consistent (TS) and temporally phased (TP). | 52 |

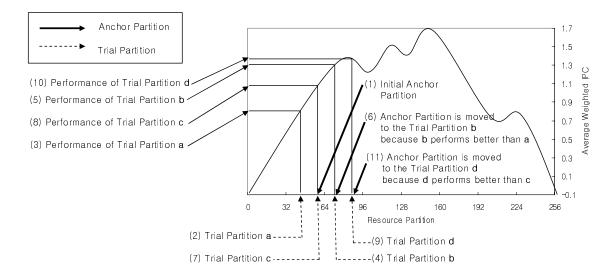

| 5.1  | Hill-climbing algorithm pseudo-code. Shaded box (a) chooses a new par-<br>tition based on samples acquired by shaded box (b) among all possible<br>directions from the currently best partition, anchor_partition                                                                                                                                                                                                                                                                                                                                       | 58 |

| 5.2  | Hill-climbing algorithm working example. The position of the anchor_partition is determined by the performance outcome of the earlier trial_partitions. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                        | 58 |

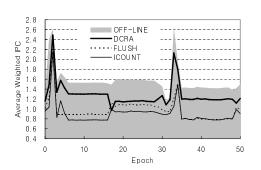

| 6.1  | Synchronized time-varying performance of OFF-LINE-Search, DCRA, FLUSH, and ICOUNT from the art-mcf workload.                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71 |

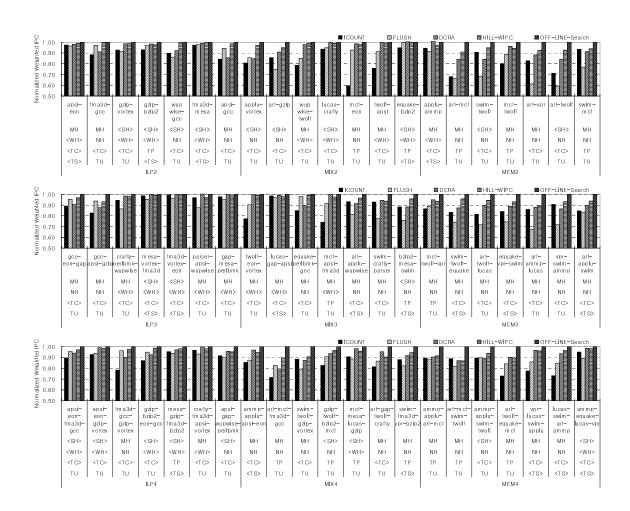

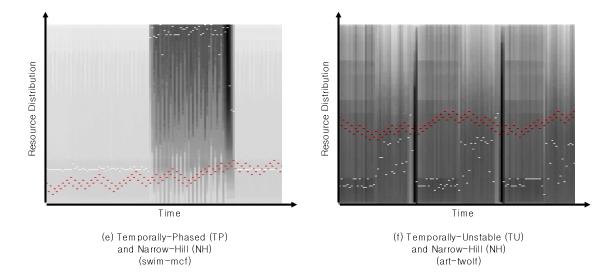

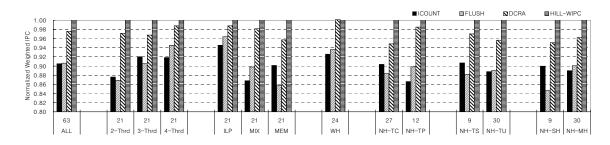

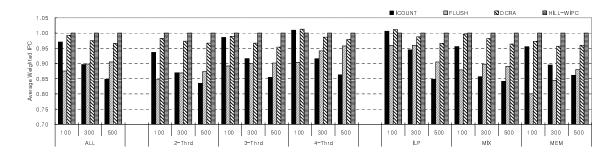

| 6.2  | The weighted IPC of ICOUNT, FLUSH, DCRA, and HILL-WIPC normal-<br>ized against OFF-LINE-Search. The labels (SH/MH, WH/NH, TC/TP,<br>and TS/TU) from the OFF-LINE-Analysis are added to each workload to<br>present the correlation between SMT performance and workload character-<br>istics.                                                                                                                                                                                                                                                           | 73 |

| 6.3  | The weighted IPC of ICOUNT, FLUSH, DCRA, and HILL-WIPC normal-<br>ized against OFF-LINE-Search by the workload type and characteristics.<br>The first X-axis label indicates the number of workloads that belongs to<br>the workload type/characteristics specified in the second X-axis label                                                                                                                                                                                                                                                          | 73 |

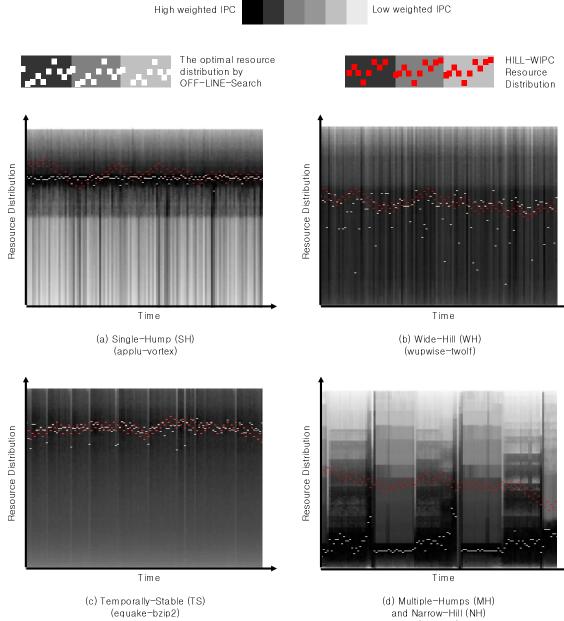

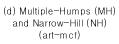

| 6.4 | Three workload examples with rich locality of performance: (a) single hump, (b) wide hill, and (c) temporally stable, and three workload examples with performance hazards: (d) multiple humps, (e) temporally phased, and (f) temporally unstable. The white dots indicate the optimal resource distribution, and the red dots indicate the resource distribution that HILL-WIPC finds. | 80  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

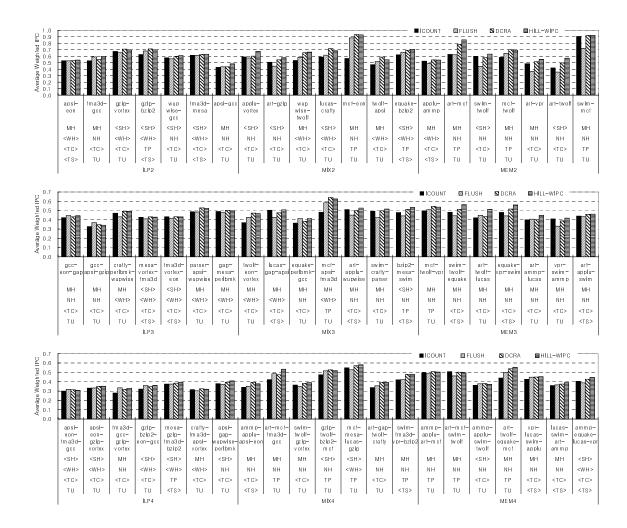

| 7.1 | The weighted IPC of ICOUNT, FLUSH, DCRA, and HILL-WIPC for all 63 workloads. Run-time characteristics and type are labeled on each workload.                                                                                                                                                                                                                                             | 85  |

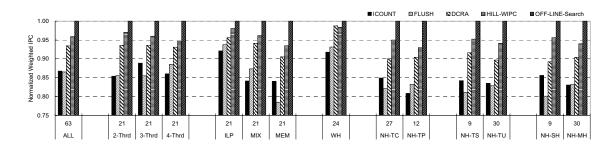

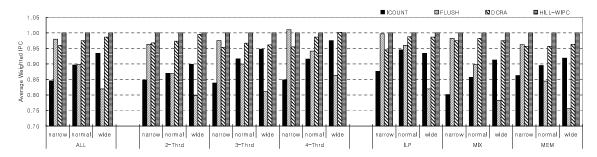

| 7.2 | The weighted IPC of ICOUNT, FLUSH, DCRA, and HILL-WIPC by the workload type and characteristics. All bars are normalized against HILL-WIPC.                                                                                                                                                                                                                                              | 85  |

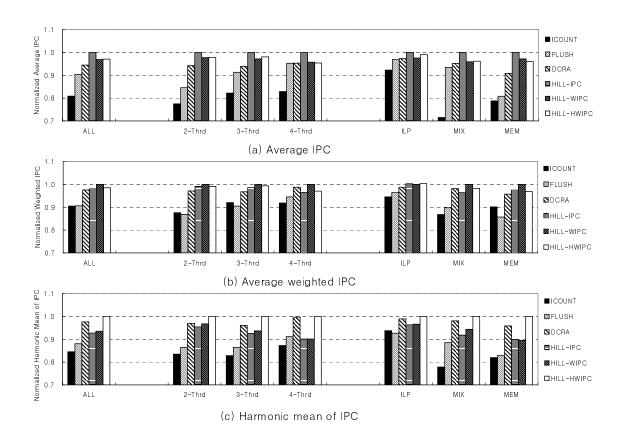

| 7.3 | Hill-Climbing versus ICOUNT, FLUSH, and DCRA under the (a) average IPC, (b) weighted IPC, and (c) harmonic mean of weighted IPC metrics.<br>Hill-Climbing uses average IPC (HILL-IPC), weighted IPC (HILL-WIPC), and harmonic mean of weighted IPC (HILL-HWIPC) as the performance-feedback metric.                                                                                      | 88  |

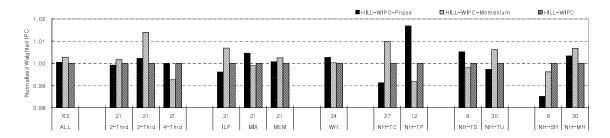

| 7.4 | Improving the baseline hill-climbing resource distribution. Hill-WIPC-Phase trains the resource distribution per phase basis. HILL-WIPC-Momentum uses momentum term to jump over the small jitters. All bars are normalized against HILL-WIPC.                                                                                                                                           | 90  |

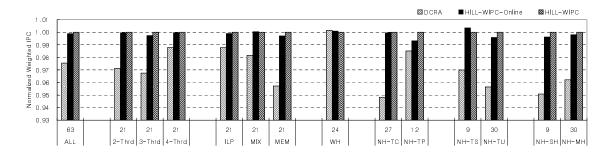

| 8.1 | Stand-alone IPC computation overhead. HILL-WIPC-Online computes the stand-alone IPC at run-time. All bars are normalized against the HILL-WIPC.                                                                                                                                                                                                                                          | 95  |

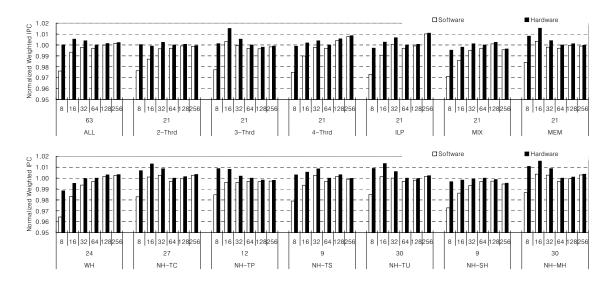

| 8.2 | The resource distribution overhead of software and hardware implementa-<br>tion as we vary the epoch size from 8K to 256K cycle. All bars are normal-<br>ized against 64K epoch size performance of hardware implementation                                                                                                                                                              | 97  |

| 8.3 | The weighted IPC of ICOUNT, FLUSH, DCRA, and HILL-WIPC as we vary the memory latency from 100 to 500 cycle. All bars are normalized against HILL-WIPC.                                                                                                                                                                                                                                   | 98  |

| 8.4 | The weighted IPC of ICOUNT, FLUSH, DCRA, and HILL-WIPC as we vary processor resource budget to "half" and "double." All bars are normalized against HILL-WIPC.                                                                                                                                                                                                                           | 99  |

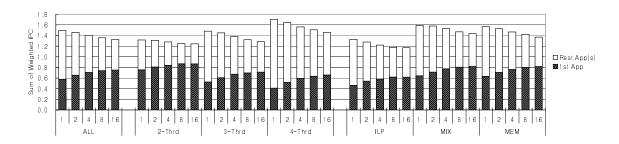

| 8.5 | The effect of prioritizing the first thread. Shaded bars show the weighted IPC of the first thread and white bars show the sum of the weighted IPC of the rest of the thread(s), as we vary the priority of the first thread from 1 to 16.                                                                                                                                               | 100 |

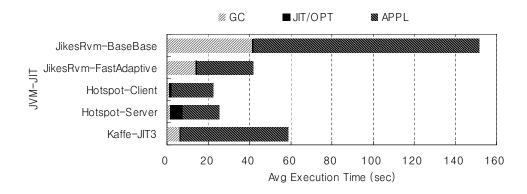

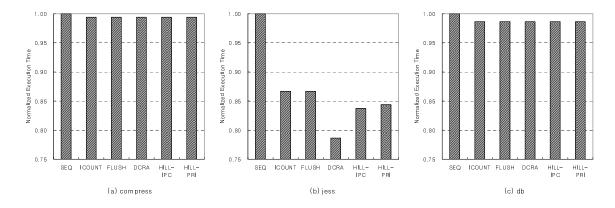

- 9.2 The normalized execution time of three SPECjvm98 applications with sequential garbage collection (labeled "SEQ") and parallel garbage collections (labeled "ICOUNT", "FLUSH", "DCRA", "HILL-IPC", and "HILL-PRI"). 107

# Chapter 1

# Introduction

## 1.1 Motivation

# 1.1.1 Simultaneous Multithreading Processors

Shared memory multiprocessor design is a natural extension of the mass produced microprocessors and yields linear or sub-linear scale performance enhancement for welldesigned parallel applications. In the past, small-scale to massively parallel multiprocessors were built to exploit thread level parallelism. Recently, single chip multi-threading processors have been actively studied. Single chip multi-threading processors allow concurrent execution of multiple threads with a single chip by maintaining multiple hardware contexts on a chip. This architecture effectively utilizes ever increasing available hardware budget in a single chip module, which is predicted by Moore's law. In addition, this architecture is a cost-effective way of exploiting thread-level parallelism because instead of having dedicated hardware resources per thread, it allows some of the on-chip hardware resources to be shared between concurrently running multiple threads thus increasing the resource utilization.

One implementation of a single chip multi-threading processor is the simultaneous multi-threading (SMT) processor [1, 2, 3], which executes multiple threads in a single chip by allowing fine grained sharing of most of the processor resources. Because a single thread typically cannot fully utilize all of a processor's available resources, fine-grained processor resource sharing improves overall resource utilization. The increased utilization directly

translates into higher processor throughput. SMT is an important architectural technique, as evidenced by the widespread attention it has received from academia [4, 5, 1, 6, 7], and by industry's willingness to incorporate it into commercial processors [8, 9]. Given single chip multi-threading will continue to be an important architectural direction, research that improves SMT performance without increasing its cost, like power consumption or fabrication cost, will remain highly relevant in future systems.

## 1.1.2 Feedback-based SMT processor resource distribution

SMT processors improve performance by allowing multiple threads to share most of the hardware resources. However, the actual performance gain of SMT processors depends greatly on how resources are distributed to individual threads. High performance occurs only when resources are distributed to those threads that will use them efficiently. Otherwise, the shared resource may be monopolized by a thread that just holds the resource for a long time during the long latency operation, making other threads to wait for the release of the resource. Hence, the mechanism for controlling resource distribution among the simultaneously executing threads play a critical role in achieving good SMT performance.

Several resource distribution techniques have been studied in the past [4, 5, 1, 6, 7]; all of them try to increase performance by reducing the amount of time instructions stall in shared processor resources. While existing resource distribution techniques have demonstrated good performance gains, one shortcoming is they optimize performance *indirectly*. As illustrated in Figure 1.1(a), resource distribution decisions are made based on hardware monitors that indicate per-thread resource usage (for example, instruction occupancy or cache miss counts); the hardware monitors may not be correlated with the actual perfor-

Figure 1.1: (a) Existing resource distribution techniques optimize performance indirectly by making decisions based on hardware monitors only. (b) Learning-based resource distribution examines actual performance (e.g., IPC) to learn the optimal resource distribution.

mance. From resource usage information, the resource distribution mechanisms can infer potential performance bottlenecks and take actions to try to alleviate them. For example, some of the techniques, such as ICOUNT [1], reduce fetch priority of a thread that consumes too many entries in the instruction fetch queue and issue queue. FLUSH [6] flushes instructions from the pipeline that belong to a thread with outstanding L2 cache miss. FPG [10] reduces fetch priority of a thread if the thread's branch prediction confidence is low. DCRA [4] reduces the resource partition of a thread if the thread has no L1 cache misses.

These actions are designed to improve performance; however, their actual performance impact on the application workload is unknown since the resource distribution mechanisms never re-evaluate their decisions at run-time by monitoring the end performance resulting from their resource distribution. Because resource distribution mechanisms optimize performance only *indirectly*, opportunities for performance gains may be missed for two reasons. First, resource distribution mechanisms are designed to target a small set of important performance bottlenecks; however, SMT processors exhibit a myriad of behaviors that are highly sensitive to the application workload mix. Existing resource distribution mechanisms cannot possibly anticipate all bottlenecks for all workloads. Second, even for the anticipated performance bottlenecks, further performance gains might still be possible because they are designed to achieve the better-not the optimal-performance.

We propose a different approach to SMT processor resource distribution that optimizes end performance *directly*. Our approach observes the impact that resource distribution decisions have on performance at run-time and feeds this information back to the resource distribution mechanisms to improve future decisions, as illustrated in Figure 1.1(b). By successively applying and evaluating different resource distributions, our approach tries to search for the best distribution over time. Because our approach searches for the optimal resource distribution based on actual performance feedback, the resource distribution decisions it makes are customized to the specific performance bottlenecks of each workload, reducing missed performance opportunities.

While similar feedback-based optimizations have been applied to run-time hardware optimization studies [11, 12, 13, 14], we are the first to apply performance feedback to SMT processor resource distribution.

# 1.1.3 Hill-Shaped SMT Processor Performance Curve

There are two ways of balancing SMT processor resource: *fetch policy* and *resource partitioning*. Fetch policy selects threads to fetch from every cycle. ICOUNT [1], FPG [10] STALL [6], and FLUSH [6] are examples of fetch policy. Resource partitioning balances the resource distribution across concurrently running threads by explicitly maintaining allowed resource share per thread. DCRA [4] and static partitioning [15, 16, 7] are examples of resource partitioning. Resource partitioning can rely on fetch policy to enforce its resource partition. For example, if a thread consumes beyond the given partition, fetch of the thread is stalled (STALL) or excessively used resources are preempted (FLUSH). We will detail

fetch policy and resource partition in Section 3.2.

Our technique maintains resource partition to explicitly distribute the shared resources among the concurrent threads, and stalls fetching of a thread if the thread consumes resources up to its partition.

To collect the feedback information, we divide SMT execution into fixed intervals in time, which we call *epochs*. At the beginning of each epoch, we set a resource partition. Then, at the end of each epoch, we measure the performance of the SMT processor during the epoch. Based on the collected history information on different resource partitions and their corresponding performance feedback, our mechanism searches for the best resource partition for the current workload. The success of our approach depends on the searching speed because we can enjoy maximum performance benefit only after our mechanism reaches (or approaches to) the optimal resource distribution.

A key observation that enables fast searching is that performance, as a function of resource distribution, does not change randomly; instead, the performance sensitivity is often "hill-shaped." In addition, the shape of the hill does not change randomly over time. Figure 1.2(a) illustrates this observation by showing the time-varying performance curve of two applications–applu and vortex–running simultaneously on an SMT processor for 30 epochs. Figure 1.2(b) shows the performance curve of three applications–mesa, vortex, and fma3d–running simultaneously on an SMT processor during an epoch. These graphs plot weighted IPC [17], one possible performance metric, as the resource partitions of individual threads are varied. In the figure, performance follows a well-defined hill shape, with a clear performance peak, and the hill shape is stable over time.

We exploit this behavior by using a *hill-climbing algorithm* [18] to search for the best resource distribution. Because searching is guided by the slope of the hill, our hill-

Figure 1.2: Performance, measured in weighted IPC metric, of (a) applu and vortex, and (b) mesa, vortex, and fma3d running simultaneously on an SMT processor, as the fraction of resources allowed to each application is varied. In (a), the Y-axis shows the amount of resources allowed to applu (vortex receives the remaining resources), and the X-axis shows the time. In (b), the X- and Y-axes show the amount of resources allowed to mesa and vortex (fma3d receives the remaining resources). The labeled arrow indicates the resource distribution that achieves peak performance.

climbing algorithm reaches the optimal resource distribution (*i.e.*, the peak of the hill) after sampling only a small portion of the resource distribution space, thus leading to low searching times.

One of the most important attributes that leads to the success of the hill-climbing algorithm is the *shape of the hill* (*i.e.*, the run-time behavior of the SMT processor performance curve). Several pitfalls related to the shape of the hill may defeat the hill-climbing algorithm. For example, if the hill has multiple humps, the hill-climbing algorithm may be trapped at one of local maxima. In addition, if the shape of the hill changes very frequently, the hill-climbing algorithm may not find an optimal resource distribution, or it may find a temporally optimized resource distribution that performs poorly in the near future. As the quality of resource distribution provided by the hill-climbing algorithm is highly affected by the shape of the hill, we conduct in-depth research on the time-varying shape of the hill in Chapter 4 before we design (in Chapter 5) and evaluate (in Chapter 6 and 7) our hill-climbing algorithm.

## 1.2 Contributions

This dissertation makes the following contributions.

Viewing SMT Processor Resource Distribution Problem as a Classical Optimization Problem

The performance of SMT processor is mainly determined by the resource distribution among the concurrently running threads. So, we view the SMT processor resource distribution problem as a search problem whose goal is finding a resource distribution that produces optimal performance. We believe this is a unique view in the SMT processor resource distribution study. This view makes us translate the resource distribution problem into a classical optimization problem, allowing us to apply general optimization problem solvers, hill-climbing algorithm, to SMT processor domain. In this dissertation, we first define the performance curve as a function of SMT processor resource distribution. Then, we design the hill-climbing algorithm that climbs up to the peak of the curve to search for the optimal resource distribution.

## Development of SMT Processor Run-Time Performance Behavior Visualization Tool

The nature of SMT processor performance as a function of the resource distribution space is unknown prior to our research. In order to understand the time-varying behavior of this SMT processor performance curve, we built a visualization tool. Using this tool, we identified several workload characteristics. Some characteristics are problematic for hill-climbing algorithm like multiple humps or extremely frequent time-varying behavior. On the other hand, many workloads have favorable characteristics to the hill-climbing, like single hump and stable temporal behavior.

#### Quantitative Analysis of SMT Processor Run-Time Performance Behavior

Based on the knowledge acquired through the visualization tool, we developed four new metrics that quantitatively measure the shape of the performance curve. Two metrics quantify the static shape of the performance curve and two metrics measure the temporal variation of the performance curve. Using these metrics, we classify workloads. This classification helps understanding and analyzing the performance of prior SMT processor resource distribution techniques as well as our hill-climbing technique because of the strong correlation between run-time workload characteristics and its performance.

### Hill-Climbing Resource Distribution Algorithm

We are the first to apply the hill-climbing algorithm to SMT processor resource distribution problem. The understanding of the time-varying performance curve from both the visualization tool and quantitative measurement enable us to customize the hill-climbing algorithm for the SMT processor resource distribution. We design our hillclimbing algorithm so that it can handle both problematic workload as well as the favorable workload characteristics.

## Evaluation of the Hill-Climbing Resource Distribution

We faithfully evaluate the performance of the hill-climbing resource distribution technique across 63 workloads. Then, we compare the performance of hill-climbing algorithm against three prior SMT processor resource distribution techniques: ICOUNT, FLUSH, and DCRA. We suggest two improvements over the baseline hill-climbing resource distribution: phase based learning and hill-climbing with momentum term. In addition, we study hill-climbing resource distribution's sensitivity to three design parameters; memory latency, amount of processor resource, and thread priority.

# SMT Processor Performance Limit Study

A performance comparison of existing resource distribution techniques against an ideal SMT processor can uncover performance bottlenecks and suggest ways to improve performance. However, figuring out the ideal performance limit of SMT processor is computationally infeasible because it is an NP-hard problem. For the first time in SMT study, we developed a heuristic that approximates the ideal performance limit of SMT processor. To make our heuristic computationally feasible, we assumed three simplifying constraints; first, per-thread resource partition is maintained to distribute resources, second, updating resource partition is allowed only at every epoch boundary, and third oracle provides information only on the next epoch. Using the performance limit suggested by our heuristic, we re-evaluate four SMT processor resource distribution techniques (including ours), detail their performance potentials, and show our mechanism is the closest to the performance limit.

## Extending Hill-Climbing technique

We show that hill-climbing is an effective mechanism for SMT processor resource distribution. Since hill-climbing algorithm is a general optimization problem solver, our technique can also be applied to more general problems, like run-time hardware optimization, which changes hardware parameters at run-time to achieve optimal performance or power consumption.

## 1.3 Road Map

The rest of the dissertation is organized as follows. Chapter 2 explains the background of our study including single chip multi-threading processors, issues on SMT processor resource distribution, and general hill-climbing algorithm. Chapter 3 lists the prior researches related to our study covering run-time hardware optimization study and SMT processor resource distribution techniques. In Chapter 4, we analyze the run-time behavior of SMT processors to better understand the time-varying performance curve. Based on this analysis, Chapter 5 presents the customized hill-climbing algorithm for SMT processor resource distribution problem domain. In Chapter 6, we show the performance of our heuristic that approximates the ideal performance limit of SMT processor and suggests the performance potential of the existing techniques. Chapter 7 evaluates the performance of hill-climbing resource distribution techniques and compares its performance against three existing techniques. Chapter 8 suggests directions to improve hill-climbing resource distribution and shows the sensitivity study results. Chapter 9 discusses the preliminary study on applying our hill-climbing technique to multi-treaded run-time system. Finally, Chapter 10 concludes the dissertation and suggests the future research directions.

# Chapter 2

## Background

### 2.1 Single Chip Multi-Threading Processors

Single chip multi-threading processors allow concurrent execution of multiple threads in a single chip by maintaining multiple on-chip hardware contexts. This architecture effectively utilizes ever increasing available hardware budget in a single chip module, which is predicted by Moore's law. In addition, this architecture is a cost-effective way of exploiting thread-level parallelism because it allows some of the on-chip hardware resources to be shared between concurrently running multiple threads, rather than dedicating them to each individual thread.

Depending on the design of the single chip multi-threading processors, the choice of the dedicated and shared hardware resources varies. Two extremes of single chip multithreading processor design are *chip multiprocessor* (CMP) and *simultaneous multithreading processor* (SMT). CMP [19, 20, 21, 22] has multiple processor cores in a single chip. Each core has its own dedicated processor resources (including branch predictor, fetch queue, issue queue, functional unit, memory port, register file, and reorder buffer) to execute a thread. However, multiple cores share the on-chip L1 and(or) L2 caches. SMT [1, 2, 3] allows execution of multiple threads in a single core by allowing fine grained sharing of most of the processor resources, as well as the L1 cache and L2 cache between concurrently running threads. The only dedicated resources to each thread are the program counter and additional storage to maintain context information (*e.g.*, architected register file).

Since the multiple cores in CMP are duplicates of a single core, CMP can use single

core design to implement multi-core CMP, thus simplifying the chip design. In addition, since each core in CMP is independent of each other, increasing the number of cores in a chip does not severely increase the complexity of the interconnections within a chip, making it scalable [20]. CMP may have either heterogeneous cores [21], with both powerful out-of-order processor core(s) mixed with simple small in-order processor core(s) in a chip, or homogeneous cores [19, 20]. Considering that the concurrently running threads may have diverse processor resource requirements, heterogeneous core CMP is an attractive design choice.

On the other hand, SMT can utilize the processor resource more efficiently because SMT allows one thread to use almost all of the shared resources when the other thread(s) cannot fully utilize them. In addition, SMT achieves higher per-core throughput by exploiting ILP between independent threads as well as within a single thread. The increased processor throughput provided by SMT, however, comes at the expense of single-thread performance. Because multiple threads share hardware resources at the same time, individual threads get fewer resources than they would have otherwise received had they been running alone. For threads with diverse characteristics, compared to heterogeneous CMP, SMT can give proper amount of resources to each thread dynamically by simply shifting the resource share between threads at run-time.

Due to these advantages of single chip multi-threading processor design, many CMP and SMT processors are commercially available these days. Intel Pentium4 with Hyperthreading [9] is an SMT product. IBM Power4, AMD Athlon64 dual core, Intel Pentium dual core, Intel Pentium quad core (Clovertown) are CMP products. IBM Power5 architecture [8] has two SMT cores in a single chip, making it an SMT and CMP hybrid. IBM Cell processor [23] has an SMT core, named PPE, and multiple CMP cores, named SPE, in a single chip, making it an SMT and heterogeneous CMP hybrid. On these commercial products, the detailed resource sharing structures are not well documented.

#### 2.2 SMT Processor Resource Distribution

In SMT processors, resource sharing between concurrently running threads allows better resource utilization because a single thread cannot fully utilize the available resources all the times. This increased resource utilization directly translates into the improved throughput. However, the resource distribution may be unbalanced losing the performance opportunities. For example, if the first thread holds large amount of shared resource and waits for the data from memory, the second thread cannot get any more resource until the first thread gets the data from the memory and releases the resource, thus reducing the resource utilization.

There are three types of shared processor resources. The first type is called a "slot", which includes fetch unit, issue unit, and functional units. A thread holds slot type resources for only one cycle. The second type is called a "queue", which includes fetch queue, issue queue, rename register, and reorder buffer. A thread can hold queue type resources for many cycles until the thread voluntarily releases the resource. The third type is called a "memory", which includes branch predictor tables and L1 cache. A thread can hold memory type resources for many cycles until the other threads claim them.

Figure 2.1 shows our classification of the shared resources. Among the three types of shared resources, only the second one, queue type, causes resource under-utilization problem because it may potentially participate in *hold-and-wait* condition and resource monopolization. Unbalanced resource distribution of slot type resource can be promptly fixed, if it happens and is detected. Unbalanced resource distribution of memory type

Figure 2.1: Block diagram of the SMT processor resources. The shared resources are classified into three types: slot type, queue type, and memory type. White boxes indicate private resources.

resource can be fixed after warming-up time.

Depending on the application characteristics and run-time phase, the amount of queue type resource requirement varies. Queue type resource is used to keep the in-flight instructions in the processor pipeline. In general, applications with high instruction level parallelism need many in-flight instructions to help find the parallelism, thus requiring many queue type resources. On the contrary, applications with long dependency chains can make progress with small amounts of queue type resources. Therefore, the balancing of the shared queue type resource distribution should take the application's current requests for the shared queue type resource into account. For example, L1 miss count (used by DCRA [4]), and the fetch / issue queue occupancy (used by ICOUNT [1]) can be used to *indirectly* figure out the application's requests for the shared queue type resource.

To correct unbalanced resource distribution, three fetch policies are used by the existing SMT resource distribution techniques. First, "fetch prioritizing" gives fetch priority to a thread, which deserves more resources. With this mechanism, after fetching from a high fetch priority thread, the low fetch priority thread can use the remaining fetch bandwidth. In addition, if the high fetch priority thread cannot use any of the fetch bandwidth due to branch misprediction or an instruction cache miss, the low fetch priority thread can fully utilize the fetch bandwidth. ICOUNT uses this mechanism. Second, "fetch stalling" stops fetching of a thread, which deserves fewer resources. Fetch-stalled threads cannot fetch any instructions, even if there are available fetch bandwidth. DCRA uses this mechanism. Third, "flushing" evicts instructions from the processor pipeline, whose thread deserves fewer resources. Flushing is the most timely way of balancing the resource distribution among the three existing mechanisms, but it is also the most costly as it needs to fetch the flushed instructions again. FLUSH [6] uses this mechanism. In Section 3.2, we will discuss the existing SMT processor resource distribution techniques, ICOUNT, FLUSH, and DCRA, in greater detail.

Our hill-climbing technique controls the allocation of the queue type resources as they affect the number of in-flight instructions in the pipeline and determines the achievable instruction level parallelism of each thread. In addition, our approach uses fetch stalling mechanism to maintain proper amount of queue type resource occupancy per thread. We will detail the ideal and implementation of our hill-climbing technique in Chapter 5.

# 2.3 Hill-Climbing Algorithm

Hill-climbing algorithm [18] is an optimization problem solver. Hill climbing attempts to maximize an evaluation function f(x) by finding the optimal x. In discrete domains, the domain of f is typically represented by vertices in a graph, where edges in the graph encode nearness or similarity of a graph. Hill climbing traverses the graph from

| 1.                | #define f evaluation function                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.                | current_vertex = initial_vertex;                                                                                                                                                                    |

| 3.<br>4.<br>5.    | <pre>do until (there is no change in current_vertex) {     for all (successor_vertex[i] = Get a successor of the current_vertex)         successor_vertex[i].score = f (successor_vertex[i]);</pre> |

| 6.<br>7.<br>8.    | <pre>if (one of the successor_vertex[*].score is better than the current_state)     current_vertex = the successor with the best score; }</pre>                                                     |

|                   | (a) Hill-climbing algorithm on discrete space                                                                                                                                                       |

| 9.<br>10.         | #define $\bigtriangledown f$ gradient of $f$ #defineDeltamovement step                                                                                                                              |

| 11.               | current_state = initial_state;                                                                                                                                                                      |

| 12.<br>13.<br>14. | <b>do until</b> (there is no change in current_stae) {<br>successor_state = current_state + ∇ <i>f</i> (current_state) * Delta;<br>successor_state.score = <i>f</i> (successor_state);              |

| 15.<br>16.<br>17. | <pre>if (successor_state.score is better than current_state's score)     current_state = successor_state; }</pre>                                                                                   |

|                   | (b) Hill-climbing algorithm on continuous space                                                                                                                                                     |

Figure 2.2: Hill-climbing algorithm on discrete domain space (a) and continuous domain space (b). In discrete domain space, the next vertex is picked among the neighboring vertices whose f value is the best (line 4-7). In continuous domain space, the next state is directed by the gradient vector (line 13-16).

vertex to vertex, always heading towards the locally increasing value of f, until a local maximum is reached. Hill climbing can also operate on a continuous domain space: in that case, the algorithm is called *gradient ascent*. Hill climbing is guided by the gradient vector in choosing the next state. Hill climbing terminates when there are no successors of the current state which are better than the current state itself. Figure 2.2(a) and (b) show the hill-climbing algorithm on discrete and continuous domain spaces, respectively. Note, the algorithm does not attempt to exhaustively try every vertex and edge (or the entire search space in the continuous domain case), so no previously visited vertex list is maintained-the algorithm only tracks the current vertex being visited.

One problem with hill-climbing algorithm is *local maxima* in the search space, where

the current state gets trapped causing the algorithm to terminate before finding the optimal state. There are several ways we can get around this problem with varying degree of success by extending the algorithm. We can use a limited amount of *backtracking* so that we record alternative reasonable looking paths which weren't taken and go back to them. Alternatively, we can use the *momentum term* by giving weight to the preceding movement direction to allow jumping over the small local maxima on the way to the optimal state. However, none of these solutions are perfect. Another extension is multiple restart stochastic hill-climbing (MRSH) [24], which simply runs an outer loop over hill-climbing. Each step of the outer loop chooses a random initial state to restart hill-climbing. The best state is kept: if a new run of hill-climbing produces a better state than the stored state, it replaces the stored state. Since at least one of the hill-climbing runs is likely to reach the optimal state successfully, MRSH is surprisingly effective in many cases.

# Chapter 3

## Related Work

### 3.1 Run-time Hardware Optimization

Processors are designed to achieve good average performance across various applications. At run-time, however, the usage of the processor resources is unbalanced; some resources are fully utilized and others are under-utilized. The unbalanced resource utilization happens because application's demand for the resource is diverse and the demand also changes over time even within an application.

To deal with the unbalanced resource utilization problem, run-time hardware optimization techniques have attempted to match the hardware configuration to the running application's resource demand by allowing some degree of flexibility in the hardware design. SMT processor resource distribution techniques [1, 10, 6, 5, 4] also tune multiple hardware parameters (*i.e.*, resource partition or fetch priority of each thread) at run-time to adapt to the time-varying application characteristics. Therefore, SMT processor resource distribution is a specific field of run-time hardware optimization study. In this section, we will compare several run-time hardware optimization studies in terms of three aspects: optimization goal, optimal configuration finding method, and configuration update frequency.

# **Optimization** Goal

There are two goals of any run-time hardware optimization. The first goal is "achieving better performance." For better performance, under-utilized hardware budget must be shifted to support heavily used resources, thus removing the performance bottleneck. For example, part of the functional unit in a host processor [25, 26] or independent coprocessor [27, 28, 29, 30] are reconfigured using FPGA to achieve optimal performance for the target application. Balasubramonian, *et al.* [13] use configurable cache organization to find the best on-chip memory partition between L1 and L2 cache for the current phase of the application. All SMT processor resource distribution techniques fix the unbalanced resource distribution by shifting the resource between concurrently running threads.

The second goal is "saving power consumption." To save power, under-utilized devices are dynamically turned off or slowed down. For example, Buyuktosunoglu, *et al.* [14] dynamically disable some of the issue queue entries based on the issue queue utilization. Manne, *et al.* [31] reduce the number of flushed instructions due to branch misprediction by preventing instruction fetching if the number of low-confidence branch predictions exceeds a threshold. Banasadi, *et al.* [32] gate the decode pipeline if the number of instructions to be decoded is less than the decode bandwidth. Karkhanis, *et al.* [12] dynamically control the maximum number of in-flight instructions in the pipeline to save power.

Even with two distinct goals in run-time hardware optimization, the techniques used for one goal can be easily applied to the other goal. For example, both studies in [31] and [10] use the confidence of the branch prediction to either save power or improve the performance.

### **Optimal Configuration Finding Method**

To maximize the goal of run-time hardware optimization, three techniques have been studied to find the best configuration at run-time. The first technique "exhaustively tries" all possible configurations, and then picks the best performing one. This approach is useful if the search space volume is very small [12]. The second technique "searches" for the optimal configurations by trying a carefully chosen sequence of configurations and then picking the best performing one. The techniques used in [13, 14] carefully increment or decrement the L1 cache or issue queue size depending on the recent performance feedback. Our hill-climbing SMT processor resource distribution uses this technique to find the optimal resource distribution. This approach increases the search speed compared to the exhaustive trials, making it applicable to large search space. The third technique "loads" one of the pre-defined configurations based on indicators. All FPGA based systems load pre-defined configurations at start-up of an application or periodically during runtime [25, 26, 27, 28, 29, 30]. Prior SMT processor resource distribution techniques rely on indicators (*e.g.* L1 / L2 cache miss count, resource occupancy, or branch misprediction count) to change the resource partition or fetch priority at run-time.

The third approach is useful if the search space volume is huge or the configuration should be chosen promptly. On the contrary, the first two approaches use the *feedback* information from the trial configurations to pick the best performing one, thus delaying the decision making time. In addition, trying all the configuration or searching for the optimal configuration out of a huge search space may require too many trials before we find the optimal one. However, the third approach determines the configuration based on the indicators without actually trying and measuring the performance of the alternative configurations. Furthermore, the indicators may not be expressive enough to show the myriad resource requirement scenarios of the application. Therefore, there is a danger that the configuration picked by indicators may be a non-optimal one.

## Configuration Update Frequency

There is a spectrum of configuration update frequencies. First, if the configuration update overhead is very high, the configuration is updated at the "application start-up time." Most of the FPGA based techniques load the pre-defined configuration at the application start-up time because loading the FPGA configuration (*i.e.*, netlist) takes at least a few minutes. Second, the configuration can be changed only when the "phase of the application shifts." Most of the cache reconfiguration techniques update the configuration when the phase of the application changes because the changing cache configuration requires invalidation of all the cache lines [13]. Third, the configuration can be updated "every fixed interval in time." Both adaptive clock frequency [33] and adaptive issue queue size [14] techniques update the configuration every fixed interval. Our hill-climbing SMT processor resource distribution also updates the resource partition every fixed interval. Fourth, the configuration is updated "every cycle." All the prior SMT processor resource distribution techniques update resource partition or fetch priority dynamically every cycle to adapt to the cycle-by-cycle changing application behavior.

There is a trade-off in determining the hardware configuration update frequency. As we increase the update frequency, the hardware adapts to the time-varying application characteristics quickly. However, with high frequency update, the run-time overhead increases due to the frequent configuration flushing operations, finding new configurations, and new configuration loading time. In addition, techniques to reduce the run-time overhead (specifically reducing "finding new configuration time") may lead to low-quality configurations.

The goal of our hill-climbing SMT processor resource distribution is to improve per-

formance. Our approach's method of finding the optimal configuration is searching after attempting a few trial configurations. The configuration is updated at every fixed intervals. Compared to the other run-time hardware optimization techniques, the uniqueness of our approach is that the sequence of the trial configurations is *systematically defined based on the hill-climbing algorithm*. Therefore, our approach reduces the number of trials, minimizes the search overhead, is expandable to huge and multi-dimensional search spaces, and provides high quality configurations. Compared to prior SMT processor resource distribution techniques, the uniqueness of our approach is *searching* for the optimal configuration out of a large number of possible configurations using feedback information, and *fixed interval* granularity configuration update.

# 3.2 SMT Processor Resource Distribution

Prior research has tried to boost SMT processor performance by improving the distribution of hardware resources to threads. One important approach is to optimize the selection of threads to fetch every cycle. ICOUNT [1] and FPG [10] are examples of such SMT fetch policies. These techniques monitor indicators of resource usage, such as resource occupancy (ICOUNT) or branch prediction accuracy (FPG). Every cycle, the threads using their resources most efficiently (*e.g.*, with low occupancy or few branch miss-predicts) are given fetch priority. By favoring efficient threads, ICOUNT and FPG increase overall throughput.

Unfortunately, fetch policies do not effectively handle long-latency operations, especially cache-missing loads. Once a thread suffers a long-latency cache-missing load, continuing to fetch the thread clogs the pipeline with stalled instructions, preventing other threads that would otherwise gainfully use the resources from receiving them. Fetch policies like ICOUNT reduce, but do not stop, the fetch of stalled threads, so they cannot prevent resource clog. Several techniques address resource clog by explicitly limiting resource distribution to threads with long-latency memory operations. The first approach is to fetch-stall the threads when they suffer long-latency memory operations. Techniques in this category differ in how they detect the stall condition. STALL [6] triggers fetch-stall when a load remains outstanding beyond some threshold number of cycles; DG [5] triggers fetch-stall when the number of cache-missing loads exceeds some threshold; and PDG [5] uses a cache-miss predictor to trigger fetch-stall.

One problem with fetch-stalling is resource clog can still occur because the stall condition is detected either too late or unreliably. Instead of anticipating resource clog and fetch-stalling, a second approach allows resource clog to occur but immediately recovers it by flushing the stalled instructions. This is the approach taken by FLUSH [6]. FLUSH is effective in preventing resource clog; however, flushing is wasteful in terms of fetch bandwidth and power consumption. Hybrid approaches (*e.g.*, STALL-FLUSH [6]) minimize the number of flushed instructions by first employing fetch-stall, and resorting to flushing only when resources are exhausted.

Finally, a third approach is to partition the processor resources. The simplest is static partitioning [15, 16, 7], but these techniques cannot adapt to changing workload behavior. In contrast, DCRA [4] partitions dynamically based on memory performance. Threads with frequent L1 cache misses are given large partitions, allowing them to exploit parallelism beyond stalled memory operations. Threads that cache-miss infrequently are guaranteed some resource share since stalled threads are not allowed beyond their partitions. Hence, DCRA prevents resource clog by containing stalled threads. Moreover, DCRA computes partitions based on the threads' anticipated resource needs, increasing partition of the threads that can use resources most efficiently.

Compared to previous techniques, hill-climbing resource distribution is most similar to DCRA. Like DCRA, our approach also uses dynamic partitioning to address resource clog and improve resource usage efficiency. However, a key distinction is our technique makes partitioning decisions based on performance *feedback*, thus optimizing end performance as illustrated in Figure 1.1. In contrast, DCRA and other previous techniques perform resource distribution based on hardware monitors like resource occupancy or cache miss counts. Hence, they optimize performance only indirectly, potentially missing opportunities for performance gains, as discussed in Chapter 1. An added benefit of exploiting feedback is we can optimize to a user-definable performance goal–like throughput, per-thread speedup, or fairness–by simply changing the performance metric used for the performance feedback. Previous techniques cannot tailor their optimizations to a specific performance goal. Lastly, because it takes time for our hill-climbing algorithm to process performance feedback, we update partitioning decisions at every *fixed interval*. Thus, our technique lies somewhere in between DCRA (update every cycle) and static partitioning (fixed) in terms of its responsiveness to dynamic runtime behavior.

## Chapter 4

## SMT Processor Run-Time Performance Behavior Analysis

The performance of SMT processor is mainly determined by the resource distribution among the concurrently running threads. Therefore, both of the existing techniques, fetch polices and resource partitioning techniques, attempt to implicitly and explicitly balance the resource distribution. To find out the best resource distribution, we propose a unique approach. We view the SMT processor resource distribution problem as the searching for the maximum performance in resource distribution space. This view allows us to translate the resource distribution problem into the classical optimization problem. Since the shape of the performance curve looks like hill, as illustrated in Figure 1.2, we apply a general optimization problem solver, hill-climbing algorithm, to the SMT processor resource distribution problem.

In this chapter, we define the performance curve on which we make our hill-climbing algorithm to climb up to search for the optimal resource distribution. Since, the nature of SMT processor performance curve is unknown as is defined and used in our research for the first time, in this chapter, we perform in-depth analysis of the performance curve and provide its look-and-feel. The analysis on the performance curve guides the design of our hill-climbing algorithm (in Chapter 5) and helps understanding the experimental results (in Chapter 6, 7, and 8).

#### 4.1 Performance Curve

To distribute resources among the concurrently running threads, we maintain resource partition for each thread. During the execution, threads are allowed to consume up to (but no more than) the allotted resources within their partition. Hence, partitioning guarantees every thread to receive some fraction of each shared resource. All possible combinations of the resource partition among the threads constitute the *resource distribution space*. As the performance of a resource partition can change over time to adapt to the changing the application behavior, we define the *performance curve*  $f_i$  at a point in time *i* as Equation 4.1.

$$f_i: resource \ distribution \ space \longmapsto performance$$

(4.1)

This hypothetical performance curve maps a resource distribution at a point in time to its performance outcome. This performance curve is the target hill where our hill-climbing algorithm searches for the peak.

The nature of the hills, (*i.e.*, performance curve) in our study are different from the hills that traditional hill-climbing algorithms assume. As described in Section 2.3, traditional hill-climbing algorithms assume fixed hills. But, in our case, the shape of the hill changes over time as the characteristics of the applications running on SMT processor change. Therefore, the peak of the hill is a moving target for which our mechanism should search.

As a first step of our research, we perform in-depth analysis on the performance curve, named *OFF-LINE-Analysis*, because the performance curve is defined and used for the first time in our research. As we will show in Chapter 7, the advantage of hill-climbing resource distribution highly relies on the shape of the performance curve. OFF-LINE- Analysis schedules resources off-line to get the perfect knowledge of the performance curve. So, this analysis provides an oracle view which any real implementation is unable to figure out at run-time and allows in-depth insight into the performance curve.

## 4.2 OFF-LINE-Analysis

The goal of OFF-LINE-Analysis is to provide the global view of the performance curve. To achieve this goal, OFF-LINE-Analysis tries to discover the whole mapping of the performance evaluation function  $f_i$  for all *i*'s in Equation 4.1 by trying all data point in resource distribution space.

## 4.2.1 Implementation Issues

There are two issues in providing the global view of the time-varying hill-shaped performance curve.

#### Huge Volume of the Resource Distribution Space