**ABSTRACT**

Title of Document: DESIGN OF A WIRELESS FISH LENGTH

MEASURING BOARD FOR FISHERIES

RESEARCH

Omar Farooq Amin, Master of Science, 2006

Directed By: Associate Professor, Omar Ramahi, Department

of Electrical and Computer Engineering,

University of Waterloo.

The goal of this work is to design and implement the fundamental technology needed to construct a wireless fish measuring board that performs non-contact length measurements. After taking the measurement, the board sends the information containing the length of the fish amongst other parameters wirelessly to a receiver located several meters away. The receiver in turn decodes the information and sends it for display on a computer monitor. The wireless transmission must be immune to the typical non-line of sight (NLOS) environments that are found in the fisheries industry. The non-contact technique used here is based on the Hall-effect sensing mechanism. The wireless link operates in the 902-928MHz Industrial, Scientific and Medical (ISM) band. The entire system was fully developed using Commercial Off-the-Shelf (COTS) components and is shown to perform satisfactorily in typical NLOS environment.

# DESIGN OF A WIRELESS FISH LENGTH MEASURING BOARD FOR FISHERIES RESEARCH

By

Omar Farooq Amin

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Master of Science 2006

Advisory Committee: Professor Omar Ramahi, Chair Professor Bruce Jacob Professor Victor Granatstein

© Copyright by Omar Farooq Amin 2006

## **DEDICATION**

To my family.

## ACKNOWLEDGEMENTS

Thanks to Professor Ramahi for all his help and the family for all the support.

## TABLE OF CONTENTS

| DEDICATION                            | ii  |

|---------------------------------------|-----|

| ACKNOWLEDGEMENTS                      | iii |

| TABLE OF CONTENTS                     | iv  |

| LIST OF TABLES                        | vi  |

| LIST OF FIGURES                       |     |

| CHAPTER 1: GENERAL INTRODUCTION       |     |

| Objectives                            |     |

| Available Technologies                | 1   |

| Basic Scheme                          |     |

| CHAPTER 2: MICROCONTROLLERS           | 4   |

| Selection                             |     |

| MSPF449 Basic Operation               | 6   |

| Clock System                          |     |

| Interrupts                            | 8   |

| Operating Modes                       | 9   |

| Peripherals                           |     |

| Analog to Digital Conversion          | 10  |

| Digital Communication                 |     |

| Timer                                 |     |

| CHAPTER 3: SENSORS                    |     |

| Selection                             |     |

| Hall-Effect Devices                   |     |

| Application                           | 20  |

| CHAPTER 4: WIRELESS TECHNOLOGY        | 23  |

| Digital Modulation                    | 23  |

| Selection of the Operating Frequency  | 25  |

| Transceiver Selection                 |     |

| RF Circuitry                          | 28  |

| Modulator/Demodulator                 | 29  |

| Mixer                                 | 30  |

| Amplifiers                            | 31  |

| Data Slicer and Bit Synchronizer      | 34  |

| Reception Modes                       | 35  |

| Basic Antenna Facts                   | 36  |

| Antenna Choice                        | 38  |

| Radio Propagation                     |     |

| CHAPTER 5: IMPLEMENTATION AND TESTING | 42  |

| System Design and Implementation      | 42  |

| Length Measurement System             | 43  |

| Wireless Transmission                 |     |

| Reception                             | 51  |

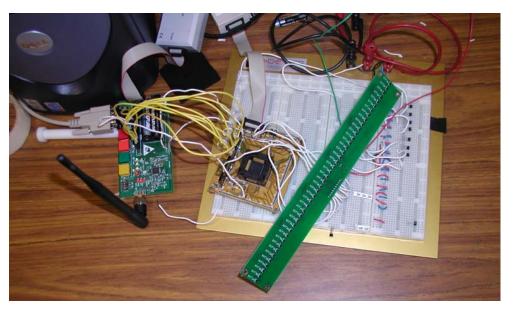

| Final Product                         | 54  |

| Device Testing                 | 56  |

|--------------------------------|-----|

| Testing Results                |     |

| Majority Vote Analysis         | 60  |

| CHAPTER 6: CONCLUDING REMARKS  |     |

| Future Work                    | 63  |

| Conclusion                     | 63  |

| APPENDIX A: LENGTH MEASUREMENT | 65  |

| APPENDIX B: TRANSMISION        | 94  |

| APPENDIX C: RECEPTION          | 125 |

| REFERENCES                     | 155 |

## LIST OF TABLES

| Table 1: Microcontroller Comparison           | 5  |

|-----------------------------------------------|----|

| Table 2: Interrupt Priorities                 |    |

| Table 3: Operation Mode Characteristics       |    |

| Table 4: Sensor Comparison                    |    |

| Table 5: Comparison of Transceiver Technology |    |

| Table 6: LOS Test Results                     | 58 |

| Table 7: Orientation Testing Results          | 58 |

| Table 8: Distance Testing                     | 59 |

| Table 9: Principal NLOS Case                  | 60 |

| Table 10: Majority Vote Improvement           | 60 |

## LIST OF FIGURES

| Figure 1: Basic Implementation                            | 3  |

|-----------------------------------------------------------|----|

| Figure 2: MSP430 Block Diagram                            | 6  |

| Figure 3: Percent Error as a function of Measured Voltage | 11 |

| Figure 4: Example Data Packet                             | 13 |

| Figure 5: Flux Density vs. TEAG                           | 20 |

| Figure 6: Initial Characterization                        | 21 |

| Figure 7: Comparison of Error Rates                       | 24 |

| Figure 8: RF Transceiver Block Diagram                    | 29 |

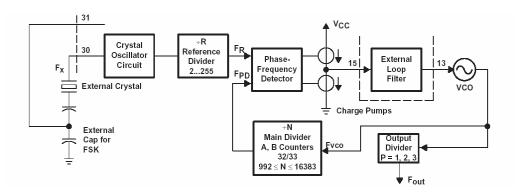

| Figure 9: PLL Block Diagram                               | 33 |

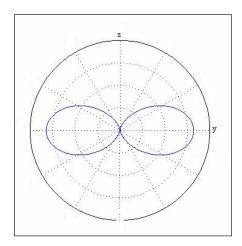

| Figure 10: Typical Half-Wave Dipole Radiation Pattern     | 39 |

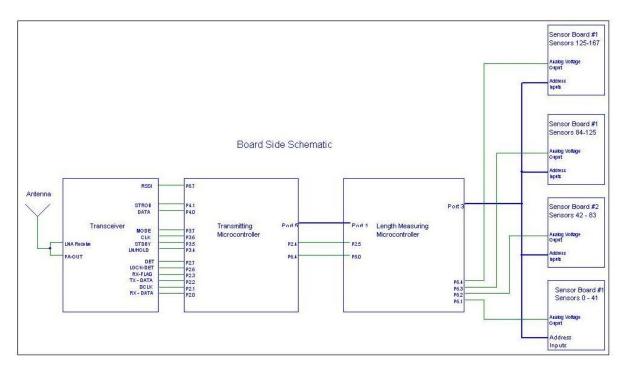

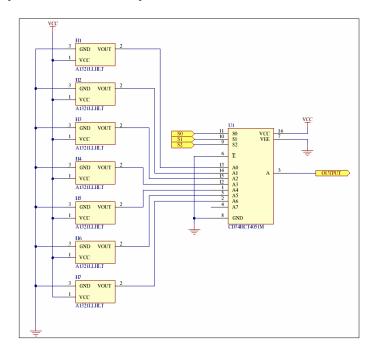

| Figure 11: Board Side Schematic                           | 43 |

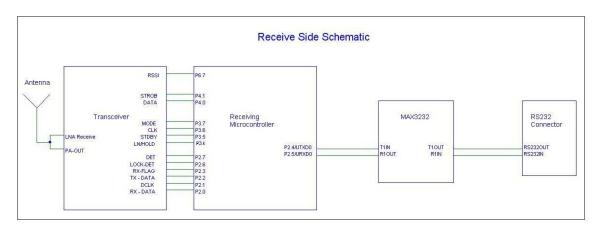

| Figure 12: Receiver Side Schematic                        | 43 |

| Figure 13: Level 1 Multiplexer Connections                | 45 |

| Figure 14: Level 2 Multiplexer Connections                | 45 |

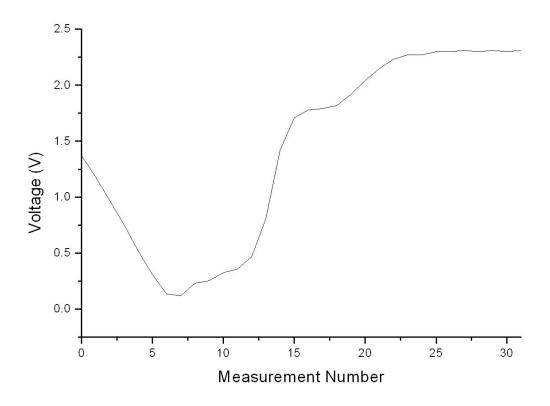

| Figure 15: Typical Voltage Characteristic                 | 47 |

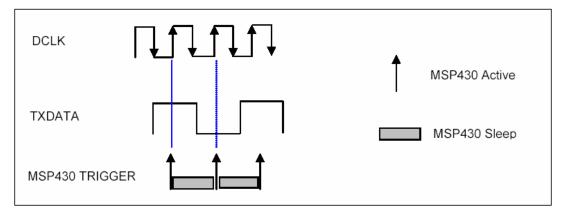

| Figure 16: Transmission Data Timing                       | 51 |

| Figure 17: Triggering on the Rising Edge                  | 53 |

| Figure 18: Triggering on Falling Edge                     | 53 |

| Figure 19: Final Implementation                           | 54 |

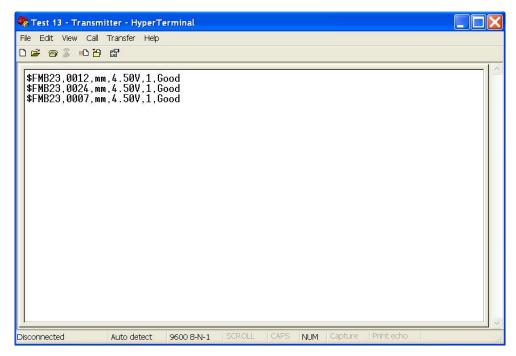

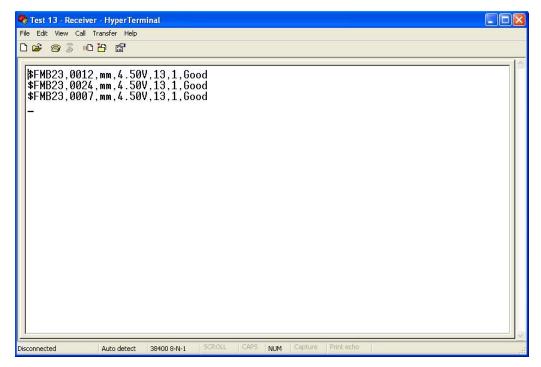

| Figure 20: Example Messages on the Transmitter Side       | 55 |

| Figure 21: Corresponding Messages on the Receiver Side    | 56 |

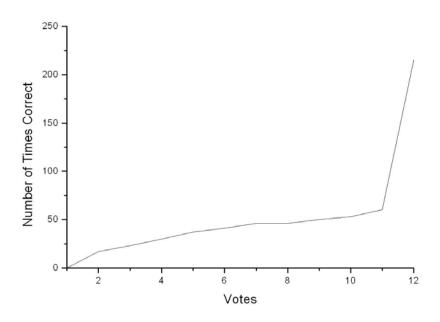

| Figure 22: Majority Voting Process                        | 61 |

## **CHAPTER 1: GENERAL INTRODUCTION**

#### **Objectives**

The goal of this project is to design the primary technology needed to construct a board that allows a user to perform length measurements on an object accurate to 1mm and send that information wirelessly to a receiver. The board will be used in fisheries research to measure the length of fish for various environmental reasons. Since the creatures being measured often move around unpredictably, we strive to design a device that has no moving parts and no wires associated with it that the creatures could become entangled in or break. Moreover, since the board will be subject to a diverse set of weather and other environmental conditions, the actual sensing elements cannot be left exposed. Thus the position sensing then must be non-contact.

In addition to these basic functional goals, we also design the board out of Commercially Off-the-Shelf (COTS) available products so that it can be produced in greater volumes at a later time without the need for custom electronics. Another consequence of this mass production is that the individual elements that make up the board should be as cost effective as possible. We also, of course, take all steps to ensure that the use of the board is as simple as possible so as to remove human error from the measurement.

As far as the wireless connection is concerned, the most important feature is that it be able to perform without line-of-sight. We design the device for short range operation in which the receiver is located a few feet from the transmitter with various non-metallic barriers obstructing the line of sight.

### Available Technologies

There is a wide array of fish length measuring technologies available in the fisheries industry. The main manufactures of these boards are Wildco, Limnoterra, Scantrol and Juniper

Systems. The first of these companies, Wildco, manufactures the 118-B30 fish measuring board (FMB). This FMB simply consists of a flat surface and a moving brass indicator arm that is placed at the end of the fish. Instead of taking an electrical measurement, this device simply allows for the end of the object to be marked and the measurement read off a number tape [1]. The next manufacturer is Limnoterra which offers many variations of the FMB IV. This FMB improves over the previous technology in that it offers electronic measurement without any moving parts. It has 1mm accuracy as desired and also performs non-contact length measurement. This FMB, however, does not allow for wireless transmission of the data from board to a receiver, rather it simply displays the data on a digital screen on the board itself [2].

Similar to the device from Limnoterra, the Scantrol FM100 performs an electronic measurement and displays it on the actual FMB, but does not wirelessly transmit the length data to a receiver. This technology also has wires connecting the display to the FMB which can become entangled when measuring a fish [3]. Finally, Juniper Systems manufacturers the LAT37 wFMB, which allows for electronic measurement to 1mm accuracy and wireless transmission to a remote receiver. The main drawback of this system is that it uses a moving part to perform the measurement [4]. Thus after surveying the available technologies we find that none fulfill our goals.

#### Basic Scheme

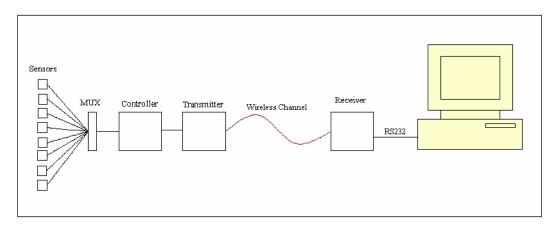

Our basic principle in this project is to measure the length of the object using a stylus placed at the end of the object. Sensing elements embedded in the actual board then will react to the proximity of this stylus and produce an electrical output proportional to the proximity of the stylus. The outputs of all the sensors will then be scanned using a series of multiplexers that eventually report all output values to a microcontroller. This microcontroller then will determine the length of the object and send its value to the transmitter. The transmitter will create the packet to be sent, modulate the message and send the data to the receiver wirelessly. On the receiver

side, the receiver will take the transmitted packet and extract the necessary information and display this information using a computer on the receiver side. The basic implementation of the system is shown in Figure 1.

Figure 1: Basic Implementation

### CHAPTER 2: MICROCONTROLLERS

#### Selection

The microcontrollers' purpose is to make all decisions based on inputs from the various sources and regulate the activity of other components. In this project, the most basic function of the microcontroller will be to use sensor outputs to find the length of the object. After finding the length, the microcontroller will send that data to the transmitting device which will wirelessly send the data to the receiver.

The main criteria used to judge different microcontroller technologies are speed, cost, power consumption, data and program memory and input/output capabilities. Since microcontrollers are often complicated to implement, technical support and accompanying software packages are also considerations. In accordance with our goal of designing the system out of COTS technology, we restrict ourselves to readily available technologies.

Although speed is usually among the most important characteristics of microcontrollers, in this project it is a secondary concern. Since many microcontrollers can deliver speeds at fractions of one million instructions per second (MIPS) and the programs in this project do not carry out computationally intensive operations, most microcontrollers on the market can deliver adequate performance. Likewise, the cost of the microcontroller itself is not of paramount importance since there will only be three microcontrollers in the entire system.

The power consumption of the microcontroller also is not of great importance since we know beforehand that the sensors will be the main source of power usage in the system. On the other hand, the random access memory (RAM) and program memory are important concerns in the microcontroller selection. The microcontrollers will be responsible for holding information from a multitude of sensors as well as holding somewhat extensive programs making the size of the RAM and program memory important. In our case the size of the memory is more important than the type as the speed of the memory look ups is not integral to the operation of the system.

The most important factor in selecting the microcontroller is its ability to take both digital and analog inputs and send digital outputs. Since there will be multiple microcontrollers in the entire system, they should have the ability to use both parallel and serial communication. The metric chosen to evaluate the microcontroller's parallel communicating ability is the number of I/O ports as this is measure of the amount of information that can be sent at once. Next, the use of the electrical sensors requires the microcontrollers to be able to take analog voltages measurements. The main concern with the analog voltage measurement is the resolution of the analog-to-digital converter (ADC) since it determines the accuracy of the measurement.

Table 1 below shows how technologies from Texas Instruments (TI), Freescale and Microchip compare [5] [6] [7].

|           |        |            |        |          | Program     |      | ADC        |

|-----------|--------|------------|--------|----------|-------------|------|------------|

| Company   | Family | Processor  | Type   | I/O Pins | Memory (kB) | RAM  | Resolution |

| TI        | MSP430 | MSP430F449 | 16 bit | 48       | 60          | 2048 | 12-bit     |

|           |        |            |        |          |             |      |            |

| Freescale | HC16   | 68HC16Y1   | 16 bit | 24       | 1024        | 2048 | 10-bit     |

|           |        |            |        |          |             |      |            |

| Microchip | PIC18  | PIC18F8520 | 8 bit  | 68       | 32          | 2048 | 10-bit     |

|           |        |            |        |          |             |      |            |

**Table 1: Microcontroller Comparison**

The family of microcontroller chosen from each company was based on which could handle our requirements without being overly complex with many unrelated functions. The particular microcontroller shown is representative of the performance of that family. The number of I/O pins needed in this project is determined by the maximum number of parallel inputs and outputs that are communicated by any of the microcontrollers. In our system, the length measuring microcontroller performs the most parallel communication. Its parallel communication load comprises of an eight-bit integer sent to the transmitter, six control bits to the analog multiplexers and possibly various digital switches to communicate with the user. All of the microcontrollers listed above have enough I/O pins to satisfy those requirements. Despite the inferior program memory in comparison to the HC16 class from Freescale, in the end, we chose

the MSP430 class, specifically the MSP430F449, from TI. The main reasons for this choice were the superior resolution of the ADC and the abundance of literature available from TI.

#### MSPF449 Basic Operation

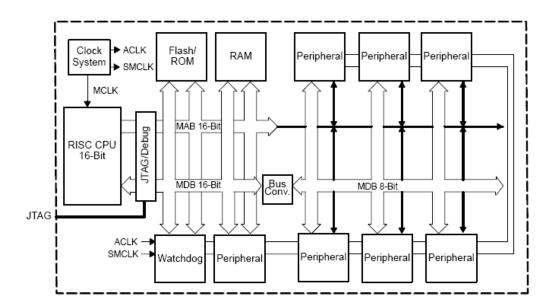

The MSP430 class of microcontrollers consists of a 16-bit microprocessor that is integrated with various peripheral devices and a clock system that allows different modes of operation as shown below in the block diagram provided by TI in Figure 2 [8].

Figure 2: MSP430 Block Diagram

As the block diagram indicates, the MSP430 brings together the operation of a 16-bit RISC CPU with various peripherals and program memory into a single device that can handle all functions of our project. The implementation of the device is greatly simplified using the embedded emulation that allows for controlled experimentation using break points and single steps in code while still allowing full speed operation. Once experimentation is complete, the same software used to for the emulation can be used to program the device [8]. There will be a host of peripherals used in this project. The specifics regarding the operation of these peripherals are set by internal registers. For example, the clock used for the ADC can be chosen to be taken from a variety of signals and the choice of signal to be used is set by an internal register.

The MSP430 has sixteen total registers, four of which are dedicated to specific functions while the other twelve can be used for general purpose. The first of these dedicated registers is the program counter (PC) which points to the next instruction to be executed. Next, the stack pointer (SP) points to the return address when an interrupt or subroutine is executed. After the stack pointer, the status register holds the status of the CPU. Of importance in this status register are the general interrupt enable (GIE), CPU off and oscillator off (OSCOFF) bits. When the GIE bit is set, all maskable interrupts are enabled, interrupts will be discussed in further depth later. As the names would suggest, the CPU off and OSCOFF bits turn off the CPU and LFXT1CLK oscillator respectively when they are set. Lastly, the constant generator registers generate common constants that are repeatedly used [8].

#### Clock System

Clock signals for the MSP430 are generated by a frequency-locked loop (FLL) that takes two or three input clock signals, presumably from a crystal or other highly accurate device, and generates four output signals. The three input signals that the FLL takes are [8]:

- LFXT1CLK: Oscillator that can use a crystal, resonator or other external clock sources.

In our case, a 32.768kHz crystal is used as the input here.

- XT2CLK: A high frequency oscillator that uses crystals, resonator or other sources. This second source is not required.

- DCOCLK: Digitally controlled oscillator (DCO) which is stabilized by the FLL.

The output signals provided by the digital FLL are:

ACLK: The ACLK, or the auxiliary clock, is sourced from the LFT1CLK, in our case the ACLK will always have a frequency of 32.768kHz. It can be selected as the clock source for many peripherals.

- ACLK/n: This is the divided ACLK frequency, it can be divided by 1, 2, 4 or 8. This is not used internally, rather it is used for external devices only.

- MCLK: The MCLK, or the master clock, can be sourced from the LFT1CLK, XT2CLK or DCOCLK. In our system, it is sourced from DCOCLK. The output of the MCLK can also be divided by 1, 2, 4, or 8.

- SMCLK: The SMCLK, or the submain clock, can also be sourced from the LFT1CLK,

XT2CLK or DCOCLK. It is used as a clock source for many peripherals.

In normal operation, the source for the SMCLK and the MCLK is the DCOCLK which is usually taken to be 32 times the LFT1CLK frequency or about 1.05MHz, but can also be other multiples of the LFT1CLK frequency. In our system the frequencies of MCLK and SMCLK are set to be 75 times the LFT1CLK frequency or 2.46MHz. Having many different clock signals helps satisfy the variable requirements on the microcontroller. On one hand the microcontroller must have a fast enough clock to respond to fast acting events, but on the other hand should have a low clock frequency while in low power modes. The multiple signals coming from the FLL allows for all of these requirements to be met [8].

#### Interrupts

In the programs for all of the microcontrollers in this system, interrupts play an important role. They allow the current process of the microcontroller to be interrupted when a specified condition is met. When the interrupt is executed, the corresponding interrupt service routine (ISR) is called. After the code contained within the ISR is processed, the microcontroller is returned to the state it was before the execution of the interrupt [9]. The MSP430 class of microcontrollers has three main types of interrupts: system, non-maskable and maskable. System interrupts are used to reset the operation of basic elements of the system such as the power up. Non-maskable interrupts are not masked by the GIE bit, rather they are set by other fields specific to each type of interrupt. Maskable interrupts can be enabled using an interrupt enable bit associated with each device or as

a whole through the GIE. If the GIE bit in the system register is cleared then all of the maskable interrupts are disabled. While an ISR is being executed, the GIE is cleared so that no maskable interrupts will interrupt the progress of the ISR. All of the interrupts that are coded into the program of microcontrollers in this project use maskable interrupts. The most common form of these maskable interrupts are device specific interrupts which occur when a certain device reaches a pre-determined condition. When two or more interrupts are pending concurrently they are serviced according to their priority, these priorities are listed in Table 2 below from [5].

| INTERRUPT SOURCE                                         | INTERRUPT FLAG                                                                        | SYSTEM INTERRUPT                                | WORD<br>ADDRESS | PRIORITY    |

|----------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------|-----------------|-------------|

| Power-Up<br>External Reset<br>Watchdog<br>Flash Memory   | WDTIFG Reset KEYV (see Note 1)                                                        |                                                 | OFFFEh          | 15, highest |

| NMI<br>Oscillator Fault<br>Flash Memory Access Violation | NMIFG (see Notes 1 and 3)<br>OFIFG (see Notes 1 and 3)<br>ACCVIFG (see Notes 1 and 3) | (Non)maskable<br>(Non)maskable<br>(Non)maskable | 0FFFCh          | 14          |

| Timer_B7†                                                | TBCCR0 CCIFG (see Note 2)                                                             | Maskable                                        | 0FFFAh          | 13          |

| Timer_B7†                                                | TBCCR1 to TBCCR6 CCIFGs<br>TBIFG (see Notes 1 and 2)                                  | Maskable                                        | 0FFF8h          | 12          |

| Comparator_A                                             | CAIFG                                                                                 | Maskable                                        | 0FFF6h          | 11          |

| Watchdog Timer                                           | WDTIFG                                                                                | Maskable                                        | 0FFF4h          | 10          |

| USART0 Receive                                           | URXIFG0                                                                               | Maskable                                        | 0FFF2h          | 9           |

| USARTO Transmit                                          | UTXIFG0                                                                               | Maskable                                        | 0FFF0h          | 8           |

| ADC12                                                    | ADC12IFG (see Notes 1 and 2)                                                          | Maskable                                        | 0FFEEh          | 7           |

| Timer_A3                                                 | TACCR0 CCIFG (see Note 2)                                                             | Maskable                                        | 0FFECh          | 6           |

| Timer_A3                                                 | Timer_A3 TACCR1 and TACCR2 CCIFGs, Maskable Timer_A3 TAIFG (see Notes 1 and 2)        |                                                 | 0FFEAh          | 5           |

| I/O Port P1 (Eight Flags)                                | pht Flags) P1IFG.0 to P1IFG.7 (see Notes 1 and 2) Maskable                            |                                                 | 0FFE8h          | 4           |

| USART1 Receive‡                                          | URXIFG1                                                                               | Maskable                                        | 0FFE6h          | 3           |

| USART1 Transmit <sup>‡</sup>                             | UTXIFG1                                                                               | Maskable                                        | 0FFE4h          | 2           |

| I/O Port P2 (Eight Flags)                                | P2IFG.0 to P2IFG.7<br>(see Notes 1 and 2) Maskable                                    |                                                 | 0FFE2h          | 1           |

| Basic Timer1                                             | BTIFG                                                                                 | Maskable                                        | 0FFE0h          | 0, lowest   |

**Table 2: Interrupt Priorities**

Table 2 shows that the highest priorities go to the system and non-maskable interrupts which are followed by peripherals masked using the GIE bit.

#### Operating Modes

One of the ways the MSP430 class of microcontrollers achieves low power operation is through the use of multiple operating modes. There is one active mode for typical operation and four different low power modes offering differing degrees of power saving. Once a low power mode is entered, interrupts are used to return to active mode. Table 3 compiled from [8] below lists the different characteristics of the various operating modes.

| Mode   | Characteristics                           |

|--------|-------------------------------------------|

| A .:   |                                           |

| Active | CPU and all clocks active                 |

|        | CPU and MCLK disabled                     |

| LPM0   | SMCLK and ACLK active                     |

|        | CPU, MCLK and DCO Oscillator disabled     |

|        | SMCLK, and ACLK active                    |

|        | DC Generator disabled if DCO not used for |

| LPM1   | MCLK or SMCLK                             |

|        | CPU, MCLK, SMCLK and DCO Oscillator       |

|        | disabled                                  |

|        | ACLK active                               |

| LPM2   | DC Generator Enabled                      |

|        | CPU, MCLK, SMCLK and DCO Oscillator       |

|        | disabled                                  |

|        | ACLK active                               |

| LPM3   | DC Generator disabled                     |

| LPM4   | CPU and all clocks disabled               |

**Table 3: Operation Mode Characteristics**

Low power operation in this project will predominantly be done in the LMP0 mode. In this mode the CPU and master clock are disabled, but the sub-master clock and the auxiliary clock are active so that the LMP0 mode can be exited based on interrupt conditions defined by those two signals.

### **Peripherals**

### Analog to Digital Conversion

MSP430F449 microcontroller has eight 12-bit ADC pins. This 12-bit resolution is covers entire the range of conversion which is specified by the  $V_{R-}$  and  $V_{R+}$  voltages that can be either input to the microcontroller or generated by the microcontroller itself. In this project we use the range from 0V to 2.5V, both ends are provided by the microcontroller.

The output of the ADC conversion is an integer,  $N_{ADC}$ , ranging from 0 to 4095, or  $2^{12} - 1$ , this integer can then easily then be used to find the input voltage by the formula [8]:

Input Voltage =

$$\frac{N_{ADC}}{4095} (V_{r+} - V_{r-}) + V_{r-}$$

(2.1)

Using our given range, (1.1) simply reduces to:

Input Voltage =

$$\frac{N_{ADC}}{4095}(2.5V)$$

(2.2)

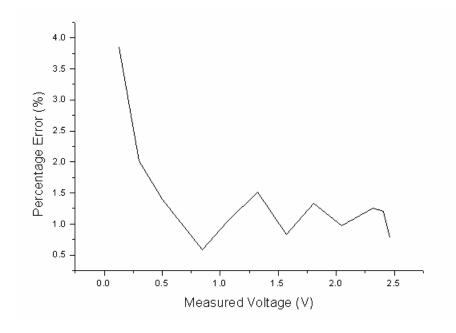

As Figure 3 shows, this ADC conversion delivers a highly accurate voltage when compared to the result obtained through the use of a digital multimeter.

Figure 3: Percent Error as a function of Measured Voltage

Figure 3 shows that aside from the smaller measurements where even a very small deviation from the digital multimeter output results in a large percentage error, most measurements had an error of less than 2 percent. We experimented with applying voltages to specify  $V_{R-}$  and  $V_{R+}$ , but found that having the microcontroller generate the appropriate values greatly simplifies the overall operation.

#### **Digital Communication**

The MSP430F449 comes with six digital communication ports with each port having eight pins that can be used for parallel communication. Each of the pins can be read from and written to independently. Many of the ports have alternate functions, for example, port six is also used for analog-to-digital conversion. Ports 1 and 2 also have the ability to generate interrupts based on either high to low or low to high transitions in digital data [8].

The MSP430F449 also allows for two modes of serial communication: UART and SPI. The SPI mode is a master-slave mode in which data is communicated by multiple devices all using the same clock provided by the master. The UART mode allows for communication that is asynchronous to other devices. Instead of sharing a clock, in the UART mode both the transmitter and receiver operate at the same baud rate. The simplicity associated with not having to have a shared clock makes the UART mode ideal for all serial communication in this project. Serial communication will mainly be used for RS232 communication between the receiver and computer.

A character to be sent or received follows a standard form in which it starts with a start bit followed by seven or eight data bits, a parity bit, an address bit, and one or two stop bits. All possible choices in format are set by the appropriate internal register and should obviously be shared by both the transmitter and receiver. The baud rate used to send the characters is determined by the clock frequency and internal registers [8].

The UART serial communication mode has two formats: the address bit multiprocessor format and the idle-line multiprocessor format. The address bit multiprocessor format is typically used when three or more microcontrollers communicate. The idle-line format is used when two devices communicate. In our application the microcontroller will be communicating with the RS232 line so the idle-line format is used.

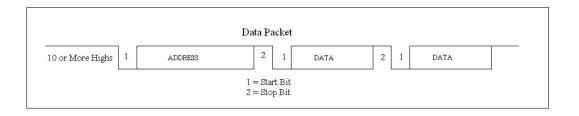

In the idle-line format, sets of data are separated by idle times. Idle lines are defined to be ten or more constant logic highs following the stop bit. A packet of information starts with a start bit and is immediately followed by a character indicating the address of the information. This character is then immediately followed by a stop bit. Another start bit indicates a data character which is then again followed by a stop bit. This pattern of start bit, data and stop bit then continues until the packet of information is completed as shown in Figure 4 below [8].

Figure 4: Example Data Packet

The UART mode also has the ability to suppress glitches and detect framing, parity, receive overrun and break condition errors. When a logic low is detected with a pulse width less than the deglitch time, typically about 900ns, it is ignored and not considered when detecting the start bit. When any of the errors are detected, the appropriate bit in the control registers is set [8].

#### Timer

There are two very similar 16-bit timers available on the MSP430F449, Timer\_A and Timer\_B, and both will be used in this project. The basic principle behind the operation of the timer is that the rising edges of the clock signal are counted and when that count reaches a predetermined value, an interrupt is generated. The period of the clock is known beforehand so the count effectively becomes the time elapsed since the start of the counter. This clock signal can be chosen from the ACLK, SMCLK, or an external clock signal [8]. The timer can operate in three different modes: up, continuous, and up/down. In the up mode, the counter counts from zero to a predetermined value programmed in the software and once the value is reached an interrupt can be generated and the counter begins to repeat the count again from zero. The continuous mode is

very similar and can be considered simply an extension of the up mode, but instead of counting to a value specified in the software it counts to 65,535, or 2<sup>16</sup>-1, as would be the maximum value expected in a 16-bit timer. This is also, of course, the highest value the up mode can count to. In up/down mode the timer counts up to a predetermined value just like the up mode, but instead of starting at zero again, it decrements the counter to zero. The timer modes used most often are the up and continuous modes, these will be used in the transmitting microcontroller to control the digital transmission of the bits to the transceiver and to turn off the board when it has been left idle for a specified time. The timers also have capture and compare capabilities. When an input is fed to the timer, the timer can be programmed to copy the contents of the count register at selected edges of the input signal. When used to compare, the timer can compare the occurrences of several different interrupts [8].

## **CHAPTER 3: SENSORS**

#### Selection

As discussed earlier, the main goal of the entire board is to perform non-contact length measurements. To accomplish this we propose a scheme in which the object is placed on the board and the user uses a hand-held stylus to mark the end point of the object on a number line. The stylus should not have any wires attaching it to the board or have to touch the sensors which are placed in a protective covering inside the board.

To accomplish these basic goals we plan to have a linear array of sensors underneath the number line, when the stylus is brought close to a particular point on the number line, the sensors underneath identify the position of the stylus. This scheme requires sensors that can, without mechanical contact, measure the proximity of a stylus. In our case we chose to measure the proximity of the stylus by inserting a permanent magnet inside of it and measuring the magnet field emanating from it.

In our search we found two basic types of sensors that can measure magnetic flux density and can be placed in a linear array: Hall-Effect sensors and magnetorestrictive sensors. Each produce an electrical output based on the input magnetic flux density. In either case, a microcontroller will scan the results of all sensors in the linear array to determine the position of the stylus. Since we strive to design the system out of COTS technology, we choose from readily available products instead of custom designs.

Although there is a multitude of different characteristics that determine the performance of a particular sensor, the most important in our case is repeatability. Repeatability specifies difference between consecutive outputs that are held at identical conditions [10]. In our design, all the data from the sensors is read by the microcontroller which can adjust the final output for many types of predictable errors. Since repeatability errors are essentially unpredictable, the microcontroller cannot adjust for them so the output is directly affected by the error.

After repeatability, the next main concern is the reliability of the sensor. The reliability is defined as likelihood the sensor will function correctly [10]. Since the sensors will be placed inside the board under a protective layer, any sensor that malfunctions cannot be replaced. This either forces the user not to measure objects in the vicinity of that sensor or replace the entire board. In our experience with Hall-Effect sensors, when they do malfunction, the output voltage with no incident magnetic field density dramatically rises to close to the supply voltage, so malfunctions are typically easily spotted by the microcontroller and the user can be alerted.

The cost of a sensor is not typically identified as being a characteristic of a sensor, but in our case it is a major criterion since we hope to build the board as cheaply as possible. Of course the cost of the sensor is measured not only in how much each individual sensor costs, but also how many sensors would be required to span the 1m and 2m boards. Furthermore, the current consumption also indirectly affects the price, since additional current requires a battery which is typically more expensive.

The non-linear characteristic of the output values is also an important characteristic of the sensor. If the output of the device can be approximated by a line and still maintain the necessary accuracy, then interpolation calculations become simpler for the microcontroller. In this context, interpolation calculations are used to find the location of the magnet when it is not over any particular sensor. The FMB, however, is calibrated beforehand and a curve for the output can be found using software such as MATLAB and be programmed into the microcontroller so this concern is not as major as the previous three. Another somewhat less important concern is the range of output values for the sensor. A larger range usually implies that changes in the input magnetic flux density result in larger changes in the output making the overall system more sensitive to changes in the input. Along with the range, the zero value of the sensor, that is the output value when there is no input magnetic field must fall in range that can be measured by the microcontroller.

Temperature effects are also normally a serious concern in sensor operation. Most companies that manufacture sensors do rigorous testing on the performance of their sensors in different temperature environments so that the microcontroller can use that data coupled with a temperature sensor to predict any deviations in output value.

As discussed earlier, our two choices for sensing technologies are Hall-Effect sensors and magnetorestrictive sensors. In a Hall-Effect device, a current is run through a conductor or semi-conductor material and when a magnetic field is applied a voltage develops that is perpendicular to both the current and the magnetic field. In physical terms, the incident magnetic field causes a build up of carriers on one side of the material which creates the potential difference [10]. An important benefit of Hall-Effect sensors is that they can detect the polarity of the input magnet field. These sensors then can have their output voltage either increased or decreased from the zero value.

Magnetorestrictive sensors, on the other hand, produce a change in resistance as a function of the magnitude of the input magnetic field. The basic physical principle behind magnetoresistance is the Lorentz force which acts perpendicular to the velocity of the charges and the magnetic field and tends to force the carriers to move in a circular pattern. This forces more carriers on one side of the material than the other. Since the carriers are moved to one side of the material the effective cross-sectional area of the material is reduced, this coupled with the reduction of carrier speed due to the circular nature of the Lorentz force results in a change in the resistance. The resistivity of the material is then given by [10]:

Resistivity =

$$\frac{\text{Voltage}}{\text{Carrier Density} \times \text{Carrier Velocity}}$$

(3.1)

Typical advantages of magnetoresistive devices are that they can operate at higher frequencies than Hall-Effect devices, offer greater sensitivity and consume less current [10].

Conventional magnetoresistive and Hall-Effect devices can both deliver repeatability that is significantly smaller than 1mm accuracy we hope to achieve so both technologies satisfy our

most important concern. Moreover, both types of devices also are known to have high lifetimes and thus high reliability [10]. Table 4 below compiled from [11]–[14] compares a Hall-Effect sensor and a magnetoresistive sensor both made by Honeywell.

| Type             | Part No. | Output<br>Current (mA) | Supply<br>Current (mA) | Operate<br>Point<br>(mT) | Temp<br>Range (°C) | Cost   |

|------------------|----------|------------------------|------------------------|--------------------------|--------------------|--------|

| Hall-Effect      | SS41     | 20                     | 15                     | 4                        | -55 to 150         | \$1.69 |

| Magnetoresistive | 2SS52M   | 20                     | 11                     | 1.5                      | -40 to 150         | \$2.68 |

**Table 4: Sensor Comparison**

The comparison shows that the technologies are very similar except for price where the magnetoresistive sensors are much more expensive. Since there will be on the order of 100 sensors in the 1m board, this leads to a substantial increase in the total cost, outweighing the savings its lower current consumption. Thus, we ended up choosing Hall-Effect sensors for our final board. We decided to go with the sensors made by Allegro instead of Honeywell because of the extensive documentation available from Allegro.

### *Hall-Effect Devices*

The Hall-Effect stipulates that when charges are passed through a conductor with velocity v and a magnetic field, B, is applied perpendicular to v that a voltage  $V_H$  measured perpendicular to both v and B develops such that:

$$V_H = \mathbf{B}\mathbf{v}D \tag{3.2}$$

Where D is the length across which the voltage is taken. This can also be expressed as [15]:

$$V_H = \frac{KBI}{t} . ag{3.3}$$

Where t is the thickness of the conducting material, I is the current and K is the Hall effect constant. The latter representation clearly shows that the Hall Voltage,  $V_H$ , is directly proportional to the incident magnetic flux density and current and inversely proportional to the thickness of the conductor. This  $V_H$  that develops is typically very small and thus very difficult to

measure accurately so packaged Hall-Effect devices usually come with some type of amplifying circuitry built in to raise the voltage levels to a reasonable level [10]. When the Hall-Effect device is exposed to high fields that often result with a magnet being very close, the device saturates so there is no increased output voltage for an increase in input flux density. This saturation does not arise from the Hall-Effect sensor itself, but rather the amplification circuit so the user can be assured that high fields will not damage the device [16].

The Hall-Effect sensor we chose to use is the Allegro A1321 device. These are three-pin devices that have a zero voltage that is half of the supply voltage which either increases or decreases according to whether the South or North pole of the magnet is applied and do not exhibit dramatic changes in output in different temperatures [17]. Their output is ratiometric, thus the output voltage is not only proportional to the incident magnet field density but also the supply voltage [18]. This allows the range of output values to be determined by the supply voltage.

The first concern when operating a Hall-Effect device is that the magnetic flux lines originating from the magnet must be perpendicular to the face of the device to bring about the desired change in output [10]. In our case, this requires the stylus to be held perpendicular to the face of the board to achieve the best results. Moreover, since the calibration of these devices will be done assuming perpendicular placement of the stylus, any tilt will bring about errors.

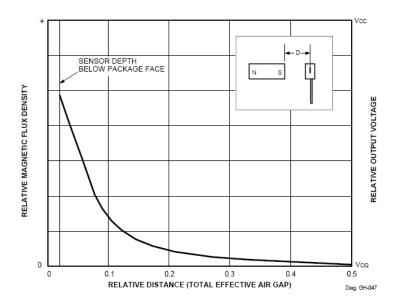

The next major concern is the consideration of the total effective air gap (TEAG). Figure 5 from [19] shows that the magnetic flux density is substantially reduced as the TEAG is increased.

Figure 5: Flux Density vs. TEAG

This graph also shows that the relative output voltage decreases dramatically as the TEAG is increased as would be expected. The TEAG not only refers to the total air gap between the sensor and the magnet, but rather the total depth between the sensor and magnet. In our case this requires the protective material covering the sensors to also be included in the TEAG.

In this application we will effectively be measuring the TEAG to determine the proximity of the stylus. In placing the stylus on the board, the user had three degrees of freedom. Our goal is only to measure the length, thus the other two degrees of freedom must be constrained to the calibration procedure. We require, therefore, that the measurement be taken when the stylus is touching the board to constrain the vertical distance from the sensor and be within the number tape on the board to constrain the depth, making the horizontal distance the only variable in the TEAG.

#### **Application**

In our application of the Hall-Effect devices, we will be primarily be operating in the unipolar slide-by mode. That is, one pole will dominate the readings coming from the Hall-Effect sensor

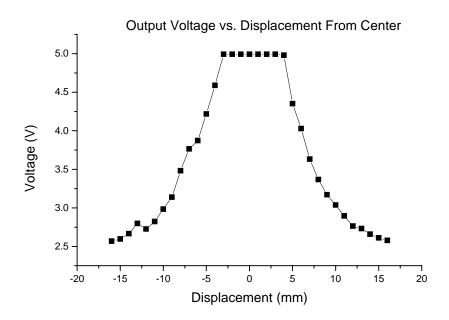

and the magnet will be effectively moved from side to side with the components of the TEAG from the packaging material and stylus predetermined. Given this mode of operation, we expect a Gaussian curve of voltages with the highest coming when the magnet is directly over the sensor and the voltages dropping off non-linearly as the magnet is moved horizontally away from the magnet in either the positive or negative directions [16].

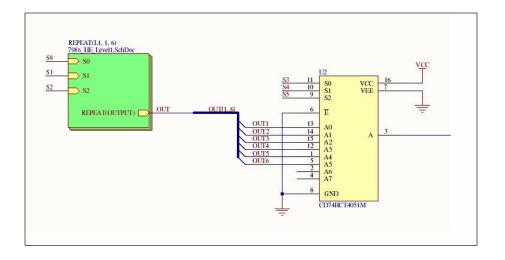

The characterization and verification of a Gaussian characteristic of the sensors was done by Abhinav Pathak. There were several characterizations done to ensure the predicable behavior of the output voltages, one of these characterizations are shown below in Figure 6.

Figure 6: Initial Characterization

In this initial characterization the magnet is held a fixed distance vertically from the sensor and displaced in the horizontal direction. Figure 6 illustrates the expected Gaussian shape, but also shows that as the magnet tends to saturate the sensor as it gets very close. In later characterizations and the final implementation we will alter the TEAG and magnet strength to avoid this saturation. Furthermore, when the sensors are actually implemented with the

microcontroller we find it advantageous to use the North Pole instead of South Pole so that the voltages drop from the zero value.

## **CHAPTER 4: WIRELESS TECHNOLOGY**

#### Digital Modulation

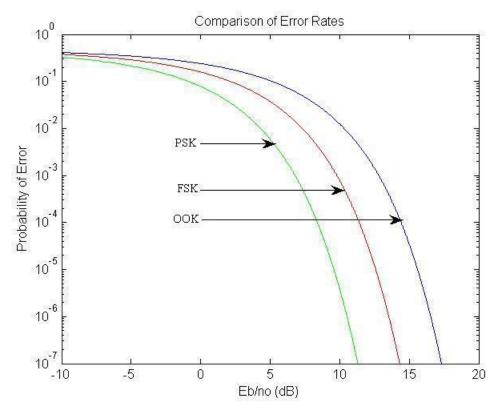

The three main digital modulation schemes that were considered for this project are amplitude shift keying (ASK), frequency shift keying (FSK), and phase shift keying (PSK). All of these schemes will be used in their binary implementation so that each modulation scheme will deliver a distinct signal corresponding to either a logic high or a logic low. Typically ASK consists of the carrier signal being turned on or off depending on the input binary sequence. In this sense ASK is also known as on-off keying (OOK). Binary FSK consists of a sinusoidal carrier whose frequency is adjusted to according to the input binary data. Binary PSK consists of a carrier whose phase is shifted between two different values to reflect the binary data. In practice these phases are usually 0 and  $\pi$  [20].

The two main criteria used to judge between different modulation schemes in this project are the probability of error in the presence of additive white Gaussian noise (AWGN) and the ease of implementation. Performance in AWGN is often used a performance metric to compare different modulation schemes. The ease of implementation is important because it helps to determine the diversity of products that implement that scheme. The eventual choice will also be judged on a variety of hardware criteria, so it helps to have a diverse set of technology to choose from.

The performance of the different modulation schemes in AWGN is computed using an optimum receiver based on the maximum likelihood rule. In all cases synchronous detection is used to compare the schemes. For OOK the probability of error, P<sub>e</sub>, can be shown to be [20]:

$$P_{\rm e} = \frac{1}{2} \operatorname{erfc} \sqrt{\frac{E_{\rm b}}{4n_{\rm o}}} \,. \tag{4.1}$$

Where  $E_b$  is the bit energy defined as the energy of the input binary signal over one bit period and  $n_o$  is defined as the integration of the noise voltage over one bit period. Thus, the probability of error then is a function of  $E_b/n_o$  which is defined as the signal to noise ratio (SNR) per bit. Next, for FSK the probability of error can also be shown to be a function of the SNR per bit [20]:

$$P_{\rm e} = \frac{1}{2} \operatorname{erfc} \sqrt{\frac{E_{\rm b}}{2n_o}} \ . \tag{4.2}$$

Lastly, the probability of error in the case of PSK can be shown to be [20]:

$$P_{e} = \frac{1}{2} \operatorname{erfc} \sqrt{\frac{E_{b}}{n_{o}}}. \tag{4.3}$$

These error probabilities are plotted as a function of the SNR per bit in Figure 7 below.

**Figure 7: Comparison of Error Rates**

As expected, the probability of error with all the modulation schemes decreases as SNR per bit increases. Figure 7 clearly shows that PSK performs the best in the presence of AWGN, followed by FSK and ASK. The next criterion used to judge between modulation schemes is the ease of implementation. OOK is the easiest to implement since it simply involves turning on and off the carrier based on the binary data. OOK also does not require coherent demodulation and can simply be demodulated using the received signal strength indication (RSSI). FSK is also simple to implement as it can be generated coherently using an IQ modulator or incoherently using a phase locked loop. Also since the signal has constant amplitude, a non-linear power amplifier can be used in the transmitter circuit. Lastly, PSK is more complex to generate because it requires coherent modulation [21].

Considering both the error probabilities and the complexity of implementation we chose FSK as our modulation scheme. This scheme provides better performance than ASK in the presence of AWGN yet still is relatively simple to implement so that there is a diverse set of technologies to choose from. Our eventual choice in transceiver technology, the basis for which will be discussed later, is the TRF6903 transceiver. The transceiver modulates the signal using a phase locked loop which produces signal with a frequency deviation of 32 KHz, thus a 64 KHz difference between the two signals. The baseband signal is coded using non-return to zero (NRZ) coding which doubles the maximum achievable data rate when compared to Manchester coding [22] and has been experimentally shown to have fewer errors in wireless transmission in a device similar, the TRF6900A, to the TR6903 [23].

#### Selection of the Operating Frequency

The selection of the frequency band is one of the most important decisions in the wireless system design as it often dictates possible choices in transceiver and antenna technology. The frequency bands that were considered are the 902-928 MHz and the 2.4-2.48GHz Industrial, Scientific and Medical (ISM) bands. Higher frequencies tend to allow for more bandwidth thus

allowing for higher data rates. It should be noted, however, that data rate is not a primary concern in this project since this is not a high speed application requiring large amounts of data to be sent over the wireless link. A selection of lower frequency is supported by the fact that antenna gain at its resonant frequency normally increases with frequency. This increased gain implies that the wave emanating from the antenna does not spread out as much, thus reducing its ability to navigate around obstacles in a NLOS environments. After considering all of the options, we chose the 902-928MHz band since data rates are not pivotal in this project and communication in this band generally performs better than the 2.4-2.48GHz band in NLOS environments [20].

#### Transceiver Selection

The function of the transceiver, or a transmitter/receiver pair, is to take digital data on transmitter side and convert it to an analog waveform fit for wireless transmission and to perform the complementary action on the receiver side. The selection criteria include the modulation technique, sensitivity, maximum output power and maximum data rate. Similar to the microcontroller selection, ease of implementation is also a concern. Documentation regarding the operation of the device and more importantly the simplicity in the integration with our chosen microcontroller is important. We again restrict ourselves to readily available technology in so that we can design the entire product out of COTS technology. This restricts us from designing a custom transceiver for this specific application. We have already chosen to use FSK modulation so we are obviously biased towards choosing a device that has FSK capability. The next consideration is the sensitivity which is defined as minimum input signal that can be converted to a meaningful voltage by the receiver [20]. This is a major concern for our project because the FMB will often be operated in severe conditions. On the other hand, we would also like to deliver as strong a signal as possible to receiver since, as was shown earlier, error rates tends to decline as the signal to noise ratio increases. Furthermore, we also would like to be able to adjust the output power based on application, increasing the power when conditions require while saving

battery life by reducing the output power in more hospitable environments. Lastly, the maximum data transfer rate is obviously a concern in designing any wireless system but as discussed earlier, this is not a paramount concern in this project. Table 5 shows a comparison of technologies based on our selection criteria [24] - [28].

|             |           | Modulation |                   | Max Output  | Maximum Data |

|-------------|-----------|------------|-------------------|-------------|--------------|

| Company     | Device    | Technique  | Sensitivity (dBm) | Power (dBm) | Rate (kb/s)  |

| Texas       |           |            |                   |             |              |

| Instruments | TRF6903   | FSK, ASK   | -103              | 8           | 64           |

| Chipcon     | CC1020    | FSK, ASK   | -121              | 10          | 153.6        |

| Linx        | ES Series | FSK        | -102              | 4           | 56           |

| Analog      |           |            |                   |             |              |

| Devices     | ADF7025   | FSK        | -104.2            | 13          | 384          |

**Table 5: Comparison of Transceiver Technology**

Table 5 shows that in the areas of concern the available technologies are somewhat similar. The main significant differences in the devices are that the transceivers from Chipcon and Analog Devices have superior sensitivity and output power. These devices also have considerably higher data rates than the other technologies. After initially considering the Linx ES transmitter/receiver technologies, we eliminated them from consideration because they discontinued the line of products we were planning on using. Even though Linx has other products that satisfy our needs, this kind of instability presents major concerns as the product should be available reliably as our goals indicate.

This left the devices from Chipcon, Analog Devices and TI. Although the Chipcon and Analog Devices technologies both out perform the TI technology in the areas of concern, we ended up deciding that this better performance did not overcome the inherent integration advantages provided by using the TI device since the chosen microcontroller is also made by TI. TI also offers a demonstration board which integrates the microcontroller and transceiver on a single PCB. This makes prototyping much simpler and can give us insights into designing a custom board when prototyping is finished. Furthermore, TI also provides example code on how

to execute wireless communication which simplifies the writing of our own code for this project. So in the end, we chose to use the TRF6903 transceiver from TI.

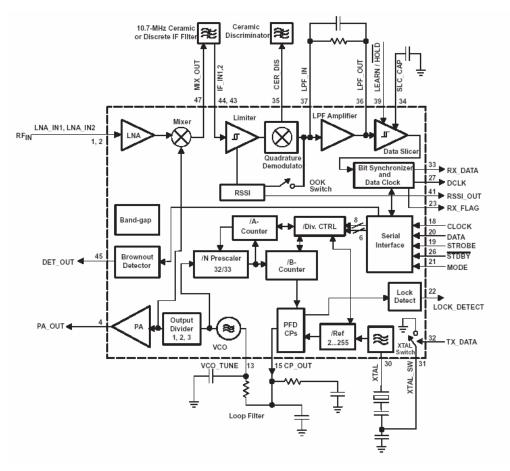

## RF Circuitry

Transceivers can generally be broken down into two main sides: the transmitter side and the receiver side. On the transmitter side the main components usually are the modulator, upconverter and the power amplifier. On the receiver side the main components consist of a low noise amplifier (LNA), the down-converter and the decoder. Both the receiver and transceiver share a transmit-receiver switch, oscillation circuit and the antenna [29]. It is important to note that many of the components on the transmitter and receiver side complement each other. For example, the up-converter and the down-converter both use mixer technologies to transform input streams into different frequency ranges and essentially act as complements to each other. Figure 8 below is the block diagram of the TRF6903 provided by TI, it will be referenced throughout the section [24].

Figure 8: RF Transceiver Block Diagram

The TRF6903 transceiver has a multitude of options that can be set for various aspects of transmission and reception. These choices are set by the microcontroller through the serial interface. Before the start of the transmission, the microcontroller sends data to the transceiver to program the program words. The transceiver has five program words which can be used to set choices such as desired output power, modulation scheme and whether the transceiver is in reception or transmission mode [24].

# Modulator/Demodulator

The first component on the transmitter side is the modulator. The modulator converts the incoming digital data stream into an analog waveform specified by the modulation scheme. It also increases the frequency of the entire stream to an intermediate frequency (IF) or in some cases all

the way to the transmission frequency. In the case that the modulator takes the stream to an IF frequency, the stream will later be converted to the band of choice later by an up-converter. The modulation in the TRF6903 is done by a phase-locked loop (PLL) which delivers the modulated signal at the desired transmit frequency, approximately 915MHz, without the need of an additional up-converter. The demodulator decodes the modulated received analog signal back to the original digital data signal. The TRF6903 uses a quadrature demodulator to demodulate the signal. As the block diagram indicates, the demodulator takes its input from the limiter.

#### Mixer

Up and down conversion of frequency are complementary operations that can both be accomplished using a mixer. In this project, only the down conversion is actually done by the mixer, the PLL serves to deliver a modulated output at the desired frequency for transmission. An ideal mixer produces an output that is proportional to the product of the inputs. When performing down-conversion, the inputs to the mixer are the RF input signal and a signal at the local oscillator frequency delivered by internal circuitry, in this case the PLL. Both of the signals can be simplified and viewed as pure sinusoids and represented as [20]:

$$V_{RF}(t) = \cos(2\Pi f_{RF}t) \tag{4.4}$$

$$V_{LO}(t) = \cos(2\Pi f_{LO}t). \tag{4.5}$$

Then the output is the product of the two input signals with an additional constant term introduced as a result of voltage loss in the operation of the mixer, it can be represented as:

$$V_{OUT} = A\cos(2\Pi f_{RF}t)\cos(2\Pi f_{LO}t). \tag{4.6}$$

Using simple trigonometric identities, the output signal can be viewed as:

$$v_{OUT} = \frac{A}{2} \left[ \cos(2\Pi t (f_{RF} - f_{LO}) + \cos(2\Pi t (f_{RF} + f_{LO})) \right]. \tag{4.7}$$

Thus the output frequency of the transmission is then simply:

$$f_{OUT} = f_{RF} \pm f_{LO}. \tag{4.8}$$

The desired frequency is the difference between the two frequencies which is selected using a low pass filter. Since the LO and RF frequencies are very close together, their sum and difference are then relatively far apart so that filtering out the sum signal can be done easily.

For ideal mixer operation, impedances at all three ports of the mixer should be matched. In many technologies, however, that is not the case. This leads to loss in output power, known as conversion loss. Matching can be done through the use of resistors with real impendence or reactive components such as capacitors and inductors which have imaginary impedance.

Adequate matching can be difficult in many cases since resistors dissipate power thus leading to overall loss and reactive components used in matching are typically highly frequency dependent. Although conversion loss is a reality for many mixer technologies, some technologies actually boast a conversion gain. Usually diode mixers have losses in the range of 4 to 7 dB and transistor mixers can deliver some gain [20]. The combination of the LNA and the mixer in the TRF6903 has a conversion gain of 18 dB [24]. The values for the LNA and mixer are given together since they work so closely together in the transceiver.

Another figure of merit relating to mixers is the noise figure. Noise figure is typically defined as [29]:

$$F = \frac{\text{SNR at Input}}{\text{SNR at Output}} \text{ [dB]}.$$

(4.9)

The combination of the LNA and the mixer in the TRF6903 has a single side band noise figure is 6.5 dB so the double side band noise figure then is 13 dB, including the external matching network [24].

### **Amplifiers**

Typically there are two general types of amplifiers that must be used in transceiver design. The first is a traditional power amplifier which is used on the transmitter side to amplify

the signal before it is transmitted. The second type of amplifier, a low noise amplifier (LNA) is used to amplify the received signal. At full utilization, the TRF6903's power amplifier delivers 8 dBm (or about 6.31mW) of output power to a matched  $50\Omega$  load. The power amplifier also has the ability to attenuate the output power by either 10dB or 20dB resulting in -2dBm (0.631mW) and -12dBm (0.0631 mW) output power to a matched load respectively. When the power amplifier is disabled, the output power delivered to a matched load is -80dBm ( $10^{-8}$  mW) [24]. This attenuation value is set by the microcontroller through the appropriate program words in the transceiver. In this project we normally output full power. The power amplifier is only activated during transmission since the current consumed and thus the power consumed rises significantly with the power amplifier active. When all other components are active but the power amplifier is disabled, the transceiver normally consumes 10mA of current, while when the power amplifier is active at full power in addition to all the other components the typical current consumption jumps to 35mA [24].

In receiver systems where there are generally low losses after the first amplifier, the noise figure of the entire system is most significantly affected by the performance of the first amplifier so a low noise amplifier is used. The output of the LNA is then fed directly to the mixer. In the TRF6903, the conversion gain of the LNA/mixer system is specified together since they work so closely together. The conversion gain of the system is 18dB and the SSB noise figure is 6.5dB. After passing through this stage, the frequency of the data is at the IF frequency, or 10.7MHz. This signal is then fed to a 10.7MHz discriminator and then to a limiter that has a gain of 86dB and a noise figure of 4dB. Finally this output is sent to the demodulator.

## Oscillation Techniques

Many of the RF components in a typical transceiver need a dependable input frequency. One method of delivering such a known frequency is through the use of crystals that oscillate due to the piezoelectric effect. When a voltage is applied across the faces of the crystal, forces are applied to bound charges which result in a vibration at a resonant frequency [29]. The reference

crystal used in this application is the Crystek 017119 which outputs a signal at 19.7MHz.

Multiples of this frequency is provided by a phase-locked loop (PLL) which takes a crystal oscillator as an input and outputs a signal with multiples of that frequency with noise and stability specifications similar to those of the highly accurate crystal oscillator [30].

A block diagram of the PLL used in the TRF6903, provided by TI, is shown below in Figure 9 [30].

Figure 9: PLL Block Diagram

The block diagram shows that the PLL basically consists of a phase detector that takes a signal at the reference frequency along with an N divided version of the output frequency. The phase detector then outputs a voltage proportional to the difference in phase of these two signals. The output of the phase detector is then fed to the voltage controlled oscillator which outputs a signal whose frequency is a function of the input of the voltage coming from the phase detector.

Eventually the PLL settles and delivers a frequency at a multiple, N, of the input reference.

During FSK operation at least two frequencies are required for transmission. This is accomplished by placing another capacitor ( $C_{FSK}$ ) in parallel to the external capacitor which is in series with the crystal oscillator. Referring back both the block diagram of the entire transceiver shown in Figure 8 and the block diagram of the PLL shown in Figure 9, we see that the effects of the  $C_{FSK}$  are controlled by the XTAL switch which is controlled by the input data. When the input data is low, the XTAL switch is closed which effectively removes the external FSK capacitor so that the net external capacitance is simply:

$$C_{net} = C_{external}. (4.10)$$

The output frequency ( $f_{logic\ low}$ ) then is based only on the single external capacitor and the crystal oscillator. When the input data is high, the XTAL switch is open which gives the net external capacitance:

$$C_{net} = C_{external} + C_{FSK}. (4.11)$$

The output frequency ( $f_{logic \, high}$ ) then is based on both capacitors [24]. In addition to serving as the modulator, during reception the PLL also delivers the LO frequency to the mixer that is used for down conversion. In the receive mode the XTAL switch is closed so that a constant frequency is delivered to mixer.

### Data Slicer and Bit Synchronizer

Before discussing the operation of the data slicer and bit synchronizer, it is instructive to look at the basic structure of a wireless packet. The packet starts off with a training sequence of alternating logic highs and lows that is used to train the internal components of the transceiver. After the training sequence, a start bit is sent that is three times the length of a normal bit to indicate that the training sequence has ended and data is about to begin. Lastly, the data is sent and the transmission is completed.

The purpose of the data slicer is to take data coming from the demodulator and output digital data to match the data originally sent by the transmitter. This is accomplished by comparing the output of the demodulator to a reference voltage. The reference voltage is set by the sample-and-hold (S&H) capacitor. During learn mode the S&H capacitor charges to the average value of the training sequence. After the training sequence is completed, the transceiver switches from learn to hold mode where it holds the S&H capacitor voltage and uses it to decipher the signal coming from the demodulator. The value of the S&H capacitor is given by [24]:

$$C_{SH} = \frac{\text{# of Training Bits}}{5*51k*(\text{Data Rate in (Hz)})}.$$

(4.12)

The time constant of the S&H capacitor is determined by factoring in an internal  $51k\Omega$  resistor. Thus the time constant is:

$$\tau = \frac{5 * (\text{Data Rate in Hz})}{\# \text{ of Training Bits}}.$$

(4.13)

This time constant then also then puts constraints on the duration of the incoming RF signal. As the voltage level of the S&H capacitor decays, the data slicer looses the ability to accurately decipher between logic highs and lows. In our project we use a 5.6nF capacitor for  $C_{SH}$ .

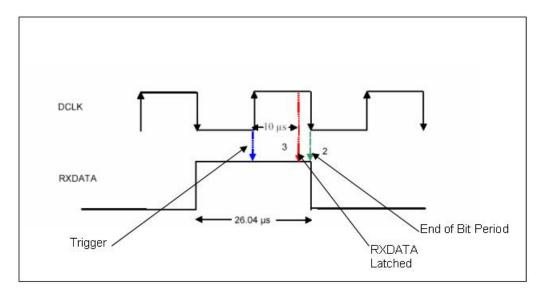

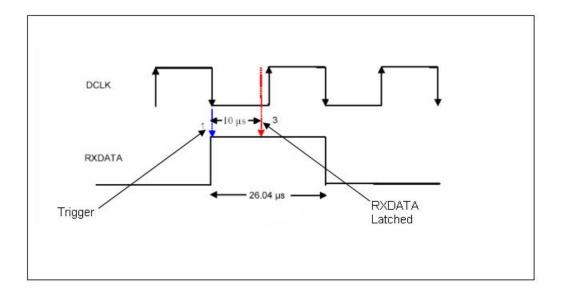

The bit synchronizer ultimately recovers the data at a predetermined frequency. The predetermined frequency is a function of the crystal and values provided by the microcontroller. The transceiver provides both the final received data at the RX\_DATA terminal and the corresponding clock at the DCLK terminal as shown in the block diagram in Figure 8.

#### **Reception Modes**

Depending on the needs of the user, the TRF6903 can operate in one of four reception modes. When operating in the raw data mode the output of the data slicer is directly fed to the output terminal RX\_DATA and the bit synchronizer is completely bypassed. In the Deglitch mode, the output of the data slicer is fed to a deglitch filter. If five or more of the last seven samples taken are logic highs, then the filter outputs a high, and if two or fewer of the last seven samples are logic highs then the filter outputs a low. If neither one of the conditions apply the value is kept the same. The frequency by which the filter samples that output of the slicer is programmed by the microcontroller. The clock used to sample the slicer data is provided at the DCLK terminal and the deglitched data is provided at RX\_DATA [24].

In clock recovery mode, the output of the deglitch filter is synchronized to a bit-rate clock. For the clock recovery mode to deliver the desired synchronous data the number of consecutive logic highs or logic lows, *NC*, must meet the condition:

$$NC < \frac{250000}{\Delta}$$

(4.14)

Where  $\Delta$  represents the error between the transmit bit rate and the receiver bit rate measure in parts-per-million (ppm). The deglitched data is outputted at the RX\_DATA terminal and the synchronous bit-rate clock is outputted at the DCLK terminal [24].

The last mode of operation is the self train mode where the transceiver also looks for the end of the training sequence in addition to performing clock recovery. The transceivers being used in this project operate in the self train mode. The outputs at the RX\_DATA and the DCLK terminal are identical to those when the transceiver is in the clock recovery mode but in the self train mode the RX\_FLAG terminal is raised to logic high for one clock cycle at the first bit not within the training sequence [24].

# Basic Antenna Facts

The antenna is the final piece of hardware on the transmitter side and the first piece of hardware on the receiver side. On the transmitter side the antenna is takes an electrical signal and converts it to an electromagnetic wave which propagates to the receiver side. On the receiver side, the antenna performs the complimentary action by converting the incoming electromagnetic wave to an electrical signal. By the Lorentz reciprocity theorem we find that the same antenna can be used for transmission and reception [31].

The radiation pattern of an antenna shows the strength of the field emanating from the antenna as a function of either the azimuthal angle,  $\varphi$ , or the elevation angle,  $\theta$  [20]. By the reciprocity theorem, this radiation pattern also shows how well the antenna receives in each direction.

The directivity of an antenna is a quantitative description of the radiation pattern. The directivity, D, of an antenna is defined as [31]:

$$D(\mathcal{G}, \phi) = \frac{\text{Power radiated per unit solid angle}}{\text{Average power radiated per unit solid angle}}.$$

(4.15)

Or equivalently as:

$$D(\mathcal{G}, \phi) = 4\Pi \frac{dP_{r}/d\Omega}{P_{r}}$$

(4.16)

where  $P_r$  is defined to be the total radiated power. Manufactures often refer to the maximum directivity simply as the directivity [31]. A high directivity cited by the manufacturer then implies that the electromagnetic wave emanating from the antenna is tightly confined and highly directional. The gain of an antenna is a closely related parameter that also takes into account the efficiency, e, of the antenna which is defined as being [20]:

$$e = \frac{P_r}{P_{in}} \tag{4.17}$$

where  $P_{in}$  is defined as being the total input power. The gain, G, of an antenna then is [20]:

$$G(\mathcal{G}, \varphi) = eD(\mathcal{G}, \phi). \tag{4.18}$$

An important receiving characteristic of an antenna is how much of the incident power is received by the antenna. This total received power can be expressed as [20]:

$$P_r = A_e S_{avg} (4.19)$$

where  $S_{avg}$  is the time average of the incident electromagnetic wave's Poynting vector and  $A_e$  is the effective area of the antenna. This area can be thought of being the effective area that captures the incoming information bearing wave. It can be shown that under matched impedance and polarization conditions, the effective area  $A_e$  can be expressed as [31]:

$$A_e = \frac{\lambda_0^2}{4\Pi} G(\theta, \phi) \tag{4.20}$$

where  $\lambda_0$  is the operating wavelength of the antenna. We are operating in the 902-928MHz frequency band so the characteristic wavelength is approximately 33cm.

Another critical parameter of an antenna is its impedance. This impendence determines the amount of power that will be delivered to the antenna. If the impedances of the transmission

line and antenna are not matched, some of the power will be reflected rather than fed to the antenna resulting in a reduction of the efficiency of the transmitting system.

#### Antenna Choice

In addition to the inverted-F PCB antenna that comes with the TI demonstration board, we also considered using a dipole antenna. In choosing the antenna we require that the antenna be able to be adjusted by the user to reduce the effects of polarization mismatch. This freedom in this azimthual and elevation directions allows for an optimal relative configuration of the transmitting and receiving antennas irrespective of the relative orientation of the FMB and the receiver. We also require the antenna be a nearly omnidirectional in the azimuthal direction as we would like to make the operation as simple as possible by not requiring a specific orientation for the antennas in the azimuthal direction.

In the end we chose a half-wave dipole antenna, the PSKN series, made by Mobile Mark. This antenna comes with a knuckle that allows its orientation to easily be changed as we had earlier stipulated. Furthermore, the dipole antenna has a predictable and an omnidirectional in the azimuthal direction making it easier to use for both users on the FMB and receiver side. It can be shown that the directivity of a half-wave dipole antenna is given by [31]:

$$D(\mathcal{G}, \phi) = 1.64 \left( \frac{\cos((\Pi/2)\cos\mathcal{G})}{\sin\mathcal{G}} \right)^{2}.$$

(4.21)

This pattern is plotted below in Figure 10:

Figure 10: Typical Half-Wave Dipole Radiation Pattern

Figure 10 shows that the antenna radiates and receives best along the y-axis and has a minimum transmission and reception along the z-axis. This shows that antenna should be oriented vertically rather than horizontally for optimum transmission. The PSKN series antenna has a maximum gain of 1.70 in the 870-960MHz band [32]. The PSKN series antenna also has an impedance of  $50\Omega$  which also is the impedance of the transmission line that feeds the antenna thus assuring no power is reflected back. Using (6.6) with a maximum gain of 1.70 we find that the maximum aperture is  $0.39\text{m}^2$ .

## Radio Propagation

Once the antenna radiates the electromagnetic wave, this information carrying wave must propagate through the communication channel during which it can be subject to a variety of effects that can impact its characteristics. The main propagation effects for communication in our frequency band are reflections, diffraction, scattering, attenuation and Doppler spread [20].

The effect of each of these factors depends heavily on the environment and application of the particular wireless device. Our goal is to design this device to work in all environmental conditions that fisheries researchers may encounter, thus we must plan for outdoor propagation in all types of weather conditions as well as indoor propagation. We assume this indoor environment to have various non-metallic obstacles blocking the line-of-sight.

Based on the conditions we expect to operate in, we make several assumptions. First we assume that the FMB and the receiver will not be moving relative to each other so Doppler shift will not be an important concern for us. Likewise, we also assume there will be no scattering objects such as foliage in the channel and no edges or corners that may cause significant diffraction. Our main concerns, then, are attenuation in the channel due to weather conditions and reflections from within their environment either indoor or outdoor. All of these channels effects tend to reduce the signal power from what would be expected in free-space propagation, thus reducing the signal to noise ratio which has been shown earlier to increase error rate.