**ABSTRACT**

Title of Dissertation: DESIGN AND FABRICATION OF ON CHIP

MICROWAVE PULSE POWER DETECTORS

Woochul Jeon, Doctor of Philosophy, 2005

Directed By: Professor John Melngailis

due to their fast pulse response time and small size.

Department of Electrical and Computer Engineering

On-chip microwave pulse-power detectors are promising devices for many electrical systems of both military and commercial applications. Most research in microwave power detector design have been focused on thermal power detectors, such as thermistors or thermocouples, due to their wide dynamic range and high frequency operation. However, due to their slow thermal response time, it is impossible to detect microwave pulses with a few micro or sub-micro seconds of pulse width. Schottky diode power detectors are the best candidates for this purpose

We have developed a means for fabricating Schottky diodes as part of any Complementary-Metal-Oxide-Semiconductor (CMOS) process by modifying the layout file. CMOS Schottky diodes were added at pre-selected locations through a CMOS process. We have also developed a process for adding or deleting Schottky diodes on a CMOS fabricated chip by using Focused Ion Beam (FIB). FIB milling and ion induced deposition were used for adding or deleting Schottky diodes at any desired location on a CMOS-fabricated chip as a post-CMOS process. Spice models

of CMOS Schottky diodes were developed and used for designing the RF front end circuits in passive RF circuits. MOSFET based RF pulsed power detector circuits were also designed and fabricated.

Fabricated power detectors were tested under direct injection and radiation of microwave pulse signals. Measured results for fabricated CMOS Schottky diodes, FIB Schottky diodes and MOSFET half-wave and full-wave rectifier circuits are summarized in a table with the pulse response time, the dynamic range, the sensitivity, and the frequency response to determine which power detector is the best choice for detecting a specific source signal.

# DESIGN AND FABRICATION OF ON CHIP MICROWAVE PULSE POWER DETECTORS

By

Woochul Jeon

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of

Doctor of Philosophy 2005

Advisory Committee:

Professor John Melngailis, Chairman/Advisor

Professor Robert W. Newcomb

Professor Agis A. Illiadis

Professor Victor L. Granatstein

Professor Michael S. Fuhrer

© Copyright by Woochul Jeon 2005

#### Preface

The thesis consists of eight chapters. Chapter 1 gives an introduction to the research. Chapter 2 presents basic operations of power detectors. Chapter 3 – 5 present the fabricated power detectors and measured results. Chapter 6 and 7 illustrate some applications of developed power detectors. Chapter 8 summarizes the thesis. Even though a number of details have been added in this thesis, the basic ideas presented in chapters 4 - 7 have been published earlier, which are in the following list.

#### Chapter 3 and Chapter 6.1:

W. Jeon, T. Firestone, J. Rodgers, and J. Melngailis, "Design and fabrication of Schottky diode, on-chip RF power detector", Proc., 2003 ISDRS, pp. 294-295, Washington DC, Dec. 2003

W. Jeon, T. Firestone, J. Rodgers, and J. Melngailis, "Design and fabrication of Schottky diode, on-chip RF power detector", Solid state electronics, Vol. 48, Iss. 10-11, pp. 2089-2093, Oct 2004

#### Chapter 4.2:

W. Jeon, T. Firestone, J. Rodgers, J. Melngailis, "On-chip RF pulse power detector using FIB as a post-CMOS fabrication process", Journal of Electromagnetics, in press

#### Chapter 4.2 and Chapter 6.2:

W. Jeon, T. Firestone, J. Rodgers, J. Melngailis, "CMOS/post-CMOS fabrication of on-chip Schottky diode microwave pulse power detectors", Proc., DET&E conference, Albuquerque, New Mexico, Aug. 2005

#### Chapter 5.1:

W. Jeon and J. Melngailis, "CMOS & Post CMOS Fabrication of on Chip Microwave Pulse Power Detectors", Proc., ISAP2005, Vol. 1, pp 221-224, Seoul, Korea, Aug. 2005

#### Chapter 5.2:

W. Jeon and J. Melngailis, "CMOS&post CMOS on-chip microwave pulse power detectors", 2005 ISDRS, Washington DC, Dec. 2005, Accepted

#### Chapter 7:

W. Jeon, J. Melngailis, and R. W. Newcomb, "CMOS passive RFID transponder with read-only memory for low cost fabrication", Proc., IEEE SOCC 05, pp. 181-184, Washington DC, Sept. 2005

W. Jeon, J. Melngailis, and R. W. Newcomb, "CMOS foundry Schottky diode microwave power detector fabrication, Spice modeling, and application", IEEE Intl. Work. Electronic Design, Test, & Applications (DELTA 2006), Jan. 2006, Accepted

## Dedication

To my loving daughter Ellena, my wife Yonghyun, my parents-in-law, and my parents.

## Acknowledgements

First and most of all, my deepest appreciation goes to my advisor, Professor John Melngailis for being an outstanding mentor. Without his support, I would have never completed my dissertation. With his brilliant ideas, he has encouraged me to explore a world I would have never experienced on my own. Whenever I wandered off the track, he guided me into the right direction with his considerable foresight and experience. His invaluable advice will always be with me.

I would also like to thank the other committee members for my dissertation: Professor Robert Newcomb, Professor Agis Illiadis, Professor Victor Granatstein, and Professor Michael Fuhrer. In particular, Professor Newcomb always had a novel suggestion when my research, especially in circuit and system design, encountered a problem. In the first stage of my graduate study, he introduced me to the world of microelectronics and gave me several lessons to survive as a graduate student.

I also appreciate the Department of Defense MURI 2001 Program for supporting my research and my growing family. In addition I wish to thank Professor Victor Granatstein and Dr. John Rodgers for many useful discussions. I am also grateful to John Barry, Tony DeMarco, and Todd Firestone for being friends and helping me with fabrication and measurement.

My wife, Yonghyun Cho, my parents, Sangyong Jeon and Haeja Lee, and my parents-in-law, Gwanghee Cho and Byungsoon Lee, have been always supportive of me in everything I did. Without their love and never-ending support, I could not have finished my graduate studies. Special thanks to my daughter, Ellena, who makes me laugh at any given moment.

## Table of Contents

| Preface                                                          | ii   |

|------------------------------------------------------------------|------|

| Dedication                                                       | iii  |

| Acknowledgements                                                 | iv   |

| Table of Contents                                                | v    |

| List of Tables                                                   | vii  |

| List of Figures                                                  | viii |

| Chapter 1 Introduction                                           | 1    |

| Chapter 2 Power detectors                                        | 4    |

| 2.1 Thermistors                                                  | 3    |

| 2.2 Thermocouples                                                | 5    |

| 2.3 Diodes                                                       | 6    |

| 2.4 Microwave pulse power detectors                              | 8    |

| 2.5 Schottky diode power detectors                               | 10   |

| 2.6 Planar Schottky diodes                                       | 13   |

| Chapter 3 CMOS Schottky diode power detector                     |      |

| 3.1 Schottky diodes by a CMOS compatible process and FIB process | 17   |

| 3.1.1 Fabrication                                                | 17   |

| 3.1.2 Measured result                                            | 19   |

| 3.1.3 Schottky diodes by Focused Ion Beam process                | 26   |

| 3.2 CMOS Schottky diodes                                         | 30   |

| 3.2.1 Fabrication                                                |      |

| 3.2.2 Measured result                                            | 30   |

| Chapter 4 Post-CMOS Schottky diode power detectors               | 35   |

| 4.1 Focused Ion Beam system                                      |      |

| 4.1.1 Liquid metal ion source                                    | 37   |

| 4.1.2 Ion column                                                 |      |

| 4.1.3 FIB milling                                                |      |

| 4.1.4 FIB ion induced deposition                                 |      |

| 4.1.5 FEI Dual Beam system 620                                   |      |

| 4.2 FIB Schottky diodes on a CMOS chip                           | 42   |

| 4.2.1 Design and fabrication                                     |      |

| 4.2.2 Measured result                                            |      |

| 4.2.3 Bridge shaped FIB Schottky diode                           | 51   |

| Chapter 5 MOSFET power detecot circuits                          |      |

| 5.1 Diode connected MOSFET with a bias circuit                   | 55   |

| 5.1.1 Operation                                                  | 56   |

| 5.1.2 Simulation and DC measured result                          | 57   |

| 5.1.3 Microwave pulse direct injectoin                           |      |

| 5.2 Full-wave rectifier circuit                                  |      |

| 5.2.1 Operation                                                  | 61   |

| 5.2.2 Simulation and DC measured result                          |      |

| 5.2.3 Microwave pulse direct injection                           |      |

| Chanter 6 Microsyava radiation massurament                       | 67   |

| 6.1 RF radiation on a silicon wafer                      | 67  |

|----------------------------------------------------------|-----|

| 6.1.1 Experiment                                         | 67  |

| 6.1.2 Measured result                                    | 69  |

| 6.2 RF radiation on a board                              | 71  |

| 6.2.1 Experiment                                         | 71  |

| 6.2.2 Measured result                                    | 73  |

| 6.2.3 Antenna gain                                       | 75  |

| Chapter 7 CMOS Schottky diode modeling and applications  | 78  |

| 7.1 CMOS Schottky diodes                                 | 78  |

| 7.1.1 CMOS Schottky diode design                         | 79  |

| 7.1.2 Measured result                                    | 79  |

| 7.2 CMOS Schottky diode SPICE modeling                   | 82  |

| 7.2.1 SPICE modeling of a fabricated CMOS Schottky diode | 82  |

| 7.2.2 Simulation result and measured reuslt              | 83  |

| 7.3 Applications                                         | 85  |

| 7.3.1 Charge pump circuit                                | 85  |

| 7.3.2 Voltage reference circuit with Schottky diodes     | 88  |

| Chapter 8 Conclusion                                     | 90  |

| 8.1 Comparison of the measured results                   | 90  |

| 8.2 Conclusion                                           | 94  |

| 8.3 Contribution                                         | 96  |

| 8.4 Challenge                                            | 97  |

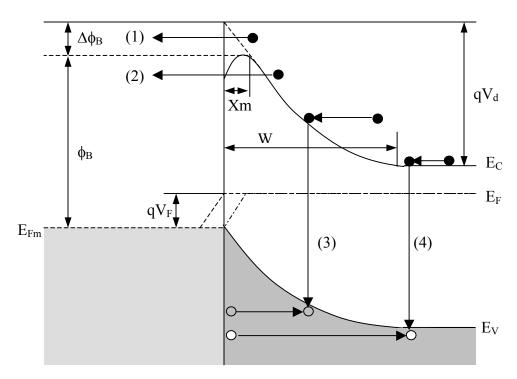

| Appendix A Schottky diode carrier transport mechanism    |     |

| B.1 Thermionic emission                                  |     |

| B.2 Tunneling through the barrier                        | 103 |

| B.3 Carrier generation and recombination                 |     |

| B.4 Minority Carrier Injection                           | 104 |

| Appendix B Barrier height calculation                    |     |

| Appendix C Charge pump circuit design                    | 114 |

| Bibliography                                             | 115 |

## List of Tables

| 1.1 | Comparison of three types of power detectors                   | 10  |

|-----|----------------------------------------------------------------|-----|

| 4.1 | Specifications of Ion beam and electron beam columns           | 42  |

| 8.1 | Summary of the measured results for fabricated power detectors | 93  |

| B.1 | Calculated Barrier heights of the fabricated Schottky diodes   | 110 |

# List of Figures

| Figure 2.1 Power detector with a balanced Wheatstone bridge                             |

|-----------------------------------------------------------------------------------------|

| Figure 2.2 Power detector with thermocouples                                            |

| Figure 2.3 (a) Power detector with diode                                                |

| (b) Simulation result for RF pulse input                                                |

| Figure 2.4 DC ouput vs. Power input curve of a diode                                    |

| Figure 2.5 Equivalent lumped-element circuit of a Schottky diode                        |

| Figure 2.6 Corss-section view of a reverse-biased CMOS Schottky diode and its           |

| associated equivalent circuit elements                                                  |

| Figure 2.7 Distributed RC network of the Schottky contact for calculating the           |

| spreading resistance                                                                    |

| Figure 3.1 Lab-fabricated Schottky diode and cross-section view                         |

| Figure 3.2 I-V curve of Schttky diode in Figure 3.1                                     |

| Figure 3.3 RF direct injection with GSG Cascade probe                                   |

| Figure 3.4 Experimental setup for RF burst direct injection                             |

| Figure 3.5 RF direct injection to $2x2 \mu m2$ Schottky diode: Frequency sweep result22 |

| Figure 3.5 RF direct injection to 2x2 μm2 Schottky diode: Power sweep result22          |

| Figure 3.7 Optput voltage pulse in response to 2GHz and 20GHz RF burst23                |

| Figure 3.8 Equivalent lumped-element circuit of a Schottky diode for calculating the    |

| pulse response time                                                                     |

| Figure 3.9 SEM images and cross-section views of fabricating steps by FIB27             |

| Figure 3.10 DC I-V measured result of a Schottky diode by FIB                           |

| Figure 3.11 Frequency sweep for FIB Schottky diode                                      |

| Figure 3.12 Power sweep for FIB Schottky diode                                 | 29    |

|--------------------------------------------------------------------------------|-------|

| Figure 3.13 GSG pads for injecting RF pulse, top view and cross-section view   | 30    |

| Figure 3.14 DC I-V measured results for FIB diodes.                            | 33    |

| Figure 3.15 RF pulse injection measured result: frequency sweep and power swee | p.34  |

| Figure 4.1 Ion column in a Focused Ion Beam system.                            | 36    |

| Figure 4.2 Liquid Metal Ion Source (LMIS).                                     | 37    |

| Figure 4.3 FIB milling.                                                        | 38    |

| Figure 4.4 FIB ion induced deposition.                                         | 40    |

| Figure 4.5 Dual Beam system.                                                   | 41    |

| Figure 4.6 Cross-sectioning by FEI Dual Beam system 620 and cross-section vie  | w of  |

| a CMOS chip.                                                                   | 43    |

| Figure 4.7 FIB Schttky diode fabrication.                                      | 44    |

| Figure 4.8 SEM pictures of the fabrication process for FIB Schottky diode      | 45    |

| Figure 4.9 Layout and SEM images of an n-type Schottky diode fabrication step  | s by  |

| FIB                                                                            | 46    |

| Figure 4.10 RF direct measurement setup                                        | 47    |

| Figure 4.11 Measure result of FIB Schottky diode: I-V curves                   | 48    |

| Figure 4.12 RF direct injection measured result.                               | 49    |

| Figure 4.13 Frequency sweep from 1GHz to 15GHz at 15dBm                        | 50    |

| Figure 4.14 Coplanar Si-MBE Schottky diode developed for rectifying antenna    | ıs by |

| Strohm et al.                                                                  | 51    |

| Figure 4.15 Bridge shaped FIB Schottky diode fabrication                       | 53    |

| Figure 4.16 RF pulse response of bridge shaped FIB Schottky diode              | 54    |

| Figure 5.1 MOSFET power detector circuit                                       | 55 |

|--------------------------------------------------------------------------------|----|

| Figure 5.2 Simulated and measured DC curve of a MOSFET power detector          | 57 |

| Figure 5.3 Experimental setup for RF burst injection to MOSFET power detector. | 58 |

| Figure 5.4 Power sweep at 1GHz.                                                | 59 |

| Figure 5.5 Frequency sweep at 5dBm.                                            | 59 |

| Figure 5.6 Full-wave rectifier circuit.                                        | 60 |

| Figure 5.7 Full-wave rectifier circuit operation.                              | 61 |

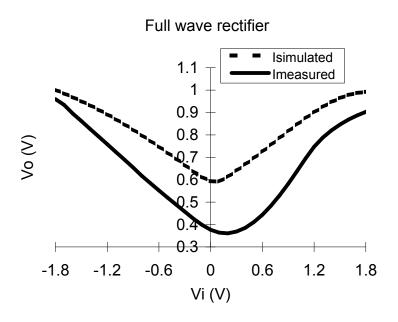

| Figure 5.8 Simulated and measured DC result.                                   | 64 |

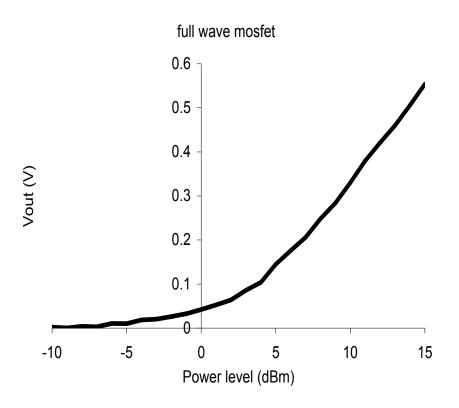

| Figure 5.9 Power sweep from –10dBm to 15dBm at 1GHz                            | 65 |

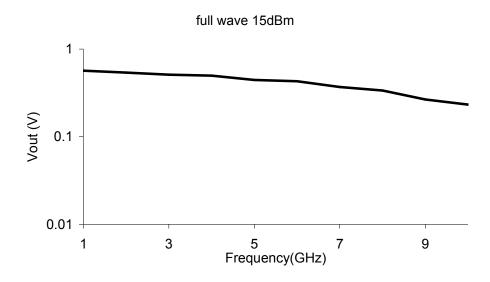

| Figure 5.10 Frequency sweep from 1GHz to 10GHz at 15dBm                        | 66 |

| Figure 6.1 RF radiation test on a patch antenna structure on a silicon wafer   | 68 |

| Figure 6.2 Frequency sweep result: RF radiation.                               | 70 |

| Figure 6.3 Power sweep result: RF radiation.                                   | 70 |

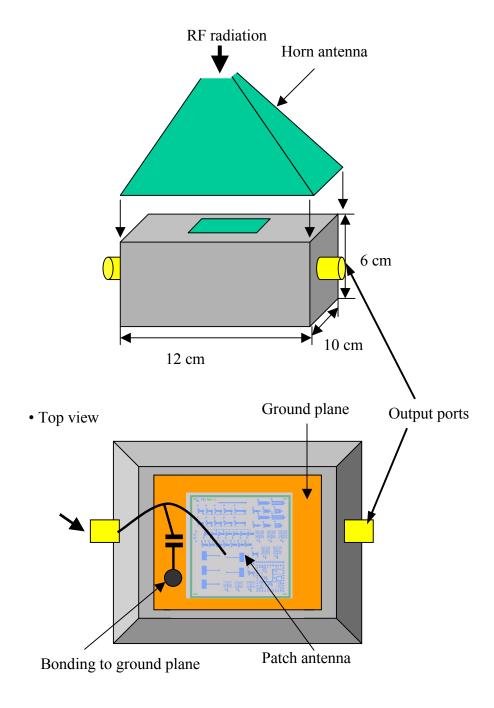

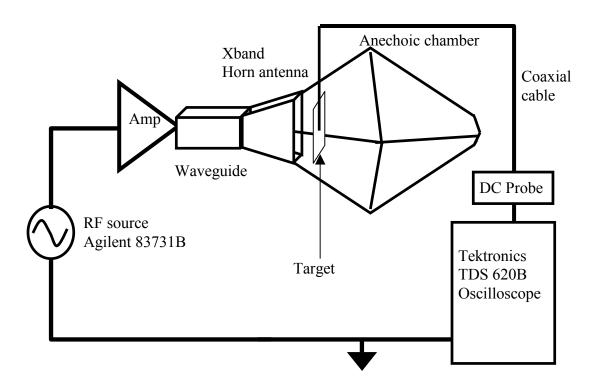

| Figure 6.4 Experimental setup for RF radiation test.                           | 71 |

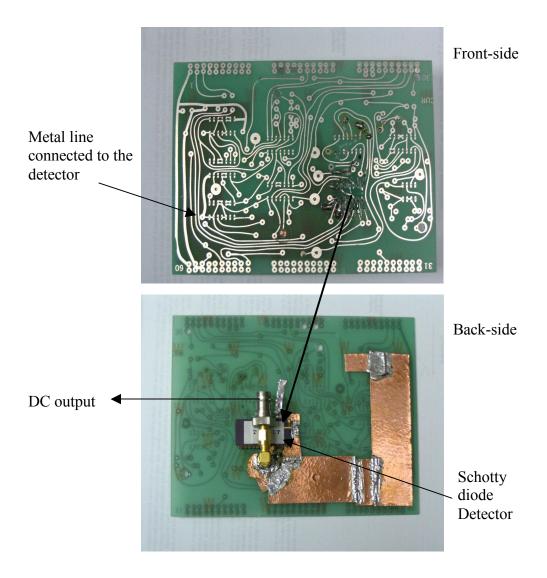

| Figure 6.5 The circuit board for RF radiation test.                            | 72 |

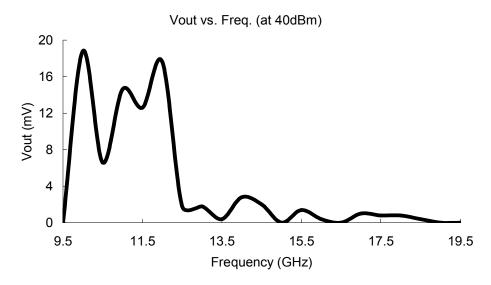

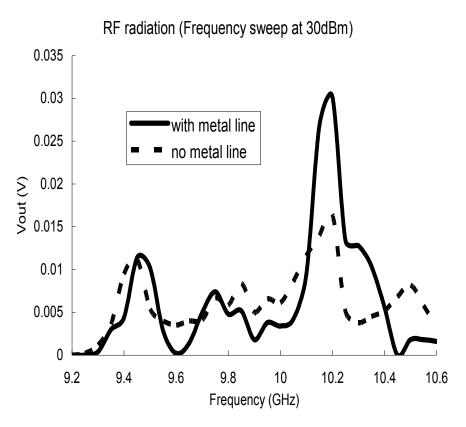

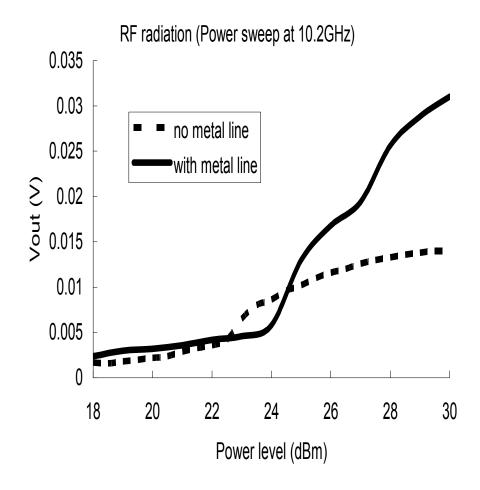

| Figure 6.6 Frequency sweep result: RF radiation.                               | 74 |

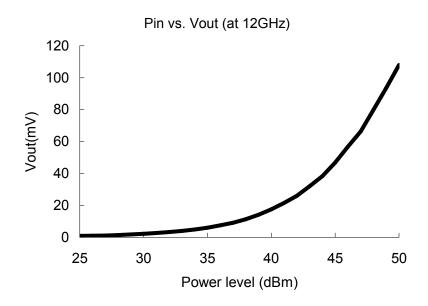

| Figure 6.7 Power sweep result: RF radiation.                                   | 75 |

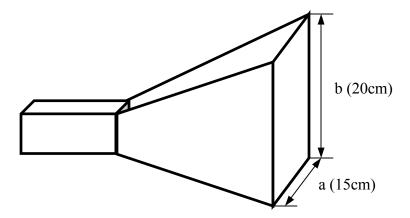

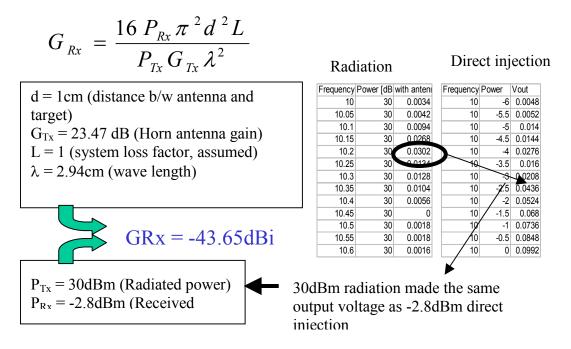

| Figure 6.8 X-band horn antenna                                                 | 77 |

| Figure 6.9 Antenna gain calculation.                                           | 77 |

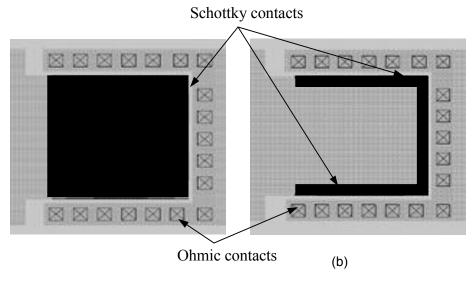

| Figure 7.1 Layouts of two CMOS Schottky diodes                                 | 79 |

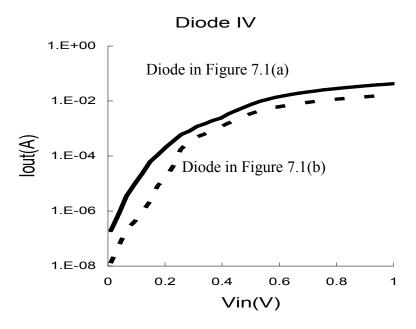

| Figure 7.2 Measured result of two Schottky diodes                              | 80 |

| Figure 7.3 DC measured result of 10 n-type large Schottky diodes               | 80 |

| Figure 7.4 DC measured result of p-type Schottky diodes                        | 81 |

| Figure 7.5 Schottky diode model for a Spice simulation                       | 83  |

|------------------------------------------------------------------------------|-----|

| Figure 7.6 Measured and simulated result of the CMOS Schottky diode          | 84  |

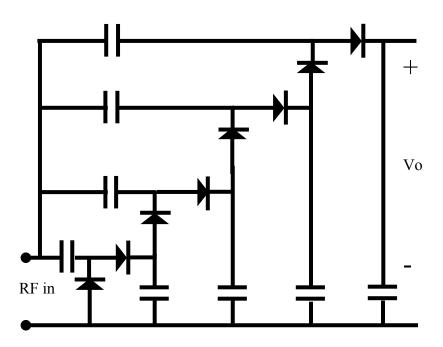

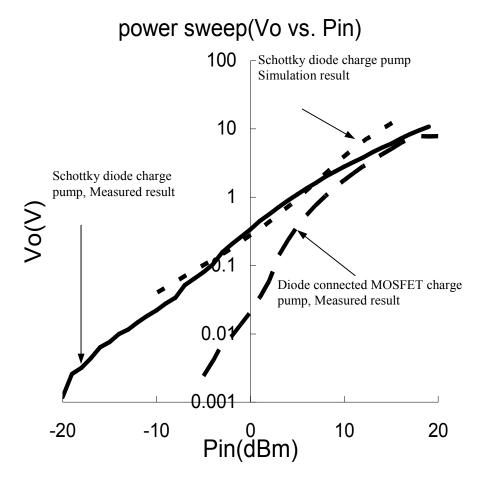

| Figure 7.7 4-stage charge pump circuit with Schottky diode                   | 85  |

| Figure 7.8 Measured and simulated result of the fabricated charge pump       | 87  |

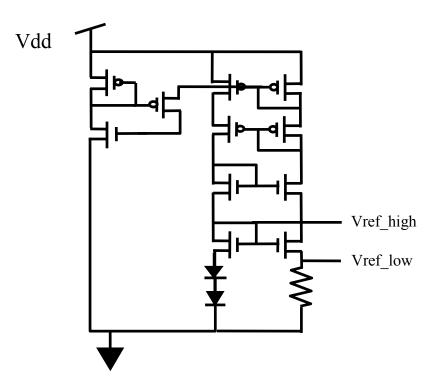

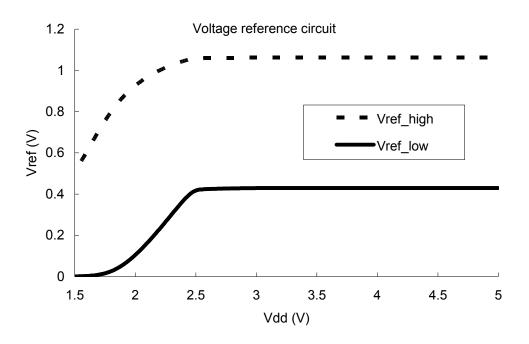

| Figure 7.9 Voltage regulator circuit with two Schottky diodes                | 88  |

| Figure 7.10 Simulation result of the voltage regulator circuit in Figure 7.9 | 89  |

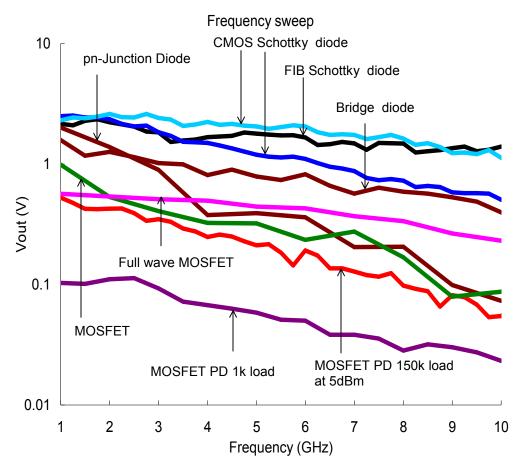

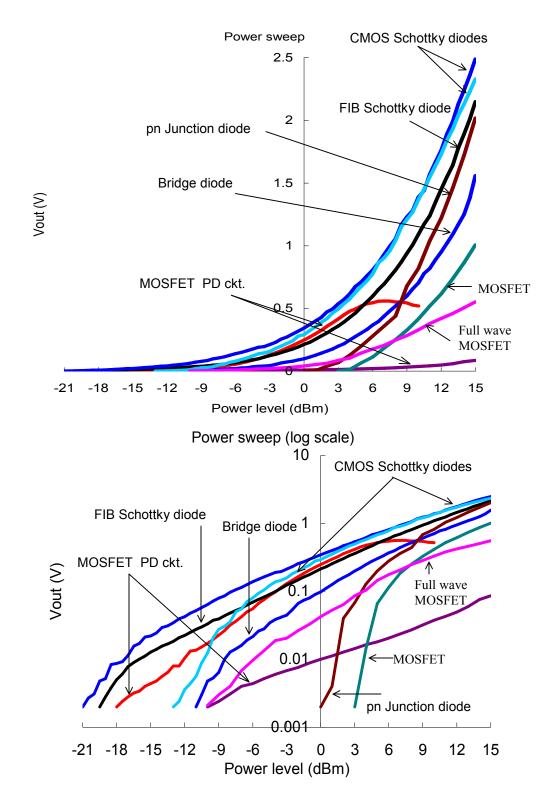

| Figure 8.1 Frequency sweep for fabricated power detectors                    | 91  |

| Figure 8.2 Power sweep for fabricated power detectors                        | 92  |

| Figure A.1 Carrier transportation mechanisms of a Schottky diode             | 100 |

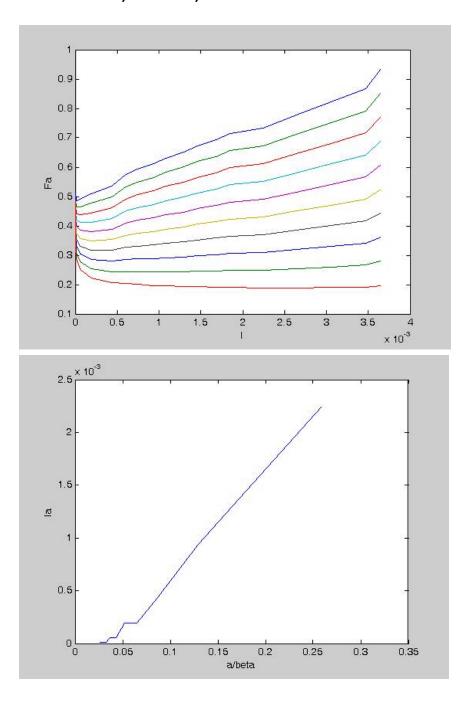

| Figure B.1 Fa-versus-I graph and Ia-versus-a/β graph.                        | 107 |

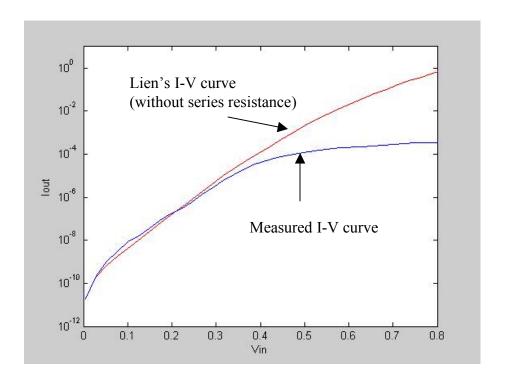

| Figure B.2 Measured I-V curve and Lien's I-V curve by MATLAB                 | 108 |

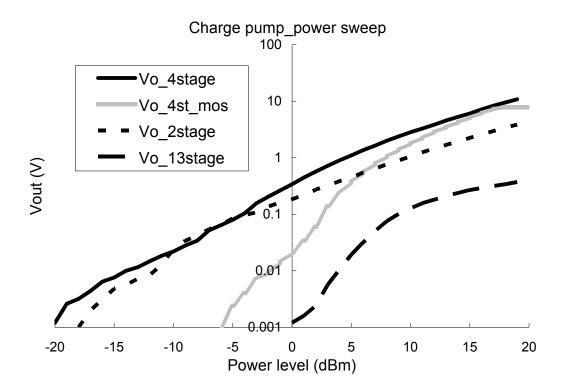

| Figure C.1 Measured results of the fabricated charge pump circuits           | 116 |

## **Chapter 1: Introduction**

Modern electronic systems are increasingly vulnerable to malfunction due to incident electromagnetic radiation, particularly since many integrated circuits operate at lower and lower voltages. The damaging RF radiation can be intentional, namely produced by high power microwave (HPM) weapons [1], or it can be due to ambient sources, such as lightning.

How, and at what level, microwaves penetrate equipment shielding and reach the vulnerable chips is of increasing interest. This motivates our project to build on-chip RF pulse power detectors both for measuring power at the chip level and at the board level and for developing strategies to mitigate its effects. Knowing the RF power levels in various chips and in various locations within chips is likely to be more useful than the "binary" information that a given external RF power level made the circuits fail.

Ideally the on-chip power detectors would have a wide dynamic range, and be fabricated in a standard CMOS process. For this purpose, several power detectors on silicon substrate have been reported, though most of them were not intended to be inserted directly on a chip. Power detectors usually used are thermistors, thermocouples, and diodes. The thermistor is used as a thermometric element and measures the temperature increase of a load, which is placed nearby and absorbs the injected RF power [2]. The thermocouples are based on the Seebeck effect, a voltage appears due to temperature gradient between two junctions in a closed circuit of two different metals, and used to measure the temperature increase of a load [2, 3]. Diodes are used to convert a high frequency signal to DC signal by rectifying the input signal.

Especially, Schottky diodes are known as fast rectifying devices and can be used as RF power detectors [4]. Because Schottky diodes have the fastest response time to a pulse input, Schottky diodes are exclusively used for RF pulse measurements. In the preliminary experiments, Schottky diodes for RF detection have been designed and built using both fabrication steps compatible with CMOS processes and post-fabrication focused ion beam (FIB) milling and deposition steps [5]. Because CMOS process is not specified for a Schottky contact, a modification of a CMOS process is required. As an alternate method, MOSFET diodes with bias circuit can be used for RF power detection for a low frequency range up to 5GHz. And, as a post-CMOS process, the use of FIB for fabricating Schottky diodes at any location of interest on a CMOS-fabricated chip is demonstrated. As an application of the suggested CMOS Schottky diodes, a charge pump circuit with CMOS Schottky diodes was designed and used in an RFID transponder.

The objectives of my thesis is design and fabrication of Schottky diode and MOSFET circuit on-chip microwave pulse power detectors by using both CMOS and post-CMOS process. We have developed a process for fabricating Schottky diodes in any CMOS process by modifying the layout file and a process for adding or deleting Schottky diodes on a CMOS-fabricated chip by using FIB. CMOS Schottky diodes are essential components for designing an RF passive integrated circuit. MOSFET based RF pulsed power detector circuits for detecting short microwave pulse with less than 100ns pulse width were designed and fabricated. Little work has been done on fabricating Schottky diode on silicon or on using MOSFET diodes for making on-chip power detectors. The use of FIB as a post-CMOS process to fabricate Schottky

diode power detectors has not been reported yet. The CMOS Schottky diodes were modelled by using Spice. The calculated I-V curves agreed with the measured DC I-V curves. The measured result and model of CMOS Schottky diodes would be helpful to reduce the effort for designing the RF front end circuits in passive RF circuits.

## **Chapter 2: Power detectors**

Thermistors, Thermocouples, and Diodes are typically used as power detectors. Both thermistors and thermocouples use the fact that the incident microwave changes the characteristics of specific materials by increasing the temperature of the materials. Diodes directly rectify the incident microwave to a half-wave signal. By filtering the rectified signal with a low pass filter and measuring the DC output, the incident power level is measured. Since diodes are of the main interest in my thesis, other two methods will be examined briefly.

#### 2.1 Thermistors

Thermistors are made from semiconductors, metallic oxides, or metals [6]. The electrical resistance of the thermistor varies with the incident power by the Joule

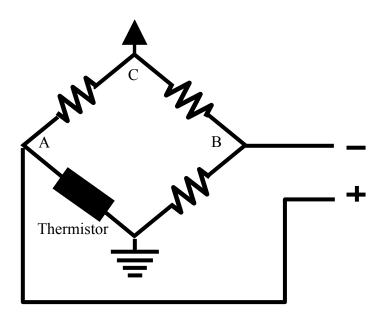

**Figure 2.1:** Power detector with a Balanced Wheatstone bridge consists of a thermistor and three identical resistors

effect. The Wheatstone bridge structure is used to measure the resistance change and hence the incident power. (Figure 2.1) Once RF power is injected to a thermistor, the resistance of the thermistor becomes lower and the voltage difference between the node A and the node B changes. A differential amplifier detects and amplifies the voltage difference and sends current to the node C for maintaining thermistor resistance to  $50\Omega$  for matching to RF source. By measuring the current output of a differential amplifier, the injected power level can be known. Typical operation range of thermistor power detector is between  $-20 \, \text{dBm}$  and  $10 \, \text{dBm}$  [2]. Kopystynski et al. [6] fabricated and measured a wide band width (dc to  $26 \, \text{GHz}$ ) power detector, which had a laser-trimmed  $50\Omega$  nichrome resistor as a thermal resistor. The dynamic range of their sensor was from  $-10 \, \text{dBm}$  to  $20 \, \text{dBm}$ .

#### 2.2 Thermocouples

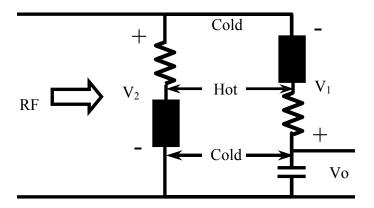

Thermocouple power detectors are based on the fact that dissimilar metals generate a voltage due to temperature difference at a hot and cold junction of the two metals. The RF power injected to both hot junctions of thermocouples generates potential difference from hot and cold junctions. (Figure 2.2)

Various types of thermocouple power detectors on silicon or other substrate materials have been suggested. The input power levels of these thermocouple power detectors are between –30dBm to 20dBm and can be extended by using an attenuator [2]. Jaeggi et al [7] used CMOS polysilicon and aluminum junction as a thermocouple and their detector worked between –30dBm and 10dBm at the frequency of up to 400MHz. Haberli et al. [8] used CMOS compatible process to fabricate a power detector with an A/D converter, and its dynamic range was –30dBm to 10dBm.

**Figure 2.2:** The Power detector with thermocouples.  $V_0 = V_1 + V_2$  Each thermo-couple consists of two different metals. (For example, Aluminum and poly silicon in CMOS process [13])

Kodato et al. [9] fabricated two thermal power sensors with Bi-Sb thermocouple. They operated in the power level of between –30dBm and15dBm and –20dBm and 20dBm at the frequency of up to 40GHz and 65GHz. The response time was 3ms and 40ms, respectively. Milanovic [10, 11, 12, 13] designed and tested a thermocouple microwave power detector fabricated through an n-well CMOS foundry with an additional etching process. They used polysilicon and metal as a thermocouple. Their detector detected the input power from –30dBm to 10dBm in the frequency range from 50MHz to 20GHz. And they improved their sensor to extend the frequency range up to 50GHz. [14, 15].

## 2.3 Diodes

Diodes, which have been used for signal level detection for a century, convert RF signals to DC signals by rectifying input signal. A diode rectifier circuit consists of a rectifying diode, a filter capacitor, and a resistor. (Figure 2.3) The diode rectifies the

incident RF signal, and the capacitor and the resistor produce a DC output by filtering out the high frequency part of the rectified signal.

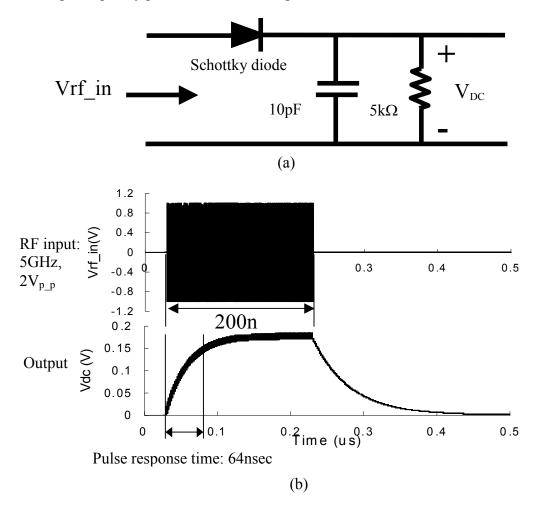

**Figure 2.3:** (a) Power detector with a Schottky diode. RF input is rectified by the Schottky diode and stored in the capacitor. (b) RF pulse input is filtered to low frequency signal. (Schottky diode model: turn on voltage: 0.2V, series resistance:  $214\Omega$ , junction capacitance: 16fF)

For a small input voltage, the series resistance can be ignored because the junction resistance is much bigger than the series resistance. And, mathematically, if we assume the therminoic emission is dominant among the carrier transport mechanisms, a diode obeys the following diode equation.

$$I = I_s(e^{\frac{q}{nkT}V} - 1)$$

(2.1)

This equation can be written as a power series for the better analysis of rectifying action.

$$I = Is(\frac{q}{nkT}V + \frac{(\frac{q}{nkT}V)^2}{2!} + \frac{(\frac{q}{nkT}V)^3}{3!} + ....)$$

(2.2)

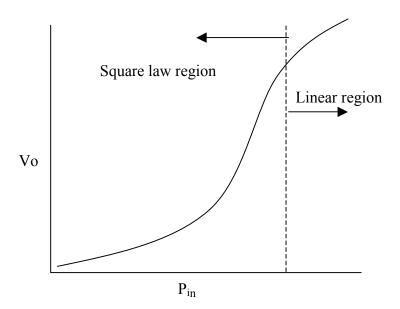

The second and other even-order terms of this series provide the rectification because negative voltage input becomes positive component in this series. The second order term is the most significant in a small signal operation and dc output is proportional to the square of power level, the diode is said to be operating in the square law region [2]. If the input signal becomes larger, the third term and higher terms become significant and the series resistance cannot be ignored, the diode is no longer in the square law operation region and moves into the linear region where the output voltage is proportional to the input voltage. (Figure 2.4) A typically biased Schottky diode has the square law region of between –70dBm to –20dBm, the transition region of between -20dBm to 0dBm, and the linear region of above 0dBm in a 50Ω matching

Figure 2.4: DC output vs. Power input curve of a diode.

system. The square law region can be extended up to 20dBm by using an attenuator, the linear compensation, molecular beam exptaxy (MBE), or Gallium-Arsenide (GaAs) semiconductor material technology [2]. Attenuators and calibrators are usually made by using digital signal processing circuitry.

Any type of diode can be used for power detection. The pn junction diode would be a sensitive RF detector. However, for the high frequency operation, minimizing the junction capacitance and the series resistance is required, and the bandwidth of the pn junction diode is limited due to the stored charge effects. Schottky diodes do not store charge in the junction and can be used for high frequency applications, and the low potential barrier across the junction increase the sensitivity of the Schottky diode power detector.

#### 2.4 Microwave pulse power detectors

The most important parameters characterizing microwave pulse detectors in circuits are the pulse response time, operating frequency, and sensitivity. The frequency range of interest in HPM source is from 1GHz to 10GHz and the pulse durations are from 10's to 100ns [16]. For detecting HPM source with 100ns of pulse width, the pulse response time of pulse power detector should be shorter than 100ns. Thermocouples, thermistors, and Schottky diodes, which can be fabricated on a standard CMOS process, have been used for RF power measurement due to their wide dynamic range [2]. Thermocouple power detectors have better performance than thermistors and due to their accuracy, broadband operation, and high dynamic range, they are usually used for power measuring instruments. Even though micron-size wires could have sub-microsecond thermal time constants, and superconducting

bolometers can be very fast, the fabrication would be expensive and it would be difficult to fabricate them directly on a silicon chip. Since both thermocouples and thermistors made by a typical fabrication process such as CMOS process have at least a few milliseconds of thermal time constant due to the heating and cooling of the sensing elements [2], they are not useful for RF pulse detection. Schottky diodes have much faster response, a few µs or less, and are the most promising devices for the RF pulse detection [4]. From the simulation result in Figure 2.3, the pulse response time of a Schottky diode is 64ns, which means any microwave pulse with more than 64ns of pulse width can be efficiently detected. Table 1.1 summarized the characteristics of three types of power detectors.

|              | Oprating frqeucncy | Dynamic Range    | Pulse Response time |

|--------------|--------------------|------------------|---------------------|

| Thermistors  | Almost no limit    | -20dBm to 10dBm  | 1-10 ms             |

| Thermocouple | Annost no mint     | -30dBm to 20dBm  | 1-10 ms             |

| Diodes       | Up to 100GHz       | -70dBm to -20dBm | 0.1-10 μs           |

Table 1.1. Comparison of three types of power detectors.

### 2.5 Schottky diode power detectors

In 1874 Karl Ferdinand Braun discovered one-way conduction in metal sulfide crystals and created the cat's whisker diode as the first step of Schottky diode [17]. L.O. Grondahl and P.H. Geiger found rectifying properties in a semiconducting copper oxide-copper junction in 1926 [18] and Dr. Walter Schottky published his diffusion theory of current transport in metal-semiconductor junctions in 1938 [19]. After his theoretical explanation, many researchers have used Schottky barrier diodes

for various applications and Siemens had begun commercially manufacturing Schottky diodes for microwave use.

Microwave power detection is one of the most popular microwave applications of Schottky diodes, since Schottky diodes are majority carrier devices and their junction capacitors can be small enough to be used for microwave rectification. Either GaAs [20] or Si [21, 22, 23] Schottky diodes are usually used for the RF power detection. GaAs Schottky diodes operating in THz region have been reported [20]. Ideally the chip power detectors would be fabricated in a standard CMOS process, and GaAs Schottky diodes do not fulfill to this purpose. Silicon Schottky diodes are known as fast rectifying devices and can be used as RF power detectors [4]. In special Molecular Beam Epitaxy (MBE) grown geometries, RF detection up to 100GHz has been reported [23, 24, 25]. However in CMOS-foundry-fabricated diodes detection of only up to 600MHz has been reported [23, 26].

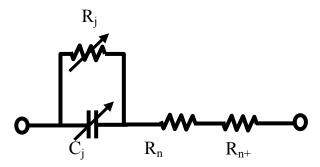

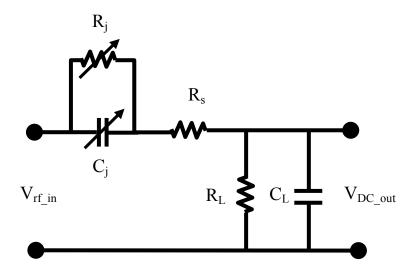

To increase this cut off frequency, we needed to examine the key factors to limit high frequency region operation. From the equivalent lumped-element circuit model of a Schottky diode (Figure 2.5), a Schottky diode obeys the same expressions as a pn

**Figure 2.5:** Equivalent lumped-element circuit of a Schottky diode.  $R_n$  is series resistance in n layer,  $R_j$  is the junction resistance,  $C_j$  is the junction capacitance, and  $R_{n+}$  is the series resistance in n+ layer. For low voltage input,  $R_j$  is much bigger than  $(R_n + R_{n+})$ . For high voltage region, the series resistance is dominant due to the small junction resistance.

junction diode. The junction capacitance, the junction resistance, and series resistances are given as [4] equation (2.3), (2.4), and (2.5).

$$C_j = A\sqrt{\frac{\varepsilon q N_d}{2(V_a + V_d)}} \tag{2.3}$$

$$\frac{1}{R_i} = \frac{dI_x}{dV_a} = AI_s \frac{q}{nkT} \exp\left(\frac{qV_a}{nkT}\right)$$

(2.4)

$$R_{series} = R_n + R_{n+} = R_o / A + R_1 / \sqrt{A}$$

(2.5)

Where A is the contact area, Nd is the doping concentration, Va is an applied voltage, Vd is the built in voltage,  $R_o$  and  $R_1$  is constant. Equation (2.5) is derived from the planar diode equation, which is introduced in the next section. Series resistance includes spreading resistance term due to the geometry of the buried layer, which is proportional to  $1/\sqrt{A}$ . From equations (2.3) and (2.5), the cut-off frequency,  $1/(R_{\text{series}}+R_j)C$ , of a Schottky diode is proportional to  $1/\sqrt{A}$ . To achieve a high cut off frequency, it is necessary to decrease the contact area and ultimately the resistance in the lightly doped n layer. To reduce the resistance in the lightly doped n layer, one method used is silicon molecular beam epitaxy (Si-MBE) [22, 25]. This process has been shown to reduce the n layer thickness to 0.3 $\mu$ m, which is near but not smaller than the depletion length of a Schottky diode. However, Si-MBE cannot be done in standard CMOS processes and another design compatible with the CMOS fabrication process is desired.

### 2.6 Planar Schottky diodes

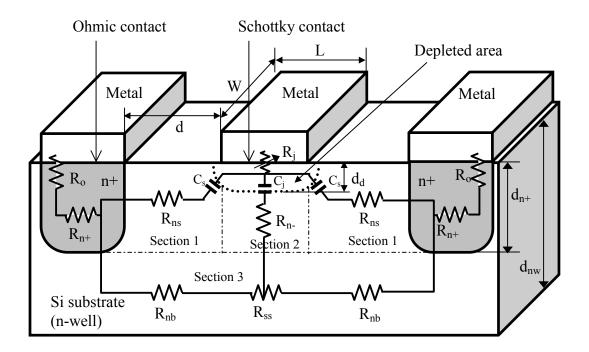

The planar diode is designed for an easy integration into circuits, especially for on-chip microwave power detection. The conduction path should be as short as possible to achieve a low series resistance. The contact area also should be small to reduce the contact capacitance and increase the cut-off frequency. Figure 2.6 shows a cross-section view of a CMOS Schottky diode and its associated equivalent circuit elements. The diode consists of a Schottky contact between the metal and the lightly doped n-well (or p-well) layer and an ohmic contact between the metal and the highly doped n+ diffusion (or p+ diffusion) layer. The active layer under the Schottky contact of length L and width W is regarded as an R-C circuit, with the capacitance of

**Figure 2.6:** Cross-section view of a reverse-biased CMOS Schottky diode and its associated equivalent circuit elements. The conduction paths were divided by three different sections – the sidewall conduction (section 1), conduction under the Schottky contact (section 2), and the body conduction (section 3).

the depletion layer and the resistance of the conduction channel. The conduction channel is divided into three paths, the sidewall conduction, the conduction under the Schottky contact, and the body conduction. (section1, 2, and 3 in Figure 2.6) The bottom capacitance  $C_d$  can be calculated from the depletion depth, which is a function of the applied voltage. The depletion depth is given by the following equation.

$$d_d = \sqrt{\frac{2\varepsilon}{qN_D} \left( V_{bi} - V_{bias} - \frac{kT}{q} \right)}$$

(2.6)

Where  $V_{bi}$  is the built in voltage,  $V_{bias}$  is the bias voltage,  $N_D$  is the doping concentration of the n-well. The series resistance is the sum of the resistances in n-well and the resistances in the n+ region. The bottom capacitance can be determined by the following equation.

$$C_d = \varepsilon \frac{WL}{d} \tag{2.7}$$

The resistances of the n+ region and the ohmic contact resistance are much smaller than that of the n-well region and can be neglected. The sidewall capacitance can be calculated by the following equation.

$$C_s = C_d \frac{d_d 2(W+L)}{WL} = 2\varepsilon(W+L)$$

(2.8)

Since the depletion depth  $d_d$  is less than  $1\mu m$ , Cs is small enough to be ignored.  $R_{ns}$  is the resistance between the sidewall and n+ region.  $R_{n-}$  in section 2 is the resistance under the Schottky contact,  $R_{nb}$  in section 3 is the resistance in the body of lightly doped layer. The following equations give the values of these resistors.

$$R_{ns} = \rho \frac{d}{W(d_{n+} - d_d)}$$

(2.9)

$$R_{n-} = \rho \frac{d_{n+} - d_d}{WL} \tag{2.10}$$

$$R_{nb} = \rho \frac{d}{W(d_{nv} - d_{n+})}$$

(2.11)

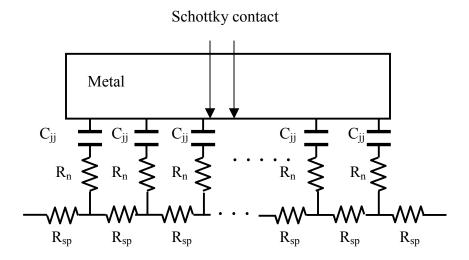

$R_{ss}$  is the spreading resistance from section 2 to section 3. Figure 2.7 shows the distributed RC network for calculating the spreading resistance in section 3. From the R-C network,  $R_n$  can be ignored due to its small value, and the spreading resistance can be calculated the following equations [27, 28, 29].

$$R_{ss} = \frac{R_{sp}}{4\sqrt{\frac{\omega R_{sp}C_{jj}}{2}}} \frac{\sinh(\sqrt{\frac{\omega R_{sp}C_{jj}}{2}}) - \sin(\sqrt{\frac{\omega R_{sp}C_{jj}}{2}})}{\cosh(\sqrt{\frac{\omega R_{sp}C_{jj}}{2}}) - \cos(\sqrt{\frac{\omega R_{sp}C_{jj}}{2}})} \approx \frac{1}{12}\sqrt{\frac{1}{WL}} \frac{\rho}{(d_{mw} - d_{n+})} \quad (2.12)$$

If we assume that W is equal to L, the series resistance is given by the following

**Figure 2.7:** Distributed RC network of the Schottky contact for calculating the spreading resistance.

equation, which shows how equation (2.5) is derived.

$$R_{series} = R_{ns} || (R_{nb} + R_{ss} + R_{n-}) \approx R_0 / A + R_1 / \sqrt{A}$$

(2.13)

Where A is the contact area of a Schottky diode. Finally, the cut-off frequency is given by

$$f_c = \frac{1}{2\pi C_i R_{series}} \propto \sqrt{1/A}$$

(2.14)

As we mentioned in the previous section, the cut-off frequency is proportional to  $1/\sqrt{A}$  .

## **Chapter 3: CMOS Schottky diode detectors**

CMOS process is the most widely used process in integrated circuit fabrication. Schottky diodes for microwave power detector circuits have been made previously through the CMOS processes [23, 26]. However, the standard CMOS process is not specified for the Schottky contacts, and it is difficult to fabricate a Schottky diode by most standard CMOS processes. As a result, the reported Schottky diode fabrication methods highly depended on the process itself, and high frequency operation was not achieved. A modification of a CMOS process for fabricating Schottky diodes through any CMOS process has been developted and reported in the following sections.

### 3.1 Schottky diodes by a CMOS compatible process and FIB process

As a preliminary research project and before using a commercial CMOS process, CMOS compatible Schottky diodes were designed, fabricated, and tested in the Ion Beam Research and Applications Laboratory at the University of Maryland.

#### 3.1.1 Fabrication

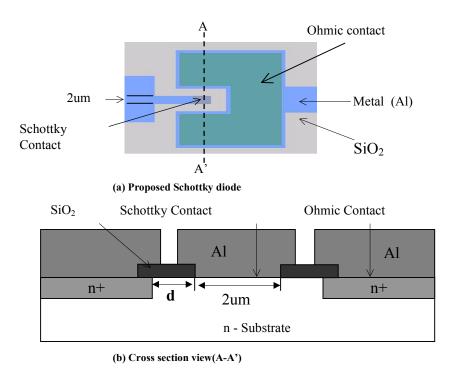

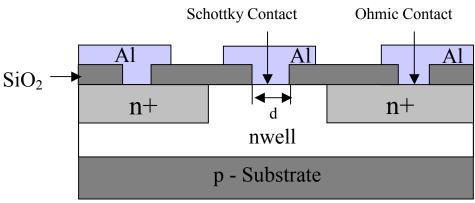

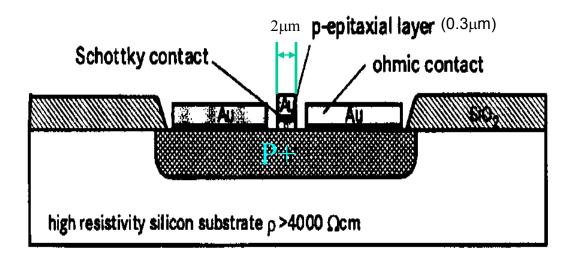

N-type Schottky diodes have been chosen because of the higher electron mobility in silicon. The basic structure (and current path) is metal-to-n-Si-to-n+Si-to-metal (Figure 3.1). To achieve a high cut-off frequency, the rectifying, metal-to-n-Si, contact area needs to be reduced and the conduction path in the n layer needs to be minimized. However, too small of a contact area limits the maximum power the device can detect before the diode burns out. In the case of MBE devices, which have an epitaxially grown n layer on top of an n+ layer, the series resistance was

**Figure 3.1:** Fabricated Schottky diode with 2um x 2um contact area which is surrounded by n+ region (a) and cross section of a Schottky diode(b)

minimized simply by reducing the thickness of the n layer [21, 23]. However this cannot be done in standard CMOS processes and another design is required.

A mask set for fabricating Schottky diodes with reduced contact size and minimum series resistance between the n and the n+ regions (i.e. minimizing the distance d in Figure 3.1) was designed, and several Schottky diodes were fabricated. Since the current CMOS process has a definitive minimum distance between the n contact and n+ layer (eg. such as 1.2μm in AMI 0.5micron process), it is difficult to reduce this distance 'd' to 0.3μm as in the Si-MBE process. The 'd' was 3μm for the fabricated Shottky diodes in our lab. For testing under RF direct injection and irradiation, the mask set included ground-signal-ground (GSG) pad structures and antenna structures respectively, which were connected to Schottky diodes. The

processing steps used in the Schottky diode fabrication were the same steps used in standard CMOS processing: patterning of  $SiO_2$ , n+ activation by rapid thermal annealing, e-beam Al deposition, and Al patterning. To reduce the contact area and minimize the conduction path in a lightly doped n layer, which typically has a  $10^{15}$  cm<sup>-3</sup> doping concentration, a mask set was fabricated, which has several Schottky diode layouts starting with  $2\mu m \times 2\mu m$  contact area.

#### 3.1.2 Measured result

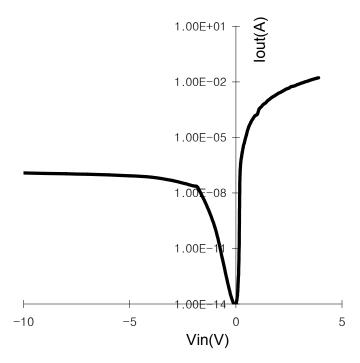

After several fabrication steps, such as phosphorus diffusion to achieve the doping concentration of 10<sup>19</sup> cm<sup>-3</sup> or more and aluminum deposition for Schottky and ohmic contacts, several diodes were fabricated, and the DC I-V characteristics were measured. The DC I-V curve of the fabricated Schottky diode in figure 3.2 shows a

**Figure 3.2:** IV curve of a Schottky diode fabricated by the CMOS process (2umx2um contact area)

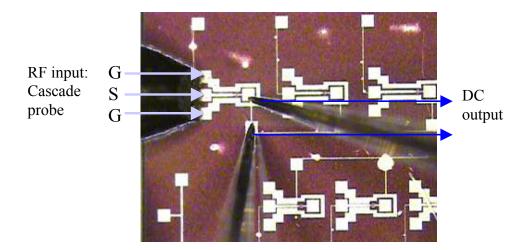

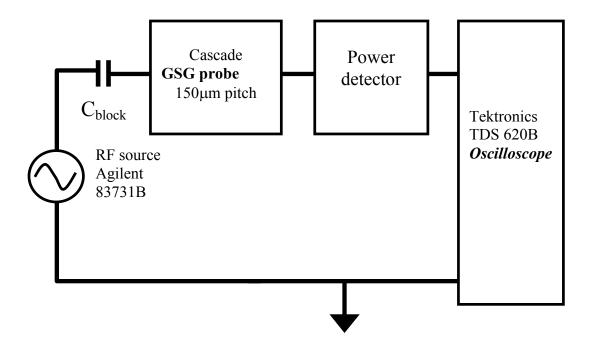

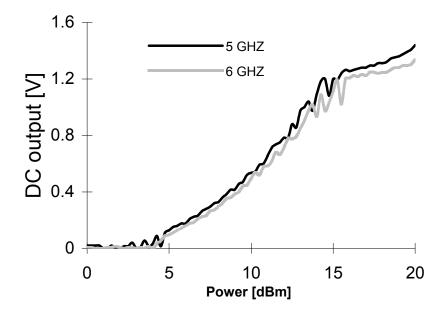

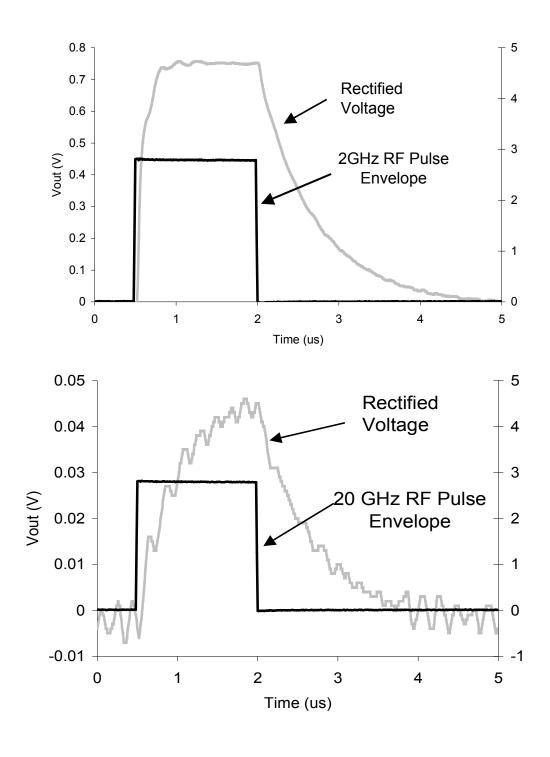

diode I-V curve with an 83Ω series resistance defined as the slope between 4V and 5V, where the series resistance is much bigger than the junction resistance. The RF power detecting characteristics of the Schottky diodes, which had a 2μm x 2μm contact area, were measured by directly injecting RF power through the GSG pads using a Cascade ACP-150 probe shown in Figure 3.3. Figure 3.4 shows the block diagram of the experiment setup. Agilent 83731B was used as an RF burst source. The injected RF signal had a pulse width of 1.5μs and a pulse repetition interval of 10ms and a frequency sweep from 1GHz to 10Ghz at an input power level 15dBm is shown in Figure 3.5. There was no apparent cutoff frequency in this frequency range. The measured result of a power sweep from 0dBm to 20dBm at 5GHz and 6GHz in Figure 3.6 shows a quadratic and a linear relationship between the input power and the detected voltage as expected. Figure 3.7 shows the measured pulse response for a 2GHz RF burst and a 20GHz RF burst input through the cascade probe. The pulse response times were 200ns and 1.2μs for 2GHz and 20GHz RF bursts, respectively.

Figure 3.3: RF direct injection with Ground-Signal-Ground Cascade probe

**Figure 3.4:** Experimental setup for RF burst direct injection with Cascade GSG probe.

**Figure 3.5:** RF direct injection to  $2\mu m \times 2\mu m$  Schottky diode: Frequency (1GHz to 10GHz) sweep at 15dBm

**Figure 3.6** RF direct injection to  $2\mu m\ x\ 2\mu m$  Schottky diode: Power (0dBm to 20 dBm) sweep at 5 and 6GHz

Figure 3.7: Output voltage pulse in response to 2GHz and 20 GHz RF burst

The pulse response time, witch is the rise time of the output pulse in response to a RF burst, can be calculated by the following lumped equivalent circuit of a diode with a load resistor and capacitor (Figure 3.8).

**Figure 3.8:** Equivalent lumped-element circuit of a Schottky diode with a load resistor and a capacitor.  $R_S$  is the series resistance,  $R_I$  is the junction resistance,  $R_I$  is the load resistance,  $R_I$  and  $R_I$  is the load capacitor,  $R_I$  is the load capacitor,  $R_I$  is the load resistance,  $R_I$  is the load resistance.

The output voltage is given by the following equations.

$$V_{o} = \frac{\frac{R_{L}}{1 + sR_{L}C_{L}}}{\frac{R_{j}}{1 + sC_{j}} + Rs + \frac{R_{L}}{1 + sC_{L}}}$$

$$= \frac{R_{L}(1 + sR_{j}C_{j})}{R_{j}(1 + sR_{L}C_{L}) + R_{S}(1 + sR_{j}C_{j})(1 + sR_{L}C_{L}) + R_{L}(1 + sR_{j}C_{j})}$$

$$= \frac{R_{L}(1 + sR_{j}C_{j})}{R_{j} + R_{S} + R_{L} + s(R_{S}R_{j}C_{j} + R_{S}R_{L}C_{L} + R_{j}R_{L}C_{L} + R_{L}R_{j}C_{j}) + s^{2}R_{S}R_{j}R_{L}}$$

(3.1)

Since the series resistance is at least 10 times smaller than the  $1M\Omega$  load resistance,  $R_s$  is assumed to be zero. As a result the output voltage is given by the following equation.

$$V_{o} = \frac{R_{L} (1 + sR_{j}C_{j})}{R_{j} + R_{L} + sR_{j}R_{L} (C_{L} + C_{j})}$$

(3.2)

From equation (3.2), the rise time can be calculated as

$$T_{r} = \frac{2.2 R_{j} R_{L} (C_{L} + C_{j})}{R_{j} + R_{L}}$$

(3.3)

Where 2.2 term comes from the definition of the rise time, which is commonly expressed as the interval between the points of 10% and 90% amplitude ( $T_r = 2.2\tau$ ,  $\tau$  is the time constant). When the frequency of the input RF signal increases, the conversion loss becomes bigger, since the diode consumes more power due to the increased capacitance. In other words, because the diode is operating in a low voltage range, the junction resistance  $R_j$  becomes bigger. As a result, the pulse response time increases. For example, if the input RF has 2GHz frequency, the rise time would be

$$T_r = \frac{2.2 R_j R_L (C_L + C_j)}{R_j + R_L}$$

$$= \frac{2.2 \times 91 \times 10^3 \times 10^6 (10^{-12} + 10^{-13})}{91 \times 10^3 + 10^6} = 204 \text{ ns}$$

where the junction resistance is assumed to be  $91k\Omega$ , and the junction capacitance is assumed to be 100fF. If the frequency of the input RF signal is 20GHz, the junction resistance is assumed to be increased 10 times to  $910k\Omega$ . From equation (3.3), the rise time is calculated to be  $1.16\mu s$ , which agree to the measured result.

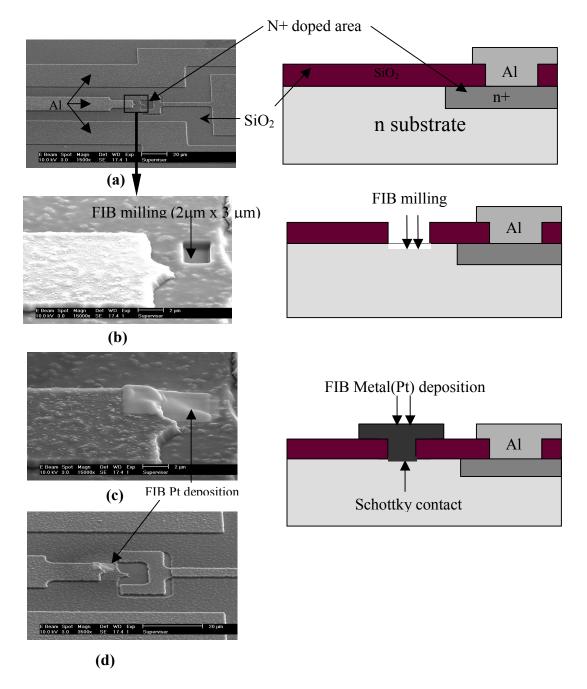

### 3.1.3 Schottky diodes by Focused Ion Beam process

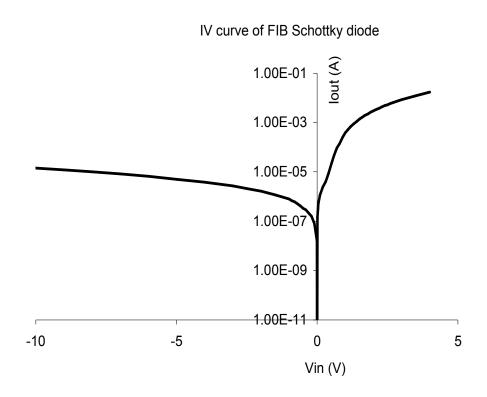

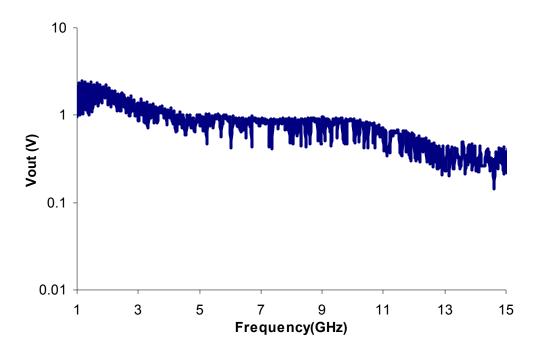

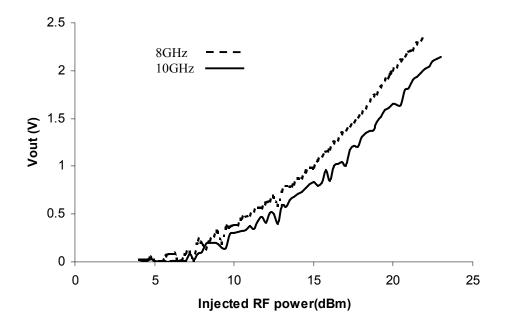

Schottky diodes were fabricated using FIB techniques as a post-CMOS fabrication process on a chip fabricated through a CMOS compatible process. A FEI Dual beam 620 was used for FIB milling and FIB ion induced deposition for the final step in the Schottky diode fabrication process. The FIB process implants Ga ions during milling and deposition, but a Ohmic contact or a Schottky contact can be still made due to the small amount of Ga ions [30]. To achieve a high cut-off frequency, we designed the contact area to be 2μm x 3μm, and the distance between the Schottky contact and the ohmic contact as 3µm. The contacts were fabricated using FIB milling and FIB ion induced deposition techniques. After fabricating the highly doped n+ layer by a CMOS process, a 2μm x 3μm rectangular area was defined by FIB milling. Platinum was deposited by FIB ion induced deposition. SEM images and cross-section views for each step are shown in Figure 3.9. The series resistance was calculated to be  $127\Omega$  (Figure 3.10), which is larger than the device discussed in the previous section. The reverse leakage current was 140nA, the barrier height and the ideality factor were calculated to be 0.392eV and 1.96, respectively. The difference in the series resistance can be attributed to only one side of the diode conducting in FIB Schottky diode compared to the three sided conducting path in the CMOS process fabricated Schottky diode. Form the microwave pulse direct injection measurement with the same experimental setup as in Figure 3.4, the cut off frequency was 10GHz and junction capacitance was calculated to be 48fF (Fig. 3.11). Power sweep results show quadratic responses at 8GHz and 10GHz (Fig. 3.12). From the power sweep measurements, both CMOS compatible diode and FIB-fabricated diode operated at 5dBm of RF input or more. Since we assumed there is no bias circuit for our detectors, our detectors had low sensitivities. Typical diode detectors require bias circuits to achieve a high sensitivity.

**Figure 3.9:** SEM images and cross-section views of fabricating steps by FIB. (a) CMOS processed device structure with only highly doped n area. (b) FIB milling of  $2\mu m \times 3\mu m$  rectangular area (c) Pt deposition (d) Fabricated Schottky diode structure

Figure 3.10: DC IV measured result of a Schottky diode by FIB

**Figure 3.11:** Measured result of the Schottky diode by FIB: Frequency sweep from 1 to 15GHz at 15dBm power injection

**Figure 3.12:** Measured result of the Schottky diode by FIB: Power sweep from 0 to 25dBm at 8 and 10GHz.

## 3.2 CMOS Schottky diodes

To fabricate power detectors through a commercial CMOS process, fabrication of CMOS Schottky diodes through three different CMOS processes (AMIS  $1.5\mu$ ,  $0.5\mu$ ,  $0.35\mu$  CMOS process) was tried. However, all failed to achieve Schottky contacts as expected. This was because the standard CMOS process is not specified for the Schottky contact, and a modification of a CMOS process was required.

#### 3.2.1 Fabrication

In a standard CMOS design, when layouts for contacts to lightly doped substrate, such as Nwell or Pwell, are drawn, the layout editor automatically generates high impurity diffusion layers at the same locations to prevent Schottky contacts. By modifying the layout file to remove these impurity diffusion layers, Schottky contacts were achieved. Various Schottky contact areas from 2μm² to 900μm² were used. The fabrication steps of a CMOS Schottky diode are simple. First, a passivation layer was opened to diffuse n-type or p-type impurity. After diffusing impurities, another passivation layer is opened to expose the silicon surface without diffusing any impurities for a Schottky contact. Contact metals are deposited to make both ohmic contact and Schottky contact. Figure 3.13 shows the ground-signal-ground (GSG) pads for injecting an RF burst by using the Cascade probe and the cross section view of a Schottky diode fabricated through the 0.5μ CMOS process.

#### 3.2.2 Measured result

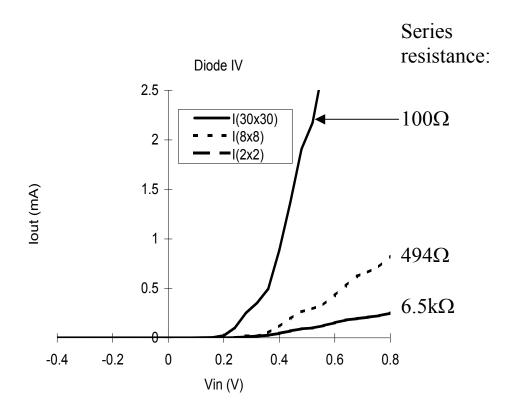

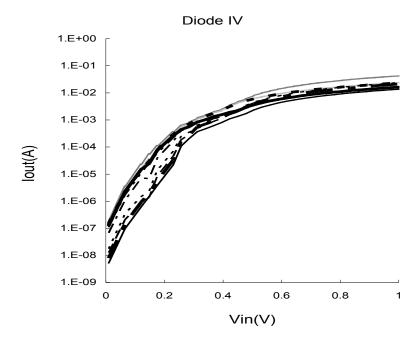

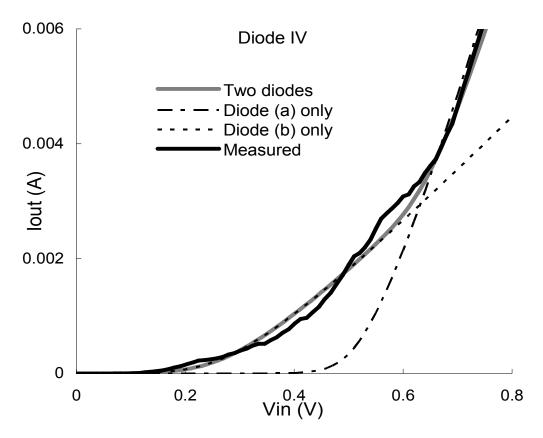

Figure 3.14 shows the DC I-V measured result for CMOS Schottky diode power detectors fabricated and tested. The series resistances of the Schottky diodes with

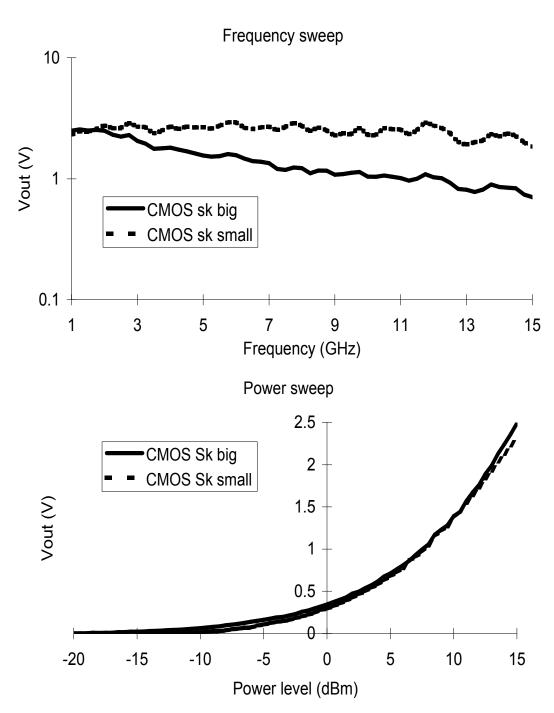

$30x30\mu m^2$ ,  $8x8\mu m^2$ ,  $2x2\mu m^2$  contact areas were  $100\Omega$ ,  $494\Omega$ , and  $6.5k\Omega$ , respectively. Figure 3.15 shows the RF pulse direct injection experiment with the same experimental setup as in Figure 3.4. An RF pulse was directly injected to the GSG pads as shown in Figure 3.13 by using the Cascade GSG probe. From the measured result, the CMOS-fabricated Schotty diode power detector with  $2x2\mu m^2$  Schottky contact area had 820ns pulse response time, 28dBm dynamic range, and began to detect -13dBm input power level. The Schottky diode power detector with  $30x30\mu m^2$  contact area had 35dBm dynamic range, 776ns pulse response time, and began to detect -20dBm input power level. From the frequency sweep measurement, smaller contact area Schottky diodes showed flatter frequency response. It was because the cut-off frequency of a Schottky diode is proportional to  $1/\sqrt{A}$  from the equations (2.3) and (2.5).

**Figure 3.13:** Ground-Signal-Ground pads for injecting RF pulse signal with Cascade probe. The magnified and the cross section view of a CMOS Schottky diode fabricated through  $0.5\mu$  CMOS process

**Figure 3.14:** DC IV measured result. The bigger the contact area was, the lower the series resistance was.

**Figure 3.15:** RF pulse direct injection measured result: Frequency sweep from 1GHz to 15GHz at 15dBm, Power sweep from –20 to 15dBm at 1GHz

# **Chapter 4: Post-CMOS Schottky diode power detectors**

Focused Ion Beam (FIB) techniques have been used for ion implantation, creating localized damage, ion milling, ion induced deposition, lithography, and scanning-ion microscopy [31]. Its applications are IC device modification and failure analysis of fabricated chips by nano scale cutting and rewiring ability [32]. FIB ion induced deposition have been used for making Ohmic contacts on a silicon wafer [30], and we have used FIB milling and ion induced Pt deposition for fabricating Schottky diodes on a silicon wafer [5]. Although, as we will discuss in chapter 4, the CMOS process can be modified to fabricate Schottky diode detectors, the FIB process permits additional detectors to be fabricated in arbitrary locations. Once FIB fabrication steps are developed and if any space is available, any number of diodes can be added on a chip, since FIB is a quite reliable and repeatable process. Typical material removal and addition rate by FIB is in the 0.1 to 1 µm<sup>3</sup> per second range. A typical Schottky diode site required two cuts and one deposition and was completed in 4 to 10 minutes. And, since FIB steps do not need any mask set, the fabrication cost can be also saved. The extra FIB steps do not harm the operation on CMOS chips since they are usually covered by thick oxide and nitride and only limited area will be exposed to ion beam. The post-CMOS-FIB fabrication, and the RF response of Schottky diodes are reported in Chapter 4.

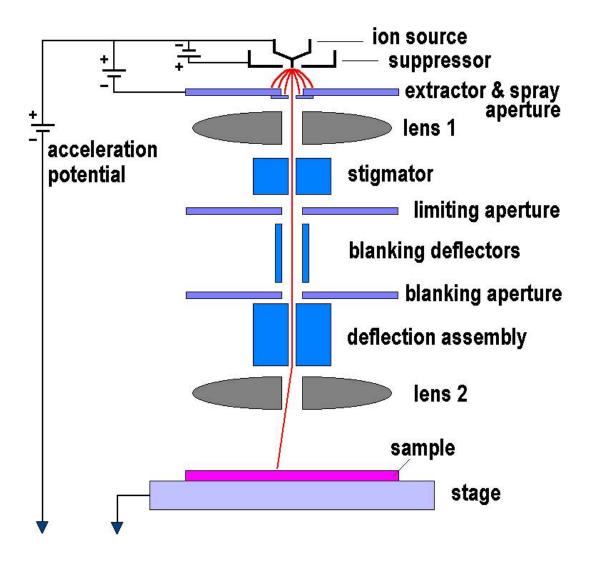

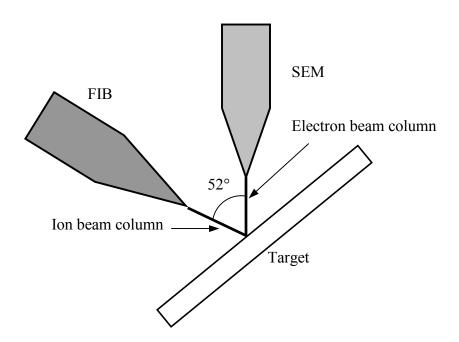

# 4.1 Focused Ion beam system

The basic operation of FIB system is almost identical to SEM, except it uses an ion source rather than electron source. The main advantage of FIB system is a pattern can be milled or deposited at any location of interest without any mask. Figure 4.1 shows a schematic diagram of an Ion column of a FIB system.

**Figure 4.1:** Ion column in a Focused Ion Beam system.

### 4.1.1 Liquid metal ion source

Liquid metal ion source (LMIS) such as Ga is used for the ion source, and the source is in a reservoir, which is in contact with a needle. (Figure 4.2) The liquid metal wets the needle and forms a round tip due to surface tension. When a high potential is applied between the tip and extractor, the liquid metal tip becomes sharper and sharper. The electric field is highest at the tip, and the sharper the tip is, the stronger the electric field is. Eventually, metal ions are emitted from the end of the tip. Ga is one of the best candidates as an LMIS due to its high surface tension and low vapor pressure at the melting point [31].

Figure 4.2: Liquid Metal Ion Source

### 4.1.2 Ion column

The ion column in Figure 4.1 focuses the ions to the target. The ion beam is generated from the LMIS by the extractor, which is typically hard at -10kV with respect to the LMIS. A typical ion emission current is set to  $2.2\mu A$  in the FEI dual

beam 620 machine. The lens 1 condenses the ion beam and the stigmator adjusts the beam stigmatism. The limiting aperture sets the beam currents to between a few pA and tens of nA by changing variable apertures. The aperture size can be set to meet the desired current on the target. To write an arbitrary pattern, the blanker is used for turning the beam off in conjunction with the deflection assembly. The deflecting assembly uses raster scanning, and the lens 2 focuses the beam to a fine spot for the best resolution. The typical acceleration potential is from 10keV to 50keV.

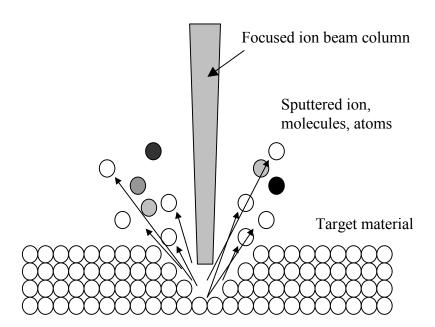

## 4.1.3 FIB milling

The "local Ion milling" is a major advantage of the FIB applications. When Ga+ions with a high current hit the target, the cascade collision process removes the target atoms from the surface, which is a physical sputtering of the target material (Figure

**Figure 4.3:** FIB milling: Ion column focused on the location to be milled. Atoms, electrons, and molecules are sputtered from the target material

4.3). Due to the size of the ion beam spot on the sample, the smallest pattern size can be a few tens of nanometers. By blanking and deflecting the beam, an arbitrary pattern can be fabricated. The yield, which is the number of ions removed per incident ion, depends on many variables and material properties, which are the sample density, the target atomic mass, the beam ion mass, and the incident angle. The reported yields are 2.6 atoms per ion with 30keV Ga+ ion for silicon [31], 2.0 molecules per ion with 68keV Ga+ ion for SiO<sub>2</sub>, and 4.2 atoms per ion with Ga+ ion for Aluminum [32] To enhance the yield, small quantities of reactive gas can be introduced via gas needles that are positioned near the area being milled. In addition, gas assisted ion milling increases the selectivity of certain types of materials such as metals and insulators and minimizes the re-deposition of the milled material.

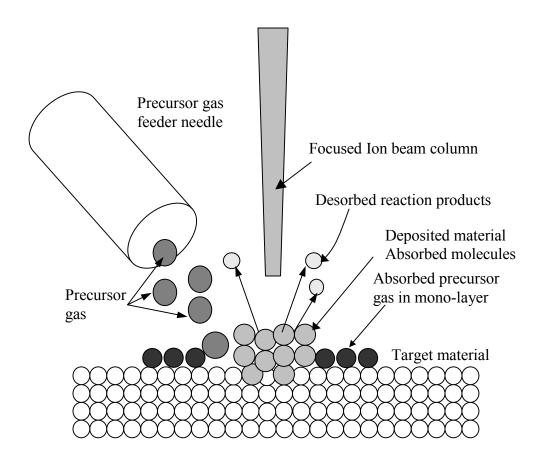

### 4.1.4 FIB ion induced deposition

A FIB system also enables the localized maskless deposition of both metals and insulator materials on to the surface by ion beam induced deposition. The deposition process is similar to the gas-assisted ion milling, except that a different precursor gas and the lower beam current are used. The precursor gases are sprayed on the surface by a fine needle. The ion beam decomposes the adsorbed precursor gases, and the desired metal remains on the surface as a thin film, while desorbed reaction products are removed through the vacuum system. (Figure 4.4) The smallest features that can be deposited are of the order of 100 nm. A typical application of FIB ion induced deposition is modifying or repairing an integrated circuit, since this technique can significantly reduce the time for debugging the circuit designs. Platinum is most widely used for this purpose, since it is inert and does not degrade due to exposure to

**Figure 4.4:** FIB ion induced deposition: Ion column focused on the location for deposition. Desorbed reaction products are removed through the vacuum system

air or to elevated temperatures or high current densities. Platinum also can be deposited directly on silicon [33]. An organometalic precursor gas, (trimethyl)-methlcyclopenta-dienylplatinum (((CH<sub>3</sub>)<sub>3</sub>(CH<sub>3</sub>C<sub>5</sub>H<sub>4</sub>))Pt), which is heated to 39 °C to vaporize it into a gaseous state, is used for platinum deposition. Typical resistivity increases derived are between  $70\Omega cm$  and  $1000\Omega cm$  compared to  $10\mu\Omega cm$  for bulk resistivity of pure platinum. The FIB deposited platinum film is contaminated by carbon, which is unwanted components of the precursor gas [33]. Even though the resistivity is elevated, the resistance can be low enough to give an electrical connection by increasing the thickness and the deposition area.

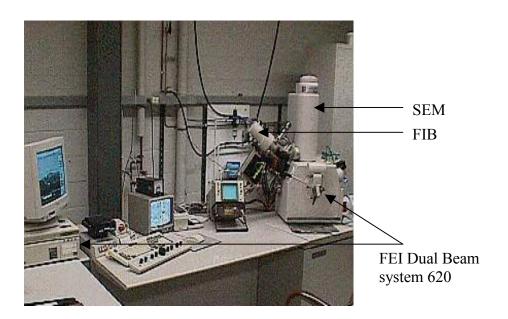

# 4.1.5 FEI Dual Beam system 620

The FIB system used for this research is Dual Beam system 620 made by FEI. Since the FEI Dual Beam system 620 has both a focused Ga+ ion beam column and a

**Figure 4.5:** Dual Beam system, FIB is for imaging, milling, and deposition, SEM is for imaging.

field emission scanning electron column, this system has the ability to mill or deposit materials by ion beam and to image with upto 52° angle by electron beam at the same time. (Figure 4.5) Examining the cross-section view of a device is one of the advantages of the Dual Beam system due to the angle between two columns. Table 4.1 shows the detailed specification of ion and electron columns of the FEI Dual Beam System 620 [34].

Table 4.1

| Ion Beam      | Ion Source      | Gallium LMIS  |

|---------------|-----------------|---------------|

|               | Energy:         | 30keV         |

|               | Beam current    | 1pA - 11.5nA  |

|               | Resolution      | 16nm          |

| Electron Beam | Electron Source | Field Emitter |

|               | Energy:         | 1-30keV       |

|               | Resolution      | 5nm           |

# 4.2 FIB Schottky diodes on a CMOS chip

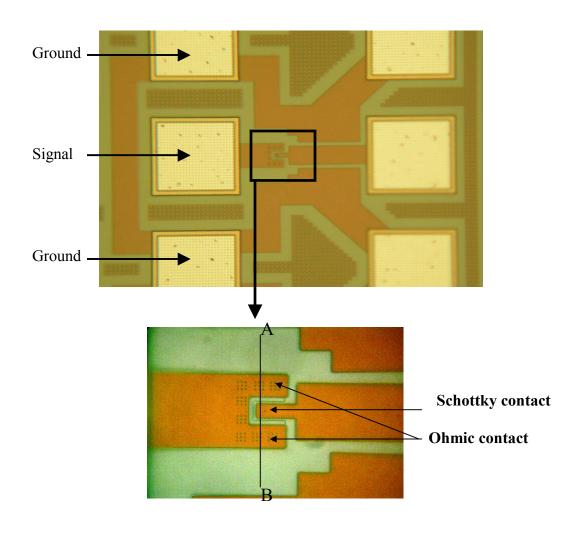

As a post-CMOS process, FIB milling and ion induced deposition can be used for fabricating Schottky diodes on a silicon chip, which was already fabricated by a standard CMOS process. Based on the design and measured result of the FIB Schottky diodes fabricated in our laboratory in Ch.3, CMOS Schottky diodes were designed and fabricated on a CMOS processed chip by 0.5μ CMOS process. Both n-type and p-type FIB Schottky diodes were fabricated and tested under the RF direct injection.

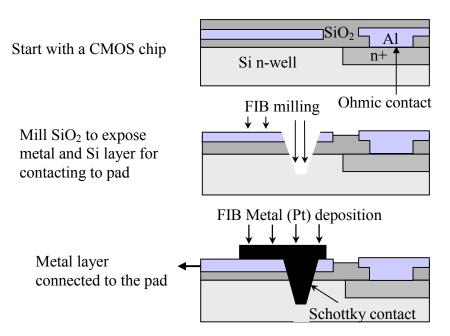

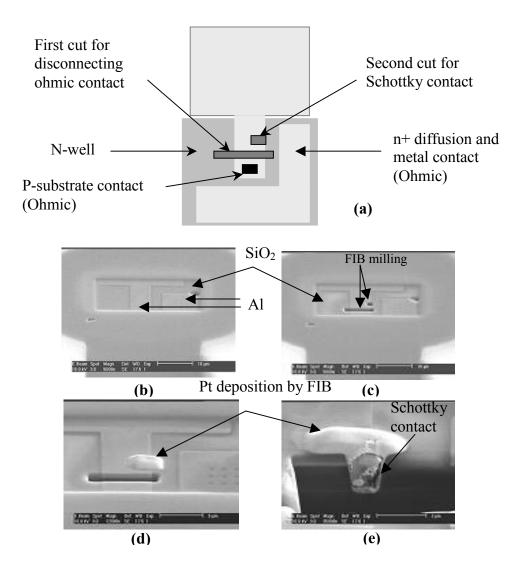

## 4.2.1 Design and fabrication

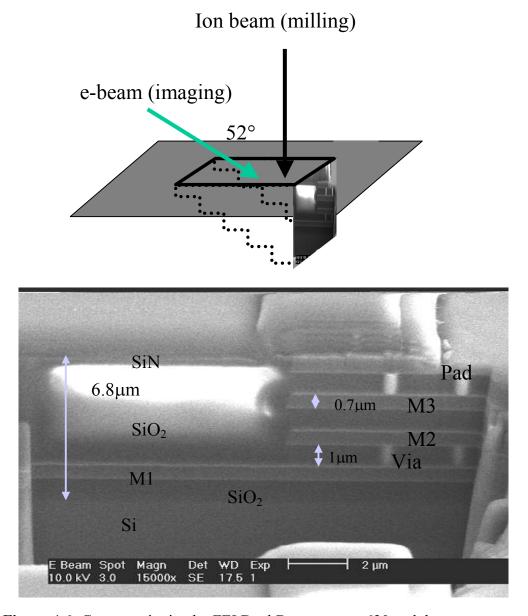

Both n-type and p-type FIB Schottky diodes on a CMOS chip fabricated by the AMIS  $0.5\mu$  CMOS process have been designed. Even though n-type Schottky diodes have higher electron mobility in silicon and better performance than p-type Schottky

**Figure 4.6:** Cross-sectioning by FEI Dual Beam system 620 and the cross-section view of a CMOS chip. Due to the thick SiN and SiO<sub>2</sub> layers, RIE process was required.

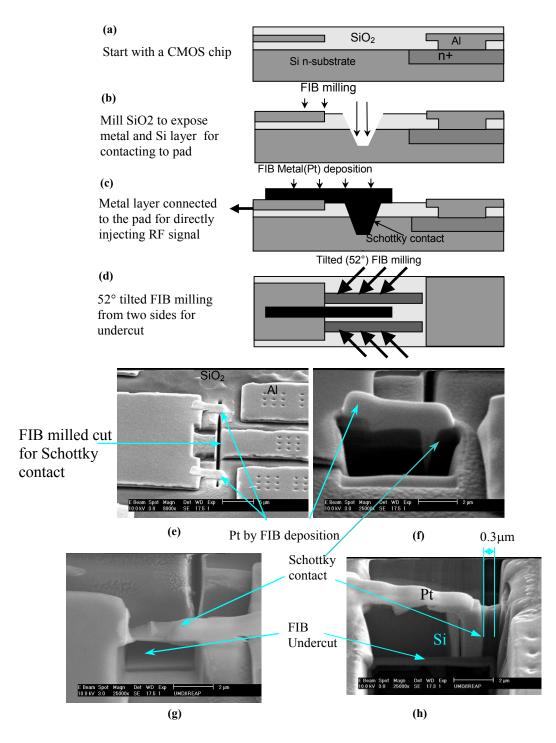

diodes, p-type Schottky diodes are also useful, and it is easier to find a location for fabricating diodes since the most CMOS processes use p-type substrate. FIB milling and ion induced deposition were used as post-CMOS steps to build Schottky diodes in specially designed locations on the CMOS chips fabricated using 0.5μ CMOS process. Before the post-CMOS process, a CMOS chip was cross-sectioned to figure out the processing steps of the 0.5μ CMOS process. (Figure 4.6) From the cross-section view, we found the oxide and nitride layer was too thick (6.8μm) for FIB fabrication. Imaging the CMOS chip with a passivation layer was also difficult, since the current of the incident ions and electrons, which were emitted from the field emitter to the SiN layer, did not have a conduction path to the ground and charged up the surface of the SiN layer. Reactive Ion Etching (RIE) and chemical etching were used to remove the nitride and to make oxide layers thin enough to be processed by FIB. Two steps of FIB millings were used to expose the metal layer by milling the

**Figure 4.7:** FIB Schottky diode fabrication, cross-section view of the fabrication steps.

**Figure 4.8:** SEM pictures of the fabrication process for FIB Schottky diode. (after milling and after deposition)

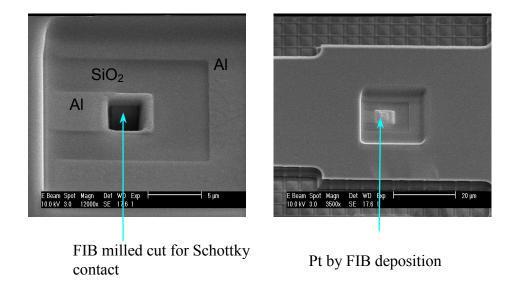

thin oxide layer and to open a rectangular hole, which exposed the silicon substrate for Schottky contacts. As a final step, Platinum was deposited by FIB ion induced deposition. Figure 4.7 and 4.8 show the processing steps and SEM pictures for each step. An FEI Dual beam 620 was used for FIB milling and ion induced deposition. N-type Schottky diodes with contact areas of  $8\mu m^2$  ( $4\mu m \times 2 \mu m$ ) and  $15\mu m^2$  (2 contacts in parallel each  $3\mu m \times 2.5\mu m$ ) on n-well and a p-type Schottky diode with contact area of  $4\mu m^2$  ( $2\mu m \times 2\mu m$ ) on p-substrate were fabricated.

To test cutting ohmic contacts and adding Schottky contacts on a CMOS chip, metal-to-nSi-to-n+Si-to-metal structures without any process modification, which was explained in chapter 3.2, was designed. Neither p-substrate nor n-well-to-metal contacts fabricated by these processes were Schottky diodes but rather ohmic contacts. The standard CMOS process does not allow any Schottky contact because either p-type or n-type are automatically implanted on any contact site. These

contacts are supposed to be ohmic to fabricate linear resisters on a chip. A contact site for the post fabrication of the Schottky diode was selected to cut the ohmic contact and to make a Schottky contact by FIB. FIB milling was used to cut the ohmic

**Figure 4.9:** Layout and SEM image of an n-type Schottky diode fabrication steps by FIB. (a) FIB milling locations for cutting ohmic contact and milling for Schottky diode fabrication. (b) Etch Silicon Nitride and Silicon oxide to expose metal layer by RIE and FIB milling (c) Disconnect existing ohmic contact (long cut) and define 2μm x 2μm rectangular area by FIB milling (d) Deposit platinum by FIB ion induced deposition (e) Cross-section of a FIB-made contact (cross-sectioned after measurement and burned out) and the "U" shaped Pt filling the via made a Schottky contact to silicon substrate.

contact and to open a rectangular hole, which exposed the silicon substrate for a Schottky contact, and platinum was deposited. (Figure 4.9)

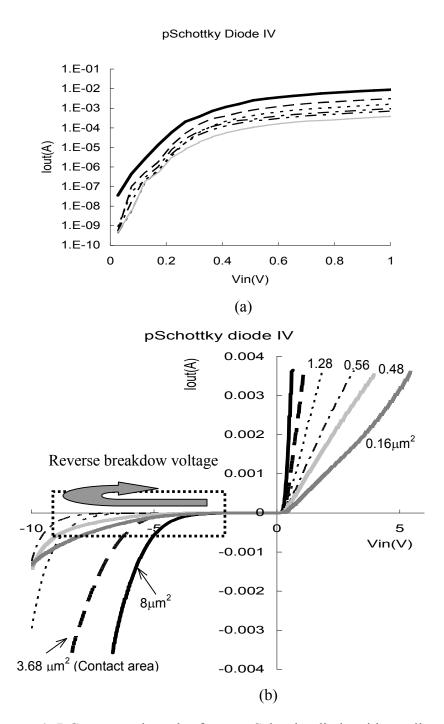

#### 4.2.2 Measured result

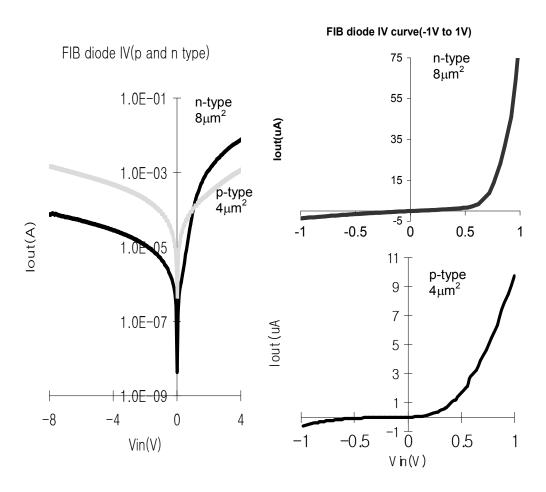

The RF power detecting characteristics were measured by the direct injection of RF power through the Cascade ACP-150 probe. Figure 4.10 shows the block diagram of the experimental setup. As a signal source we used the Agilent 83731B RF signal generator, which can generate a signal in the frequency range of 1GHz to 20GHz and maximum power level of 15dBm. Figure 4.11 shows I-V curves of fabricated Schottky diodes. From these curves the series resistance of lightly doped n layer was calculated to be  $227\Omega$  defined as the slope between 4 and 5V, and the measured junction capacitance was 627fF at zero bias condition. For p-type diode, the series resistance was calculated to be  $903\Omega$ , which is bigger due to smaller contact area,

**Figure 4.10:** RF direct injection measurement setup: RF source generates a signal from 1GHz to 20GHz at a maximum power level of 15dBm. Cascade probe has 150μm pitch with Ground-Signal-Ground configuration. As a load, a 8pF and  $10M\Omega$  probe was used(C= 8pF, R =  $10M\Omega$ ). C<sub>block</sub> is a DC blocking capacitor.

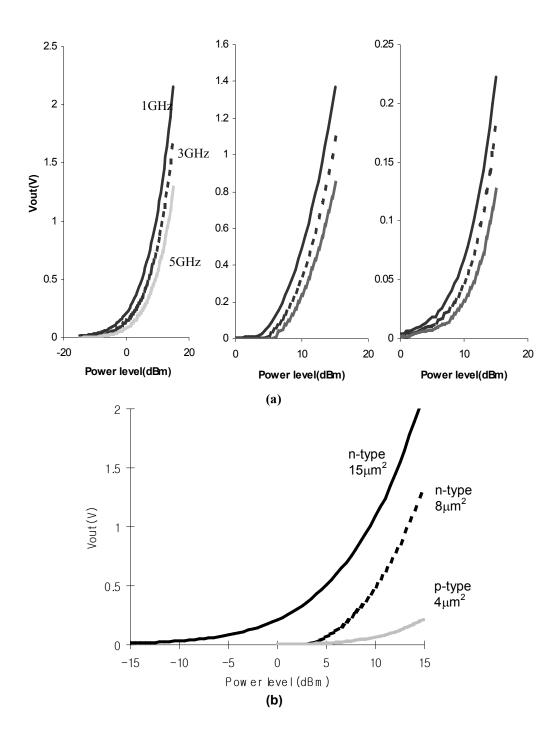

lower carrier mobility, and different barrier heights between n-type and p-type Schottky contact to platinum. Figure 4.12 and 4.13 show the measured result of the RF power direct injection to a Schottky diode through the ground-signal-ground (GSG) pads. Figure 4.12 shows the measured result of the power sweep for three diodes at the power level of -15dBm to 15dBm for the 15 $\mu$ m<sup>2</sup> n-type Schottky diode and 0dBm to 15dBm for the 6 $\mu$ m<sup>2</sup> n-type Schottky diode and the 4 $\mu$ m<sup>2</sup> p-type Schottky diode at 1GHz, 3GHz,

**Figure 4.11:** Measured result of FIB Schottky diodes: IV curves of the n-type Schottky diode with  $8\mu m^2$  contact area and p-type diode with  $4\mu m^2$  contact area. Due to tunneling at high reverse bias at p-type diode, reverse leakage current increased.

**Figure 4.12:** (a) Power sweep from -15dBm to 15dBm at 1GHz, 3GHz, and 5GHz for three diodes: n-type  $15\mu\text{m}^2$  diode,  $6\mu\text{m}^2$  diode, and p-type  $4\mu\text{m}^2$  Schottky diode, respectively. (b) Power sweep for three diodes at 1GHz

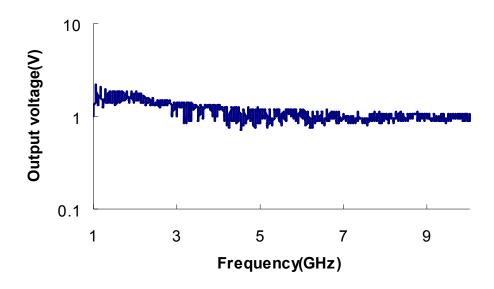

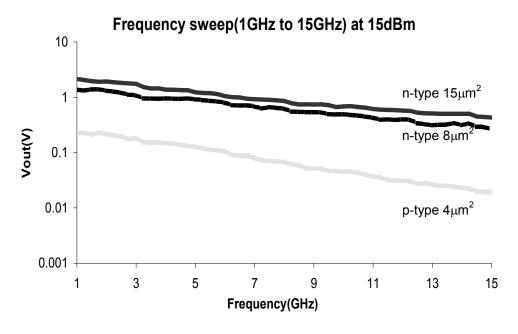

and 5GHz. This result shows quadratic curves and its dynamic range was 30dBm at zero bias condition. 30μs and 10μs pulse width and 10ms period RF pulses were injected for power sweep experiment. 30μs RF pulses were injected only to the 15μm² n-type Schottky diode due to its longer response time (i.e. the rise time of the rectified output pulse) of 6μs. Figure 4.13 shows the measured results of three frequency sweeps from 1GHz to 15GHz at an input power level of 15dBm. When the contact area decreased, the rectified output voltage decreased due to the increase of the junction resistance. Even though the smaller contact area Schottky diodes showed the lower rectified voltage, since this diode has much shorter pulse response time than that of bigger contact area Schottky diode, smaller diode has a better performance for detecting the RF pulse signal. The pulse response time at 1GHz 15dBm pulse input was 192 ns for the 4μm² p-type diode, 2.56 μs for the 8μm² n-type diode, and 6μs for

**Figure 4.13:** Frequency sweep from 1GHz to 15GHz at the power level of 15dBm

the 15  $\mu m^2$  n-type diode. This result shows the smaller area p-type Schottky diode power detector has better performance in the RF pulse detection, though its rectified voltage was about 10 times smaller than that of the  $15\mu m^2$  n-type diode. The smaller rectified voltage is, the shorter the pulse response time Schottky diode has. This fact indicates that even p-type Schottky diode has lower rectification due to higher junction and series resistance, if contact area is small enough, it can be used as a RF pulse power detector.

## 4.2.3 Bridge shaped FIB Schottky diode

A typical process for fabricating a Schottky diode for high frequency applications is using molecular beam epitaxy (MBE) for growing a very thin, 0.3µm, lightly doped

**Figure 4.14:** Coplanar Si-MBE Schottky diode developed for rectifying antennas by Strohm et al.

\* Ref: K.M. Strohm, J. Buecher, & E. Kasper, Daimler Benz Research, Ulm, IEEE Trasn. MTT Vol.46, 669, (May, 1998)

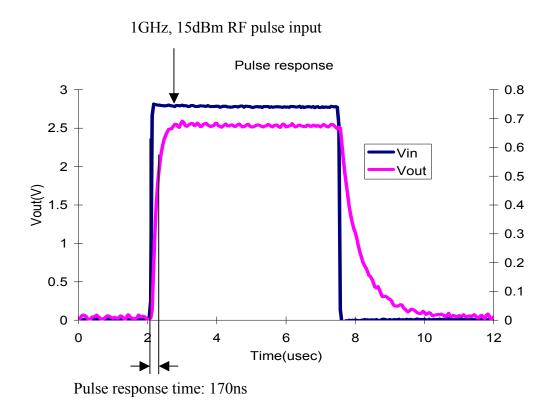

layer on top of the highly doped layer. Strohm et al. have fabricated a Silicon Schottky diode by using Si-MBE process to make a Schottky contact, and the reported operating frequency was 93GHz (Figure 4.14) [35]. To make a similar structure as the reported Si-MBE Schottky diode, a bridge shaped FIB Schottky diode was designed and fabricated. Tilted FIB milling was used to make undercut triangular bridge shaped Schottky contacts on the fabricated n-type Schottky diode with 8µm² contact area described in the previous chapter. Figure 4.15 shows the processing steps and the SEM pictures of the fabricated bridge shapted Schottky diode. Contact area was measured to be 1 µm<sup>2</sup>. The measured result showed that the bridge shaped Schotty diode had 170ns pulse response time, (Figure 4.16) 25dBm dynamic range, and began to detect -10dBm input power level. Because of the increase of the junction resistance, the frequency response of the bridge shaped Schottky diode became worse than that of the Schottky diode without undercut. This is because the contact area is not large enough to ignore the reverse tunneling current. Even though the frequency response became worse than before, the pulse response time was significantly reduced from 2.6µs to 170ns due to the smaller contact capacitance.

**Figure 4.15:** FIB Schottky diode fabrication, (a), (b), and (c): cross-section view (d): top view, and SEM images of a FIB processed bridge shaped diode, (e) Milling silicon and Platinum deposition, (f) Cross section of the fabricated device: refer (c), (g) Undercut by tilted FIB to minimize capacitance, (h) Another bridge shaped diode with 0.3um of lightly doped layer

Figure 4.16: RF pulse response of Bridge shaped FIB Schottky diode, the pulse response time was 170ns

# **Chapter 5: MOSFET power detector circuits**

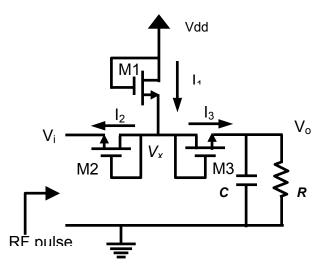

A simple diode connected MOSFET can be used as a rectifier. However, its turn on voltage, usually 1V, is too high for small microwave signal detection and a bias circuit or a dc source is required to improve the sensitivity. Rantni et al. suggested a MOSFET power detector by adding dc sources to bias the gate of the MOSFET [36]. However, since their approach required a huge MOSFET, the pulse response time, which is the most important parameter for detecting RF pulses, was estimated to be 10's of μs. Their approach was also very sensitive to the variation of the bias voltage at the gate of the MOSFET. To minimize these problems, MOSFET power detector circuits were developed and fabricated through a 0.5μ CMOS process.

## 5.1 Diode connected MOSFET with a bias circuit

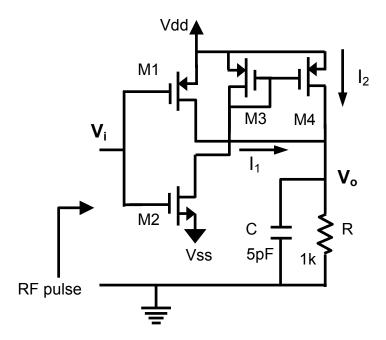

To increase the sensitivity of a simple diode connected (gate connected to drain) MOSFET, a bias circuit was added. Figure 5.1 shows the proposed circuit. M3 is diode connected nMOSFET and M1 supplies the bias current  $I_1$ .

**Figure 5.1:** MOSFET power detector circuit: depends on the polarity of RF input, bias current  $I_1$  flows to one of  $M_2$  or  $M_3$ .

### 5.1.1 Operation

When the input voltage  $V_i$  is less than 0, and  $I_1$  is equal to  $I_2$ ,  $V_{xo}$  ( $V_x$  when  $V_i$  is equal to 0V) can be calculated and  $I_3$  is small enough to be neglected by the following equations.

$$I_{1} = K \frac{w_{1}}{l_{1}} (V_{dd} - V_{xo} - V_{T})^{2} \qquad I_{2} = K \frac{w_{2}}{l_{2}} (V_{x} - V_{T})^{2}$$

$$V_{xo} = \left(\frac{\sqrt{l_{2}w_{1}}}{\sqrt{l_{2}w_{1}} + \sqrt{l_{1}w_{2}}}\right) V_{dd} + \left(\frac{\sqrt{l_{2}w_{1}} - \sqrt{l_{1}w_{2}}}{\sqrt{l_{2}w_{1}} + \sqrt{l_{1}w_{2}}}\right) V_{T}$$

(5.1)

$$V_o = I_{o3} \left( e^{\frac{q}{kT} (V_{xo} - V_o)} - 1 \right) R \tag{5.2}$$

Where,  $K = \mu C_{ox}q/2kT$ , w is the width and l is the length of the channel. When Vi becomes bigger than 0V and  $I_3$  is not negligible and the output voltage  $V_0$  begins to rise by the following equations.

$$I_2 = K \frac{w_2}{l_2} (V_x - V_i - V_T)^2$$

(5.3)

$$I_3 = K \frac{w_3}{l_3} (V_x - V_o - V_T)^2$$

(5.4)

$$I_{1} = K \frac{w_{1}}{l_{1}} (V_{dd} - V_{x} - V_{T})^{2} = K \frac{w_{2}}{l_{2}} (V_{x} - V_{i} - V_{T})^{2} + K \frac{w_{3}}{l_{3}} (V_{x} - V_{o} - V_{T})^{2}$$

(5.5)

$$V_o = I_3 R \tag{5.6}$$

By solving (3)-(6), Vi and Vo are square functions of  $V_x$ .

$$V_o = aV_x^2 + bV_x + c (5.7)$$

$$V_{i} = a' V_{x}^{2} + b' V_{x} + c'$$

(5.8)

Where a,b,c,a',b', and c' are constants. As a result, the output voltage Vo has a linear dependence on the input voltage Vi by the following equation.

$$V_o = AV_i + B \tag{5.9}$$

Where A is a positive constant and B is a constant and near to 0 when Vi is equal to 0. When Vi is much bigger than 0V, almost all bias current flows to M3,  $I_1$  is equal to  $I_3$ , and the output voltage becomes constant,  $I_3R$ .

### 5.1.2 Simulation and DC measured result

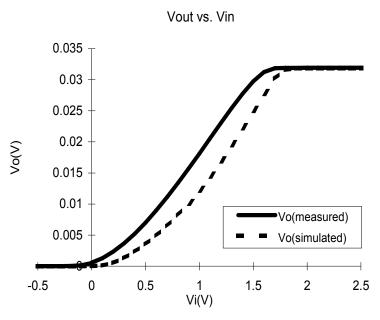

Figure 5.2 shows the DC simulation result and the DC measured result of the proposed MOSFET power detector. Both results are seen to agree. For the low input region, Vi is less than 0.7V, the circuit operates in the subthreshold mode, and smooth curve between Vi and Vo was observed.

**Figure 5.2:** Simulated and measured dc curve of a MOSFET power detector. Measured result showed turn on voltage shift to -0.1V.

**Figure 5.3:** Experimental setup for RF burst direct injection with Cascade GSG probe.

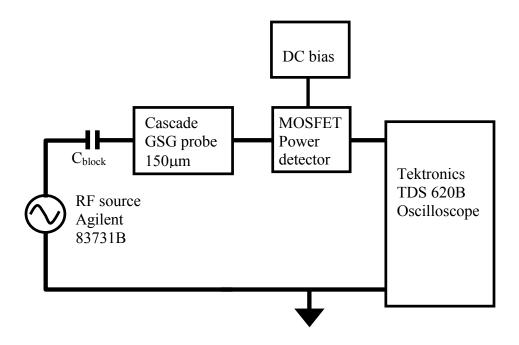

### 5.1.3 Microwave pulse direct injection

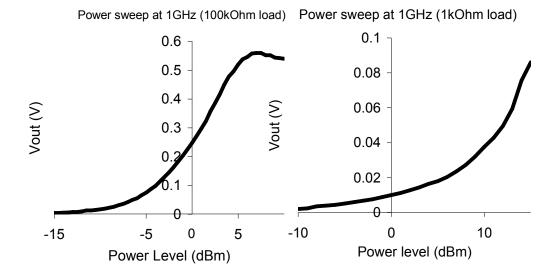

The RF power detecting characteristics were measured by the direct injection of RF power through the Cascade ACP-150 probe. Figure 5.3 shows the block diagram of the experimental setup, which is similar to the Schottky diode measurement except an additional voltage source. We used the Agilent 83731B RF signal generator, which has a frequency range of 1GHz to 20GHz and maximum power level of 15dBm. Figure 5.4 and 5.5 show the measured result of the RF power direct injection to the fabricated MOSFET power detector through the ground-signal-ground (GSG) pads. Figure 5.4 shows the measured result of the power sweep from -15dBm to 15dBm for the MOSFET detector circuit with 100k $\Omega$  load and -10dBm to 15dBm for 1k $\Omega$  load at 1GHz. Both results showed curves of approximately quadratic shapes. RF pulse of

$10\mu s$  width and 10ms period RF pulses were injected in power sweep experiment. For the MOSFET detector with a  $100k\Omega$  load, the dynamic range was 21dBm, and the

**Figure 5.4:** Power sweep at 1GHz, RF direct injection to two of the same MOSFET power detectors with a  $100k\Omega$  load and a  $1k\Omega$  load.

**Figure 5.5:** Frequency sweep at 5dBm for the MOSFET detector with a  $100k\Omega$  load and at 15dBm for the MOSFET detector with a  $1k\Omega$  load.

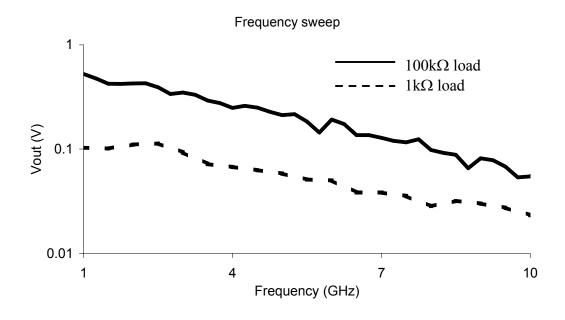

pulse response time was 200ns. Because the supply voltage was limited, the output voltage became saturated, when the input power level was over 6dBm. For the MOSFET detector with a  $1k\Omega$  load, the dynamic range was 25dBm, and the pulse response time was 52ns. Even though the output voltage was small due to the low power efficiency, the pulse response time was shorter and the dynamic range increased. Figure 5.5 shows the measured results of the frequency sweep from 1GHz to 10GHz at the input power level of 5dBm for the  $100k\Omega$  load MOSFET and 15dBm for the  $1\Omega$  load MOSFET. The MOSFET detector with a higher load resistance showed faster roll off.

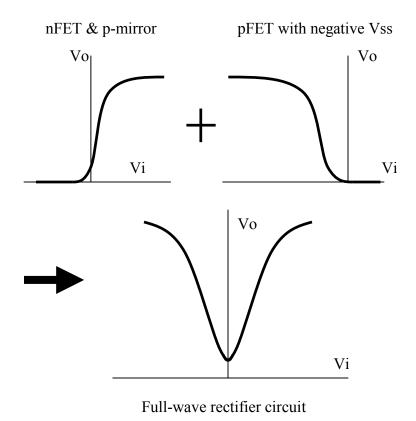

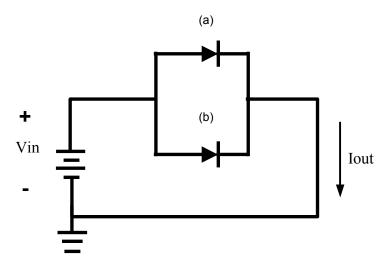

## 5.2 Full-wave rectifier circuit

For more sensitive microwave detection and wide dynamic range, a full-wave rectifier circuit was developed and fabricated. Figure 5.6 shows the proposed

Figure 5.6: Full-wave rectifier circuit