ABSTRACT

Title of dissertation: DEEP SUBMICRON CMOS VLSI CIRCUIT

RELIABILITY MODELING, SIMULATION

AND DESIGN

Xiaojun Li, Doctor of Philosophy, 2005

Dissertation directed by: Professor Joseph B. Bernstein

Reliability Engineering

CMOS VLSI circuit reliability modeling and simulation have attracted intense research interest in the last two decades, and as a result almost all IC Design For Reliability (DFR) tools now try to incrementally simulate device wearout mechanisms in iterative ways. These DFR tools are capable of accurately characterizing the device wearout process and predicting its impact on circuit performance. Nevertheless, excessive simulation time and tedious parameter testing process often limit popularity of these tools in product design and fabrication.

This work develops a new SPICE reliability simulation method that shifts the focus of reliability analysis from device wearout to circuit functionality. A set of accelerated lifetime models and failure equivalent circuit models are proposed for the most common MOSFET intrinsic wearout mechanisms, including Hot Carrier Injection (HCI), Time Dependent Dielectric Breakdown (TDDB), and Negative Bias Temperature Instability (NBTI). The accelerated lifetime models help to identify the most degraded transistors in a circuit in terms of the device's terminal voltage

and current waveforms. Then corresponding failure equivalent circuit models are incorporated into the circuit to substitute these identified transistors. Finally, SPICE simulation is performed again to check circuit functionality and analyze the impact of device wearout on circuit operation. Device wearout effects are lumped into a very limited number of failure equivalent circuit model parameters, and circuit performance degradation and functionality are determined by the magnitude of these parameters.

In this new method, it is unnecessary to perform a large number of small-step SPICE simulation iterations. Therefore, simulation time is obviously shortened in comparison to other tools. In addition, a reduced set of failure equivalent circuit model parameters, rather than a large number of device SPICE model parameters, need to be accurately characterized at each interim wearout process. Thus device testing and parameter extraction work are also significantly simplified. These advantages will allow circuit designers to perform quick and efficient circuit reliability analyses and to develop practical guidelines for reliable electronic designs.

# DEEP SUBMICRON CMOS VLSI CIRCUIT RELIABILITY MODELING, SIMULATION AND DESIGN

by

## Xiaojun Li

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2005

#### Advisory Committee:

Professor Joseph B. Bernstein, Chair/Advisor

Professor Aris Christou

Professor Ali Mosleh

Professor Martin Peckerar

Professor Carol Smidts

# **DEDICATION**

I would like to dedicate this work to my pretty daughter Kemeng, who entered the world while I was working on this dissertation. Her first cry delivers to me the great pleasure of creation and being fatherhood. Her tender yet beauteous life sprouts like a bud in early spring, bearing vital force and hope, which always inspires me to work diligently and strive toward excellence.

## **ACKNOWLEDGMENTS**

I owe my gratitude to all the professors and colleagues who have made contributions to this dissertation. Their company and persisting guidance make my study and research experience of the last three years in the University of Maryland a period of rewarding time in my life journey.

First of all, I would like to thank my advisor, Professor Joseph B. Bernstein, for providing financial support for my study since I came to Maryland in summer 2002. He also granted me privileges to work on various challenging and interesting projects in the field of microelectronics reliability. With his sharp insight, he laid the foundation and formulated some of the original ideas for this dissertation work which perfectly matches my expertise and interest. He is one of the most gracious and knowledgeable professors I ever met in my life. It is a great pleasure to work with him and learn from him both in academic and in everyday life during the last several years.

I would also like to thank those professors serving on my dissertation committee. I became acquainted with them either from taking their courses or participating in their projects. Their profound knowledge and enlightening discussions instilled many essential ingredients into this dissertation work. Their persisting support and invaluable guidance are proved to be indispensable for me to improve my research capability. Furthermore, I sincerely appreciate Dr. Ernest Wu at IBM Microelectronics Division and Dr. Sufi Zafar at IBM T. J. Watson Research Center. They are very generous to share pre-published papers with me. Without their help, I could not finish the modeling work of some wearout mechanisms in a short time.

Finally, I owe my deepest gratitude to my wife. She gave up her successful career and comfortable life in Shanghai and came to Maryland to support my study. We have been staying together and living through the hard time when I was pursuing the doctoral degree. She is the most dependable partner whenever I head for a new higher life goal.

## TABLE OF CONTENTS

| Li | List of Figures                                         | viii |

|----|---------------------------------------------------------|------|

| 1  | Introduction                                            | 1    |

|    | 1.1 CMOS Scaling and New Reliability Challenges         | 1    |

|    | 1.2 Purpose of the Dissertation                         |      |

|    | 1.3 Dissertation Organization and Chapter Overviews     |      |

| 2  | 2 Simulation Models and Algorithms                      | 10   |

|    | 2.1 Overview                                            | 10   |

|    | 2.2 Review of Reliability Simulation Tools              | 12   |

|    | 2.2.1 Reliability Simulation in Virtuoso UltraSim       | 12   |

|    | 2.2.2 Reliability Simulation in Eldo                    |      |

|    | 2.3 Limitations and Improvements                        | 17   |

|    | 2.4 Assumptions and Justification                       | 22   |

|    | 2.5 Summary of Lifetime and Circuit Models              | 24   |

|    | 2.5.1 Hot Carrier Injection                             | 25   |

|    | 2.5.2 Time Dependent Dielectric Breakdown               | 25   |

|    | 2.5.3 Negative Bias Temperature Instability             | 27   |

|    | 2.6 Reliability Prediction and Simulation Algorithms    |      |

|    | 2.6.1 Circuit Lifetime and Failure Rate Prediction      | 29   |

|    | 2.6.2 Circuit Reliability Simulation Algorithm          | 33   |

| 0  |                                                         | 9.0  |

| 3  | J                                                       | 36   |

|    | 3.1 Introduction                                        |      |

|    | 3.2 Accelerated Lifetime Model                          |      |

|    | 1                                                       |      |

|    | 3.4 Implementation in MaCRO                             |      |

|    | 3.5 Conclusion                                          | 53   |

| 4  | Time Dependent Dielectric Breakdown Effect and Models   | 54   |

|    | 4.1 Introduction                                        | 54   |

|    | 4.2 Accelerated Lifetime Model                          | 55   |

|    | 4.3 Failure Equivalent Circuit Model                    |      |

|    | 4.4 Implementation in MaCRO                             |      |

|    | 4.5 Conclusion                                          |      |

| 5  | Negative Bias Temperature Instability Effect and Models | 80   |

| -  | 5.1 Introduction                                        |      |

|    | 5.2 Accelerated Lifetime Model                          |      |

|    | 5.3 Failure Equivalent Circuit Model                    |      |

|    | 5.4 Implementation in MaCRO                             |      |

|    | 5.5 Conclusion                                          | 96   |

| 6 | Elec       | tromigration Lifetime Models and Parameter Extraction   | 98  |

|---|------------|---------------------------------------------------------|-----|

|   | 6.1        | Introduction                                            | 98  |

|   | 6.2        | Electromigration Failure Physics                        | 99  |

|   |            | 6.2.1 Nucleation-Dominated Failure Physics              | 100 |

|   |            | 6.2.2 Growth-Dominated Failure Physics                  | 100 |

|   | 6.3        | Electromigration Lifetime Models                        | 101 |

|   | 6.4        | Model Parameter Extraction                              | 102 |

|   |            | 6.4.1 Current Density                                   | 103 |

|   |            | 6.4.2 Current Acceleration Factor and Activation Energy | 105 |

|   |            | 6.4.3 Temperature Effects                               | 108 |

|   |            | 6.4.4 Example of Typical Values                         | 110 |

|   | 6.5        | Electromigration of Copper Wires                        |     |

| 7 | Dors       | ating Voltage and Temperature for Reliability           | 112 |

| ' | 7.1        | Introduction                                            |     |

|   | 7.2        | Circuit Design and Simulation                           |     |

|   | 7.3        | Simulation Results and Analysis                         |     |

|   | 1.0        | 7.3.1 Voltage Derating Analysis                         |     |

|   |            | 7.3.2 Temperature Derating Analysis                     |     |

|   |            | 7.3.3 Voltage Transfer Analysis                         |     |

|   | 7.4        | Derating Model and Derating Factor                      |     |

|   | 7.4        | Derating Factor and Simulation                          |     |

|   | 7.6        | Conclusion                                              |     |

|   |            |                                                         |     |

| 8 |            | AM Reliability Simulation and Analysis                  | 132 |

|   | 8.1        | Introduction                                            |     |

|   | 8.2        | SRAM Circuit Design and Simulation                      |     |

|   | 8.3        | Preview of SRAM Failure Behaviors                       |     |

|   | 8.4        | Device Lifetime Calculation                             |     |

|   | 8.5        | SPICE Reliability Simulation with Circuit Models        |     |

|   |            | 8.5.1 HCI                                               |     |

|   |            | 8.5.2 HCI+TDDB                                          |     |

|   | 0.0        | 8.5.3 HCI+TDDB+NBTI                                     |     |

|   | 8.6<br>8.7 | Reliability Design Techniques                           |     |

|   | 0.1        | Conclusion                                              | 198 |

| 9 | Sum        | amary                                                   | 159 |

|   | 9.1        | Results                                                 |     |

|   | 9.2        | Main Contributions                                      |     |

|   | 9.3        | Future Work                                             | 163 |

| Α | MAT        | ΓLAB Programs for Circuit Model Calculation             | 165 |

|   | A.1        | Hot Carrier Injection                                   |     |

|   | A.2        |                                                         |     |

|   |            | Negative Bias Temperature Instability                   |     |

| В  | Flowchart of Lifetime and Reliability Trend Prediction | 169 |

|----|--------------------------------------------------------|-----|

| С  | Terms and Abbreviations                                | 170 |

| Bi | bliography                                             | 172 |

## LIST OF FIGURES

| 2.1 | Hot carrier reliability simulation flowchart in Virtuoso UltraSim. Device wearout modeling is the focus of the reliability analysis [17]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | HCI reliability simulation in Eldo [19]. A large number of SPICE simulation iterations have to be carried out to obtain accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16  |

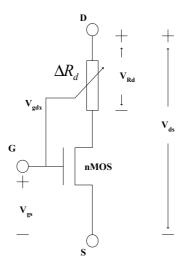

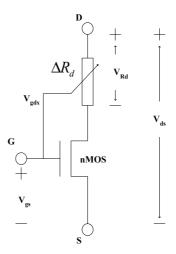

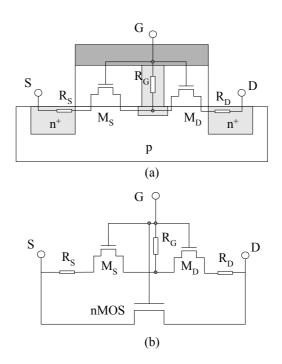

| 2.3 | HCI circuit model in MaCRO. In the model: $V_{gdx} = V_{gs} - V_t - V_{ds}$ and $V_{Rd} = I_{ds} \Delta R_d$ . $V_t$ is threshold voltage and $I_{ds}$ is the current from node $D$ to $S$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26  |

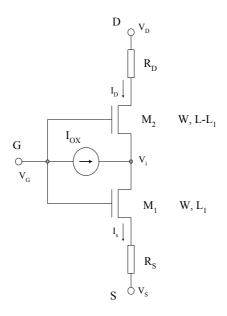

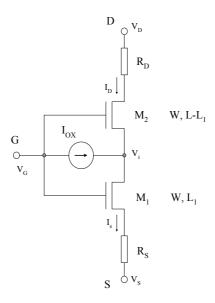

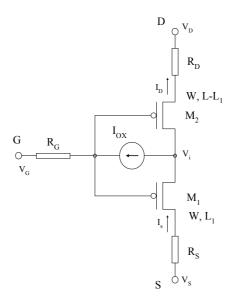

| 2.4 | TDDB circuit model in MaCRO. $I_{OX} = I_S - I_D$ is a voltage-dependent current source representing breakdown path current injection effect. $R_D$ and $R_S$ characterize the resistance in the source and the drain extensions, respectively. $L_1$ represents breakdown location in terms of the source edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27  |

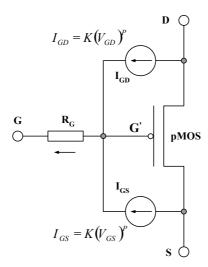

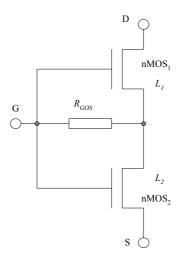

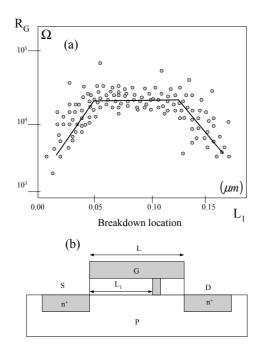

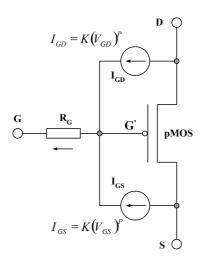

| 2.5 | NBTI circuit model in MaCRO. The inclusion of $I_{GD}$ and $I_{GS}$ inherently accounts for oxide breakdown effects and also supplies leakage currents for $R_G$ whose voltage drop is equivalent to pMOSFET threshold voltage degradation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28  |

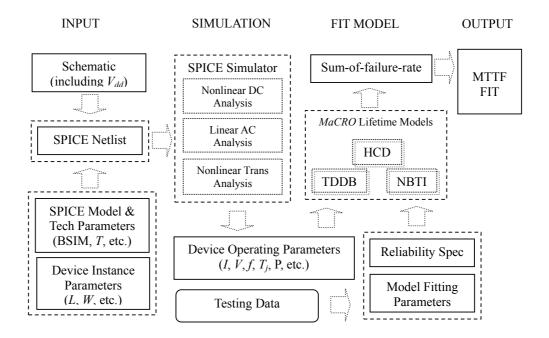

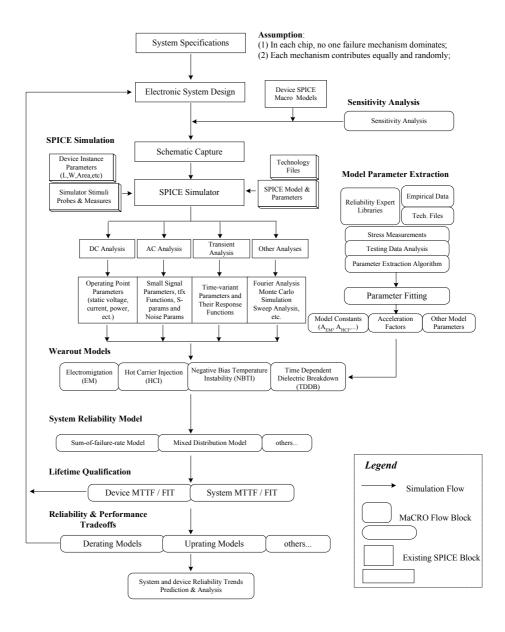

| 2.6 | Flowchart of device and circuit lifetime and failure rate prediction process with MaCRO lifetime models. SPICE simulation predicts device terminal voltage and current stress profiles, and model fitting parameters are determined from device testing work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32  |

| 2.7 | MaCRO circuit reliability simulation algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35  |

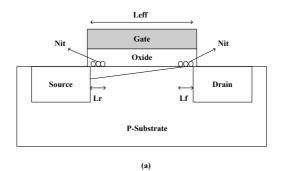

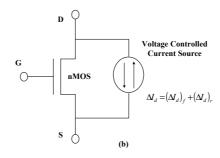

| 3.1 | BERT nMOSFET HCI circuit model. (a) Bidirectional interface trap generation near both drain and source. $L_f$ and $L_r$ represent forward and reverse hot carrier damaged regions. (b) HCI drain current $\Delta I_d$ circuit model [52]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45  |

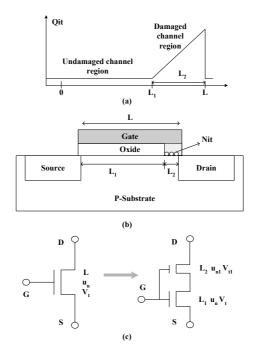

| 3.2 | UIUC nMOSFET HCI two-transistor series model. (a) Triangular oxide charge distribution profile used in model derivation. (b) Cross-sectional view of nMOSFET with hot carrier damage, $L_2$ is damaged channel region. (c) Two-transistor series circuit model. The parasitic transistor has different channel mobility and threshold voltage with the channel length $L_2$ set to $0.1\mu m$ [46, 51, 55]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46  |

| 3.3 | HCI circuit model in MaCRO. In the model: $V_{gdx} = V_{gs} - V_t - V_{ds}$ and $V_{Rd} = I_{ds} \Delta R_d$ . $V_t$ is threshold voltage and $I_{ds}$ is the current from node $D$ to $S$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48  |

|     | $_{1000}$ $_{D}$ $_{00}$ $_{D}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00}$ $_{00$ | -10 |

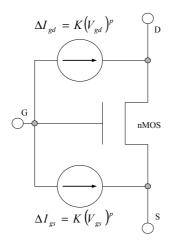

| 4.1 | Power-law leakage current model. The exponent $p$ varies from 5 to 2 as the degradation level increases. $K$ reflects the "size" of the breakdown spot                                                                                                                                                                                                                                                                                                                             | 64 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | TDDB GOS model for gate-to-channel breakdown of nMOSFET with $n^+$ -poly gate. The channel lengths of nMOS1 and nMOS2 follow the relation: $L_1 + L_2 = L$ where $L$ is the undamaged nMOSFET channel length. The parameter $R_{GOS}$ is related to the size and location of the breakdown path. A value of $R_{GOS}$ as low as $3K\Omega$ was used in the simulation in [82]                                                                                                      | 65 |

| 4.3 | TDDB RF equivalent circuit model. Model parameters for simulation in [84] are set as: $R_G = 85.4\Omega$ , $R_D = R_S = 12.14\Omega$ , $R_{GD} = 6.88K\Omega$ , $R_{GS} = 23K\Omega$ , $C_{GDO} = C_{GSO} = 15.3fF$ , $C_{jDB} = C_{jSB} = 7fF$ , $R_{DSB} = 80K\Omega$ , $R_{DB} = R_{SB} = 49.37\Omega$                                                                                                                                                                          | 67 |

| 4.4 | TDDB circuit model for nMOSFET with hard gate oxide breakdown and operated in positive gate voltage. (a) Cross-sectional view of breakdown structure. (b) Equivalent circuit model. Model parameters for simulation in [86] are set as: $R_G = 1K\Omega$ , $L_{M_S} + L_{M_S} = 0.09\mu m$ , $W_{M_S} = W_{M_S} = 0.25\mu m$ , $R_D$ and $R_S$ vary from $2.5K\Omega$ (at source and drain) to $12.5K\Omega$ (at the middle of the channel)                                        | 70 |

| 4.5 | MaCRO TDDB circuit model for nMOSFET with hard gate oxide breakdown. $I_{OX} = I_S - I_D$ is a voltage dependent current source representing breakdown path current injection effect. $R_D$ and $R_S$ characterize the resistance in the source and the drain extensions, respectively. $L_1$ represents breakdown location away from the source edge                                                                                                                              | 74 |

| 4.6 | Relationship between effective gate resistance $R_G$ and oxide breakdown location $L_1$ . The bias condition is $V_G = 1.5V$ , $V_D = V_S = 0$ . (a) Reproduce from [87] with illustrative data. (b) Cross-sectional view of breakdown location                                                                                                                                                                                                                                    | 77 |

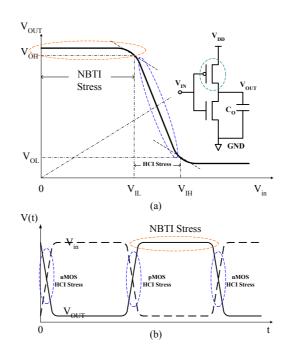

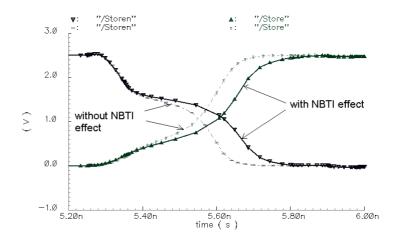

| 5.1 | The different stress time windows of HCI and NBTI for an inverter in (a) VTC plot and (b) input-output waveform plot. HCI stresses devices only during the dynamic switching periods when both gate voltage and drain voltage are high enough and there is current flowing through the device. NBTI stresses pMOS devices mainly during the period when they are in one of the two static operation states when gate voltage is negative with respect to drain and source voltages | 82 |

| 5.2 | MaCRO NBTI circuit model. NBTI-induced pMOSFET threshold voltage increase is modeled as absolute gate-to-source voltage decrease. Gate tunneling current flowing through the gate resistance $R_G$ leads to the increase of voltage at point $G'$ . This corresponds to the decrease of pMOSFET absolute gate-to-source voltage and therefore mimics the threshold voltage degradation effect. Gate tunneling current is modeled with two voltage controlled current sources which follow the form of a power law relation as: $I = KV^P$ 92 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

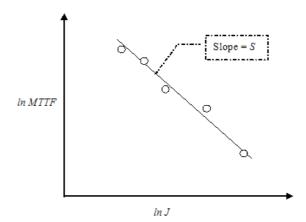

| 6.1 | Plot of $\ln MTTF$ vs. $\ln J$ to illustrate the fitting method in extracting $n$ and judge the linearity of the dependence [138]                                                                                                                                                                                                                                                                                                                                                                                                            |

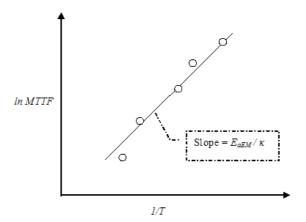

| 6.2 | Plot of $\ln MTTF$ vs. $1/T$ to illustrate the fitting method in extracting $E_{aEM}$ and judge the linearity of the dependence [138]                                                                                                                                                                                                                                                                                                                                                                                                        |

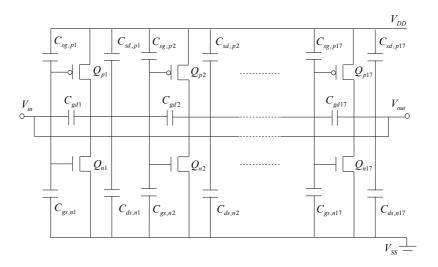

| 7.1 | The schematic diagram of the ring oscillator which consists of 17-stage CMOS inverters and interconnecting capacitors                                                                                                                                                                                                                                                                                                                                                                                                                        |

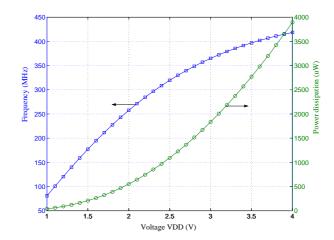

| 7.2 | The derating relationship of frequency and power dissipation vs. $V_{DD}$ . When voltage increases 4 times, the frequency increases about 5 times, whereas the power dissipation increases near to 100 times 117                                                                                                                                                                                                                                                                                                                             |

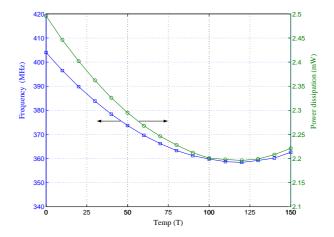

| 7.3 | The derating curves of frequency and power dissipation vs. temperature. Operation frequency and power dissipation follow nonlinear trends when temperature is derated and simulation shows a minimum frequency value at temperature around $120^{\circ}C$                                                                                                                                                                                                                                                                                    |

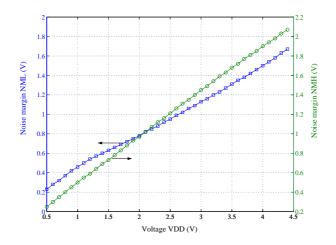

| 7.4 | The simulation results for $NM_L$ and $NM_H$ vs. $V_{DD}$ . Over the voltage derating range of 4.0V to 1.2V, $NM_L$ and $NM_H$ approximately decrease linearly with $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                 |

| 7.5 | DC VTC curves at different power supply voltage (from $0.5V$ to $4.5V$ ). When $V_{DD}$ scales down, the transition region of VTC reduces proportionally. When $V_{DD}$ is lower than $0.8V$ , the transition region disappears, and the VTC exhibits a hysteresis behavior 124                                                                                                                                                                                                                                                              |

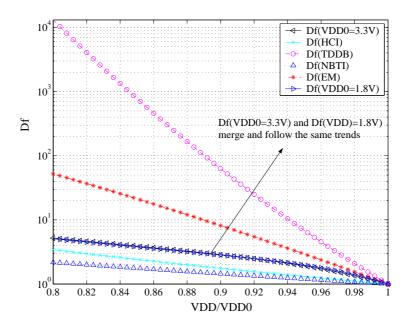

| 7.6 | Trends of $D_f$ vs. $V_{DD}/V_{DD}^0$ with typical model parameters from the $0.18\mu m$ technology. $V_{DD}$ is derated within the range $[100\% \sim 80\%]$ of its rated value $V_{DD}^0 = 3.3V$ . The trend of $D_f$ when $V_{DD}^0 = 1.8V$ is also plotted for comparison                                                                                                                                                                                                                                                                |

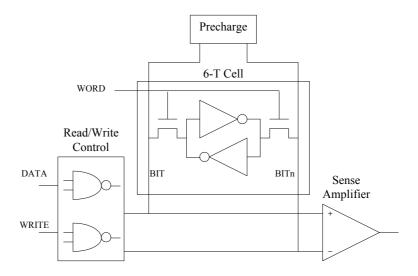

| 8.1 | The one bit SRAM structural block diagram. The circuit consists of one bit 6-T cell, read/write control logic and output sense amplifier $133$                                                                                                                                                                                                                                                                                                                                                                                               |

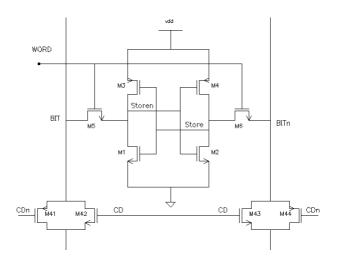

| 8.2  | Schematic of the one bit 6-T SRAM cell. Store/Storen represent cell state. WORD line enables the two pass transistors M5 and M6 during memory read and write cycles                                                                                                                                  | 35         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

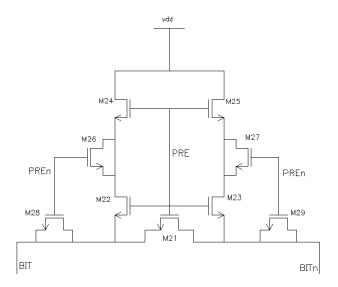

| 8.3  | Schematic of the precharge circuit. BIT/BITn lines are pre-charged to the same voltage level before each read and write operation. $M26 \sim M29$ are included for reducing transient charge injection effects 13                                                                                    | 36         |

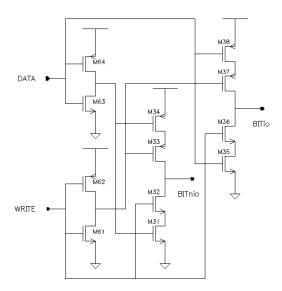

| 8.4  | Schematic of the write control circuit. WRITE signal controls the connections of DATA line and BITio/BITnio lines. BITio/BITnio lines are connected to BIT/BITn by the two transmission gates ( $M41 \sim M44$ )                                                                                     | 37         |

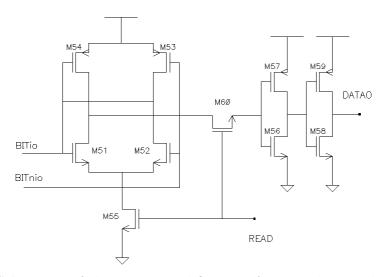

| 8.5  | Schematic of the sense amplifier. READ signal controls the operation of the latch amplifier and the connection between BIT/BITn and the output. The latch amplifier magnifies BIT/BITn line swings to full digital levels                                                                            | 88         |

| 8.6  | SRAM SPICE simulation stimuli. PRE exerts before each read/write operation. CD signal enables the transmission gates $M41 \sim M42$ and WORD signal enables the pass transistors $M5 \sim M6$ during each read/write operation. The "0" or "1" is available on DATA line during each write operation | 39         |

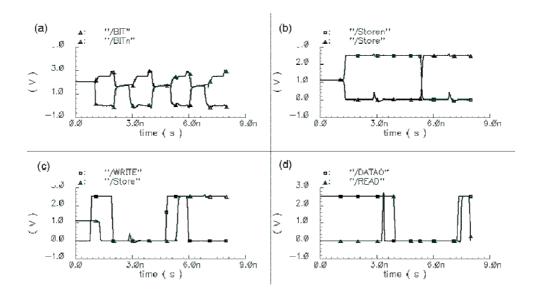

| 8.7  | SRAM SPICE simulation results. (a) shows waveforms of BIT/BITn signals, (b) shows SRAM cell state signals Store/Storen, (c) is write operation result, and (d) is read operation result                                                                                                              | 10         |

| 8.8  | Device lifetime calculation results for the three failure mechanisms: (a) HCI, (b) TDDB, and (c) NBTI. The horizontal axis denotes device's index, and vertical axis denotes lifetime value normalized to $\tau_1 \sim \tau_3$ , respectively                                                        | 13         |

| 8.9  | Comparison of transition delay of $M58$ before and after inverter sizing. Proper sizing significantly reduces dynamic switching delay, thereby suppressing HCI effect. $W_n = 0.6 \mu m$ before sizing, and $W_n = 1.8 \mu m$ after sizing                                                           | 14         |

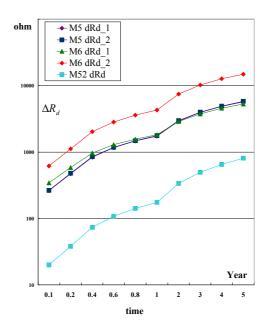

| 8.10 | $\Delta R_d$ values of $M5, M6, M52$ at different stress times. The unit of horizontal axis is time in years, the vertical axis is in logarithmic scale and in unit Ohm                                                                                                                              | <u>1</u> 7 |

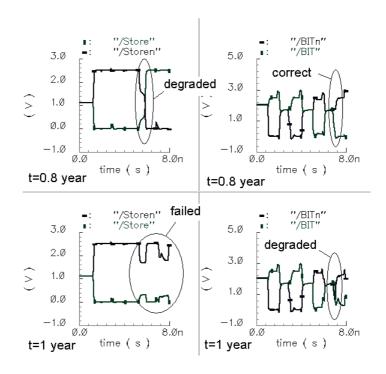

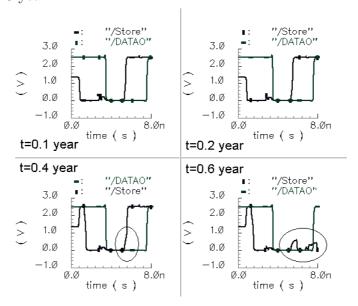

| 8.11 | The simulated waveforms of the SRAM cell Store signal and output DATAO signal after different stress times. At $t=1$ year, Store signal does not jump to high as expected during the "write 1" cycle indicating failure of SRAM cell                                                                 | 18         |

| 8.12 | The waveforms of SRAM Store/Storen signals and BIT/BITn signals before and after circuit failure. Store/Storen signals do not flip due to the degradation in BIT/BITn signals when a reverse value is being written to the SRAM cell                                                                                                        | . 149 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

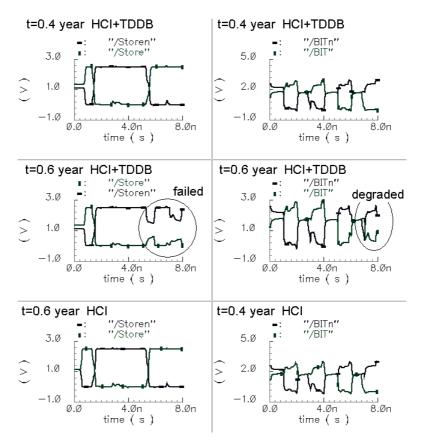

| 8.13 | The simulated waveforms of the SRAM cell Store signal and output DATAO signal at different HCI+TDDB stress times. At $t=0.6$ year, Store signal does not jump to high during the "write 1" cycle indicating failure of SRAM cell                                                                                                            | . 150 |

| 8.14 | The waveforms of the SRAM Store/Store signals and BIT/BITn signals before and after circuit failure                                                                                                                                                                                                                                         | . 151 |

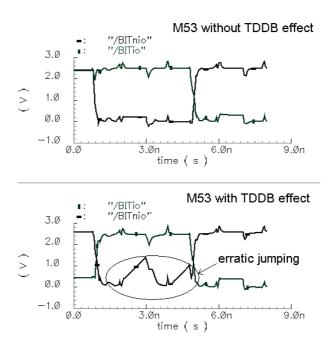

| 8.15 | The TDDB effect of $M53$ on sense amplifier output stability. The breakdown in $M53$ provides additional current path between BITnio and $V_{DD}$ and tends to pull up BITnio when it is at low level in "read 0" and "write 1" cycles                                                                                                      | . 152 |

| 8.16 | The TDDB+NBTI circuit model for a pMOSFET. $R_G$ and $I_{ox}$ account for threshold voltage degradation due to NBTI. $I_{ox}$ and the two split pMOSFETs represent TDDB damage. $R_D$ and $R_S$ characterize the resistances in drain and source extensions. They are excluded in this SRAM case study in order to simplify simulation work | . 153 |

| 8.17 | The NBTI effects on SRAM cell transition speed. The switching speed of SRAM cell Store/Storen signals degrades when NBTI damage on $M3$ is considered                                                                                                                                                                                       | . 154 |

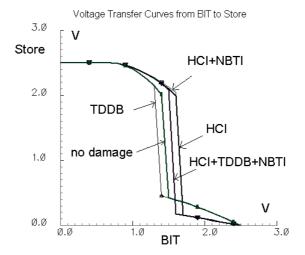

| 8.18 | Voltage transfer curves of BITn-to-Storen for different combinations of failure mechanisms. From left to right, the curves represent effects of TDDB, no damage, HCI+TDDB+NBTI, HCI, and HCI+NBTI, respectively. NBTI has negligible effect on SRAM cell stability                                                                          | . 155 |

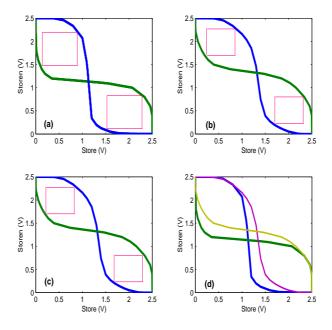

| 8.19 | Butterfly plots for various failure mechanisms. (a) denotes the no-<br>damage operation, (b) shows SNM degradation due to TDDB, (c)<br>shows the combined effect of TDDB+NBTI, and (d) is the combina-<br>tion of the previous three plots. The difference in (b) and (c) is very<br>small indicating that NBTI is not a dominant effect    | . 156 |

| R 1  | MaCRO Flow of lifetime failure rate and reliability trend prediction                                                                                                                                                                                                                                                                        | 160   |

### Chapter 1

#### Introduction

#### 1.1 CMOS Scaling and New Reliability Challenges

The scaling of CMOS technology into deep submicron regimes has brought about new reliability challenges, which are forcing dramatic changes in approaches to integrated circuit reliability assurance. Product cost and performance requirements will be substantially affected, or even superseded, by reliability constraints [1]. The traditional reliability assurance methods, which relied on failure detection and analysis at the end of a lengthy product development process, are rapidly losing efficiency due to the reliability trends predicted by 2003 International Technology Roadmap for Semiconductor (ITRS'03) [2].

For most applications, current overall chip reliability levels need to be maintained over the next fifteen years, despite the possible risks induced by multiple major technology breakthroughs. This constraint requires continuous improvement in reliability per transistor and per unit length of metal interconnect due to the continuous shrinkage of device dimensions. Scaling pushes device performance to the limits of technology and gradually eats up circuit reliability margins. Therefore, the accurate tradeoffs between performance and reliability must be addressed before

committing design to production.

The projected failure in time (FIT) of technology nodes from 90nm to 65nm in ITRS'03 is on the order of 10 to 100. However, experimentally determining FIT values this low by traditional reliability qualification methods requires a huge number of device-hours of Accelerated Life Testing (ALT). Approximately  $9 \times 10^7$  device-hours of testing are required to prove a failure rate of 10 FITs at 60% confidence level if no failures occur during the testing [3]. The increased cost and excessive time consumed by testing work demand that accurate lifetime models and efficient reliability simulation tools must be available in product design stages.

The validity of the voltage and temperature acceleration methods that have been utilized in reliability screening and qualification processes, such as burn-in and ALT, becomes questionable due to the diminished margins for proper acceleration of these stress factors. The traditional FIT and acceleration factor determination methods that rely on the multiplication of individual acceleration factors need to be revisited, and the correlation of these factors must be explored and modeled for the purpose of accurate failure rate prediction.

Finally, as circuits become increasingly complex, two irreversible trends can be noted: First, a given device within a chip is stressed for a decreasing fraction of the reliability testing time; Second, a longer delay is required to correct the reliability problem by process and design iterations [4].

All of the above trends demand that device lifetime and circuit reliability be accurately characterized and predicted during the product design process. This can only be fulfilled by effective IC reliability simulation tools.

CMOS circuit reliability simulation has attracted intense research interest in the last two decades. Significant progress in modeling device wearout mechanisms has led to the emergence of quite a few successful reliability simulation tools [5, 6, 7, 8, 9]. The simulation algorithms adopted by these tools physically characterize the device wearout process under real circuit stress environments and incrementally simulate circuit performance degradation in iterative ways. This physics-of-failure based iterative simulation algorithm often produces accurate simulation results with the disadvantage of excessive computational and experimental work. Some attempts have been made to improve simulation efficiency by employing the fast timing simulation method [10, 11] or by performing gate-level circuit simulation [12]. However, the device wearout-based simulation and testing philosophy is preserved. As a result, even though reliability simulation is generally regarded as an essential step in deep submicron CMOS circuit designs, the tedious device aging test and model parameter extraction work often discourage chip designers from exercising IC reliability simulation in their everyday work.

In review of reliability simulation practice in industrial and academic communities, it is obvious that some fundamental concepts and techniques have been universally adopted that not only form the common foundation of legacy reliability simulation tools but also nurture new ideas in some previously unresearched areas. These new ideas will give rise to developments and breakthroughs of new IC reliability simulation methods, which are both efficient and effective.

### 1.2 Purpose of the Dissertation

This dissertation focuses on developing a new Maryland Circuit Reliability – Oriented (MaCRO) SPICE simulation method, which is built upon the constant failure rate concept and equivalent circuit modeling techniques. MaCRO consists of a series of accelerated lifetime models and failure equivalent circuit models for common silicon intrinsic wearout mechanisms, including Hot Carrier Injection (HCI), Time Dependent Dielectric Breakdown (TDDB), and Negative Bias Temperature Instability (NBTI), respectively. In this new method, the overall simulation flow is straightforward, and SPICE engine is only initiated for very limited times to simulate the impact of device wearout on circuit functionality. Therefore, simulation time is obviously shortened. Also, a reduced set of failure equivalent circuit model parameters at each interim wearout process, rather than a large number of device SPICE model parameters, need to be accurately characterized. Thus, device testing and parameter extraction processes are also significantly simplified. These advantages allow circuit designers to perform quick and efficient circuit reliability analyses and to develop practical guidelines for reliable electronic designs.

#### 1.3 Dissertation Organization and Chapter Overviews

This dissertation is organized into nine chapters, moving from MaCRO simulation algorithms to model developments to application examples. The overall structure follows a top-down-then-bottom-up presentation style: The first two chapters are a top-level overview of MaCRO simulation method and some other state-of-

the-art DFR tools; The middle four chapters present detailed developments of all MaCRO models and equations, which are basic ingredients of the MaCRO simulation algorithms; The following two chapters discuss two different kinds of top-level applications of MaCRO models by circuit simulation examples; Finally, the last chapter concludes the dissertation with a summary of contributions of this dissertation and suggestions for future work.

A brief overview of each chapter is given below to quickly walk readers through the overall dissertation. Note that for brevity, starting from the following paragraph, the term "accelerated lifetime model" is abbreviated to "lifetime model", and the term "failure equivalent circuit model" is abbreviated to "circuit model".

Chapter 2 provides readers a taste of the primary MaCRO models as well as overall simulation algorithms. First, two commercial state-of-the-art reliability simulation tools are reviewed, followed by a discussion of their limitations and possible improvements. Then, a set of MaCRO lifetime models and circuit models for each wearout mechanism are summarized. Finally, the overall MaCRO simulation algorithms, tailored for two distinct application purposes, are presented.

Chapters 3 to 5 introduce the detailed development of the lifetime and circuit models for HCI, TDDB and NBTI, respectively. Chapter 3 is dedicated to HCI effect and discusses the modeling process for this somewhat "old" wearout mechanism. In this chapter, the  $\Delta R_d$  model proposed elsewhere is improved to include the contributions of both interface trap generation and oxide charge trapping effects, the latter one being neglected in the original  $\Delta R_d$  model. This improvement, although complicating parameter extraction work, is physically more comprehensive

and accurate in characterizing hot carrier damages.

Chapter 4 focuses on TDDB effect and presents detailed development of lifetime and failure circuit models for this important wearout mechanism. This chapter proposes an advanced TDDB lifetime model that combines many important experimental observations, including power law voltage acceleration, non-Arrhenius temperature acceleration, Poisson area scaling statistics, and cumulative failure percentile scaling effects. Before introducing the new MaCRO circuit model, a thorough review of existing TDDB circuit models is presented for the sake of compensating for the obvious absence of overview papers of this kind in this area. From this careful review, an important error in the most frequently used TDDB SPICE circuit model is identified. Finally, a new TDDB circuit model is proposed and the number of model parameters is reduced to only one, which significantly simplifies its application process in circuit reliability analysis.

Chapter 5 covers NBTI effect and introduces lifetime and circuit models for this relatively new wearout mechanism. Based on an existing physics and statistics based model, a new NBTI lifetime model is developed that explains most experimental observations on NBTI-induced threshold voltage variations, including fractional power law dependence, saturation phenomenon, and dynamic recovery effects. Weibull statistics is included in explaining this NBTI lifetime model, thereby providing a new understanding of NBTI degradation behaviors. Starting from this new lifetime model, a physics-of-failure based NBTI circuit model, which is both simple and expandable, is developed. It is presumed to be the first NBTI damaged circuit model in literature.

Besides the aforementioned MOSFET-related wearout mechanisms, another important failure type intrinsic to Silicon chips is Electromigration (EM). Distinct from other mechanisms, EM is a metallization-related wearout process. For simplicity, MaCRO does not consider the impact of EM on circuit functionality. However, it includes the contribution of EM in circuit failure rate prediction and product derating behavior analysis. Chapter 6 focuses on EM failure physics and lifetime modeling, and provides practical guidelines in extrapolation of current density and activation energy to estimate EM failure rates. The EM models are integrated into MaCRO and combined with other lifetime models to help designers properly derate device and circuit operating parameters for reliability improvement and to predict reliability trends in future technologies.

The MaCRO models can be used for various application purposes depending on different data availability. If all lifetime model parameters can be obtained from experimental work, then MaCRO can accurately calculate the circuit lifetimes and failure rates. If process parameters of future technologies are projected, then MaCRO can predict reliability trends over generations and identify critical failure mechanisms. Based on the previous two applications, MaCRO can be further used in derating product voltage and temperature for reliability enhancement. If circuit functionality is of primary interest, MaCRO can quickly identify more damaged transistors in circuit in terms of the device's terminal voltage and current stress profiles, then MaCRO can include corresponding circuit models in the second round of SPICE simulation, which will reveal whether or not circuit functionality is maintained. Among these different applications, derating for reliability and circuit

reliability simulation are of primary importance and more difficult to implement. Chapter 7 addresses the derating method while chapter 8 shows a circuit example for reliability simulation with failure models.

Chapter 7 explores how device and circuit operating parameters, such as switching speed and power dissipation, scale with voltage and temperature. A 17-stage CMOS ring oscillator is simulated under different stress conditions to characterize the accurate derating relations and trends. Reduced voltage, frequency and temperature will reduce internal stresses in devices, thereby improving the devices' reliability. Since all these variations for a single device are proportional, the ratios can be applied to a full circuit with the help of a simple derating model. From the ring oscillator simulation, some practical design guidelines are formulated for developers to correctly derate devices for long-life applications.

In Chapter 8, a simple SRAM circuit is designed and simulated to demonstrate how to apply MaCRO to circuit reliability modeling, simulation, analysis and design. The SRAM circuit, implemented with a commercial  $0.25\mu m$  technology, consists of functional blocks of one bit 6-transistor (6-T) cell, precharge, read/write control and sense amplifier. The SRAM operation sequence of "write 0, read 0, write 1, read 1" is first simulated in SPICE to obtain terminal voltage and current stress profiles of each transistor. Then, normalized lifetimes of all transistors, in terms of each wearout mechanism, are calculated with the corresponding lifetime models. These lifetime values are sorted to single out the most damaged transistors. Finally, the selected transistors are substituted with circuit models, and SPICE simulation is performed again to characterize circuit performance, functionality, and

failure behaviors. Simulation shows that for the  $0.25\mu m$  technology, HCI and TDDB have significant effects on SRAM cell stability and Voltage Transfer Characteristics (VTC) while NBTI mainly degrades cell transition speed when the cell state flips. The illustrative SRAM simulation work proves by using MaCRO models that circuit designers can better understand the damage effects of HCI/TDDB/NBTI on circuit operation, quickly estimate circuit functional lifetime, make appropriate performance and reliability tradeoffs, and formulate practical design guidelines to improve circuit resistance to failures.

Chapter 9 concludes this dissertation. The main contributions of this work are summarized and some suggestions for future work are proposed.

#### Chapter 2

#### Simulation Models and Algorithms

#### 2.1 Overview

The advent of deep submicron technologies and the continuing shrinkage of MOSFET physical geometries have raised many new challenges in predicting circuit lifetimes and securing sufficient reliability margins. One of the essentials of reliable IC production is consistently fabricating a product that is capable of sustaining its intended functionality for specified time under stated operating conditions. The established practice has been to incrementally improve reliability through a lengthy design-manufacture-test cycle, however, this method is proved to be prohibitively expensive in most small-volume productions. Furthermore, some of the long-term wearout mechanisms cannot be identified and properly weeded out only by accelerated burn-in tests [13]. These considerations, in addition to fierce competition and higher pressure in achieving a shorter time-to-market objective, have impelled product reliability analysis to be addressed in advance at the initial design stage.

The development and use of effective reliability simulation methods are one of promising solutions for this early analysis and assessment. Once the reliability factors of the circuit are calibrated through simulation, the results can be compared

with initial specifications or limits. If the predicted reliability falls short of the requirements, new design iterations will be performed to improve the circuit robust-ness to failures. This cycle may be repeated for several times until the simulated reliability is satisfied. The ultimate goal of circuit reliability simulation, i.e. DFR, is toward Built-In-Reliability (BIR) allowing designers properly weigh performance and reliability tradeoffs and fully explore potentials of deep submicron technologies.

There are three distinct design levels at which DFR strategies are applicable:

(a) at technology-level, where various material and structural failure mechanisms can be simulated with Technology Computer Aided Design (TCAD) tools; (b) at circuit-level, where the reliability of overall circuits and the impact of failure mechanisms on circuit operations can be characterized; (c) at package-level, where circuits as one entity are stressed mechanically, electrically and thermally for reliability qualification [14]. The focus of this dissertation work is on the circuit-level DFR implementation.

There are very few simulation tools built from scratch, and MaCRO is unexceptional. The best way to understand the similarity and differentiation between MaCRO and other simulation methods is reviewing them side by side in the same framework. In this chapter, first, two commercial state-of-the-art reliability simulation tools are reviewed. What follows is a discussion of their limitations and possible improvements. Finally, a snapshot of the MaCRO models and simulation algorithms is given. The subsequent chapters zoom into each of these models and present their development and applications in details.

### 2.2 Review of Reliability Simulation Tools

Hot carrier induced MOS device wearout is one of the most critical reliability issues for deep submicron CMOS integrated circuits. Hot carrier reliability models and simulation methods have been proposed and widely implemented in the semi-conductor industry for many years. To some extent, the accuracy of hot carrier reliability simulation represents the robustness and efficiency of an entire reliability simulator, therefore, for simplicity, HCI simulation is employed here as the vehicle to deliver the basic concepts, modeling techniques and simulation flows realized in some commercial state-of-the-art reliability tools.

#### 2.2.1 Reliability Simulation in Virtuoso UltraSim

Virtuoso UltraSim is the Cadence FastSPICE circuit simulator capable of predicting and validating timing, power and reliability of mixed-signal, complex digital and System-on-Chip (SoC) designs in advanced technology of  $0.13\mu m$  and below. It has a set of specialized reliability models (AgeMos) for HCI and NBTI simulation [15]. In the simulation, an Age parameter is calculated for each nMOSFET with the following formula:

$$Age(\tau) = \int_{t=0}^{t=\tau} \left[ \frac{I_{sub}}{I_{ds}} \right]^m \frac{I_{ds}}{W \cdot H} dt$$

(2.1)

where W refers to the channel width of the transistor, m and H are technology dependent parameters and determined from experiments,  $I_{sub}$  is the substrate current,  $I_{ds}$  is the drain-to-source current,  $\tau$  is the stress time. For pMOSFETs, the gate current  $I_{gate}$  instead of  $I_{sub}$  is used to determine the Age parameter. The degree of

device wearout has been experimentally found to be a function of this Age parameter for wide ranges of channel lengths and stress conditions, and the relationship has a plausible theoretical basis [16].

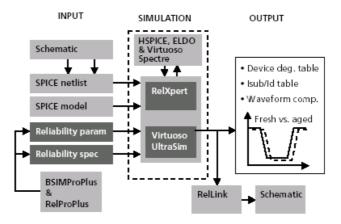

The simulation starts with device parameter extraction and modeling. From the SPICE model parameters of fresh devices, some other device parameters are added to accurately model  $I_{sub}$ . The next step is AgeMos extraction. Based on the Age parameter calculated from the fresh simulation, the AgeMos applies the degradation models, which can communicate with most SPICE-like simulators, to the aged circuit simulation. Reliability simulation with Virtuoso UltraSim is an iterative process, in which a large number of iterations are often needed in order to obtain accurate modeling results. The simulator can calculate and output the degradation results to predict the lifetime of each MOSFET within a circuit [17]. The overall simulation flow is illustrated in Fig.2.1.

Figure 2.1: Hot carrier reliability simulation flowchart in Virtuoso UltraSim. Device wearout modeling is the focus of the reliability analysis [17].

The fundamental models and algorithms of reliability simulation realized in Virtuoso UltraSim found their origins in Berkeley Reliability Tool (BERT) which gives rise to many other reliability simulation tools. Most of these descendent tools are based on the same Age parameter modeling concept. The main advantages of these BERT-like tools are accuracy and SPICE compatibility, however, they also impose a burden on designers to correctly extract device's fresh and degraded parameters and may lead to nonphysical trends, which prevents their popularity in reliability design process.

#### 2.2.2 Reliability Simulation in Eldo

Eldo is a circuit simulator developed by Mentor Graphics which delivers all the capability and accuracy of SPICE-level simulation for complex analog circuits and SoC designs. In Eldo, the substrate current  $I_{sub}$  is not selected as the primary reliability parameter. In general, drain current  $I_d$ , threshold voltage  $V_t$  or transconductance  $g_m$  is often used as a degradation monitoring parameter, and the stress time resulting in 10% decrease of one of these monitoring parameters is arbitrarily set to the device lifetime. Degradation of  $I_d$  is a good monitor for digital circuits, while  $V_t$  shift is suitable for analog applications. Hot carrier reliability simulation in Eldo adopts  $I_d$  as degradation monitoring parameter and characterizes it with a compact  $\Delta I_d$  model, which directly models the difference of drain currents between fresh and aged devices.

There exist two competing mechanisms which lead to the obvious hot carrier

induced drain current variations between fresh and degraded devices: the deviation of  $I_d$  from its linear dependency of  $V_{ds}$  due to velocity saturation effects and the decreasing of  $\Delta I_d/I_d$  due to the reduction of charged interface states [18]. In Eldo, the  $\Delta I_d$  is modeled with equ.(2.2) to (2.5), which unify the subthreshold, linear and saturation regions with a simple relation for both forward and reverse operation modes [19]:

$$\frac{\Delta I_d}{I_d} = \frac{B_6(1 - e^{-B_1 V_{gs}}) + B_2}{1 + B_5(V_{gs} - B_3 V_t)} \times \frac{N_{it} L_{it}}{L_{eff}} \times \frac{1}{1 + \alpha(V_{ds} - V_{low}) + \beta V_{ds}}$$

(2.2)

$$V_{low} = A_3 V_{dsat} (2.3)$$

$$\alpha = \frac{A_1}{1 + A_4 (V_{as} - V_t)^{A_2}} \tag{2.4}$$

$$\beta = A_5 V_{gs} + A_6 \tag{2.5}$$

where  $N_{it}$  is the interface trap density,  $L_{it}$  is the extension of the damage within the channel,  $L_{eff}$  is the effective channel length,  $V_{gs}$  is the gate-to-source voltage,  $V_t$  is the threshold voltage,  $V_{ds}$  is the drain-to-source voltage,  $V_{dsat}$  is the drain saturation voltage,  $A_1$  to  $A_6$  and  $B_1$  to  $B_6$  are model fitting parameters.

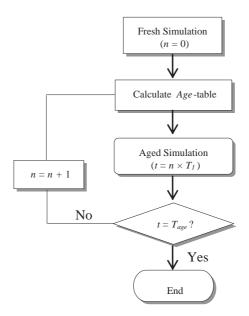

The same Age parameter defined by equ.(2.1) is incorporated to model the "age" of each transistor. The HCI aging process is simulated in an iterative way as depicted in Fig.2.2.

The period  $T_{age}$  at which the circuit performance is to be tested is divided into smaller time intervals  $T_1$ . The Age table is calculated at the end of each time interval and a new simulation with Eldo is carried forward. This process is repeated

Figure 2.2: HCI reliability simulation in Eldo [19]. A large number of SPICE simulation iterations have to be carried out to obtain accuracy.

until  $T_{age}$  is reached. This iterative scheme can account for the gradual change of bias conditions as a result of device wearout.

The  $\triangle I_d$  modeling approach provides the possibility to have a relatively simpler parameter extraction process. It is suitable to model bi-directional stress and asymmetrical drain current behavior. However, because this approach also adopts both Age parameter and small-step iterative algorithm in the degradation simulation process, it inherits the same limitations of the BERT-like tools as discussed before.

### 2.3 Limitations and Improvements

Although the previous brief review reveals both the advantages and limitations of the contemporary reliability simulation tools, a further discussion is necessary for the sake of identifying the fundamental reasons for these limitations and understanding how MaCRO models and simulation algorithms overcome some of these limitations.