#### **ABSTRACT**

Title of Dissertation: EXPERIMENTAL STUDY OF BIAS TEMPERATURE

INSTABILITY AND PROGRESSIVE BREAKDOWN OF

ADVANCED GATE DIELECTRICS

Baozhong Zhu, Doctor of Philosophy, 2005

Directed By: Professor Joseph Bernstein

Department of Mechanical Engineering

Dr. John Suehle

Semiconductor Electronics Division, NIST

With shrinking gate dielectrics, the reliability requirements of semiconductor gate dielectrics become more and more difficult to maintain. New physical mechanisms and phenomena are discovered and new challenges arise.

At the same time, some issues, which have been minor in the past, begin to show bigger impact, such as the Negative Bias Temperature Instability issue. The dynamic NBTI phenomenon was studied with ultrathin SiO<sub>2</sub> and HfO<sub>2</sub> devices. With a dynamic stress condition, the device lifetime can be largely extended due to the reduced NBTI degradation. This reduction is contributed to the annealing of fixed oxide charges during the stress off period. A mathematical model is also established to explain this phenomenon.

With alternative gate dielectrics' introduction, new issues associated with these materials and device structures are also raised. Those issues need to be studied in detail before fully incorporation of new materials. Compared with SiO<sub>2</sub> devices, the NBTI degradation of HfO<sub>2</sub> has a similar trend. However, it is found that they have different

frequency response than the SiO<sub>2</sub> devices. This difference is later found due to the traps inside the gate dielectrics. Detailed studies show that NBTI degradations at dc stress and dynamic stress conditions have different temperature acceleration factors due to the bulk traps. The disappearance of this difference by insetting a detrapping period further proves this observation.

As we enter the ultrathin gate dielectrics regime, the electron tunneling mechanisms behind the gate dielectrics breakdown shift. Consequently, gate dielectrics breakdown mode also shifts from the clear-detected hard breakdown to the noisy soft breakdown. Thus new lifetime extrapolation models are needed. The progressive breakdown of ultrathin SiO<sub>2</sub> is studied by a two-step test methodology. By monitoring the degradation of the progressive breakdown path in terms of the activation energy, the voltage acceleration factor, two kinds of breakdown filaments, the stable one and the unstable one, were studied. The stable filament is found to be a breakdown filament independent of the original breakdown filament, and the unstable filament is the continuing degradation of the original filament.

# EXPERIMENTAL STUDY OF BIAS TEMPERATURE INSTABILITY AND PROGRESSIVE BREAKDOWN OF ADVANCED GATE DIELECTRICS

By

#### Baozhong Zhu

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2005

### **Advisory Committee:**

Professor Joseph Bernstein, Chair/Advisor Dr. John Suehle, Co-Advisor Professor Ichiro Takeuchi Professor Carol Smidts Professor Ali Mosleh Professor Martin Peckerar © Copyright by Baozhong Zhu 2005

### Dedication

To my parents and my wife

### Acknowledgements

At first, I would like to give my sincere thanks to Prof. Joseph Bernstein. He is the one who led me into the field of microelectronics reliability engineering. He has given me the greatest opportunity to explore a whole new world.

At the same time, I would like to thank my co-advisor Dr. John Suehle at National Institute of Standards and Technology. For the past three years, Dr. Suehle has been not only an advisor in the academic study and technical research but also a great friend in life. Most important of all, he gave me a great opportunity to make full use of my practical research abilities.

Special thanks go to Dr. Eric Vogel at NIST for technical discussions and support. Additional thanks would also go to Dr. Dawei Heh at University at Maryland, Dr. Yuan Chen at JPL, Dr. Jinping Han at Infineon, and Dr. Sang-Mo Koo at NIST for their great help.

I would also like to thank my parents for giving me strength and encouragement.

Great thanks would also go to my brother and sister; they have been sharing my part of responsibilities to support our whole family.

An accomplishment as this could not be made without the great support of my wife. I appreciate her tolerance of a PhD at home.

### Table of Contents

| Dedication                                                   | ii |

|--------------------------------------------------------------|----|

| Acknowledgements                                             |    |

| Table of Contents                                            | iv |

| List of Figures                                              | vi |

| Chapter 1 Introduction                                       | 1  |

| 1.1 Brief history of semiconductor devices                   | 1  |

| 1.2 Scaling of MOS devices                                   | 1  |

| 1.3 Reliability requirements of gate dielectrics             | 2  |

| Chapter 2 MOSFET Basics                                      |    |

| 2.1 Basics of MOSFETs                                        | 5  |

| 2.1.1 I <sub>d</sub> -V <sub>g</sub> Characteristics         | 5  |

| 2.1.2 Simplified Device Fabrication                          | 6  |

| 2.2 Device Quality Characterization                          |    |

| 2.2.1 Capacitance Voltage Measurement (CV)                   |    |

| 2.2.2 The Dielectric Tunneling Current Characterization (IV) |    |

| 2.2.3 Charge Pumping Measurement (CP)                        |    |

| 2.2.4 Subthreshold Swing (SS)                                |    |

| Chapter 3 Gate Dielectrics Integrity                         |    |

| 3.1 Introduction                                             | 19 |

| 3.2 Reliability Engineering Basics                           | 19 |

| 3.2.1 Definitions and Basic Concepts                         |    |

| 3.2.2 Common Reliability Functions and Bathtub Curve         | 20 |

| 3.2.3 Accelerated Testing                                    |    |

| 3.3 Ultrathin Gate Dielectric Reliability                    | 23 |

| 3.3.1 Physical Mechanisms of Dielectric Breakdown            | 23 |

| 3.3.2 Dielectrics Stress Methodologies                       |    |

| 3.3.3 Lifetime Extrapolation Models                          |    |

| 3.4 Statistics and Percolation Theory of Breakdown           | 32 |

| Chapter 4 Negative Bias Temperature Instability              | 40 |

| 4.1 Introduction                                             | 40 |

| 4.2 Static NBTI                                              | 41 |

| 4.2.1 Degradation Phenomena                                  | 41 |

| 4.2.2 NBTI Mechanisms                                        | 44 |

| 4.2.3 Device Lifetime Extrapolation                          | 46 |

| 4.2.4 NBTI Impact on Circuits                                |    |

| 4.3 Dynamic NBTI of Ultrathin SiO <sub>2</sub>               | 48 |

| 4.3.1 Introduction                                           | 48 |

| 4.3.2 Devices and Experimental Setup                         | 49 |

| 4.3.3 Results and Discussion                                 |    |

| 4.3.4 Conclusion                                             |    |

| 4.4 Dynamic NBTI of HfO <sub>2</sub> Devices                 | 55 |

| 4 4 1 Introduction                                           | 55 |

| 4.4.2 Device and Experimental Setup                           | 56  |

|---------------------------------------------------------------|-----|

| 4.4.3 Results and Discussion                                  |     |

| 4.4.4 Conclusion                                              | 63  |

| Chapter 5 Progressive Breakdown of Ultrathin Gate Dielectrics | 77  |

| 5.1 New Breakdown Phenomena of Advanced Gate Dielectrics      | 77  |

| 5.1.1 Hard Breakdown and Soft Breakdown                       | 77  |

| 5.1.2 Definition of Failure                                   | 78  |

| 5.1.3 New Reliability Methodology                             | 78  |

| 5.1.4 Impact of Soft Breakdown                                | 80  |

| 5.1.5 Dielectric Breakdown of HfO <sub>2</sub>                | 81  |

| 5.2 Progressive Breakdown of SiO <sub>2</sub>                 | 83  |

| 5.2.1 Introduction                                            |     |

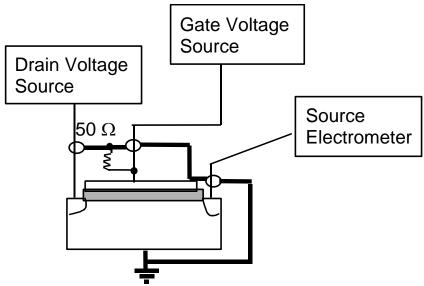

| 5.2.2 Devices and Experimental Setup                          |     |

| 5.2.3 Results and Discussion                                  |     |

| 5.2.4 Conclusion                                              | 89  |

| Chapter 6 Conclusion.                                         | 103 |

| Appendices                                                    | 105 |

# List of Figures

| Fig. 1.1. The scaling of device minimum feature size.                                                             | 4   |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 1.2. The scaling of the equivalent oxide thickness of different applications                                 |     |

| Fig. 2.1. The three regions of a MOSFET                                                                           | 17  |

| Fig. 2.2. The CV curve of a MOS capacitor.                                                                        | 18  |

| Fig. 2.3. The peak current vs. the frequency                                                                      | 18  |

| Fig. 3.1. The bathtub curve of the product lifetime.                                                              |     |

| Fig. 3.2. The comparison of 1/E model and E model.                                                                |     |

| Fig. 3.3. The cell based percolation theory                                                                       |     |

| Fig. 3.4. The relationship between Weibull slope and gate oxide thickness                                         |     |

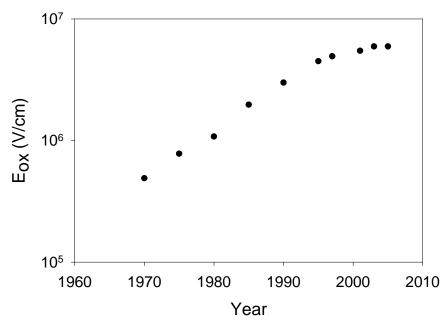

| Fig. 4.1. The electric field at different technology generations.                                                 |     |

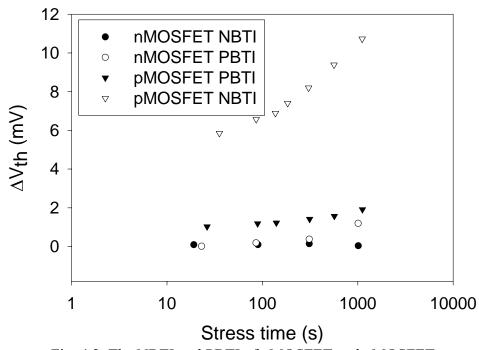

| Fig. 4.2. The NBTI and PBTI of nMOSFET and pMOSFET                                                                |     |

| Fig. 4.3. The band diagram of flat band and inversion conditions of nMOSFETs                                      |     |

| pMOSFETs                                                                                                          |     |

| Fig. 4.4. The electrochemical reaction model of NBTI                                                              |     |

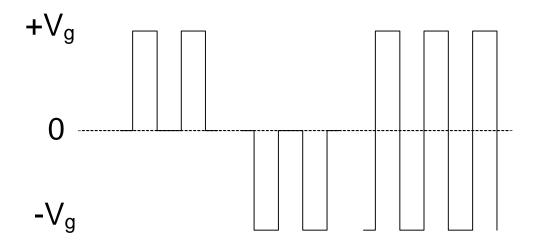

| Fig. 4.6. The stress waveforms for the pulsed NBTI study                                                          |     |

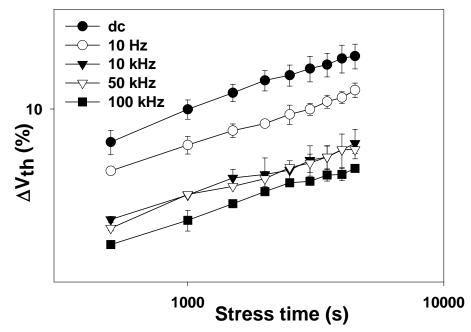

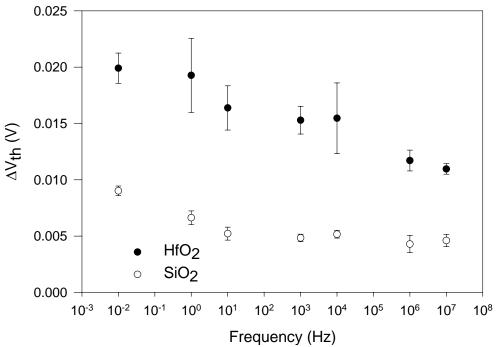

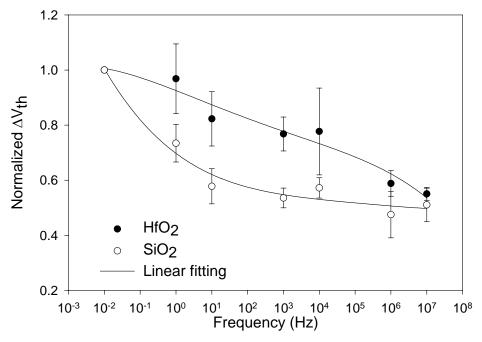

| Fig. 4.7. The frequency dependence of $\Delta V_{th}$                                                             |     |

|                                                                                                                   |     |

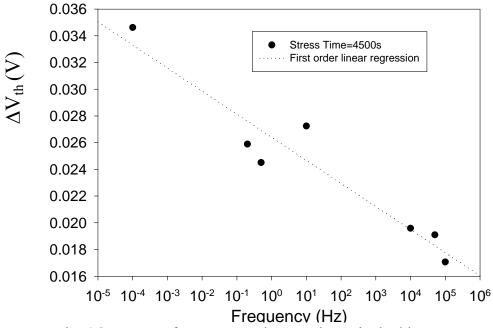

| Fig. 4.8. $\Delta V_{th}$ vs. frequency, under negative unipolar bias stresses                                    |     |

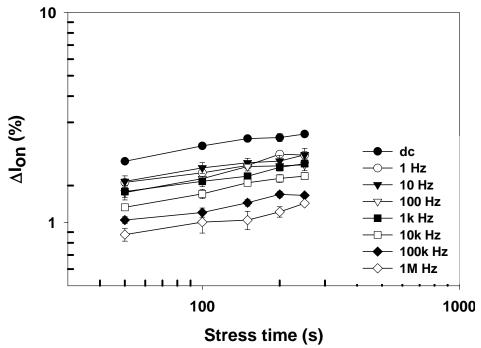

| Fig. 4.9. The frequency dependence of $\Delta I_{on}$                                                             | 69  |

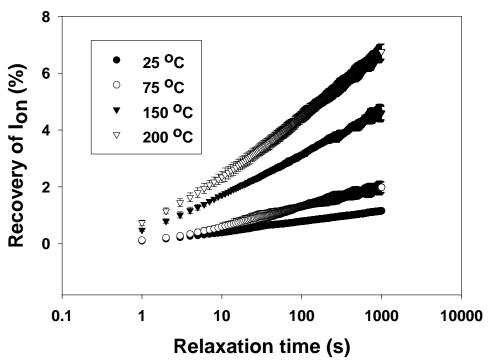

| Fig. 4.10. The recovery of $I_{on}$ at different temperatures                                                     | 69  |

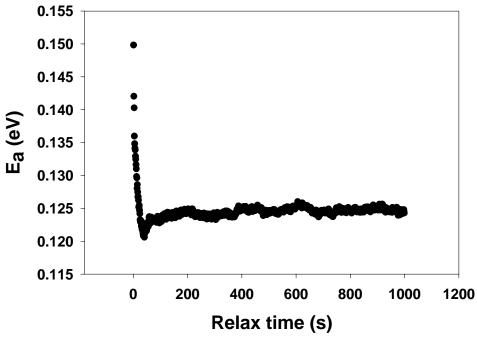

| Fig. 4.11. The activation energies extrapolated from data in Fig. 4.10                                            | 70  |

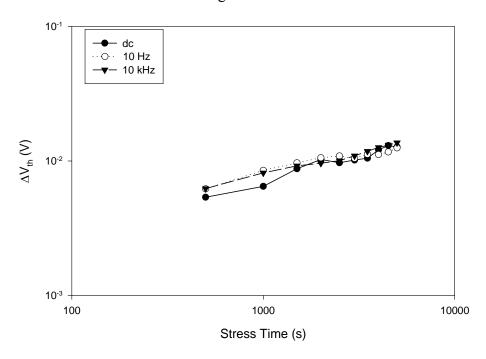

| Fig. 4.12. $\Delta V_{th}$ under positive unipolar stress with different frequencies                              |     |

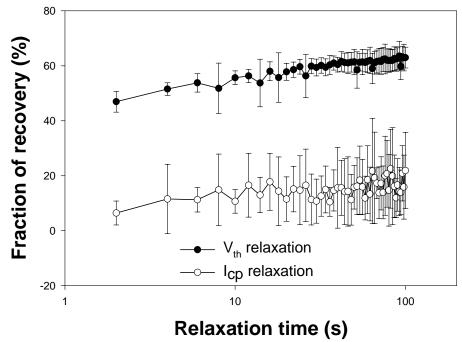

| Fig. 4.13. The annealing of $\Delta I_{cp}$ and $\Delta V_{th}$                                                   |     |

| Fig. 4.14. $\Delta V_{th}$ under different stress conditions with a 10 kHz frequency                              |     |

| Fig. 4.15. The model fitting of $\Delta I_{on}$ with different stress conditions and different stress conditions. |     |

| oxide thickness                                                                                                   |     |

| Fig. 4.16. The measured time constants related with the stress on and stress                                      |     |

| 1                                                                                                                 | 72  |

| Fig. 4.17. Time evolution of $\Delta V_{th}$ of HfO <sub>2</sub> devices and the control SiO <sub>2</sub> sample. | 73  |

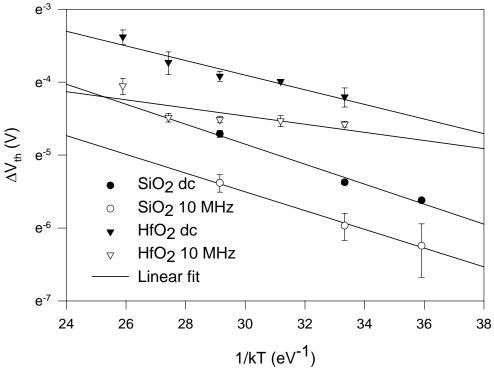

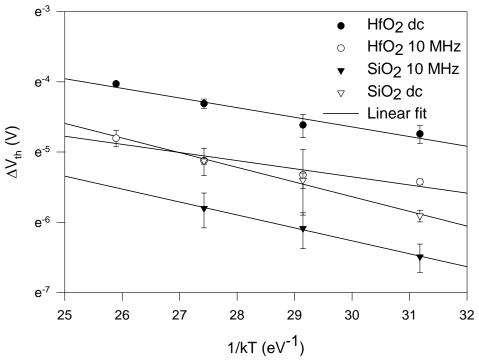

| Fig. 4.18. Comparison of the frequency dependence of $\Delta V_{th}$ of HfO <sub>2</sub> devices and              | the |

| control SiO <sub>2</sub> sample                                                                                   |     |

| Fig. 4.19. Comparison of the frequency dependence of normalized $\Delta V_{th}$ of H                              |     |

| devices and the control SiO <sub>2</sub> sample                                                                   |     |

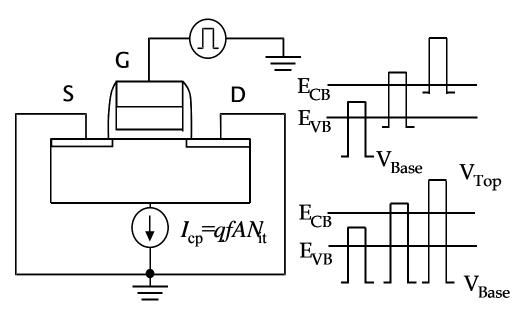

| Fig. 4.20. The two charge pumping measurements.                                                                   |     |

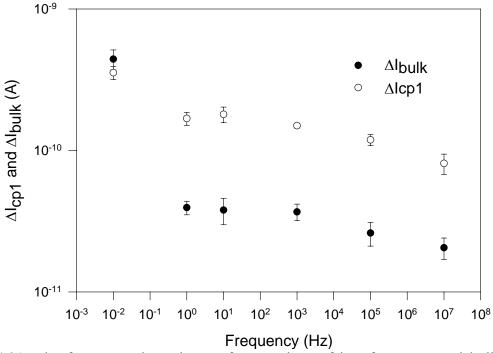

| Fig. 4.21. The frequency dependence of generations of interface traps and bulk to                                 |     |

|                                                                                                                   |     |

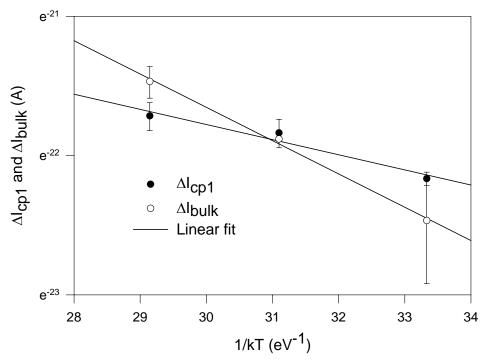

| Fig. 4.22. Different temperature acceleration factors of charge pumping currents                                  |     |

| to interface traps and bulk traps.                                                                                | 75  |

| Fig. 4.23. The temperature acceleration of generations of interface traps and bulk                                  |

|---------------------------------------------------------------------------------------------------------------------|

| traps                                                                                                               |

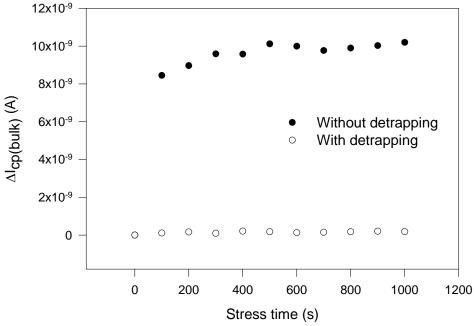

| Fig. 4.24. The charge pumping current due to the bulk traps with and without                                        |

| detrapping period76                                                                                                 |

| Fig. 4.25. The temperature acceleration of $\Delta V_{th}$ of HfO <sub>2</sub> devices and control SiO <sub>2</sub> |

| devices at two stress conditions.                                                                                   |

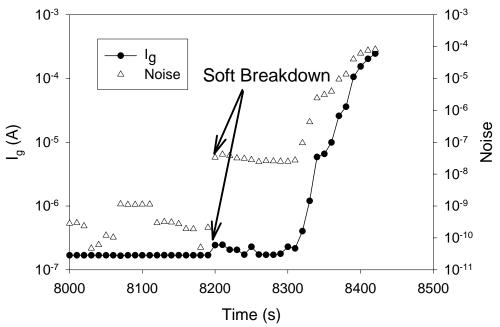

| Fig. 5.1. The soft breakdown of gate dielectrics                                                                    |

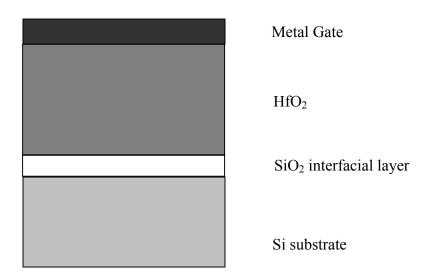

| Fig. 5.2. The schematic structure of the HfO <sub>2</sub> device                                                    |

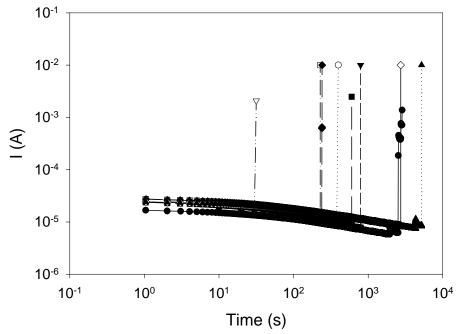

| Fig. 5.3. Constant voltage stress of the HfO <sub>2</sub> devices                                                   |

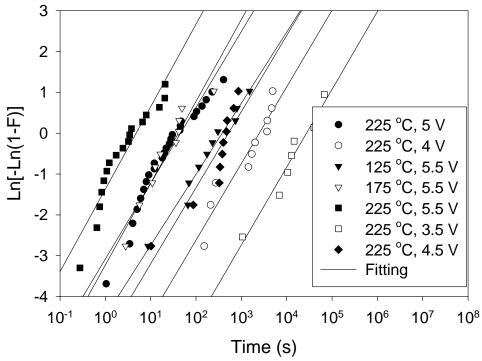

| Fig. 5.4. Lifetime distribution of HfO <sub>2</sub> devices                                                         |

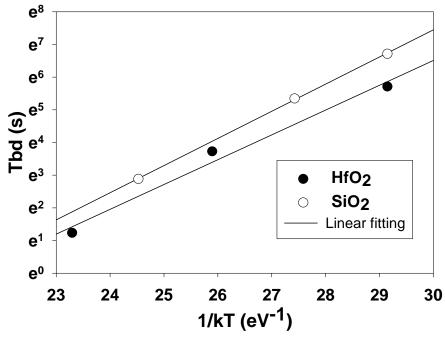

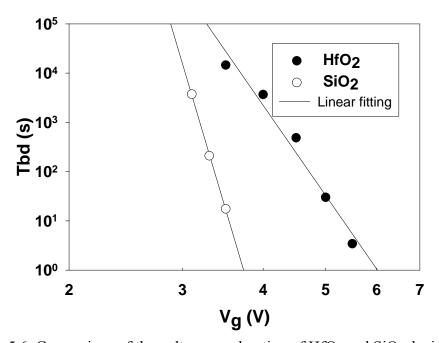

| Fig. 5.5. Comparison of the temperature dependence of HfO <sub>2</sub> and SiO <sub>2</sub> devices93               |

| Fig. 5.6. Comparison of the voltage acceleration of HfO <sub>2</sub> and SiO <sub>2</sub> devices93                 |

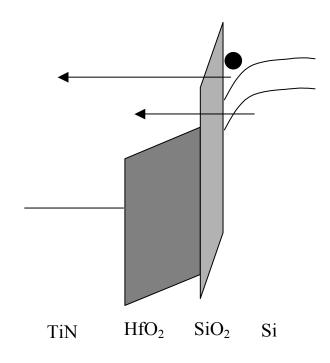

| Fig. 5.7. The substrate injection stress of the HfO <sub>2</sub> device94                                           |

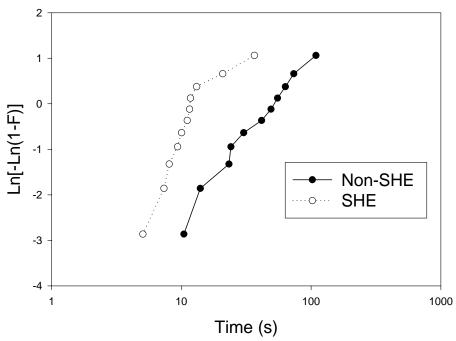

| Fig. 5.8. The influence of substrate hot electron injection to the device lifetime                                  |

| distribution94                                                                                                      |

| Fig. 5.9. The substrate hot electron injection of the HfO <sub>2</sub> device                                       |

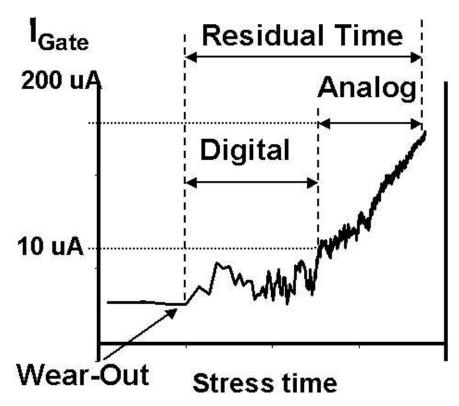

| Fig. 5.10. Stable soft breakdown of the gate oxide                                                                  |

| Fig. 5.11. Unstable soft breakdown of the gate oxide.                                                               |

| Fig. 5.12. The digital and analog phases                                                                            |

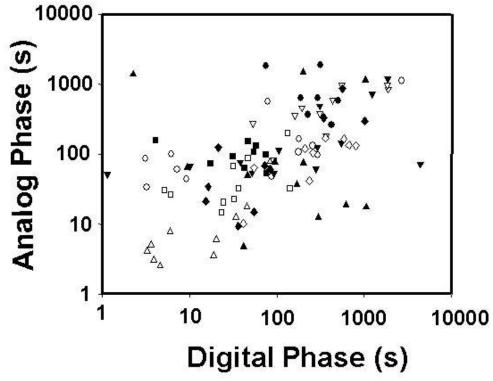

| Fig. 5.13. The correlation between the length of the analog and digital phase of the                                |

| unstable soft breakdown                                                                                             |

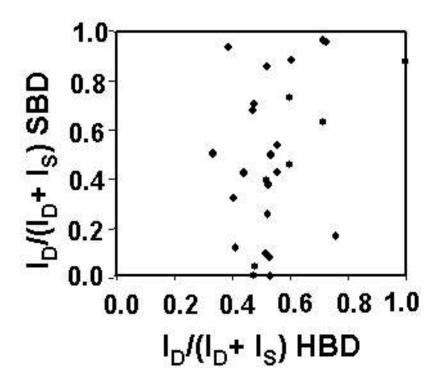

| Fig. 5.14. The correlation between the first breakdown and final breakdown of stable                                |

| soft breakdown                                                                                                      |

| Fig. 5.15. The correlation between the first breakdown and final breakdown of                                       |

| unstable soft breakdown 99                                                                                          |

| Fig. 5.16. The voltage acceleration of the unstable soft breakdown                                                  |

| Fig. 5.17. The temperature dependence of the unstable soft breakdown                                                |

| Fig. 5.18. The temperature dependence of the unstable, stable soft breakdown and the first breakdown                |

| Fig. 5.19. The voltage acceleration of the residual time for unstable, stable sof                                   |

| breakdown and the first breakdown                                                                                   |

| Fig. 5.20. SHEI test for the unstable breakdown filament                                                            |

| Fig. 5.21. SHEI test for the stable breakdown filament                                                              |

| Fig. 5.22. The influence of the current compliance to the consequent stress leakage                                 |

| current                                                                                                             |

| Fig. 5.23. The influence of first breakdown hardness to the residual time103                                        |

| - 17. 55. Ind miliagues of mot of same till milaneous to the festiman tillio                                        |

### Chapter 1

### Introduction

#### 1.1 Brief history of semiconductor devices

W. Shockley, J. Bardeen and W. H. Brattain invented the bipolar transistor in 1947. After that, great efforts were invested in the field of semiconductors. In 1959, J. Kilby demonstrated the concept of Integrated Circuits (IC). D. Kahng and M. M. Attala fabricated the first Metal Oxide Semiconductor Field Effect Transistor in 1960. These two events provided the basis for the microelectronics industry evolution. Since then, the MOSFET has become the most important part for very large-scale integrated circuits. By 1990, the number of devices manufactured on a chip had grown from 100,100 devices per chip to more than 32 million devices per chip. Thus, the era of ultra large-scale integration has begun.

#### 1.2 Scaling of MOS devices

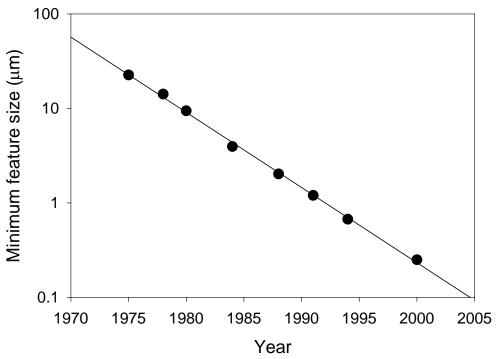

The increasing of device density has been accompanied by shrinking minimum feature size, which had decreased from 25  $\mu m$  at 1960s to 0.5  $\mu m$  at 1990s', and 0.25  $\mu m$  at year 2000, as shown by Fig. 1.1 [1, 2].

The scaling of device dimensions (channel length, equivalent oxide thickness, and junction depth) largely increased the device density and reduced the transistor cost. Initially, the industry followed the constant voltage scaling. With this scaling mode,

this resulted in large oxide field, which degraded the oxide integrity. Later, a constant electrical field scaling method was used. However, this made integration with different technologies difficult, as they would have different operating voltages. Practically, the industry follows a compromised scaling model of the constant voltage and electrical field models. Further process improvements and new structures are introduced to overcome those difficulties.

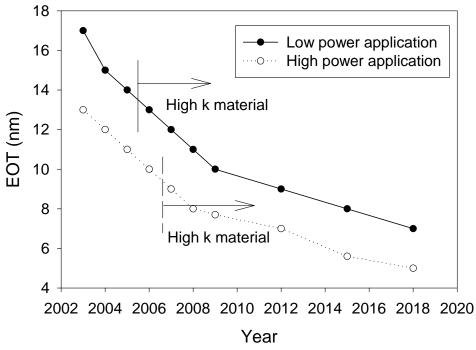

Suggested by the International Technology Roadmap for Semiconductors (ITRS) [3], the introduction of alternative gate dielectrics is predicted from 2005 to 2007 depending on the technology application, as shown by Fig. 1.2. Due to the stringent leakage requirements for low standby power devices, the leakage current specifications cannot be met with conventional gate dielectrics in the sub 1.5 nm regime. Thus, the high-*k* dielectrics are likely first introduced in these applications. These alternative dielectrics will be deposited by either a chemical vapor deposition technique [4, 5], physical vapor deposition[6], jet vapor deposition [7] or molecular beam epitaxy [8, 9]. More work and new technologies are still needed.

#### 1.3 Reliability requirements of gate dielectrics

With shrinking gate dielectrics, the reliability requirements become more and more difficult to maintain. New physical mechanisms and phenomena are discovered and new challenges arise. As we enter the ultrathin gate dielectrics regime, the electron tunneling process is dominated by the direct tunneling instead of FN tunneling [10]. The gate dielectrics breakdown mode also shifts from the clear-detected hard breakdown to the noisy soft breakdown [11, 12]. Thus new lifetime

extrapolation models are needed. At the same time, some issues, which have been minor in the past, begin to show bigger impact, such as the Negative Bias Temperature Instability issue. Therefore, new study methods and understandings are required.

With alternative gate dielectrics' introduction, new issues associated with these materials and device structures are also raised. Traps inside the bulk dielectrics and near the interface cause instability to the threshold voltage of MOSFETs and impose new risk to the reliability of devices [13]. New gate dielectric breakdown mechanism has also been suggested [14]. Those issues need to be studied in detail before fully incorporation of new materials.

Fig. 1.1. The scaling of device minimum feature size.

Fig. 1.2. The scaling of the equivalent oxide thickness of different applications.

## Chapter 2

### **MOSFET Basics**

#### 2.1 Basics of MOSFETs

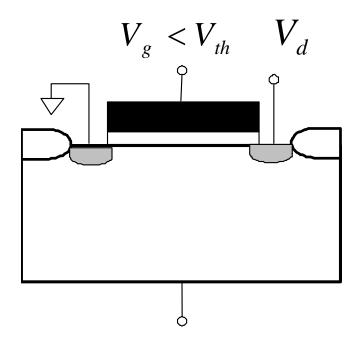

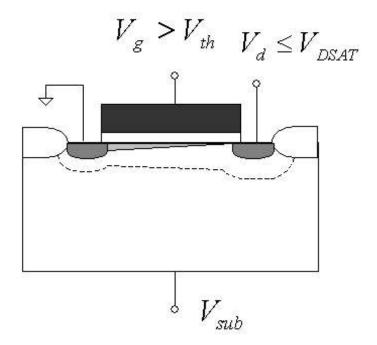

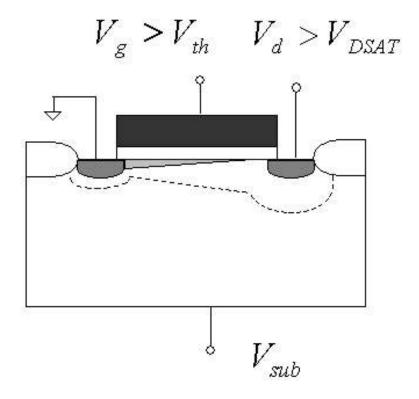

The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is a four terminal field controlled device. The n-type MOSFET (nMOSFET) consists of a source and a drain, two highly conducting n-type semiconductor regions, which are isolated from the p-type substrate by reversed-biased p-n diodes. A metal or polycrystalline gate covers the region between source and drain. The gate is separated from the semiconductor by the gate oxide. The basic structure of an nMOSFET and the corresponding circuit symbol are shown in Fig. 2.1. The basic device parameters are the channel length (L), which is the distance between the two  $n^+$ -p junctions, the channel width (W), the dielectric thickness  $t_{OX}$ , the junction depth and the substrate doping density (N<sub>A</sub>).

### 2.1.1 $I_d$ - $V_g$ Characteristics

Many models developed for the simulation of MOSFET's operation. We will briefly describe the MOSFET's operation based on the quadric model, which is relative simple and gives good approximation [15].

The operation of a MOSFET can be divided into three regions: cutoff, linear, and saturation, as shown in Fig. 2.1. At the cutoff region, the gate voltage  $V_g$  is smaller

than the threshold voltage of the device  $V_{\it th}$ , which is the turn on gate voltage of the device. The drain current  $I_{\it d}$  is zero.

When the gate voltage increases to  $V_g \ge V_{th}$ , and  $V_g - V_{th} \ge V_d \ge 0$ , the device is in the linear region. The drain current Id is given by

$$I_d = \frac{W}{L} \mu_{eff} C_{OX} (V_g - V_{th}) V_d.$$

Here,  $\mu_{\it eff}$  is the effective carrier mobility.

The threshold voltage is given by

$$V_{th} = V_{FB} + 2\phi_F + \frac{\sqrt{2\varepsilon_{Si}qN_A(2\phi_F)}}{C_{OX}}.$$

The device turns into the saturation regime when  $V_g \ge V_{th}$  and  $V_d \ge V_g - V_{th}$ . The drain current is given by

$$Idsat = \frac{W}{2L} \mu_{eff} C_{OX} (V_g - V_{th})^2.$$

#### 2.1.2 Simplified Device Fabrication

A brief description of MOSFET fabrication is given using nMOSFET as an example. The starting material is a p-type, <100> oriented, lightly doped polished silicon wafer. The <100> orientation is preferred over <111> because it has an interface trap density that is about one-tenth that of <111>. The first step is to form the oxide isolation region using LOCOS technology. A thin pad oxide is thermally grown, followed by a silicon nitride deposition. A photoresist mask defines the active device area and boron channel stop nitride layer not covered by the photoresist mask

is subsequently removed by etching. After stripping the photoresist, the wafer is placed in an oxidation furnace to grow an oxide, field oxide, then the nitride layer is removed and to drive in the boron implant.

The second step is to grow the gate oxide and to adjust the threshold voltage. The composite nitride-oxide layer over the active device area is removed, and a thin gate oxide layer is grown. For an enhancement device, boron ions are implanted in the channel region to increase the threshold voltage to a predetermined value. For a depletion device, arsenic ions are implanted in the channel region to decrease the threshold voltage.

The third step is to form the gate. Polysilicon is deposited and is heavily doped by diffusion or implantation of phosphorus to a typical sheet resistance of 20 to 30  $\Omega$ /sq. This resistance is adequate for MOSFETs with gate lengths larger than 3  $\mu$ m. For shorter devices, a polycide (a composite layer of metal silicide and polysilicon) can be used as the gate material to reduce the sheet resistance to about 1  $\Omega$ /sq.

The fourth step is to form the source and drain. After the gate is patterned, it serves as a mask for the arsenic implantation to form the source and drain, which are self-aligned with respect to the gate.

The last step is metallization. A phosphorus-doped oxide is deposited over the entire wafer and is followed by heating the wafer to give a smooth surface topography. Contact windows are defined and etched. A metal layer, such as aluminum, is then deposited and patterned. The gate contact is usually made outside the active device area to avoid possible damage to the thin gate oxide.

#### 2.2 Device Quality Characterization

#### 2.2.1 Capacitance Voltage Measurement (CV)

Maintaining the quality and reliability of gate oxides is one of the most critical and challenging tasks in any semiconductor fab. Vigorous characterization and monitoring is critical for maintaining gate oxide uniformity and quality across the wafer.

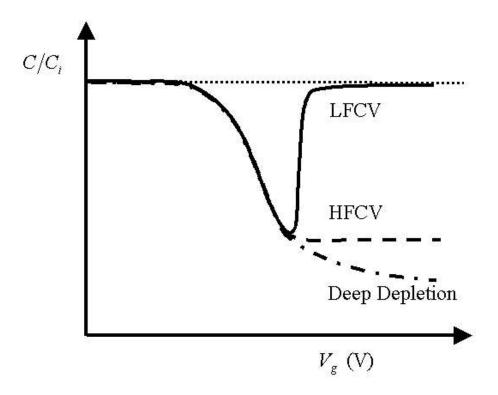

Many electrical techniques have been developed over the years to characterize gate oxide quality. CV test offers a wealth of device and process information, including bulk, interface charges, and many MOS device parameters. CV measurements are typically made on a capacitor, manufactured with the gate oxide grown at the same time under similar circumstances. From the analysis of the CV characteristics, we can get information of the fast interface state density, fixed oxide charge and slow interface state density. The shortage of CV method is the requirement of a large area capacitor and the difficulty to extrapolate the results to the actual device in the product line. The generated CV curve is characterized into three regions, as indicated by Fig. 2.2.

#### Accumulation region

For a p-substrate MOS capacitor, the accumulation region of the CV curve is observed when negative voltages are applied to the gate. The negative polarity causes majority carriers to be attracted toward the gate. Because the oxide is a good insulator, these holes accumulate at the oxide/substrate interface.

A CV test measures the oxide capacitance in the strong accumulation region; the CV curve slope is essentially flat. Therefore, the oxide thickness can be extracted

from the oxide capacitance. However, the CV curve for a very thin oxide often does not saturate to a flat slope. In that case, the measured oxide capacitance differs from the true oxide capacitance.

#### Depletion region

nMOS capacitor differs from a parallel-plate capacitor as the gate voltage moves toward positive values. Roughly, the following occurs:

- 1) The positive gate electrostatically repels holes from the oxide/substrate interface.

- 2) A carrier-depleted area forms beneath the oxide, creating a depletion region.

As a result, the high frequency CV analyzer measures two capacitances in series, the oxide capacitance and the depletion capacitance.

As the gate voltage becomes more positive, the following occurs:

- 1) The depletion region penetrates more deeply into the substrate.

- 2) The depletion capacitance becomes smaller, and the total measured capacitance becomes smaller consequently.

#### Inversion region

As the gate voltage increases beyond the threshold voltage, carrier generation and recombination move toward the carrier generation. The positive gate voltage both generates electron-hole pairs and attracts electrons, which are minority carriers, towards the gate. Again, because the oxide is a good insulator, these minority carriers accumulate at the oxide/substrate interface. Thus forms an inversion layer. Above a certain positive gate voltage, most of the available minority carriers are in the

inversion layer, and further gate voltage increases do not further deplete the semiconductor. Thus, the depletion region reaches a maximum depth.

However, the minority carrier generation is much slower than the MHz frequency range of high frequency CV measurements [16]. Therefore, once the depletion region reaches a maximum depth, the capacitance measured by the high frequency CV (HFCV) is still based on the majority carrier position and distribution. Thus, the capacitance measured by HFCV is the oxide capacitance in series with the maximum depletion capacitance, which is often referred to as the minimum capacitance.

When measuring the high frequency capacitance while sweeping the gate voltage "quickly", deep depletion occurs [17]. Quickly means that the gate voltage must be changed fast enough so that the structure is not in thermal equilibrium. One then observes that, when ramping the voltage from flatband to threshold and beyond, the inversion layer is not or only partially formed. This occurs since the generation of minority carriers cannot keep up with the amount needed to form the full inversion layer.

#### 2.2.2 The Dielectric Tunneling Current Characterization (IV)

As the oxide thickness continues scaling, the reliability issues as well as the physical mechanisms behind also change. One of the new phenomena of ultrathin gate oxides is the electron tunneling mechanism changes from the Fowler-Nordheim (FN) tunneling to the direct tunneling, as shown in Fig. 2.3. FN tunneling is a quantum mechanical tunneling process. The electrons will inject into the conduction band of dielectric through a triangular barrier.

The tunneling density is given by

$$J_{FN} = AE_{OX}^2 \exp\left(-\frac{B}{E_{OX}}\right)$$

Here

$$A = \frac{q^3}{16\pi^2 \eta \phi_B} \quad B = \frac{4(2m_{OX})^{1/2} \phi_B^{3/2}}{3q\eta}$$

Direct tunneling is also a quantum mechanical tunneling process. It occurs when electrons tunnel through the gate oxide region directly from the gate to the channel region. The direct tunneling current density is given by

$$J_{DT} = \frac{AE_{OX}^{2}}{\left[1 - \left(\frac{\phi_{B} - qV_{OX}}{\phi_{B}}\right)^{1/2}\right]^{2}} \exp\left[-\frac{B}{E_{OX}} \frac{\phi_{B}^{3/2} - (\phi_{B} - qV_{OX})^{3/2}}{\phi_{B}^{3/2}}\right]$$

Here A and B have the same definition as in the FN tunneling equation.

For thick oxides, which are larger than 5.0 nm, the FN tunneling is the dominating transport mechanism. However, when with the scaling of gate oxides, the conduction mechanism is dominated by the direct tunneling, where the electrons inject into the conduction band of anode through a trapezoidal barrier. This is true especially with ultrathin oxides with  $V_{OX}$  less than  $\phi_B$ , which is about 3.0 V [10, 18, 19].

Another important tunneling process is trap assisted tunneling [20-22]. Trap assisted tunneling occurs when electrons tunnel through the oxide into traps and then from the traps into the silicon substrate.

Besides those three tunneling processes, there are other factors that can influence the behavior of the tunneling current. One of them occurs due to the gate and drain overlap region [23]. The tunneling process through the valence band is also important especially in ultrathin gate oxides [10]. Electron hopping, field emission and the Poole Frenkel emission are other factors that need consideration [16].

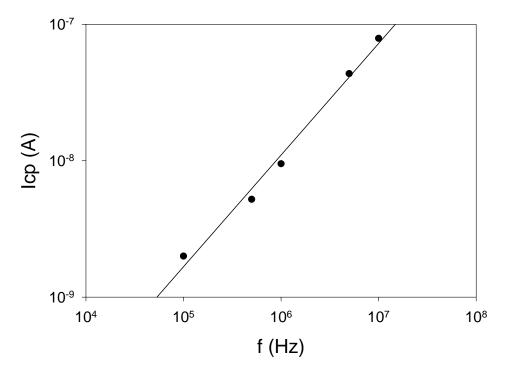

#### 2.2.3 Charge Pumping Measurement (CP)

The Si/SiO<sub>2</sub> interface in MOSFETs plays an important role in determining the device parameters and affects reliability and lifetime of the device. Thus it is important to measure and characterize the interface properties in order to understand the origin and physical properties of the interface states in a MOS system.

Depending on the distance from the interface, interface states can be divided as fast states and slow states. The fast states are those locating at or near the Si/SiO<sub>2</sub> interface and therefore they can readily exchange charge with the Si substrate by capturing or emitting charge carriers. The amount of charge captured by the fast states is a function of the surface potential and therefore a function of the gate voltage. The slow states are located in the oxide within a short distance from the interface. The charge carriers can tunnel through the oxide. Thus the tunneling time constant is the time constant for the slow state to charge up or discharge. The tunneling time constant increases exponentially with the tunneling distance.

The charge pumping method uses a measurable substrate current due to the recombined trapped charge induced by repeatedly pulsing the gate from accumulation to inversion to characterize interface states in MOSFETs. This method does not rely on admittance measurements, and is well suited for use on small transistors. A mean interface trap density representative of values between flatband and threshold is determined according to measured charge pumping current as a function of gate pulse frequency. A distribution of interface trap density between flatband and threshold can

also be obtained by measuring charge pumping current as a function of gate pulse rise and fall times.

The main advantage of the charge pumping measurement is that the measurements are done on the actual transistor without needing a separate test device. The results of this technique are relatively more precise and can be used to obtain quick results in a simple experiment or detailed results with sophisticated modifications. The sensitivity of this technique permits the measurement on small geometry transistors present in modern VLSI technology.

A model describing the behavior of both slow and fast states has been developed [24-27]. From Shockley-Read-Hall (SRH) statistics, the occupancy factor, F, of a trap as a function of time can be described as

$$\frac{dF}{dt} = c_n(E) - F[c_n(E) + c_p(E)]$$

Where  $c_n$  is the capture rate of electrons and  $c_p$  is the capture rate of holes. In this equation, the emission of electrons and holes are neglected because capture processes dominate the charge pumping.

The capture rate of electrons and holes is given by  $c_n = n_s \sigma_n v_{th}$  and  $c_p = p_s \sigma_p v_{th}$ . Here,  $n_s$  and  $p_s$  are surface concentration of electrons and holes,  $\sigma_n$  and  $\sigma_p$  are capture cross section of electrons and holes,  $v_{th}$  is the thermal velocity.

For fast states, the filling fraction, which represents a state's change in occupancy factor during one gate pulse period, is defined as

$$\Delta F_{FS} = F_{\text{max}} - F_{\text{min}} = \frac{\left(1 - e^{-\frac{c_n}{2f}}\right) \left(1 - e^{-\frac{c_p}{2f}}\right)}{1 - e^{-\frac{c_n}{2f} - \frac{c_p}{2f}}}$$

Where  $F_{\text{max}}$  and  $F_{\text{min}}$  are the maximum and minimum value of F during one gate pulse, and f is the gate pulse frequency.

The charge pumping current is obtained as

$$I_{cp}(f) = qAf \int_{E_{low}}^{E_{high}} N_{FS}(E) \Delta F_{FS} dE$$

Here A is the area of the device,  $E_{high}$  and  $E_{low}$  are the maximum and minimum positions in the energy of the Fermi level within the bandgap during one gate pulse. NFS is the density of the fast states.

Apparently, the measured charge pumping current will be roughly a linear function of the signal frequency f, as proved by Fig. 2.3.

#### 2.2.4 Subthreshold Swing (SS)

Another simpler and more convenient interface traps assessment method is the subthreshold swing evaluation [28]. The subthreshold swing, S, is defined as the gate voltage required to vary the subthreshold current  $I_d$  by one decade.

$$S = \frac{\partial V_g}{\partial \log I_d}$$

It can be further simplified as [29]:

$$S = \frac{kT}{q} \ln(10) (1 + C_d / C_i)$$

If there is a large interface state density  $D_{it}$ , an interface state capacitance  $C_{it}=qD_{it}$  is in parallel with  $C_d$ . Consequently,  $C_d$  in the above equation will increase to  $C_d+C_{it}$ .

Thus, the change of subthreshold swing  $\Delta S$  is a direct evidence of the change of interface state density [16]:

$$\Delta S = \frac{kT}{q} \ln(10) \frac{qD_{it}}{C_i}.$$

**Cutoff Region**

Linear Region

Saturation Region

Fig. 2.1. The three regions of a MOSFET.

Fig. 2.2. The CV curve of a MOS capacitor.

Fig. 2.3. The peak current vs. the frequency

### Chapter 3

# Gate Dielectrics Integrity

#### 3.1 Introduction

Driven by the higher performance and circuit density, the scaling of microelectronics continues with gate leakage current and the reliability of gate dielectrics as two critical limiting factors. Due to the characteristics of reliability engineering, it is crucial to use correct physical models, statistics and acceleration factors to extrapolate the device lifetime from the accelerated tests. Thus, accelerated tests and lifetime extrapolations based on those tests must be robust, valid, and performed on statistically significant sample sizes.

#### 3.2 Reliability Engineering Basics

#### 3.2.1 Definitions and Basic Concepts

Reliability: The probability that a component will perform a specific function under specific conditions for a specific period of time.

Thus, the objectives of reliability engineering are to meet/exceed customer expectations, eliminate reliability concerns prior to qualifications and volume ramp, and allow more aggressive performance without increasing risk of failure.

Several functions are defined before the study of dielectrics reliability. Those functions are commonly used in the field of statistics as well as reliability engineering [30, 31].

Reliability function R(t) is the fraction of population that survives until time t, it is also known as the survival function.

Failure probability function F(t) is the fraction of population that fails before time t. Related with the reliability function, we have F(t) = 1 - R(t).

Probability density function f(t) mathematically describes the number of devices failing between a time interval dt, as shown by  $f(t) = \frac{dF(t)}{dt}$ .

The failure rate  $\lambda(t)$  is defined as the ratio of probability that the failure occurs in this interval divided by the interval length  $\Delta t$ :

$$\lambda(t) = \frac{R(t) - R(t + \Delta t)}{\Delta t R(t)}.$$

Hazard rate or instantaneous failure rate h(t) describes the rate at which a unit is expected to fail, given that it has survived time t.

$$h(t) = \lim_{\Delta t \to 0} \frac{R(t) - R(t + \Delta t)}{\Delta t R(t)} = \frac{1}{R(t)} \frac{-dR(t)}{dt} = \frac{f(t)}{R(t)}.$$

The failure rate  $\lambda(t)$  and hazard rate h(t) are mathematically different, however, they are often used interchangeably in conventional reliability engineering.

#### 3.2.2 Common Reliability Functions and Bathtub Curve

Exponential distribution:  $f(t) = \lambda e^{-\lambda t}$ ,  $\lambda$  is the failure rate.

Weibull distribution:  $f(t) = \left(\frac{\beta}{\eta}\right) \left(\frac{t}{\eta}\right)^{\beta-1} e^{-\left(\frac{t}{\eta}\right)^{\beta}}$ ,  $\beta$  is the Weibull slope and shape parameter,  $\eta$  is the characteristic lifetime.

Lognormal distribution:  $f(t) = \frac{1}{t\sigma\sqrt{2\pi}}e^{-\frac{1}{2}\left(\frac{Ln(t)-Ln(\mu)}{\sigma}\right)^2}$ ,  $\sigma$  is the shape parameter and  $\mu$  is the median time-to-fail.

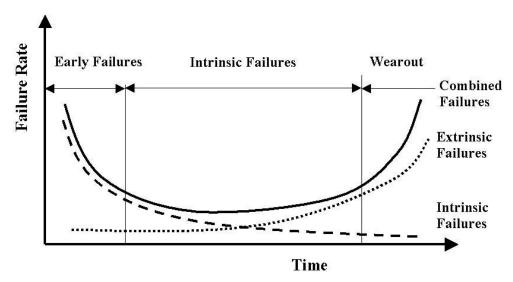

Reliability engineers often describe the lifetime of a population of products using a graphical representation called the bathtub curve, as shown in Fig. 3.1 [30, 32]. The bathtub curve consists of three periods: an infant mortality period with a decreasing failure rate followed by a normal life period (also known as "useful life") with a low, relatively constant failure rate and concluding with a wear-out period that exhibits an increasing failure rate. The bathtub curve failure rate curve is really the addition of two kinds of failure rates: the extrinsic failure rates and the intrinsic failure rates.

The bathtub curve does not depict the failure rate of a single item, but describes the relative failure rate of an entire population of products over time. Some individual units will fail relatively early (infant mortality failures), others will last until wearout, and some will fail during the relatively long period typically called normal life. Failures during infant mortality are highly undesirable and are always caused by defects and blunders: material defects, design blunders, errors in assembly, etc. Normal life failures are normally considered to be random cases of "stress exceeding strength." However, many failures often considered normal life failures are actually infant mortality failures. Wear-out is a fact of life due to fatigue or depletion of materials. A product's useful life is limited by its shortest-lived component. A product

manufacturer must assure that all specified materials are adequate to function through the intended product life.

Note that the bathtub curve is typically used as a visual model to illustrate the three key periods of product failure and not calibrated to depict a graph of the expected behavior for a particular product family. It is rare to have enough short-term and long-term failure information to actually model a population of products with a calibrated bathtub curve.

#### 3.2.3 Accelerated Testing

Why do we need the accelerated testing?

During the technology development, it is hard to quantify the bathtub curve as the time until a failure occurs is over a period of months to years. To solve this problem, we use accelerated testing to simulate the filed use reliability degradation mechanisms. The validity of accelerated testing is based on two assumptions:

- (1) The failure mechanisms can only be quantified if they are observed.

- (2) Accelerated testing is a "clock multiplier" to observe failures in a reasonable time.

The following table shows the common variables and their respective affecting fields in the semiconductor industry [31].

| Variables                   | Affecting fields                      |

|-----------------------------|---------------------------------------|

| Voltage                     | Dielectrics, transistor               |

| Temperature                 | Dielectrics, transistor, interconnect |

| Current                     | Interconnect                          |

| Humidity                    | Packaging                             |

| Mechanical stress/vibration | Packaging                             |

The time-to-failure modeling with accelerated testing is an exact application of accelerated tests. With the help of accelerated testing, the time-to-failure (*TTF*) of a sample can be modeled as

$$TTF = A * \xi^{-N} * e^{-\frac{E_A}{k_B T}}.$$

Here  $\xi$  is the generalized stress, which brings about an irreversible change in the material's properties and causes fails,  $E_A$  is the Arrhenius activation energy, A is a process dependent coefficient, and N is the stress dependent coefficient.

#### 3.3 Ultrathin Gate Dielectric Reliability

#### 3.3.1 Physical Mechanisms of Dielectric Breakdown

There are two categories of oxide failures: the extrinsic and intrinsic failures. The extrinsic failures occur as a result of defects in the oxide or problems associated with the fabrication of the oxide. Those failures tend to occur early in the life of the oxide. They also have a different distribution than intrinsic failures. This can result in a bimodal distribution if the poor quality oxides are included in the accelerated tests. Intrinsic failures are failures due to breakdown in the defect-free oxide. Intrinsic failures determine the true lifetime of a high quality oxide.

The exact physical mechanism of oxide breakdown is still not known [33]. The general idea is that a driving force such as the applied voltage or the tunneling electron current creates defects in the gate oxide. The effects accumulate with time and eventually reach a critical density and trigger a sudden loss of the dielectric properties. Thus the defect generation is critical to understand the mechanisms of

oxide breakdown. Currently, there are three main theories established for the defect generation, the anode hole injection model, the anode hydrogen release model, and the voltage driven model.

Anode hole injection model (AHI)

This model was established on the evidence that tunneling electrons must be the driving force for wearout and breakdown in ultrathin SiO<sub>2</sub>[34, 35]. According to this model, the oxide breakdown is caused by holes injected from the anode. Electrons injected from the cathode into the oxide cause impact ionization events generating holes. Those holes inject back from the anode and trapped in the oxide near the cathode. They will distort the band diagram and increase the electric field near the cathode, and consequently enhance the electron tunneling current. In the direct tunneling regime, which is the dominating tunneling process with ultrathin gate oxides, the energy of the tunneling electrons is proportional to the applied gate voltage [36]. When considering a physical process for defect creation in thin oxides, it is important to consider the energy required for such a process to occur. At energies below those required for anode impact ionization, anode hole injection was believed to take place via surface plasma process [36, 37]. This process requires electrons with energies greater than 7 eV for hot hole injection and subsequent trapping.

The AHI model was questioned when the origin of substrate current could be linked to physical mechanisms other than tunneling holes. These mechanisms include generation recombination processes in the substrate and photo excitation processes due to photons generated by energetic electrons in the gate region[38, 39]. However, recent experimental evidence and modeling have demonstrated that AHI can indeed

be operative in ultrathin oxides at low gate voltages. It is showed that bulk defect generation is increased significantly and  $Q_{bd}$  decreased for devices with lightly doped  $n^+$  polysilicon gate electrodes[10].

#### Anode hydrogen release model (AHR)

There is evidence for a defect generation mechanism involving the release of atomic hydrogen from the anode by energetic tunneling electrons [40]. It has been know that hydrogen can induce a number of defects in silicon dioxide films by internationally exposing MOS devices to hydrogen [41-43]. A trap creation process attributed to the release of atomic from the Si/SiO<sub>2</sub> interface has been shown to have a threshold voltage of approximately 5.0 V [40]. This process has been shown to continue at the voltage as low as 1.2 V, which includes the regime of circuit operating voltages. There is evidence for hydrogen involvement in defect generation and breakdown. It was shown that exposure of bare SiO<sub>2</sub> films to atomic hydrogen radicals, in the absence of any electric field, will produce electrically active defects essentially identical to those produced by electrical stress or radiation.

The primary argument against the hydrogen release model for oxide breakdown is the observation that  $Q_{bd}$  does not appear to improve if an isotope of hydrogen is used to passivate the Si/SiO<sub>2</sub> interface [44]. It has been reported that deuterated oxide film has suppressed hydrogen desorption from the interface with silicon and consequently improved immunity to interfacial trap generation due to hot carrier injection.

#### E model

Different from the AHI and AHR models, which are current driven, the E model suggests that the electrical field drives the defect generation and current flowing through the oxide plays a second role at most. This model considers the interaction of the electrical field with the dipole moments associated with oxygen vacancies in the  $SiO_2$ . The dipole and electric field interaction reduces the activation energy for the Si-Si bond breakage. The oxygen vacancy is the breakdown precursor. The E model assumes that the tunneling currents play no role in breakdown and the acceleration factor is constant independent of field electric field or gate voltage. The activation energy required to break the bond is reduced by the dipolar energy, leading to a quantitative prediction for the field dependence of the activation energy for dielectric breakdown, which agrees well with experiments. The distribution of energies of the weak bonds could account for a wide range of observations of the temperature and field dependence of  $SiO_2$  breakdown times, since the defect which dominates the breakdown process may change depending on stress conditions [45].

The E model was hypothesized based on an electric field driven defect generation process that yielded the same observed dependence of oxide lifetime on electric field [46]. This model known as the E model indicated that the applied electric field interacts with the weak Si-Si bonds associated with oxygen vacancies in the amorphous  $SiO_2$  film. The applied electric field eventually breaks the weak bond and creates a permanent defect or trap. This defect is referred to as the E' center, which is a structure in the  $SiO_2$ , having an unpaired electron localized on a silicon atom, which

is bonded to three oxygen atoms. Tunneling electrons are not necessary in the E model to create defects.

The E model has attained widespread acceptance. However, the exponential dependence on field is not proof of the validity of the particular physical model. As the SHEI experiment pointed out that the charge to breakdown  $Q_{bd}$  is strongly dependent on the substrate bias, even though the oxide field is fixed. Therefore  $Q_{bd}$  is correlated with the electron energy not the electric field.

# 3.3.2 Dielectrics Stress Methodologies

In order to predict the lifetime of devices correctly, proper accelerated stress tests are needed. Depending on the process technologies and test goals, three stress methods are commonly used in accessing the oxide reliability [47].

## Constant Voltage Stress (CVS)

The constant voltage stress (CVS) is popularly used during the sample stresses. In this method, a constant stress voltage is applied to the device gate or substrate, and the current vs. time (I-t) characteristics are recorded. The oxide breakdown is characterized by a sudden increase of the current (hard breakdown), or when the gate current noise exceeds a specified current noise level, which corresponds to a soft breakdown event (soft breakdown). This breakdown is characterized by distribution parameters, thus a sufficient sample size is required to determine those parameters accurately. At a fixed stress voltage,  $T_{bd}$  and  $Q_{bd}$  decrease with oxide thickness; therefore it is used often with ultrathin oxides tests.

#### Ramp I-V

In a ramp I-V the gate voltage is increased rapidly from zero until a sudden increase in the gate leakage current is measured. In this measurement, the breakdown is monitored as a function of gate bias from which a breakdown field is determined. In principle different failure modes can be detected with this method. This method is beneficial for extrinsic distribution, and improves resolution.

#### Constant Current Stress (CCS)

Constant current stress (CCS) is another popular stress method. As stated by the name, a constant current is applied to the device, and the voltage vs. time characteristics (V-t) is recorded. It is found that the charge to breakdown,  $Q_{bd}$  is stress current dependent, and for a fixed stress current,  $T_{bd}$  and  $Q_{bd}$  increase strongly for ultrathin oxides. Therefore, this method is often used in thicker oxides.

$$Q_{bd}$$

VS  $T_{bd}$

$Q_{bd}$  and  $T_{bd}$  are two breakdown parameters critical to the gate oxide breakdown study.  $Q_{bd}$ , defined as the time integrated current density that flows through the oxide until breakdown occurs is a physically meaningful quantity. However, the quantity of interest for an electronic component is the failure rate derived from the lifetime or time-to-breakdown,  $T_{bd}$ . For a constant voltage stress,  $\int\limits_0^{T_{BD}} J dt = Q_{BD}$ , where J is the instantaneous value of the current density [48]. For ultrathin oxides, the current is nearly constant until breakdown (in remarkable contrast to thicker oxides), therefore  $T_{BD} = \frac{Q_{BD}}{J}$ . Therefore  $T_{bd}$  and  $Q_{bd}$  will yield comparable result with ultrathin oxide breakdown.

# 3.3.3 Lifetime Extrapolation Models

#### E model

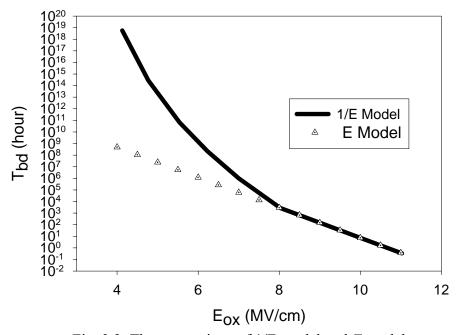

E model is an empirical model for breakdown developed by observing the electric field dependence of TDDB data [49, 50]. When the logarithm of the time-to-failure was plotted against applied electric field, a straight line was observed, i.e.  $t_{BD} \propto e^{-\gamma E}$ , where E is the electric field and  $\gamma$  is the electric field acceleration factor. Acceleration parameters for the electric field and temperature could be extracted from the model to allow extrapolation of oxide lifetime from accelerated stress conditions. 1/E model

The 1/E model is a popular breakdown model with ultrathin oxides. According to this model, a fraction of electrons entering the anode have sufficient energy to create hot holes that are injected back into oxide. The injected holes will generate defects in the oxide, and breakdown occurs when a critical hole fluency is reached. According to the 1/E model, the acceleration factor increases at smaller  $E_{\rm ox}$ .

1/E model was proposed based on anode hole injection [35, 51]. In this case, tunneling electrons (based on FN tunneling) transferred energy to holes in the anode, where they are injected into the oxide film. An earlier version of the model was based on a feedback mechanism where injected holes became trapped and modified the oxide potential barrier to enhance additional electron injection. Eventually, the positive feedback process caused a current runaway leading to breakdown. In this case, the time-to-failure was proportional to the inverse of applied electric field, i.e.  $t_{BD} \propto e^{\beta E}$ , where  $\beta$  is the electric field acceleration factor. The reciprocal field dependence is a consequence of the FN tunneling current, which is the driving force

for the defect generation. At higher voltages (~9 V), holes can be generated in the oxide by impact ionization processes and subsequently trapped, leading to breakdown.

Both the E model and the 1/E model assumed a temperature dependence of the form  $t_{BD} \propto e^{\frac{E_a}{kT}}$ ; where  $E_a$  is referred to as the thermal activation energy, k is Boltzmann constant, and T is the absolute temperature.  $E_a$  is due to different physical processes depending on the model assumed. In the E model, Ea is related to the enthalpy of activation for oxide breakdown or it is related to the temperature dependence of the hole generation coefficient and the slope of the FN tunneling characteristic in the 1/E model [52].

## The Unification of E and 1/E model

The prediction of E model and 1/E model is quite different at the low electric field. However, this cannot be verified by direct test since  $T_{bd}$  is extremely long with such low fields. In recent years, there have been efforts to unify these two models. First, it is shown that the field enhanced bond breaking and hole generation and trapping process coexist and degrade oxide. At high fields 1/E and at low fields E model prevails [53]. Another research pointed out that the dominant carriers were different at different fields. At high fields, the holes are the dominant factor and electrons dominate the low fields [54]. Similar results showed that E and E are competing processes, the dominating mechanism depends on precursor mix and hole current density [55]. The molecular physics based complementary model also indicates that field and current induced oxide degradation occur simultaneously if one reaction dominates [45].

## Voltage driven model

The validity of an electric field driven model becomes questionable after the observation of results from substrate hot electron injection experiments and the thickness and polarity dependence of ultrathin gate oxide breakdown. A thermochemical wearout process should only be related to the magnitude of the electric field and the length of time it is applied to the gate, not to the amount of charge injected. The substrate hot electron injection (SHEI) experiment shows that  $T_{bd}$  is proportional to the inverse of the indicted current density [23]. Other experiments were conducted where changing the polysilicon gate doping while maintaining a fixed gate voltage can modulate the electric field [10, 56]. The results show that the lifetime is nearly independent of polysilicon doping, which is contradictory to the electric field driven model.

Even though the voltage driven model is accepted as the correct model for the ultrathin gate dielectrics, there is a still question that how to extrapolate the device lifetime based on the accelerated tests.

At first an exponential law was suggested as

$$T_{bd} \propto \exp(\gamma V_g)$$

Here  $\gamma$  is the stress voltage acceleration factor.

However, it is found that  $\gamma$  is not constant for different  $V_g$ , even for the same oxide thickness [57]. The measured  $T_{bd}$  and  $Q_{bd}$  at lower voltages are much higher than expected from the exponential law extrapolation based on high voltage data and there is a systematic concave line up of the data, leading to higher  $\gamma$  at lower voltages [57, 58].

To solve this problem, an empirical power law is established as

$$T_{bd} \propto V_g^{-n}$$

Based on the experimental data, n~44 is extrapolated. However, it is difficult to explain with a simple physical process. Recently, the multiple hydrogen release model is used to explain the power law dependence [59, 60]. However, it is still too early to draw conclusions.

#### 3.4 Statistics and Percolation Theory of Breakdown

Projection of dielectric lifetime of a product from data collected by stressing test devices under accelerated test conditions requires a number of correct models and assumptions. The voltage and temperature must be accurately extrapolated from the accelerated test conditions. Scaling from the area of the test structure to that of the product must be performed with the proper model. Finally, the choice of the failure distribution must be correct, especially, since the 100 ppm level is usually specified requiring accurate estimation of the low failure rate tails.

Lognormal statistics have been used for some time to fit reliability data from accelerated life tests to induce various failure mechanisms such as electromigration and oxide breakdown [61-64]. There has been discussion concerning the validity of lognormal statistics for thin oxide breakdown. Although lognormal statistics may fit failure data over a limited sample set, it has been demonstrated that the Weibull distribution more accurately fits large samples of TDDB failure data, particularly, at lower failure rates. More importantly, lognormal statistics does not predict the observed area dependence of  $T_{bd}$  for ultrathin gate oxides. Furthermore, the Weibull

shape parameter  $\beta$  is experimentally observed to decrease as the oxide thickness is decreased. The model based on percolation theory has been proposed to explain the oxide thickness dependence of  $\beta$  and how it relates to  $N_{bd}$ , the number of defects at breakdown.

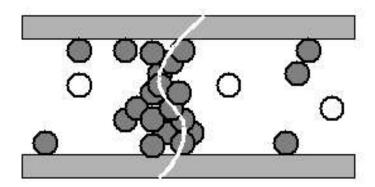

According to the percolation theory, the defects are generated randomly throughout the gate oxide film. As the defects generation continues, the defect density increases. When the defect density reaches a critical value  $N_{bd}$ , the defects will connect each other and finally can connect the both edges of the oxide film, which leads to the breakdown of the oxide. If this is true, the thinner oxide will have a lower critical defect density, and a larger area device will have a larger probability to have a conduction path with the same oxide thickness and defect density. In this way, the area dependence of the breakdown can also be explained.

The  $N_{bd}$  will decrease with decreasing oxide thickness. As the oxide thickness scaling down, one defect will be enough to create the breakdown path, which means that  $N_{bd}$  becomes constant instead of decreasing with thinner oxide.

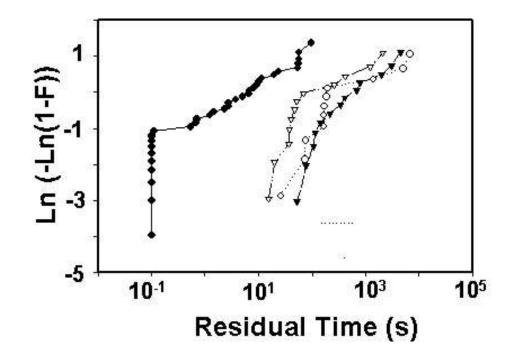

The statistics of gate oxide breakdown are described using the Weibull distribution  $F(x) = 1 - e^{-\left(\frac{x}{\alpha}\right)^{\beta}}$ , where F is the cumulative failure probability; x is either the charge or time to breakdown. The characteristic life  $\alpha$  is the 63.2% lifetime, and  $\beta$  is the slope parameter or Weibull slope. Plotting  $W \equiv Ln[-Ln(1-F)]$  against Ln(x) yields a straight line with slope  $\beta$ .

The gate oxide failure is a weakest-link type of problem because failure of the whole chip is defined by the failure of the first individual device, and a device fails if

any small portion of the gate area of the device breakdown. From statistics, if the probability of any one unit failing is p then the probability of any one of N independent units failing is

$$F = 1 - (1 - p)^N$$

,

So that

$$Ln[-Ln(1-F)] = Ln(N) - Ln[-Ln(1-p)].$$

As predicted by the percolation model, the value of  $N_{bd}$  will decrease with thinner oxide thickness, showing by the wider failure distribution and smaller  $\beta$ .

The Weibull plot thus has the extremely useful property that if the area is increased by a factor N then the curve shifts vertically by Ln(N). If the desired low failure rate is  $F_{chip}$  over the product lifetime  $T_{life}$  for the total gate area  $A_{ox}$  on the chip, this is equivalent to a higher failure rate  $F_{test}$  in time  $T_{test}$  on the test structures with area  $A_{test}$ . Then we get

$$\frac{T_{life}}{T_{test}} = \left(\frac{A_{test}}{A_{ox}}\right)^{\frac{1}{\beta}} \left(\frac{Ln(1-F_{chip})}{Ln(1-F_{test})}\right)^{\frac{1}{\beta}} \approx \left(\frac{A_{test}}{A_{ox}} \frac{F_{chip}}{F_{test}}\right)^{\frac{1}{\beta}}.$$

The assumption in the above equation is that  $\beta$  is independent of  $V_g$ . This equation is used to scale measured breakdown times to the expected product lifetime, or equivalently to estimate the chip failure rate from test structure measurements. Since  $F_{chip}$  is less than  $F_{test}$ , and  $A_{test}$  is typically less than  $A_{ox}$ , then  $T_{test}$  is larger than  $T_{life}$ . So it is always necessary to use accelerated stress conditions. Thus it is important to understand the voltage dependence and is also reason so much attention is paid to the physical model for trap generation and breakdown.

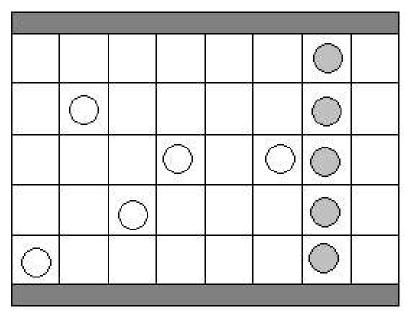

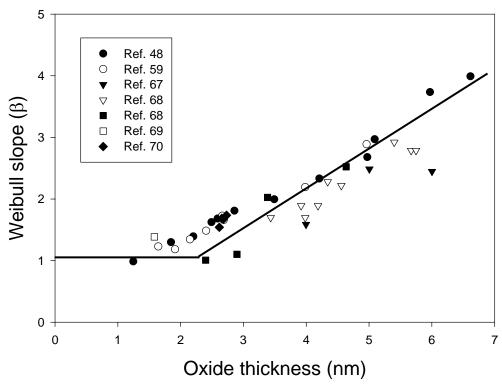

Another key characteristic of the percolation theory is the relationship between the Weibull distribution slope  $\beta$  and the oxide thickness  $t_{ox}$ . With a thicker oxide,  $\beta$  becomes lager. Many papers are published to establish this relationship [48, 65, 66]. With the help of Fig. 3.3, a simple model can be used to explain this.

The bulk oxide can be considered as a lattice structure with a characteristic length  $a_0$ . Thus if the oxide area is A, the number of column is  $N=A/a_0^2$ . With the similar definition, the number of cells in one column is  $n=t_{OX}/a_0$ .

Assume  $\lambda$  is the fraction of defective cells, the cell cumulative failure distribution is then given as

$$F_{cell} = \lambda$$

.

If all the cells in one column are fail, the column will fail. Thus the failure distribution of the column is

$$F_{cell} = \lambda^n$$

.

as

Since the oxide breakdown is a weakest-link issue, the device failure distribution and the Weibit, W are given as

$$F = 1 - \left(1 - \lambda^n\right)^N$$

$$W = Ln[-Ln(1-F)] = Ln[-NLn(1-\lambda^n)]$$

Since  $\lambda$  usually is much less than 1, the above equation can be further simplified

$$W = Ln[-NLn(1-\lambda^n)] \approx Ln(N) + nLn(\lambda).$$

Compared with the original model of the percolation theory, n is corresponding to the Weibull distribution slope  $\beta$ . Thus the relationship between the oxide thickness  $t_{ox}$  and  $\beta$  is established as

$$\beta = \frac{t_{OX}}{a_0} \tag{a}$$

In this way, as the oxide thickness continues shrinking,  $\beta$  will approaches to unit  $t_{ox}$  as is equal or less than  $a_0$ .

Fig. 3.4 shows the published data of the Weibull slope  $\beta$  as a function of oxide thickness [48, 59, 67-70]. There are two characteristics of this figure. First, the Weibull slope  $\beta$  has a linear relationship with the oxide thickness if the oxide thickness is thicker than about 2 nm, which can be explained well by equation (a). Second, as the oxide thickness continues shrinking,  $\beta$  approaches unit. The reason for this is also very clear since one defect would cause the failure of the entire gate oxide, as the defect size is equal or smaller than the oxide thickness.

It should be mentioned that although the percolation theory can predict the statistical behavior of breakdown well, the parameters extrapolated from it might not correspond to the real physical mechanisms. For example, the defect size extrapolated form it may not be the real physical dimensions. As we know, the defect generation inside the oxide is not uniform. There are more defects near the interface and source and drain region. However, percolation theory and the Weibull distribution are more reasonable and intuitive compared with other theories. At the same time, even though this theory was developed for the SiO<sub>2</sub>, it is still applicable to the other gate dielectrics. However, when the high-*k* dielectrics are used, an interfacial layer is

always inserted between the silicon substrate and the gate bulk oxide. Thus, even for the same structure, the Weibull slope will be quite different depends on the breakdown occurs at the bulk oxide or the interfacial layer. At the same time, the critical oxide thickness when  $\beta$  approaches unit will also be different, depending on the exact physical structures of the defect. Further study in this area is still needed[71, 72].

Fig. 3.1. The bathtub curve of the product lifetime.

Fig. 3.2. The comparison of 1/E model and E model.

Fig. 3.3. The cell based percolation theory.

Fig. 3.4. The relation ship between Weibull slope and the oxide thickness.

# Chapter 4:

# Negative Bias Temperature Instability

## 4.1 Introduction

In the modern semiconductor industry, statistical physics and the physics of understanding how complex systems interact will become increasingly important especially as we enter the era of megascale integration and SOC IC production. This is especially true for variance and defect interactions that become magnified when investigating the electrical output characteristics as device geometry shrinks [73].

For the next generation of SOC and IC products, there is a new barrage of challenge for us to overcome[74, 75]. Those challenges have critical impact on product yield, product reliability, chip testability/performance prediction, and understanding of the process integration. Among the key problems affecting the semiconductor industry are Negative Bias Temperature Instability (NBTI), gate oxide leakage current, power consumption, etc. As devices are scaled and the density on chip increases, the probability of a circuit encountering lethal accelerated NBTI degradation increases. Hence, the impact of NBTI on yield is expected to increase as SOC complexity and integration increase.

#### 4.2 Static NBTI

# 4.2.1 Degradation Phenomena

pMOSFETs suffer NBTI when stressed with negative gate voltages at elevated temperatures. The typical stress condition of NBTI is 100-250 °C and less than 6 MV/cm oxide electrical fields. A higher electrical field will lead to hot carrier degradation. This stress condition is typical during the burn in. However, it is also approached in high performance ICs during the routine operation. Fig. 4.1 shows the trend in electric fields for CMOS circuits, showing that oxide electrical fields of the magnitude to generate NBTI are typical in today's circuits[76].

The main characteristics of NBTI are decreases of drain current  $I_{on}$  and transconductance  $g_m$ , and the absolute off current  $I_{off}$ , and threshold voltage  $V_{th}$  increase. The threshold voltage  $V_{th}$  and flatband voltage  $V_{fb}$  of a MOSFET are given by (1) and (2) respectively [15].

$$V_{th} = V_{FB} - 2\phi_F - \frac{|Q_B|}{C_{cor}}$$

$$V_{fb} = \phi_{MS} - \frac{Q_f}{C_{ox}} - \frac{Q_{it}(\phi_s)}{C_{ox}}$$

The fixed oxide charge  $Q_f$  and the interface-trapped charge density  $Q_{ii}$  are the two factors determine the threshold voltage shift. Positive increases in them will lead to the negative threshold voltage shift.

$$\Delta V_{th} = -\frac{\Delta Q_{it}(\phi_s)}{C_{OX}} - \frac{\Delta Q_f}{C_{OX}}$$

During the NBTI degradation, the threshold voltage will shift to the negative direction, thus either the interface traps or the fixed oxide charges will change during the NBTI stress.

The simplest form of the driving current  $I_{on}$  and transconductance  $g_m$  of a MOSFET are given as

$$I_{on} = \frac{W}{2L} \mu_{eff} C_{ox} (V_g - V_{th})^2$$

$$g_{m} = \frac{W}{L} \mu_{eff} C_{ox} (V_{g} - V_{th})$$

As shown by those two equations, the parameters leading to  $I_{on}$  and  $g_{m}$  degradation are the threshold voltage shift and the mobility  $\mu_{eff}$  change. The mobility degradation mainly comes from the interface trap generation, leading to additional surface-related scattering.

NBTI mainly occurs to pMOSFETs and appears to be negligible for positive gate voltage and for either positive or negative gate voltages in nMOSFETs as shown in Fig. 4.2.

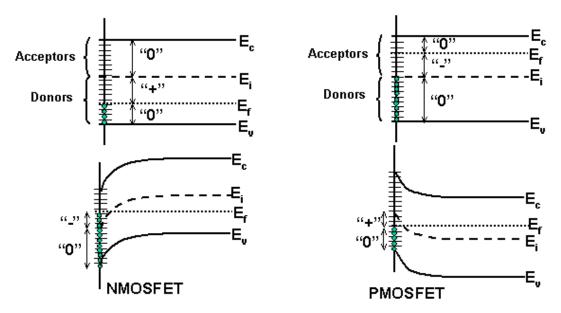

The reason of this phenomenon can be well explained by the interface traps behavior of nMOSFETs and pMOSFETs. An interface trap in MOSFETs is an interface trivalent Si atom with an unsaturated valence electron at the SiO<sub>2</sub>/Si interface, denoted by  $Si_3 \equiv Si^{\bullet}$ . The  $\equiv$  represents three complete bonds to other Si atoms and the \* represents the fourth, unpaired electron in a dangling bond.

Interface traps are electrically active defects with an energy distribution throughout the Si band gap. Acted as generation/recombination centers, they contribute to low frequency noise, leakage current, and reduced mobility, drain

current, and transconductance. Once occupied by electrons or holes, the device threshold voltage will shift by equation (1).

Interface traps act as acceptor-like or donor-like depending on their relative position to the band gap [77]. Acceptor-like interface traps are neutral when they are empty and negative when occupied by electrons. Donor-like interface traps are positive when they are empty and neutral when occupied by electrons. Depending on its relative position to the Fermi energy level, an interface trap will be occupied by an electron or empty.

As shown by Fig. 4.3, at flatband condition electrons occupy the states in the lower half of the band gap, and those traps are neutral. Those between mid gap and the Fermi energy are negatively charged since they are occupied acceptor states. Those above the Fermi level are unoccupied acceptors states and they are neutral. For a pMOSFET device, the fraction of interface traps between mid gap and the Fermi level is unoccupied donors, when the device is in inverted state. Those interface traps are positively charged, thus leading to the negative threshold voltage shift in a pMOSFET.

Since the interface traps are acceptors in the upper half of the band gap and donors in the lower half of the band gap, they affect the threshold voltage shift in nMOSFET and pMOSFET differently. At flatband condition, the interface trap charge in nMOSFET is positive and in pMOSFET is negative. At inversion condition, the interface trap charge is negative in nMOSFET and positive in pMOSFET. However, the fixed oxide charge is positive, thus at inversion nMOSFET:  $Q_f - Q_{it}$ , pMOSFET:  $Q_f + Q_{it}$ . Hence the pMOSFET is more vulnerable to NBTI stress [78].

#### 4.2.2 NBTI Mechanisms

After first been studied by Deal [79], NBTI has been a hot spot and many models for the physical mechanisms have been established. Among those models, holes injected into the oxide, tunneling electrons and electrochemical reactions were the main subjects.

# Hole trapping model

The hole trapping model is based on avalanche hole injection measurements on unstressed MOS capacitors and the NBTI tests[80-82]. This model proposes that the negative midgap voltage shift, which is believed to be a measure of the change of positive oxide charge without the contribution from interface states, is due to the filling of intrinsic hole traps. All the positive charge generated by preceding negative bias stress can be removed by the positive bias stress. But the exact mechanism for hole injection into the oxide is still unknown.

# Thermally assisted electron tunneling model

The thermally assisted electron tunneling model was established by Breed[83, 84]. According to this model, the neutral or positive centers, which cause the charge trapping, are located near the interface in the oxide. Under negative bias stress, the centers are excited. The electrons in the excited states then tunnel into empty states of the conduction band of the silicon. This process is a thermally assisted tunneling process.

#### Reaction-Diffusion model

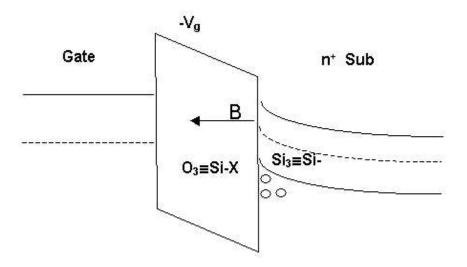

Several authors proposed the electrochemical reaction model, or the Reaction-Diffusion model, which has been accepted by many researchers in recent years [8588]. This model explains the NBTI effect in terms of electrochemical reactions. Fig. 4.4 shows the schematic diagram of this model.

Basically, there are two reactions in this model.

$$Si_3 \equiv Si - X + A \iff Si_3 \equiv Si^* + B$$

$$O_3 \equiv Si - X + C + p^+ \Leftrightarrow O_3 \equiv Si^+ + B$$

$$B_{interface} \Leftrightarrow B_{bulk}$$

(Diffusion)

Here, Si3≡Si-X is a trivalent silicon, a defect near the interface. X, A, B, and C are unknown neutral species. Si3≡Si• is a neutral trivalent silicon backboned by three other silicon atoms, functioning as an interface trap near the interface. O3≡Si+ is a positively charged species, serving as a positive charge in the oxide.

The first reaction accounts for the interface trap generation. The trivalent silicon reacts with A and produces the interface trap and B. There are different definitions for A and B. Some suggest A as a hydrogen ion and B a hydrogen atom. But there are also some suggestions in different ways. The second reaction is for the fixed oxide charge generation reaction. There are a number of suggestions for the C species as well. The diffusion of the product B would produce the phenomenon of NBTI. There are also some other variant electrochemical reaction models, which explain the NBTI effect with one electrochemical reaction. It is clear that regardless of mechanism, holes certainly play an important role in the NBTI effect.

#### 4.2.3 Device Lifetime Extrapolation

In order to precisely predict the lifetime of the device experienced NBTI degradation, a correct model is needed. Generally, a threshold voltage shift  $\Delta V_{th}$  caused by NBTI can be expressed as

$$\Delta V_{th} = A f_1(t) f_2(V_g) \exp\left(\frac{-E_a}{kT}\right).$$

Here  $f_1$  and  $f_2$  are functions account for the time dependence and gate voltage dependence.

Based on the physical mechanisms and experimental data, several models for the time dependence have been suggested.

Logarithmic time dependence

$$\Delta V_{th} = ALog(t)$$

This model was established on the ideal of charge trapping, wherein carriers tunnel into existing traps[79]. According to this model, the NBTI is field accelerated, and there is little or no temperature activation. The saturation behavior is due to the finite trap density. There is significant deviation at long time when using this model. However, it is frequently observed in recent high-*k* gate dielectrics experiments.

Exponential time dependence

$$\Delta V_{th} = A \exp\left(\frac{t}{\tau}\right)$$

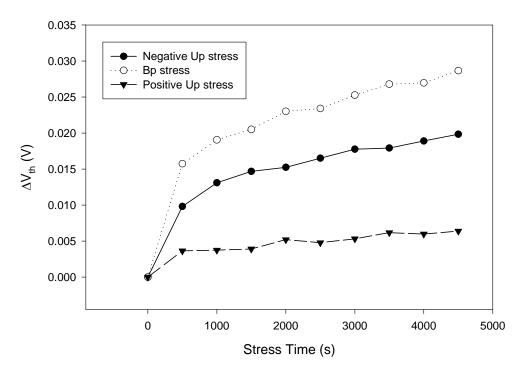

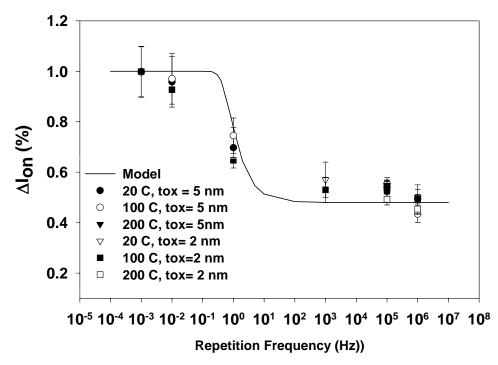

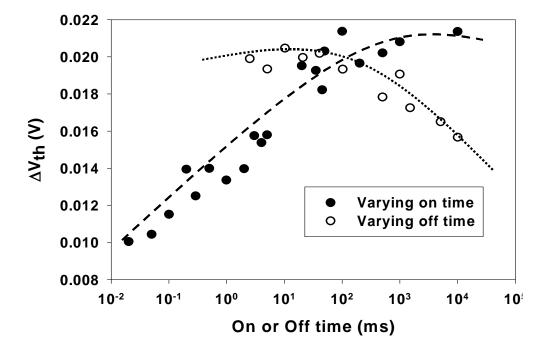

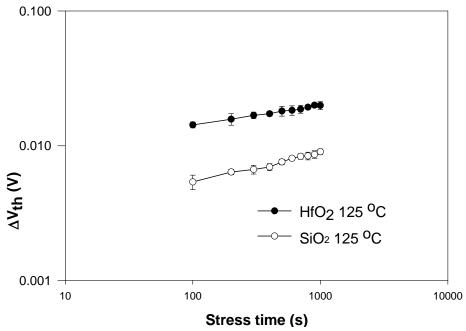

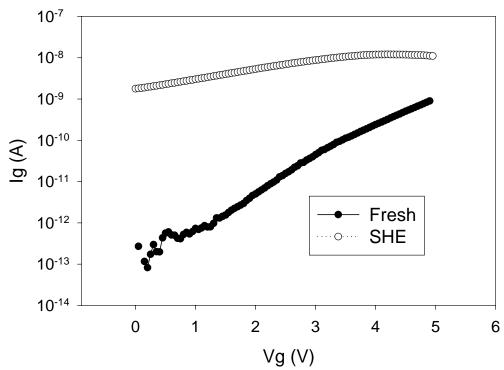

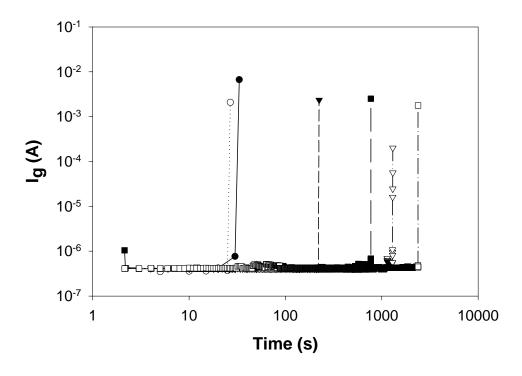

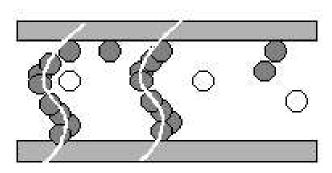

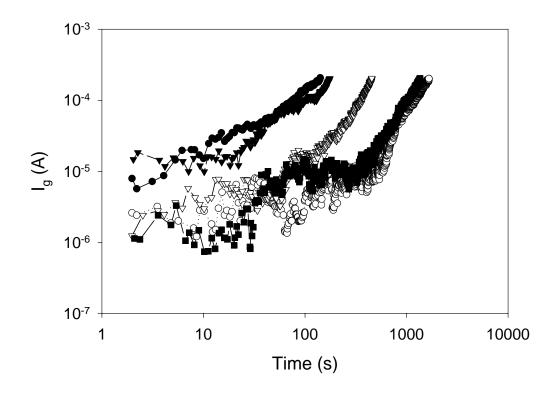

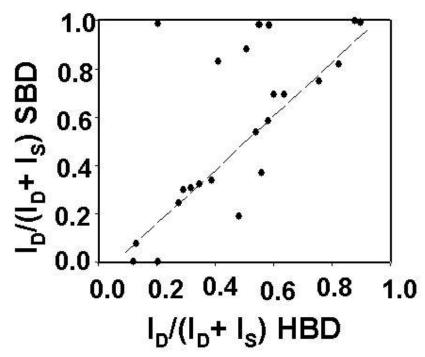

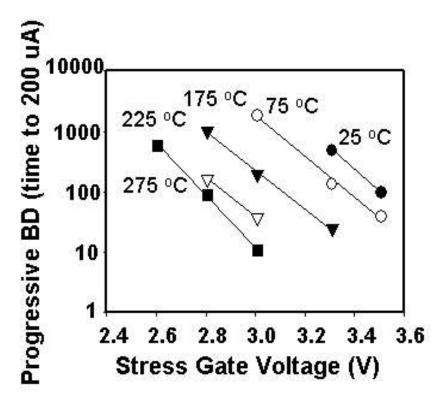

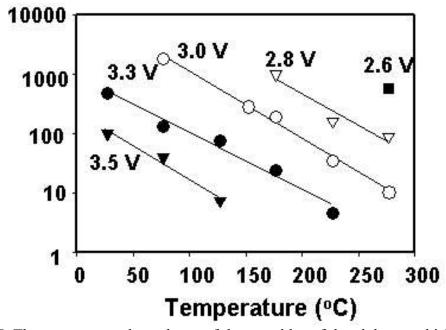

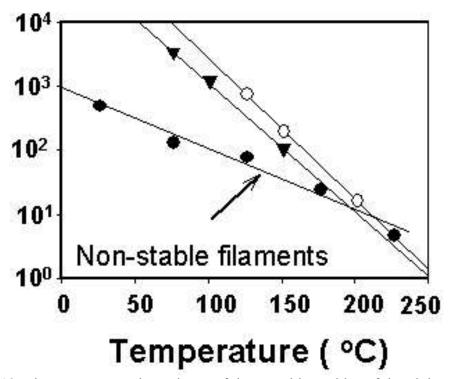

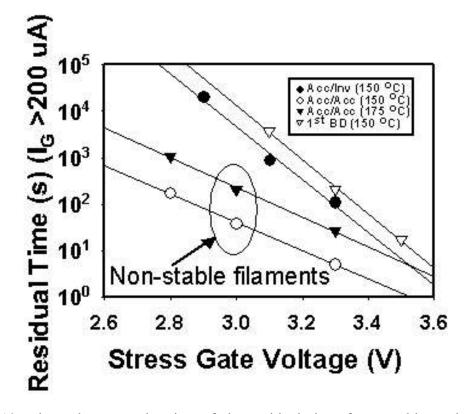

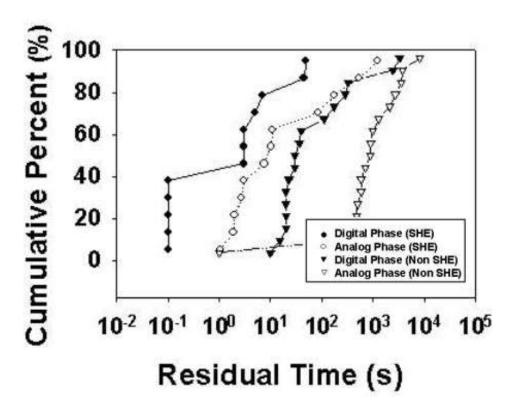

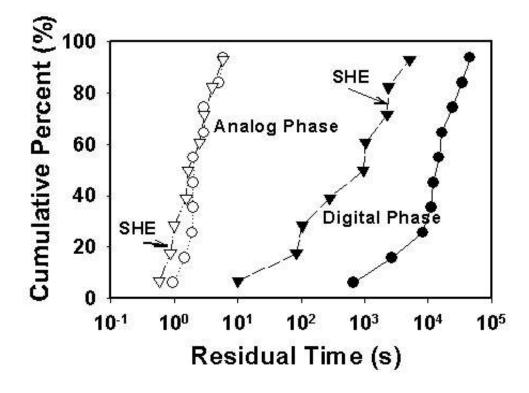

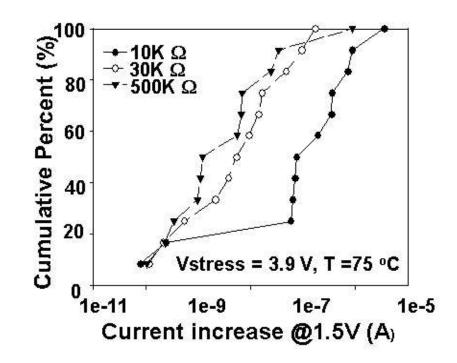

$$\Delta V_{th} = A \exp\left(\frac{t}{\tau_1}\right) + B \exp\left(\frac{t}{\tau_2}\right)$$