#### ABSTRACT

| Title of Dissertation:    | ANALOG SYSTEM-ON-A-CHIP WITH<br>APPLICATION TO BIOSENSORS.         |

|---------------------------|--------------------------------------------------------------------|

|                           | Angela M. Hodge, Doctor of Philosophy, 2005                        |

| Dissertation Directed By: | Professor, Robert W. Newcomb, Electrical<br>Engineering Department |

This dissertation facilitates the design and fabrication of analog systems-on-achip (SoCs). In this work an analog SoC is developed with application to organic fluid analysis. The device contains a built-in self-test method for performing on-chip analysis of analog macros. The analog system-on-a-chip developed in this dissertation can be used to evaluate the properties of fluids for medical diagnoses. The research herein described covers the development of: analog SoC models, an improved set of chemical sensor arrays, a self-contained system-on-a-chip for the determination of fluid properties, and a method of performing on-chip testing of analog SoC sub-blocks.

### ANALOG SYSTEM-ON-A-CHIP WITH APPLICATION TO BIOSENSORS

By

Angela Marie Hodge

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2005

Advisory Committee: Professor Robert W. Newcomb Chair Professor Mona Zaghloul Professor Martin Peckerar Professor Carlos Berenstein Professor Reza Ghodssi

© Copyright by

Angela M. Hodge

# Dedication

Jeremiah 29:11 For I know the thoughts I have for you says the Lord: thoughts of PEACE (SHALOM) and not of evil to give you an expected end. (KJV)

"For I know the plans I have for you," declares the LORD, "plans to prosper you and not to harm you, plans to give you hope and a future." (NIV)

# Lord Jesus,

I thank you for your thoughts, your peace, your mercy, and your strength.

To Robert Spencer and Carolyn Van Hodge, I couldn't imagine better parents. Thank you, you are a blessing to us.

To Dr. Robert W. Newcomb, Thank you for your help, and excellence in advising me.

# Acknowledgements

The author wishes to thank Dr. and Mrs. Robert Fischell for founding the Fischell Fellowship for biomedical engineering research and for funding this research and dissertation.

The author also acknowledges the MOSIS educational program which provided free fabrication of integrated circuits designed in this dissertation. This dissertation, therefore, acknowledges the organizations that jointly funded the MOSIS educational program: MOSIS, AMIS, and IBM.

The work in this dissertation began as a collaborative effort with The University of Maryland's Electrical Engineering Department, Microsystems Laboratory (Dr. Robert W. Newcomb and Angela Hodge), The George Washington University (Drs. Mona Zaghloul and Sharokh Ahmadi), and The United States Naval Academy (Dr. Louisa Sellami).

In 2000, through employment at the National Institute of Standards and Technology, Electronics and Electrical Engineering Laboratory, Semiconductor Electronics Division, Hodge expanded the research through the use of the division's microelectronics fabrication facility. Hodge wishes to thank Russell Hadjay for the numerous hours of processing facility training she received to further the efforts of this dissertation. This dissertation also acknowledges the efforts of the student co-op from The George Washington University, Onur Tigli, in instituting some of the device layout.

This dissertation also acknowledges worked performed through employment and collaboration with the Naval Research Laboratory's (NRL): Code 6800, Electronics Science and Technology Division and Code 6900, Center for Biomolecular Science and Engineering. The work performed in this dissertation, relevant to these NRL entities includes the analysis of the gateless field effect transistor (macromolecular sensor). Particular acknowledgement is made to EOIR contractor, Stephanie Fertig, for training Hodge received in performing linker chemistry and for efforts made by Fertig and Dr. Leonard Tender to perform the surface chemistry through which DNA sensitivity was achieved. Additional acknowledgement is made to NRL employees, F. Keith Perkins and Martin Peckerar for the use and design of test equipment and procedures for macromolecular sensor testing and for the use of their fabricated macromolecular sensors.

# Table of Contents

| Dedication                                                                    | ii   |

|-------------------------------------------------------------------------------|------|

| Acknowledgements                                                              | iii  |

| Table of Contents                                                             | v    |

| List of Tables                                                                |      |

| List of Figures                                                               |      |

| Chapter 1 Introduction                                                        | 1    |

| Section 1.1 Motivation for the Research                                       | 1    |

| Section 1.2 Statement of Proposed Problem                                     | 4    |

| Section 1.3 Outline of the Methodology                                        | 6    |

| Subsection 1.3.1 Multi-Sensor System Architecture                             | 6    |

| Subsection 1.3.2 Testbench-on-a-Chip Methodology                              | 7    |

| Subsection 1.3.3 Biosensor Systems                                            | 8    |

| Section 1.4 Dissertation Contributions                                        |      |

| Chapter 2 Background                                                          | . 14 |

| Section 2.1 Overview                                                          | 14   |

| Section 2.2 System-on-a-Chip (SoC) Technology                                 | . 15 |

| Section 2.3 Built-In Self-Test                                                | . 19 |

| Section 2.4 Built In Self Test with Oscillation Test Strategy                 | 24   |

| Section 2.5 SystemC and System-on-a-Chip Modeling                             | 34   |

| Section 2.6 Chemical Field Effect Transistor Biosensors                       |      |

| Section 2.7 Summary                                                           | 68   |

| Chapter 3 Novel Development of an Analog System-on-a-Chip with Built-In Self- |      |

| Test                                                                          |      |

| Section 3.1 Overview                                                          | 70   |

| Section 3.2 Fluid Analyzer SoC                                                | 72   |

| Section 3.3 Analysis and Design of Biosensors for Fluid Testing               | 75   |

| SubSection 3.3.1 VLSI Implementation of Chemical Field Effect Transistor      |      |

| Subsection 3.3.1.1 Hand Calculations for the CHEMFET                          | 77   |

| Subsection 3.3.2 A Gateless Field Effect Transistor                           | 86   |

| Subsection 3.3.2.1 Hand Calculations for Gateless FET                         | . 88 |

| Section 3.4 Oscillation Based Built-In Self-Test (OBIST)                      | . 90 |

| Section 3.5 Development of SoC Models                                         | 109  |

| Subsection 3.5.1 Introduction to SoC Models of Biosensors and the OBIST       |      |

| Method                                                                        | 110  |

| Section 3.6 Summary                                                           | 123  |

| Chapter 4 Results                                                             | 126  |

| Section 4.1 Overview                                                          | 126  |

| Section 4.2 Simulation and Experimental Evaluation of Biosensors              | 127  |

| Section 4.3 Built-In Self-Test Methods                                        | 135  |

| Section 4.4 System-on-Chip Model Outputs                                  |     |

|---------------------------------------------------------------------------|-----|

| Section 4.5 Summary                                                       | 179 |

| Chapter 5 Conclusions and Open Problems                                   | 180 |

| Section 5.1 Overview                                                      |     |

| Subsection 5.1.1 Background in Analog System-on-Chip Devices              |     |

| Subsection 5.1.2 Roadblocks Addressed in This Dissertation                | 181 |

| Section 5.2 Dissertation Results for fluid analyzer Analog System-on-Chip | 183 |

| Subsection 5.2.1 Oscillation Based Built-In Self-Test (OBIST)             | 183 |

| Subsection 5.2.2 Biosensors for Fluid Analysis                            | 183 |

| Subsection 5.2.2.1 VLSI Adaptation of CHEMFET                             | 185 |

| Subsection 5.2.2.2 Evaluation of Gateless Field Effect Transistor         | 186 |

| Subsection 5.2.3 System-on-Chip Modeling                                  | 188 |

| Section 5.3 Open Problems and Future Work                                 | 188 |

| Subsection 5.3.1 Built-In Self-Test                                       | 188 |

| Subsection 5.3.2 System-on-Chip Modeling and Analog Intellectual Property | 189 |

| Subsection 5.3.3 Biosensor Stability and Longevity                        | 190 |

| Section 5.4 Summary                                                       | 191 |

| Appendix A: Trapped Charge                                                | 193 |

| Appendix B: List of References for Self-Assembled Monolayer Applications  | 197 |

| Appendix C: SystemC-based SoC Models of Sample Counter and OBIST          | 200 |

| REFERENCES                                                                | 215 |

| CURRICULUM VITAE                                                          | 224 |

| End Notes                                                                 | 229 |

# List of Tables

| Table 2-1 Shown are the catastrophic fault results on LCD, in which the for  | ır          |

|------------------------------------------------------------------------------|-------------|

| transistors for the VLSI adaptation of the Chemical Field Effect Trans       | istors have |

| an error of 4x in their respective W/L ratio.                                | 17          |

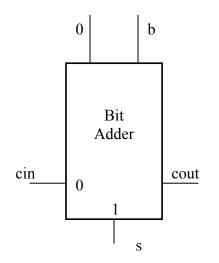

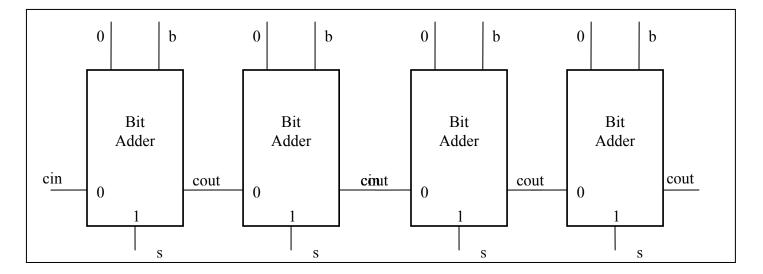

| Table 2-2 SystemC Based Bit Adder Module                                     | 45          |

| Table 2-3 Bit Adder Testbench                                                | 46          |

| Table 2-4 4-Bit Adder Model                                                  | 47          |

| Table 2-5 Characteristic responses for a 4-bit adder. These responses are us | sed as the  |

| testbench for the SoC model of the adder                                     | 47          |

| Table 2-6 SystemC output for 4-bit adder.                                    | 51          |

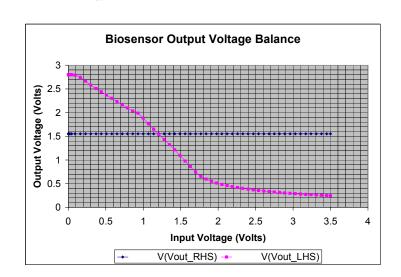

| Table 4-1 Biosensor Response Vout1                                           | 155         |

| Table 4-2 Biosensor Response Vout2                                           | 155         |

| Table 4-3 Voltage Controlled Oscillator (VCO) Response                       | 155         |

| Table 4-4 Zero-Crossing Detector (ZCD)                                       | 155         |

| Table 4-5 Biosensor Response Vout1                                           | 173         |

| Table 4-6 Biosensor Response Vout2                                           | 173         |

| Table 4-7 Voltage Controlled Oscillator (VCO) Response                       | 173         |

| Table 4-8 Zero-Crossing Detector (ZCD)                                       | 173         |

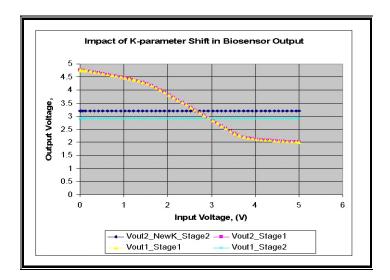

| Table 4-9 Parameters for the SoC Built-In Self-Test model                    |             |

| Table 4-10 Parameters for the SoC Built-In Self-Test model with new KP       | parameter   |

| in biosensor circuit                                                         |             |

# List of Figures

| Figure 1.1 Architecture for N-Sensor Smart Sensor on a Chip                         | 2    |  |

|-------------------------------------------------------------------------------------|------|--|

| Figure 2.1 Simplified Test Structure of the Oscillation Test Strategy               | . 25 |  |

| Figure 2.2 The schematic on the left is a 2-Stage CMOS Operational Amplifier        |      |  |

| Schematic. Circuit Under Test for OTS [9]. The schematic on the right               |      |  |

| represents the oscillation feedback system created with the additional resistors    | 3    |  |

| and capacitor.                                                                      | . 28 |  |

| Figure 2.3 Block Based Design of Signal Conversion Process                          | . 32 |  |

| Figure 2.4 Level Crossing Detector                                                  |      |  |

| Figure 2.5 Example of modeling Time for SoC applications. Shown is the method       | of   |  |

| changing the default time resolution and of setting a new time variable             | . 40 |  |

| Figure 2.6 Model showing events and event finders.                                  | . 41 |  |

| Figure 2.7 SoC Module                                                               | . 42 |  |

| Figure 2.8 SoC Channel                                                              | . 43 |  |

| Figure 2.9 SystemC Based Adder Module Code                                          | . 43 |  |

| Figure 2.10 Bit-Adder Symbol                                                        | . 45 |  |

| Figure 2.11 4-Bit Adder Symbol                                                      |      |  |

| Figure 2.12 Common implementations of the basic CHEMFET [97]                        |      |  |

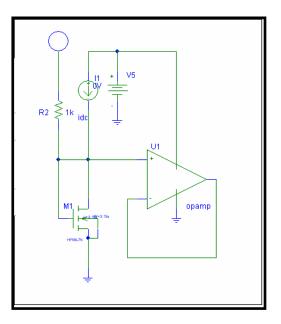

| Figure 2.13 Measurement circuit for ChemFET work function.                          |      |  |

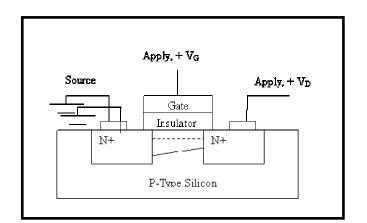

| Figure 2.14 Idealized ChemFET cross section schematic.                              | . 59 |  |

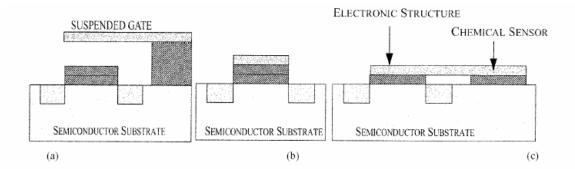

| Figure 2.15 Schematic Diagram of the suspended beam cross section area              |      |  |

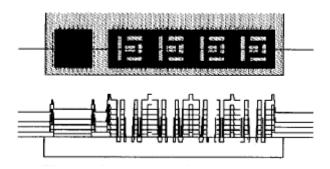

| Figure 4.1 Biosensor Layout                                                         |      |  |

| Figure 4.2 Cross-Section of upper transistors in VLSI adaptation of ChemFET         |      |  |

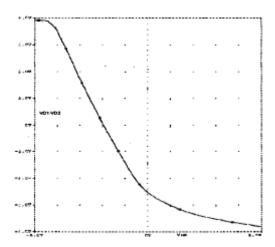

| Figure 4.3 Extracted Circuit Output Voltage versus Vset.                            | 129  |  |

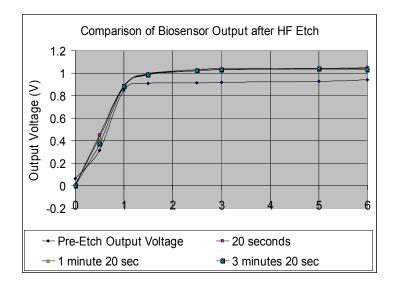

| Figure 4.4 Output Voltage versus Input Voltage for Biosensor versus time in HF      |      |  |

| solution                                                                            | 130  |  |

| Figure 4.5 Biosensor Output Voltage versus Voltage Controlled Transistor Input      |      |  |

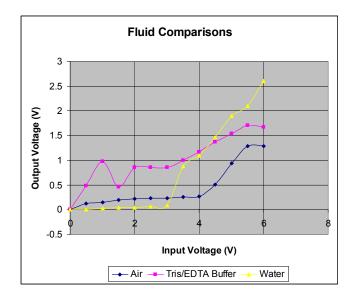

| Voltage for various fluids under test                                               |      |  |

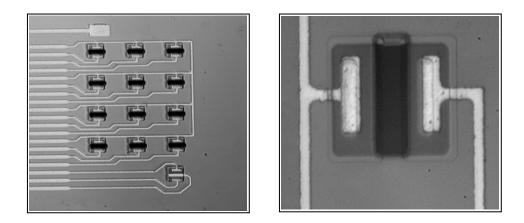

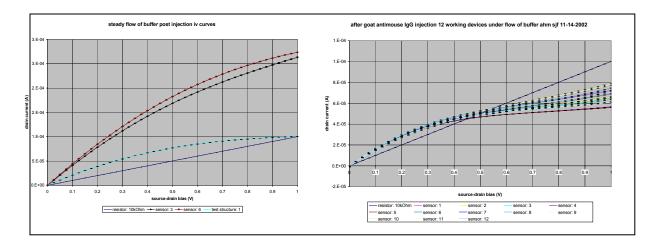

| Figure 4.6 Fabricated macromolecular sensors. The figure on the left is an array of | 12   |  |

| fabricated macromolecule sensors with gate electrode and body contact. The          |      |  |

| figure on the right shows a single macromolecule sensor where the active area       |      |  |

| the dark rectangle across the device middle.                                        |      |  |

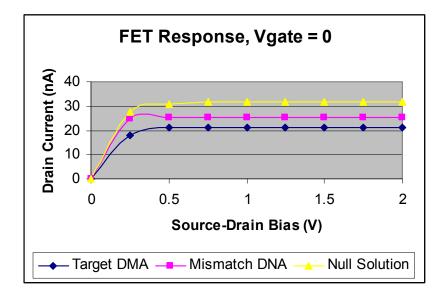

| Figure 4.7 Current-voltage response curves for devices exposed to mismatched DN     |      |  |

| matched DNA and buffer. There was little noise in the measurement in all cas        | es.  |  |

| The mismatched DNA showed slight response (which proved not to be                   |      |  |

| significant). The matched DNA showed clear response. The drain-source               |      |  |

| current is on the y-axis. The source-drain bias is on the x-axis.                   | 133  |  |

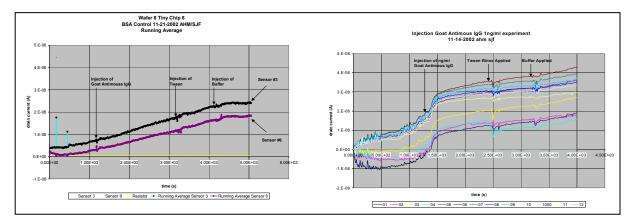

| Figure 4.8 Voltage Soak Results. The graph on the left is the BSA control. The      |      |  |

| graph on the right is the antibody match                                            | 134  |  |

| Figure 4.9 Macromolecular sensor results IV Curves. The graph on the left is the    |      |  |

| BSA control. The graph on the right is the antibody "match"                         |      |  |

| Figure 4.10 Counter Response to clock-like signals of unique periods                |      |  |

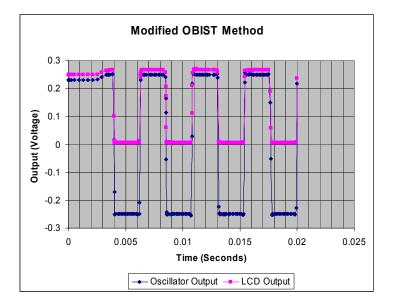

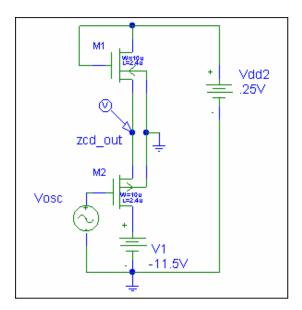

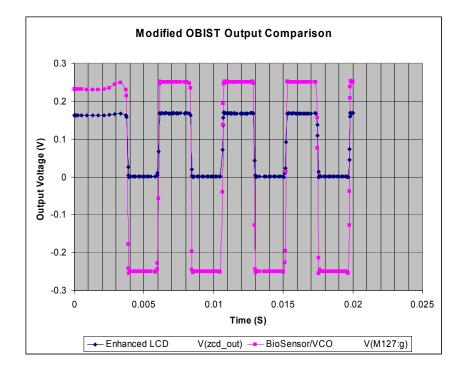

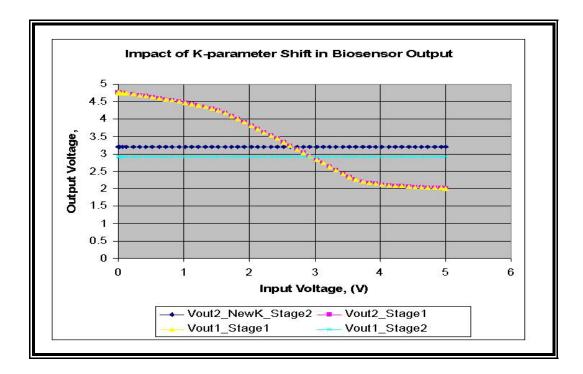

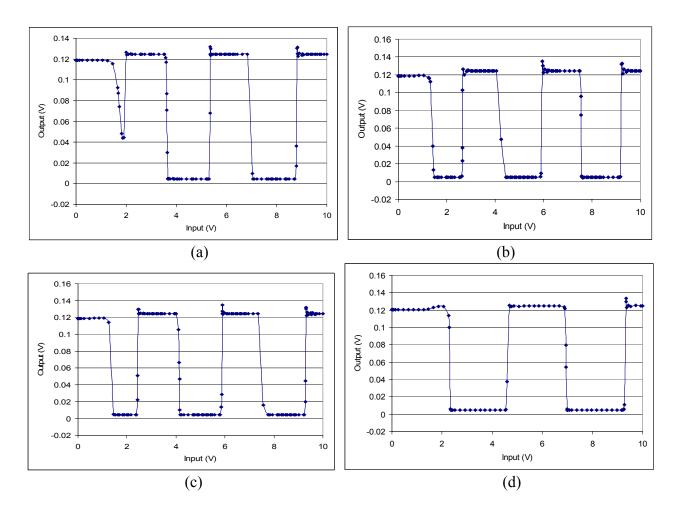

- Figure 4.20 Shown are the catastrophic fault results on ZCD, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 75% in their respective W/L ratio. In 4.20 (a) the error is in transistor

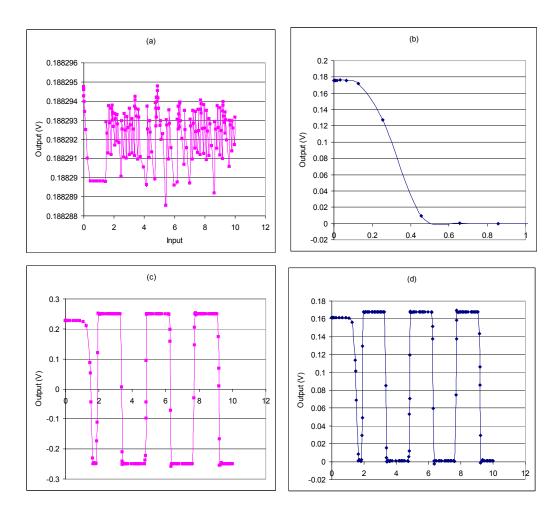

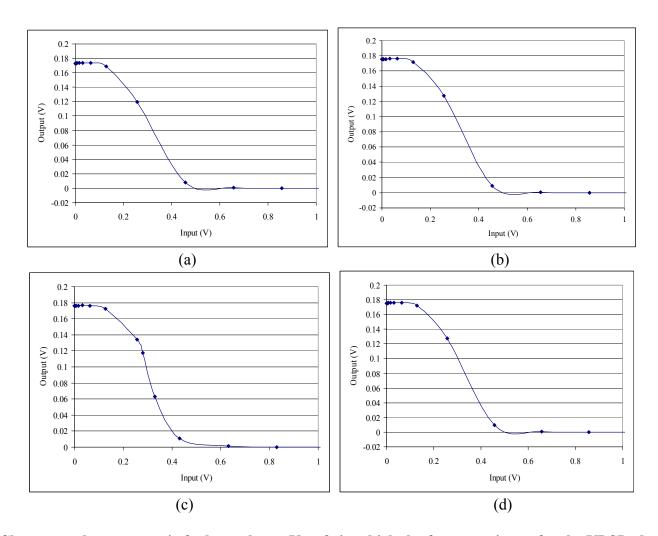

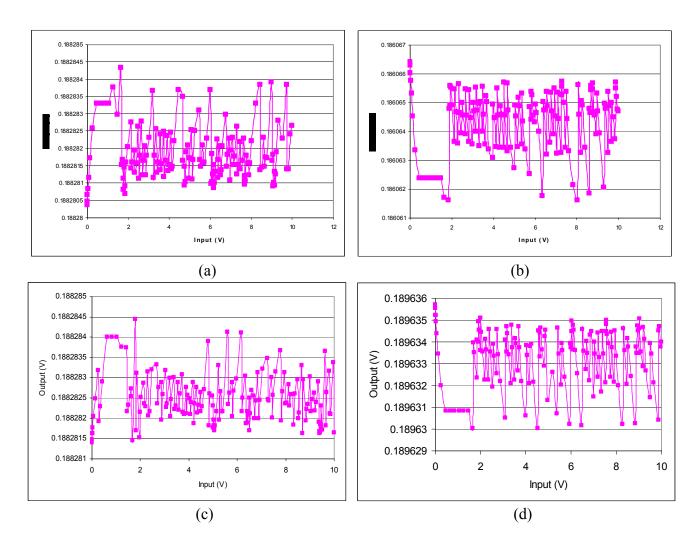

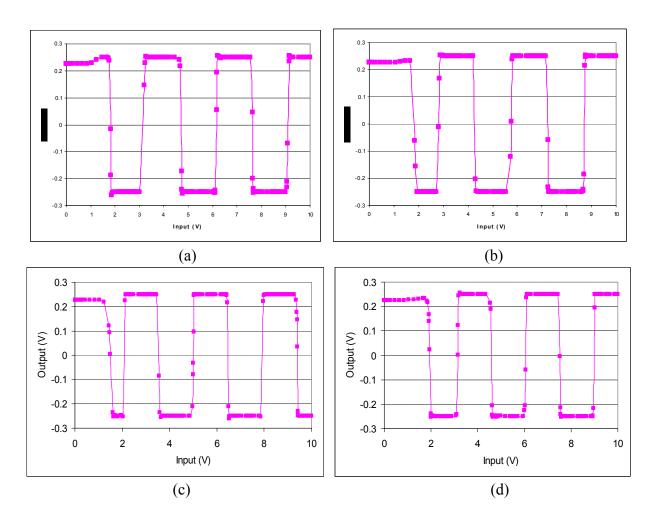

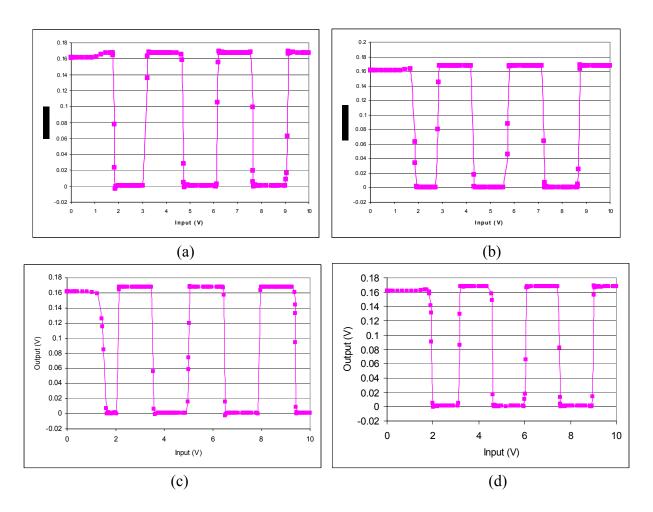

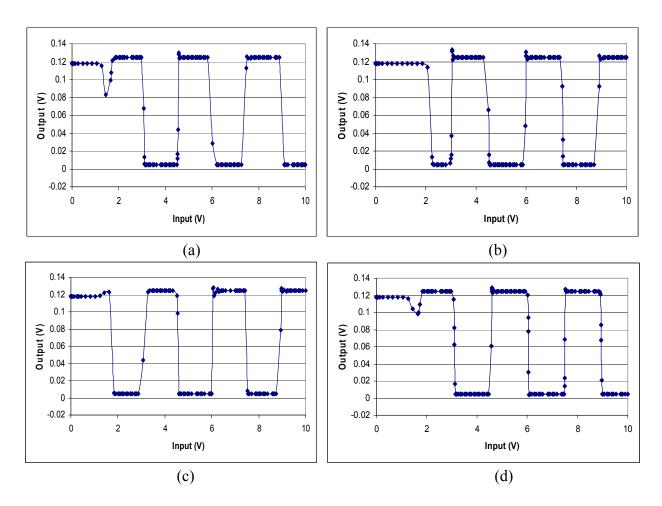

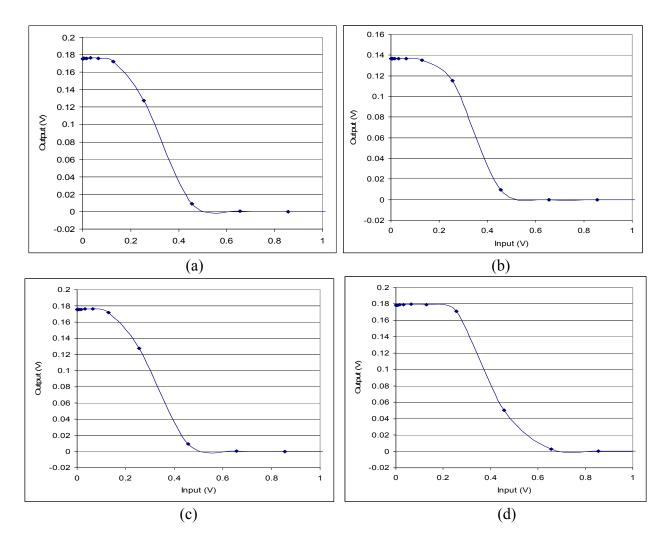

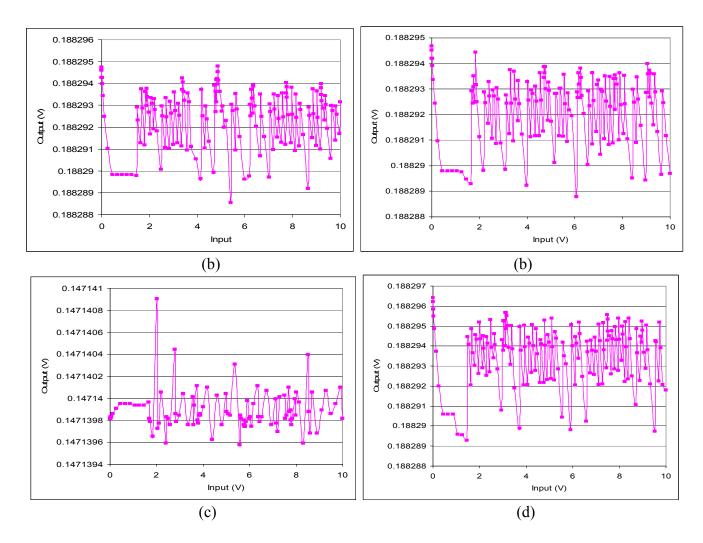

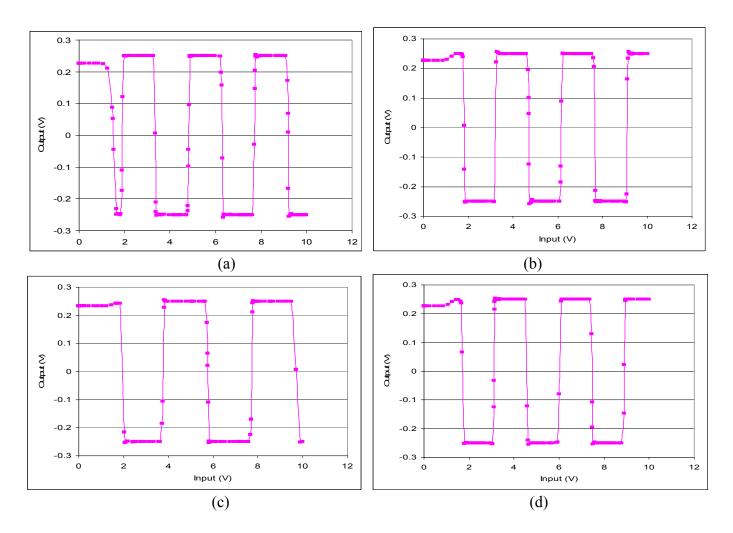

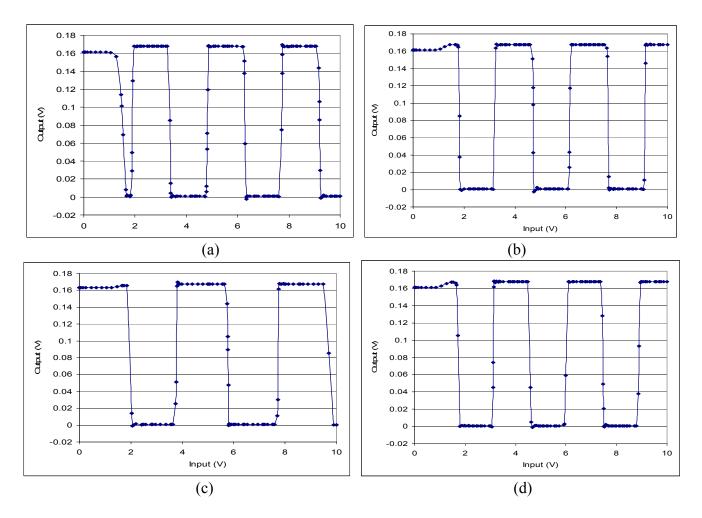

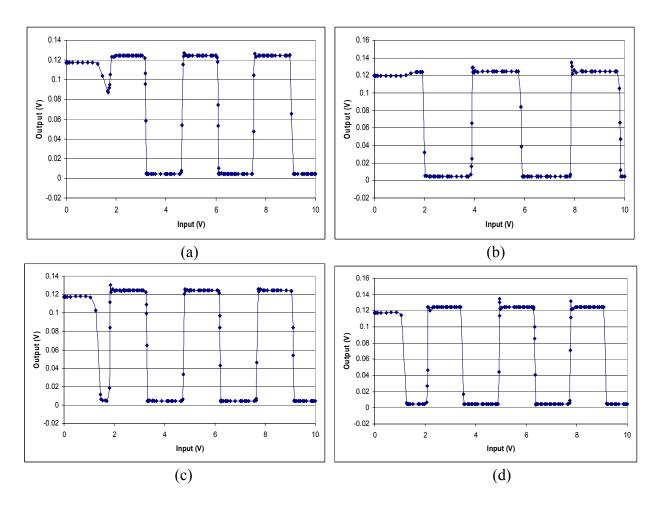

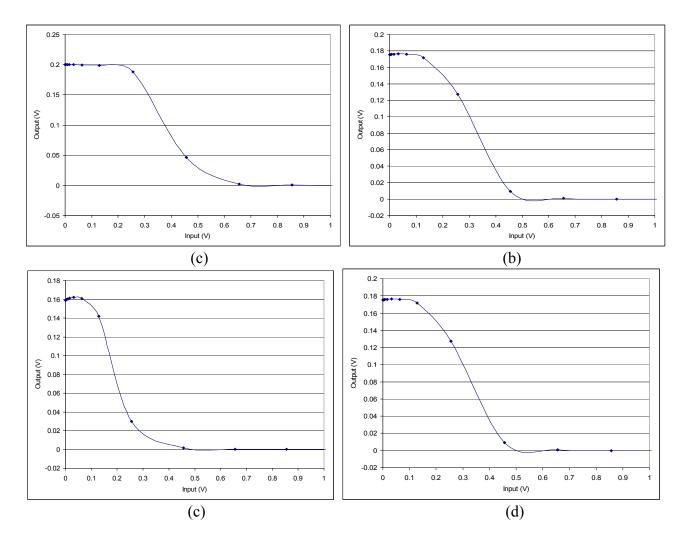

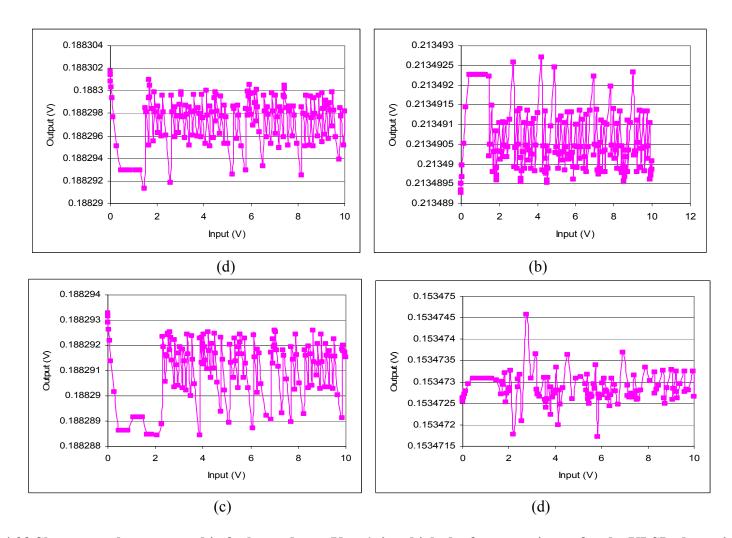

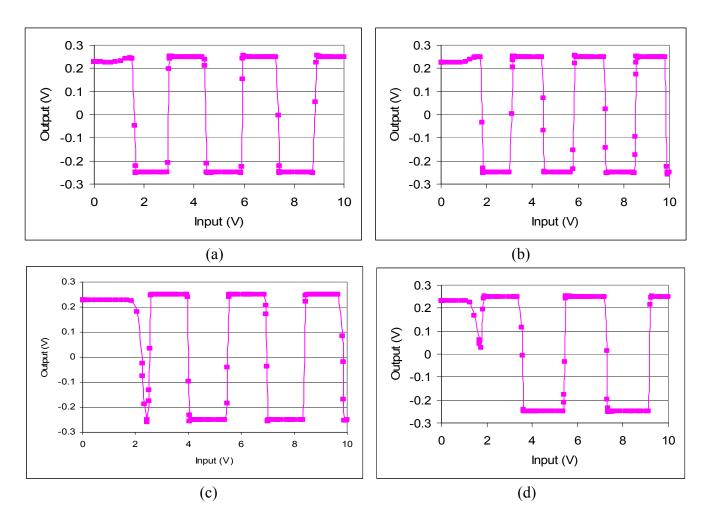

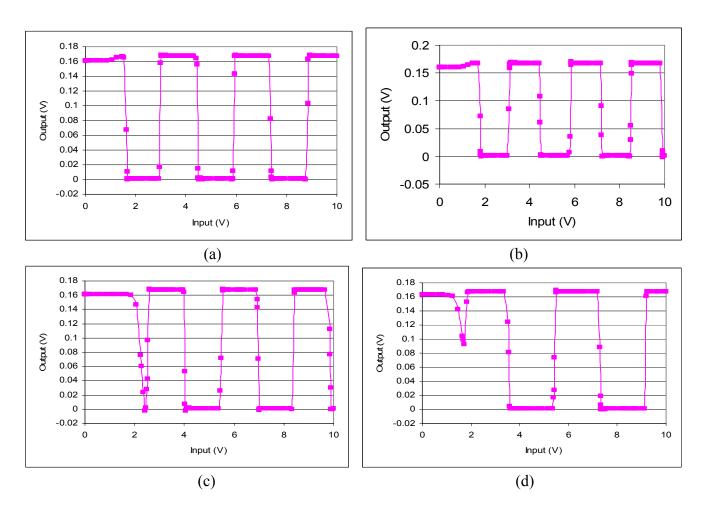

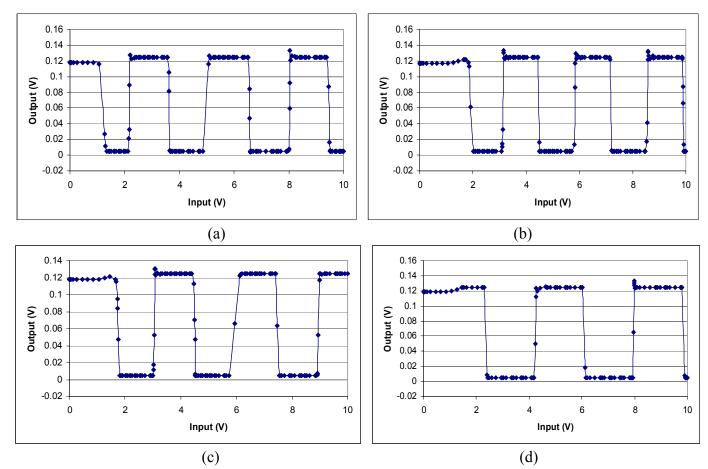

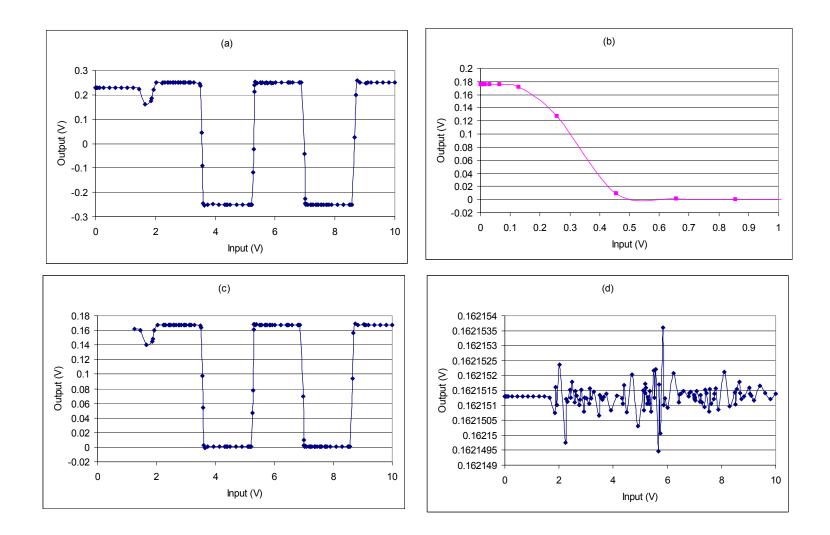

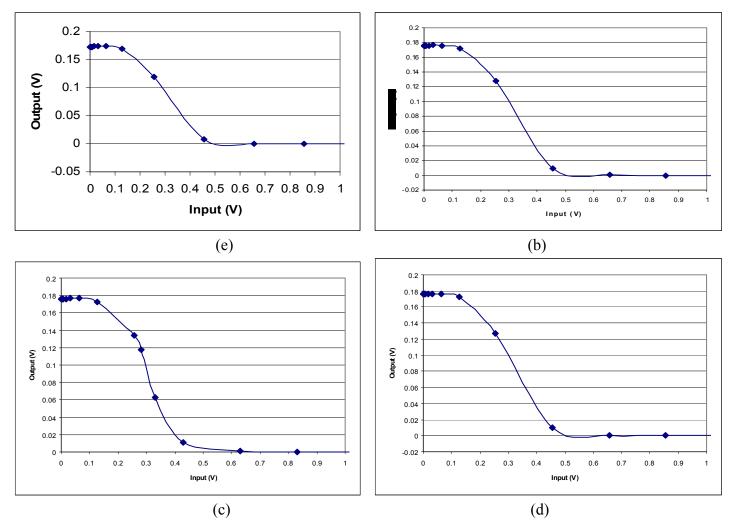

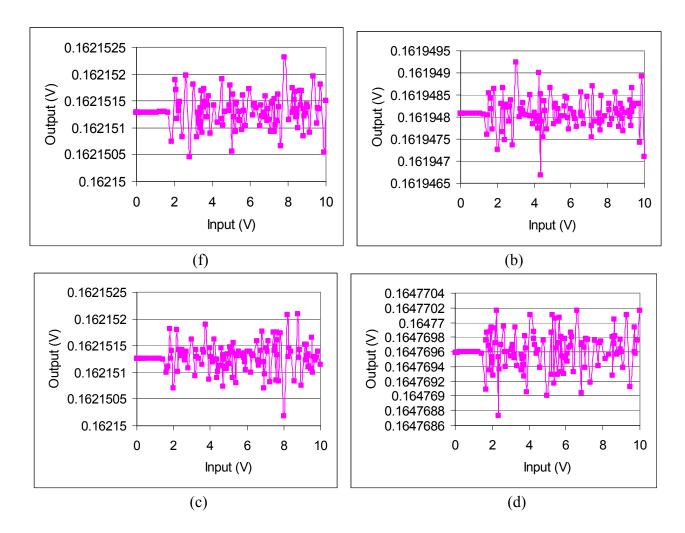

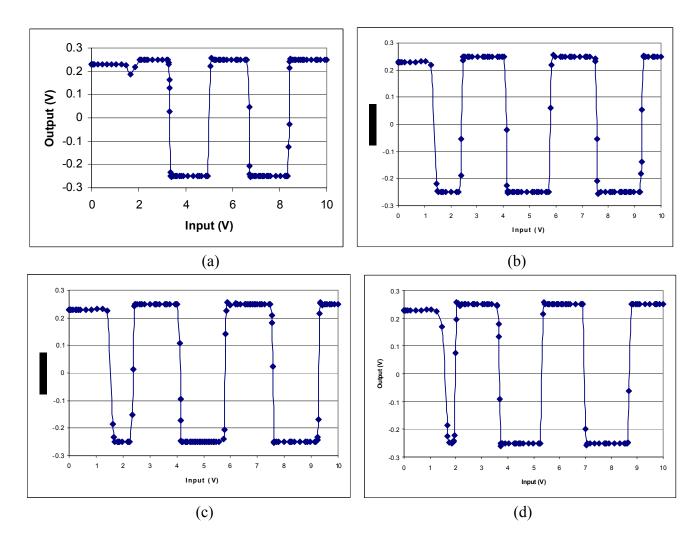

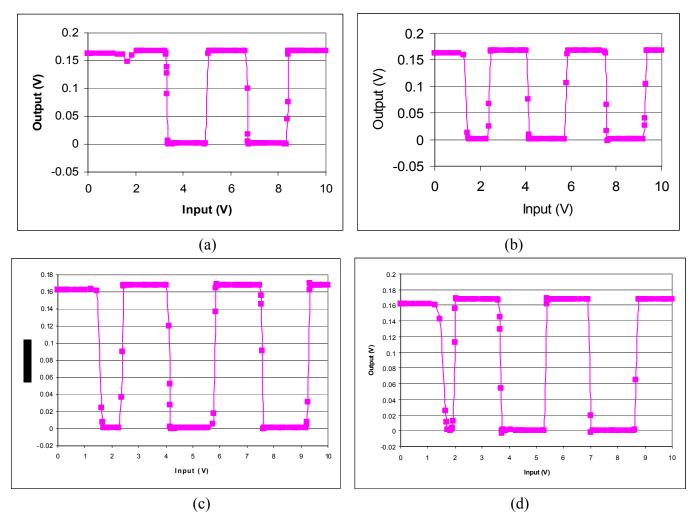

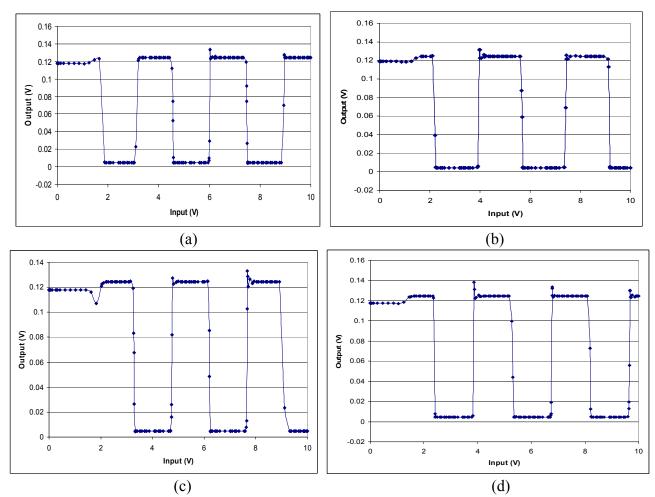

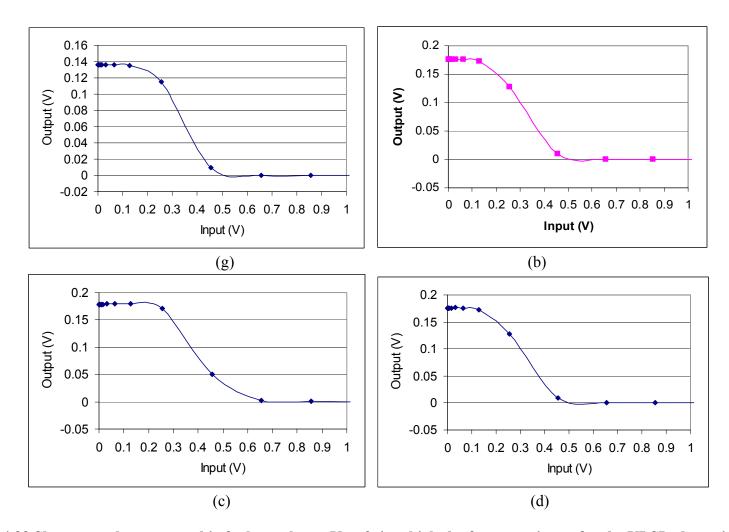

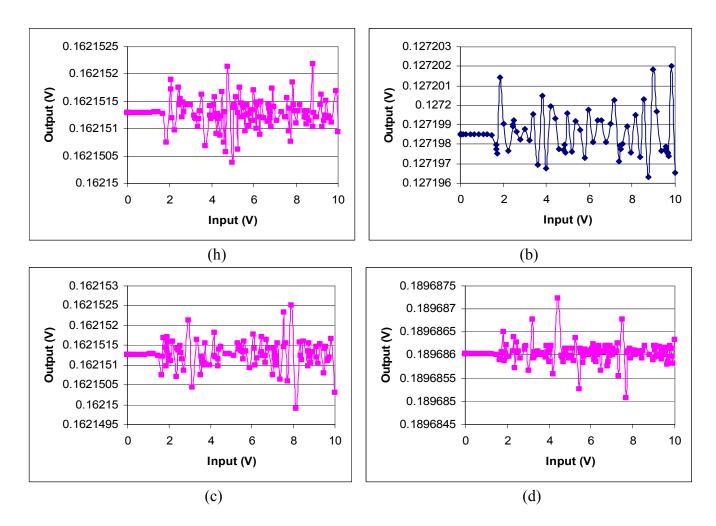

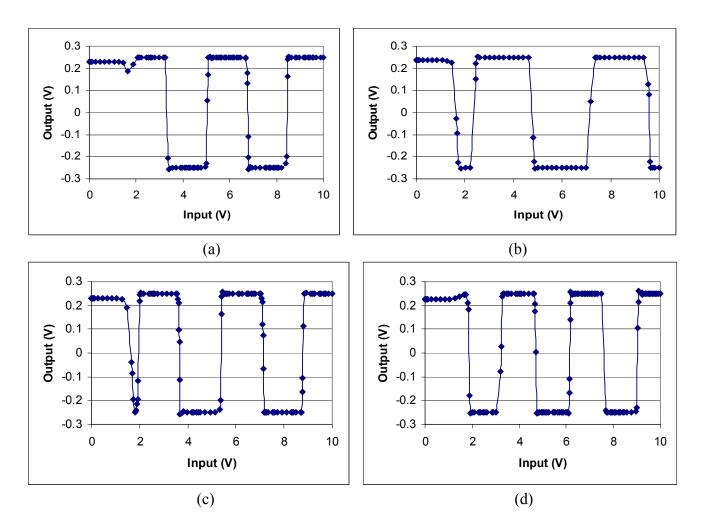

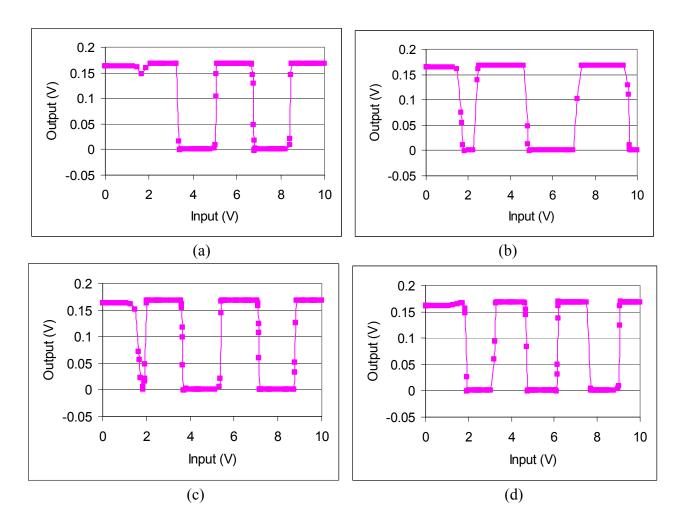

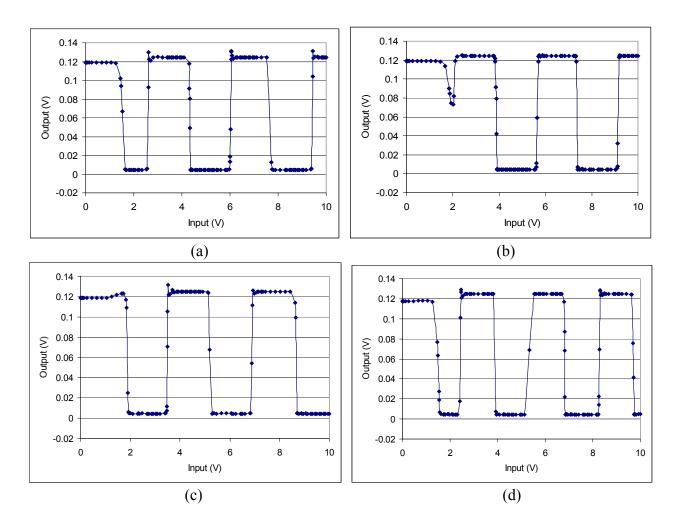

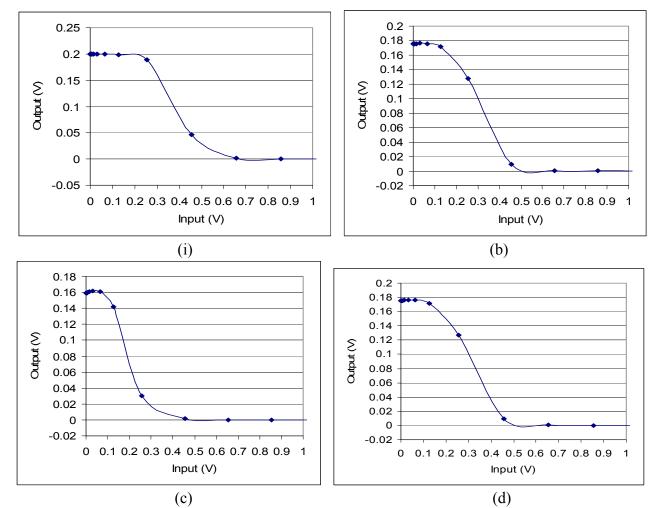

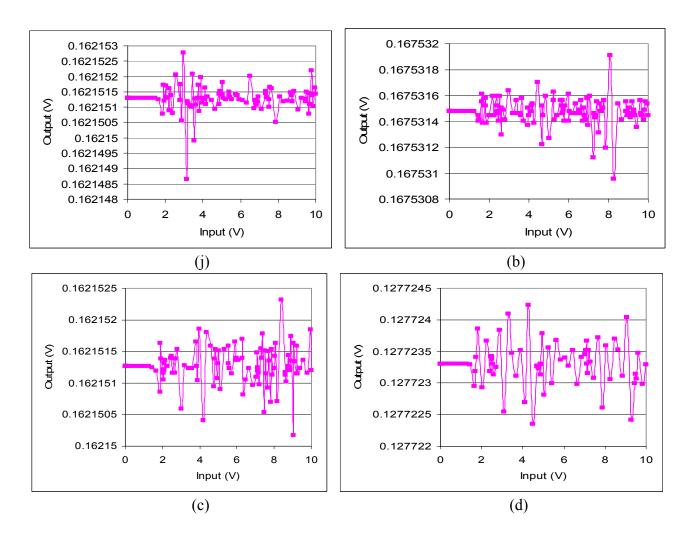

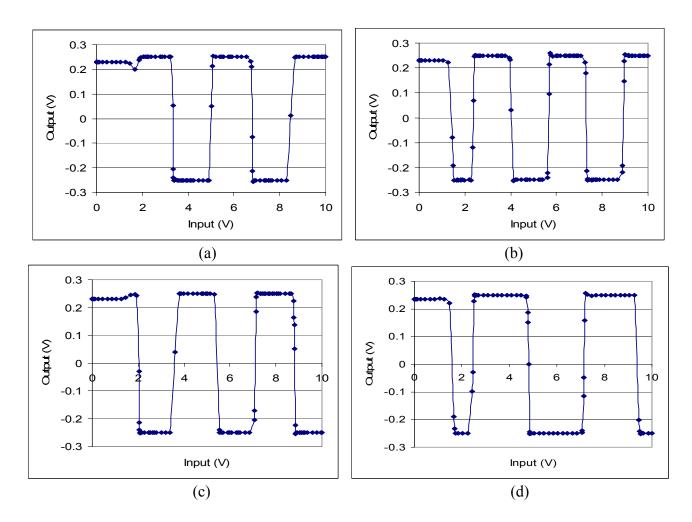

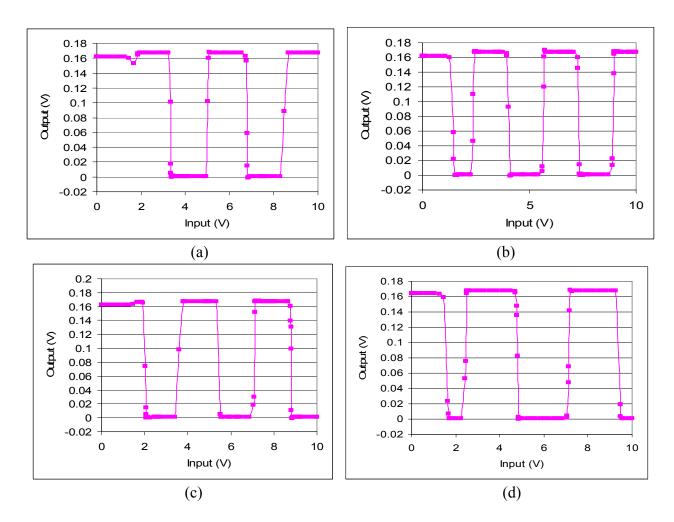

M1, in 4.20 (b), the error is in transistor M2, in 4.20 (c) the error is in transistor M3, and in 4.20 (d) the error is in transistor M4...... 148 Figure 4.21 Shown are the catastrophic fault results on LCD, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 75% in their respective W/L ratio. In 4. 21 (a) the error is in transistor M1, in 4. 21 (b), the error is in transistor M2, in 4. 21 (c) the error is in transistor M3, and in 4. 21 (d) the error is in transistor M4...... 149 Figure 4.22 Shown are the catastrophic fault results on Vout2, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 4x in their respective W/L ratio. In 4.22 (a) the error is in transistor M1, in 4.22 (b), the error is in transistor M2, in 4.22 (c) the error is in transistor Figure 4.23 Shown are the catastrophic fault results on Vout1, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 4x in their respective W/L ratio. In 4.23 (a) the error is in transistor M1, in 4.23 (b), the error is in transistor M2, in 4.23 (c) the error is in transistor M3, and in 4.23 (d) the error is in transistor M4...... 151 Figure 4.24 Shown are the catastrophic fault results on VCO, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 4x in their respective W/L ratio. In 4.24 (a) the error is in transistor M1, in 4.24 (b), the error is in transistor M2, in 4.24 (c) the error is in transistor M3, and in 4.24 (d) the error is in transistor M4......152 Figure 4.25 Shown are the catastrophic fault results on ZCD, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 4x in their respective W/L ratio. In 4.25 (a) the error is in transistor M1, in 4.25 (b), the error is in transistor M2, in 4.25 (c) the error is in transistor Figure 4.26 Shown are the catastrophic fault results on LCD, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 4x in their respective W/L ratio. In 4.26 (a) the error is in transistor M1, in 4.26 (b), the error is in transistor M2, in 4.26 (c) the error is in transistor Figure 4.27 Shown are the parametric fault-free output responses of the OBIST with a new KP parameter in use. In 4.27 (a) Biosensor Vout1, in 4.27 (b) Biosensor Figure 4.28 Shown are the parametric fault results on Vout2, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 10% in their respective W/L ratio. In 4.28 (a) the error is in transistor M1, in 4.28 (b), the error is in transistor M2, in 4.28 (c) the error is in transistor M3, and in 4.28 (d) the error is in transistor M4......158 Figure 4.29 Shown are the parametric fault results on Vout1, in which the four transistors for the VLSI adaptation of the Chemical Field Effect Transistors have an error of 10% in their respective W/L ratio. In 4.29 (a) the error is in transistor M1, in 4.29 (b), the error is in transistor M2, in 4.29 (c) the error is in transistor

# **Chapter 1 Introduction**

#### Section 1.1 Motivation for the Research

In a number of areas, it would be useful to have available smart sensors that can determine the properties of a fluid and from those make a reasoned decision. Among such areas of interest might be ecology, food processing, and health care [1]. For example, in ecology it is important to preserve the quality of water from which a number of parameters are of importance, including physical properties such as color, odor, and pH, as well as up to 40 inorganic chemical properties and numerous organic ones [2]. Therefore, in order to determine the quality of water it would be extremely useful if there were a single system on a chip which could be used in the field to measure the large number of parameters of importance and make a judgment as to the safety of the water. For such, a large number of sensors are needed as well as a means of coordinating the readouts of the single sensors into a user friendly output from which human decisions could be made. As another example, the food processing industry needs sensors to tell if various standards of safety are met. In this case it is important to measure the various properties of the food, for example the viscosity and thermal conductivity of cream or olive oil [3]. In biomedical engineering, biosensors are becoming of considerable importance as they have the potential to aid in medical diagnoses by providing a means of analyzing biological fluids for the existence of antibodies, which are proteins, commonly associated with diseases. There are a number of different types of biosensors including

electrochemical sensors, thermal sensors, mass flow sensors and optical sensors [4, 5, 6].

In the biomedical engineering field, methods for the selective determination of compounds in fluids are very important in clinical analysis. Present methods often require a long reaction time and involve complicated and delicate procedures. One valuable application in the health care area is that of the use of multiple sensors for maintaining in space astronaut health. In this arena, an array of eleven sensors is used to maintain the quality of recycled air although separate control and is effected by the use of an external computer. Therefore, the development of inexpensive and miniaturized sensors that are highly selective and sensitive and for which control and analysis is present all on one chip is very desirable.

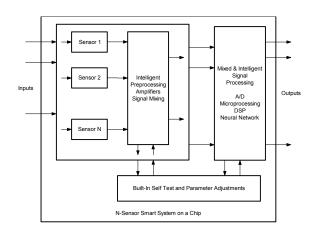

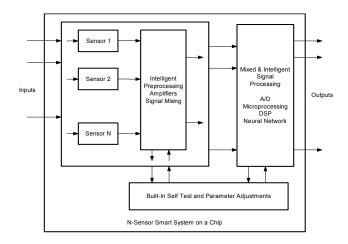

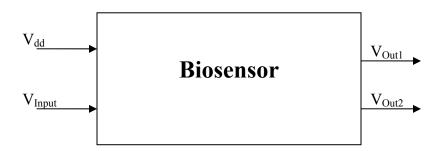

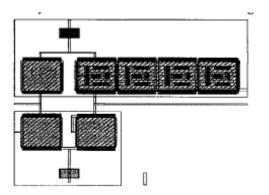

Figure 1.1 Architecture for N-Sensor Smart Sensor on a Chip

These types of sensors can be implemented on a semiconductor substrate with very large scale integration (VLSI) technology. Because the sensors are fabricated on a semiconductor substrate, additional signal processing circuitry can easily be integrated into the chip thereby readily providing functions such as multiplexing and analog-to-digital conversion. In numerous other areas, one could find similar uses for a smart multi-sensor array from which measurements can be made easily with a small portable device.

The proposed architecture of these systems as shown in figure 1.1, can be configured with multiple inputs, sensors, and outputs. In addition to this is a series of smart signal processing elements called built-in self-test (BIST) devices, which are capable of evaluating each of the unique systems (sensors, analog-to-digital converters, etc) on the chip. In this system, there may be many classes of input signals (for example, material [as a fluid] and user [as an indicator of what to measure]). On each of these inputs, there may be many sensors (for example, one material may go to several sensors, each of which senses a different property [such as dielectric constant in one and resistivity in another]. The sensor signals are treated as an N-vector and combined as necessary to obtain the desired outputs, of which there may be many (such as an alarm for danger and indicators for different properties). For example, a patient with kidney disease may desire a system-on-a-chip (SoC) that gives an indication of when to report to the hospital. For this, the SoC would indicate a deviation of the dielectric constant from normal. In addition the spectral properties of peritoneal fluid may be sensed, with appropriate warning indicators for abnormal readings. These indicators could be combined to detect the presence and percentage of creatinine, a protein produced by the muscles and released in blood, in a fluid sample. A signal output for the system could indicate the percent of creatinine in the fluid with an appropriate warning alarm or indicator light when such percentages reach dangerous levels.

The underlying goal of this research is to develop biosensor devices capable of performing on-chip self-diagnostics. This work focuses on creating an on-chip built-in self-test (BIST) scheme for an array of biosensors and other system-on-a-chip related medical devices. This research will assist the medical industry by aiding in the early detection of faulty sensor devices used for the detection and treatment of disease. This research will aid health care providers in saving human lives, by providing an early warning system for the detection of faulty equipment and sensors.

In addition to developing a novel BIST method, this work will perfect the development of two unique multi-sensor systems. The first sensor system studied will be capable of detecting impurities in fluid. The principle behind the type of biosensor used in this research is that, by evaluating the effects of resistivity changes on the gain of a ChemFET, impurities can be detected in any liquid. The second sensor system studied will exploit the use of biosensors in performing matches and mismatches of antibody antigens and/or deoxyribonucleic acid (DNA) for the purpose of deciphering chemical compounds.

#### Section 1.2 Statement of Proposed Problem

The driving force in today's semiconductor industry is the need to maintain a rate of improvement in speed and size reduction of 2x every eighteen months in high-performance components. Currently, these improvements rely exclusively on advances made in semiconductor miniaturization technology. The 1999 International Technology roadmap for Semiconductors (ITRS) suggests that, "innovation in the techniques used in circuit and system design will be essential to maintain the

historical trends in performance improvement" [7]. Achievement of this advancement in circuit and system design techniques is increasingly becoming dependent on integrating multiple silicon technologies on the same chip. The devices that result from the aforementioned integration of multiple technologies are commonly referred to as System-on-a-Chip (SoC) devices.

Design is paramount for all categories of the ITRS roadmap. This is especially true for the SoC category where time-to-market for an Application Specific Integrated Circuit (ASIC) is a key attribute for new product delivery. Design is additionally important for SoC devices because of increasing system complexity. The growth of system complexity is due to the diversity of SoC design styles, integrated passive components, and the increased need to incorporate embedded software. Design for SoC devices will become increasingly difficult with the growing interaction among design levels, the difficulties associated with including multiple designs onto a single chip, design process predictability, and the growing size and dispersion of design teams.

These challenges are overcome with the use of block-based design approaches that emphasize design reuse. System blocks often contain a layout file that is used for the fabrication process and an Analog Hardware Description Language (AHDL) behavioral model used to describe the interaction of system components during the design process. Each system block should have features that allow for the implementation of on chip Built-in Self-Test (BIST). The emergence of the SoC paradigm imposes various metrology and standardization challenges. These include metrology for multi-technology process monitoring, BIST calibrations, validation of

behavioral model representations, and benchmarking simulation of system-on-a-chip systems interactions.

Another significant challenge involves ensuring the testability of a System-ona-Chip of IC design. This is a formidable task, as testability within the context of mixed technology integrated circuits is not well defined. Testability is defined in this dissertation as controllability and observability of significant waveforms within a circuit. For most IC designers, significant waveforms are input/output signals that can be obtained at every stage of the circuit. The first stage of the circuit input is assumed to be controllable; while during the last stage, output is observable.

Some have proposed methods of assuring testability that involve the use of oscillatory BIST techniques [8, 9]. The BIST method using an oscillation-based test circuit has been shown to have the potential of overcoming common problems associated with conventional test methods. This BIST method has also been shown to be effective for any type of mixed analog/digital circuitry used as system blocks.

#### Section 1.3 Outline of the Methodology

Subsection 1.3.1 Multi-Sensor System Architecture

The architecture of the Multi-Sensor Smart System is given in figure 1, where there are multiple inputs, sensors, and outputs. A built-in self-test (BIST) element is included between each signal processing element. In this system, there may be many classes of input signals (for example, material [as a fluid] and user [as indicator of what to measure]). Each of the inputs may be directed to many sensors (for example, one material may go to several sensors, each of which senses a different property [such as dielectric constant in one and resistivity in another]).

The sensor signals are treated as an N-vector and combined as necessary to obtain the desired outputs, of which there may be many (such as an alarm for danger and indicators for different properties). For example, a patient with kidney disease may desire a system on a chip that gives an indication of when to report to the hospital. In this case, an indication of deviation of dielectric constant from normal and spectral properties of peritoneal fluid may be sensed. Once combined, they indicate the presence of creatinine (a protein produced by the muscles and released in the blood) in the fluid. Here, the signal output is recognized as the percent of creatinine in the fluid and an alarm when at a dangerous level.

To design multi-technology SoCs such as in figure 1, block-based design approaches that emphasize design reuse are preferred, to reduce overall design time and cost of testing the new device. System blocks often contain a layout file that is used for the fabrication process an Analog Hardware Description Language (AHDL) behavioral model used to describe the interaction of system components during the design. To validate the interaction between various sensors, signal processing, and BIST sub-blocks, further development of a unique Testbench-on-a-Chip methodology.

#### Subsection 1.3.2 Testbench-on-a-Chip Methodology

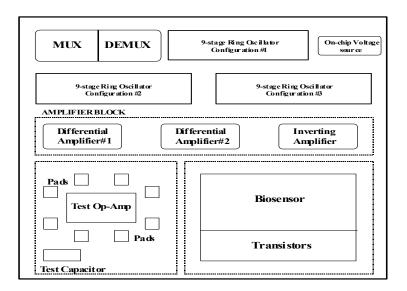

The Testbench-on-a-Chip evaluates the interactions between key sub-blocks of the multi-sensor smart system. Figure 2 shows the block diagram of the Testbench-on-a-Chip. The most important aspect of the Testbench-on-a-Chip

methodology is to be able to multiplex input signals from different sensor system blocks or reference signals from different sensor system blocks or reference signals to different BIST system blocks. The outputs of the BIST system blocks are then multiplexed to the digital out of the TBOC. This enables the use of a computer controlled test system to select and analyze the interaction between different system blocks for a wide range of computer controlled test vectors.

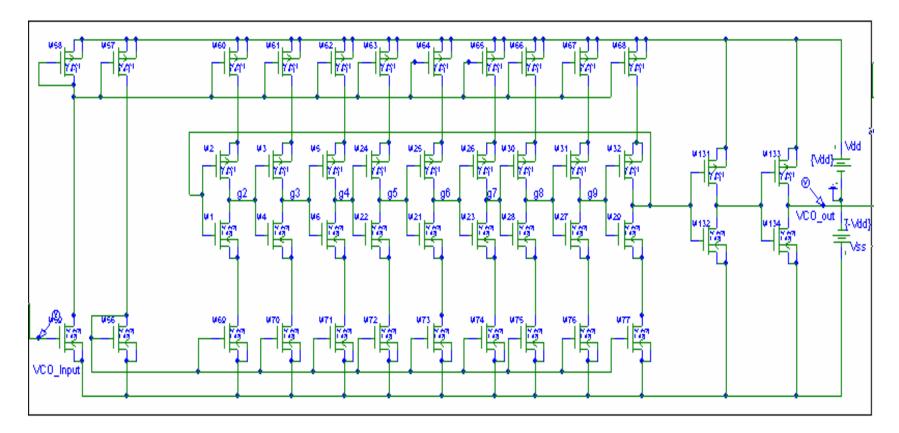

The following sections describe the electronic circuitry used for my proposed Testbench-on-a-Chip in more detail. Included in this circuitry description are biosensors, ring oscillators, test op amps, and smart signal processing in the form of a MUX/DeMUX pair.

#### Subsection 1.3.3 Biosensor Systems

The class of biosensors studied in this work is designed to analyze physical properties of fluids. These sensors are capable of deciphering various characteristics associated with fluids including: pH, resistivity, and dielectric constant. The sensors can also discern inorganic and organic chemical properties. Such sensors are implemented using micro-electro-mechanical system (MEMES) technology. The sensor circuit can be fabricated on a semiconductor substrate that allows for the integration of additionally signal processing circuitry onto the chip. An array of such sensors can be used to determine multiple properties of a fluid, using a single chip.

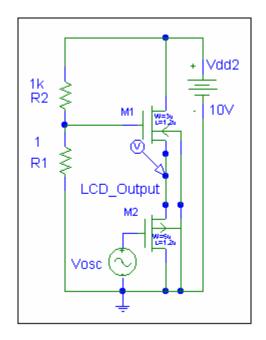

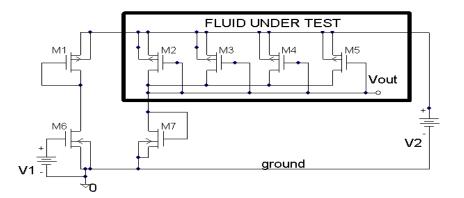

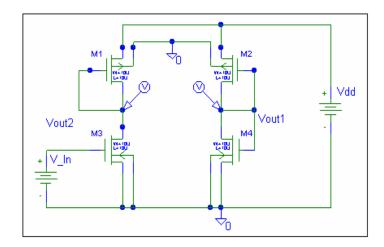

Figure 3 is a schematic of the sensors studied for the detection of fluid properties. This example sensor circuit operates as a dielectric constant measurement device. This sensor can be provided as part of an integrated micro-system designed to determine the properties of a fluid. The fluid-sensing transistor in this sensor is a

VLSI adaptation of the CHEMFET. The sensor operates as a capacitive-type bridge such that a balance can be set for a normal dielectric constant. In the presence of a fluid, the unbalance that occurs within this sensor bridge is used to evaluate the fluid's dielectric constant.

The four CMOS transistors form the bridge: M1, M6, M7, and the fluidsensing transistor comprised of transistors M2 through M5. The fluid-sensing transistor and transistor M1 the PMOS (p-type MOSFETs) transistors in the diode connected configuration (gate connected to drain). The lower two transistors, M6 and M7, are NMOS type (one diode connected and the other with a gate voltage control). The output, Vout, of the sensor circuit is taken between the junction of the fluidsensing transistor and the diode-connected transistor, M7.

The transistors, M2 through M5, have openings in their gates to allow fluid to flow between the silicon substrate and the polysilicon gate where the gate oxide has been removed. This allows the fluid to behave as the gate dielectric for that transistor. Each of the transistors has a ratio of 10u/10u. The overall W/L ratio of the fluid-sensing transistor is therefore 40u/40u.

The fluid-sensing transistor is constructed out of four transistors with all terminals connected in parallel to increase the gain constant parameter KP that is proportional to the dielectric constant. Fabrication of the sensor is based on a sacrificial etch process, where the silicon dioxide gate dielectric in the fluid-sensing transistor is removed by chemical etch. This activity is accomplished by opening holes in protective layers using what is known as the, over-glass cut method available in the MOSIS-MEMS fabrication process.

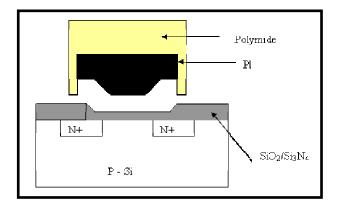

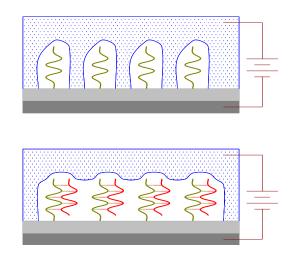

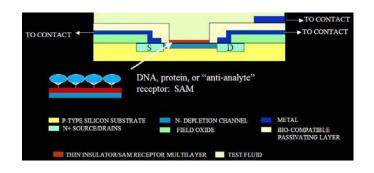

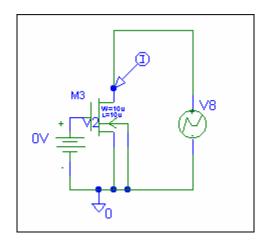

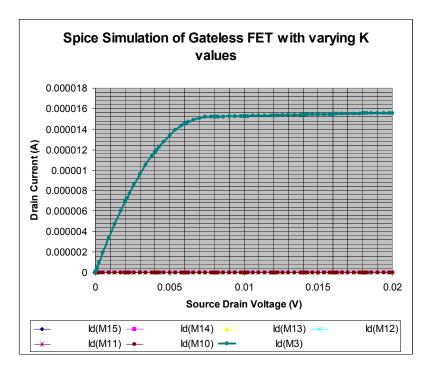

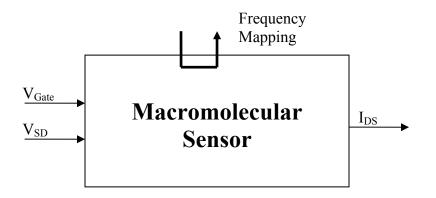

The other sensor under study in this work is a biological macromolecular sensor for early detection of diseases. Over the course of this research, I will propose an analytic model for this sensor. The sensor, is a gateless depletion-mode field effect transistor (FET) having a source implant and a drain implant that are spatially arranged within a semiconductor structure. The source and drain are separated by an active channel, which is covered by a dielectric layer. The dielectric layer has a bottom surface, which is in contact with the active channel and a top surface, which is in contact with a sample solution. The top of surface of this gateless FET is modified with a receptor for detecting the presence of target antibody antigens and/or DNA strands. A reference electrode is attached externally to the sample solution. Figure 4, below shows the cross section of the device. The cilia-like structures or microchannels described also represent DNA and/or antibody antigen receptor sites.

The sensor detects the presence of target molecules in the sample solution by measuring the change in current between the source and drain. The change in current occurs via one of two methods. The first is due to the change in capacitance of the receptor-modified dielectric film/sample solution interface when target molecules bind to the molecular receptors. The second is the result of charged molecules binding to the receptor-modified dielectric film or sample solution interface.

The gateless field effect transistor will be evaluated for its ability to adequately detect matches in target, antibody antigen solutions. The sensors are active element devices capable of developing circuit gain. Such devices are known for their high input impedance, which makes them suitable for pre-amplifier application. Figure 5 below presents a schematic diagram of the gateless field effect

transistor. This provides the basis for the analytic model I will create, which will lend itself to development of chemical sensor simulations.

The gateless FET is small, easily mass-produced, and directly integrable in electronic systems. Large numbers of these devices can be packed into small areas, lending to the straightforward implementation of arras. One of the added advantages of the FET is that it can discriminate between charge and the thickness of a deposited film.

In spite of the many advances that have been made in the development of mixed signal technologies and biomedical devices, traditional methods of these implementations are limited by Moore's law. Moore's law suggests that, improvement in the development of semiconductor devices appears in the factor of 2X increase in device performance every 18 months. As system complexity becomes greater with time, there is a need to develop methods of maintaining this rate of improvement while decreasing time to market. The remainder of this work will address the issues associated with system-on-a-chip development of mixed signal technology. The example SoC developed in this work has application to the field of biomedical engineering as it serves as a means of testing biological and related fluids on a single chip.

#### Section 1.4 Dissertation Contributions

• Design of an Analog System-on-a-Chip for testing fluidic properties including: DNA, Antibody Antigen, and Dielectric Constant

In chapter 3 of a novel system-on-a-chip (SoC) design is provided. The design encompasses the use of an array of biosensors to perform on-chip

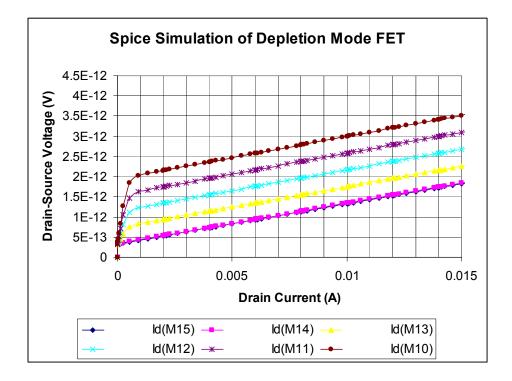

measurements of a transistor's response to the dielectric constant of a fluid under test. The biosensors are analyzed and evaluated with hand calculations and SPICE simulations. Included in this analysis is the fabrication and evaluation of a gateless field effect transistor and a VLSI implementation of the ChemFET in chapter 4.

#### Models and Implementation of analog system-on-chip macros

Analog system-on-chip sub-blocks such as a chemical field effect transistor, macromolecular sensor, built-in self-test, voltage controlled oscillators, and level crossing detectors, are evaluated. Models of BIST sub-blocks and the responses of these sub-blocks to faults in a biosensor are transformed into equivalent system on a chip models. Hand calculations, system-level implementations, and SystemC source Code (SoC Model) implementations are provided for each device in chapter 3. In chapter 4, the SoC models are simulated and compared against equivalent SPICE simulations and hand calculations.

# • Design, implementation, and simulation of an analog SoC subblock testing procedure.

An oscillation based built in self test procedure is developed in chapter 3 to perform parametric and catastrophic testing of system-on-a-chip sub-blocks. The procedure involves the use of an oscillation based built-in self-test (BIST) method to detect potential system errors that may exist beyond a reasonable tolerance. The method developed is a modification of a previously developed oscillation test strategy and is novel in its application to sensor technologies. In chapter 4,

simulations of the oscillation based BIST components are provided. These simulations are generated by SPICE and through the analysis of hand calculations.

• Design and evaluation of fabricated fluid analyzer sensors in the presence of antibody antigens (DNA), buffer, water, and air.

In chapter 3 the design of fluid analyzer sensors is presented. Included in the design are equations that model sensor performance and fabrication techniques. Chapter 3 also describes the process by which antibody antigens are attached to the sensors for substance evaluation. In Chapter 4 measurements of the gateless field effect transistor response to the presence of antibody antigens are presented. The response of the VLSI implementation of the ChemFET to various fluids is also shown in chapter 4.

# **Chapter 2 Background**

#### Section 2.1 Overview

One of the challenges of developing systems-on-a-chip is making analog mixed-signal (AMS) intellectual property (IP) for off the shelf applications as ubiquitous as digital IP. This is largely due to the fact that the end user's design requirements preclude the "clean" reuse, seen when working with digital blocks [10]. This is because the performance of analog SoC designs is far more affected by system-level requirements such as technology, power, die size, and package type, than digital designs. Other variables that affect the feasibility of developing analog SoC sub-blocks include inherent performance sensitivity to designer specified variables such as: wirebond or flip-chip package, the desired I/O pitches, the number of metal layers in the technology process or whether the user wants to use a "lowvoltage" or "generic" process. As such, digital SoC IP development has seen significantly more progress than the analog IP equivalents.

Analog designers, however, have made progress in a few areas. The first is the development of standards for AMS interfaces. The second is in the development of software tools for migrating analog circuits across similar process technologies.

In this chapter we discuss the current state of the art in system-on-chip development with application to biosensors. In section 2.2 information on SoC technology is provided. In section 2.3, built-in self-test (BIST), mainstream methods of performing SoC Test and verification are discussed. In section 2.4, the use of the

oscillation test strategy for BIST is analyzed. Section 2.5 offers a discussion of the current state of the art in system-on-chip modeling. While in section 2.6 a discussion of mainstream biosensor devices is provided. The contents of this chapter are summarized in section 2.7.

#### Section 2.2 System-on-a-Chip (SoC) Technology

For over a decade integrated circuit technology has seen significant changes beginning with the adoption of high-level description languages such as VHDL (very high-speed IC description language) and Verilog. The industry has also seen marked increase in manufacturing foundries. There has also been a shift in IC business away from vertically integrated semiconductor companies towards horizontally strong design companies [11]. This represents a shift from IC companies composed of large design teams, expensive manufacturing factories, and internal CAD tools development teams towards design houses. IC fabrication foundries have cornered the manufacturing market.

These changes reflect the never-ending increase of silicon capacity available to system and IC designers that has been predicted by Moore's Law. This now brings to the forefront, a cyclical crisis in design methodology and engineering productivity generating a ripple effect through the electronics industries [12]. The system-on-achip era, however, requires more than available silicon, it requires a new design methodology roadmap based on IP reuse needs.

There are now three industry leaders in the field of electronic-CAD tools development: Cadence Design Systems Inc., Synopsys Inc., and Mentor Graphics Corporation. Such commercial tools give IC design engineers the flexibility that is

needed to switch jobs easily; whereas, in-house tools that are specific to a given company's infrastructure are not as marketable to IC designers and today's manufacturing companies.

There has also been a trend over the past few years towards design services such as intellectual property (IP) providers, IC testing services, equipment-rental companies, etc. These companies provide a service to IC design practice as they facilitate the SoC design methodology, which has lead to new IC design business models and electronic-CAD tools development.

The starting point of any design project is writing the specifications. Such specifications, executable specifications, are typically written in C, C++ and/or HDL. Formal specifications are the characterization of the design, defined independently of any implementation. Once these specifications are identified, formal methods and tools can be used to check against the specifications. During this process decisions about timing and synthesis, functional design issues, physical design issues, verification strategies, and test strategies must be made.

The IC creation cycle can be broken up into four main steps: Concept, Design, Verification, and Implementation. For the Design to Verification step, there are certain industry wide acceptance ratios for specific tasks. These are identified by table 2.1 [13]. These ratios identify that the research effort most poignant to IC design revolves around verification. The verification process can be viewed in a hierarchical manner with reusable IP cores, SoC leave cells. Thus, the SoC design methodology can be divided into the following: identification of system requirements, writing preliminary specifications, developing high-level algorithmic

models, refining and testing algorithms, determining hardware/software requirements (characterizing the library of hardware/software macros & interface protocols), defining interfaces, partitioning device components into macros, and writing preliminary specifications for the macros.

| Task               | Time Ratio (%) |

|--------------------|----------------|

| Verification       | 40             |

| RTL + Synthesis    | 20             |

| IC Layout          | 10             |

| Test               | 10             |

| System Integration | 10             |

| Other              | 10             |

Table 2-1 Shown are the catastrophic fault results on LCD, in which the fourtransistors for the VLSI adaptation of the Chemical Field Effect Transistorshave an error of 4x in their respective W/L ratio.

System-on-Chip (SoC) and mixed-signal devices in the marketplace will continue to increase rapidly as the semiconductor electronics industry enters the era of multimillion-gate chips. It has been predicted by some that within the next few years, state-of-the-art integrated circuits (ICs) will exceed 12 million gates and operate at speeds surpassing 600 MHz [14]. The IC industry has found that manufacturing costs for these devices are dominated by the direct and indirect costs associated with testing [15]. Involved in testing an IC are the direct costs associated with procurement of test equipment and time to test and the indirect costs of developing test procedures. Moreover, the analog portion of mixed analog/digital circuitry although making up less than 10% of the overall chip area, has test procedures that tend to dominate the test time of mixed technology chips. This is due to the following:

- Accurate analog signal sources must be fabricated onto the circuit under test (CUT).

- Specialized equipment containing precision circuitry must be used to test Analog-to-Digital converters (ADCs) and Digital-to-Analog converters (DACs).

- 3. Current methods for testing ADCs and DACs require the use of expensive test equipment.

- 4. Cables that run from the CUT to the ADC's and DAC's of the tester often introduce parasitics that affect the performance of the chip [11].

Built-In Self-Test methods are expected to assist designers in avoiding many of these concerns. A necessary challenge to overcome involves ensuring the testability of an IC design. This is a formidable task as testability within the context of integrated circuits is not well defined. Testability is defined as controllability and observability of significant waveforms within a circuit structure [16]. For most IC designers, significant waveforms are input/output signals that can be obtained at every stage of a circuit design. The first stage of the circuit, input, is assumed to be controllable; while, the last stage, output, is observable.

#### Section 2.3 Built-In Self-Test

BIST methods will prove invaluable in assessing the real time accuracy and functionality of system-on-a-chip devices. Mixed signal BIST, in particular, will see increased usage in devices [17]. Despite the general consensus that suggests BIST as a relatively new technology, its principles have been used as part of high-performance analog design processes for several years [18]. Mixed signal BIST is used extensively in most auto-calibration techniques and feedback loops. However, to date no published approach performs on chip measurements of all key intellectual property (IP) device parameters (including analog-to-digital (ADC) and digital-to-analog (DAC) converters) while keeping time to test lower than conventional automatic test equipment (ATE) [19]. In general the field of mixed signal design and test has seen that simulations, silicon performance, and economic feasibility are continuously in competition with one another. For example, BIST circuit gate area is of economic importance because it increases IC area and because IP providers tend not to compare the BIST area to the overall IC circuit, but solely to the circuit-under-test (CUT) [20].

The problem with testing mixed-signal circuits arises from the fact that digital and analog fault models are inherently different. While digital fault models are understood to be stuck-at faults, analog fault models not quite as well defined or mature [21]. Moreover, analog signals are imprecise. Therefore, the accuracy of the measurement becomes a key concern. This represents a stark contrast to the logic '1' or '0' measurements of digital circuits. The many advantages of BIST cannot be fully exploited in mixed-signal circuits as long as the analog portions of mixed-signal technologies remain unsure. As such, in recent years, analog and mixed-signal

circuits have grown in importance and as a consequence several researchers have begun to address the problem of BIST for analog and mixed-signal circuits [9,10].

There are in general two categories of BIST techniques: functional and faultbased. Functional BIST apply traditional stimuli, such as sinusoidal or multi-tone waveforms, and measure the functional specifications of the circuit under test (CUT). Fault-based BIST techniques, however, are designed to detect faults using unconventional stimuli and signatures. Most of the BIST schemes test the analog blocks in a mixed-signal circuit using the digital-analog-digital path. This is unlike the analog-digital-analog path used by conventional external tests.

Several functional BIST schemes have been proposed for special classes of analog and mixed-signal circuits. Many of these schemes are based on on-chip functional testing of analog specifications including signal-to-noise ratio (SNR), frequency response and intermodulation distortion. Moreover, mixed-signal circuits with on-chip digital signal processing (DSP) cores may be used to perform DSPbased Fast Fourier Transform (FFT) testing. Here, the DSP core generates a 512point sinusoidal input stimulus that is applied to the ADC via the DAC. An FFT analysis of the output response from the ADC is used to measure the combined performance of the DAC and ADC.

For circuits that do not contain a DSP core, the area overhead of performing an FFT analysis is extremely high. To counteract this, digital filtering techniques can be used. In these instances, on-chip sine or multi-tone test stimulus is generated using an over sampling based signal generator. Although, this generator is predominantly digital it includes an imprecise low pass filter. A narrow band digital filter is used to

measure the output performance of the circuit by separating the signal from noise power. As such the filter must be carefully designed to minimize the bias in test results.

Other BIST structures revolve around testing offset, gain, integral and differential linearity of DACs and successive approximation type ADCs. For these methods, a counter is used to generate the test stimulus and the output is sampled and compared with an appropriate reference voltage, which is selected by an analog multiplexer.

In contrast, fault-based tests are aimed at detecting manufacturing defects, which are modeled as faults, as opposed to measuring the functional specifications. In fact, several fault test schemes have been proposed that use different kinds of waveforms as test stimuli, which are easy to generate on-chip. These schemes typically compress the output response into various signatures. However, as a result of the imprecise nature of analog circuits and the absence of a direct mapping been the signatures and functional specifications, it is possible the test may result in a "fail" response for good circuits. As such, these BIST approaches for analog circuits must be evaluated not only on the basis of area overhead and fault coverage, but also yield coverage.

HBIST is a fault-based BIST scheme for mixed signal (hybrid) circuits. It allows the evaluation of analog test responses within a digital kernel system. Analog test stimuli, provided by the Hybrid Test Stimulus Generator (HTSG, an on-chip generator) are based on digital shift registers, which are used as signature analyzers. This digital BIST scheme has a very low area and performance impact. To overcome

the limitation of digital signatures, which inherently cannot accommodate tolerances in analog signals, a pattern manipulator is used to prevent the application of those input values that place the output response within the tolerance range of the comparator.

Another fault-based BIST method involves an analog signature analysis scheme that accommodates tolerances in analog signals. This method uses digital integration to accumulate the analog test response signature and computes the probabilities of aliasing and false rejection as a function of circuit tolerances and the signature register width. The absolute value of the signal is taken before integrating to reduce aliasing due to fault masking. The use of an analog integrator as a signature analyzer is also a feasible solution. Additionally, another on-chip test response measurement technique that takes into account the tolerance of signals uses special detectors, window comparators, for verifying whether or not the parameters converted to voltages are within an acceptable window.

A test technique for analog linear time-invariant (LTI) circuits embedded between DAC and ADC involves the linear transformation of the output sequence. This transformation of the input random process is analyzed by the first and second moments (mean, auto- and cross-correlations). These signatures are computed using digital arithmetic operations and have been compared with respect to fault coverage, hardware overhead and testing time. Correlations have better fault coverage than the mean. Autocorrelation requires less hardware and testing time compared to cross correlation. Further, research has shown that cross-correlation signatures are an approximation to a circuit's impulse response [22]. Another pseudorandom test

technique, the Fischer method, is used as a discrimination technique to define the boundaries of the signature space in order to maximize the fault and yield coverage and minimize the number of signatures required. Logistic discrimination analysis has also been used to select a minimal set of measure and tests consisting of DC and low frequency AC stimuli.

A concurrent test method for linear analog circuits, is one in which tests are based on continuous checksums. The checking circuit is implemented by a cascade of integrators and is virtually fixed regardless of the size of the original circuit. This scheme generates a non-zero signal in the case of fan error in the ac transfer function of the circuit. The method can be simplified for application to DC testing.

Another approach to fault-based testing involves self-checking analog circuits as presented by Vinnakota and Harjani [23]. In this work we see the way in which dual-rail code can be used to design self-checking fully differential analog circuits. The underlying methodology is geared towards the detection of transient faults.

A final style of BIST schemes involves low-cost vectorless BIST schemes that eliminate the need for test stimuli selection and application. These schemes convert the circuit into an oscillation mode during test. Faults cause the circuit to either stop oscillating or result in an oscillation frequency that differs beyond the tolerance range of the circuit's nominal value. The oscillation frequency can be evaluated using pure digital circuitry and interfaced to the boundary scan. The test method consists of portioning the complex circuit into functional building blocks such as operational amplifier, comparator, filter, PLL, etc., which are converted into circuits oscillate by adding additional circuitry or by cutting the damping loops and digitally

programming the filter coefficients. This process tends to achieve significant reduction in test times as compared to traditional testing methods. The oscillation test strategy is of particular interest and will be discussed in further detail in the following section.

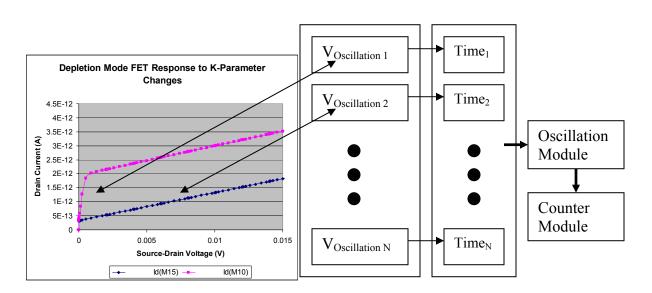

#### Section 2.4 Built In Self Test with Oscillation Test Strategy

The oscillation test strategy (OTS) created by Arabi and Kaminska works by partitioning a complex analog circuit into functional building blocks such as: amplifier, operational amplifier (opamp), comparator, Schmitt trigger, filter, voltage reference, oscillator, phase lock loop (PLL), etc. or a combination of these blocks [24]. During the test mode, by adding some additional circuitry, each building block is converted to a circuit producing sustained oscillations. The oscillation frequency f<sub>osc</sub> can be expressed either as a function of the CUT components or as a function of its important parameters. The building blocks that inherently generate a frequency such as oscillators do not need to be rearranged and their output frequency is directly evaluated. All operations are managed using control logic (CL).

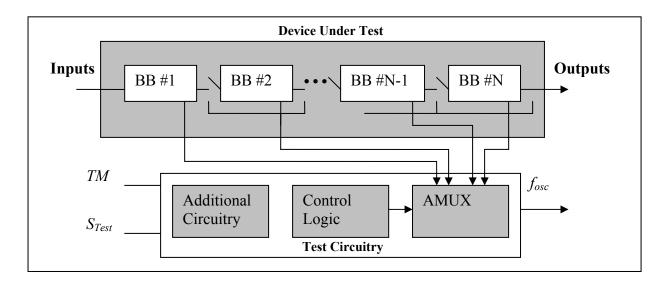

Figure 2.1 below illustrates the application of the OTS method as a design for test (DFT) technique to improve the testability and ease the test problem. In the test mode, the CUT is partitioned into building blocks that are converted to oscillators using some additional circuitry. An analog multiplexer (AMUX) selects the output of the building block under test and its oscillation frequency is externally evaluated using test equipment. Before starting the test procedure the functionality of the test circuitry is verified by activating the test signal.

Figure 2.1 Simplified Test Structure of the Oscillation Test Strategy

The first step for this on-chip test method involves converting an analog building block to an oscillator with the use of appropriate feedback loops and adjustments to ensure sustainable oscillations. Depending on the CUT the feedback loop can be negative, positive or a combination of them.

Observability of a fault in a component  $C_i$  (or a parameter  $P_i$ ) is defined through the sensitivity of the oscillation frequency  $f_{osc}$  with respect to the variations of the component  $C_i$  (or the parameter  $P_i$ ). To increase the observability of a defect in a component (or a fault in a parameter), the sensitivity of the oscillation frequency with respect to that component (or parameter) should be increased. In other words, during the conversion process of the CUT to an oscillator, the oscillator architecture must be chosen to insure the maximum possible number of contributions for each of the CUT components to the resulting oscillation frequency. Existing faults in the CUT related to components (or parameters that are involved in the oscillator structure manifest themselves as a deviation of the oscillation frequency. Therefore, the deviation of the oscillation frequency from its nominal value may be employed to testify to the existence of a fault. The tolerance band of  $f_{osc}$  for each CUT is determined using a Monte Carlo analysis taking into account the nominal tolerance of all important technology and design parameters. The accuracy necessary for additional circuitry is around the same accuracy provided for other CUT components.

The process of evaluating the OTS method involves understanding the fault modeling process. Analog fault modeling, for example, involves either parametric (soft) or catastrophic (hard) faults. Parametric faults, caused by statistical fluctuations in the manufacturing process, comprise the small deviation of CUT parameters from their tolerance band. Catastrophic faults are introduced by random defects and result in failures in various components. They are provoked, for example, by dust particles on a photolithographic mask which may cause either a short (open circuit), or large deviation of CUT parameters from their tolerance band such as width-to-length (W/L) ratio of a MOS transistor [25, 26].

Many studies have been devoted to determine the dominant fault type and to define the appropriate fault models. Research results denoted that 80-90 percent of observed analog faults were catastrophic faults consisting of shorts and opens in diodes, transistors, resistors and capacitances [27, 28]. It was also found that a test method which detects 100% of catastrophic faults did also find the majority of soft faults depending on the deviation value of the soft fault. The occurrence probability of faults has also been considered by Arabi and Kaminska. Their studies suggest that

catastrophic faults, and especially short faults, are dominant in both bipolar and CMOS processing technologies.

The catastrophic faults considered by Arabi and Kaminska in the evaluation of the OTS method comprise all possible shorts between circuit nodes and open faults at all circuit nodes excluding the transistor gates. An open fault was simulated by introducing a 10 M-ohm resistor. A short fault was modeled by a 10 ohm resistor.

A general method useful for converting an analog building block to an oscillator consists of adding a feedback loop to its structure and then adjusting the feedback elements to establish and sustain oscillation. Depending on the CUT the feedback loop can be negative, positive or a combination. The area overhead depends on the CUT and the chosen oscillator structure. In the case where a single oscillation frequency is not sufficient to cover all target faults, a suitable element of the feedback may be varied to produce different oscillation frequencies.

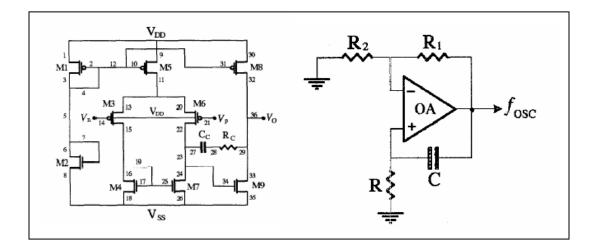

The OTS method was evaluated against a two stage CMOS operational amplifier (circuit under test) figure 2.2 below. This oscillator employs both positive and negative feedback. The op-amp is first converted to a limited-gain amplifier and then cascaded with a simple RC high-pass filter to construct a band-pass circuit. If the gain of the pass-band system is slightly greater than unity at its central frequency, connecting the output of the band-pass circuit to its input will result in sustained

Figure 2.2 The schematic on the left is a 2-Stage CMOS Operational Amplifier Schematic. Circuit Under Test for OTS [9]. The schematic on the right represents the oscillation feedback system created with the additional resistors and capacitor.

oscillations at its central frequency. In reality noise at the input of the system is bandpass filtered, slightly amplified, and then fed back to the input, and the same action is repeated. Therefore, the system tends to oscillate at its central frequency. The amplitude of oscillations is limited by non-linear properties of the op-amp. The higher the quality-factor is of the band-pass system the purer the sinusoidal oscillation frequency. The equation model for the op-amp and oscillator follow.

The total amplifier dc open-loop gain is given by [29]

$$a_{v} = \frac{g_{m3}g_{m9}}{(g_{ds6} + g_{ds7})(g_{ds8} + g_{ds9})}, (2.1)$$

where the channel conductances,  $g_m$  and  $g_{ds}$ , are defined as

$$g_{m} = \frac{\partial i_{D}}{\partial v_{GS}} \left| I_{D} \cong \sqrt{\left(2\mu_{o}C_{ox}W/L\right)} I_{D} \right|, (2.2)$$

$$g_{ds} = \frac{\partial i_D}{\partial v_{BS}} | I_D \cong I_D \lambda, (2.3)$$

in which  $\mu_o$  is the channel surface mobility,  $C_{ox}$  is the capacitance per unit area of the gate oxide, W and L are effective channel width and length, respectively, and  $\lambda$  is the channel length modulation parameter of the transistor. The current  $I_D$  represents the quiescent current and is provided by M1, M2, and M5 transistors, assumed to operate in the saturation region.

The unity-gain bandwidth of the operational amplifier is calculated as follows

$$\omega_T = -a_v p_1 = g_{m1} / C$$

. (2.4)

As the operational amplifier is compensated, its transfer function can be given by a single pole transfer function

$$a_{v}(s) = \frac{a_{v}}{1 - s / p_{1}} \quad (2.5)$$

approximated by,

$$a_v(s) \approx \frac{-a_v p_1}{s} \quad (2.6)$$

in which  $p_1$  represents its dominant pole.

The affects of adding the positive and negative feedback loops (to produce oscillation frequency,  $f_{osc}$ ) are shown by the equations that follow. The positive feedback loop consists of an RC delay and the negative feedback comprises a voltage divider. To facilitate the mathematical analysis the combination of feedback loop is presented by a singe negative feedback block in which the positive feedback appears as a term with negative sign. The feedback block converts the operational amplifier under test to a second order system which has the potential of oscillation. The new transfer function is derived as follows

$$A_{v}(s) = \frac{a_{v}(s)}{1 + a_{v}(s)f(s)}$$

(2.7)

. .

where,

$$f(s) = G - \left(\frac{-s/p_2}{1 - s/p_2}\right)(2.8)$$

By substituting  $a_{v}(s)$  and f(s) in  $A_{v}(s)$  we obtain

$$A_{\nu}(s) = \frac{a_{\nu}p_1(p_2 - s)}{s^2 + ((1 - G)a_{\nu}p_1 - (p_1 + p_2))s + (Ga_{\nu}p_1p_2 + p_1p_2)}.$$

(2.9)

The system poles are obtained by equating the denominator of the new transfer function to zero. In order to construct an oscillator from this new transfer function, its poles must be placed on the imaginary axis in the s- domain by forcing the coefficient of the term s to zero which is realized by proper selection of the value of G as follows

$$G = 1 - \frac{p_1 + p_2}{a_v p_1} (2.10).$$

The conversion of the circuit under test's analog signal to an oscillating frequency signal is modeled by the following equations. The natural oscillation frequency for the new system is given by

$$\omega_{osc}^{2} = Ga_{v}p_{1}p_{2} + p_{1}p_{2} = a_{v}p_{1}p_{2} - p_{2}^{2}.$$

(2.11)

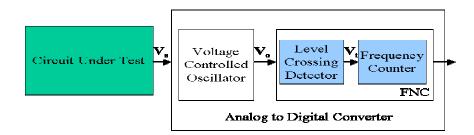

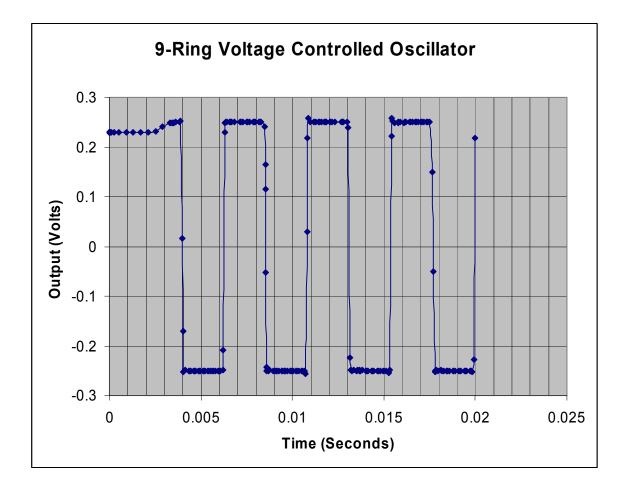

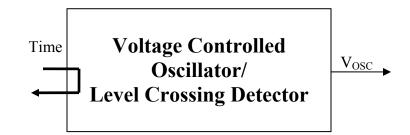

In which the oscillation frequency,  $f_{osc}$ , is  $\frac{\omega_{osc}}{2\pi}$ . This oscillation frequency strongly depends on important characteristics of the operational amplifier (or circuit) under test which, are determined by all components of the device. Existing faults in the device under test will show a deviation in device characteristics from their nominal value. This can be monitored as above by observing the oscillation frequency. With the development of the oscillating signal comes the need for conversion with a frequency to number converter (FNC) as shown by figure 2.3.

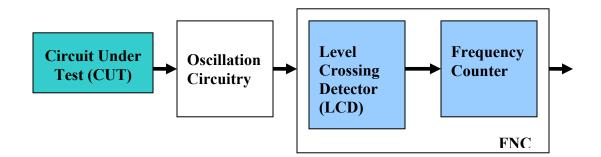

Figure 2.3 Block Based Design of Signal Conversion Process

In order to evaluate the oscillation frequency coming from a building block in the test mode, the frequency is first converted to a corresponding number. The figure above shows the block diagram of the frequency to number converter (FNC). The FNC is comprised of a level crossing detector and a frequency counter. It uses a simple and fully digital circuit which converts each frequency to a related number. The oscillation frequency  $f_{osc}$  of the selected building block is first passed through a level-crossing detector (LCD) to obtain a rectangular waveform compatible with logic levels and is then applied to a counter. The counter is enabled by the high level of reference frequency (  $f_{\rm REF}$  ), therefore during the high state of the reference frequency the counter counts, and during its low state the center is disabled and stops counting. The output value of the counter contains a number which is related to its input frequency, coming from the building block under test, and can be evaluated by the control logic (CL) during the low-state of  $f_{REF}$ . The CL resets the counter after evaluating its output number. Therefore, an accurate frequency-to-number conversion is obtained. The accuracy of the system is determined by the reference

frequency and the bit number of the counter M. The digital output value is given

by

$$B = \frac{f_{osc}}{2f_{REF}}$$

.

This technique provides reasonable accuracy and satisfies the requirements of the application. A schematic representation of the LCD implemented in CMOS is shown in the figure 2.4 below. The LCD is designed using a CMOS current source inverter which acts as a comparator. The current source is a common gate configuration using a p-channel transistor with the gate tied to a dc bias voltage. The bias voltage has been adjusted to obtain a trip voltage  $V_{TRP} = 1V$ . The trip voltage is given by the input voltage required to make the current of the transistor M1 equal to the bias current I<sub>B</sub>. The gain of the comparator is given as

$$\frac{V_{OUT}}{V_{IN}} = \frac{-g_{m1}}{g_{ds1} + g_{ds2}} = \left(\frac{2K_N'W_1}{L_1I_B}\right)^{1/2} \left(\frac{-1}{\lambda_1 + \lambda_2}\right), (2.12)$$

where W<sub>1</sub> and L<sub>1</sub> are the effective channel width and length,  $K'_N = \frac{\mu C_{ox}}{2}$  is the transconductance parameter and  $\lambda$  is the channel length modulation parameter of the transistor M1.

Whereas a great deal of progress continues to be made in the area of built-in self-test for mixed signal technologies, the problem is far from being solved. This is due to the fact that issues such as area and performance overhead, fault model/coverage, the DFT/BIST automation process and interface to digital tools need to be resolved first. Today very complex mixed-signal multi-chip modules (MCMs) are being designed and in the future, such MCMs will contain buried passives, optoelectronic interconnections, RF components and very closely coupled digital and analog parts. Therefore, the problem of design for testability (DFT) and built-in selftest will continue to be of great concern to researchers in the semiconductor industry. The research discussed in chapters 3 and 4, address many of the concerns surrounding the development of a robust method of performing on-chip test of multiple types of mixed signal IP.

**Figure 2.4 Level Crossing Detector**

# Section 2.5 SystemC and System-on-a-Chip Modeling

Essential to today's semiconductor industry is rapid delivery SoCs. As such, early and accurate modeling of an entire system is essential for lowering the time-tomarket of complex embedded devices. Modeling SoCs requires the development of system-level design specifications that define both the hardware and embedded software contained within SoCs [30]. Full system modeling of sensors and related SoC devices typically involves the analysis of circuit equations that describe the functionality of the system.

Much of today's analog modeling is limited to computer-aided electrical circuit analysis software such as SPICE and VHDL-AMS (Very High Speed Hardware Description Language – Analog Mixed Signal). VHDL-AMS is a standard, which serves to unify hardware description languages while making the libraries of elements that could be accessible by other users or designers. While SPICE is a design tool that falls into the category of general purpose analog circuit simulators.

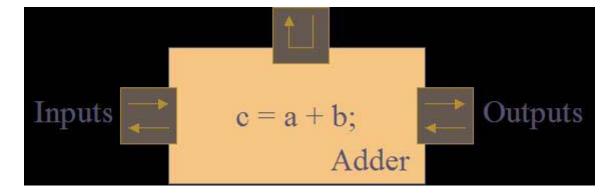

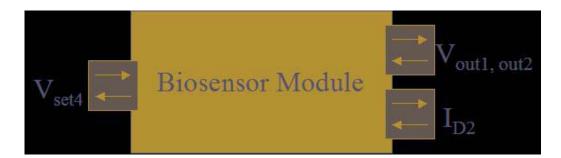

SPICE is used for initial design development, debugging and performing system diagnostics. With SPICE simulation, circuit blocks may be represented as behavioral elements and simulated in a functional form. Behavioral elements allow designers to test circuit theory without the time involved in developing transistor and component-level descriptions of each circuit function. System on a Chip models differ from previous work [31, 32] in that they are developed to be system modules that can be applied to System-C library and Malab/Simulink environments.

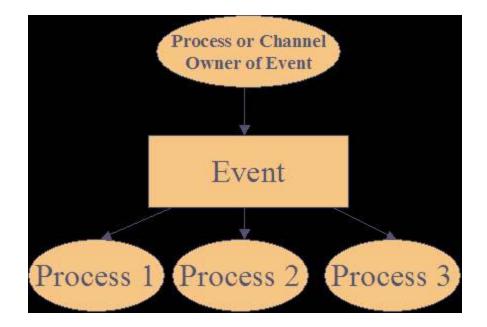

SystemC and other hardware description languages (HDLs) make it easy to combine multiple IP blocks into a single simulation. As such, SoC models of mixed signal technologies are developed from high-level descriptions of circuit operations. The approach to module development (system level design) of biosensors and mixed signal technologies involves creating the full model of the device and capturing the inputs and outputs between each stage of the system. The output of the systems modules are then compared against simulated outputs of electrical equivalent circuits.

The system module development scheme used for systems-on-a-chip augment traditional methods of developing models of biosensor devices and facilitates the incorporation of these sensors in SoC designs.

The semiconductor industry will soon see software and hardware design streamlined into a single flow process. The increasing complexity of SoCs has introduced the need for abstract executable specifications that cover both hardware and embedded software. Hardware description languages (HDLs) like SystemC ameliorate the development of such specifications (models).

#### SystemC Background

SystemC is like a standard design and verification language that spans from concept to implementation in hardware and software. Prior to 1999 there were many proprietary C or C++ based SoC design environments that did not have an open standard. As such their usefulness was limited since model availability from IP vendors did not exist. SystemC was developed by the Open SystemC Initiative (OSCI), a consortium of major EDA and IP companies that contributes to and governs SystemC development and distribution. It has now become the de facto standard for system level design. As such, IP vendors are beginning to provide SystemC compatible models of their IP.

SystemC is based on C++. One of the objectives of the language is to improve overall productivity for designers of electronic systems. In many cases, today's systems contain application-specific hardware and software. Additionally, the hardware and software are usually co-developed on a tight schedule, the systems

have tight real-time performance constraints, and thorough functional verification is required to avoid expensive and sometimes catastrophic failures.

SystemC allows engineers to design both the hardware and software components together as these components would exist on the final system, but at a high level of abstraction. This higher level of abstraction gives the design team a fundamental understanding early in the design process of the intricacies and interactions of the entire system and enables better system trade offs, better and earlier verification, and overall productivity gains through reuse of early system models as executable specifications.

As with most design languages, SystemC has evolved. SystemC is the result of the evolution of many concepts in the research and commercial EDA communities. Many research groups and EDA companies have contributed to the language. The language began as a very restrictive cycle-based simulator, essentially an RTL language. It is now evolving into a true system design language that includes both software and hardware concepts. Although SystemC does not specifically support analog hardware or mechanical components, there is no reason why these aspects of a system cannot be modeled with SystemC constructs or with co-simulation techniques.

SystemC is not a traditional programming language, it is a class library within a well established language, C++. SystemC is not a panacea that will solve every design productivity issue. However, when SystemC is coupled with the SystemC Verification Library, it does provide in one language many of the characteristics relevant to system design and modeling tasks that are missing or scattered among the

other languages. Additionally, SystemC provides a common language for software and hardware, C++.

The SystemC Verification (SCV) library is a methodology-specific library. It is the most significant of the potential libraries used by SystemC. This library adds support for modern high-level verification language concepts such as constrained randomization, introspection, and transaction recording. The first release of the SCV library occurred in December of 2003 after over a year of Beta testing.

# **Design Methods**

Design methods surrounding SystemC are currently maturing and vary widely. In the next few years, these methods will settle into a cohesive design methodology (with a few variants among certain industry segments). The resulting methodology will feel similar to the methodologies in use today, but at higher levels of abstraction. To some, the concept of using one unified language for hardware and software development appears revolutionary, but this concept is clearly an evolutionary path for those who frequently work in both domains.

Although tools and language constructs exist in SystemC to support registertransfer-level (RTL) modeling and synthesis, a major reason for using the language is to work at higher abstraction levels than RTL. SystemC's ability to model RTL designs enables support of design blocks generated by higher level (behavioral or graphical entry) synthesis tools or to support legacy design blocks.

#### **Benefits of SystemC**