# Title of dissertation:MODERN DRAM MEMORY SYSTEMS:<br/>PERFORMANCE ANALYSIS AND A HIGH<br/>PERFORMANCE, POWER-CONSTRAINED<br/>DRAM SCHEDULING ALGORITHMDavid Tawei Wang, Doctor of Philosophy, 2005Dissertation directed by:Associate Professor Bruce L. Jacob<br/>Department of Electrical and Computer Engineer-<br/>ing, and Institute for Advanced Computer Studies

ABSTRACT

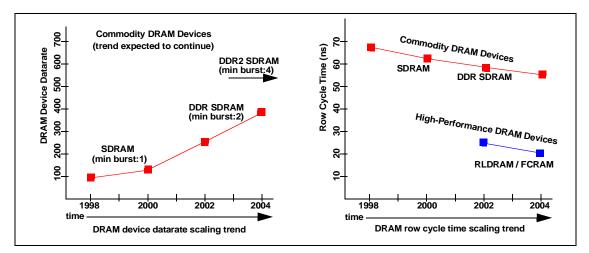

The performance characteristics of modern DRAM memory systems are impacted by two primary attributes: device datarate and row cycle time. Modern DRAM device datarates and row cycle times are scaling at different rates with each successive generation of DRAM devices. As a result, the performance characteristics of modern DRAM memory systems are becoming more difficult to evaluate at the same time that they are increasingly limiting the performance of modern computer systems. In this work, a performance evaluation framework that enables abstract performance analysis of DRAM memory systems is presented. The performance evaluation framework enables the performance characterization of memory systems while fully accounting for the effects of datarates, row cycle times, protocol overheads, device power constraints, and memory system organizations.

This dissertation utilizes the described evaluation framework to examine the performance impact of the number of banks per DRAM device, the effects of relatively static DRAM row cycle times and increasing DRAM device datarates, power limitation constraints, and data burst lengths in future generations of DRAM devices. Simulation results obtained in the analysis provide insights into DRAM memory system performance characteristics including, but not limited to the following observations.

- The performance benefit of having a 16 banks over 8 banks increases with increasing datarate. The average performance benefit reaches 18% at 1 Gbps for both open-page and close-page systems.

- Close-page systems are greatly limited by DRAM device power constraints, while open-page systems are less sensitive to DRAM device power constraints.

- Increasing burst lengths of future DRAM devices can adversely impact cache-limited processors despite the increasing bandwidth. Performance losses of greater than 50% are observed.

Finally, This dissertation also present a unique rank hopping DRAM commandscheduling algorithm designed to alleviate the bandwidth constraints in DDR2 and future DDRx SDRAM memory systems. The proposed rank hopping scheduling algorithm schedules DRAM transactions and command sequences to avoid the power limiting constraints and amortizes the rank-to-rank switching overhead. Execution based simulations show that some workloads are able to fully utilize the additional bandwidth and significant performance improvements are observed across a range of workloads.

### MODERN DRAM MEMORY SYSTEMS: PERFORMANCE ANALYSIS AND SCHEDULING ALGORITHM

by

David Tawei Wang

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2005

Advisory Committee:

Associate Professor Bruce L. Jacob, Chair Associate Professor Shuvra S. Bhattacharyya Associate Professor Tsung Chin Associate Professor Donald Yeung Associate Professor Charles B. Silio Jr. © Copyright by

David Tawei Wang

2005

# Table of Contents

| CHAPTER 1 | Introduction 1                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1.1 Problem Description                                                                                                                                                                                                                    |

|           | 1.2 Contributions and Significance                                                                                                                                                                                                         |

|           | 1.3 Organization of Dissertation                                                                                                                                                                                                           |

| CHAPTER 2 | DRAM Device: Basic Circuits and Architecture .       7         2.1 Introduction:       7         2.2 DRAM Device Organization       8         2.3 DRAM Storage Cells       11         2.3.1 Cell capacitance, Leakage and Refresh       11 |

|           | 2.4 DRAM Array Structures                                                                                                                                                                                                                  |

|           | 2.5 Differential Sense Amplifier                                                                                                                                                                                                           |

|           | 2.5.1Functionality of Sense Amplifiers in DRAM Devices152.5.2Circuit Diagram of a Basic Sense Amplifier16                                                                                                                                  |

|           | 2.5.2       Circuit Diagram of a basic sense Amplifier       10         2.5.3       Basic Sense Amplifier Operation                                                                                                                        |

|           | 2.5.4 Voltage Waveform of Basic Sense Amplifier Operation 20                                                                                                                                                                               |

|           | 2.5.5 Writing into DRAM Array 22                                                                                                                                                                                                           |

|           | 2.6 DRAM Device Control Logic                                                                                                                                                                                                              |

|           | 2.6.1 Mode Register Based Programmability 25                                                                                                                                                                                               |

|           | 2.7 DRAM Device Configuration                                                                                                                                                                                                              |

|           | 2.7.1 Device Configuration Trade-offs 27                                                                                                                                                                                                   |

|           | 2.8 Data I/O                                                                                                                                                                                                                               |

|           | 2.8.1         Burst Lengths and Burst Ordering         29           2.8.2         N-bit Prefetch                                                                                                                                           |

|           | 2.9 DRAM Device Packaging                                                                                                                                                                                                                  |

|           | 2.10 A 256 Mbit SDRAM Device                                                                                                                                                                                                               |

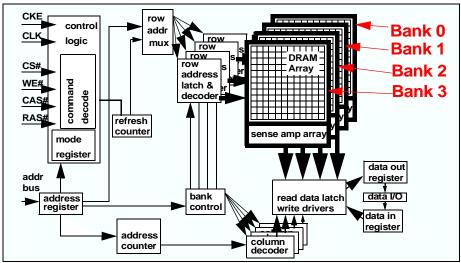

|           | 2.10.1 SDRAM Device Block Diagram 34                                                                                                                                                                                                       |

|           | 2.10.2 Pin Assignment and Functionality 35                                                                                                                                                                                                 |

|           | 2.11 Process Technology and Scaling Considerations                                                                                                                                                                                         |

|           | 2.11.1 Cost Considerations 37                                                                                                                                                                                                              |

|           | 2.11.2 DRAM-versus-Logic Optimized Process Technologies 38                                                                                                                                                                                 |

| CHAPTER 3 | DRAM Memory System Organization 41                                                                                                                                                                                                         |

|           | 3.1 Conventional Memory system 41                                                                                                                                                                                                          |

|           | 3.2 Basic Nomenclature                                                                                                                                                                                                                     |

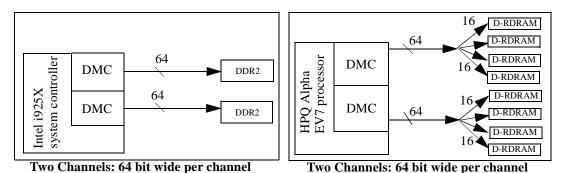

|           | 3.2.1 Channel 44                                                                                                                                                                                                                           |

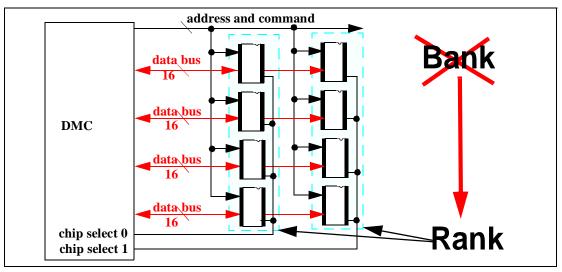

|           | 3.2.2 Rank 48                                                                                                                                                                                                                              |

### TABLE OF CONTENTS

| 3.2.3 Bank     |                                   | 49 |

|----------------|-----------------------------------|----|

| 3.2.4 Row -    |                                   | 50 |

| 3.2.5 Column   | ,                                 | 51 |

| 3.2.6 Memory   | y System Organization: An Example | 52 |

| 3.3 Memory     | Modules                           | 53 |

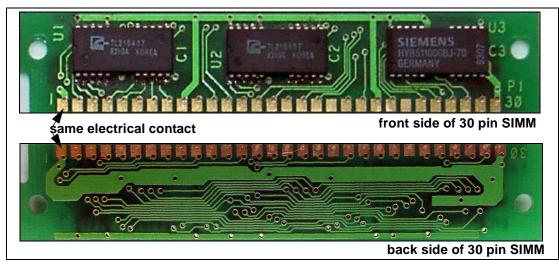

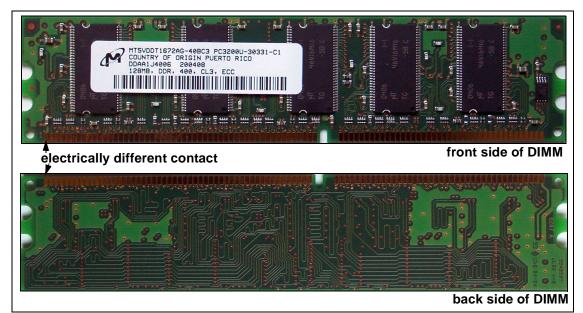

| 3.3.1 Single I | n-line Memory Module (SIMM)       | 55 |

| 3.3.2 Dual In  | -line Memory Module (DIMM)        | 56 |

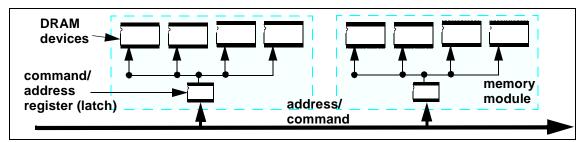

| 3.3.3 Register | red Memory Module                 | 57 |

| 3.3.4 Memory   | y Module Organization             | 59 |

| 3.3.5 Serial P | Presence Detect (SPD)             | 60 |

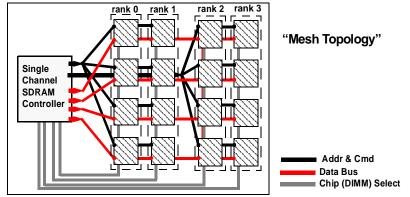

| 3.4 Memory     | System Topology                   | 61 |

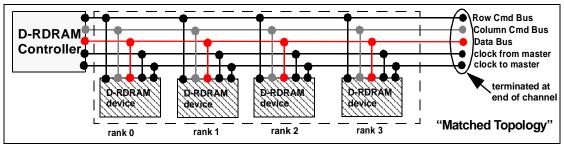

| 3.4.1 Direct H | RDRAM System Topology             | 62 |

#

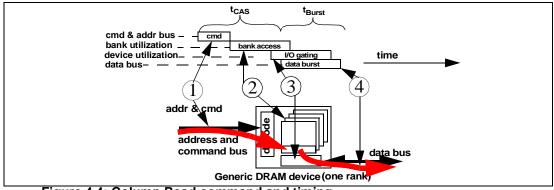

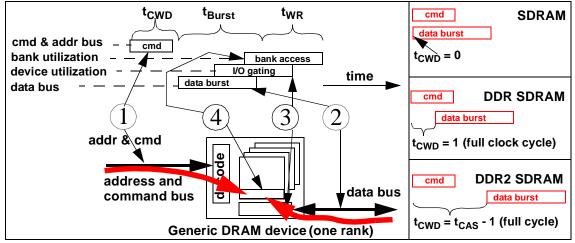

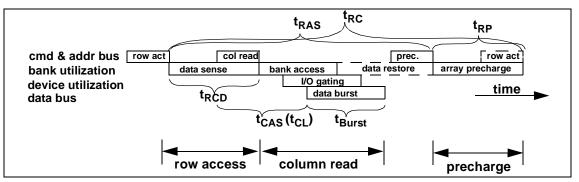

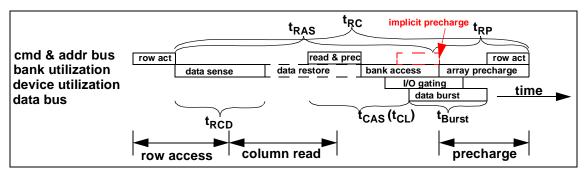

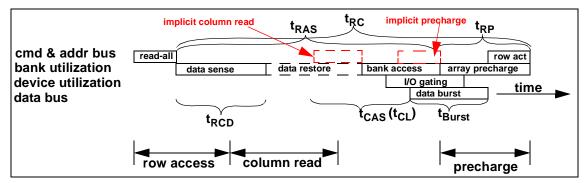

| 4.1.1Generic DRAM Command Format674.1.2Summary of Timing Parameters694.1.3Row Access Command704.1.4Column Read Command714.1.5Column Write Command724.1.6Precharge Command734.1.7Refresh Command744.1.8A Read Cycle774.1.9Complex Commands784.2DRAM Command Interactions81                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1.3       Row Access Command       70         4.1.4       Column Read Command       71         4.1.5       Column Write Command       72         4.1.6       Precharge Command       73         4.1.7       Refresh Command       74         4.1.8       A Read Cycle       77         4.1.9       Complex Commands       78 |

| 4.1.4Column Read Command714.1.5Column Write Command724.1.6Precharge Command734.1.7Refresh Command744.1.8A Read Cycle774.1.9Complex Commands78                                                                                                                                                                                  |

| 4.1.5       Column Write Command       72         4.1.6       Precharge Command       73         4.1.7       Refresh Command       74         4.1.8       A Read Cycle       77         4.1.9       Complex Commands       78                                                                                                  |

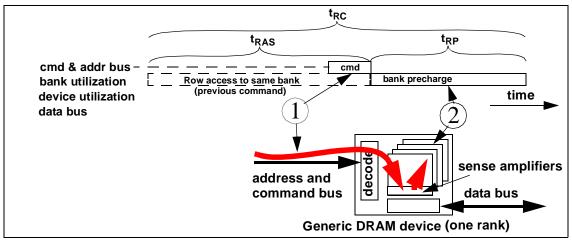

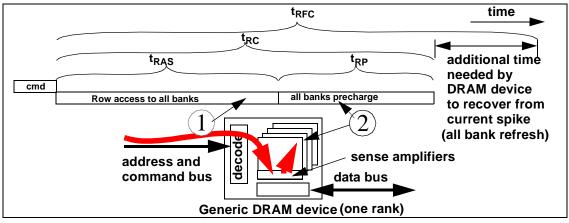

| 4.1.6       Precharge Command       73         4.1.7       Refresh Command       74         4.1.8       A Read Cycle       77         4.1.9       Complex Commands       78                                                                                                                                                    |

| 4.1.7       Refresh Command       74         4.1.8       A Read Cycle       77         4.1.9       Complex Commands       78                                                                                                                                                                                                   |

| 4.1.8         A Read Cycle         77           4.1.9         Complex Commands         78                                                                                                                                                                                                                                      |

| 4.1.9 Complex Commands 78                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                |

| 4.2 DRAM Command Interactions                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                |

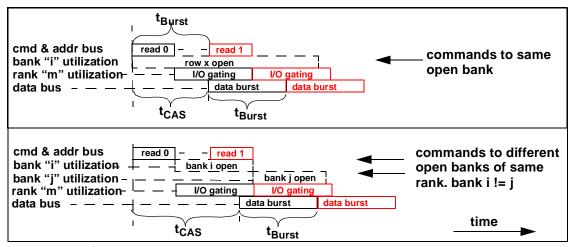

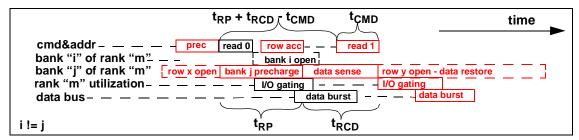

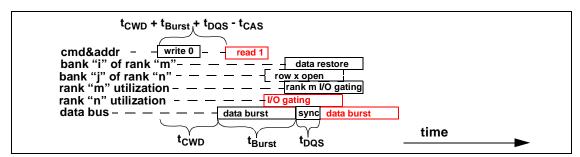

| 4.2.1 Consecutive Reads to Same Rank 82                                                                                                                                                                                                                                                                                        |

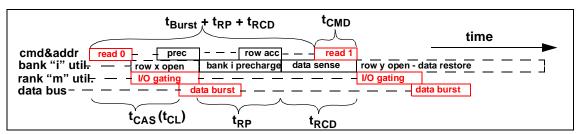

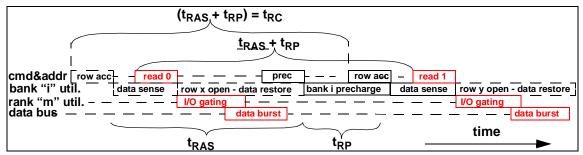

| 4.2.2 Consecutive Reads to Different Rows of Same Bank 83                                                                                                                                                                                                                                                                      |

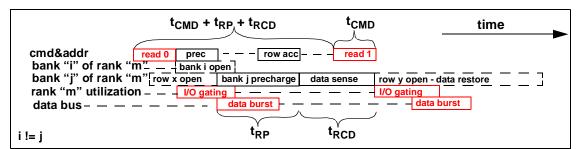

| 4.2.3 Consecutive Reads to Different Banks: Bank Conflict 86                                                                                                                                                                                                                                                                   |

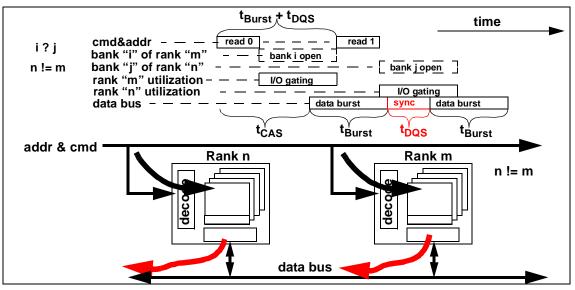

| 4.2.4 Consecutive Read Requests to Different Ranks 88                                                                                                                                                                                                                                                                          |

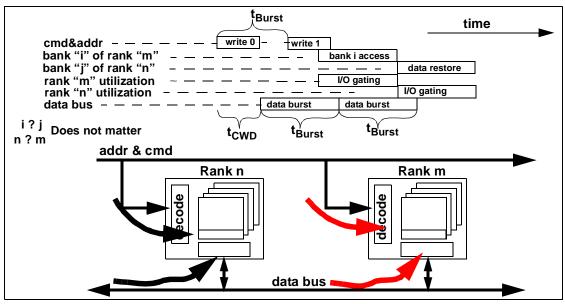

| 4.2.5 Consecutive Write Requests: Open Banks 89                                                                                                                                                                                                                                                                                |

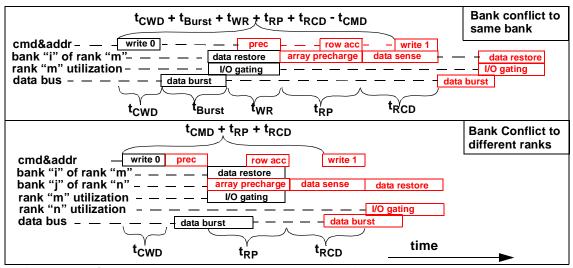

| 4.2.6 Consecutive Write Requests: Bank Conflicts 90                                                                                                                                                                                                                                                                            |

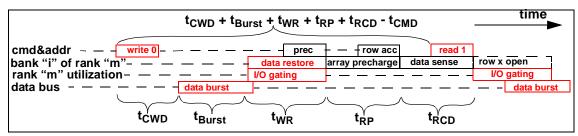

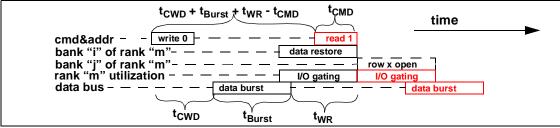

| 4.2.7 Write Request Following Read Request: Open Banks 92                                                                                                                                                                                                                                                                      |

| 4.2.8 Write Following Read: Same Bank, Conflict, Best Case 93                                                                                                                                                                                                                                                                  |

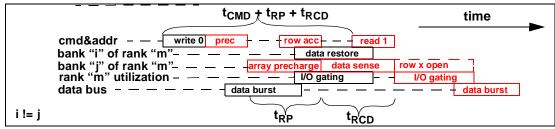

| 4.2.9 Write Following Read: Different Banks, Conflict, Best Case 94                                                                                                                                                                                                                                                            |

| 4.2.10 Read Following Write to Same Rank, Open Banks 95                                                                                                                                                                                                                                                                        |

| 4.2.11 Read Following Write to Different Ranks, Open Banks 96                                                                                                                                                                                                                                                                  |

| 4.2.12 Read Following Write to Same Bank, Bank Conflict 97                                                                                                                                                                                                                                                                     |

| 4.2.13 Read Following Write: Different Banks Same Rank, Conflict: Best Case 98                                                                                                                                                                                                                                                 |

| 4.3 Minimum Scheduling Distances 100                                                                                                                                                                                                                                                                                           |

| 4.4 Additional Constraints: Power 102                                                                                                                                                                                                                                                                                          |

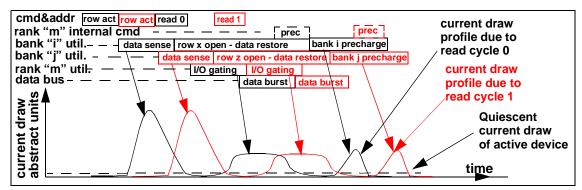

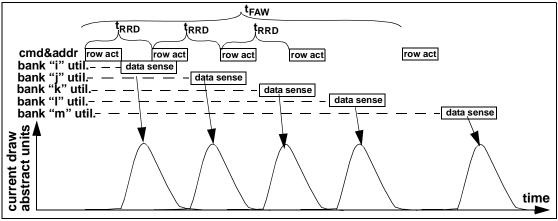

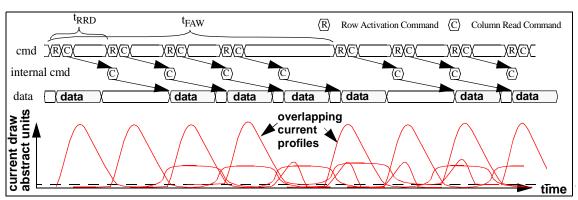

| 4.4.1 tRRD: Row to Row (activation) Delay 104                                                                                                                                                                                                                                                                                  |

| 4.4.2 tFAW: Four Bank Activation Window 105                                                                                                                                                                                                                                                                                    |

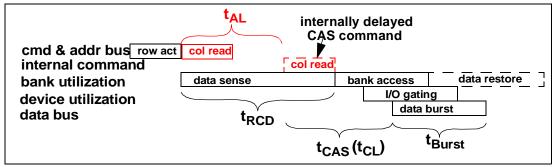

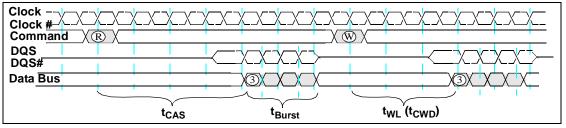

| 4.5 DDR2 SDRAM Protocol 107                                                                                                                                                                                                                                                                                                    |

| 4.5.1 DDR2 SDRAM Memory System Basics 107                                                                                                                                                                                                                                                                                      |

| 4.5.2 Typical Parameter Values 108                                                                                                                                                                                                                                                                                             |

|           | 4.6 Summary 110                                              |

|-----------|--------------------------------------------------------------|

| CHAPTER 5 | DRAM Memory Controller 112                                   |

|           | 5.1 Primary Functions 112                                    |

|           | 5.2 Row-buffer Management Policy 114                         |

|           | 5.2.1 Open-Page Row-buffer Management Policy 114             |

|           | 5.2.2 Close-Page Row-Buffer Management Policy 115            |

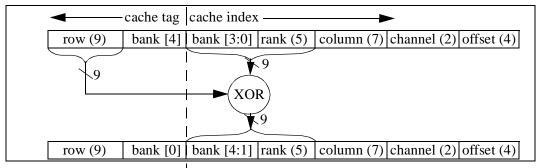

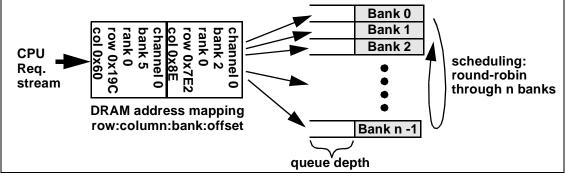

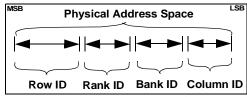

|           | 5.3 Address Mapping Scheme 117                               |

|           | 5.3.1 System Organization Variable Definition 117            |

|           | 5.3.2 Available Parallelism in DRAM System Organization 118  |

|           | 5.3.3 Baseline Address Mapping Schemes 121                   |

|           | 5.3.4 Parallelism versus Expansion Capability 123            |

|           | 5.3.5 Bank Address Aliasing (stride collision) 124           |

|           | 5.4 Memory Transaction and DRAM Command Ordering Schemes 129 |

|           | 5.4.1 Write Caching 130                                      |

|           | 5.4.2 DRAM-Bank-Centric Request Queuing Organization 131     |

|           | 5.4.3 Feedback Directed Scheduling 133                       |

|           |                                                              |

| CHAPTER 6 | Performance Analysis Methodology: Request Access             |

### CHAPTER Distances: 134

| 6.1   | Motivation                                              | 134 |

|-------|---------------------------------------------------------|-----|

| 6.1.1 | DRAM Device Scaling Considerations                      | 135 |

| 6.1.2 | Execution Based Analytical Framework                    | 136 |

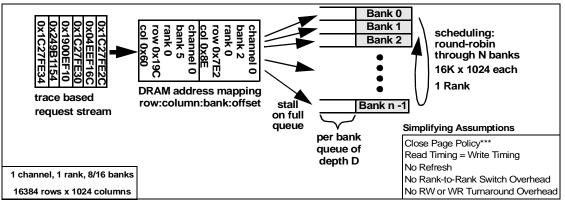

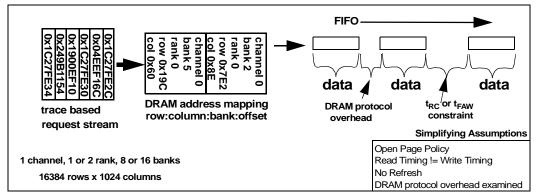

| 6.1.3 | Trace Based Analytical Framework                        | 138 |

| 6.1.4 | Trace Based versus Execution Based Analytical Framework | 138 |

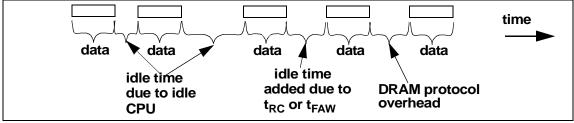

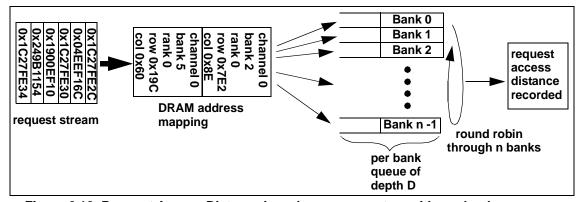

| 6.2   | The Request Access Distance Framework                   | 140 |

| 6.2.1 | Computing DRAM Protocol Overhead                        |     |

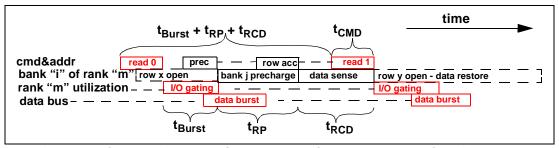

| 6.2.2 | Computing Row Cycle Time Constraints                    | 142 |

| 6.2.3 | Computing tFAW Constraints                              | 146 |

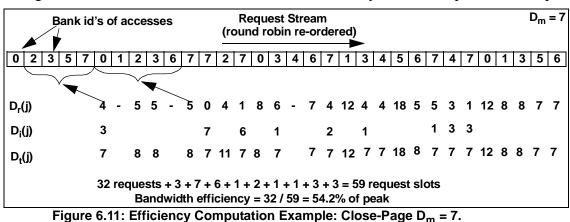

| 6.2.4 | DRAM Memory System Bandwidth Efficiency Computation     |     |

| 6.2.5 | System Configuration                                    | 149 |

| 6.3   | Impact of Refresh                                       | 151 |

| 6.4   | Applied Examples                                        | 153 |

| 6.4.1 | Close-Page System Example                               | 153 |

| 6.4.2 | Open-Page System Example                                | 154 |

# CHAPTER 7 DRAM Memory System Performance Analysis: Results 156

| 7.1   | Introduction                           | 156 |

|-------|----------------------------------------|-----|

| 7.1.1 | Workloads                              | 157 |

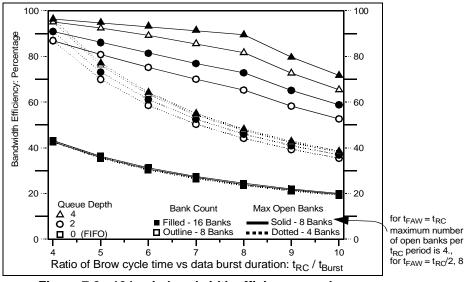

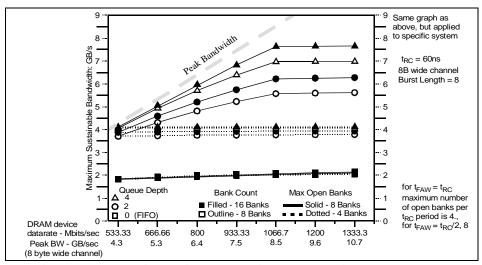

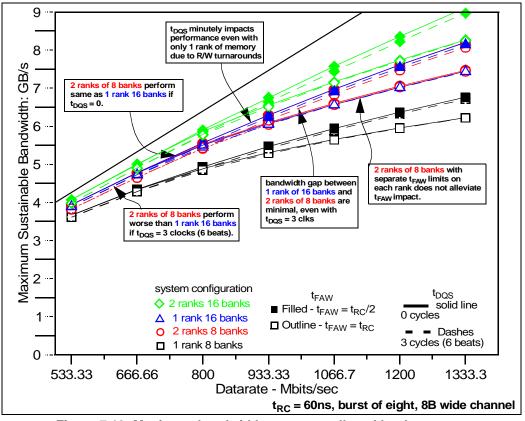

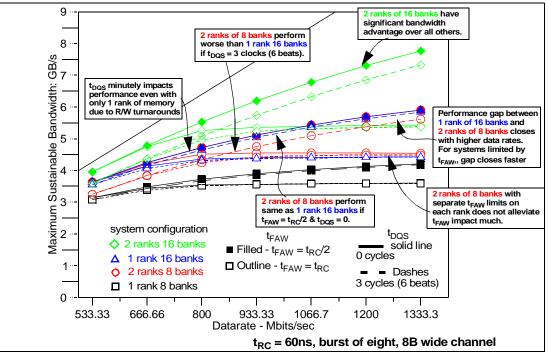

| 7.2   | Close-page System Performance Analysis | 158 |

| 7.2.1 | System Configuration Assumptions       | 158 |

| 7.2.2 | Workload Characteristics: 164.gzip     | 160 |

### TABLE OF CONTENTS

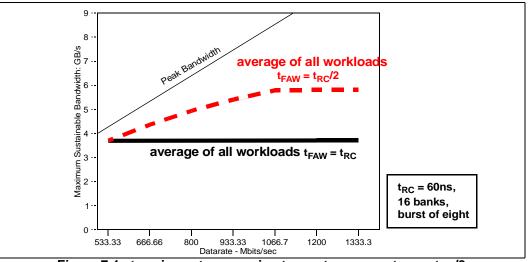

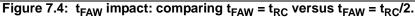

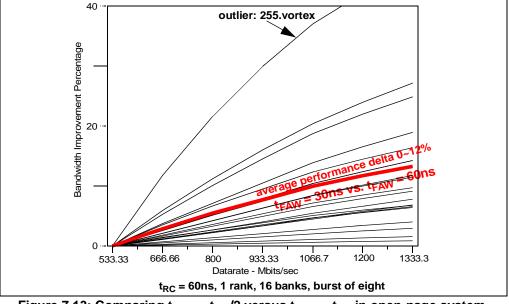

| 7.2.3 | tFAW Limitations in Close-page Systems: All Workloads       | 163 |

|-------|-------------------------------------------------------------|-----|

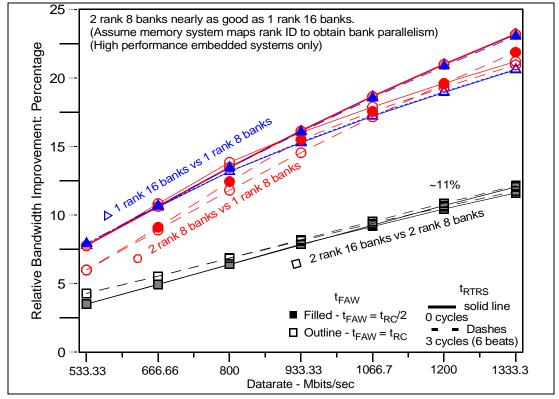

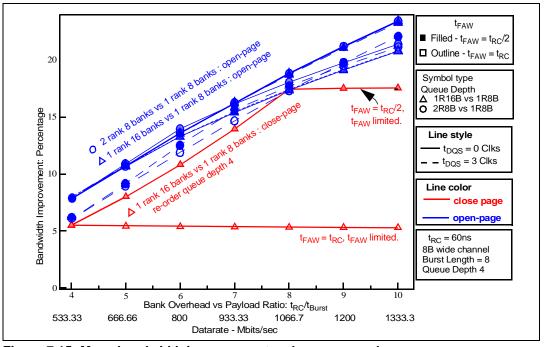

| 7.2.4 | Bank Comparison: 8 versus 16: All Workloads                 |     |

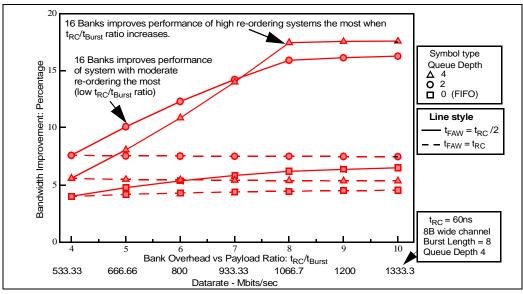

| 7.2.5 | Burst Length Impact: SPEC Workloads                         | 166 |

| 7.2.6 | Queue Depth Analysis                                        | 170 |

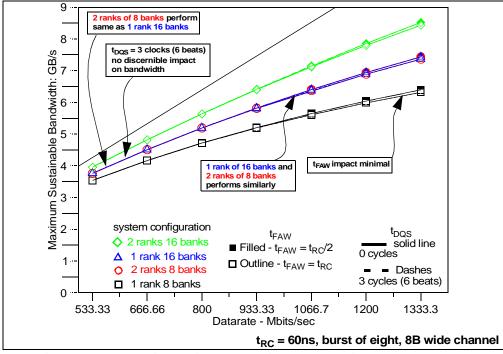

| 7.3   | Open-page System Performance Analysis                       | 172 |

| 7.3.1 | System Configuration Assumptions                            | 172 |

| 7.3.2 | Address Mapping                                             | 173 |

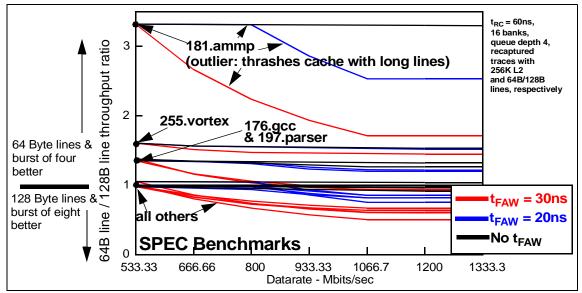

| 7.3.3 | Average of All Workloads                                    | 174 |

| 7.3.4 | Workload Characteristics: 164.gzip                          | 176 |

| 7.3.5 | Workload Characteristics: 255.vortex                        | 177 |

| 7.3.6 | tFAW Limitations in Open-page System: All Workloads         | 179 |

| 7.3.7 | Configuration Comparison: 1R8B vs. 2R8B vs. 1R16B vs. 2R16B | 180 |

| 7.4   | DRAM Performance Analysis Summary                           | 182 |

# CHAPTER 8 Power-Constrained DDRx Scheduling Algorithm 183

|           | 8.1   | Introduction                                                          |

|-----------|-------|-----------------------------------------------------------------------|

|           | 8.2   | Background Information 185                                            |

|           | 8.2.1 | Row Buffer Management Policy 185                                      |

|           | 8.2.2 | Timing Parameters 186                                                 |

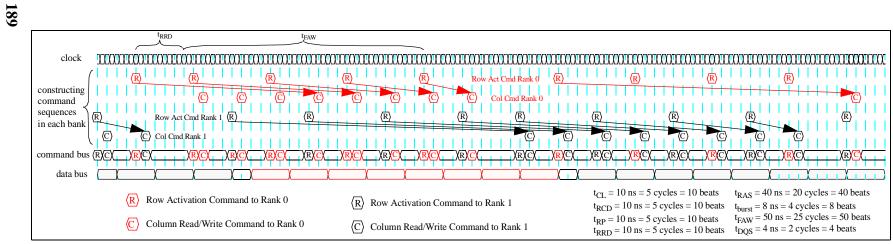

|           | 8.2.3 | Bank Activation Window Limited Memory System 186                      |

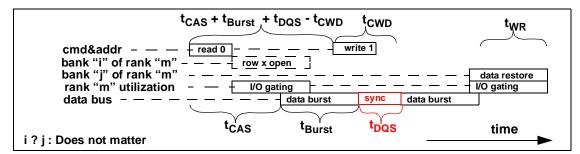

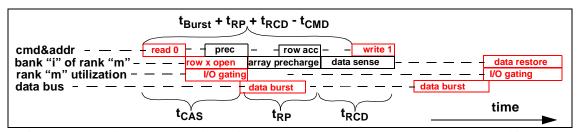

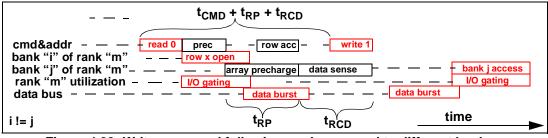

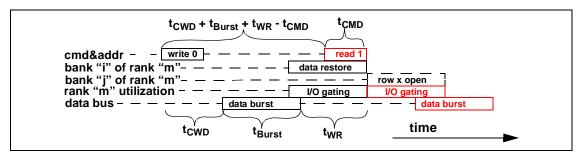

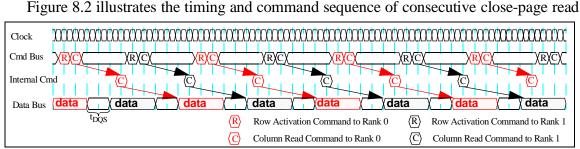

|           | 8.2.4 | Consecutive Commands to Different Ranks: Data Bus Synchronization 187 |

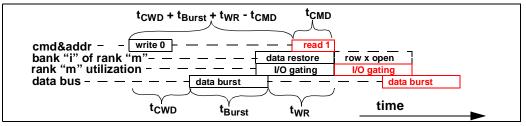

|           | 8.3   | Proposed Rank Hopping Scheduling Algorithm 190                        |

|           | 8.4   | Experimental Methodology 193                                          |

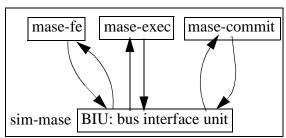

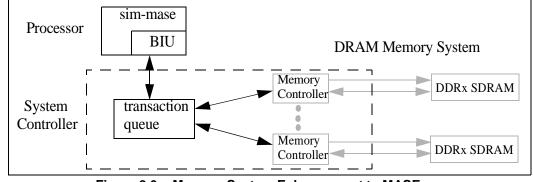

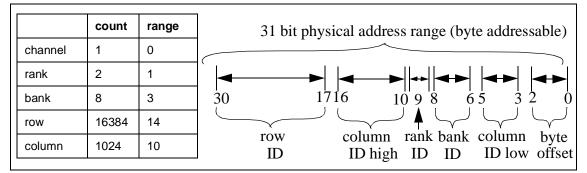

|           | 8.4.1 | Simulation Framework 193                                              |

|           | 8.4.2 | System Configuration 197                                              |

|           | 8.4.3 | Address Mapping and Row Buffer Management Policy 197                  |

|           | 8.4.4 | $\mathbf{J}_{\mathbf{J}}$                                             |

|           | 8.4.5 | 1 8                                                                   |

|           | 8.4.6 | 8                                                                     |

|           | 8.4.7 | Workloads 203                                                         |

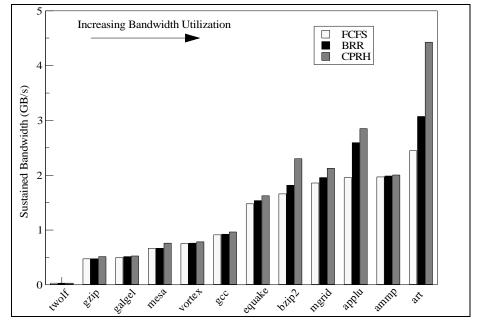

|           | 8.5   | Simulation Results                                                    |

|           | 8.5.1 | Improvement in Sustained Bandwidth 204                                |

|           | 8.5.2 | Workload Speedups 205                                                 |

|           | 8.5.3 | Memory Access Latency Distribution 206                                |

|           | 8.6   | Quick Summary of the Rank Hopping Algorithm 210                       |

| CHAPTER 9 | Con   | ncluding Remarks 212                                                  |

|           | 9.1   | Summary and Contributions                                             |

|           | 9.2   | Limitations                                                           |

|           | 9.3   | Related Work                                                          |

|           | 9.4   | Future Work                                                           |

| TABLE OF CONTENTS |                                                                     |       |  |

|-------------------|---------------------------------------------------------------------|-------|--|

| APPENDIX A        | Workload Descriptions                                               | 217   |  |

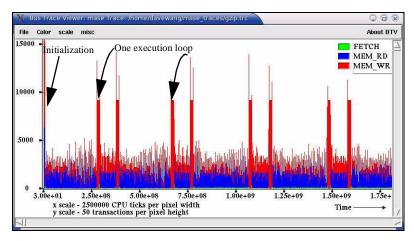

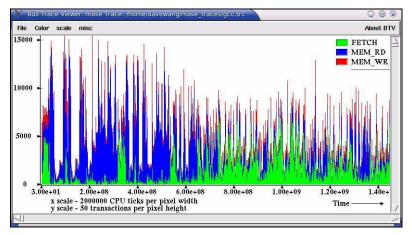

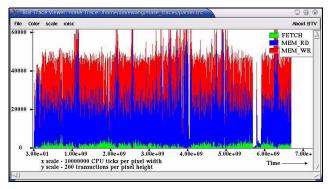

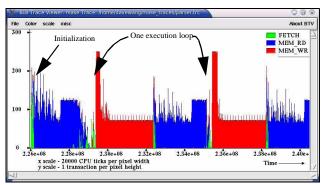

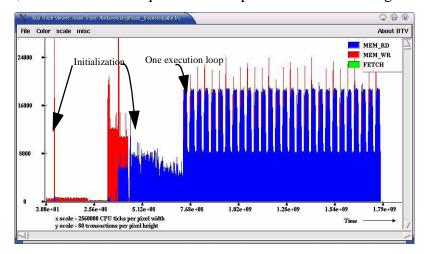

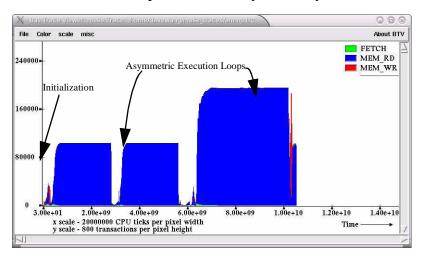

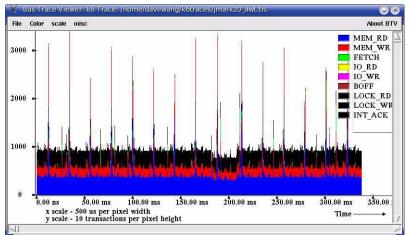

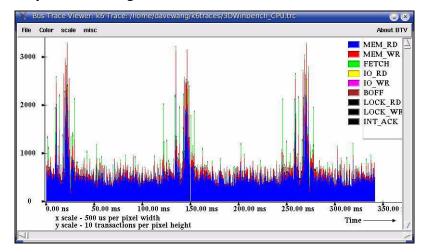

|                   | A.1 Trace Fundamentals                                              | 217   |  |

|                   | A.2 Description of Workloads                                        | 219   |  |

|                   | A.2.1 164.gzip: C Compression                                       |       |  |

|                   | A.2.2 176.gcc: C Programming Language Compiler                      | - 221 |  |

|                   | A.2.3 197.parser: C Word Processing                                 | - 222 |  |

|                   | A.2.4 255.vortex: C Object-oriented Database                        | - 223 |  |

|                   | A.2.5 172.mgrid: Fortran 77 Multi-grid Solver: 3D Potential Field - | - 224 |  |

|                   | A.2.6 178.galgel: Fortran 90 Computational Fluid Dynamics           |       |  |

|                   | A.2.7 179.art (SPEC CPU 2000 FP Suite)                              | - 226 |  |

|                   | A.2.8 183.equake: C Seismic Wave Propagation Simulation             |       |  |

|                   | A.2.9 188.ammp: C Computational Chemistry                           |       |  |

|                   | A.2.10 JMark 2.0 - AWT, CPU and Complex Arithmetic                  |       |  |

|                   | A.2.11 3DWinbench - CPU                                             |       |  |

|                   | A.2.12 SETI@Home - 3 Segments                                       |       |  |

|                   | A.2.13 Quake 3 - 5 Segments                                         | - 232 |  |

| APPENDIX B        | Glossary of Terminology                                             | 234   |  |

|                   | Bibliography                                                        | 236   |  |

# CHAPTER 1 Introduction

Performance of modern computer systems have seen dramatic improvements in the past thirty years due to advancements in silicon process technology. The advancements in silicon process technology have enabled the number of transistors on a single chip to roughly doubled every two years as suggested by Moore's Law. As a corollary to Moore's Law, processor performance has also doubled roughly every two years in the same time period due to a combination of the larger transistor budget and the increased switching speed of those transistors. However, increases in processor performance did not lead to comparable increases in performance of computer systems for all types of applications. The reason that increases in processor performance did not lead directly to comparable increases in computer system performance is that computer system performance is fundamentally constrained by the interaction between the processor and memory elements. Moreover, in contrast to the rapid improvements in processor performance, memory system performance has seen only relatively modest improvements in the past thirty years. The result of the imbalance in performance scaling trends between processor and memory is that modern computer systems are increasingly constrained by the performance of memory systems; in particular, the performance of DRAM based memory systems. The work in this dissertation is dedicated to the investigation of DRAM memory system performance characteristics, and the result of the investigation is then used to evaluate and support the design of future DRAM devices.

# 1.1 Problem Description

Computer system performance is increasingly limited by the performance of DRAM based memory systems due to the fact that the rate of DRAM memory system performance increase has lagged the rate of processor performance increase in the past thirty years. One reason that DRAM memory system performance has consistently lagged processor performance is that DRAM memory systems typically consist of one or more chips that are designed and manufactured separately from the processor, and the performance of the interconnected multi-chip DRAM memory system is difficulty to scale to achieve higher datarate and lower access latency. One apparent solution to the problem of access latencies introduced by system level interconnects between processors and memory systems is to integrate the memory system with the processor onto the same silicon die. However, in the case of the integrated memory system, the size of the silicon die limits the storage capacity of the memory system, and that capacity cannot be configured by the end user as needed for different operating environments. Moreover, the die area used by the memory system could have been used by performance enhancing features or more processor cores. In essence, the integration of processor and memory system onto the same silicon die is currently a viable solution for only a limited subset of high performance systems. As a result, high performance processors are keeping silicon die area for use by logic transistors, and memory transistors for main memory are still constructed separately from the processor chip. For example, high performance processors such as Intel's Itanium and Pentium processors, AMD's Opteron processor, and IBM's Power5 processors are all moving toward multi-core designs or already contain multiple processor cores per chip, and the study of the memory system as a separate entity will continue to have great relevance for the foreseeable future.

A second reason that the rate of increase of DRAM memory system performance has lagged the rate of increase of processor performance is that while high performance processors are specialized parts and typically command high price premiums, standard DRAM devices are commodity items that can be freely purchased from multiple vendors. The commodity nature of standard DRAM devices means that DRAM device manufacturers are extraordinarily sensitive to manufacturing costs, and only features that provide substantial performance benefits for minimal cost increments are considered in each new generation of standard DRAM devices. However, there is great difficulty in the determination of performance impact for different performance enhancing features proposed for each new generation of DRAM devices, and that difficulty arises from the fact DRAM memory system performance depends on a large number of independent variables such as workload characteristics of memory access rate and request sequence, memory system architecture, and memory system configuration. As a result, system architects and design engineers will often disagree as to the impact of various performance enhancing features, since that performance impact depends on the configuration of specific systems.

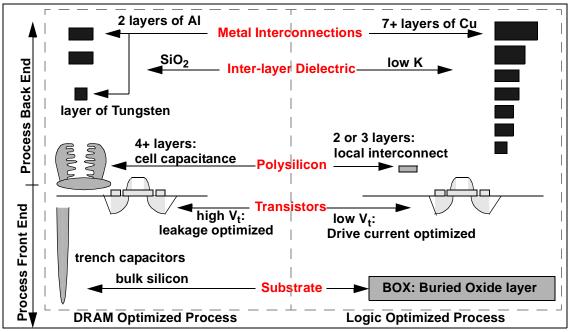

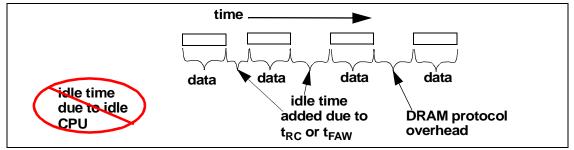

Presently, DRAM device datarates are increasing with each new generation of DRAM devices at the rate of 100% every three years, and DRAM row cycle times are decreasing at a rate of approximately 7% per year[22]. The collective trends are increasing the ratio of row cycle times to the duration of data bursts on the data bus. As a result, to maintain a given utilization rate of memory system bandwidth, more requests must be issued to the DRAM memory system in parallel for each successive generations of higher data rate DRAM devices. Collectively, these trends form the larger picture that while DRAM based memory system performance are increasingly limiting system performance, it is becoming more

difficult to maintain efficiency in each successive generations of higher data rate DRAM devices. Moreover, system architects and design engineers often disagree as to the desirability of various proposed DRAM device and system enhancements designed to increase DRAM memory system performance. With these considerations forming the background, the work in this dissertation is devoted to the creation of a common basis that system architects and design engineers can use to quantify the impact of various proposed performance enhancing features in modern DRAM devices, subjected to different workloads, system architecture and system configurations.

# 1.2 Contributions and Significance

The contribution of this dissertation is three-fold. Specifically, The contributions are the following:

- We create a parameterized and abstract DRAM memory access protocol. With proper definition of timing parameters, the DRAM memory access protocol accurately models DRAM device and system level interactions of SDRAM, DDR SDRAM, DDR2 SDRAM and DDR3 SDRAM memory access protocols. The creation of the abstract DRAM memory access protocol ensures that the analytical work performed for one memory system retains context for direct comparison against another memory systems. i.e. comparisons of an SDRAM memory system against a DDR2 SDRAM memory system.

- We derive a set of mathematical equations that establish the relationship between DRAM memory system configuration, timing parameters and the maximum achievable bandwidth.

The formalized methodology is then utilized to examine the performance of future DRAM

memory systems given different DRAM system configurations, device data rates, row cycle times, DRAM device power limitations, rank-to-rank data bus turnaround overheads, readand-write data bus turnaround overheads, cache line burst lengths, and the number of banks in a given DRAM device.

We create a DRAM transaction and command scheduling algorithm that groups row activation commands and column access commands separately to ensure that maximum bandwidth can be maintained despite the existence of constraints such as data bus synchronization overhead in DDR, DDR2 and DDR3 SDRAM memory systems and mechanisms that limit peak power in DDR2 and DDR3 memory systems.

To aid the evaluations of performance and manufacturing cost trade-offs in modern DRAM devices, the work in this dissertation proceeds through a detailed examination of modern DRAM memory systems, starting from a description of modern DRAM devices and ending with the introduction of a high performance, power-constrained DRAM transaction and command scheduling algorithm. We believe that the performance evaluation methodology can contribute directly to the evaluation process of future DRAM device and memory system cost-performance trade-offs. We also believe that the DRAM transaction and command scheduling algorithm can contribute directly to the design of future high performance memory systems that must support high request rate access patterns with low spatial locality.

# 1.3 Organization of Dissertation

In this dissertation, the DRAM memory system is methodically examined from the transistor level to the system level. In this first chapter, a brief introduction to the dissertation is given. In Chapter 2, basic DRAM device architecture is described, and important details of DRAM device operations are examined in depth. In Chapter 3, typical DRAM based memory system topology and system architectures are described. The details provided in Chapters 2 and 3 are then used to create a generic DRAM memory access protocol in Chapter 4. The generic DRAM memory access protocol methodically examines the interactions between DRAM commands in a DRAM memory system. Then, from the description of the generic DRAM access protocol, a table of minimum scheduling distances between combinations of DRAM commands is summarized as table 4.3. Chapter 5 then examines DRAM controller designs and address mapping policies. The table of minimum scheduling distances is then used to form the foundation of a formalized methodology for the computation of maximum DRAM system bandwidth, hereafter referred to as the *Request Access Distance* methodology. The *Request Access Distance* methodology for the computation of maximum DRAM system bandwidth is formally defined in Chapter 6. In Chapter 7, results from studies based on the use of the Request Access Distance methodology are presented and analyzed. In Chapter 8, a unique rank-hopping memory scheduling algorithm is proposed and studied. The algorithm is designed to alleviate various constraints imposed upon high datarate DDRx SDRAM devices. Chapter 9 summarizes this work with concluding remarks. Finally, in Appendix A, the workloads used in the investigation of maximum DRAM system bandwidth in Chapter 7 are described in detail, and a glossary of terminology is enclosed in Appendix B.

# CHAPTER 2 DRAM Device: Basic Circuits and Architecture

# 2.1 Introduction:

To facilitate the study of DRAM based memory systems, this chapter describes basic circuits and architecture of DRAM devices. For all practical purposes, it is impossible to provide a complete overview as well as an in depth coverage on the topic of DRAM circuits and architecture in a single chapter. The limited goal in this chapter is to provide a broad overview of functionalities of circuits and common functional blocks in DRAM devices sufficient to provide a basic understanding of internal circuits and architecture of modern DRAM devices. With the understanding of the fundamentals of DRAM device operations in place, more advanced discussions of architectural trade-offs at the DRAM device and system level would then be possible.

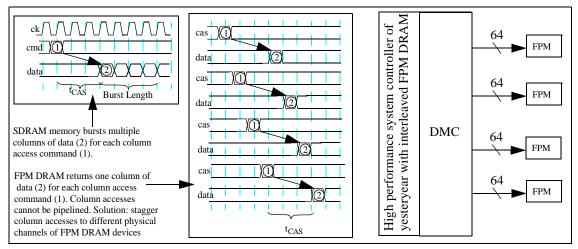

This chapter begins the examination of modern DRAM devices with the description of a basic fast page mode (FPM) DRAM device. Various components such as DRAM storage cells, DRAM array structure, voltage sense amplifiers, control logic and decoders are then examined separately.

# 2.2 DRAM Device Organization

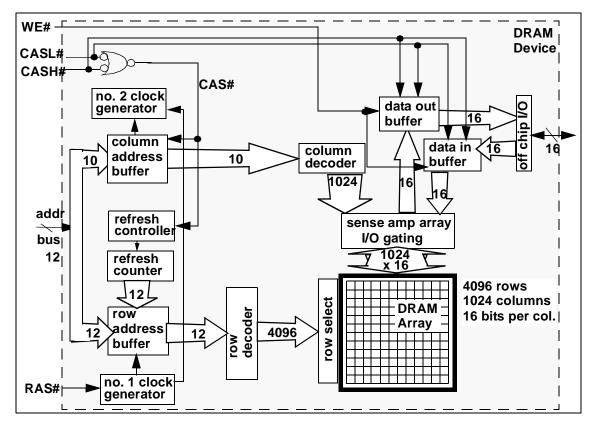

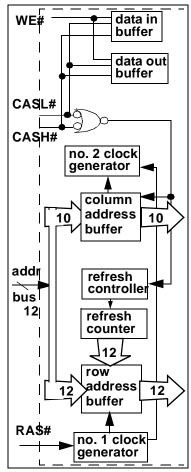

Figure 2.1 illustrates the organization and structure of a **Fast Page Mode** (FPM) DRAM device. Internally, the array of DRAM storage cells in Figure 2.1 is organized as 4096 rows, 1024 columns per row, and 16 bits of data per column. In this device, each time a row access occurs, a 12 bit address is placed on the address bus and the **row address strobe** (RAS) is asserted by an external memory controller. Inside the DRAM device, the address on the address bus is buffered by the row address buffer, then sent to the row decoder. The row address decoder then accepts the 12 bit address and selects one of 4096 rows of storage cells. The data values contained in the selected row of storage cells are then sensed and maintained in the array of sense amplifiers. Each row of DRAM cells in this chip consists of 1024 columns and each column is 16 bits wide. That is, a 16 bit wide column is the basic

Figure 2.1: 64 Mbit Fast Page Mode DRAM Device (4096 x 1024 x 16).

addressable unit of memory in this device, and each column access that follows the row access would ordinarily read or write 16 bits of data from the same row of DRAM. The FPM DRAM device does allow each 8 bit half of the 16 bit column to be accessed independently through the use of separate **column access strobe high** (CASH) and **column access strobe low** (CASL) signals. The way that a column access is engaged is similar to the row access in that the memory controller would place a 10 bit address on the address bus, but then assert the appropriate **column access strobe** (CAS#) signals. Internally, the DRAM chip then takes the 10 bit column address, decodes it and uses it to select one column out of 1024 columns. The data for that column is then placed onto the data bus or overwritten with data from the data bus depending on the **write enable** (WE) signal.

All DRAM devices, from the FPM DRAM device to modern DDRx<sup>\*</sup> SDRAM devices, possess similar basic organizations. All DRAM devices have one or more arrays of DRAM cells organized into a number of rows and columns, with a column being the smallest unit of addressable memory on that device. All DRAM devices also have some logic circuits that control the timing and sequence how the device operates. In the case of the FPM DRAM device shown in Figure 2.1, the chip has internal clock generators as well as a built-in refresh controller. In most cases, the DRAM device itself controls the relative timing of the sequence of events for a given action. The FPM DRAM device also keeps the address of the next row that needs to be refreshed, so when the memory controller asserts a new refresh command to the DRAM device, the row address to be refreshed can be loaded from the internal refresh counter rather than having to load a separate row address from the off chip address bus. Also, pin usage has always been restrictive on DRAM devices. As a result,

<sup>\*.</sup> DDRx denotes DDR, DDR2, and variants of future DDRx SDRAM devices

modern DRAM devices move data onto and off of the device through a set of bi-directional input-output pins connected to the system. Finally, advanced DRAM devices such as ESDRAM, Direct RDRAM and RLDRAM have evolved to include more logic circuitry and functionality on chip, such as row caches or write buffers that allow for read-around-write functionality. These circuitry improve performance but add to the die cost of the DRAM device. As a result, they are not found in standard DRAM devices. However, these performance enhancing features may prove to be necessary elements in future high datarate DRAM devices.

# 2.3 DRAM Storage Cells

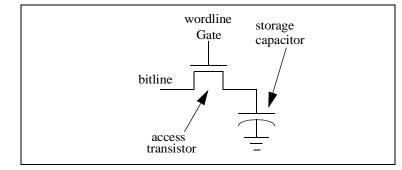

Figure 2.2 shows a circuit diagram of the basic one transistor, one capacitor (1T1C) cell

Figure 2.2: Basic 1T1C DRAM Cell Structure.

structure used in modern DRAM devices as the basic storage unit. In the structure illustrated in Figure 2.2, when the access transistor is turned on by applying a voltage on the gate of the access transistor, a voltage representing the data value may be placed onto the bitline and used to charge the storage capacitor. The storage capacitor then retains the stored charge for a limited period of time after the voltage on the wordline is removed and the access transistor is turned off. However, due to leakage currents through the access transistor, the electrical charge stored in the storage capacitor gradually dissipates. As a result, before the stored charge decays to indistinguishable values, data stored in DRAM cells must be periodically read-out and written back in a process known as *refresh*. Otherwise, the stored electrical charge will gradually leak away and the value stored in the capacitor will no longer be resolvable after some time.

### 2.3.1 Cell capacitance, Leakage and Refresh

In a 90 nm process technology optimized for the manufacturing of DRAM devices, the capacitance of a DRAM storage cell in a typical DRAM device is on the order of 30 fF, and the leakage current of the DRAM access transistor is on the order of 1 fA [23]. With the cell

capacitance of 30 fF and leakage current of 1 fA, a typical DRAM cell can retain the state of the stored data for hundreds of milliseconds. That is, hundreds of milliseconds after data is written, the electrical charge of a DRAM cell will still resolve to the stored digital value by the *differential sense amplifier*. Some cells in a typical DRAM device can even hold the stored data value for upwards of several seconds. However, a reliable memory systems must be designed in such a manner that not a single bit of data would be lost due to charge leakage. The result of this requirement means that every single DRAM cell in a given device must be refreshed at least once before any single bit in the entire device would lose its stored charge due to leakage. In most modern DRAM memory systems, the storage cells in standard DRAM devices are typically refreshed once every 32 or 64 ms. In some cases where DRAM cells have low capacitance storage capacitors or high leakage currents through the access transistor, the time period between refresh intervals must be reduced to ensure reliable data retention.

# 2.4 DRAM Array Structures

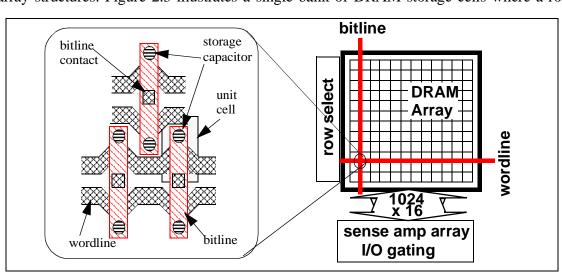

In DRAM devices, large numbers of DRAM cells are grouped together to form DRAM array structures. Figure 2.3 illustrates a single bank of DRAM storage cells where a row

Figure 2.3: Top Down view of DRAM array.

address is sent to the row decoder, and the row decoder selects one row of cells. A row of cells is formed from one or more wordlines that are driven concurrently to activate one cell on each one of thousands of bitlines. There may be hundreds of cells connected to the same bitline, but only one cell will place its stored charge from its storage capacitor on the bitline at any one time. The resulting voltage on the bitline is then resolved into a digital value by a differential sense amplifier. Figure 2.3 illustrates an abstract DRAM array in a top down view, and it also abstractly illustrates the size of a cell in the array. The size of a unit cell in Figure 2.3 is 8 F<sup>2</sup>. In the context of DRAM cell size, "F" is a process independent metric that denotes the smallest feature size in a given process technology. In a 90 nm process technology, F is literally 90 nm, and an area of 8 F<sup>2</sup> translates to 64800 nm<sup>2</sup> in the 90nm process. The cross sectional area of a DRAM storage cell is expected to scale linearly with respect to the process generation, maintaining the 6-8 F<sup>2</sup> cell size in each generation.

In modern DRAM devices, the capacitance of a storage capacitor is far smaller than the capacitance of the bitline. Typically, the capacitance of a storage capacitor is one-tenth of the capacitance of the long bitline that is connected to hundreds of other cells. The relative capacitance values create the scenario that when the small charge contained in a cell is placed on the bitline, the resulting voltage on the bitline is small and difficult to measure in an absolute sense. In DRAM devices, the voltage sensing problem is resolved through the use of a differential sense amplifier that compares the voltage of the bitline to a reference voltage. In the following section, the functionality of the differential sense amplifier is examined in some detail.

### 2.5 Differential Sense Amplifier

In DRAM devices, the functionality of resolving small electrical charges stored in storage capacitors into digital values is performed by a differential sense amplifier. In essence, the differential sense amplifier takes the voltages from a pair of bitlines as input, senses the difference in voltage levels between the bitline pairs and amplifies the difference to one extreme or the other.

### 2.5.1 Functionality of Sense Amplifiers in DRAM Devices

Sense amplifiers in modern DRAM devices perform three different functions. The first function that sense amplifiers perform in a DRAM device is to sense the minute change in voltage that occurs when an access transistor is turned on and a storage capacitor places its charge on the bitline. The sense amplifier compares the voltage on that bitline against a reference voltage as provided on a separate bitline and amplifies the voltage differential to the extreme so that the storage value can be resolved as a digital one or a zero. This role of the sense amplifier is its primary role in DRAM devices, as it senses minute voltage differentials and amplifies them to represent the digital value.

The second function of sense amplifiers in a modern DRAM device is that sense amplifiers also restores the value of a cell after the voltage on the bitline is sensed and amplified. The act of turning on the access transistor allows a storage capacitor to share its stored charge with the bitline. However, the process of sharing the stored value from a storage cell discharges the storage cell. After the process of charge sharing occurs, the voltage level within the storage cell would be roughly equal to the voltage on the bitline, and this voltage level cannot be used for another read operation. As a result, after the sensing and amplification operation, the sense amplifier must also restore the amplified voltage vale to the storage cell.

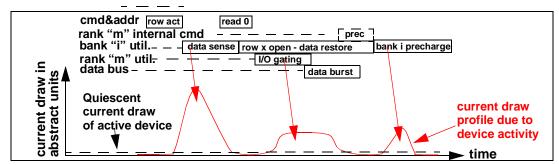

The third and somewhat surprising function of sense amplifiers in a modern DRAM device is that arrays of sense amplifiers also act as temporary data storage. That is, after data values contained in storage cells are sensed and amplified, the sense amplifiers continue to drive the sensed data values until the DRAM array is precharged and readied for another access. In this manner, data in the same row of cells can be accessed by reading them from the sense amplifier without repeated row accesses to the cells themselves. In this role, the array of sense amplifiers effectively acts as a row buffer that caches an entire row of data. As a result, an array of sense amplifiers is also referred to as a row buffer. Row buffer management policies in essence control operations of the sense amplifiers will retain the data for an indefinite period of time<sup>\*</sup>, or will discharge it immediately after data has been restored to the storage cells. Active sense amplifiers consume additional current above quiescent power levels, and effective management of sense amplifier operation is an important task for systems seeking optimal trade off points between power and performance.

### 2.5.2 Circuit Diagram of a Basic Sense Amplifier

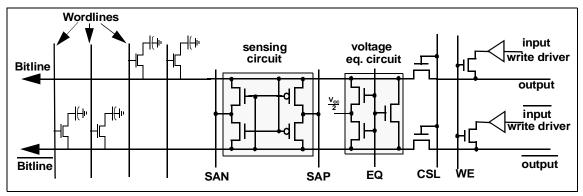

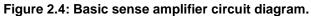

Figure 2.4 shows the circuit diagram of a basic sense amplifier. Complex sense amplifiers in modern DRAM devices contain the basic elements shown in Figure 2.4 as well as additional circuit elements for array isolation, careful balance of the sense amplifier structure, and faster sensing capability. In the basic sense amplifier circuit diagram shown in Figure 2.4, the **equalization (EQ)** signal line controls the voltage equalization circuit. The

<sup>\*.</sup> Indefinitely long until mandatory refresh cycle kicks in.

functionality of this circuit is to ensure that the voltages on the bitline pairs are as closely matched to each other as possible. Since the differential sense amplifier is designed to amplify the voltage differential between the bitline pairs, any voltage imbalance that exists on the bitline pairs prior to the activation of the access transistors would degrade the effectiveness of the sense amplifier.

The heart of the sense amplifier is the set of 4 cross-connected transistors, labelled as the sensing circuit in Figure 2.4. The sensing circuit is essentially a bi-stable circuit, designed to drive the bitline pairs to complementary voltage extremes, depending on the respective voltages on the bitlines at the time the **SAN** and **SAP** sensing signals are activated. After the assertion of the **SAN** and **SAP**, the bitlines are driven to the full voltage levels. The column select line (**CSL**) then turns on the output transistors and allows the fully driven voltage to reach the output and be read out of the DRAM device. At the same time, the access transistor for the accessed cell remains open, and the fully driven voltage on the bitline now re-charges the storage capacitor. In case of a write operation, the input write drivers provide a larger current to overdrive the sense amplifiers and the bitline voltage. The open cell would then be overwritten by the new data values asserted by the input write drivers.

Figure 2.5: Illustrated diagrams of sense amplifier operation. Read(1) example.

### 2.5.3 Basic Sense Amplifier Operation

Figure 2.5 shows four different phases in the sensing operations of a differential sense amplifier. In Figure 2.5, the operations of a sense amplifiers is labelled as phases zero, one, two and three. The reason that the precharge phase is labelled as phase zero is because the precharge phase is typically considered as a separate operation from a row access operation. That is, while the *Precharge* phase is a prerequisite for the subsequent phases of a row access operation, it is typically performed separately from the row access. On the other hand, *Access, Sense*, and *Restore* are three different phases that are performed atomically in sequence for any row access operation.

Phase zero in Figure 2.5 is labelled as *Precharge*, and it illustrates that before the process of reading data from a DRAM array can begin, the bitlines in a DRAM array is precharged to a reference voltage,  $V_{ref}$ . In many modern DRAM devices,  $V_{cc}/2$ , the voltage half way between the power supply voltage and ground, is used as the reference voltage. In Figure 2.5, the equalization circuit is activated, and the bitlines are precharged to  $V_{ref}$ .

Phase one in Figure 2.5 is labelled as (cell) *Access*, and it illustrates that as a voltage is applied to the right most wordline, that wordline is overdriven to a voltage that is at least  $V_t$  above  $V_{cc}^*$ . The voltage on the wordline activates the access transistors, and the charge in the storage cell is discharged onto the bitline. In this case, since the voltage in the storage cell was a high voltage value that represented a digital value of "1", the voltage on the bitline increases from  $V_{ref}$  to  $V_{ref}^+$ . As the voltage on the bitline changes, the higher voltage on the bitline begins to affect operations of the cross connected sensing circuit. In the case illustrated in Figure 2.5, the slightly higher voltage on the bitline begins to drive the lower NFet to be more conductive than the upper NFet. Conversely, the minute voltage difference drives the lower PFet to be less conductive than the upper PFet. The bitline voltage thus biases the sensing circuit and readies it for the sensing phase.

<sup>\*.</sup> The maximum voltage that can be placed across the access transistor is  $V_{gs} - V_t$ . ( $V_t$  is the threshold voltage of the access transistor,  $V_{gs}$  is the gate-source voltage on the access transistor) By overdriving the wordline voltage to  $V_{cc} + V_t$ , the storage capacitor could be charged to full voltage (maximum of  $V_{cc}$ ) by the sense amplifier in the restore phase of the sensing operation. The higher-than- $V_{cc}$  wordline voltage is generated by additional level-shifting voltage pumping circuitry not examined in this text.

Phase two in Figure 2.5 is labelled *Sense*, and it illustrates that as the minute voltage differences drives a bias into the cross connected sensing circuit, SAN, the DRAM device's Nsense amplifier control signal, turns on and drives the voltage on the lower bitline down<sup>\*</sup>. Figure 2.5 shows that as SAN turns on, the more conductive lower NFet allows SAN to drive the lower bitline down in voltage from  $V_{ref}$  to ground. Similarly, SAP, the Psense amplifier control signal drives the bitline to a fully restored voltage value that represents the digital value of "1". The SAN and SAP control signals thus collectively force the bi-stable sense amplifier circuit to be driven to the respective maximum or minimum voltages.

Finally, phase three of Figure 2.5 is labelled as *Restore*, and it illustrates that after the bitlines are driven to the respective maximum or minimum voltage values, the overdriven wordline remains active and the fully driven bitline voltage now restores the charge in the storage capacitor through the access transistor. At the same time, the voltage value on the bitline can be driven out of the sense amplifier circuit to provide the requested data. In this manner, the contents of a DRAM row can be accessed and driven out of the DRAM device concurrently with the data restoration process.

### 2.5.4 Voltage Waveform of Basic Sense Amplifier Operation

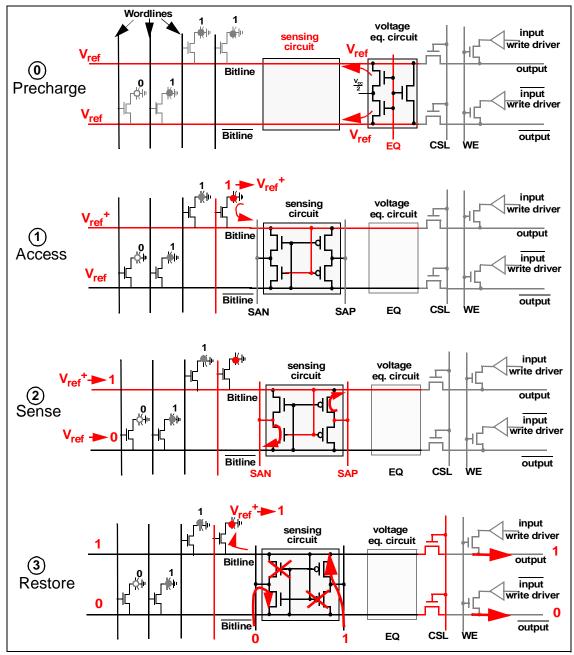

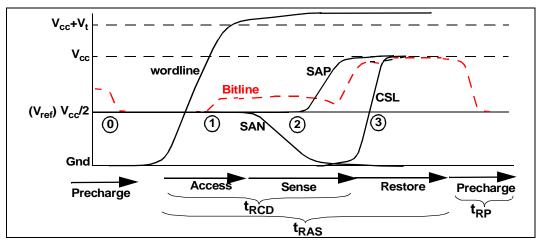

Figure 2.6 shows the voltage waveforms for the bitline and selected control signals illustrated in Figure 2.5. The four phases labelled in Figure 2.6 corresponds to the four phases illustrated in Figure 2.5. Figure 2.6 shows that before a row access operation, the bitline is precharged, and the voltage on the bitline is set to the reference voltage,  $V_{ref}$ . In phase one, the wordline voltage is overdriven to at least  $V_t$  above  $V_{cc}$ , and the DRAM cell

<sup>\*.</sup> In modern DRAM devices, the timing and shape of the SAN and SAP control signals are of great importance in defining the accuracy and latency of the sensing operation. However, for the sake of brevity, this text assumes that the timing and shape of these important signals are optimally generated by the control logic.

Figure 2.6: Simplified sense amplifier voltage waveform. Read(1) example. discharges the content of the cell onto the bitline and raises the voltage from  $V_{ref}$  to  $V_{ref}^+$ . In phase two, the sense control signals SAN and SAP are activated in quick succession and drives the voltage on the bitline to the full voltage. The voltage on the bitline then restores the charge in the DRAM cells in phase three.

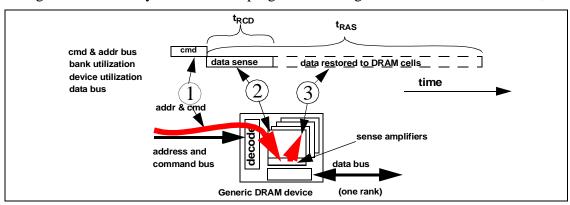

Figure 2.6 illustrates the relationship between two important timing parameters:  $t_{RCD}$  and  $t_{RAS}$ . Although the relative durations of  $t_{RCD}$  and  $t_{RAS}$  are not drawn to scale, Figure 2.6 shows that after time  $t_{RCD}$ , the sensing operation is complete, and the data can be read out through the DRAM device's data I/O after that time. However, after time period of  $t_{RCD}$  from the beginning of the activation process, data has yet to be restored to the DRAM cells. Figure 2.6 shows that after time period of  $t_{RAS}$  from the beginning of the activation process, the data restore operation is assumed to be complete, and the DRAM device is ready to accept a precharge command that will complete the entire row cycle process after time period of  $t_{RP}$

### 2.5.5 Writing into DRAM Array

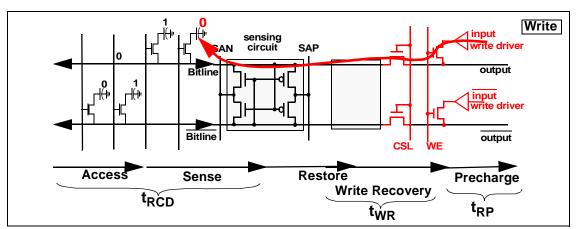

Figure 2.7 shows a simplified timing characteristic for the case of a write command. As

Figure 2.7: Row activation followed by column write into DRAM array.

part of the row activation command, data is automatically restored from the sense amplifiers to DRAM cells. However, in the case of a write command in commodity DRAM devices, data written by the memory controller is buffered by the I/O buffer of the DRAM device and used to overwrite the sense amplifiers and DRAM cells<sup>\*</sup>. In this case, the restore phase may be extended by the write recovery phase. Similar to the relative timing described in Figure 2.6, the addition of a column write command simply means that a precharge command cannot be issued until after the correct data values have been restored to the DRAM cells. The time period required for write data to overdrive the sense amplifiers and through written to the DRAM cells is referred to as the write recovery time, denoted as  $t_{WR}$  in Figure 2.7.

<sup>\*.</sup> Some DRAM devices such as Direct RDRAM devices have write buffers. Data isn't driven directly into the DRAM array by the data I/O circuitry in that case, but the write mechanism into the DRAM array remains the same when the write buffer commits the data into the DRAM array prior to a precharge operation.

# 2.6 DRAM Device Control Logic

All DRAM devices contain some basic logic control circuitry to direct the movement of data onto, within, and off of the DRAM devices. Essentially, some control logic must exist on DRAM devices that accepts externally asserted signal and control, then orchestrates an appropriately timed sequences of internal control signals to direct the movement of data. As an example, previous discussion on sense amplifier operations hinted to the complexity of the intricate timing sequence in the assertion of the wordline voltage followed by assertion of the SAN and SAP sense amplifier control signals, followed yet again by the column select signal. The sequence of timed control signals are generated by the control logic on DRAM devices.

Figure 2.8: Control logic for 32 Mbit FPM DRAM device.

Figure 2.8 shows the control logic that generates and controls the timing and sequence of signals for the sensing and movement of data on the FPM DRAM device illustrated in Figure 2.1. The control logic on the FPM DRAM device asynchronously accepts external signal control and generates the sequence of internal control signals for the FPM DRAM device. The external interface to the control logic on the FPM DRAM device is simple and straightforward, consisting of essentially 3 signals: **row access strobe (RAS)**, **column access strobe (CAS)**, and **write enable (WE)**. The FPM DRAM device described in Figure 3.21 is a device with a 16 bit wide data bus, and the use of separate CASL and CASH signals allow the DRAM devices to control each half of the 16 bit wide data bus separately.

In FPM DRAM devices, the controller to FPM DRAM device interface is an asynchronous interface, and the memory controller directly controls the timing of the movement of data inside the FPM DRAM device. In early generations of DRAM devices such as FPM DRAM devices, the direct control of the internal circuitry of the DRAM device by the external memory controller and the asynchronous nature of the device interface means that the DRAM device could not be well pipelined, and new commands to the DRAM device may not be initiated until the movement of data for the previous command is completed<sup>\*</sup>. The asynchronous nature of the interface means that system design engineers can implement different memory controller that operated at different frequencies, and designers of the memory controller are solely responsible to ensure that the controller can correctly control different DRAM devices from different DRAM device and module manufacturers, possibly with subtle timing variations.

<sup>\*.</sup> For every rule, there are exceptions to the rule. Pipeline burst EDO devices were designed to have some limited pipelining capability with an implicit clocking scheme.

### 2.6.1 Mode Register Based Programmability

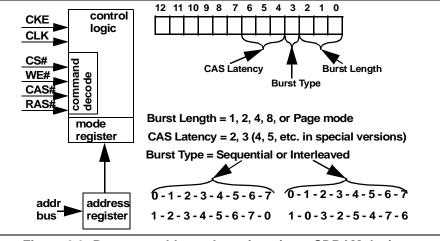

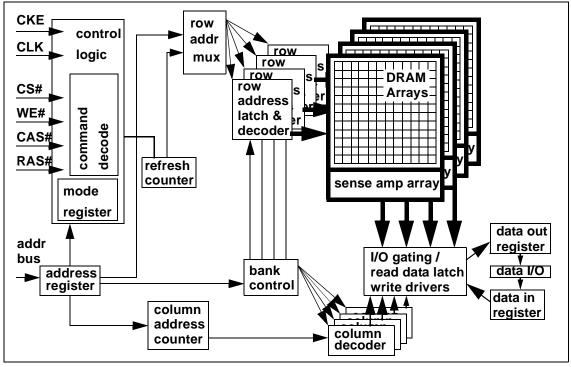

Modern DRAM devices are controlled by synchronous statemachines whose behavior depends on the input values of the command signals as well as the values contained in the programmable mode register in the control logic. Figure 2.9 shows that in an SDRAM

Figure 2.9: Programmable mode register in an SDRAM device.

device, the mode register contains three fields: CAS latency, burst type, and burst length. Depending on the value of the CAS latency field in the mode register, the DRAM devices returns data two or three cycles after the assertion of the column read command. The value of the burst type determines the ordering of how the SDRAM device returns data, and the burst length field determines the number of columns that a SDRAM device will return to the memory controller with a single column read command. SDRAM devices can be programmed to return 1, 2, 4, 8 columns, or an entire row. Direct RDRAM devices and DDRx SDRAM devices contain more mode registers that control ever larger set of programmable operations including, but not limited to: different operating modes for power conservation, electrical termination calibration modes, self test modes, and write recovery duration.

# 2.7 DRAM Device Configuration

DRAM devices are classified by the number of data bits in each device, and that number typically quadruples from generation to generation. For example, 64 Kbit devices were followed by 256 Kbit devices, and those devices were in turn followed by 1 Mbit devices. Recently, half generation devices that merely double the number of data bits of previous generation devices have been used to facilitate smoother transitions between different generations. As a result, 512 Mbit devices now exist along side 256 Mbit and 1 Gbit devices.

In a given generation, a DRAM device may be configured with different data bus widths to facilitate its use in different applications. Table 2.1 shows three different configurations of

| Device configuration | 64 Meg x 4 | 32 Meg x 8 | 16 Meg x 16 |

|----------------------|------------|------------|-------------|

| Number of banks      | 4          | 4          | 4           |

| Number of rows       | 8192       | 8192       | 8192        |

| Number of columns    | 2048       | 1024       | 512         |

| Data bus width       | 4          | 8          | 16          |

TABLE 2.1: Three different configurations of 256 Mbit SDRAM device

a 256 Mbit device. Table 2.1 shows that a 256 Mbit SDRAM device may be configured with a 4 bit wide data bus, an 8 bit wide data bus or a 16 bit wide data bus. In the configuration with a 4 bit wide data bus, an address provided to the SDRAM device to fetch a single column of data will receive 4 bits of data, and there are 64 million separately addressable locations in the device with the 4 bit data bus. The 256 Mbit SDRAM device with the 4 bit wide data bus is thus referred to as the 64 Meg x4 device. Internally, the 64 Meg x4 device consists of 4 bits of data per column, 2048 columns of data per row, 8192 rows per bank and there are 4 banks in the device. Alternatively, a 256 Mbit SDRAM device with a 16 bit wide data bus will have 16 bits of data per column, 512 columns per row, 8192 rows per bank, and 4 banks in the 16 Meg x16 device.

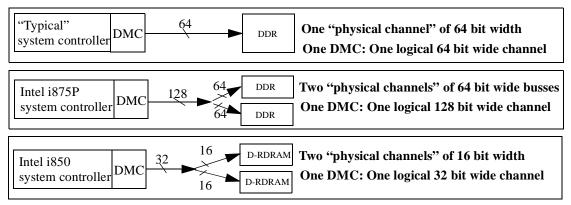

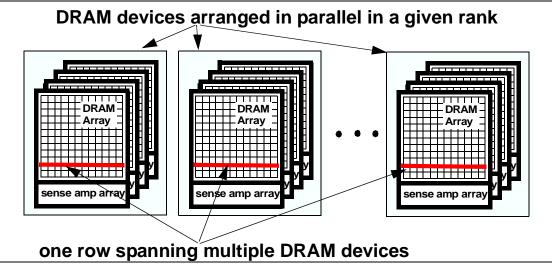

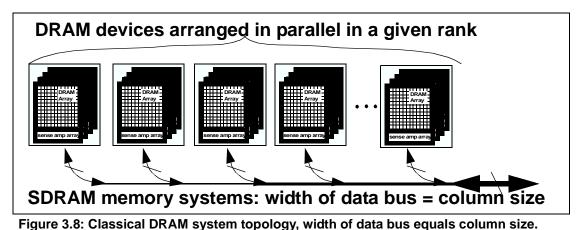

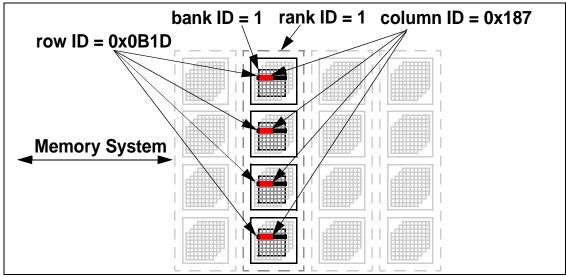

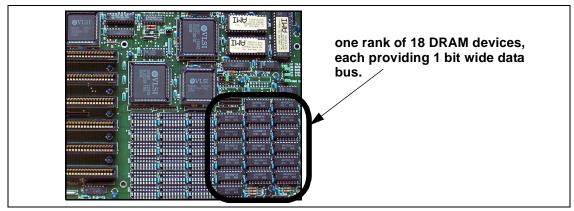

In a typical application, four 16 Meg x16 devices can be connected in parallel to form a single *rank* of memory with a 64 bit wide data bus and 128 MB of storage. Alternatively, sixteen 64 Meg x4 devices forms a single rank of memory with a 64 bit wide data bus and 512 MB of storage. DRAM memory system organizations are examined separately in a following chapter.

### 2.7.1 Device Configuration Trade-offs

In the 256 Mbit SDRAM device, the size of the row does not change in different configurations, and the number of column per row simply decreases with wider data busses specifying a larger number of bits per column. However, the constant row size between different configurations of DRAM devices within the same DRAM device generation is not a generalized trend that can be extended to different device generations. For example, table

| Device configuration | 512 Meg x 4 | 256 Meg x 8 | 128 Meg x 16 |

|----------------------|-------------|-------------|--------------|

| Number of banks      | 8           | 8           | 8            |

| Number of rows       | 16384       | 16384       | 8192         |

| Number of columns    | 2048        | 1024        | 1024         |

| Data bus width       | 4           | 8           | 16           |

TABLE 2.2: Three different configurations of 1 Gbit DDR2 SDRAM device

2.2 shows different configurations of a 1 Gbit DDR2 SDRAM device where the number of bits per row differs between the x8 configuration and the x16 configuration.

DDR2 SDRAM devices at the 1 Gbit and above densities have 8 banks of DRAM arrays per device. In the x4 and x8 configuration of the 1 Gbit DDR2 SDRAM device, there are 16384 rows per bank and each row consists of 8192 bits. In the x16 configuration, there are 8192 rows and each row consists of 16384 bits. These different configurations lead to different numbers of bits per bitline, different numbers of bits per row activation, and different number of bits per column access. In turn, differences in the number of bits moved per command lead to different power consumption and performance characteristics for different configurations of the same device generation. For example, the 1 Gbit, x16 DDR2 SDRAM device is configured with 16384 bits per row, and each time a row is activated, 16384 DRAM cells are simultaneously discharged onto respective bitlines, sensed, amplified then restored. The larger row size means that a 1 Gbit, x16 DDR2 SDRAM device with 16384 bits per row consumes significantly more current per row activation than 1 Gbit x4 and x8 configuration with 8192 bits per row. The differences in current consumption characteristics of DRAM devices.

### 2.8 Data I/O

### 2.8.1 Burst Lengths and Burst Ordering

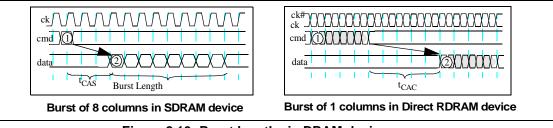

In SDRAM and DDRx SDRAM devices, a column read command moves a variable number of columns. As illustrated in the section on the programmable mode register, an SDRAM device can be programmed to return 1, 2, 4, or 8 columns of data as a single burst that takes 1, 2, 4 or 8 cycles to complete. In contrast, a Direct RDRAM device returns a single column of data with an 8 beat<sup>\*</sup> burst. Figure 2.10 shows an 8 beat, 8 column read data

Figure 2.10: Burst lengths in DRAM devices.

burst from an SDRAM device and an 8 beat, single column read data burst from a Direct RDRAM device. The distinction between the 8 column burst of an SDRAM device and the single column data burst of the Direct RDRAM device is that each column of the SDRAM device is individually addressable, and given an a column address in the middle of an 8 column burst, the SDRAM device will re-order the burst to provide the data of the requested address first. This capability is known as critical-word forwarding. For example, in an SDRAM device programmed to provide a burst of 8 columns, a column read command with a column address of 17 will result in the data burst of 8 columns of data with the address sequence of 17-18-19-20-21-22-23-16 or 17-16-19-18-21-20-23-22, depending on the burst type as defined in the programmable register. In contrast, each column of a Direct RDRAM

<sup>\*.</sup> In DDRx and Direct RDRAM devices, two beats of data are transferred per clock cycle.

device consists of 128 bits of data, and each column access command moves 128 bits of data in a burst of 8 contiguous beats in strict burst ordering. That is, differing from SDRAM and DDRx SDRAM devices, Direct RDRAM devices support neither programmable burst lengths nor different burst ordering.

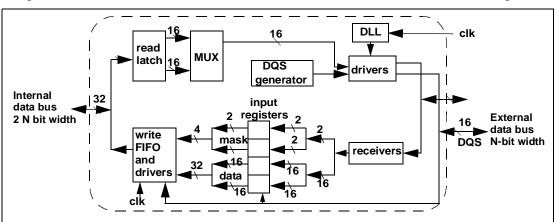

#### 2.8.2 N-bit Prefetch

In SDRAM devices, each time a column read command is issued, the control logic determines the duration and ordering of the data burst, and each column is moved separately from the sense amplifiers through the I/O latches to the external data bus. However, the separate control of each column limits the operating data rate of the DRAM device. As a result, in successive generations of SDRAM, and DDRx SDRAM devices, successively larger numbers of bits are moved in parallel from the sense amplifiers to the read latch, and the data is then pipelined through a multiplexor to the external data bus.

Figure 2.11 illustrates the data I/O structure of a DDR SDRAM device. Figure 2.11

Figure 2.11: Data I/O in DDR SDRAM device illustrating 2-bit prefetch.

shows that given the width of the external data bus as N, 2N bits are moved from the sense amplifiers to the read latch, the 2N bits are then pipelined through the multiplexors to the external data bus. In DDR2 SDRAM devices, and the number of bits prefetched by the internal data bus is 4N. The N bit prefetch strategy in DDRx SDRAM devices means that internal DRAM circuits can remain essentially unchanged between transitions from SDRAM to DDRx SDRAM, but operating data-rate of DDRx SDRAM devices can be increased to levels not possible with SDRAM devices. However, the downside of the N bit prefetch architecture is that short bursts are no longer supported. For example, in DDR SDRAM devices, a minimum burst length of 2 columns of data are accessed per column read command, and in DDR2 SDRAM devices, a minimum burst length of 4 columns of data are accessed per column read command. This trend is likely to continue in future generations of DDR3 and DDR4 SDRAM devices, thus requiring longer data bursts for each successive generations of higher data rate DRAM devices.

## 2.9 DRAM Device Packaging

One difference between DRAM and logic devices is that most DRAM devices are commodity items whereas logic devices such as processors and *application specific integrated circuits (ASIC)* are typically specialized devices that are not commodity items. The result of the commodity status for DRAM devices is that even more so than logic device manufacturers, DRAM device manufacturers are extraordinarily sensitive to cost. One area that reflects the cost sensitivity is the packaging technology utilized by DRAM devices. Table 2.3 shows the expected pin count and relative costs from the 2002 *International*

|                                       | 2004       | 2007        | 2010        | 2013        | 2016        |

|---------------------------------------|------------|-------------|-------------|-------------|-------------|

| Semi Generation (nm)                  | 90         | 65          | 45          | 32          | 22          |

| High Perf. device pin count           | 2263       | 3012        | 4009        | 5335        | 7100        |

| High Perf. device<br>cost (cents/pin) | 1.88       | 1.61        | 1.68        | 1.44        | 1.22        |

| Memory device pin count               | 48-160     | 48-160      | 62-208      | 81-270      | 105-351     |

| Memory device pin cost<br>(cents/pin) | 0.34 -1.39 | 0.27 - 0.84 | 0.22 - 0.34 | 0.19 - 0.39 | 0.19 - 0.33 |

TABLE 2.3: ITRS roadmap projections for package pin count and costs

*Technology Roadmap for Semiconductors (ITRS)* for high performance logic devices as compared to memory devices. Table 2.3 shows the trend that memory chips such as DRAM will continue to be manufactured with relatively lower cost packaging with lower pin count and lower cost per pin.

Figure 2.12 shows 4 different packages used in previous and current generations of

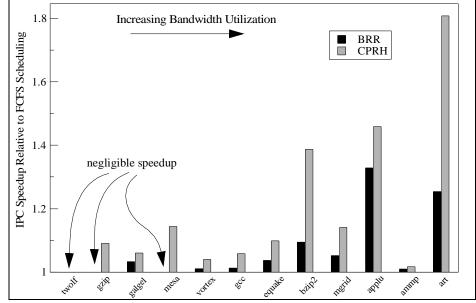

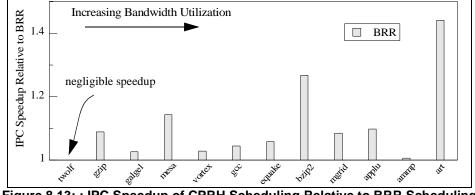

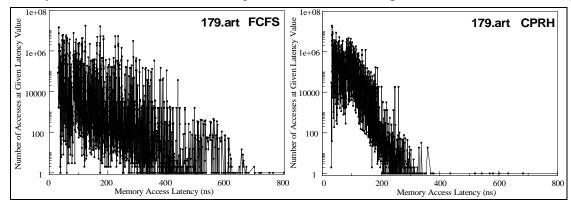

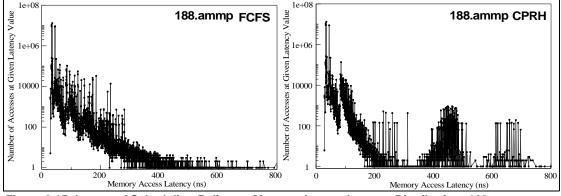

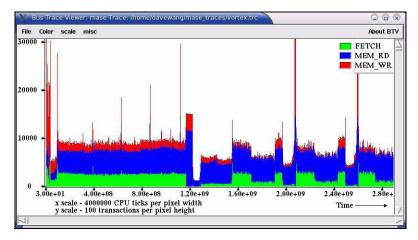

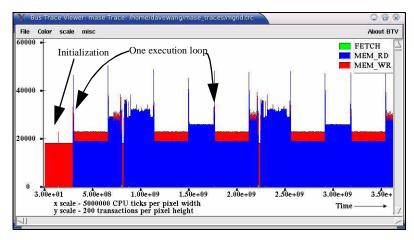

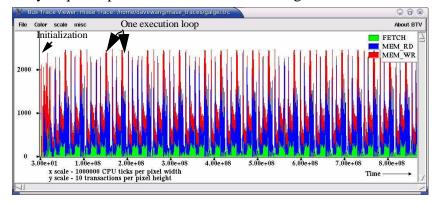

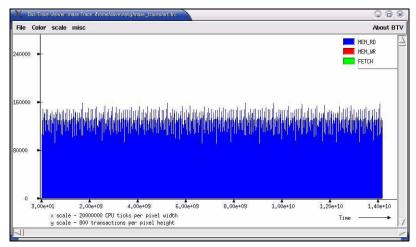

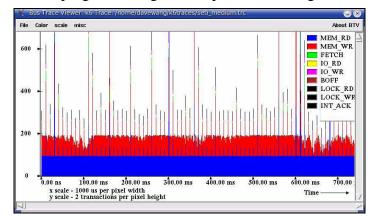

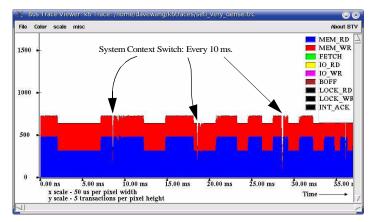

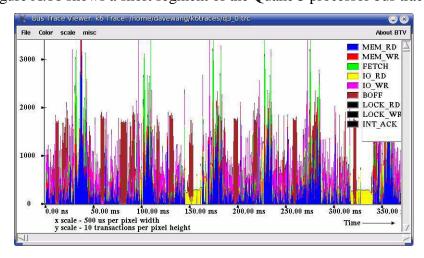

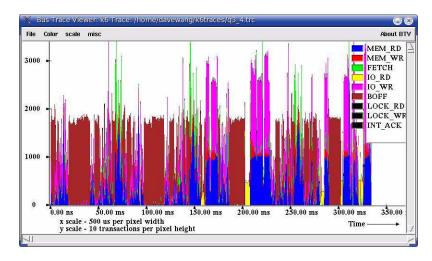

Figure 2.12: DRAM device packages.