**ABSTRACT**

Title of Dissertation: LOW PHASE NOISE DESIGN TECHNIQUES FOR

PHASE LOCKED LOOP BASED INTEGRATED RF

FREQUENCY SYNTHESIZERS

Weixin Kong, Doctor of Philosophy, 2005

Dissertation Directed By: Professor H. C. Lin

performance requirements of the wireless application.

Department of Electrical and Computer Engineering

The explosive growth of wireless communication market today has brought an increasing demand for high performance radio-frequency integrated circuits (RFIC) at low cost. As a result, there is a great interest in integrating the various blocks of a communication system on a single chip transceiver. One of the most difficult components to integrate is the frequency synthesizer that generates the local oscillator (LO) carrier signal. The difficulty comes mostly from the very stringent phase noise

In this dissertation, we are interested in improving phase noise performance of integrated phase-locked-loop (PLL) based radio-frequency (RF) frequency synthesizers. The most important phase noise contributors in a PLL are voltage controlled oscillator (VCO) and Phase Frequency Detector/Charge Pump/Frequency Dividers (PFD/CP/Divider). In this dissertation, we focus on the analysis of the phase noise generation mechanism in these key building blocks and the derivation of the analytical relationship between their phase noise performance and circuit design parameters. For VCO, based on the understanding of phase noise generation process

in cross-coupled CMOS LC VCO, a simple yet accurate analytical phase noise model was proposed and a closed form formula for the fitting factor in Leeson's model is derived. For PFD/CP/Divider, due to the presence of many digital components, their phase noise model is studied from the point of view of timing jitter. The analytic equation that relates the PFD/CP/Divider 1Hz normalized phase noise floor and circuit parameters is derived. Based on the theoretical analysis, the design schemes for optimizing the phase noise performance are proposed and verified by simulation and experimental prototype measurement.

# LOW PHASE NOISE DESIGN TECHNIQUES FOR PHASE LOCKED LOOP BASED INTEGRATED RF FREQUENCY SYNTHESIZERS

By

## Weixin Kong

B.S., Tsinghua University, 1996 M.S., Brown University, 2001

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2005

Advisory Committee: Professor H. C. Lin, Chair Professor R. Newcomb Professor M. Pecht Professor N. Goldsman Professor P. Abshire © Copyright by Weixin Kong 2005

# Acknowledgements

First, I would like to thank my advisor, Professor H. C. Lin, for his guidance and encouragement throughout this Ph.D. work. I am deeply grateful to him for giving me the opportunity to be a part of the MIPS program and for leading me into the wireless transceiver project which eventually resulted in this dissertation.

I would also like to thank Professors R. Newcomb, M. Pecht, N. Goldsman and P. Abshire for serving on my committee.

I want to extend special thanks to Dr. Kai Duh, president of Maryland Semiconductor Inc., for making the project for this Ph.D. work possible, for constant and generous support during the project.

I would like to thank my colleagues at Maryland Semiconductor Inc.: C. H. Yeh and Leon Luo for RF transceiver and synthesizer design help; Jay Chen for system knowledge; Johnathan Pfeifer and Bin Zhang for layout work and technical support in the lab. Their support and friendship have been a great help.

I would like to thank my parents, my sister and my wife. They are the source of my strength and the reason of my endeavor.

This research was supported in part by the MIPS (Maryland Industrial Partnerships)

Program between the University of Maryland and the Maryland Semiconductor Inc.,

where this work was performed.

# Table of Contents

| Acknowledgements                                                 | ii  |

|------------------------------------------------------------------|-----|

| Table of Contents                                                | iii |

| List of Abbreviations                                            | v   |

| Chapter 1: Introduction                                          | 1   |

| 1.1 Motivation                                                   | 1   |

| 1.2 Organization of the dissertation                             | 2   |

| Chapter 2: Frequency Synthesizer and Phase Noise                 | 3   |

| 2.1 Role of frequency synthesizer in a wireless transceiver      | 3   |

| 2.2 Why phase noise is important?                                | 4   |

| 2.2.1 The definition of phase noise                              | 4   |

| 2.2.2 Phase noise effect on receiver performance                 | 7   |

| 2.3 Architectures of frequency synthesizers                      |     |

| 2.4 Introduction to PLL based frequency synthesizers             | 10  |

| 2.4.1 What is PLL based frequency synthesizers?                  |     |

| 2.4.2 Linear model of PLL based frequency synthesizers           |     |

| 2.4.3 Type and order of PLL                                      |     |

| 2.4.4 Charge pump based PLL                                      | 15  |

| 2.5 Noise sources in PLL based frequency synthesizers            |     |

| 2.6 Closed loop PLL output phase noise spectrum                  |     |

| Chapter 3: Design Techniques for Low Phase Noise VCOs            |     |

| 3.1 Introduction to oscillators                                  |     |

| 3.1.1 Feedback modeling and oscillation conditions               | 26  |

| 3.1.2 Negative resistance modeling                               |     |

| 3.1.3 Oscillator start-up conditions and amplitude stabilization |     |

| 3.2 CMOS cross-coupled LC oscillator topologies                  |     |

| 3.3 Related work on LC VCO phase noise model                     | 35  |

| 3.4 A generalized linear phase noise model                       | 38  |

| 3.4.1 Phasor representation of AM and PM noise                   |     |

| 3.4.2 Phase noise from LC tank                                   |     |

| 3.4.3 Phase noise from cross-coupled pair                        | 40  |

| 3.4.4 Phase noise from tail current source                       | 43  |

| 3.4.5 Total phase noise equation                                 | 44  |

| 3.4.6 Comparison with other models                               | 45  |

| 3.5 A low phase noise 2 GHz LC VCO design and analysis           | 46  |

| 3.5.1 Tank passive components design                             |     |

| 3.5.2 Circuit design                                             |     |

| 3.5.3 Analysis and simulatiom                                    |     |

| 3.5.4 Measurement results                                        |     |

| Chapter 4: Low phase noise PFD/CP/Divider design                 |     |

| 4.1 Introduction to PFD/CP/Divider in PLL                        |     |

| 4.1.1 PFD (Phase-Frequency Detector) and CP (Charge Pump)        |     |

| 4.1.2 Divider                                                    | 61  |

| 4.2 Related work on PFD/CP/Divider phase noise analysis     | 62  |

|-------------------------------------------------------------|-----|

| 4.3 Organization of this chapter                            | 63  |

| 4.4 Dead zone free PFD/CP design                            | 64  |

| 4.5 Timing jitter and phase noise                           |     |

| 4.6 PFD/CP/Divider phase noise model                        | 68  |

| 4.6.1 PFD/Divider phase noise                               | 68  |

| 4.6.2 Charge pump phase noise                               | 79  |

| 4.7 Low phase noise PFD/CP/Divider design                   | 80  |

| 4.7.1 Dead zone free PFD/CP                                 |     |

| 4.7.2 Prescaler                                             | 81  |

| 4.7.3 CMOS divider and PFD                                  | 82  |

| 4.7.4 Prediction of total phase noise from PFD/CP/Divider   | 83  |

| Chapter 5: Experimental Prototype Design                    | 84  |

| 5.1 Introduction to the WLAN 802.11b/g RF transceiver       | 84  |

| 5.2 Determining specifications of the frequency synthesizer |     |

| 5.2 Prototype design                                        | 87  |

| 5.2.1 Frequency plan                                        | 88  |

| 5.2.2 Frequency divider programming                         | 89  |

| 5.2.3 Loop filter design                                    |     |

| 5.3 Measurement results                                     |     |

| Chapter 6: Conclusions                                      | 101 |

| Bibliography                                                |     |

# List of Abbreviations

AC Alternating Current

**AM** Amplitude Modulation

**BER** Bit Error Rate

**BPSK** Binary Phase shifted Keying

CMOS Complementary Metal Oxide Semiconductor

CP Charge Pump

DC Direct Current

**EVM** Error Vector Magnitude

IC Integrated Circuit

IF Intermediate Frequency

**ISF** Impulse Sensitivity Function

LC Inductor Capacitor

LNA Low Noise Amplifier

LO Local Oscillator

LPF Loop Filter

**NMF** Noise Modulation Function

NMOS N-channel Metal Oxide Semiconductor

PA Power Amplifier

PD Phase Detector

PFD Phase Frequency Detector

PSD Power Spectral Density

PLL Phase Locked Loop

PM Phase Modulation

PMOS P-channel Metal Oxide Semiconductor

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase Shifted Keying

RF Radio Frequency

RMS Root Mean Square

SNR Signal to Noise Ratio

SSB Single Side Band

VCO Voltage Controlled Oscillator

VSA Vector Signal Analyzer

WLAN Wireless Local Area Network

vi

# **Chapter 1: Introduction**

#### 1.1 Motivation

The wireless personal communication market has been growing explosively due to the ever emerging new applications and dropping prices. A low cost, small, long-battery-life solution has been the dream for decades. Many efforts have been devoted to the integration of such circuits in low-cost technology in order to reach the goal. Most of the baseband signal processing circuits use a CMOS process because of lower cost and higher integration capability. Recently research efforts are being made to integrate most RF functions in CMOS with the goal of realizing single-chip RF-to-baseband systems.

A PLL (Phase Locked Loop) based frequency synthesizer is one of the major building blocks for an RF transceiver. The role of a frequency synthesizer is to provide the reference frequency for frequency translation in wireless transceivers. An integrated frequency synthesizer in CMOS process that meets strict phase noise performance requirements of today's wireless communication standards remains a challenging problem due to both technology limitations on high quality on-chip passive components and lack of a proper and efficient optimization methodology.

This research focuses on the analysis and design techniques for low phase noise integrated phase-locked-loop (PLL) based radio-frequency (RF) frequency synthesizers in CMOS technology. In the dissertation, the phase noise generation mechanism in the key building blocks is analyzed and the analytical relationship between their phase noise performance and circuit design parameters is derived.

Based on the theoretical analysis, the design schemes for optimizing the phase noise performance are proposed and verified by simulation and experimental prototype measurement.

#### 1.2 Organization of the dissertation

In Chapter 2, the fundamentals of frequency synthesizer and phase noise are reviewed. Various noise sources in PLL based frequency synthesizers are identified and their contributions to the overall closed loop phase noise are derived.

In Chapter 3, low phase noise design techniques for CMOS cross-coupled LC VCO are examined. A generalized linear phase noise model based on physical mechanism of phase noise is proposed and a closed form phase noise formula for LC cross-coupled VCO is derived.

In Chapter 4, low noise design techniques for other blocks in PLL are presented, including low noise frequency dividers, phase frequency detectors and charge pumps. Due to the presence of many digital components, their phase noise model is studied from the point of view of timing jitter. The analytic equation that relates the PFD/CP/Divider 1Hz normalized phase noise floor and circuit parameters is derived.

In Chapter 5, the design of an experimental prototype and the measurement results are presented.

Chapter 6 concludes the dissertation.

# **Chapter 2: Frequency Synthesizer and Phase Noise**

# 2.1 Role of frequency synthesizer in a wireless transceiver

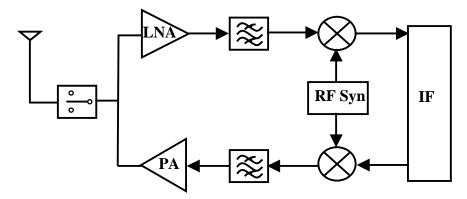

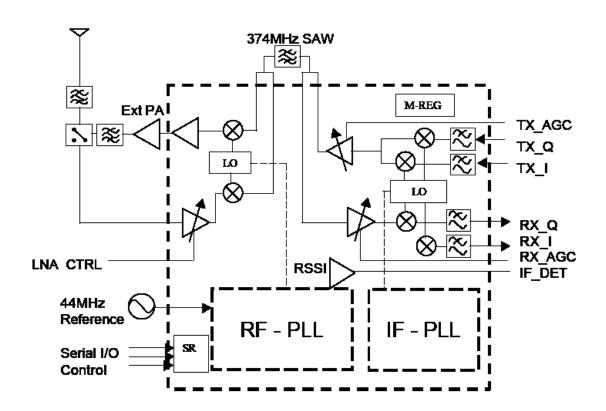

The role of a frequency synthesizer is to provide the reference frequency for frequency translation in wireless transceivers [Raza97]. Fig. 2.1 shows the block diagram of a typical super-heterodyne wireless transceiver RF section. A RF synthesizer is used to generate the local oscillator (LO) signals in down- and upconversion mixers for the frequency translation.

Figure 2.1 A typical wireless transceiver RF section

The function of frequency synthesizer is similar in receiver and transmitter path and generally the requirement of receiver is more stringent. So in the following discussion, we will focus on receiver path.

Considering the receiver path in the above diagram, there are several different channels being received at the antenna. The RF frequency synthesizer is tuned so that the output signal of the down-conversion mixer is at a constant IF frequency. The signal is then easier to filter and deal with because it is at a fixed and lower frequency from this point on.

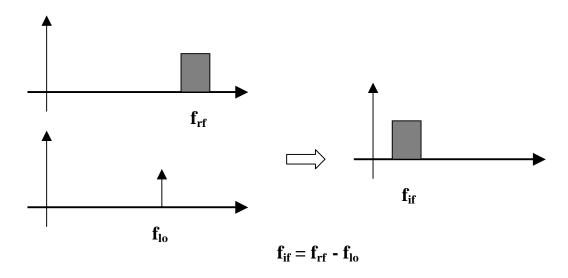

As shown in Fig. 2.2, an ideal frequency synthesizer generates a single frequency tone. In the receiver case, it mixes with the received RF signal spectrum and shifts it down to IF. The output spectrum is the convolution result of the synthesizer tone with the received RF signal spectrum.

Figure 2.2 Role of frequency synthesizer in receiver path

#### 2.2 Why phase noise is important?

#### 2.2.1 The definition of phase noise

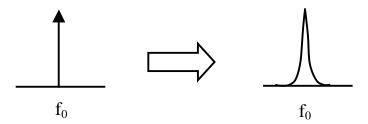

In section 2.1 we showed that the ideal output spectrum of a frequency synthesizer should be a single tone at the desired frequency in order to provide the reference frequency for accurate frequency translation. A single tone in the frequency domain is equivalent to a pure sinusoidal waveform in the time domain. In a practical frequency synthesizer, the random amplitude and phase deviations occur due to the inherent (e.g., device thermal and shot noise) and external (e.g., power line disturbance) noise sources. These deviations produce energy in the frequencies other than the desired

frequency. Figure 2.3 shows the spectrum of ideal and practical frequency synthesizer output signal. Phase noise is the parameter to measure the spectral purity of a frequency synthesizer output signal.

Figure 2.3 Spectrum of ideal and practical frequency synthesizer output

The ideal synthesizer output has a pure sinusoidal waveform

$$V(t) = A_0 \cos \omega_0 t, \qquad (2.1)$$

where  $A_0$  and  $\omega_0$  are nominal amplitude and angular frequency of the signal. When amplitude and phase fluctuations are included, the waveform becomes

$$V(t) = [A_0 + \varepsilon(t)]\cos[\omega_0 t + \phi(t)], \qquad (2.2)$$

where g(t) represents amplitude fluctuations and  $\phi(t)$  represents phase fluctuations. Because amplitude fluctuations can be easily removed or greatly reduced by a limiter, we concentrate on phase fluctuations in a frequency synthesizer design. The  $\phi(t)$  represents the random phase fluctuations. The spectral density of the phase fluctuations is

$$S_{\phi}(f) = \int_{-\infty}^{+\infty} R_{\phi}(\tau) e^{-j2\pi f \tau} d\tau, \qquad (2.3)$$

where  $R_{\phi}(\tau)=E[\phi(t)\phi(t-\tau)]$  is the auto-correlation function of the random phase changing process. When amplitude fluctuations are negligible and the root-mean-

square (RMS) value of  $\phi(t)$  is much smaller than 1 radian, the frequency synthesizer output signal can be written as

$$V(t) = [A_0 + \varepsilon(t)] \cos[\omega_0 t + \phi(t)] \approx A_0 \cos[\omega_0 t + \phi(t)] \approx A_0 \cos[\omega_0 t] - A_0 \sin[\omega_0 t] \phi(t).$$

$$(2.4)$$

The spectral representation of V(t) can be approximated as

$$S_V(f) = \frac{A_0^2}{2} \left[ \delta(f - f_0) + S_{\phi}(f - f_0) \right], \tag{2.5}$$

where the first term represents our desired signal at nominal frequency  $f_0$  and the second term represents the undesired noise components at frequency offset  $\Delta f = f - f_0$ .

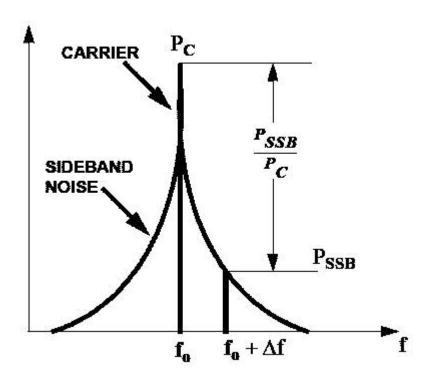

Figure 2.4 Definition of SSB phase noise

Phase noise is specified as the ratio of noise power in 1Hz bandwidth at a certain offset frequency from carrier to the carrier power [Bagh65], Figure 2.4. It is called

single side-band (SSB) phase noise and the unit is dBc/Hz. The SSB phase noise can be expressed as

$$L(\Delta f) = 10\log \frac{P_{SSB}(f_0 + \Delta f, 1Hz)}{P_{carrier}} \qquad (dBc/Hz)$$

(2.6)

where  $P_{SSB}(f_0 + \Delta f, 1Hz)$  is the noise power in 1Hz bandwidth at offset frequency  $\Delta f$  from carrier frequency  $f_0$  and  $P_{carrier}$  is the total carrier power.

## 2.2.2 Phase noise effect on receiver performance

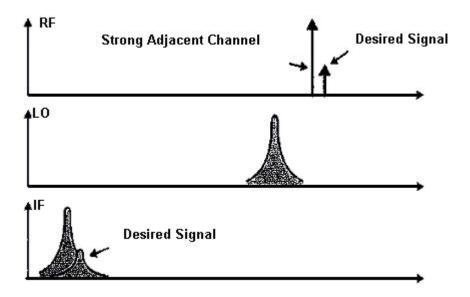

Figure 2.5 Reciprocal mixing effect on receiver performance

The phase noise has two independent impacts on the receiver front end's signal to noise ratio (SNR), hence bit error rate (BER). The first impairment is called **reciprocal mixing** [Raza96], coming out because of the presence of adjacent channel interference. To understand this impairment, consider the situation in Figure 2.5. The LO signal for down-conversion has a noisy spectrum as shown in Figure 2.3. The receiver sees two RF signals, one desired signal with small power level and one

interference signal at adjacent channel with large power level. The down-converted signal will consist of two overlapping spectra. The desired signal suffers from significant noise due to the tail of the interference signal.

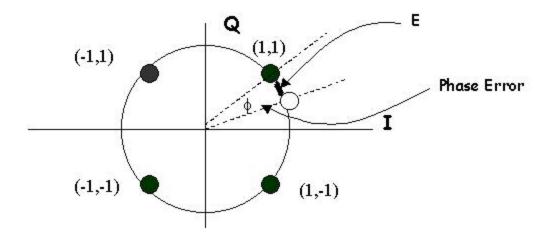

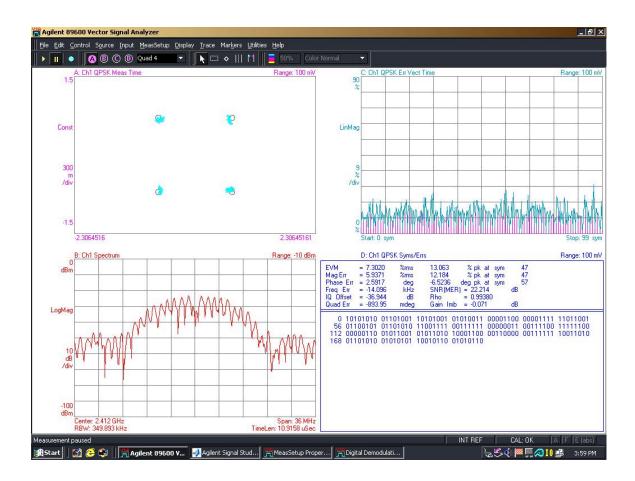

Figure 2.6 Phase impairment effect on QPSK signal demodulation

The second impact, called phase impairment [Leun02], is best understood in the phase domain. In the phase domain, the phase noise appears as phase error. Assume the frequency synthesizer is used to demodulate a phase-encoded signal, such as QPSK (Quadrature Phase Shifted Keying) signal. Figure 2.6 shows the constellation diagram of QPSK signal and the effect of phase noise on its demodulation. In the figure, the darkened circle at upper-right corner corresponds to the ideal signal for bits (1,1) if there is no phase error. Due to the phase noise of LO signal, the actual demodulated signal is the non-filled circle. The phase error between the ideal signal and the actual received signal is statistically distributed and typically modeled using Gaussian distribution with standard deviation equal to root-mean-square (RMS) phase error of the Local Oscillator. If the RMS phase error is large enough, it could cause

the signal to be mis-detected. Higher order modulation schemes, such as QAM16 and QAM64, have more compact constellation diagram than simple QPSK. They are more subject to Local Oscillator phase impairment effect.

The phase impairment effect is always there, with or without interference, whereas the reciprocal mixing effect is there only when there is adjacent channel interference. Which impact is more dominant depends mostly on the applications. Generally speaking, the reciprocal mixing is dominant in narrow band low data rate applications because of small channel spacing and simple modulation scheme, while the phase impairment effect is dominant in broad band high data rate applications because of large channel spacing and complex modulation scheme.

# 2.3 Architectures of frequency synthesizers

There are many ways to implement a frequency synthesizer. For an integrated radio transceiver, we want the synthesizer to be able to generate a tunable frequency in the gigahertz range with low phase noise using minimum power. A **direct digital frequency synthesizer** [Abid94] is best known for its fast switching and very fine frequency resolution. It can also easily be integrated because no off chip components are required. But due to technology limitations, it takes large power consumption to synthesize very high frequencies directly. A **phase-locked-loop-based indirect frequency synthesizer** [Egan81] is the most commonly used technique due to its high performance, namely, low phase noise and low power consumption. We will focus on PLL based frequency synthesizers in this dissertation.

#### 2.4 Introduction to PLL based frequency synthesizers

#### 2.4.1 What is PLL based frequency synthesizers?

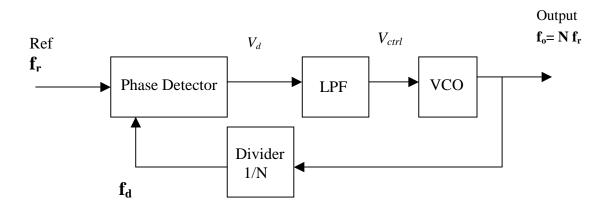

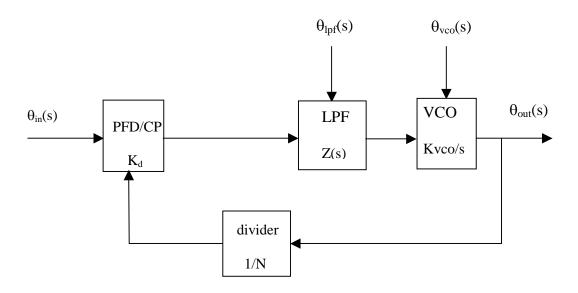

A PLL based frequency synthesizer contains four basic components as shown below in Figure 2.7.

Figure 2.7 Typical PLL based frequency synthesizer block diagram

The Phase detector (PD) determines the difference between the phases of two signals and converts the difference to an error signal  $V_d$ . The loop filter (LPF) removes the high-frequency components from  $V_d$  and generates  $V_{ctl}$ , the voltage-controlled oscillator (VCO) controlling voltage. The VCO produces the output frequency. The frequency divider determines the ratio of the desired VCO frequency and the reference frequency.

A Phase-Locked-Loop locks the output phase or frequency to an accurate reference, which is usually implemented by a Crystal. When the loop is locked, the Phase Detector sees two in-phase waveforms  $f_r$  and  $f_d$  at its inputs and  $f_o$  equals to  $Nf_r$ . If for some reason  $f_r > f_d$ , Phase Detector generates positive  $V_d$  and  $V_{ctrl}$  goes up. So

the VCO output frequency increases. Vice versa, if  $f_r < f_d$ ,  $V_{ctrl}$  goes down and the VCO output frequency decreases.

There are many different ways to implement the circuit blocks of a PLL. The PLLs can be roughly classified into two classes based on the implementation of phase detector, *i.e.* linear PLLs and digital PLLs. The linear PLLs (LPLL) use analog multiplier as phase detector. The digital PLLs use digital phase detectors such as EXOR gates, edge triggered JK flip flops, or tri-state phase-frequency detectors.

In a modern PLL, the phase detector is usually implemented by tri-state phase frequency detector combined with charge pump (PFD/CP). The PFD can detect both the phase and frequency difference between two signals. Consequently, the PFD/CP based PLL will have infinite pull-in range, irrespective of the type of loop filter used.

### 2.4.2 Linear model of PLL based frequency synthesizers

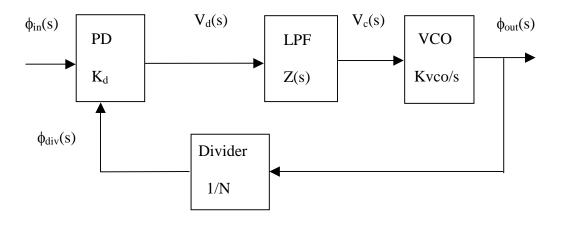

Figure 2.8 A linear model for PLL

Generally, a linearized model can be used to get more insight into the PLL design. Fig. 2.8 shows the linear model of a typical PLL. In the linear model, the PD has a gain of  $K_d$  (V/rads), the loop filter has a transfer function Z(s), and the VCO has a

gain of Kvco (rads/sV). We use phase as the input and output variable in the model. Because phase is the integrated value of frequency, an integrator 1/s is included in the VCO block so that the VCO block has a gain of  $K_{vco}$  /s. The open loop transfer function G(s) can be written as

$$G(s) = K_d Z(s) \frac{K_{vco}}{s} \frac{1}{N}$$

(2.7)

Therefore the closed loop transfer function can be written as

$$H(s) = \frac{\phi_{out}(s)}{\phi_{in}(s)} = N \frac{G(s)}{1 + G(s)}$$

(2.8)

### 2.4.3 Type and order of PLL

The order of PLL is defined as the number of poles of the open loop transfer function G(s). The simplest PLL is a first order loop, in which loop filter is a simple gain block with gain  $K_p$ . Without loss of generality, let  $K_p$  equal to 1. The transfer function

$$G(s) = K_d \frac{K_{vco}}{s} \frac{1}{N} = \frac{K}{s}, \text{ where } K = \frac{K_d K_{vco}}{N}$$

(2.9)

$$H(s) = N \frac{G(s)}{1 + G(s)} = N \frac{K}{s + K}$$

(2.10)

The **loop bandwidth**  $\omega_c$  is defined as the frequency where the open loop transfer function G(s) drops to unity. We can see that  $\omega_c$  is always equal to the DC gain K for the first order PLL. The closed loop transfer function has only modest attenuation at the stop bands, *i.e.* -20dB/decade.

A simple RC based low pass filter creates a second order PLL if it is used as the loop filter. The loop filter transfer function Z(s) can be written as

$$Z(s) = \frac{1}{1 + sRC} = \frac{1}{1 + \frac{s}{\omega_{LPF}}}$$

(2.11)

Therefore the loop transfer function

$$G(s) = K_d Z(s) \frac{K_{vco}}{s} \frac{1}{N} = \frac{K\omega_{LPF}}{s^2 + \omega_{LPF} s}$$

, where  $K = \frac{K_d K_{vco}}{N}$  (2.12)

$$H(s) = N \frac{G(s)}{1 + G(s)} = N \frac{K\omega_{LPF}}{s^2 + \omega_{LPF} s + K\omega_{LPF}}$$

(2.13)

The open loop transfer function G(s) has two poles, one at the origin and one at the loop filter 3dB cutoff frequency  $\omega_{LPF}$ . The closed loop transfer function H(s) can be written as a familiar form that describes a second order feedback system

$$H(s) = N \frac{\omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2} , \qquad (2.14)$$

where

$$\omega_n = \sqrt{K\omega_{LPF}}$$

,  $\xi = \frac{1}{2}\sqrt{\frac{\omega_{LPF}}{K}}$ .

$\omega_{\rm n}$  and  $\zeta$  are the natural frequency and damping factor of the system. The second order PLL gives us one more degree of freedom in setting the loop bandwidth. The loop bandwidth depends on both the DC gain K and the loop filter 3dB cutoff frequency  $\omega_{\rm LPF}$ . The closed loop transfer function has -40dB/decade attenuation at stop bands.

The first and second order PLL discussed above has only one pole at origin in their open loop transfer function G(s). The number of poles at origin in G(s) is defined as **the type of PLL**. The above PLLs are called type I PLL. One problem of the type I PLL based frequency synthesizers is their limited hold in and pull in range. **The hold** in range is the frequency range over which a PLL can statically maintain phase

tracking. **The pull-in range** is the range within which a PLL can get locked from unlocked state. These two parameters describe the PLL locking process. If the PLL is initially unlocked, the phase error,  $\phi_e = \phi_{in} - \phi_{div}$ , can take an arbitrarily large value and as a result, the linear model is no longer valid. The mathematics behind the unlocked state is beyond the scope of this dissertation. Please refer to [Gard79] for detail explanation.

The limited hold in and pull in range issue is solved in the type II PLL. The type II PLL has two poles at the origin in its open loop transfer function G(s). The type II PLL has infinite hold in and pull in range. The second pole at origin can be created by including an integrator in loop filter Z(s), which means we need an active loop filter for typical Phase Detector implementations. The active loop filters generate extra noise and consume more power. Another solution is to use a tri-state phase frequency detector (PFD) and charge pump. This charge pump based PLL (CPLL) can implement type II PLL using passive loop filter and is the most popular structure in modern PLL design. The CPLL will be discussed in next section.

## 2.4.4 Charge pump based PLL

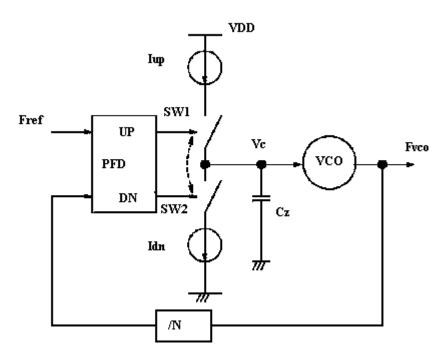

Figure 2.9 Block diagram of charge pump based PLL

Figure 2.9 shows a simplified charge pump based PLL (CPLL) block diagram. A phase frequency detector (PFD) is a digital phase detector having UP, DOWN, and high impedance, three states based on the phase and frequency relation of its input. A charge pump consists of two switched current sources which drive a combination of several resistors and capacitors to form a filter for the PLL with a pole at the origin. The switches of a charge pump are controlled by the PFD output signals UP and DOWN. Since the pulse width of the UP (DOWN) signal is proportional to the amount of phase error at the PFD input, the charge pump will charge (discharge) capacitor  $C_z$  accordingly while switch SW1 (SW2) is on. The VCO control voltage Vc is proportional to the integration of phase error  $\phi_e$  and can be written as

$$V_c(s) = \frac{\phi_e I_{cp}}{2\pi} \frac{1}{sC_z}.$$

(2.15)

The open loop transfer function G(s) becomes

$$G(s) = \frac{I_{cp}}{2\pi} \frac{1}{sC_z} \frac{K_{vco}}{s} \frac{1}{N}$$

(2.16)

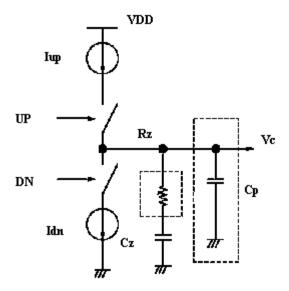

This type II, second order loop is not stable since two poles are at the origin. To make the system stable, a zero is inserted by adding a resistor  $R_z$  in series with  $C_z$  as shown in Figure 2.10. Now the open loop transfer function G(s) becomes

$$G(s) = \frac{I_{cp}}{2\pi} \frac{1 + sR_z C_z}{sC_z} \frac{K_{vco}}{s} \frac{1}{N},$$

(2.17)

which contains a zero at  $\omega_z = 1/R_z C_z$ . In Figure 2.10, there is an additional capacitor  $C_p$ , which is commonly used to improve the stop band attenuation performance. The final open transfer function G(s) is

$$G(s) = \frac{I_{cp}K_{vco}}{2\pi N} \frac{1 + sR_zC_z}{s^2(C_z + C_p)(1 + sR_zC_1)}, \text{ where } C_1 = \left(\frac{1}{C_z} + \frac{1}{C_p}\right)^{-1}. \quad (2.18)$$

Figure 2.10 Loop filter with additional zero and pole

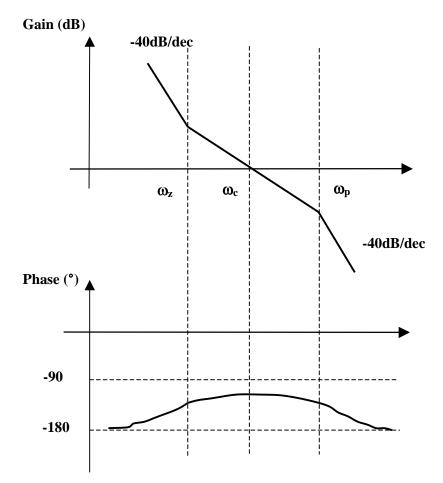

Figure 2.11 shows the Bode plot of a CPLL with the loop filter shown in Figure 2.10. This is a type II, third order loop with one zero at  $\omega_z = 1/R_z C_z$  and one pole at  $\omega_p = 1/R_z C_1$  in addition to two poles at the origin. To guarantee an enough phase margin, we usually place zero  $\omega_z$  at  $\alpha$  times below loop bandwidth  $\omega_c$  and the third pole  $\omega_p$  at  $\beta$  times above  $\omega_c$ . The factors  $\alpha$  and  $\beta$  are typically set to  $3 \sim 4$  to give a phase margin of approximately  $45 \sim 60$  degree. In the above case, it means  $C_p << C_z$ . The third pole  $\omega_p = 1/R_z C_1 \approx 1/R_z C_p$ . The loop bandwidth  $\omega_c$  equals approximately

$$\omega_c \approx \frac{I_{cp} K_{vco} R_z}{2\pi N} \frac{C_z}{C_z + C_p} \approx \frac{I_{cp} K_{vco} R_z}{2\pi N}.$$

(2.19)

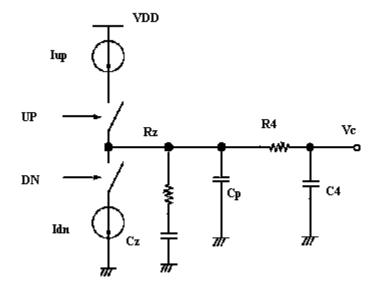

This type II, third order CPLL is the most popular PLL architectures used in RF frequency synthesizers and is the focus of this dissertation. To improve further the stop band attenuation performance, it is possible to add the fourth pole in G(s) by

adding another resistor  $R_4$  and capacitor  $C_4$  in its loop filter, shown in Figure 2.12. The analysis of this type II, fourth order CPLL can be carried out similarly as above.

Figure 2.11 Bode plot of type II, third order PLL

Figure 2.12 Loop filter with the fourth pole

# 2.5 Noise sources in PLL based frequency synthesizers

The focus of this dissertation is the phase noise performance of PLL based frequency synthesizers. The sources of phase noise within a PLL synthesizer include:

- 1. VCO phase noise

- 2. Reference oscillator phase noise

- 3. Noise from the PFD/CP and digital dividers

- 4. Noise from components in the loop filter

Figure 2.13 Noise sources in a PLL

These noise sources are grouped into three groups in Figure 2.13. Noise sources 2 and 3 are combined as one input phase noise  $\theta_{in}$ . VCO phase noise is represented by  $\theta_{vco}$  and loop filter phase noise is represented by  $\theta_{lpf}$ . The three groups of noise sources experience different transfer functions to  $\theta_{out}$ , as given in Table 2.1.

| source               | Transfer function                                                                            |

|----------------------|----------------------------------------------------------------------------------------------|

| $\theta_{ m in}$     | $H_1(s) = \frac{\theta_{out}(s)}{\theta_{in}(s)} = N \frac{G(s)}{1 + G(s)}$                  |

| $	heta_{ m vco}$     | $H_2(s) = \frac{\theta_{out}(s)}{\theta_{vco}(s)} = \frac{1}{1 + G(s)}$                      |

| $\Theta_{	ext{lpf}}$ | $H_3(s) = \frac{\theta_{out}(s)}{\theta_{lpf}(s)} = \frac{K_{vco}}{s} \frac{G(s)}{1 + G(s)}$ |

Table 2.1 Noise transfer functions in a PLL

Notice that the transfer function for  $\theta_{in}$  is a low-pass function with a gain of N at frequencies below the loop bandwidth. This means the noise contribution from the reference, PFD/CP, and divider is referred to the output enhanced in effect by N at low offset frequencies from the carrier, and suppressed at high offset frequencies from the carrier. The transfer function from the VCO to the synthesizer output is a high-pass function. It means the lower-frequency part of the noise from the VCO can be corrected by the relatively fast PLL. But for the higher-frequency part of the noise from VCO, the loop is not fast enough and is essentially an open loop. The response from the loop filter noise to the output depends on the loop filter. For example, the 3rd-order PLL has a loop filter with one zero and two poles, which gives the above transfer function a band-pass characteristics.

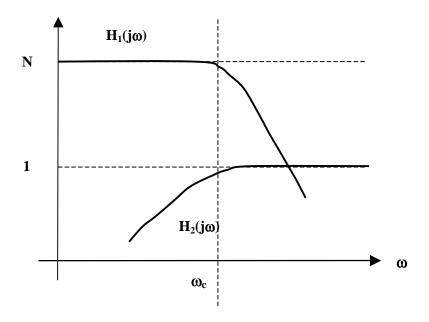

Among these noise sources, the dominant ones are VCO and PFD/CP/Divider. Also they are more difficult to predict in design because they are usually implemented on chip. The reference and loop filter are usually made from off-chip discrete components and can be modeled with good accuracy using measured phase noise data for the reference, and conventional noise models from circuit theory for the loop filter. The noise transfer functions from PFD/CP/Divider and VCO to the output are shown in Figure 2.14.

Figure 2.14 Noise transfer function for PFD/CP/Divider (H<sub>1</sub>) and VCO (H<sub>2</sub>)

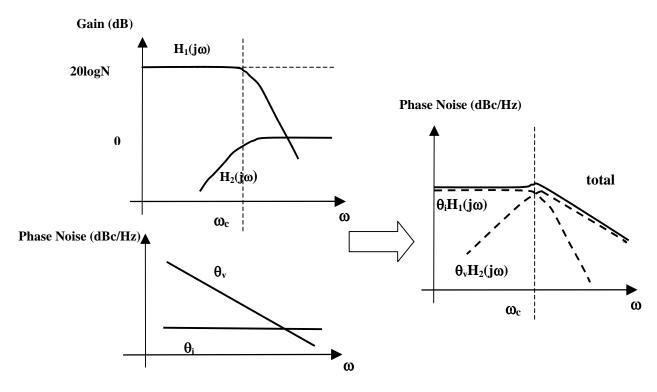

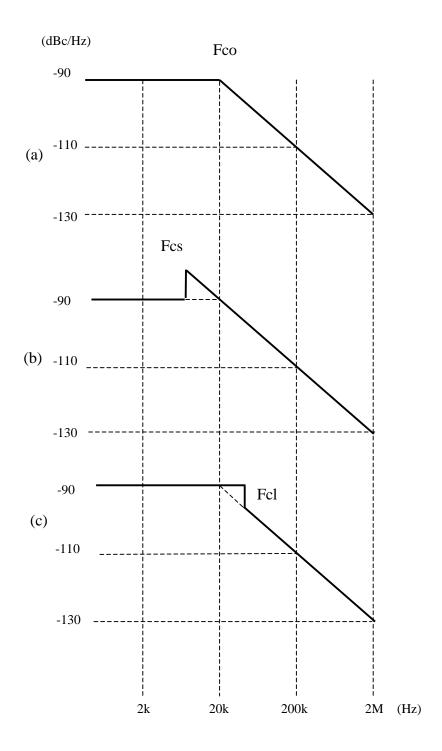

# 2.6 Closed loop PLL output phase noise spectrum

The Noise sources described in section 2.5 experience different transfer functions and are combined at the PLL output. Figure 2.15 shows a typical frequency synthesizer output spectrum. Here we consider only the white noise dominated VCO and PFD/CP/Divider noise. In white noise dominated region, free running VCO phase noise has a -20dB/decade slope and PFD/CP/Divider noise is flat respected to frequency offset. After shaping by their respective transfer function, we can see there are two distinct regions in the output total phase noise spectrum. In the region where offset frequency is smaller than loop bandwidth, the phase noise flattens out as an in band phase noise floor. This noise floor is dominated by PFD/CP/Divider because VCO phase noise is suppressed in this region. In the region where offset frequency is larger than loop bandwidth, the phase noise declines in the slope of about -

20dB/decade. The phase noise in this region is dominated by VCO because PFD/CP/Divider noise is suppressed.

Figure 2.15 PLL output phase noise spectrum

One measure to characterize the PLL output phase noise spectrum is the integrated Root Mean Squared (RMS) phase error. Its definition is

$$\Delta \phi = \frac{180}{\pi} \sqrt{2 \int_{a}^{b} L(f) df} , \qquad (2.20)$$

where  $\Delta \phi$  is the RMS phase error in degrees and L(f) is the phase noise in dBc/Hz at frequency offset f. a and b are integration limits. Usually a is very close to carrier and b is selected to be the same as channel bandwidth. This RMS phase error degrades SNR in the following manner

$$SNR = \left(\frac{180}{\pi \cdot \Delta \phi}\right)^2. \tag{2.21}$$

The RMS phase error depends on the phase noise levels in the two distinct regions and the overall phase noise spectrum shape. To reduce this RMS phase error, we must

- 1. Reduce the out of band region phase noise,

- 2. Reduce the in band phase noise floor,

- 3. Optimize the phase noise spectrum shape to get the minimal integration value.

The items 1 and 2 are the focus of this dissertation and will be discussed in detail in the following two chapters. The item 3 is belong to the system level and will be discussed in the experimental prototype design in Chapter 5.

# **Chapter 3: Design Techniques for Low Phase Noise VCOs**

VCO are key components in RF frequency synthesizers. It determines the out of band phase noise performance. The most popular integrated RF VCO architecture is a cross-coupled inductor-capacitor (LC) tank CMOS oscillator due to its relatively low phase noise, ease of implementation and differential operation. The implementation of the cross-coupled LC VCO has received lots of attention in recent years as evidenced by the large number of publications reporting improved phase noise performance [Cran97, Muer00] and higher operating frequency [Leva02, Tang02]. However lacking a clear understanding of the physical mechanism of phase noise generation in these VCOs is still a bottleneck for the circuit designer [Rael00]. This chapter will first briefly review the basics of oscillators in section 3.1. Then some popular CMOS cross-coupled LC VCO topologies are introduced in section 3.2. Section 3.3 presents two previous VCO phase noise models. Next a generalized linear phase noise model based on physical mechanism of phase noise is proposed and a closed form phase noise formula for LC cross-coupled VCO is derived in section 3.4. In section 3.5, a 2GHz VCO design example is described and the simulation and measurement results are compared to the theory prediction.

#### 3.1 Introduction to oscillators

#### 3.1.1 Feedback modeling and oscillation conditions

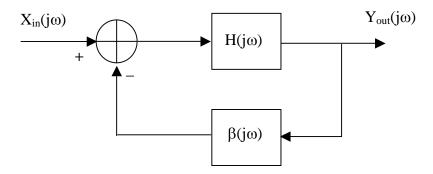

All oscillators can be analyzed by modeling them as feedback systems. Figure 3.1 shows a general block diagram of a linear feedback system with forward and feedback transfer functions represented by  $H(j\omega)$  and  $\beta(j\omega)$  respectively. The transfer function  $Y_{out}/X_{in}$  of the linear systems in Figure 3.1 is the general equation for a feedback system

$$\frac{Y_{out}(j\omega)}{X_{in}(j\omega)} = \frac{H(j\omega)}{1 + H(j\omega)\beta(j\omega)}$$

(3.1)

Figure 3.1 A linear feedback model for oscillators

The necessary conditions for steady state oscillation to occur are known as the Barkhausen criteria. These conditions require that the gain around the feedback loop equal to unity and the total phase shift around the loop equal to (2m+1) times 180 degrees where m is an integer value including zero. The gain and phase conditions are expressed as

$$|H(j\omega)\beta(j\omega)| = 1, \tag{3.2}$$

and

$$\angle H(j\omega)\beta(j\omega) = (2m+1) \cdot 180^{\circ}. \tag{3.3}$$

When these conditions are satisfied, a signal at the input of the gain stage will be amplified and returned back to the input in phase resulting in a self-sustaining signal. This feedback loop viewpoint has been especially useful in describing the operation of traditional oscillators (based on single active devices) such as the Colpitts, Hartley, and Pierce oscillators, *etc*.

## 3.1.2 Negative resistance modeling

**(b)**

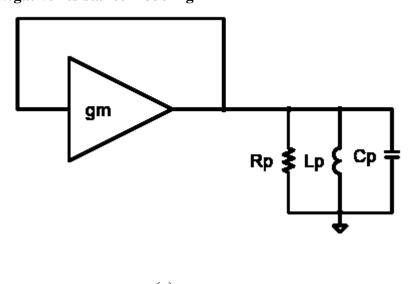

Figure 3.2 A negative resistance model for LC oscillators

An alternate way to describe the operation of oscillators involves the concept of negative resistance, Figure 3.2. Negative resistance modeling can be regarded as a special case of feedback modeling. Figure 3.2 shows a model of a simple negative resistance LC oscillator. In this figure the active device is a simple transconductance amplifier connected in positive feedback and is connected to a LC tank circuit. It is straightforward to show that the tank circuit sees a negative resistance of  $-R_a = -\frac{1}{g_m}$  looking back into the transconductor output. It can be shown that this negative resistance will exactly cancel the equivalent parallel resistance of the tank circuit if the Barkhausen criteria are satisfied. The steady state oscillation condition

$$-R_a + R_p = 0 ag{3.4}$$

This makes sense because the active device must add enough energy to the circuit to cancel the total losses of the tank circuit.

Negative resistance oscillators have the property that they continue to generate a negative resistance even when the tank circuit is removed. On the other hand, removing the tank circuit from a feedback oscillator breaks the feedback loop that creates the negative resistance and a negative resistance cannot be measured. Although both representations are equivalent, the negative resistance viewpoint will be utilized for the oscillator analyses of this dissertation.

### 3.1.3 Oscillator start-up conditions and amplitude stabilization

for the negative registance model is expressed as

The previous two subsections discussed linear oscillator models and steady state oscillation conditions. In real oscillators, the analysis of the nonlinear effects can not

be done using small signal model. We first look at the oscillator start-up conditions using negative resistance model. In order for the circuit of Figure 3.2 to oscillate, the magnitude of the negative resistance Ra must be smaller than the parallel resistance of the tank circuit Rp. In other words, the transconductance  $g_m$  must be larger than the tank loss 1/Rp. The ratio of transconductance  $g_m$  to the equivalent LC tank conductance 1/Rp is referred to as the startup safety factor

$$\alpha = \frac{g_m}{1/R_p} = g_m R_p. \tag{3.5}$$

Integrated oscillators are usually designed with a startup safety factor of at least 2. When this start-up condition is met, the oscillator output will be an exponentially growing sine wave according to the small signal linear model.

It should be noted that the excess negative resistance for start-up does not result in an exponentially growing oscillation amplitude since nonlinear effects ultimately limit the maximum voltage swing. To help understand the non-linear amplitude stabilization effect, we assume the transconductor  $g_m$  in Figure 3.2 has the following nonlinear relationship to voltage

$$I_{out} = g_m V - bV^3. (3.6)$$

This is referred as "Van Der Pol" oscillator [Pol20]. The simplified form of this non-linearity allows us to get a closed form solution for the steady state peak voltage

$$V_{peak} = \sqrt{\frac{4}{3} \frac{\alpha - 1}{bR_p}}, \qquad (3.7)$$

where  $\alpha = g_m R_p$  is the startup safety factor. The startup process works as following. When the signal level is small, the system has two right-hand plane poles and its time response is a growing sine wave. The increase of the signal level will reduce the effective negative transconductance due to the non-linear effect. Eventually the effective negative transconductance reduces to a value which exactly cancels 1/Rp and we get a steady state oscillation level in the time domain.

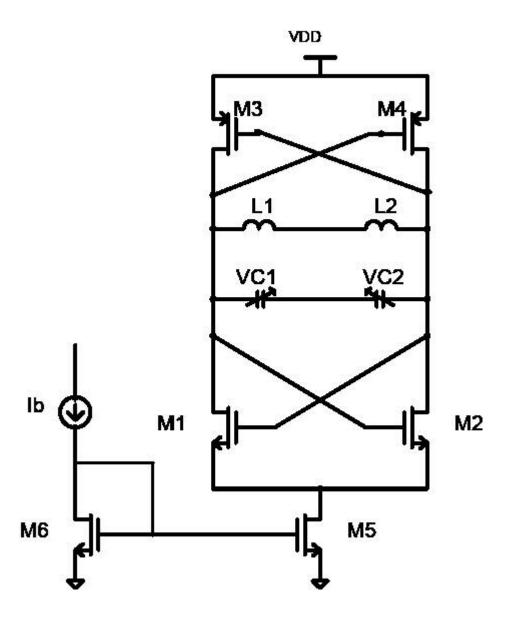

# 3.2 CMOS cross-coupled LC oscillator topologies

It is possible to implement an oscillator in CMOS technology using single active devices in traditional topologies such as the Hartley or Colpitts. However, most recent implementations of CMOS LC oscillators have utilized a differential topology. Differential topologies are advantageous in integrated circuits, since they are less susceptible to supply voltage noise that is often present in on-chip power rails. Furthermore, many integrated RF systems would benefit from the use of a differential local oscillator (LO) since typical integrated mixers are double-balanced Gilbert Cell topologies. In these cases, the use of a differential oscillator eliminates the need for single-ended to differential conversion circuitry.

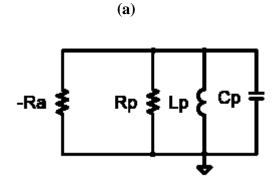

Figure 3.3 A simple NMOS cross-coupled LC oscillator

The most popular differential oscillator topologies are the cross-coupled LC oscillators, Figure 3.3, which utilize two cross-coupled transconductors (FETs) to produce a negative resistance similar to the transconductor of Figure 3.2.

The DC analysis of this circuit is simple since the inductors can be replaced by short circuits. The DC bias point is determined by  $V_{GS} = V_{DD}$  and  $V_{DS} = V_{DD}$ . Assuming the cross coupled NMOS devices to be long channel FETs (for conceptual purposes only, short channel devices are actually used in the actual high frequency oscillator design), and neglecting the body effect, the drain current can be written as:

$$I_{DS} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2,$$

(3.8)

where  $\mu_n$  is the surface mobility of the electrons in the NMOS channel,  $C_{ox}$  is the oxide capacitance per unit area, and  $V_{th}$  is the device threshold voltage. The transconductance of one FET at this balance state is

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}}\Big|_{V_{GS} = V_{DS} = V_{DD}} = \mu_n C_{ox} (V_{DD} - V_{th})$$

(3.9)

The input resistance seen looking into the cross-coupled NMOS transistors can therefore be shown to be  $-\frac{2}{g_m}$ . In order for the circuit of Figure 3.3 to oscillate, the magnitude of this negative resistance must be smaller than the equivalent parallel

resistance of the tank circuit.

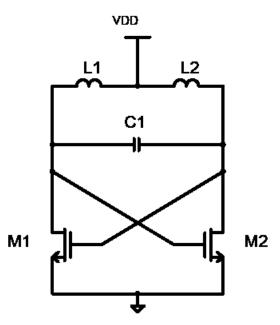

In the simple NMOS cross-coupled LC oscillator in Figure 3.3, the DC bias is set by the supply voltage and the size of the devices since V<sub>GS</sub> and V<sub>DS</sub> are both equal to V<sub>DD</sub>. This severely limits the flexibility of the circuit since the negative resistance is effectively controlled by the power supply voltage. Varying the negative resistance will also vary the oscillation amplitude. This is an important fact since the phase noise performance (discussed in the next section) depends directly on the oscillation amplitude. For these reasons, it is desirable to have a means of controlling the negative resistance. This can be achieved by limiting the supply current. Figures 3.4 shows the NMOS versions of this circuit with a FET current mirror that is used to control the bias current, and therefore the negative resistance of the circuit. The bias current that flows through the mirror device is referred to as the tail current. The value of this tail current also sets the total power dissipation of the oscillator. Having a means of controlling the bias current allows the designer to make the best compromise between phase noise and power dissipation. Figure 3.4 also features two varactors instead of fixed capacitors to achieve voltage controlled frequency tuning function.

Figure 3.4 NMOS cross-coupled pair LC VCO with tail current

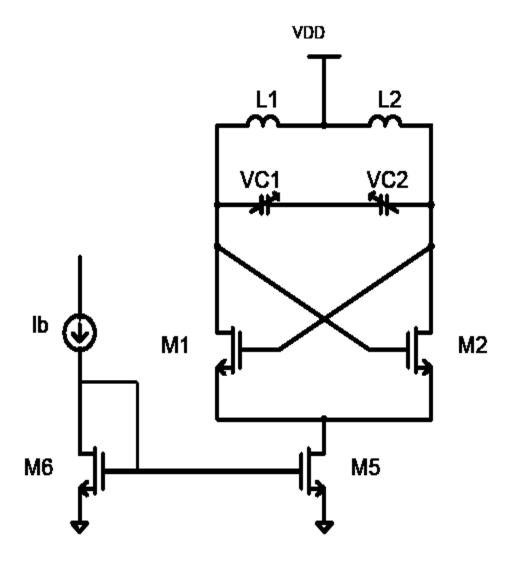

The N-PMOS complementary cross-coupled LC oscillator circuit is the result of using both PMOS and NMOS cross coupled pairs in parallel to generate the negative resistance. Figure 3.5 shows a simple complementary cross-coupled LC VCO. Since the same bias current flows through both the PMOS and NMOS devices, the negative resistance can be twice as large for the same power consumption. Viewing the negative resistance generated by the PMOS and NMOS devices in the same manner as discussed above, the total negative resistance of this circuit is the parallel

combination of the two individual cross-coupled FET circuits. The negative resistance is given by

$$R_{negative} = -\frac{2}{g_{mn} + g_{mp}}. \tag{3.10}$$

Figure 3.5 N-PMOS complementary cross-coupled pair LC VCO with tail current

This complementary pair topology has some advantages: (i) It gives doubled output amplitude if both topologies work in current-limited region at the same bias current; (ii) It can be optimized to have more symmetric output waveforms leading to smaller 1/f noise up-conversion [Haji99]. We will analyze and optimize the phase noise performance of this topology in the following sections.

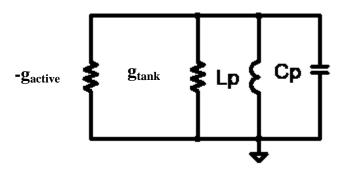

## 3.3 Related work on LC VCO phase noise model

Figure 3.6 Equivalent circuits of cross-coupled LC VCO

**Leeson's model:** The first and still widely used VCO phase noise model is Leeson's linear model [Lees66]. It will be beneficial to briefly derive the linear noise model for cross-coupled LC tank VCO. We redraw the negative model in Figure 3.6 using conductance representation. In Figure 3.6,  $g_{tank}$  models the loss of the LC tank due to inductor and varactor parasitics and  $g_{active}$  models the negative conductance provided by the cross-coupled N-PMOS pair. We now can get the impedance of the LC tank at some small frequency displacement  $\Delta \omega$  from center frequency  $\omega_0$  expressed as

$$Z(\omega_0 + \Delta \omega) = \frac{1}{g_{\tan k} + \frac{1}{j(\omega_0 + \Delta \omega)L} + j(\omega_0 + \Delta \omega)C}$$

$$\approx j \frac{\omega_0 L}{2\Delta \omega / \omega_0} = jR_p \frac{\omega_0}{2Q\Delta \omega},$$

(3.11)

where Q is the quality factor of the LC tank while  $R_p=1/g_{tank}$  is the total equivalent parallel resistance of the LC tank. The PSD (Power Spectrum Density) of current noise due to tank loss can be written as

$$i_n^2/\Delta f = 4kT/R_n, (3.12)$$

where T is the temperature while k is Boltzemann's constant. The phase noise due to tank thermal noise is

$$L(\Delta\omega) = \frac{1}{2} \left( \frac{\overline{v}^2_{noise}}{\overline{v}^2_{signal}} \right) = \frac{1}{2} \left( \frac{\left| Z(\omega_0 + \Delta\omega \right|^2 i_n^2 / \Delta f}{V_0^2 / 2} \right)$$

$$= \frac{kTR_p}{V_0^2} \left( \frac{\omega_0}{Q\Delta\omega} \right)^2.$$

(3.13)

$V_0$  is the differential output voltage peak amplitude and depends on bias current. For N-PMOS complementary cross-coupled LC oscillator,  $V_0=4/\pi I_{bias}R_p$  [Haji99]. The ½ before the parentheses in the derivation is based on the equal partition of the AM and PM noise. We are interested in phase noise (PM) only. To include the noise contribution of the active devices, Leeson introduced a heuristic parameter F. Total phase noise can be written as follows [Lees66],

$$L(\Delta\omega) = \frac{kTR_{eff}(1+F)}{V_0^2} \left(\frac{\omega_0}{\Delta\omega}\right)^2.$$

(3.14)

$R_{\it eff} = R_{\it p}/Q^2$  is the total equivalent series resistance of the LC tank.

**Hajimiri's model:** Leeson's model is based linear time invariant analysis. But the oscillator is an autonomous non-linear circuit and the non-linearity and time variant is essential for its operation. Hajimiri's model [Haji98] first introduces a special function: **Impulse Sensitive Function** (**ISF**) which describes how much phase shift results from applying a unit impulse at any point in time, such that phase shift response to a unit impulse is expressed as

$$h_{\Phi}(t,\tau) = \frac{\Gamma(\omega_0 t)}{q_{\text{max}}} u(t-\tau), \qquad (3.15)$$

where  $\Gamma(\omega_0 t)$  is the **ISF** function of the output waveform which represents the timevarying sensitivity of the oscillator's phase to perturbations and  $q_{max}$  is the maximum charge offset across the capacitor. The total excess phase due to a noise current can therefore be described by the expression:

$$\theta(t) = \int_{-\infty}^{+\infty} h_{\Phi}(t,t)i(t)dt = \int_{-\infty}^{t} \frac{\Gamma(\omega_0 t)}{q_{\text{max}}}i(t)dt.$$

(3.16)

Then using phase modulation approach to convert phase to voltage and get the side band phase noise as follows:

$$L\{\Delta\omega\} = 10 \cdot \log \left( \frac{\frac{\overline{i_n^2}}{\Delta f} \sum_{n=0}^{+\infty} c_n^2}{8q_{\text{max}}^2 \Delta\omega^2} \right), \tag{3.17}$$

where  $\overline{i_n^2}/\Delta f$  is the power spectral density of input noise current.  $c_n$  is the coefficient of Fourier transform of ISF function.  $\Delta \omega$  is the frequency offset from carrier frequency.

### 3.4 A generalized linear phase noise model

The understanding of the phase noise mechanism and an appropriate phase noise model is very important in the design and optimization of cross-coupled pair LC VCOs. Various attempts for phase noise analysis have resulted in several phase noise models as discussed in section 3.3. But lacking of physical insight and simple yet accurate analysis makes these models difficult to use in the design.

The Leeson's model is based on a linear model of LC resonator. It correctly models the phase noise due to LC tank. But the noise factor F is empirical and the model does not give ways to predict it from circuit parameter. Without the knowledge of this noise factor, we can not use Leeson's model to optimize VCO phase noise performance. The Hajimiri's model uses linear time variant analysis to include noise due to active devices and the effect of non-linearity. It is inherently more accurate. But we need to calculate the ISF function for every noise source. These ISF functions are too complicated to get from hand calculation. Moreover, to include the effect of periodic varying noise sources, the Noise Modulation Function (NMF) is introduced [Apar02]. The NMF functions are also hard to get analytically. So in practice these ISF and NMF functions can only be gotten by simulation. Hence the Hajimiri's model is mostly simulation based and suitable more for verification than for design.

The difficulty of VCO phase noise analysis comes mostly from: (i) all oscillators are inherently nonlinear and traditional linear analysis is invalid; (ii) time variant of phase noise sensitivity to noise source; (iii) cyclostationary noise sources due to devices switching on and off. The general non-linear time variant analysis is too involved to be used in the design hand calculation. So in this dissertation, we propose

a generalized linear phase noise model [Kong03, Kong04-1]. The model combined linear small signal analysis and non-linear large signal concept. It is possible to predict the phase noise performance using the proposed model from circuit parameters known to designer.

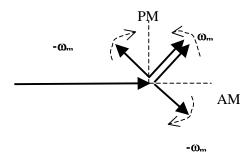

## 3.4.1 Phasor representation of AM and PM noise

Figure 3.7 Phasor Representation of AM and PM noise

We can represent a perfect oscillation signal as a vector  $\mathbf{V_0}$  rotating at frequency  $\omega_0$ . In time domain, it is written as  $V_0(t) = A_0 \cos \omega_0 t$ . The noise produces amplitude and phase fluctuations when superimposed on the perfect oscillator signal. As shown in Figure 3.7, at frequency offset  $\omega_{\rm m}$  and  $-\omega_{\rm m}$ , there are two noisy vector  $\mathbf{V_m}$  and  $\mathbf{V_{-m}}$  rotating relative to  $\mathbf{V_0}$ . It clearly shows that when the two vectors are in negative phase they produce AM (Amplitude Modulation) noise only while when the two vectors are anti-phase they produce PM (Phase Modulation) noise only. In time domain, the two cases are written as

### 1.AM noise

$$V_m(t) + V_{-m}(t) = A_m \cos((\omega_0 + \omega_m)t + \phi) + A_m \cos((\omega_0 - \omega_m)t - \phi)$$

$$= (2A_m \cos(\omega_m t + \phi))\cos(\omega_0 t).$$

(3.18)

#### 2. PM noise

$$\begin{aligned} V_m(t) + V_{-m}(t) &= A_m \cos((\omega_0 + \omega_m)t + \phi) + A_m \cos[(\omega_0 - \omega_m)t + \pi - \phi] \\ &= -(2A_m \sin(\omega_m t + \phi))\sin(\omega_0 t). \end{aligned} \tag{3.19}$$

As can be seen later, this representation is especially useful in the analysis of biasing current source noise contribution.

#### 3.4.2 Phase noise from LC tank

Phase noise from LC tank has been derived by Leeson's linear model as follows,

$$L(\Delta\omega) = \frac{kTR_{eff}}{V_0^2} \left(\frac{\omega_0}{\Delta\omega}\right)^2$$

(3.20)

$R_{\it eff} = R_{\it p}/Q^2$  is the total equivalent series resistance of the LC tank.

## 3.4.3 Phase noise from cross-coupled pair

Thermal noise of cross-coupled MOSFET's may significantly contribute to the output phase noise and must be modeled. In Leeson's model, it is represented as a fitting factor F. Our aim here is to derive its analytic expression represented by circuit parameters.

One popular method [Cran98, Ham01], though having no theory basis, is to evaluate the cross-coupled MOS current noise PSD at the completely balanced time (i.e., the zero-crossing of the differential tank voltage). We will first look at this method briefly. Suppose the transconductance of one side of MOS transistor is  $g_m$ . The differential total transconductance will be  $g_m/2$ . To ensure stable startup,  $g_m/2$  is often designed greater than  $1/R_p$ . Let  $i_{n1}$  and  $i_{n2}$  be the current noise of the left and right MOSFET in cross-coupled pair. Their PSD will be

$$i_{n1}^2/\Delta f = i_{n2}^2/\Delta f = 4kT\gamma g_m$$

.

$\gamma$  is a device noise parameter depending on technology. For long channel device,  $\gamma$ =2/3. For short channel device,  $\gamma$ =2~5. Assume the two current noise sources are uncorrelated, the total current noise PSD across the different LC tank is

$$i_n^2 / \Delta f = \frac{1}{4} \left( i_{n_1}^2 / \Delta f + i_{n_2}^2 / \Delta f \right) = \frac{1}{2} 4kT \gamma g_m = \frac{4kT \gamma \alpha}{R_n}.$$

(3.21)

Here we let  $g_m/2=\alpha(1/R_p)$ . Usually  $\alpha$  is chosen between 3~5.

Since these noise current sources have the same effect as the noise source of the LC tank, the same transfer function can be used to obtain the output noise due to the active devices as

$$L\{\Delta\omega\} = kT \frac{R_p \gamma \alpha}{V_0^2} \left(\frac{\omega_o}{Q\Delta\omega}\right)^2. \tag{3.22}$$

It means that in Leesons' model the F factor due to cross-coupled pair will be  $F=\gamma\alpha$ . It is concluded from this analysis that using larger devices for cross-coupled pair will result in larger excess noise factor and will increase phase noise at a given bias current.

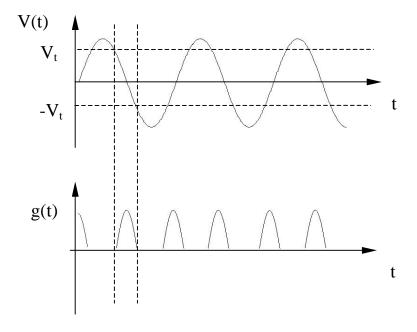

The drawback of this analysis is that it neglects the fact that the cross-coupled pair is always switching. The biasing point of the devices changes periodically with time. So the current noise PSD of cross-coupled pair has periodically time-varying statistics. It is not appropriate to model it as a stationary noise source. Fortunately, it can be shown that if the biasing point is changing with time, the resulting channel thermal noise is still white, with a time-varying PSD given by the same equation as for the time-invariant case if we replace the fixed transconductance with the time-varying one [Tria96]. In the following analysis, we will calculate the time average output noise and use it to evaluate phase noise.

We first note that the cross-coupled pair only contributes phase noise when they are both in saturation region. When one side is tuned off, the other side will be cascoded on the bias current source and the cross-coupled pair will contribute little to output noise [Terr99], as shown in Figure 3.8. During the time period of both sides are on, the total differential transconductance is

$$g(t) = \frac{g_{m1}(t)g_{m2}(t)}{g_{m1}(t) + g_{m2}(t)}$$

(3.23)

The corresponding current noise PSD is

$$i_n^2(t)/\Delta f = 4kT\gamma g(t) \tag{3.24}$$

Figure 3.8 Time-varying transconductance of cross-coupled pair

The time average current noise PSD is

$$i_n^2 / \Delta f = 4kT \gamma \overline{g} \tag{3.25}$$

The time average transconductance must be equal to one over the total parallel tank resistance, or in equation form

$$\overline{g} = 1/R_p \tag{3.26}$$

We obtain the output phase noise due to the active devices as

$$L\{\Delta\omega\} = kT \frac{R_p \gamma}{V_0^2} \left(\frac{\omega_o}{Q\Delta\omega}\right)^2$$

(3.27)

## 3.4.4 Phase noise from tail current source

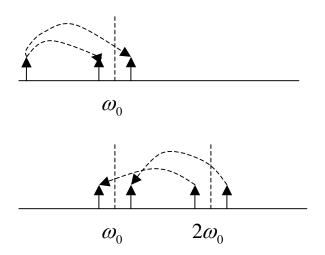

Figure 3.9 Tail noise up conversion and down conversion

For the bias current source, the cross-coupled pair acts as a single balanced mixer. So it will up-convert the low frequency noise and down-convert the noise at  $2f_0$  to the fundamental frequency  $f_0$ , Figure 3.9. The conversion gain is in the form

$$G(\Delta\omega) = \frac{2}{\pi} R_p \frac{\omega_0}{2Q\Delta\omega} \tag{3.28}$$

Here we need to make a difference between up-converted low frequency noise and down-converted 2f<sub>0</sub> noise.

For the low frequency noise, say at frequency  $\omega_m$ , the up-converted noise at  $\omega_0+\omega_m$  and  $\omega_0-\omega_m$  is from the same source and in negative phase. This is shown by

$$\cos(\omega_m t + \phi)\cos\omega_0 t = \frac{1}{2} \left[\cos((\omega_0 + \omega_m)t + \phi) + \cos((\omega_0 - \omega_m)t - \phi)\right]$$

(3.29)

So the up-converted noise will produce AM noise only. For the  $2f_0$  noise, say at frequency  $2\omega_0+\omega_m$  and  $2\omega_0-\omega_m$ , the down-converted noise at  $\omega_0+\omega_m$  and  $\omega_0-\omega_m$  is from different sources and in random phase. This is shown by

$$\cos((2\omega_0 + \omega_m)t + \phi)\cos\omega_0 t = \frac{1}{2}\left[\cos((\omega_0 + \omega_m)t + \phi) + \cos((3\omega_0 + \omega_m)t + \phi)\right]$$

(3.30)

$$\cos[(2\omega_0 - \omega_m)t + \gamma]\cos\omega_0 t = \frac{1}{2}\left[\cos((\omega_0 - \omega_m)t + \gamma) + \cos((3\omega_0 - \omega_m)t + \gamma)\right] \quad (3.31)$$

$\phi$  and  $\gamma$  are phases of different sources and not correlated. So the down-converted noise will produce one half AM noise and one half PM noise.

So phase noise due to bias current source will be

$$L\{\Delta\omega\} = 4kT\gamma_{bias}g_{bias}\frac{R_p^2}{\pi^2Q^2}\left(\frac{\omega_0}{\Delta\omega}\right)^2\frac{1}{V_0^2/2}$$

(3.32)

### 3.4.5 Total phase noise equation

Finally, combining each device noise with the tank output noise, the total excess output noise factor for the oscillator can be found.

$$F = \gamma + \frac{8}{\pi^2} \gamma_{bias} g_{bias} R_p \tag{3.33}$$

### 3.4.6 Comparison with other models

We have reviewed Leeson's model and Hajimiri's model for oscillator phase noise modeling. Several numerical simulators [Cade01, Agil04] are now also available to assist the circuit designer to predict phase noise of integrated VCO. So what is the point of another phase noise model? The reason is that the previous models are either measurement based or simulation based. They can not give physical insight and simple yet accurate formula for the phase noise. At present, the situation of the oscillator designer is similar to the designer of amplifiers who has only SPICE simulator, but who lacks physical insight and methods for simple yet accurate analysis with which to optimize a circuit.

Leeson's classic model is based on a linear model of an LC resonator in steadystate oscillation through application of negative conductance concept. However,

without knowing the excessive noise factor, which Leeson leaves as an unspecified

measurement based factor, the actual phase noise cannot be predicted. Hajimiri's

model uses linear time variant analysis to capture the effect of large signal periodic

switching of oscillators. It is inherently more accurate. But the ISF functions and

NMF functions are generally too complicated to get from hand calculation and can

only be obtained by computer simulation. The commercial simulators, such as

spectreRF from Cadence, use methods similar to Hajimiri's model and are usually

more involved [Caden00]. Table 3.1 compares our proposed model with the other

three phase noise models.

|            | Need         | Need        | Closed form | Simplicity   |

|------------|--------------|-------------|-------------|--------------|

|            | Measurement? | Simulation? | formula?    |              |

| Proposed   | No           | No          | Yes         | simple       |

| Leeson's   | Yes          | No          | No          | simple       |

| Hajimiri's | No           | Yes         | No          | complex      |

| SpectreRF  | No           | Yes         | No          | More complex |

Table 3.1 Comparison of phase noise models

# 3.5 A low phase noise 2 GHz LC VCO design and analysis

## 3.5.1 Tank passive components design

**Inductor design:** From the phase noise equations from section 3.4, we can see that the tank quality factor Q strongly affects the phase noise of the oscillator. The inductor in a LC oscillator is usually the most critical circuit element in the design. Typically, the Q of the inductor dominates the total Q of the tank circuit. In addition, the tuning range of a VCO is strongly affected by the self-resonant frequency ( $f_{sr}$ ) of an inductor. The self-resonant frequency is the frequency at which capacitive parasitics result in a zero net reactance; beyond this frequency the inductor becomes capacitive.

Traditionally, inductors have been incorporated as discrete components located off chip (often as small surface mounted parts). While off chip inductors can have extremely good performance, it is desirable to use on chip inductors and eliminate as many discrete components as possible. This reduces the board-level complexity and

component count, which in turn leads to a direct reduction in cost. As an alternative to off chip inductors, some RF integrated circuits have utilized bonding wires as inductors. While bonding wires can have a relatively high Q (on the order of 50), they can also suffer from large variations in inductance value since wire bonding is a mechanical process that cannot be as tightly controlled as photolithographic processes.

Monolithic inductors fabricated as simple planar spirals are now widely used on silicon based substrates. The inductance of a monolithic inductor is defined solely by its geometry. Modern photolithographic processes provide extremely tight geometric tolerances. For this reason monolithic inductors have very small variations in their performance. But their Qs are usually less than 10.

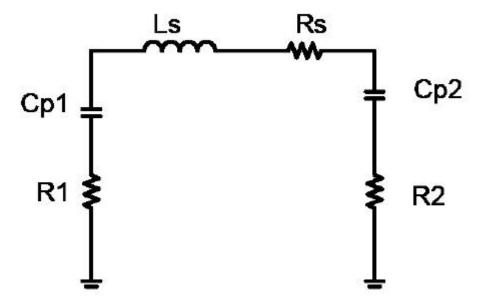

Figure 3.10 Equivalent lumped model for spiral inductor

In a standard CMOS process, metal layers can be used to construct on-chip spiral inductors. Several issues associated with the on-chip inductor need to be taken care of

to improve its performance. First, there is series resistance in the metal layers which reduces the quality factor of the inductor. Second, there is capacitive coupling from the metal to substrate which reduces the self-resonant frequency of the inductor. Third, there is resistance in the conducting substrate which also reduces the quality factor of the inductor. These non-idealities are modeled in the lumped pi model for the spiral inductor as shown in Figure 3.10. *Ls* models the series inductance and *Rs* models the series resistance of the metal. *Cp1* and *Cp2* model the capacitive coupling of the metal and the substrate. *R1* and *R2* model the resistive path in the substrate. The optimal layout of an inductor depends on the inductance value, the particular

process and the frequency of operation.

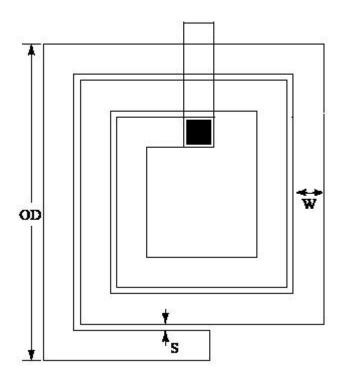

Figure 3.11 Geometry of square spiral inductor

The design of the planar inductor for high quality factor is not the focus of this dissertation. So the detailed inductor design process will not be described here. In this dissertation the inductors are designed primarily by iteration. 2GHz is the desired frequency of operation and we try to obtain oscillation near this frequency. Since a tank circuit with C = 1pF and L = 6nH resonated near 2GHz, this was the chosen as the starting point for the design. The final designed inductor geometry is a 2.5-turn square spiral shown in Figure 3.11. The final parameters are outside diameters (OD) 200um, tracewidths (W) 10um, and an interwinding spacing (S) 2um.

**Varactor design:** Although the quality factor of the tank circuit will be dominated by the inductor, the design of the varactor is also critical. If the varactor is not carefully designed its series resistance could signicantly lower the overall Q of the tank circuit, adversely impacting the phase noise of the oscillator.

Traditionally, discrete VCO implementations have used junction varactor diodes. These diodes are operated under reverse bias and are designed to enhance the variability of their depletion capacitance with reverse bias voltage. In a monolithic environment designers are much more restricted in the choice of tuning elements. The junction diodes that are available in a standard silicon CMOS process are not optimized for use as varactors; still, many monolithic LC oscillators have used such diodes as tuning elements. In a typical n-well CMOS process there are three types of junction diode structures available: n+/p-bulk, p+/n-well, and n-well/p-bulk. The only suitable choice for a junction varactor diode is the p+/n-well junction. Since the pbulk is typically connected to ground, the other structures would require a negative bias voltage in order to be reverse biased. The p+/n-well structure also has a lower series

resistance due to the higher n-well doping level compared to the p-bulk. A p+/n-well structure can typically have a quality factor of 20 or better. One disadvantage of junction varactors is that they can become forward biased by large amplitude voltage swings.

MOS capacitor, instead of a junction diode, can be used for the tuning element of the VCO. The MOS capacitor operates in a similar manner as a simple parallel plate capacitor in series with a depletion junction capacitance. In MOS capacitor the plates of the capacitor are formed by the polysilicon gate and the channel of a MOSFET. The capacitance of this MOS device varies nonlinearly as the DC gate bias of the MOSFET is varied through accumulation, depletion and inversion operation region.

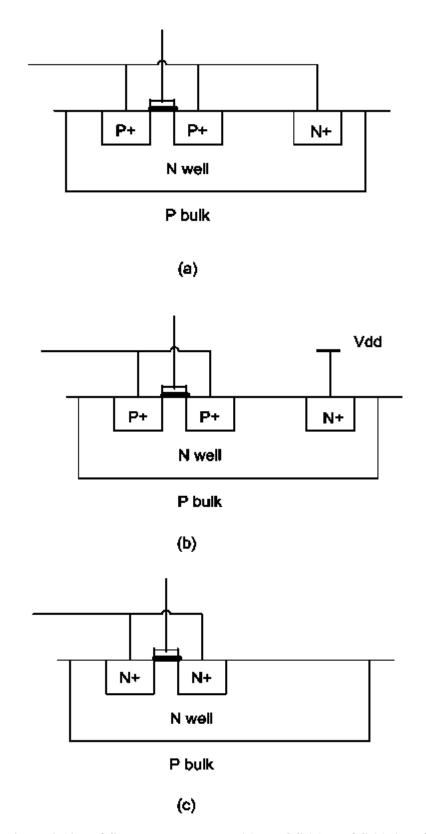

There are three types of MOS structures suitable to be used as varactors. Figure 3.12 shows the cross sections for each of these three structures. Each structure shown is situated in an n-well; however, these devices could also be implemented in the p-bulk as well. N-well is preferred because the bulk terminal of an n-well can be biased at a variable voltage (in an n-well process), whereas the p-bulk must be at ground potential.

The first structure consists of a PMOS transistor with the drain, source and bulk connected together (D=S=B) to form one node of the capacitor, and with the polysilicon gate as the other node, Figure 3.12 (a). This structure has a DC capacitance that varies nonmonotonically, since the device can operate in inversion, depletion, and accumulation region. The DC capacitance in both inversion and accumulation is approximated by Cox, which can be calculated from the device dimensions as a simple parallel plate capacitor. If fringing effects are neglected,

Figure 3.12 MOS varactor structure (a) PMOS (b)I-MOS (c) A-MOS

$$C_{ox} = \frac{\varepsilon_{ox}WL}{t_{ox}}, (3.34)$$

where tox is the gate oxide thickness. If a MOS varactor is to be used as the tuning element of a low frequency oscillator, then the non-monotonic characteristic can be problematic. At high frequency, the charge in the inversion layer does not change from the equilibrium state corresponding to the applied DC voltage. The high frequency capacitance therefore reflects only the charge variation in the depletion layer and the (rather small) movement of the inversion layer charge. The high frequency C-V characteristic of this structure becomes monotonic.

The second option is the inversion mode MOS capacitor, figure 3.12 (b). This structure is identical to a MOSFET. The drain and source are shorted together to form one capacitor terminal while the polysilicon gate forms the other. However, the bulk (n-well) of this structure is connected to the highest voltage available in the circuit, Vdd. Since the nwell connection of the device is always at a higher or equal potential with respect to the gate, the device can only operate in inversion. The C-V characteristic of this structure is monotonic and can be used as the tuning element in VCO. The capacitances of the D=S=B and Inversion mode capacitors can both be simulated by the BSIM3v3 models.

MOS capacitors can also be designed to operate in accumulation mode. Figure 3.12 (c) shows the structure of an accumulation mode MOS (A-MOS) capacitor. This structure departs somewhat from the standard PMOS transistor, since it replaces the p+ diffusions of the drain and source with n+ regions. This suppresses the injection of minority carriers (holes) into the channel and prevents it from inverting. The use of n+ regions also obviates the need for n+ ohmic contacts to bias the n-Well, so this

structure can be smaller than the other MOS capacitors. Since this device works in accumulation and depletion only, the capacitance characteristic of this structure is also monotonic. This structure typically has higher Q value compared with the previous two options due to the higher mobility of electron. The main drawback of this structure is its characteristics are not represented in the device models supplied by the vendor because this structure is no longer a MOS transistor. In order to simulate the behavior of this structure, a device simulator must be used, requiring detailed knowledge of process parameters such as doping concentrations.

The A-MOS varactor is selected in this design due to its higher quality factor. From the starting point of tank C = 1pF and L = 6nH resonating near 2GHz, the maximum capacitance value of the varactor is decided to be 1.8 pF considering the parasitic capacitors of inductor and cross-coupled MOS devices.

## 3.5.2 Circuit design

The np-Pair is chosen due to its lower power consumption and reduced 1/f noise up-conversion. The supply voltage we use is 2.7 V. To meet the power consumption constraint of specifications, we set  $I_{bias} = 2.5 \text{mA}$ .

Each inductor has an inductance value of 2.7nH with quality factor 7.4 at 2GHz. The tank Reff = 9.2 ohm. Tank equivalent parallel resistance  $R_p$ =  $R_{eff}$   $Q^2$ =503 ohm. Tank transconductance  $g_{tank}$  = 2mS. Let startup factor  $\alpha$  =3.5. We need the sum transconductance of one NMOS and one PMOS to be  $g_n+g_p=\alpha*2$   $g_{tank}=14$ mS. To reduce 1/f noise up-conversion, we choose  $g_n=g_p$ = 7mS. From these parameters and 0.25um CMOS technology parameters, we get NMOS size as W/L =40/0.25 and PMOS size as W/L=120/0.25.

From the phase noise model, we should have bias current source transconductance  $g_{bias}$  and  $\gamma_{bias}$  as small as possible. So we will choose large length and small width for the current source MOSFET. But transconductance  $g_{bias}$  must be large enough to ensure that the device works in saturation region. The final size we choose is W/L = 200/4.

#### 3.5.3 Analysis and simulatiom

From the phase noise model, differential output amplitude

$$V_0 = 4/\pi I_{bias} R_p = 1.6V \tag{3.34}$$

When oscillation frequency is 2GHz, the predicted phase noise at 1MHz is

$$L(1MHz) = \frac{KTR_{eff} (1 + \gamma + \frac{8}{\pi^2} \gamma_{bias} g_{bias} R_p)}{V_0^2} \left(\frac{2 \times 10^9}{10^6}\right)^2 = -127 dBc / Hz$$

(3.35)

In the calculation, we choose  $\gamma_{\text{bias}} = 2/3$  and  $\gamma = 2.5$ .

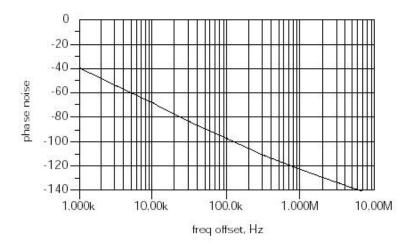

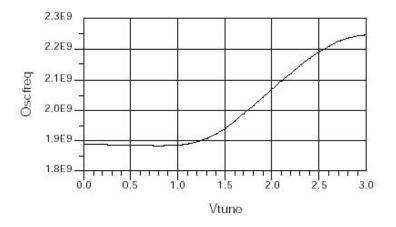

We simulated the phase noise and frequency tuning characteristics of the final circuit design using Agilent ADS. The simulation results are shown in Figure 3.13 and Figure 3.14. Figure 3.13 shows the phase noise v.s. frequency offset when the oscillation frequency is at 2GHz. The simulated phase noise at 1MHz offset is -126 dBc/Hz. It is in good agreement with our analysis result. Figure 3.13 (b) shows the simulated frequency tuning curve of the 2G VCO. When tuning voltage changes from 1~2.7 V, the oscillation frequency changes from 1.9~2.2GHz.

Figure 3.13 Simulated VCO phase noise v.s. frequency offset

Figure 3.14 Simulated VCO frequency tuning curve

## 3.5.4 Measurement results

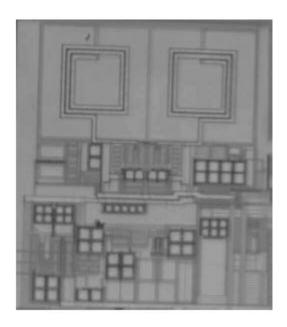

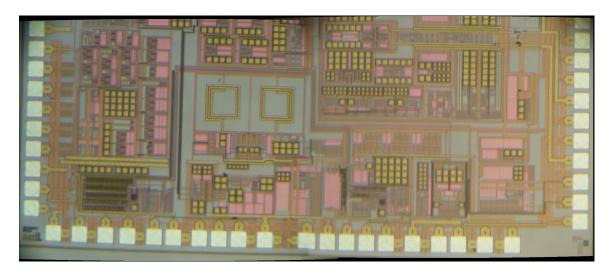

The 2GHz VCO is fabricated in TSMC CMOS 0.25um process. The die photograph is shown in Figure 3.15.

Figure 3.15 Die photograph of 2GHz VCO

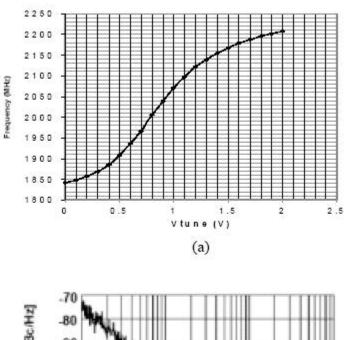

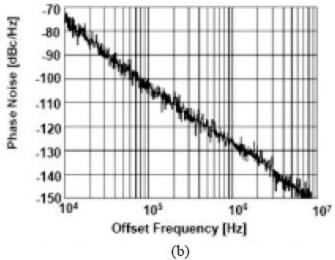

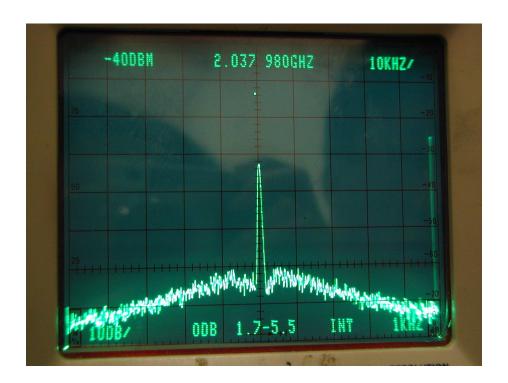

The measurement results are shown in Figure 3.16. Figure 3.16 (a) shows the measured frequency tuning curve of the 2GHz VCO. When tuning voltage changes from 0.5~2.2 V, the oscillation frequency changes from 1.9~2.2GHz. It covers the 14 channels of 802.11b/g applications. The tuning range is about 15%. Figure 3.16 (b) shows the phase noise v.s. frequency offset when the oscillation frequency is at 2 GHz. The measured phase noise at 1MHz offset is -125 dBc/Hz. It is in good agreement with our analysis and simulation result.

Figure 3.16 Measured 2GHz VCO performance (a) VCO frequency tuning curve (b) VCO phase noise v.s. offset frequency

# Chapter 4: Low phase noise PFD/CP/Divider design

As discussed in section 2.6, PFD/CP/Divider determines the in-band phase noise floor of the closed loop PLL. As the wireless design evolves into higher operating frequency and higher data rate, PFD/CP/Divider becomes more important. High data rate is usually achieved by broad band operation and high order modulation scheme, such as QAM64. As shown in section 2.2, the phase impairment effect will dominate in this case. The measurement of phase impairment is RMS phase error which depends both on in-band and out of band phase noise. On the other hand, integrated VCO performance becomes worse at higher operating frequency. Thus, we have to use relatively noisy VCO to meet the strict RMS phase error specifications. So it is desirable to use a wide bandwidth PLL to suppress the VCO phase noise. More PFD/CP/Divider phase noise will contribute to the closed loop phase noise in a wide bandwidth PLL. Thus, optimization of PFD/CP/Divider phase noise becomes a very important issue.

#### 4.1 Introduction to PFD/CP/Divider in PLL

# **4.1.1 PFD (Phase-Frequency Detector) and CP (Charge Pump)**

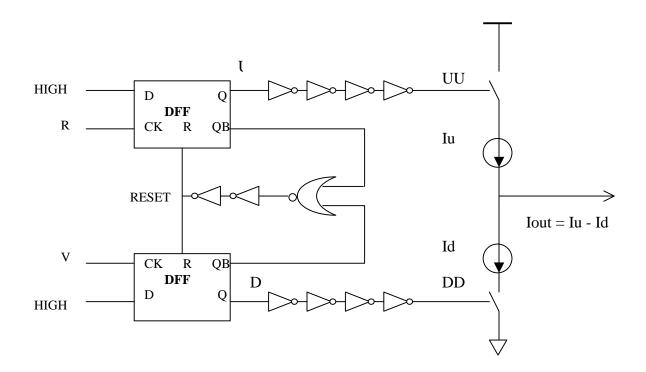

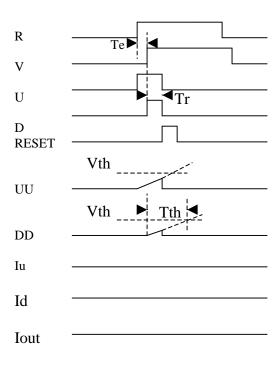

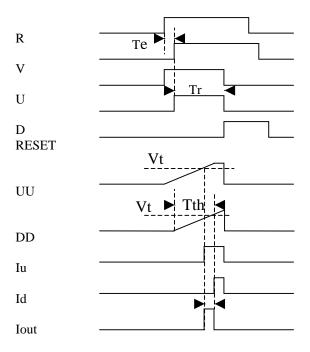

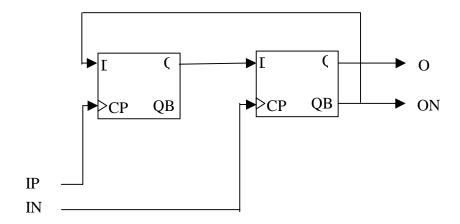

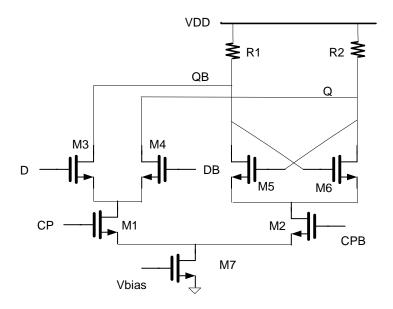

In a PLL, the control voltage of the VCO comes from the filtered output of PFD (Phase-Frequency Detector) and CP (Charge Pump), which contains the information of how much the divided VCO signal leads or lags reference signal in terms of phase. Figure 4.1 shows a block diagram of a typical PFD/CP implementation.

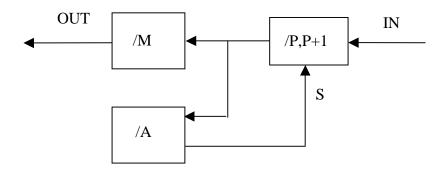

Figure 4.1 Block diagram of PFD/CP

The top DFF (D-type Flip-Flop) generates a high signal when a rising edge from reference signal (R) is received. This high signal will turn on the top switch and allow the current to charge the loop filter. The top switch will keep on until a rising edge from divided VCO (V) is received, which generates a high signal in the bottom DFF and resets both DFFs through the NOR gate in the reset path. When the rising edge of V is leading R, the operation is similar except that the down switch will turn on and the current will discharge the loop filter. The pulse width of the current waveform indicates the phase/frequency difference of R and V signal.