#### **ABSTRACT**

Title of dissertation: QUALIFICATION OF METALLIZED OPTICAL FIBER

CONNECTIONS FOR CHIP-LEVEL MEMS

**PACKAGING**

Michael Andrew Deeds, Doctor of Philosophy, 2004

Dissertation directed by: Associate Professor Peter Sandborn

Department of Mechanical Engineering

A MEMS-based Safety and Arming (S&A) device is being developed for the next generation of Navy torpedoes. The MEMS-based S&A consists of a high aspect ratio MEMS chip fabricated by deep reactive ion etching (DRIE) of silicon on insulator substrates (SOI). The micro-machined structures, which include environmental sensors, actuators, and optical components, are susceptible to stiction related failures. A robust package is essential to transform the fragile MEMS S&A device into a rugged package capable of reliably functioning throughout the military stockpile to target sequence. To adequately protect the MEMS device from deleterious effects of the external environment, the package must be housed in a hermetic, organic-free package.

This dissertation presents the design of, analyzes, and qualifies a die-level fluxless packaging concept. The die-level package consists of a metallized seal ring patterned around the perimeter of the chip, including the fiber groove, sidewalls, and base. The fiber grooves provide a fiber optic interconnect between the microstructure area and the

macro-environment. A cap chip, with a matching seal ring, completes the clamshell package. Solder is deposited onto the seal ring and in the grooves at the wafer-level on the device and cap chips. A fluxless, and hence organic-free, soldering process joins and seals the fiber-chip assembly on the chip-level.

The conditions that govern fluxless soldering are addressed and tailored for success in the developed design. Surface energy models are used to understand the fluxless soldering conditions and to study the geometric stability of fluid solder joints at the fiber to chip interface. Several techniques for fabrication of the chips and assembly of the packages are investigated.

The effects of leak rate of the package seal on the internal package environment are discussed in detail to establish an acceptable leak rate of small volume MEMS packages.

The calculations are then furthered to determine the acceptable leak path dimensions to ensure moisture does reach unacceptable levels during the package life.

The presented work represents the first reported organic-free (fluxless) die-level package seal with optical fibers that cross the seal boundary.

# Qualification of Metallized Optical Fiber Connections for Chip-Level MEMS Packaging

By

Michael Andrew Deeds

Dissertation submitted to the faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctorate of Philosophy

2004

#### **Advisory Committee:**

Associate Professor Peter Sandborn, Chair Professor Don Barker Professor Chris Davis Associate Professor Don DeVoe Associate Professor Pat McCluskey

# **Dedication**

For my daughter Alison Hope Deeds who became my true inspiration through her bravery and strength.

### Acknowledgements

This is the fun part. There are so many people to thank for their support throughout my personal life, work, and school. I'd like to start with my advisor, Dr. Peter Sandborn. Your patience and timely persistence was key to the realization of this quest.

I greatly appreciate the hard work and tutelage from my associates and friends at JHU/APL, especially Allen Keeney and John Lehtonen. Thanks, Allen, for your eager support and "can do" attitude.

I have received tremendous guidance and support during my career at NSWC.

From the early days when Vic Carlson taught me to always put a date on everything.

Ralph Balestrieri, Tim Hennessey, Carolyn Vaughan, and John Hendershot who initiated me into the world of mechanical design. Lawrence Fan for granting me numerous opportunities of responsibility in the exciting field of MEMS and his patience and encouragement in my pursuit of a doctorate degree. I want to thank all the guys on the MEMS design team, Dan, Gabe, Kevin, Tom, David, Eric, John, and Kris. The unselfish, team-oriented environment that we thrive in is a direct result of their collective good attitude. I want to extend my appreciation to Bob Kavetsky for facilitating the transfer of my academic research from fluids to MEMS packaging. I want to thank virtually everyone in the Weapons Department and beyond (including the then Technical Director of Indian Head, Mary Lacy) for their kindness, understanding, and support when my daughter was diagnosed with cancer.

Which brings me to my family. My heart goes out to Alison, who has taught me more in her 5 years than I was able to learn in the thirty years leading up to her birth. My son, Drew, who at the age of 1 is already preparing himself to help his old man fix up his fleet of cars. I must graciously thank my wife, Chrissy, for her patience through several of my all night modeling and writing binges. The mornings after those nightsmust have been entertaining as I took things out to the trash that never belonged there and then asked what she did with them. I want to extend my most humble gratitude to my parents, who have always believed in me and are the primary reason I pursued a doctorate degree in the first place. Ma, thanks for impressing upon me the value of a good education and for just being you, an accomplished woman and even better mother. Dad, they don't make them any better than you. Thanks for being a great parent, role model, and friend. Which brings me to my brothers and sisters (this could take some time, for I have 6 of them). Suzi, I thank you for rushing to my aide in my weakest moment. Somehow, I knew you would. You not only helped Ali through her treatment, but also helped me to help her. Angela, you to helped me to stand tall when I could barely stand at all. Don, so many years of good memories and another awesome role model. Jack, you have always been there for me with well thought out and helpful guidance. Lou, I still miss our football games at Granddad's house. Nancy, thanks for being my pal for all these years. Pat and Packy, thanks for a great friendship that has only grown stronger after 33 years. And perhaps most importantly, I want to thank the doctors, nurses, and technicians at Children's National Medical Center and National Institute of Health. There is no greater responsibility than saving a child's life. Dr. Seibel, I thank you for saving my little girl.

# **Table of Contents**

| <b>CHAPTER</b> | 1: INTRODUCTION                                              | 1   |

|----------------|--------------------------------------------------------------|-----|

| 1.1 N          | MEMS packaging                                               | 2   |

|                | MOEMS Packaging                                              |     |

| 1.3            | The United States Navy's MEMS safety and arming (S&A) device | 5   |

| 1.4 N          | Motivation for improved MEMS packaging                       | 8   |

| 1.4.1          | Increase packaged MEMS die yield                             | 9   |

| 1.4.2          | Design flexibility                                           | 11  |

| 1.4.3          | Increase package life cycle                                  | 12  |

| 1.4.4          | Cost                                                         | 13  |

| 1.5 F          | Package requirements                                         | 14  |

| 1.6            | Other relevant efforts and background literature             | 15  |

| 1.6.1          | Fiber optic packaging                                        |     |

| 1.6.2          | Metallized fiber                                             |     |

| 1.6.3          | MEMS packaging                                               |     |

| 1.6.4          | MOEMS packaging                                              |     |

| 1.6.5          | Fluxless soldering                                           |     |

| 1.6.6          | Solder energy modeling                                       |     |

|                | Scope and objective of present effort                        |     |

|                | 2: INTERCONNECT DESIGN AND FABRICATION                       |     |

|                | Device and cap chip design                                   |     |

|                | Fiber                                                        |     |

|                | Optical fiber interface                                      |     |

|                | Solder system design                                         |     |

| 2.4.1          | Solder selection                                             |     |

| 2.4.2          | Solder deposition                                            |     |

| 2.4.3          | Undermetallization                                           |     |

|                | Test structure fabrication runs                              |     |

|                | Device and cap chip process flow                             |     |

|                | Fluxless soldering                                           |     |

|                | Cleaning                                                     |     |

|                | Heat application and assembly                                |     |

|                | eak rate of gases                                            |     |

|                | Military standard for hermetic seal evaluation               |     |

| 2.10.2         | 1                                                            |     |

| 2.10.3         | 1                                                            |     |

|                | Summary                                                      |     |

|                | 3: EXPERIMENTAL RESULTS & MODELING                           |     |

|                | Manually applied solder to wetable and non-wetable surfaces  |     |

|                | Open faced solder test coupons                               |     |

| 3.2.1          | Initial feasibility and joint gold content                   |     |

| 3.2.2          | Multiple overplate test structure reflow results             | 124 |

| 3.2.3     | Gold evaporated on indium                                           | 134 |

|-----------|---------------------------------------------------------------------|-----|

| 3.2.4     | Localized heating reflow results                                    | 136 |

| 3.3 Mo    | deling                                                              | 138 |

| 3.3.1     | Young's wetting model                                               |     |

| 3.3.2     | Surface Evolver modeling                                            | 143 |

| 3.3.2.    | 1 Open face solder joint; solder free to pull in                    | 144 |

| 3.3.2.    | 2 Open face solder joint; solder forced to wet pad                  | 150 |

| 3.3.2.    | 3 Open face solder joint; variable wetting angles; single volume    | 157 |

| 3.3.2.    | 4 Open face solder joint; variable wetting angles; discrete volumes | 161 |

| 3.3.2.    | 5 Fiber in a rectangular groove                                     | 165 |

| CHAPTER 4 | : TEST AND EVALUATION                                               | 171 |

| 4.1 Ins   | pection                                                             | 171 |

| 4.2 Fib   | er pull tests                                                       | 174 |

| 4.3 Die   | shear                                                               | 177 |

| 4.4 Hig   | ghly accelerated life testing (HALT)                                | 178 |

| CHAPTER 5 | : SUMMARY                                                           | 183 |

| 5.1 Sui   | nmary and Conclusions                                               | 183 |

| 5.2 Co    | ntributions                                                         | 185 |

| 5.3 Rec   | commendations                                                       | 186 |

| APPENDIX  | A: MEMS-BASED SAFETY AND ARMING SYSTEM                              | 188 |

| APPENDIX  | B: SURFACEEVOLVER MODEL FILES                                       | 190 |

| REFERENC  | ES                                                                  | 208 |

# **List of Tables**

| Table 1-1: Temperature and humidity conditions necessary to form condensation         |

|---------------------------------------------------------------------------------------|

| before freezing                                                                       |

| Table 1-2: Environmental study results of indium die attach material                  |

| Table 2-1: Thermodynamic properties of selected compounds (298K, 1 atm, 1 mole) 73    |

| Table 2-2: Disassociation temperature and pressure of indium oxide                    |

| Table 2-3: Ratio of hydrogen to water vapor for thermodynamically favorable           |

| reduction of indium oxide and tin oxide80                                             |

| Table 2-4: Material property data for indium and indium oxide                         |

| Table 2-5: Pilling-Bedworth ratio for indium and selected common metal oxides 83      |

| Table 2-6: MIL-STD-883 fine leak test rejection criteria for selected package         |

| volumes (Test method 1014.1 test condition A <sub>1</sub> )91                         |

| Table 2-7: Theoretical minimum leak rate of selected gases                            |

| Table 3-1: Indium wire reflow results on bare silicon in a reducing environment 112   |

| Table 3-2: Gold-tin wire reflow results on bare silicon in a reducing environment 113 |

| Table 4-1: Die shear results                                                          |

| Table 4-2: Coefficient of thermal expansion of materials in HALT test                 |

| Table 4-3: HALT test parameters                                                       |

# **List of Figures**

| Figure 1-1: AXSUN Technologies Acutune Detector Module                       | 5  |

|------------------------------------------------------------------------------|----|

| Figure 1-2: Baseline MEMS S&A packaging sequence (F/O denotes optical fiber) | 7  |

| Figure 1-3: MEMS S&A chip in Kovar® package                                  | 8  |

| Figure 2-1: DRIE optical channels                                            | 34 |

| Figure 2-2: DRIE cap chip                                                    | 36 |

| Figure 2-3: KOH etched cap chip                                              | 37 |

| Figure 2-4: DRIE optical interconnect geometry                               | 38 |

| Figure 2-5: Gold dissolution in indium.                                      | 43 |

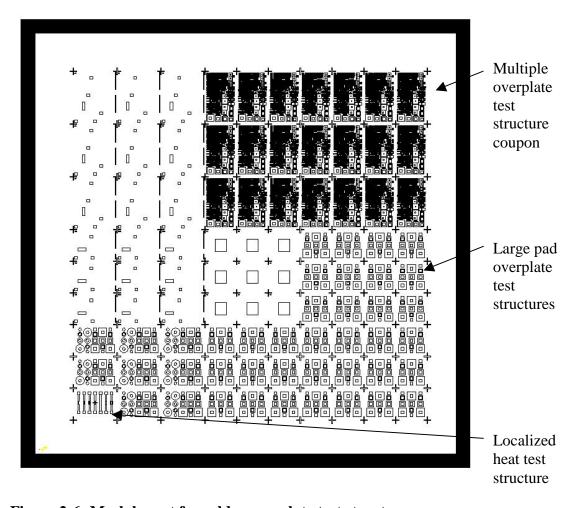

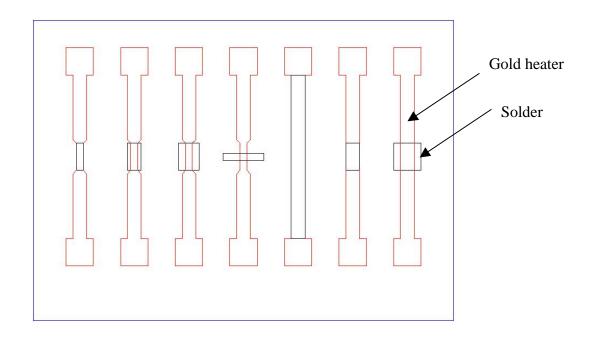

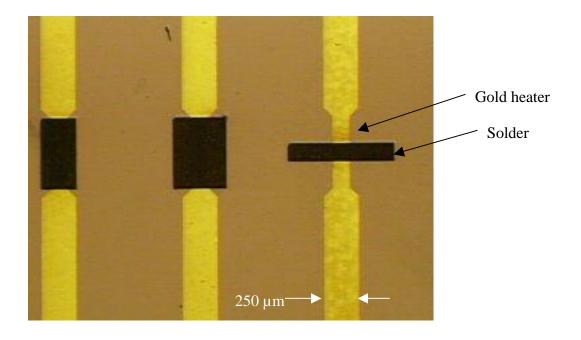

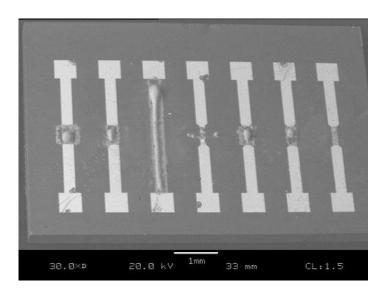

| Figure 2-6: Mask layout for solder overplate test structures                 | 44 |

| Figure 2-7: Multiple overplate test structure coupons                        | 45 |

| Figure 2-8: Fabricated structures on a multiple overplate chip               | 46 |

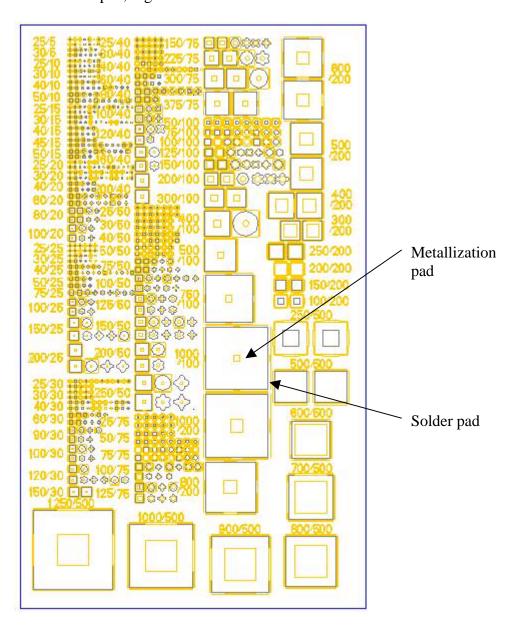

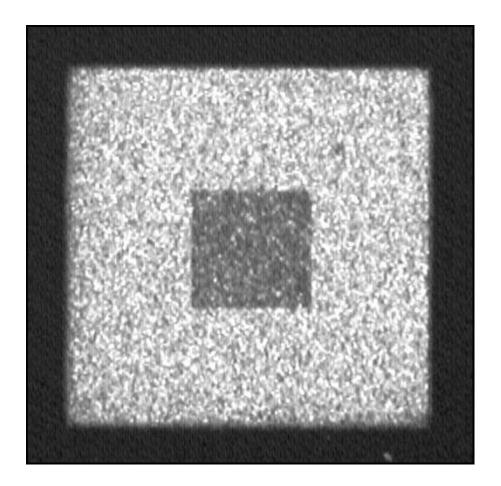

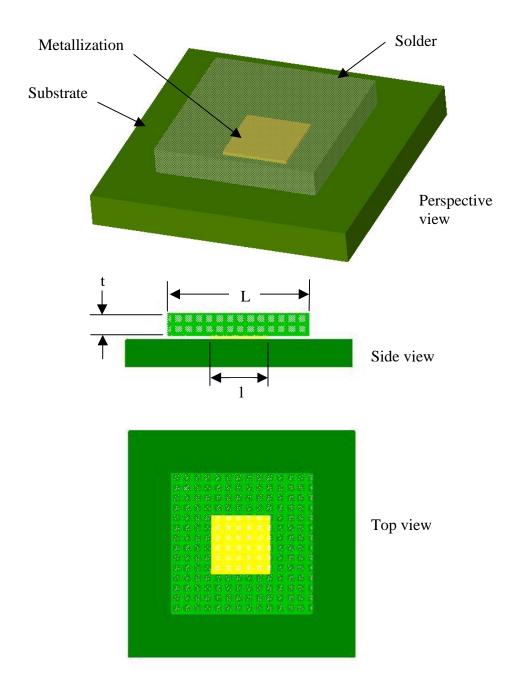

| Figure 2-9: Overplate test structures                                        | 47 |

| Figure 2-10: Localized heat test structure chip layout                       | 51 |

| Figure 2-11: Structures on a localized heat test structure chip              | 52 |

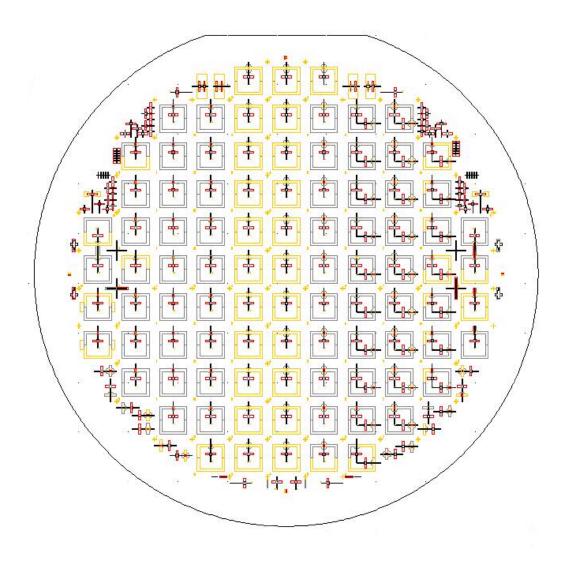

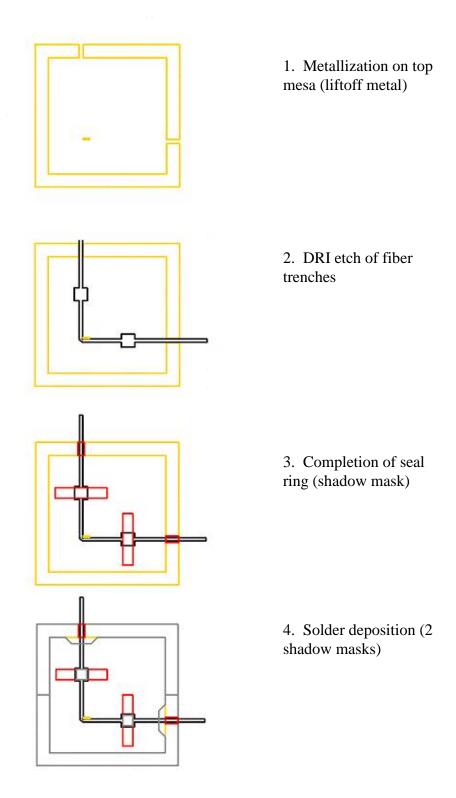

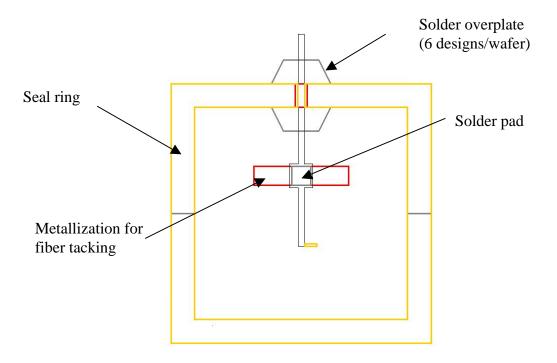

| Figure 2-12: DRIE chip-level package layout                                  | 56 |

| Figure 2-13: Process flow to make seal ring                                  | 58 |

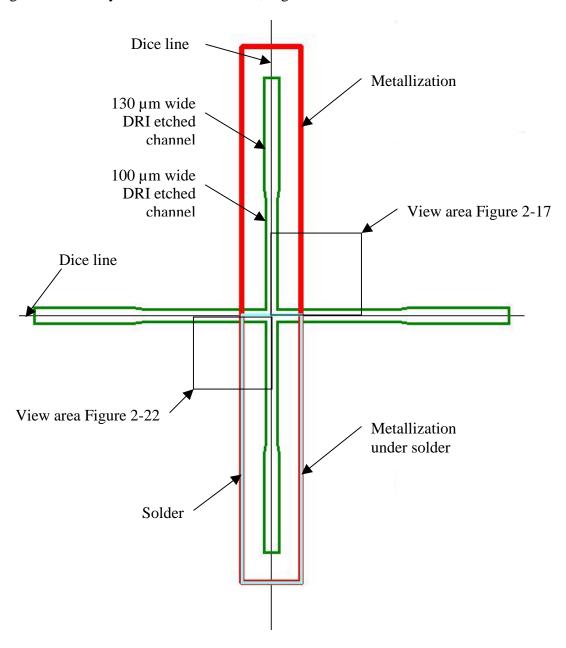

| Figure 2-14: DRIE chip-level seal test structure, 1 fiber                    | 59 |

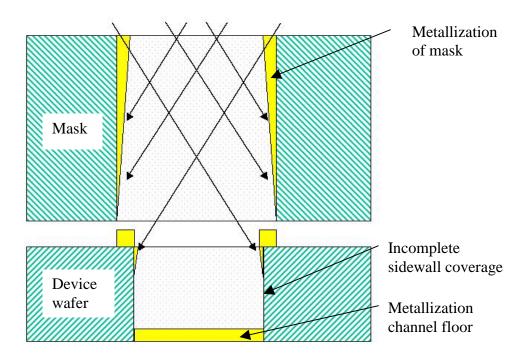

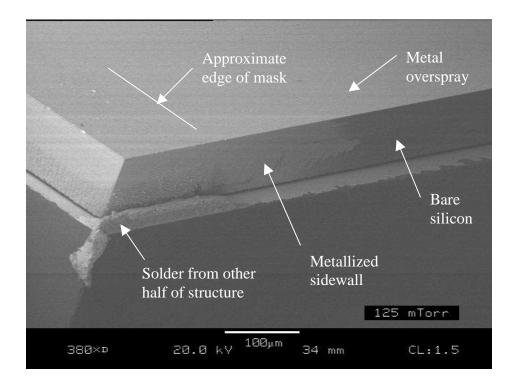

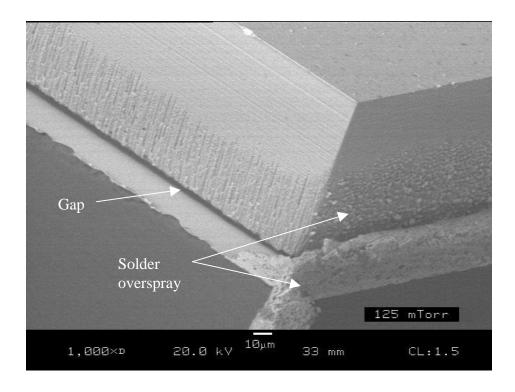

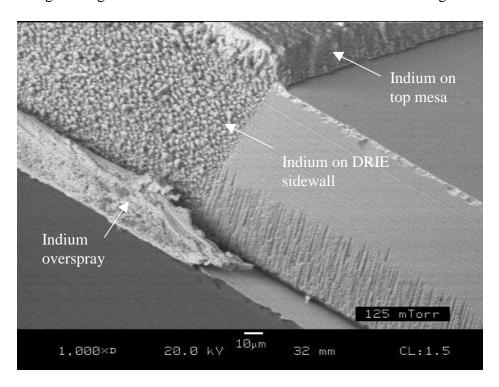

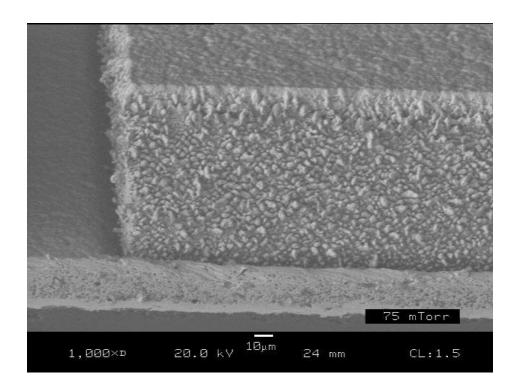

| Figure 2-15: Effect of thick mask on sidewall coverage                       | 60 |

| Figure 2-16: DRIE metallization and solder deposition metrology structure    | 62 |

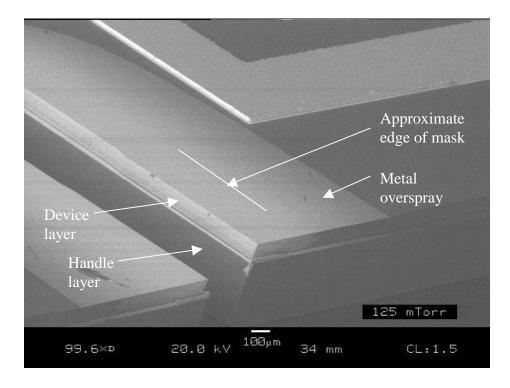

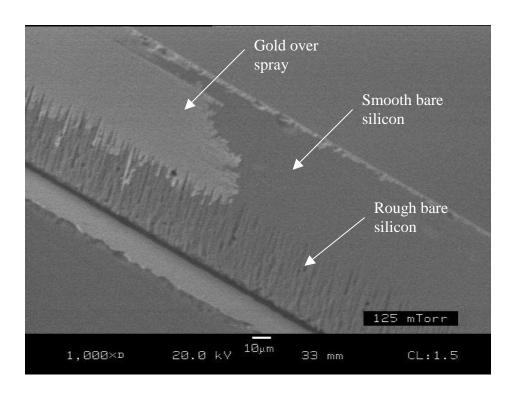

| Figure 2-17: Metal coverage of metrology structure (50x)                     | 63 |

| Figure 2-18: Metal coverage of metrology structure (190x)                    | 64 |

| Figure 2-19: Metal coverage of metrology structure (500x)                              | 5  |

|----------------------------------------------------------------------------------------|----|

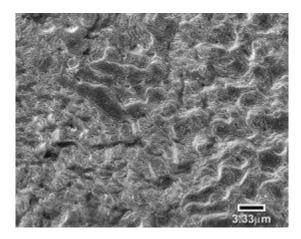

| Figure 2-20: Surface roughness of DRIE silicon wall                                    | 6  |

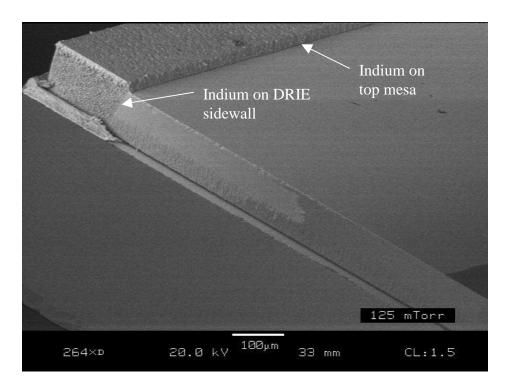

| Figure 2-21: Solder coverage of metrology structure (132x)                             | 7  |

| Figure 2-22: Solder coverage of metrology structure (500x)                             | 8  |

| Figure 2-23: Solder coverage of buried oxide gap (500x)                                | 9  |

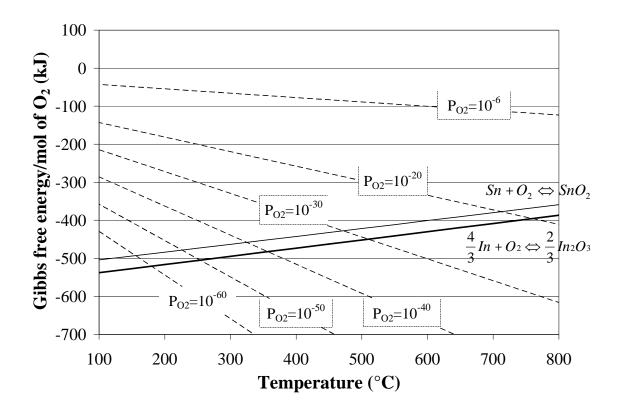

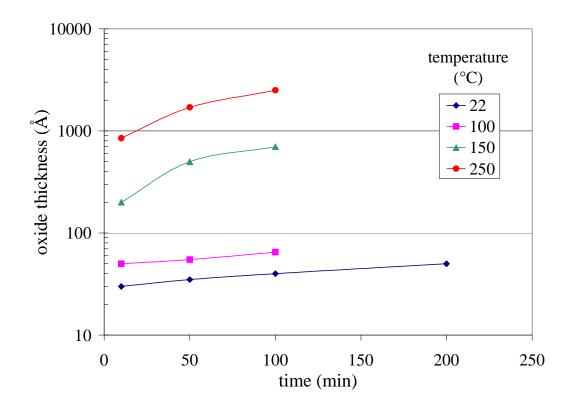

| Figure 2-24: Ellingham diagram for indium and tin oxide reduction                      | 6  |

| Figure 2-25: Indium oxide layer thickness growth on InSn film as a function of         |    |

| exposure temperature and time to ambient oxygen, adapted from Kuhmann [67]8            | 2  |

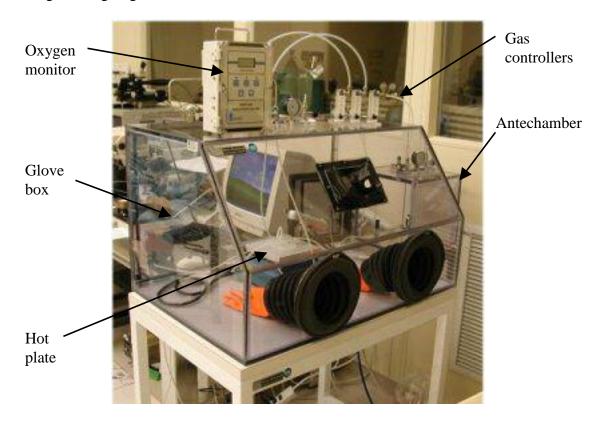

| Figure 2-26: Glove box set-up for reflow                                               | 6  |

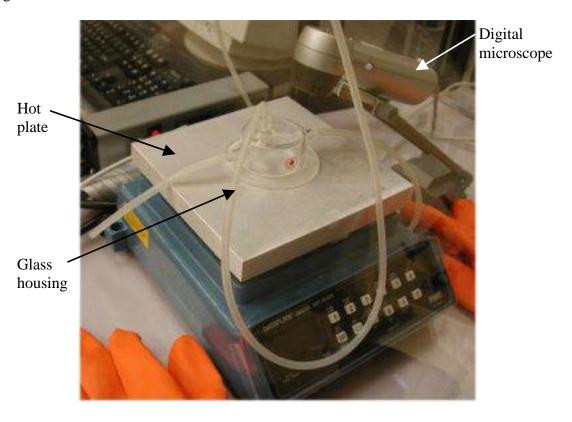

| Figure 2-27: Programmable hot plate with reflow housing                                | 7  |

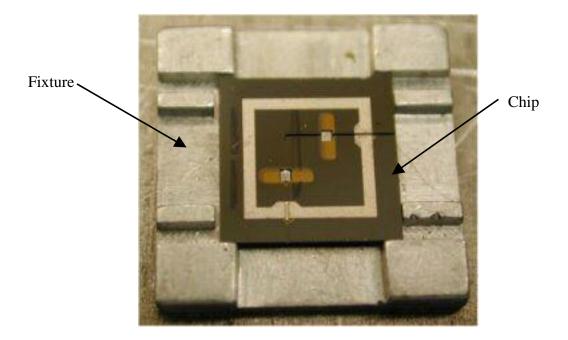

| Figure 2-28: Chip alignment fixture                                                    | 9  |

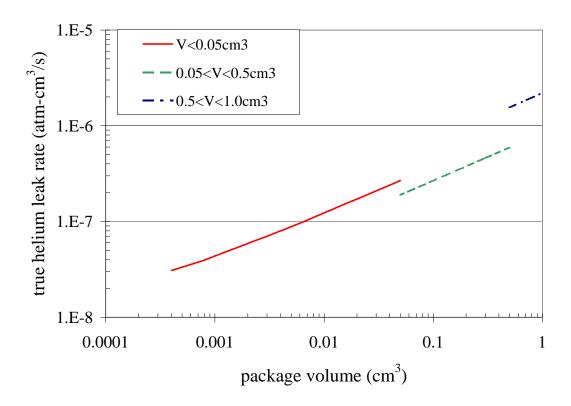

| Figure 2-29: MIL-STD-883 rejection limit of true leak rate of helium as a function     |    |

| of volume (test condition A <sub>1</sub> )9                                            | 14 |

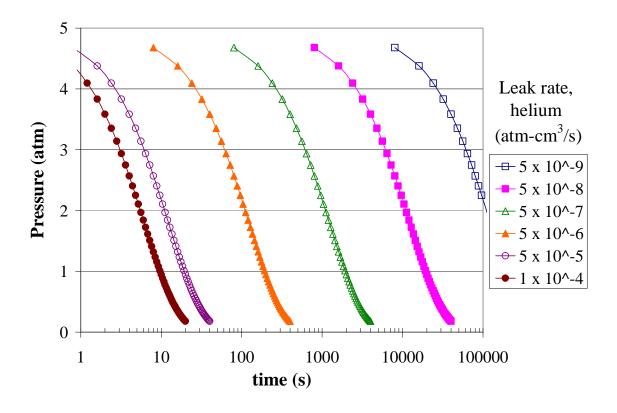

| Figure 2-30: Helium leak rate from a 0.0006 cm <sup>3</sup> package initially at 5 atm | 5  |

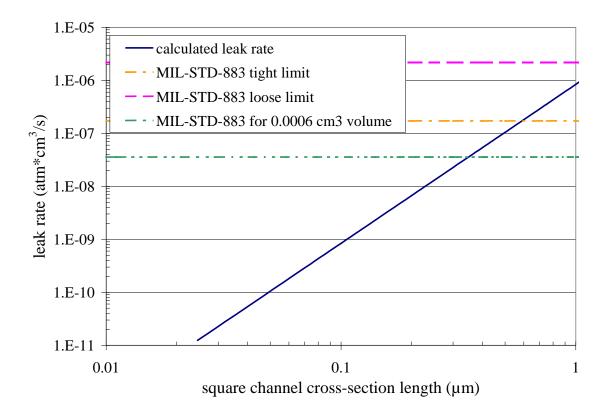

| Figure 2-31: Theoretical true leak rate of helium as a function of leak path cross-    |    |

| section (500µm seal)9                                                                  | 19 |

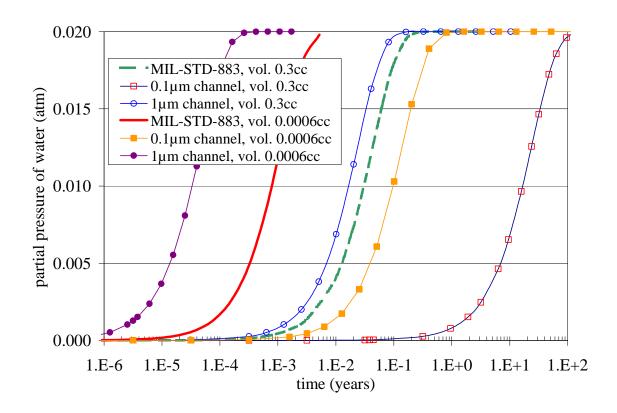

| Figure 2-32: Migration of moisture into a sealed package                               | 1  |

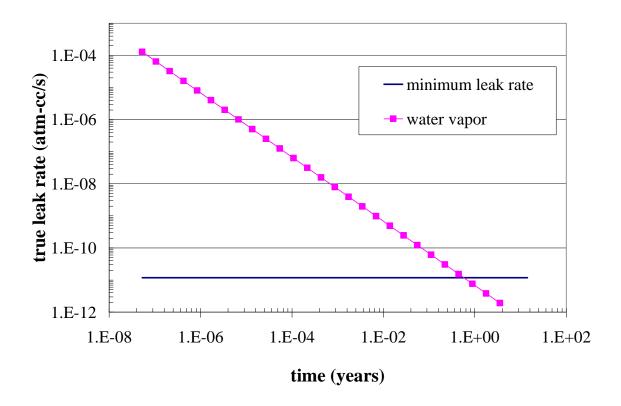

| Figure 2-33: Time for package to reach unacceptable moisture level                     | 4  |

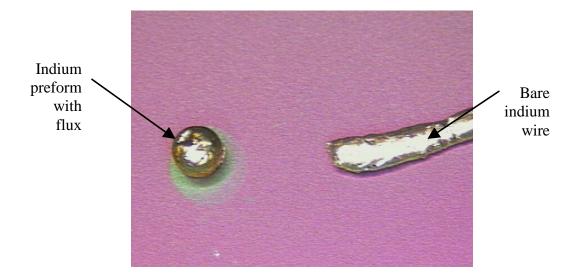

| Figure 3-1: Reflow results of flux indium and indium wire on silicon                   | 7  |

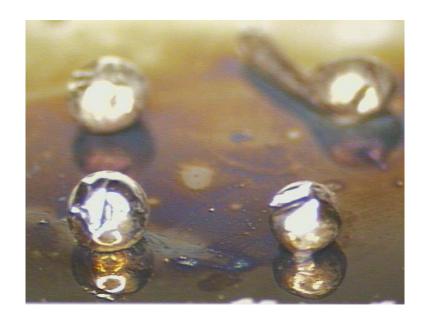

| Figure 3-2: Bare indium wire samples after reflow                                      | 2  |

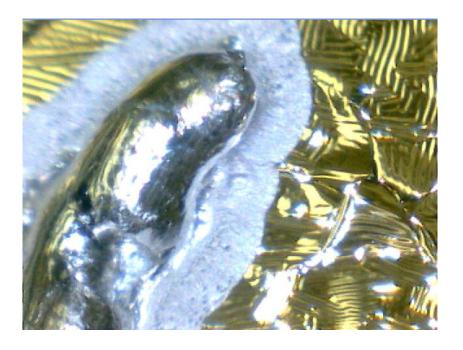

| Figure 3-3: Indium flowing out of oxide bag                                            | 4  |

| Figure 3-4: Oxide bag after complete reflow                                            | 5  |

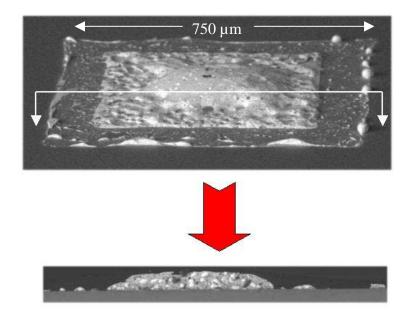

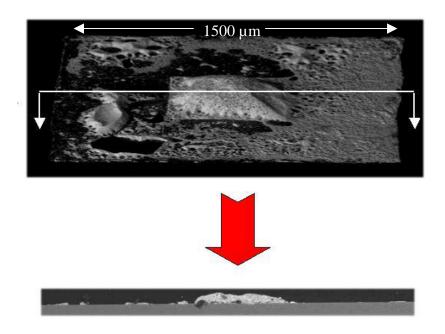

| Figure 3-5: Small overplate test structure                                         | 118 |

|------------------------------------------------------------------------------------|-----|

| Figure 3-6: Large overplate test structure                                         | 119 |

| Figure 3-7: Cr/Au/In after 275°C reflow: 1000 Å gold                               | 120 |

| Figure 3-8: Cr/Au/In after 275°C reflow: 5000 Å gold                               | 120 |

| Figure 3-9: 26% Au by weight.                                                      | 122 |

| Figure 3-10: 10% Au by weight.                                                     | 122 |

| Figure 3-11: 2.8% Au by weight                                                     | 123 |

| Figure 3-12: Au-In Phase Diagram                                                   | 124 |

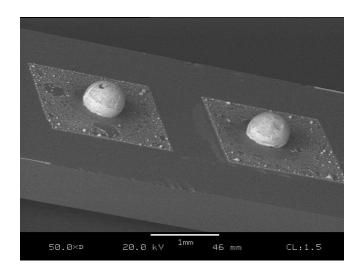

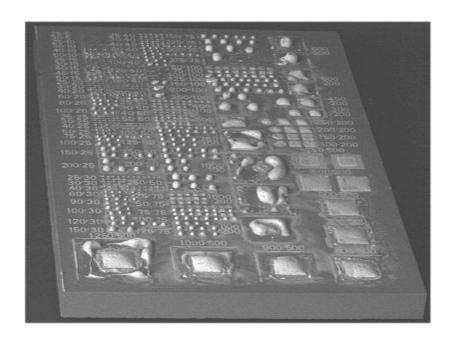

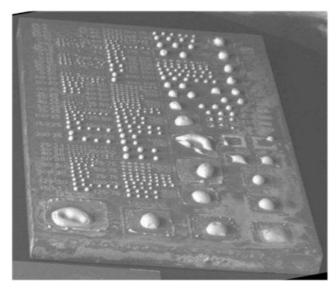

| Figure 3-13: TiW/Au/In multiple overplate test structure after reflow              | 125 |

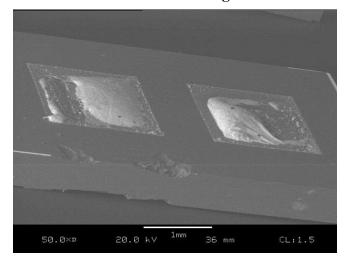

| Figure 3-14: Cr/Au/In multiple overplate test structure after reflow               | 126 |

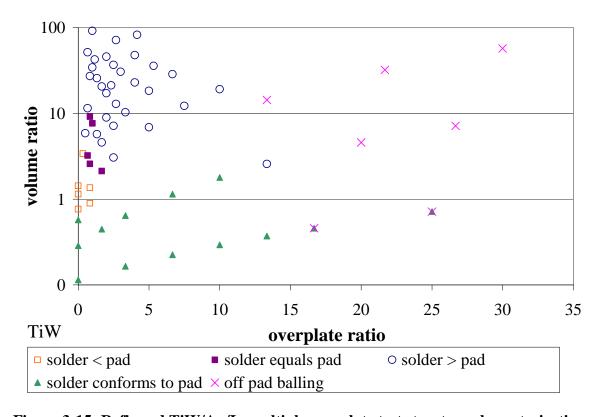

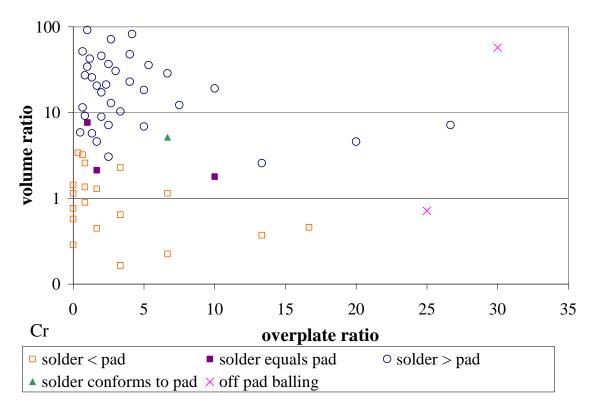

| Figure 3-15: Reflowed TiW/Au/In multiple overplate test structure characterization | 126 |

| Figure 3-16: Reflowed Cr/Au/In multiple overplate test structure characterization  | 127 |

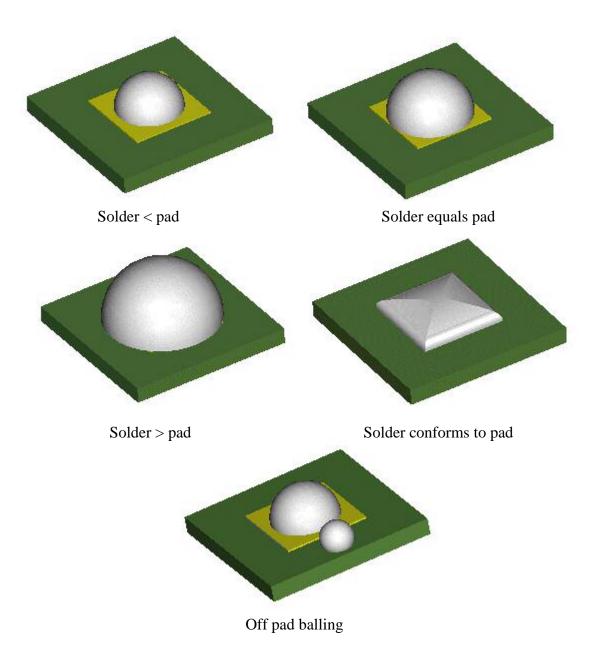

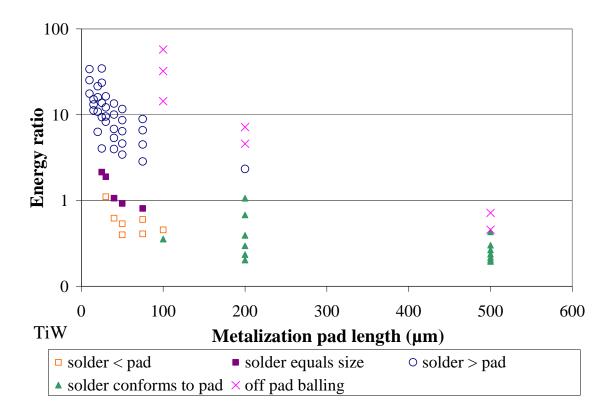

| Figure 3-17: Categories post reflow shapes of open faced solder joints             | 128 |

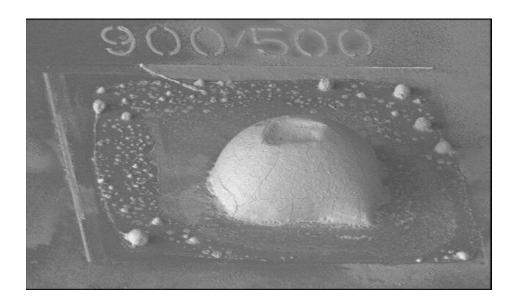

| Figure 3-18: 900 x 900 x 15 μm indium on 500 x 500 μm Cr/Au pad after reflow       | 129 |

| Figure 3-19: 900 x 900 x 15 μm indium on 500 x 500 μm TiW pad after reflow         | 130 |

| Figure 3-20: Mound spanning metallization pad and beyond                           | 131 |

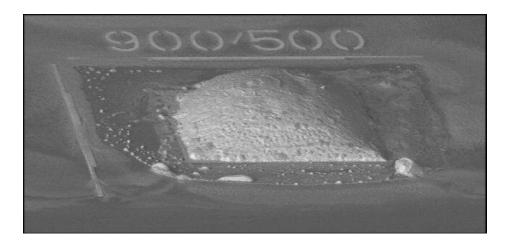

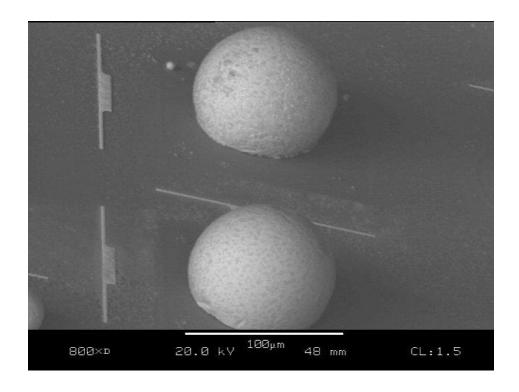

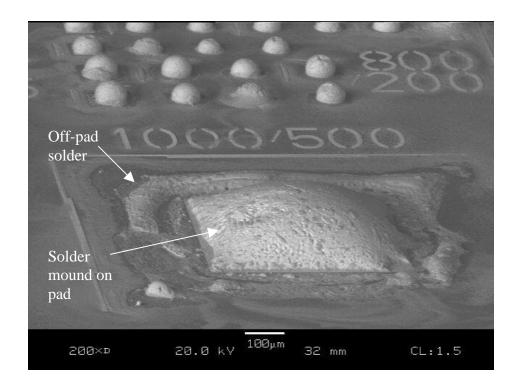

| Figure 3-21: Off-pad balling of solder                                             | 132 |

| Figure 3-22: Pad size effects on solder wetting                                    | 133 |

| Figure 3-23: TiW/Au/In/Au test structure on pad, crucible deposited indium         | 135 |

| Figure 3-24: Cr/Au/In surface on pad, boat deposited indium                        | 135 |

| Figure 3-25: TiWIn surface on pad (DRIE wafer), boat deposited indium              | 136 |

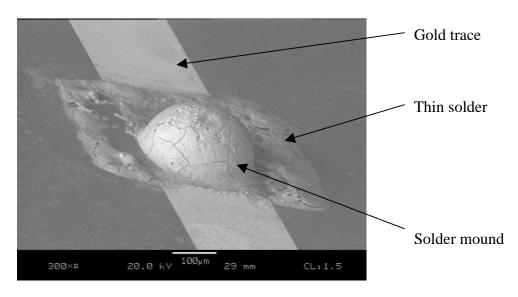

| Figure 3-26: Localized reflow test chip: after reflow                              | 137 |

| Figure 3-27: Close-up of localized reflow solder mound                              | 7 |

|-------------------------------------------------------------------------------------|---|

| Figure 3-28: Surface tension forces and wetting angle of a solid-liquid-vapor       |   |

| interface139                                                                        | 9 |

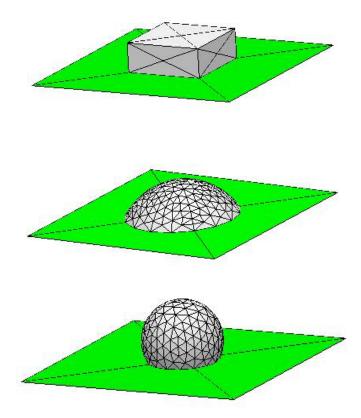

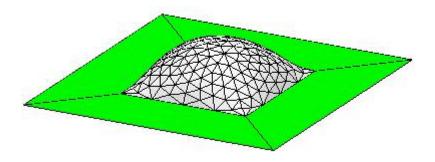

| Figure 3-29: Surface Evolver model results with solder free to wet entire surface:  |   |

| before reflow (top), 60° wet angle (middle), and 120° wet angle (bottom)14-         | 4 |

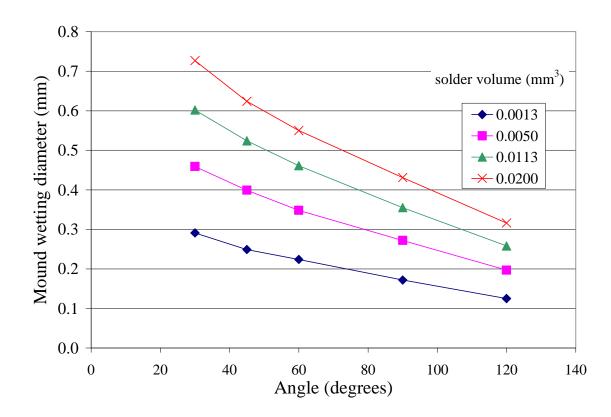

| Figure 3-30: Effect of wetting angle and volume on wetting diameter (from open face |   |

| model with free boundary conditions)                                                | 5 |

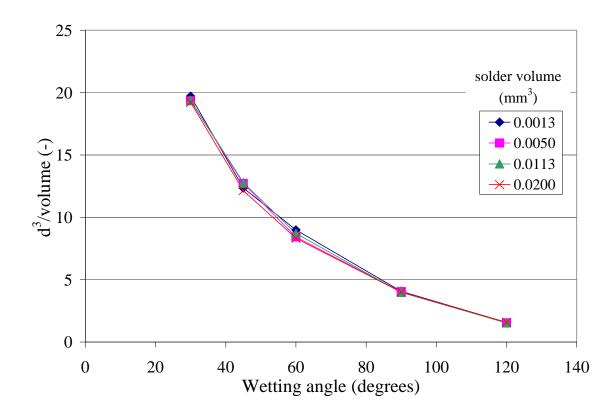

| Figure 3-31: Normalization of solder mound diameter by solder volume (from open     |   |

| face model with free boundary conditions)14                                         | 6 |

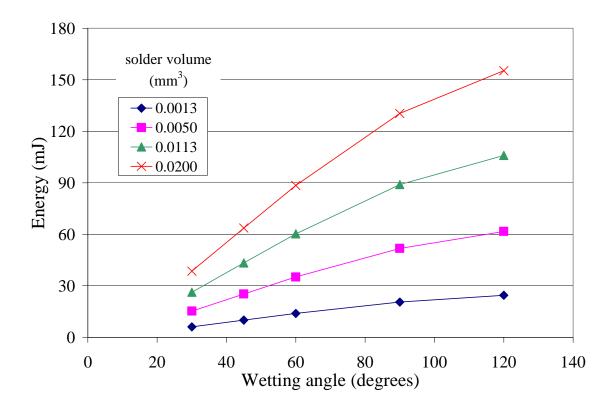

| Figure 3-32: Effect of wetting angle and solder volume on fluid solder energy (from |   |

| open face model with free boundary conditions)14                                    | 7 |

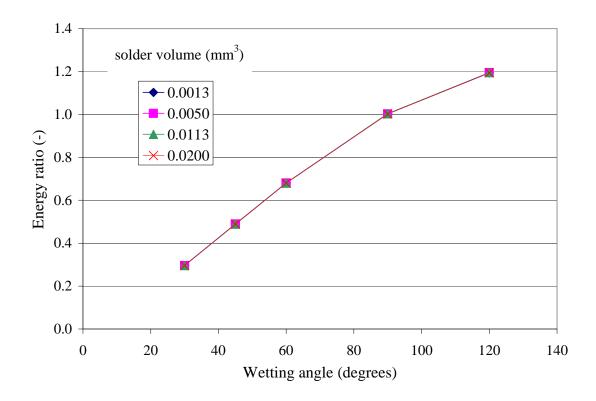

| Figure 3-33: Energy normalized by the energy of an equivalent volume wetted         |   |

| hemispherical mound (from open face model with free boundary conditions) 149        | 9 |

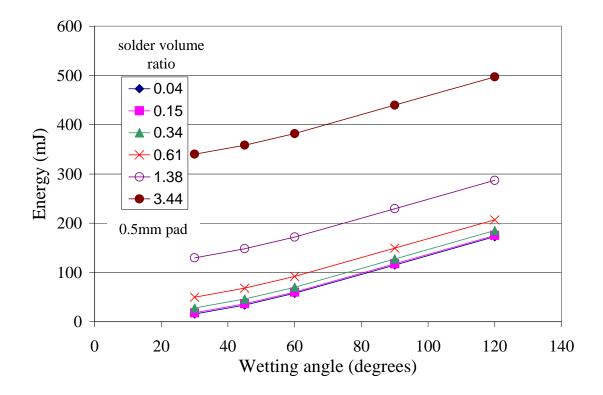

| Figure 3-34: Effect of wetting angle and solder volume on fluid solder energy (from |   |

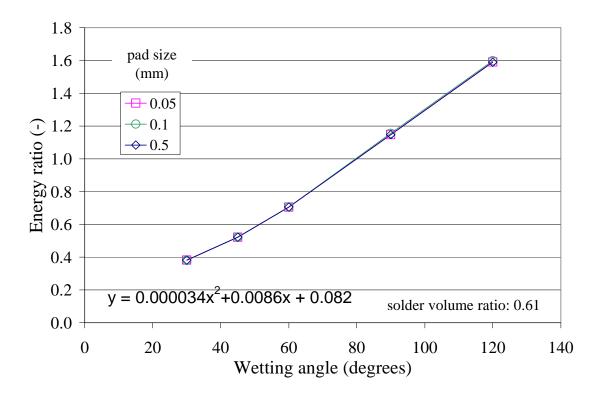

| open face model with solder forced to wet metallization pad)150                     | 0 |

| Figure 3-35: Energy ratio of solder on a 0.5mm pad (from open face model with       |   |

| fixed boundary conditions)                                                          | 1 |

| Figure 3-36: Open face model shape prediction for solder constrained to             |   |

| metallization pad; volume ratio 0.04                                                | 2 |

| Figure 3-37: Open face model shape prediction for solder constrained to             |   |

| metallization pad; volume ratio 0.6153                                              | 3 |

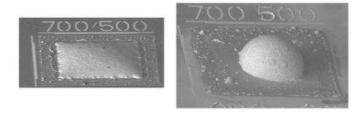

| Figure 3-38: Identical design reflow samples with different wetting results           |

|---------------------------------------------------------------------------------------|

| (700x700x15μm In pad on 500μm square Cr/Au pad)                                       |

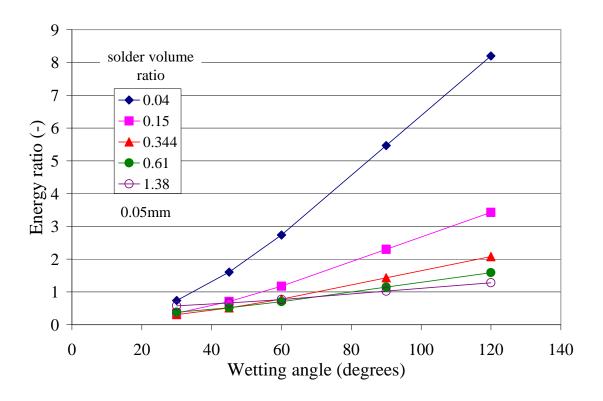

| Figure 3-39: Energy ratio of solder as a function of pad size (from Surface Evolver   |

| model with fixed boundary conditions)                                                 |

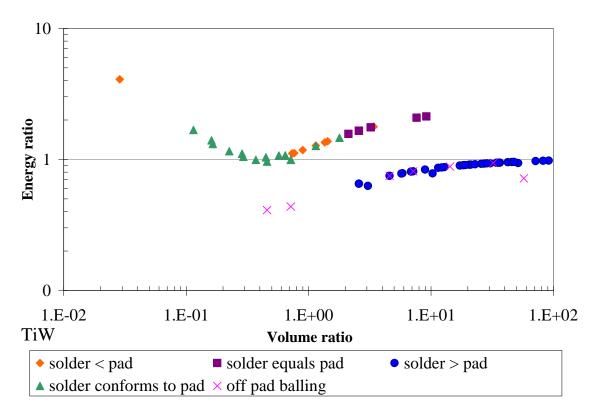

| Figure 3-40: Effects of energy and volume ratio on post reflow solder geometry 157    |

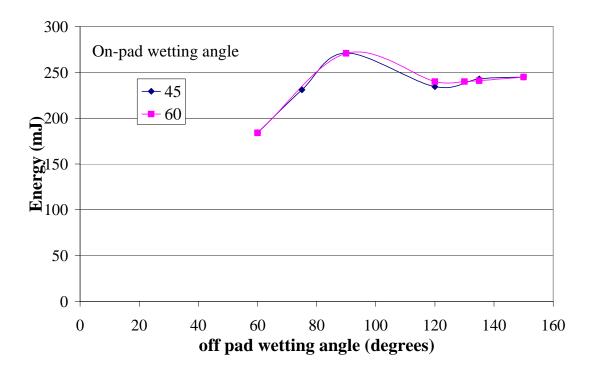

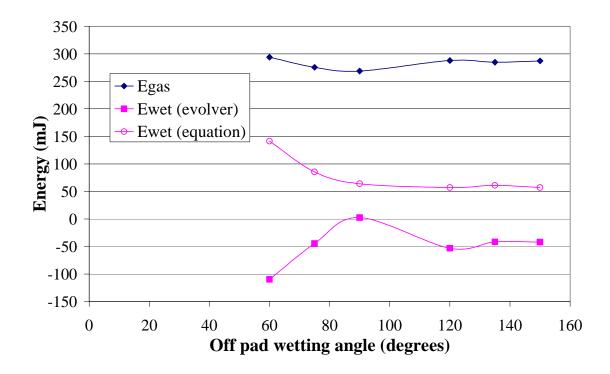

| Figure 3-41: Single volume, discrete wetting angle model results                      |

| Figure 3-42: Energy components of the variable wetting angle model (45° on pad        |

| wetting angle)                                                                        |

| Figure 3-43: Variable wetting model with 180° off-pad wetting angle; ggg iteration    |

| scheme [details of iteration schemes is documented in Appendix B] 161                 |

| Figure 3-44: Variable wetting model with 180° off-pad wetting angle; gg2 followed     |

| by ggg iteration scheme162                                                            |

| Figure 3-45: Variable wetting model with 60° off-pad wetting angle 163                |

| Figure 3-46: Variable wetting model with 120° off-pad wetting angle                   |

| Figure 3-47: Off-pad wetting (1250µm In pad on 500µm TiW/Au pad)                      |

| Figure 3-48: Solder in groove before reflow                                           |

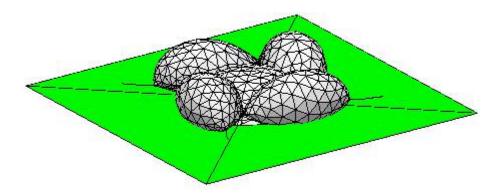

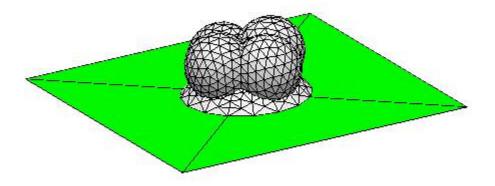

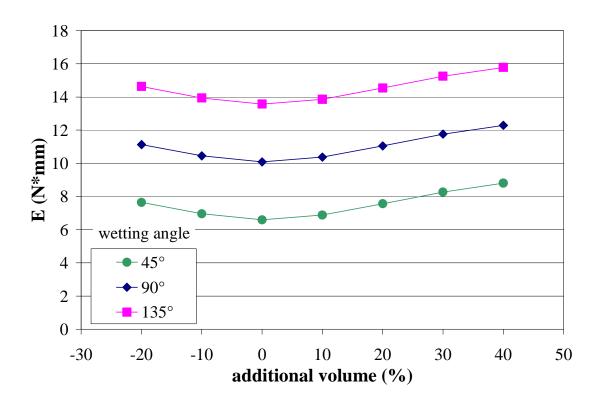

| Figure 3-49: Solder shape in fiber-groove interface with a nominal solder volume 167  |

| Figure 3-50: Solder shape in fiber-groove interface with 20% less than nominal solder |

| volume (solder deprived)                                                              |

| Figure 3-51: Solder shape in fiber-groove interface with 20% more than nominal        |

| solder volume (excess solder)                                                         |

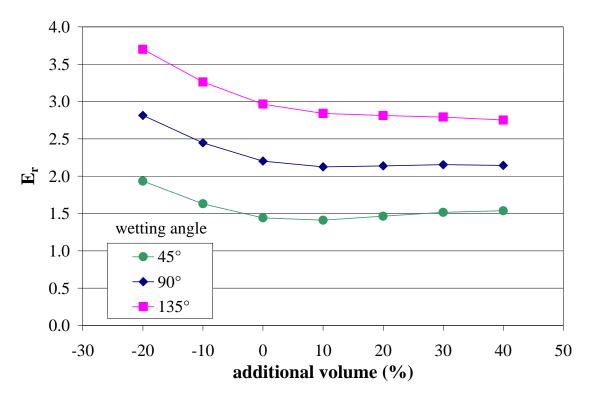

| Figure 3-52: Effects of wetting angle and solder volume on solder energy (fiber-          |     |

|-------------------------------------------------------------------------------------------|-----|

| groove model)                                                                             | 169 |

| Figure 3-53: Effects of wetting angle and solder volume on solder energy ratio            |     |

| (fiber-groove model)                                                                      | 170 |

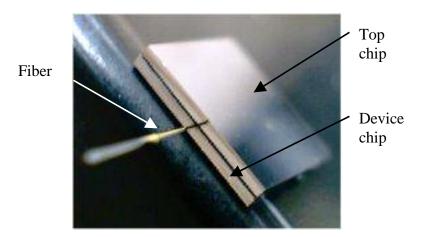

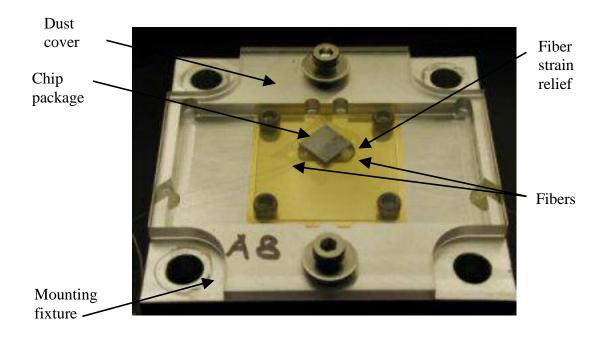

| Figure 4-1: Assembled chip-level package test structure                                   | 171 |

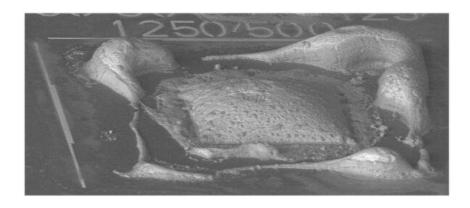

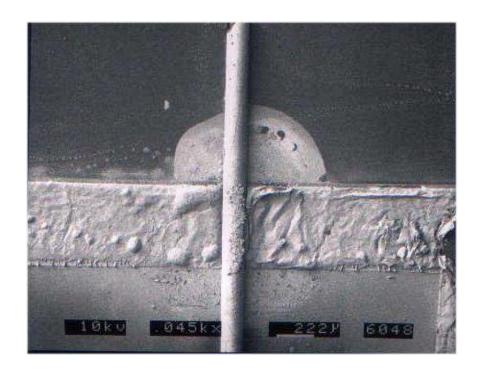

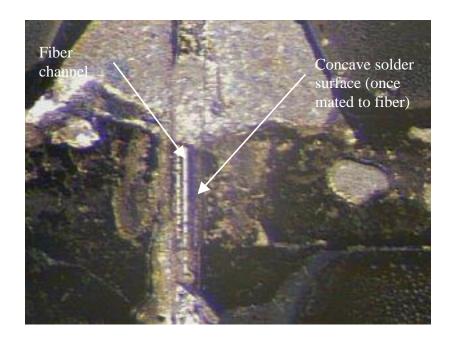

| Figure 4-2: Fiber in the groove of device chip after die shear                            | 173 |

| Figure 4-3: Top chip fiber groove after die shear                                         | 174 |

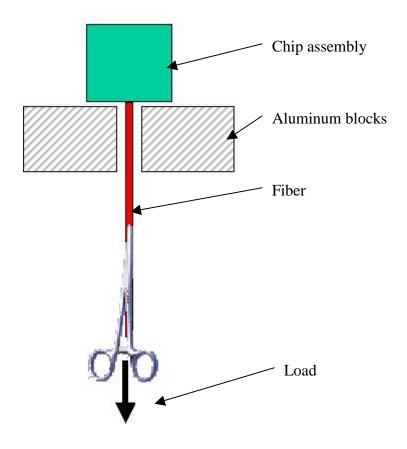

| Figure 4-4: Fiber pull test set-up.                                                       | 175 |

| Figure 4-5: Fiber after destructive pull test                                             | 176 |

| Figure 4-6: Chip-level package with 2 fibers in HALT test fixture                         | 179 |

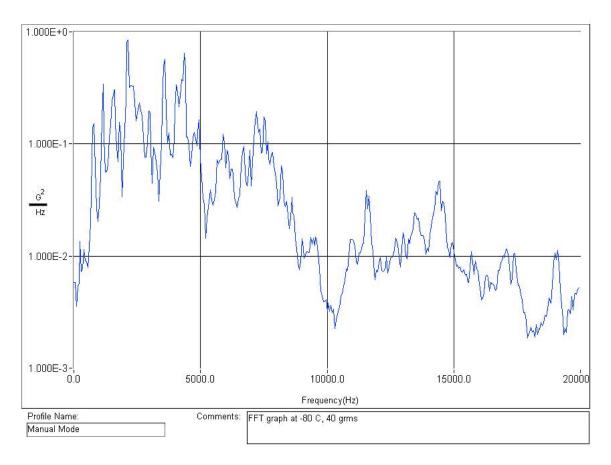

| Figure 4-7: Sample power spectral density of random vibration test (40 g <sub>rms</sub> ) | 181 |

| Figure 0-1: MEMS S&A chip in a Kovar® package                                             | 188 |

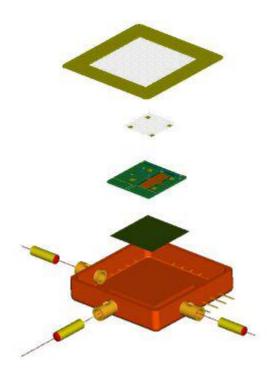

| Figure 0-2: MFMS S&A exploded view                                                        | 189 |

#### CHAPTER 1: INTRODUCTION

Microelectromechanical systems (MEMS) technology was first introduced in the 1960s in the form of pressure sensors. The MEMS structures in the pressure sensors, etched diaphragms with embedded resistors, are based on small deflections without friction or stiction related issues. Packaging of these sensors was able to readily leverage common integrated circuit (IC) packaging techniques, including passivation. In the 1980s, MEMS accelerometers entered the commercial market. The MEMS accelerometers did not need to directly interface with the surrounding environment. Packaging techniques for the accelerometers leveraged established IC packaging techniques, resulting in a more readily adaptable commercial product.

By the 1990s, MEMS research had expanded into more complex devices such as accelerometers, relays, optical devices, motors, pumps, and valves. The potential applications of MEMS also grew, spanning military, telecommunication, automotive, biological, hydrodynamic, and aerodynamic fields [1]. The expansion of MEMS into these fields arose from material improvements and processing advances. The new applications acted to further the advancement of MEMS technology.

Surface micro-machining and deep reactive ion etching (DRIE) expanded the potential for MEMS far beyond the bulk etched pressure sensors of the 1960s [2]. These processes provide precise control of mechanical structure geometry. As a result, complex systems can now be fabricated with or without assembly. However, the new devices posed new issues. Micron-sized contaminants rendered devices useless. Stiction, a

phenomenon where the surface micromachined device becomes bonded to the substrate, became a common source of device failure, both during processing and in-field use.

Understanding material properties, friction, and wear at the micro-scale became important. In addition, the effect of humidity and the forces associated with fluid surface tension became critical to device performance. The role of the package grew to not only protect the device from the external environment but also to interface with the environment. The package could also enhance the device performance through control of the internal environment. It became clear that, although IC packaging techniques could still be leveraged, new packaging techniques needed to be developed [3].

## 1.1 MEMS packaging

MEMS packaging can build upon IC packaging, but significant differences in the package requirements necessitate new designs, processes, and evaluation techniques [4]. Perhaps the most striking characteristic of many MEMS devices is that they are required to react to and influence the external environment while at the same time be protected from it. In addition, the mechanical interaction between multiple MEMS structures and the fact that moving structures exist inside the package require that additional issues, such as stiction, be addressed. Passivation techniques, which have greatly enhanced the reliability of IC packaging, are not directly applicable to MEMS devices due to the relatively large-scale motion of their components. Finally, the introduction of new

materials and processes on the chip introduces new failure modes and requires unique reliability assessment techniques.

Shouldering the burden of several often conflicting requirements, the package cost of MEMS is estimated to be somewhere from 60% to 95% of the final product [1, 5]. Two of the most successful commercial MEMS products, Analog Devices' accelerometers (e.g., ADXL models) and Texas Instruments' Digital Mirror Device<sup>TM</sup>, are both packaged hermetically [6, 7]. The prominence of hermetic packaging in MEMS arises for several reasons:

- Difficulty in passivating moving structures (corrosion failures)

- Effect of moisture on moving structures (stiction and friction)

- Effect of moisture on reflecting surfaces

- Control of out-gassing materials in the package (stiction, friction, mirror haze).

Despite the advances made by Analog Devices and Texas Instruments, relatively few MEMS devices have reached the commercial market. This is due largely to the unique requirements placed on the packaging by each unique device and its intended application. Several aspects of packaging, such as protection from contaminants and moisture control, are common to most MEMS devices. However, the manner in which the MEMS interface with the external environment significantly affects the package architecture. As a result, most MEMS devices will require application-specific packaging designs. The industry could, however, benefit from a common toolbox of technologies and processes to successfully package devices.

To produce a reliable, cost effective system, packaging must be considered early in the design cycle. The device drives the functional requirements of the package. A device that is not designed for packaging can put enormous and unnecessary demands on the package (functional, performance, and economic).

## 1.2 MOEMS Packaging

Microoptoelectromechanical systems (MOEMS), which are MEMS integrated with photonics, share the traditional challenges of MEMS with the additional issues of optical interconnects and of optical surface contamination. The challenges posed by optical interconnects pales in comparison to the potential payoff. Traditionally, switching in the telecommunication industry is performed electrically, even in optical networks. MOEMS offers significant savings in power, cost, and volume. More importantly, it eliminates bottlenecks at the electrical switch or router and allows wavelength division multiplexing (WDM) to reach its full performance potential.

Facilitating all optical networks, MOEMS is expected to have a huge impact on the telecommunications market [8, 9]. The optical component market, in general, is projected to grow anywhere from 35% to 50% per year for the next several years [5, 10]. MOEMS is well positioned to impact the existing market as well as the expanding market. Most MOEMS applications place additional emphasis on hermetic packaging due to potential contamination of the optical surfaces [11]. The proliferation of hermetic optical packaging needs has resulted in a library of stadard packages and numerous

sources for custom package fabrication [12]. AXSUN Technologies uses a metal butterfly package to protect their MOEMS device, Acutune Detector Module, Figure 1-1 [13].

Figure 1-1: AXSUN Technologies Acutune Detector Module

#### 1.3 The United States Navy's MEMS safety and arming (S&A) device

A MOEMS-based safety and arming system (S&A) for use in underwater weapons has been developed by the Indian Head Division, Naval Surface Warfare Center [4, 14, 15]. MEMS are the enabling technology for the next generation of lightweight torpedoes. Reducing volume by an order of magnitude, MEMS technology provides a means to reduce the diameter of torpedoes to one third to one half of previous systems. In addition, the expanding infrastructure of MEMS fabrication facilities is a stark contrast to the dwindling conventional mechanical S&A component-manufacturing infrastructure.

The purpose of the S&A system is to arm and detonate the weapon when appropriate and to prevent inadvertent weapon detonation. Reliability of the S&A is critical to the survivability of Naval assets, including the ship and its crew.

The S&A is composed of environmental sensors and actuators that control two fiber optic switches with mechanical locks. All structures are fabricated using the Bosch DRIE process [2] and are selectively released to eliminate micro-assembly. Silicon on insulator (SOI) wafers are utilized to provide an accurate etch stop and to provide an accurate gap between the MEMS structures and the underlying substrate. The S&A has been demonstrated in 100 µm and 125 µm device layer thickness. Once specified environmental operation criteria are met, the S&A arms by removing locks and pushing opposing optical fibers in and out of direct alignment with each other using v-beam electrothermal actuators [16, 17]. The switch is configured so that the fibers are initially offset in the out-of-line (off) position and are then actuated to the in-line (on) position.

The S&A chip has to be able to operate in a variety of environments, including temperature, humidity, shock, and vibration. The device must have a shelf life of 20 years. Although the S&A device is only required to function (arm) once, both its safety and arming functions are critical. The S&A must be highly reliable throughout its life to ensure weapon safety and function. To meet the above requirements, the package must be hermetically sealed (this requirement is discussed in more detail in Section 1.5). The baseline packaging approach for the Navy S&A is to adapt conventional hermetic packaging techniques from the high reliability IC and telecommunication applications. In this approach, the S&A chip is enclosed in a hermetic housing, such as Kovar®, a specialty nickel cobalt alloy with a thermal coefficient of expansion close to silicon. The package is hermetically sealed at each interconnect, including electrical and optical

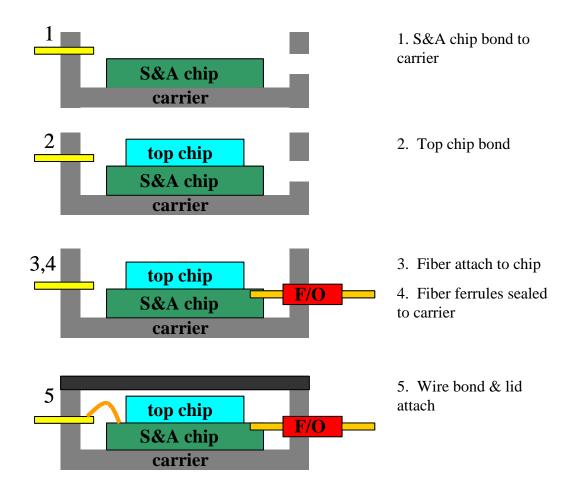

interfaces. The final hermetic seal is formed by sealing a Kovar® lid to the package. The sequence used to package the S&A is shown in Figure 1-2.

Figure 1-2: Baseline MEMS S&A packaging sequence (F/O denotes optical fiber)

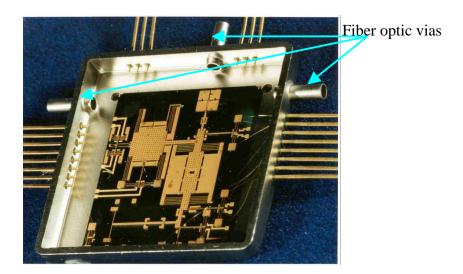

Notice that several packaging steps are performed before the exposed MEMS structures are protected. The S&A chip in its package is shown in Figure 1-3.

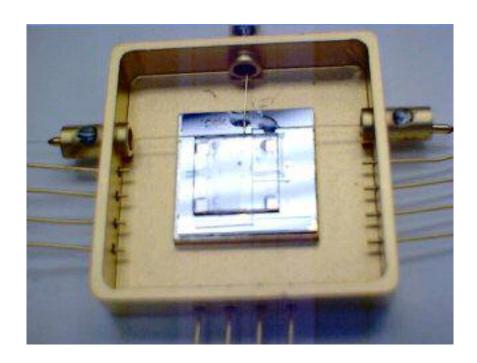

Figure 1-3: MEMS S&A chip in Kovar® package

#### 1.4 Motivation for improved MEMS packaging

This section provides the motivation for this dissertation and the resulting benefits of this research. The role of packaging in the integrated circuit (IC) industry has transformed the IC market. Low-cost, reliable packaging was the final hurdle for the boom in the IC industry. Likewise, packaging is likely to have a similar effect on the commercialization of the MEMS technology. As the IC industry continues to benefit from the extensive research in IC package reliability, MEMS packaging must leverage the lessons that have been learned. However, MEMS, unique in its nature, will require unique solutions and evaluation techniques. Most successfully commercialized MEMS share two important commonalities:

- They are hermetic

- The hermetic seal is formed between 2 chips

The goal of this research is to provide a sealed package with optical fibers crossing the seal boundary using only batch fabrication techniques to form the package. This elimination of the Kovar® package is to be done without compromising hermeticity. However, a hermetic seal between two chips with a fiber crossing the hermetic boundary has yet to be demonstrated. This dissertation provides the foundation to realize a package in which the microstructure area is hermetically sealed between two chips with provisions for fibers to cross the boundary. This section details the benefits of realizing this package.

#### 1.4.1 Increase packaged MEMS die yield

For the economy of batch fabrication to be realized for complex MEMS, high yields are required at each yield-critical phase of production. Significant yield issues may arise during fabrication, structure release, dicing, and packaging. Although 100% yield is not expected, even a 90% yield at each of these four critical steps would reduce final packaged yield to a meager 66%.

Low yields in the front-end processing are more acceptable than in the back-end processing because less has been invested in the product at the beginning of the process (this statement assumes that test and/or inspection can identify and scrap defective products during the fabrication process). Estimates for the packaging cost of a finished MEMS product may be anywhere from 60% to 95% of the overall cost [5]. A loss during the packaging process is therefore much more costly than at any other stage of development. The loss at the packaging phase can arise from two general sources:

- Before packaging, the unprotected device is exposed to a harmful environment (e.g., errant dust particles, rough handling, etc.)

- The environmental conditions associated with the packaging process induce a failure

Therefore, the packaging techniques need to be developed to protect the MEMS as early as possible in the packaging process. In addition, benign packaging environments are desirable to limit induced failures.

High reliability applications often use a ceramic or specialty metal package to house and hermetically seal the critical components. These carrier-level packages do not provide protection of the microstructure area until the final packaging step.

Alternatively, some high reliability hermetic applications, such as Analog Devices' hermetic accelerometers, have been able to eliminate the carrier and seal the microstructure between two chips. Using its wafer-level sealing process, Analog Devices was the first to mass-produce MEMS accelerometers in 1993 with their ADXL50 model, which was the first commercial surface micromachined device [18, 19]. This chip seal approach provides protection of the fragile MEMS structures early in packaging process, thus exposing the structures to less handling and contaminants. A chip-level seal enables performing several packaging steps, such as die attach and wire bonding, after the MEMS is already protected.

#### 1.4.2 Design flexibility

Both MEMS and optical devices are sensitive to humidity, out-gassing, and corrosion. The humidity in the package alters the friction between movable MEMS devices and can cause a phenomenon known as stiction. Stiction occurs when the once suspended MEMS structure makes contact with the substrate and the forces from MEMS actuators are insufficient to overcome the surface forces, most typically van der Waals forces. In more severe cases, external, macro-forces break the MEMS structure before the stiction can be alleviated. The fiber optic reflectors and fiber ends are also degraded by humidity. Out-gassing of organic material can also cause both stiction and fiber optic surface contamination. These concerns combine to greatly limit the viable material choices available to the packaging engineer. In addition, the use of out-gassing species requires compatibility studies between the selected bond materials and the MOEMS structures. A change in the assembly process or change in organic material selection will thus require additional compatibility testing. The addition of compatibility concerns expands the matrix of tests performed during test and evaluation. Another compounding factor is that compatibility concerns further burdens the interpretation of accelerated aging tests of the MEMS devices, which are performed in the absence of acceleration factors that are specific to MEMS failure mechanisms, further compounding risk.

Generally, it is prudent to minimize the variety of materials in the package to reduce the amount of testing required and to reduce the risk of field failures. Performing a chip-level hermetic seal accomplishes this. The hermetic portion of the package is as

small as possible, reducing, in most cases, the variety and quantity of materials involved. This allows for more freedom in the selection of packaging materials in the latter packaging steps. For example, out-gassing concerns from the die attach material are not relevant to a package sealed at the chip-level.

#### 1.4.3 Increase package life cycle

Little field data exists on the life of MEMS. Acceleration factors for accelerated aging tests that hope to accelerate MEMS-specific failure mechanisms are educated guesses, if they exist at all. The understanding of the failure modes specific to MEMS is in its infancy. An extensive environmental conditioning program can add great confidence with regards to the robustness of the MEMS/MOEMS package, but cannot accurately predict the package life. If the life of the product falls short of the design goal, the life may be extended by periodic maintenance, such as inert gas back-fill, typical for most long-term storage military systems.

The chip-level packaging approach should increase the life of the MEMS package. The protection early in the packaging phase reduces the defects introduced into the system. Defects often are undetected in the screening phase (especially in the case of MEMS because there is little knowledge about how to design an effective screen), but reveal themselves years later after repeated environmental exposure. Reducing the variety of materials in the MOEMS portion of the package also decreases the risk of future failures. And finally, the increased design flexibility allows the package designer

to choose packaging material based on its mechanical and thermal properties without the additional constraints of chemical compatibility.

#### 1.4.4 Cost

All of the reasons cited above have an impact on cost. Increasing die yields reduces the number of rejected die and also packaged devices. Greater design flexibility allows an additional emphasis on cost reduction through material and process selection. Another factor reducing cost is the reduction of testing requirements that shortens the design cycle providing shorter time to market at a lower unit cost. Increasing package life impacts system maintenance and inventory and reduces system sustainment costs.

Consider, for example, the carrier package. Specialty metals, typically Kovar®, are used to provide a close coefficient of thermal expansion match at the die mount between the silicon chip and the package. Glass seals in the walls of the package provide the electrical isolation and the hermetic feed through for the electrical interconnects. Kovar® is an expensive metal that is difficult to machine, typically handled by specialty machine shops. The glass electrical interconnect seal is also a specialty process. The result, for custom applications, is a carrier that can cost upwards of \$100. Contrast that to a chip, which can serve as a hermetic lid for pennies.

#### 1.5 Package requirements

To meet the requirements presented in Section 1.3, the package must be hermetically sealed and free of organics [20]. Although the Naval requirements were the driver for the selection of an organic-free hermetic package, other MEMS applications, such as telecommunications, share similar issues that result in the same package definition.

The two key factors driving hermetic enclosure requirement for the MEMS structures are the following:

- Moisture content in the package affects the performance of the MEMS device and can lead to catastrophic stiction failures.

- 2) Optical components (mirrors, lenses, etc.) are also sensitive to moisture.

The actual usage temperature of MEMS (and in particular the Navy S&A device shown in Figure 1-3) will vary over a wide range, making the usage relative humidity difficult to control. The storage temperatures will vary over an even greater range. This is significant in that it is imperative not to form condensation in or around the MEMS. Recall that MEMS devices are prone to stiction related failures; that is, capillary forces from moisture in the package draw the suspended structures to the substrate and the van der Waals forces keep them there. Even a small amount of moisture in the package during packaging or ingress during storage can result in condensate formation (Table

1-1). The values calculated in Table 1-1 are derived from the thermodynamic steam tables assuming a constant pressure control volume.

Table 1-1: Temperature and humidity conditions necessary to form condensation before freezing

| Process                              | Temperature | Relative humidity<br>(0 °C dew point) |

|--------------------------------------|-------------|---------------------------------------|

| Typical room (air used in packaging) | 22 °C       | 22%                                   |

| Packaging                            | 125 °C      | 0.25%                                 |

| Storage                              | 60 °C       | 3%                                    |

Another factor in the reliability of MEMS is organic out-gassing. Out-gassed species pollute the internal environment and contaminate the optical surfaces and MEMS structures. A hermetic package can prevent ingress of organics from outside the package. However, a hermetic package also traps out-gassed materials inside the package. Therefore, a packaging design and process that yields a hermetic package with minimal internal volatile material is sought. Elimination of organics precludes the use of adhesives and solder fluxes within the sealed portion of the package. In addition, the package seals must maintain their integrity throughout the life of the MEMS.

#### 1.6 Other relevant efforts and background literature

Due to large potential economic payoff of fielded MEMS devices, the details of the package design and processing tend to be guarded as trade secrets and as a result slowed

the progress of the industry [21]. More specifically, details of optical component packaging are not widely shared. Even less is published on MOEMS optical interconnects. Knowledge about optical interconnection methods is a highly guarded trade secret, even regarding the traditional fiber-to-carrier seal. Due to the fact that MOEMS is still in its infancy, this section also includes a brief description of relevant MOEMS work currently being performed.

#### 1.6.1 Fiber optic packaging

The vast majority of fiber optic components are hermetically packaged [22]. This holds true even if MOEMS are not inside the package. Although there has been a significant effort to launch non-hermetic packages, most of the telecommunication industry uses hermetic components. The Telcordia standard, GR-468-CORE [23], imposed on all components in the telecommunication industry is, in general, stricter than military standards. The lower-end market, for example light emitting diodes, utilizes both hermetic and non-hermetic packages. The packaging of micro-optical components is key to the proliferation of commercial MOEMS [24].

It is the very fact that so little is published on packaging techniques for fiber optic components that fuels the fiercely competitive nature of the networking market at infrastructure companies such as Agere and Cisco, and contributes to the close guarding of intellectual property.

Agilent recently introduced a non-hermetic package for an optical transceiver that satisfies the Bellcore standard [25]. An encapsulation technique with silicone was used to achieve the hermetic-equivalent reliability. Strict attention to details in the design of the device and package are necessary to implement an approach such as this that uses passivation and encapsulation. In addition, the life of the non-hermetic package has yet to be demonstrated in field use.

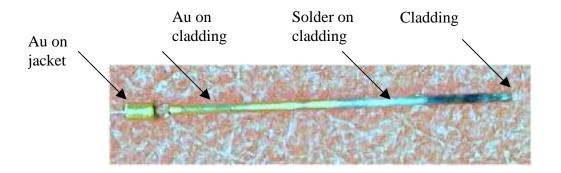

#### 1.6.2 Metallized fiber

In Section 2.1, it will be established that most fiber optic packages are hermetic. A key component to make these packages hermetic is metallized fiber. The metal is hermetically sealed to the fiber and provides a surface for solder to wet and form a hermetic seal. To make metallized fiber, the jacket is stripped off the end of the fiber over a specified length, usually on the order of a few millimeters. The exposed cladding is then coated with a nickel adhesion layer to facilitate soldering. This process is considered mature and metallized fiber can be readily ordered to customer specifications [22]. The metallization scheme can be specified by the end user, but usually consists of a gold plating over nickel. The gold prevents oxidation of the nickel and the nickel serves as the wetable surface for solder during packaging.

The fiber metallization facilitates attachment of the fiber to both the chip and the carrier. For the chip attachment, the fiber is typically soldered or welded to a metallized portion of the chip. Often a welding tab is placed on the fiber to facilitate the attachment

to the chip. The soldering and welding techniques avoid the use of organics and provide a robust, precise alignment between the fiber and the chip. For the attachment to the carrier, the metallized fiber is often first soldered to a Kovar® ferrule and the ferrule is the soldered to the package. The ferrule serves two purposes. First and foremost, the ferrule reduces the gap between the fiber and the hole in the wall of the package. The hole in the package is made much larger than the fiber to accommodate the welding tab for the chip attachment. The large clearance between the fiber and the conduit requires use of more solder and results in a weaker bond than a thinner solder joint. The second reason for a ferrule is to provide a robust feature for the automated grippers used in the assembly of the fiber to the chip and carrier. The ferrule does increase the cost of the fiber significantly and the complexity results in another potential leak path and thus increases likelihood for hermetic seal failures. Designs that eliminate the use of a ferrule benefit from reduced cost, reduced complexity, and should result in greater reliability. The key is to eliminate the ferrule while still maintaining the needed positional accuracy between the fiber and the chip.

#### 1.6.3 MEMS packaging

MEMS packaging continues to be an active area of research [26]. Presently, packaging platforms are tailored to the application as well as the processing techniques and the microstructure materials selected to fulfill the application specific requirements.

The MEMS industry is unlikely to achieve the level of standardization achieved by the IC

industry due to the fact that the MEMS must often interact with the environment and typically must maintain a certain degree of motion [27]. However, processes and techniques for one application can be applied or adapted to another. There is a strong need in the industry for standard packaging tools that are applicable across numerous applications [28]. Aside from pressure sensors, which only consist of the deflection of a silicon diaphragm, most commercial MEMS devices are hermetically sealed [29]. Accelerometers, rate sensors, and optical mirrors are typically hermetic. The hermeticity allows for control of the internal package environment, including humidity, pressure, and out-gassing. The hermetic package is not just critical to the long-term reliability of the package, but also impacts the performance of the device. From a reliability perspective, the hermetic seal protects the MEMS device from stiction related failures. In addition, it reduces the likelihood of corrosion related failures. From a performance perspective, the hermetic seal allows precise control over the internal environment. Moisture levels and pressure in the package can be selected to optimize the MEMS device performance. Various techniques are being explored to form the hermetic seal. Most of these techniques are being applied at the wafer-level to reduce final product cost, enhance product reliability, and reduce yield losses. Anodic bonding uses glass to make the hermetic seal and thus avoid stresses due to large coefficient of thermal expansion mismatch [30, 31, 32]. Silicon fusion bonding is advantageous in that two silicon wafers can be directly bonded together without any other material, but requires high bonding temperatures [33]. Solder remains an attractive choice since the seal can be performed at lower temperatures [34, 35, 36]. Finally, 0-level packaging approaches are being

investigated where micro-caps over the MEMS structures can be formed during the micro-machining process [37, 38].

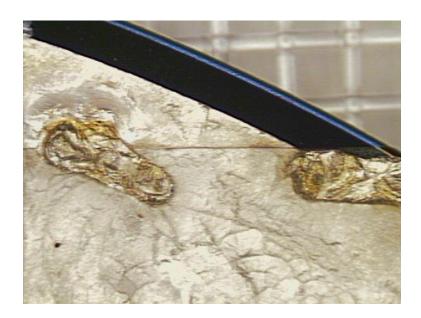

Die attach of MEMS structures requires special consideration. A comprehensive study was performed jointly between NSWC and the University of Maryland's CALCE center to evaluate materials for die attach and chip-to-chip attach [39,40]. Indium samples were fabricated using the sequence outlined in Section 2.6. In this study a coefficient of thermal expansion (CTE) mismatch was introduced by bonding a silicon die to a ceramic die. Reflow of the indium samples was performed in a fixture at an extremely low value of absolute pressure. Test structures were inspected for delamination using scanning acoustic microscopy (SAM) and then put through a battery of environmental testing, including accelerated aging, thermal cycling, and shock. After completion of environmental testing, samples were again inspected for delamination and then die sheared. The indium solder did not see delamination growth due to environmentally induced stresses, Table 1-2. In addition, the indium samples were stronger in die shear than the organic based materials.

Table 1-2: Environmental study results of indium die attach material

| Environmental<br>Conditioning                  | Range of initial delamination (%) | Delamination<br>growth<br>(%) | Range of<br>die shear<br>(MPa) | Average<br>die shear<br>(MPa) |

|------------------------------------------------|-----------------------------------|-------------------------------|--------------------------------|-------------------------------|

| None                                           | 2 - 30                            | 0                             | 4.5 - 6.3                      | 5.2                           |

| 100 days<br>85% RH at 85°C                     | 9 - 48                            | 0                             | 7.0 - 8.4                      | 7.7                           |

| Thermal cycling:<br>28 cycles<br>-54°C to 71°C | 0 - 0                             | 0                             | 5.5 – 7.4                      | 6.4                           |

| Shock: 250 gs, 4.5 ms                          | 10 -38                            | 0                             | 4.6-13.8                       | 7.9                           |

#### 1.6.4 MOEMS packaging

As a subset of MEMS packaging, MOEMS are also primarily hermetic. The reliability of the packaged device and the repeatability of the packaging process are the major hurdles to commercialization of MOEMS [41, 42, 43]. Hermetic packages with accommodations for optical fibers are commercially available [12]. Other packages, such as Texas Instruments' successfully commercialized MOEMS based overhead projector, use specialized hermetic packaging techniques. Still others, such as Agere's 64x64 3D MEMS optical switch, have developed non-hermetic solutions [44]. Optical interconnects for MOEMS have historically consisted of a hermetic interconnect where the fiber passes through a wall. However, wave-guides and windows are feasible alternatives to the fiber optic interconnect.

Current efforts in MEM/MOEMS packaging at the universities are not focused on optical interconnection. The Center for Advanced Manufacturing and Packaging of Microwave, Optical, and Digital Electronics (CAMPmode) at the University of Colorado at Boulder is a National Science Foundation (NSF) funded organization with a strong focus on MOEMS packaging [45,46]. However, most of CAMPmode published MOEMS packaging work is focused on lens alignment. The Defense Advanced Research Projects Agency (DARPA) has established the University Opto Centers program that focuses on the integration of photonics, electronics and MEMS [47]. Although many of these DARPA funded projects utilize waveguide interconnects, none appear to address interconnects with fibers at this time.

## 1.6.5 Fluxless soldering

Fluxless soldering continues to be an active research field, as it has been for the last 20 years. Environmental concerns are driving the industry away from the standard leadbased solders as well as the conventional rosin-based fluxes. The role of the flux is to effectively clean the oxides from both the solder and the surfaces to be wetted. Metal oxides typically have a very high melting point and inhibit the chemical bond between the solder and the wetting surface [48]. The flux is critical to forming a reliable solder joint, however, residue from the flux is the primary source of corrosion and out-gassing related failures in microelectronics [49]. The rosin-based fluxes can be difficult to remove and trap corrosive flux activators. In a conventional soldering process, the rosinbased flux is cleaned with a chlorofluorocarbon (CFC), which was banned by the Clean Air Act of 1995. As a result, no-clean and water-based fluxes were developed to replace the CFC-based cleaners [50]. These alternatives fluxes fail to clean the oxides as effectively as the rosin-based fluxes. As a result, soldering processes with non-rosin based fluxes often require control over the oxygen content in the environment during reflow [51]. In addition, the no-clean fluxes leave behind an unsightly residue. Conceptually, the no-clean fluxes do not require post solder reflow cleaning, but are typically cleaned for aesthetics as well as out-gassing concerns. The cleaners used to remove the no-clean and water-based cleaned fluxes still suffer from environmental concerns and do not clean the flux residue as effectively as the CFC cleaners. As a result, soldering for high reliability applications, such as space applications, is performed

without the aid of fluxes [52, 53]. Some systems, such as MEMS, are adversely affected by liquids due to stiction related issues and are difficult to clean due to small clearances between structures. This has further driven the need for fluxless soldering processes.

Fluxless soldering processes fall into two major categories:

- Passivation of the metallization surface and solder

- Atmospheric control of the oxygen content

Passivation of the metallized surface prevents oxidation of the solder. The passivation layer is dissolved into the solder joint during reflow. A fluxless soldering process using a vacuum deposition of gold onto indium was demonstrated for a variety of solder systems [54, 55, 56, 57, 58, 59]. In these processes, the indium in the pure indium or binary lead/indium, silver/indium, or tin/indium binary solder systems react with the gold to form a gold indium intermetallic that passivates the solder, thus preventing oxidation formation.

In an atmosphere-controlled soldering process, the atmosphere either protects the solder and wetting surfaces from further oxidation or reduces the existing oxides from these surfaces. Nitrogen and vacuum are used to prevent further oxidation during the reflow process [60, 61, 62]. Lee found that the atmosphere must be below 180 ppm for reliable wetting of indium solder to a nickel surface [63]. Dong found that a tin-indium solder would not spread on nickel in an inert environment unless the oxygen concentration was on the order of 10 ppm [64, 65]. Dong reports the reduction rate of the indium oxide, but fails to cite the thermodynamic conditions at which the reduction took place. The use of hydrogen to reduce oxides from the metal surfaces was demonstrated

to be feasible by Kuhmann [66] at temperatures well above the reflow temperature of the solder. Based on a thermodynamic analysis, Kuhmann later refuted the work of several others that claimed to be using hydrogen to reduce oxides at reflow temperatures [67]. Alternatively, formic acid vapor can also be used to reduce metal oxides in the soldering process [68].

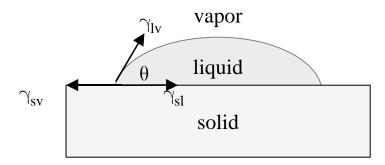

## 1.6.6 Solder energy modeling

Modeling the solder shape, energy, and forces provides a deeper understanding of the solder process and can result in a valuable design tool. Empirical data can be used to obtain necessary data, but the complexity of the soldering process and the difficulty in controlling all of the factors that govern it make it difficult to obtain a firm understanding of the effects of the design parameters. A model need not necessarily be absolutely accurate to provide an understanding of the trends that govern the final shape of the solder joint. Rather the model should provide the designer a qualitative tool to predict the solidified solder geometry and the energy state of the solder in the fluid state. The final shape and energy state of a fluid and the resultant forces between the fluid and the boundary surfaces can be solved in a closed form for the simplest of cases using the Laplace Equation of Capillarity [69]. For more complex scenarios, several numerical techniques can be used to resolve the shape and energy of the fluid [70]. The energy state and geometry of a fluid, such as solder during reflow, can be modeled using Surface Evolver [71]. Surface Evolver is software developed at Susquehanna University by

Kenneth Brakke to study the surfaces shaped by surface tension and other energies, such as gravitational potential energy. It evolves a user-defined shape to a minimal energy state constrained by user-applied boundary conditions. Energy modeling of the solder can be used to predict final joint shape and reliability. Yeung used an energy model to predict the final joint shape to guide design of flip-chip and wafer-level packaging [72, 73]. The restoring force between two misaligned chips was studied at the Center for Advanced Manufacturing and Packaging at the University of Colorado under a DARPA contract [74]. The modeling was later extended to determine equilibrium shape and the final position of a MEMS structure that was actuated by the wetting forces of the molten solder [75]. These self-assembly techniques were verified experimentally [76, 77]. The stresses calculated in the Surface Evolver model of the molten solder, can be coupled into a finite element model for stress analysis of the resulting solder joint [78].

## 1.7 Scope and objective of present effort

A potentially hermetic package between two chips with a fiber crossing the hermetic boundary has yet to be demonstrated. The work in this dissertation lays the foundation for a chip-level fiber-based optical interconnect. The broad objective of this research is to demonstrate a fiber optic connection into a hermetic chip-level MEMS package supported by the development of an experimental database of soldering test structures combined with energy modeling.

The optical interconnect treated in this dissertation is formed by reflowing solder to seal between the two chips and at the fiber-to-chip interfaces, including the fiber groove. The chips are batch fabricated using MEMS compatible fabrication techniques. The steps added to the process to make the structures for the hermetic seal are all performed at the wafer-level using batch fabrication techniques. The undermetallization is sputtered onto the top mesas of the chips and into the grooves. The solder is evaporated on the top mesas of the chips and into the grooves. The solder and undermetallization designs are modeled using an energy minimization software tool, Surface Evolver, to provide guidance on the joint design. The assembly of the chip and fiber uses an inert environment, or preferably a reducing environment to provide more consistent post-reflow solder joint shape and consistency.

Several steps had to be completed to realize the chip-level optical interconnect package. These steps encompass fabrication, design, modeling, soldering, and assembly techniques. Each of these key steps required advancement in the state of the art or an improved fundamental understanding to result in a consistent, producible package.

1. Design and process development for fabricating the sealing die interface: First a design and processing approach was conceived and refined to seal a fiber between two chips (Sections 2.1 and 2.6). The selected design approach for this dissertation requires a hermetic seal of a round fiber in a faceted groove. In addition, a contiguous metallization ring is needed on the top mesa, on the fiber groove sidewalls, and on the bottom of the fiber grooves. Process techniques were tailored to meet these requirements. In addition, the sealing of the round

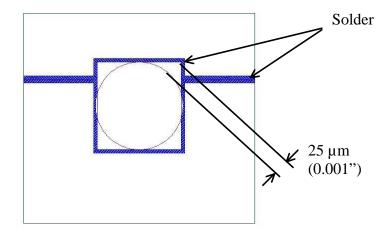

fiber in a faceted groove required additional solder volume near these interconnects. Masks had to be appropriately designed to define the wetable areas of the chip and to provide sufficient solder to fill the void geometry. The deposition techniques and the practical limits necessary to form solder pads significantly larger than the undermetallization pads were developed and evaluated.

- 2. Solder system design: The second major task that was addressed is the design of the solder system, Section 2.4. The metallization of the fibers and chips must be selected to ensure good adhesion, wetting, and compatibility with the solder. The thickness of each layer also plays an important role from both a thermodynamic and metallurgical perspective, which ultimately affects the success of any soldering technique. Proper selection of material and the material thickness of adhesion layer, wetting layer, passivation layer, and the solder layer are interdependent and dictate the success of a fluxless soldering process, joint strength, and joint reliability.

- 3. Fluxless soldering process: The third major task was to assess the viability of fluxless soldering and then apply the fluxless soldering process. The fluxless soldering process, although very dependent on the solder system, can be thought of being comprised of both the cleaning and assembly of the chips. A thermodynamic model that ideally governs the reactions of the metal oxides was applied and tailored to the reduction of oxides considered in this dissertation, Section 2.7. The understanding of thermodynamics behind the soldering process

was used to interpret the reflow results and then adapt the cleaning and assembly processes to realize the fluxless soldering process. An assembly process was designed to minimize solder oxidation, Section 2.9. The assembly process encompasses a series of steps and characteristics, including the handling of the die after cleaning, the method to apply the heat for reflow, the amount of heat to apply, the heat rate, and the gaseous reflow environment.

- 4. Joint stability modeling: Modeling is used as a design tool to predict the final energy, and thus the stability, of the reflowed solder joint, Section 3.3. In addition, the model provides a deeper understanding of the interaction between the wetting forces and the surface tension forces.

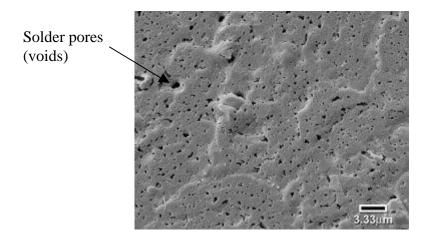

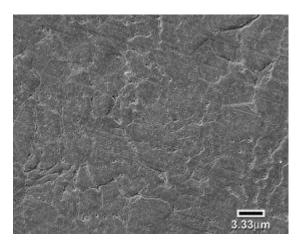

- 5. Experimental valdation: The final major task was to evaluate the reflowed solder coupons, Section 3.1 and 3.2. A scanning electron microscope (SEM) equipped with an energy dispersive x-ray (EDX) was used to evaluate the quality of unsectioned and cross-sectioned solder joints. The EDX was particularly useful in identifying grain structures in post reflow solder joints. Destructive tests, such as die shear, were used as a quantitative evaluation of the quality of the solder.

The primary contribution of this dissertation is a method to hermetically seal a metallized optical fiber between two chips without the use of a flux. To date, no such package has been reported, with or without the use of fluxes. In addition to this umbrella contribution, several smaller contributions were also realized. First, a method to deposit a contiguous metal layer onto all the surfaces of a MEMS fabricated groove was

demonstrated. Second, a Surface Evolver model was generated to predict the flow of solder on a surface with a variable wetting angle. Third, the behavior of high aspect ratio indium solder during reflow, especially with regards to fluxless soldering, was examined. Fourth, a Surface Evolver model was generated to predict the stability of a solder joint between a round fiber and a faceted groove. Finally, conditions for fluxless soldering with indium were defined.

In Chapter 2, the design of test structures and the methods to fabricate these structures is presented. Imddition, the parameters that govern the fluxless soldering process are examined. In Chapter 3, the energy modeling and the experimental results of the test structures is presented and discussed. In Chapter 4, the robustness of the package is evaluated through fiber pull, die shear, and highly accelerated life testing.

#### CHAPTER 2: INTERCONNECT DESIGN AND FABRICATION

In this chapter, the approach used to form a chip-level hermetic MOEMS package in which the fiber crosses the hermetic boundary is presented in detail [79]. The design concept is presented and associated issues are discussed. The batch fabrication processes used to make the chips, common to most MEMS foundries, are discussed and evaluated. The coverage of the sidewalls of the high aspect ratio trenches, one of the key features that must be realized for the producibility of the presented design, is evaluated for different processing techniques. The rationale of the solder system selection and parameter variations studied in this dissertation are discussed. The solder system is a critical step in the design of any solder joint due to formation of brittle intermetallics and failures along grain boundaries. For fluxless soldering applications, especially those that utilize capillary forces to drive the solder flow, the selection of the solder system requires further emphasis such that oxidation formation is limited and intermetallic formation does not impede the flow of the solder during wetting. To further address the fluxless soldering and oxidation, a thermodynamic model that governs the reactions of the metal oxides was applied and tailored to the reduction of oxides considered in this dissertation. After demonstrating that a vacuum and inert reflow environments are insufficient for fluxless soldering of the candidate solders, the use of a hydrogen reducing gas is discussed with a focus on the thermodynamic conditions to reduce the oxygen in the atmosphere to the point where the conditions are favorable to the reduction of the metal oxide. Having noted that the reduction of the oxide without use of flux is not trivial,

methods to remove the native oxide from the solder are presented. To further develop appropriate handling techniques, the reoxidation rate of the metal oxide as a function of temperature is introduced.

## 2.1 Device and cap chip design

In the studied approach, the fiber is to be sealed between two chips. The device chip is from a silicon on insulator (SOI) wafer with a 300 $\mu$ m handle wafer and a 100  $\mu$ m device wafer. SOI wafers are commonly used in DRIE applications. A SOI wafers used in this dissertation consist of a 2  $\mu$ m oxide sacrificial layer sandwiched between two silicon wafers, 300  $\mu$ m and 100  $\mu$ m thick in this case [80]. The 300 $\mu$ m layer serves as the handle wafer, providing compatibility with the fabrication equipment as well as rigidity during processing and in use. The 100  $\mu$ m layer is the active or device layer. The device layer is machined to create the MEMS structures, such as the optical mirror. The sacrificial layer can be etched to selectively release structures and thus allow movement of the micromachined structures. A 100  $\mu$ m device layer was selected to meet the requirements of the Navy MEMS S&A (Appendix A) and is considered fixed for the present effort. The thickness of the active layer is similar to other optical devices and the present technique may be extended to those applications.

The multimode fiber used in the present effort will have an approximately  $125~\mu m$  outer diameter. Hence the fiber will protrude from the groove. The cap chip, made from silicon, was micromachined to account for this protrusion.

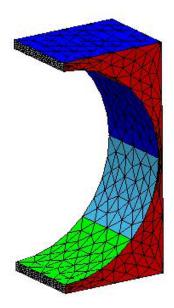

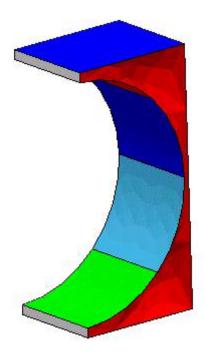

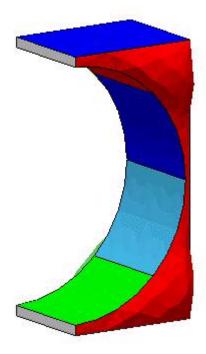

The channel dimensions in the DRIE die (Figure 2-1) must be optimized to meet two primary goals. The first goal is to house and provide passive alignment between the fiber and the MEMS structures. The second is to allow for the formation of a hermetic seal without the use of any fluxes. The use of flux with MEMS is undesirable from two standpoints 1) the surface tension of the flux is likely to cause stiction, and 2) residual matter from the flux is difficult to remove from or between the MEMS structures. The passive alignment structures have been used in the S&A since 1997 and are not within the scope of this research [16]. Provisions were made for the passive alignment structures to ensure complete process compatibility. These designs were directly imported into a layout created strictly for the present effort. To maximize die yield in the fabrication process, entire S&A chips were not fabricated. However, the test structures were fabricated using essentially the same processing techniques used to make the entire S&A to ensure future process compatibility.

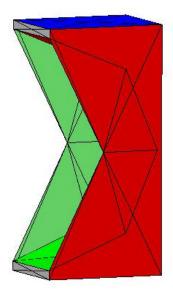

To facilitate the seal between the chips and between the fiber and chips, metal was patterned in a ring around the perimeter of the chips and in the DRIE grooves, respectively. There are three key elements to achieve a hermetic seal at these interfaces:

- Perimeter seal

- Metallization and solder deposition into the DRIE channel

- Reflow of solder in grooves

The perimeter seal is the most straightforward facet of the hermetic seal formation. The challenge in the perimeter seal lies in the criteria to form the seal without the use of fluxes. The impact of the decision to forgo the use of fluxes is discussed in detail in

Section 2.7. The process windows developed here represent the simplest case and does not address the need for the solder to move during reflow to fill voids. Rather, it provides a starting point for the conditions for fluxless soldering to be viable. The fluxless soldering process was demonstrated through a series of tests. First, bare indium wire was used to determine the process variables that govern the fluxless soldering process. Next, metallized chips with evaporated solder were bonded together and die sheared to assess the integrity of the bond in the process windows determined in the bare indium wire experiments.

In the second step the processing techniques had to be tuned to ensure a complete coating of the metallization onto the sidewall of the DRIE groove in the device layer.

The metallization has to cover the cap chip grooves as well, but this is not as challenging as the deeper trenched device chip. Complete coverage of the etched grooves with metal is the key to providing a wetable surface for the solder. Without complete metallization, the solder fails to wet the silicon and thus a hermetic seal is not obtained. In addition to depositing the metal in the fiber groove, the metal also has to overlap the perimeter seal ring to complete the continuous seal around the entire chip. After formation of the metallization ring around the chip, solder is deposited over the metallization to facilitate the formation of the hermetic seal. The solder could be applied via a preform, but batch fabrication techniques are preferred. Once a complete metallized groove is formed, solder will be deposited into the grooves and around the perimeter. The deposition technique for the solder is most likely shadow masked sputtering, as is discussed in more detail in

Section 2.6. The third step, discussed in Section 2.9, is to perform a complete reflow of the perimeter seal and optical interconnect.

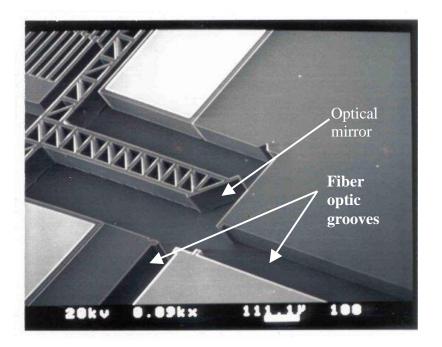

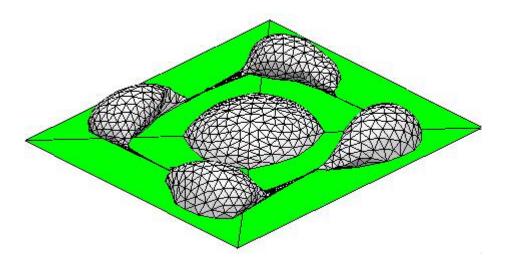

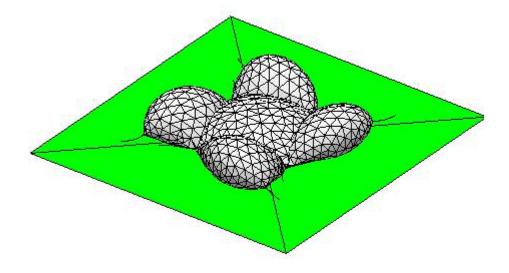

Figure 2-1: DRIE optical channels

The chip designs, device and cap, layouts were generated in AutoCAD and then transferred to L-edit (Tanner EDA) for mask production. The mask designs were sent to Cronos (JDS Uniphase) and John Hopkins University's Applied Physics Lab (JHU/APL) for review and fabrication. After a full review, CRONOS performed the DRIE portion of the fabrication and JHU/APL performed the metallization, indium deposition, and dicing.

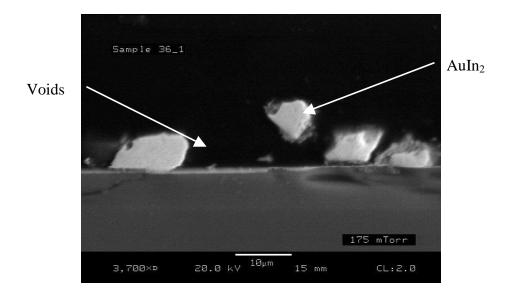

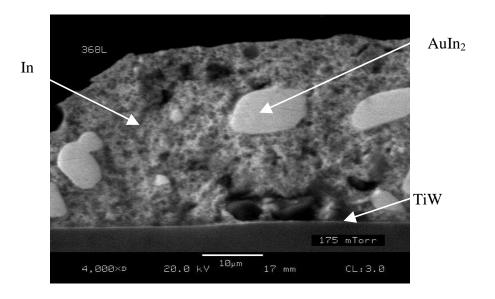

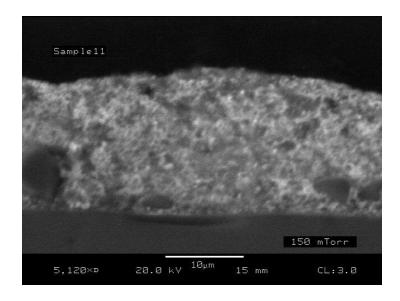

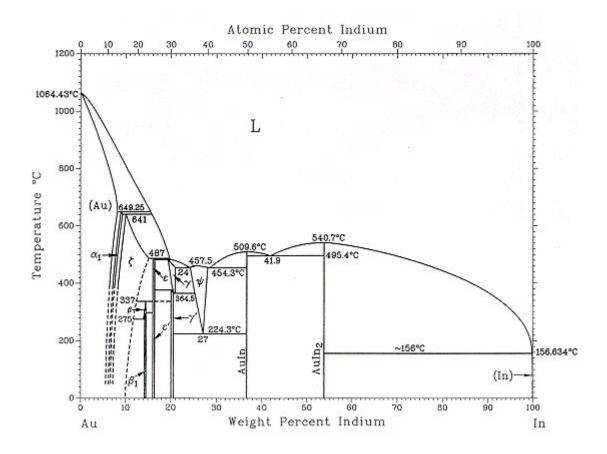

#### 2.2 Fiber