#### ABSTRACT

# Title of Thesis: EVALUATING THE IMPACT OF MEMORY SYSTEM PERFORMANCE ON SOFTWARE PREFETCHING AND LOCALITY OPTIMIZATIONS

Degree candidate: Abdel-Hameed A. Badawy

Degree and year: Master of Science, 2002

Thesis directed by: Professor Donald Yeung Department of Electrical and Computer Engineering

Software prefetching and locality optimizations are two techniques for overcoming the speed gap between processor and memory known as the memory wall as suggested by Wulf and Mckee [57]. This thesis evaluates the impact of memory trends on the effectiveness of software prefetching and locality optimizations for three types of applications: regular scientific codes, irregular scientific codes, and pointer-chasing codes. For many applications, software prefetching outperforms locality optimizations when there is sufficient bandwidth in the underlying memory system, but locality optimizations outperform software prefetching when the underlying memory system doesn't provide sufficient bandwidth. The break-even point, or equivalently the crossover bandwidth point, occurs at roughly 2.4 GBytes/sec, for 1 GHz processors on today's memory systems, and will increase on future memory systems. This thesis also studies the interactions between software prefetching and locality optimizations when applied in concert. Naively combining the two techniques provides a more robust application performance in the face of variations in memory bandwidth and/or latency, but does not yield additional performance gains. In other words, the performance won't be better than the best performance of the two techniques alone. Also, several algorithms are proposed and evaluated to better combine software prefetching and locality optimizations, including an enhanced tiling algorithm, padding for software prefetching, and index prefetching.

#### Evaluating the Impact of Memory System Performance on Software Prefetching and Locality Optimizations

by

Abdel-Hameed Abdel-Salam Badawy

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Master of Science 2002

Advisory Committee:

Professor Donald Yeung Professor Manoj Franklin Professor Chau-Wen Tseng

i

#### ACKNOWLEDGMENTS

This is going to be a long list of people to thank since prophet Muhammad said "Whoever is not thankful to people is not thankful to ALLAH(GOD)" so please bear with me.

I would like to thank Aneesh Agrawal for his efforts which helped me to finish this work leading to this thesis. Aneesh implemented the memory system model on top of SimpleScalar which was called sim-bw. He gave me a jump-start on the benchmarks and the simulator while he was an intern at DEC in summer of 2000. Also, I would like to thank all my lab-mates including [Choi, Dongkeun, Deepak, Gautham, Aamer, and Zahran] for their support during the deadlines of HPCA'2001 and ICS'2001. They are just a wonderful group of people to work nearby them.

Also, I am grateful to Gabe Rivera (professor Chau-Wen's student) who helped me understand his work on tile selection techniques and for his willingness to discuss his work with me. Also, I would like to thank Hansoo Han for giving us his locality optimized code for the irregular array benchmarks.

I would like to thank professor Chau-Wen for his suggestions, guidance, and support. He really has a great inertia to put work together. I learnt from him never to give up submitting papers to conferences no matter what and never give up. I learnt from him to always think positively and work as fast as possible.

At last but not least, I would also like to thank my advisor, professor Donald Yeung. I appreciate very much his valuable contributions to my understanding of computer architecture at large and to the topics covered in this thesis, and specifically my experience as a graduate student under his supervision. He deserves much more than what I can say here.

I would also like to thank my family for their love support, encouragement and supplications. I would love thank my wife for her continual support in every way possible. Also, I would like to thank her family for their supplications and love.

Finally, I thank GOD, or equivalently ALLAH in Arabic, the all mighty who have given human beings countless blessings. To name one, our ability to do research and to ask and answer questions that lead humanity to prosper and flourish. All the praise and thank are due to the LORD of the whole universe. Allah the self-sufficient master, whom all creatures need and needs none of them. The one who begets not, nor was he begotten and there is none co-equal or comparable unto him.

### Contents

| LIST OF FIGURES v |                                                                                                                                                                                                                                                                                    |                                                                                                |  |  |  |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| LIST OF TABLES    |                                                                                                                                                                                                                                                                                    |                                                                                                |  |  |  |  |  |  |  |  |  |

| ABBREVIATIONS vii |                                                                                                                                                                                                                                                                                    |                                                                                                |  |  |  |  |  |  |  |  |  |

| 1                 | Introduction1.1The Memory Wall1.2Introducing Software Prefetching1.3Introducing Locality Optimization1.4Thesis Organization                                                                                                                                                        | <b>1</b><br>1<br>3<br>7<br>8                                                                   |  |  |  |  |  |  |  |  |  |

| <b>2</b>          | Related Work                                                                                                                                                                                                                                                                       | 11                                                                                             |  |  |  |  |  |  |  |  |  |

| 3                 | 3.1       Affine Array Accesses         3.2       Indexed Array Accesses         3.3       Pointer-Chasing Accesses         3.3       Pointer-Chasing Accesses         Software Prefetching         4.1       Affine Array Prefetching         4.2       Indexed Array Prefetching | <ol> <li>15</li> <li>17</li> <li>19</li> <li>21</li> <li>22</li> <li>25</li> <li>28</li> </ol> |  |  |  |  |  |  |  |  |  |

| 5                 | 5.1Tiling for Affine Accesses5.2Reordering for Indexed Accesses                                                                                                                                                                                                                    | <b>32</b><br>33<br>35<br>38                                                                    |  |  |  |  |  |  |  |  |  |

| 6                 | 6.1Methodology6.2Varying Memory Bandwidth6.3Varying Memory Latency                                                                                                                                                                                                                 | 40<br>40<br>45<br>53<br>58                                                                     |  |  |  |  |  |  |  |  |  |

| 7  | Algorithm Enhancements |                                           |    |  |  |  |  |  |

|----|------------------------|-------------------------------------------|----|--|--|--|--|--|

|    | 7.1                    | Enhancing Tiling for Software Prefetching | 65 |  |  |  |  |  |

|    | 7.2                    | Padding for Software Prefetching          | 70 |  |  |  |  |  |

|    | 7.3                    | Index Prefetching                         | 75 |  |  |  |  |  |

| 8  | Con                    | clusion                                   | 79 |  |  |  |  |  |

| 9  | Future Work            |                                           |    |  |  |  |  |  |

| BI | BIBLIOGRAPHY           |                                           |    |  |  |  |  |  |

### List of Figures

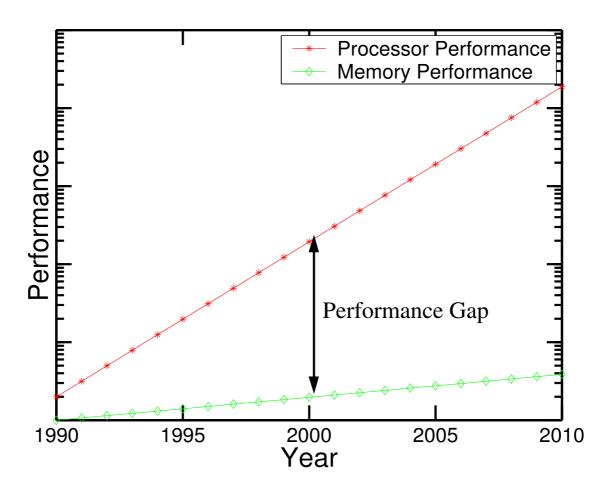

| 1.1 | Comparison of processor performance to memory performance over time.                                                                                                                                                                                         | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

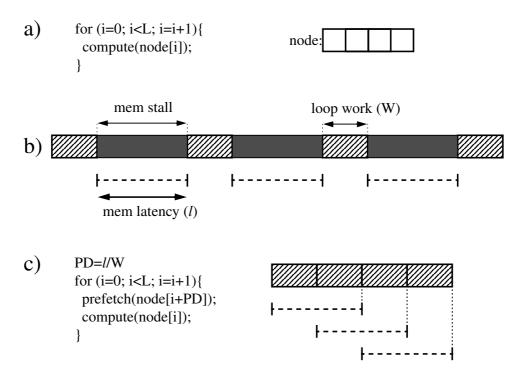

| 1.2 | Array traversal. a) Code with data structure. b) Time-line without                                                                                                                                                                                           |    |

| 1.0 | prefetching. c) Code and time-line with prefetching.                                                                                                                                                                                                         | 5  |

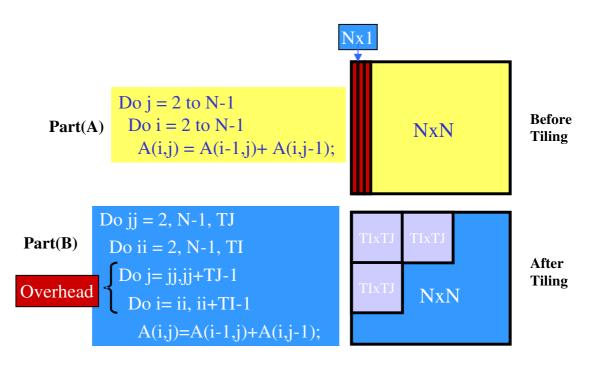

| 1.3 | Example Locality Optimization (Tiling). Part(A) Original code without any optimizations. Part(B) Tiled code                                                                                                                                                  | 7  |

| 3.1 | Example of 3 different access patterns. Part(A) Affine Array Access example code. Part(B) Indexed Array Access example code.                                                                                                                                 |    |

|     | Part(C) Pointer-Chasing Access example code.                                                                                                                                                                                                                 | 16 |

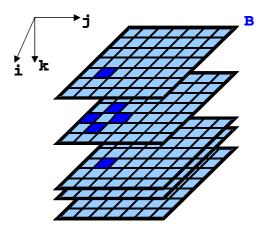

| 3.2 | The computation order and direction of progress in 2D JACOBI                                                                                                                                                                                                 | 17 |

| 3.3 | The computation order and direction of progress in 3D JACOBI                                                                                                                                                                                                 | 17 |

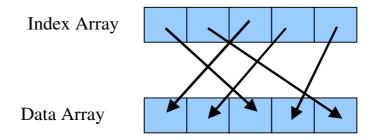

| 3.4 | Showing the relationship between the index and indexed arrays be-                                                                                                                                                                                            |    |

|     | fore inspector-executor runs                                                                                                                                                                                                                                 | 18 |

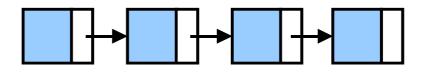

| 3.5 | Chasing pointers to access list nodes                                                                                                                                                                                                                        | 19 |

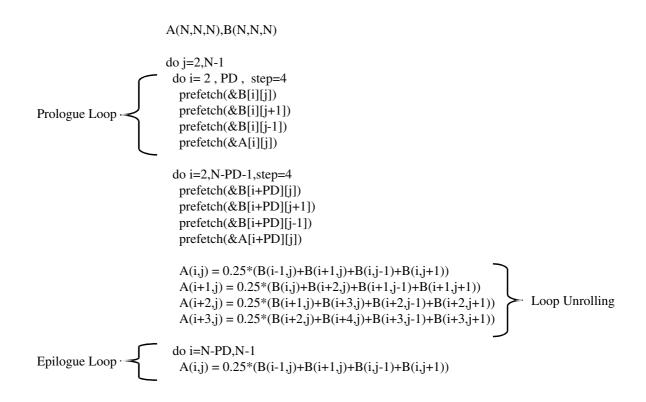

| 4.1 | Example affine array prefetching for the 2D Jacobi kernel using Mowry's algorithm [38]. The prefetch algorithm involves three steps:                                                                                                                         |    |

| 4.2 | loop unrolling, prefetch scheduling, and loop peeling Example indexed array prefetching for a molecular dynamics kernel using the algorithm in [38]. The prefetch algorithm is similar to the algorithm for affine arrays, with several extensions to handle | 23 |

| 4.3 | indexed arrays                                                                                                                                                                                                                                               | 26 |

|     | arrays. Part(B) shows the prefetch pointer initialization code                                                                                                                                                                                               | 29 |

| 4.4 | Jump Pointers inserted into the list nodes.                                                                                                                                                                                                                  | 29 |

| 4.5 | Prefetch Array pointers labelled "P" added to the list nodes already                                                                                                                                                                                         |    |

|     | having jump pointers                                                                                                                                                                                                                                         | 30 |

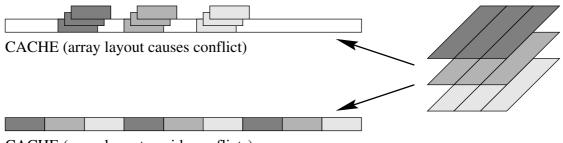

| 5.1 | Example of conflict misses under two array layouts                                                                                                                                                                                                           | 33 |

| 5.2 | Example Locality optimized codes for affine array, indexed array                                                                                                                                                                                             | -  |

|     | and pointer-chasing codes.                                                                                                                                                                                                                                   | 33 |

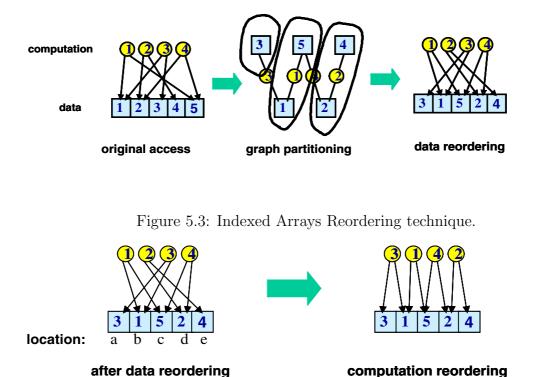

| 5.3 | Indexed Arrays Reordering technique.                                                                                                                                                                                                                         | 36 |

| 5.4 | Indexed Array computation reordered after the reordering operations.                                                                                                                                                                                         | 36 |

|     |                                                                                                                                                                                                                                                              |    |

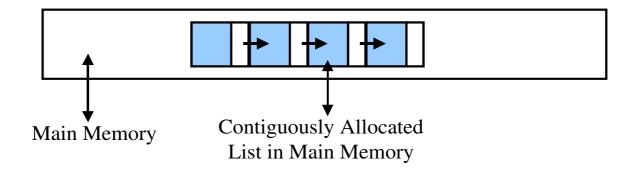

| 5. | 5 | Ι | lin | ıke | d | list | cont | tigu | ousl | v | alle | ocat | ed | in | Main | Μ | emor | v. |  |  |  |  | -39 | ) |

|----|---|---|-----|-----|---|------|------|------|------|---|------|------|----|----|------|---|------|----|--|--|--|--|-----|---|

|    |   |   |     |     |   |      |      | 0    |      |   |      |      |    |    |      |   |      | /  |  |  |  |  |     |   |

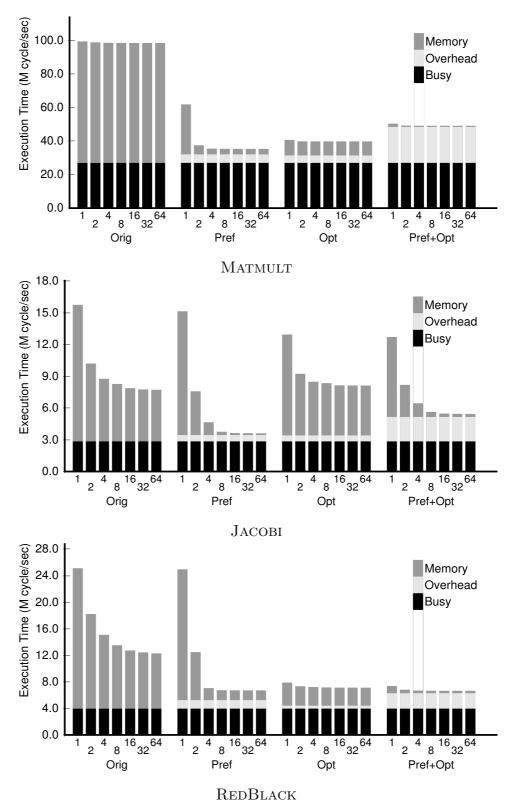

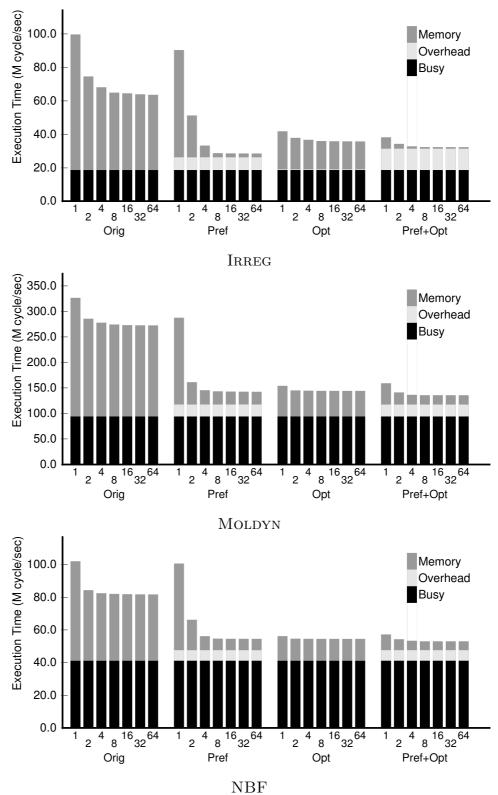

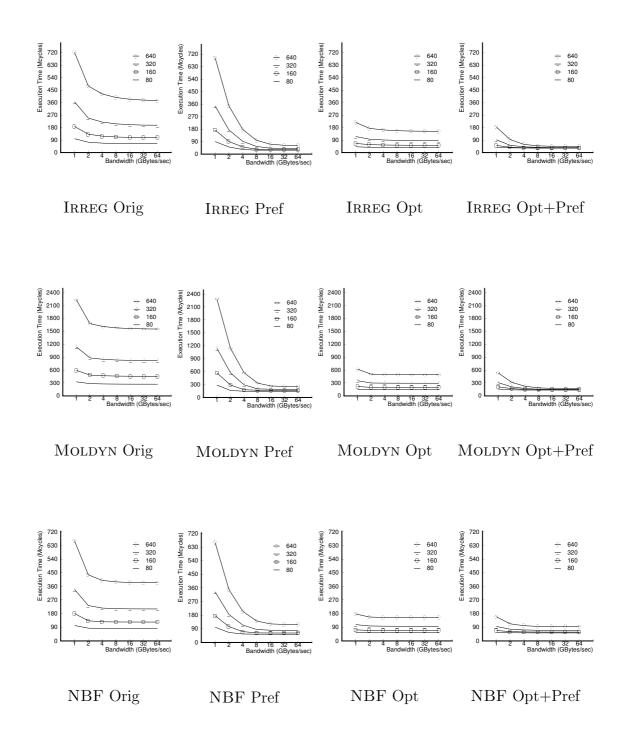

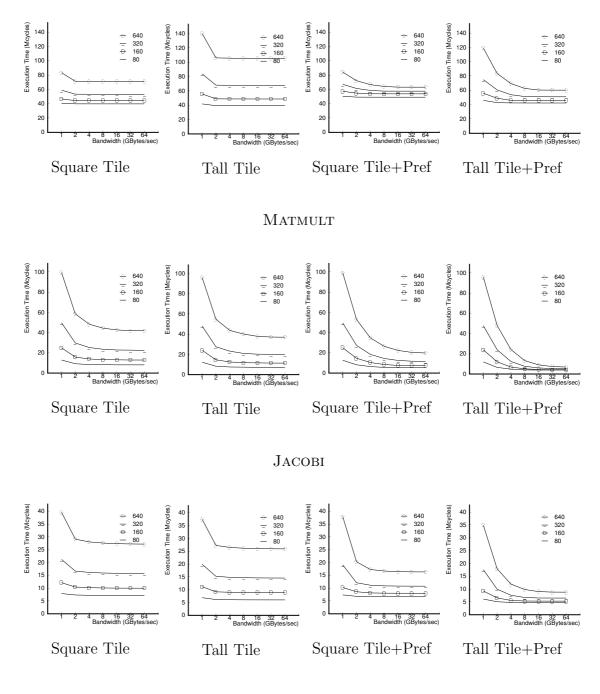

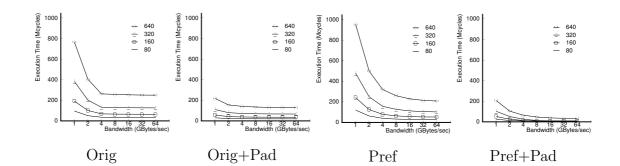

- 6.1 Affine Array applications execution time breakdown under memory bandwidth scaling with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations(Opt+Pref). Memory latency is fixed at 80 cycles. 46

- 6.2 Indexed Array execution time breakdown under memory bandwidth scaling with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations(Opt+Pref). Memory latency is fixed at 80 cycles. . . . 47

- 6.3 Pointer-chasing applications execution time breakdown under memory bandwidth scaling with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations(Opt+Pref). Memory latency is fixed at 80 cycles. 48

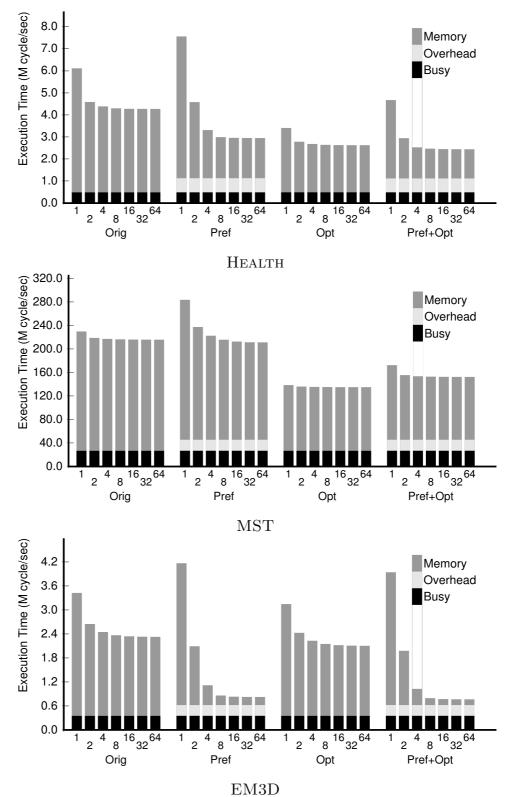

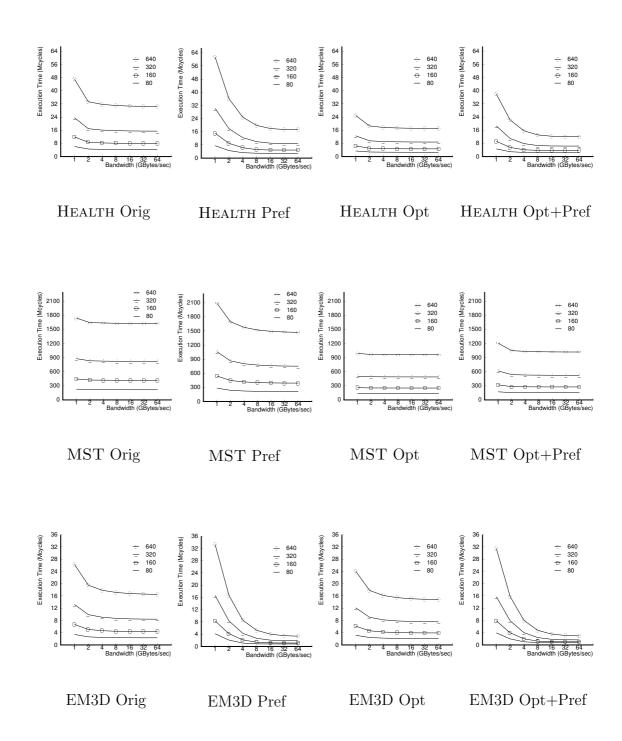

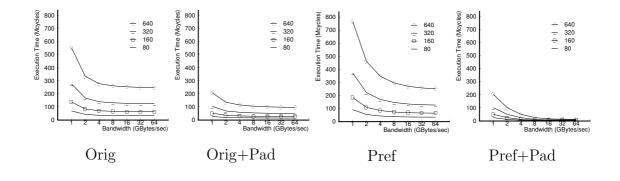

- 6.5 Execution time under both memory bandwidth and latency scaling for indexed array and pointer-chasing benchmarks with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations (Opt+Pref). 55

- 6.6 Execution time under both memory bandwidth and latency scaling for indexed array and pointer-chasing benchmarks with no optimizations (Orig), with software prefetching (Pref), with locality optimization (Opt), and with combined optimizations (Opt+Pref). 56

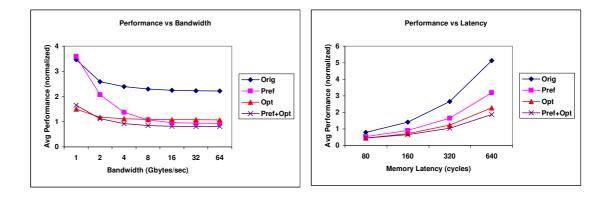

- 6.7 Comparing average performance for different versions of programs relative to memory bandwidth and latency. Performance is normalized relative to the original program with 1 Gbyte/sec bandwidth and 80 cycle latency.

63

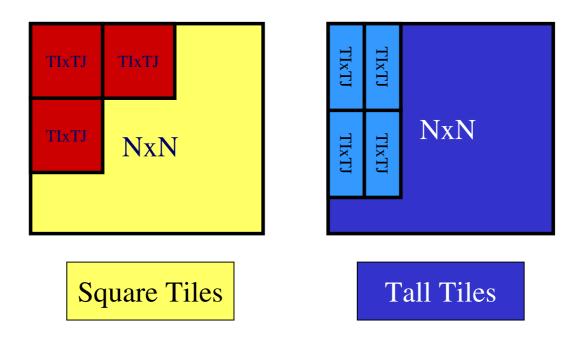

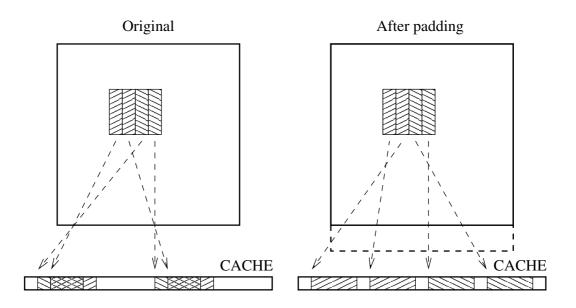

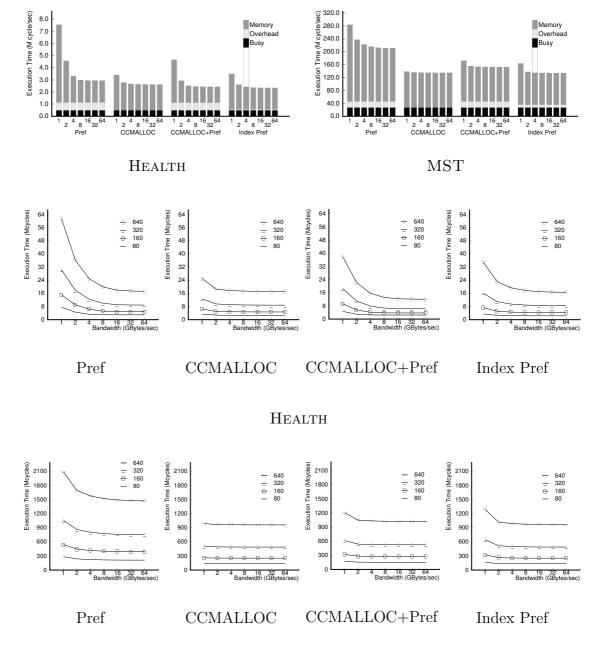

- 7.1Two configurations one with square tiles and one with tall tiles. . . 66 7.2Comparing square tiles and tall tiles with and without prefetching. 69 7.3Layout of Data in the Cache before and after padding. . . . . . . 717.4737.5Comparing index prefetching (Index Pref) to prefetch arrays (Pref), CCMALLOC memory allocation (CCMALLOC), and combined optimizations (CCMALLOC+Pref). In the top two graphs, memory

latency is fixed at 80 cycles.

77

### List of Tables

| 6.1 | Benchmark summary.                                                      | 41 |

|-----|-------------------------------------------------------------------------|----|

| 6.2 | Prefetch distances for REDBLACK, JACOBI and MATMULT for the             |    |

|     | different latencies                                                     | 44 |

| 6.3 | Prefetch distances for IRREG, MOLDYN and NBF for the different          |    |

|     | latencies                                                               | 44 |

| 6.4 | Prefetch distances for HEALTH, MST and EM3D for the different           |    |

|     | latencies                                                               | 44 |

| 6.5 | Equi-performance bandwidths for 80, 160, 320, and 640-cycle mem-        |    |

|     | ory latencies. The last column reports the average over the 9 bench-    |    |

|     | marks. All memory bandwidths are in Gbytes/sec                          | 50 |

| 6.6 | Prefetch distances for the combined version of REDBLACK, JACOBI         |    |

|     | and MATMULT for the different latencies                                 | 58 |

| 6.7 | Prefetch distances for the combined version of IRREG, MOLDYN and        |    |

|     | NBF for the different latencies.                                        | 59 |

| 6.8 | Prefetch distances for the combined versions of HEALTH, MST and         |    |

|     | EM3D for the different latencies.                                       | 59 |

| 7.1 | Tile sizes for square and tall-tile versions of the affine array bench- |    |

|     | marks.                                                                  | 67 |

| 7.2 | Prefetch distances for REDBLACK, JACOBI and MATMULT for the             | 0. |

|     | different latencies with tall tiles applied.                            | 68 |

| 7.3 | The prefetch distances for the padded versions of REDBLACK and          |    |

| -   | JACOBI.                                                                 | 71 |

|     |                                                                         |    |

#### ABBREVIATIONS

| ISA                     | Instruction Set Architecture                                                               |

|-------------------------|--------------------------------------------------------------------------------------------|

| L1                      | Level 1                                                                                    |

| L2                      | Level 2                                                                                    |

| KB                      | Kilobyte (1024 Bytes)                                                                      |

| MB                      | Megabyte (1024 Kilobytes)                                                                  |

| PD<br>JPP<br>PDE<br>AVG | Prefetch Distance<br>Jump Pointer Prefetching<br>Partial Differential Equations<br>Average |

| MM                      | Matrix Multiply                                                                            |

| Jac                     | Jacobi                                                                                     |

| RB                      | RedBlack                                                                                   |

| Irreg                   | Irregular Mesh Solver                                                                      |

| Mol                     | Moldyn                                                                                     |

| Health                  | Columbian Health Simulation                                                                |

| MST                     | Minimum Spanning Tree                                                                      |

| gpart                   | Graph Partitioning                                                                         |

| rcb                     | Recursive Coordinate Bisection                                                             |

| Orig                    | Original Code                                                                              |

| Pref                    | Code instrumented with Prefetching                                                         |

| Opt                     | Code instrumented with the appropriate Locality Optimization Technique                     |

Pref+Opt Code instrumented with both Prefetching and Locality Optimization

## Chapter 1 Introduction

#### 1.1 The Memory Wall

The performance of microprocessors continues to improve at an impressive pace. In fact, microprocessor performance increases by 58% per year. However, memory system performance improves by only 7% in the same amount of time [23], leading to an exponential increase in the *processor-memory performance gap* [57]. In the early 1980's, memory systems were fast enough to keep up with processors. Unfortunately, since processor and memory performance increase at different exponential rates, their difference in performance increases exponentially. Figure 1.1 illustrates how extreme this problem is, plotting both memory and processor performance over time. The time axis is on a linear scale; however, the performance axis is on a logarithmic scale. Figure 1.1 shows that processor performance is a factor of 100 higher than memory performance in 2000, and it will reach a factor of 5000 in 2010.

The most effective known solution to alleviate this problem is to use caches. Caches are small, fast memories that store recently accessed data. The

Figure 1.1: Comparison of processor performance to memory performance over time.

principle of temporal locality states that once data is accessed, it is likely to be accessed again in the near future. Therefore, data will likely be accessed multiple times and only need to be retrieved from main memory the first time it is accessed. This allows successive accesses to be satisfied from the faster cache, effectively reducing the average latency required to access data. However, since caches are limited in size, they do not in all cases have enough capacity to fit the application's working set especially for large applications. Also, some applications do not have sufficient temporal locality to allow caches to reduce the average latency of a data access. Consequently, while caches are typically effective, they do not completely address the memory gap problem.

When a processor accesses data from main memory, it must wait for the memory system to retrieve the data. This is called a memory stall. As the processor-memory performance gap continues to widen, memory stalls increase and application performance becomes increasingly limited by the memory system performance. Other techniques are required to fully address the memory wall problem. The rest of this Chapter introduces two existing techniques, software prefetching and data locality transformations.

#### 1.2 Introducing Software Prefetching

Two promising approaches for improving memory performance are *software prefetching* and *locality optimizations*. This section briefly introduces software prefetching. Software prefetching executes explicit prefetch instructions to initiate loading data from memory to cache early. Prefetching works by pre-loading data from memory before the processor requests it so that it is ready when the processor performs the access, thus hiding the latency of the memory access from the processor. Prefetching can be controlled in either hardware or software. In this thesis, software prefetching is considered. In software prefetching, the compiler identifies loops that are likely to cause frequent cache misses, and inserts prefetch instructions into the application loop code to prefetch the data in advance of its use. The compiler does this by pairing each LOAD instruction with a PREFETCH instruction that prefetches data to the cache. Scheduling is done for the PREFETCH instruction so that the data is available to the processor when it is requested.

When data is prefetched, it is loaded from memory and put into cache [7, 34] or a special buffer called a *prefetch buffer* [28, 47]. When data is prefetched into a prefetch buffer, it is moved into the L1 cache when it is referenced by the processor. This prevents inaccurately prefetched data from polluting the cache and thus evicting useful cache blocks. In this thesis, prefetching into the L1 cache is considered only. Figure 1.2a illustrates software prefetching using a simple code example. This code sequentially loads data from an array, shown on the right side of Figure 1.2a, and performs some computation on each array element. Figure 1.2b shows the execution time-line for the array traversal in Figure 1.2a. It shows that most of the execution time is spent in memory stall. With Prefetching shown in Figure 1.2c, each element of the array can be preloaded to avoid memory stalls and thus the latency is hidden underneath the execution of the loop computations. On each loop iteration, the

4

Figure 1.2: Array traversal. a) Code with data structure. b) Time-line without prefetching. c) Code and time-line with prefetching.

array element accessed PD loop iterations ahead is prefetched. The value PD is referred to as the *prefetch distance*, and determines how far ahead (in terms of loop iterations) to prefetch data from memory. In other words, PD determines the number of loop iterations necessary to hide the latency of one array element access. Figure 1.2c also shows the execution time-line for the array example with a prefetch distance of two.

The code shown in Figure 1.2c does not prefetch the first PD elements of the array because the first element prefetched is node[0+PD]. To address this problem, a prologue loop is added to the code just before the traversal code loop (not shown in Figure 1.2). The prologue loop prefetches the first PD elements of the array without performing any computation on the data itself. The time-line in Figure 1.2c is shown for "steady state" iterations only, so it doesn't show the prologue loop prefetches. The value of the prefetch distance, PD, is computed according to Equation 1.1

$$PD = \lceil l/W \rceil \tag{1.1}$$

where l is the memory latency and W is the amount of work per loop iteration. Unfortunately, the values of l and W are not exactly known at compile time. The value of l depends on whether data is found in the L1 cache, L2 cache, or main memory. The value of W varies if there are conditional statements in the loop body. Since both l and W are not constant, typically worst case values are chosen. Also, note that PD must be rounded up to the nearest whole number, thus we use the ceiling in the equation for the prefetch distance. Both conservative estimates of the prefetch distance and roundoff error can result in PD being too high and data being prefetched too early. The problem with early prefetches is that the data being pre-loaded to the cache may be evicted before it is consumed by the processor.

Prefetching is effective only if sufficient memory bandwidth exists to transfer all prefetched data in time. If the memory system cannot transfer the data fast enough, memory stalls will remain unresolved and degrade overall performance. As processor speeds increase, memory bandwidth requirements increase too since the processor will consume data at a faster pace, requiring the memory system to supply data more rapidly in order to avoid stalling the processor.

Figure 1.3: Example Locality Optimization (Tiling). Part(A) Original code without any optimizations. Part(B) Tiled code.

#### **1.3 Introducing Locality Optimization**

In comparison to prefetching outlined in the previous section, locality optimizations use compiler or run-time transformations to change the computation order and/or data layout of a program to increase the locality of the processor's memory access patterns, improving the probability that the processor accesses data that is already in the cache. Thus locality optimizations are not latency tolerance techniques like prefetching. Instead, they are latency reduction techniques since they use compiler or run-time transformations in order to make better use of the data that is already present in the cache.

Figure 1.3 illustrates a particular form of locality optimization called tiling [14, 29, 30, 42, 44]. This technique is particularly useful for statically allocated regular arrays. Figure 1.3 part(A) illustrates a two dimensional version of the Jacobi code. The original computation proceeds down the columns of the array. Since the computation of each array element uses neighboring values along rows, there is reuse across outer loop iterations. Unfortunately, this reuse cannot be exploited unless multiple columns fit in the cache simultaneously, which does not occur for large arrays or small caches. The locality optimization algorithm is applied to the loop either by hand or the compiler.

Figure 1.3 part(B) illustrates JACOBI code with tiling. Two more loops are inserted to force the computation to go tile by tile, exploiting reuse along rows and columns more effectively. This causes the number of cache misses and the amount of traffic moved from memory to cache to go down, thus improving the overall system performance. In effect, locality optimization techniques increase the reuse of the data that is already in the cache so that when it gets evicted it will not be used again later since the application has exhausted this piece of data for all the computations that needs this piece of data. In general, when locality optimization techniques are applied to a specific application and it turns out to be successful, both average memory latency and bandwidth usage are reduced. On the negative side, the additional loops inserted by tiling introduce overhead, similar to the overhead that prefetch instructions introduce in software prefetching.

#### 1.4 Thesis Organization

Both software prefetching and locality optimizations have been studied in isolation. This thesis conducts an in-depth evaluation that compares the two techniques under different memory system design points. The evaluation uses benchmarks from three broad classes of data-intensive applications. In addition, the evaluation uses a single unified simulation environment based on the Simple-Scalar tool set [5] with a detailed memory system to enable a meaningful comparison. The primary focus of the work is to compare the importance of *latency tolerance* provided by software prefetching and *latency reduction* provided by locality optimizations on future high-performance memory systems. The work also investigates the interactions of software prefetching and locality optimizations when applied in concert both naively and then with some enhancements to increase the effectiveness of their combination.

The contributions of this thesis are as follows:

- Compare the efficacy of software prefetching and locality optimizations for three types of data-intensive applications in terms of performance.

- Quantify the impact of memory system parameters, such as bandwidth and latency, in future memory systems on the relative effectiveness of software prefetching and locality optimizations.

- Examine the performance of integrated software prefetching and locality optimizations, then propose and evaluate several enhancements to increase their combined performance.

The rest of this thesis will be organized as follows. First, related work is discussed in Chapter 2. Second, the three memory access patterns are explained

in Chapter 3. Then, different optimizations for each access pattern is discussed. Chapter 4 discusses software prefetching optimizations. Chapter 5 discusses locality optimizations. The experimental results are presented in Chapter 6. Improved algorithms are discussed in Chapter 7. Chapter 8 presents the conclusions. Finally, Chapter 9 discusses the future extensions to this thesis.

## Chapter 2 Related Work

This thesis is similar to Saavedra *et al* [49], in which they evaluated unimodular transformations, tiling, and software prefetching for matrix multiply only using a cache simulator as their measurement environment. Mowry *et al* [39] evaluated software prefetching and tiling for two scientific applications. This thesis is focused on memory system parameters scaling and quantification of their impact on software prefetching and locality optimizations. The previous works have considered only a fixed technology point. Furthermore, 3 classes of benchmarks are studied in this thesis requiring different types of optimizations. New enhancements are proposed to better combine software prefetching and locality optimizations, as well as an enhancement to software prefetching when applied to array-based benchmarks. The experimental evaluation methodology used is a detailed execution-driven simulator for a modern processor and memory system.

Most of the work done before has been devoted to the study of the two techniques in isolation, and little work has been done to study the combined techniques. To our knowledge, the only one to do this is Saavedra *et al* [49]. The conclusions in that paper were negative. They concluded that the combination suffers degradation in performance due to destructive interference but didn't suggest anything to address the problem.

Software prefetching for affine array accesses has been studied in [37, 28, 7] as will be described in detail in Section 4.1. Hardware prefetching [10, 41, 19, 18, 26] uses hardware to identify the access pattern automatically. Prefetch engines for affine array accesses [53, 9, 13, 11] provide hardware support for prefetching, but rely on the programmer or compiler to identify the access pattern, *i.e.* the hardware itself doesn't detect the access pattern automatically like hardware prefetching. Intel and AMD are both having some hardware prefetching techniques in their latest processors (Pentium 4 and Athlon 4 chips) [33, 24].

Prefetching for pointer-chasing traversals uses one of four approaches. The first approach inserts additional pointers, called *jump pointers*, into the data structure of the application to connect non-consecutive list elements [27, 48, 32], as will be described in detail in Section 4.3. The second approach uses natural pointers for prefetching [47, 34, 32]. This technique prefetches pointer chains sequentially, but schedules each prefetch as early in the loop iteration as possible to maximize memory latency overlap. The third approach uses a hardware table, called a *Markov predictor* [25], to predict link node addresses for prefetching. Finally, the fourth approach uses a special allocation technique to allocate nodes contiguously in memory which enables indexed access to the list nodes. This approach was first proposed in [32] and is called *data linearization prefetching*.

12

evaluated in Section 7.3.

Data locality has been studied extensively in the literature. Computation-reordering transformations such as loop permutation and tiling are the primary optimization techniques [56]. Chapter 5 will discuss these techniques in greater detail. Data layout optimizations such as padding and transpose have been shown to be useful in eliminating conflict misses and improving spatial locality [43]. Padding is studied as an enhancement to software prefetching in Section 7.2. Several cache miss estimation techniques have been proposed to help guide data locality optimizations [20, 56]. Tiling has been proven useful for linear algebra codes [30, 56, 14] and multiple loop nests across time-step loops [51]. In comparison, tiling for 3D stencil codes is applied in these benchmarks which cannot be tiled with existing methods. Tiling for 3D and 2D arrays is discussed in detail in Section 5.1.

Researchers have examined irregular computations mostly in the context of parallel computing, using the run-time [16] or compiler [31] to support accesses on message-passing multiprocessors. A few have also looked at techniques for improving locality [1, 17]. The techniques for irregular computations are discussed in detail in Section 5.2.

Few researchers have investigated data layout transformations for pointer-based data structures. Chilimbi *et al.* investigated allocation-time and run-time techniques to improve locality for linked lists and trees [12]. Further extensions are introduced in this work to use this technique in conjunction with software prefetching. Also, index prefetching utilized this allocation methodology as discussed later in Section 7.3. Calder*et al.* use profiling to guide layout of global and stack variables to avoid conflicts [6]. Carlisle *et al.* investigate parallel performance of pointer-based codes in Olden [8].

## Chapter 3 Memory Access Patterns

The type of software prefetching and locality optimizations to use depend on the memory access pattern of the application code. This Chapter discusses three common memory access patterns that occur in the benchmarks used by this thesis. In the following sections, affine array accesses, indexed array accesses and pointer-chasing accesses are discussed.

#### **3.1** Affine Array Accesses

Affine array access is the most basic access pattern. This pattern arises when traversing arrays, as shown in Figure 3.1 Part(A). This figure shows the 2D JACOBI code. All the array elements accessed are statically known at compile time since the indices of the arrays are linear functions of the loop induction variable. The access pattern used in the 2D JACOBI code fragment is usually called a stencil. In a stencil, three columns are needed to perform the computation. It is necessary to have all three columns in the cache for high performance. Figure 3.2 shows the computation elements and how the computation progresses in the array. 3D solvers suffer from very bad cache

| // Affine Array Accesses | // Indexed Array Accesses         | // Pointer-Based Structures              |

|--------------------------|-----------------------------------|------------------------------------------|

| // (2D Jacobi Kernel)    | // (Molecular Dynamics)           | // (Linked List Traversal)               |

| A(N,N,N),B(N,N,N)        | X1(M), X2(M), index(N)            | <pre>struct node {val, next} *ptr;</pre> |

| do j=2,N-1               | do $t = 1$ , time                 | while () {                               |

| do i=2,N-1               | do $i = 1, N$                     | <pre>ptr-&gt;next = malloc(node);</pre>  |

| A(i,j) = 0.25 *          | d = X1(index(i))-X2(index(i))     | ptr = ptr -> next;                       |

| (B(i-1,j)+B(i+1,j)+      | force = $d^{**}(-7) - d^{**}(-4)$ | ptr->val = ;                             |

| B(i,j-1)+B(i,j+1))       | X1(index(i)) += force             | }                                        |

|                          | X2(index(i)) += -force            | while (ptr->next){                       |

|                          |                                   | ptr = ptr->next;;                        |

|                          |                                   | }                                        |

| Part(A)                  | Part(B)                           | Part(C)                                  |

Figure 3.1: Example of 3 different access patterns. Part(A) Affine Array Access example code. Part(B) Indexed Array Access example code. Part(C) Pointer-Chasing Access example code.

performance [4, 52, 55]. A version of JACOBI extended to 3 dimensions is shown in Figure 3.3. This figure shows a pictorial image of the computation order. The dark squares are the neighboring elements that are averaged. The computation averages 6 elements: 4 in the main plane and one element for each plane above and below the main plane as shown in the figure. For high performance in this case, the cache needs to hold three entire  $N \times N$  planes. Assuming double precision data and a write-through cache so that array A doesn't interfere with B, a 16K Byte L1 cache can hold a 3D array of size  $26 \times 26 \times M$ , where M is the third dimension of the array which can be any number. As the problem size increases the problem gets worse. In comparison, the same sized cache can hold data up to  $682 \times M$  array in case of a 2D version of JACOBI.

Affine array accesses are common in dense-matrix codes such as linear algebra and PDE solvers. Such access patterns can also be found in image

Figure 3.2: The computation order and direction of progress in 2D JACOBI.

Figure 3.3: The computation order and direction of progress in 3D JACOBI.

processing and signal processing codes; they are particularly common in DSP applications. An important feature of affine array accesses is that they allow

Figure 3.4: Showing the relationship between the index and indexed arrays before inspector-executor runs.

known. The data array, which is the main computation array, is indexed by another array which is called the *index array*. This pattern results in an irregular access pattern since the data array elements accessed depend on the contents of the index array.

Figure 3.1 Part(B) is a simple piece of code extracted from one of the applications that uses indexed arrays. The array named *index* is accessed in an affine manner similar to the arrays in the previous section. The two arrays X1 and X2 are indexed by the contents of the *index* array. The accesses are irregular due to the randomness of the data stored in the array *index*. The cache performance of applications using indexed arrays can be poor since both spatial and temporal locality in such applications is typically low due to the irregularity of the access pattern.

Figure 3.4 shows the relationship between the index array and the indexed "data" array. Unlike Affine array accesses, which can be improved using compile-time transformations, indexed array accesses cannot be improved at compile-time since the *index* array values are known only at run-time. To improve the performance of such applications, run-time transformations are

Figure 3.5: Chasing pointers to access list nodes.

required to change the access patterns dynamically.

#### 3.3 Pointer-Chasing Accesses

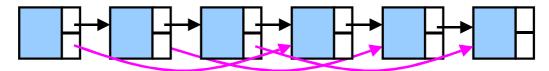

The third and final access pattern is pointer-chasing accesses. As the name suggests, this access pattern is characterized by pointer dereference operations. This results in an access pattern that is as random in nature as indexed arrays discussed above. Applications using linked lists, trees, and graph data structures are examples of codes that produce such access patterns.

Figure 3.1 Part(C) shows an example of creating and traversing a singly-linked list. The list nodes are dynamically allocated at run-time. The length of the list is usually a parameter that is known only at run-time. Figure 3.5 can be used to help describe the list access pattern. As shown in this figure, the list nodes are linked through pointers. To traverse the list, the pointers are dereferenced one after another in a serial manner. This access pattern cannot be analyzed by the compiler to improve its locality since the pointer locations are not known statically. Memory locations are known only at run-time which makes the locality optimizations of these types of codes possible at run-time only. Whereas, prefetching is not hindered by the fact that the memory location are not known at compile-time but is hindered by the fact that the accesses are inherently serial. In pointer-chasing codes, it is common for spatial and temporal locality to be low. Thus, the cache behavior of these applications can be poor. The pointer-chasing accesses force the accesses to be sequentialized since the next node cannot be accessed until the pointer pointing to that node is found in the current node. Pointer-chasing codes are quite common in applications such as databases, and advanced pointer-based data structures found in many applications.

## Chapter 4 Software Prefetching

Software prefetching is a well-known prefetching technique for pre-loading data into the cache from memory. Software prefetching relies on the programmer or the compiler to insert explicit prefetch "Pre-load" instructions and schedule them far enough in advance to hide or "tolerate" the latency of the memory accesses. The job of the compiler or the programmer is to identify memory accesses that are likely to miss in the cache, and to issue a prefetch for that piece of data to avoid stalls due to cache misses.

There exist several techniques to implement software prefetching for affine array codes [7, 28, 38, 37]. These techniques can be easily extended for indexed array codes [40]. Researchers have also proposed software prefetching techniques for pointer-chasing applications [27, 48, 47, 34, 32].

The advantage of software prefetching is that it is controlled by software and hence does not need much special hardware support. The only support needed is lockup-free caches which allow multiple outstanding misses, and ISA support in the form of a prefetch instruction. Consequently, software prefetching is relatively cheap compared to hardware prefetching. In this thesis, three software prefetching algorithms proposed previously in the literature for the three different memory access patterns described in Chapter 3 are studied both in isolation and in combination with the appropriate locality optimization technique. This chapter describes the three software prefetching algorithms.

#### 4.1 Affine Array Prefetching

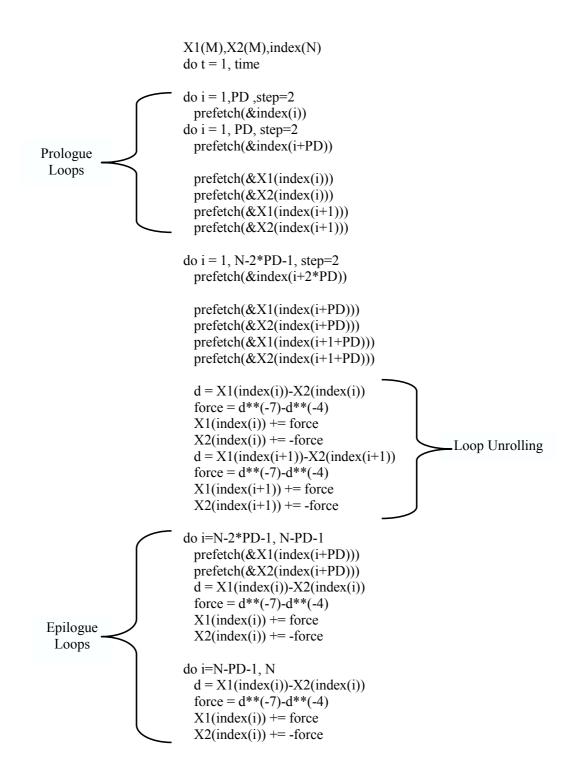

Affine array prefetching inserts prefetches for loops traversing affine arrays. The algorithm used is Mowry's algorithm [38]. In this thesis, Mowry's algorithm is applied by hand, even though it has been automated by a compiler. This algorithm prefetches only the missing data items. The algorithm is comprised of three steps. The first is to identify the instances of the data items that are going to miss in the cache. The second is to perform loop unrolling and loop splitting to isolate the memory references that will miss. The degree of loop unrolling is determined by the size of the data element and the size of the cache block. The third and final step is to schedule the prefetches such that they arrive in cache just prior to being accessed by the computation. The distance (in loop iterations) a prefetch instruction is scheduled before its consumption is called the *prefetch distance*. The 2D Jacobi kernel from Figure 3.1 Part(A) has been instrumented with Mowry's algorithm. The instrumented code appears in Figure 4.1. Figure 3.2 can be used to visualize the computation order and progress for 2D JACOBI.

The first step is to identify the references that will miss in the cache. The

Figure 4.1: Example affine array prefetching for the 2D Jacobi kernel using Mowry's algorithm [38]. The prefetch algorithm involves three steps: loop unrolling, prefetch scheduling, and loop peeling.

missing references are those in the innermost loops. Using compiler analysis to determine the locality of the data access pattern, the missing elements are identified. In the unrolling step, the loop is unrolled to expose the leading memory reference from each cache block that will cause a cache miss. Only the missing reference from a cache block is prefetched. When the prefetch comes back, the whole cache block will be brought to the cache and thus no further prefetch instructions for any of the elements belonging to that cache block are necessary. Thus, the loop unrolling step minimizes prefetch overhead since only one prefetch is issued per cache block.

The 2D JACOBI code in Figure 4.1 shows the prefetch instructions, loop unrolling, and the scheduling of the prefetch instructions. Each statement in the code reference four B array elements and one A array element. All elements referenced in the same statement lie in different cache blocks except for the two elements B(i-1,j) and B(i+1,j) which lie on the same cache block, thus an unnecessary prefetch is saved. The compiler or the programmer can figure out that only four prefetches are needed for each statement, assuming a data element size of 8 bytes and a 32-byte cache block. Hence the loop is unrolled four times.

Scheduling the prefetches is necessary since there isn't enough work in a single unrolled loop iteration under which to hide the memory latency. Thus, the prefetch instructions need to be issued some number of loop iterations in advance to give them enough slack to hide the cache miss. The distance in loop iterations necessary to hide a cache miss latency is called the *prefetch distance*. Computing the prefetch distance is done using the formula  $\lceil \frac{l}{w} \rceil$ ; l is the memory latency and

w is the work in one loop iteration, as mentioned in Chapter 1. Since every prefetch instruction needs to be scheduled exactly PD iterations ahead, a "prologue loop" should be inserted before the main computation loop to prefetch the first PD elements. Similarly, the last PD iterations will not need any prefetching. Thus, an "epilogue loop" needs to be inserted after the main loop computation to perform the last PD iterations without prefetching. The transformation to handle the first and last PD loop iterations in the prologue and epilogue loops is called "loop peeling".

Imagine a pipeline that executes the loop iterations. In such a pipeline, the prologue loop is filling up the pipeline with the first few data elements needed, and the *epilogue loop* executes the last PD iterations without prefetching, essentially draining the pipeline. Figure 4.1 illustrates the prologue and epilogue loops created by the loop peeling transformations.

#### 4.2 Indexed Array Prefetching

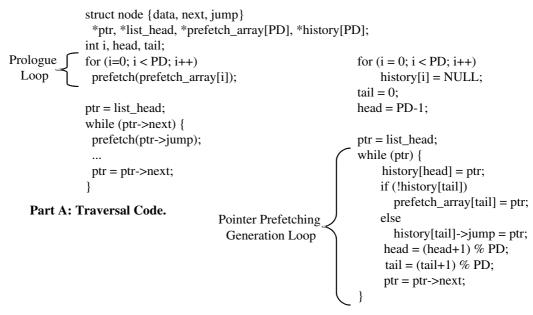

Indexed array accesses, of the form X1(index(i)), are very similar to affine array accesses except they have a single level of indirection since each reference is actually two references performed back to back. The algorithm used to instrument prefetching for indexed array accesses is also the Mowry algorithm [40]. Figure 4.2 shows a simplified molecular dynamics kernel (very similar to the MOLDYN, IRREG, and NBF benchmarks used in the performance evaluation) after all the necessary transformations have been applied.

The strategy is to prefetch two back-to-back (serialized) prefetches, one

Figure 4.2: Example indexed array prefetching for a molecular dynamics kernel using the algorithm in [38]. The prefetch algorithm is similar to the algorithm for affine arrays, with several extensions to handle indexed arrays.

for the index array value, and another for the data array value. The index array can be prefetched like the affine array case, as described in Section 4.1. Then, when the prefetch for that index array element completes, a prefetch for the data array can be issued using the index array data that came back. Thus, the index array prefetches should start PD iterations before the data array. In addition, two prologue and epilogue loops are required, as shown in Figure 4.2: one loop to start the index array prefetches before the data array, and one loop to start the data array prefetches. Then, the computations start.

Looking back at the pipeline example mentioned above in explaining how prefetching works, there are two prefetch pipelines with two different prefetch distances for indexed arrays. Thus, at the end of the computations, two epilogue loops are needed: one to prefetch the last PD entries of the data array while performing the computations for  $2 \times PD$  iterations before the end of the computations, and another final loop to perform only the remaining PDcomputations at the end of the array.

Loop unrolling is used to reduce the number of prefetches in the index array. Loop unrolling is not effective at reducing the prefetch overhead for the data array since the compiler cannot figure out which elements of the data array belong to the same cache block. Hence, the compiler must conservatively schedule a prefetch for every reference of the data array increasing the prefetch overhead for this array. The loop unrolling degree is 2 in Figure 4.2 only to limit the size of the example code. Thus, loop unrolling will help the index array only since it is treated as an affine array. The *prefetch distance* is computed in the

same way as affine array codes.

### 4.3 Pointer-Chasing Prefetching

Prefetching pointer-chasing accesses is the most challenging of the three prefetching techniques. The problem with pointer-chasing accesses is that the memory references performed along a pointer chain are inherently serial. As shown in Figure 3.5, each node of the list can be accessed only after all previous list node pointers have been dereferenced sequentially. The serial nature of pointer references is known as the *pointer-chasing problem*.

One promising technique for addressing the pointer-chasing problem is jump pointer prefetching [48, 32]. In this technique, the list data structure is modified to permit prefetching of list nodes further down the pointer chain without traversing the intermediate list nodes. Jump pointer prefetching instruments the list nodes with extra pointers, called jump pointers. As this name suggests, jump pointers point to some number of nodes down the list to permit access to later nodes. Similar to previous prefetching techniques, the distance between where a jump pointer originates and where it points to is the prefetch distance. Jump pointers break the sequentiality of the list node accesses. Computing the prefetch distance in jump pointer prefetching is the same as in other prefetching techniques.

Figure 4.3-Part A shows a "while" loop that has been instrumented with jump pointer prefetching. Figure 4.4 shows how prefetch pointers are inserted into a list, and how these prefetch pointers point to list elements further down

Part B: Prefetching Pointers Creation Code.

Figure 4.3: Example pointer prefetching for a linked list traversal using jump pointers and prefetch arrays [27]. Part(A) shows the traversal code instrumented with prefetching through jump pointers and prefetch arrays. Part(B) shows the prefetch pointer initialization code.

Figure 4.4: Jump Pointers inserted into the list nodes.

the list, this breaking the sequentiality of pointer accesses.

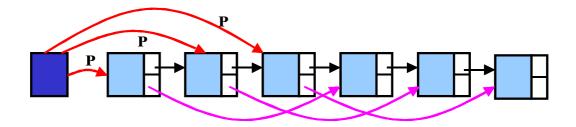

One problem with jump pointers is that there are no jump pointers pointing to the first PD nodes of the list. Thus, a technique is needed to help generate something similar to the prologue loop in affine and indexed arrays. This technique is called *prefetch arrays* [27]. In this enhancement to jump pointer prefetching, an array of pointers is constructed to point to the first PD elements of the list, and a "prologue loop" is added to prefetch the first PD elements

Figure 4.5: Prefetch Array pointers labelled "P" added to the list nodes already having jump pointers.

using the array of pointers. Figure 4.5 shows prefetch array pointers for the linked list example, and labels them with the letter "P". Figure 4.3-Part A shows the additional prologue loop code needed to issue prefetches through the prefetch arrays.

Before prefetching can start, the prefetch pointers must be set. Figure 4.3-Part B shows an example of prefetch pointer creation code which uses a history pointer array [32] to set the prefetch pointers. The history pointer array, called "history" in Figure 4.3-part B, is a circular queue that records the last PD link nodes traversed by the creation code. Whenever a new link node is traversed, it is added to the head of the circular queue and the head is incremented. At the same time, the tail of the circular queue is tested. If the tail is NULL, then the current node is one of the first PD link nodes in the list since PD link nodes must be encountered before the circular queue fills. In this case, we set one of the "prefetch array" pointers to point to the node. Otherwise, the tail's jump pointer is set to point to the current link node. Since the circular queue has depth PD, all jump pointers are initialized to point PD link nodes ahead, thus providing the proper prefetch distance. Normally, the compiler or programmer ensures the prefetch pointer initialization code gets executed prior to prefetching, for example on the first traversal of a linked list data structure. Furthermore, if the application modifies the linked data structure after the prefetch pointers have been initialized, it may be necessary to update the prefetch pointers either by re-executing the initialization code or by using other fix up codes, adding extra overhead to the pointer prefetching technique.

# Chapter 5 Locality Optimizations

Locality optimizations are the second technique to be evaluated in this thesis. This techniques are orthogonal to software prefetching. Software prefetching tries to hide the latency of references by issuing loads early for those references that are expected to miss in the cache. Locality optimizations try to change data layout and/or computation order of the programs so that the application's *data locality* is increased [56]. Data locality optimizations improve the application's data reuse which already exists but is not exposed. Changing the computation order and data layout of the program at compile and/or run-times exposes this data reuse.

Reuse comes in two forms. One is temporal reuse where data accesses to the same location of memory are repeated in time. Temporal reuse can be exploited by reordering the computations to finish all computations on a particular element before moving on to the next element. The second is spatial reuse where data accesses to nearby locations are performed together. Spatial reuse can be exploited by reordering the computations to perform computations on elements that are close in space before moving on to other computations.

CACHE (array layout avoids conflicts)

Figure 5.1: Example of conflict misses under two array layouts.

| $ \begin{array}{c} \textit{// Tiled 3D Jacobi} \\ A(N,N,N),B(N,N,N) \\ do \ kk=2,N-1,TK \\ do \ jj=2,N-1,TJ \\ do \ ii=2,N-1,TI \\ \hline \\ \textbf{Tiled} \\ \textbf{Loops} \\ \begin{array}{c} \text{do } k=kk,kk+TK-1 \\ do \ j=jj,jj+TJ-1 \\ do \ i=ii,ii+TI-1 \\ A(i,j,k) = 0.16667 \ * \\ (B(i-1,j,k) + B(i,j-1,k) + \\ B(i+1,j,k) + B(i,j+1,k) + \\ B(i,j,k-1) + B(i,j,k+1)) \end{array} $ | //Inspector-Executor for<br>//Molecular Dynamics<br>inspect_reorder(&E(2,N))<br>do t = 1, time<br>if (recalc)<br>E() =<br>do i = 1, N<br>d = X(E(1,i))-X(E(2,i))<br>force = d**(-7)-d**(-4)<br>X1(E(1,i)) += force<br>X2(E(2,i)) += -force | <pre>// Pointer-Based Structures // (Linked List Traversal) struct node{val, next} *ptr, *list; while () {     ptr-&gt;next = ccmalloc(node);     ptr = ptr-&gt;next;     ptr-&gt;val =; } while (ptr-&gt;next) {     ptr = ptr-&gt;next;; }</pre> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part(A)                                                                                                                                                                                                                                                                                                                                                                                            | Part(B)                                                                                                                                                                                                                                    | Part(C)                                                                                                                                                                                                                                            |

Figure 5.2: Example Locality optimized codes for affine array, indexed array and pointer-chasing codes.

In data locality optimizations, the compiler or run-time code examines the application to see what type of data locality can be exploited to improve the application's cache performance. Several data locality optimizations have been proposed in the literature. These optimizations target different access patterns. In the next three sections, locality optimizations for the three access patterns discussed earlier in Chapter 3 will be explained.

## 5.1 Tiling for Affine Accesses

Locality optimizations for affine array accesses are straightforward to apply because the access patterns can be analyzed exactly at compile time. The transformation for such access patterns is called *tiling*. In tiling, loop permutation and strip-minning are applied to arrange the access pattern into small tiles that can fit completely in the cache [56]. The main idea is to instrument the innermost loop to make the accessed data fit in the cache and thus achieve the requirement of better reuse. A significant problem with tiling techniques is that conflict misses can occur. Such misses will cause tile data to be evicted from cache before they are fully reused [30]. This effect is shown in Figure 5.1.

Figure 5.2 part(A) shows tiling applied to the 2D Jacobi code introduced in Chapter 3. The goal in tiling for Jacobi is to keep the three columns needed for each computation in the cache. To address the cache conflicts problem, *tile size selection* and *array padding* can be applied to avoid conflict misses in tiles [14, 42, 44].

Avoiding conflicts in tiling problems, especially for 3D problems is discussed in Rivera *et al.* [45]. They consider 4 possible solutions to reduce conflict misses when applying tiling. They dismiss 3 of these solutions and are left with one good solution. Tile size selection avoids conflicts by carefully selecting tile dimensions tailored to the particular array dimensions so that no conflicts occur. An algorithm called the Euclidean remainder algorithm is used to compute sequences of nonconflicting tile dimensions [14, 44] for 2D arrays. Also, an extension of this technique is discussed in [45] to apply this algorithm to 3D arrays. A cost function is required in these algorithms to pick one tile size out of all the generated tile sizes. A greedy algorithm is used to search for improved tile size candidates by increasing the tile dimensions and testing for conflicts. The

tile size is continually extended until no more extensions are possible without introducing conflicts.

Even when choosing non-conflicting tiles, performance of tiling may suffer for certain array dimensions. For instance, given a  $341 \times 341 \times M$  array, the best tile size available is (110,4). The problem with this tile size is that the second tile dimension is small. When one or more tile dimensions are small, performance suffers. Note that the original problem was doing computations assuming a tile size of (341,1), the new tile size won't be effective enough in improving the locality of the application. The solution is to use padding to enable better tile sizes [43]. Padding algorithms for picking the optimal tile size are NP-complete. However, good tile sizes can be obtained using heuristics that have reasonable complexity.

### 5.2 Reordering for Indexed Accesses

As was discussed previously in Chapters 3 and 4, indexed array accesses are difficult to optimize since compile-time analysis cannot determine the access patterns. Instead, indexed array accesses must be optimized at runtime [1, 17, 35, 36]. Saltz *et al.* designed a compiler which generates calls to an inspector to process memory access patterns at run-time. The same approach can be used to improve the locality of indexed array access patterns.

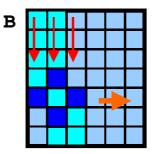

Figure 3.4 shows the relationship between the index array and the data (indexed) array. Indexed array accesses can be optimized using an inspector-executor approach [16] as shown in Figure 5.2 part(B). The outcome of

Figure 5.4: Indexed Array computation reordered after the reordering operations. such a transformation is a change of the layout of the data that forces the access to the data array to be more regular, thus resulting in better cache performance.

The reordering process is shown in Figure 5.3. This figure shows the partitioning and the reordering of the data and index arrays taking place. Since almost all molecular dynamics and electromagnetic codes interact pairs of data according to their geometric coordinate data. The problem lends itself to a directed graph. Several data and computation locality transformations exist to solve the problem of improving the locality of such graphs. One of these techniques is called Graph Partitioning techniques (GPART). This technique is based on hierarchical clustering. It generates quality partitions like the ones in

Figure 5.3 quickly. The main advantage of this technique is that it has low overhead since it only considers edges between partitions. GPART closely matches the performance of more sophisticated partitioning algorithms, with one third of the overhead [1, 35, 21].

An example is shown in Figure 5.4. Circles represent computations (loop iterations), squares represent data (array elements), and arrows represent data accesses. Initially, memory accesses are irregular, but either computation or data may be reordered to improve temporal and spatial locality. Note that each iteration accesses two array elements. Computations can be viewed as edges connecting data nodes, resulting in a graph. Locality optimizations can then be mapped to a graph partitioning problem. Partitioning the graph and putting nodes in a partition close in memory can then improve spatial and temporal locality. Applying lexicographic sorting after partitioning captures even more locality.

The hierarchical structure in GPART is similar to that of recursive coordinate bisection (RCB), which is a data reordering algorithm used when data is unevenly distributed. RCB is based on geometric coordinate information. RCB recursively splits each dimension into two by finding the median of the data coordinates in that dimension. After partitioning, data items are stored consecutively within each partition. Loop iterations are lexicographically sorted based on the data accessed [17, 21, 36]. RCB has higher overheads than other techniques but is most likely to work well with unevenly distributed data. The right half of Figure 5.4 shows the computations after the partitioning technique

has been applied and shows how the computations will access the array in a different order compared to the original access order. These algorithms are defined in more detail in [21, 22].

### 5.3 Memory Allocation For Pointers

Pointer-based applications typically suffer from poor cache performance just like indexed array codes since the allocation of these data structures is dynamic and typically exhibits low spatial locality. Pointer-based applications are harder to optimize than indexed array codes because of their dependence upon pointers and dynamic allocation of new data items. Due to the pointer chasing problem, link nodes must be traversed sequentially, as explained in Sections 3.3 and 4.3.

Cache-conscious allocation has been introduced to improve the locality of such accesses [6, 12]. This technique packs nodes of data that are logically contiguous onto the same cache line so that they are physically contiguous in memory, thus increasing spatial locality. The node packing is achieved using a custom memory allocator called "CCMALLOC".

Figure 5.5 shows how nodes from a linked list are allocated in a cache-conscious fashion using CCMALLOC. Figure 5.2 part(C) shows a simple list allocation code that uses CCMALLOC to allocate list nodes on nearby cache blocks dynamically. The modification is quite simple: replacing MALLOC with CCMALLOC. This optimization is applied to all pointer-chasing benchmarks used.

CCMALLOC works in the following way: it takes a pointer as an

Figure 5.5: Linked list contiguously allocated in Main Memory.

argument and allocates current and future nodes close to it. It reserves space for future data blocks when allocating the first node [12].

Note one problem with CCMALLOC is that dynamic data structures which change after allocation may not benefit from this optimization. Frequent insert and delete operations after allocation will make logically contiguous nodes physically non-contiguous.

## Chapter 6 Experimental Evaluation

In this Chapter, the performance of software prefetching as well as that of locality optimizations is evaluated independently and when combined together naively. The experimental methodology in doing the evaluation is explained in detail. Then, the results for software prefetching and locality optimizations under different memory bandwidths and latencies are shown for all 9 benchmarks studied. Finally, the naive combination is discussed. Later in Chapter 7, enhancements for more effectively combining software prefetching and locality optimizations are presented and evaluated.

### 6.1 Methodology

In this section, the methodology used to evaluate the different techniques is presented. This thesis evaluates 9 benchmarks. The evaluation considers different versions of each benchmark: original, prefetching, locality optimized, and the combined version which includes both prefetching and locality optimizations. All experiments are performed on the same cycle accurate simulator, and all benchmarks were run to completion.

| Application | Problem Size        | Access Pattern  |

|-------------|---------------------|-----------------|

| MATMULT     | 200x200 matrices    | Affine array    |

| Jacobi      | 200x200x8 grid      | Affine array    |

| RedBlack    | 200x200x8 grid      | Affine array    |

| IRREG       | 14K node mesh       | Indexed array   |

| Moldyn      | 13K molecules       | Indexed array   |

| NBF         | 144K mols           | Indexed array   |

| Health      | 5 levels, 500 iters | Pointer-chasing |

| MST         | 1024  nodes         | Pointer-chasing |

| EM3D        | 10K nodes           | Pointer-chasing |

Table 6.1: Benchmark summary.

As discussed in Chapter 3, three different access patterns are evaluated. For each access pattern, three benchmarks are instrumented and evaluated. Table 6.1 lists all the benchmarks used along with their problem sizes and memory access patterns.

The Affine array benchmarks are MATMULT, which multiplies two matrices, REDBLACK, which performs a 3D red-black successive-over-relaxation, and JACOBI, which performs a 3D JACOBI relaxation. Both JACOBI and REDBLACK are frequently found in PDE solvers, such as MGRID from the SPEC/NAS benchmark suite.

The indexed array benchmarks are IRREG, which is an iterative PDE solver for an irregular mesh, MOLDYN, which is abstracted from the non-bonded force calculation in CHARMM [16], a key molecular dynamics application used at NIH to model macromolecular systems, and NBF (Non Bonded Force kernel), which performs a molecular dynamics simulation. NBF is taken from the GROMOS benchmark suite [54].

Finally, the pointer-chasing benchmarks are HEALTH, which simulates the

Columbian health care system, MST, which computes a minimum spanning tree, and EM3D, which simulates electromagnetic wave propagation through 3D objects. HEALTH, MST, and EM3D are from the OLDEN benchmark suite [46].

For reasons that will appear later on in the results provided for EM3D, a more detailed explanation of what the application is actually doing and how it is doing it is introduced here. The major data structure of EM3D is an array that contains the set of magnetic and electric nodes [15] since Electromagnetic waves travel through space as alternating magnetic and electric fields. EM3D simulates these fields with two sets of nodes: enodes and hnodes, where each set of nodes corresponds to one of the fields. The area or surface on which the electromagnetic field is to be simulated is modeled by a mesh of the e and hnodes. Each node is given an initial value, and a list of it's neighboring nodes. (enodes have hnodes for neighbors and hnodes have enodes for neighbors.) Each node is connected to each of its neighbors via an edge that has an associated coupling coefficient. The list of nodes, edges, and the edge coefficients form a bipartite graph [50].

The original code is instrumented by hand to generate the prefetching, locality optimized and the combined versions of each application. These codes are compiled for our target architecture which is based on the SimpleScalar tool set [5] and models a 1GHz 4-way issue dynamically-scheduled processor. The simulator simulates all aspects of the processor, including the functional units, the reorder buffer, the branch predictors, register renaming, the instruction fetch unit, the load-store unit, the caches (data and instructions), and of course, the register file. The simulator is cycle accurate. The original memory system model

from the SimpleScalar tool set was modified to account for the contention on the L2-memory system bus. It was assumed that the L1-L2 bus link has infinite bandwidth. No MSHRs are modeled. This approach maximizes the concurrency in the memory system to expose memory bandwidth limitations. Also, a prefetch instruction was added to the ISA of the processor.

The experiments were done using the following cache organization: A split 8-KByte direct-mapped L1 cache with 32-byte cache blocks, and a unified 256-KByte 4-way set-associative L2 cache with 64-byte cache blocks. The latency of the L1 cache is one cycle, while the L1-L2 bus latency is 7 cycles and has infinite bandwidth. Although the cache sizes are small, they are matched to the small problem sizes used for the benchmarks in order to limit the simulation time.

Using this simulator model, each benchmark version is evaluated with different L2-memory latencies and different memory bandwidths to study the effects of memory system parameters on software prefetching and locality optimization performance. The L2-memory latency is varied from 80 to 640 cycles in powers of two, and memory bandwidth is varied from 1 Gbytes/sec to 64 Gbytes/sec also, in powers of two. The lower end of both the latency and bandwidth ranges simulated captures the trends of existing memory systems which have latencies of around 100 cycles and bandwidths of around 2-3 GBytes/sec. The mid and high end of the latency and bandwidth ranges simulated capture the characteristics of future architectures. All these number are capturing the trends in single processor system and doesn't extend to multi-processor systems.

| Latency in Cycles | RedBlack | Jacobi  | Matmult |

|-------------------|----------|---------|---------|

| 80                | 12       | 8, 36   | 24      |

| 160               | 24       | 16,68   | 44      |

| 320               | 48       | 28, 136 | 88      |

| 640               | 96       | 56, 268 | 176     |

Table 6.2: Prefetch distances for REDBLACK, JACOBI and MATMULT for the different latencies.

| Latency in Cycles | IRREG                 | Moldyn    | NBF |

|-------------------|-----------------------|-----------|-----|

| 80                | 8, 20, 20, 40         | 1,1,2     | 2   |