## Ph.D. Dissertation Optimization within a Unified Transformation Framework

Wayne Anthony Kelly Advisor: Professor William W. Pugh Department of Computer Science University of Maryland, College Park, MD 20742 wak@cs.umd.edu

December 8, 1996

# Contents

| 1        | Intro          | oduction                                           |   |

|----------|----------------|----------------------------------------------------|---|

| <b>2</b> | $\mathbf{The}$ | Abstractions                                       |   |

|          | 2.1            | Tuple Relations and Sets                           |   |

|          | 2.2            | Distributing Computation                           |   |

|          |                | 2.2.1 Traditional Abstractions                     |   |

|          |                | 2.2.2 My New Abstraction                           |   |

|          | 2.3            | Ordering Computation                               |   |

|          |                | 2.3.1 Traditional Abstractions                     | 1 |

|          |                | 2.3.2 My New Abstraction                           | 1 |

|          | 2.4            | Combining Distribution and Ordering of Computation | 2 |

| 3        | $\mathbf{The}$ | Algorithms                                         | 2 |

|          | 3.1            | The Issues                                         | 2 |

|          | 3.2            | Selecting Space Mappings                           | 2 |

|          |                | 3.2.1 Introduction                                 | 2 |

|          |                | 3.2.2 Candidate Space Mappings                     | 2 |

|          |                | 3.2.3 Estimating Parallelism                       | 4 |

|          |                | 3.2.4 False Sharing on Shared Memory Architectures |   |

|          |                | 3.2.5 Estimating Communication                     | : |

|          |                | 3.2.6 The Search Problem                           | 3 |

|          |                | 3.2.7 Alignment                                    | 5 |

|          |                | 3.2.8 An Example: adi                              | 5 |

|          | 3.3            | Selecting Time Mappings                            | 5 |

|          |                | 3.3.1 Introduction                                 | 3 |

|          |                | 3.3.2 Estimating Data Locality                     | 4 |

|          |                | 3.3.3 Incompatible Time Mappings                   | 4 |

|          |                | 3.3.4 The Search Problem                           | 4 |

|          |                | 3.3.5 Constant Levels and Offsets                  | 4 |

|          | 3.4            | The Search Procedure                               | 4 |

|          |                | 3.4.1 The Simple Search Procedure                  | 4 |

|          |                | 3.4.2 Pruning Strategies                           | 4 |

|          |                | 3.4.3 Time-limited Searches                        | 4 |

|          |                | 3.4.4 Semi-automatic Systems                       | 4 |

|          | 3.5            | Code Generation                                    | 4 |

|          |                | 3.5.1 Introduction                                 | 4 |

|          |                | 3.5.2 Scanning Multiple Polyhedra                  | 4 |

|          |                | 3.5.3 Generating SPMD Code                         | 5 |

|          |                | 3.5.4 Inserting Synchronization                    | 5 |

|          |                | 3.5.5 Reduction Optimizations                      | 5 |

|          |                | 3.5.6 Examples                                     | 5 |

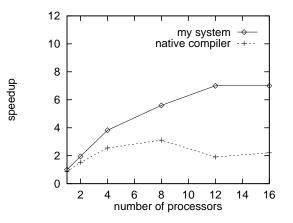

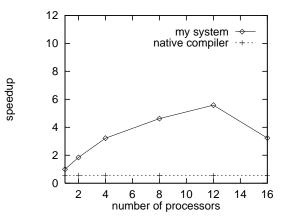

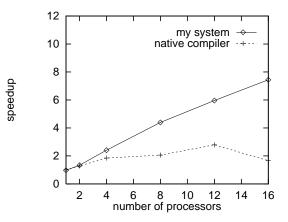

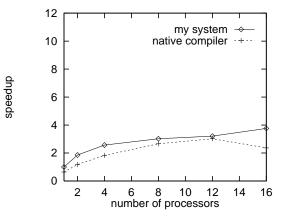

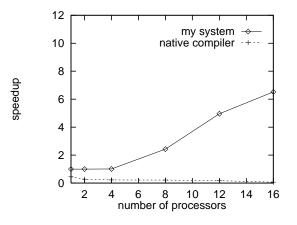

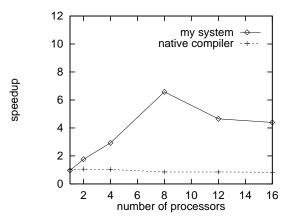

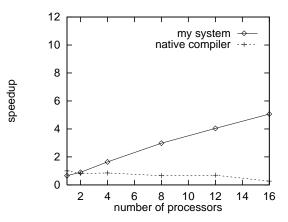

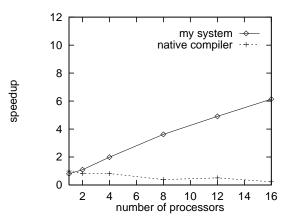

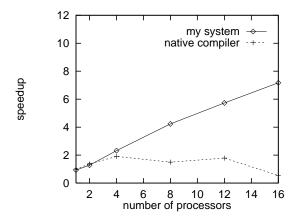

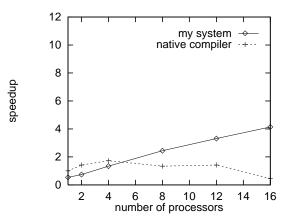

| 4        | $\mathbf{Exp}$ | perimental Results       | 61        |

|----------|----------------|--------------------------|-----------|

|          | 4.1            | The Implementation       | 61        |

|          | 4.2            | Efficiency               | 61        |

|          | 4.3            | Effectiveness            | 64        |

|          | 4.4            | ${ m Robustness}$        | 68        |

| <b>5</b> | $\mathbf{Rel}$ | ated Work                | <b>74</b> |

|          | 5.1            | Distributing Computation | 74        |

|          | 5.2            | Ordering Computation     | 75        |

|          | 5.3            | Generating Code          | 78        |

| 6        | Fut            | ure Work                 | 80        |

|          | 6.1            | Distributed Memory       | 80        |

|          | 6.2            | Arbitrary Control Flow   | 80        |

|          | 6.3            | Multiple Procedures      | 80        |

|          | 6.4            | Improved Space Mappings  | 80        |

|          | 6.5            | Improved Time Mappings   | 81        |

|          | 6.6            | My Ultimate Goal         | 81        |

| 7        | Cor            | nclusions                | 82        |

## Chapter 1

# Introduction

Supercomputers have dramatically increased the amount of computing power available to scientists. These performance improvements have made it feasible to realistically model a much larger class of scientific problems than has previously been possible. Examples of such problems include atmospheric modeling, molecular dynamics and fluid dynamics.

Two basic methods have been used to achieve the very high levels of performance of these new machines. The first method is to make the processor more powerful. This is primarily how the earliest supercomputers such as the Cray 1 achieved their high performance. The problem with this approach is that physical factors such as the speed of light and heat dissipation place an absolute upper bound on obtainable performance. The other method used to increase computing power is to use multiple processors that can work in parallel. Over the last five years, the trend has been towards massively parallel computers, where hundreds or even thousands of processors are used [Ken92].

The problem with using multiple processors is that it is very difficult to write programs that can attain the theoretical peak performance of these machines. The reasons for these difficulties include load balancing problems, memory contention, interprocessor communication bottlenecks, and lack of explicit parallelism. So, while massively parallel machines promise a great deal, the results obtained in practice have been disappointing.

Two approaches have been used to program massively parallel machines. The first approach requires the programmer to write explicitly parallel code, i.e all responsibility is placed on the programmer. The programmer must specify what computations should be performed on which processors, and what communications are required. This approach is clearly not acceptable in the long term, as it places too onerous a burden on the programmer.

The other approach is to have the programmer write normal sequential programs, and then have a compiler convert these sequential programs into explicitly parallel programs. This approach has the advantage that no additional responsibilities are placed on the programmer. The source programs used with this approach also tend to be more portable than explicitly parallel source programs. Of course, the problem with this approach is that converting sequential programs into efficient parallel programs is a very difficult task. So, not surprisingly, existing parallelizing compilers for massively parallel machines often fail to produce satisfactory results [Blu92, SH91].

There are two basic choices to be made when parallelizing a program. First, the computations of the program need to be distributed amongst the set of available processors. Second, the computations on each processor need to be ordered. Approaches taken to the second of these tasks have traditionally been very ad-hoc. Specifically, parallelizing compilers have attempted to parallelize programs and improve their performance by applying a sequence of source to source transformations, such as loop interchange, loop skewing and loop distribution [Wol89a]. Each of these transformations has its own legality checks and transformation rules. These checks and rules make it hard to analyze or predict the effects of compositions of these transformations, without actually performing the transformations and analyzing the resulting code.

I have developed a new framework that unifies the problems of distributing and ordering computation. This framework is based on a simple but powerful mathematical abstraction for representing these decisions. I have also developed algorithms for making these decisions within this framework. These algorithms are extremely extensible, in that the set of transformations considered and the performance estimators used to decide which transformation to apply, are not hard wired into the system. Users are able to modify or write their own performance estimators to reflect the factors which affect performance on their particular architecture. They can also modify the set of transformations considered, so as to obtain the trade-off between efficiency and effectiveness that best suits their individual needs. Conversely, many of the abstractions and algorithms I have developed have applications outside of the framework developed here.

## Chapter 2

# The Abstractions

There are two basic choices to be made when parallelizing a program. First, the computations of the program need to be distributed amongst the set of available processors. Second, the computations on each processor need to be ordered. In this chapter I describe the abstractions that have traditionally been used to represent these choices. I'll discuss the problems associated with these traditional abstractions and I'll propose new abstractions that are designed to solve some of these problems. Before discussing these new abstractions I will first describe an abstraction called tuple relations upon which the other new abstractions are based.

### 2.1 Tuple Relations and Sets

An integer k-tuple is simply a point in  $\mathbb{Z}^k$ . A *tuple relation* is a mapping from tuples to tuples. A single tuple may be mapped to zero, one or more tuples. All the relations I consider map from k-tuples to k'-tuples for some fixed k and k'. I introduce variables corresponding to each of the input and output positions. Relationships between these variables and those corresponding to symbolic constants are represented as logical formulas involving affine equality and inequality constraints. For example, the following relation maps all tuples [i, j] to the tuple [i, i] if i is even and j is between 1 and the symbolic constant n, or i is less than j:

$$\{[i, j] \to [i, i] \mid (\exists \alpha \text{ s.t. } i = 2\alpha \land 1 \le j \le n) \lor i < j\}$$

I have helped develop the Omega Library [KMP+95, KPRS95] which is a set of C++ classes for representing and manipulating tuple relations and sets. The Omega Library can represent any tuple relation or set that can be described using Presburger arithmetic. Presburger formulas are made up from logical quantifiers  $(\forall, \exists)$ ; logical operations  $(\lor, \land, \Rightarrow, \neg)$ ; and affine equality and inequality constraints on integer valued variables. Although Presburger arithmetic has extremely high theoretical worst case complexity,  $O(2^{2^{2^n}})$ , the Omega library has been extensively tuned to handle simple cases, and typically takes only a few milliseconds to produce a result.

Table 2.1 gives a brief description of some of the operations on integer tuple relations and sets that we have implemented. The following are some examples of operations on tuple relations

and sets:

$$\begin{array}{ll} \text{If} & I = \{[i,j] \mid 1 \leq i \leq n \land 1 \leq j \leq i\} \\ \text{and} & T = \{[i,j] \to [i+j,i]\} \\ \text{then} & Range(Restrict\_Domain(T,I)) = \{[x,y] \mid y+1 \leq x \leq 2y \land y \leq n\} \\ \\ \text{If} & C_{22} = \{[i,j,k] \to [i',j',k'] \mid (i=i' \land j'=j+1 \land k=k') \lor i'=i+1\} \\ & T_{12} = \{[i,j] \to [i,j,k]\} \\ & T_{21} = \{[i,j,k] \to [i',j'] \mid i'=i+1 \land j'=j+1\} \\ \\ \text{then} & T_{21} \circ C_{22}^* \circ T_{12} = \{[i,j] \to [i',j'] \mid i < i'\} \end{array}$$

| Operation          | Definition                                                                                                                 |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| Composition        | $x \to z \in F \circ G \Leftrightarrow \exists y \text{ s.t. } x \to y \in F \land y \to z \in G$                          |

| Inverse            | $x \to y \in F^{-1} \Leftrightarrow y \to x \in F$                                                                         |

| Union              | $x \mathop{\rightarrow} y \in F \cup G \Leftrightarrow x \mathop{\rightarrow} y \in F \lor x \mathop{\rightarrow} y \in G$ |

| Intersection       | $x \to y \in F \cap G \Leftrightarrow x \to y \in F \land x \to y \in G$                                                   |

| Restrict Domain    | $x \rightarrow y \in Restrict\_Domain(F,S) \Leftrightarrow x \rightarrow y \in F \land x \in S$                            |

| Restrict Range     | $x \rightarrow y \in Restrict\_Range(F,S) \Leftrightarrow x \rightarrow y \in F \land y \in S$                             |

| Domain             | $x \in Domain(F) \Leftrightarrow \exists y \text{ s.t. } x \to y \in F$                                                    |

| Range              | $y \in Range(F) \Leftrightarrow \exists x \text{ s.t. } x \to y \in F$                                                     |

| Projection         | $x \in \prod_{1,\dots,v} S \Leftrightarrow  x  = v \land \exists y \text{ s.t. } xy \in S$                                 |

| Transitive Closure | $x \to y \in F^* \Leftrightarrow x \to y \in F \lor \exists z \text{ s.t. } x \to z \in F \land z \to y \in F^*$           |

| Is satisfiable ?   | $Is\_Satisfiable(S) \Leftrightarrow \exists x \in S$                                                                       |

Table 2.1: Operations on tuple sets and relations

Tuple relations and sets and their associated operations have an enormous number of applications other than those described in this dissertation. Some of the applications to which they have already been applied include:

- Data dependence analysis

- Program transformations

- Redundant synchronization removal

- Code generation

- Induction variable analysis

- Safety and Coverage analysis for finite state systems

## 2.2 Distributing Computation

The units of computation that are distributed amongst the processors of a multiprocessor machine may be either entire tasks or individual iterations of loops. Task-level parallelism works best on distributed systems such as networks of workstations because it generally involves a lesser amount of inter-processor communication, which is particularly expensive on such systems. Loop-level parallelism works best on tightly-coupled massively parallel machines because it is more likely to provide sufficient parallelism to make use of all available processors. Such parallelism is most likely to be found in programs for scientific applications which consist mainly of **for** loops and assignment statements involving arrays. The scientific community is consequentially the largest group of users of massively parallel computers today. This thesis deals exclusively with loop-level parallelism.

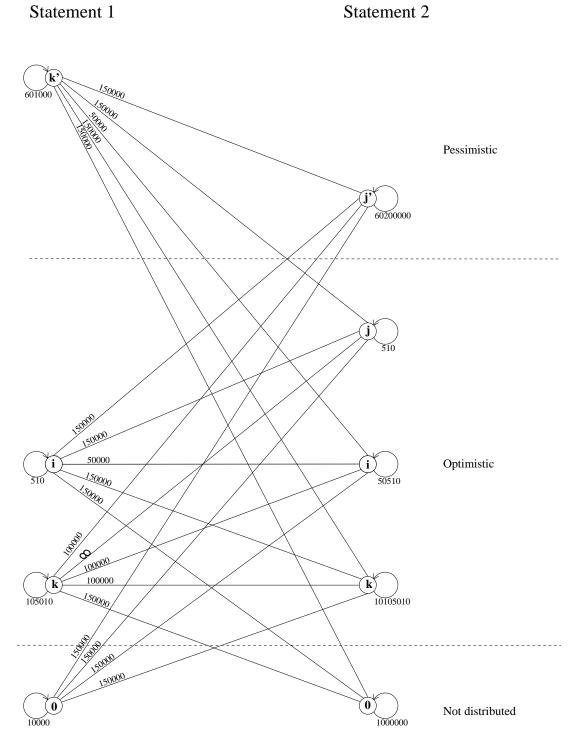

Figure 2.1: Why doall loops are insufficient for NUMA machines

### 2.2.1 Traditional Abstractions

Traditionally, the distribution of computations is specified via either doall and doacross loops or via a data distribution for each array.

### **Doall and Doacross Loops**

One way to specify the parallelism available in a program written in a sequential language is to annotate the do loops in that program as being either doall, doacross or dosequential [ZC91].

A doall loop indicates that all of the iterations of that loop are independent and therefore can be executed in any order (including in parallel). A doall loop does not indicate which iterations should be performed on which processors. The mapping of iterations to processors is determined either statically by some latter phase of the compilation/linking process or dynamically by the runtime system.

A doacross loop indicates that it is possible to partially overlap the execution of the loops iterations. There are generally some ordering constraints on the loop iterations, but not so many that the iterations must be executed entirely sequentially. These ordering constraints are enforced by explicit synchronization statements that must be inserted in the body of such loops.

A dosequential loop indicates that it is not possible to overlap the execution of any of the loop iterations. In practice, a loop could be marked as being dosequential even if it could be marked as being doall or doacross. This is generally done when it is estimated that the overhead associated with executing the loop in parallel is higher than the potential savings due to parallelism.

In the case of Uniform Memory Access (UMA) [AG94] machines, the fact that doall and doacross loops cannot control the mapping of iterations onto processors is of no consequence since the choice of mapping can not affect performance (provided some care is taken to ensure load balancing). However, in the case of Non-Uniform Memory Access (NUMA) machines [AG94], the choice of mapping can have a substantial affect on performance. For NUMA machines, the choice of mapping will determine which data accesses will be satisfied locally and which data accesses will require communication with other processors.

Consider for example the program shown in Figure 2.1. If for both loops, iteration i is assigned to processor i, then inter-processor communication will be required. If, however, iteration i of the first loop is assigned to processor i and iteration i of the second loop is assigned to processor i-1, then no inter-processor communication will be required. In most modern NUMA architectures, the time required to access data from another processor is orders of magnitudes longer than the time required to access data that is on processor.

### **Data Distributions**

In order to control the mapping of iterations onto processors, a different method of representing parallelism in programs is required. A common approach is the so called *data parallel* paradigm. In this model, parallelism is achieved by performing the same operation on different data elements at the same time. The distribution of computation to processors is specified implicitly

```

PROCESSORS procs(32)

TEMPLATE T(1024)

ALIGN a(i) with T(i)

ALIGN b(i) with T(i-1)

DISTRIBUTE T(block) onto procs

```

Figure 2.2: Data distribution

```

do i = 1 to n

s = 0.

do j = 1 to i - 1

s = s + a(n-i+1,n-j+1) * x(n-j+1)

x(n-i+1) = (a(n-i+1,n+1) - s) / a(n-i+1,n-i+1)

```

Figure 2.3: Reduction example where a data distribution is not optimal

in such systems via data distribution annotations [HKT91, For92] and the owner-computes rule [CK88]. A data distribution is an affine mapping from the elements of an array to a virtual processor array. The owner-computes rule states that each iteration should be performed on the virtual processor that "owns" the array element being written. Virtual processors are folded onto physical processors in either a block, cyclic or block-cyclic manner. Data distributions may be either static or dynamic. A static distribution means that the same distribution is used throughout the entire execution of the program and a dynamic distribution means that different distributions will be used during various phases of the program's execution. Figure 2.2 shows an example of a data distribution (and corresponding alignment statement) for the program in Figure 2.1.

Data distributions are an appropriate abstraction for machines with logically distributed memories. Such machines require the programmer or compiler to explicitly manage the storage and transfer of data. On machines with logically shared memories, however, data distributions may not be the most appropriate abstraction. On such machines, data is automatically transferred from one processor's memory to another's as required. In this context, data distributions are simply an indirect way to specify a computation distribution and as such are unnecessarily restrictive. Data distributions, when used with the owner-computes rule, do not allow different iterations of the same statement that write to the same array element to be executed on different processors. Such computation distributions are often desirable, especially for statements that are performing a reduction. A reduction is a set of operations that compute a scalar value from an array[ZC91]. For example, in the program shown in Figure 2.3, it would be best to assign iteration [i, j] to virtual processor j in order to perform the reduction in parallel.

The other drawback with data distributions is that either a static data distribution must be chosen, or the program must be divided into phases between which data redistributions will be performed. If the compiler is not going to consider restructuring the program in a major way then this is not a major problem. If, however, the compiler is trying to both automatically select data distributions and restructure the program, then deciding how to divide a program into phases can be particularly difficult as it also involves making decisions about the best order in which to perform the computations.

### 2.2.2 My New Abstraction

I use a relatively new abstraction called a space mapping [Fea94, AL93b] to directly map the computations of a program to a virtual processor array. I associate a tuple relation  $S_p$ , with

```

\begin{split} S_1 : & \{[i] \rightarrow [i]\} \\ S_2 : & \{[i] \rightarrow [i-1]\} \\ \\ & \text{block\_size} = \max(0, \text{ceiling}((n+1)/n\text{procs})) \\ & \text{lb} = 0 + \text{my\_id*block\_size} \\ & \text{ub} = \min(n, \text{lb+block\_size-1}) \\ & \text{do t} = \max(1, \text{lb}) \text{ to } \min(n, \text{ub}) \\ & a(t) = t \\ & \text{do t} = \max(0, \text{lb}) \text{ to } \min(n-1, \text{ub}) \\ & b(t+1) = a(t) \end{split}

```

Figure 2.4: Space mappings and corresponding SPMD code.

each statement p. It specifies that each iteration i of statement p will be executed on virtual processor  $S_p(i)$ . The input arity of  $S_p$  is equal to the number of loops surrounding statement p and the output arity is equal to the dimensionality of the virtual processor array. I will only consider space mappings that are functions (i.e., each iteration i of statement p is mapped to a unique virtual processor  $S_p(i)$ ). As with data distributions, the virtual processor array is folded onto the physical processor array in either a blocked, cyclic, or block-cyclic fashion.

By directly mapping iterations to virtual processors (rather than using data decompositions), I am able to represent a wider range of computation distributions and hence have more freedom in trying to minimize inter-processor communication. In addition, I can represent dynamic data distributions without having to partition the program into phases between which redistribution will occur. Figure 2.4 shows an example of space mappings that could be used for the program in Figure 2.1, together with the SPMD code that would result from applying these space mappings with a blocked distribution. In the (SPMD) Single Program Multiple Data programming model, all processors execute an identical copy of the program. The key to SPMD programming is that each processor can access a variable (commonly called my\_proc) that allows the program running on that processor to know which processor it is running on. This makes it possible to explicitly control which iterations are performed on which processors.

A separate space mapping is associated with each statement, however, what constitutes a statement may vary. In this dissertation, I generally assume that each assignment statement in the original program is a separate statement. However, an entire basic block, or any other well nested section of code could be considered a single statement. At the other extreme, an assignment statement could be decomposed into the machine code instructions required to execute it, each of which could be considered a separate statement. Obviously, there is a trade-off between the flexibility of mapping finer-grained statements, and the extra time required to consider a greater number of possibilities.

### 2.3 Ordering Computation

Program transformations can generally be classified into one of three classes:

- **Reordering transformations**, where the same set of computations are performed but in a different order. Examples of this class include loop interchange, statement reordering and loop distribution.

- Storage modifying transformations, where the same computations are performed in the same order but with the intermediate results being stored in different locations. Examples of this class include array and scalar expansion and privatization.

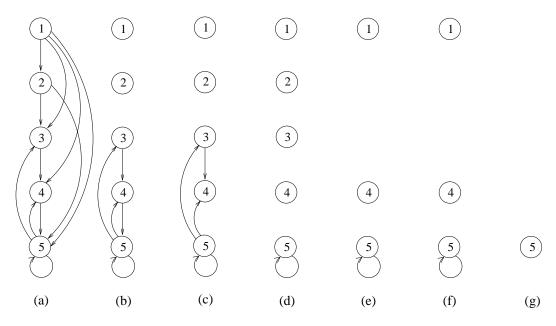

Figure 2.5: A sequence of traditional transformations

Algorithm modifying transformations, where a different set of computations are performed to compute the same final result. Examples of this class include induction variable replacement and reordering reduction operations.

In this thesis I deal only with reordering transformations; however, I assume that some other transformations such as induction variable replacement, and scalar/array expansion will have been performed before the transformations described here. I also assume that other transformations such as code hoisting and strength reduction will be performed after the transformations described here.

### 2.3.1 Traditional Abstractions

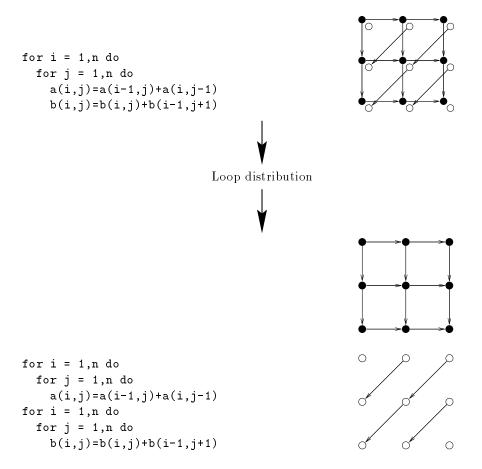

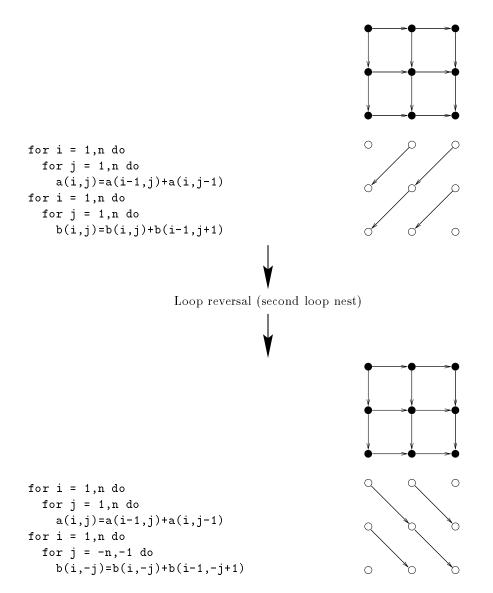

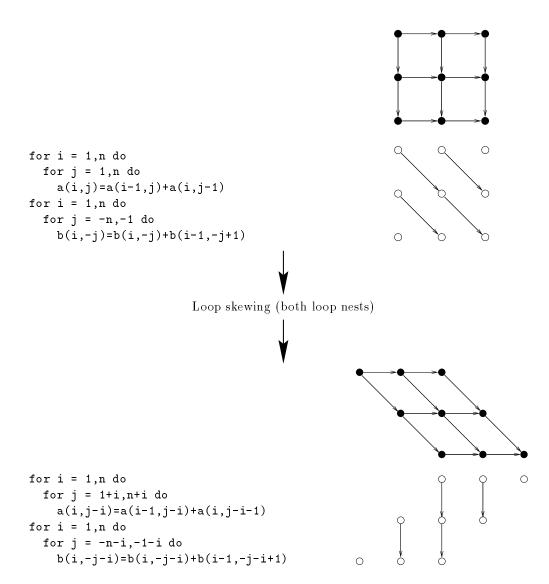

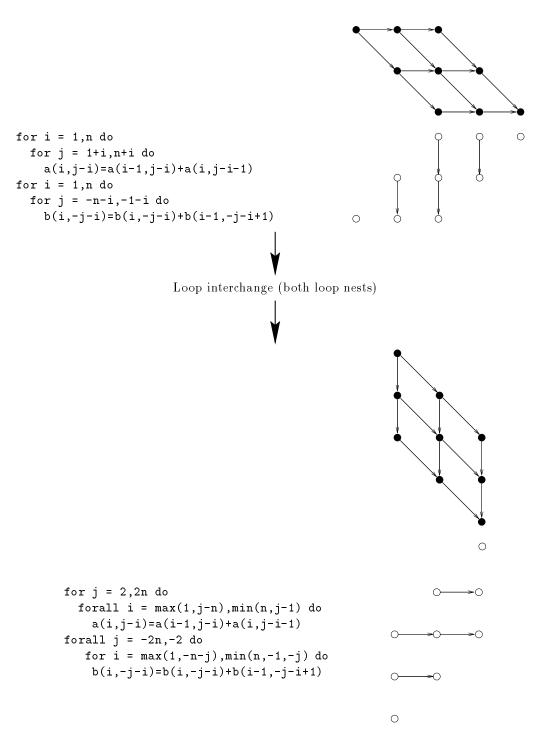

Optimizing compilers reorder iterations of statements to improve instruction scheduling, register use, cache utilization, and to expose parallelism. Many different reordering transformations have been developed and studied, such as loop interchange, loop distribution, skewing, tiling, index set splitting and statement reordering [AK87, Wol89c, Wol90, CK92]. Figures 2.5 through 2.8 show an example of such a sequence of transformations (black dots correspond to iterations of the first statement and white dots correspond to iterations of the second statement). Each of these transformations has its own special legality checks and transformation rules. These checks and rules make it hard to analyze or predict the effects of compositions of these transformations, without actually performing the transformations and analyzing the resulting code.

Figure 2.6: A sequence of traditional transformations, continued

Figure 2.7: A sequence of traditional transformations, continued

Figure 2.8: A sequence of traditional transformations, continued

Iteration space:

Figure 2.9: Program and associated iteration space

Unimodular transformations [Ban90, WL91] go some way towards solving this problem. Unimodular transformations are able to describe any transformation that can be obtained by composing loop interchange, loop skewing, and loop reversal. Such a transformation is described by a unimodular linear mapping from the original iteration space to a new iteration space. For example, loop interchange in a doubly nested loop maps iteration [i, j] to iteration [j, i]. This transformation can be described using a unimodular matrix:

$$\left[\begin{array}{rr} 0 & 1 \\ 1 & 0 \end{array}\right]$$

Unfortunately, unimodular transformations are limited in two ways: they can only be applied to perfectly nested loops, and all statements in the loop nest are transformed in the same way. They therefore cannot represent some important transformations such as loop fusion, loop distribution and statement reordering [Wol89c].

### 2.3.2 My New Abstraction

Before describing the abstraction I use to represent the ordering of computations, I first need to define some terms.

#### Iteration spaces

Each statement p has associated with it an iteration space  $I_p$ , which is a subspace of  $\mathcal{Z}^{n_p}$  (where  $n_p$  is the number of loops nested around p). A statement's iteration space is the set of iterations for which that statement will be executed.

More formally  $[x_1, \ldots, x_n] \in I_p$  if and only if:

$$\forall j, \ 1 \leq j \leq n \Rightarrow L_j(x_1, \dots, x_{j-1}, \vec{s}) \leq x_j \leq U_j(x_1, \dots, x_{j-1}, \vec{s})$$

where  $L_j$  and  $U_j$  are functions representing the lower and upper bounds respectively of the  $j^{th}$  loop around p, and  $\vec{s}$  is a vector of symbolic constants.

For example, Figure 2.9 shows a program and its associated iteration space.

### Time mappings

I have developed a new abstraction called time mappings for specifying the order in which iterations should be executed. I associate a separate time mapping,  $T_p$ , with each statement p.

A time mapping is a tuple relation that maps each point (or iteration) in the original iteration space  $I_p$  to a unique point in a new iteration space I'. The set of time mappings as a whole, Time Mapping:

Transformed program:

```

do i = 1 to n

1 s(i) = 0

do t = 1 to n-1

do i = t+1 to n

2 s(i) = s(i) + a(t,i)*b(t)

3 b(t+1) = b(t+1) - s(t+1)

```

Figure 2.10: Time mapping and associated transformed program

describe a 1-1 mapping from the set of original iteration spaces to a single new iteration space. That is:

$$\forall p, q, i, j \ T_p(i) = T_q(j) \Rightarrow p = q \land i = j \tag{2.1}$$

The iterations will be executed in lexicographic order based on their coordinates in the new iteration space. So, specifying a time mapping is effectively specifying a reordering of the iterations.

Figure 2.10 shows an example of a set of time mappings for the program in Figure 2.9. This time mapping maps iteration [5,7] in the original iteration space of statement 2 to iteration [1,7,0,5] in the new iteration space and maps iteration [6] in the original iteration space of statement 1 to iteration [0,6]. Iteration [0,6] is lexicographically less than iteration [1,7,0,5], so in the transformed code, the iteration originally referred to as iteration [6] of statement 1 will be executed before the iteration originally referred to as iteration [5,7] of statement 2. So, as this example demonstrates, by mapping to a single new iteration space, I can specify the relative order in which iterations should be executed, even for iterations belonging to different statements.

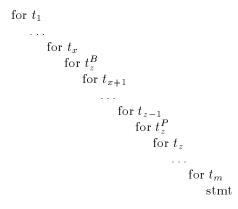

The transformed code will always contain the same elementary statements as the original code, but will contain different loop structures. The new loop structures execute in lexicographic order, all and only those iterations in the new iteration space. In Section 3.5 I will describe an algorithm I have developed for generating transformed code given a set of time mappings.

Time mappings can be considered a generalization of Unimodular transformations. Time mappings are more general in the following respects:

- I associate a separate time mapping with each statement, whereas unimodular transformations require a single unimodular matrix to be used to transform all statements in the body of a perfectly nested loop.

- Unimodular transformations only allow linear mapping to be specified. Time mappings allow any mapping to be specified that can be expressed in Presburger arithmetic.

- In particular, time mappings can easily represent affine mappings. An affine expression is equivalent to a linear expression plus a constant term. For example, i + j is linear, i + j + 1 is affine. There is no advantage in using affine mappings rather than linear mappings if only one mapping is being used to transform all statements (as is the case for unimodular transformations), since a constant term will simply translate all points in the new iteration space and not affect their relative order. However, if more than one mapping is specified (as is the case for time mappings), then using different constant terms in different mappings can affect the relative order of the

Code adapted from OLDA in Perfect club (TI)

Time Mapping (to expose parallelism)

Transformed code

Figure 2.11: OLDA with time mappings, and resulting transformation

points in the new iteration space (as was demonstrated in the previous example). Affine mappings allow me to represent a number of traditional transformations in addition to those representable using unimodular transformations, including statement reordering, loop distribution, loop fusion, and loop alignment.

- Time mappings can also represent pseudo-affine mappings. A pseudo-affine expression is an expression that involves affine expressions and integer division and modulo operations (provided the denominator is a known integer constant). Pseudo-affine mappings allow me to represent a number of additional transformations including strip mining (or tiling).

- Time mappings allow different affine (or pseudo-affine) mappings to be specified for different parts of the iteration space of a single statement. This allows me to represent index set splitting transformations.

Time mappings can represent not only all of the traditional transformations mentioned above, but also any sequence of these traditional transformations. I have therefore simplified the problem of reordering the iterations of a program to finding a time mapping for each statement. This simple and elegant representation makes it much easier to reason about reordering transformations.

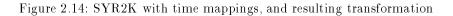

Some more examples of time mappings are given in Figures 2.11 through 2.14.

### Legality

Not all time mappings correspond to legal transformations, so I need a way to distinguish between legal and illegal time mappings. A time mapping is legal if the transformation it describes preserves the semantics of the original code. This is true if the new ordering of the iterations respects all of the dependences in the original code.

I assume that the programs contain only static control flow, so control dependences do not have to be considered. Three types of data dependences can occur; flow, output and anti. It LU Decomposition without pivoting

do 20 k = 1, n

do 10 i = k+1, n

10

$$a(i,k) = a(i,k) / a(k,k)$$

do 20 j = k+1, n

20  $a(i,j) = a(i,j) - a(i,k) * a(k,j)$

Time Mapping (for locality)

$$\begin{array}{ccc} T_{10}: \{[k,i & ] \rightarrow [64((k-1) \; div \; 64) + 1, 64(i \; div \; 64), k, k, i]\} \\ T_{20}: \{[k,i,j] \rightarrow [64((k-1) \; div \; 64) + 1, 64(i \; div \; 64), j, k, i]\} \end{array}$$

Transformed code

Figure 2.12: LU with time mappings, and resulting transformation

Code adapted from CHOSOL in the Perfect club (SD)

```

do 30 i=2,n

10     sum(i) = 0.

do 20 j=1,i-1

20     sum(i) = sum(i) + a(j,i)*b(j)

30     b(i) = b(i) - sum(i)

```

Time Mapping (to expose parallelism)

| $T_{10}$ : | $\{ [i] \}$ |     | $\rightarrow$ | [0,  | i,     | 0, | 0]}      |

|------------|-------------|-----|---------------|------|--------|----|----------|

| $T_{20}$ : | $\{ [ i, $  | j ] | $\rightarrow$ | [1,  | j,     | 0, | $i ] \}$ |

| $T_{30}$ : | $\{ [i] \}$ |     | $\rightarrow$ | [ 1, | i - 1, | 1, | 0]}      |

Transformed code

```

do 10 i = 2,n /* parallel */

10   sum(i) = 0.

do 30 t2 = 1, n-1

do 20 i = t2+1,n /* parallel */

20        sum(i) = sum(i) + a(t2,i)*b(t2)

30        b(t2+1) = b(t2+1) - sum(t2+1)

```

Figure 2.13: CHOSOL with time mappings, and resulting transformation

Banded SYR2K adapted from BLAS

Time Mapping (for locality and to expose parallelism)

$T_{10}: \{ [i, j, k] \rightarrow [j-i+1, k-j, k] \}$

Transformed code

is generally possible (though not always desirable) to remove output and anti dependences by performing array expansion. Two possible approaches can be taken:

- Determine legality based on only flow dependences and then remove any output and anti dependences that are not respected, by performing array expansion on the arrays involved in those dependences.

- Determine a priori, which arrays will be expanded and then determine legality based on flow dependences and whichever output and anti dependences remain.

Most of the previous work on program transformations uses data dependence directions or distances to summarize dependences between array references. These abstractions are sufficient for simple transformations such as unimodular transformations, but they are not precise enough to determine the legality of loop fusion and a number of other transformations without actually applying the transformation and re-evaluating dependences. Since my framework includes loop fusion, they are not sufficient for my purposes either. I evaluate and represent dependences exactly using integer tuple relations. If there is a data dependence from  $s_p[i]$  (i.e., iteration *i* of statement *p*) to  $s_q[j]$  then the tuple relation  $D_{pq}$  representing the dependences from *p* to *q* will map tuple *i* to tuple *j*.

The legality requirement is then simply:

$$\forall i, j, p, q, Sym \quad i \to j \in D_{pq} \Rightarrow T_p(i) \prec T_q(j) \tag{2.2}$$

where  $\prec$  means lexicographically precedes and Sym is the set of symbolic constants in  $D_{pq}$ . Intuitively, if there is a data dependence from  $s_p[i]$  to  $s_q[j]$  then iteration *i* must be executed before iteration *j* in the transformed program. To be well-formed, the time mappings must also be 1-1 (see Equation 2.1).

### **Representing Traditional Transformations**

In this section I demonstrate how time mappings can be used to represent all transformations that can be obtained by applying any sequence of the following traditional transformations:

$$\begin{aligned} & \texttt{Orig}(\mathbf{S}, \, [i_1, \, \dots, \, i_k] \rightarrow [f_1, \, \dots, \, f_a]) \\ & \texttt{case } S \texttt{ of} \\ & \text{``for } i_{k+1} = \dots \texttt{ to } \dots \texttt{ do } S_1 ``: \\ & \texttt{return Orig}(S_1, \, [i_1, \, \dots, \, i_k, \, i_{k+1}] \rightarrow [f_1, \, \dots, \, f_a, \, i_{k+1}]) \\ & \text{``}S_1; S_2; \dots; S_m ``: \\ & \texttt{return } \bigcup_{p=1}^m \texttt{Orig}(S_p, \, [i_1, \dots, \, i_k] \rightarrow [f_1, \dots, \, f_a, p]) \\ & \text{``assignment } \# p ``: \\ & \texttt{return } T_p : \{ \ [i_1, \dots, \, i_k] \rightarrow [f_1, \dots, \, f_a] \ \end{aligned} \end{aligned}$$

Figure 2.15: Computes mapping that corresponds to the original execution order

Figure 2.16: Abstract syntax tree

- Loop Distribution

- Statement Reordering

- Loop Fusion

- Loop Interchange

- Loop Skewing

- Loop Reversal.

- Strip-mining

- Index Set Splitting

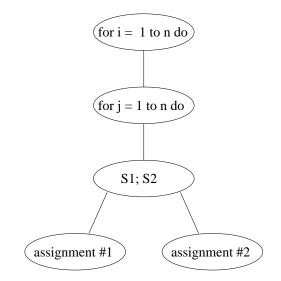

I will describe how to construct time mappings to represent traditional transformations by describing how to modify time mappings that correspond to the original execution order of programs. The time mapping that corresponds to the original execution order of a program can be constructed by a recursive descent of the abstract syntax tree (AST). Nodes in the AST have three forms: loops, statement lists and assignment statements. The function Orig (see Figure 2.15), when called with arguments of S and  $[] \rightarrow []$ , returns a time mapping that corresponds to the original execution order in S.

For example, the program in Figure 2.5 has the AST shown in Figure 2.16 and the time mapping that corresponds to the original execution order is:

$$\begin{array}{l} T_1: \{[i,j] \to [i,j,0] \ \} \\ T_2: \{[i,j] \to [i,j,1] \ \} \end{array}$$

The general form of these time mappings is:

$$T_p:[i_p^1,\ldots,i_p^{m_p}]\to [f_p^1,\ldots,f_p^{n_p}]$$

The  $f_p^j$  expressions are referred to as mapping components and are classified as being either syntactic components (always an integer constant) or loop components (a linear function of the loop variables of that statement).  $syntactic(f_p^j)$  is a boolean function which is true iff  $f_p^j$  is a syntactic component.  $loop(f_p^j)$  is true iff  $f_p^j$  is a loop component. The common syntactic level of two statements  $s_p$  and  $s_q$  is defined as:

$$\operatorname{csl}(s_p, s_q) \equiv \min\{j - 1 \mid 1 \le j \land f_p^j \ne f_q^j \land \operatorname{syntactic}(f_p^j) \land \operatorname{syntactic}(f_q^j)\}$$

Intuitively, the common syntactic level of two statements is the deepest loop which surrounds both statements. Figures 2.17 and 2.18 describe how to construct time mappings to represent traditional transformations by modifying the time mappings I have just described. Since these rules can be applied repeatedly, I can represent not only standard transformations but also any sequence of standard transformations.

Figures 2.19 through 2.20 show how these rules are used to derive the time mapping:

$$\begin{array}{rrrr} T_1: & \{[i, & j] \rightarrow [1, & i+j, & i, & 1]\} \\ T_2: & \{[i, & j] \rightarrow [2, & i-j, & i, & 2]\} \end{array}$$

which is equivalent to the sequence of traditional transformations shown in Figures 2.5 through 2.8.

## 2.4 Combining Distribution and Ordering of Computation

The abstractions used for reordering computation can be used in isolation to specify a new total ordering of the iterations, or they can be used together with the abstractions for distributing computation to specify a new partial ordering of the iterations. When used with space mappings (or any other abstraction for specifying the distribution of computation), time mappings are used only to specify the relative execution order for iterations on the same physical processor. That is, if two iterations are executed on different physical processors, then the time mappings do not specify the relative order in which these iterations should be executed. If data dependences exist between iterations on different physical processors then synchronization statements will be used to ensure that those iterations are executed in the appropriate order. These ordering constraints together with the ordering constraints implied by the time mappings will generally only specify a partial ordering of the iterations. The absence of a total ordering is what allows parallelism to be exploited.

**Distribution:** distribute the loop at depth L over the set of statements D, with statement p going into  $r_p^{\text{th}}$  loop.

Requirements:  $\forall p, q \ p \in D \land q \in D \Rightarrow \mathsf{loop}(f_p^L) \land L \leq \mathsf{csl}(p,q)$

Transformation:  $\forall p \in D$ , replace  $T_p$  by  $[f_p^1, \ldots, f_p^{(L-1)}, r_p, f_p^L, \ldots, f_p^n]$

**Statement Reordering:** reorder the set of statements D, at level L so that the new position of statement p is  $r_p$ .

Requirements:  $\forall p, q \ p \in D \land q \in D \Rightarrow \texttt{syntactic}(f_p^L) \land L \leq csl(p,q) + 1 \land (L \leq csl(p,q) \Leftrightarrow r_p = r_q)$

Transformation:  $\forall p \in D$ , replace  $T_p$  by  $[f_p^1, \ldots, f_p^{(L-1)}, r_p, f_p^{(L+1)}, \ldots, f_p^n]$

**Fusion:** fuse the loops at level L for the set of statements D, with statement p going into the  $r_p^{\text{th}}$  loop.

Requirements:  $\forall p, q \ p \in D \land q \in D \Rightarrow \texttt{syntactic}(f_p^{(L-1)}) \land \texttt{loop}(f_p^L) \land L-2 \leq csl(p,q) + 2 \land (L-2 < csl(p,q) + 2 \Rightarrow r_p = r_q)$ Transformation:  $\forall p \in D$ , replace  $T_p$  by  $[f_p^1, \dots, f_p^{(L-2)}, r_p, f_p^{(L)}, f_p^{(L-1)}, f_p^{(L+1)}, \dots, f_p^n]$

Unimodular Transformation: Apply a  $k \times k$  unimodular transformation U to a perfectly nested loop containing the set of statements D, at depth L. Note: Unimodular transformations include loop interchange, skewing and reversal [Ban90, WL91].

Requirements:  $\forall i, p, q \ p \in D \land q \in D \land L \leq i \leq L+k-1 \Rightarrow \mathsf{loop}(f_p^i) \land L+k-1 \leq csl(p,q))$ Transformation:  $\forall p \in D$ , replace  $T_p$  by  $[f_p^1, \ldots, f_p^{(L-1)}, U[f_p^L, \ldots, f_p^{L+k-1}]^\top, f_p^{L+k}, \ldots, f_p^n]$

**Strip-mining:** strip-mine the level L loop for the set of statements D, with block size B

Requirements:  $\forall p, q \ p \in D \land q \in D \Rightarrow loop(f_p^L) \land L \leq csl(p,q)) \land B$  is a known integer constant

Transformation:  $\forall p \in D$ , replace  $T_p$  by  $[f_p^1, \ldots, f_p^{(L-1)}, B(f_p^{(L)} \text{ div } B), f_p^{(L)}, \ldots, f_p^n]$

Figure 2.17: Representing traditional transformations

**Index Set Splitting:** split the iteration spaces of the set of statements D, using condition CRequirements: C is affine expression of constants and indexes common to the set of statements D.

Transformation:  $\forall p \in D$ , replace  $T_p$  by  $(T_p \mid C) \cup (T_p \mid \neg C)$

Figure 2.18: Representing traditional transformations, continued

**Original Time Mappings:**

$$\begin{array}{l} T_1: \{[i,j] \to [i,j,1]\} \\ T_2: \{[i,j] \to [i,j,2]\} \\ f_1^1 = i, \ f_1^2 = j, \ f_1^3 = 1, \ f_2^1 = i, \ f_2^2 = j, \ f_2^3 = 2 \\ \texttt{loop}(i) = True, \ \texttt{loop}(j) = True, \ \texttt{loop}(1) = False, \ \texttt{loop}(2) = False \\ csl(1,2) = 2 \end{array}$$

### Loop distribution:

$$L = 1, D = \{1, 2\}, r_1 = 1, r_2 = 2$$

Requirements:

$$\begin{split} \forall p, q \ p \in \{1, 2\} \land q \in \{1, 2\} \Rightarrow \texttt{loop}(f_p^1) \land 1 \leq csl(p, q) \\ \text{Transformation:} \\ T_1 : \ \{[i, j] \rightarrow [1, i, j, 1]\} \\ T_2 : \ \{[i, j] \rightarrow [2, i, j, 2]\} \end{split}$$

### Loop reversal second loop (Unimodular Transformation):

$$k = 1, U = (-1), D = \{2\}, L = 3$$

Requirements:

$\begin{array}{l} \forall i, p, q \ p \in \{2\} \land q \in \{2\} \land 3 \leq i \leq 3 \Rightarrow \texttt{loop}(f_p^i) \land 3 \leq csl(p,q) \\ \text{Transformation:} \\ T_1 : \ \{[i, \ j] \rightarrow [1, \ i, \ j, \ 1]\} \\ T_2 : \ \{[i, \ j] \rightarrow [2, \ i, \ -j, \ 2]\} \end{array}$

Loop skewing first loop (Unimodular Transformation):

$$k = 2, U = \begin{pmatrix} 1 & 0 \\ 1 & 1 \end{pmatrix}, D = \{1\}, L = 2$$

Requirements:

$$\begin{split} \forall i, p, q \ p \in \{1\} \land q \in \{1\} \land 2 \leq i \leq 3 \Rightarrow \texttt{loop}(f_p^i) \land 3 \leq csl(p,q) \\ \text{Transformation:} \\ T_1 : \ \{[i, \ j] \rightarrow [1, \ i, \ i+j, \ 1]\} \\ T_2 : \ \{[i, \ j] \rightarrow [2, \ i, \ -j, \ 2]\} \end{split}$$

Figure 2.19: Deriving time mappings

Loop skewing second loop (Unimodular Transformation):

$$k = 2, U = \begin{pmatrix} 1 & 0 \\ 1 & 1 \end{pmatrix}, D = \{2\}, L = 2$$

Requirements:

$\begin{array}{l} \forall i, p, q \ p \in \{2\} \land q \in \{2\} \land 2 \leq i \leq 3 \Rightarrow \texttt{loop}(f_p^i) \land 3 \leq csl(p,q) \\ \text{Transformation:} \\ T_1 : \ \{[i, \ j] \rightarrow [1, \ i, \ i+j, \ 1]\} \\ T_2 : \ \{[i, \ j] \rightarrow [2, \ i, \ i-j, \ 2]\} \end{array}$

Loop interchange first loop (Unimodular Transformation):

$$k = 2, U = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}, D = \{1\}, L = 2$$

Requirements:

$\begin{array}{l} \forall i, p, q \ p \in \{1\} \land q \in \{1\} \land 2 \leq i \leq 3 \Rightarrow \texttt{loop}(f_p^i) \land 3 \leq csl(p,q) \\ \text{Transformation:} \\ T_1: \ \{[i, \ j] \rightarrow [1, \ i+j, \ i, \ 1]\} \\ T_2: \ \{[i, \ j] \rightarrow [2, \ i, \ i-j, \ 2]\} \end{array}$

Loop interchange second loop (Unimodular Transformation):

$$k = 2, \ U = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}, \ D = \{2\}, \ L = 2$$

Requirements:

$\begin{array}{l} \forall i, p, q \ p \in \{2\} \land q \in \{2\} \land 2 \leq i \leq 3 \Rightarrow \texttt{loop}(f_p^i) \land 3 \leq csl(p,q) \\ \text{Transformation:} \\ T_1 : \ \{[i, \ j] \rightarrow [1, \ i+j, \ i, \ 1]\} \\ T_2 : \ \{[i, \ j] \rightarrow [2, \ i-j, \ i, \ 2]\} \end{array}$

Figure 2.20: Deriving time mappings continued

## Chapter 3

# The Algorithms

### 3.1 The Issues

As was stated earlier, the task of mapping a program written in a sequential programming language onto a multi-processor machine can be divided into two major subproblems: deciding how to distribute the computation amongst the available processors and deciding how to order the computations. Finding a close to optimal solution in a feasible amount of time for either of these problems in isolation is still an open problem; it is even more difficult to solve these problems simultaneously.

To simplify the problem, I first decide how to distribute the computations amongst the available processors, and then, based on that decision, decide how to order the computations. In making this simplification however, I am very mindful of the fact that the two problems are tightly coupled. As much as possible, I have tried to take this into account when devising methods to solve the first of these problems, namely distributing the computations.

In deciding how to distribute the computations amongst the available processors, I want to minimize the amount of communication between processors while at the same time preserving some degree of parallelism. Minimizing communication between processors can be accomplished without regard to the order of the computations. However, achieving sufficient parallelism does depend on the execution order.

Through a combination of scalar and array expansion or privatization, loop distribution, statement reordering and loop interchange, it is often possible to expose parallel loops that did not exist in the original program. Even if parallel loops exist in the original program, distributing the iterations of the newly exposed parallel loops rather than the original parallel loops might result in a higher granularity of parallelism or in lower inter-processor communication costs. In some cases, there may be no parallel loops to exploit, but the program may be able to be transformed to use doacross/pipelining techniques to allow computation and communication to be overlapped.

The phase that distributes the computations will be followed by a phase that reorders the computations so as to achieve maximal parallelism from the chosen distribution. So, it is important not to be influenced by the original computation order when evaluating how much parallelism could be achieved by distributing the iterations of a particular loop.

An overview of my entire optimization system is shown in Figure 3.1. Each of the sub-tasks shown in this overview will be explained in the remained of this chapter. The reader is advised to refer back to this overview from time to time, as they progress through this material.

### Select Space Mappings:

Calculate extended direction vectors for communication analysis Calculate transitive data dependences for parallelism analysis Analyze blocked distribution:

Analyze comm. for each pair of candidate space mappings Analyze parallelism for each candidate space mapping Search for best combination of candidate space mappings

if (any statement has an unbalanced workload)

Analyze cyclic distribution:

Analyze comm. for each pair of cand. space mappings Analyze parallelism for each cand. space mapping

Search for best combination of cand. space mappings if (cost of cyclic solution < cost of blocked solution)

then Unbalanced, so use cyclic distribution

else Unbalanced, but use a blocked distribution

else Balanced, so use a blocked distribution

Form affine space mappings by adding constants

### Select Time Mappings:

Analyze locality for each candidate loop permutation Analyze compatibility for each pair of cand. loop permutations Search for best combination of candidate loop permutations Form time mappings by adding constant levels to best perm.

### Generate Code:

Generate new loop structures using time mappings Generate SPMD code using space mappings Insert synchronization for inter-processor dependences

Figure 3.1: Overview of the entire optimization process

## 3.2 Selecting Space Mappings

### 3.2.1 Introduction

The problem of automatically distributing computation has been addressed by a large number of authors [Gup92, Fea94, AL93a, BKK93, GAL95, SSP+95]. My work improves on most previous work in the following ways:

- 1. I am not influenced by the order of the computation of the original program. I use methods to determine the parallelism inherent in the program rather than the parallelism that can be obtained using the computation order in the original program.

- 2. When analyzing parallelism, I not only examine each loop to determine whether its iterations can be run entirely independently, but also whether its iterations can be pipelined (a lesser but still important form of parallelism). Exploiting this form of parallelism requires that a SPMD rather than a SIMD model be used.

- 3. I associate a space mapping with each statement, which allows me to represent dynamic data distributions without having to partition the program into phases, as well as allowing me to represent non-data distributions.

- 4. I obtain accurate indications of the relative volumes of different inter-processor communications by computing the dimensionality of value-based flow dependence relations [PW93] (an abstraction that precisely describes which iterations actually read values written by which other iterations). This allows me to analyze communication costs without knowing the order of the computations.

- 5. I solve the resulting graph search problem exactly, and have shown experimentally that I can normally do so in a feasible amount of time by using a number of very effective but safe pruning strategies. Other researchers use heuristic or greedy algorithms.

- 6. I simultaneously optimize for communication and parallelism, trading one off for the other where necessary to obtain an overall optimal solution.

Throughout this section, I make a number of simplifying assumptions, such as the assumption that all loops have an equal number of iterations (which I denote as n). Some of these assumptions could be eliminated at the cost of substantial complications to my framework. However, the point of my algorithm is not to identify that one decomposition is 10% better than another; my cost model is not sensitive or accurate enough to answer those kinds of questions. It is unclear if there is any way to answer those kinds of questions other than by performing time trials on the target machine. My methods are designed to find a distribution such that no significantly better distribution exists, and could be easily altered to generate a list of all such decompositions.

### 3.2.2 Candidate Space Mappings

Two basic approaches can be taken to selecting space mappings:

- First generate a finite set of candidate space mappings for each statement. This creates a finite search space where each solution corresponds to selecting one candidate space mapping for each statement. Exact or heuristic search procedures can then used to find an optimal or close to optimal solution from amongst this set of solutions.

- Use a method that directly synthesizes the optimal space mapping for each statement.

```

for i = 1 to n

for j = 1 to n

1: a(i,j) = ...

for k = 1 to n

2: ... = a(i,k+1)

```

Figure 3.2: Extended direction vectors

The disadvantage of the first approach is that if the optimal space mapping is not included in the set of candidate space mappings then it will not be selected. This is not a serious problem in practice because optimal space mappings tend to be very simple in realistic examples. It is therefore very easy to generate a small set of candidate space mappings that will likely contain the optimal space mapping.

The second approach has two major disadvantages. First, it is very difficult to accurately estimate complex performance properties such as communication latency and data locality without having actual space mappings in mind. Second, the synthesis process is inherently global rather than local (i.e., the space mapping chosen for one statement may affect the space mappings that should be chosen for all other statements). The size of the resulting optimization problem (which often can be formulated as an integer programming problem) will therefore be at least proportional to the number of statements in the program. The exponential nature of such problems means that this approach will generally scale poorly to larger programs.

I have therefore decided in favor of the first approach. In my current implementation, I only consider space mappings that map to one dimensional processor arrays. My set of candidate space mappings consists of each dimension in the original iteration space, plus zero (which corresponds to not distributing the computation). For example, the candidate space mappings for statement 1 in the program shown in Figure 3.2 are:

| $\{[i, j]$ | $\rightarrow$ | [i]     |

|------------|---------------|---------|

| $\{[i, j]$ | $\rightarrow$ | $[j]\}$ |

| $\{[i, j]$ | $\rightarrow$ | $[0]\}$ |

It would be possible to extend my implementation to consider other candidates (including skewed mappings) whenever there is some reason to believe they might be desirable. In any case, the candidate space mappings will be linear (as opposed to affine). In Section 3.2.7, I will describe how to select constant offsets to add to these linear space mappings.

In order for my search procedure to select an optimal solution from amongst the set of all possible solutions there must be some metric for comparing solutions. In the next two sections, I will describe how to estimate the parallelism that will result from selecting each of the candidate space mappings and the amount of inter-processor communication that will result from selecting various pairs of candidate space mappings. The parallelism and communication estimates are combined to give an overall performance estimate for each solution.

### 3.2.3 Estimating Parallelism

In this section I describe my methods to determine the parallelism inherent a program. My first observation is that the most useful form of parallelism is between different iterations of the same statement, rather than between iterations of different statements. This implies that each statement should be examined separately to determine whether any of its iterations can be executed in parallel. In doing so, however, I want to ignore any constraints on parallelism imposed by the original loop order or by other statements that just happen to be in the same loop nest. On the other hand, it is clearly not sufficient to examine each statement in isolation. It turns out that what I need to consider are all direct and transitive self data dependences of

```

for r = 1 to n

for p = 1 to n

for q = 1 to n

e_{pq} = e_{pq} \lor (e_{pr} \land e_{rq})

```

Figure 3.3: Floyd-Warshall algorithm

```

for i = 1 to n

for j = 1 to n

D'_{ij} = D_{ij}

for r = 1 to n

for p = 1 to n

for q = 1 to n

D'_{pq} = D'_{pq} \cup (D'_{pr} \circ D'^*_{rr} \circ D'_{rq})

```

Figure 3.4: Modified form of Floyd-Warshall algorithm

each statement. This takes into account constraints on parallelism imposed by other statements, but only those that can't be avoided. I consider all flow dependences, and whichever output and anti dependences remain after array expansion has been performed (deciding when to apply array expansion is outside the scope of this thesis, and was performed manually for the experiments presented in Section 4).

I have developed two methods for computing transitive self data dependences. Both methods use the same basic algorithm, which is a modified form of the Floyd-Warshall algorithm for computing the transitive closure of a graph (see Figure 3.4). The input to this algorithm is a set of variables  $D_{pq}$  representing all direct data dependences from statement p to statement q. The output is a set of variables  $D'_{pq}$  representing all transitive data dependences from statement pto statement q.

The original Floyd-Warshall algorithm (see Figure 3.3) can be used to determine the existence of a transitive dependence from any given statement to any other given statement (including itself); however, it cannot determine which iterations of those statements are dependent. To obtain this additional information, rather than using boolean valued variables, I use variables that describe which iterations are dependent on which other iterations. These values need to be combined using union and composition operations rather than boolean "and" and "or" operations. The other modification to the algorithm is somewhat subtle and involves the addition of the  $D'_{rr}^*$  term. This transitive closure term is added because to find all transitive dependences from statement p to statement q, I need to consider dependence "chains" of the following form:

If there is a transitive dependence from some iteration i of statement p to some

Figure 3.5: Transitive dependences

iteration j of statement q and a transitive self dependence from iteration j of statement q to iteration k of statement q and finally a dependence from iteration k of statement q to some iteration m of statement r, then there is a transitive dependence from iteration i of statement p to iteration m of statement r (see Figure 3.5).

Computing transitive data dependences is very useful for a number of applications other that parallelism analysis, for example they can also be used to detect redundant synchronization statements.

The only difference between the two methods that I have developed is the abstraction used to represent dependences.

### An exact method

The first method uses tuple relations to represent data dependences, and uses the operators described in Table 2.1. This method will generally compute the set of transitive dependences exactly. The problem with this method, however, is that the size of the dependence relations generated, and hence the time required to generate them, tends to increase rapidly as the number of the statements is increased. I have found that this method is infeasible for analyzing large programs.

### A faster but less accurate method

My other approach is to use extended direction vectors [WB87, Wol91a] to represent dependences. A dependence direction vector is a vector  $(v_1, \ldots, v_m)$ , where  $v_i$  is either '-', '0', or '+', indicating whether the difference between the level *i* index variable at the source of the dependence is less than, equal to, or greater than the level *i* index variable at the sink of the dependence. For a normal direction vector, the length of the vector is equal to the maximum common loop depth of the two statements. An extended direction vector has length equal to the minimum loop depth of the two statements. For example, for the flow dependence from statement 1 to statement 2 in Figure 3.2, the value of the level 1 index variable *i*, at the source of the dependence. Also, the value of the level 2 index variable *j*, at the source of the dependence, is less than the value of the level 2 index variable *k*, at the sink of the dependence. So, the dependence is represented by the direction vector (0) and by the extended direction vector (0, -).

When taking the union of two sets of extended direction vectors, vectors are combined if and only if doing so will not lead to the loss of information (i.e., if the entries are all identical but one). For example, (0, +) and (0, 0) can be combined to produce (0, 0+); however, (0, +) and (+, 0) can't be combined to produce (0+, 0+) (as that would imply that (0, 0) and (+, +) are possible direction vectors). When taking the union of sets of extended direction vectors with different lengths (which occurs when considering transitive dependences through statements which are not as deeply nested as the statement in question), the shorter vectors are padded with '\*', indicating that '-', '0' and '+' are all possible. The composition of direction vectors is performed element-wise and is defined in the obvious manner (i.e. composing '+' and '0' produces '+', composing '+' and '-' produces '\*', etc). For extended direction vectors, the transitive closure operation is simply a "no-op" (i.e., '+'' = '+', '0'' = '0' and '-'' = '-').

#### Loop Transformations

I wish to analyze the parallelism that would result from selecting each candidate space mappings without being influenced by the original loop order. My current implementation considers all legal loop permutations of the loops surrounding each statement (including all combinations of reversing the loops). It would also be possible to extend my implementation to consider

```

for t_1

...

for t_{z-1}

for t_z^P

for t_z^B

for t_z

...

for t_m

stmt

```

Figure 3.6: Straight forward loop structure for block-cyclic

other unimodular loop transformations (including skewed transformations) when there is some reason to believe they might be desirable.

The candidate space mappings are classified according to the amount of synchronization they will require (and hence how much parallelism they permit) within each particular permutation. Even if all permutations of the loops are legal (a number which is exponential in the number of loops), only a very small amount of time will be required, since each statement is considered separately and statements are seldom nested within more than 4 or 5 loops. Each candidate space mapping is given an overall classification based on the amount of synchronization it will require using the best permutation for that particular candidate. The set of best permutations for the candidate space mapping that is ultimately selected will later be used as the starting point for selecting a time mapping for that statement.

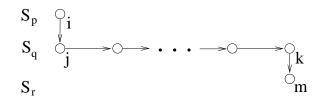

### Synchronization costs

To analyze the amount of synchronization that will be required for a particular candidate using a particular permutation, the structure of the loops that would ultimately be used must be considered. I analyze the general case of using a block-cyclic distribution rather than separately analyzing both the block and cyclic cases. If the loop of the candidate space mapping is at level z in the current permutation (and the statement is nested within m loops), then a straight forward implementation of block-cyclic distribution would lead to the loop structure shown in Figure 3.6.

The  $t_z^P$  loop iterates over the set of physical processors, the  $t_z^B$  loop iterates over the blocks and the  $t_z$  loop iterates over the iterations within each block. In a block distribution the  $t_z^B$ loop will be degenerate and in a cyclic distribution the  $t_z$  loop will be degenerate.

Figure 3.7: Improved loop structure for block-cyclic

We define:

- $\mathbf{x}$  as the deepest loop level that carries a transitive self-dependence with a negative dependence distance at the distributed loop level.

- **y** as the deepest loop level that carries a transitive self-dependence with a positive dependence distance at the distributed loop level.

It is legal to move the  $t_z^B$  loop out to just inside the  $t_x$  loop, so a better loop structure is shown in Figure 3.7.

This can be converted to SPMD code as follows:

- Remove the  $t_z^P$  loop.

- Insert a barrier inside the  $t_z^B$  loop, if necessary, to enforce any dependences going from higher numbered physical processors to lower numbered physical processors.

- Insert post-and-wait style synchronization inside the  $t_y$  loop, if necessary (i.e. if x < y), to enforce any dependences going from lower numbered physical processors to higher numbered physical processors. The form of post-and-wait style synchronization that I use causes each processor (except the lowest numbered processor) to wait for the next lowest numbered processor.

My decision to use this style of post-and-wait synchronization and to use it only to synchronize dependences from lower numbered physical processors to higher numbered physical processors was made in order to simplify analysis, to allow multiple dependences to be satisfied by a single post-and-wait pair, and to avoid the possibility of deadlock. It is certainly not the only choice that could be made; for example, post-and-wait style synchronization could be used to synchronize only those dependences from higher numbered physical processors to lower numbered physical processors. If more sophisticated techniques were used to avoid deadlock or if other forms of post-and-wait style synchronization were used, then post-and-wait style synchronization could even be used to synchronize at least some dependences in both directions.

By moving the  $t_z^B$  loop out as far as possible, a minimal number of barriers will be executed. The placement of the  $t_z^B$  loop also implies that any dependences carried by loops  $t_{x+1}$  through  $t_{z-1}$  will be from a lower numbered physical processor to a higher numbered physical processor, so some form of parallelism (either pure or pipelined) will result within each iteration of the  $t_z^B$  loop.

On some architectures it is more efficient to synchronize using forms of synchronization other than barriers, for example using send and receive pairs on a distributed memory machine. The point I am trying to make is not that barriers should be used, but rather that at the places where I have said barriers should be inserted, some form of non-pipelined synchronization will be used. So from a purely cost point of view, it is reasonable to model this as a barrier.

The maximum amount, D, by which different processors can be expected to be out of lock-step, is computed as follows:

- If any dependences are carried by the distributed loop, the expected delay between the time processor p can start, and the time processor p + 1 can start, will be  $L + Bn^{m-y}$ , where L is the inter-processor message latency, B is the block size, n is the number of iterations per loop, and P is the number of physical processors<sup>1</sup>. The wait from when the first processor reaches a barrier until the last reaches the barrier will be P 1 times the delay between successive processors. I simplify this slightly to  $D = P(L + Bn^{m-y})$ .

- If no dependences are carried by the distributed loop, but there are inter-processor dependences carried by loops  $t_{x+1}$  through  $t_{y-1}$ , then those dependences from processor p to processor p+1 may force processor p+1 to lag L behind processor p. I again simplify slightly and estimate D = PL.

- If no inter-processor dependences are carried by loops  $t_{x+1}$  through  $t_y$ , then the processors should remain synchronized to within D = L.

The number of barrier synchronizations performed will be  $\frac{n^{x+1}}{BP}$ . To perform a barrier synchronization, the processors must exchange messages (costing L) and synchronize (costing D). Since  $D \ge L$ , I simplify the cost per barrier to D. The total synchronization cost for each statement is therefore  $\frac{n^{x+1}D}{BP}$ .

### Load balance

The loop bounds of each statement are examined to determine whether the amount of work in each iteration will be constant. If any statements have unbalanced loops, then a cyclic distribution is considered in addition to considering a block distribution. When evaluating block distributions for candidates with unbalanced workloads, an additional  $\frac{n^m}{2}$  time is added to the overhead estimate. This heuristic is based on the fact that most unbalanced workloads are a result of triangular loops and the difference between the amount of work in a triangular loop and a rectangular loop is  $\frac{n^m}{2}$ . In Section 3.2.5 higher communication estimates will be used for some dependences when using a cyclic distribution.

#### Compatible candidates

After synchronization analysis has been performed, the minimum degree of synchronization required for each candidate will be known. For each candidate there will be a set of legal loop permutations that lead to this minimum degree of synchronization. For example, the candidate space mapping  $\{[k, i] \rightarrow [k]\}$  for statement 1 in Figure 3.8 will produce parallel execution at loop depth 2, only if loop permutation (i, k) is used for statement 1. Similarly, the candidate space mapping  $\{[k, i, j] \rightarrow [j]\}$  for statement 2 will produce parallel execution at loop depth 2, only if one of the following legal loop permutations are used for statement 2:  $\{(k, -j, -i), (k, -j, i), (k, j, -i), (k, j, i)\}$ .

Unfortunately, in this case, because of data dependences, the first statement's permutation: (i, k), can not be used with any of the second statement's permutations:  $\{(k, -j, -i), (k, -j, i), (k, j, -i), (k, j, i)\}$ . In other words, if candidate  $\{[k, i] \rightarrow [k]\}$  is selected for the first statement and candidate  $\{[i, j, k] \rightarrow [j]\}$  for the second statement, then parallelism will not be able to be achieved at loop depth 2 for both statements no matter how the iterations are reordered. Thus, analyzing parallelism for each statement in isolation can lead to overestimation of parallelism.

$<sup>^{1}</sup>$ In my current implementation I simply set L = 10, n = 100, P = 10 and B = 1 or 10, for cyclic and block distributions respectively

Figure 3.8: Gaussian elimination

To address this problem, I consider all pairs of statements (p,q), and determine which candidates of statement p are compatible with which candidates of statement q. Candidate  $C_p$  of statement p is compatible with candidate  $C_q$  of statement q if there exist permutations  $\pi_p$  and  $\pi_q$  for statements p and q respectively such that  $\pi_p$  produces the minimum degree of synchronization for  $C_p$ ,  $\pi_q$  produces the minimum degree of synchronization for  $C_q$ , and  $\pi_p$  is compatible with  $\pi_q$  (see the next subsection on compatible permutations).

This compatibility information will be used when constructing the search problem described in Section 3.2.6 to try to ensure that parallelism is not overestimated as described above. The compatibility tests are only performed on each pair of statements in isolation. It is theoretically possible for each pair of selected candidates to be compatible but for the set of candidates as a whole to be incompatible. However, since transitive dependences are used in determining which permutations are compatible, it is very unlikely that this will occur. This problem has not arisen in any of the examples I have tried. If this ever did occur it would be very easy to detect, and it would be necessary to expand the search space in order to find a compatible solution.

#### Compatible permutations

The following test is used to determine whether permutation  $\pi_p$  for statement p is compatible with permutation  $\pi_q$  for statement q. First, a set of direction vectors is constructed that describe the order in which the iterations of statement q will be executed if loop permutation  $\pi_q$  is applied. These direction vectors do not correspond to actual data dependences, but rather to ordering constraints that will be satisfied if that permutation is used. For example, if permutation (k, i, j) is used for statement 2 in Figure 3.8 then the following set of direction vectors  $\{(0, 0, +), (0, +, *), (+, *, *)\}$  would be constructed. In general, the set will be:

$$c_{qq} = \bigcup_{m \in \{0, \dots, n-1\}} \left\{ \pi_q(\underbrace{0, \dots, 0}_{m}, +, \underbrace{*, \dots, *}_{n-m-1}) \right\}$$

(3.1)

where  $\pi_q(x_1, \ldots, x_n)$  means apply permutation  $\pi_q$  to the vector  $(x_1, \ldots, x_n)$ . Applying a permutation to a direction vector also involves reversing directions as indicated by the permutation. For example, if permutation (k, j, -i) was used for statement 2 then the following set of direction vectors would be constructed  $\{(0, +, 0), (0, *, -), (+, *, *)\}$ .

Next, these ordering constraints are combined with the transitive dependences between statements p and q to infer new ordering constraints on statement p under the assumption that permutation  $\pi_q$  will be used for statement q. The new ordering constraints are:

$$c_{pp} = D'_{pq} \circ c_{qq} \circ D'_{qp} \tag{3.2}$$

This calculation can be performed using either tuple relations or extended direction vectors. Permutation  $\pi_p$  is compatible with permutation  $\pi_q$  if and only if  $\pi_p$  is legal with respect to the new set of ordering constraints  $c_{pp}$ .

For example, if in the example from Figure 3.8,  $\pi_2 = (k, j, -i)$  then:

| $c_{22}$          | = | $\{(0,+,0),(0,*,-),(+,*,*)\}$ | (from Eqn $3.1)$ |

|-------------------|---|-------------------------------|------------------|

| $D'_{12}$         | = | $\{(0,0)\}$                   | (from Fig 3.4)   |

| $D_{21}^{\prime}$ | = | $\{(+, 0+)\}$                 | (from Fig 3.4)   |

| $c_{11}$          | = | $\{(+,*)\}$                   | (from Eqn $3.2)$ |

So permutation (i, k) for statement 1 is incompatible with permutation (k, j, -i) for statement 2 because (i, k) is not legal with respect to  $c_{11}$  (since the permuted direction vector  $\pi_1(c_{11}) = \{(*, +)\}$  is not lexicographically positive).

### 3.2.4 False Sharing on Shared Memory Architectures