#### Abstract

Title of Dissertation: Compiler-Assisted Scheduling for Real-Time Applications: A Static Alternative to Low-Level Tuning

Seongsoo Hong, Doctor of Philosophy, 1994

Dissertation directed by: Assistant Professor Richard Gerber Department of Computer Science

Developing a real-time system requires finding a balance between the timing constraints and the functional requirements. Achieving this balance often requires last-minute, low-level intervention in the code modules – via intensive hardware-based instrumentation and manual program optimizations. In this dissertation we present an automated, static alternative to this kind of human-intensive work. Our approach is motivated by recent advances in compiler technologies, which we extend to two specific issues on real-time programming, that is, feasibility and schedulability.

A task is infeasible if its execution time stretches over its deadline. To eliminate such faults, we have developed a synthesis method that (1) inspects all infeasible paths, and then (2) moves instructions out of those paths to shorten the execution time.

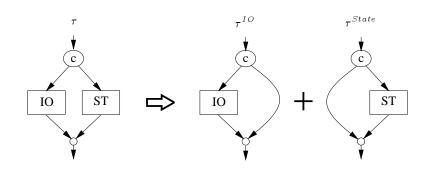

On the other hand, schedulability of a task set denotes an ability to guarantee the deadlines of all tasks in the application. This property is affected by interactions between the tasks, as well as their individual execution times and deadlines. To address the schedulability problem, we have developed a task transformation method based on program slicing. The method decomposes a task into two subthreads: the IO-handler component that must meet the original deadline, and the state-update component that can be postponed past the deadline. This delayed-deadline approach contributes to the schedulability of the overall application. We also present a new fixed-priority preemptive scheduling strategy, which yields both a feasible priority ordering and a feasible taskslicing metric.

## Compiler-Assisted Scheduling for Real-Time Applications: A Static Alternative to Low-Level Tuning

by

Seongsoo Hong

Dissertation submitted to the Faculty of the Graduate School of The University of Maryland in partial fulfillment of the requirements for the degree of Doctor of Philosophy 1994

Advisory Committee:

Assistant Professor Richard Gerber, Chair/Advisor Professor Ashok K. Agrawala Professor John Gannon Professor Virgil Gligor Associate Professor William Pugh Associate Professor Udaya A. Shankar © Copyright by Seongsoo Hong 1994

# Table of Contents

| List of Tables |       |                                         |     |  |  |

|----------------|-------|-----------------------------------------|-----|--|--|

| Li             | st of | Figures                                 | iii |  |  |

| 1              | Intr  | roduction                               |     |  |  |

|                | 1.1   | Motivation                              | 3   |  |  |

|                | 1.2   | Compiler Transformations                | 6   |  |  |

|                |       | 1.2.1 Feasible Code Synthesis           | 6   |  |  |

|                |       | 1.2.2 Real-Time Task Slicing            | 7   |  |  |

|                | 1.3   | Summary of Contributions                | 8   |  |  |

|                | 1.4   | Outline of the Dissertation             | 9   |  |  |

| 2              | Rela  | lated Work 10                           |     |  |  |

|                | 2.1   | Formal Methods                          | 10  |  |  |

|                | 2.2   | Real-Time Programming Languages         | 11  |  |  |

|                | 2.3   | Real-Time Compiler Tools                | 12  |  |  |

| 3              | The   | e Language of Time-Constrained Events 1 |     |  |  |

|                | 3.1   | Design Goals                            | 15  |  |  |

|                | 3.2   | Timing Constructs and Their Semantics   | 16  |  |  |

|                | 3.3   | Example TCEL Code                       | 18  |  |  |

| 4 | Bas                                       | e Notations                                                          | <b>21</b> |  |  |

|---|-------------------------------------------|----------------------------------------------------------------------|-----------|--|--|

|   | 4.1                                       | Flow Graphs                                                          | 21        |  |  |

|   | 4.2                                       | Basic Compiler Definitions                                           | 23        |  |  |

| 5 | Transformation 1: Feasible Code Synthesis |                                                                      |           |  |  |

|   | 5.1                                       | The Problem and Our Solution                                         | 28        |  |  |

|   |                                           | 5.1.1 The Problem of Feasible Code Synthesis                         | 29        |  |  |

|   |                                           | 5.1.2 Solution Strategy                                              | 32        |  |  |

|   | 5.2                                       | Section Decomposition                                                | 33        |  |  |

|   |                                           | 5.2.1 Determining Section Boundaries                                 | 33        |  |  |

|   |                                           | 5.2.2 Deriving Code-Based Timing Constraints                         | 35        |  |  |

|   | 5.3                                       | Code Scheduling                                                      | 38        |  |  |

|   |                                           | 5.3.1 The Top-Level Algorithm                                        | 39        |  |  |

|   |                                           | 5.3.2 Subroutine Schedule_Section $(S, D, DUR(\mathbf{S}), V_{bar})$ | 40        |  |  |

|   | 5.4                                       | Summary                                                              | 49        |  |  |

| 6 | Transformation 2: Real-Time Task Slicing  |                                                                      |           |  |  |

|   | 6.1                                       | Background                                                           | 51        |  |  |

|   |                                           | 6.1.1 Characterization of Discrete Control Software                  | 52        |  |  |

|   |                                           | 6.1.2 Fixed-Priority Preemptive Scheduling                           | 54        |  |  |

|   |                                           | 6.1.3 Scheduling with Compiler Transformations                       | 56        |  |  |

|   | 6.2                                       | Automatic Task Decomposition by Program Slicing                      | 59        |  |  |

|   |                                           | 6.2.1 The Program Slicing Algorithm                                  | 60        |  |  |

|   |                                           | 6.2.2 Assigning Times to Subtasks                                    | 62        |  |  |

|   | 6.3                                       | Scheduling Alternatives and Their Analyses                           | 64        |  |  |

|   | 6.4                                       | Priority Ordering with Task Slicing                                  | 67        |  |  |

|   |                                           | 6.4.1 Feasibility Test                                               | 68        |  |  |

|   |                                           | 6.4.2 The Algorithm                                                  | 68        |  |  |

|   |                                           | 6.4.3 A Larger Example                                               | 69        |  |  |

|   | 6.5 | Summ     | ary                                         | 70 |

|---|-----|----------|---------------------------------------------|----|

| 7 | Pra | ctical   | Considerations and Prototype Implementation | 73 |

|   | 7.1 | Practi   | cal Considerations                          | 73 |

|   |     | 7.1.1    | Limits of Data-Flow Analysis                | 74 |

|   |     | 7.1.2    | Limits of Timing Analysis                   | 74 |

|   |     | 7.1.3    | User Interaction                            | 75 |

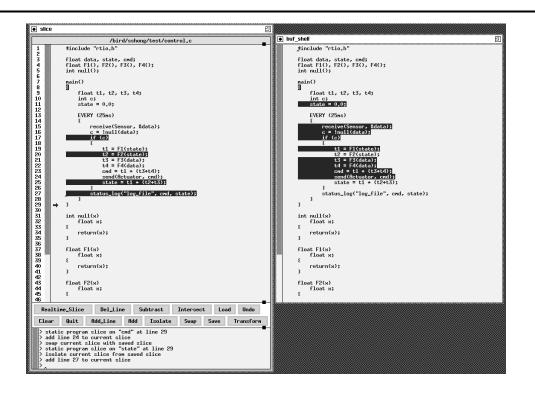

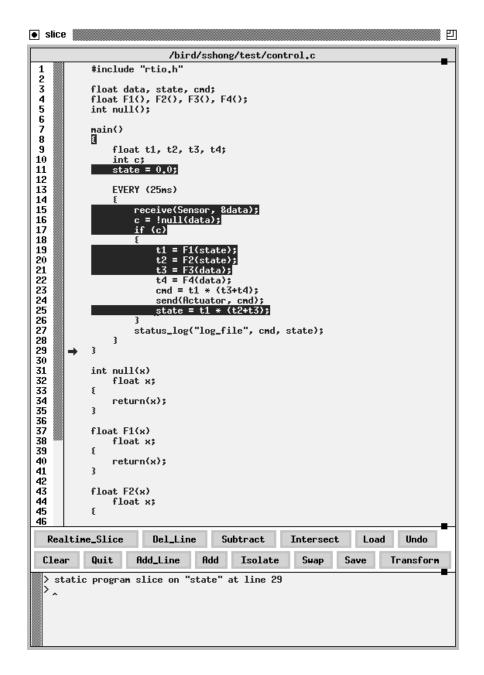

|   | 7.2 | TimeV    | Vare/SLICE: the Prototype Implementation    | 75 |

|   |     | 7.2.1    | TimeWare/SLICE Tool Screens                 | 76 |

|   |     | 7.2.2    | Commands                                    | 76 |

|   |     | 7.2.3    | Implementation                              | 79 |

|   | 7.3 | Summ     | ary                                         | 80 |

| 8 | Con | clusio   |                                             | 81 |

| 0 | Con | iciusioi | 15                                          | 01 |

|   | 8.1 | Future   | Directions                                  | 83 |

# List of Tables

| 5.1 | Timing Constraints of S3 and S4          | 38 |

|-----|------------------------------------------|----|

| 6.1 | Example Task Set                         | 71 |

| 6.2 | Priority Assignment with Program Slicing | 72 |

# List of Figures

| 1.1 | Software Development Process: Two Alternatives                                                                                                                                                                 | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Event-Based Specification of Sensor-Controller System                                                                                                                                                          | 4  |

| 1.3 | Two TCEL Programs with the Same Semantics                                                                                                                                                                      | 5  |

| 1.4 | Run-Time Behavior of a TCEL Periodic Task                                                                                                                                                                      | 8  |

| 3.1 | Flow Graph of <b>do</b> Construct                                                                                                                                                                              | 17 |

| 3.2 | Behavior of Periodic Timing Construct                                                                                                                                                                          | 18 |

| 3.3 | (A) TCEL Source Code for the Flight Controller and (B) Corresponding Flow Graph                                                                                                                                | 20 |

| 5.1 | Software Development Process: Revisited for Feasible Code Synthesis                                                                                                                                            | 28 |

| 5.2 | Flow Graph of <b>do</b> Construct and its Section Division                                                                                                                                                     | 34 |

| 5.3 | Flight Controller Program: After Section Decomposition                                                                                                                                                         | 36 |

| 5.4 | Top-Level Algorithm for Code Synthesis                                                                                                                                                                         | 39 |

| 5.5 | (A) Source Code in TCEL, (B) Corresponding Intermediate Code in GSA Form, (C)<br>Intermediate Code after Bookkeeping-Free Transformations, and (D) Intermediate<br>Code after Transformations with Bookkeeping | 41 |

| 5.6 | Speculative Code Motion: (A) Original Code, (B) Corresponding GSA Code and                                                                                                                                     |    |

| 0.0 | (C) Speculatively Transformed Code                                                                                                                                                                             | 43 |

| 5.7 | The Section Scheduling Algorithm (Schedule_Section)                                                                                                                                                            | 46 |

| 5.8 | The Section Scheduling Algorithm (Sched)                                                                                                                                                                       | 47 |

| 5.9 | Flight Controller Program: After Code Scheduling                                                                                                                                                               | 48 |

| 6.1 | Software Development Process: Revisited for Real-Time Task Slicing                                                                                                                                             | 51 |

| 6.2  | Generalized Slicing Method for Schedulability Tuning                                                                                                                          | 52 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

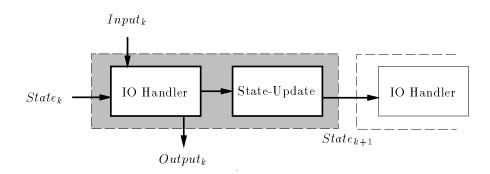

| 6.3  | Task Instance at the $k^{th}$ Period                                                                                                                                          | 53 |

| 6.4  | Dynamic Behavior of Periodically Implemented Control-Loop                                                                                                                     | 53 |

| 6.5  | TCEL Program for Task $\tau_2$                                                                                                                                                | 56 |

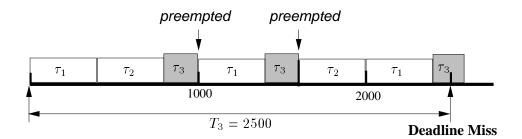

| 6.6  | Simulated Time Line for the Example Task Set                                                                                                                                  | 57 |

| 6.7  | Decomposed Task at the $k^{th}$ Period $\ldots \ldots \ldots$ | 58 |

| 6.8  | Two Decomposed Subtasks of Task $\tau_2$                                                                                                                                      | 58 |

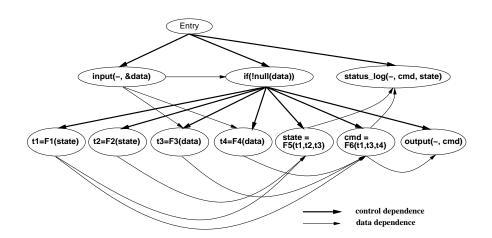

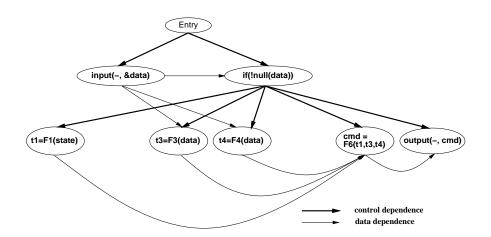

| 6.9  | Program Dependence Graph                                                                                                                                                      | 61 |

| 6.10 | Slice with respect to Criterion $\langle L9, cmd \rangle$                                                                                                                     | 62 |

| 6.11 | Slicing a Conditional                                                                                                                                                         | 63 |

| 6.12 | Algorithm for Priority Ordering with Slicing Decision                                                                                                                         | 70 |

| 7.1  | Tool Screens of TimeWare/SLICE                                                                                                                                                | 77 |

| 7.2  | Output of TimeWare/SLICE                                                                                                                                                      | 78 |

| 8.1  | Software Development Process: Two Alternatives                                                                                                                                | 82 |

#### Chapter 1

## Introduction

A real-time application is characterized by the existence of two competing factors: its functional specification and its temporal requirements. Functional specifications define valid translations from inputs into outputs. As such they are realized by a set of programs, which *consume* CPU time. Temporal requirements, on the other hand, place upper and lower bounds between *occurrences of events* [9, 24]. An example is *the robot arm must receive a next-position update every 10ms*. Such a constraint arises from the system's requirements, or from a detailed analysis of the application environment. Temporal requirements implicitly *limit* the time that can be provided by the system's resources.

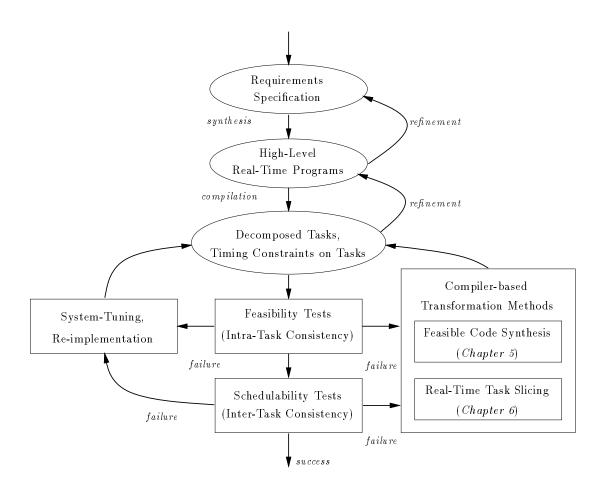

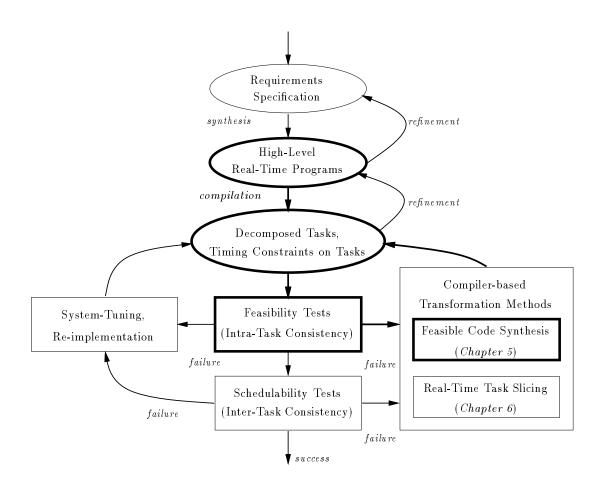

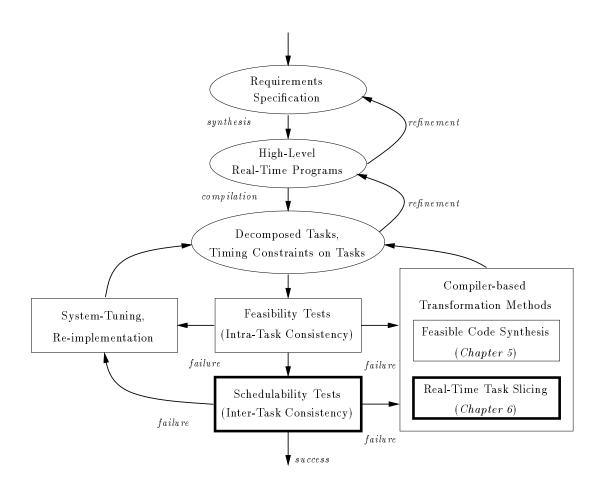

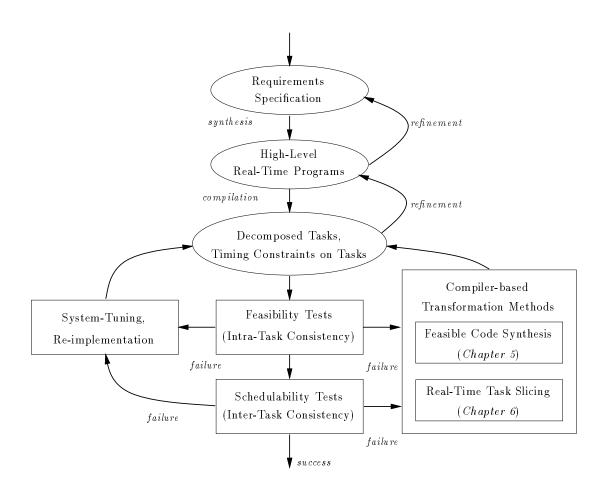

Figure 1.1 illustrates the real-time software development process from a high-level requirements specification to a low-level implementation. First, high-level requirements are translated into real-time programs. Then the programs are compiled into real-time tasks, and timing constraints are imposed on these tasks. After the compilation, the programmers must assure that each of the tasks in the application will meet its timing constraints on the underlying hardware platform. This process is called a *feasibility test*.

The programmers must also assure that the whole application will adhere to the timing constraints, even in the presence of direct and indirect interactions among the tasks, such as task blocking and preemption. This process is called a *schedulability test*. If the programmers cannot guarantee either of the tests, the result is careful refinement of the implementation. As shown in Figure 1.1, we can think of two alternatives as a means for the low-level system refinement: system-tuning and compiler-based task optimization.

Low-level tuning of the application can be a time-consuming process. It often involves using expensive hardware monitors (e.g., in-circuit emulators, logic analyzers, etc.), manually counting instruction-cycle times, hand-optimizing the code, and experimenting with various orderings of

Figure 1.1: Software Development Process: Two Alternatives

operations. As a last resort, entire subsystems may have to be re-designed altogether.

The goal of this dissertation research is to provide programmers with a powerful alternative to low-level tuning. It is based on compiler-based transformation tools. Our approach consists of two inter-related components: a real-time programming language and static compiler transformation methods. The programming language not only provides a means for expressing timing constraints within a source program, but it also lays a foundation for sound compiler transformation methods. As shown in Figure 1.1, our compiler transformation methods include *feasible code synthesis* and *real-time task slicing*.

#### 1.1 Motivation

Our approach is motivated by the success of static compiler transformation technologies in code parallelization and program debugging. It is a natural step to adopt these technologies to real-time domains, where developers lack powerful software engineering tools to apply at the tuning stage. This stage can consume a disproportionate amount of project's budget.

To carry out this approach, it is imperative to find a real-time programming language to provide high-level timing constructs with unambiguous semantics. This allows us to define a class of semantics-preserving transformations for them. Unfortunately, most existing real-time programming languages do not fulfill the requirement. We conceive this as a problem of "code-based specifications."

Consider experimental real-time programming languages which have been proposed in the literature [23, 27, 30, 33, 40]. They provide high-level real-time constructs such as "within 10ms **do** B," where the block of code "B" must be executed within a 10 millisecond time frame. These languages, while providing a convenient framework for *expressing* time in programs, have done little to ease the process of translating a real-time specification into schedulable code.

The reason is straightforward: Language constructs such as "within 10ms do B" establish constraints on *blocks of code*. However, "true" real-time properties establish constraints between the *occurrences of events* [9, 24]. While language-based constraints are very sensitive to a program's execution time, specification-based constraints must be maintained regardless of the platform's CPU characteristics, memory cycle times, bus arbitration delays, etc.

Our approach is to treat a real-time program as (1) an event-based timing specification, which represents the system's real-time requirements; and (2) a functional implementation, that is, the system's code. We carry out this approach with a real-time syntax quite similar to those found in the abovementioned languages. However, in our approach the interpretation is quite different. Instead of constraining blocks of code, the timing constructs establish constraints between the observable events within the code.

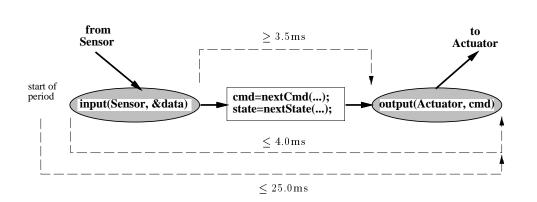

The language we propose is called Time-Constrained Event Language (TCEL). As an example of TCEL code, consider the following specification fragment, which is rendered pictorially in Figure 1.2:

- (1) Every 25ms, an external sensor sends a message to the controller, containing physical world measurement data.

- (2) The controller must receive every message.

- (3) Using the sensor data and the current state, the controller computes a next-position command and sends it to an actuator.

- (4) To achieve steady state, transmission of cmd is made no earlier than 3.5ms after receipt of data.

- (5) To guarantee response-time threshold, transmission of cmd is made no later than 4.0ms after receipt of data.

- (6) Based on the sensor-input, the controller updates its current state.

Figure 1.2: Event-Based Specification of Sensor-Controller System

Within our event-based framework, the program fragments in Figure 1.3 realize the specification. The system's only observable events occur instantaneously during the executions of the "output" and "input" operations. The "do" statement establishes timing constraints only between these two operations. On the other hand, the local statement "cmd = nextCmd(data, state)" is only constrained by the program's natural control and data dependences.

Armed with this interpretation, our compiler treats both programs as having equivalent semantics. This is quite different from the approaches mentioned above, where timing constructs establish constraints on code. In that interpretation, program A would first receive its data, then delay for 3.5ms and finally, evaluate nextCmd and send the result within the remaining 0.5ms. Program B would receive its data, evaluate nextCmd, then delay for 3.5ms and finally, send the result within 4.0ms of evaluating nextCmd.

Both programs may fail to implement the specification on some hardware platforms. If nextCmd is a CPU-intensive function (and thereby requires over 0.5ms of execution time), program A is

```

/* Program A */

every 25ms

do

input(Sensor, &data);

start after 3.5ms finish within 4.0ms

{

cmd = nextCmd(state, data);

state = nextState(state, data);

output(Actuator, cmd);

}

/* Program B */

every 25ms

do

{

input(Sensor, &data);

cmd = nextCmd(state, data);

}

start after 3.5ms finish within 4.0ms

{

state = nextState(state, data);

output(Actuator, cmd);

```

Figure 1.3: Two TCEL Programs with the Same Semantics

}

inherently unschedulable. On the other hand, program B establishes a constraint between the evaluation of nextCmd and the nextState, and not between the two specified events. Both programs would have to be rewritten to achieve the desired effect. The necessary corrections would include manually decomposing nextCmd, as well as adjusting the timing constraints. The actual changes would heavily depend on the particular characteristics of the computer, and thus, the very reason for using high-level timing constructs would be defeated.

There are several immediate benefits to our semantics for real-time constructs. First, a source program is not hardware-specific, and thus maintains the abstract, "portable" spirit of a high-level language. Since the timing constraints refer only to specification-based events, they need not be platform-specific. Second, this decoupling of timing constraints from code blocks enables a more straightforward implementation of an event-based specification.

But of most importance, some of the arduous, assembly-language level hand-tuning can now be accomplished semi-automatically – by compiler optimization techniques. In this dissertation we present two of such techniques: one that relies on Trace Scheduling, and the other based on program slicing. Traditionally, Trace Scheduling has been used in instruction scheduling, etc., and program slicing has been used in program analysis and debugging. Here, the objective is different: to achieve guaranteed real-time performance. In doing this we use the observable events as "signposts," which constrain the places where code can be moved. These events, as well as data dependences, establish the limiting constraints for the optimization algorithm.

#### **1.2** Compiler Transformations

Armed with the event-based semantics of TCEL, we have developed two compiler transformation techniques, which we call *feasible code synthesis* and *real-time task slicing*. The objective of feasible code synthesis is to achieve internal consistency between a task's execution time and its timing constraints specified with "do" constructs. On the other hand, the objective of real-time task slicing is to enhance inter-task schedulability. This transformation is applicable to "every" periodic constructs.

#### 1.2.1 Feasible Code Synthesis

We call a code segment *infeasible* if its execution time stretches over its specified deadline. Feasible code synthesis localizes and corrects such a fault via a two-step process. First, the compiler decomposes a "**do**" construct into a set of code blocks according to the control structure, and then

automatically derives a set of dispatch equations from the language-based timing constraints. This step is necessitated by a gap between the event-based semantics model of source programs and the code-based execution model of real-time schedulers. In fact, most real-time schedulers only accept timing constraints on the start and finish times of *tasks*. The compiler thereby satisfies the scheduler's requirements by transforming event-driven source programs into constrained blocks of code, and providing the dispatch equations for the scheduler.

Next, the compiler attempts to correct feasibility faults with respect to the derived dispatch equations. This is done by a variant of Trace Scheduling, in which worst-case execution time paths of the infeasible task are selected, and unobservable code is moved to shorten their execution time.

For simple illustration, suppose that nextCmd in Program A of Figure 1.3 executes longer than 0.5ms and hence Program A is infeasible. As a solution, "nextCmd(data, state)" can be inlined, and then decomposed into two parts – one which is flow-dependent on the parameters data and state, and another which is invariant of them. This second part can be lifted out of the do statement altogether. We elaborate on this transformation method in Chapter 5.

#### 1.2.2 Real-Time Task Slicing

Real-time task slicing considers a more ambitious goal – inter-task transformations for schedulability. The effect of this transformation is global, though it is individually applied to a small number of tasks selected from an unschedulable application.

The key idea behind this method is based on a simple fact, that is, an application's schedulability improves if we increase the deadlines of its constituent tasks. The same effect is achieved by allowing a task to slide past its deadline, while maintaining the original event-based semantics. We can realize this benefit by transforming a task, so that its time-sensitive component always executes within its frame, while postponing the rest of the task.

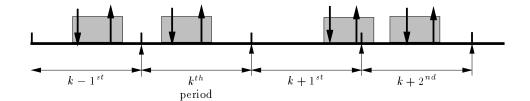

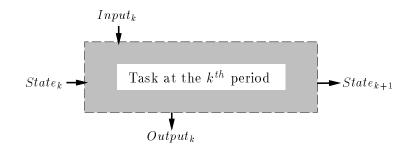

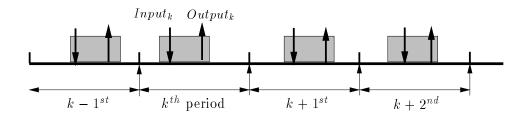

To systematically carry out the transformation, we harness a novel application of *program* slicing [41, 52, 53]. An unschedulable task is decomposed into two subthreads: one that is "time-critical" and the other "unobservable." The unobservable subthread is then appended to the end of time-critical thread, with TCEL semantics being maintained. Figure 1.4 pictorially illustrates the net effect of this transformation. The downward (upward) arrow of the  $k^{th}$  frame represents the execution of input (output) event in the same time frame.

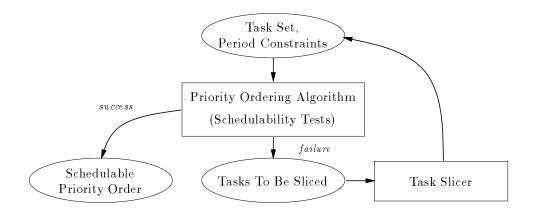

Since the goal of the transformation comes from the scheduler component of the real-time system, the framework consists of the following ingredients.

Figure 1.4: Run-Time Behavior of a TCEL Periodic Task

- (1) An algorithm which uses standard fixed-priority preemptive scheduling analysis to find unschedulable tasks which need task slicing.

- (2) A program slicer which decomposes a task and isolates the thread that can be postponed.

- (3) An online component of the scheduler which enforces precedence constraints between task interactions.

In Chapter 6 we will discuss in detail the fixed-priority preemptive scheduling paradigm as well as the application of program slicing method.

#### **1.3 Summary of Contributions**

The major contributions of this dissertation is itemized as follows:

- The event-based abstraction is a widely used approach in the formal methods literature. We have extended it into a full-blown real-time programming language called TCEL. The event-based semantics of TCEL makes it straightforward to realize a high-level specification into a real-time program. This semantics allows a clear and unique interpretation of high-level timing constructs, and thus enables us to define safe compiler transformations for TCEL programs. Although TCEL has been implemented on top of the C programming language, it can be used with other programming languages such as Pascal or Fortran. It is a general, flexible mechanism for high-level timing annotations, and is not specific to a particular language.

- We have developed an automatic method of translating a high-level TCEL program into schedulable units of code. When implemented within a TCEL compiler, this method decom-

poses a TCEL program into tasks, and then derives code-based timing constraints from the language-based timing constraints. This method automatically refines the original timing constraints to account for the effects caused by programs' control structures.

- We have developed an automatic compiler method that is used to transform an infeasible task into a feasible one. This problem is an intractable one, as will be proved. Thus we have invented an approximation approach based on Trace Scheduling.

- We have developed another compiler transformation method that is used to enhance the realtime schedulability of an input task set. This method automatically decomposes a task so that the real-time scheduling method can guarantee timely execution of observable operations, while local operations need not lead to scheduling overrun.

- We have developed a priority ordering algorithm that not only assigns feasible priorities, but also selects a subset of tasks to be transformed. The guiding metric is schedulability.

#### 1.4 Outline of the Dissertation

This dissertation is organized as follows. In Chapter 2 we survey background and related work. In Chapter 3 we introduce TCEL with an example program. In Chapter 4 we introduce basic notations for flow graphs and standard compiler technologies which are used throughout the dissertation. In Chapter 5 we present the first transformation method, *feasible code synthesis*, along with a motivating example. Then, in Chapter 6 we present the second transformation method, *real-time task slicing*, and we discuss its underlying theory of fixed-priority, preemptive scheduling. In Chapter 7 we consider the practical limitations of our compiler-based approach, and propose solutions to overcome these problems. We also briefly show TimeWare/SLICE, our prototype implementation of the real-time task slicer, which reflects our philosophy on tool-based system development. Finally, in Chapter 8 we conclude this dissertation with future research directions.

#### Chapter 2

## **Related Work**

In this chapter we survey related work in real-time programming. First, we review some of formal methods that have laid the foundation for our event-based semantics. We also study real-time programming languages, since they have influenced the design of TCEL's timing constructs. Finally, we survey compiler-based real-time tools, and compare them with our approach.

#### 2.1 Formal Methods

TCEL's semantics was inspired by a principle commonly applied in formal methods. That is, when reasoning about a real-time concurrent system it is often useful to consider only "events of interest," and to abstract away local-state information. Indeed, almost all formal models ease this process by making some distinction between an "event" and a corresponding "action." In this section we survey four such methodologies: Real-Time Logic [24], RTRL [9], Timed IO Automata [37] and ACSR [29].

**RTL.** Real-Time Temporal Logic possesses an underlying event-action model. It captures the temporal ordering between an application's actions and its events. An action in RTL is the execution of an operation which consumes a certain amount of system resources. The effects of actions are revealed by events that are generated before and after they execute. The occurrence of an event is defined to be instantaneous, while the execution of an action takes non-zero time. Thus a timing constraint is an assertion about temporal relationships between certain events. The conjunction of these timing assertions are "the system specification," and they must imply that key safety properties are maintained.

**RTRL.** RTRL (Real-Time Requirements Language) is a formal specification language developed for use in modeling telephone switching systems. In RTRL, a real-time system is viewed as a finite-state machine, in which a response at any instance is determined by the system's state and the external inputs. Hence the timing constraints are established between external inputs and responses. Unlike the events in RTL, however, these external inputs and responses denote signals (of a switching system) rather than points in time, and thus have duration times.

**Timed I/O Automata.** A timed I/O automaton is essentially a state transition system consisting of state variables and events, where each of the events has an enabling condition and an action. A timed I/O automaton has a set of timing assumptions, each of which specifies an event set and an interval during which the event set can be continuously enabled since its last occurrence. Thus the timing assumptions place constraints on the event-firing times [46]. A "behavioral abstraction" of a timed I/O automaton allows reasoning about only the event sequences, since local state information can be ignored in the abstraction.

**ACSR.** The computation model of ACSR (Algebra of Communicating Shared Resources) addresses two key issues in modeling a real-time system: concurrency and communication. An application specified in ACSR consists of a set of communicating processes that use shared resources for execution and synchronization with one another. A timed action in ACSR takes unit time to execute and consumes a set of resources during that time. Synchronization between actions is supported by events that are instantaneous, and consume no resources.

**Impact of Formal Methods.** Strongly motivated by the event-action models, we have extended the event-action abstraction into to a "full-blown" real-time programming language, in which the "events" correspond to actual IO operations within C code. A logical consequence of the event-action model is the ability to exploit this looser semantics, and to use compiler transformations to move unobservable instructions out of over-constrained code blocks.

## 2.2 Real-Time Programming Languages

Most other real-time languages do not make such a distinction, and instead place constraints on the boundaries of code blocks. Two paradigms are used in these languages: either constraints are expressed directly in the program itself (as in [33, 30, 54]), or they are postulated in a separate interface, and then passed to the scheduler as directives. A common language-based approach (first presented in [30]) is to provide constructs such as "within t do {...}," "at t do {...}" and "after t do {...}." An alternative, taken in [33], is to set up linear constraint expressions on the the start times and deadlines of code blocks. We have borrowed from both approaches: in the TCEL source we use the higher-level constructs, while in our intermediate code we make use of the constraint representation. But in TCEL the semantics is quite different, as it establishes constraints between the observable events within the code, and not on the code's textual boundaries.

#### 2.3 Real-Time Compiler Tools

There have been many other compiler-based approaches to real-time programming, most of which address different real-time programming problems and rely on different techniques. However, they share a common goal, namely, enhancing predictability and schedulability of real-time applications. In this section we survey tools, and then show where we can place our tools in the realm of real-time programming.

Schedulability Analyzer for Real-Time Euclid. Among the early approaches was the schedulability analyzer [49], specifically developed for the timing and scheduling analyses of programs written in Real-Time Euclid [27]. The schedulability analyzer consists of a front-end and a backend. The front-end is incorporated into the code generator of the Real-Time Euclid compiler, and it produces a segment tree that represents compilation units such as modules, monitors or routines. Using a segment tree, the back-end computes the execution time profile of each segment considering synchronization, phasing, and IO between segments, as well as execution times of segments' instructions. We believe that such a technique is infeasible in a practical sense, because it presents an intractable circularity between the compiler-based analyzer and the scheduler. The result of the analysis affects that of scheduling, and vice versa.

**Compiler-Assisted Adaptive Scheduling.** Gopinath and Gupta introduced a technique called compiler-assisted adaptive scheduling in [18]. In their work, the compiler indexes a piece of code into four classes on the basis of predictability and monotonicity. Then it rearranges the code to support adaptive run-time scheduling. Unlike our approach, which is entirely static in terms of both program analysis and scheduling, their approach was developed to aid in dynamic runtime scheduling. However, their work still demonstrates that a successful interplay between the compiler and scheduler is possible without introducing a circularity between them.

**Partial Evaluation**. Partial evaluation may conceptually be understood as compile-time evaluation of constant expressions. Partial evaluation of a source program not only reduces constant expressions in the program into simple values, but also simplifies some control structures such as loops and conditionals. In [39] Nirke and Pugh applied the technique of partial evaluation to realtime programming to produce residual code that is both more optimized and more deterministic.

Safe Real-Time Code Optimizations. Conventional compiler optimizations are designed to reduce the expected or average execution time of programs without taking in account the exact timing behavior of programs. On the other hand, optimizations for hard real-time must meet stringent timing constraints. In [36] Marlowe and Masticola examine a large class of conventional code transformations, and then classify them for application in real-time programming by the notion of safe real-time code transformations. To do so, they assume time-critical statements (or events) in the underlying programming language, and interpret deadlines as relationships between the executions of time-critical statements. This approach comes closest to our work, in that the timing behavior of real-time programs is described in terms of events or the executions of time-critical statements. Unlike the semantics for TCEL, however, the execution times of non-time-critical statements are not explicitly decoupled from timing constraints imposed on the events. This is because the start of a process or start of a critical section is still considered "time-critical." As a result, the applicability of some transformations may be unnecessarily restricted.

**Timing Tools.** Predicting the worst-case execution time of a program is a fundamental requirement to build a real-time application. Indeed, the results of our compiler-based methods rely on timing tools, since both the feasibility and schedulability of tasks are a function of predicted worst-case executions of the transformed tasks.

The technique reported in [42] is based on a simple source-level timing schema, and it is fairly straightforward to implement in a tool. In [19] another approach for more accurate timing was proposed. Since the resulting tool is able to analyze micro-instruction streams using machine-description rules, it is retargetable to various architectures. On the other hand, both approaches do not address the problem of predicting architecture-specific timing behaviors due to various latencies in the memory hierarchy and pipelines. Recently, several approaches have been developed to account for this timing variance. In [55] Zhang et al. presented a timing analyzer based on a mathematical model of the pipelined Intel 80C188 processor. This analysis method is able to take into account the overlap between instruction execution and fetching, which is an improvement over schemes where instruction executions are treated individually. In [44] Arnold et al. developed a

timing prediction method called *static cache simulation* to statically analyze memory and cache reference patterns. A similar but more advanced approach was reported in [32]. While the latter approach is able to predict pipeline stalls as well, both approaches essentially rely on attribute grammars [2] to propagate cache hit information backward in a flow graph.

However, no static timing tool is precise enough to be used with complete confidence for developing production-quality software. Moreover, even sophisticated timing analysis methods such as [32, 44] are not appropriate for fine-grained instruction timing. In Chapter 7 we explain how we can effectively use these tools in spite of the limitations, by also taking advantage of software profiling, as well as static timing prediction. Specifically, our slicing technique does not *require* any static analyzer: it can be used to first transform the program, with the timing carried out later by a runtime profiler.

### Chapter 3

## The Language of Time-Constrained Events

In this chapter we present TCEL's timing constructs to express timing constraints within a highlevel program. These high-level timing constructs make explicit reference to *observable events* as well as *time*, so that the specification-level timing constraints can be extracted from the source code, and then conveyed to real-time schedulers.

#### 3.1 Design Goals

The objectives of the TCEL design are (1) to lay a semantic foundation for developing safe real-time compiler transformation techniques; and (2) to provide high-level timing constructs that enable a compiler to automatically translate a high-level real-time specification into executable code. In addition to these, the design of the timing constructs is motivated by the following practical goals:

- To add a minimal set of features to existing languages. To this end, we embedded timing constructs in C, and then extended it as a real-time programming language. Our constructs are syntactic descendents of the *temporal scope* in [30].

- To keep the definition of an observable event as general as possible. The notion of an observable event is a relative term depending on the application system. We support a generalizable mechanism in that observable events are classified by the programmer, and the resulting event specification is externally provided for a TCEL compiler. Such a specification may include input and output operations, message passing primitives and memory accesses to shared variables. For simplicity, in the sequel we consider all "input" and "output" operations to be observable.

#### **3.2** Timing Constructs and Their Semantics

We first elaborate the "do" construct which establishes several types of relative timing constraints. Its general form is as follows.

> do  $\langle \text{reference block} \rangle$ [start after  $t_{min}$ ] [start before  $t_{max1}$ ] [finish within  $t_{max2}$ ]  $\langle \text{constraint block} \rangle$

The reference block (RB) and the constraint block (CB) are simply C statements, or alternatively, timing constructs themselves. The "do" construct induces the following timing constraints:

- start after  $t_{min}$ : There is a minimum delay of  $t_{min}$  between the last event executed in the RB, and the first event executed in the CB.

- start before  $t_{max1}$ : There is a maximum delay of  $t_{max1}$  between the last event executed in the RB, and the first event executed in the CB.

- finish within  $t_{max2}$ : There is a maximum delay of  $t_{max2}$  between the last event executed in the RB, and the last event executed in the CB.

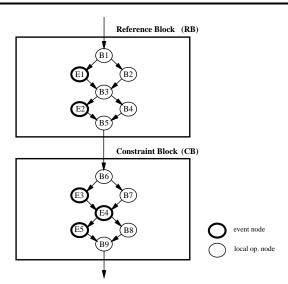

Since either block may contain conditionals, depending on the program's state there may be several such events executed either "first" or "last." For example, consider the fragment from a typical flow graph in Figure 3.1.

Depending on the path taken, the last event executed in the reference block may be either E1 or E2. Similarly, the first event in the constraint block will be E3 or E4, while the last event will be either E4 or E5. To denote such possibilities, we introduce two mappings FIRST and LAST from code blocks to sets of events. That is,  $LAST(RB) = \{E1, E2\}$ ,  $FIRST(CB) = \{E3, E4\}$  and  $LAST(CB) = \{E4, E5\}$ . Thus, the "do" construct introduces two potential constraints between an executed event from LAST(RB) and another from FIRST(CB), as well as one constraint between two executed events from LAST(RB) and LAST(CB) each.

The second real-time construct denotes a statement with cyclic behavior of a positive periodicity:

every p [while (condition)] [start after  $t_{min}$ ] [start before  $t_{max1}$ ] [finish within  $t_{max2}$ ] (constraint block)

Figure 3.1: Flow Graph of **do** Construct

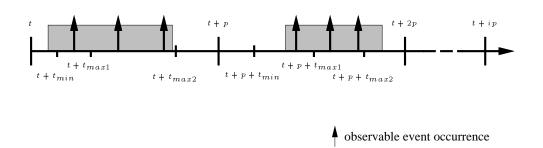

As long as the "while" condition is true, the observable events in the constraint block execute every p time units. Akin to an untimed while-loop, when the condition evaluates to *false* the statement terminates. However, unlike the untimed counterpart, event operations cannot be part of the condition. In its real-time behavior, the interpretation of the "every" construct is similar to that of "do." For example, assume that the statement is first scheduled at time t, and that the "while" condition is true for periods 0 through i. The periodic constraints established by this statement are depicted in Figure 3.2, where the time-line shows the first two instances of the statement.

Examining the time-line, we see that the **every** statement is released at time t, and that within the first frame, the first observable event (denoted by an arrow) occurs between  $t + t_{min}$  and  $t + t_{max1}$ . Similarly, the first frame's last event occurs before  $t + t_{max2}$ . Generalizing, the following constraints are induced for period i where  $i \ge 0$ :

- start after  $t_{min}$ : The first event executed in the CB occurs after  $t + i \cdot p + t_{min}$ .

- start before  $t_{max1}$ : The first event executed in the CB occurs before  $t + i \cdot p + t_{max1}$ .

- finish within  $t_{max2}$ : The last event executed in the CB occurs before  $t + i \cdot p + t_{max2}$ .

Figure 3.2: Behavior of Periodic Timing Construct

#### 3.3 Example TCEL Code

As we have stated, timing constructs may be arbitrarily nested. Consider the program in Figure 3.3(A), which is a (very gross) 2-dimensional abstraction of an aircraft navigation/control loop. A set of route coordinates are maintained in the array "GOAL," which is managed by another module. These coordinates are accessed using index variable "i," which is initialized before the periodic loop, and updated within the loop body. The TCEL program's role is to (1) sample the aircraft's current coordinates, its (true) heading, roll, and its ground speed; (2) get the next route coordinate to visit; (3) compute the relative attitude between the heading and the coordinate; and (4) adjust the course by updating throttle and roll. Adjustments are made in discrete increments, and are contingent on the *current* roll and velocity, as well as the amount that the course must be changed.

The timing constraints are induced as follows:

- (1) Control updates are made periodically, with rate 50/second.

- (2) In order to give the actuators time to get updated (and for the craft to respond accordingly), all updates must be made within the first 5ms of each period.

- (3) Velocity (ground speed) is obtained via a "request-response" protocol from an external unit; the response arrives with maximum latency of 0.75ms.

- (4) To correlate ground speed with outputs, all throttle and flap updates must be made within of 3.1ms of actual ground speed sample. In the best case this may be made upon issuing the request.

- If the specification mandated additional timing constraints, clearly we could employ further

levels of nesting to achieve them. For example, suppose we desired to add a fifth timing requirement to the four listed above:

(5) The final two outputs must be correlated within 0.5ms of each other. (This is not unrealistic, since the two outputs control are coordinated to effect the angular adjustment.)

To accomplish this we would replace the sequential composition with an additional nested TCEL statement:

do

output(THROT, throttle);

finish within 0.5ms

output(FLAP\_Cntrl, wflap);

The net runtime effect would simply be a refinement of the potential behaviors; i.e., the time-event relationships exhibited by the altered program would be a subset of those in the original version.

```

every 20ms finish within 5ms

\mathbf{do}

Periodic

/* Get current position, heading & roll */

input(GPS, &x, &y);

input(NAV, &theta);

input(IMU, &roll);

input(GPS, &x,&y)

/* Request current velocity */

input(NAV, &theta)

output(Cntrl_out, REQ_VEL);

input(IMU, &roll)

start after 0.75ms finish within 3.1ms

output(Cntrl_out, REQ_VEL)

/* Get current velocity */

input(Cntrl_in, &vel);

.75ms

/* Update target position */

input(Cntrl_int, &vel)

if (GOAL[i].passed) {

if(GOAL[i].passed)

gx = GOAL[i].x;

true

gy = GOAL[i].y;

gx=GOAL[i].x

ğy=GOAL[i].y

i=(i+1)%NCOORD

i = (i+1) \% NCOORD;

rtheta=compRelAtt(theta, x,y, gx,gy)

if(|rtheta|<EPS)

/* Using relative attitude w.r.t target, */

true

/* compute angular adjustment.

*/

if(vel<VHIGH)

dtheta=0.0

rtheta = compRelAtt(theta, x, y, gx, gy);

true

dtheta=rtheta

if (|\text{rtheta}| < \text{EPS})

dtheta = 0.0;

else {

if(vel < VHIGH)

wflap=compFlapw(roll,vel,dtheta)

throttle=compThrot(roll,vel,dtheta)

dtheta = rtheta;

else

output(THROT, throttle)

dtheta = safeDtheta(rtheta, roll);

}

output(FLAP_Cntrl, wflap)

/* Adjust flap and throttle for heading. */

wflap = compFlapw(roll, vel, dtheta);

throttle = compThrot(roll, vel, dtheta);

output(THROT, throttle);

tmin tmax1 tmax2

output(FLAP_Cntrl, wflap);

Entry Node

}

```

20ms

5ms

3.1ms

false

false

safeDtheta(rtheta,roll)

Exit Node

false

dtheta =

Reference Block (RB)

**Constraint Block (CB)**

## Chapter 4

## **Basic Notations**

The output of the TCEL compiler's machine-independent pass is the code in an intermediate representation, encapsulated in a *flow graph* [2]. We extend the format of a flow graph to hold the original timing information. For example, Figure 3.3(B) shows the extended flow graph for our flight controller program in Figure 3.3(A), where for the sake of brevity we have left the code in its original C form. In this chapter we first introduce two types of flow graphs, and then define basic notations of standard compiler technologies. These notations include a data structure called a *program dependence graph*, and a code representation called *static single assignment* form. We will use these notations throughout this dissertation.

#### 4.1 Flow Graphs

A flow graph is a natural representation of an intermediate program from which other important information (such as data and control dependences) is extracted by standard static analysis techniques. In order to help compilers deal with nested program structures we define a hierarchical flow graph as well as a standard flow graph.

**Flow Graph.** A flow graph is a standard, flattened representation of a program, in which a node denotes a fragment of straight-line code and an edge specifies potential flow of control from one node to another.

**Definition 4.1** A flow graph FG(B) of code block B is a directed graph

where V is a set of basic blocks of B, and the two distinguished nodes entry(B) and exit(B) that denote the unique entry and exit of B, respectively. E is a set of edges representing potential control flow.

**Hierarchical Flow Graph.** It is sometimes necessary to explicitly specify the program's original hierarchical levels of scoping in a flow graph. We call this structure a *hierarchical flow graph*.

**Definition 4.2** A hierarchical flow graph HFG(B) of code block B is a directed graph

where V is a set of nodes, and E is a set of edges representing potential control flow between nodes. A vertex  $n \in V$ , however, may be either a basic block of B, an entry node, an exit node, or another hierarchical flow graph HFG(B').

Thus all nested constructs, including loops, are reduced into single nodes in a hierarchical flow graph. In our work we do not lift code out of loops, and thus we treat HFG's as acyclic graphs, since we can ignore all back edges.

Of course our hierarchical structure assumes that the underlying programming language is "perfectly structured." That is, any two statements  $S_1$  and  $S_2$  in the program are in one of the following forms:

- 1.  $S_1$  is contained in  $S_2$ ;

- 2.  $S_2$  is contained in  $S_1$ ; or

- 3.  $S_1$  and  $S_2$  are disjoint.

Since many real-time programming languages allow only "structured" programs without unrestricted  $gotos^1$ , we assume that our programs possess this property.

Since nodes in both a flow graph and a hierarchical flow graph have the same interface and structure, all notations defined for a flow graph are used in a hierarchical flow graph. We can easily extend traditional compiler terminology to HFG's as well. In the following sections we define basic compiler notations for HFG(B) = (V, E, entry(B), exit(B)).

<sup>&</sup>lt;sup>1</sup>We disallow **break** statement as well, since it is a special instance of **goto**.

#### 4.2 **Basic Compiler Definitions**

**Paths.** A path (or trace) between  $n_1, n_2 \in V$  is denoted by " $n_1 \rightarrow b n_2$ ," where b is the sequence of nodes traversed between (and including)  $n_1$  and  $n_2$ . When b includes a node  $m \in V$ , we denote this by overloading the set membership operator, i.e., as " $m \in b$ ."

We also use the path relation, but omit the actual path, to denote the existence of *some* path between two nodes, i.e.,

$$n_1 \to n_2 \stackrel{\text{def}}{=} \exists \ b :: n_1 \to^b n_2$$

We assume that for any node  $n \in V, n \to n$ .

**Dominator and Postdominator.** A node d is called a *dominator* of node n, if every path from *entry*(B) to n goes through d. Similarly, a node p is a *postdominator* of node n, if every path from n to *exit*(B) goes through d [2].

**Data dependence.** Let Def(n) and Use(n) be sets of variables defined and used by node n in B, respectively. For instructions  $s_1, s_2 \in B$ ,  $s_2$  is *data dependent* on  $s_1$  (denoted " $s_1 \stackrel{d}{\rightarrow} s_2$ ") iff there is a path b such that  $s_1 \rightarrow^b s_2$  and

$$\exists v \in Def(s_1) \cap Use(s_2) :: (\forall s \in B :: (s \in b) \land v \in Def(s)) \Rightarrow s = s_1)$$

For instructions  $s_1$  and  $s_2$  in B, we say that  $s_2$  is *transitively* data dependent on  $s_1$  (denoted " $s_1 \stackrel{d}{\longrightarrow} s_2$ ") iff there is a path

$$s_1 \stackrel{d}{\rightharpoonup} s'_1 \stackrel{d}{\rightharpoonup} s''_1 \stackrel{d}{\rightharpoonup} \dots \stackrel{d}{\rightharpoonup} s_2$$

We extend the notion of data dependence for nodes of *HFG*. For nodes  $n_1, n_2 \in V$ ,  $n_2$  is *data* dependent on  $n_1$  (denoted " $n_1 \stackrel{d}{\longrightarrow} n_2$ ") iff

$$\exists s_1 \in n_1, s_2 \in n_2 :: s_1 \stackrel{d}{\rightharpoonup} s_2.$$

**Control Dependence.** For nodes  $n_1, n_2 \in V$ ,  $n_2$  is *control dependent* on  $n_1$  (denoted " $n_1 \stackrel{c}{\rightharpoonup} n_2$ ") if one of the following holds:

- 1.  $n_1$  is an entry vertex and  $n_2$  is not nested within any loop or conditional; or

- 2.  $n_1$  represents a control predicate and  $n_2$  is immediately nested within the loop or the conditional whose predicate is represented by  $n_1$ .

Our definition of control dependence is simpler than that found in [11], since it covers a restricted language possessing only structured program constructs.

**Reaching Definitions.** For a node  $n \in V$  and an expression e in B, we define reaching definitions RD(n, e) as a set of nodes m such that

$$\exists b ::: (m \to^b n \land \exists v \in Def(m) \cap Use(e) :: \forall n' \in V ::: ((n' \in b) \land v \in Def(n')) \Rightarrow n' = m).$$

In other words, RD(n, e) is a set of nodes whose definitions of some variables in Use(e) are available at node n.

**Dependence Closure (Static Backward Program Slice).** The dependence closure for node n in the block B, denoted by "DC(n, B)," contains n and all nodes m that reach n via zero or more control or data dependence edges. It is inductively defined by the following least fix-point operation:

$$\begin{array}{lll} DC(n,\mathbf{B}) &=& fix \ F(\{n\}), \ \text{where} \\ F(S) &=& \{m \in V \,|\, \exists \, n' \in S :: m \stackrel{d}{\longrightarrow} n' \ \lor m \stackrel{c}{\longrightarrow} n'\} \ \cup S \end{array}$$

When we are concerned only with data dependences, we make use of *data dependence closure*, "DDC(n, B)" defined as below.

$$DDC(n, \mathbf{B}) = \{ m \in V \mid m \stackrel{d}{\longrightarrow} n \} \cup \{ n \}$$

In fact, a dependence closure and a data dependence closure are equivalent to a static backward program slice and a static data slice, respectively [52].

**Program Dependence Graph.** A program dependence graph is an intermediate program representation that stores both the data and control dependences for each operation in a program.

Formally, the program dependence graph is a directed graph PDG(B) = (U, W), where

- The vertex set U is equal to V in HFG(B).

- The edges W are of two sorts: either a control dependence between  $n_1$  and  $n_2$  such that  $n_1 \stackrel{c}{\longrightarrow} n_2$ , or a data dependence between  $n_1$  and  $n_2$  such that  $n_1 \stackrel{d}{\longrightarrow} n_2$ .

In addition, we define " $m \Rightarrow_* n$ " to mean that there is a path starting from node n and ending at node q in PDG(B).

**Static Single Assignment Form.** The static single assignment (SSA) form of a program can be considered not only as a sparse representation of flow data dependences, but also as a notation where the spurious data dependences such as output and anti-dependences are eliminated [7, 8].

A program is defined to be in SSA form if each use of a variable is reached by exactly one assignment to it [8]. Thus, a program's SSA representation can be obtained iteratively applying the following process: For each variable in the program, (1) unique names are given to all of its appearances on the left-hand-side of an assignment; and (2) all of the uses reached by that assignment are renamed to correspond to the new name. The following examples demonstrate this process. In the straight line code, each assignment to a variable is given a subscripted name, and all of its uses are then renamed as well.

$$\begin{array}{ll} v = f(); & v_1 = f(); \\ a = v + 1; & a = v_1 + 1; \\ v = g(); & v_2 = g(); \\ b = v + 2; & b = v_2 + 2; \end{array}$$

Conditional statements require a bit more work in achieving the SSA form. At confluence points in the CFG, merge functions called  $\phi$ -functions are introduced. A  $\phi$ -function for a variable merges its possible values from distinct incoming control flow paths, and produces one argument for each control flow predecessor.

if cond

then

$$v = f();$$

else  $v = g();$   $\Longrightarrow$

$a = v;$

$p = cond;$

if  $P$

then  $v_1 = f();$

else  $v_2 = g();$

$v_3 = \phi(v_1, v_2);$

$a = v_3;$

In addition to a confluence point immediately following a conditional, another type of confluence point exists at every loop header. For each variable v defined in a loop body, two values of v, namely one assigned v before the loop, the other within the loop, merge at the confluence point of the loop header. Thus a  $\phi$ -function for v is introduced there.

Here we denote the value initialized before the loop by  $\mathbf{v}_0$  (subscript 0).

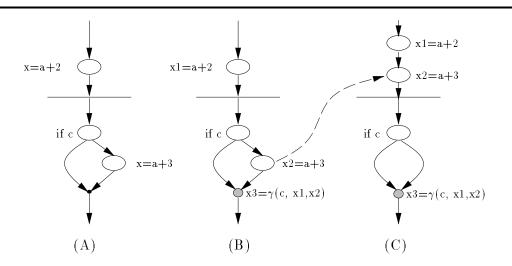

Gated Single Assignment Form. Although SSA form allows for efficient representation of data flows in a program, it possesses a weakness in terms of program transformability. For example, in the above code the  $\phi$ -function is structurally bound to the conditional "if P," since the  $\phi$ -function " $v_3 = \phi(v_1, v_2)$ " can be executed only after the outcome of "P" is known. Such a coupling will be avoidable, if we parameterize the  $\phi$ -function with the associated predicate.

Gated single assignment (GSA) form solves this problem [20]. GSA form is an extension of SSA form with new functions that encode control over value assignment. The following code fragments show translation from a conditional into the code in GSA form.

if cond then v = f();else v = g();  $\Longrightarrow$  a = v; p = cond;if P then  $v_1 = f();$ else  $v_2 = g();$   $v_3 = \gamma(P, v_1, v_2);$  $a = v_3;$

The  $\gamma$ -function denotes the extension. The first argument of the  $\gamma$ -function is the predicate associated with the original  $\phi$ -function and its remaining arguments are the same as the  $\phi$ -function. Having our intermediate programs in GSA form, we can treat  $\gamma$ -functions in the same way as we deal with any other statement.

In GSA, loops need a special form of pseudo-assignment function other than a  $\gamma$ -function. The reason is the confluence points at loop headers are not associated with particular conditional predicates. Thus for each variable v defined in a loop body, a definition  $v' = \mu(v_{init}, v_{iter})$  is inserted at the loop header, where  $v_{init}$  is the initial value of v reaching the header from outside and  $v_{iter}$  is the iterative value reaching along the back-edge of the loop [20]. In our example below we denote  $v_{init}$  and v' by  $v_0$  and  $v_1$ , respectively.

#### Chapter 5

## **Transformation 1: Feasible Code Synthesis**

In this chapter we address translating a TCEL program into a low-level representation eligible for real-time scheduling. To give a clear understanding of the problem domain, consider Figure 5.1. Our problem domain at hand – denoted by the components with bold lines – actually contains two problems. The first problem lies in compiling a TCEL program into the schedulable units, and the second problem deals with attaining the feasibility of an infeasible task.

We approach the first problem with a compiler-based decomposition method. This method enables a TCEL compiler to automatically translate a TCEL source program into a set of decomposed tasks, and it derives a set of timing equations for them. Later, at runtime, a scheduler benefits from this decomposition method, since it can efficiently dispatch the tasks according to their time schedules (or priorities) based on both their execution times and associated timing equations.

The second problem arises when any task is determined to have an execution time conflicting with the derived timing constraints. In this case, it is impossible for any scheduler to generate a feasible schedule for the task set. We develop a compiler transformation method to automatically correct such feasibility faults based on a variant of Trace Scheduling [12]. We name this method *feasible code synthesis*. In this method, the compiler picks the worst-case execution time paths of an infeasible task and moves unobservable code to eliminate the overload.

The remainder of this chapter is organized as follows. In Section 5.1 we formally state the feasible code synthesis problem, and show that it is essentially an intractable problem. Then we briefly discuss our solution strategy. In Sections 5.2 and 5.3 we explain the transformation strategy.

Figure 5.1: Software Development Process: Revisited for Feasible Code Synthesis

### 5.1 The Problem and Our Solution

Compiling a TCEL program into schedulable code raises two fundamental issues, which are endemic to all real-time systems.

- 1. A program may not be *feasible*, i.e., a single process's execution time may conflict with its own real-time constraints.

- 2. While the program may be feasible, it may not be *schedulable* under any tractable real-time scheduling algorithm.

As for the feasibility problem, consider the following TCEL fragment:

```

do

input(P, &m);

start after 10ms finish within 20ms

{

input(Q, &x);

S; [20ms]

output(R, y);

}

```

The code's timing constraints mandate a 10ms latency between the events generated by "input(P, &m)" and "input(Q, &x)," as well as a 20ms deadline between the events generated by "input(P, &m)" and "output(R, y)." Meanwhile, the bracketed "20ms" denotes that the unobservable statement S requires a maximum of 20ms to execute, a bound obtained by a timing analysis tool (e.g., [19, 32, 42, 47, 55]). Consequently, the program possesses an inherent conflict, since S requires 20ms to execute while it is only allowed 10ms.

We address this problem by an approach we call *feasible code synthesis*. In our example this would involve decomposing S and, if possible, moving instructions not dependent on " $\mathbf{x}$ " out of the overloaded section. However merely achieving feasibility may be of little help, since the transformed code may still not be schedulable under any known methods. For example, when a program contains if-then-else branches, then the actual execution paths (and the events executed) are determined dynamically. But since schedulers must provide guarantees, they do not have the flexibility to instantaneously, dynamically reschedule a task set whenever an event is triggered. Indeed, while an event-based semantics makes conceptual sense at the source-program level, most real-time schedulers only accept timing constraints on the start and finish times of *tasks*.

Since the strategies used to achieve feasibility have a profound affect on the ultimate task structure, we solve these two problems together. Thus the role of the TCEL compiler is to partition event-driven source programs into time-constrained blocks of code, in which all of the blocks are feasible.

### 5.1.1 The Problem of Feasible Code Synthesis

Even without the code block partitioning component, achieving feasibility is a nontrivial problem. This is obviously the case if we allowed potentially unbounded loops (or conditional jumps), which would render the problem undecidable. But since real-time programs must be amenable to worstcase timing estimates, we assume that upper bounds can be obtained for execution times. Formally, we let "wt(S)" denote a statement's worst-case execution time, where we assume that  $wt(S) \in [0, \infty)$  for any statement S. Obviously "wt" is implementation dependent, and its tightness is determined by the quality of the analysis tool used to generate the bound.<sup>1</sup>

While the feasibility problem may be decidable for our domain, it is not necessarily trivial. Even when a program is structured like our example above, and where S is a *basic block*, simply deciding whether the program can be made feasible is still NP-hard.

The problem can be stated as follows: given a TCEL timing construct

### do RB start after $t_{min}$ start before $t_{max1}$ finish within $t_{max2}$ CB

is it possible to transform RB and CB to meet the following constraints?

- (1) On any execution path, the original ordering of observable events is maintained.

- (2) The original data and control dependences are not violated between instructions and events.

- (3) The code's execution time does not conflict with the timing constraints between the events.

Clauses (1)-(2) imply that the transformed code must be functionally correct: events may not be reordered, and the original relationships between input and output data must be maintained. Clause (3) means that the new code is feasible.

This problem is NP-hard, due to the existence of immovable operations and data dependences.

#### **Theorem 5.1** Feasible code synthesis is NP-hard.

**Proof:** The proof follows by a straightforward transformation from "Partition[SP12]" [13] to feasible code synthesis. Consider an instance (A, s) of Partition, where  $A = \{a_1, a_2, \ldots, a_n\}$  is a set of elements, and where  $s : A \mapsto \mathbb{N}$  is the cost of each element. Letting  $\sum_{i=1}^{n} s(a_i) = 2T$ , a partition of A is some  $A' \subseteq A$  such that  $\sum_{a \in A'} s(a) = T = \sum_{b \in A - A'} s(b)$ . Determining whether such an A'exists is equivalent to determining whether the following TCEL program can be made feasible:

<sup>&</sup>lt;sup>1</sup>We return to this issue in Chapter 7.

do  $E_1$ : input(P, &x);start after T start before T finish within 2T{  $E_2$ : output(Q, g(x)); $[s(a_1)]$  $L_1$ :  $x_1 = f_1(\mathbf{x});$  $L_2$ :  $x_2 = f_2(\mathbf{x});$  $[s(a_2)]$ :  $x_n = f_n(\mathbf{x});$  $L_n$ :  $[s(a_n)]$ **output**( $\mathbf{R}$ ,  $\mathbf{h}(x_1,\ldots,x_n)$ );  $E_3$ : }

Here  $E_1 - E_3$  generate events,  $L_1 - L_n$  are unobservable instructions, and each line is considered atomic (that is, a line must be relocated as a single entity). Then by the construction,

- (1)  $E_2$ ,  $L_1 L_n$  are mutually data independent.

- (2)  $E_2$ ,  $L_1 L_n$  are data dependent on  $E_1$ .

- (3)  $E_3$  is data dependent on  $L_1 L_n$ .

If we assume that  $wt(L_i) = s(a_i)$  for  $1 \le i \le n$ , and that  $wt(E_j) = 0$  for  $1 \le j \le 3$ , then there exists a partition of our original set A if and only if there is a feasible transformation for the program.

As for the "only if" part, assume there is a partition  $A' \subseteq A$ . Then for all  $a_i \in A'$ , moving the corresponding instruction  $L_i$  between the events  $E_1$  and  $E_2$  ensures feasibility: exactly T execution time is consumed between  $E_1$  and  $E_2$ , and another T is used between  $E_2$  and  $E_3$ .

As for the "if" part, assume there is a feasible transformation. Then, since 2T execution time is used overall, the constraints mandate that exactly T of it be used between  $E_1$  and  $E_2$ , and the rest between  $E_2$  and  $E_3$ . Thus we must move some set of instructions  $L \subseteq \{L_1, \ldots, L_n\}$  between  $E_1$  and  $E_2$ , where  $\sum_{L_j \in L} wt(L_j) = T$ . But then the corresponding elements in A form a partition.  $\Box$

When both the constraint block and reference block consist of straight-line code, the problem is obviously in NP as well. A feasible ordering can always be "guessed" and then verified, which consequently yields the following corollary.

**Corollary:** Feasible code synthesis is NP-complete for straight-line code.  $\Box$

#### 5.1.2 Solution Strategy

In proving Theorem 5.1 we used the simplest possible TCEL program, which possessed just two basic blocks. In this case a feasible transformation would simply reorder the instructions, while keeping the program's fundamental structure intact.

But the situation gets significantly more complicated when the program possesses branches, and when the events that get executed are determined at runtime. Since attaining feasibility mandates that we statically guarantee the timing constraints along *all* execution paths, reordering the instructions along a *single path* may not be sufficient. In the worst of all cases, all paths of a multi-branching program would have to be "expanded," and then each one reordered individually – potentially requiring time *and* space exponential in the original number of instructions. Clearly this is not an attractive solution approach. Moreover, it would render the problem of *schedulable* task decomposition – our second objective – next to impossible.

Thus we take the following alternative approach, in which feasible tasks are synthesized in a two-step process – section decomposition (Section 5.2) and code scheduling (Section 5.3).

Section Decomposition. First the code is translated into its gated single assignment (GSA) form [8, 20]. This representation serves two purposes: (1) it yields a compact means of representing the data-dependence relation discussed in Chapter 4; and (2) GSA's convention of uniquely naming each variable assignment is precisely what we require in the code transformations phase.

Next, the timing construct is decomposed into *sections*, which represent the natural schedulable "task" units. This step involves determining the section boundaries, as well as generating a set of dispatch equations that constrain the start and finish times of each section.

**Code Scheduling.** In this step the dispatch equations are checked for their consistency with the code's execution time. If there is an inconsistency, program transformations are used to relocate unobservable code across section boundaries.

The algorithm is a greedy approximation, in that each section is processed locally, with the goal of attaining consistency for an entire program. The following strategy is used: if a given section is determined to be over-constrained, code is moved out of the section and "up" on the HFG. After the section at hand is determined consistent, another section can be processed in reverse topological order. Thus the net result is an "upward migration" of unobservable instructions, which terminates either when the program achieves consistency, or it is determined to be inconsistent.

An analogous strategy is used for programs with nested timing constructs. In this case the HFG

is scheduled in a "bottom-up" manner. That is, the innermost nodes in the HFG are scheduled first, with the goal of satisfying their local constraints. Then, the surrounding node is handled. If this level is found inconsistent, the inner nodes are "opened up" once again, and more aggressive optimization is carried out.

The actual transformations are similar to those used in Trace Scheduling [12]. As the name implies, the Trace Scheduling algorithm works on specific traces: it selects a path (or trace) from a given code block, and then selects instructions on that path to move. Such an approach is well suited to our purpose, because it can focus on the traces that have the maximum execution time among all traces within a given code block.

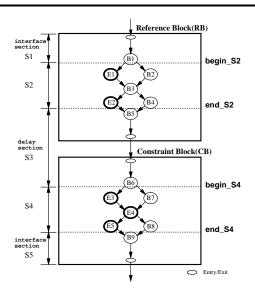

### 5.2 Section Decomposition

Section decomposition is the process of decomposing the program into a set of "code blocks" (or *sections*). The input is the original HFG (e.g., that portrayed in Figure 3.3(B)), with the output being a slightly different HFG, which is more amenable to real-time dispatching. This involves dividing a timing construct into five code sections, as portrayed in Figure 5.2. As can be seen, the reference block is decomposed into three sub-blocks. The unobservable code before the first observable statement becomes an interface section (S1). The code containing the observable statements becomes the reference section (S2). The unobservable code after the observable statements becomes the first part of the delay section (S3). Consequently, the topmost unobservable code of the constraint block becomes the second part of S3, and so on.

### 5.2.1 Determining Section Boundaries