# ABSTRACT

# Title of Thesis: REMAINING LIFE ASSESSMENT PROCESS OF ELECTRONIC SYSTEMS

Vidyasagar Shetty, Master of Science, 2003

# Thesis directed by: Dr. Michael Pecht, Professor Department of Mechanical Engineering

The remaining life assessment (RLA) process is a reliability prediction process, which predicts amount of life left in a system. Remaining life assessment is performed on hardware, which has already seen operational life. This thesis details the remaining life assessment process in detail and also provides a case study of remaining life assessment performed on the Shuttle Remote Manipulator System (SRMS). The electronics of Shuttle Remote Manipulator System was designed in the 1970s with a target application life of ten years. They have performed without any failures for over 20 years. The remaining life assessment process was done to investigate if the life of the SRMS could be extended until the year 2020. The remaining life assessment concluded that the electronics could be extended until 2020 due to the robust design and lack of damage caused to the assemblies.

# REMAINING LIFE ASSESSMENT PROCESS OF ELECTRONIC SYSTEMS

by

Vidyasagar Shetty

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Master of Science 2003

Advisory Committee:

Professor Michael Pecht, Chairman/Advisor Associate professor Patrick McCluskey Associate professor Peter Sandborn

Copyright by Vidyasagar Shetty 2003

#### ACKNOWLEDGEMENTS

I would like to thank my family for their support, and prayers for all these years. I would like to thank Dr. Michael Pecht for funding me and giving me an opportunity to complete my Master of Science degree. I like to express my regards and gratefulness for Dr.Diganta Das and Keith Rogers. Dr.Das has been my guiding force for the two years of my life spent in CALCE. He has taught me the virtues of patience and hard work and I am forever indebted to him for that. I would especially like to thank Dr. Michael Pecht, Dr. McCluskey and Dr. Sandborn, and for serving on my thesis committee. Finally I would like to thank my fellow students and friends, whose help not only made my graduation possible, but also made the entire graduate experience worthwhile. Thanks to Pavan Davuluri, Kunal Goray, Toby Syrus, Joe Varghese, Ji Wu, Yuki Fukuda, Eric Stellrecht, Keith Rogers, Sachi Mishra, Niranjan, Sanjay and Satyanarayna. Thanks to Sanjay Tiku, Yuki Fukuda, Niranjan, Anoop, and Rajgopal for being my friends and helping me out during my school and personal life. There are many other individuals whom I have left out, but I hope they know that their contributions have been appreciated. Special thanks to David Hiemstra and Stephen Martin of MD robotics who are sponsors of my project.

# TABLE OF CONTENTS

| 1 | Backgrou   | and and Motivation                                                     | 1       |

|---|------------|------------------------------------------------------------------------|---------|

|   | 1.1 Spa    | ce Shuttle Remote Manipulator System                                   | 2       |

|   | 1.2 Wh     | y RLA of SRMS and hardware chosen for RLA                              | 4       |

| 2 | Steps In I | Remaining Life Assessment Process                                      | 7       |

|   | 2.1 Phy    | sical analysis of assemblies                                           | 7       |

|   | 2.1.1      | Investigation of degradation, quality in assemblies through non dest   | ructive |

|   | means      | 7                                                                      |         |

|   | 2.1.2      | Investigation of degradation in assemblies through destructive physi   | cal     |

|   | analysis   | 8                                                                      |         |

|   | 2.1.3      | Degradation assessment and identify loads causing failures             | 9       |

|   | 2.2 Life   | cycle environment profile (LCEP)                                       | 9       |

|   | 2.2.1      | Define life cycle environment and associated load conditions           |         |

|   | 2.2.2      | Identify life cycle loads                                              | 11      |

|   |            | ΕΑ                                                                     |         |

|   |            | ual remaining life assessment                                          |         |

|   | 2.4.1      | Design Capture                                                         |         |

|   | 2.4.2      | Life cycle environment and operation assessment                        |         |

|   | 2.4.3      | Failure Risk assessment:                                               |         |

|   |            | elerated testing                                                       |         |

|   | 2.5.1      | Determine acceleration loads and duration of tests:                    |         |

|   | 2.5.2      | Perform accelerated testing and analyze results:                       |         |

| 3 |            | Analysis of Assemblies                                                 |         |

|   |            | estigation of degradation, quality in assemblies through nondestructiv |         |

|   |            | means                                                                  |         |

|   | 3.1.1      | Disassembly and boards for inspection                                  |         |

|   | 3.1.2      | Low Magnification Visual Inspection                                    |         |

|   | 3.1.3      | Board Inspection                                                       |         |

|   | 3.1.4      | Dimensional Characteristic Compliance                                  |         |

|   | 3.1.5      | Component Inspections                                                  |         |

|   | 3.1.6      | Non operating Failure Mechanisms                                       |         |

|   |            | Findings and observations:                                             |         |

|   |            | clusion                                                                |         |

|   |            | estigation of degradation through destructive analysis                 |         |

|   | 3.4.1      | Destructive Physical Analysis of Selected Components                   |         |

|   | 3.4.2      | X-ray Analysis                                                         |         |

|   | 3.4.3      | Evaluation of Rejection Criteria – Capacitor (MIL-STD-1580A [1],       |         |

|   | U          | 6 for layout)                                                          |         |

|   | 3.4.4      | Evaluation of Rejection Criteria – Transformers (MIL-STD-1580A<br>37   | [1] 9)  |

| 4 |            |                                                                        |         |

|   |            | rmal Life cycle                                                        |         |

|   | 4.2 Vib    | ration                                                                 | 55      |

| 5 | Failure M  | Iodes and Effects analysis                                             | 60      |

| 6 | Virtual re | emaining life assessment                                               | 64      |

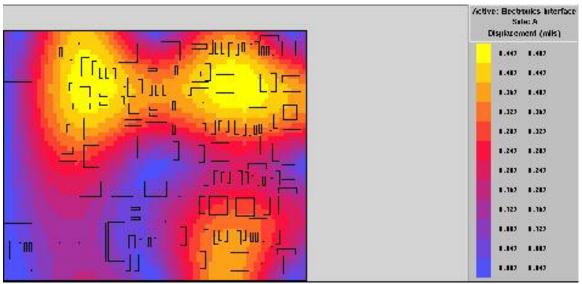

| (  | 5.1  | Design capture                                              | 64 |

|----|------|-------------------------------------------------------------|----|

| (  | 5.2  | Assumptions and difficulties in design capture for calcePWA |    |

| (  | 5.3  | Life Cycle Environment and Operation Assessment             | 71 |

|    | 6.3. | 1 Thermal Loads                                             | 71 |

|    | 6.3. | 2 Vibration Loads                                           |    |

| (  | 5.4  | Failure Risk Assessment                                     | 75 |

| 7  | Acc  | elerated testing                                            |    |

| 8  | Con  | clusions                                                    |    |

| 9  | Futu | ıre Work                                                    |    |

| 10 | C    | Contributions                                               |    |

# **1** Background and Motivation

Maintaining the reliability of electronic products is a major concern for companies because the failure to do so can lead to huge financial losses. For e.g., Toshiba corp. agreed to a \$1.1 billion settlement for allegedly selling defective laptop computers in the U.S., the first fallout from a wave of lawsuits and government inquiries over a flaw that may be common to the products of many major computer makers1. This thesis is an attempt at improving the reliability process by developing a reliability prediction process called Remaining Life Assessment (RLA). The Remaining Life Assessment (RLA) process is a reliability prediction process, which predicts amount of life left in a system. Remaining life assessment can be done on systems, which have seen a considerable amount of life. This thesis presents the RLA approach through the case study of the RLA of Space Shuttle Remote Manipulator System (SRMS). The RLA process can help in the improving the reliability of electronics systems by being able to detect failures and causes of failure that would occur in the systems exposed under certain life cycle conditions. The remaining life assessment process is to certain extent a derivation of PoF process developed and used by CALCE. The Computer Aided Life Cycle Engineering (CALCE) Center at the University of Maryland developed a PoF approach for electronic product qualification and accelerated testing in the early 1990s. The PoF approach utilizes knowledge of the life-cycle load profile, package architecture, and material properties in identifying potential failure mechanisms and provides a rational method of analysis and testing to predict expected life cycles in the field application (1-5). Physics of failure (PoF) supplies the link between failures under normal use conditions and the failures taking place during the accelerated tests. PoF establishes a qualitative and quantitative

1

relationship between the particular failure mechanisms, the product properties, and environmental conditions.

All the research for the project (RLA of SRMS) has been performed in CALCE-UMCP (University of Maryland College park). The sponsor of the project was MD Robotics (MDR), Canada. All the information about SRMS has been provided by MDR.

#### **1.1** Space Shuttle Remote Manipulator System

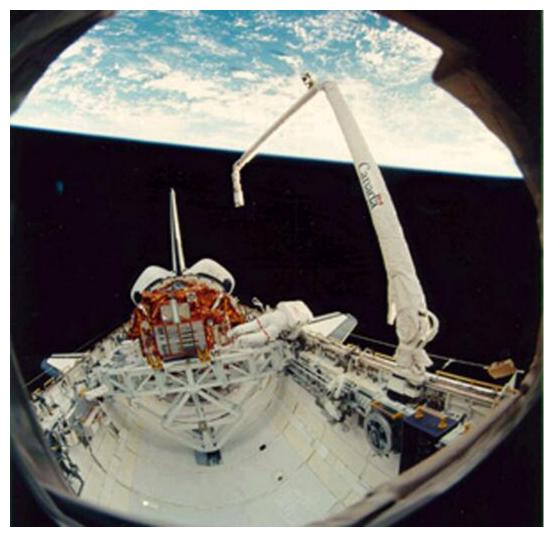

This section introduces the case study material i.e. Space Shuttle Remote Manipulator System (SRMS, Figure 1-1). Since its maiden voyage aboard U.S. Space Shuttle Columbia in 1981, the Shuttle Remote Manipulator System (SRMS), known as Canadarm, has demonstrated its reliability, usefulness, and versatility and has provided strong, yet precise and delicate handling of its payloads. Canadarm was designed, developed and built by Spar Space Systems Robotics operation, now MD Robotics under contract to the National Research Council of Canada. The first arm was Canada's contribution to NASA's Space Shuttle Program. Subsequently, NASA ordered four additional units. Canadarm has performed flawlessly for 20 years; placing satellites into their proper orbit and retrieving malfunctioning ones for repair. Perhaps its most notable mission was the repair of the Hubble Space Telescope. Canadarm was used as a mobile work platform for astronauts during numerous space walks required to repair the faulty telescope. Canadarm played a critical role retrieving the satellite, placing it in the cargo bay for repairs, and then re-deploying it. Unplanned exercises for Canadarm have included knocking a block of ice from a clogged waste-water vent that might have endangered the shuttle upon re-entry, pushing a faulty antenna into place, and successfully activating a satellite that failed to go into proper orbit. In December 1998 Canadarm played a critical role in the first assembly mission of the International Space

2

Station, mating the U. S. Unity node to the Russian-built Zarya. Canadarm will continue to play a vital role in the assembly of the space station. The Shuttle Remote Manipulator System consists of a shoulder, elbow and wrist joint separated by an upper and lower arm boom. The shoulder joint has two degrees of freedom, the elbow joint has one degree of freedom, and the wrist joint has up to three degrees of freedom. At a total weight of approximately 905 lbs., the Canadarm has recently been upgraded to maneuver payloads of up to 266,000 kgs. (in the weightlessness of space). Canadarm uses an end effector with a specially designed grapple fixture to place payloads in orbit.

Figure 1-1: SRMS

# 1.2 Why RLA of SRMS and hardware chosen for RLA

The successor to the Space Shuttle, the second-generation Reusable Launch Vehicle

(RLV), is not expected to be ready before 2020 and hence NASA hopes to extend the usage of the Space Shuttles into the year 2020. NASA has asked its major contractors to conduct remaining life assessment of the key components of the Space Shuttle, since MDR manufactures SRMS it was asked to do the RLA of SRMS.

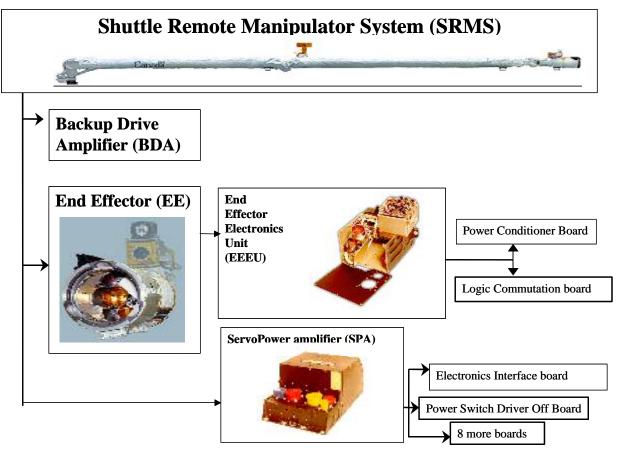

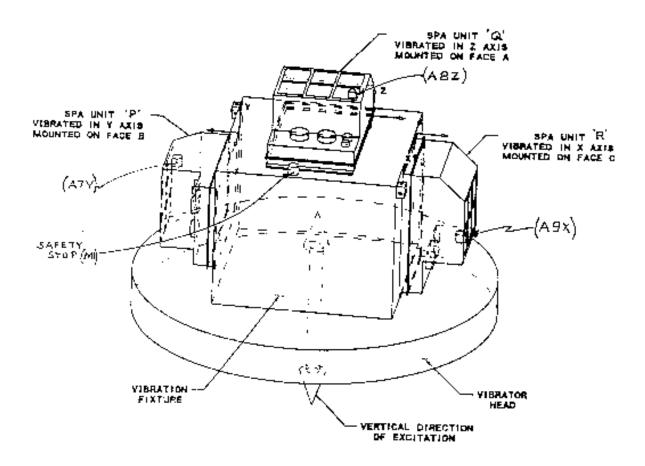

Figure 1-2 shows the physical hierarchy of the SRMS. There are many systems and sub systems in the SRMS as observed from the physical hierarchy diagram. Since it is not possible that all the systems be analyzed for RLA. The EEEU was chosen as a

representative of the remaining life of the SRMS. The EEEU was chosen because boards in the EEEU experience the most harsh of all environmental conditions and they had the highest number of components per boards. However the EEEU units are still being used in the SRMS and hence physical analysis step of the RLA couldn't be performed. Hence as a physical representative of EEEU, SPA unit was chosen.

Similarities between the SPA and EEEU are:

- ③ SPA boards are similar to EEEU in terms of board layers (same number of layers and board materials), components, size, and exposure to similar testing (thermal, vibration) conditions.

- ③ The EEEU and some of the SPA units are in close proximity to each other in the SRMS, therefore the life cycle loads that contribute to damage to the boards affect both similarly.

- ③ The two units were designed and manufactured at the same time using same design rules and following the same standards.

- ③ The test schedules for the two units are similar.

Figure 1-2: Physical hierarchy of the SRMS

# 2 Steps In Remaining Life Assessment Process

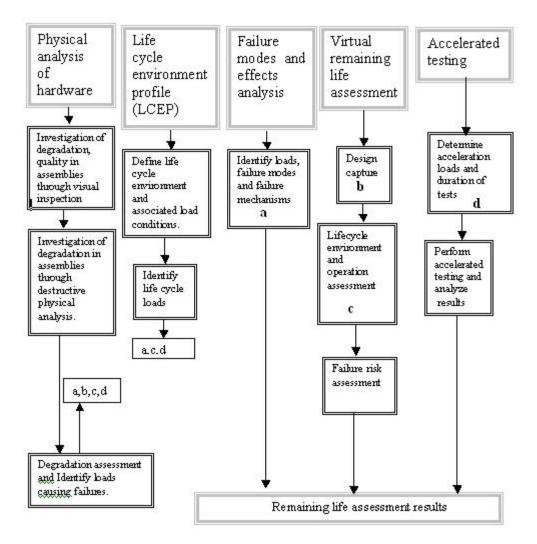

#### 2.1 Physical analysis of assemblies

Physical analysis is the first step of the remaining life assessment process, as required by the RLA process the hardware available for physical analysis, needs to have been in operation for a certain period of time. The hardware may be present either in the form of a complete assembly or just the boards may be available for analysis. In the event of the presence of a assembly, first a tear down has to be performed and the boards have to be separated out. The tear down process has its importance in the fact that it is possible to analyze the working dimensions and tolerance and based on teardown experience it is possible to make improvements for future designs. Physical analysis gives an opportunity to evaluate other damages and deteriorations that may be caused by the environmental effects not accounted for in simulation processes. Tear down, visual inspection and destructive physical analysis formed the part of physical analysis process step of RLA.

# 2.1.1 Investigation of degradation, quality in assemblies through non destructive means

After the tear down is performed on the assembly visual inspection is performed on the boards. The visual inspection process helps to identify externally observable anomalies. Visual inspection may be performed by the naked eye or with the help of an optical microscope or sometimes an X-ray microscope. Visual inspection helps in identifying failures like large cracks ,voids or wiredebonding which are evident. E.g., the lead frame stamping process leaves residual stresses and sharp blurs that act as stress concentrators.

7

# 2.1.2 Investigation of degradation in assemblies through destructive physical analysis

Destructive physical analysis is done on boards to detect internal anomalies. Destructive

physical analysis can only be performed after it is made sure that the visual inspection

process is complete and all the external anomalies are detected.

#### 2.1.3 Degradation assessment and identify loads causing failures

Based on the external and internal anomalies observed, it is possible to characterize if the anomalies occurred during manufacturing or during operation. A reverse engineering type of approach can be done to investigate anomalies and find out the loads that are responsible for the anomalies.

#### **2.2** Life cycle environment profile (LCEP)

To investigate the cause of failures that occur during the life cycle of the electronics it is imperative to accurately characterize that the stress loads experienced during its life. Through the development of accurate Life Cycle Environment Profile (LCEP) based on the events that take place in the life of electronics it is possible to identify loads, which act on the electronics. A life cycle environment profile (LCEP) is a forecast of events and associated environmental conditions that equipment will experience from manufacture to end of life. A life cycle environment profile helps to identify all possible load combinations so that the stresses acting on the product can be identified and can be incorporated in the product's design, test and qualification process to ensure the reliability of the electronic equipment for its entire life. Past research describes the need for life cycle analysis of electronic products in order to ensure product reliability[3]-[6]. The failure modes and mechanisms can be identified for each load which helps in improving the design by providing safeguards against failures for present systems and designing for better reliability in future systems. Environmental loads corresponding to manufacture and assembly, testing, handling, shipping, storage before and/or between usage, operation and rework are accounted for in the LCEP.

Importance of creating a LCEP is:

- Design engineers faced with the task of effective design need to provide safeguards against failure causing loads. LCEP can help identify the failure causing loads.

- Reliability Engineers encountering failures would like to get to the root cause of problems to weed them out. LCEP can identify life-threatening loads and from the loads it is possible to identify the failure modes and mechanisms. A comparison can be made of the failures observed with anticipated failures and hence root cause of failures can be identified.

- Not all environments merit consideration in determining the reliability of each product many are below the practical threshold for each part because the environment are sufficiently benign or because the inherent characteristics of the product are not susceptible to the stresses associated with the environment. Through LCEP it is possible to estimate the potential damage which can be caused by each load. E.g., Space electronics may be stored for long periods under benign temperatures which may have no effect on the electronics.

- If a LCEP is prepared for a particular system, then the same LCEP can be used for qualifying other systems manufactured in the future. E.g., A LCEP created for space electronics may show high operational temperatures. Using this temperature profile it is possible to qualify future space electronics by making them undergo testing at the temperatures and also providing safeguards. Hence the electronics used in the future are more reliable than previous ones.

The steps in developing an LCEP are as follows:

#### **2.2.1** Define life cycle environment and associated load conditions

Describe the expected events occurring from manufacture to end of life. This step called as the LCEP step. For example, in the case of a space shuttle , these events or phases include assembly, qualification, , transportation to launch site, storage at the launch pad, launch, operation and rework. The entire life cycle of the electronic product should be separated into the key phases or events. The events are generally decided based on the commonality of loads acting on the system for a particular duration.

#### 2.2.2 Identify life cycle loads

Identify the significant loads (temperature, vibration) from LCEP. Identify failure modes and mechanisms for each load. Use the listing of the failure modes and mechanisms as a means for improving reliability. For e.g., during qualification testing the space assemblies are subjected to temperature cycling. During temperature cycle testing, products are held at cold temperature long enough to establish temperature stabilization and appropriate creep and stress relaxation of materials. Following this cold dwell materials are heated to the hot dwell where they remain for another minimum time period. The dwell at each extreme and two transition times constitute one cycle. Common failure modes include parametric shifts and catastrophic failures; common failure mechanisms include wirebonds fatigue, cracked or lifted dies, and package failure.

#### **2.3 FMEA**

A FMEA is a qualitative technique for determining and listing the possible failure modes, by which the product may fail. FMEA involves an analysis of the system to determine the effect of component or subsystem failure on the overall performance of the system and on the ability to meet performance requirements or objectives [42]. Based on the captured design and loading conditions, the possible failure modes and mechanisms are identified. A literature search or knowledge from similar existing products can aid in identification of possible mechanisms and modes. A FMEA is generally constructed in a table format. The major components or subsystems of the product are listed in the first column. The physical failure modes for each component are listed in the second column. In the third column the possible failure mechanisms are identified for each respective entry in columns one and two. The effects of the failure on the product are listed in the fourth column. Additional columns containing failure probability, criticality, or alternative failure ranking, determined from previous product knowledge, may be included for a more quantitative analysis. Likewise, columns listing symptoms or methods of failure detection may be listed to help identify specific failure modes and mechanisms. For example, an FMEA of surface mount components assembled to a PWB under temperature cycling, may identify an electrical open as a failure mode due to thermomechanical fatigue mechanism.

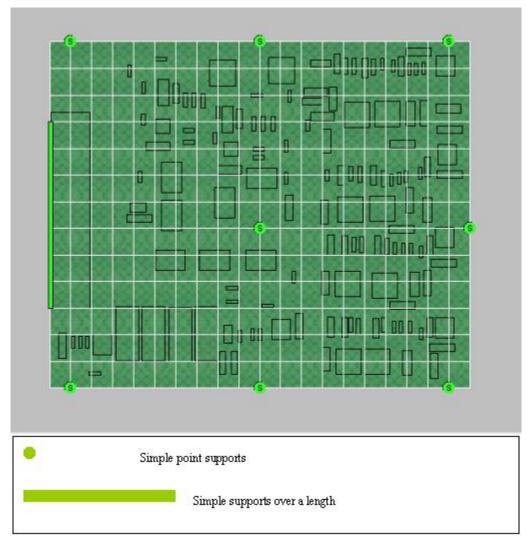

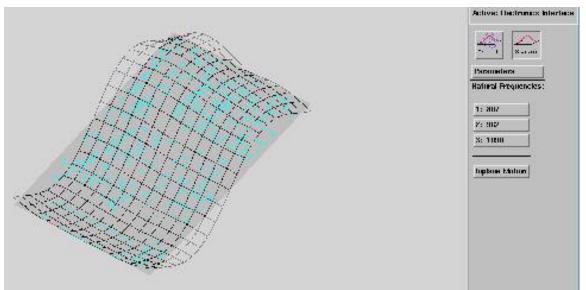

#### 2.4 Virtual remaining life assessment

Virtual remaining life assessment is performed to determine the remaining life at the circuit card assembly level. Virtual remaining life assessment is basically a simulation process where electronics are simulated under various life threatening loads . Software that can be used for VRLA are ansys, abacus, calcePWA etc.

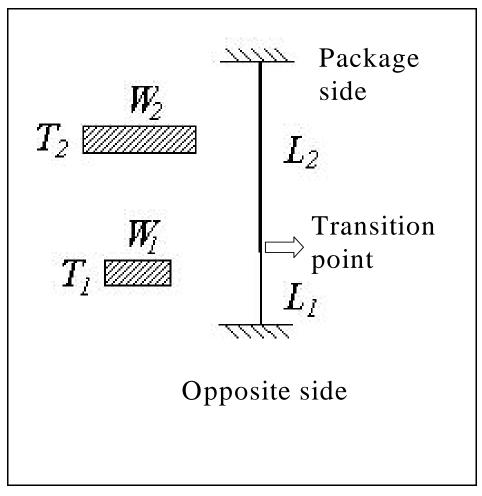

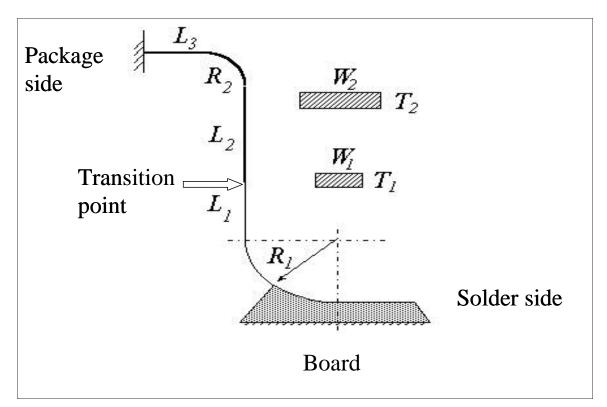

#### 2.4.1 Design Capture

Design capture is the process of identifying and documenting geometrical, material, and mounting information to generate a model of the physical hardware. Design capture involves evaluating the electronic system at all hierarchies (e.g., enclosure, circuit cards, parts, physical interfaces) based on the objectives of the assessment. Each individual component of the CCA is characterized by a set of geometrical and material parameters by the hardware capture and material identification and properties. Geometric data for a product is generally defined by the product's manufacturer by means of design drawings or electronic design files. Information may be obtained from the manufacturer, conducting reverse engineering, or by making reasonable assumptions based on literature and prior experience. Information such as component and interconnect geometry, circuit card geometry, and mounting conditions are needed for a model of the hardware. The identification of materials used in the construction of the electronic product is needed to understand the behavior of the materials and their failure response when subjected to loads in PoF. The material properties define how a material will react and degrade due to loads applied during manufacture, assembly, storage, transportation, installation, rework, and operation.

#### 2.4.2 Life cycle environment and operation assessment

Environmental and operational loads are applied to models of the product, created from the hardware capture, to determine the maximum stress areas in the product. During the stress assessment, the global loads experienced at the system level, are transformed to local loads throughout the product. The local loads are used to determine the potential failure sites. Te damage assessment utilizes the local loads (e.g., temperature at a component, curvature of the PWB below a component) found in the stress assessment and determines the time-to-failure of each failure site based on the failure mechanisms of interest. Since the same load can excite more than one failure mechanism, damage models representing the various mechanisms are used to estimate the time-to-failure for each failure mechanism. Likewise, multiple loads may excite the same failure mechanisms; therefore load interaction toward a failure mechanism must be considered when conducting the damage assessment. Models representing multiple load interactions should be used when available, even when a model is not available, the product's response to the multiple loads must be identified.

#### 2.4.3 Failure Risk assessment:

Each failure site is ranked in terms of time-to-failure based on the results of the damage assessment for each failure mechanism in the life assessment. An initial reliability assessment is made based on the shortest time-to-failure.

# 2.5 Accelerated testing

Accelerated testing is conducting to cause the life aging process of products to occur at a rate faster than would be obtained under normal operating conditions. The steps involved in accelerated testing include the following:

- 1. Determine acceleration loads and duration of tests

- 2. Perform accelerated testing and analyze results

Care must be taken in specifying the accelerated conditions so that the failure modes and failure mechanisms are neither introduced nor removed. Excessive acceleration of a failure mechanism may trigger a failure mechanism that that may be dominant at service loads. This failure mechanism shifting may provide misleading service life predictions. Each stress may also cause multiple failure mechanisms to be accelerated with different sensitivities. For e.g., Temperature accelerates electromigration, ionic contamination and surface charge spreading but at different rates. Conversely a particular failure mechanism may be activated by multiple stresses. For e.g., corrosion is accelerated by temperature and humidity. In light of these complexities accelerated testing should not be employed without a thorough understanding of how the test correlates with service conditions. Table 2-1 gives examples of failure mechanisms and acceleration parameters.

| Failure mechanisms          | Acceleration parameters                  |

|-----------------------------|------------------------------------------|

| Failure crack initiation    | • Step load or displacement              |

|                             | Thermal shock                            |

| Fatigue crack propagation   | Cyclic load displacement and temperature |

| Diffusion                   | Absolute temperature                     |

|                             | Concentration gradient                   |

| Interdiffusion              | • Absolute and cyclic temperature        |

| Deadhesion and delamination | Absolute temperature                     |

|                             | Relative humidity                        |

Table 2-1: Failure mechanisms and acceleration parameters

|                               | Contaminants                    |  |

|-------------------------------|---------------------------------|--|

| Corrosion                     | Absolute temperature            |  |

|                               | Relative humidity               |  |

|                               | Contaminants                    |  |

| Electromigration              | Current density                 |  |

|                               | • Absolute temperature and      |  |

|                               | temperature gradients           |  |

| Electron-hole pair generation | • Radiation and dose rate       |  |

| Popcorning                    | • Relative humidity followed by |  |

|                               | thermal shock                   |  |

#### **2.5.1** Determine acceleration loads and duration of tests:

Based on the dominant failure mechanisms and the critical failure sites found in the physical analysis and virtual remaining life assessment, environmental loads are selected that will precipitate the mechanisms. The environmental loads needed for accelerated testing will dictate the type of environmental testing equipment needed. For the accelerated test, failure needs to be defined based on the objectives of the test. Failure can be defined when an electrical parameter (i.e. voltage, resistance, current) is beyond specification or when the product ceases to operate (i.e. electrical open). A parameter that is beyond specification may be caused by an intermittent failure, where the product continues to operate but cumulative effects will grow to until the product ceases to operate. A failure that causes the product not to operate occurs when the stress level exceeds the threshold product strength. Examples of the threshold strengths are the tensile strength of a brittle material or the temperature level at which a component begins to malfunction. The failure detection scheme chosen for the testing need to be able to detect the defined failure. Failure detection and monitoring schemes need to be developed for the notification of a failure. The failure detection scheme should be able to monitor the critical failure sites and their likely failure modes. Characterizing the product response over the accelerated test loads enables insight into the interaction effects

between the applied environmental loads. The specimen characterization enables a prediction of the response of the specimen under accelerated test loads. If the loading profiles of the overstress test are similar to the selected test loads then the data for the specimen response characterization can be collected over the entire accelerated load range of the overstress test.

#### **2.5.2** Perform accelerated testing and analyze results:

The test specimens are exposed to the accelerated tests. Monitoring of the test specimens during accelerated testing provides a time-to-failure. The test failures should be documented by recording when, where, what, the load level, and pictures of the failure. Each test failure should be analyzed to determine the root cause failure mechanism. The precipitated failure modes and mechanisms of the accelerated tests should correspond to the failure modes and mechanisms predicted to occur. A reliability assessment is made based on the test results and the objectives of the product assessment. A failure free operating period, failure rate, or mean time to failure may be found by statistical analysis given enough samples and the test objectives. The acceleration factor calculated in section can be used to quantitatively extrapolate a time-to-failure from the accelerated test environment to the field application environment. The assessment can serve the purposes of customer confidence, product development decisions, risk identification, warranties, and certification and regulatory concerns.

# **3** Physical Analysis of Assemblies

# **3.1** Investigation of degradation, quality in assemblies through nondestructive and destructive means

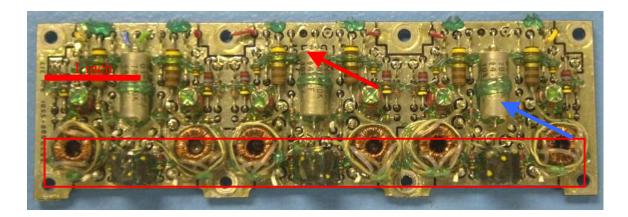

# 3.1.1 Disassembly and boards for inspection

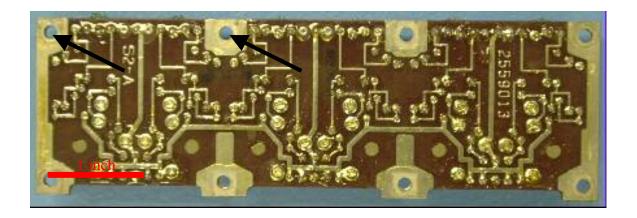

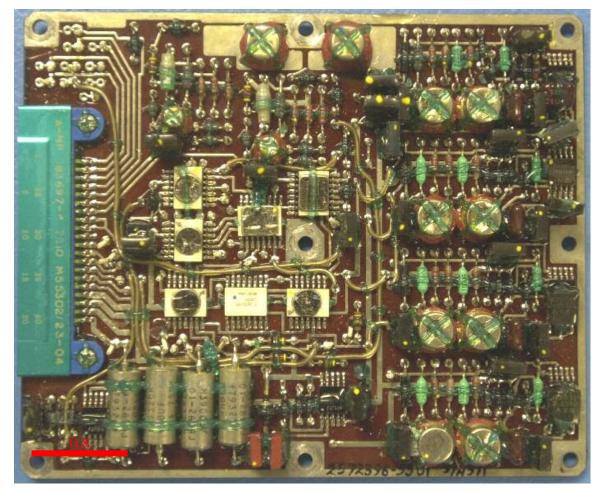

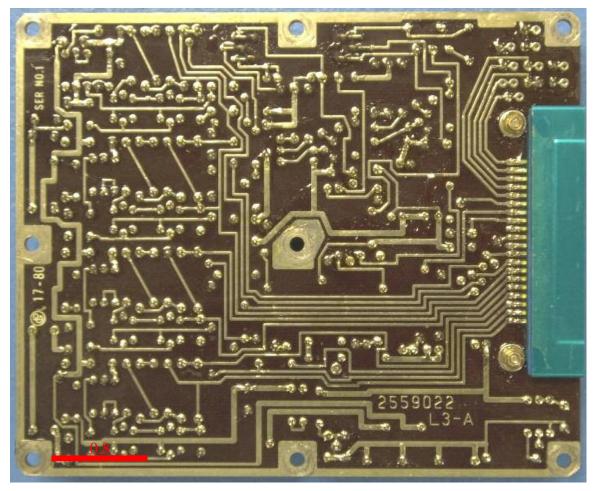

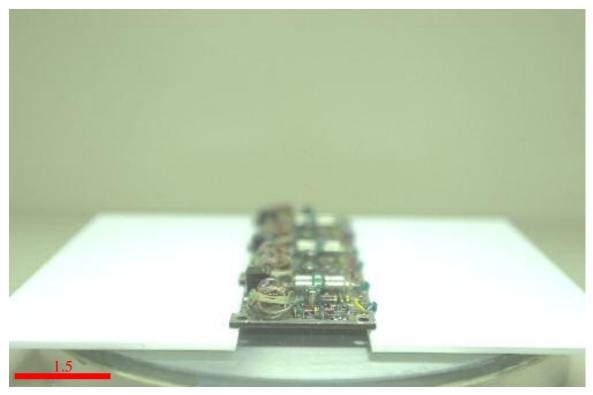

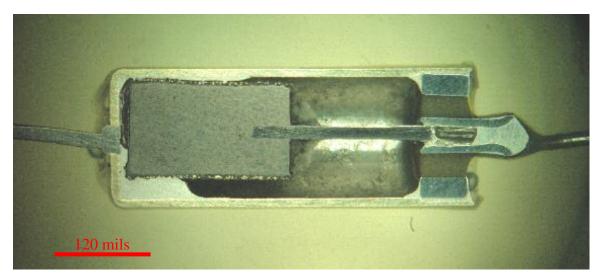

Disassembly was performed on one of the Analog Servo Power Amplifiers. Physical

analysis was performed on two of the circuit card assemblies (CCAs), identification

numbers 2559013 and 2559022, which were removed from the module (see Figure-

Figure 3-1-Figure 3-3), during the complete teardown of the unit.

| Board | Identification | Name of CCA                  | Analysis          |

|-------|----------------|------------------------------|-------------------|

|       | Number         |                              |                   |

| 1     | 2559013        | Power Switch Driver          | Visual inspection |

|       |                | "OFF" Board                  |                   |

|       |                | Subassembly                  |                   |

| 2     | 2559022        | <b>Electronics Interface</b> | Visual inspection |

|       |                | Board                        |                   |

During the teardown, the following observations were made:

- Irreversible fasteners were used to secure assembly

- Conformal coating covering the boards and components

- Wires were bundled together and attached to the board with adhesive; no damage was observed

- Adhesive was also used to secure the parts to the boards

- There was limited physical working dimensions

Inspections were performed in accordance with:

MSFC-STD-136 (June 11, 1971) Parts Mounting Design Requirements for Soldered Printed wiring Board Assemblies 11, and

- NASA-STD-8739.2 (August 31, 1999) Workmanship Standard for Surface Mount Technology, Chapter 12 12.

- IPC-A-610 (Revision C, January 2000), Acceptability of Electronic Assemblies

[4]; Class 31

• ANSI/IPC-A-600 (Revision E August 1995), Acceptability of Printed Boards, Chapter 2 8

The inspections investigated the boards, components, and interconnections. These

included:

- Board edges

- Base material

- Solder joints, connector pins

- Plated through holes

- Solder resist

- Dimensional characteristics

- Coatings

- Component damage

- Bow and twist

- Component mounting/securing

<sup>&</sup>lt;sup>1</sup> It was assumed that this product is Class 3 (IPC-A-610 Revision C, January 2000) therefore; acceptance and conformance were based on this classification.

<sup>&</sup>lt;u>Class 3 – High Reliability Electronics Products</u>; Includes the equipment and products where continued performance or performance-on-demand is critical. Equipment downtime cannot be tolerated, and the equipment must function when required, as in the case of life support items or flight control systems. Assemblies in this class are suitable for applications where high levels of assurance are required, service is essential, or the end-use environment may be uncommonly harsh.

# 3.1.2 Low Magnification Visual Inspection

Based on Table 3-2 10, (Table 1-2 Inspection Magnification in section 1.8 Magnification Aids and Lighting, of IPC-A-610 Revision C, January 2000) along with the statement from MDR that the land widths are 0.030 inches, a magnification of 4X should be used (see highlighted section in table below). Each of the two boards was inspected using hand held illuminated magnifiers of 5X magnification. A low magnification stereoscope (15 - 60X) was used for areas of interest where it was determined that higher magnification was needed.

| Land Widths or Land<br>Diameters        | Inspection             | Referee                |  |

|-----------------------------------------|------------------------|------------------------|--|

|                                         | Magnification<br>Power | Magnification<br>Power |  |

| >1.0 mm [0.039 in]                      | 1.75X                  | 4X                     |  |

| 0.5 to 1.0 mm<br>[0.020 to 0.039 in]    | 4X                     | 10X                    |  |

| 0.25 to 0.5 mm<br>[0.00984 to 0.020 in] | 10X                    | 20X                    |  |

| <0.25 mm [0.00984 in]                   | 20X                    | 40X                    |  |

Table 3-2: Inspection Magnification

# **3.1.3 Board Inspection**

(note that the boards are covered with conformal coating, hence observations are made

through this covering)

At 5X magnification, the assemblies were checked for:

- Surface imperfections such as burrs, nicks, cut fibers, weave exposure or voids in the boards

- Conformal coating coverage

- Solder mask quality

- Subsurface imperfections such as foreign inclusions, measling/crazing, delamination between layers of the base material and/or between the base material and metal cladding, or laminate voids

- Imperfections in the conductive circuitry such as reduction of conductor width or thickness due to nicks, pinholes, or scratches

- Visible discoloration due to corrosion, contamination, overheating or electrical overstress (EOS) damage

- Isolated metal particles

- Board warpage (IPC-TM-650, number 2.4.22, procedure #1) using a flat glass plate and ceramic plated to elevate the sample so that it is supported only by the edges (see Figure 3-4 and Figure 3-5). % bow = (0.085 -0.07)/5.1 = 0.3% for board identification number 2559022. The specification specifies a maximum of 1.5%. For the other board, identification number 2559013, the % bow was 0.4%.

The results of the board visual inspection yielded no criteria for rejection in the above areas examined.

#### **3.1.4** Dimensional Characteristic Compliance

After 20 years of storage/use, based on the assembly drawings supplied by MDR (2559013.pdf 6and 2559022.pdf 7) for the two boards on which visual inspection was done, physical dimensions (as given in the layout and board drawings) that could be measured, were within the specified tolerances. Measurements for the conductor spacing (minimum: 0.027 inches), conductor width (minimum: 0.022 inches), plated-through-hole (PTH) diameter (inner diameter: 0.032 inches) and lead diameter (0.02 inches) were all in compliance with the guidelines in MSFC-STD-136 11.The specification states that

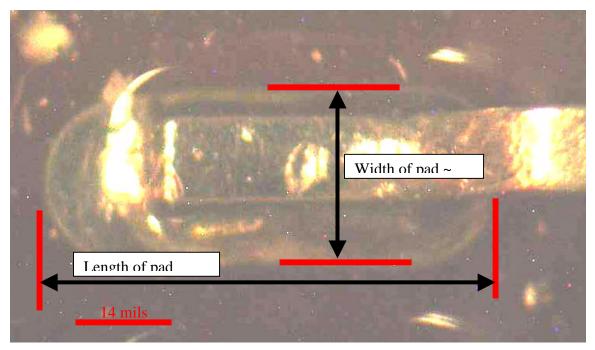

component hole diameter shall be a maximum of 0.015 inches larger than the nominal component lead diameter. Using the measurements for the conductor spacings and metallization width (not thickness), and PTH and pad external dimensions. Plated-through-hole diameter (0.032 inches) minus the lead diameter (0.02 inches) is equal to 0.012 inches. This complies with the specification of < 0.015 inches. Minimum spacing between adjacent conductors for conformally coated boards shall be 0.0003 inches/peak volt. Based on our measurements, conductor spacing (minimum – 0.027 inches), these boards can withstand a peak of 0.027/0.0003 = 90 volts. The solder pads for the surface mount components all appear to be longer than twice their width (see Figure 3-6). Some of the PTHs in board 2559013 did not have annular rings on the component side. The fillets of the solder joints on the component side of the board would be smaller compared to the joints on the other side where there are annular rings (cross-sectioning needed to clearly view this). A picture is included in the board DPA report subsection.

# **3.1.5** Component Inspections<sup>1</sup>

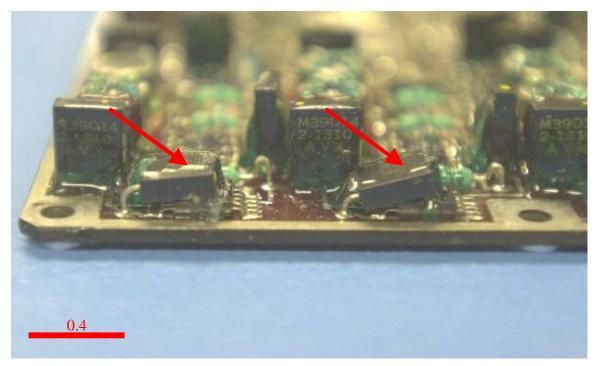

From an external view, no anomalies were noted on any of the components inspected on the four boards. It was noted that some of the components were bent at the leads to accommodate limited space in the vertical direction (see Figure 3-7). In accordance with NASA-STD-8739.2, Chapter 12 – Quality Assurance Provisions, and MSFC-STD-136, inspections were conducted in the following applicable areas:

Solder Paste Application (visual observation of location, amount, and alignment of solder with respect to pad, reject criteria given in paragraph A below)

• Part Alignment

<sup>&</sup>lt;sup>1</sup> note that the components are completely covered with conformal coating, hence observations made are through this covering

- Part Appearance

- Soldered Interconnections

The results of the visual inspection yielded no criteria for rejection in the above areas examined.

The reject criteria are as follows:

- Solder paste application

- Solder paste bridging between lands

- Isolated solder paste

- Void in the solder paste (only external)

- Solder paste misalignment that covers more than 25% of the open area between lands

- Smeared solder paste bridging conductors

#### Part Alignment

- Piggy-backed or stacked parts

- Chip parts have lateral overhang more than 25 percent the width of the part or inside overhang more than 50 percent of the end termination width

- Chip part tilting exceeds 25 percent of part thickness

# Part Appearance

- Improper tinning of part leads.

- Part improperly supported or positioned (polarity, centering, planarity).

- Part damaged (especially cracks in ceramic parts).

- Cut, nicked, stretched, or scraped leads exposing base metal (except smooth impression marks resulting from bending tool holding forces).

- Flux residue.

- Improper positioning of leads to solder pad for lap terminations.

- Improper lead bending and cutting.

- Spliced part leads.

### Soldered Interconnections

- Cold solder connection.

- Overheated solder connection.

- Fractured solder connection (externally visible)

- Poor wetting.

- Blowholes, and pinholes

- Insufficient solder

- Splattering of flux or solder on adjacent areas

- Contamination (e.g., lint, flux, dirt).

- Dewetting.

- Non-wetting.

- Dull or frosty appearance.

- Solder scratches.

For impact of these defects, refer to Solders and Soldering, Fourth Edition, written by

Howard H. Manko 15.

# 3.1.6 Non operating Failure Mechanisms

These failure mechanisms are to be considered during storage and non-powered Ferry Flight and ground transportation. See "Long-Term Non-Operating Reliability of Electronic Products" 14 for more details. It has been noted by MD Robotics that the assemblies are stored in climate controlled atmosphere where they are free from contamination, corrosive gases, radiation, shock and vibration. The temperature and humidity is kept under strict control. There are no specific recommendations regarding how long a printed board can be stored, or specific recommendations on temperature and humidity requirements for optimum storage conditions 13. The non-operating failure mechanisms examined are described.

#### 3.1.6.1 Corrosion

Corrosion is defined as the chemical or electrochemical reaction of a metal with the surrounding environment. The continuation and rate of the corrosion process depend on the nature of the corrosion product. Conditions that accelerate corrosion include relative humidity, high temperatures, high contaminant concentrations, and the presence of dirt or dust, which can hold more moisture on the surface of the metal. Of these factors, relative humidity is the most important. Rapid acceleration of corrosion occurs beyond a critical value of relative humidity Corrosion also becomes more acute as product metallization tracks become narrower, and the separation between metallization tracks becomes closer. Since the boards and components are conformally coated, and no pits or nicks were observed during the visual inspection, it would be difficult for moisture to get to the metallic areas. Also, the metallization tracks on the boards are relatively large (0.03" compared to 0.003"[9]) and also widely spaced. These make failure due to corrosion unlikely.

#### 3.1.6.2 Shock and Vibration (also addressed by VQ)

Shock and vibration are common accelerators of failure. The most frequent vibrationinduced failures include flexing of leads and interconnects and the dislodging or damaging of parts and structures, or foreign particles in electronics. The degree of failure

25

generally depends on the natural frequencies, deflections, and mechanical stresses within components and materials produced by the shock and vibration environment. If the mechanical stresses so produced are below the acceptable long-term safe working stress of the materials involved, failures should not occur acceptable safe levels. Non-operating vibration levels during storage, Ferry Flights, and ground transportation are not significantly large or long-lasting when compared with launches or vibration tests. Since all of the components, wires and the majority of the fasteners are secured by solithane adhesive, damage from shock or vibration in the storage environment is unlikely. The effects of the solithane are not addressed in the virtual qualification, but would make things better (more secure parts).

#### 3.1.6.3 Thermal

According to MDR, in a year's period approximately 356 days are spent in storage, which amounts to a period of 7120 cycles for 20 years and the temperature ranges from 27 to 17 °C. Approximately once every 3 missions, a Ferry Flight occurs over a 7 hour period with a temperature ranges from –40 to +35oC. The main failure mechanisms due to temperature excursions include fatigue and fracture of various package components, which occur primarily as a result of mismatches in the coefficients of thermal expansion (CTE) of the various materials that make up the assembly. This is covered in the virtual qualification section.

#### 3.1.6.4 Electrical

Although perhaps not readily apparent, non-operating electronics can be subject to significant electrical failure mechanisms. While electrostatic discharge (ESD) is the most common in storage/dormancy environments, electrical failure can also be caused from

26

static charging of dust particles and organic vapors. Since the metal traces on the boards are relatively large, 0.03 inches compared to 0.003 inches (the state of practice in 2000) the possibility of damage due to ESD is negligible since the charge is distributed uniformly over the conductive trace – the larger the trace, the smaller the charge density. For the components, although the visual inspection did not reveal any anomalies, electrical testing is necessary to verify their integrity.

#### **3.2 Key Findings and observations:**

None of the two visually inspected boards had anomalies based on the acceptance criteria of standards: IPC-A-610 (2000), ANSI/IPC-A-600 (1995), MSFC-STD-136 (1971), and NASA-STD-8739.2 (1999). There is no observation, which would suggest a decrease in the expected life. Based on the observations during the teardown, in addition to the visual inspection observations, reworking the units is not recommend because:

- ③ The units are difficult to reassemble (screws, bolts and nuts hold the units together in such a way, that once taken apart, it is tough to reassemble them due to limited physical working dimensions). Since each unit may be assembled differently, "teardown procedure" as given by MD Robotics, may not be applicable to all units.

- ③ The wires and components, in particular transformers and transistors, on the boards are secured with an adhesive, which makes it difficult to remove them.

- ③ Based on the visual inspection, the PWB assemblies are robust and would probably not suffer from failure mechanisms normally incurred during storage such as electrostatic discharge (relatively large metallization lines and conductor spacing) corrosion due to moisture ingress (no defects in conformal coating which covers the board and components), fatigue or cracking due to thermal excursions

(no cracks, chips or nicks observed on board, parts or interconnections), and damage from shock and vibration (due to how the parts and boards are secured).

### 3.3 Conclusion

From the visual inspection, no anomalies for the specified areas, were noted in any of the components or boards. These boards are of good quality, as seen by the external examination. The spacing and widths of the pads and traces are relatively large, making the PWB assemblies virtually immune to electro-chemical failure mechanisms. Also, the intact and complete coverage of the conformal coating will help to ensure that no moisture gets in to start contamination which could lead to corrosion. Note that this inspection is only external, and does not address parameters that may be examined during destructive physical analysis (DPA).

А

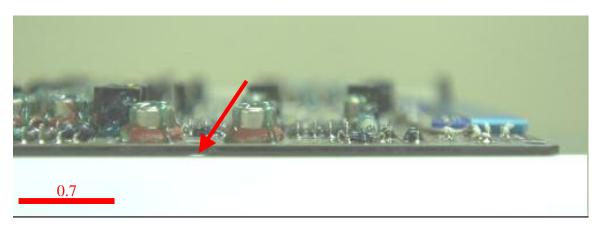

Figure 3-1 : These photos show the component side (A) and solder side (B) of board #1, identification number 2559013. A red rectangular box in A highlights some of the components (transformers) that would be difficult to remove. Also shown (see red arrow) is one of the PTHs that has not annular ring on this side. A blue arrow in A shows the adhesive used to secure the parts and wires. The 8 mounting holes (see black arrows in B) make the board more vibration resistant. Visual inspection was performed on this board

Figure 3-2: This photo shows the component side of board #2, identification number 2559022. Visual inspection was performed on this board.

Figure 3-3: This photo shows the solder side of board #2, identification number 2559022. Visual inspection was performed on this board.

Figure 3-4: This photo shows the setup to measure board flatness. The board is suspended by its edges on ceramic plates on a flat glass plate.

Figure 3-5: This photo shows the area where the measurement was taken for the board flatness assessment.

Figure 3-6: This photo shows the length of a pad compared to the width  $(0.08/0.03 \sim 2.7 > 2)$  which is greater than twice the width, in compliance to the specification.

Figure 3-7: This photo shows bent components on board #2. This is done to facilitate small vertical clearances in these areas.

# **3.4** Investigation of degradation through destructive analysis

## 3.4.1 Destructive Physical Analysis of Selected Components

The cross-sectioned components were two tantalum capacitors (removed from board

number 2559017) and two transformers (removed from board 2559023) (Table 3-3)

| Board Number | Action                  |

|--------------|-------------------------|

| 2559017      | DPA on two capacitors   |

| 2559023      | DPA on two transformers |

Table 3-3 Source of parts for DPA

## **3.4.1.1 DPA procedure for the components**

Each component was visually inspected using a low magnification microscope (10 - 50

X) and electrically tested. Since the transformers could not be removed from the board without risk of damage, the transformers were left on the board while the capacitors were removed. The components were then potted in a room-temperature cure epoxy resin (Allied High Tech Products). Potting ensures that there is no relative motion between the

board or part materials with respect to each other and also prevents chipping or edge rounding during cutting, grinding, and polishing. The cure is done under vacuum to remove any trapped air present in the sample. If air is trapped, it will cause bubbles to form in the epoxy resin and creating problems during the cross-sectional procedure and optical examinations. After the epoxy resin solidifies, sections of interest are cut out with a liquid cooled diamond edge-sectioning saw. An initial rough grind at 240 grit is used to remove material and get close to the area of interest. The sample undergoes successive grinding steps using SiC grinding paper (Allied High Tech Products). The grinding process moves on to a finer grit size only after all scratches from the previous grinding step have been removed. Typically, a sequence of 240-600-200 grit is used. The sample is then polished using 0.3 micron alumina (Allied High Tech Products). Samples are thoroughly cleaned between each stage of sample preparation. Micrographs of the polished cross sections are taken using optical (15 to 1000X) and/or environmental scanning electron (ESEM) microscopy (used when larger magnifications or higher resolutions are required)

#### **3.4.1.2** Results of Preliminary Evaluation

The results of the destructive physical examination do not reveal any problems of

degradation with the capacitors or transformers.

## **3.4.1.3** Electrical Testing

Electrical testing of the components revealed that each was functional. None of the coils for the transformers was open or shorted (resistance in each coil was less than 1 ohm). The capacitance values and leakage currents for the capacitors were within specification (see Table 3-4).

| Component | Capacitance (mF)      |       | Specification (mF) |

|-----------|-----------------------|-------|--------------------|

| Capacitor | Capacitor 4.89<br>10% | 4.7 ± | 0.0                |

| Capacitor | Capacitor 4.89<br>10% | 4.7 ± | 0.0                |

Table 3-4 Source of partss for DPA

# 3.4.2 X-ray Analysis

No anomalies or defects were observed in the X-rays of the components (see Figure 44

and Figure 45).

# 3.4.3 Evaluation of Rejection Criteria – Capacitor (MIL-STD-1580A [1], see Figure 46 for layout)

A. Cracks extending through the glass header

B. Tubulet filled with solder less than 25% of its length when solder-plated leads are used and less that 50% of its length when gold-plated leads are used.

C. Voids in the tubulet solder or solder separation from the leads that reduces the solder fill requirements mentioned in "B."

D. Anode (tantalum slug) not parallel to case within 15 degrees. Voids in tubulet solder or solder separation from lead or tubulet that reduces the fill to less than 25% of tubulet height for solder plated leads and less that 50% of its length when gold-plated leads are used.

E. Solder spikes inside unit or eyelet solder extending beyond bottom of tubulet.

F. Broken or cracked anode lead weld.

G. Anode immersed in solder that is less than 1/3 of its height.

H. Anchor solder cracked or pulled away from anode slug.

I. Solder buildup on inside of can with height greater than 0.50 mm (0.02 inches) resulting from solder rundown during sealing process.

- J. Anode totally immersed in solder.

- K. Anode cracked, broken or distorted.

- L. Loose material 0.25 mm (0.01 inches) or large enough to bridge shortest distance

between lead and can, or between tantalum pellet and can.

- M. Any defect that reduces the part reliability (e.g., bulges or dents in the case).

- N. Failure to meet external visual requirements.

- 1. Cracks on the cracks seal.

- 2. Cracked or cold solder joint around seal area.

- 3. Flux or foreign material on anode lead and around seal area.

None of the criteria that would cause the samples to be rejected were found in the capacitor cross-sections (see Figure 47 through Figure 51).

# 3.4.4 Evaluation of Rejection Criteria – Transformers (MIL-STD-1580A [1] 9)

a. Wire size not in accordance with MIL–STD-981 and applicable specification or

drawing.

b. Interconnect ribbon not in accordance with applicable specification or drawing.

c. Internal wire leads attached only by soldering with no evidence of mechanical

anchoring.

d. Wire windings that cross over other turns in going from one wound segment to adjacent segment.

- e. Nicks, kinks, reduction in wire cross-section, or evidence of other wire damage.

- f. Evidence of flux or other types of residues.

- g. Teflon tape

- h. Charred, crushed, discolored, or damaged wire insulation.

i. Repaired or spliced coil wire.

j. Wire-to-lead termination connections that do not show a sufficient stress relief loop.

k. Cold solder joints, or solder joints with no fillet around wire or termination.

1. No evidence of weld tip indentation in welded joints.

m. Cracks in welded joints.

n. Loose or splattered weld.

o. Lack of three (3) full nonoverlapping wraps of wire at each post termination.

p. Stranded conductor wire at terminations that does not show pretinning or that shows large globules of solder that obscure the wire contour, or wire swelling due to excess wicking.

q. Solder that is not chemically Type Sn 60, Sn 62, or Sn 63 in accordance with QQ-

S-571 or (for wire gauges smaller than size No. 38) Sn 10 for Class S devices.

r. Coils or other electronic components that show evidence of overheating.

s. Fractures, cracks, or pinholes in solder joint.

t. Solder joints with sharp tips or peaks or with a protruding, bare wire-end or bare strands of a conductor.

u. Foreign or extraneous matter embedded in or adherent to wire joints, between windings, or cores, or thin impregnation.

## Conclusion

Although the samples contain voids in the solder, and slight pin misalignment, no reason for rejection was found, based on the criteria set by Mil-Std-1580 and what was observed in the cross-section.

38

А

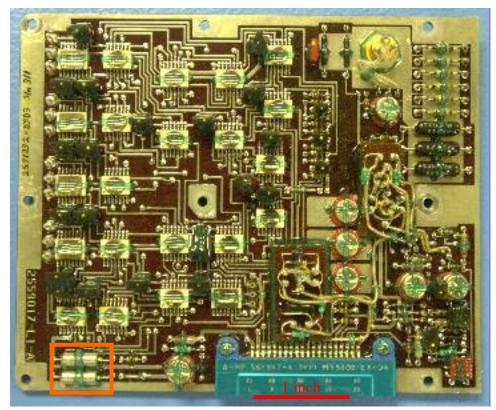

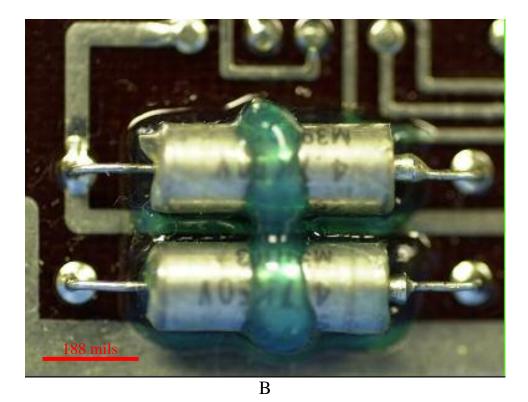

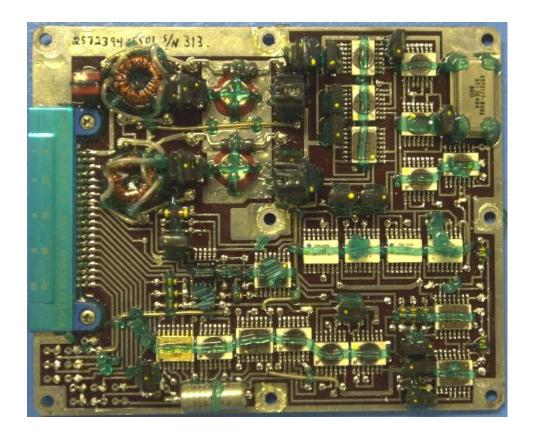

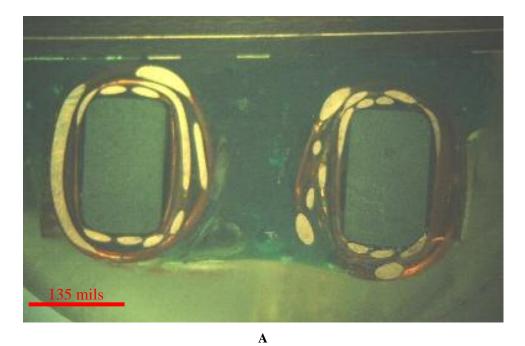

Figure 3-8These photos show the location on board number 2559017 from where the two capacitors for the DPA were removed (see red box in A). Figure B shows an enlargement section with the two capacitors.

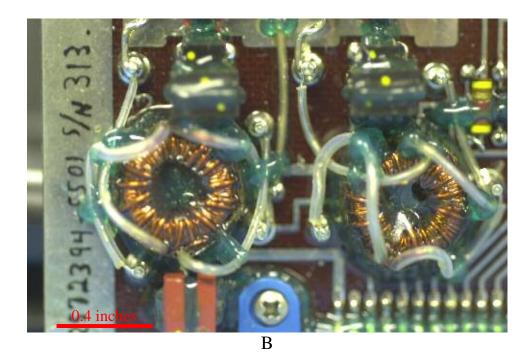

Figure 3-9: These photos show the location on board number 2559023 from where the two transformers for the DPA were removed (see red box in A). Figure B shows an enlarged section with the two transformers.

A

В

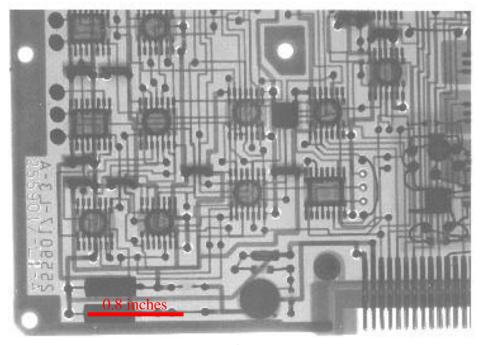

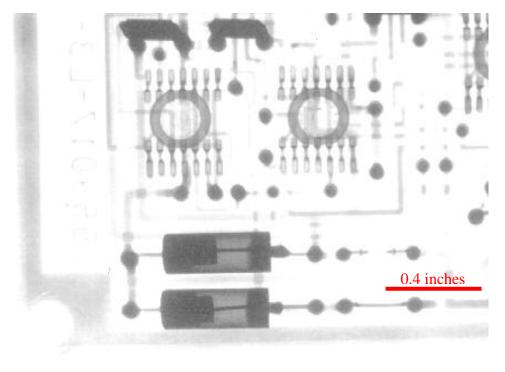

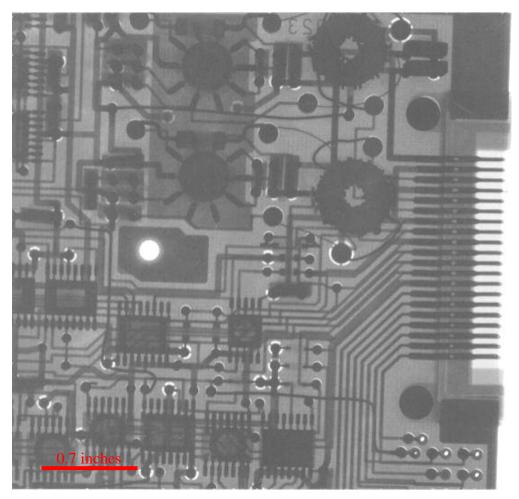

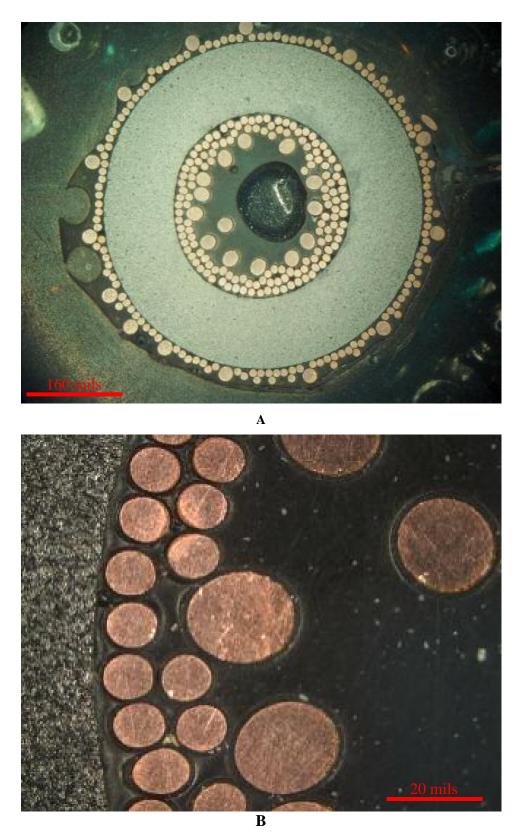

Figure 3-10: These X-ray images show the layout for board number 2559017 in the area containing the two capacitors that were removed for the DPA. Figure B shows an enlarged section with the two capacitors.

Figure 3-11: This X-ray image shows the layout for board number 2559023 in the area containing the two transformers that were removed for the DPA.

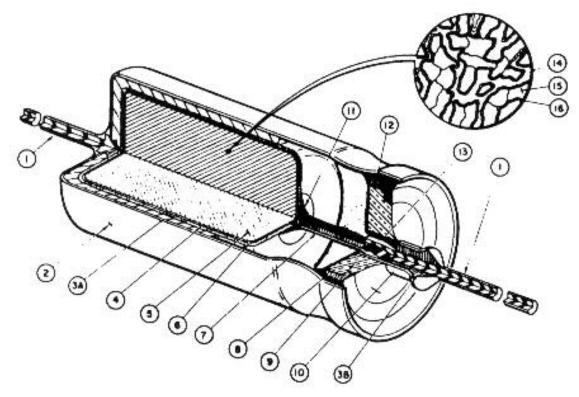

Figure 3-12: This schematic shows a typical solid tantalum capacitor (MIL-STD-1580A).

1. External leads

2. Case

3.

A. Solder

B. Solder

1. Conductive paint

- 2. Slug

- 3. Carbon film

- 4. Anode riser

- 5. Seal assembly

- 6. Seal assembly

- 7. Seal assembly

- 8. Permanganate

- 9. Case

- 10. Anode riser to lead lap

weld

- 11. Oxide coating

- 12. Core

- 13. Dielectric film

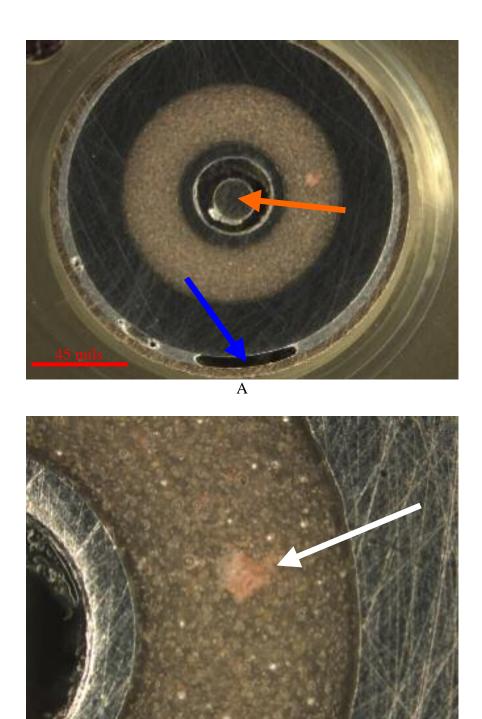

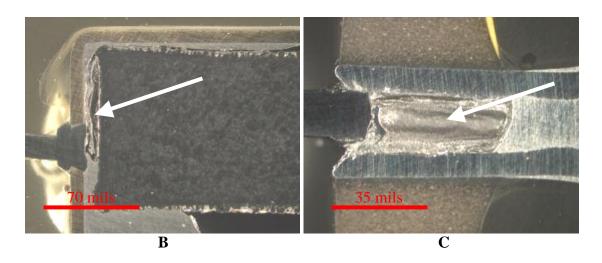

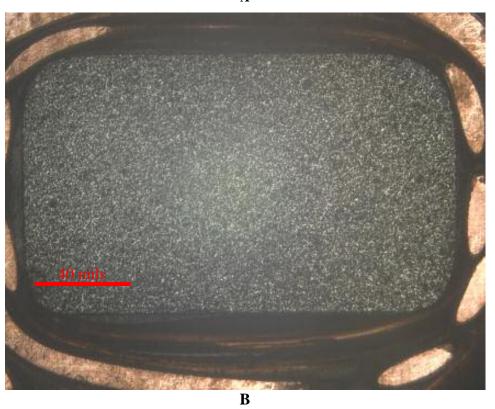

Figure 3-13: These photos show the cross-section top view of one of the tantalum capacitors. In A, it can be observed that the pin is not exactly centered, and that there are some voids in the solder. B is an enlargement of an area in A where a reddish discoloration was seen in the glass seal.

В

Figure 3-14: These photos show the cross-sectional side overview of one of the tantalum capacitors (A). In B a void in the solder in the around the tantalum plug can be seen. In C a void in the solder in the tubulet is shown.

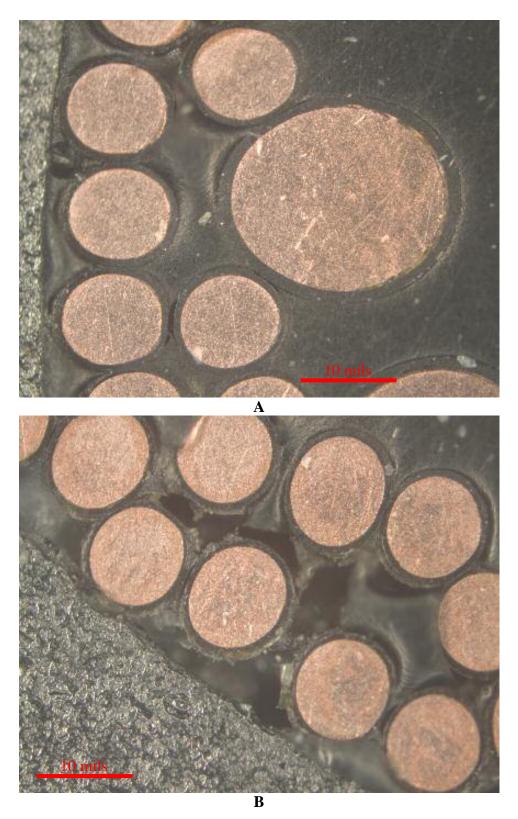

Figure 3-15: These photos show the cross-section top view of one of the transformers. B, an enlargement of an area in A, shows the separation between the coils.

Figure 3-16: These photos show the cross-section top view of one of the transformers. In B, it can be observed that there are voids between the coil wires.

Figure 3-17: These photos show the cross-sectional side overview of one of the transformers. B is an enlargement of an area in A.

# 4 LCEP

The life cycle loading for this project includes the environmental conditions that the boards are exposed during its complete life (e.g., testing, transportation, operation). The number of missions undertaken by an individual unit in the first 20 years is 15 for this project. Two profiles used for the simulation are:

- 20 years of life based on the environment seen by the boards in the last 20 years of operation

- 40 years of life, which includes the expected environment for the next 20 years of operation assuming an increased frequency of shuttle launch.

The life cycle loading characteristics included both operating and non-operating conditions. The testing for units may be done in two stages. One stage is during the manufacture of the electronic modules (e.g., SPA, EEEU) and the other is during the assembly of the complete SRMS. The complete SRMS consists of electronic modules and mechanical hardware. Where applicable, the environmental profiles are identified to be "module build" and "SRMS build."

## 4.1 Thermal Life cycle

The thermal conditions are modeled for the SRMS unit, which had the worst environmental profile. The worst case refers to the Flight EEEU, which had to go undergo qualification (qualification is typically done only once after the initial manufacture for a unit not used in space missions) due to major design changes.

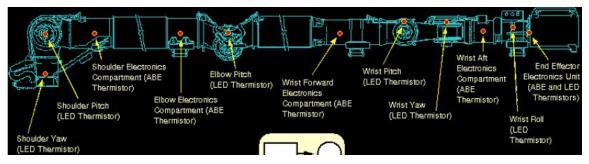

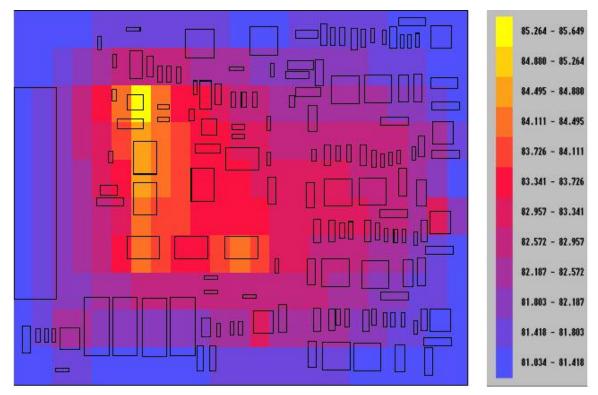

Figure 4-1: Location of thermistors on the SRMS

Figure 4-1 shows the location of the thermistors on the SRMS. The ABE thermistor at the EEEU unit end was used to obtain operation thermal cycle data.

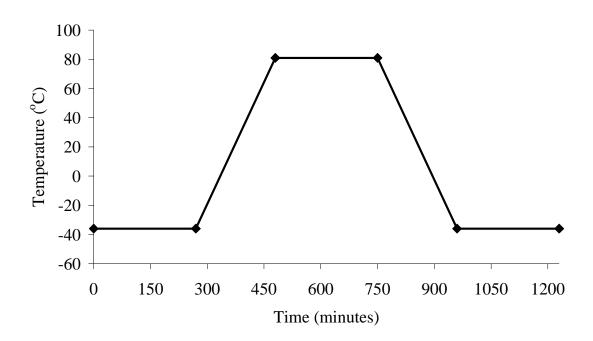

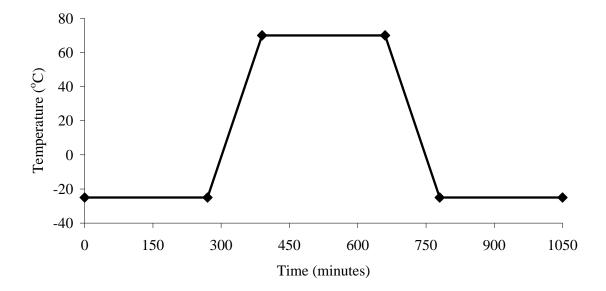

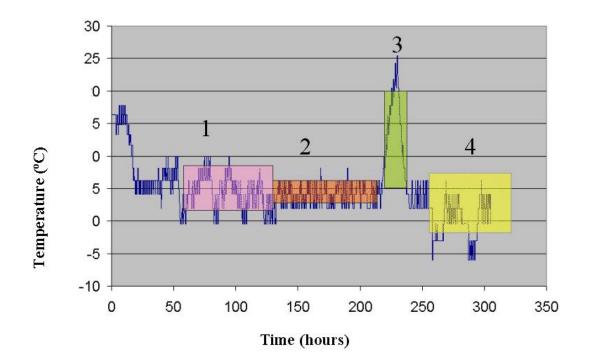

Qualification (powered up): Qualification is used to see if the unit can withstand space conditions. It consists of 50.5 cycles. The temperature profile experienced is between – 36 to 81°C. Out of the 50.5 cycles, 26 are during module build. The additional cycles were performed during SRMS build after the unit was redesigned. The profile of this cycle is shown in Figure 4-2.

Figure 4-2 Qualification temperature cycle

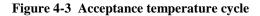

Acceptance (powered up): After assembly or rework, the units have to be requalified through acceptance tests to see if they are capable of undertaking the next mission. 1.5 cycles of thermal cycling are undergone during the module build, 2 cycles are undergone during the SRMS build. From the testing after missions, and following rework of the units, there have been 16 more thermal cycles, so the total is 20 cycles with temperatures ranging from -25 to 70 °C. Figure 4-3 shows the profile of acceptance temperature cycle.

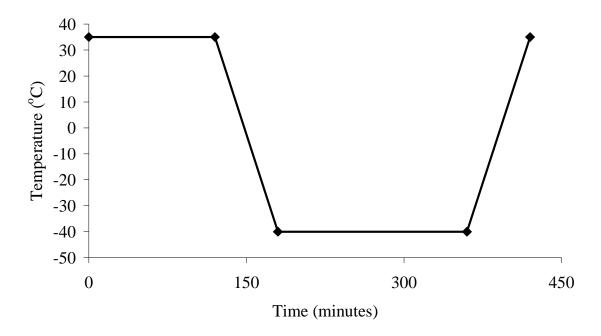

Ferry flight (non-operating): The Ferry Flights need to be undertaken when the shuttle cannot land in Florida and it uses the alternate landing site of Edwards Air force Base in California. This flight diversion takes place once in about every 3 missions so total number of ferry flights is 5 for 20-year operation. The temperature profile experienced is between -40and 35 °C. Figure 4-4 shows the profile of Ferry flight temperature cycle.

## Figure 4-4 Ferry flight temperature cycle

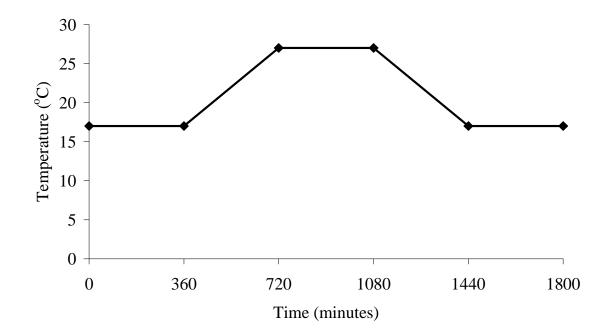

Storage (non-operating): Each SRMS spends approximately 356 days a year in climate controlled storage. The temperature profile experienced is between 17 and 27°C. It is assumed that one temperature cycle occurs each day so the total number of cycles is 7120 ( $20 \times 356$ ). Figure 4-5 shows the profile of storage temperature cycle.

#### Figure 4-5 Storage temperature cycle

Operation (powered up): consists of 4 different operation cycles based on the environmental profile given by MD Robotics. Figure 4-6 shows the profile of operation temperature cycle. The four temperature cycles are as follows:

Operation cycle 1: This cycle approximates the zone 1 shown in Figure 4-6. The temperature range is from 2 to 10 °C. Each cycle has 185 minutes-dwell time at maximum temperature, 175 minutes dwell time at minimum temperature, 720 minutes ramp from minimum to maximum temperature, 270 minutes ramp from maximum to minimum temperature. There are 3 cycles in one mission. In 15 missions over 20 years, the total number of cycles is 45.

Operation cycle 2: This cycle approximates the zone 2 shown in Figure 4-6. The temperature range is from 2 to 6 °C. Each cycle takes 1.5 hours broken up uniformly between dwell times at maximum and minimum temperature and the ramp up and the ramp down times. There are 16 cycles in one mission of 12 days, so there are a total number of 192 cycles. In 15 missions over 20 years, the total cycles are 2880. Operation cycle 3: This cycle approximates the zone 3 shown in Figure 4-6. The temperature range is from 4 to 25 °C. Each cycle has 60 minutes-dwell time at maximum temperature, 720 minutes dwell time at minimum temperature, 720 minutes ramp from minimum to maximum temperature, 720 minutes ramp from maximum to minimum temperature. There are 2 cycles in one mission. In 15 missions over 20 years, the total cycles are 30.

Operation cycle 4: This cycle approximates the zone 4 shown in Figure 4-6. The temperature range is from –6 to 4°C. Each cycle takes 720 minutes-dwell time at maximum temperature, 360 minutes dwell time at minimum temperature, 360 minutes

54

ramp from minimum to maximum temperature, 360 minutes ramp from maximum to minimum temperature. There are 2 cycles in one mission in 15 missions over 20 years the total number of cycles are 30.

The temperature conditions given above are for the first 20 years. It is expected that each SRMS would undertake 25 more missions in the next 20 years. During the next 20 years, it will undergo 75 cycles more of operation temperature cycle 1, 4800 of operation temperature cycle 2, 50 of operation temperature cycle 3, 50 of operation temperature cycle 4, 7000 cycles more of storage, 16 cycles more of acceptance and 9 more ferry flight cycles.

Figure 4-6 Operation temperature cycle example

## 4.2 Vibration

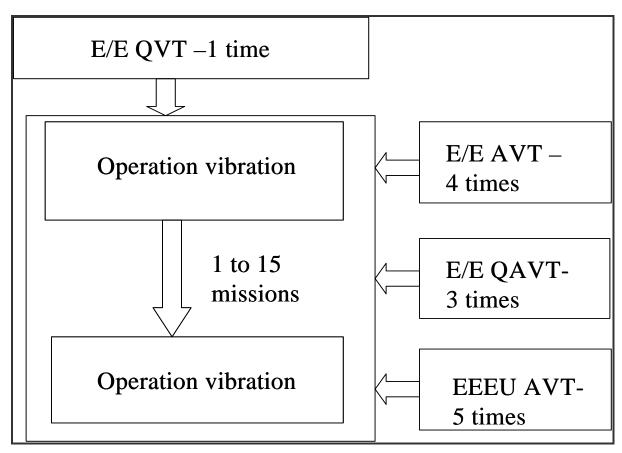

The vibration data given by MD Robotics follow the same build profile as that of thermal conditions. Figure 4-7 shows the graphical description of vibration profiles. From the

graphical description, it can be inferred that the Qualification for the End Effector is done only once and at the beginning. The 20-year profile sees 4 acceptance, and 3 qualification and acceptance vibration tests for the End Effector. The acceptance vibration is performed 5 times for the End Effector electronics unit. Each vibration profile is explained in detail below.

End Effector Electronics unit acceptance vibration test (EEEU AVT): The End Effector Electronics Unit undergoes acceptance tests after construction or rework. It is done for a period of 1 minute and since it is done 5 times a total time of 5 minutes is taken for 20 year profile. Table 4-1 EEEU AVT gives the power spectral density (PSD) values for the cycle at different frequencies.

| Frequency (Hz) | Power Spectral  |  |

|----------------|-----------------|--|

|                | Density (g2/Hz) |  |

| 20             | 0.032           |  |

| 80             | 0.500           |  |

| 200            | 0.500           |  |

| 2000           | 0.005           |  |

**Table 4-1 EEEU AVT**

Figure 4-7: Graphical description of vibration profiles

End Effector acceptance vibration test (E/E AVT): This is acceptance vibration done for the whole End Effector assembly to confirm workmanship (quality of the work) of the unit after construction or rework. This test is done 4 times for 15 missions; and the takes one minute each time. Table 4-2gives the power spectral density (PSD) values for the cycle at different frequencies.

| Frequency (Hz) | <b>Power Spectral</b> |  |

|----------------|-----------------------|--|

|                | Density               |  |

|                | (g2/Hz)               |  |

| 20             | 1                     |  |

| 80             | 1                     |  |

| 275            | 0.085                 |  |

| 470            | 0.05                  |  |

Table 4-2: E/E AVT

| 2000 | 0.05 |

|------|------|

|------|------|

End Effector quality and acceptance vibration test (E/E QAVT): This vibration cycle is performed during Qualification of the unit. The purpose of QAVT is to prove that the Qualification unit is designed well enough to survive all AVT's, which a flight unit will see. It is done 3 times for 15 minutes each. Table 4-3 gives the power spectral density (PSD) values for the cycle at different frequencies.

| Frequency (Hz) | <b>Power Spectral</b> |  |

|----------------|-----------------------|--|

|                | Density               |  |

|                | (g2/Hz)               |  |

| 20             | 0.017                 |  |

| 80             | 0.068                 |  |

| 350            | 0.068                 |  |

| 2000           | 0.012                 |  |

| Table | 4-3: | E/E | QA | VT |

|-------|------|-----|----|----|

|-------|------|-----|----|----|

End Effector qualification vibration test (E/E QVT): This vibration cycle is performed during Qualification of the unit. The purpose of QVT is to prove that the Qualification unit is designed well enough to survive all life vibrations, which a flight unit will see. It is done once for 50 minutes. Table 4-4 gives the power spectral density (PSD) values for the cycle at different frequencies.

| Frequency (Hz) | Power Spectral<br>Density<br>(g2/Hz) |

|----------------|--------------------------------------|

| 20             | 0.010                                |

| 80             | 0.040                                |

| 350            | 0.040                                |

| 2000           | 0.007                                |

Table 4-4: E/E QVT

Operation vibration: This refers to the vibration that the boards are exposed to in a normal mission, it lasts for 5 seconds, and since there are total of 15 missions the total time taken is 75 seconds. The PSD profile of the End Effector Electronics unit qualification vibration test (EEEU QVT) is used for operation profile because it is considered as an indicator of operation vibration. Table 4-5 gives the power spectral density (PSD) values at different frequencies.

| Frequency | Power    |  |

|-----------|----------|--|

| (Hz)      | Spectral |  |

|           | Density  |  |

|           | (g2/Hz)  |  |

| 20        | 0.010    |  |

| 80        | 0.040    |  |

| 350       | 0.040    |  |

| 2000      | 0.007    |  |

Table 4-5: Operation vibration

The data for 40 years includes 8 more EEEU AVT's and 125 (5 seconds per launch) seconds more for operation vibration.

# 5 Failure Modes and Effects analysis

Failure modes and effects analysis (FMEA) was done to identify the different failures and modes of failure that can occur at the component, subsystem, and system levels. The FMEA was initially done based on the failures that have occurred and were observed during the physical analysis. FMEA identified temperature and vibration as the two loads that would possible cause maximum damage on the electronics. Table 5-1 gives a FMEA done on the system and second half of the table gives a complete listing of failure effects for space electronics.

| FAILURE MODES                                                                                                        | FAILURE LOADS AND EFFECTS                                                                                                                                                                                                                                                 |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Open circuit, unmating of contact surfaces of connectors.                                                            | Vibration and g forces encountered during launch.                                                                                                                                                                                                                         |  |

| Possible instability of transformers, corrosion of metallization, electrical open, shift in parametrics.             | High temperature(150 degree c) because of solar radiation. High temperature proximity of power sources where heavy electric currents have heating effects.                                                                                                                |  |

| Wire breakage and broken leads.                                                                                      |                                                                                                                                                                                                                                                                           |  |

| Effect of fretting or mechanical fatigue of interconnection materials.                                               | Cracks of voids around weld circumference.                                                                                                                                                                                                                                |  |

| Weld at low heat produce too small spot weld size<br>and inadequate weld strength under tension and<br>shear.        | Open circuits, component failures, electrical resistance of wirebonds increase significantly as a function of time and temperature.                                                                                                                                       |  |

| Reduction in contact efficiency when dissimilar metals are in contact.                                               | Thermal cycling causes the reduction in contact<br>efficiency continued cycling expansion and<br>contradiction may cause one part to slightly exceed<br>its material elastic limit at one temperature extreme.                                                            |  |

| Thermal fatigue cracking.                                                                                            | Stresses imposed in solder joints during thermal cycling where free thermal expansion is partly or entirely restrained.                                                                                                                                                   |  |

| Cleavage fracture caused due to formation of intermetallics.                                                         | Under high temperatures.                                                                                                                                                                                                                                                  |  |

| Formation of cracks due to board distortion problems.                                                                | High temperature may cause the base laminate of PCBs to rise above the glass transition temperature in turn causing the epoxy or the laminate to become soft causing a relaxation of the support medium which is usually woven glass fibre thus causing board distortion. |  |

| Failures (open circuit – solder joint) due to                                                                        | Caused due to temperature cycling during                                                                                                                                                                                                                                  |  |

| difference on expansion and contraction of PCB's,<br>component parts and conformal coating applied to<br>assemblies. | qualification tests.                                                                                                                                                                                                                                                      |  |

| Degradation of internal copper tracks to plated                                                                      | Caused by repeated thermal shocks by reworking of                                                                                                                                                                                                                         |  |

| Events of LCEP<br>during which the<br>load occurs | Environment            | Principal effects                                                                                                                                                                        | Typical failures<br>induced                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Testing and operation                             | High temperature       | Thermal aging<br>Oxidation<br>Structural change<br>Chemical reaction<br>Softening, melting and<br>sublimation<br>Viscosity reduction/<br>evaporation<br>Physical expansion<br>outgassing | Insulation failure due to<br>melting<br>Alteration of electrical<br>properties due to changes<br>in resistance<br>On chip failures<br>(metallization migration,<br>Kirkendall voiding in<br>wirebonds, slow trapping,<br>time dependent dielectric<br>breakdown) 1820<br>Melting of solder joints<br>1921<br>Unequal expansion of<br>assemblies leading to<br>fracture 19<br>Ionic contamination 19 |