#### ABSTRACT

| Title of Thesis:    | MEMORY SUBSYSTEM DESIGN FOR                                                |  |

|---------------------|----------------------------------------------------------------------------|--|

|                     | EXPLICIT MULTITHREADING ARCHITECTURES                                      |  |

| Degree candidate:   | Joseph Nuzman                                                              |  |

| Degree and year:    | Master of Science, 2003                                                    |  |

| Thesis directed by: | Professor Uzi Vishkin<br>Department of Electrical and Computer Engineering |  |

Explicit multithreading (XMT) is a parallel programming approach for exploiting on-chip parallelism. An important enabler for XMT is sufficient memory bandwidth to support parallelism. For targeted deep-submicron VLSI processes, chip designers will be faced with the widely acknowledged issues of rising interconnect RC delays and shortening clock periods. Comprehensive memory design for an XMT architecture has never before been rigorously studied. This thesis relies on an examination the implications of the XMT programming model on memory subsystem design to motivate a potential framework for on-chip memory interconnection. Many system-level issues are considered, and analytical electrical interconnect modeling is used to demonstrate the physical viability of new structures in future processes. It is estimated that a chip, built in a 2008 process with 1024 hardware execution contexts, may be capable of a sustained on-chip memory transaction throughput of 1430 GB/s.

# MEMORY SUBSYSTEM DESIGN FOR EXPLICIT MULTITHREADING ARCHITECTURES

by

Joseph Nuzman

Thesis submitted to the Faculty of the Graduate School of the University of Maryland at College Park in partial fulfillment of the requirements for the degree of Master of Science 2003

Advisory Committee:

Professor Uzi Vishkin, Chairman/Advisor Professor Gang Qu Professor Ankur Srivastava © Copyright by Joseph Nuzman 2003

# DEDICATION

To my mother, Susan, and father, Dwayne.

#### ACKNOWLEDGEMENTS

Firstly, I would like to thank Dr. Uzi Vishkin. I first began working with Dr. Vishkin as an undergrad in February 1997, and have been involved with his research, in some form or another, for over six years. It is a rare privilege to have been so deeply involved in a project as challenging, ambitious, and expansive as XMT. In addition to guiding this work, Dr. Vishkin has provided many lessons on the value of tenacity. Thanks, Uzi.

I owe a debt of gratitude to many others who have influenced my work. Shlomit Dascal helped to mentor me during my first steps in research. Efraim Berkovich helped to lay much of the groundwork for my later research. Particularly helpful was our collaboration on the first XMT simulator. Dr. Manoj Franklin was kind enough to provide direction during certain stages of my research. Dr. Jeff Davis provided helpful technical input. Aydin Balkan provided many helpful comments on this thesis. Lastly, I'd like to acknowledge the many contributions of Dorit Naishlos. My collaboration with Dorit was by far the most productive and stimulating period of my research career. Without her example, this work would never have been what it is.

# TABLE OF CONTENTS

| Li       | List of Tables ix |                                              |    |  |  |

|----------|-------------------|----------------------------------------------|----|--|--|

| Li       | st of             | Figures                                      | x  |  |  |

| 1        | Intr              | oduction                                     | 1  |  |  |

| <b>2</b> | Ove               | erview of the XMT Framework                  | 4  |  |  |

|          | 2.1               | XMT Programming Model                        | 5  |  |  |

|          | 2.2               | The XMT Architecture                         | 8  |  |  |

|          | 2.3               | The XMT Compiler                             | 14 |  |  |

| 3        | ΑI                | Discussion of Memory from an XMT Perspective | 17 |  |  |

|          | 3.1               | Statement of the Design Goal                 | 18 |  |  |

|          | 3.2               | Overview of Existing Technologies            | 19 |  |  |

|          | 3.3               | XMT Consistency Model                        | 21 |  |  |

|          |                   | 3.3.1 Thread-Local View                      | 22 |  |  |

|          |                   | 3.3.2 Standard (Non-Fork) Spawn Regions      | 22 |  |  |

|          |                   | 3.3.3 Forking Spawn Regions                  | 27 |  |  |

|          | 3.4               | Instruction Memory                           | 27 |  |  |

|          | 3.5               | Prefix-Sum Support                           | 28 |  |  |

| 4        | Nev            | w Men   | nory Subsystem Architecture  | 31 |

|----------|----------------|---------|------------------------------|----|

|          | 4.1            | Memo    | ory Structure                | 31 |

|          | 4.2            | Interc  | connect Design               | 35 |

|          |                | 4.2.1   | Crossbar Interconnect        | 35 |

|          |                | 4.2.2   | Novel Solution               | 37 |

|          |                | 4.2.3   | Summary                      | 41 |

| <b>5</b> | $\mathbf{Sys}$ | tem In  | nplementation                | 43 |

|          | 5.1            | Proces  | ssing Cluster Architecture   | 43 |

|          | 5.2            | Cache   | e Module Design              | 46 |

|          | 5.3            | Optim   | nizations                    | 48 |

|          |                | 5.3.1   | Lowering Latency             | 48 |

|          |                | 5.3.2   | Single Address Problem       | 52 |

|          | 5.4            | Instru  | action Memory Subsystem      | 54 |

|          | 5.5            | Parall  | lel Register Implementation  | 54 |

|          |                | 5.5.1   | ISA Specifications           | 54 |

|          |                | 5.5.2   | Hardware Implementation      | 55 |

|          |                | 5.5.3   | Asynchronous Parallel Queues | 59 |

| 6        | Des            | sign St | udy                          | 63 |

|          | 6.1            | Specif  | fications                    | 63 |

|          |                | 6.1.1   | Design Goals                 | 63 |

|          |                | 6.1.2   | Floorplan Layout             | 64 |

|          |                | 6.1.3   | Specific Choices             | 68 |

|          | 6.2            | Area (  | Calculation                  | 72 |

|          |                | 6.2.1   | General Methodology          | 72 |

|   |     | 6.2.2   | Results                                              | 74  |

|---|-----|---------|------------------------------------------------------|-----|

|   | 6.3 | Timin   | g Estimation                                         | 78  |

|   |     | 6.3.1   | General Methodology                                  | 78  |

|   |     | 6.3.2   | Results                                              | 81  |

| 7 | Cor | clusio  | n                                                    | 84  |

| Α | Glo | ssary o | of New Programming Constructs                        | 86  |

| в | XM  | T-M     |                                                      | 91  |

|   | B.1 | Introd  | uction                                               | 92  |

|   | B.2 | Explic  | it Multi-Threading (XMT)                             | 95  |

|   |     | B.2.1   | The XMT Programming Model                            | 96  |

|   |     | B.2.2   | XMT High-Level Language Level                        | 97  |

|   |     | B.2.3   | The XMT Instruction Set Architecture (ISA)           | 98  |

|   |     | B.2.4   | A Design Principle Guiding XMT: No-busy-waits Finite |     |

|   |     |         | State Machines                                       | 100 |

|   | B.3 | Decen   | tralized XMT Microarchitecture                       | 101 |

|   |     | B.3.1   | Prefix-sum Implementation                            | 103 |

|   |     | B.3.2   | Spawn/Join Implementation                            | 104 |

|   |     | B.3.3   | Global Register Coordination                         | 106 |

|   |     | B.3.4   | Memory System                                        | 107 |

|   | B.4 | Exper   | imental Evaluation                                   | 110 |

|   |     | B.4.1   | Experimental Framework                               | 110 |

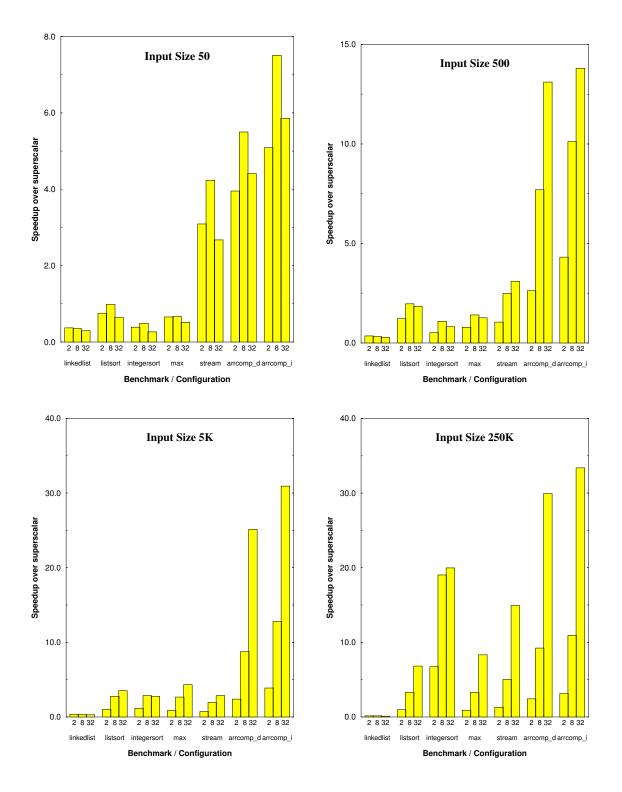

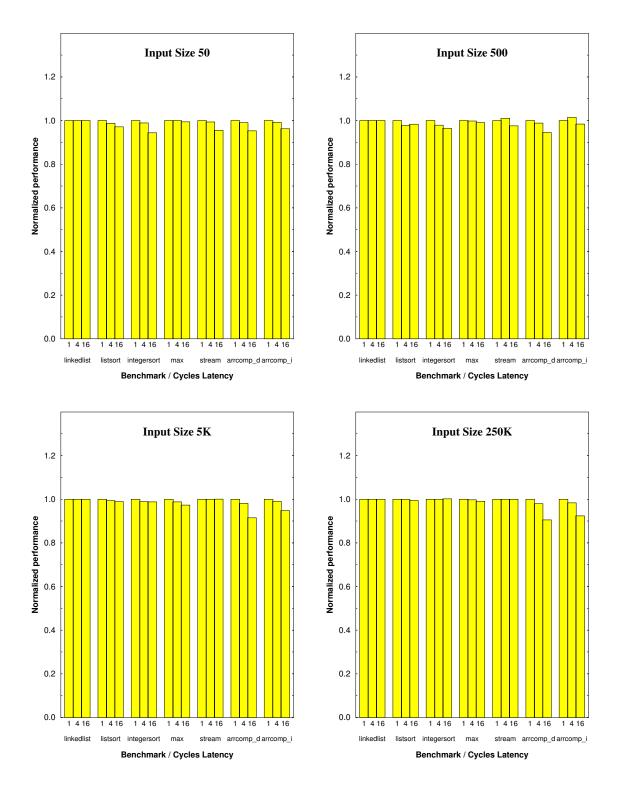

|   |     | B.4.2   | XMT-M Performance                                    | 114 |

|   |     | B.4.3   | Effect of Cross-chip Communication Latency on XMT-M  |     |

|   |     |         | Performance                                          | 115 |

|    | B.5            | Relate                              | ed Work                                        | 116 |

|----|----------------|-------------------------------------|------------------------------------------------|-----|

|    | B.6            | Concluding Remarks                  |                                                |     |

| С  | $\mathbf{Syn}$ | nchronous Crossbar Interconnect     |                                                |     |

|    | C.1            | A new approach to parallel memories |                                                |     |

|    |                | C.1.1                               | Modeling parallel memories                     | 124 |

|    |                | C.1.2                               | Parallel coordination                          | 126 |

|    |                | C.1.3                               | Parallel distribution                          | 129 |

|    | C.2            | Impler                              | mentation considerations                       | 129 |

|    |                | C.2.1                               | Interconnection network design                 | 129 |

|    |                | C.2.2                               | All-to-all connection                          | 130 |

|    |                | C.2.3                               | Prefix-sum                                     | 131 |

|    | C.3            | Design                              | ı study                                        | 131 |

|    |                | C.3.1                               | Specific choices                               | 132 |

|    |                | C.3.2                               | Unidirectional interconnect - Pairing of nodes | 132 |

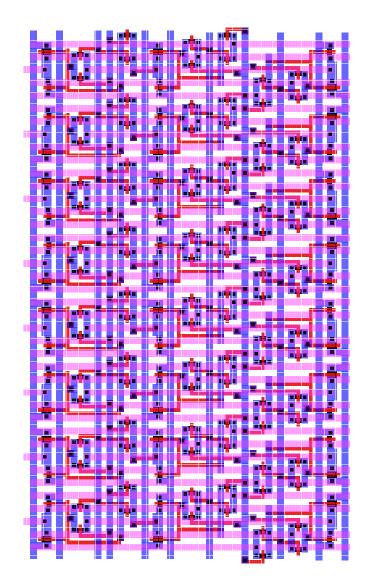

|    |                | C.3.3                               | Building block: Mux node                       | 133 |

|    |                | C.3.4                               | For a better aspect ratio: Triple mux node     | 133 |

|    |                | C.3.5                               | Big picture                                    | 136 |

|    |                | C.3.6                               | Area analysis                                  | 136 |

|    | C.4            | Integra                             | ation with XMT                                 | 139 |

|    |                | C.4.1                               | Cluster corresponds to PE?                     | 139 |

|    |                | C.4.2                               | General prefix-sum implementation              | 139 |

|    |                | C.4.3                               | Spawn implementation                           | 140 |

| D  | Har            | dware                               | Implementation of Prefix-Sum                   | 141 |

| Bi | bliog          | graphy                              |                                                | 145 |

## LIST OF TABLES

| 6.1 | System Configuration                        | 71 |

|-----|---------------------------------------------|----|

| 6.2 | Technology Parameters - Area Estimation     | 73 |

| 6.3 | KSMS Configuration - Relevant Parameters    | 75 |

| 6.4 | Area Estimation Results - DRAM case         | 76 |

| 6.5 | Area Estimation Results - SRAM case         | 76 |

| 6.6 | Technology Parameters - Transistor Modeling | 79 |

| 6.7 | Technology Parameters - Wire Modeling       | 80 |

| 6.8 | Timing Estimation Results                   | 82 |

## LIST OF FIGURES

| 2.1 | Program counter + stored program                               |  |  |

|-----|----------------------------------------------------------------|--|--|

| 2.2 | TCU program snippet 10                                         |  |  |

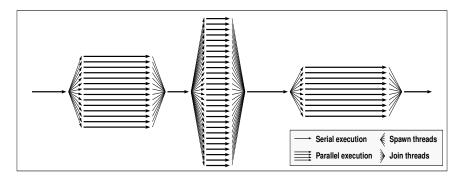

| 2.3 | XMT code shape                                                 |  |  |

| 4.1 | Parallel memory modules                                        |  |  |

| 4.2 | Memory system interconnect                                     |  |  |

| 4.3 | Traditional layout                                             |  |  |

| 4.4 | New layout                                                     |  |  |

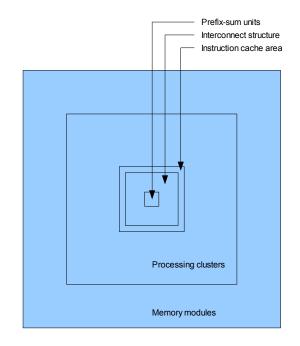

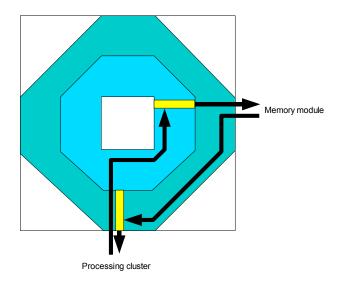

| 6.1 | General floorplan                                              |  |  |

| 6.2 | Memory network                                                 |  |  |

| B.1 | Parallelism profile for the XMT model                          |  |  |

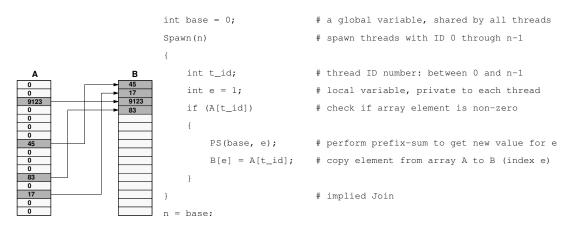

| B.2 | The array compaction problem                                   |  |  |

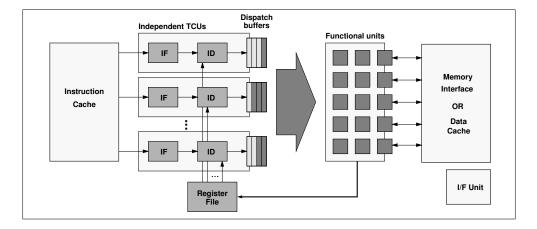

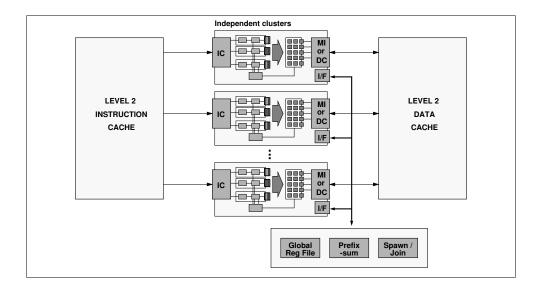

| B.3 | An XMT-M Cluster                                               |  |  |

| B.4 | An XMT-M processor                                             |  |  |

| B.5 | Flowchart depicting activities of a TCU upon receiving a Spawn |  |  |

|     | command                                                        |  |  |

| B.6 | Cache coherence hazards for XMT                                |  |  |

| B.7 | Benchmarks                                                     |  |  |

| B.8 | XMT-M Speedups relative to serial computing                    |  |  |

| B.9 | Effect of cross-chip (global) communication latency on XMT-M |

|-----|--------------------------------------------------------------|

|     | performance                                                  |

| C.1 | Mux node VLSI layout                                         |

| C.2 | Triple mux node VLSI layout                                  |

| C.3 | Stacked triple mux nodes VLSI layout                         |

## Chapter 1

## Introduction

The challenge of exploiting the large and fast-growing number of transistors available on modern chips has motivated the exploration of parallel architectures. Researchers have considered parallelism in two main categories. The first is at an ultra fine-grained level, among instruction sequences. However, the limited amount of instruction-level parallelism (ILP) present in programs, and the difficulties to uncover it [31] [59] prevent computers from fully exploiting the available on-chip resources. An alternative source of parallelism is at the level of coarse-grained multithreading, and has been traditionally expressed under the shared memory or the message-passing programming models, either directly by programmers, or with the aid of parallelizing compilers.

While some new architectures ([22] [53]) have the ability to exploit fine-grained parallelism, they report difficulties obtaining fine-grained multi-threaded codes for today's important uniprocessor programs [23]. On one hand, parallelizing compilers have been only partially successful at automatically converting serial codes. On the other hand, the programming models currently available to programmers were originally designed to target multi-chip parallel architectures, and therefore do not fit a single-chip environment. XMT (explicit multi-threading) attempts to bridge the gap between the ultra fine-grained on-chip parallelism and the coarse-grained multi-threaded program by proposing a framework that encompasses both programming methodology and hardware design. XMT tries to increase available ILP using the rich knowledge base of parallel algorithms. Relying on parallel algorithms, rather than on a compiler, programmers express extremely fine-grained parallelism at the thread level.

Early papers on XMT have discussed in detail its fine-grained single program multiple data (SPMD) multi-threaded programming model, architectural support for concurrently executing multiple contexts on-chip, and preliminary evaluation of several parallel algorithms using hand-coded assembly programs [56] [13]. The introduction of an XMT compiler, allowed us to evaluate XMT for the first time as a complete environment ("vertical prototyping"), using a much larger benchmark suite (with longer codes) than before. The evaluation of the XMT compiler and evaluation of the programming model were published in two specialized workshops, [39] and [40] respectively. The followup [41] presented the integrated results, as well as the interplay between the programming model and the other components of XMT (compiler and architecture).

XMT as a framework developed starting from the area of parallel algorithms. While the goals are ambitious, every effort has been made to make the means as modest as possible. Those novel elements which are essential, including the spawn-join construction and the no-busy-wait ideal, are layered on top of standard computing concepts in the least disruptive manner possible.

In keeping with the thrust of the framework as a whole, the approach to XMT hardware design has been largely opportunistic: recognizing the changing constraints of system design with new technology. Wherever possible, the architectural philosophy of XMT has been to rely on proven elements. This allows XMT design to benefit from general technological progress in the industry. However, to enable the framework to work effectively, XMT has been forced to distinguish itself in two hardware architectural aspects. The first piece, the hardware prefix-sum mechanism, provides for the low-overhead coordination of many parallel threads. This was first introduced in [55] in 1997. The second piece is an effective on-chip parallel memory subsystem. This second enabling technology is presented in detail for the first time in this thesis.

We begin by briefly reviewing the XMT multi-threaded programming model, architecture, and compiler technology in Chapter 2. We then step back to consider the characteristics of memory subsystem design from an XMT perspective in Chapter 3. Chapter 4 serves to present the essential points of the proposed memory architecture. This is followed by Chapter 5, which considers issues in implementing the memory as part of the system as a whole. Chapter 6 evaluates the low-level characteristics of a practical design in deep submicron technology, including area and timing details. Finally, Chapter 7 concludes.

The reader may wish to consider that this thesis documents research largely finished by late 2000, but presented for submission at this time.

## Chapter 2

## **Overview of the XMT Framework**

Most of the programming effort involved in traditional parallel programming (domain partitioning, load balancing) is of lesser importance for exploiting on-chip parallelism, where parallelism overhead can be made low and memory bandwidth can be made high. This observation motivated the development of the XMT programming model. XMT is intended to provide a parallel programming model, which is (1) simpler to use, yet (2) efficiently exploits on-chip parallelism.

These two goals are achieved by a number of design elements; The XMT architecture attempts to take advantage of the faster on-chip communication times to provide more-uniform memory access latencies. In addition, a specialized hardware primitive (prefix-sum) exploits the high on-chip communication bandwidth to provide low overhead thread creation. These low overheads allow the efficient support of fine-grained parallelism. Fine granularity is in turn used to hide memory latencies, which, in addition to the more uniform memory accesses, supports a programming model where locality is less of an issue. The XMT hardware also supports dynamic load balancing, relieving the programmers of the task of assigning work to processors. The programming model is simplified further by letting threads always run to completion without synchronization (no busy-waits), and synchronizing accesses to shared data with a prefix-sum instruction. All these features enable efficient support for simple, algorithm-centric spawn-join semantics. The end result is a flexible programming style, which encourages the development of new algorithms, and is expected to target a wider range of applications.

## 2.1 XMT Programming Model

The programming model underlying the XMT framework is an arbitrary CRCW (concurrent read concurrent write) SPMD (single program multiple data) programming model. In the XMT programming model, an arbitrary number of virtual threads, initiated by a *spawn* and terminated by a *join*, share the same code [58]. The arbitrary CRCW aspect dictates that concurrent writes to the same memory location result in an arbitrary one committing. No assumption needs to be made beforehand about which will succeed. This permits each thread to progress at its own speed from its initiating *spawn* to its terminating *join*, without ever having to wait for other threads; that is, no thread busy-waits for another thread. The implied "independence of order semantics" (IOS) allows XMT to have a shared memory with a relatively weak coherence model. An advantage of using this easier to implement SPMD model is that it is also an extension of the classical PRAM model, for which a vast body of parallel algorithms is available in the literature. (Previous XMT papers related the relaxation in the synchrony of PRAM algorithms to works such as [10] and [20] on asynchronous PRAMs).

The programming model also incorporates the *prefix-sum* statement. The *prefix-sum* operates on a base variable, B, and an increment variable, R. The result of a *prefix-sum* (similar to an atomic fetch-and-increment) is that B gets the value B + R, while the return value is the initial value of B. The primitive is es-

pecially useful when several threads simultaneously perform a prefix-sum against a common base, because multiple prefix-sum operations can be combined by the hardware to form a multi-operand prefix-sum operation. Because each prefixsum is atomic, each thread will receive a different return value. This way, the parallel prefix-sum command can be used for implementing efficient and scalable interthread synchronization, by arbitrating an ordering between the threads.

The XMT-C high-level language is an extension of standard C. The extensions are described individually in Appendix A. A parallel region is delineated by spawn and join statements. Synchronization is achieved through the prefix-sum and join commands. Every thread executing the parallel code is assigned a unique thread ID, designated TID. The spawn statement takes as arguments the number of threads to spawn and the ID of the first thread. Consider the following example of a small XMT-C program. Suppose we have an array of n integers, A, and wish to "compact" the array by copying all non-zero values to another array, B, in an arbitrary order. The code below spawns a thread for each element in A. If its element is non-zero, a thread performs a prefix-sum (ps in XMT-C) to get a unique index into B where it can place its value:

```

m = 0;

spawn(n,0);

{

int TID;

if (A[TID] != 0) {

int k;

k = ps(&m,1);

B[k] = A[TID];

}

}

join();

```

The SpawnMT model of [56] does not support nested initiation of an arbitrary-

size spawn within a parallel spawn region. Such a feature, while useful, would be difficult to realize efficiently with hardware support. As an alternative, Vishkin [57] extended the programming model to support a fork operation. A thread can perform a fork operation to introduce a new virtual thread as work is discovered. Forks must be executed one at a time by a single thread, but forks from multiple threads can be performed in parallel. The fork extension allows the programmer to approach many problems in a more asynchronous and dynamic manner. In XMT-C, *fspawn* is used when forking may be necessary, in lieu of a nested spawn. Within an *fspawn*, an *xfork* indicates a fork operation.

The attempt to develop general-purpose parallel algorithms that map well to different parallel machines, has led researchers to utilize different parallel models. In [45] the QSM model is used to design and analyze general-purpose parallel algorithms, along with a suitable cost metric (which is shown to be accurate for big problem sizes). The algorithms they present are adaptations of PRAM algorithms and their mapping to other parallel models is discussed. XMT is also motivated by the attempt to provide a way to map general-purpose parallel algorithms to a real parallel machine. The XMT architecture is designed to provide such a prototype target machine for which it is easy to map PRAM algorithms, using the XMT programming model.

MIT's Cilk [19] also provides a multi-threaded programming interface and execution model, however, there are two important differences in scope. First, since Cilk is targeted at compatibility with existing symmetric multiprocessor (SMP) machines, load balancing in software was important. XMT provides hardware support to bind virtual threads to thread control units (TCUs) exactly as the TCUs become available. The low-overhead of XMT is designed to be applicable to a much broader range of applications. Second, Cilk presents a programming model that tries to match very closely standard serial programming constructs, where forking a thread takes the form of a function call. While XMT also bases its programming model on standard C, the programmer is expected to rethink the way parallelism is expressed. The wide-spawn capabilities and prefix-sum primitive are present to support the many algorithms targeted to the PRAM model. One has to keep in mind that XMT is PRAM-like programming, but not exactly PRAM programming.

## 2.2 The XMT Architecture

The most important distinguishing characteristics of an XMT architecture are low-overhead mechanisms for the management of parallelism. New elements not present in standard microprocessor design are introduced for the purpose of supporting the parallel programming model.

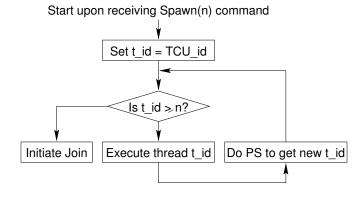

The XMT programming model allows programmers to specify an arbitrary degree of parallelism in their code. Clearly, real hardware has finite execution resources, so in general all threads cannot execute simultaneously. In an XMT machine, a TCU executes an individual virtual thread. Upon termination, the TCU performs a prefix-sum operation in order to receive a new thread ID. The TCU will then emulate the thread with that new ID. All TCUs repeat the process until all the virtual threads have been completed.

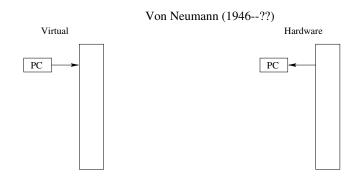

This is illustrated: (i) through a comparison with the von Neumann stored program and program counter apparatus (Figure 2.1), and (ii) through a snippet of the program of a TCU (Figure 2.2).

We begin with Figure 2.1. Its upper part, entitled "Von Neumann (1946–??),"

Figure 2.1: Program counter + stored program

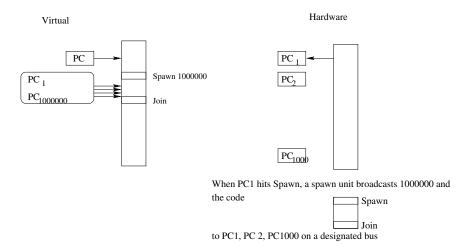

Figure 2.2: TCU program snippet

illustrates the program counter apparatus in serial machines, which has dominated general-purpose computing since 1946, with no end in sight to its reign. The *right-hand side* (of the upper part of Figure 2.1) depicts the hardware apparatus, where one command at a time is brought to the program counter. The *left-hand side* (of the upper part of Figure 2.1) demonstrates how the programmer is often educated to think about this apparatus — the virtual outlook. Here the program counter is the one to move; it moves from one location of the memory to another, perhaps like a book analogy, where the finger of a reader advances from one line of the book to another. The fact that this von Neumann apparatus has survived orders of magnitude improvements in speed since the 1940s makes it a remarkable "Darwinistic" success story. For this reason we sought to upgrade, rather than replace in a disruptive manner, this successful apparatus.

The lower part of Figure 2.1, entitled "XMT," illustrates the new apparatus.

The *left-hand side* (of the lower part of Figure 2.1) depicts the virtual description. There is still one computer program as in the von Neumann apparatus. In the above book analogy, finger (program counter) number 1 moves from one line of the book to another, until it reaches a special command called Spawn. The Spawn command specifies a number of "threads" which can be performed in parallel. Since we are concerned at the moment with the virtual side, any number of threads may be specified. Figure 2.1 diagrams 1,000,000 threads. The virtual threads, initiated by a Spawn and terminated by a Join, share the same code. At run-time, different threads may have different lengths, based on individual control flow decisions. The programmer's understanding will be that each of the threads can progress (guided by one finger per thread) from the Spawn command to a subsequent Join command at its own speed. At the Join, the thread expires. Once all the virtual threads expire, finger number 1 continues. The main difference in the hardware description on the *right-hand side* (of the lower part of Figure 2.1), is that the number of program counters is fixed (the figure mentions 1000), and does not change as a function of the Spawn command at hand. When program counter number 1 executes a Spawn command it broadcasts the instructions of a thread (i.e., until a Join command) to the other program counters. This broadcast is performed on a broadcast network, which due to the simple topology required could be made very efficient. The program counters start by executing the first 1000 among the 1,000,000 threads, one thread each. When a program counter completes its thread, it starts executing one of the yet-to-be-executed threads. This is done until all of the 1,000,000 threads finish.

Figure 2.2 illustrates the program of a TCU. Suppose that n = 1,000,000 threads are to be executed as a result of a Spawn command. The figure assumes

that n, and the SPMD code, were broadcast to all TCUs. TCU i starts by executing the respective virtual thread i, but only if i is not larger than n. Upon finishing the execution of a virtual thread, the TCU uses a prefix-sum computation to obtain the ID of the next virtual thread it should execute, and proceeds to execute it if that ID is not larger than n. Note that the only communication among TCUs above was through the prefix-sum computation.

This functionality is enabled by support at the instruction set level. With this architecture, all TCUs independently execute a serial program. Each accepts the standard MIPS instructions, and possesses a standard set of MIPS-type registers locally. The expanded instruction set architecture (ISA) includes a set of specialized global registers, called prefix-sum registers (PR), and a few additional instructions. New instructions are used for thread management (Appendix A may be consulted for a glossary which includes separate descriptions of these new instructions). A spawn instruction activates all TCUs and broadcasts a new PC at which all TCUs will start executing. The *pinc* instruction operates on the PR registers, and performs a parallel prefix-sum with value 1. A specialized global prefix-sum unit can handle multiple *pinc*'s to the same PR register in parallel. Simultaneous *pinc*'s from different TCUs are grouped, and the prefix-sum is computed and broadcast back to the TCUs. A prefix-sum functional unit with 64 single-bit inputs is very similar to a 64-bit integer adder (please see Appendix D or [55] for additional details on this unit); in each cycle only the differential increments are calculated and sent back to the clusters. This process is pipelined and completes within a constant number of cycles. *pread* performs a parallel read (prefix-sum with value 0) of a (replicated) PR register, and *pset* is used (serially) to initialize a PR register. The psm instruction allows for communication and

synchronization between threads. It performs a prefix-sum operation with an arbitrary increment to any location in memory. It is an atomic operation, but due to hardware limitations, operations to the same base address are not performed in parallel (i.e., concurrent psm's will be queued). This is similar to a fetch-and-increment [18] primitive (see [2]). A ps command at the XMT-C level is translated to a psm instruction.

Additional instructions exist to support the nested forking mechanism. A new thread to be forked requires some form of initialization. This initialization can be performed by the forking thread with the aid of *psalloc* and *pscommit*. The *psalloc* instruction works like a *pinc*, but the increment to the PR register is not visible to anyone else until the forking thread performs the corresponding *pscommit*. This allows the forking thread to initialize data (usually just a pointer) before a forked thread starts. Note that like the *pinc* instruction, *psalloc/pscommit* from many TCUs can be performed in parallel batches. The last new instruction, *suspend*, is also used when forking may occur. An idle TCU can suspend, waiting for its assigned thread ID to become valid, without consuming any execution resources.

The fundamental hardware units of execution for the machine are these multiple TCUs, each of which contains a separate execution context. In implementation, an individual TCU basically consists of the fetch and decode stages of a simple pipelined processor. To increase resource utilization and to hide latencies, sets of TCUs can be grouped together to form a cluster, each cluster quite similar in spirit to an SMT processor. The TCUs in a cluster share a common pool of functional units, as well as memory access and prefix-sum access resources. The clusters can be replicated repeatedly on a given chip.

More detail about XMT architecture prior to the work of this thesis can be

found in Appendix B.

## 2.3 The XMT Compiler

A strength of the XMT model is that its performance potential does not hinge on the development of sophisticated compiler analysis and transformation techniques. The results of the paper were obtained with a prototype compiler which performs only relatively straightforward transformations of the programmer's code.

Parallel execution in the XMT architecture requires handling:

- transition to parallel mode activate all the TCUs and set up their environment;

- thread creation and termination emulate the virtual threads on each TCU, obtain a thread ID for each, and verify that it is a valid ID (i.e., less than the spawn size);

- transition back to serial mode detect when all threads have terminated, and resume serial execution.

In first presentations of XMT, these tasks were handled entirely by hardware automatons. Later work introduced a scheme whereby the preceding tasks are orchestrated by compiler. This choice pays off in performance and flexibility. For example, the compiler is free to schedule certain operations to have a per-TCU cost rather than a per-thread cost. Additionally, the more general hardware allows for various extensions, such as different forking schemes, and can easily support parallelization models other than XMT.

| Original Xmt-C program                                                                      | Transformed to                                                                                                                                                |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>main() {     spawn(num_threads, offset);     {         int TID;         int TID;</pre> | <pre>main() {     spawn_setup(num_threads, offset);     main_0_spawn(); }</pre>                                                                               |

| **THREAD-CODE**<br>}<br>join();<br>}                                                        | <pre>main_0_spawn () {     int TID, maxtid, offset;     spawn_init(&amp;max_tid, &amp;offset);     TID = TCUID + offset;     while (TID &lt; max_tid) {</pre> |

|                                                                                             | **THREAD-CODE**                                                                                                                                               |

|                                                                                             | <pre>TID = get_new_tid(); }; tcu_halt_suspend(); }</pre>                                                                                                      |

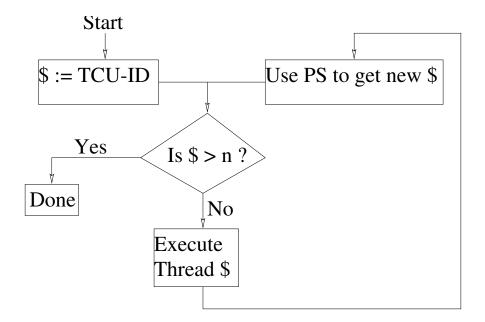

Figure 2.3: XMT code shape

The prototype XMT compiler consists of two phases:

- The front end ("Xpass") a source-to-source translator based on SUIF [60]. This phase converts the XMT code with its parallel constructs into regular C code with specialized assembly templates for run-time threading support.

- The back end (gcc) builds an executable file from the C code produced by Xpass. As we based our simulator implementation on the SimpleScalar ISA, we used the version of gcc from the SimpleScalar 2.0 package (gcc 2.6.3).

The general scheme used by Xpass is based on transforming parallel codes into parallel procedures. The compiler transforms the parallel region (the code in the spawn-join block) into the body of the procedure. When the procedure is called, the processing units are awakened, and each starts to execute the procedure body, which emulates the threads on each TCU. Figure 2.3 presents a high level example of the transformations performed by our compiler.

Producing this structure involves two tasks:

- Outlining. Detect all parallel regions (spawn-join blocks) and create a function definition for each (a "spawn-function"). Replace the spawn-join block with a call to the spawn-function.

- 2. Spawn-function transformation. Add TCU initialization code and thread emulation constructs to the spawn-function. These constructs include wrapping the body of the spawn-join block with a loop to emulate the threads, and inserting assembly templates.

## Chapter 3

# A Discussion of Memory from an XMT Perspective

Computer designers are recognizing that memory system performance is increasingly becoming critical to efficient execution [61]. At first glance, memory issues might appear to be the Achilles heel of the XMT framework. Parallel algorithms commonly require more memory operations than their serial counterparts. Preliminary studies have found XMT programs to be no exception [4].

However, the XMT model of computation provides an opportunity to break through the memory-bound limitations of serial computation and make more efficient use of memory. We will consider how to revisit memory subsystem design for this very different computational model, within the constraints of future chip technology.

Before proposing any specific solutions, we will first lay the groundwork by explicating the unique challenges and opportunities facing the XMT memory system designer. In this chapter, we will describe the primary design goal that will guide design, we will review existing technology as it might apply to an XMT system, we will define the constraints placed on the designer by the XMT consistency model, we will highlight the different assumptions relevant to the task of instruction fetching, and finally we will discuss the requirements of hardware prefix-sum operation support.

## 3.1 Statement of the Design Goal

It is important to define exactly what we wish to achieve with a memory design. A general-purpose computer system must be capable of handling efficiently a wide variety of cases, including different: patterns of memory access, granularity of data structures, and structures of parallelism.

To support the range of programs that may fall under the PRAM-like programming methodology of XMT, we must be particularly ambitious. Difficult programs may exhibit:

- Data access from many execution contexts. In the near future, we expect to support up to 1024 simultaneous thread contexts on a single-chip XMT machine.

- Very fine-grained threads. XMT's PRAM-style algorithmics often encourage minimal length threads. Additionally, these small threads may operate on just a single piece of data. Together, this implies that in many cases there may be little to gain from locality of reference (either spatial or temporal) within a single thread.

- Irregular, unpredictable access patterns. XMT attempts to broadly support all types of applications, including those with irregular modes of access, such as those operating on pointer based data structures. Furthermore, XMT hardware is designed to operate in a rather asynchronous fashion,

rather than in a scheduled, lock-step fashion. As a result, we cannot rely on orderly or predictable access patterns of access from different threads.

In this paper, the following primary principle is followed: design a system capable of handling the most difficult common case, as described by the points above. Later, we will offer suggestions to improve performance further when more forgiving types of programs or workloads offer opportunities for optimization, or for handling less common cases, such as codes providing less concurrent parallelism than a machine is designed for.

## 3.2 Overview of Existing Technologies

To understand the necessity for an entirely new design effort, it is important to recognize that existing memory designs are inappropriate for an XMT system.

Nearly all popular microprocessors are designed to execute serial programs. In serial computing, parallelism is limited to that which can be extracted from a single thread of execution. The key to efficient computation is to complete a memory request as soon as possible after it is issued. Not surprisingly, memory architecture design for serial machines has tended to emphasize reduction of latency as the primary design goal. Two important characteristics evident in the access patters of many serial programs are spatial locality and temporal locality. On-chip caches have been the primary means of leveraging these two properties to reduce latency of access.

With the fine-grained parallelism for which XMT is designed, a single thread may not exhibit the properties of spatial and temporal locality of reference to the same degree. However, the simultaneous existence of many threads can mean that latency of memory access within individual threads does not have to throttle performance. If many simultaneous memory accesses can be supported, than progress can be made while some threads are waiting for memory results. While successful at reducing average access latency for many serial programs, traditional memory hierarchies do not provide the necessary bandwidth capacity to support an XMT system, nor do they support the level of overlap necessary to effectively hide latencies.

Memory subsystems developed for massively parallel machines also are a poor fit for an XMT environment. Multi-chip implementations impose the constraints of very high latency and limited bandwidth between nodes, compared to a singlechip implementation. Such systems have proven effective only for very coarsegrained sharing. Vector architectures, (eg. [44]), demand lock-step timing and highly regular data access. We must look elsewhere for broader application support.

More recently, chip multiprocessors (CMPs) have begun to appear [22]. These systems have so far been essentially single chip implementations of traditional symmetric multiprocessors (SMP). Such systems use CPU-local caches, perhaps backed by a shared cache. The designs have been tuned to running multiple independent programs (no-sharing), or to very coarse-grained threading. Like those in SMP systems, the local caches use directory or update-based coherence schemes, and are connected by a bus or low-order crossbar. These traditional interconnects and coherence schemes would not scale to the number of processor resources targeted for an XMT system, nor would they be appropriate for the fine-grained sharing common in PRAM-style algorithms.

Current research designs will not provide satisfactory solutions from an XMT

perspective. MIT's RAW project also aims to harness on-chip parallelism, but takes a very different philosophical approach to computer system design. Processors are paired with small, low-latency local memories into a unit called a tile. Tiles are placed in an array fashion. The connection network is a grid topology, where each tile can talk with its four neighbors. DRAMs can be connected at the edges of the array of tiles. The RAW architecture exposes to software the details of data placement, data movement, and switch scheduling. On RAW, the programmer (or a sophisticated compiler) orchestrates movement of data from DRAM to local RAM, and from tile to tile. The simple programmer model of a uniform, global memory space does not map well to this architecture.

Another approach is to target the memory system for streaming applications. The Imagine project takes this approach, optimizing for compiler-scheduled streaming media applications. Such an architecture does not apply well to nonregular applications, especially where parallelism is not plentiful.

## **3.3** XMT Consistency Model

It is useful to carefully consider the shared memory consistency requirements of the XMT programming model. By making explicit what can be expected by the programmer, such considerations provide important constraints on memory system design, and also guide the compiler in performance-critical tasks like register allocation. In this section we present a practical discussion of memory consistency as it affects XMT system design.

#### 3.3.1 Thread-Local View

XMT programming uses serial semantics as a starting point. When in serial mode, XMT follows serial ordered memory requests. Similarly, within a thread, serial consistency should be respected. This means that an individual thread should see its updates in the order they are issued.

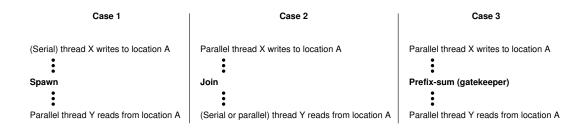

#### 3.3.2 Standard (Non-Fork) Spawn Regions

One of the most important aspects of the XMT programming model is the Independence-of-Order-Semantics (IOS). Recall that a spawn-join block declares a number of virtual threads. By convention, IOS implies that these virtual threads may execute in any order, in serial or in parallel. Because of the lack of order constraints, the implication is that memory consistency between different threads need not be maintained. The spawn-join construct demands only that memory be consistent at the start of a spawn operation (ie. that all spawn-region threads have access to updates performed by the serial-mode thread), and that memory again be consistent at the conclusion of a join operation (ie. the resumed serialmode thread has access to all updates performed by the spawn-region threads).

Note that this does not imply that all virtual threads must start with memory in the pristine state that existed when the spawn began. Updates from arbitrary other threads may have changed the state of memory before any particular thread begins executing.

Note also that updates from a particular thread to *different* locations are not necessarily visible to other threads in the order issued. An XMT programmer may not reason about ordering between threads without utilizing a prefix-sum operation. When spawn and join are the only mechanisms used for synchronization, memory consistency can either be maintained or be ignored for the duration of the spawn region. This property can give significant flexibility to a hardware designer. While an XMT program may specify very short virtual threads, in hardware a single TCU may emulate many virtual threads one after another. This means that, even for a very fine-grained spawn, the region of relaxed consistency may be quite significant.

The picture becomes more complex when the prefix-sum operation is considered. Recall that the XMT programming model draws much of its power from the use of prefix-sum operations within a spawn-region to provide no-busy-wait synchronization and dynamic ordering. While no static ordering is implied, interaction by way of prefix-sum allows for threads to determine an ordering of certain operations at run-time. This ordering may have implications for memory consistency assumptions.

Berkovich [4] terms a prefix-sum operation that forces inter-thread memory operations to be ordered a *gatekeeper prefix-sum*. Consider the following code fragment in which 2 threads compute the sum of a 4 element array A. The sum should be placed in the first element of A.

```

gatekeeper = 0;

spawn(2, 0); /* spawn two threads, starting with ID 0 */

{

int count;

A[TID*2] = A[TID*2] + A[TID*2 + 1]; /* sum two elements */

count = ps(&gatekeeper, 1);

if (count == 1) { /* 2nd of two to hit the gatekeeper ? */

A[0] = A[0] + A[2]; /* compute total = sum 2 partials */

}

}

join();

```

Each thread computes the sum of two unique elements of A, and overwrites an element with this value. After writing its first sum, each thread performs a prefixsum with increment 1 to the gate-keeper variable. The first to arrive gets value 0 and is done. The second to arrive gets value 1. This second thread now knows that the first thread has already performed the prefix-sum, and hence must have already written the partial sum to the array. Therefore, the second thread can read the value written by the other thread, and compute the total sum correctly. The gatekeeper prefix-sum operation provides the synchronization which allows the thread to assume memory consistency at that point.

Note that usage of prefix-sum in a spawn block does not necessarily imply that such an ordering of memory operations must be enforced. Take the common example of array compaction. Here, we copy the non-zero elements of array A to array B.

```

b_size = 0;

spawn(a_size, 0);

{

int index;

if (A[TID] != 0) {

index = ps(&b_size, 1);

B[index] = A[TID];

}

}

join();

```

The prefix-sum is used to provide each thread that wishes to write to array B with a unique index. Despite this ordering (implied by the assignment of indexes), there is no implied dependencies between the memory operations of different threads.

If a gatekeeper prefix-sum is one around which we must enforce memory

consistency, it is useful to be able to determine what is or isn't a gatekeeper. Berkovich suggests the following compile-time method for identifying gatekeeper prefix-sums. A prefix-sum is treated as a gatekeeper prefix-sum if the thread has a control dependency on the result of the prefix-sum. Note that the first example above (the toy summation) fits this rule, while the second example (array compaction) does not. The intuition is that if the threads don't modify their behavior as a result of the run-time ordering, then they aren't subject to anything but the static assumptions.

While this rule was never intended as a sufficient condition for identifying the gatekeeper property, it is important to recognize that it is not a necessary condition either. Consider the following reimplementation of the first example, where the control dependence has been transformed into a data dependence. After the first ps operation, local variable *count* contains either the value 0 or the value 1. After the arithmetic inversion on the next line, it possesses the value 0 or -1. Since (for a two's-complement system) -1 is represented in binary as all 1's, we can use count as a bit-wise and-mask to conditionally zero the partial sum value. The second (non-conditional) ps is therefore a noop for the zero-value case. This second ps does not return a result, and only serves to allow both threads to perform an addition without interfering with each other. gatekeeper = 0;/\* spawn two threads, starting with ID 0 \*/ spawn(2, 0);{ int count, masked; A[TID\*2] = A[TID\*2] + A[TID\*2 + 1];/\* sum two elements \*/ count = ps(&gatekeeper, 1); count = -count;/\* -1 is all 1's in two's complement \*/ masked = A[2] & count; /\* mask value to zero for 1st thread \*/ ps(&A[0], masked); /\* noop for 1st thread, sum for 2nd \*/ } join();

While this example is entirely contrived, the programmer should be able to expect it to work correctly.

Gatekeeper prefix-sums appear to be most useful in a class of algorithms which we will describe as asynchronous. Examples of this class of algorithm are described in [57]. A reduced-synchrony algorithm often has a more synchronous alternative. The balanced tree paradigm of [57], can be implemented with a single spawn-join region that uses gatekeeper prefix-sum operations to synchronize without busy-waiting. Alternately, a spawn-join region can be executed for each level of the tree, with no memory ordering within each spawn, only between spawns. We term this style of algorithm *level synchronous*, since the spawnjoins serve as a synchronization barrier between each level of the tree. While the level-synchronous algorithm may be easier to support from a memory designer's perspective, the asynchronous class of algorithms are useful and must be supported efficiently as well.

From the hardware designer's perspective, we will leave the identification of gatekeeper operations as a task for compiler to determine. This means the hardware should provide support for both gatekeeper and non-gatekeeper variants of the prefix-sum instructions. From the compiler's perspective, it is always safe to treat user-specified prefix-sums as gatekeepers. It may be useful to provide a programmer-visible non-gatekeeper option until compiler technology exists to provide useful discrimination.

We make the following observation, which has strong implications in practice. In a standard spawn-region, the prefix-sum operation used by the threading runtime to generate new thread IDs is *not* a gatekeeper. This very common case is not programmer-visible, and does not require compiler techniques to identify.

## 3.3.3 Forking Spawn Regions

Within a region that may allow forking of threads (fspawn-join), additional considerations apply. When a thread performs an xfork() or the more useful xfork\_and\_init(), it implies an order between the fork operation and the start of the new thread that is instantiated. Therefore all updates performed by the forking thread up to the point of forking should be visible to the new thread.

The practical importance of this property is that xfork is used when new work is discovered or created. Beyond the memory consistency requirements implied by the xfork, we often must provide the new thread with some sort of pointer to the new work. The issues related to this are discussed in section 5.5.

## **3.4** Instruction Memory

The memory design requirements for supporting instruction fetch are entirely different then those considered for (data) load/store support. There are three key points that differentiate instruction memory in an XMT system.

1. Instruction memory access is read-only.

As is typically done in standard computer design, we can consider the text segment of a program to remain unchanged throughout the life of the program. This property has a non-trivial implication for a parallel machine, since all fetch units will always have a coherent view of the instruction memory space, and memory consistency is a non-issue.

2. A thread's instruction access patterns exhibit significant locality and predictability of reference. The properties of temporal and spatial locality present in serial code have enabled the effective use of instruction caches in microprocessors. These properties are no less evident within an XMT thread. In fact, the manner in which multiple virtual threads are emulated on a single TCU, reinforces these characteristics.

3. The SPMD programming model suggests parallel threads will usually be accessing a common range of instruction locations.

We note that supporting instruction fetch bandwidth for an XMT system is a substantially different problem than supporting data access, and should not be significantly more demanding overall than for serial computing.

# 3.5 Prefix-Sum Support

Support for the operation of the prefix-sum primitive is another task of the XMT system designer. As described in section 2.2, the XMT ISA supports two distinct kinds of prefix-sum operations. Recall that with the parallel prefix-sum-to-register operation, the increment value is limited to single bit, and the choice of base variable is limited to a small set of special registers. On the other hand, the prefix-sum-to-memory instruction allows an arbitrary value increment, and the base variable can be any location in memory.

The prefix-sum-to-register operation is integral to XMT's dynamic thread scheduling. It also is useful in other contexts such as a parallel implementation of the partition step of the quicksort algorithm [40]. In these contexts, it is important for a wide-parallel XMT system to perform many such operations in parallel. The calling restrictions of the prefix-sum-to-register operation are designed to allow a special gadget (see Appendix D) to provide this capability. Implementation details will be discussed in section 5.5.

Implementation of the prefix-sum-to-memory operation likely requires making tradeoffs in performance. To guide these design choices, we make some observations about how this primitive is applied. The key observation is that in many applications, psm may be used in parallel by many different threads, but the number of collisions (that is, simultaneous operations on the same base), is often very limited.

A prime example of this phenomenon is seen in algorithms that follow the balanced tree paradigm of [57]. Here, each gatekeeper is the base variable of exactly two prefix-sum operations. There may be very many prefix-sum operations executed by different threads in parallel, but no more than two will be relative to the same base.

Other examples tend to exhibit similar behavior. Often, in problems involving directed acyclic graphs (DAG) [4][40], a counter exists at each node. Threads perform a prefix-sum operation to this counter to indicate a visit from a particular incoming edge. In this way, a thread can determine if it is the last to visit a particular node. As threads traverse the DAG simultaneously, many threads may perform prefix-sums in parallel. However if nodes have a limited in-degree, the number of collisions at any particular base will be limited.

As yet another example, consider the following hypothetical binning (bin-sort like) operation. A large array of data elements exist. Each data element will be assigned to one of many possible bins based on its value. A counter exists for each bin. A thread is spawned for each array element, and each thread increments (by means of a prefix-sum) the counter of the bin to which its element belongs. If the input array values are sufficiently distributed, we expect no particular counter to have to support many simultaneous increments.

Certainly, an array could be encountered that exhibits bad behavior from this perspective. An array of elements that all belong to the same bin is an example. If we did not know ahead of time that this would be the structure, we could not know to use a single counter with our parallel prefix-sum-to-register primitive. With the prefix-sum-to-memory primitive, the expected collisions would occur.

Similarly, a DAG traversal algorithm could be applied to an edge-heavy graph with few nodes and very large in-degrees. With such a pathological input, we again may encounter large numbers of collisions.

To support these kind of situations, the ideal prefix-sum-to-memory implementation would support many simultaneous operations to common or different bases. However, it would appear that support only for different bases in parallel would cover the majority of common cases.

## Chapter 4

# New Memory Subsystem Architecture

This chapter introduces a new memory system design for an XMT system. We present a non-standard on-chip memory organization, and an interconnection network tuned for deep-submicron VLSI implementation. For clarity, this chapter focuses only on the data memory subsystem, and only describes the essential elements of the design. This scheme forms the backbone of an effective memory design. Chapter 5 will follow up with implementation details, optimizations, and other aspects of the design.

Certain mechanisms described in this chapter are covered under patent application [43].

# 4.1 Memory Structure

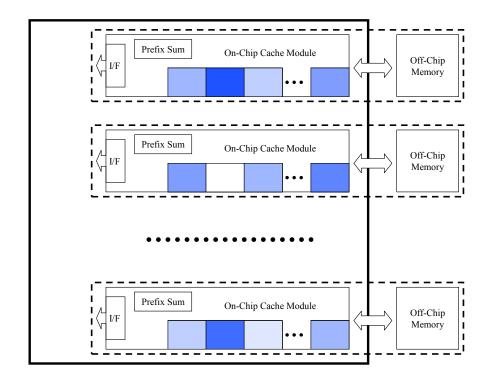

The copious transistor budgets enabled by future chip technology will allow for enough on-chip RAM to hold rather large working sets. Additionally, connectivity within a chip has the potential to provide as much communications bandwidth as needed. The PRAM-like model presented by XMT demands that the memory subsystem support the simultaneous access by many threads to arbitrary locations in a shared memory space. It is clear that a large, monolithic cache could never support the demands of such a system. Also, since memory speed drops as size and number of ports increases, it pays to use smaller independent modules.

The goal is to parallelize the memory. In a system with many independent memory modules, many requests to different modules can be serviced at the same time. We will have many processing elements generating memory requests, and many independent memory modules to service the requests. By instantiating enough small cache modules that can all be accessed simultaneously, one can allow for sufficient bandwidth to satisfy many threads at once.

However, to match the shared memory orientation of the programming model, the memory subsystem must present a coherent global memory space. For a system with a small degree of memory parallelism, many solutions could be effective. But maintaining coherence among potentially hundreds of modules appears to be too costly to implement effectively.

Any sort of snooping scheme would incur a huge bandwidth cost. It would require that all writes be broadcast in some manner to all cache modules that might house that address. The total write bandwidth then is throttled by the bandwidth of the broadcast mechanism. This occurs in the scheme from Appendix B, where writes are throttled by the capacity of the ring interconnect.

With a directory-based cache coherence scheme, the centralized directory would quickly become the limiting factor in data access. Also, with fine-grained data access supported by XMT, directory management of small data lines could be prohibitively expensive.

To sidestep the coherence issues, the memory address space may be partitioned among the memory modules, such that a given address can reside at only

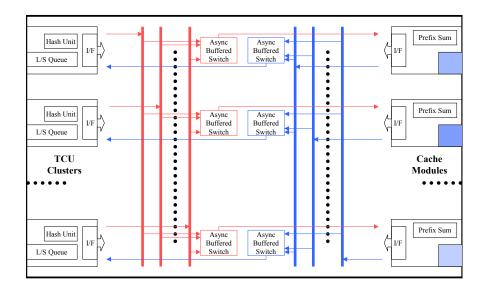

Figure 4.1: Parallel memory modules

one location (Figure 4.1). By precluding duplicate values from being located at different modules, we avoid the problem of multiple update or of maintaining a directory of value locations. By sacrificing mobility of address locations, we are forced to deal with two related issues.

• There is a mapping from memory addresses to specific memory modules. Each memory module has limited capacity to service requests. Therefore when different memory addresses are accessed simultaneously by different threads, we'd wish them to map to different memory modules. One solution might be to rely on software to map data structures to memory modules to avoid collisions. This solution is inadequate for the breadth of applications that might be encountered. Irregular, unpredictable applications can not rely on programmers or sophisticated compilers to distribute memory accesses.

Borrowing a concept from parallel computing, we support randomized hashing to distribute addresses among the memory modules [37]. By using a random or pseudo-random hash to map locations word-by-word, we can probabilistically bound the number of collisions, without relying on any property of data access. Hashing strategies will be discussed in Chapter 5.

A hashing scheme does not solve one class of collisions: when many threads simultaneously attempt to access the *same address*, contention will occur. This situation will be considered a special case, and approaches to handling it will be presented in Section 5.3.

The on-chip memory modules can be considered to be caches containing a subset of the data held in off-chip memory. One can make effective use of off-chip memory by extending the address partitioning to independent off-chip memory modules that serve the on-chip caches. By supporting many outstanding external requests, off-chip bandwidth can be fully utilized, even for non-streaming types of applications.

The modular memory design can be naturally extended to support multiple simultaneous prefix-sum-to-memory (psm) operations. psm operations can map to memory modules in the same way as a read or write. By incorporating a single adder into each memory module, the atomic addition can be implemented serially within each module. Such an implementation supports parallel psm to addresses at different modules, but multiple psm operations to the same address must be queued.

Recall that support for many simultaneous accesses to a single global register

(pinc) is implemented using a separate interconnect which incorporates parallel prefix-sum hardware. Details will be provided in section 5.5.

## 4.2 Interconnect Design

An XMT system inherently implies many execution units, and we propose to implement many independent memory modules. A substantial challenge for an XMT design is to provide connectivity between the many execution units and the many memory modules on-chip.

Due to the flat memory model supported, memory requests from a given thread can travel to any memory location on the chip. A latency cost for such memory accesses cannot be avoided. While the capacity for sending signals increases with each technology shrink, the latency for propagating signals down a long wire is increasing. Fortunately, the parallelism and independence of order characteristic of XMT threading allows for such latency to be tolerated. While many threads stall waiting for memory requests to propagate through the network, forward progress can be made by other threads, provided enough thread contexts are instantiated simultaneously. Our solution will therefore focus on providing maximum useful bandwidth to the memory subsystem.

#### 4.2.1 Crossbar Interconnect

#### Investigating the Synchronous Crossbar

The interconnection network must allow as many simultaneous connections between processing elements and memory elements as possible. It is reasonable to restrict the capacity of the endpoints to a single connection at a time. However, at any given time, a processing element may need to connect to any single memory element, and a memory element may need to connect to any single processing element.

The classic solution for such an interconnection network is the crossbar switch. While it has the potential to provide the requisite connectivity, the crossbar has yet to be proven as a large-scale on-chip interconnect. In particular, the area cost of a crossbar is known to be  $O(n^2)$ , where n is the number of ports. However, our investigations indicate that a full crossbar topology will be a feasible structure for the on-chip interconnect for XMT systems based on near-future VLSI technology. Please refer to Appendix C for a report of this work.

To use such a topology in a system, there must be some method for scheduling the switch settings so ports can communicate without stomping on each other. Such a method should be scalable, decentralized, and efficient. Appendix C also describes solutions for scheduling a synchronous crossbar switch.

#### Issues

The above-mentioned work demonstrates the feasibility (from an area cost standpoint) of a crossbar structure. However, several factors make the synchronous crossbar a less than ideal solution. The first issue is that orchestrating unpredictable access among the various (processing elements and memory modules) ports adds unnecessary overhead. While Appendix C introduces several methods to handle this scheduling problem, all solutions require some sort of global coordination to set a particular configuration. Ideally, messages would freely access their destinations, with contention dealt with locally only where it occurs.

Other limitations of the synchronous crossbar approach are dictated by deep-

submicron VLSI realities. It is well documented that wire delay will become an increasingly important factor in future chip design. As process dimensions shrink, transistor delay goes down while wire resistance goes up. To reach high operating frequencies requires a design to use short, low-capacitance wires. A crossbar design with high connectivity is a large structure. Modulating signals on a long wire across the structure at speeds near that at which the active devices are capable becomes infeasible.

Furthermore, clock distribution across a large chip also becomes more difficult. At high frequency, stable clock distribution is an increasingly difficult design problem. The ITRS [47] projects a growing disparity between clock speeds that can be achieved locally and those that can be achieved across a chip. Additionally, high performance clocking trees with large drivers consume a large amount of power. In contemporary Alpha processor designs, the clock tree consumes 50% of the processor power [38].

## 4.2.2 Novel Solution

Certain characteristics of XMT provide an opportunity for a novel technological solution. The XMT high-level programming language is a multi-threaded model that attempts to mimic no-busy-wait finite state machines; that is where no (software) thread ever needs to suspend its progress, while waiting for another thread. Execution then consists of a plurality of (software) threads that follow Independence of Order Semantics (IOS); that is, different speeds of execution among threads including some different orders of executions of reads and writes to a memory location can be tolerated. Thus, a trust of XMT is that such threads need to synchronize relatively infrequently, which provides an opportunity for

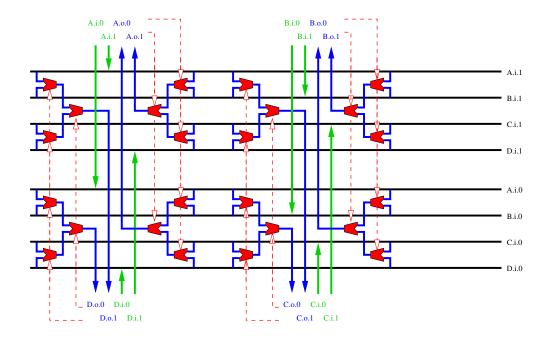

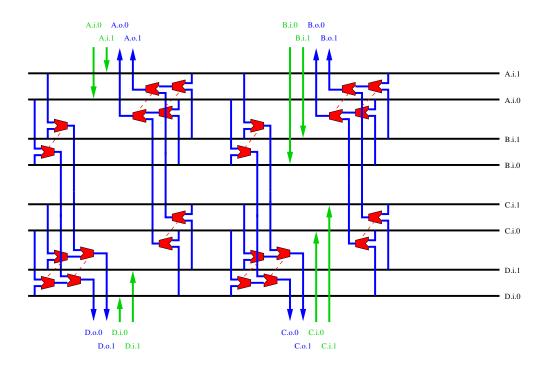

Figure 4.2: Memory system interconnect

reduced-synchrony hardware implementation.

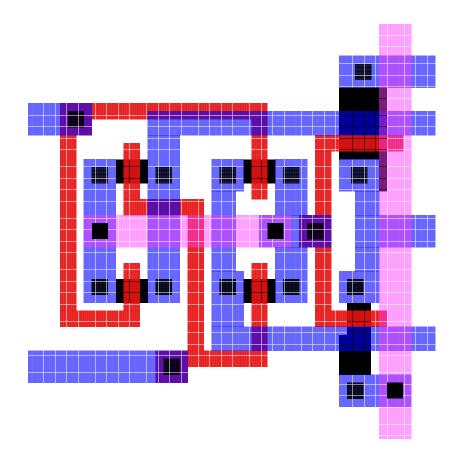

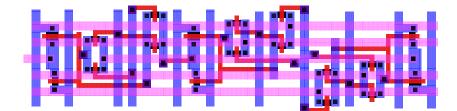

We propose a decentralized routing scheme (Figure 4.2). The basic topology of a mux-tree crossbar can be maintained, with routing at each destination performed locally by a "tree of gatekeepers". This tree of gatekeepers is formed from locally synchronous switch points that select from two inputs depending on which arrives first. The gatekeepers structure mimics the multiplexor tree of a synchronous crossbar, but allows requests to proceed locally as they are able, rather than using a global schedule.

#### **Datapath Layout**

As an illustration of the change in datapath, we provide two figures. Both diagrams illustrate the datapath layout of an interconnect between four ports A, B, C, D. Each port has a 2-bit input port (green) going into the interconnect and a 2-bit output port (blue) coming out of the interconnect. The red boxes are

Figure 4.3: Traditional layout

multiplexors (muxs) where a decision is made to pass one input or the other.

Figure 4.3 represents the more conventional design. The layout can be described as a series of bit slices stacked on top of one another. In Figure 4.4, the 2 bits from a given port are "bundled" together and follow the same global route throughout. The dashed lines connect pairs of muxs that are coupled as a single logical 2-bit mux (mux-pair).

By abandoning scheduled switching in favor of a more dynamic scheme, we introduce a new requirement. A data bundle written into the interconnect potentially can go to any of the destinations (4 possibilities in the example). If the data is initially labeled with the intended destination, a leaf from each mux-tree can interpret the label to determine if it should enter that particular mux-tree. The label can be discarded at this point.

Similarly, when data is received at an output port, the source of the data

Figure 4.4: New layout

must be determined. Each mux-pair can encode the local decision made and pass this data on toward the root of the tree. The receiver can determine the sender from this information.

#### **Reduced Synchrony Switching**

This new configuration enables a scheme where switching decisions are made at the switch points. Messages should be allowed to progress through a switchpoint as soon as they arrive. To achieve this goal we turn to asynchronous control techniques. Each node of the mux-tree buffers a single data bundle. At each mux-pair, two data bundles compete to progress towards the root of the tree. An arbiter primitive [51] guards access to the buffer associated with the mux. The first of the two data bundles to arrive will win and be latched into the data buffer. If a second bundle arrives before the first clears the mux, then the second will be granted next access. This switching automaton could be designed to incorporate alternation between inputs when both are continually attempting access. When applied globally, an alternation policy can prevent starvation.

#### Pipelining

For this design to be effective, it is important that many simultaneous requests be supported by pipelining throughout the interconnection network. Asynchronous design can also be applied to pipelining the wires in the form of micropipelining [51]. Long wires can be highly pipelined to form independently latched, self-timed short wire stages. Each bundle of wires (2-bit bundles in the example) requires 2 control wires to handshake between stages. Data can proceed from one stage to the next when the next stage has cleared.

## 4.2.3 Summary

Such a design can potentially overcome the limitations of the synchronous crossbar described earlier. The locally determined switching avoids global communication and coordination, while enabling efficient utilization of connectivity. The high degree of pipelining enables high bandwidth by allowing many data bundles in flight at once. Meanwhile, long wires are avoided to speed stage-to-stage transfers and to reduce driver size.

Furthermore, an asynchronous global interconnect allows for all processing elements to be independently clocked. This eliminates the need for a global clock tree and allows for processing clusters to be clocked as fast as can be achieved locally, without regard to global considerations. In this chapter, we have presented a novel and potentially successful solution to the design problem. However, there is plenty of room for implementing some of these ideas in different ways. The idea of localized switching decisions can also be applied to a less asynchronous design. Instead of having an entirely unclocked interconnection network, it would be possible to partition the network into independently clocked domains. For example, each binary mux tree could be operated in a self-synchronous manner. Or, each mux tree could be reworked to operate locally in a reduced synchrony manner. The pipelines that feed the trees could be fully asynchronous, or divided into self-synchronous subdomains. A reduced synchrony design might have performance advantages over a fully asynchronous design, as the control and decision making logic is likely to be simplified. Further work is needed to determine which alternatives will perform the best.

## Chapter 5

# System Implementation

In this chapter we will discuss the proposed memory subsystem strategy in the context of an entire practical system. We will first discuss the structure and operation of the processing clusters, and then that of the memory modules. We will then propose potential techniques for reducing latency of access in certain cases. Finally, we will fill in the remaining holes by describing the implementation of instruction fetch memory and of parallel register operation.

This chapter will try to describe the practical design space, while Chapter 6 will focus on suggesting specific choices for a design starting point.

# 5.1 Processing Cluster Architecture

In previous expositions of XMT architecture, the concept of a cluster of TCUs was based on sharing of execution hardware. In this scheme, each cluster of TCUs was similar to an SMT processor, where multiple concurrent threads make efficient use of shared functional units.

When considering a large-scale XMT system as a whole, we realize that efficient use of execution resources may be a less important goal than efficient use of memory resources. While per-unit functional unit cost remains constant when scaling to higher hardware parallelism, the per-unit cost of global communication rapidly goes up.

From this perspective, a cluster should be based around a single interconnect port. The execution resources in a cluster can be considered to be generating memory requests so as to keep the memory network busy. When global communication can cost several cycles, we need to queue memory requests from many threads to keep the pipelined network busy.

By choosing the degree of clustering sufficiently high, the memory subsystem can be used efficiently during periods of plentiful parallelism. However, if the degree of clustering is so high that the TCUs within a cluster significantly impede each other, than load balancing issues are possible at the tail of a spawn, should one cluster be overtaxed and another idle. Clearly, a balance should be struck.

Of course, SMT style functional unit sharing can be implemented within such a memory-oriented cluster. The choice of SMT style clustering degree can be independent of the choice of memory-oriented clustering degree.