### DEPARTAMENTO DE ENGENHARIA ELETROTÉCNICA E DE COMPUTADORES

# ANDRÉ ALEXANDRE PIRES DUARTE

Licenciado em Engenharia Eletrotécnica e de Computadores

Low-Power and Low-Noise Clock Generator for High-Speed ADCs

MESTRADO EM ENGENHARAIA ELETROTÉCNICA E DE COMPUTADORES

Universidade NOVA de Lisboa Março, 2022

### DEPARTAMENTO DE ENGENHARIA ELETROTÉCNICA E DE COMPUTADORES

# Low-Power and Low-Noise Clock Generator for High-Speed ADCs

#### ANDRÉ ALEXANDRE PIRES DUARTE

Licenciado em Engenharia Eletrotécnica e de Computadores

Orientador: Luís Bica Oliveira,

Professor Associado, Universidade NOVA de Lisboa

Júri:

Presidente: Filipe de Carvalho Moutinho,

Professor(a) Catedrático(a), FCT-NOVA

Arguentes: João Carlos de Palma Goes,

Professor(a) Catedrático(a), FCT-NOVA

Orientador: Luís Bica Oliveira,

Professor Associado, FCT-NOVA

MESTRADO EM ENGENHARIA ELETROTÉCNICA E DE COMPUTADORES

Universidade NOVA de Lisboa

#### Low-Power and Low-Noise Clock Generator for High-Speed ADCs

Copyright © André Alexandre Pires Duarte, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa.

A Faculdade de Ciências e Tecnologia e a Universidade Nova de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objetivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

# Acknowledgments

I will start by thanking Prof. Luis Olivera for all the motivation, support and reassurance he provided during the whole thesis. Even with the pandemic and in the most difficult times I went through he was always there and was always available to help.

I also want to thank my parents for all the motivation they gave me throughout the thesis and the entire course, because there were moments when I thought about giving up and they were the ones who gave me the necessary strength to finish it.

Finally, I want to thank a special friend who in my most difficult moments never abandoned me and who has always helped me throughout my life.

### Resumo

O rápido desenvolvimento das tecnologias de comunicação de alto desempenho, reflete uma tendência clara na exigência dos requisitos impostos aos conversores analógico-digital (ADCs). Deste modo, verifica-se que estes requisitos implicam elevadas frequências não só sinal de entrada, como também frequências elevadas de amostragem o que se traduz numa maior sensibilidade do circuito ao ruído térmico e consequente aumento ruído de fase. Esta problemática, surge como propósito principal deste documento, no qual se procurará, como objetivo principal, o desenvolvimento de uma arquitetura que permita gerar múltiplos sinais de relógio a altas frequências de entrada e períodos de amostragem, com um baixo jitter e baixa energia consumida de forma a tornar mais eficiente e rápido o funcionamento de ADCs. Ruido térmico.

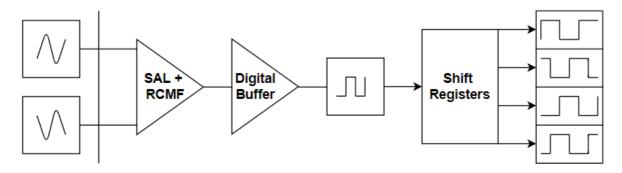

Esta dissertação propõe uma arquitetura composta por um amplificador de sinal de relógio que converte o duplo sinal de entrada num único sinal de saída, um amplificador digital que transforma uma onda sinusoidal numa onda quadrada e por fim um gerador de fase múltipla de sinais de relógio (MPCG), constituído por registos de deslocamento. Ambas as arquiteturas são implementadas em tecnologia CMOS de 130 nm.

A arquitetura é alimentada com um sinal LVDS de 200 mV de amplitude e com uma frequência de 1 GHz, de forma a obter à saída 8 sinais de relógio de onda quadrada com uma amplitude de 1,2 V e com 125 MHz de frequência. Os sinais obtidos à saída posteriormente alimentarão uma arquitetura de 8 canais com multiplexagem temporal.

A área total do circuito implementado é cerca de  $8054,3~\mu\text{m}^2$ , para uma potência dissipada de 5,3~mW e para um valor de *jitte*r de 1,13~ps.

Esta nova arquitetura será direcionada para todo o tipo de entidades que trabalham com dispositivos que são constituídos por ADCs de alta velocidade de desempenho, de forma a poder melhorar o funcionamento desses mesmos dispositivos, tornando o processamento de sinal continuo para sinal discreto o mais eficiente possível.

**Palavras-chave:** amplificador de sinal de relógio, gerador de fase múltipla de sinais de relógio (MPCG), baixo jitter, baixa energia consumida, alta frequência, ADCs.

## **Abstract**

The rapid development of high-performance communication technologies reflects a clear trend in demanding requirements imposed on analog-to-digital converters (ADCs). Thus, it appears that these requirements imply higher frequencies not only for the input signal but also higher sampling frequencies, which translates into a higher sensitivity of the circuit to thermal noise and consequent increase in phase-noise. This arises as to the main purpose of this document, which will seek, as its main objective, the development of an architecture that allows the generation of multiple clock signals at high input frequencies with low jitter and low power dissipation to make ADCs more efficient and faster.

This dissertation proposes an architecture implemented by a Clock Buffer that converts a differential input signal into a single-ended output signal, a Digital Buffer that transforms a sine wave into a square wave, and finally a Multi Clock Phase Generator (MPCG), consisting of Shift Registers. Both architectures are implemented in 130 nm CMOS technology.

The architecture is powered by a LVDS signal with an amplitude of 200 mV and a frequency of 1 GHz, in order to output 8 square wave clock signals with an amplitude of 1.2 V and with a frequency of 125 MHz. The signals obtained at the output later will feed an architecture of 8 Time-Interleaved ADCs.

The total area of the implemented circuit is about 8054.3  $\mu m^2$ , for a dissipated power of 5.3 mW and a jitter value of 1.13 ps.

This new architecture will be aimed at all types of entities that work with devices that are made up of high-speed performance ADCs, to improve the operation of these same devices, making the processing from a continuous signal to a discrete signal as efficiently as possible.

**Keywords:** Clock Buffer, Multi-Phase Clock Generator, low jitter, low power, high frequency, ADCs.

# **Contents**

| Acknowledgments                                    | V     |

|----------------------------------------------------|-------|

| Resumo                                             | VII   |

| Abstract                                           | VIII  |

| Contents                                           | IX    |

| List of Figures                                    | XIII  |

| List of Tables                                     | XVI   |

| Acronyms                                           | XVIII |

| 1. Introduction                                    | 1     |

| 1.1. Context and Motivation                        | 1     |

| 1.2. Problems and Objectives                       | 2     |

| 1.3. Document Organization                         | 3     |

| 2. Basic concepts of ADCs                          | 4     |

| 2.1. ADC Architectures                             | 4     |

| 2.1.1. Parallel (Flash) ADC                        | 5     |

| 2.1.2. Counter type ADC                            | 6     |

| 2.1.3. Successive-Approximation Register (SAR) ADC | 7     |

| 2.1.4. Dual-slope integration ADC                  | 8     |

| 2.1.5. Pipeline ADC                                | 9     |

| 2.2. Time-Interleaving ADCs                        | 10    |

| 2.3. Performance Metrics                           | 11    |

| 2.3.1. Aperture Jitter (jitter noise)              | 12    |

| 2.3.1.1 Cycle-to-Cycle litter                      | 12    |

| 2.3.1.2. Period jitter                                         | 13 |

|----------------------------------------------------------------|----|

| 2.3.1.3. Long-term Jitter                                      | 13 |

| 2.3.1.4. Phase jitter                                          | 13 |

| 3. State of Art                                                | 15 |

| 3.1. Clock Buffer                                              | 15 |

| 3.1.1. Clock Recovery Circuitry                                | 17 |

| 3.1.2. Existing topologies                                     | 18 |

| 3.2. Multi-Phase Clock Generator                               | 23 |

| 3.2.1. Different Topologies                                    | 23 |

| 3.2.1.1. Shift Registers                                       | 24 |

| 3.2.1.2. Delay Locked Loop (DLL)                               | 25 |

| 3.2.2. Output Jitter                                           | 25 |

| 3.2.2.1. SR Output Jitter                                      | 26 |

| 3.2.2.2. DLL Output Jitter                                     | 26 |

| 3.2.3. Jitter Comparison Between Topologies                    | 28 |

| 3.2.3.1. Comparing Jitter Transferred from the Reference Clock | 28 |

| 3.2.3.2. Comparing Jitter Generated Due to Thermal Noise       | 28 |

| 3.3. Discussion                                                | 28 |

| 3.3.1. Clock Buffer                                            | 29 |

| 3.3.2. Multi-Phase Clock Generator                             | 30 |

| 3.4. Proposed Circuit                                          | 31 |

| 4. Circuit Implementation                                      | 33 |

| 4.1. Clock Buffer                                              | 33 |

| 411 Clock Buffer Sizing                                        | 34 |

| 4.1.2.   | Scaling W and L                         | 36 |

|----------|-----------------------------------------|----|

| 4.1.3.   | DC Operating Point                      | 42 |

| 4.2.     | Multi-Phase Clock Generator             | 42 |

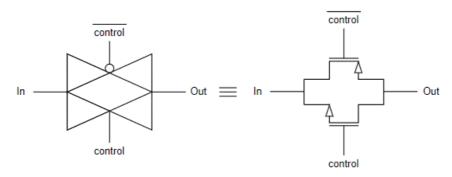

| 4.2.1.   | Transmission Gates                      | 43 |

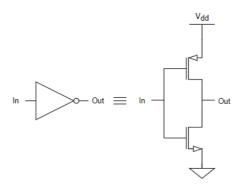

| 4.2.2.   | Inverter                                | 45 |

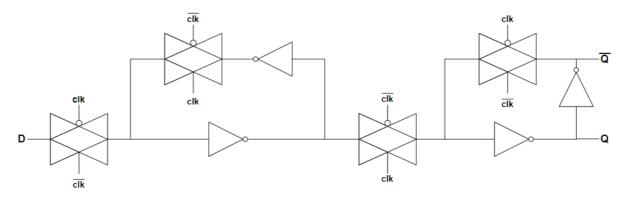

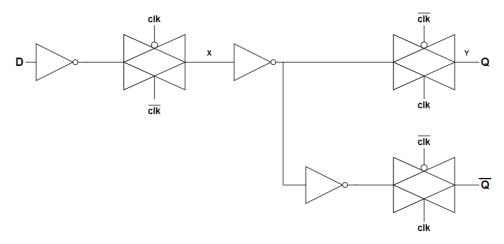

| 4.2.3.   | D-type Flip-Flops                       | 45 |

| 4.2.3    | 3.1. Types of Memory                    | 46 |

| 4.2.3    | 3.2. Different Topologies               | 47 |

| 4.2.3    | 3.3. Flip-Flop Sizing                   | 49 |

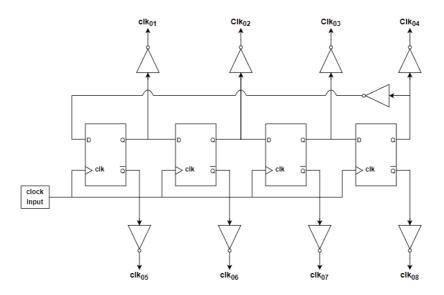

| 4.2.4.   | Shift Registers                         | 51 |

| 4.2.4    | 4.1. Ring-Counter                       | 52 |

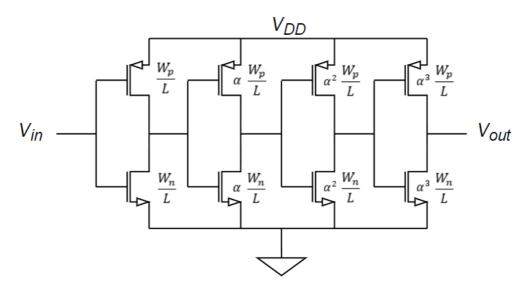

| 4.3. I   | Digital Buffer                          | 53 |

| 4.3.1.   | Digital Buffer Sizing                   | 54 |

| 4.4.     | Clock Circuit                           | 54 |

| 4.4.1.   | Rx                                      | 54 |

| 4.4.2.   | D-type Flip-flop                        | 56 |

| 4.4.3.   | Shift Register                          | 57 |

| 5. Elect | ric Simulations                         | 59 |

| 5.1. I   | Description of the Electric Simulations | 59 |

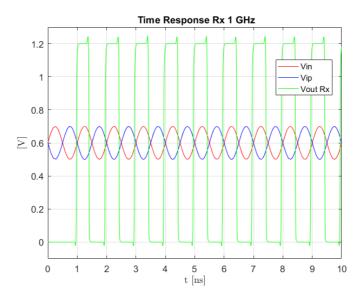

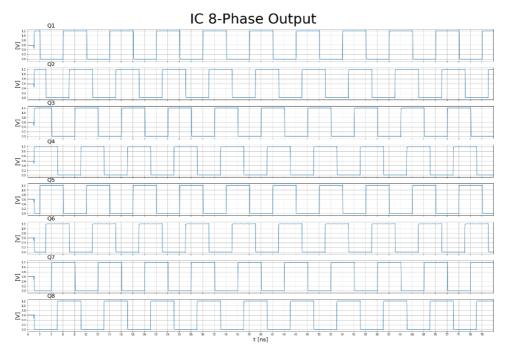

| 5.2.     | Γime Response Simulations               | 59 |

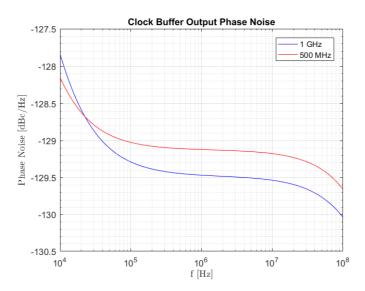

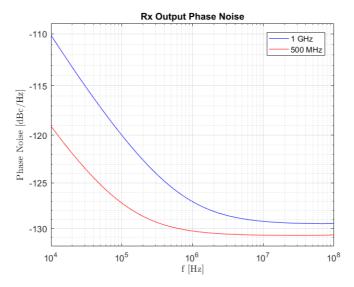

| 5.3. I   | Phase-Noise Analysis                    | 61 |

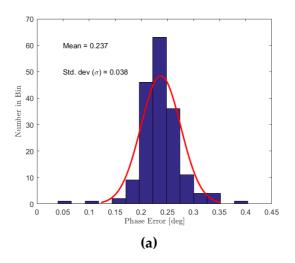

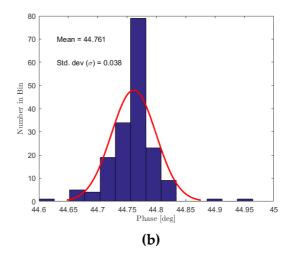

| 5.3.     | Monte Carlo Simulation                  | 66 |

| 5.4. I   | Discussion                              | 67 |

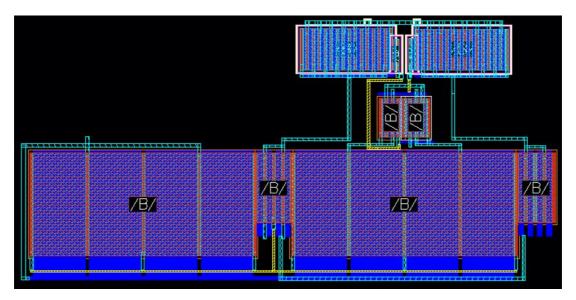

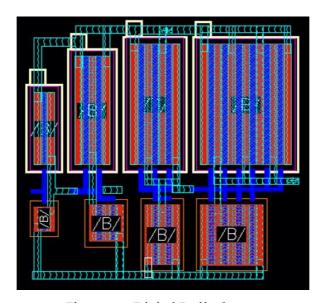

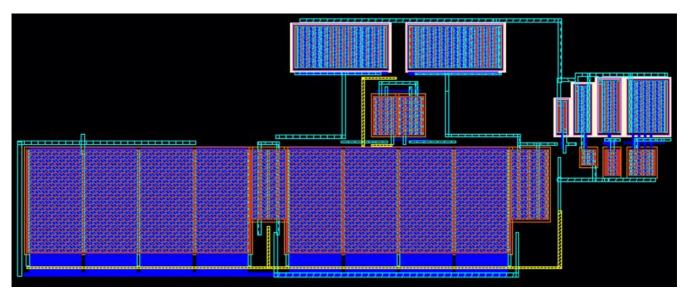

| 6. Layo  | ut                                      | 69 |

|    | 6.1.   | Rx Core                          | 70 |

|----|--------|----------------------------------|----|

|    | 6.2.   | Shift Register                   | 73 |

|    | 6.3.   | Analysis of the results          | 77 |

| 7. | Cor    | nclusions                        | 79 |

|    | 7.1.   | Future Work                      | 80 |

| 8. | Ref    | erences                          | 81 |

| A  | ppendi | x A: DC Operating Point          | 85 |

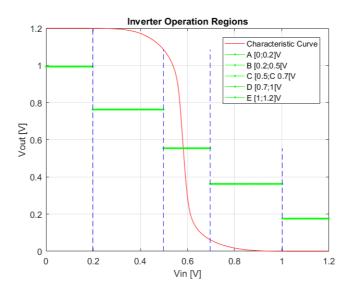

| A  | ppendi | x B: Inverter operating mode     | 86 |

| A  | ppendi | x C: litter calculation function | 88 |

# **List of Figures**

| Figure 2.1- N-bit flash ADC based in [4]5                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2- Counter type ADC based in [4].                                                                                               |

| Figure 2.3- A block diagram for a successive-approximation ADC based in [4]                                                              |

| Figure 2.4- A basic block diagram for a dual-slope integration ADC based in [4]                                                          |

| Figure 2.5- Pipeline ADC based in [4].                                                                                                   |

| Figure 2.6 Time-interleaved ADC with N channels based in [5]                                                                             |

| Figure 2.7- Phase Noise plot based in [11]14                                                                                             |

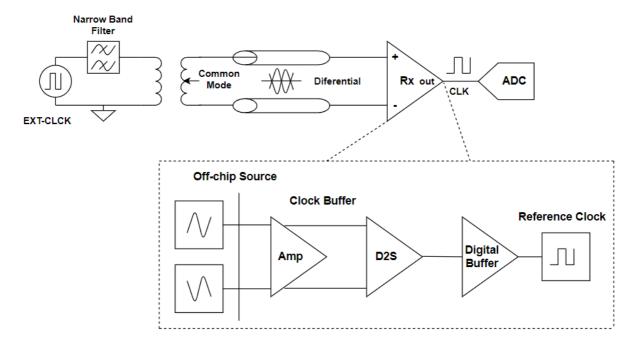

| Figure 3.1- Simplified block diagram of a possible scheme for a clock recovery circuit. a Current mode, b) Voltage mode c) Simple Buffer |

| Figure 3.2- Simplified block diagram of a possible scheme for ultra-low-jitter clock recovery circuit based in [15]                      |

| Figure 3.3- Schematics of the selected low-jitter clock recovery circuits. a) SRL, b) SALPF                                              |

| c) SRL+SALPF d) SAL+RCMF based in [15]21                                                                                                 |

| Figure 3.4- More schematics of the selected low-jitter clock recovery circuits. a) QILA, by HGRA, c) LNLGA based in [18]                 |

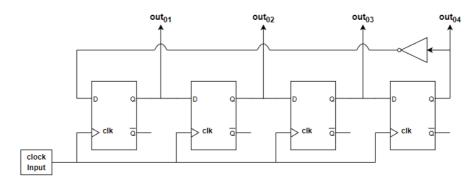

| Figure 3.5- SR MPCG architecture based in [19]24                                                                                         |

| Figure 3.6- DLL MPCG architecture based in [19]25                                                                                        |

| Figure 3.7- Final schematic of the proposed circuit                                                                                      |

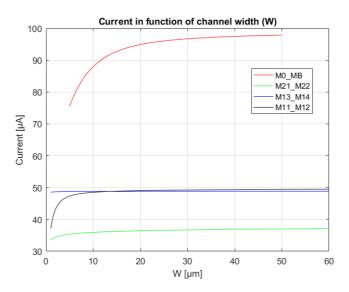

| Figure 4.1- Current behavior of the SAL+RCMF circuit transistors as a function of their channel width                                    |

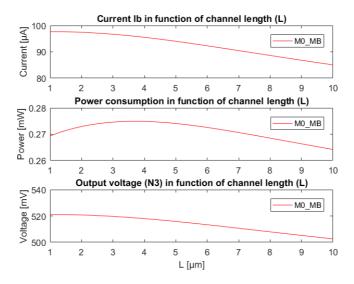

| Figure 4.2- Current/Power and Output voltage behavior of the SAL+RCMF circuit                                                            |

| transistors M0 and MB as a function of their channel length                                                                              |

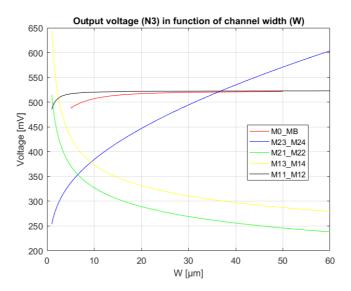

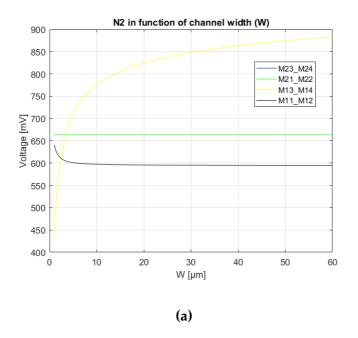

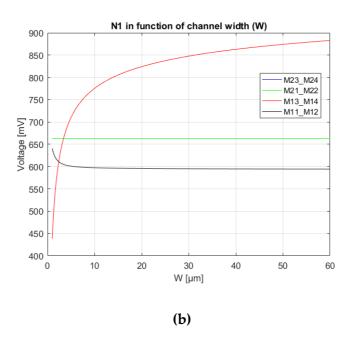

| Figure 4.3- Output voltage behavior of the SAL+RCMF circuit transistors as a function     |

|-------------------------------------------------------------------------------------------|

| of their channel width                                                                    |

| Figure 4.4- Node voltage behavior of the SAL+RCMF circuit transistors a function of       |

| their channel width a) N2L, b) N1                                                         |

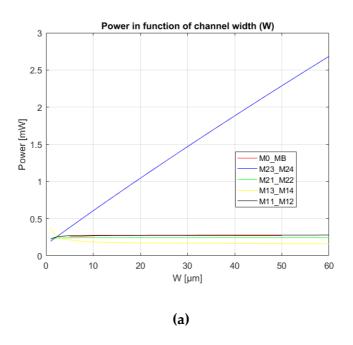

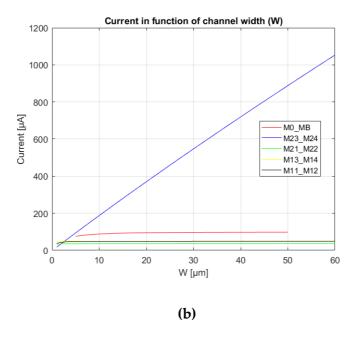

| Figure 4.5- a) Power behavior of the SAL+RCMF circuit transistors as a function of their  |

| channel width. b) Current behavior of the SAL+RCMF circuit transistors as a function of   |

| their channel width                                                                       |

| Figure 4.6- CMOS Transmission gate and symbol representation presented in [22] 43         |

| Figure 4.7- CMOS Inverter and symbol representation                                       |

| Figure 4.8- Single-threshold transmission gate flip-flop presented in [29]                |

| Figure 4.9- Dynamic transmission gate flip-flop presented in [26]                         |

| Figure 4.10- Johnson Ring Counter                                                         |

| Figure 4.11- Chain of inverters with exponentially increasing size based in [40] 53       |

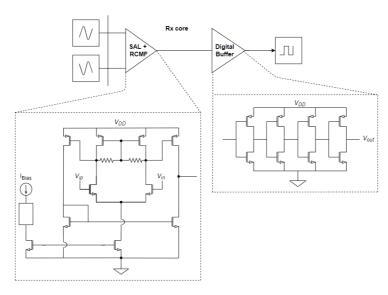

| Figure 4.12- Rx core circuit                                                              |

| Figure 4.13- SR final circuit                                                             |

| Figure 5.1- Simulation results of the Rx core,                                            |

| Figure 5.2- Simulation results of the 8-phase IC                                          |

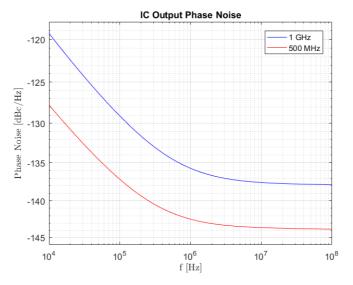

| Figure 5.3- Simulation results of the clock buffer output phase noise                     |

| Figure 5.4- Simulation results of the Rx core output phase noise                          |

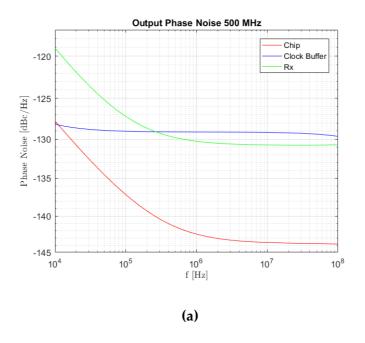

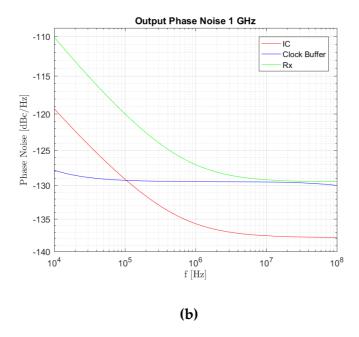

| Figure 5.5- Simulation results of the IC output phase noise                               |

| Figure 5.6- Simulation results of the CC and its elements output phase noise. a) 500 MHz, |

| b) 1 GHz64                                                                                |

| Figure 5.7- Histogram of the simulated a) Phase Difference b) Phase (200 Monte Carlo      |

| runs)                                                                                     |

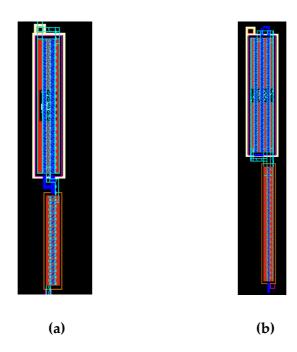

| Figure 6.1- Clock Buffer layout                                                           |

| Figure 6.2- Digital Buffer layout                                  | . 71 |

|--------------------------------------------------------------------|------|

| Figure 6.3- Rx core layout.                                        | . 72 |

| Figure 6.4- a) Inverter Layout, b) Transmission gate Layout        | . 73 |

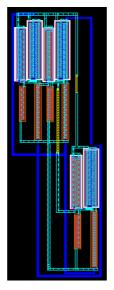

| Figure 6.5- DTG flip-flop Layout.                                  | . 74 |

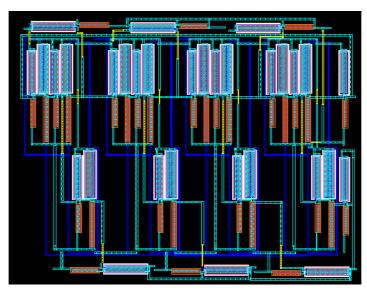

| Figure 6.6- SR Layout                                              | . 74 |

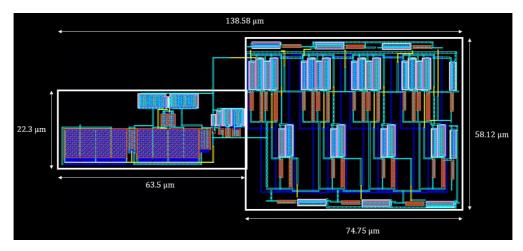

| Figure 6.7- Chip Layout                                            | . 75 |

| Figure B.1- Operations Regions of the CMOS Inverter based in [43]. | . 86 |

| Figure C.1- Imporfile function code                                | . 88 |

| Figure C.2- Code to calculate Jitter.                              | . 89 |

| Figure C.3- Jitter function code.                                  | . 89 |

# **List of Tables**

| Table 3.1- Advantages and disadvantages of the clock buffer architectures           |

|-------------------------------------------------------------------------------------|

| Table 4.1- Dimensions of the SAL+RCMF circuit transistors                           |

| Table 4.2- New dimensions of the SAL+RCMF circuit transistors                       |

| Table 4.3- DC Operating Point – New voltages of the SAL+RCMF circuit transistors 42 |

| Table 4.4- Truth Table of the Transmission Gate presented in [22]                   |

| Table 4.5- Dimensions of CMOS Inverter transistors                                  |

| Table 4.6- Dimensions of CMOS transmission gate transistors                         |

| Table 4.7- Dimensions of the Digital Buffer transistors                             |

| Table 4.8- Final dimensions of the SAL+RCMF circuit transistors                     |

| Table 4.9- Power and Delay output result of the DTG and STTG flip-flop 56           |

| Table 5.1- Power consumption of the IC and its elements                             |

| Table 5.2- RMS Jitter of the IC and its elements                                    |

| Table 5.3- RMS Jitter of the SR                                                     |

| Table 5.4- Power consumption and jitter of the IC and its elements                  |

| Table 5.5- Jitter of the SR                                                         |

| Table 6.1- Layout areas of the elements of the Rx core                              |

| Table 6.2- Layout areas of the elements of the SR                                   |

| Table 6.3- Layout areas of the elements of the IC                                   |

| Table 6.4- Comparison between the proposed Rx and other Rx core implementation @500 |

| Mhz                                                                                 |

| Table 6.5- Comparison between the proposed CC and other CC implementation @1 Ghz.   |

|                                                                                     |

Table A.1- DC Operating Point - Voltages of the SAL+RCMF circuit transistors............ 85

# **Acronyms**

ADC Analog-to-Digital Converter

CMOS Complementary metal-oxide-semiconductor

**CP Charge Pump**

D2S differential-to-single

DAC Digital-to-Analog Converter

DLL Delay-locked loop

DU Delay unit

**ENOB Equivalent Number of Bits**

FFD flip-flop D

FL Flip-Logic

HGRA High-Gain Regenerative Amplifier

CC Clock Circuit

LVDS Low-Voltage Differential Signal

LP Loop Filter

LSB Least Significant Bit

LNLGA Low-Noise Low-Gain Amplifier

MPCG Multi-Phase Clock Generator

MSB Most Significant Beat

NMOS N-channel metal-oxide-semiconductor

PD Phase Detector

PMOS P-channel metal-oxide-semiconductor

PNOISE Periodic Noise Analyses

**PSS Periodic Steady State**

QILA Quasi-Infinite Load Amplifier

RCMF continuous-time passive common-mode feedback circuit

SAL Differential Amplifier with active load

SALPF Differential Amplifier with active load and positive feedback

SFDR Spurious-Free Dynamic Range

SINAD Signal-to-Noise and Distortion Ratio

SNR Signal-to-Noise Ratio

SR Shift Registers

SRL Differential Amplifier with resistive load

VCDL Voltage Control Delay unit

1

## 1. Introduction

#### 1.1. Context and Motivation

Nowadays, the technology of integrated circuits is in constant development and mutation, being, therefore, relevant to the appearance of new solutions in the most diverse areas of application [1]. In fact, in most of the new electronic systems, recently developed, there is a tendency to replace analog circuits by equivalent digital systems, which makes ADC systems with an increasing importance in all electronic systems, and they are subject to a constant need of evolution.

Data-converters have several applications, namely in communication systems, mobile devices, medical devices, among others. This shift to equivalent digital systems, it is directly reflected in an increase in the data storage process in the digital domain. The success of this modification will imply the implementation of high-resolution ADCs, with high sampling rate, to improve the efficiency and speed with which analog information can be converted into digital, that is, the rapid evolution of ADCs will allow signal conversion in continuous-time, for discrete-time signal, with great quality factor. However, there are several challenges in this type of implementation, since the resolution of the ADC decreases with the sampling period and with the input frequency, which results in a conflict between the accuracy and speed of the converter [2]. Thus, the main factor to consider when it comes to converter degradation is the clock jitter, it is essential to limit this factor to high input frequencies, since this causes uncertainties in the sampling instant, resulting in loss of ADC resolution. To counteract such consequences, it is important to develop an architecture that can balance both jitter minimization and signal sampling performance.

Another important factor to consider, not only in ADCs but in all electronic circuits, is the power dissipated by them, being necessary to find a balance between consumed power and jitter. Throughout this document, some architectures that meet the intended requirements, mentioned above, will be addressed.

### 1.2. Problems and Objectives

This dissertation aims to develop a multiphase clock generation circuit for high-speed ADCs with minimal phase-noise, jitter and the lowest power dissipation possible. However, during its design, several challenges will have to be considered, namely: sizing an architecture capable of generating a clock signal that will feed the converter, allowing to work with high input frequencies in a range between 500 MHz and 1 GHz and minimizing the jitter values, below 1 ps [3] resulting from the input frequency range; keep the power dissipation of the circuit at values within considerable ranges, below 10 mW.

The intended architecture will be divided into three main sub-architectures, depending on the desired requirements. In an initial phase, two sinusoidal signals of about 200 mV peak-to-peak will be generated by two ideal voltage sources, which will feed a clock buffer. In a second phase, the clock buffer will process these signals, which, in turn, will amplify them and transform the differential input signals into a single-ended output clock signal. This signal will later be processed in a digital buffer that will transform the sinusoidal wave into a new wave, a pulse with a square shape with 1.2 V peak-to-peak. Finally, this single-ended signal will feed a new architecture, which will generate an even number of signal clock phases. This architecture will be scaled with D flip-flops to obtain an 8-phase output signal with a 50 % duty cycle and a frequency range between 65 MHz and 125 MHz. The duty cycle can be changed according to the system's needs, for example, to 12.5 % using logical NAND gates.

This dissertation will focus essentially on the aforementioned architectures, which are the main points of interest. For the success of this work, it is intended to use existing architectures, size them with a 130 nm CMOS technology, and group them, so that they fulfill the intended simulation requirements.

#### 1.3. Document Organization

This dissertation is organized by several themes, consisting of 7 Chapters and an Appendix. Note that each Chapter may include multiple sections.

Chapter 1 presents a first general approach to the content that will be presented, framing the importance that ADCs have gained in the technological world. In this context, the problem/focus of the dissertation is described, introducing the objectives.

In chapter 2, a brief review of concepts is made, namely what types of ADCs and metrics to consider when working with this type of devices.

Chapter 3 consists of a review of the available literature. This chapter addresses the work and research done in this field and what insights they can provide for the elaboration of the dissertation. In this way, the main operating characteristics of architectures capable of meeting what is intended are explored in detail, stating different implementation topologies. Subsequently, the main advantages and disadvantages of each topology are presented, and, through this information, it will be possible to develop a model that uses the best characteristics of the best topologies.

Chapter 4 presents the characteristics of the main topologies chosen for the implementation of the Clock Circuit (CC) as well as its sizing.

In Chapter 5, electrical simulations of the CC are elaborated to test its performance with the main interest in power and Phase jitter performance. At the end of the chapter, the electrical simulations results are duly discussed.

Chapter 6 presents the layout of the various CC elements and how they were implemented. In the final part of the chapter, the results obtained from the electrical simulations and from the layout are compared with other architectures previously studied and identical to those that were implemented.

Finally, in Chapter 7, the conclusions of the dissertation study are presented, proposing some future works that would be interesting to investigate to complement this dissertation.

2

# 2. Basic concepts of ADCs

#### 2.1. ADC Architectures

The rapid evolution of digital integrated circuit technologies has led to the development of signal processing systems, increasing their level of sophistication. This development of signal processing systems brought a set of new advantages such as easy operation, high reliability and good stability. These integrated circuits operate on a wide variety of continuous-time signals, including telecommunications, consumer electronics, instrumentation, warfare systems, medical imaging, speech, among others [1]. The constant development of analog-to-digital converters (ADCs) is one of the main keys to the great success of these integrated circuits. The function of the ADC is to convert continuous analog signals to discrete digital signals, so to get a high performance of electronic systems, it is important to understand the important role that the digital-to-analog (DAC) converter plays. As a result, the number of signals to be digitized increased, which led to a diverse selection of data converters in terms of architecture, resolution and sampling rates [4].

Throughout this chapter, different types of ADC architectures will be analyzed. Each type of converter has its own set of features that satisfy different applications. There is, however, a set of ADCs that are most used in today's digital world, among them are: Flash ADC, Digital Ramp ADC, Dual-slope ADC, Successive Approximation Register ADC (SAR), Pipeline ADC. These types can vary on three main metrics: accuracy, interface, and speed.

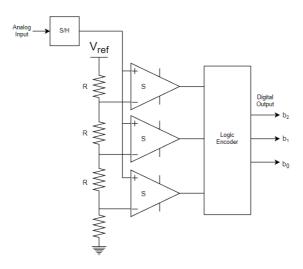

#### 2.1.1. Parallel (Flash) ADC

Parallel (Flash) ADC (Figure 2.1) is a kind of ADC with the highest converter rate and, therefore, is best suited for applications that require large bandwidth. However, this converter has some limitations. To be one of the fastest to convert the analog signal into a digital signal will need more chip area which translates into a higher cost, consumes more power and has a very limited resolution. These limitations will have a big impact on the ADC performance for high frequencies. An N-bit Flash ADC employs  $2^{N}$ -1 cascading comparators and  $2^{N}$  resistors. The input signal is applied to the ADC on all comparators. Then the comparators will compare the unknown input voltage with the voltage corresponding to each comparator. The voltage corresponding to each comparator depends on the periodicity level in the ADC, i.e., the resistance of the chain to which the comparator is associated. The result of the comparisons is a digital thermometer code that will later be decoded and translated into N bits. [4].

The resolution of the converter is directly dependent on the number of comparators and resistors, that is, for a higher resolution, more devices will have the ADC. If the goal is for the comparator to perform quickly, it must run at relatively high-power levels. Therefore due to the large number of high-speed comparators, the Flash ADC has some problems, these include high power dissipation which consequently leads to a rather large and expensive chip size (the bigger the chip the more expensive it is). In addition to these problems, it is important that the chain resistance remains relatively low to provide suitable bias current to the comparators.

Figure 2.1- N-bit flash ADC based in [4].

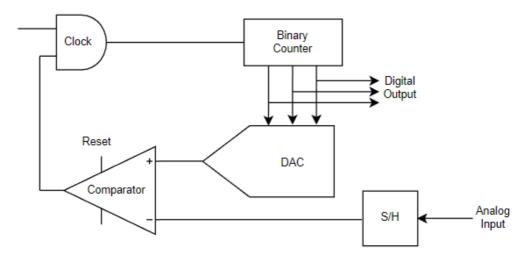

#### 2.1.2. Counter type ADC

Counter type ADC (Figure 2.2) is a converter that produces a sawtooth signal that rises or falls. When the conversion cycle begins, the timer starts counting until the voltage at the single oscillator output (ramp voltage) matches the ADC input signal. Then the comparator triggers and the value recorded by the timer is saved. Since the ramp voltage is normally generated by a single oscillator, the ramp time is more sensitive to temperature. To counteract this sensitivity, there is a solution that consists of using a counter with a clock to activate a DAC and using a comparator to preserve the time recorded by the counter. The main improvement of this new ramp implementation is that to store the voltage value obtained in the second signal comparison, the system only requires another register and another comparator [4].

There is a very simple way to implement a Counter type ADC with just a capacitor, a resistor and a microcontroller. When the analog input signal is connected to the comparator terminal, the binary counter is activated. The counter will later feed the DAC, to convert the digital signal to analog so that it can be compared to the input voltage. As the counter gradually increments the DAC output will increase. Until the DAC output voltage exceeds the unknown analog input voltage, this process will continue. This process will not only cause the counter to stop but will also affect the comparator output by changing its value. The corresponding time the counter takes to stop will represent the analog input voltage value.

Figure 2.2- Counter type ADC based in [4].

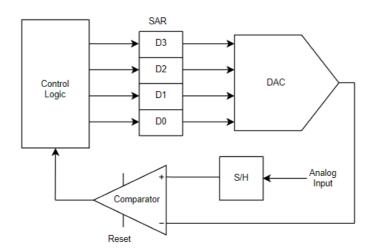

#### 2.1.3. Successive-Approximation Register (SAR) ADC

A successive-approximation Register ADC (Figure 2.3) works by using not only a comparator that allows finding the input voltage by performing a binary search, but also a digital-to-analog converter (DAC). Compared to digital ramp ADC it is much faster because the binary search is performed on all of the ADC quantization levels that it has at its disposal before converging to the final value. Explaining by other words the ADC converges to the value closest to the analog input voltage by using digital logic. Although it is more advantageous than the digital ramp ADC, it has a high resolution, which makes it slower, ceiling a maximum speed of about 5 Msps. Compared to other ADCs it has a simpler design which allows high resolution and high speed, a significant small chip area and a good balance between speed and cost. This features make this type of converter used in most modern IC ADCs [4].

As mentioned, there is a binary search to obtain the corresponding digital signal at ADC's output. The search begins with the most significant bit (MSB) and works on decoding the bits until it reaches the least significant bit (LSB). When the conversion starts the control logic sets the most significant bit of the successive approximation register (SAR) with a value of "1" and the other bits are initialized at "0". Afterwards the SAR information is fed into the digital-to-analog converter which produces an analog voltage (half of the reference voltage). This voltage is compared with the unknown voltage supplied to the input of the ADC. If the input voltage is smaller than the DAC output value, then the comparator induces the SAR control logic to reset the MSB back to "0" and set the next bit to "1" to repeat the process. If, on the other hand, the input voltage is higher than the voltage at the output of the DAC, this bit will remain at "1". After finding the value of the bit, the next significant bit will also be set to the value of "1" and the previous process is repeated. At the end of the search the result at the SAR output is a digital estimation of the analog signal sampled at the ADC input.

Figure 2.3- A block diagram for a successive-approximation ADC based in [4].

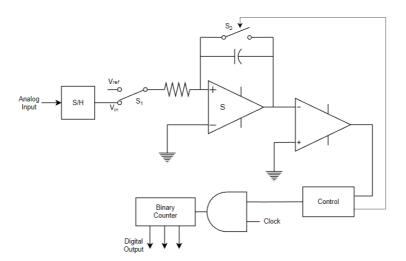

#### 2.1.4. Dual-slope integration ADC

Dual-slope ADC (Figure 2.4) applies an unknown input voltage to the integrator and this voltage increases until a predetermined amount of time (T), at which time the binary counter is initialized. After that period, the reference voltage, but with opposite polarity is applied to the integrator. During this period the integration capacitor accumulates charge. Based on the integration of the charge accumulated by the input voltage until the reference voltage is injected into the integrator (T) and the time (t) at which the output of the integrator returns to zero a binary value is defined by the counter. This binary value will be a representation of the input voltage. The time measurement of (t) is done in the same unit as the converter clock, therefore longer integration times allows higher resolutions. However there is a trade-off between resolution and ADC speed, by sacrificing resolution the ADC can be faster [4].

Converters of this type are used for their linearity and flexibility. However, to further decrease power consumption, a single-slope ADC may be another option. Single-slope ADC can be a more attractive solution to minimize power consumption because the converter is implemented by digital circuits, which only consume current when there is a pulse transition. Dual-slope ADC applications are limited to low sampling frequency, once the ADC requires many conversion clocks for one sampling.

Figure 2.4- A basic block diagram for a dual-slope integration ADC based in [4].

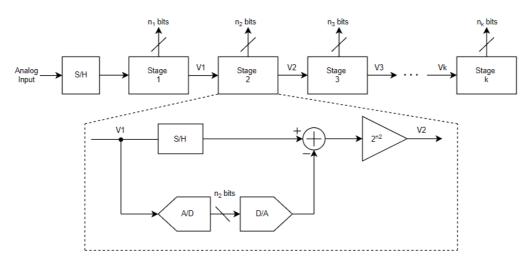

#### 2.1.5. Pipeline ADC

A pipeline ADC consists of several consecutive stages, each stage with 2 or 3 steps. In the first step, the input voltage is first sampled and held steady by a sample-and-hold while the ADC quantifies this voltage in n<sub>2</sub> bits. These bits will be fed to the DAC which generates an analog output where it will later be subtracted from the input signal. In the last step, the result obtained from the subtraction is amplified and fed to the next state. The ADC pipeline is an amplitude quantizer that has several stages in cascade where the digitization is performed. The number of stages depends on the resolution of the ADC, normally it matches the number of bits in the ADC. By using analog registers in the implementation of the ADC such as sample-and-hold amplifiers (SRAs) it is possible to obtain high conversion performance.[4].

Some modern pipelined ADCs employ a technique called "digital error correction" which greatly reduces the accuracy requirements of the ADCs used in their implementation. This implementation resorts to the use of individual comparators. The use of comparators allows the architecture to tolerate large displacements due to internal decision-level overlaps between successive stages. With this implementation, the conversion will depend exclusively on the precision, not only of the residual signals, but also on the conversion speed. However, there are still limitations as the gain is not corrected for errors in the individual DAC as well as in the gain amplifiers. Based on what has been mentioned, the pipeline is a very attractive architecture for applications that operate at high sampling rates.

Figure 2.5- Pipeline ADC based in [4].

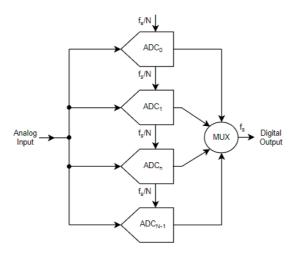

### 2.2. Time-Interleaving ADCs

A Time-Interleaved ADC (Figure 2.6) is made up of *N* parallel channels of any kind of ADC architecture that alternately each process a sample, where a channel's sampling frequency no need to match the Nyquist Criterion. However, when the analog samples are processed and converted to the digital domain, they form a sequence where the sampling frequency respects the Nyquist criterion. Thus, an ideal TI-ADC allows sampling with *N* channels equivalent to sampling with an ideal ADC with a sampling rate *N* times higher. The channels of a TI-ADC can have different implementations based on the conversion technology used and the intended objective, for example by selecting high-rate ADCs and then choosing which factor is more important to value, power or resolution. By increasing the number of channels, it is possible to increase the sampling rate of the TI-ADC. In an ideal and theoretical model, the dimensioning of the sampling rate would be according to the number of channels. Nevertheless, this process is not so linear, as there are mismatches between channels that directly influence and limit the performance of TI-ADCs. [5].

The fact that there is a tendency to downscaling IC technologies can complicate the matching of components that implement this type of architecture, but on the other hand, the increase in density makes it possible to add equivalent digital components with small costs. The existing method to mitigate the problems of analog conversion circuits is to add equivalent digital circuits. TI-ADCs are an excellent representative example of this type of technology where implementations will be increasingly worked on and improved.

Figure 2.6.- Time-interleaved ADC with N channels based in [5].

As the main objective of this document is to obtain a system capable of processing high-resolution and high-speed sampling signals, it is necessary to consider an ADC architecture that complies with the new communication standards. Today's ADC technologies work very close to their limits and have limitations that prevent them from being properly pushed any further, as it is rather challenging to design ICs with sub-micron technologies. However, increasing the density of the components has a significant advantage since the circuit allows the dimensioning of a digital circuit with a smaller area. By reducing the chip area, it allows adding new components that will only have small additional costs. Parallelism is a method used to overcome the aforementioned performance limits. Splitting the analog information that is fed into the ADC input into multiple parallel channels, converting them independently, and finally recombining the samples into a digital output signal makes the signal conversion process much more efficient. Thus, the ADC architecture that will be considered will be the TI-ADC [6].

#### 2.3. Performance Metrics

Before taking an approach to the clock signal that feeds the ADC, there is a need to adequately understand the main characteristics and parameters inherent to the ADC. Since there is a great variety of converters of this type, as has already been shown, it is essential to consider a large number of evaluation parameters, as there is still no universal parameter. However, we can consider a range of more relevant parameters, which will influence its normal functioning, they are: SNR; SFDR; THD; SINAD; and ENOB [7].

The SNR relates the effective power of the ADC input signal to the noise power. The higher this ratio, the lower the noise at the ADC input.

$$SNR = 10\log\left(\frac{P_{signal}}{P_{noise}}\right)$$

(2.1)

The THD refers to the effective power of all harmonics present in the converter with the power of the input signal.

$$THD = 10\log\left(\frac{P_{\text{harmonics}}}{P_{\text{signal}}}\right) \tag{2.2}$$

SINAD, like SNR, also relates the effective power of the ADC input signal, but also considers distortion rather than just noise power. SINAD as it considers the power of all

spectral components fully represents the overall dynamic performance of the ADCs. SINAD also differs from SNR, as it emphasizes harmonic distortion, more specifically the first five harmonics.

$$SINAD = 10log\left(\frac{P_{signal}}{P_{noise} + P_{distorcion}}\right)$$

(2.3)

ENOB is a very important metric for ADC performance and directly reflects the equivalent number of ADC bits. To calculate this parameter, a method called the sine wave adjustment method is used, for a given sampling time.

ENOB =

$$\frac{\text{SINAD} - 1.76}{6.02}$$

(2.4)

The SFDR has a formula that is very similar to THD. However, it refers to the effective power of the fundamental wave with the maximum harmonic power.

$$SFDR = 10\log\left(\frac{P_{\text{harmonic}}}{P_{\text{signal}}}\right)$$

(2.5)

#### 2.3.1. Aperture Jitter (jitter noise)

Jitter is characterized as the time difference of the final signal edge set, both rising and falling from the ideal signal values. Clock signals are subject to noise and other disturbances that are primarily responsible for causing oscillations. The main factors causing oscillations in clock signals include coupled interference from nearby circuits, power supply variations, device noise, load conditions and thermal noise.

One of the main noise meters is jitter and there are four primary measures for clock jitter. Based on the performance requirements that the clock signal needs to achieve depending on the application for which it is applied, the measure for the jitter calculation is chosen. The following are the major types of jitter [10]: Long Term Jitter, Cycle to Cycle Jitter, Phase Jitter and Period Jitter.

#### 2.3.1.1. Cycle-to-Cycle Jitter

Cycle-to-Cycle jitter is the maximum deviation between adjacent consecutive clock periods. These periods are defined for a fixed number of cycles, which can vary but are normally within 1,000 cycles or 10,000 cycles. In other words, Cycle-to-Cycle jitter takes into account the rising edge of two adjacent clock periods and calculates the maximum deviation between them, so it can be reported as an RMS value in ps. If there is a need to limit a sudden jump in frequency, cycle-to-cycle jitter is used as a monitoring metric. This means that the characteristics that this type of jitter has are normally used to demonstrate the instability of systems that work with spread-spectrum clock signals, since they have less sensitivity to the spread-frequency feature [10].

#### 2.3.1.2. Period jitter

Period jitter is the difference between two clock periods for a given random number of cycles. The selection of periods, however, is not random and the highest clock period and the lowest clock period are selected. There are several publications that take a different approach and define this type of jitter as the difference between the ideal period and the measured clock period. By having access to several individual clock periods, they can be measured which allows calculating not only the average clock period, but the peak-to-peak value and the standard deviation, as well [10].

#### 2.3.1.3. Long-term Jitter

Long-term jitter measures the clock signal deviation at the clock signal output from the ideal position over numerous cycles. To choose the most suitable number of cycles to obtain the jitter value, it is necessary to consider the application of the signal. This type of jitter has different characteristics from both Cycle-to-Cycle and Period Jitter because for a designated continuous flow of clock cycles over a long time interval, it considers the cumulative jitter value, that is, the jitter increases as the number of cycles increases. It is for this reason that long-term jitter is sometimes called accumulated jitter [10].

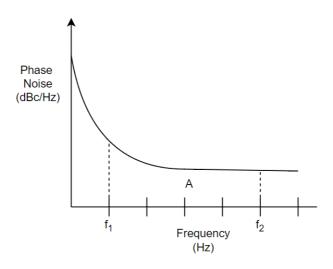

#### 2.3.1.4. Phase jitter

Before talking about Phase Jitter it makes sense to explain what Phase-Noise is. Phase-noise can be described in two ways, either as a graphical representation of continuous noise for a given range of frequencies or a set of noise values at different frequency shifts. Let's focus on the first definition, considering a curve that represents the continuous noise for a given frequency spectrum, it is possible to integrate this curve in which the result of this integration will represent the Phase Jitter value expressed in seconds. When the signal, where the jitter is to be analyzed is a square wave, it is necessary to consider the carrier frequency. It makes sense to make this consideration because it is in the carrier frequency that are located most of the

noise energies [10]. Nevertheless, there is always a trace of signal energy that is "leaked" in a range of frequencies that can go to either side of the carrier. Phase jitter will be the jitter on which this document will focus the most and as such, it is necessary to find the method to find its value. To calculate this value, it is necessary to consider two offset frequencies and then relate the amount of phase noise energy contained between them relative to the carrier [11] (Figure 2.7).

Figure 2.7- Phase Noise plot based in [11].

The RMS Phase Jitter between  $f_1$  and  $f_2$  is defined by equation (2.6):

RMS Phase Jitter =

$$\frac{\sqrt{2 \int_{f_1}^{f_2} 10^{A/10}}}{2\pi f_c}$$

(2.6)

### 3. State of Art

Nowadays, one of the most important challenges for ADC architectures is to achieve the combination between a high value of SNR and a low value of THD, being, therefore, necessary to obtain a low jitter clock signal [12]. This problem becomes more difficult to mitigate when we are dealing with converters that require clock signals with high input frequencies. At the initial instant of sampling, there is a phenomenon called jitter, mentioned above, which directly influences the performance and noise of the system. Thus, digitizing high-speed signals requires adequate low-jitter reconstruction of the clock signal to fulfill the targeted sampling performance. For this purpose, a circuit called clock buffer was created, which aims to reconstruct the initial clock signal transforming it into a low jitter signal.

#### 3.1. Clock Buffer

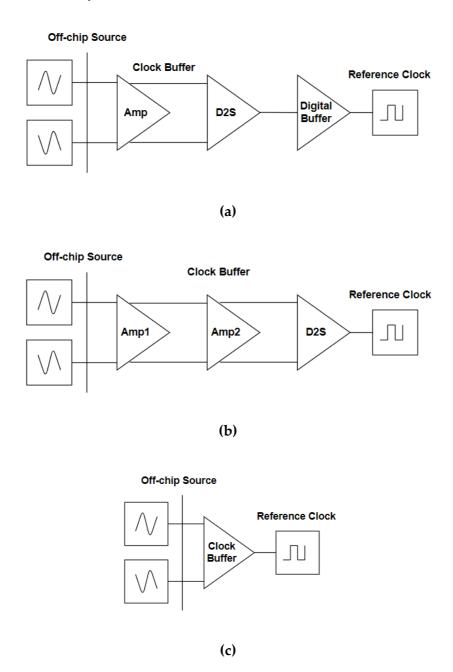

The clock buffer's function is to pre-amplify the input signal and transform the sinusoidal input wave into an output wave, with characteristics identical to the square wave. To obtain a wave with as perpendicular a slope as possible, the buffer needs to have a large mesh gain and, in turn, produce a low intrinsic noise. The first stage of the buffer is quite simple and consists of a differential-input and differential-output structure. One aspect to consider, to minimize noise, is to use resistors as load sources, instead of the active loads, if this possibility is valid. The second floor of the buffer is built by a differential input, but by a single output, unlike what was sized on the first stage. Additionally, still, regarding the second stage, it should be noted that the structure was selected, considering that one of the purposes of the buffer is to transform a sinusoidal differential signal into a single output signal (D2S circuit) [1], [13]. The buffer will require another architecture to connect to manually, a digital buffer that aims to flatten the output signal curve, both in the ascending and descending phases, accelerating the rise and fall time of the clock signal, which will be used to power the MPCG. The transistors and resistors are independent of each other, for the noise existing in the first stage, this must be amplified by the second stages of the buffer, which will have a significant impact on the total output noise. For this reason, the first floor is sized with active loads. Figure 3.1 shows schematics of base clock buffer architectures, where all types of architectures will be analyzed.

Figure 3.1- Simplified block diagram of a possible scheme for a clock recovery circuit. a) Current mode, b) Voltage mode c) Simple Buffer

#### 3.1.1. Clock Recovery Circuitry

The on-chip clock recovery circuit (Rx) (Figure 3.2) considers several types of architectures, with several stages, which feature in its constitution a front-end differential amplifier, an optional differential to single-ended converter (D2S), which can do so much. operate in voltage mode as in current mode [14]. Afterwards, this converter is followed by a buffer with a back-end output. If the architecture does not have the D2S amplifier in the circuit, its role is played by the digital output buffer. However, this approach will not be the most suitable, which may imply some consequences, namely in the significant degradation in the performance of the ADC, for a given value of consumed power. As the purpose is to obtain a signal with low jitter and power, the use of the D2S stage becomes mandatory [15].

Figure 3.2- Simplified block diagram of a possible scheme for ultra-low-jitter clock recovery circuit based in [15].

In fact, as the aim is to minimize jitter, the D2S stage gains significant importance, as it plays a fundamental role in the clock signal reconstruction process [16]. The functioning of the D2S has a great impact on the slope of the clock signal curve, when it has a positive value, but it also impacts the gain that is obtained in the various stages of the circuit. As already mentioned, the objective is to reach a topology that allows to obtain performances with very low jitter values. To achieve this performance, the clock signal is applied as a differential

waveform, with characteristics very similar to the sine wave. This signal is obtained with the aid of a narrowband filter, together with a low jitter oscillator. The purpose of the circuit is to recover the internal clock signal, without clock jitter degradation, inside the chip. Once the input signal enters the chip, the front-end clock recovery (Rx) circuit will transform the differential signal into a low jitter single clock (CLK) signal that will later feed the ADC. With this approach, the clock signal is retrieved at the intended requirements.

The main objective in a clock signal recovery circuit is the signal reconstruction through a filtered wave very identical to the sinusoidal one, which is fed to the input. From a more functional point of view, the circuit must detect the zero point of voltage between the positive and negative input of the circuit. The clock buffer consists of a core (Rx), which basically consists of a comparator between the zero point of voltage crossing, in each period, and a digital output buffer, which provides the necessary conduction capacity for the load of output and consists of two cascaded CMOS inverters [15].

#### 3.1.2. Existing topologies

As already discussed, the clock buffer can either operate in both voltage or in current mode so that, for both modes, different architectures will be presented. According to Juan Núñez et al.[15], there are several types of architectures, which can be compared to each other. On the other hand, two important characteristics were detected in the sizing of the low jitter clock signal recovery circuit, the D2S operation and the achievable gain.

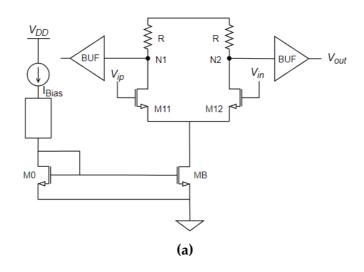

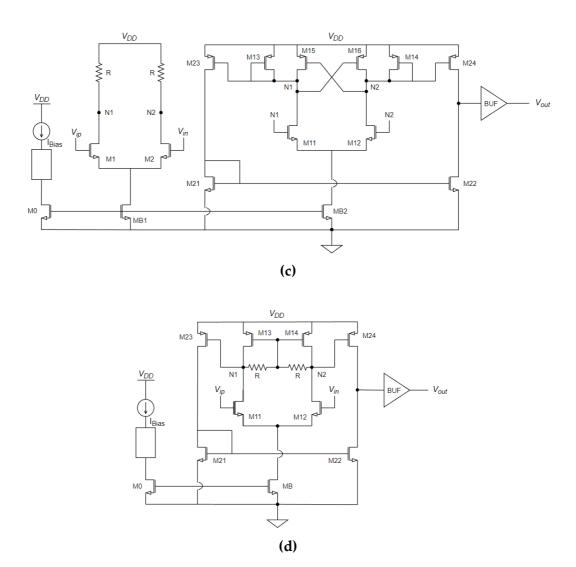

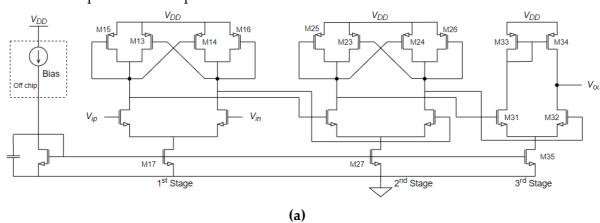

#### Differential stage with resistive load (SRL)

The first architecture (Figure 3.3 a)) is based on a differential amplifier with resistive load (SRL) and represents a simplified scheme of the Rx core. The main disadvantage observed in this approach is that the conversion performed on the D2S circuit inputs is done in voltage mode by the digital output buffer (BUF). An additional, dummy buffer will have to be added to compensate the load of the transistor's nodes N1 and N2. As a result of this approach, the circuit will show relatively small gains and inefficient power consumption as a result half of the RX core energy is wasted. Furthermore, the size of this architecture can be quite complicated for low jitter and power consumption [15].

#### Differential stage with active load and positive feedback (SALPF)

The SRL architecture (Figure 3.3 b)) has many limitations, so, to alleviate the problems, it faces, a new topology was suggested, which uses a front-end differential amplifier, with active load together with a differential to single-ended (D2S) circuit in current mode, formed by transistors. The transistors M13 and M14 are in diode configuration and they represent the

active load of the circuit, they are also part of two current mirrors, while the transistors which are responsible to increase the output gain and are optionally used as positive feedback (PF), are the M15 and M16. The amount of feedback desired in the circuit can be controlled by the ratio of the original diode effect transistors to the M15-M16 cross pair.

This architecture can be called SALPF, as it presents a solution with positive feedback and at the same time can reach a considerable gain factor. The use of diodes in the circuit makes it possible to fix the first stage's operation point, at the low impedance output node. In extreme cases, where there is no positive-feedback, which is abbreviated to SAL, transistors M15 and M16 are no longer part of the circuit and the gain of the first stage is lower, because of the diode connection [15].

#### Two-stage architecture based on a SRL and a SALPF (SRL + SALPF)

In the third structure, a new approach was explored, in which two amplifiers with different functions were grouped together. This approach considered the possibility of using a dedicated D2S circuit, fully differential, to integrate the second stage of the circuit, to improve the gain. The resulting circuit, identified as SRL + SALPF, can be represented as a cascade circuit of receiver cores from both the SRL architecture and the SALPF architecture, in which the differential to single-ended signal conversion is decoupled from the first stage. As in the SALPF architecture (Figure 3.3 c)), transistors M13 and M14 connected to the diode fix the operating point, while transistors M15 and M16, responsible for the partial feedback of the second stage and increase circuit's voltage gain. Finally, transistors M21 to M24 perform de D2S operation. [15].

## Differential stage with active load and passive common mode feedback (SAL + RCMF)

Taking these considerations into account, an alternative architecture (SAL+RCMF) has been decvided. This architecture (Figure 3.3 d)) consists of a first stage, completely differential, with an active load (SAL) and incorporates the D2S circuit in current mode (transistors M21 to M24). To establish the DC operating point in the drain of the PMOS transistors (N1 and N2), a new circuit was considered. This new approach consists of a continuous-time, with common-mode feedback circuit (RCMF), that embodies two resistors. This type of approach will not only allow an increase in the SAL circuit gain, which translates into an increase in the first stage gain, but, at the same time, it manages to define an appropriate input voltage for the D2S circuit (transistors M23 and M24) as well. In addition to what was mentioned, this architecture, demonstrated by the simulation carried out by the name of the author of the article, will allow a significant reduction in power consumption for a given jitter value. It is a very attractive approach, but it is important to emphasize that he main upper hand of this topology does not

depend exclusively on the differential pair of the first stage, but also on the relationship between the two stages, that is, on the combination with the D2S circuit, since without its presence the jitter could be considerably higher [15].

Figure 3.3- Schematics of the selected low-jitter clock recovery circuits. a) SRL, b) SALPF, c) SRL+SALPF d) SAL+RCMF based in [15].

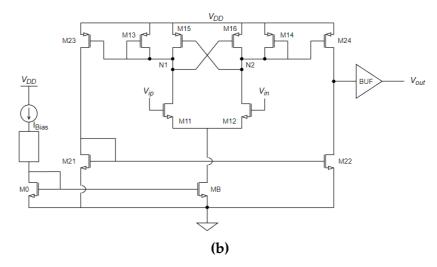

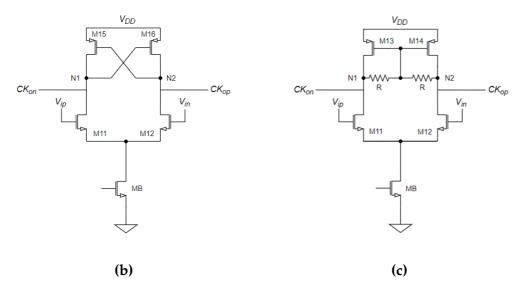

#### Quasi-Infinite Load Amplifier (QILA)

According to Cheng, Long et al.[18], a clock recovery circuit is presented, with characteristics quite identical to those already mentioned, however with some alterations. This topology is composed of two SALPF circuits and a D2S circuit which, unlike the previous topologies, operates in voltage mode and not in current mode, as in the other architectures. Another apparent difference in this topology is the fact that the SALPF and D2S circuits are independent of each other and, as such, this topology is called Quasi-Infinite Load Amplifier (QILA).

As can be seen from Figure 3.4 a), it becomes quite evident that the active load transistors, M13 and M14, work in diode configuration, in the first SALPF circuit, as well as transistors M23 and M24 in the second SALPF circuit. On the other hand, the set of transistors M15 and M16 in the first SALPF circuit and the set M25 and M26 in the second SALFP circuit are used as positive feedback to increase the amplifier gain. Finally, it should be mentioned that the topology will be composed of the D2S circuit that works in voltage mode.

# Low-noise low-gain amplifier (LNLGA) and High-gain regenerative amplifier (HGRA)

In the same article a comparison of this amplifier was made to two others, widely used in clock recovery circuits, a Low-noise low-gain amplifier (LNLGA) and High-gain regenerative amplifier (HGRA) [16]. From what was presented in the article, the Quasi-Infinite Load Amplifier has superior characteristics when compared to the LNLGA (Figure 3.4 c)) and HGRA (Figure 3.4 b)), since, through the circuit simulation, the LNLGA presented a substantially lower gain and the output signal does not show a peak, making it more vulnerable to noise. The slope of the HGRA output signal has a more defined peak, but it is still subject to a cancellation factor, which happens when the amplitude of the input signal is small. Thus, the amplitude of the output signal does not change [18]. A possible solution to this problem would be to increase the value of the current at the input, which would result in an increase in power consumption.

Figure 3.4- More schematics of the selected low-jitter clock recovery circuits. a) QILA, b) HGRA, c) LNLGA based in [18].

#### 3.2. Multi-Phase Clock Generator

The next step focuses on the implementation of an architecture, which will make it possible to convert the signal obtained at the end of the clock buffer and reproduce it into eight signals with identical characteristics, but with different phases. These signals will later feed into the TI-ADC architecture. Note that, in this case, eight clock signals were considered, but the scaling can be done for any even number of outputs. As mentioned above, jitter plays an important role in clock signal processing and taking this into account, it is necessary to find the type of architecture that best minimizes this factor.

#### 3.2.1. Different Topologies

To implement the intended architecture, Delay-locked loops (DLLs) and Shift Registers (SRs) are the options to consider. Therefore, it is necessary to carry out a study that allows us to infer which of the two has better characteristics, in order to more adequately satisfy the objectives that must be fulfill.

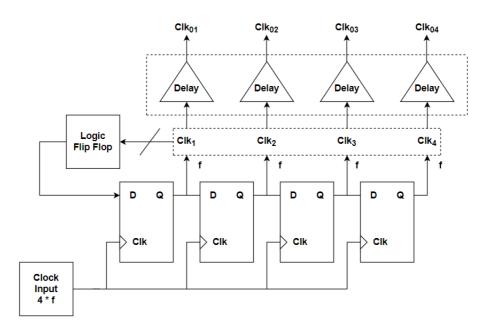

#### 3.2.1.1. Shift Registers

The architecture of an SR MPCG (Figure 3.5) consists of a chain of D flip-flops (DFF) with N (where N represents the number of output signals) identical DFF's. A reference clock signal, with a frequency  $N \cdot f$ , feeds the chain of flip-flops. To generate the input clock signal, considering that we are working at high frequencies, we chose to use a sine wave signal, to avoid timing and reflection errors due to the input impedance adaptation problems. input. Next, a clock buffer is designed to amplify the input clock signal by modifying the input waveform to a square-wave clock signal. The possible architectures for the clock buffer structure have already been analyzed in previous chapters.

Figure 3.5- SR MPCG architecture based in [19].

The signal obtained at the output of the clock buffer will be the reference clock signal, which will feed the chain of D flip-flops (DFF). In other words, the outputs of the D flip-flops chain work with a given input frequency and the MPCG, constituted by Shift Registers, works as a frequency divider, depending on the number of outputs. Since an DFF is sensitive to rising peaks, the Q output of each DFF is delayed, relative to the output of the previous DFF, by a reference clock period, which is equivalent to a  $2\pi$  / N phase delay [19].

8

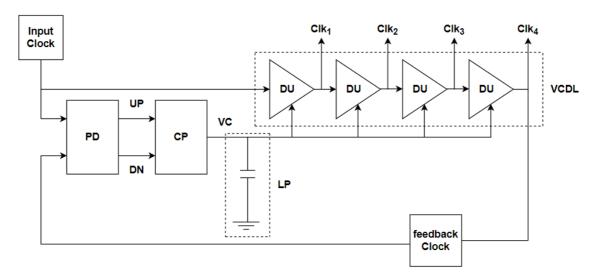

#### 3.2.1.2. Delay Locked Loop (DLL)

A Delay-Locked Loop (Figure 3.6) (DLL) consists of four main components: a phase detector (PD), a charge pump (CP), a closed loop filter (LF) and a voltage-controlled delay line (VCDL). The system has N delay units (DU) per each N DLL outputs.

Figure 3.6- DLL MPCG architecture based in [19].

The DLL operation starts with the phase detector PD which compares the phase difference between the reference clock signal and the delayed clock signal, i.e., the signal from one of the VCDL outputs. On the other hand, the charge pump converts the phase detector output into a control voltage (VC), by charging or discharging the filter capacitor. The VC changes the delay of each delay cell in the VCDL, this means that when the phase of the feedback clock signal is more advanced than that of the reference clock signal, VC increases the delay of VCDL and vice versa. The negative feedback in the closed loop will have the function of adjusting VC, to reduce the phase error, until reaching the moment when the rise time of the reference clock signals, and the feedback signals are aligned. Since each delay cell provides the same delay, with the same control voltage value, the DLL will produce a well-proportioned multiphase clock signal if the loop is closed [19].

#### 3.2.2. Output Jitter

Both implementations have advantages and disadvantages, which essentially depend on the type of use that is given to them, so there is a need to understand the reasons that can lead to opting out of one of them, depending on the other. Thus, it should be noted, once again, that one of the main points influencing the performance of the ADC is noise, which is associated with jitter. Next, an attempt will be made to understand the impact of jitter on the two architectures under analysis and, thus, choose the one that best responds to the intended problem.

#### 3.2.2.1. SR Output Jitter

The output jitter of the SR MPCG can be divided into two parts that will be duly analyzed and studied: jitter transferred from the reference clock signal and jitter generated by the chain of flip-flops D. The logic inversion circuit only has the function of changing the logic value of the entry of the first FFD and will have no contribution to jitter. Regarding the jitter transferred from the reference clock signal, the SR MPCG does not show improvement when compared to the VCDL. It is important to note that any timing error in the reference clock signal will be transferred to the outputs of the FFD chain., The FFD chain generates two types of jitter: mismatch jitter and noise jitter. However, the FFD chain does not accumulate jitter in the transition from one flip-flop to the other since each FFD output acts only as an input to the next FFD. An FFD can be designed in many ways and one of the approaches is the master/slave class methodology. For a design aimed at optimal characteristics, the only latch that contributes to jitter is the slave one, as the master functions as an "enabler" [19].

If the rms noise and mismatch noise of an FFD (latch) unit are defined as  $\sigma_{t,latch,noise}^2$  and  $\sigma_{t,latch,mis}^2$ , respectively, the average variance in the jitter value, for the set of clock signals with N phases generated, through the Shift Registers, will be calculated as follows:

$$\left(\sigma_{t,SR,noise}^{2}\right)_{medN} = \frac{1}{N} \cdot \sum_{n=1}^{N} n \cdot \sigma_{latch,noise}^{2} = \sigma_{latch,noise}^{2}$$

(3.1)

$$\left(\sigma_{t,SR,mis}^{2}\right)_{medN} = \frac{1}{N} \cdot \sum_{n=1}^{N} n \cdot \sigma_{latch,mis}^{2} = \sigma_{latch,mis}^{2}$$

(3.2)

#### 3.2.2.2. DLL Output Jitter

The DLL MPCG output jitter can be distinguished into three main divisions, but the focus will be more on the first two: The jitter transferred by the reference clock signal to the DLL and the jitter generated by the VCDL. When the reference clock signal is transferred to the DLL outputs, the jitter has peak values of this transfer. The DLL, however, has some limitations as it not able to decrease the jitter of the reference clock signal. On the other hand, by choosing a low closed loop bandwidth for the DLL, peak jitter values can be reduced.. For an ideal DLL architecture, the closed loop jitter contribution is negligible and can therefore be

ignored. Given the previous information, the main problem and concern is essentially with the jitter resulting from the VCDL. In an MPCG DLL, the architecture used in its implementation, VCDL can generate two types of jitter: random noise jitter, in which the main responsible for this type of jitter is phase noise, and mismatch jitter, which, as the name implies, is caused by the mismatch of the delay units. For the first type of jitter, that is, the noise jitter produced by VCDL, the DLL circuit does not show significant improvements. Again, the VCDL noise jitter is lower for low values of the closed loop bandwidth, a situation that would be quite identical to a free-running VCDL execution. Jitter, as it is transmitted, from delay unit to delay unit, will accumulate. The DLL's closed loop can significantly improve deterministic mismatch jitter, contrary to the effect it has on phase noise jitter,. The fact that the reference clock signal is properly aligned on both the input and the output of the VCDL causes the deterministic time error to be equal to zero, in contrast to the middle of the VCDL where the mismatch jitter is maximum [19].

If the jitter noise variation of a delay unit is represented by  $\sigma^2_{t,DU,noise}$  and, assuming the presence of uncorrelated white noise, the jitter noise variation at the output of the n<sup>th</sup> delay unit will be n times greater. To quantify the jitter value of a set of N-phase clock signals, the average jitter variance of the N signals has a significant amount. The average jitter variance of noise generated by DLL can be calculated by:

$$\left(\sigma_{t,DU,\text{noise}}^{2}\right)_{\text{medN}} = \frac{1}{N} \cdot \sum_{n=1}^{N} n \cdot \sigma_{t,DU,\text{noise}}^{2} = \frac{N+1}{2} \cdot \sigma_{t,DU,\text{noise}}^{2}$$

(3.3)

By defining the mismatch jitter variance of each delay unit as  $\sigma^2_{t,DU,mis}$ , the jitter variation at the output of the n<sup>th</sup> delay unit can be calculated by:

$$\sigma_{t,DU,mis}^2 = \frac{n(N+n)}{2} \cdot \sigma_{t,DU,mis}^2$$

(3.4)

To obtain the average value, the following expression is considered:

$$\sigma_{t,DLL,mis}^2 = \frac{N^2 - 1}{6N} \cdot \sigma_{t,DU,mis}^2 \tag{3.5}$$

#### 3.2.3. Jitter Comparison Between Topologies

#### 3.2.3.1. Comparing Jitter Transferred from the Reference Clock

From what was analyzed in the previous point, it is possible to notice that both the DLL and the SR MPCGs do not present improvements in the jitter of the reference clock signal. Taking this into account, it is known that the SR MPCG needs a reference clock signal with a frequency N times greater than the DLL, where N represents the number of clock signals intended for the output. If both signals are generated by the same source, the one that generates the signal for the SR must operate with a frequency N times greater than that of the DLL. However, higher operating frequencies will influence another important factor, power consumption [19].

Although the SR MPCG works with a frequency N times higher, the jitter produced is the same, in both cases, considering that both have the same power and the same design quality. On the other hand, it is important to be aware of the limitations that exist when increasing the frequency, and in addition to the reference signal source, the power consumption of the clock buffer can also become an issue.

#### 3.2.3.2. Comparing Jitter Generated Due to Thermal Noise

In most architectures designed to generate clock signals, jitter and power are, in fact, two very important parameters, as has been mentioned throughout the document. By manipulating the admittance, both noise and mismatch jitter can always be reduced, as long as they balance with an increase in power consumption. DLL is made up of N delay units, which contribute to jitter and power consumption. In turn, an SR has N branches contributing to the jitter and the same number of branches contributing to the power dissipation. The result of the comparison depends on the amount of delay units, that is, on the number of signals you want to obtain. In an MPCG DLL, the input source sets the working frequency and the VCDL sets the delay between the N output clock signals. Both the reference signal generator source and the delay units need to be adjusted so that the entire circuit runs at the same frequency. In contrast, the SR MPCG allows for greater flexibility. For different frequency values, only the source generating the reference signal needs to be adjusted, since the frequency and delay between the N output clock signals are defined by the clock period of the input source [19]

#### 3.3. Discussion

In this chapter, a final balance will be made between the different implementations, listing the advantages and disadvantages of the various possibilities, making it necessary to choose not only the best architecture for the clock buffer, but also for the MPCG.

#### 3.3.1. Clock Buffer

Table 3.1 shows the advantages and disadvantages of the different architectures presented in the state of the art.

Table 3.1- Advantages and disadvantages of the clock buffer architectures.

| Clock Buffer | Advantages                     | Disadvantages                     |

|--------------|--------------------------------|-----------------------------------|

|              | -Very simplified design.       | - It is necessary to add a        |

|              |                                | dummy buffer.                     |

|              |                                | - Low gain and inefficient        |

| SRL          |                                | power consumption.                |

|              |                                | - High jitter value.              |

|              |                                | -The D2S circuit operates in      |

|              |                                | voltage mode.                     |

| CALDE        | - Superior features to SRL.    | -Limitations on power             |

| SALPF        | - Relatively higher gain.      | dissipation.                      |

|              | - Superior features to SALPF.  | - Higher Power/Jitter trade-off   |

|              | - Joins two types that         | value than SALPF.                 |

|              | architectures.                 |                                   |

| SRL + SALPF  | - High power consumption,      |                                   |

|              | for a given jitter value.      |                                   |

|              | - The D2S circuit operates in  |                                   |

|              | current mode.                  |                                   |

|              | - Buffer with better           | - It requires accurate transistor |

|              | Power/jitter trade-off         | electrical models at high         |

| SAL + RCMF   | - The lowest power             | frequency.                        |

|              | dissipation for a given jitter |                                   |

|              | value.                         |                                   |

| LNLGA        | - Low jitter and power         | - Higher noise instability        |

| LINEON       | dissipation.                   | - Low gain.                       |

| HGRA         | - Higher gain and robustness   | - Higher jitter values and        |

| HGNA         | against noise than LIGA.       | power dissipation than LGNA       |

|              | - Higher gain and has a        | - The D2S circuit operates in     |

|              | sharper clock signal peak than | voltage mode.                     |

| QILA         | LNLGA.                         |                                   |

|              | - Less noise and lower power   |                                   |

|              | dissipation than HGRA.         |                                   |

Based on what is described in the table the two best architectures for the buffer implementation are SAL+RCMF and QILA. However, the SAL+RCMF architecture, as it operates in current mode, has a significant advantage over QILA. This will be the circuit to implement and size as far as the clock buffer is concerned.

#### 3.3.2. Multi-Phase Clock Generator

Based on what has already been mentioned and on the comparisons made between the two possibilities of MPCG, SR has a lower noise instability than the DLL counterpart, for a given power consumption.

The analysis made before shows that for mismatched jitter values DLL MPCG may have a small advantage in some high frequency cases.

Regarding the implementation of both circuits, the SR MPCG is easier, since it does not require so many components, namely a phase detector, a charge pump, a closed-loop filter. On the other hand, it can be more difficult to implement in applications that have a high number of outputs (N) and a high operating frequency (f) as requirements, as the SR works based on the following denotation:  $2N^*f$ . On the other hand, it is also important to consider, in this type of approach, the loading of the input source to be more severe in the SR MPCG, since it requires adding 2N DFFs. However, this problem can be solved by manipulating the value of admittances, reducing them considerably, which would result in a decrease in the size of the DFFs. In this way, less jitter would be generated, compared to the delay units, saving energy and chip area [19].

To finalize the comparison between the two circuits, MPCG consisting of Shift Registers will be the solution to implement since it is a digital circuit that has a large range of operating frequencies. In addition to what has been mentioned, an SR can change its output frequency and has the flexibility to generate clock signals with different duty cycles [20].

### 3.4. Proposed Circuit

Based on the conclusions obtained in the state of the art, it is possible to visualize the model of the architecture to be implemented (Figure 3.7).

Figure 3.7- Final schematic of the proposed circuit.

4

### 4. Circuit Implementation

#### 4.1. Clock Buffer

In the state of the art, it was concluded that the clock buffer circuit would be SAL+RCMF (Figure 3.3 d)), and in this chapter the sizing of the transistors of this circuit will be discussed. The circuit geometry is described through the length (L) and width (W) of each transistor and a careful selection of these values for each transistor is necessary, in order to make the circuit as efficient as possible.

The starting point of the clock buffer sizing methodology is to select for all transistors in the circuit their nominal polarization condition, where an input signal with a voltage close to  $V_{DD}/2$  will be considered, which is the maximum recommended value. To understand bias conditions, it makes sense to define overdrive voltages for a given bias current.

$$(|V_{OD}| = |V_{GS}| - |V_{TH}|) \tag{4.1}$$

Since the current that feeds the differential pair is half of the Bias source current and the relationship between current mirrors and transistors are a concern of the first stage, it is possible to significantly reduce the independent variables with the proposed parameterization.

In the sizing methodology is not a critical factor the specific selection of the initial polarization, as it will have an optimization later. At the beginning of the DC operating point, for a complete analysis, the main criteria are as follows:

- Bias all transistors in the saturation region and strong inversion.