#### UNIVERSIDAD DE SEVILLA

DOCTORAL THESIS

### Neuromorphic auditory computing: towards a digital, event-based implementation of the hearing sense for robotics

Author:

Daniel Gutiérrez Galán

Supervisors:

Dr. Alejandro Linares Barranco Dr. Ángel F. Jiménez Fernández

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the

Robotics and Computer Technology Lab. Departamento de Arquitectura y Tecnología de Computadores

July, 2022

# **Declaration of Authorship**

I, Daniel Gutiérrez Galán, declare that this thesis, titled "Neuromorphic auditory computing: towards a digital, event-based implementation of the hearing sense for robotics", and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

#### UNIVERSIDAD DE SEVILLA

## Abstract

#### Escuela Politécnica Superior

Departamento de Arquitectura y Tecnología de Computadores

Doctor of Philosophy

## Neuromorphic auditory computing: towards a digital, event-based implementation of the hearing sense for robotics

by Daniel Gutiérrez Galán

In this work, it is intended to advance on the development of the neuromorphic audio processing systems in robots through the implementation of an opensource neuromorphic cochlea, event-based models of primary auditory nuclei, and their potential use for real-time robotics applications.

First, the main gaps when working with neuromorphic cochleae were identified. Among them, the accessibility and usability of such sensors can be considered as a critical aspect. Silicon cochleae could not be as flexible as desired for some applications. However, FPGA-based sensors can be considered as an alternative for fast prototyping and proof-of-concept applications. Therefore, a software tool was implemented for generating open-source, user-configurable Neuromorphic Auditory Sensor models that can be deployed in any FPGA, removing the aforementioned barriers for the neuromorphic research community.

Next, the biological principles of the animals' auditory system were studied with the aim of continuing the development of the Neuromorphic Auditory Sensor. More specifically, the principles of binaural hearing were deeply studied for implementing event-based models to perform real-time sound source localization tasks. Two different approaches were followed to extract interaural time differences from event-based auditory signals. On the one hand, a digital, event-based design of the Jeffress model was implemented. On the other hand, a novel digital implementation of the Time Difference Encoder model was designed and implemented on FPGA.

Finally, three different robotic platforms were used for evaluating the performance of the proposed real-time neuromorphic audio processing architectures. An audio-guided central pattern generator was used to control a hexapod robot in real-time using spiking neural networks on SpiNNaker. Then, a sensory integration application was implemented combining sound source localization and obstacle avoidance for autonomous robots navigation. Lastly, the Neuromorphic Auditory Sensor was integrated within the iCub robotic platform, being the first time that an event-based cochlea is used in a humanoid robot. Then, the conclusions obtained are presented and new features and improvements are proposed for future works.

#### Acknowledgements

Becoming a Doctor of Philosophy has been one of my biggest dreams since I was young. The path has been long and the task has turned difficult, but there have been people all along this time who either have support me or have hated me. To those who have helped me in any kind of situation: thank you all very much. I have no words to let you all know how much I appreciate you. To those who have tried to bring me down: you were my biggest motivation. I have hundreds of words for those people, but only one that can be written here: "empathy".

I bought my first computer when I was 9 years old. All my friends asked for the Play Station 2. Instead, I asked for a Pentium 4 with 256 MBytes of RAM memory. Fransico José Junquero told me *"this is going to be the future, and you have the potential to learn whatever you want"*. Without that advice, I would not have asked for a computer, I would not have written these lines. Thank you very much, this thesis also belongs to you.

Then, I started to show interest for mathematics. When I was 14 years old, although my marks in math were good, my teacher D. Raúl Espinosa asked me "What degree would you like to study at the University?", and I replied "Computer Engineering". Without any doubt, he told me "Man, your study methodology is shit. You must change it if you want to survive to the first year of university." He was right, and my marks in math during those two years were horrible. Nevertheless, I learned to be self-critical and to identify when I was doing things wrong. Many thanks, Raúl.

Right after that period, in the year before moving to the university, I met one of the best teachers I have ever had: Carmelo. He taught me the best methodology to study any science-related subject. Nowadays, I still use his methodology also for this thesis. And because of that, studying math was not a nightmare anymore; instead, it was a game to be enjoyed. I will teach my students by using the same procedure. It will be an honour.

From the University of Seville, where I started to study Computer Engineering in 2014, I would like to thanks all the professors I had, because I took the best from all of them. In particular, I would like to thank David Ruíz Cortés, since he was the first who believed in me. And I also have to say sorry, since we started working together in big data but I realized I preferred hardwarerelated tasks. I will never forget our first meeting when you told me *"Fight to be the boss and then change every single thing that it is not fair here"*. I am on my way.

In addition, thanks to all my colleagues from the Department of Architecture and Technology of Computers, to which I belong since 2016, for all the advice, both scientist and non-scientist discussions, good and bad moments. You all became my family when I started to spend more than 10 hours per day in the lab. I will take the liberty of mentioning some colleagues who especially have shared more moments with me. Thank you, Ricardo and Antonio, for being good friends, Rafa, Elena, Fernando, Paco, Gabriel, Manuel Domínguez and Manuel Rivas, among others, for sharing with me your experience, and finally Juanma, and Alberto, for the technical support and your predisposition.

Although I tried to work in a small company, refusing my dream of working at the university, I felt that was not my place. It would be impossible to be the person who I am today without the confidence of Alejandro Linares Barranco, Ángel Jiménez Fernandez, who also are my supervisors, and Juan Pedro Domínguez Morales, who is my friend, my mentor, and the guy with who I would go to hell. Thank you very much Alejandro for giving me the opportunity to make my dream come true, letting me learn thousands of things at the best research centres and with the best researchers. In addition, thank you very much Ángel for being my inspiration and my reference, for supporting me and for being my friend. Both Alejandro and you have been the persons in charge to train me, and all my appreciation goes to you.

However, I have been able to write those lines because of Juan Pedro. Man, we have walked around in Manchester, Bielefeld, Berlin, Paris, Capo Caccia, Cádiz, and Seville. We have cried, we have worked during weekends and holidays... But the most important thing, you have remembered me to not give up. Thank you very much for everything. I would need half of this thesis just for mentioning every single thing you have helped me or shared with me.

During the years I have been PhD. student, I have travelled a lot. It is still incredible for me how much I have learned from all the places I have visited. I would say that I have learned more from every single visit rather than from the whole PhD. itself. The first event I attended as a PhD. student was to the Capo Caccia Neuromorphic Workshop in 2017. Two important events occurred there which were decisive for my career: 1) it was the first time I saw the iCub robot from the Istituto Italiano di Tecnologia; at that moment, I thought "I have to work with this robot"; 2) I met amazing people there who nowadays are great researchers and friends. I would like to say thanks to Charlotte Frenkel, Tim Walther, Alessandro Aimar, Enea Ceolini, Stefano Buccelli, Elisa Donati, James Knight, Moritz Milde, and Giacomo Pedretti for sharing with me those awesome two weeks. And also for saving my life during the "red wine saturation" episode.

There was only one problem at that moment: my English level was not enough to share my thoughts. The "English problem" was solved by Franca Oldenburg, our English teacher at the beginning, our best friend now. I could not be writing this document in English without your help. Thank you for being such a nice person, teacher, and friend.

Regarding to working with the iCub robot, the path was longer. I had the great opportunity to do a research visit to the SpiNNaker group at the University of Manchester, led by Professor Steve Furber, in 2017. I could work with Robert

James, Qiam Liu, Garibaldi Pineda Garcia, Gabriel Fonseca Guerra, Luís Plana, Andrew Rowley, Michael Hopkins, Alan Stokes and Simon Davidson. Thank you very much for letting me feel like a part of your team. Special mention to Jesko Meißel, one of my flatmates in Manchester, for opening my mind.

The most important turning point for my PhD. was in 2018, when I attended to the Barcelona Cognition, Brain and Technology Summer School. After the good experience in Capo Caccia, I attended to this summer school with high expectations. Once there, I realized it was not a neuromorphic summer school, instead the main topic was more focused on neuroscience. For those two weeks, several work groups were created, but I could not find any work group related to my research topic. Then, it happened: Adrián Fernández Amil told me about the sound localization procedure in humans, and I got fascinated. Thank you very very much for that conversation, it redirected my research topic. Furthermore, I met amazing people there: Joan, Diletta, Valeria, Giampiero, Jordi, Álvaro, and María. To all of you: thank you very much! You changed my file.

Right after the summer school, I went to Bielefeld to collaborate with the group of Prof. Elisabetta Chicca for two weeks. My good friend Tim Walther was working there, and he made it much easier. Thanks for the AquaFitness classes, for organizing dinners and for the awesome beer testing. Thanks also to Martin for all the good moments and coffee breaks. Especially, I would like to thank Thorben, with whom I have worked hard in different projects, for being such a nice colleague, and to Philipp, for being aware of me and tolerating the pure tone tests in his office. I will never forget the Jalapeños restaurant and its amazing Nachos.

In November 2018, Prof. Chiara Bartolozzi visited Seville for giving a talk. I met her at Capo Caccia Neuromorphic Workshop in 2017, when she presented a demo using iCub. Different from the Daniel that attended to that workshop, one year and a half later, I had enough knowledge to have a scientist discussion with Chiara. We talked about the possibility to include our neuromorphic audio sensor within the iCub, the potential applications of that, and how much I would like to work with her, her group, and the robot. Today, I can say that it was one of the best decision of my life. Thanks a lot, Chiara, for believing in me since the beginning, for helping me during the visits and for still being my mentor.

I could say that 2019 was my best year in terms of research. I went again to Bielefeld for two weeks, where I started a very nice project with Thorben and Juan Pedro that was afterwards presented at BioCAS conference. I got a fellowship from NEUROTECH for attending to the Capo Caccia Neuromorphic Workshop 2019. This time, both my English usage and my experience in the neuromorphic field were much better. I would like to thank Hector Gonzalez, Lyes Khacef, Arren Glover, Moritz Milde, Marco Monforte, Giulia D'Angelo, Omar Oubari, Melika Payvand, Ole Richter, Michael Schmuker, Baris Serhan, Beck Strohmer, Pau Vilimelis, Enea Ceolini, and Kathrin Aguilar for everything. We did not know, but that was the last time the contest was going to be held before COVID-19. And it was amazing!

Then, in July 2019 I moved to Genova for three months research visit at the Italian Instituto of Technology, with Prof. Chiara Bartolozzi. The visit would not have been possible without the help and perseverance of Marta Caracalli, who was fighting against the bureaucracy of both institutions. Thank you very much Marta for your help, your determination, and for your perfect Spanish. Also, thanks for being such a nice friend. And the project would not have been successfully finished without the help of Arren Glover, thanks to his advice and technical support, Maurizio Casti, available 24\7 for anything (thanks for the gifts after each visit!), Massimiliano Iacono and Marco Monforte, for making every single task easier, and Chiara Bartolozzi, for her support and useful advice.

But the biggest thing I got from that visit was the people I met there: my best friend Dennis, with who I lived one of the best summers ever, still remembering our last techno party in Milan; Ander, sharing hundreds of beers; again Marco and Massi, for all the hours we have spent together in the lab; Simon, Elisa, Viola, Shuman, Elena, Simeon, Ella, Giuseppe, Prashanth, Giulio, Damiano, Luca, Leandro, Juan, Raquel, Fabrizio, Christopher, Marlena, Guido, Tommaso, Virginia, and many more. You guys are my Italian family. Thank you very much.

On the personal side, I have a clear idea of the list of things I would like to thank. To the thousands of litters of coffee, for keeping me awake when I had too much work, and to the hundreds of litters of Jägermeister, for letting me forget all the bad moments. To Spotify, for 40000 minutes of music every year, providing me from techno music to classic music. To Steam, for stealing me hundreds of hours playing videogames instead of doing research. To Overleaf, for turning my account to the PRO version to write these lines after they felt my pain. To my friends, for remembering me every single day that I could be working in a big company earning a lot of money instead of doing shitty research.

And finally, to my family, my parents Isidoro and Regla, my brother Rubén, and my dog Arturo, for giving me their unconditional love and support, and for understanding all the sacrifices I did during these last five years. And especially to the persons I loved and love, for all the time separated by too many kilometres and the long conversations through video calls in which you all pushed me to keep working.

I know that this acknowledgements section has become longer, but both this thesis document and the current version of myself would not be possible and make no sense without every single person or situation mentioned in these lines. Thank you all for everything. You all made my life better.

#### Contents

| De | eclara             | ation of | Authorship        |                                    | iii |

|----|--------------------|----------|-------------------|------------------------------------|-----|

| Al | ostra              | ct       |                   |                                    | v   |

| Ac | Acknowledgements v |          |                   |                                    |     |

| I  | Th                 | esis     |                   |                                    | 1   |

| 1  | Intr               | oductio  | on                |                                    | 3   |

|    | 1.1                | Motiv    | ation             |                                    | 4   |

|    | 1.2                | Neuro    | omorphic engineer | ing                                | 7   |

|    |                    | 1.2.1    | Taking inspiratio | n from the nervous system          | 9   |

|    |                    | 1.2.2    | From biology to e | engineering                        | 13  |

|    | 1.3                | The se   | ense of hearing . |                                    | 20  |

|    |                    | 1.3.1    | Auditory system   | in biology                         | 20  |

|    |                    |          | 1.3.1.1 The ear   |                                    | 21  |

|    |                    |          | 1.3.1.1.1         | Outer ear                          | 21  |

|    |                    |          | 1.3.1.1.2         | Middle ear                         | 22  |

|    |                    |          | 1.3.1.1.3         | Inner ear                          | 23  |

|    |                    |          |                   | y ascending pathway                | 28  |

|    |                    |          | 1.3.1.2.1         | Cochlear nuclei                    | 30  |

|    |                    |          | 1.3.1.2.2         | Superior Olive                     |     |

|    |                    |          | 1.3.1.2.3         | Inferior colliculus                |     |

|    |                    | 1.3.2    |                   | of the auditory system on circuits | 39  |

|    |                    |          |                   | al cochleae                        | 41  |

|    |                    |          | 1.3.2.1.1         | Lyon's model                       |     |

|    |                    |          | 1.3.2.1.2         | Lyon & Katsiamis' model            |     |

|    |                    |          | 1.3.2.1.3         | Analog cochleae                    |     |

|    |                    |          | 1.3.2.1.4         | Digital cochleae                   | 47  |

| 2  | Obi                | ectives  |                   |                                    | 53  |

| _  | 2.1                | Objec    |                   |                                    | 53  |

|    | 2.2                | ,        |                   |                                    | 55  |

| 2 | One        |                | a Nauromorphic Auditory Sancor                     | 57       |

|---|------------|----------------|----------------------------------------------------|----------|

| 3 | 3.1        |                |                                                    | 57<br>57 |

|   | 3.1<br>3.2 |                |                                                    | 57<br>58 |

|   | 3.2        | 3.2.1          |                                                    | 50<br>59 |

|   |            | 3.2.1          | 0                                                  | 59<br>59 |

|   |            | 3.2.2<br>3.2.3 |                                                    | 60       |

|   |            | 3.2.3<br>3.2.4 | 1                                                  | 60<br>61 |

|   | 3.3        | NASI           |                                                    | 62       |

|   | 3.3        | 3.3.1          |                                                    | 62<br>62 |

|   |            | 3.3.2          |                                                    | 63       |

|   |            | 3.3.3          |                                                    | 66       |

|   |            | 3.3.4          | 0 1                                                | 72       |

|   | 3.4        |                |                                                    | 76       |

|   | 5.4        | TI GA          | vs. Asic                                           | 10       |

| 4 | Eve        | nt-base        | d models for the sound source localization task    | 79       |

|   | 4.1        | Introd         | luction                                            | 79       |

|   | 4.2        | Event          | -based model of the Superior Olivary Complex 8     | 81       |

|   |            | 4.2.1          | Implementing the Cochlear nucleus                  | 82       |

|   |            | 4.2.2          |                                                    | 88       |

|   |            |                | 4.2.2.1 Jeffress model implementation overview 8   | 88       |

|   |            |                | 4.2.2.2 Coincidence detector neuron model          | 89       |

|   |            |                | 4.2.2.3 Delay line model                           | 91       |

|   |            |                |                                                    | 93       |

|   |            |                | 4.2.2.5 Medial Superior Olive model                | 96       |

|   |            | 4.2.3          | 1                                                  | 02       |

|   |            | 4.2.4          |                                                    | 04       |

|   |            | 4.2.5          | Integrating NAS and SOC: The Neuromorphic Auditory |          |

|   |            |                | Complex                                            | 04       |

|   |            | 4.2.6          |                                                    | 08       |

|   |            |                |                                                    | 10       |

|   |            |                | 4.2.6.2 How does the frequency affect?             |          |

|   |            |                |                                                    | 15       |

|   |            | 4.2.7          |                                                    | 18       |

|   | 4.3        | Altern         |                                                    | 19       |

|   |            | 4.3.1          | The Time Difference Encoder model                  |          |

|   |            | 4.3.2          | Time Difference Encoder model implementation 12    |          |

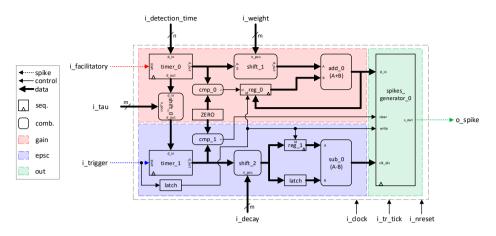

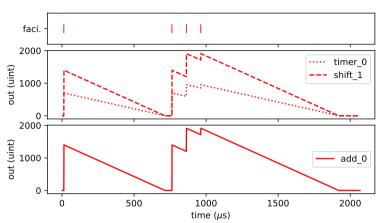

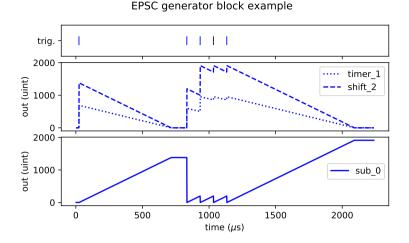

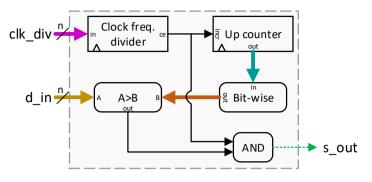

|   |            |                | 4.3.2.1 Gain-generator block                       |          |

|   |            |                | 4.3.2.2 EPSC-generator block                       |          |

|   |            |                | 4.3.2.3 Spike-generator block                      |          |

|   |            | 4.3.3          | Analysis and results                               |          |

|   |            |                | 4.3.3.1 Simulation                                 | 33       |

4.3.3.2FPGA implementation1414.3.4Real-time neuromorphic application1444.3.5Conclusion1474.4Comparison between both approaches148

| 5  |      |         |            | o applications for robotics                      | 151 |

|----|------|---------|------------|--------------------------------------------------|-----|

|    | 5.1  |         |            |                                                  |     |

|    | 5.2  | Motiva  |            | cases of use                                     |     |

|    |      | 5.2.1   | NeuroPo    | od: from audio to locomotion through spiking CPG |     |

|    |      |         | 5.2.1.1    | The hexapod robot                                | 154 |

|    |      |         | 5.2.1.2    | Hardware setup: bi-direction communication       |     |

|    |      |         |            | between an FPGA and SpiNNaker in real-time       | 157 |

|    |      |         | 5.2.1.3    | Spiking Central Pattern Generator                | 158 |

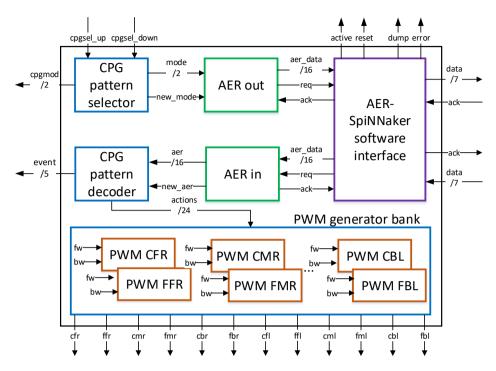

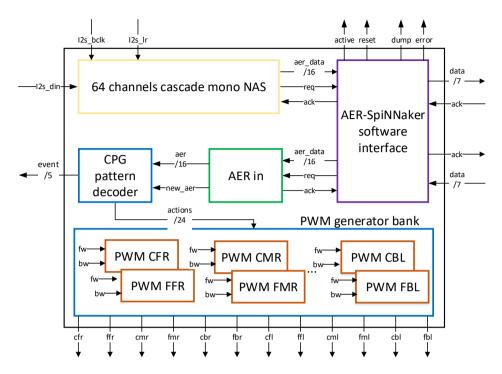

|    |      |         | 5.2.1.4    | NeuroPod HDL top module architecture             | 160 |

|    |      |         | 5.2.1.5    | Simulation results                               |     |

|    |      |         | 5.2.1.6    | Towards an audio-guided behavior                 | 167 |

|    |      | 5.2.2   | Audio-v    | isual sensory integration                        | 173 |

|    |      |         | 5.2.2.1    | Problem to solve                                 | 173 |

|    |      |         | 5.2.2.2    | Bio-inspired solution                            | 174 |

|    |      |         | 5.         | 2.2.2.1 Optical Flow Encoder Network (OFE)       | 174 |

|    |      |         | 5.         | 2.2.2.2 Sound Source Direction Network (SSD) .   | 175 |

|    |      |         | 5.         | 2.2.2.3 Sensory Integration Network (SI)         |     |

|    |      |         | 5.2.2.3    | Hardware setup                                   |     |

|    |      |         | 5.2.2.4    | Simulation test and results                      | 178 |

|    |      |         | 5.2.2.5    | First steps to a closed-loop system              | 180 |

|    |      | 5.2.3   |            | orphic implementation of auditory perception in  |     |

|    |      |         | the iCub   | robotic platform                                 |     |

|    |      |         | 5.2.3.1    | The iCub robot                                   |     |

|    |      |         | 5.2.3.2    | Hardware integration of the NAC                  |     |

|    |      |         | 5.2.3.3    | Software integration of the NAC                  | 191 |

|    |      |         | 5.2.3.4    | Implementing an auditory perception application  |     |

|    |      |         |            | in real-time                                     |     |

|    |      |         | 5.2.3.5    | Datasets, tests, and preliminary results         |     |

|    | 5.3  | Is it w | orth to do | the effort?                                      | 211 |

| 6  | Con  |         |            | ure works                                        | 213 |

|    | 6.1  |         |            |                                                  |     |

|    | 6.2  | Future  | e works .  |                                                  | 216 |

| 7  | Bibl | iograpl | hy         |                                                  | 217 |

|    |      |         |            |                                                  |     |

| II | A    | opend   | ices       |                                                  | 237 |

| Α  | Ope  | nNAS    | software   | tool                                             | 239 |

|    |      |         |            | ens summary                                      | 239 |

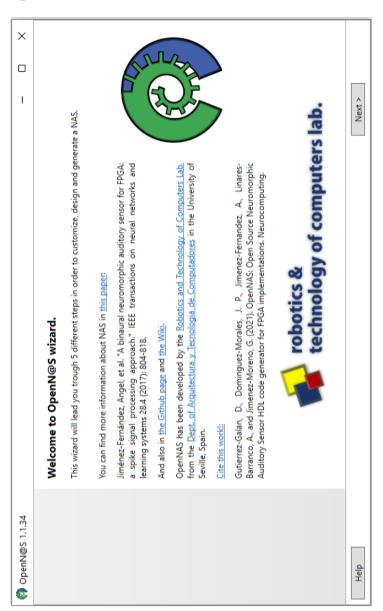

|    |      | A.1.1   |            | AS welcome screen                                |     |

|    |      | A.1.2   |            | AS common settings screen                        |     |

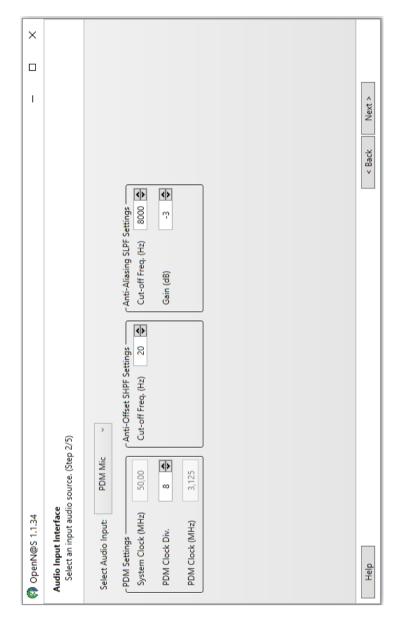

|    |      | A.1.3   |            | AS input interface screen                        |     |

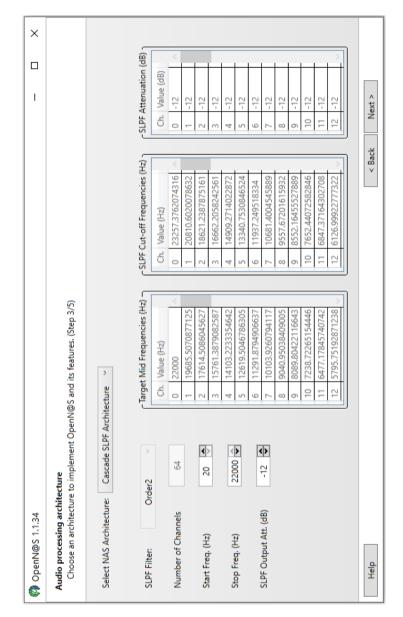

|    |      | A.1.4   | OpenNA     | AS processing architecture screen                | 243 |

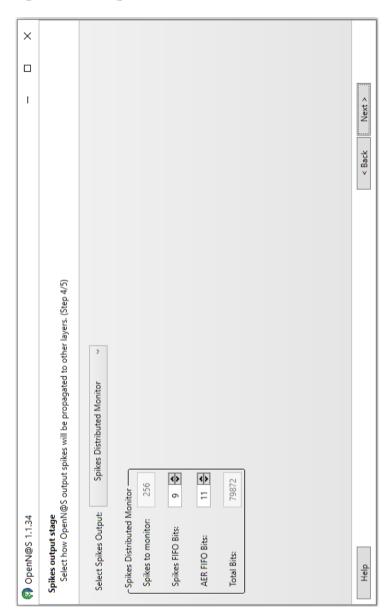

|   |     | A.1.5                                    | OpenNAS output interface screen                                                                                                                                                                                                                                                                                                                                                                    | 4                          |

|---|-----|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

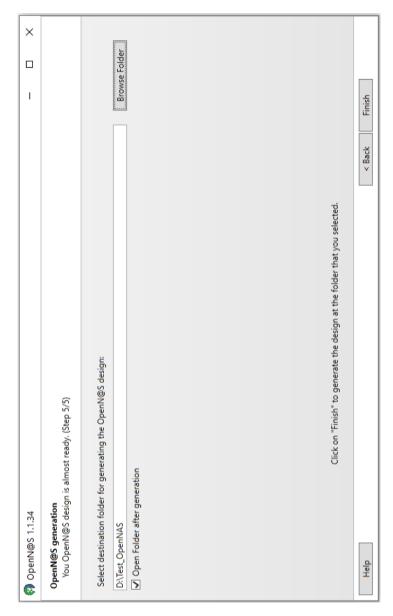

|   |     |                                          | OpenNAS destination folder screen                                                                                                                                                                                                                                                                                                                                                                  |                            |

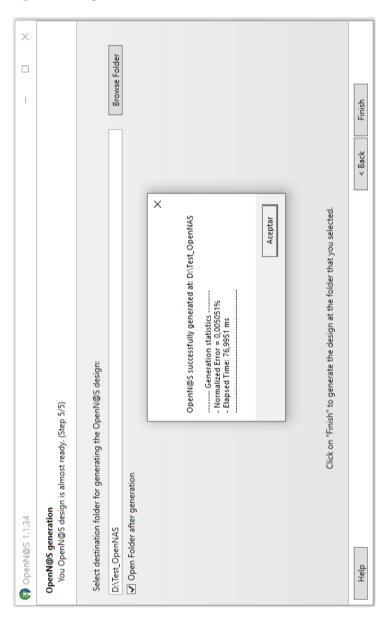

|   |     |                                          | OpenNAS generation success screen                                                                                                                                                                                                                                                                                                                                                                  |                            |

| B | NAS | SIC test                                 | 24 <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                    | 7                          |

|   | B.1 | NASI                                     | C test PCB files                                                                                                                                                                                                                                                                                                                                                                                   | 7                          |

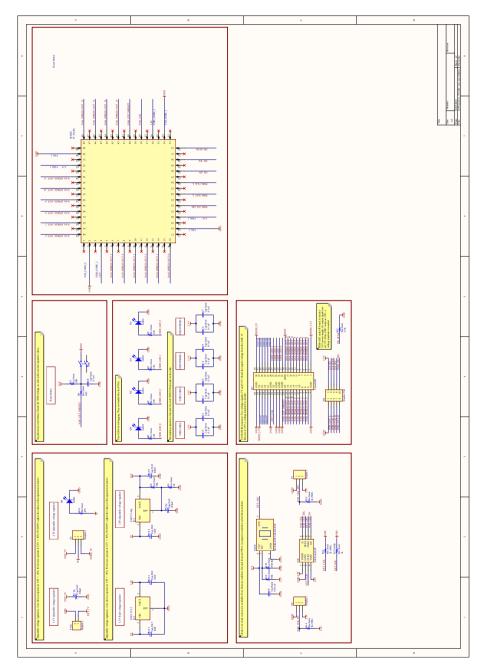

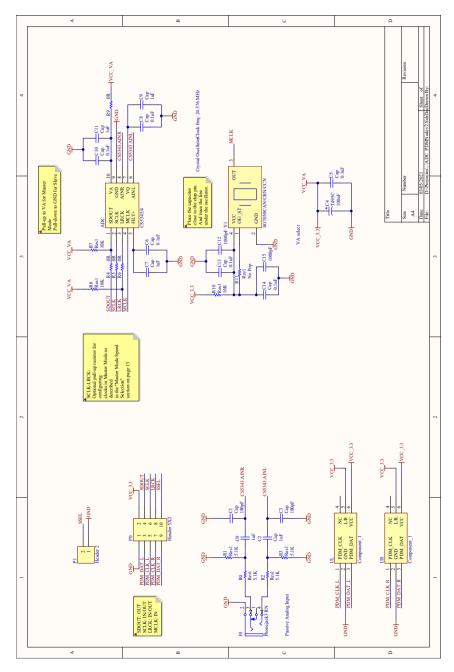

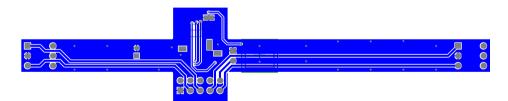

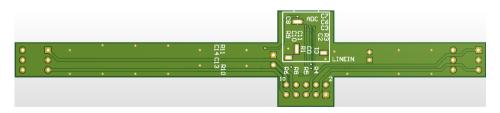

|   |     | B.1.1                                    | Schematic: NASIC_test_pcb.SchDoc                                                                                                                                                                                                                                                                                                                                                                   | 8                          |

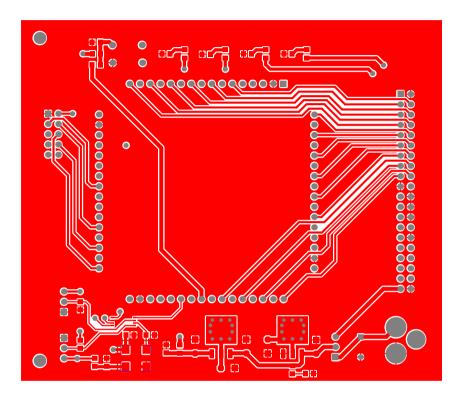

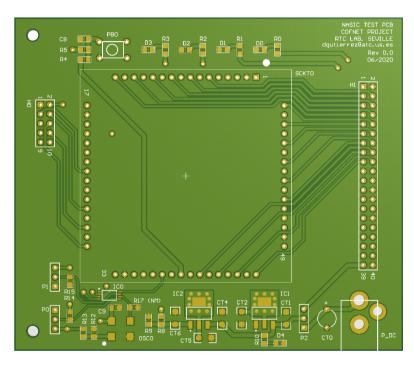

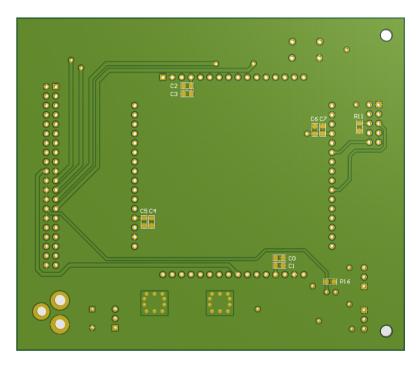

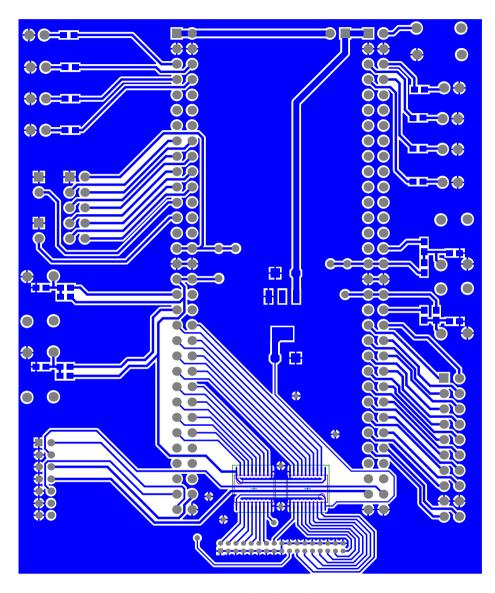

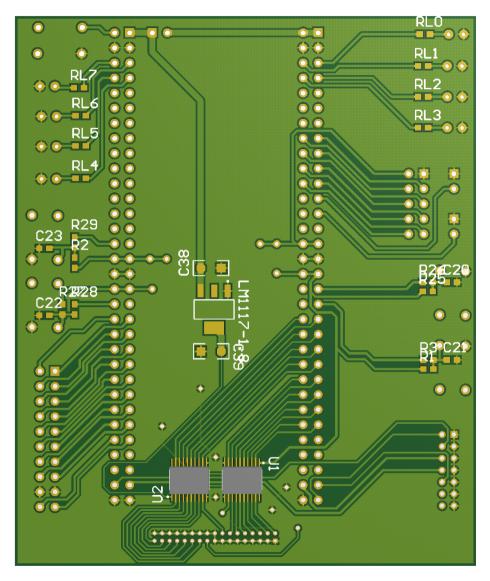

|   |     | B.1.2                                    | Board top: NASIC_test_pcb.PcbDoc                                                                                                                                                                                                                                                                                                                                                                   |                            |

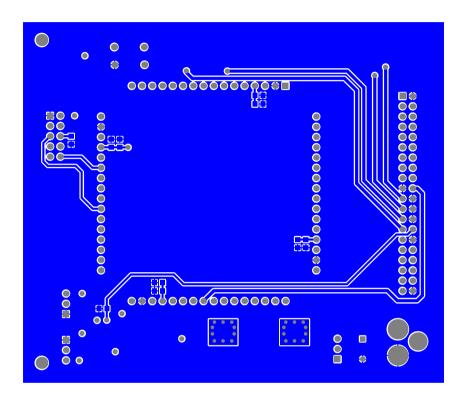

|   |     | B.1.3                                    | Board bottom: NASIC_test_pcb.PcbDoc                                                                                                                                                                                                                                                                                                                                                                |                            |

|   |     |                                          |                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

| C | Gen | eric pu                                  | rpose PCBs 25                                                                                                                                                                                                                                                                                                                                                                                      | 3                          |

| C |     |                                          | rpose PCBs       25         PDM microphones board PCB files       25                                                                                                                                                                                                                                                                                                                               | -                          |

| C |     |                                          | PDM microphones board PCB files                                                                                                                                                                                                                                                                                                                                                                    | 3                          |

| C |     | ADC-                                     | PDM microphones board PCB files                                                                                                                                                                                                                                                                                                                                                                    | 3<br>4                     |

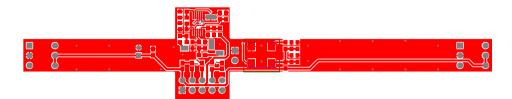

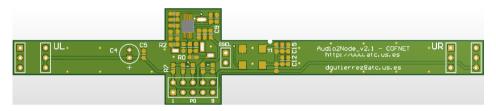

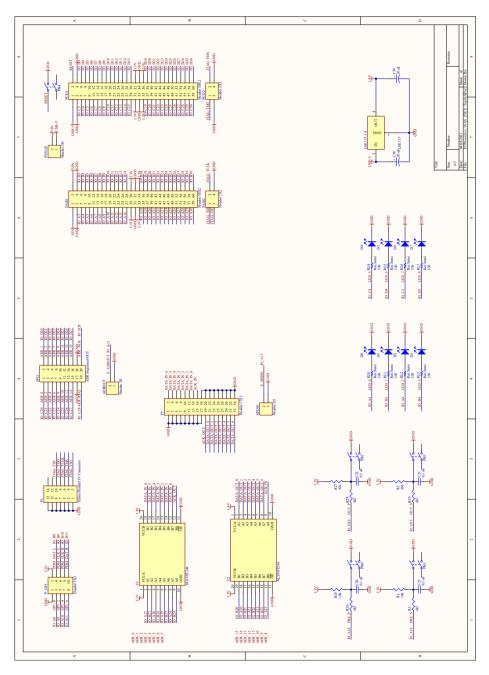

| C |     | ADC-1<br>C.1.1                           | PDM microphones board PCB files                                                                                                                                                                                                                                                                                                                                                                    | 3<br>4<br>5                |

| С | C.1 | ADC-1<br>C.1.1<br>C.1.2<br>C.1.3         | PDM microphones board PCB files       250         Schematic: ADC_PDM_mic_board.SchDoc       250         Board top: ADC_PDM_mic_board.PcbDoc       250                                                                                                                                                                                                                                              | 3<br>4<br>5<br>5           |

| С | C.1 | ADC-1<br>C.1.1<br>C.1.2<br>C.1.3         | PDM microphones board PCB files       250         Schematic: ADC_PDM_mic_board.SchDoc       250         Board top: ADC_PDM_mic_board.PcbDoc       250         Board bottom: ADC_PDM_mic_board.PcbDoc       250         Board bottom: ADC_PDM_mic_board.PcbDoc       250                                                                                                                            | 3<br>4<br>5<br>5<br>6      |

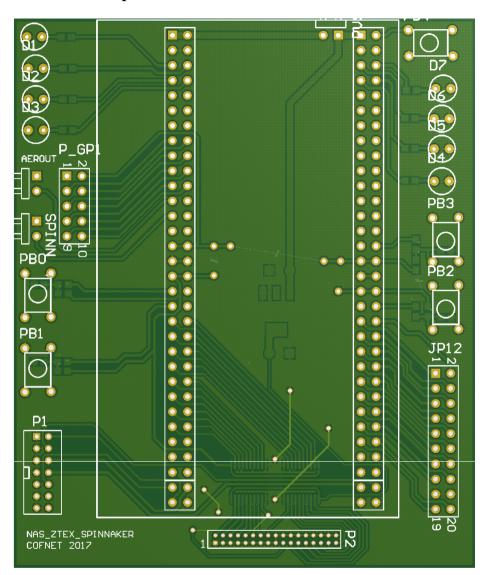

| С | C.1 | ADC-1<br>C.1.1<br>C.1.2<br>C.1.3<br>ZTEX | PDM microphones board PCB files       250         Schematic: ADC_PDM_mic_board.SchDoc       250         Board top: ADC_PDM_mic_board.PcbDoc       250         Board bottom: ADC_PDM_mic_board.PcbDoc       250         Board bottom: ADC_PDM_mic_board.PcbDoc       250         251       251         Board bottom: ADC_PDM_mic_board.PcbDoc       250         2013 base board PCB files       250 | 3<br>4<br>5<br>5<br>6<br>7 |

# List of Figures

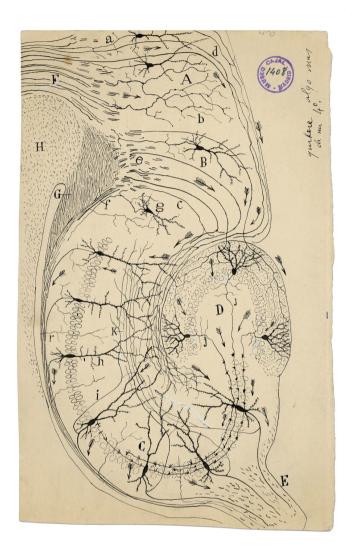

| 1.1   | Cajal's drawing of neurons in the hippocampus, a region of the       |    |

|-------|----------------------------------------------------------------------|----|

|       | brain important to memory.                                           | 10 |

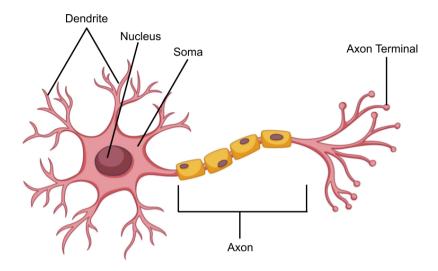

| 1.2   | Simplified neuron anatomy.                                           | 11 |

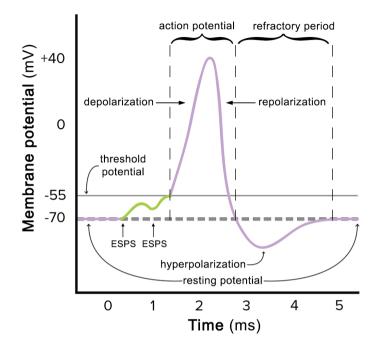

| 1.3   | Diagram of a spike generated by a neuron (taken from                 |    |

|       | (Domínguez Morales, 2018))                                           | 12 |

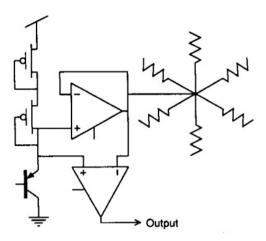

| 1.4   | Schematic of pixel circuit from the Mahowald retina model (taken     |    |

|       | from (Mead, 1990)                                                    | 14 |

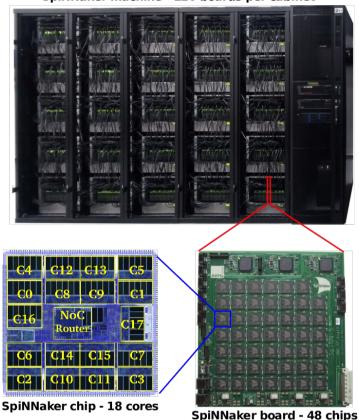

| 1.5   | SpiNNaker machine project from chip to cabinete (taken from          |    |

|       | (Sugiarto et al., 2017)                                              | 16 |

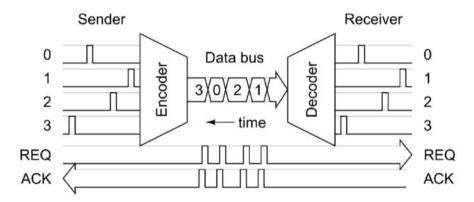

| 1.6   | Transmission of an event using AER representation. Image taken       |    |

|       | from (Lazzaro et al., 1993)                                          | 17 |

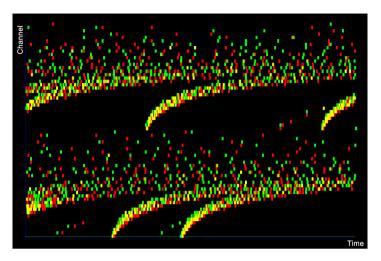

| 1.7   | Screenshot of NAVIS tool.                                            | 19 |

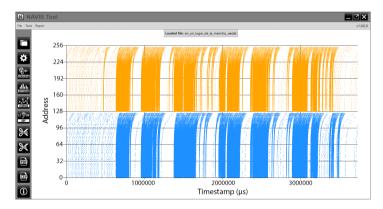

| 1.8   | Main window of NAVIS tool showing the cochleogram of the             |    |

|       | sentence "En un lugar de La Mancha". Blue dots represent the         |    |

|       | output of the left 64-channels, while orange dots represent the      |    |

|       | output for the right channels. Image taken from (Dominguez-          |    |

|       | Morales et al., 2017c)                                               | 19 |

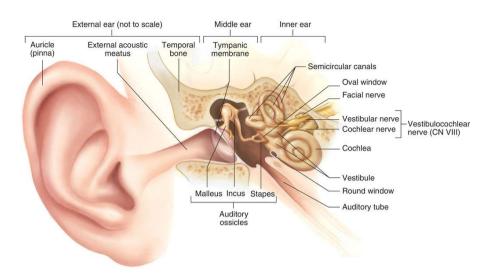

| 1.9   | Anatomy of the ear. Image taken from (Patton et al., 2012)           | 22 |

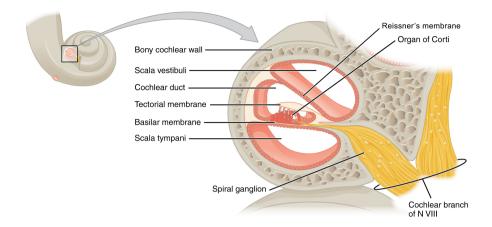

|       | Detailed cross section of the cochlea.                               | 24 |

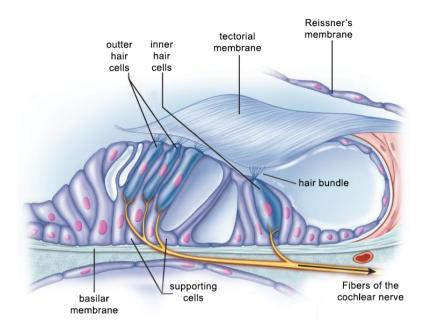

|       | Inner structure of the Organ of Corti.                               | 25 |

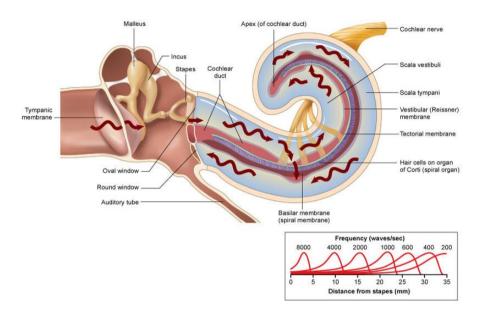

| 1.12  | Effect of sound waves on cochlear structures. Image taken from       |    |

|       | (Patton et al., 2012)                                                | 26 |

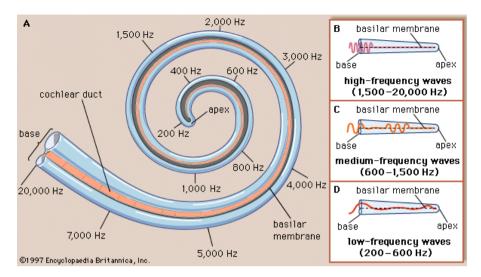

| 1.13  | Tonotopic distribution of the cochlea (A). Localization of high-     |    |

|       | frequency (B), medium-frequency (C) and low-frequency (D)            |    |

|       | responses in the cochlea. Image taken from (Domínguez Morales,       |    |

|       | 2018).                                                               | 27 |

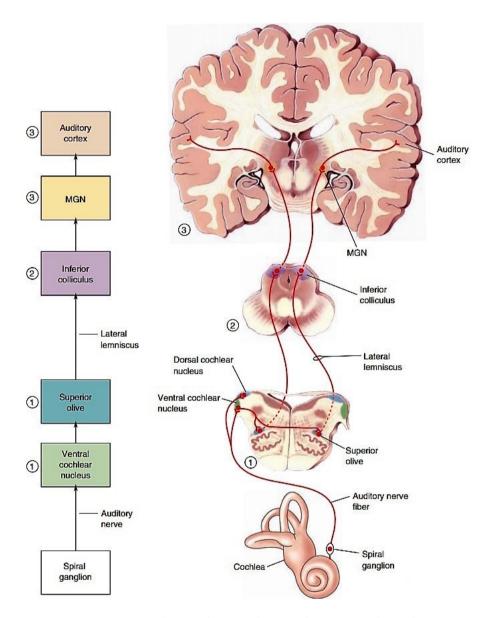

| 1.14  | Ascending Auditory Pathways scheme. Neural signals can               |    |

|       | travel from the spiral ganglion to auditory cortex via numerous      |    |

|       | pathways. Here, a primary pathway is shown schematically (at         |    |

|       | left) and through brain stem cross sections. Notice that only the    |    |

|       | connections from one side are illustrated at right image. Image      | •  |

| 1 4 - | taken from (Bear et al., 2020).                                      | 29 |

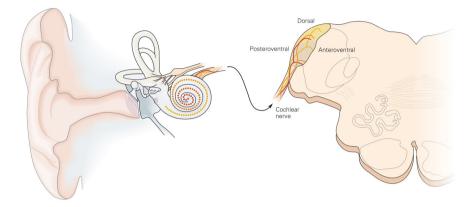

| 1.15  | Cochlear nerve fibers terminate in the dorsal and ventral cochlear   |    |

|       | nuclei in a tonotopic organization. Image taken from (Kandel et al., | 01 |

|       | 2000)                                                                | 31 |

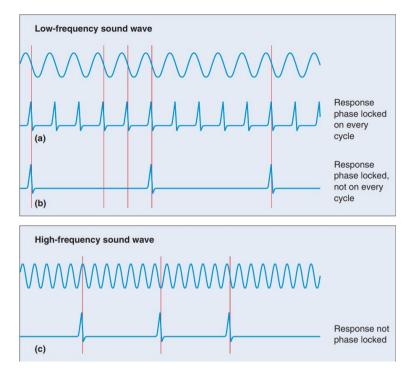

| 1.16 | Phase locking in the response of auditory nerve fibers. Sound at<br>a low frequency can elicit a phase-locked response, either (a) on<br>every cycle of the stimulus or (b) on some fraction of the cycles.<br>(c) At high frequencies, the response does not have a fixed-phase                                                                |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.17 | relationship to the stimulus. Image taken from (Bear et al., 2020)<br>Phase-locked discharges of an auditory nerve fiber (A) and                                                                                                                                                                                                                | 33  |

|      | a spherical bushy cell of the Anteroventral Cochlear Nucleus (AVCN) (B). Image taken from (Schnupp et al., 2011).                                                                                                                                                                                                                               | 34  |

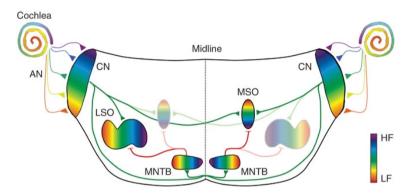

| 1.18 | Schematic drawing of primary auditory sound localization circuits<br>in the mammalian brainstem. Image taken from (Kandler et al.,                                                                                                                                                                                                              |     |

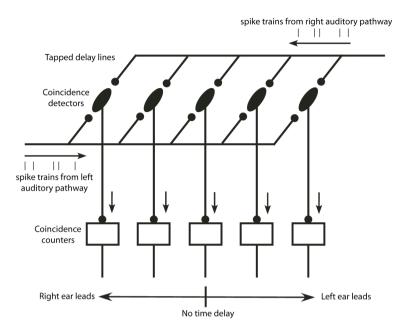

| 1.19 | 2009)                                                                                                                                                                                                                                                                                                                                           | 35  |

|      | counters (rate integrators) of the Jeffress model. Image taken from (Cariani, 2011).                                                                                                                                                                                                                                                            | 36  |

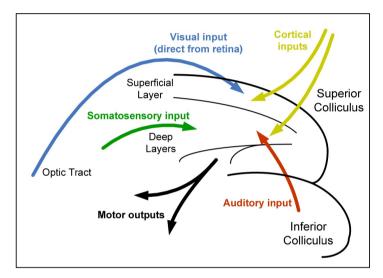

| 1.20 | Sensory and cortical information flows in the Superior Colliculus (SC). The superficial layer of the SC is directly connected to the optic tract, while the deep layers receive auditory (from the inferior colliculus) and somatosensory input. Cortical feedback moderates the processing in the deep layer and influences the motor outputs. |     |

|      | Image taken from (Pavlou and Casey, 2010).                                                                                                                                                                                                                                                                                                      | 38  |

| 1.21 | Historical tree diagram of different artificial cochleae developed.                                                                                                                                                                                                                                                                             |     |

|      | Image taken from (Domínguez Morales, 2018)                                                                                                                                                                                                                                                                                                      | 40  |

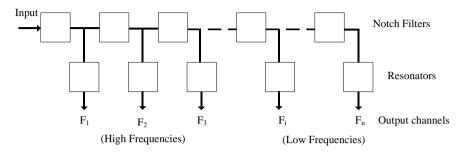

| 1.22 | Lyon's model's cochlea's filters' block diagram. Image taken from (Domínguez Morales, 2018)                                                                                                                                                                                                                                                     | 42  |

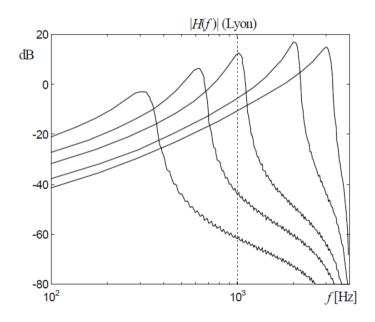

| 1.23 | Frequency response of Lyon's model (64 sections) for the following characteristic frequencies: 3.0, 2.0, 1.0, 0.6 and 0.3 kHz. Image                                                                                                                                                                                                            |     |

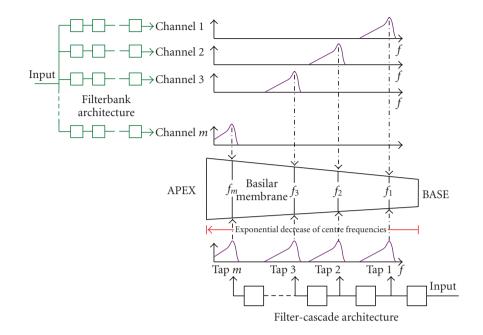

| 1.24 | taken from (Miró Amarante, 2013) Graphical representation of the filterbank and filter-cascade architectures in the Lyon-Katsiamis model. Image taken from                                                                                                                                                                                      | 42  |

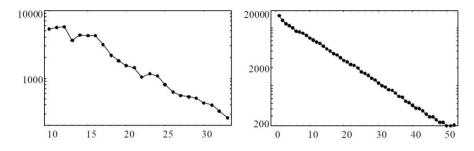

| 1.25 | (Katsiamis et al., 2007)<br>Cutoff frequencies (Hz) distribution in Watts' artificial cochlea<br>(left) and van Schaik's (right). Image taken from (Van Schaik et al.,                                                                                                                                                                          | 44  |

|      | 1996)                                                                                                                                                                                                                                                                                                                                           | 46  |

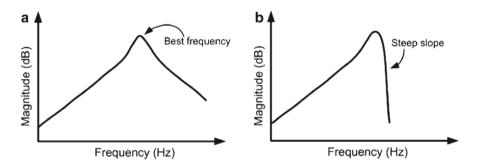

| 1.26 | Frequency response of a second order filter in a parallel topology (a) and in a cascade topology (b). Image taken from                                                                                                                                                                                                                          |     |

|      | (Domínguez Morales, 2018)                                                                                                                                                                                                                                                                                                                       | 46  |

| 1.27 | Block diagram of the digital cochlea proposed by Summerfield et al. Image taken from (Summerfield and Lyon, 1992)                                                                                                                                                                                                                               | 48  |

| 1.28 | Frequency response of the digital cochlea implementation by                                                                                                                                                                                                                                                                                     | -10 |

| -    | Leong et al. Image taken from. Image taken from (Leong et al.,                                                                                                                                                                                                                                                                                  |     |

|      | 2003)                                                                                                                                                                                                                                                                                                                                           | 49  |

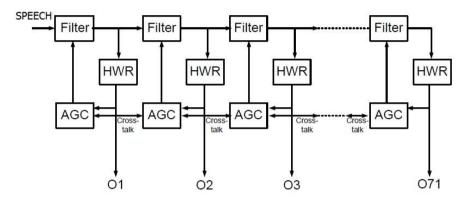

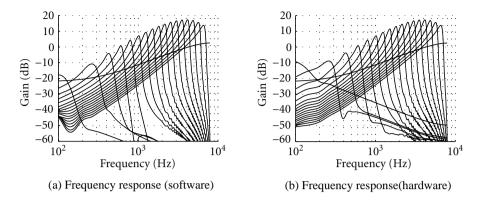

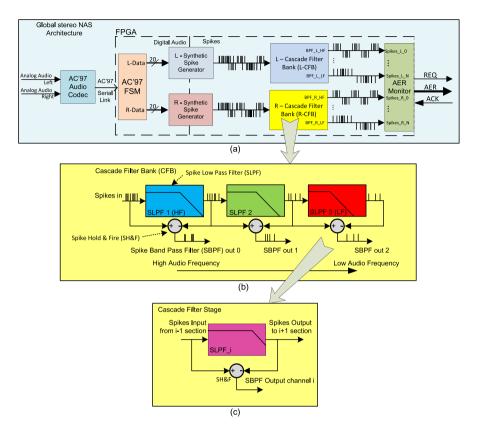

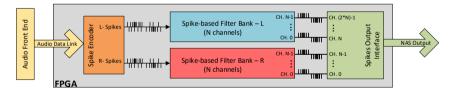

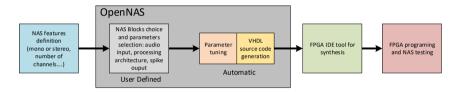

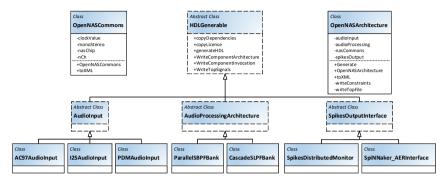

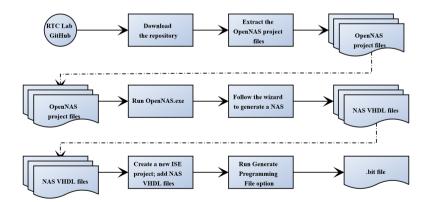

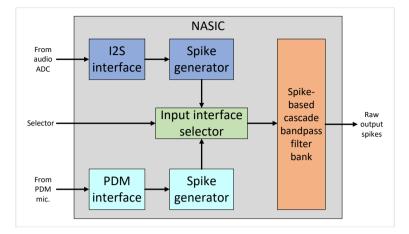

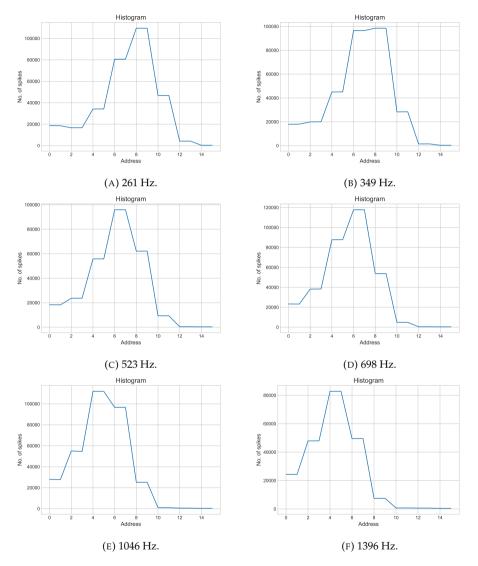

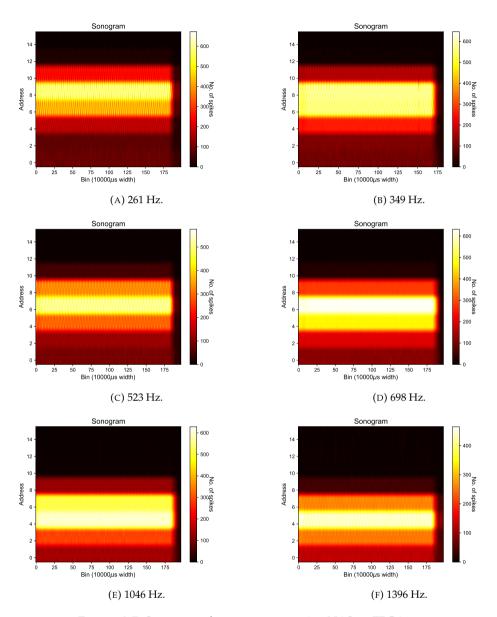

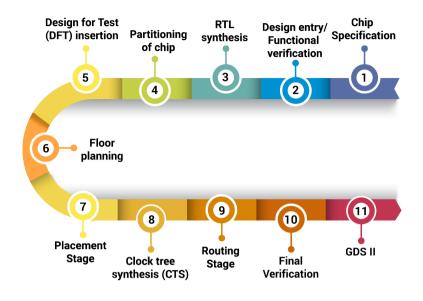

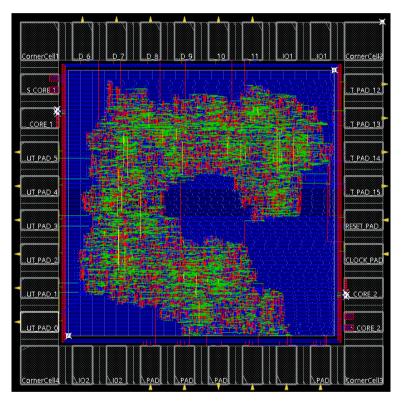

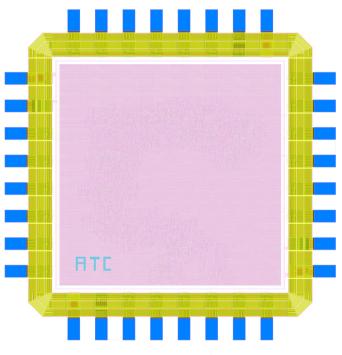

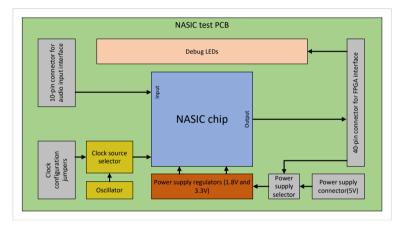

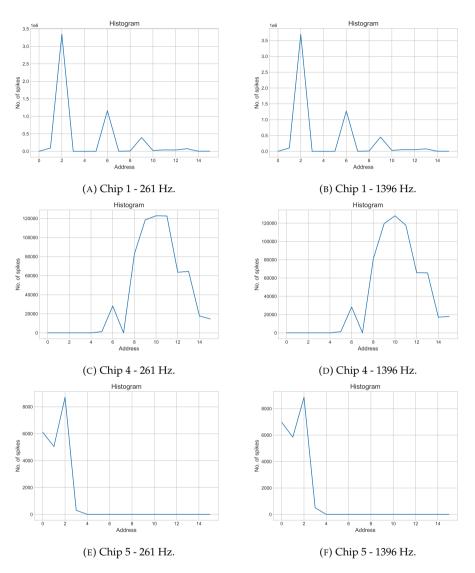

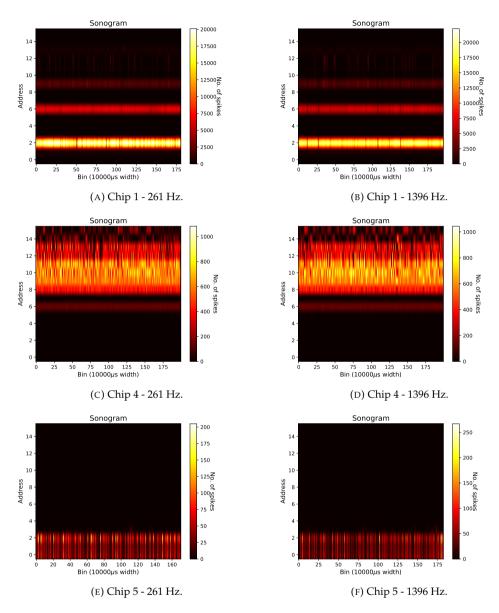

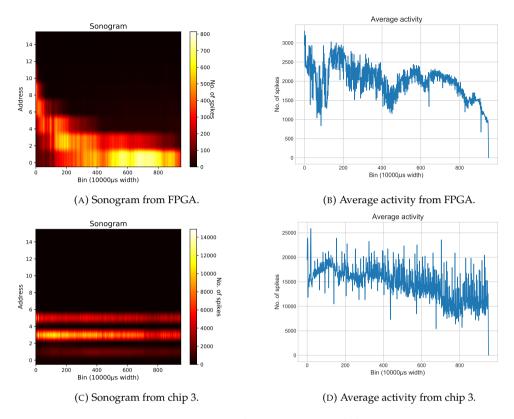

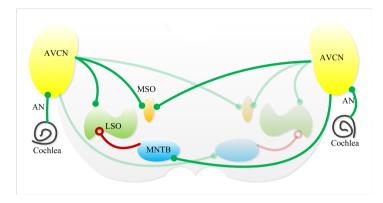

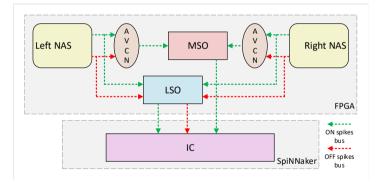

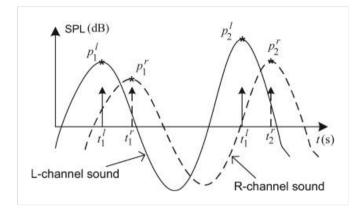

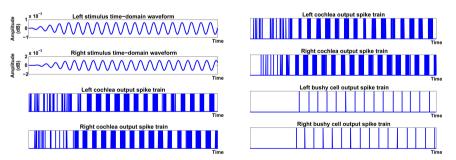

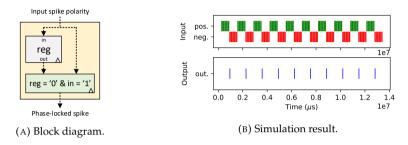

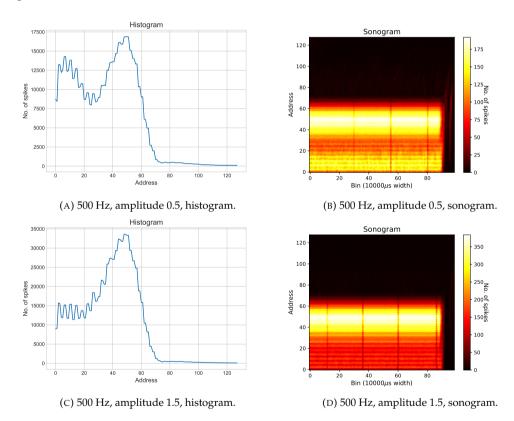

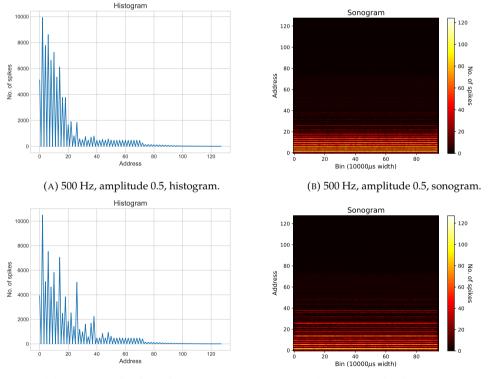

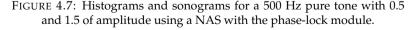

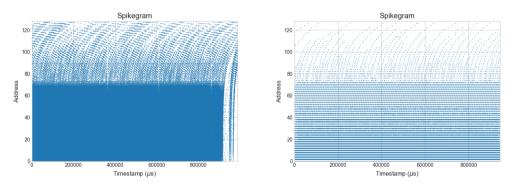

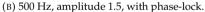

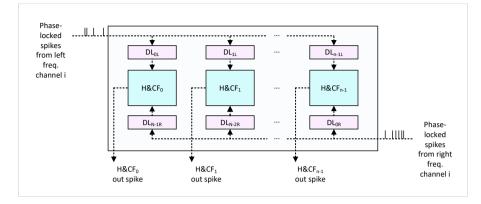

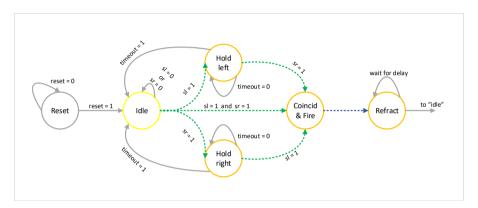

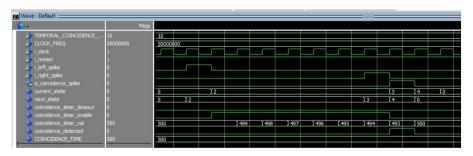

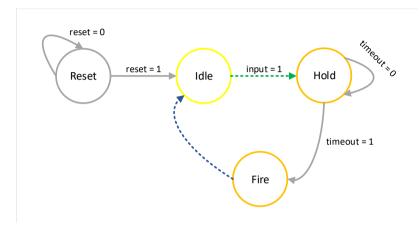

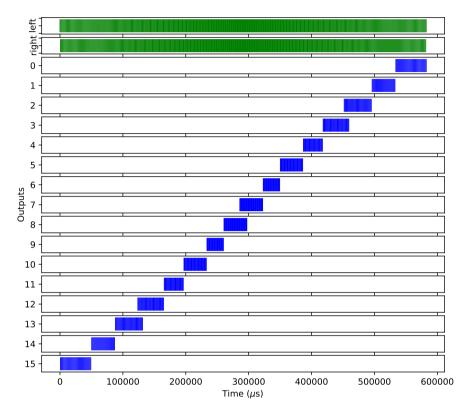

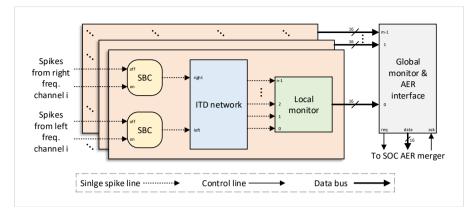

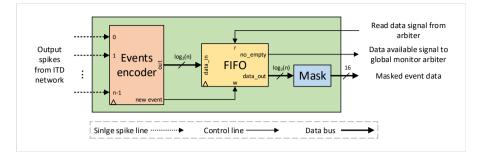

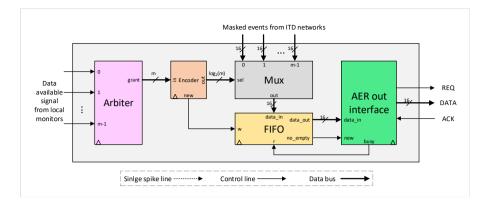

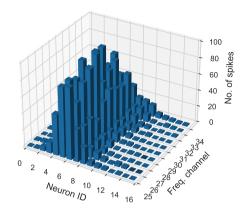

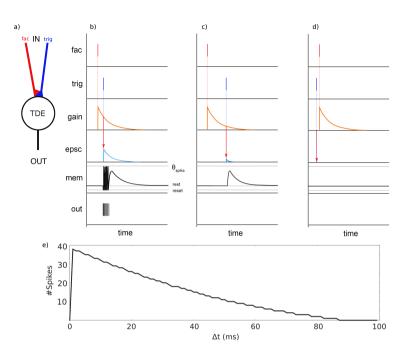

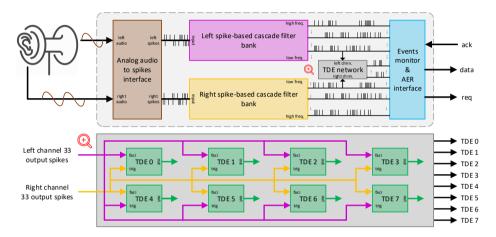

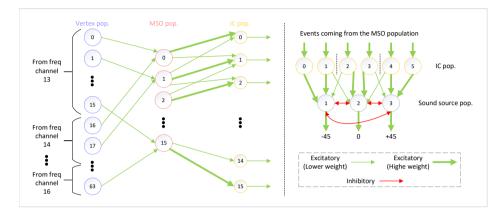

1.29 (a) Global NAS architecture. (b) Filter banks with Cascade topology, CFB. (c) Single CFB stage containing an SLPF and an SH&F. Image taken from. Image taken from (Jimenez-Fernandez 51 Block diagram of the complete architecture of a binaural 3.1 Neuromorphic Auditory Sensor (NAS). 58 Design flow diagram for full NAS synthesis. 3.2 59 OpenNAS class diagram. 3.3 60 OpenNAS tool usage flow. 3.4 61 3.5 NASIC's internal architecture block diagram. 64 Histograms from pure tones using NAS on Field-Programmable 3.6 Gate Array (FPGA). Middle frequencies associated to each frequency channel were: channel 0, 22000 Hz; channel 1, 8090 Hz; channel 2, 2975 Hz; channel 3, 1094 Hz; channel 4, 402 Hz; channel 5, 148 Hz; channel 6, 54 Hz; and channel 7, 20 Hz. 65 Sonograms from pure tones using NAS on FPGA. . . . . . . . . . 3.7 67 ASIC design workflow. Image taken from https://www. 3.8 68 NASIC cells distribution after the place & route process. 69 3.9 70 3.11 NASIC test Printed Circuit Board (PCB) block diagram. . . . . . . 72 73 3.13 Histograms from pure tones using NASIC. 74 75 77 Superior Olivary Complex in biology. Green lines represents 4.1 excitatory connections, while red lines indicates inhibitory connections. Image taken from (Liu et al., 2013). 80 Block diagram of the NSSOC model for FPGA. 4.2 81 Representation of the phase lock effect. Image taken from (Liu 4.3 et al., 2013)..... 83 4.4 Example of the phase lock effect. 83 4.5 Block diagram and simulation results of the spherical bushy cell 84 Histograms and sonograms for a 500 Hz pure tone with 0.5 and 1.5 4.6 of amplitude using a NAS without phase-lock. 85 Histograms and sonograms for a 500 Hz pure tone with 0.5 and 1.5 4.7of amplitude using a NAS with the phase-lock module. . . . . . . 86 4.8 Examples of recordings using NAS without and with phase-lock. 87 Block diagram of the proposed implementation for the Jeffress 4.9 89 4.10 Finite State Machine (FSM) of the Spike Hold&Coincidence Fire 90

| 4.11  | Simulation results of the SHCF module. States 0, 2, 3,                 |     |

|-------|------------------------------------------------------------------------|-----|

|       | and 4 corresponds to IDLE, WAIT_RIGHT, COINCIDENCE, and                | 01  |

| 4 1 0 | REFRACTORY, respectively.                                              | 91  |

|       | FSM of the Delay Line module.                                          | 92  |

| 4.13  | Simulation results of the Delay Line (DL) module. States 0, 1, and     |     |

|       | 2 to <i>IDLE</i> , <i>HOLD</i> , and <i>FIRE</i> , respectively        | 92  |

| 4.14  | Example of the ITD network when using a sweep                          | 94  |

|       | Block diagram of the proposed MSO model.                               | 97  |

|       | Block diagram of the MSO local events monitor.                         | 98  |

| 4.17  | Block diagram of the MSO global events monitor.                        | 99  |

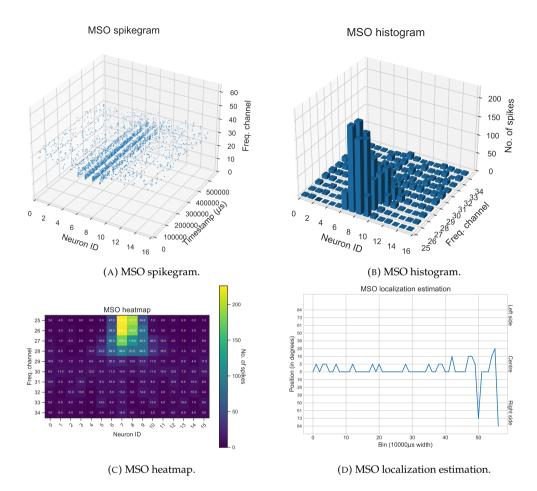

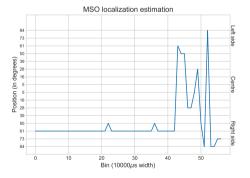

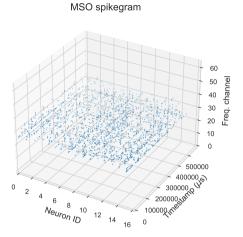

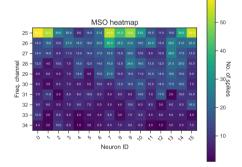

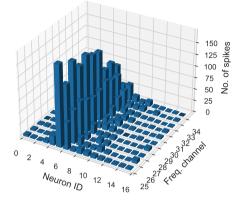

| 4.18  | Results from a behavioral simulation of a Medial Superior Olive        |     |

|       | (MSO) model when using a 1000 Hz pure tone, placed in front            |     |

|       | of the reference, with a distance of 1.5 meters. The plots were        |     |

|       | generated using pyNAVIS                                                | 101 |

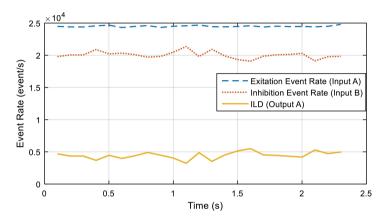

| 4.19  | Interaural Level Difference (ILD) (encoded as an event-rate)           |     |

|       | measured over time obtained from the input data that generates         |     |

|       | the left and right NAS when the sound source is placed at 45° from     |     |

|       | the head. Figure taken from (Cerezuela-Escudero et al., 2018).         | 103 |

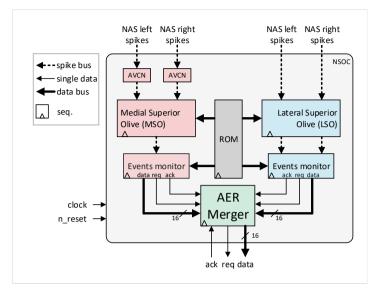

| 4.20  | Block diagram of the proposed SOC module.                              | 105 |

|       | Block diagram for the integration between the NAS model and the        | 100 |

| 1.21  | SOC model.                                                             | 106 |

| 4 22  | Event package format.                                                  |     |

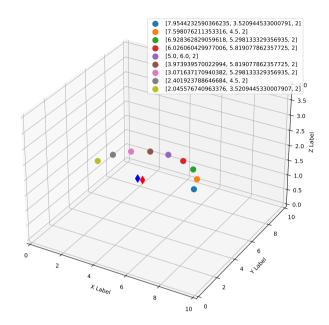

|       | Virtual room created for testing the Neuromorphic Auditory             | 100 |

| 1.20  | Complex (NAC). Diamond shape indicates the microphones pair,           |     |

|       | where blue diamond correspond to the left microphone and red           |     |

|       | diamond correspond to the right microphone. Therefore, sound           |     |

|       | sources are placed in front of the microphones pair. The sound         |     |

|       |                                                                        | 100 |

| 4 0 4 | source 0 is the one placed completely on the right.                    | 109 |

|       | Comparison between different configurations of the MSO.                |     |

|       | Frequency comparison using model 2.                                    |     |

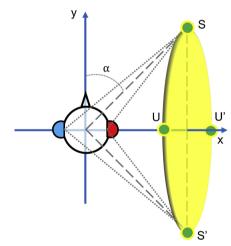

|       | Concept of cone of confusion. Figure taken from (Risoud et al., 2018). |     |

|       | Effect of the cone of confusion for model 2.                           | 117 |

| 4.28  | Theoretical behavior representation of the Time Difference Encoder     |     |

|       | (TDE) model based on the model proposed by Milde et al.(Milde          |     |

|       | et al., 2018). a) TDE schematic with facilitatory (fac) and trigger    |     |

|       | (trig) input and spiking output. b) Case one: A small positive time    |     |

|       | difference between facilitatory and trigger spikes leads to a high     |     |

|       | number of output spikes (out). c) Case two: large positive time        |     |

|       | difference leads to no output spikes. d) Case three: A negative time   |     |

|       | difference leads to no output spikes. e) Number of TDE output          |     |

|       | spikes in dependency of time difference $\Delta t$ between two input   |     |

|       | events (gain: gain factor, epsc: exponential postsynaptic current,     |     |

|       | mem: membrane potential).                                              | 121 |

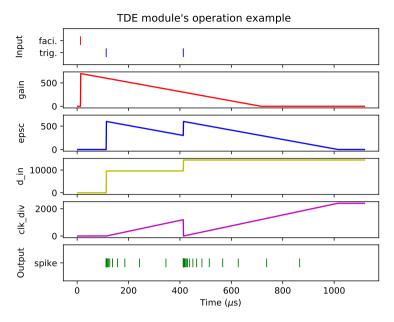

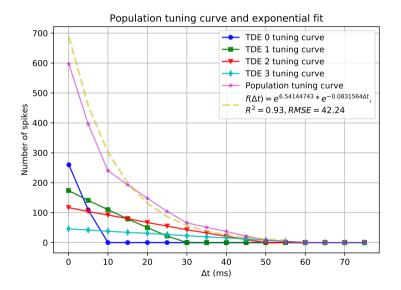

- 4.31 EPSC-generator block output example. First, the model is stimulated with a single facilitatory event before the first trigger event. Then, the current value of *shift\_1* is loaded in *timer\_1*. The accumulative effect is also shown when multiple triggers are received. The *sub\_0* module generates an increasing signal, which is used as the clock divider value for the spike generator block. . . 129

- 4.34 Register-Transfer Level (RTL) simulation for twelve basic cases of the TDE model with a time resolution of microseconds. Red, blue, and green are related to facilitatory, trigger, and spike generator, respectively.

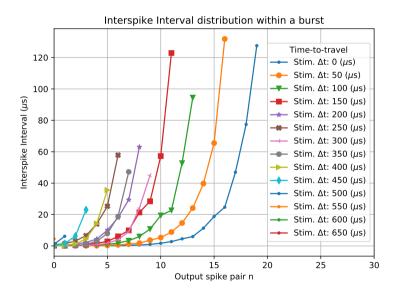

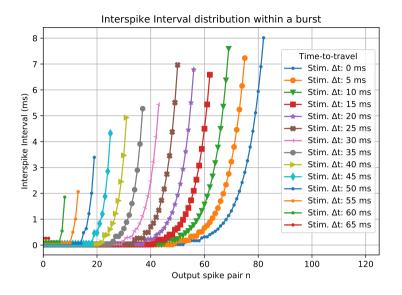

| 4.35 | TDE Interspike Interval (ISI) response for a facilitatory-trigger pair with different $\Delta t$ values for a microseconds resolution configuration. Note that the smallest $\Delta t$ value used was not zero |            |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

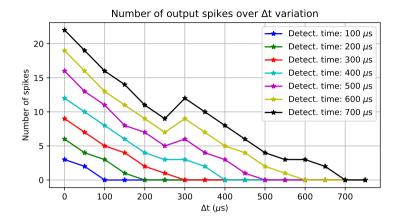

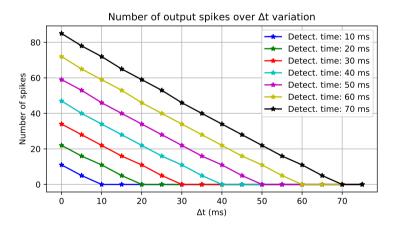

| 4.36 |                                                                                                                                                                                                                | 136        |

| 4.37 | ms                                                                                                                                                                                                             | 137        |

| 4.38 | time reference tick                                                                                                                                                                                            | 138        |

| 4.39 | time reference tick                                                                                                                                                                                            | 138        |

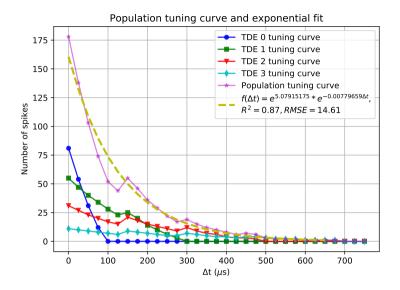

| 4.40 | microseconds time reference tick                                                                                                                                                                               | 140<br>140 |

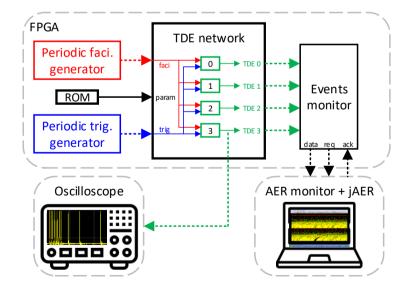

| 4.41 | Block diagram of the setup for real-time measurements acquisition.                                                                                                                                             | 140        |

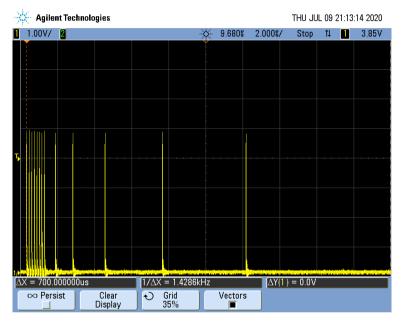

| 4.42 | Output spikes captured by using an oscilloscope                                                                                                                                                                | 142        |

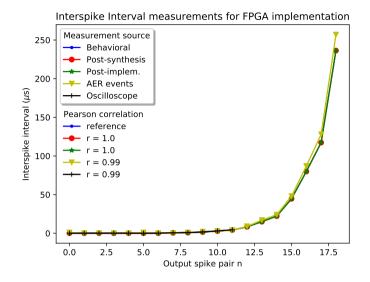

| 4.43 | Comparing the TDE response from different measurement sources.                                                                                                                                                 | 143        |

| 4.44 | Detailed block diagram of the FPGA top module for the proof-of-                                                                                                                                                |            |

|      | concept, containing both the NAS and the TDE populations                                                                                                                                                       | 145        |

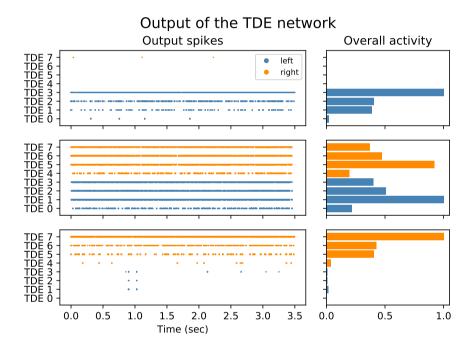

| 4.45 | Raster plot of the output events from the TDE population and                                                                                                                                                   |            |

|      | normalized overall activity. The plots were generated using                                                                                                                                                    |            |

|      | pyNAVIS tool (Dominguez-Morales et al., 2021b). TDEs 0 to 3 (left                                                                                                                                              |            |

|      | population) correspond to indexes 0 to 3 in 4.8, and TDEs 4 to 7                                                                                                                                               |            |

|      | (right population) also correspond to indexes 0 to 3 in the same                                                                                                                                               |            |

|      | table. Therefore, TDE 0 and TDE 4 use the same configuration and                                                                                                                                               |            |

|      | so on                                                                                                                                                                                                          | 146        |

| 5.1  | An octopus-inspired soft robotic arm. Credit: Harvard SEAS                                                                                                                                                     | 151        |

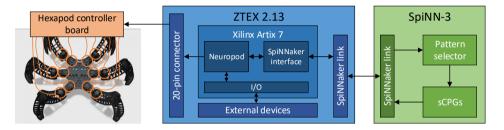

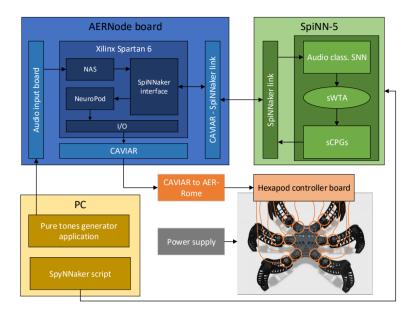

| 5.2  | Block diagram of the entire system. It is composed of the<br>SpiNNaker board, an FPGA-based board, and a 3D-printed                                                                                            | 101        |

|      | hexapod robot frame.                                                                                                                                                                                           | 155        |

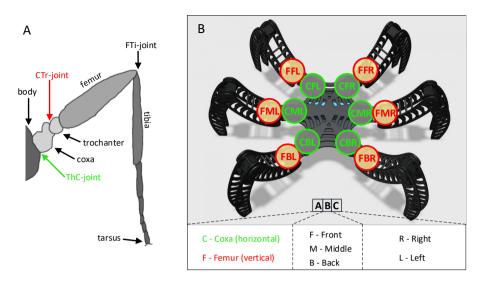

| 5.3  | A) Biological representation of an arthropod's leg anatomy. B)                                                                                                                                                 |            |

|      | Hexapod robot leg actuator IDs                                                                                                                                                                                 | 156        |

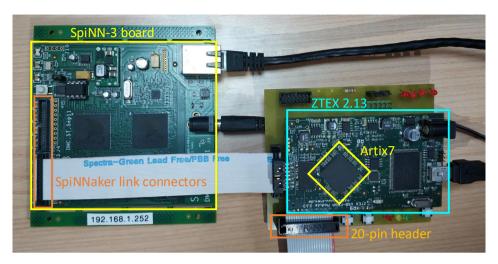

| 5.4  | SpiNN-3 machine and ZTEX 2.13 board.                                                                                                                                                                           | 158        |

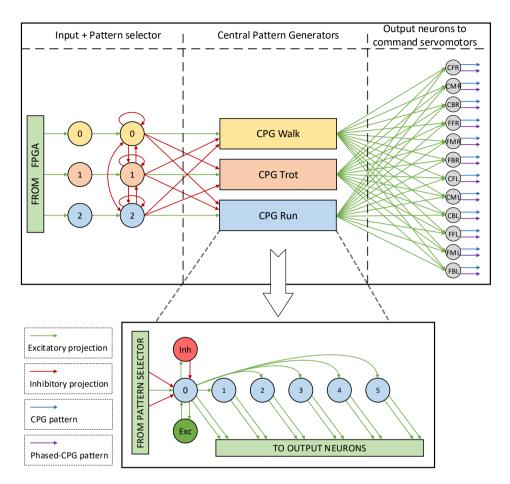

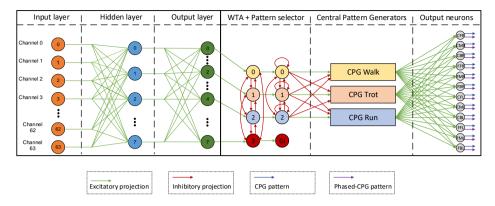

| 5.5  | Diagram of the spiking neural network model used (top) with an                                                                                                                                                 |            |

|      | in-depth view of the CPG architecture (bottom).                                                                                                                                                                | 159        |

| 5.6  | •                                                                                                                                                                                                              | 161        |

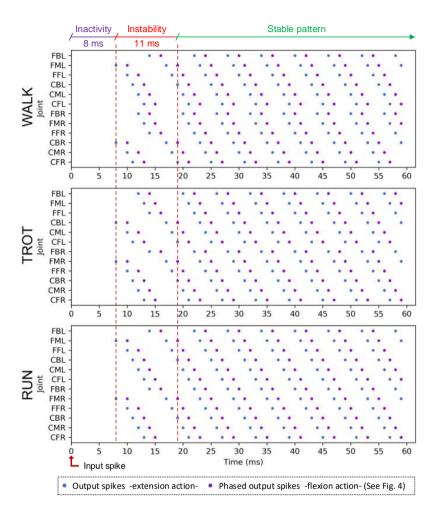

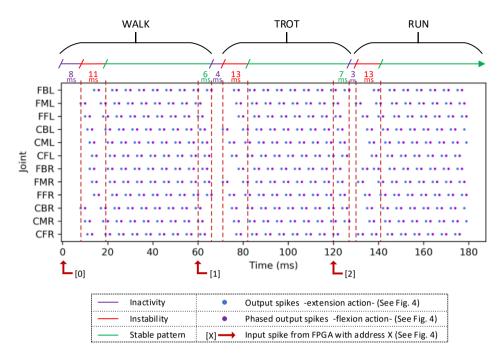

| 5.7  | Output spikes for each gait pattern simulated on SpiNNaker                                                                                                                                                     |            |

| 5.8  | Output spikes from the SpiNNaker simulations that show the gait                                                                                                                                                |            |

|      | pattern change behavior.                                                                                                                                                                                       | 164        |

| 5.9  | Block diagram of the updated NeuroPod system. It is composed of                                                                                                                                                |            |

|      | the SpiNNaker board, implementing different networks, an FPGA-                                                                                                                                                 |            |

|      | based board, in which the NAS was deployed, and a 3D-printed                                                                                                                                                   |            |

|      | hexapod robot frame.                                                                                                                                                                                           | 168        |

|      | -                                                                                                                                                                                                              |            |

|              | Audio-guided NeuroPod FPGA top module overview.                                                                             | 169   |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|-------|

| 5.11         | Diagram of the complete spiking neural network model used for                                                               |       |

|              | the audio-guided NeuroPod. This network is composed of several                                                              | 4 = 0 |

| F 10         | sub-networks, where each of them has a specific task.                                                                       |       |

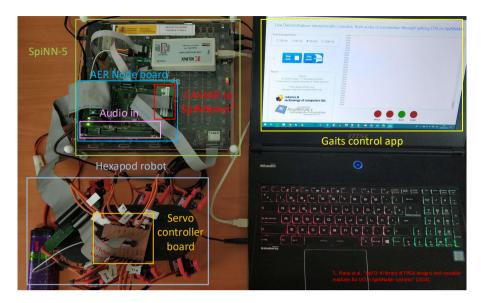

|              | Audio-guided NeuroPod hardware setup.                                                                                       | 171   |

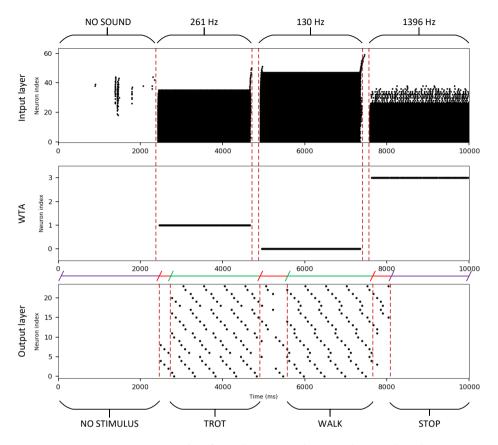

| 5.13         | Output spikes from the SpiNNaker simulations that show the gait                                                             | 170   |

| <b>F</b> 1 4 | pattern change behavior according to the input auditory stimuli.                                                            | 172   |

| 5.14         | The autonomous robot navigates through a cluttered environment.                                                             | 174   |

| F 1 F        | It tries to reach a sound source while avoiding obstacles.                                                                  | 174   |

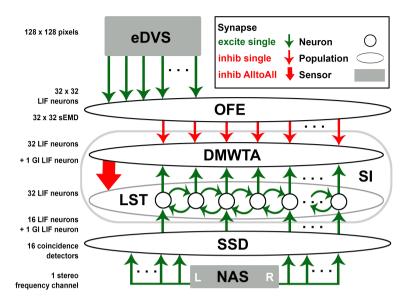

| 5.15         | Complete network. The Optical Flow Encoder (OFE) population                                                                 |       |

|              | consists of the SPatio-Temporal Correlation (SPTC) Leaky                                                                    |       |

|              | Integrate-And-Fire (LIF) population and the spiking Elementary                                                              |       |

|              | Motion Detector (sEMD) population. The Sound Source Direction (SSD) population includes coincidence detector neurons and an |       |

|              | additional hard Winner-Take-All (WTA) network. Each WTA                                                                     |       |

|              | consists of an excitatory LIF neuron population and one Global                                                              |       |

|              | Inhibitory (GI) neuron. All excitatory LIF neurons are connected                                                            |       |

|              | to the GI neuron. The GI neuron projects back onto the excitatory                                                           |       |

|              |                                                                                                                             | 177   |

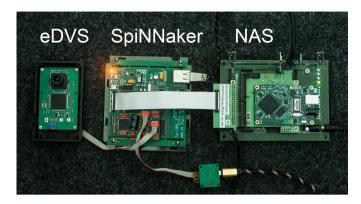

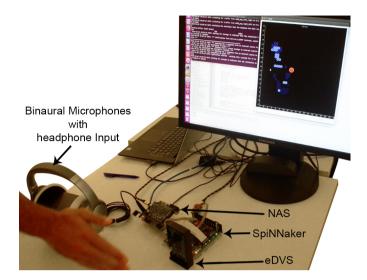

| 5 16         | embedded Dynamic Vision Sensor (eDVS) and NAS feeding spikes                                                                | 177   |

| 0.10         | into a SpiNN-3 board through the SpiNNlink connectors. The                                                                  |       |

|              | eDVS can directly process visual input while the NAS receives                                                               |       |

|              | stereo audio input through an audio jack.                                                                                   | 178   |

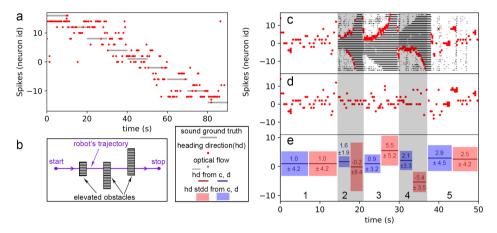

| 5.17         |                                                                                                                             |       |

|              | to a 180 degrees sound source direction sweep. (b) Setup to record                                                          |       |

|              | Optical Flow (OF) data used in Figure 5.17c. An eDVS is mounted                                                             |       |

|              | on top of a robotic platform which drives purely translational with                                                         |       |

|              | a speed of $\sim 0.8$ m/s through the scene. The first obstacle is located                                                  |       |

|              | in the middle of the visual field, the second one on the right side                                                         |       |

|              | and the last one on the left side. All obstacles are positioned at least                                                    |       |

|              | 40 cm above the ground so that the robot can drive underneath                                                               |       |

|              | them. Heading directions for a centered sound source with OF                                                                |       |

|              | (c) and without OF (d). (e) Heading direction mean and heading                                                              |       |

|              | direction standard deviation (stdd) with OF (red) and without OF                                                            |       |

|              | (blue) for five different time periods with different visual scenarios                                                      | 179   |

| 5.18         | Hardware setup for the test scenario with real-time input and static                                                        |       |

|              | sensors' position. The screen shows the response of the system.                                                             |       |

|              | Red dot: heading direction; blue dots: optical flow                                                                         | 181   |

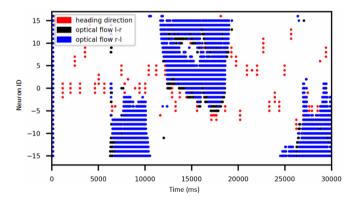

| 5.19         | Output spikes from both the heading direction network and                                                                   |       |

|              | optical flow estimation network for the static hardware setup real-                                                         |       |

|              | time test                                                                                                                   | 181   |

xxi

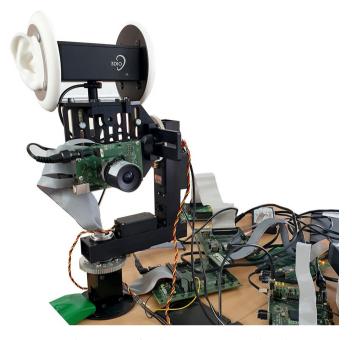

| 5.20         | Hardware setup for the test scenario with real-time input and<br>dynamic sensors' position. It is composed by the Neuromorphic<br>Pan-Tilt-Unit including the Event-Based Camera, Neuromorphic |       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|              | Auditory Sensor with 3DIO Binaural Microphone, and SpiNNaker                                                                                                                                   |       |

| F 01         | board                                                                                                                                                                                          |       |

|              | The iCub robot. Picture taken from (Parmiggiani et al., 2012)                                                                                                                                  | 184   |

| <i>3.</i> 22 | (A) Photograph of the iCub head electronics. (B) Photograph of the iCub head electronics. Pictures taken from (Parmiggiani et al., 2012)                                                       | 186   |

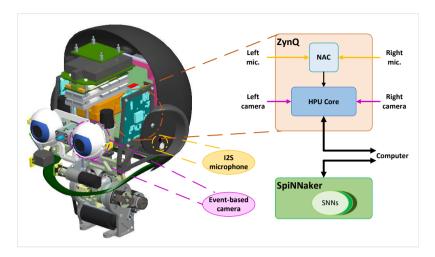

| 5 23         | CAD view of the iCub head components with a block diagram                                                                                                                                      | . 100 |

| 0.20         | of the proposed NAC-iCub integration. CAD picture taken from                                                                                                                                   |       |

|              | (Parmiggiani et al., 2012)                                                                                                                                                                     | 188   |

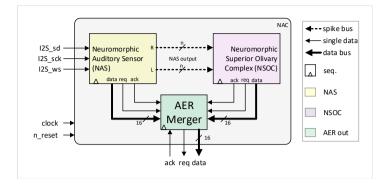

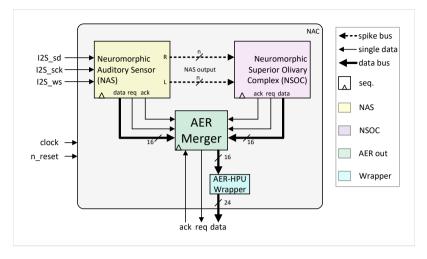

| 5.24         | Block diagram of the NAC model integrated within the iCub                                                                                                                                      |       |

|              | robot. It is based on the one shown in Fig. 4.21, adding just the                                                                                                                              |       |

|              | Address Event Representation (AER)-Head Processing Unit (HPU)                                                                                                                                  |       |

|              | wrapper module.                                                                                                                                                                                |       |

|              | AER-HPU wrapper output event package format.                                                                                                                                                   | 189   |

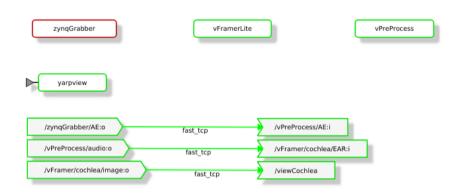

| 5.26         | Yet Another Robot Platform (YARP) modules diagram for the basic                                                                                                                                | 107   |

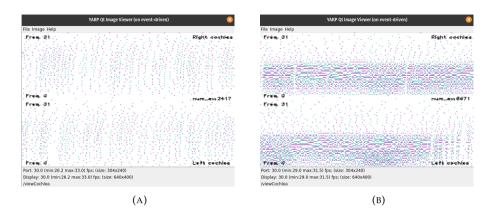

| 5 27         | cochlea visualizer application shown in yarpmanager Cochlea visualizer window showing iCub's auditory events                                                                                   | 192   |

| 5.21         | activity. (A) Events' activity when no sound is played. Those                                                                                                                                  |       |

|              | events correspond to the noise produced by the iCub's fan. (B)                                                                                                                                 |       |

|              | Events' activity when a 500 Hz tone is played.                                                                                                                                                 | 193   |

| 5.28         | Example recording from a woman reading a list of words in front                                                                                                                                |       |

|              | of the iCub robot, with a distance of 0.5 meters. (A) Spikegram. (B)                                                                                                                           |       |

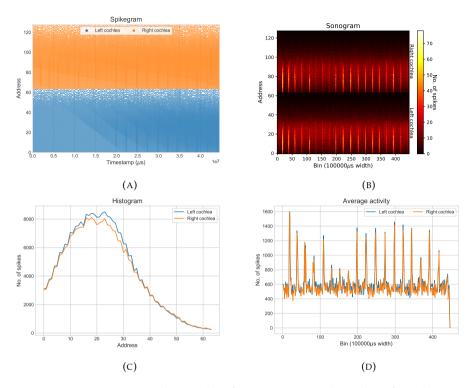

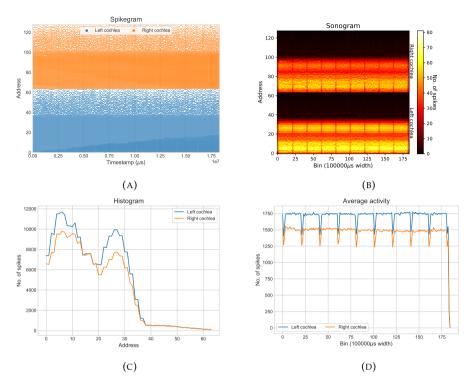

|              | Sonogram. (C) Histogram. (D) Average activity.                                                                                                                                                 | 194   |

| 5.29         | YARP modules diagram for the sound source localization                                                                                                                                         |       |

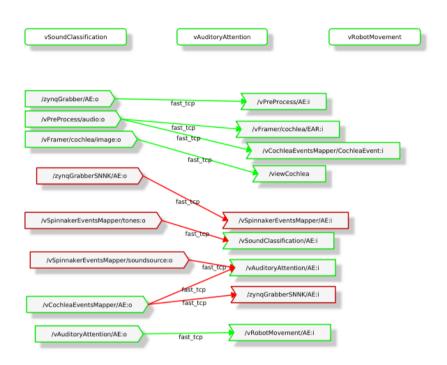

| <b>- 2</b> 0 | application shown in yarpmanager.                                                                                                                                                              |       |

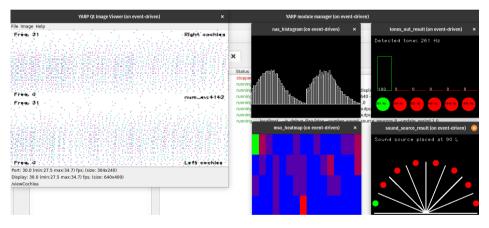

|              | YARP visualizers for the auditory perception model.                                                                                                                                            | 197   |

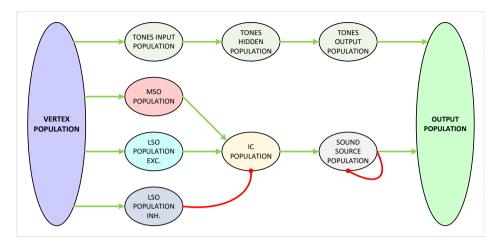

| 5.31         | Overview diagram of the Spiking Neural Networks (SNNs) implemented on SpiNNaker to implement the auditory perception                                                                           |       |

|              | on iCub.                                                                                                                                                                                       | 199   |

| 5.32         | Spiking neural network diagram of the inferior colliculus model                                                                                                                                | 177   |

| 0.02         | implemented on SpiNNaker.                                                                                                                                                                      | 200   |

| 5.33         | NAS response plots for a 523 Hz pure tone placed at the left. (A)                                                                                                                              |       |

|              | Spikegram. (B) Sonogram. (C) Histogram. (D) Average activity                                                                                                                                   | 202   |

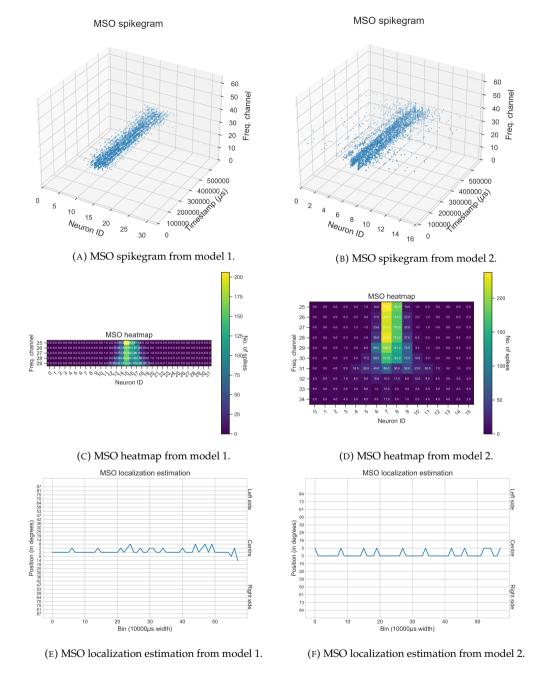

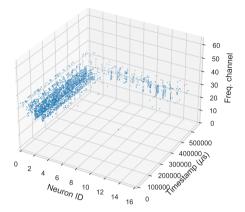

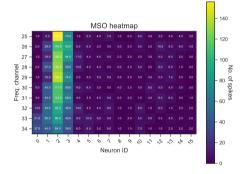

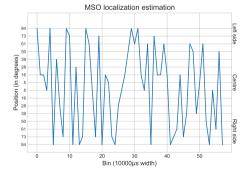

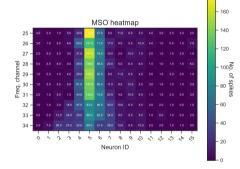

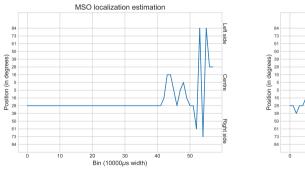

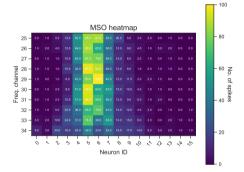

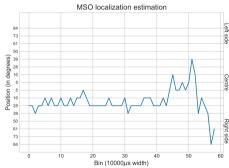

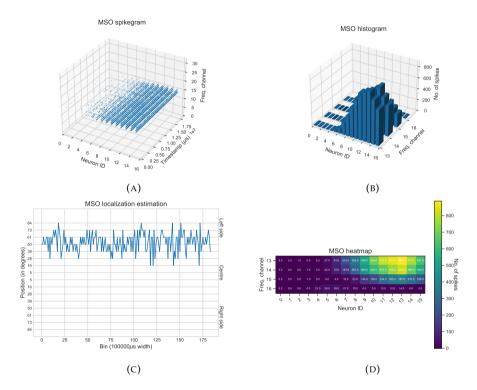

| 5.34         | MSO response plots for a 523 Hz pure tone placed at the left.                                                                                                                                  |       |

|              | (A) MSO spikegram. (B) MSO histogram. (C) MSO localization                                                                                                                                     |       |

|              | estimation. (D) MSO heatmap.                                                                                                                                                                   | 203   |

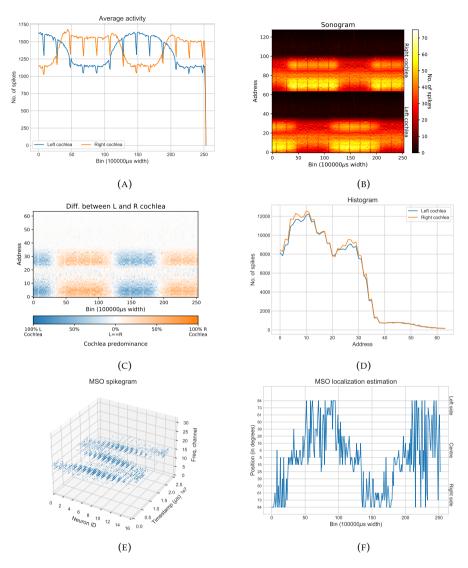

| 5.35         | NAS' response plots (Figs. (Å) Average activity, (B) Sonogram, (C)                                                                                                                             |       |

|              | Difference, and (D) Histogram) and MSO response plots (Figs. (E)                                                                                                                               |       |

|              | MSO spikegram and (F) MSO localization estimation) for a 523 Hz pure tone while moving the iCub head from left to right and back                                                               |       |

|              | with a constant velocity.                                                                                                                                                                      | 207   |

|              |                                                                                                                                                                                                | -07   |

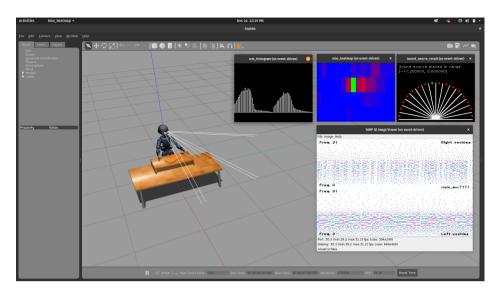

| 5.36 | Screenshot of Gazebo simulator while performing a sound source localization simulation with a virtual neuromorphic iCub and real recordings as input stimuli. | 208 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

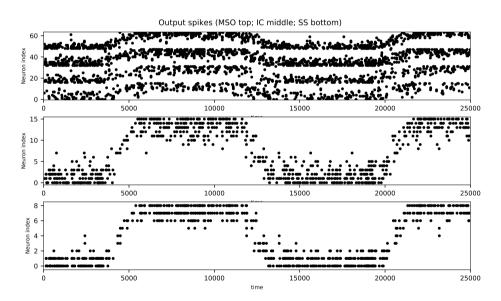

| 5.37 | Output spikes for each gait pattern simulated on SpiNNaker                                                                                                    |     |

|      | OpenNAS tool welcome message.                                                                                                                                 |     |

|      | OpenNAS screen for step 1: common settings                                                                                                                    |     |

|      | OpenNAS screen for step 2: audio input interface                                                                                                              |     |

|      | OpenNAS screen for step 3: audio processing architecture                                                                                                      |     |