# Design and performance analysis of front and back Pi 6 nm gate with high K dielectric passivated high electron mobility transistor

#### Yadala Gowthami, Bukya Balaji, Karumuri Srinivasa Rao

Department of Electronics and Communication Engineering, Koneru Lakshmaiah Educational Foundation, Guntur, India

# Article Info ABSTRACT Article history: Advanced high electron mobility transistor (HEMT) with dual front gate, back

Received Sep 7, 2022 Revised Dec 21, 2022 Accepted Feb 4, 2023

#### Keywords:

Front and back pi gate High K dielectric material Passivation layers Silicon dioxide Technology computer aided design tool Advanced high electron mobility transistor (HEMT) with dual front gate, back gate with silicon nitride/aluminum oxide (Si3N4/Al2O3) as passivation layer, has been designed. The dependency on DC characteristics and radio frequency characteristics due to GaN cap layers, multi gate (FG and BG), and high K dielectric material is established. Further compared single gate (SG) passivated HEMT, double gate (DG) passivated HEMT, double gate triple (DGT) tooth passivated HEMT, high K dielectric front Pi gate (FG) and back Pi gate (BG) HEMT. It is observed that there is an increased drain current (Ion) of 5.92 (A/mm), low leakage current (Ioff) 5.54E-13 (A) of transconductance (Gm) of 3.71 (S/mm), drain conductance (Gd) of 1.769 (S/mm), Cutoff frequency (fT) of 743 GHz maximum oscillation frequency (Fmax) 765 GHz, minimum threshold voltage (Vth) of -4.5 V, on resistance (Ron) of 0.40 (Ohms) at  $V_{qs} = 0$  V. These outstanding characteristics and transistor structure of proposed HEMT and materials involved to apply for upcoming generation high-speed GHz frequency applications.

This is an open access article under the <u>CC BY-SA</u> license.

#### **Corresponding Author:**

Bukya Balaji

Department of Electronics and Communication Engineering, Koneru Lakshmaiah Educational Foundation Guntur, Andhra Pradesh-522502, India Email: vahividi@gmail.com

### 1. INTRODUCTION

In power electronics for the past decades, silicon (Si) is the predominant material and long-established material. Silicon material possesses low saturation velocity and low operating temperature capability for handling power. There is the prerequisite of large current, faster-switching speed, high transconductance, high power density, and high-efficiency requirements for radio frequency (RF) applications [1]. Silicon is limited to reporting these requirements. Gallium arsenide (GaAs), gallium nitride (GaN), indium phosphide (InP), and silicon carbide (SiC) are conventional available wide band gap materials [2]. Comparatively among these materials, GaN has the properties to meet the prerequisite. GaN can be operated at high temperatures, it has a wide band gap, high saturation velocity, and high critical field. For high-power applications, GaN is a suggestable and suitable material [3], [4]. GaN has balancing properties and more advantages compared to Si, SiC, GaN, and GaAs where it can withstand the performance of the transistor [5]. GaN has achieved demand among the other semiconductor materials which is widely used in designing modern electronics and solid-state switches [6]. A narrow channel enables it to work at very high frequencies, providing low noise performance. GaN-based high electron mobility transistor (HEMT) provides a narrow channel [7]. In HEMT two different semiconductor materials with the same lattice constant, and different band gaps are layered on one other. The two-dimensional electron gas (2DEG) is developed at the interface of 2 different materials. Electron mobility

takes place from source to drain. A wide variety of HEMTs are present such as T, gama gate, camel shape gate (CG), multiple grating field plate (MGFP), gate field plate (GFP), discrete field plate (DFP) gate based MOS-HEMT. Early breakdown effects, Leakage current, and short channel effect are the limitation of the existing transistor. In the Pi gate, GaN HEMT also small leakage current, and dynamic power losses are present across the Schottky gate.

For the existing HEMT to improve the characteristics of the device GaN layers, front Pi gate, and back Pi gate are incorporated [8]. These cap layers passivation layers provide sealing the first layer of HEMT structure from external atmospheric fluctuations [9]. The proposed high K dielectric FG and BG HEMT overcomes the limitation of dual gate HEMT and exhibits optimized HEMT Structure which gives optimistic DC and RF characteristics [10]. The results show that high K dielectric FG and BG HEMT results improved on current, trans conductance, drain conductance, maximum oscillation frequency, improved Cutoff frequency, with reduced leakage current [11]. In this structure GaAs, GaN, InP, and SiC can meet the improved performance parameters compared to conventional HEMT. Among these materials, GaN has high saturation velocity, high wideband gap, and high critical field properties. Therefore, Gallium Nitride HEMT structure is suitable for low power applications.

To overcome these effects existing convention transistors are modified. For the existing HEMT to improve the characteristics of the device GaN layers, front Pi gate, and back Pi gate are incorporated HEMT is constructed by deploying two semiconductor substances with identical lattice constant, and distant band gap materials are stacked on one another. At the interjunction of these 2DEG is formed. A broad class of HEMTs is existent namely Gama gate, T gate, GFP, CG, DFP, MGFP Gate HEMT. These are limited by early high Leakage current, breakdown effects, and more short channel effects. Conventional transistors are optimized to overcome these effects.

#### 2. DEVICE STRUCTURE AND SIMULATION PARAMETERS

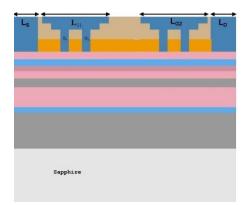

Dual Pi gate HEMT with hetero passivation layer is shown in Figure 1 structure. Since  $Si_3N_4/Al_2O_3$ exhibits the least  $C_{GS}$  and  $C_{GD}$  reducing surface traps, it is chosen as passivation layers [12]. 3 unique features of the structure, one is it consists of 2 Pi gates, secondly, it consists of a hetero passivation layer [13]. The unique properties of AlN make its usage in lighting, renewable energy, electronics, and optics. It is a solid nitride of aluminum material [14]. At room temperature, it has approx. 6eV of the band gap [14]. AlN layer used for carrier confinement reduction in alloy scattering improved scattering [15]. GaN Cap layer of 2 nm is deployed on the top of the structure [16]. By using GaN cap layer carrier mobility improved, improve transport mechanism [17]. The probability of penetrating the mobility electron into AlGaN is reduced due these layers [18]. High conduction is possible due to the presence of cap layer [19]. Scattering of alloy reduced, and better confinement of carrier, improved conductivity and mobility is observed by employing the cap layer on the top of heterostructure which proposed makes easy to fabric ohmic contact. A dual gate increases I<sub>D</sub> drain current and reduces leakage current, in turn, reflects on transconductance [20]. Silicon dioxide (SiO<sub>2</sub>), silicon carbide (6H-SiC), Si, and GaN of material with wide band gap semiconductors ultra-power microwave and radiofrequency application required material with high band gap [21]. These requirements can be met by the above for the past decades' work on transistors is processed to reduce the size of the transistor [22]. But too much reduction in the size of the transistor results increase in leakage current, increase in power dissipation losses [23], so hetero materials with high electron mobility are loosening to overcome the limitation of existing conventional transistors. Marino et al. [24] proposed HEMTs increase conductivity drain current (I<sub>D</sub>), trans conductance (gm), on resistance (Ron), and threshold voltage (Vth). Off current (Ioff), f<sub>T</sub>, f<sub>max</sub> get reflected in a positive direction. The performance of 6 nm gate HEMT is compared with different passivation layers ie  $SiO_2$ .  $Si_3N_4$ ,  $Al_2O_3$  and  $Si_3N_4/Al_2O_3$  the proposed device is verified with passivation and without passivation layer using the TCAD tool. In multiple directions, the structure is simulated and verified using the Silvaco TCAD tool [25]. Less lattice mismatch materials are used and designed the structure keeps cost in view. The proposed structure operates at high power and high-frequency operation. The electrons may scatter during the active state to avoid this problem  $SiO_2$  is used to confine the electron in the channel and let the electron flow from source to drain [26] aluminum nitride (AIN) material is used to reduce the material mismatch. If there is more mismatch electron scatter and leads to scattering losses. SiO2 and Si materials are used to lower scattering due to alloy disorder aluminum with different mole fractions is used to improve the performance [27]. ATLAS method and models were used for the proposed device.

It is observed by Johnson's figure of merit that GaN ideal candidate for high temperature and high power due to its high electron mobility, saturation velocity, and high breakdown voltage. These cap layers passivation layers provide sealing the first layer of HEMT structure from external atmospheric fluctuations the narrow channel plays a key role that triggers the device to work at microwave frequencies, this is provided by GaN. HEMT is constructed by deploying two semiconductor substances with identical lattice constant, and distant band gap materials are stacked on one another A broad class of HEMTs is existent namely Gama gate, T gate, GFP, CG, DFP, MGFP gate HEMT. Back barrier layer (BBL) thickness results in reduction in leakage current and dynamic  $R_{on}BBL$  can be varied from 0 to 200 nm GaN channel is wurtzite crystal structure.it possess high Bandgap of 3.49 (EV) with electron mobility of 900 (cm<sub>2</sub>/vs), electron peak velocity is  $2.7 \times 10^7$  (cm/s), 2DEG sheet electron density is  $20 \times 10^{12}$  (cm<sup>-2</sup>), Critical breakdown field 3.3 (MV/cm), thermal conductivity >1.7 (W/cm-K), relative dielectric constant ( $\varepsilon_r$ ) -9.0 GaN material possess high thermal conductivity, high saturation drift velocity. These properties are required for the device to work in high frequency for having high power switching and to work at high temperatures Heterojunction is formed when two material of different band gaps with almost the same lattice constant. The field effect transistor that incorporates heterojunction is called the HEMT.

20n Al<sub>2</sub>O<sub>3</sub> thickness was deployed. Al<sub>0.75</sub> Ga<sub>0.25</sub>N, Al<sub>0.52</sub>Ga<sub>0.45</sub>N, AlN (Spacer layer), GaN, AlN, Al<sub>0.52</sub>Ga<sub>0.45</sub>N, Al<sub>0.75</sub>Ga<sub>0.25</sub>N these materials are deployed in this sequence respective with 36 nm, 38 nm, 34 nm, 43 nm, 34 nm, 38 nm, 36 nm. Spacer layer is to improve the density of 2DEG aluminum nitride is stable at temperatures over 2,000° in inert atmosphere. It possesses high thermal conductivity. Dual pi gate HEMT with hetero passivation layer is proposed. SiO2, 6H-SiC, Si, and GaN of material with wide band gap semiconductors ultra-power microwave and RF application required material with high Band Gap. The proposed high K dielectric FG and BG HEMT overcomes the limitation of dual gate HEMT and exhibits optimized HEMT structure which gives optimistic DC and RF characteristics.

Figure 1. Double gate HEMT with Si<sub>3</sub>N<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub> passivation layers

# 3. SIMULATION RESULTS AND DISCUSSION

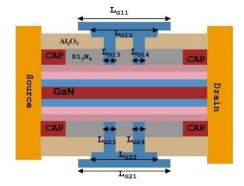

Device simulations are performed using the Silvaco TCAD tool. In this paper various existing transistors having T shaped gates, camel shaped gates, MGFP gates, GFP gates, and DFP gate-based MOS-HEMT. The first layer of the HEMT will form a tight bond with the metal to create the seal. This sealing eliminates elements from corroding. Figure 1, shows HEMT with a dual Pi gate [28]. Dual gate eliminates short channel effects, helps to use the device in high-frequency applications, and increases the efficiency of the channel Figure 2, shows the proposed structure consists high K dielectric FG-BG HEMT structure with Si<sub>3</sub>N<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub> passivation layers. The two gates play a key role in improving drain current and conductance. The performance of the device is optimized. To optimize results, the position of metal is also an important constraint. The depletion region in the channel gets modified which adds to the performance improvement of the device. The capacitance is related as in the (1), where A is the area of the capacitance,  $\varepsilon_0$  is free space permittivity, K is dielectric constant of the material, t is capacitor oxide insulator thickness. As the capacitance is related to *k* by altering *k* we can improve the capacitance, where the derive current can be improved.

$$C = \frac{kA\varepsilon_0}{t} \tag{1}$$

$$I_{D,Sat} = \frac{WC\mu(V_G - V_{th})^2}{2L}$$

(2)

The drain current of a proposed device is calculated using (2), where drain current is directly proportional to gate capacitance, width of the channel, mobility of the carrier and inversely proportional to length of the gate. The threshold voltage and gate voltages are measured in volts and its range up to 1v. The saturated drain current of this device is more than the hetero junction and conventional HEMT.

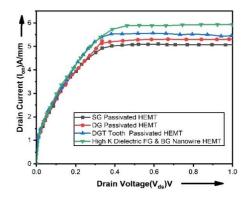

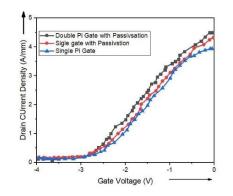

Figure 3 shows drain current changes concerning various drain voltage characteristics of HEMTs with various physical structures of 6 nanometers at  $V_{gs} = 0$  V i.e., Single Pi gate passivated (SGP) HEMT, double gate passivated (DGP) HEMT, double gate triple tooth passivated (DGT) HEMT, high K dielectric FG and BG HEMT at gate voltage  $V_{gs} = 0$  V is shown. It results in an increased drain current ( $I_d$ ) of 5.92 A/mm appearing for the proposed high K dielectric FG and BG HEMT.

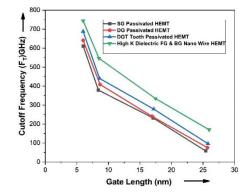

From (3) Cutoff frequency ( $f_T$ ) depends on the length of the gate (Lg) and the saturation velocity of the material and trans conductance. As drain current increases, trans conductance increases. As the trans conductance is directly proportional to the cutoff frequency, the cutoff frequency increased to 743 GHz. So, by proper placement of the transistor gate, the required cutoff frequency can be attained.

$$Cutoff \ Frequency = \frac{Vsat}{2 \prod Lg} \tag{3}$$

Figure 4 shows the Cutoff frequency ( $f_T$ ) concerning gate length, of HEMTs with various physical structures of 6 nanometers at  $V_{gs} = 0 V$  i.e., single Pi Gate passivated HEMT, double gate passivated HEMT, double gate triple tooth passivated HEMT, high K dielectric FG and BG HEMT at gate voltage  $V_{gs} = 0 V$  is shown. It resulted in an increased Cutoff frequency ( $f_T$ ) of 743 GHz. appeared for proposed high K dielectric FG and BG HEMT.

Figure 2. High K dielectric FG-BG HEMT structure with Si<sub>3</sub>N<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub> passivation layers

Figure 3. Drain current changes concerning various drain voltage characteristics for HEMTs with various physical structures of 6-nanometer technology at  $V_{gs} = 0 V$

Figure 4. Cut-off frequency variations at different gate lengths for various physical structures at  $V_{ds} = 0.2 V$

Trans conductance (gm) is defined as the ratio of change in drain current ( $I_d$ ) to the change in the change in the gate to source voltage ( $V_{GS}$ ) represented in (4).

$$Transconductance = \frac{dI_D}{dV_{GS}} \tag{4}$$

Design and performance analysis of front and back Pi 6 nm gate with high K ... (Yadala Gowthami)

(5)

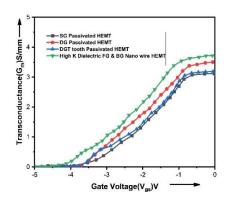

Figure 5 shows Trans conductance ( $G_m$ ) concerning gate voltage  $V_{gs}$  for HEMTs with various physical structures of 6 nanometers at  $V_{ds} = 0.2 V$  i.e., Single Pi Gate passivated HEMT, double gate passivated. HEMT, double gate triple tooth passivated HEMT, high K dielectric FG and BG HEMT at various gate voltage is shown. It is shown that increased trans conductance of 3.71 S/mm. appeared for proposed high K dielectric FG and BG HEMT. Figure 6 shows the variations of drain current density with various gate voltage for single gate, single gate passivation layer and double gate passivation layer structures. In this figure, it is observed that the current density characteristics are varies according to the various gate voltage by considering single gate, single gate passivation and double gate with passivation model using different work functions.

Table 1 shows the DC characteristics exhibited by HEMT with various passivation on layers. Such as SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, and Si<sub>3</sub>N<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub>, single gate with a passivation layer (SGP) [29], DGP, passivated double gate with triple tooth (DGP-TT), the characteristics such as drain current (I<sub>D</sub>), Trans conductance ( $g_m$ ),  $I_{off}$ , cut off frequency ( $f_T$ ), obtained from Si<sub>3</sub>N<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub> passivated dual gate GaN HEMT with triple tooth are illustrated. it is observed that DGP-TT N=3 HEMT exhibited optimized results of  $I_D = 4.9$  A/mm, the leakage current of 9.5E-11(A), transconductance of 2.7 S/mm, cutoff frequency 560 GHz, drain conductance 0.657 (S/mm), on resistance 0.6 (ohm mm) [30]. The gate to source capacitance is product of trans conductance and cut off frequency represented in (5) where gm is trans conductance [31].

Figure 5. Trans conductance of various gate voltages

Figure 6. Variations of drain current density with various gate voltages for SG, SGP, DG-P

Table 1. Performance metrics for the reported structures

|              | Table 1. Terrormanee metries for the reported structures |                          |           |          |           |           |  |  |  |  |

|--------------|----------------------------------------------------------|--------------------------|-----------|----------|-----------|-----------|--|--|--|--|

|              | Ion (A/mm)                                               | I <sub>off</sub> (A)E-11 | Gm (S/mm) | FT (GHz) | GD (S/mm) | RON (Ωmm) |  |  |  |  |

| SiO2         | 3.75                                                     | 9.40                     | 1.33      | 470      | 0.356     | 1.36      |  |  |  |  |

| A12O3        | 3.98                                                     | 8.99                     | 1.37      | 493      | 0.389     | 1.2       |  |  |  |  |

| Si3N4        | 4.2                                                      | 4.50                     | 1.41      | 521      | 0.409     | 1.3       |  |  |  |  |

| Si3N4/ Al2O3 | 4.4                                                      | 4.22                     | 1.45      | 537      | 421       | 0.86      |  |  |  |  |

| SG           | -                                                        | -                        | 1.33      | 537      | 0.356     | 0.8       |  |  |  |  |

| SGP          | 4.4                                                      | -                        | 1.45      | 537      | 0.421     | 0.79      |  |  |  |  |

| DGP          | 4.6                                                      | -                        | 1.72      | 540      | 0.534     | 0.77      |  |  |  |  |

| DGP-TT, N=1  | 4                                                        | 1.09                     | 2         | 520      | 0.423     | 0.75      |  |  |  |  |

| DGP-TT, N=2  | 4.2                                                      | 7.46                     | 2.4       | 530      | 0.45      | 0.72      |  |  |  |  |

| DGP-TT, N=3  | 4.9                                                      | 9.54                     | 2.7       | 560      | 0.657     | 0.6       |  |  |  |  |

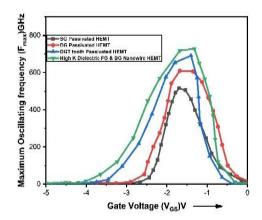

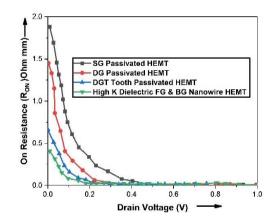

Figure 7 shows the maximum oscillation frequency (fmax) concerning gate voltage characteristics of HEMTs with various physical structures of 6 nanometers at  $V_{ds} = 0.2 V$  i.e., Single Pi gate passivated HEMT, double gate passivated HEMT, double gate triple tooth passivated HEMT, high K dielectric FG and BG HEMT at gate voltage  $V_{gs} = 0 V$  is shown. It resulted that, an increased Cutoff frequency (fT) of 743 GHz. Appeared for proposed high K dielectric FG and BG HEMT. Figure 8 shows on resistance ( $R_{on}$ ) concerning drain voltage ( $V_{ds}$ ) characteristics of HEMTs with various physical structure 6 nanometers at gate voltage = 0V i.e., single Pi gate passivated HEMT, double gate passivated HEMT, double gate triple tooth passivated HEMT, high K dielectric FG and BG HEMT at gate voltage  $V_{gs} = 0 V$  is shown. It resulted on resistance of ( $R_{on}$ ) of 0.40 (Ohms) appeared for proposed the high K dielectric FG and BG HEMT.

Figure 7. Maximum oscillation frequency with various gate voltages for SG passivated, DG passivated, DGT tooth passivated, high K dielectric HEMT

Figure 8. On resistance variation to various drain voltage for SG passivated, DG passivated, DGT tooth passivated, high K dielectric HEMT

In Table 2 comparison of existing HEMT structures characteristics are simulated and compared with the proposed structure characteristics. The proposed passivated dual Pi 6 nm gate length HEMT resulted in low leakage current ( $I_{off}$ ), high drain current (on current), high trans conductance ( $g_m$ ), high Cutoff frequency, low threshold voltage ( $V_{th}$ ), high  $I_{on}/I_{off}$ . These improvised DC characteristics and RF characteristics help to implement the proposed HEMT in RF applications. Due to the high electron mobility of the material property, dual gate, passivation enhancement and optimized performance are obtained for the proposed structure.

T gate, Gama gate, CG, MGFP gate, GFP gate, and DFP Gate based MOS-HEMTs are the available transistors currently. The available transistor has its applications. Early breakdown effects are present in the existing MOS-HEMTs. Proposing the partitioned novel shape gate leads to resistance reduction which increases  $f_{max}$ .

The results show that high K dielectric front gate (FG) and back gate (BG) HEMT results improved on current, trans conductance, drain conductance, Maximum oscillation frequency, improved Cutoff frequency, with reduced leakage current. Proposed structure for high K dielectric FG and BG caped HEMT resulted in best results compared to other existing results. High drain current, high trans conductance, high drain conductance, low on-resistance, high cut off frequency, high maximum oscillation frequency ( $f_{max}$ ), low leakage current, and high  $I_{on}/I_{off}$  are obtained.

| proposed structure characteristics |       |        |        |       |          |       |        |       |         |        |           |

|------------------------------------|-------|--------|--------|-------|----------|-------|--------|-------|---------|--------|-----------|

| Gate Shape                         | MGF   | DFP    | GFP    | Camel | Gama     | Т     | Pi     | SG-P  | DG P    | DGT    | Proposed  |

|                                    | Т     |        |        |       |          |       |        |       |         | TP     | Structure |

| (Lg) nm                            | 20    | 20     | 20     | 20    | 20       | 20    | 6      | 6     | 6       | 6      | 6         |

| Ion (A/mm)                         | 2E-2  | 5E-2   | 5.5E-2 | 7E-2  | 1        | 2     | 4      | 4.4   | 4.6     | 4.9    | 5.92      |

| $I_{off}(A)(E-11)$                 | 360   | 250    | 60.2   | 47    | 43.2     | 18    | 8.65   | 1     | 2.63E-1 | 5.6E-2 | 1.2E-2    |

| $I_{on}/I_{off}$                   | 5.56E | 2.00E- | 9.14E- | 0.001 | 001 0.02 | 0.1   | 4.62E- | 4.40E | 1.75E+0 | 8.75E+ | 4.93E+02  |

| (E+8)                              | -05   | 04     | 04     | 0.001 |          |       | 01     | +00   | 1       | 01     |           |

| f <sub>max</sub> (GHz)             | 38    | 50     | 65     | 80    | 100      | 425   | 485    | 490   | 500     | 520    | 765       |

| $f_T(GHz)$                         | 14    | 18     | 40     | 60    | 90       | 310   | 400    | 537   | 540     | 560    | 743       |

| $g_m(S/mm)$                        | 0.098 | 0.217  | 0.297  | 0.327 | 0.501    | 0.9   | 1.51   | 1.45  | 1.72    | 2.7    | 3.71      |

| $V_{th}(V)$                        | -1    | -1     | -1     | -1.4  | -1.5     | -2.8  | -3.7   | -3.76 | -3.8    | -4     | -4.5      |

| $g_d(S/mm)$                        | 0.084 | 0.091  | 0.095  | 0.098 | 0.116    | 0.148 | 0.353  | 0.456 | 0.534   | 0.657  | 1,769     |

| $R_{on}(\Omega mm)$                | 3.8   | 3.6    | 2.5    | 1.8   | 1.5      | 1     | 0.8    | 0.75  | 0.7     | 0.6    | 0.4       |

Table 2. Comparison of existing HEMT structures characteristics is simulated and compared with the proposed structure characteristics

#### 4. CONCLUSION

High K dielectric FG and BG 6 nano-wire HEMT with GaN Cap layer are proposed in the paper and its performance is analyzed for obtaining optimized results. The proposed structure is collated with a few existing HEMT structures. The DC characteristics and RF characteristics are sorted out and reported improved drain current of 5.92 (A/mm), trans conductance of 3.71 (S/mm), the reduced leakage current of 5.54E10-13 (A), Cutoff frequency of 743 GHz, maximum oscillation frequency of 765 GHz, drain conductance of 1.76 (S/mm), the threshold voltage of -4.5V, on resistance of 0.40 Ohms. The dominant characteristics of the proposed device aid to apply in high frequency application.

#### REFERENCES

- R. Chu et al., "1200-V normally off GaN-on-si field-effect transistors with low dynamic on-resistance," IEEE Electron Device Letters, vol. 32, no. 5, pp. 632–634, May 2011, doi: 10.1109/LED.2011.2118190.

- [2] W. Wang et al., "Improvement of power performance of GaN HEMT by using quaternary InAlGaN barrier," IEEE Journal of the Electron Devices Society, vol. 6, pp. 360–364, 2018, doi: 10.1109/JEDS.2018.2807185.

- [3] J. H. Hwang, S.-M. Kim, J. M. Woo, S.-M. Hong, and J.-H. Jang, "GaN HEMTs with quaternary in 0.05 Al 0.75 Ga 0.2 N Schottky barrier layer," *physica status solidi (a)*, vol. 213, no. 4, pp. 889–892, Apr. 2016, doi: 10.1002/pssa.201532566.

- [4] S. Alluri, K. Mounika, B. Balaji, and D. Mamatha, "Optimization of multiplexer architecture in VLSI circuits," AIP Conference Proceedings, 2021, doi: 10.1063/5.0059332.

- [5] B. Liao, Q. Zhou, J. Qin, and H. Wang, "Simulation of AlGaN/GaN HEMTs' breakdown voltage enhancement using gate fieldplate, source field-plate and drain field plate," *Electronics*, vol. 8, no. 4, Apr. 2019, doi: 10.3390/electronics8040406.

- [6] N. M. Shrestha, Y. Li, and E. Y. Chang, "Step buffer layer of Al 0.25 Ga 0.75 N/Al 0.08 Ga 0.92 N on P-InAlN gate normally-off high electron mobility transistors," *Semiconductor Science and Technology*, vol. 31, no. 7, Jul. 2016, doi: 10.1088/0268-1242/31/7/075006.

- [7] L. Yang et al., "Improvement of subtreshold characteristic of gate-recessed AlGaN/GaN transistors by using dual-gate structure," *IEEE Transactions on Electron Devices*, vol. 64, no. 10, pp. 4057–4064, Oct. 2017, doi: 10.1109/TED.2017.2741001.

- [8] U. Radhakrishna, "Modeling gallium-nitride based high electron mobility transistors: linking device physics to high voltage and high frequency circuit design," Massachusetts Institute of Technology, 2016.

- S. Alluri, B. Balaji, and C. Cury, "Low power, high speed VLSI circuits in 16nm technology," AIP Conference Proceedings, 2021, doi: 10.1063/5.0060101.

- [10] B. Balaji, K. S. Rao, K. G. Sravani, and M. Aditya, "Design, performance analysis of GaAs/6H-SiC/AlGaN metal semiconductor FET in submicron technology," *Silicon*, vol. 14, no. 13, pp. 7857–7861, Aug. 2022, doi: 10.1007/s12633-021-01545-y.

[11] K. Zhang, C. Kong, J. Zhou, Y. Kong, and T. Chen, "High-performance enhancement-mode Al 2 O 3 /InAlGaN/GaN MOS high-

- [11] K. Zhang, C. Kong, J. Zhou, Y. Kong, and T. Chen, "High-performance enhancement-mode Al 2 O 3 /InAlGaN/GaN MOS highelectron mobility transistors with a self-aligned gate recessing technology," *Applied Physics Express*, vol. 10, no. 2, Feb. 2017, doi: 10.7567/APEX.10.024101.

- [12] P. K. Kumar, B. Balaji, and K. S. Rao, "Performance analysis of sub 10 nm regime source halo symmetric and asymmetric nanowire MOSFET with underlap engineering," *Silicon*, vol. 14, no. 16, pp. 10423–10436, Nov. 2022, doi: 10.1007/s12633-022-01747-y.

- [13] I.-H. Hwang et al., "High-performance E-mode AlGaN/GaN MIS-HEMT with dual gate insulator employing SiON and HfON," physica status solidi (a), vol. 215, no. 10, May 2018, doi: 10.1002/pssa.201700650.

- [14] J. Zhuge, R. Wang, R. Huang, X. Zhang, and Y. Wang, "Investigation of parasitic effects and design optimization in silicon nanowire MOSFETs for RF applications," *IEEE Transactions on Electron Devices*, vol. 55, no. 8, pp. 2142–2147, Aug. 2008, doi: 10.1109/TED.2008.926279.

- [15] K. Sehra, V. Kumari, V. Nath, M. Gupta, and M. Saxena, "Optimization of asymmetric \$π\$ gate HEMT for improved reliability & frequency applications," in 2019 IEEE 9th International Nanoelectronics Conferences (INEC), Jul. 2019, pp. 1–4, doi: 10.1109/INEC.2019.8853857.

- [16] W. Sun et al., "Investigation of trap-induced threshold voltage instability in GaN-on-Si MISHEMTs," IEEE Transactions on Electron Devices, vol. 66, no. 2, pp. 890–895, Feb. 2019, doi: 10.1109/TED.2018.2888840.

- [17] Y. Gowthami, B. Balaji, and K. S. Rao, "Design and performance evaluation of 6nm HEMT with silicon sapphire substrate," *Silicon*, vol. 14, no. 17, pp. 11797–11804, Nov. 2022, doi: 10.1007/s12633-022-01900-7.

- [18] D. Kim, J. Alamo, J. Lee, and K. Seo, "Performance evaluation of 50 nm In0.7Ga0.3 as HEMTs for beyond CMOS logic applications," *Proceedings of IEDM Technical Digest*, 2005.

- [19] K. Shinohara et al., "220GHz fT and 400GHz fmax in 40-nm GaN DH-HEMTs with re-grown ohmic," in 2010 International Electron Devices Meeting, Dec. 2010, pp. 30.1.1--30.1.4, doi: 10.1109/IEDM.2010.5703448.

- [20] J. Lin, D. A. Antoniadis, and J. A. del Alamo, "Impact of intrinsic channel scaling on InGaAs quantum-well MOSFETs," *IEEE Transactions on Electron Devices*, vol. 62, no. 11, pp. 3470–3476, Nov. 2015, doi: 10.1109/TED.2015.2444835.

- [21] S.-X. Sun et al., "Numerical simulation of the impact of surface traps on the performance of InP-based high electron mobility transistors," *Physica status solidi (a)*, vol. 214, no. 10, Oct. 2017, doi: 10.1002/pssa.201700322.

- [22] J. Joh and J. A. del Alamo, "Impact of gate placement on RF power degradation in GaN high electron mobility transistors," *Microelectronics Reliability*, vol. 52, no. 1, pp. 33–38, Jan. 2012, doi: 10.1016/j.microrel.2011.09.008.

- [23] I. Rossetto et al., "Evidence of hot-electron effects during hard switching of AlGaN/GaN HEMTs," IEEE Transactions on Electron Devices, vol. 64, no. 9, pp. 3734–3739, Sep. 2017, doi: 10.1109/TED.2017.2728785.

- [24] F. A. Marino, N. Faralli, T. Palacios, D. K. Ferry, S. M. Goodnick, and M. Saraniti, "Effects of threading dislocations on AlGaN/GaN high-electron mobility transistors," *IEEE Transactions on Electron Devices*, vol. 57, no. 1, pp. 353–360, Jan. 2010, doi: 10.1109/TED.2009.2035024.

- [25] D. Fanning, L. Witkowski, J. Stidham, H.-Q. Tserng, M. Muir, and P. Saunier, "Dielectrically defined optical T-gate for high power GaAs pHEMTs," in 2002 GaAs MANTECH Digest of Papers, 2002, pp. 83–86.

- [26] C.-H. Chen et al., "AlGaN/GaN dual-gate modulation-doped field-effect transistors," Electronics Letters, vol. 35, no. 11, pp. 933–935, 1999, doi: 10.1049/el:19990627.

- [27] A. D. Latorre-Rey, J. D. Albrecht, and M. Saraniti, "Generation of hot electrons in GaN HEMTs under RF class A and AB PAs," in 2017 75th Annual Device Research Conference (DRC), Jun. 2017, pp. 1–2, doi: 10.1109/DRC.2017.7999436.

- [28] N.-Q. Zhang, B. Moran, S. P. DenBaars, U. K. Mishra, X. W. Wang, and T. P. Ma, "Effects of surface traps on breakdown voltage and switching speed of GaN power switching HEMTs," in *International Electron Devices Meeting. Technical Digest (Cat. No.01CH37224*), 2001, pp. 25.5.1--25.5.4, doi: 10.1109/IEDM.2001.979575.

- [29] O. Ambacher et al., "Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Gaface AlGaN/GaN heterostructures," Journal of Applied Physics, vol. 85, no. 6, pp. 3222–3233, Mar. 1999, doi: 10.1063/1.369664.

- [30] Y. Gowthami, B. Balaji, and K. S. Rao, "Design and analysis of a symmetrical low-\$κ\$ source-side spacer multi-gate nanowire device," *Journal of Electronic Materials*, Jan. 2023, doi: 10.1007/s11664-023-10217-z.

- [31] S. Arulkumaran, T. Egawa, L. Selvaraj, and H. Ishikawa, "On the effects of gate-recess etching in current-collapse of different cap layers grown AlGaN/GaN high-electron-mobility transistors," *Japanese Journal of Applied Physics*, vol. 45, no. 8, pp. L220--L223, Feb. 2006, doi: 10.1143/JJAP.45.L220.

# **BIOGRAPHIES OF AUTHORS**

**Gowthami Yadala b S s b** born in India. She received the master degree from JNTUK and currently pursuing his Ph.D. from KL University, India. She published 2 publications in the field of HEMT journals. Her research interests include development of Heterojunction High Electron Mobility Transistors for Biomedical applications. She can be contacted at email: gowthami.y89@gmail.com.

**Bukya Balaji D S C** was born in India. He received the master degree in VLSI Systems from JNTUK, India in 2009 and Ph.D. from OPJS University in 2017. He is currently working as Associate Professor in KL University, Vijayawada, AP, and India. He published more than 25 journal papers and 8 conference papers in the field of MOS fabrication and analysis. He can be contacted at vahividi@gmail.com.

**Karumuri Srinivasa Rao Karumuri Signification** Wassborn in India. He received the master and Ph.D. degrees from Central University. He is currently a Professor and the Head of the Microelectronics Research Group, Department of Electronics and Communication Engineering, KL University, Guntur, India. He is working on MEMS Project worth of 40 Lakhs funded by SERB, India. He has published more than 5 papers in the IEEE journals and more than 90 in international research publications (SCI) and presented more than 45 conference technical papers around the world. His current research interests include MEMS-based reconfigurable antennas actuators, Bio-MEMS, RF MEMS switches, and RF MEMS filters. He can be contacted at srinivasakarumuri@gmail.com.