We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

6,300 Open access books available 171,000

190M Downloads

Our authors are among the

TOP 1%

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# Chapter

# Inertness and Other Properties of Thin Ruthenium Electrodes in ReRAM Applications

Amrita Chakraborty, Mohammad Al-Mamun and Marius Orlowski

# Abstract

Building nonvolatile memory such as resistive random access memory (ReRAM) directly into a CMOS backend (BEOL) would reduce latency in connectivity-constrained devices and reduce chip's footprint by stacking non-volatile memory (NVM) on top of the logic circuits. This co-integration is facilitated by a broad commonality between ReRAM and BEOL as both rely on the same basic metal-insulator-metal (MIM) structure. One good candidate for a ReRAM cell is the  $Cu/TaO_x/Pt$  device. As platinum (Pt) is not an economic choice, a BEOL-compatible replacement is desirable. A good candidate to replace Pt electrode is ruthenium (Ru), currently being used as a liner/diffusion barrier in sub-15 nm technology nodes and soon to supplant tungsten as via, and copper (Cu) as interconnect materials. We report on extensive characterization of a Cu/TaO $_x$ / Ru device and compare its performance and reliability with extant ReRAM devices. Against the background of well-characterized non-Ru ReRAM devices, Cu/TaO<sub>x</sub>/Ru cell constitutes a micro-laboratory for testing a wide range of Ru properties with the Cu nanofilament as a probe. Since the temperature of the cell can be controlled internally from  $27^{\circ}$ C to  $\sim 1100^{\circ}$ C, thin Ru layers can be subjected to much more comprehensive tests than it is possible in the interconnect MIM structures and reveal and confirm interesting material properties, including the impact of embedment.

**Keywords:** chemical inertness, surface roughness, thermal conductivity, grain nucleation, columnar grains, stopping power, diffusion barrier, melting temperature, layer embedment, surface nucleation, adatom surface diffusion

# 1. Introduction

This chapter looks at the material properties of thin Ru films from the perspective of their suitability for use as an inert electrode in ReRAM cells, such as Cu/TaO<sub>x</sub>/Ru [1], that lends itself to be readily integrated in the CMOS back-end-of-line (BEOL) [2]. Advanced interconnects at 10 nm half-pitch, in order to overcome the scaling issues with Cu interconnects, increasingly pin hopes on ruthenium metallization, not only as a liner and diffusion barrier for Cu, but also as a stand-alone material for contact plug, via, and even interconnect lines [3–5]. Such integration of ReRAM

memory into BEOL has the potential of reducing the latency in connectivity-constrained computational devices and of bringing logic and memory closer together [6–8]. This co-integration is rendered possible and viable as low-k dielectrics and Cu/Ru/Co interconnect lines already prefigure a ReRAM device as a MIM structure, and the crossbar architecture of a typical two-terminal ReRAM memory array consists of electrode lines that may serve as interconnect lines and vice versa with metal vias being replaced by ReRAM switching layer. The replacement of the via material with the switching layer leads to the concept of formation of conductive vias on the fly, by an application of an electric pulse after the IC chip has been already manufactured [9]. Building NVM directly into a CMOS low-k interconnect back-end, would not only reduce latency in connectivity constrained computational devices but also reduce the footprint of a chip by stacking memory on top of the logic. Upon successful integration, the interconnect information bottleneck could be untied and morphed into several system architectures using the same basic universal hardware platform.

Given the auspicious circumstances, we elucidate in this chapter the material properties of Ru in the light of comparison of the performance of a Cu/TaO<sub>x</sub>/Ru device with its well-researched ReRAM counterparts. In addition, as the ReRAM devices, such as Cu/TaO<sub>x</sub>/Ru, can be intrinsically and locally heated up to ca 1100°C, thin Ru layers can be subjected to much more comprehensive tests than it is possible in the interconnect MIM structures to reveal material properties of as a stand-alone and as an embedded Ru material.

The ReRAM devices, by themselves, have recently been of great interest to both industry and academia as a potential replacement for a stand-alone volatile dynamic random-access memory (DRAM) and nonvolatile flash memories (NVM) that are nearing the end of their dimensional scaling roadmaps [7]. These two-terminal devices exhibit figure eight-like pinched current-voltage (I–V) hysteresis switching between a high resistance OFF state  $(R_{off})$  and a low resistance ON-state  $(R_{on})$  with memristive characteristics [10–12]. Resistive memory cells also hold promise for neuromorphic applications [13–15]. A specific subcategory of a ReRAM device, the conductive bridge random access memory (CBRAM) is being extensively explored as a promising candidate for a resistive memory device [16] and serves here as a probe into Ru property materials. In general, a CBRAM device consists of an active anode, an insulating layer, and an inert cathode. The anode consists of Cu, Ag, or Ni, which can dissolve in the solid electrolyte layer [17, 18]. The resistive switching (RS) behavior can be explained by a formation and rupture of a Cu conductive filament (CF). The insulating layer, a dielectric, also called the switching layer, such as  $Ta_2O_5$ ,  $TaO_x$ , GeSe, GeS<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and SiO<sub>2</sub> [19], allows for ion and defect electromigration when an electric field is applied. When a positive voltage is applied to the Cu electrode, Cu<sup>+</sup> cations are generated according to the redox reaction,  $Cu \leftrightarrow Cu^+ + e^-$ , which dissolve, and migrate into the solid electrolyte [20]. Cu<sup>+</sup> cations, after traversing the switching layer under the influence of an electric field, are electrochemically reduced on the Pt cathode which acts as an effective diffusion barrier for Cu atoms. As more Cu atoms accumulate, a nanoscale conductive filament (CF) is formed, shorting the two electrodes in so-called FORM and SET processes. The FORM operation describes the formation of the CF for the first time in a virgin memory cell. The SET operation is the restoration of an already-formed conductive filament after it had been partially ruptured in the so-called RESET operation. The ON state is characterized by the resistance of the Cu CF, R<sub>on</sub>, and when the CF is ruptured the device reverts to a high resistance OFF-state, characterized by the off-resistance, Roff. The ON/OFF ratio of CBRAM is usually significantly higher than 10<sup>3</sup> [21] and potentially allows multilevel

switching in a single memory cell to store more than one bit of data [22]. To date, Cu/ TaO<sub>x</sub>/Pt based devices have proven to be one of the more popular types of CBRAM devices due to numerous reports of excellent unipolar and bipolar switching characteristics, device performance, retention, reliability, endurance, and yield [23, 24]. Commercialization of non-volatile memory products based on RS devices derived from a Cu/TaO<sub>x</sub>/Pt cell has also been reported [25].

Against this backdrop, the main focus of the chapter lies on the Cu/TaO<sub>x</sub>/Ru device. As already mentioned, Ru is a good candidate to replace Pt and has been already deployed in the earlier CMOS BEOL technology nodes supplanting Ta or TaN as the liner material [26, 27]. Ru is ca. 45 times less expensive than Pt but has similar inertness properties as Pt. Pt and Ru are both transition metals with almost identical outer shell structure: The electron configuration for Ru is [Kr]4d<sup>7</sup>5s<sup>1</sup> for Pt [Xe] 4f<sup>14</sup>5d<sup>9</sup>6s<sup>1</sup>, where Kr and Xe denote the noble gases, Krypton and Xenon, respectively. Ru has a single electron in the fifth orbital and 15 electrons in the fourth orbital, while the larger Pt atom has a single electron in the sixth orbital and 17 electrons in the incomplete fifth orbital. In addition, the Ru-Cu phase diagram shows negligible solid solubility between the two elements, even at 900°C, rendering Ru an excellent diffusion barrier for Cu diffusion [28]. The work function of Ru of 4.75 eV is comparable to that of Cu 4.7 eV and much lower than that of Pt of 6.35 eV which has the highest work function among metals. The material properties of metals under consideration in this investigation are summarized in **Table 1**. The work function difference between Cu and Pt/Ru is partly responsible for the higher forming and set voltages in Ru devices as compared with Pt devices.

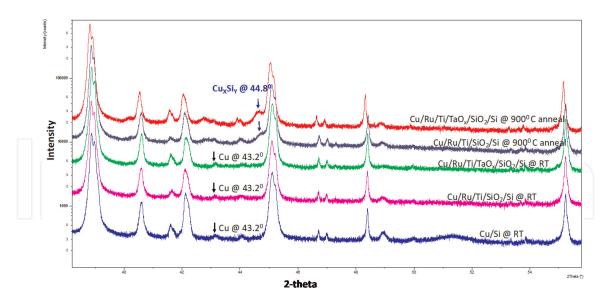

The chapter is organized as follows: In Section 2, we describe briefly the fabrication process of the ReRAM cells employed here. In Section 3 we establish the characteristic features of the electrical performance of a Cu/TaO<sub>x</sub>/Pt device, serving as our base line device, for comparisons with its counterparts, the Ru and cobalt (Co) devices. In Section 4 we discuss the analogous electric characteristics of the Cu/TaO<sub>x</sub>/Ru, or Ru device for short. In this framework, we discuss how the performance of the Ru device differs from the performance of derivative devices and how these differences in performance can be related to material properties of Ru. In Section 5, we analyze how the surface roughness (SR) properties of the metals, established by Atomic Force Microscope (AFM) measurements, have an impact on the electric performance of the respective devices. In Section 6, we present results on reliability and endurance tests of the three devices, which show that Ru shows markedly degraded reliability behavior compared with the Pt devices. In Section 7, we present evidence that different embedment scenarios of the same identical Ru device, lead to significantly different electrical performance and reliability of Ru devices. Finally, in Section 8, we present x-ray diffraction (XRD) studies of the pertinent layer systems annealed at elevated

| 4.7 | 386 | 1001 |     |

|-----|-----|------|-----|

|     | 500 | 1084 | 2.7 |

| 6.3 | 69  | 1770 | 1.8 |

| 4.7 | 116 | 2334 | 1.5 |

| 5.0 | 69  | 1495 | 2.3 |

|     |     |      |     |

Table 1.

Material properties of metals: Work function, thermal conductivity, and melting temperature, and surface roughness at 27°C after EBPVD deposition of metals used in our resistive switching devices.

temperatures and show that at annealing temperatures higher than 425°C, interlayer reactions in terms of formation of ruthenium and copper silicide occur, and lead to degraded functionality, particularly of the Ru devices.

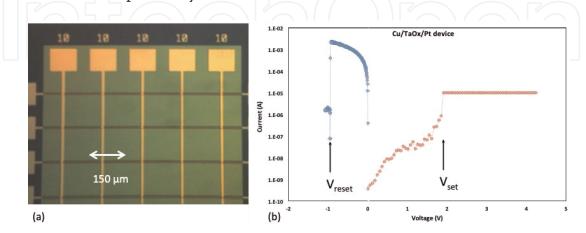

# 2. Fabrication of ReRAM devices

Figure 1a shows the optical micrograph of the crossbar architecture and the device cross section of a typical Cu/TaO<sub>x</sub>/Pt resistive switch. The devices are fabricated in a crossbar array on a thermally oxidized Si substrate with a SiO<sub>2</sub> thickness of 730 nm. Both metal electrodes and the metal oxide were deposited by electron beam physical vapor deposition (EBPVD) and patterned by layer lift-off technique. A thin titanium (Ti) layer of 25 nm was used between Pt/Ru/Co and SiO<sub>2</sub> to improve the adhesion of the Pt/Ru/Co layer. The thickness of the  $TaO_x$  switching layer is 25 nm. The width of metal lines varies between 5 and 35 µm resulting in rectangular device areas of the device in the range of (5 to 35) x (5 to 35)  $\mu$ m<sup>2</sup>. The distance between the metal lines is 150 µm. All metal layers (Cu, Pt, Ru, Co, Cr, Ti) were deposited by EBPVD in a Kurt Lesker e-beam PVD-250 chamber. I-V characteristics were measured by a Keithley 4200-SCS at room temperature. The oxygen-deficient TaO<sub>x</sub> ( $x \approx 1.9$ ) was deposited also in the PVD-250 chamber by evaporating  $Ta_2O_5$  pellets without  $O_2$  injection into the evaporation chamber. The thicknesses of Ru, Pt, Co, and Cu layers are 50, 50, 50, and 150 nm, respectively. The details of the sample manufacturing process have been given in [21, 29] where the role of the stoichiometry parameter x in  $TaO_x$  on resistive switching properties is being discussed in detail.

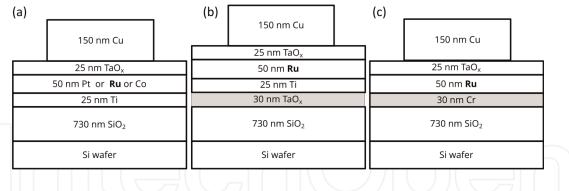

**Figure 2** shows the cross-section view of five devices that have been manufactured for this study. **Figure 2a** shows the base line device of  $Cu/TaO_x/Pt$  including the two derivative devices, where Pt has been replaced by Ru and Co electrodes. **Figure 2b** shows a different embedment of an identical  $Cu/TaO_x/Ru$  device as in **Figure 2a**, where an additional  $TaO_x$  layer has been inserted below the device proper, between the 730 nm thick field oxide and the Ti glue layer. **Figure 2c** shows still another embedment case of the Ru device, where the Ti glue layer has been replaced by a Chromium (Cr) glue layer. The additional 30 nm thick  $TaO_x$  layer, and the Cr layer have also been deposited by EBPVD.

#### Figure 1.

(a) Optical micrograph of the crossbar architecture of the  $Cu/TaO_x/Pt$ ,  $Cu/TaO_x/Ru$ , and  $Cu/TaO_x/Co$  devices. (b) Set and reset operation of the Cu/TaOx/Pt device with  $I_{cc} = 10 \ \mu$ A. The I-V characteristics of  $Cu/TaO_x/Ru$  and  $Cu/TaO_x/Co$  devices look very similar. The critical switching voltages,  $V_{form}$ ,  $V_{set}$ , and  $V_{res}$  for the  $Cu/TaO_x/Pt$ ,  $Cu/TaO_x/Ru$ , and  $Cu/TaO_x/Co$  devices are summarized in **Table 2**.

Figure 2.

Cross-sections of the five ReRAM devices. (a) Baseline Cu/TaOx/Pt device with two derivative devices, where Pt is replaced by Ru and Co. (b) Identical Ru device as in (a) but with additional  $TaO_x$  layer inserted between Ti glue layer and 730 nm thick field oxide. (c) another case of embedment of the Ru devices where the Ti glue layer has been replaced by a Cr glue layer.

# 3. Electrical properties of ReRAM cell (Cu/TaO<sub>x</sub>/Pt)

In this section, we establish the basic device properties of the  $Cu/TaO_x/Pt$  device. Those properties will serve as a base line comparison for the performance of the Cu/ TaO<sub>x</sub>/Ru device. The analysis of the differences between those devices and the Cu/  $TaO_x/Co$  device allow us to assess the material properties of Ru. When a positive voltage applied to the Cu electrode of a  $Cu/TaO_x/Pt$  is swept at a constant voltage ramp rate rr [V/s], the current will remain substantially zero until a critical voltage, V<sub>set</sub> is reached, at which a Cu CF is formed connecting the Cu and Pt electrodes with each other, and the cell switches from a high resistive state (HRS) characterized by  $R_{off}$  (1–900 M $\Omega$ ) to a low resistive state (LRS) characterized by  $R_{on}$  (70 $\Omega$ –15 k $\Omega$ ), yielding a ratio of  $R_{off}/R_{on} \approx 10^3 - 10^7$ . When the voltage is swept back, ohmic behavior is observed until a negative voltage V<sub>res</sub> is reached when the CF is ruptured and the current collapses to a very small value. A typical log-scale I-V switching characteristic of the Pt device is shown in **Figure 1b**. When the cell is set to an ON-state for the very first time, one speaks of a forming operation, characterized by the forming voltage, V<sub>form</sub>. Since, during the set operation relatively few Cu atoms have to be added to pluck the gap of the ruptured filament, V<sub>set</sub> is usually substantially smaller than V<sub>form</sub>. For Cu/TaO<sub>x</sub>/Pt devices, we find distribution of  $V_{form}$  with a mean,  $V_{form,m}$  = 4.5 V and a standard deviation of  $\sigma$  = 0.6 V, the V<sub>set</sub> distribution with a mean, V<sub>set,m</sub> = 2.8 V, and standard deviation,  $\sigma = 0.6$  V. The rupture of the CF is triggered mainly by Joule's heating at a critical current  $I_{res} = V_{res}/R_{on}$ . The  $V_{res}$  distribution of our Cu/TaO<sub>x</sub>/Pt devices is characterized by  $V_{res,m}$  = -0.9 V and  $\sigma$  =0.3 V. The electric characteristics in terms of threshold voltages for all devices are summarized in Table 2. These distributions apply roughly both to a multitude of devices as well as to a single device that has

|                         | V <sub>form,m</sub> [V] | $\sigma_{form}\left[V\right]$ | $V_{\text{set,m}}\left[V\right]$ | $\sigma_{set}\left[V ight]$ | V <sub>res,m</sub> [V] | $\sigma_{res}\left[V\right]$ |

|-------------------------|-------------------------|-------------------------------|----------------------------------|-----------------------------|------------------------|------------------------------|

| Cu/TaO <sub>x</sub> /Pt | 4.5                     | 0.6                           | 2.8                              | 0.6                         | -0.9                   | 0.3                          |

| Cu/TaO <sub>x</sub> /Ru | 7.3                     | 0.7                           | 4.4                              | 0.8                         | -3.4                   | 0.7                          |

| Cu/TaO <sub>x</sub> /Co | 4.7                     | 2.2                           | 2.7                              | 0.9                         | -1.0                   | 0.6                          |

Table 2.

Critical switching voltages,  $V_{form}$ ,  $V_{set}$ , and  $V_{res}$  for the Cu/TaO<sub>x</sub>/Pt, Cu/TaO<sub>x</sub>/Ru, and Cu/TaO<sub>x</sub>/Co devices along with their sigma distribution values.

been switched repeatedly. The endurance of the Pt devices depend on the  $I_{cc}$  current during the set operation. For not too low  $I_{cc}$  (>10 µA) and not too high  $I_{cc}$  (<5 mA), the device can be switched very often. Typically, in a few cases, a device was switched for 220 times, and it could still be switched even further. In most instances, a compliance current  $I_{cc}$  is imposed, lest the devices be damaged. No  $I_{cc}$  current limitation is applied during the reset operation.  $R_{on}$  of the LRS state depends on  $I_{cc}$  via Eq. (1), where the exponent n for cation filaments is very close to unity.

$R_{\rm on} = A/I_{\rm cc}^{\rm n} \tag{1}$

The  $R_{on}$ - $I_{cc}$  relation in Eq. (1) has been reported to be valid for numerous anode/ electrolyte/cathode material systems [30–32] with n  $\approx$  1. For Pt devices we obtain A = 0.5 V and n = 1.01. In ref. [1] it has been shown that the constant A in Eq. (1) is universally correlated to the minimum set voltage for all metallic conductive filaments reported so far. During the reset operation, the ReRAM cell is exposed to large currents which raises the temperature of the filament by depositing Joule's heat, primarily, in the Cu CF. When critical temperature in the filament has been reached, the Cu atoms begin to diffuse out and the filament is ruptured. The reset currents defined as  $I_{res} = V_{res}/R_{on}$  are typically in a few mA range. Hence, most of the Joule's heat,  $Q_{IH}$  deposited during the reset operation is given by Eq. (2)

$$Q_{JH} = \int_{0}^{t_{res}} \frac{V^{2}(t)}{R_{on}} dt = \int_{0}^{V_{res}/rr} \frac{rr^{2} \times t^{2}}{R_{on}} dt = \frac{V_{res}^{3} \times I_{cc}}{3 \times rr \times K}$$

(2)

where  $V_{res}$  is the reset voltage,  $t_{res} = V_{res}/rr$  is the reset time. The reset ramp rate, rr, and the compliance current,  $I_{cc}$ , may be used to control amount of heat deposited in the cell. Depending on chosen values for  $I_{cc}$  and rr,  $Q_{JH}$  can vary from 3 to 60  $\mu$ J [33]. The possibility of controlling the dissipated heat in the filament in terms of compliance current,  $I_{cc}$ , and ramp rate, rr will be important for the characterization and analysis of the electrical performance of the Ru, Pt, and Co devices.

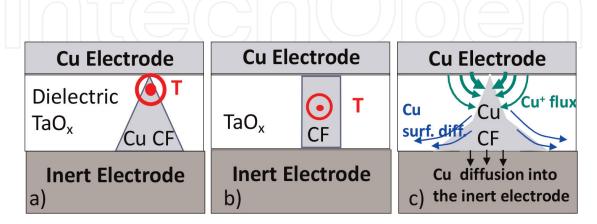

The geometrical shape of the filament has considerable implication of the reset operation. Three different shapes of Cu CF are shown in **Figure 3**. In **Figure 3a**, a CF in the shape of a truncated cone with a sharp constriction at the top is shown. The bulk of its resistance is concentrated at the tip of the cone. Filaments with a sharp

#### Figure 3.

Three different shapes of the Cu filament that may occur at different SET operation conditions with location of the highest temperature during RESET operation indicated. (a) Highly resistive Cu CF with sharp constriction at the top of the cone. (b) a low resistance Cu CF of cylindrical shape. (c) Constructive and destructive Cu fluxes during formation of Cu CF.

constriction at the top of the cone easily can be ruptured since the maximum Joule's heat is deposited at the tip and leads there to a high local temperature, which, in turn, triggers Cu out diffusion and formation of a gap in the filament. When the filament is ruptured, the HRS state of the cell is being restored. In contrast, the cylinder shape of a robust Cu filament shown in **Figure 3b** leads to much lower resistance and the temperature hot spot is moving away from the Cu/TaO<sub>x</sub> interface to midway between the electrode interfaces, where it is much more difficult to reach high temperature and cause out-diffusion of a larger number of Cu atoms to form a gap. Experimentally, we consistently find that the rupture of a filament is more difficult at lower  $R_{on}$  resistance, that is, formed at higher  $I_{cc}$  than at high  $R_{on}$  resistance formed at low  $I_{cc}$ .

During the final stage of the set operation there are two Cu fluxes that are responsible for the formation of the filament as shown in Figure 3c. The constructive flux occurs at the tip of the filament where the voltage drop is the largest and creates high electric field between the filament tip and the Cu electrode, which, in turn, allows for an enhanced transport of Cu<sup>+</sup> ions from the Cu electrode to the filament even after establishing the initial connection between the Cu filament and the Cu electrode. The role of I<sub>cc</sub> is to limit the resulting voltage drop and thus to set a limit on the electric field driving the Cu<sup>+</sup> ion transport. When sufficient number of Cu atoms is deposited at the tip, the resistance of the filament decreases, reducing the electric field at the tip and bringing the formation of the filament to a halt at a given  $I_{cc}$ . When  $I_{cc}$  is increased, then the electric field at the tip increases proportionally, triggering additional arrival of Cu<sup>+</sup> ions until the resistance of the filament drops sufficiently to reduce the electric field and, thus, to halt further Cu<sup>+</sup> ion transport. The other Cu flux is the Cu atom diffusion flux that weakens the base of the filament leading to a gradual change of the filament's shape from a truncated cone to cylinder-like shape. The second Cu flux has two components: (i) Lateral Cu diffusion along the TaO<sub>x</sub>/inert electrode interface, and (ii) Cu diffusion into the inert electrode. The Cu atom diffusion flux out of the filament at the base is impacted by the thermal conductivity of the inert electrode. Ceteris paribus, the inert electrode with high heat conductivity will be able to remove heat at a higher rate than an electrode with low heat conductivity. The larger heat removal rate will result in lower attainable maximum temperature of the Cu CF. Hence, a cell with inert electrode of low thermal conductivity is bound to display enhanced Cu diffusion and structural weakening of the filament at a lower V<sub>res</sub> voltages than high thermal conductivity electrode. The high temperature in the filament during the reset will trigger Cu diffusion near the base of the filament partly into the dielectric, partly along the TaO<sub>x</sub>/inert electrode interface, and partly into the inert electrode if the inertness of the electrode be somehow compromised. The net result of those diffusion components is a weakening of the base of the cone and a gradual transformation of the shape of the filament from a sharply cone-shaped into a more cylinder-shape filament as shown in **Figure 3b**. Once the shape of the filament is sufficiently close to that of a cylinder, it becomes very resistant to rupturing, and the number of switching cycles comes to a halt.

## 4. Electric characteristics of the ruthenium (Cu/TaO<sub>x</sub>/Ru)

The electrical characterization of the Ru device reveals that the device behaves very much like Pt and Co devices, albeit with some notable differences that can be all satisfactorily explained in terms of the material properties of the three metals given in **Table 1**.

**Table 2** summarizes the critical switching voltages for the three devices and shows that all the critical voltages of the Ru devices are considerably higher than those of Pt devices:  $\Delta V_{form}(Ru-Pt) = 2.7 \text{ V}$ ,  $\Delta V_{set}(Ru-Pt) = 1.6 \text{ V}$ , and  $\Delta V_{res}(Ru-Pt) = 2.5 \text{ V}$ . One notices that the work function difference  $\Delta \varphi(Ru,Cu)/q = 1.6 \text{ V}$  between Pt and Ru corresponds exactly to  $\Delta V_{set} = 1.6 \text{ V}$  between Pt and Ru devices indicating that  $V_{set}$  values are being reached at the same strength of the electric field. Since the work function contributes to the internal electric field across the dielectric, this difference was to be expected. Comparing now  $V_{form}$  of Pt and Ru devices one notes that  $V_{form}$  for Ru is higher by 2.8 V than  $V_{form}$  for Pt, significantly higher than 1.6 V. This differential can be accounted in part by 1.6 eV as a difference of the work function between Pt and Ru, as discussed before.

The remaining voltage differential of 1.2 V can be attributed to the electric field enhancement factor that is correlated to the higher SR of Pt (1.8 nm) than that of Ru (1.5 nm). Higher SR, in general, causes a higher local field across the oxide at the same voltage, or in other words, the same critical field required for the Cu CF formation is reached at lower voltage in Pt than in a Ru device. In Table 2, one observes also that V<sub>form</sub> for Co device is only slightly higher than V<sub>form</sub> for Pt device, despite a work function difference of  $\Delta \phi$ (Pt-Co)/q = 1.3 V. Based on the work function argument, one would expect a higher V<sub>form</sub> by about 1 V for Co devices than for Pt devices. However, one notes that the surface roughness of Co (2.4 nm) is significantly higher than that of Pt (1.8 nm). (SR will be discussed in more detail in Section 8.) The higher surface roughness of Co leads to a large enhancement factor of the local electric field due to the smaller curvature radius at the tip of the asperity. For a more detailed discussion of how the field enhancement factor correlates with SR, see ref. [34]. The differences in SR explain that in order to reach a critical field required for the formation of a filament a lower voltage is needed in case of a rougher surface of Co than for smoother interfaces of Pt or Ru. Both effects help lower the V<sub>form</sub> voltage of Co devices to a voltage only slightly higher than V<sub>form</sub> for a Pt device. These comparisons show that for the filament formation the local electric field, and by extension, the surface roughness, is an important factor. One also notices that the surface roughness correlates well with the standard deviation of the V<sub>form</sub> distributions of the three metals. The highest standard deviation observed for Co ( $\sigma_{form(Co)}$  = 2.2 V) correlates well with highest surface roughness of  $SR_{(Co)}$  = 2.4 nm of the cobalt devices, compared with the respective values of  $\sigma_{form(Ru)} = 0.6 \text{ V}$  and  $SR_{(Ru)} = 1.5 \text{ nm}$  for Ru, and  $\sigma_{\text{form}(Pt)} = 0.6 \text{ V and } SR_{(Pt)} = 1.8 \text{ nm. for Pt devices.}$

Because of the work function difference between Pt and Cu of 1.6 eV, there is a considerable built-in field that favors Cu<sup>+</sup> ion transport toward the Pt electrode. In fact, it has been observed [35] that even at a TaO<sub>x</sub> thickness of 25 nm, the work function difference is sufficiently high to set the device spontaneously into a conductive state after the device has previously been reset. This means that the electric field in the ruptured gap of the filament has reached the critical field of  $3 \times 10^6$  V/cm [36] to set the device spontaneously. Not a single instance of spontaneous setting of the devices has been observed for the Ru and Co devices tested at the same conditions. Thus, the spontaneous forming of a ruptured filament is enabled by the high work function difference between Pt and Cu metal electrodes. Therefore, in the absence of the built-in electric field, the electric field in Ru device has to be increased considerably by application of external bias to reach the critical field strengths in the TaO<sub>x</sub> dielectric. It has been shown [36] that a field of  $\approx 2.9 \times 10^6$  V/cm has to be reached in order to establish a Cu CF across a thin TaO<sub>x</sub> dielectric layer, independently of the nature of the inert electrode.

Next, we discuss the large difference in  $V_{res}$ , between Ru and Pt device,  $\Delta V_{res}$ (Ru-Pt) = 3.4–0.9 = 2.5 V, see Table 2. There is a general consensus that the rupturing of the Cu filament is attributed to the partial dissolution of the filament due to the Joule's heating. The local temperature at the thinnest part of the filament can reach temperature in excess of 1084°C [37]. 1084°C is the melting temperature of Cu (see Table 1) and melting of Cu electrodes has been experimentally observed after excessive heating of a ReRAM cell [38]. At such high temperature, the Cu atoms of the Cu CF diffuse out, may undergo the redox reaction in  $TaO_x$ , and are returned as  $Cu^+$  ions by the electric drift fields back to the Cu electrode or stay immobilized in TaO<sub>x</sub> material. The dissolution of the filament, triggered primarily by the Cu out-diffusion into the TaO<sub>x</sub> matrix, depends on the critical temperature reached in the constriction of the CF. The overall balance of heat stored in the nanofilament is given by the resistive Joule's heating of the nanofilament and via heat removal mainly by the heat sinks of the two relatively cold mesoscopic electrodes. The largest interface of the nanofilament is formed with the inert electrode (Pt, Ru, and Co) which forms the base of a truncated cone or a cylinder of the filament with the inert electrode (Figure 3). In this context, one notices that Ru has thermal conductivity of 119 W/Km almost twice those of Co and Pt of 69 W/Km (Table 1). Thus, lower thermal conductivity of the inert electrode requires less Joule's heating than an inert electrode with high thermal conductivity as the heat accumulates in the nanofilament in a shorter time than in the case of high thermal conductivity of the inert electrode. When inspecting the  $V_{res}$  voltages of the three devices in **Table 2**, one notices that the  $V_{res}$  values for Pt (-0.9 V) and Co (-1.0 V) devices are essentially the same, which correlates again very well with the same thermal conductivities of the two metals of 69 W/Km.

Since the Cu filament in all three devices serves as our probe into the analysis of the material properties of the three inert electrode metals (Ru, Pt, Co), it is instrumental to ensure that the nature of the Cu CF probe is the same in the three devices. To this end, we have measured  $R_{on}$  dependence on  $I_{cc}$  of the three devices. We find that all devices display the same dependence given in Eq. (1) with exponent n being very close to 1, and the constants A of eq.(1), being 2.0 V, 0.5 V, and 0.5 V, for Ru, Pt, and Co devices. These values correlate very well with the V<sub>set</sub> values for these devices given in **Table 2**. The high A value for Ru is consistent with the interpretation given in [1] that A reflects the lowest possible set voltage of the device.

Conductive filaments can also be fingerprinted by their temperature coefficient of resistance (TCR),  $\alpha$ , as defined by the temperature dependence of the R<sub>on</sub> resistance: R(T) = R(T<sub>o</sub>) × [1 +  $\alpha$ (T-T<sub>o</sub>)], which sensitively depends on the strength of the Cu filament. We have extracted the TCR from resistance measurements of R<sub>on</sub> of Cu CF as a function of temperature, T. We find for a weak Cu CF of R<sub>on</sub>  $\approx$  15 k $\Omega$  (corresponding to I<sub>cc</sub> = 10  $\mu$ A) following TCR values for the three devices: TCR (Ru device) = 0.00236 K<sup>-1</sup>, TCR(Pt-device) = 0.00235 K<sup>-1</sup>, and TCR(Co device) = 0.00235 K<sup>-1</sup>. It can be seen that they are almost identical. The same TCR measurements have been repeated for stronger (lower resistance) Cu CFs set at three orders of magnitude higher I<sub>cc</sub>, I<sub>cc</sub> = 10 mA. For I<sub>cc</sub> = 10 mA we obtain much lower R<sub>on</sub> value for the Cu filaments of 510  $\Omega$ , 230  $\Omega$ , and 315  $\Omega$  for the Ru, Pt, and Co devices, respectively. For the three robust CFs we obtain very similar TCR values are extracted: TCR (Ru device) = 0.0035 K<sup>-1</sup>, TCR(Pt device) = 0.0036 K<sup>-1</sup>, and TCR(Co device) = 0.0036 K-1, which are, again, very similar. These values are typical of strong Cu filaments; for comparison the TCR of bulk Cu is 0.0039–0.004 K<sup>-1</sup>. These results ensure that in all the three devices the Cu filaments have the same properties conferring, thus, confidence that the Cu CF may serve as a reliable probe into the properties of the inert electrode materials Ru, Pt, and Co.

## 5. Surface roughness studies of Ru, Pt, Co, and Cu

In this section, we investigate the surface roughness of Ru, Pt, Co, and Cu thin films (50 nm) as a function of anneals at elevated temperatures for two cases: free and passivated metal surfaces. The impact of SR of metal electrodes on local field enhancement, dielectric breakdown, including ReRAM performance is well known and has recently attracted a lot of interest. A review of the impact of surface roughness on numerous devices and phenomena, including gas breakdown, dielectric breakdown in RF MEMS devices, in triboluminescence, MIM structures, capacitors, and ReRAM memory cells can be found in [34]. As early as 1928, Eyring et al. [39] found that logarithms of currents of extracted electrons from asperities display linear relation with the reciprocal of electric field strength at the tip of an asperity. The asperity has been modeled as a prolate spheroid of length c and base radius b. A field enhancement factor has been derived:

$$\beta = \left(\frac{c/r}{\ln\left(2\frac{b}{r}\right) - 1}\right) \tag{3}$$

where  $r = b^2/c$ . For micro size asperities with  $c = 16 \ \mu m$  and  $b = 0.7 \ \mu m$  one obtains an enhancement factor of  $\beta = 187$ . Countless studies have confirmed since then the impact of the electric field enhancement factor on various physical systems [34].

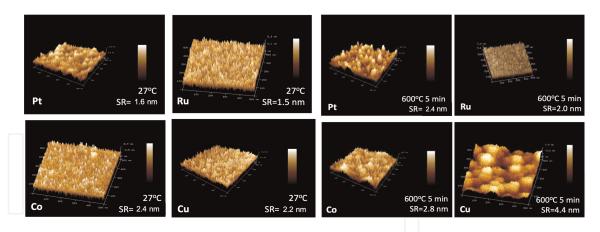

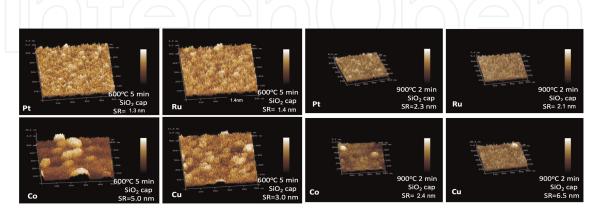

Separately from the ReRAM devices, we have deposited by EBPVD blanket layers of the four metals (Pt, Ru, Co, and Cu), each 50 nm thick, and using Rapid Thermal Annealing (RTA) annealed them at various temperatures with free and SiO<sub>2</sub>-passivated surfaces - mimicking, thus, conditions that are likely to occur in the actual ReRAM cell during the switching events. Using Atomic Force Microscope (AFM), we have measured the surface roughness of the Pt, Ru, Co and Cu at room temperature, that is, just after their depositions by EBPVD, and after anneals using RTA of the free surfaces at 425°C for 8 min, 600°C for 5 min, and at 900°C for 2 min. As the SR of free surfaces after an anneal at 425°C, 600°C, and 900°C are not expected to be entirely representative of what may happen inside the memory cells, where the critical surfaces are interfaced with a  $SiO_2$  or a  $TaO_x$  switching layer, we have passivated the surfaces of all metals with 30 nm SiO<sub>2</sub> layer and subjected the samples to the same anneals at 425°C for 8 min, at 600°C for 5 min, and at 900°C for 2 min. After the anneals are done, the 30 nm  $SiO_2$  layer has been removed by a soft buffer oxide etchant (BOE) etch, highly selective to the metals, to expose the surface of the inert metals for the subsequent AFM measurements. The results of surface roughness measurements are summarized in Table 3.

Several interesting observations can be drawn from **Table 3**. In general, the surface roughness of a free surface increases with increasing anneal temperature. This increase is much larger for free than for passivated surfaces. It can be seen that an anneal at 600°C or 900°C with a passivated surface, leads to a smoothing effect of the surface compared to a free metal surface. However, occasionally, some irregularities defy the general trend. For example, the surface roughness of Co annealed at 600° is higher with passivation than without it. It is seen that at room temperature (27°C) out

|    | 27°C | F.S. 600°C<br>5 min | F.S. 900°C<br>2 min | SiO <sub>2</sub> 425°C<br>8 min | SiO <sub>2</sub> 600°C<br>5 min | SiO <sub>2</sub> 900°C<br>2 min |

|----|------|---------------------|---------------------|---------------------------------|---------------------------------|---------------------------------|

| Pt | 1.8  | 2.4                 | 4.9                 | 1.6                             | 1.3                             | 2.3                             |

| Ru | 1.5  | 2.0                 | 4.2                 | 1.3                             | 1.4                             | 2.1                             |

| Co | 2.4  | 2.8                 | 14.0                | 7.3                             | 5.0                             | 2.4                             |

| Cu | 2.2  | 4.4                 | 12.0                | 4.1                             | 3.0                             | 6.5                             |

|    |      |                     |                     | $\sim$ ( ( $\sim$               |                                 |                                 |

Table 3.

Surface roughness of metal surfaces in nm as a function of temperature and presence or absence of a SiO<sub>2</sub> passivation layer. F.S. denotes a free metal surface annealed at different temperatures. SiO<sub>2</sub> denotes the cases in which the metal was covered by a 30 nm SiO<sub>2</sub> during the anneal, and the SiO<sub>2</sub> was removed by a soft oxide etch after the anneal [34] © The Electrochemical Society reproduced by permission of IOP Publishing. Chakraborty A, Al-Mamun M, Orlowski M. Impact of surface roughness and material properties of inert electrodes on the threshold voltages and their distributions of ReRAM memory cells" ECS J. Sol. St. Sci. Technol.2022;11:104007; DOI: 10.1149/2162-8777/ac9c91.

of the four metals the lowest surface roughness has ruthenium of 1.5 nm. The surface roughness of a free Pt surface increases moderately after the 600 and 900°C anneals to 2.4 and 4.9 nm, respectively. When, however, Ru (Pt) is covered during the anneal with SiO<sub>2</sub>, the surface roughness after 600°C anneal is measured to be only 1.4 nm (1.3 nm) and climbs to 2.1 nm (2.3 nm) at 900°C. Thus, the surface roughness of Ru and Pt with passivation, when annealed at 600°C, are even smaller than at 27°C. The low increase of surface roughness of Ru with temperature compared to other metals is consistent with the fact that Ru has the highest melting temperature (2334°C) of the four metals, see Table 1. The highest surface roughness of a free surface at 27°C is found for Cu and Co to be 2.2 nm and 2.4 nm, respectively. The surface roughness of Co increases to 2.8 nm after an anneal of 600°C for a free surface, but becomes very large for free surfaces annealed at 900°C yielding 14.0 nm for Co and 12 nm for Cu. One observes that with SiO<sub>2</sub> passivation the surface roughness increase is much more moderately and is capped at 5.0 nm for Co and by 6.5 nm for Cu. It is noted that the highest surface roughness for Cu and Co and correlates well with their low melting temperatures, Cu (1084°C) and Co(1495°C). The SR of Pt displays an intermediate behavior between Ru and Co. The SR of Pt is smaller than that of Co and Cu but is higher than that of Ru. After anneals at 425, 600, and 900°C with passivated surfaces, the SR Pt increases moderately slightly more than that of Ru. This correlates well with the melting temperature of Pt ( $T_m = 1770^{\circ}C$ ) and that of Ru ( $T_m = 2335^{\circ}C$ ). These results for surface roughness apply to thin layers deposited by EBPVD. Similar trends are expected to hold for other deposition techniques. It is known, for example, that SR of Pt films deposited by plasma enhanced atomic layer deposition [40] is lower than that of PVD and lies usually below 1 nm. Nevertheless, because the metals are deposited by the same method where the deposition rate has been kept the same for all four metals, the surface roughness results should be indicative of their differences in material properties.

**Figure 4** shows the AFM pictures of free surfaces of the metals at room temperature (27°C) and after an RTA anneal at 600°C for 5 min. One can see that the Ru surface is most stable of all metals, while the surface of Cu undergoes a significant reconstruction. The cases of Co and Pt lie in-between, showing a strong correlation between surface roughness and the corresponding melting temperature. Thus, with the exception of Cu, the topology of surface and surface roughness of the metals do not change appreciably. In case of Cu, however, a complete surface reconstruction is

#### Figure 4.

AFM pictures of free surfaces of Pt, Ru, Co, and Cu at 27°C and at annealed at 600°C for 5 min with the average surface roughness indicated [34] © The Electrochemical Society reproduced by permission of IOP Publishing. Chakraborty A, Al-Mamun M, Orlowski M, "Impact of Surface Roughness and Material Properties of Inert Electrodes on The Threshold Voltages and Their Distributions of ReRAM Memory Cells" ECS J. Sol. St. Sci. Technol.2022;11:104007; DOI: 10.1149/2162-8777/ac9c91.

being observed. While at room temperature, the Cu surface resembles that of the inert electrode metals Pt, Ru, and Co, the Cu surface at 600°C shows formation of large clumps or hillocks of more than 100 nm size in diameter, while the finer dendrites on those hillocks appear to have the same needle-like structure as Cu at the 27°C. The similarities extend even to the surface morphology as both surfaces for Cu and Co undergo surface reconstruction, particularly severe in case of Cu and Co at 900°C. In **Figure 5**, the surface roughness of the metals is shown after being passivated and annealed at 600 and 900°C with a SiO<sub>2</sub> passivation layer on top. Before the AFM measurement the SiO<sub>2</sub> layer has been removed by a soft HF etch.

At 600°C, for Cu and Co, one can see hillock formation with SR higher than that at 27°C but significantly smaller than that of the free surfaces annealed at the same temperatures. It can also be seen that for Ru and Pt the SR is much smaller than for free surfaces and even smaller than their SR at room temperature. Thus, with respect to the surface roughness, the metals Pt and Ru may rightfully be called inert metals with respect to the thermal properties of their surfaces. After a 900°C anneal, the topography of the Ru, Pt, and Co surfaces does not change much, and the SR increases

#### Figure 5.

AFM pictures of passivated surfaces of Pt, Ru, Co, and Cu annealed at 600 and 900°C. Before taking AFM measurements the SiO2 passivation layer was stripped by a soft etch [34] © The Electrochemical Society reproduced by permission of IOP Publishing. Chakraborty A, Al-Mamun M, Orlowski M. "Impact of Surface Roughness and Material Properties of Inert Electrodes on The Threshold Voltages and Their Distributions of ReRAM Memory Cells", ECS J. Sol. St. Sci. Technol.2022;11:104007; DOI: 10.1149/2162-8777/ac9c91.

moderately over those measured at 27°C and the anneal at 600°C. Overall, it can be concluded from **Table 3** that a passivation layer suppresses the increase of SR with increasing temperature significantly.

We have also measured the surface roughness of the switching layers  $SiO_2$  and  $TaO_x$ , deposited in both cases by PVD directly on oxidized Si-wafers. We obtain SR at room temperature of 0.9 and 1.0 nm, for  $SiO_2$  and  $TaO_x$ , respectively, and annealed at 600°C the SR drops to 0.53 and 0.62 nm, respectively. The reflowing property of  $SiO_2$  and  $TaO_x$  has a significant smoothing effect on the surface roughness of the inert electrode. Our results confirm the findings that nanometer thin  $SiO_2$  [41] and  $TaO_x$  [42] have much better reflow properties than their mesoscopic or bulk counterparts which need doping such as boron and/or phosphorous to lower the reflow temperature.

The reflow properties of SiO<sub>2</sub> and TaO<sub>x</sub> layers have been confirmed by measurements of surface roughness of Ru covered with SiO<sub>2</sub>, the electrolyte with the smallest native surface roughness. Even the mere deposition of  $SiO_2$  has a smoothing effect. In case of Ru, the SR at room temperature is 1.5 nm, but when covered with PVD-SiO<sub>2</sub> the surface roughness of the SiO<sub>2</sub>/Ru bilayer is only 1.2 nm. Since SR of SiO<sub>2</sub> deposited directly on the oxidized Si wafer is 0.9 nm, it can be seen that the composite surface roughness of the two layers is not additive and that  $SiO_2$  exerts a smoothing effect. If the cumulative SR were additive, the SR would add up to 2.4 nm. Even more remarkably is the smoothing effect of  $SiO_2$  at higher temperatures: the surface roughness of SiO<sub>2</sub> on Ru after the anneals of 250°C for 5 min, 600°C for 5 min, and 900°C for 2 min remains at a more or less constant value of 1.3 nm. This is contrasted with the surface roughness of a free Ru surface after the 900°C anneal when the  $SiO_2$  layer has been removed after the anneal of 2.1 nm and the SR of a free Ru surface after 900°C anneal of 4.2 nm. Thus, dielectrics such as  $SiO_2$  or  $TaO_x$  display even stronger surface smoothing action at elevated temperatures. These results suggest a method of reducing the surface roughness of metals by depositing a thin sacrificial layer of dielectric such as TaO<sub>x</sub>, or SiO<sub>2</sub> followed by an anneal at moderate temperatures such as 425°C before removing the passivation layer by a soft BOE etch.

Finally, we wish to comment on how the surface roughness relates to the electric field enhancement factor,  $\beta$ , given in Eq. (3). The  $\beta$  enhancement factor depends largely on the curvature radius at the top of an asperity. Surface roughness, on the other hand, quantifies only the deviations of the asperities in the direction normal to the surface and does not account for the curvature radius of the tip. Nevertheless, as seen from **Figure 4**, the surface morphology of the four metals at room temperature is very similar and the respective field enhancements may still be expected to correlate well with the surface roughness as a lump parameter.

## 6. Degraded reliability and endurance of Cu/TaO<sub>x</sub>/Ru device

The major drawback of the Ru devices as compared to their Pt counterparts is their limited switching capacity. While Pt devices can be switched repeatedly back and forth for at least 220 times, Ru devices are becoming non-resettable after several setreset operations (usually less than 13), and sometimes even after the first set operation, when the set operation is performed at high  $I_{cc}$ . In some cases, it was even difficult to reset a high resistance Cu filament in a Ru device formed at  $I_{cc}$  as low as 5  $\mu$ A. The failure of the Ru devices after a few switching cycles is likely to be related to the specific geometric configuration of the Cu filament which may be caused either by

the diminished stopping power of the Ru electrode for Cu diffusion into the Ru film or by an increased surface diffusion as compared to that for the Pt electrode.

It is well known that even in extant ReRAM devices, including Pt devices, it is difficult and sometimes impossible to reset the cell if the cell has been set at high I<sub>cc</sub>. For a low I<sub>cc</sub>, the shape of the CF can be approximated by a truncated cone as shown in (**Figure 3a**) where the bulk of the CF's resistance resides in the tip of the cone. Since during the reset the power dissipated in the filament is equal to  $I_{res}^2 \times R_{on}$ , the highest temperature is reached in the constriction at the tip of the cone, where the rupturing of the filament is easy. At high I<sub>cc</sub>, the R<sub>on</sub> decreases sharply by adding Cu atoms to the upper section of the cone, rendering filament's shape more and more cylindrical (**Figure 3b**). In this case, the maximum temperature, in the absence of any pronounced constriction, is reached in the middle section of the cylinder, where the low resistance filament is relatively strong. Hence, rupturing of the CF becomes difficult or impossible.

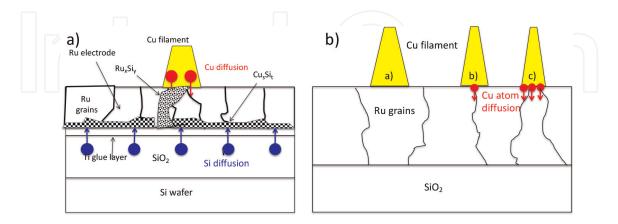

The cylindrical shape of the CF may also be obtained if the base of the cone in contact with Ru electrode erodes, see Figure 6. As the bottom base of the CF is reduced, while new Cu<sup>+</sup> ions are added from the top during the set operation, the shape of the filament will transform gradually into a cylindrical shape. There are several possible mechanisms for the erosion of the base of the filament: (i) Cu surface diffusion along the Ru interface (ii) crystallization of Ru and out-diffusion of Cu along the Ru grain boundaries, (iii) formation of Cu and Ru silicides. Those degradation mechanisms are depicted in Figure 6a and will be discussed further in Section 8. Whereas, with a nearly perfect stopping power, the shape of the filament in the Pt device can be assumed to remain conical with more or less sharp tip at the Cu electrode, the shape of the Cu filament in a Ru device is more cylinder-like, especially, when the Ru device was self-annealed by undergoing several set-reset switching cycles. We find also large variability of performance among Ru devices becoming noticeable after a few switching cycles. This variability may be explained by the relative location of the Cu filament with respect to the locations of the Ru grain boundaries as illustrated in Figure 6b. When there is no such overlap, the cell would perform well for several switching cycles. If, however, there is overlap of the base of

#### Figure 6

(a) Possible mechanisms of the hypothesized degradation of the Ru electrode. Elevated local temperatures in the immediate vicinity of the filament may cause Si diffusion into Ru, possibly along Ru grain boundaries and lead to  $Ru_xSi_y$  reactions. Cu may use the Ru grain boundaries as diffusion paths and may also undergo a silicidation reaction. (b) Relative location of the Cu filament with respect to the Ru grain boundaries likely to explain the large variability of performance see in Ru devices [35] © The Electrochemical Society reproduced by permission of IOP Publishing. Al-Mamun M, King, S, Orlowski M. "Thermal and Chemical Integrity of Ru Electrode in Cu/TaOx/ Ru ReRAM Memory Cell", ECS J. Sol. St. Technol.2019; 8: N220; DOI: 10.1149/2.0121912jss.

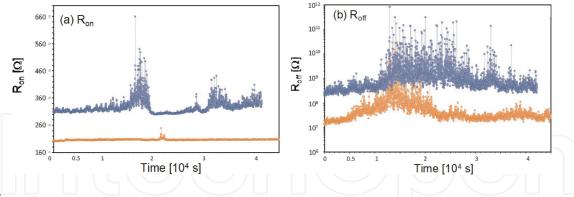

Figure 7.

The retention of Ru and Pt devices (a) for the on-state characterized by  $R_{on}$ , and (b) for the off-state characterized by  $R_{off}$  [35] © The Electrochemical Society reproduced by permission of IOP Publishing. Al-Mamun M, King, S, Orlowski M. "Thermal and Chemical Integrity of Ru Electrode in Cu/TaOx/Ru ReRAM Memory Cell", ECS J. Sol. St. Technol.2019; 8: N220; DOI: 10.1149/2.0121912jss.

the filament with one or more grain boundaries, then Cu atoms may be easily depleted from the filament via enhanced Cu diffusion along the grain boundaries.

In this context, we wish to mention that in ref. [21] other related ReRAM devices, such as  $Cu/TaO_x/Ti$  and  $Cu/TaO_x/Ta$  have been compared to the benchmark device  $Cu/TaO_x/Pt$  and were found significantly inferior to the Pt device. The Ru device is found to perform better than the Ti and Ta devices.

As already mentioned, in terms of endurance Pt devices are by far best, switching over 200 times, followed by Co devices that can be switched at optimum conditions up to 40 times, while Ru devices could be switched at best 13–14 times. The retention of both binary states characterized by R<sub>on</sub> and R<sub>off</sub> for all three devices is good. In **Figure 7** the retention of the on- and off-states for Ru and Pt devices is shown.

It can be seen from **Figure 7** that the level of noise for Ru devices is higher than for Pt devices for both bit states, characterized by  $R_{on}$  and  $R_{off}$ . While  $R_{off}$  fluctuations of Ru devices are irrelevant as the outlier lie in the tens of G $\Omega$  range, the outliers for  $R_{on}$  are more of a concern, as its variation can be as high as 75%. Such large fluctuations could pose, inter alia, a problem for the multibit storage applications and for the stability of the sense amplifiers when reading the cell. For comparison the variations of  $R_{on}$  and  $R_{off}$  in Pt devices are less than 10% as discussed in more detail in ref. [35].

Before focusing on specific mechanisms that degrade the inertness properties of Ru films, we will discuss performance changes of nominally the same devices caused by their different integration scheme, called here the "embedment" aspect.

## 7. Impact of embedment on the performance of Cu/TaO<sub>x</sub>/Ru devices

To study the relative degradation of Cu/TaO<sub>x</sub>/Ru vs. Cu/TaO<sub>x</sub>/Pt devices, we have manufactured two nominally identical Cu/TaO<sub>x</sub>/Ru devices (where the layers of the device proper have been processed at the same time), however embedded differently on the Si wafer as shown in **Figure 2b** and **c**. The Ru device A has the same substrate as the Pt device, that is Ti(25 nm)/SiO<sub>2</sub>(730 nm)/Si-wafer, while the Ru device B is manufactured on the layer stack Ti(20 nm)/TaO<sub>x</sub>(30 nm)/SiO<sub>2</sub>(730 nm)/Si-wafer. Thus, Ru device B has an additional TaO<sub>x</sub>-30 nm layer inserted between SiO<sub>2</sub> and Ti layers as shown in **Figure 2b**. We find that the Ru device B with the additional TaO<sub>x</sub> layer shows much better performance (up to 37 switching cycles) than the Ru device A, at all test conditions, although to a varying degree. The degree of the improvement in the switching properties between the two embedment scenarios, depends on the amount of internal Joule's heat exposure and varies with the levels of applied compliance current and ramp rate, which control the amount of heat according to Eq. (2). The highest improvement of device B over the device A is found for  $I_{cc}$  = 50  $\mu$ A and rr = 0.2 V/s (high heat dissipation), and little improvement in performance between the two devices can be observed for the condition  $I_{cc} = 1 \mu A$  and rr = 2.0 V/s (small heat deposition) - a regime where both devices perform the best. It is found that at  $I_{cc}$  = 50 µA and rr = 0.2 V/s the Ru device A does not display resistive switching behavior at all, i.e., the device is dysfunctional. The device A cannot be reset after the filament has been formed the very first time. However, when the reset ramp rate is increased fivefold to rr = 1 V/s - thus reducing the Joule's heat dissipated in the device - the device A can be neither set or, if the set operation is eventually successful, the device cannot be reset, that is, the resistive switching cell has been permanently damaged. In contrast, device B, with the additional  $TaO_x$ , layer shows some resistive switching behavior for a few cycles (maximum 6). Hence, it can be concluded that high heating effects are detrimental to both devices. But, while Ru device B displays some, if small, degree of resistive switching behavior (5–6 switching cycles), Ru device A does not display resistive switching at all. Keeping the reset ramp rate at 0.2 V/s but now reducing the  $I_{cc}$  current from 50  $\mu$ A to 1  $\mu$ A, we observe improved resistive switching behavior for both devices with the frequency of the Ru devices B being twice as high (maximum 22 cycles) as for the Ru devices A (maximum 10 cycles). These results clearly demonstrate that the endurance of the device is directly related to the amount of heat deposited in the devices leading to some adverse reactions which are mitigated by the insertion of the TaO<sub>x</sub> layer subjacent to the Ru film.

Another embedment case has been implemented when two identical devices Cu/ TaO<sub>x</sub>/Ru have been fitted with different glue layers as shown in **Figure 2c** [2]. Here, the Ti glue layer for the inert electrode has been replaced with a Cr glue layer of 30 nm. It was found that the electric performance of nominally identical devices depends sensitively on the nature of the glue layer. We find that the V<sub>res</sub> value for Ru/ Cr is 0.4 V larger (V<sub>res(Ru/Cr)</sub> = -3.8 V) than for the Ru/Ti device (V<sub>res(Ru/Ti)</sub> = -3.4 V). This could have been predicted on the grounds of four times higher thermal conductivity for Cr [94 W/mK] than that of Ti [22 W/mK] leading in case of Ru/Cr to much higher heat removal rate from the Cu CF during the reset operation, as discussed already in Section 4. In case of Ru/Ti, the Joule's heat generated in the filament cannot be as easily dissipated, and lingers therefore for some time around the hot spot in the filament, as in the case of the Ru/Cr device. Both embedment experiments suggest that the heat generated in the memory cell may trigger some kind of chemical or grain growth reactions that can be somewhat mitigated by the insertion of the TaO<sub>x</sub> layer.

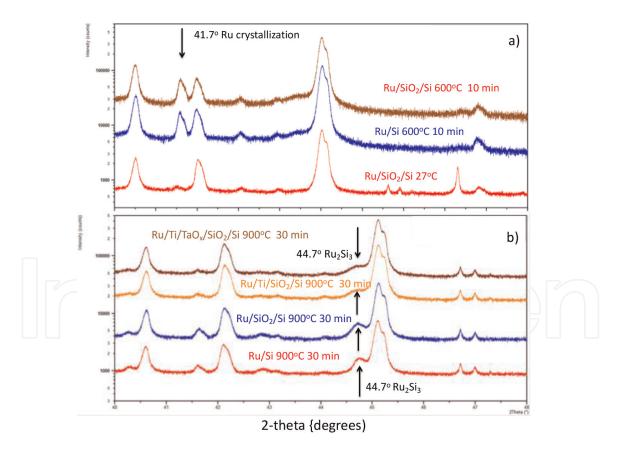

#### 8. XRD studies of different embedment of Ru layers

In order to find out what kind of chemical reactions may occur in the Ru devices at various temperatures, we have manufactured among many auxiliary blanket multilayer structures on oxidized Si wafers following samples: (i) Ru(50 nm)/Si, (ii) Ru (50 nm)/SiO<sub>2</sub>(611 nm)/Si, and (iii) Ru(50 nm)/Ti(40 nm)/TaO<sub>x</sub>/SiO<sub>2</sub>(611 nm)/Si that we consider here. The auxiliary samples are bound to avail some information on Ru

crystallization and the presence of new materials such as silicides using the XRD technique. The XRD measurements have been performed on the three samples for three annealing conditions: (i) unannealed, that is, at 27°C, (ii) annealed at 600°C for 10 min, and (iii) annealed at 900°C for 30 min. In **Figure 8a**, a Ru crystallization peak at 42.15° can be seen on the XRD spectra for all samples with a Ru layer at 27°C and after an anneal at 600°C, and 900°C. This is in agreement with XRD studies of similar layer systems reported in [43]. XRD signals for samples of Ru/Si at 300 K, Ru/Si after an RTP anneal at 600°C for 10 min, and for Ru/SiO<sub>2</sub>/Si after an anneal at 600°C for 10 min are also shown in **Figure 8a**. It is seen that a Ru<sub>2</sub>Si<sub>3</sub> crystallization peak appears as a result of the 600°C anneal. An XRD signal (more of a shoulder than a peak) of ruthenium silicide Ru<sub>2</sub>Si<sub>3</sub> at 44.7° is observed next to a broad Si wafer peak only after 900°C anneal as shown in Figure 8a. This is in agreement with observations of Ru<sub>2</sub>Si<sub>3</sub> XRD detection made in ref. [44]. We observe this peak on the following samples: Ru/ Si, Ru/SiO<sub>2</sub>/Si, Ru/Ti/SiO<sub>2</sub>/Si, and Cu/Ru/Ti/SiO<sub>2</sub>/Si. The strongest Ru<sub>2</sub>Si<sub>3</sub> signal can be seen for the Ru/Si and Ru/SiO<sub>2</sub> samples. From comparison of Figure 8b with Figure 8a it, can be seen that the XRD signal at 44.7° is absent for the anneal at 600° C and also for the unannealed sample. The Ru<sub>2</sub>Si<sub>3</sub> shoulder is either not there or very weak, as seen in **Figure 8b**. From **Figure 8b** it is also seen that the Ru<sub>2</sub>Si<sub>3</sub> peak at 41.7°

#### Figure 8.

XRD spectra of (a) three-layer structures:  $Ru/SiO_2/Si$  as deposited, Ru/Si and  $Ru/SiO_2/Si$  after a 600°C 10 min anneal. The Ru crystallization peak has been also observed at other layer structures with a Ru layer only after a 600°C anneal. The peak is very weak at room temperature and disappears after an anneal at 900°C for 30 min. (b) Four-layer structures annealed at 900°C for 30 min: Ru/Si,  $Ru/SiO_2/Si$ ,  $Ru/Ti/SiO_2/Si$  and  $Ru/Ti/TaO_x/SiO_2/Si$ . On all structures a  $Ru_2Si_3$  shoulder can be observed at 44.7°C next to a large signal 45.12°C which stems from the Si wafer as verified by XRD spectra on Si and  $SiO_2/Si$  structures [35] © The Electrochemical Society reproduced by permission of IOP Publishing. Al-Mamun M, King, S, Orlowski M. "Thermal and Chemical Integrity of Ru Electrode in Cu/TaOx/Ru ReRAM Memory Cell", ECS J. Sol. St. Technol.2019; 8: N220; DOI: 10.1149/2.0121912jss.

#### Figure 9.

XRD spectra of the same layer structures as in **Figure 8b** but capped by Cu layer. A Cu silicide peak can be observed at  $44.8^{\circ}$  only after the anneal at  $900^{\circ}$ C [35].

disappears at 900°C, again in agreement with observations made in [43]. In layer structures of **Figure 8b** that have been capped with an additional Cu layer, the XRD spectra show formation of copper silicide at 44.8° only at 900°C as shown in **Figure 9**. Thus, at high temperatures Cu and Si may diffuse through Ru/Ti and Ru/Ti/TaO<sub>x</sub> layers to undergo a copper silicide reaction.

In summary, the XRD studies have revealed formation of Ru grains, formation of two kinds of Ru silicides,  $Ru_2Si_3$  and  $Ru_2Si_3$ , and that insertion of the  $TaO_x$  layer between  $SiO_2$  and Ti acts as a diffusion barrier for Si and suppresses the  $Ru_2Si_3$  reaction. The XRD study corroborates not only the difference in electrical performance between Pt and Ru device but also among the Ru devices embedded on different substrates. Considering these results, it appears that while the inertness properties of Pt and Ru are similar up to about 200°C, at elevated temperatures, Pt is by far more inert than Ru ensuring superior switching performance of the Cu/TaO<sub>x</sub>/Pt over the Cu/TaO<sub>x</sub>/Ru device.

## 9. Conclusions

Against the backdrop of analogously characterized Cu/TaO<sub>x</sub>/Pt and Cu/TaO<sub>x</sub>/Co devices, we have used electrical properties of a Cu/TaO<sub>x</sub>/Ru ReRAM cell, to elucidate material properties of 50 nm ruthenium films. The circumstance that an electric switching operation of a ReRAM cell allows to raise temperature of the Cu filament inside a ReRAM memory cell from 27°C up to ca. 1100°C, in a controlled way [45], turns the Cu/TaO<sub>x</sub>/Ru device into a nano-laboratory for investigation of the material properties of Ru at different temperatures. The present electric analysis of the devices has been complemented by extensive material studies of relevant layer systems annealed at various temperatures using XRD, and by studies of the surface roughness of free and passivated metal surfaces, both unannealed as well as annealed at elevated temperatures, using AFM. From these studies, a consistent picture emerges allowing a compelling explanation of

all differences of the ReRAM cell's electric characteristics in terms of the Ru material properties.

$Cu/TaO_x/Ru$  devices compared to  $Cu/TaO_x/Pt$  devices have higher forming, set, and reset voltages. The higher V<sub>form</sub> and V<sub>set</sub> voltages can be partly or entirely attributed to the work function difference between Pt and Ru of 1.6 eV and partly to the significant difference in surface roughness between Pt and Ru. The higher V<sub>res</sub> voltage for Ru device than for Pt or Co devices is a consequence of much higher thermal conductivity of Ru than that of Pt and Co. It was also found that while Pt devices can be switched more than hundred times, the number of switching cycles of Ru devices is very limited. The performance deterioration of Ru devices is particularly conspicuous when the cell is exposed to high Joule's heat dissipation during the set and reset switching cycles. At low Joule's heat dissipation, the switching performance of both Ru and Pt devices is initially comparable. The Joule's heat dissipation is, thus, a major factor determining the endurance properties of the device as it triggers degradation of the inertness properties of Ru caused by grain crystallization as well as silicide formation. The degraded integrity of the inert electrode appears to have a major impact on the Cu diffusional fluxes which, in turn, determine the geometrical shape of the Cu conductive filament. Additional embedment experiments have corroborated these conclusions. In an embedment experiment, an identical device proper is embedded in different ways on the Si wafer. It has been demonstrated that the electrical switching properties of nominally the same resistive switching device Cu/TaO<sub>x</sub>/Ru, when embedded differently, Cu/TaO<sub>x</sub>/Ru/Ti/SiO<sub>2</sub>/Si vs. Cu/TaO<sub>x</sub>/ Ru/Ti/TaO<sub>x</sub>/SiO<sub>2</sub>/Si, differ substantially. This is the result of chemical and structural interactions of the device proper with its immediate environment. The chemical and structural changes of Ru films are brought about by the nanometer dimension of the layers involved and triggered by Joule's heat deposition during the switching of the ReRAM cell. This finding points to a broader and critical impact of the device's embedment on its structural, material integrity, and, eventually, its electrical reliability and endurance properties. The insertion of a TaO<sub>x</sub> layer between the SiO<sub>2</sub> and Ti glue layer suppresses the Ru crystallization and silicide reaction somewhat and, eo ipso, improves the electrical performance and endurance of the Ru device on the Ti/TaO<sub>x</sub>/SiO<sub>2</sub>/Si substrate as compared to the Ru device manufactured on the Ti/ SiO<sub>2</sub>/Si substrate. Embedment structures with different glue layers (Cr vs. Ti) have corroborated the role of thermal conductivity in determining the actual value of V<sub>res</sub>. The surface roughness studies have shown a strong impact of surface roughness on V<sub>form</sub>, evidenced by the three devices. Furthermore, it turned out that deposition of a sacrificial dielectric layer followed by an anneal leads to a drastic reduction of surface roughness of a metal.

The advantages and disadvantages of Ru over Pt devices are summed up in **Table 4**. The most important disadvantage of the Ru device is its limited switching cycling ability. This could be perhaps addressed in future work by minimizing Joule's

| Inert electrode | Threshold voltages | retention | Endurance cycling ability | BEOL integrability |

|-----------------|--------------------|-----------|---------------------------|--------------------|

| Ru              | high (-)           | (+)       | <14 (-)                   | (++)               |

| Pt              | low (+)            | (++)      | >200 (++)                 | (-)                |

Table 4.

Figure of merit comparison between Ru and Pt ReRAM device. (+) and (-) denote advantages and disadvantages, respectively.

heat exposure during the switching operations. The use of ruthenium in ReRAM cells appears to be viable if the internal temperature of the cell could be limited to temperature not exceeding ca 350°C, which puts a severe constraint on how the cells are being programmed and erased. Up to 440°C, Ru exhibits similar stopping power and inertness properties as Pt. Hence, the deployment of Ru in BEOL, where the temperature during a circuit operation does not exceed 440°C [46], appears to be viable. However, at elevated temperatures above ca 400°C, the inertness properties of Pt are vastly superior to those of Ru.

# Author details

Amrita Chakraborty, Mohammad Al-Mamun and Marius Orlowski<sup>\*</sup> Bradley Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, VA, USA

\*Address all correspondence to: m.orlowski@vt.edu

# IntechOpen

© 2023 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

# References

[1] Liu T, Kang K, El-Helw S, Potnis T, Orlowski M. Physics of the voltage constant in multilevel switching of conductive bridge resistive memory. Japanese Journal of Applied Physics. 2013;**52**:084202. DOI: 10.7567/ JJAP.52.084202

[2] Al-Mamun M, Orlowski M. Challenges to implement resistive memory cells in the CMOS BEOL. ECS Transactions. 2017;**80**(6):13-23

[3] Benasconi R, Magagnin L. Reviewruthenium as diffusion barrier layer in electronic interconnects. Journal of ECS. 2019;**166**(1):D3219-D3225

[4] Wen LG, Adelmann C, Pedreira OV, Dutta S, Popovici M. Ruthenium metallization for advanced interconnects.

IEEE Internet Interconnect Technique.

2016;2016:34-36

[5] Zahedmanesh H, Gonzales VV,Tokei Z. Nano-ridge bending during conformal ruthenium metallization. ACS Applied Nano Materials. 2021;4: 5643-5648

[6] Tada M, Okamoto K, Sakamoto T, Miyamura M, Banno N, Hada H. Polymer solid-electrolyte switch embedded on CMOS for nonvolatile crossbar switch. IEEE Transactions on Electrical Development. 2011;**58**:4398

[7] The International Technology Roadmap For Semiconductors. 2015. Available from: http://www.semiconduc tors.org/clientuploads/Research\_Tech nology/ITRS/2015

[8] Liu TY, Yan TH, Scheuerlein R, Chen Y, Lee JK, Balakrishnan G. A 130.7mm<sup>2</sup> 2-layer 32Gb ReRAM memory device in 24nm technology. In: 2013 IEEE Sol.-S. Circ. Conf. Digest. San Francisco. 2013. pp. 210-211. DOI: 10.1109/ ISSCC.2013.6487703

[9] Orlowski M, Ghosh G, Verma A. Method to manufacture highly conductive vias & PROM memory cells by application of electric pulses. US Patent Application Publication 2019/ 0058120 A1, Feb. 21, 2019

[10] Yang JJ, Strukov DB, Stewart DR. Memristive devices for computing. Nature Nanotechnology. 2013;**8**:13

[11] Strukov B, Snider DR, Stewart R, Williams RS. The fourth circuit element. Nature. 2008;**453**:80

[12] Chua LO, Kang SM. Memristive devices and systems. Proceedings of the IEEE. 1976;**64**(2):209-223. DOI: 10.1109/ PROC.1976.10092

[13] An H, Al-Mamun MS, Orlowski MK, Yi Y. Learning accuracy analysis of memristor-based nonlinear computing module on long short-term memory. In: Proceedings of the International Conference on Neuromorphic Systems, Knoxville, Tennessee. ACM: New York, NY; 2018

[14] Beigi MV, Memik G. Thermal-aware optimizations of ReRAM-based neuromorphic computing systems. In: Proc. 55th Annual Des. Autom. Conf. San Francisco, 24-28 June 2018. p. 324

[15] Azghadi MF, Chen YC, Eshraghian JK, Chen J, Lin CY, Amirsoleimani A, et al. Complementary metal oxide semiconductor and Memristive hardware for neuromorphic computing. Advanced Intellectual System. 2020;**2**:1900189

[16] Waser R, Dittmann R, Staikov G, Szot K. Redox-based resistive switching memories – Nanoionic mechanisms, prospects, and challenges. Advanced Materials. 2009;**21**:2632

[17] Kaeriyama S, Sakamoto T, Sunamura H, Mizuno M, Kawaura H, Hasegawa T, et al. A nonvolatile programmable solid-electrolyte nanometer switch. IEEE Journal of Solid-State Circuits. 2005;**40**:168

[18] Kozicki MN, Park M, M. Mitkova M. Nanoscale memory elements based on solid-state electrolytes. IEEE Transactions on Nanotechnology. 2005;4:331

[19] Fowler BW, Chang YF, Zhou F, Wang Y, Chen PY, Xue F, et al. Electroforming and resistive switching in silicon dioxide resistive memory. RSC Advances. 2015;5:21215-21236

[20] Xiao B, Gu T, Tada T, Watanabe S. Conduction paths in Cu/a-Ta2O5/Pt atomic switch: First-principles studies. Journal of Applied Physics. 2014;**115**: 034503

[21] Ghosh G, Kang Y, King SW, Orlowski M. Role of CMOS Back-end metals as active electrodes for resistive switching in ReRAM cells. ECS Journal of Solid State Science and Technology. 2017;**6**(1):N1-N9

[22] Calderoni A, Sills S, Cardon C,

Faraoni E, Ramaswamy N. Engineering ReRAM for high-density applications.

Microelectronic Engineering. 2015;

137:145

[23] Ohno T, Samukawa S. Resistive switching in a few nanometers thick tantalum oxide film formed by a metal oxidation. Applied Physics Letters. 2015; **106**:173110

[24] Kurnia F, Jung C, Lee B, Liu C. The evolution of conducting filaments in forming-free resistive switching Pt/TaOx/Pt structures. Applied Physics Letters. 2015;**107**:073501

[25] Kawahara A, Azuma R, Ikeda Y, Kawai K, Katoh Y, Tanabe K, et al. An 8Mb multi-layered cross-point ReRAM macro with 443MB/s write throughput. IEEE International Solid-State Circuits Conference. 2012;**2012**:432-434. DOI: 10.1109/ISSCC.2012.6177078

[26] Rullan J, Ishizaka T, Cerio F, Mizuno S, Yang CC. Low-resistance wiring and 2xnm void-free fill with CVD ruthenium liner and direct seed copper. Solid State Technology. 2016;**2016**:432

[27] Standaer T, Beique G, Chen H-C, Chen S-T, Hamieh B, Lee J. BEOL process integration for the 7nm technology node. IEEE Interconnect Technical Conference. 2016;**2016**:2-4. DOI: 10.1109/IITC-AMC.2016.7507636

[28] Masalski TB. Cu-Ru Phase Diagram, in Binary Alloy Phase Diagrams, Editors Masalski, Okamoto. Materials Park: American Society of Metals; 1990. p. 1467

[29] Kang Y, Verma M, Liu T,

Orlowski M. Formation and rupture of multiple conductive filaments in Cu/ TaO<sub>x</sub>/Pt device. ECS Solid State Letters.

2012;1:48-50

[30] Liu T, Kang Y, Verma M, Orlowski M. I–V characteristics of antiparallel resistive switches observed in a single Cu/TaO<sub>x</sub>/Pt Cell. IEEE Electrode Deviation Letters. 2012;**33**:429

[31] Liu T, Verma M, Kang Y, Orlowski M. Coexistence of Bipolar and Unipolar Switching of Cu and Oxygen Vacancy Nanofilaments in Cu/TaOx/Pt Resistive Devices. ECS Solid State Letters. 2012;1:Q11

[32] Ghosh G, Orlowski M. Write and erase threshold voltage interdependence

in resistive switching memory cells. Transactions on IEEE Electronic Devices. 2015;**62**:2850

[33] Ghosh G, Orlowski M. Correlation between set and reset voltages in resistive RAM cells. Current Applied Physics. 2015;**15**:1124

[34] Chakraborty A, Al-Mamun M, Orlowski M. Impact of surface roughness and material properties of inert electrodes on the threshold voltages and their distributions of ReRAM memory cells. ECS Journal of Solid State Science Technology. 2022;**11**:104007

[35] Al-Mamun M, King S, Orlowski M. Thermal and chemical integrity of Ru electrode in Cu/TaOx/Ru ReRAM memory cell. ECS Journal of Solid State Technology. 2019;**8**:N220

[36] Ali R, Fan Y, King SW, Orlowski M. Modeling and simulation of Cu diffusion and drift in porous CMOS backend dielectrics. APL Materials. 2018;**6**: 066101

[37] Al-Mamun S, Orlowski M. Performance degradation of nanofilament switching due to Joule. Heat Dissipation Electronics. 2020;**9**(1):127

[38] Al-Mamun M, Chakraborty A, Orlowski M. Methodology for Mitigation of ReRAM Reliability Issues Caused by Thermal Cross-Talk. 2022 submitted for publication

[39] Eyring C, Milikan R. Field currents from points. Physical Review. 1928;**31**: 900

[40] Kim HJ, Kaplan KE, Schindler P, Xu S, Winterkorn MM, Heinz DB, et al. Electrical properties of ultrathin platinum films by plasma enhanced atomic layer deposition. ACS Applied Materials & Interfaces. 2019;**11**:9594 [41] Simpson DL, Crosswell RT, Reisman A, Temple D, Williams CK. Planarization processes and applications - I. Undoped GeO2-SiO2 glasses. Journal of Electro-Chemical Society. 1999;**146**(10):3860

[42] McKinley KA, Sandler NP. Tantalum pentoxide for advanced DRAM applications. Materials Research Society Symposium Proceedings. 1997;**446**: 299-307

[43] Peterson CS, Baglin JE, Dempsy JJ, La Placa S. Silicides of ruthenium and osmium: Thin film reactions, diffusion, nucleation, and stability. Journal of Applied Physics. 1982;**53**:4886

[44] Arunagiri TN, Zhang Y, Chyan O,El-Bouanani M, Kim MJ, Chen KH, et al.5nm ruthenium thin film as a directlyplateable copper diffusion barrier.Applied Physics Letters. 2005;86:083104

[45] Al-Mamun M, Orlowski M. Electron Tunneling between vibrating atoms in a copper nano-filament. Scientific Reports. 2021;**11**:7413

[46] Jenkins M, Austin DZ, Conley JF, Ghosh G, Orlowski M, King SW. Review—Beyond the highs and lows: A perspective on the future of dielectrics research for Nanoelectronic devices. ECS Journal of Solid State Science & Technology. 2019;8:N159