## University of Texas Rio Grande Valley ScholarWorks @ UTRGV

Theses and Dissertations - UTB/UTPA

7-2011

# Design for soft error tolerance in FPGA-implemented asynchronous circuits

Yu Bai University of Texas-Pan American

Follow this and additional works at: https://scholarworks.utrgv.edu/leg\_etd

Part of the Electrical and Computer Engineering Commons

## **Recommended Citation**

Bai, Yu, "Design for soft error tolerance in FPGA-implemented asynchronous circuits" (2011). *Theses and Dissertations - UTB/UTPA*. 244. https://scholarworks.utrgv.edu/leg\_etd/244

This Thesis is brought to you for free and open access by ScholarWorks @ UTRGV. It has been accepted for inclusion in Theses and Dissertations - UTB/UTPA by an authorized administrator of ScholarWorks @ UTRGV. For more information, please contact justin.white@utrgv.edu, william.flores01@utrgv.edu.

## DESIGN FOR SOFT ERROR TOLERANCE IN FPGA-IMPLEMENTED ASYNCHRONOUS CIRCUITS

A Thesis

by

YU BAI

Submitted to the Graduate School of the University of Texas Pan-American In partial fulfillment of the requirements for the degree of

Master of Science

July 2011

Major Subject: Electrical Engineering

## DESIGN FOR SOFT ERROR TOLERANCE IN FPGA-IMPLEMENTED ASYNCHRONOUS

## CIRCUITS

A Thesis by YU BAI

## COMMITTEE MEMBERS

Dr. Weidong Kuang Chair of Committee

Dr. Hasina Huq Committee Member

Dr. Yul Chu Committee Member

July 2011

Copyright 2011 Yu Bai All Rights Reserved

## ABSTRACT

Bai Yu, <u>Design for Soft Error Tolerance in FPGA-Implemented Asynchronous Circuit</u>. Master of Science (MS), July, 2011, 82 pp., 4 tables, 46 figures, references, 24 titles.

This research in its present form is the result of experimentation on effect of soft error in FPGA-implemented asynchronous circuit. The conclusion are drawn that asynchronous circuit are much easier to detect soft error than synchronous circuits. The asynchronous circuit is implemented in FPGA with software fault injection method to analyze the behavior of soft error generation in FPGA implementation asynchronous circuits. The proposed detection circuit can detect all soft errors that generated in FPGA-implemented asynchronous circuit.

The contributions include: investigation of FPGA structure, investigation of soft error model in FPGA, mechanism of FPGA implemented asynchronous circuit, behavior of soft error injection in FPGA look up table that implemented asynchronous circuit, and proposed detection scheme. The research on soft error injection in FPGA routing system and soft error rate estimation will be done in the future.

## DEDICATION

I would like to give my thanks to the mighty God. He loves me and guides me in His way. Without God these all works are impossible to be done. While I was on the path through the valley of the shadow of death, He helped and guided me. Thanks God for everything You did. The completion of my MS studies would not have been possible without the support of my family. My mother, Guimin Zhang, my father Shaogang Bai, wholeheartedly inspired, motivated and supported me by all means to accomplish this degree.

## **ACKNOWLEDGEMENTS**

I want to give thanks to my supervisor Dr. Weidong Kuang for his real love. He treats me as my father. His real abundant academic experience and excellent teaching method built up the good foundation for my future studies. His precise research attitude gives me a good model to follow. He is my lighthouse that gives me the way to go. I would like to give thanks to Dr. Yul Chu and Dr. Hasina Huq too. You are really faithful to serve department and help students. I also want to thanks to all teachers taught me in UTPA Electrical Engineering Department. Your lesson helped me a lot.

The work presented in this thesis was supported by Electrical Engineering Department. Thank Dr. Foltz the chair of Electrical Engineering Department for his faithful serving to students. Without your support I cannot finish this thesis. The teaching and researching with Electrical Engineering Department gives me good experiences for future research. I take this opportunity to thank all staffs in UPTA for always being willing to help me.

## TABLE OF CONTENTS

| Page                                               |

|----------------------------------------------------|

| ABSTRACT iii                                       |

| DEDICATION iv                                      |

| ACKNOWLEDGEMENTS v                                 |

| TABLE OF CONTENTS vi                               |

| LIST OF TABLES viii                                |

| LIST OF FIGURESix                                  |

| CHAPTER I. INTRODUCTION 1                          |

| 1.1 overview of modern FPGA                        |

| 1.2 soft error background and previous work        |

| 1.3 brief background work on Asynchronous circuits |

| CHAPTER II. ASYCHRONOUS CIRCUIT ON FPGAS           |

| 2.1 FPGA architecture                              |

| 2.2 NCL circuit                                    |

| 2.2.1 Completion criteria 13                       |

| 2.2.2 Threshold gates with hysteresis 15           |

| 2.2.3 NCL pipeline                                 |

| 2.2.4 NCL registers                                |

| 2.3 FPGA implementation circuit                    |

| CHAPTER III. SOFT ERROR MODES IN FPGAS AND EXPERIMENTAL FAULT     |

|-------------------------------------------------------------------|

| INJECTION                                                         |

| 3.1 soft error models in FPGAs 24                                 |

| 3.1.1 Transient error                                             |

| 3.1.2 Permanent error                                             |

| 3.1.2.1 Routing error                                             |

| 3.1.2.2 Bit-flip on look up table configuration bits              |

| 3.1.2.3 Bit-flip on control/clocking bits                         |

| 3.2 fault injection method                                        |

| CHAPTER IV. SOFT ERROR IN FPGA-BASED ASYCHRONOUS CIRCUIT          |

| 4.1 soft error generation and simulation in single Threshold gate |

| 4.2 soft errors propagation and simulation in NCL pipelines       |

| CHAPTER V. PROPOSED SOFT ERROR DETECTION SCHEME AND SIMULATION49  |

| 5.1 soft error detection schemes                                  |

| 5.2 soft error detection scheme simulations                       |

| CHAPTER VI CONCLUSION AND FUTURE WORK                             |

| REFERENCES                                                        |

| APPENDIX A                                                        |

| APPENDIX B                                                        |

| BIOGRAPHICAL SKETCH                                               |

## LIST OF TABLES

## Page

| Table 2.2.1: Dual-rail encoding        | 14 |

|----------------------------------------|----|

| Table 2.3: Truth table of set LUT      | 23 |

| Table 4.1: Soft error of TH34w2        | 41 |

| Table 4.2: Soft errors in NCL pipeline | 47 |

## LIST OF FIGURES

## Page

| Fig 1.2.1: Mechanism of soft errors in MOSFET 4                       |

|-----------------------------------------------------------------------|

| Fig 1.2.2: Induced current 4                                          |

| Fig 2.1.1: Xilinx FPGA structure                                      |

| Fig 2.1.2: Logic elements (LEs)                                       |

| Fig 2.1.3: The architecture of Cyclone FPGAs 11                       |

| Fig 2.1.4: Architecture of SRAM-based 4-input look-up table (LUT) 11  |

| Fig 2.1.5: SRAM-FPGA architecture model 12                            |

| Fig 2.1.6: PIPs control in switch block 13                            |

| Fig 2.2.1.1: Weak conditions for NCL completeness of input 15         |

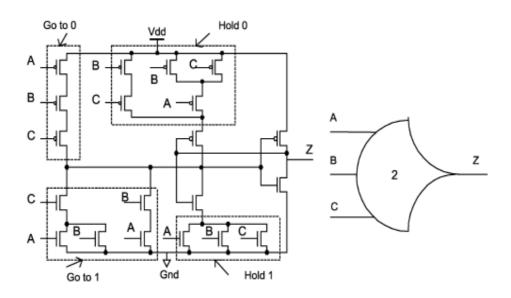

| Fig 2.2.2.1: Schematic and symbol of TH23 16                          |

| Fig 2.2.2.2: Schematic and symbol of TH23W2 16                        |

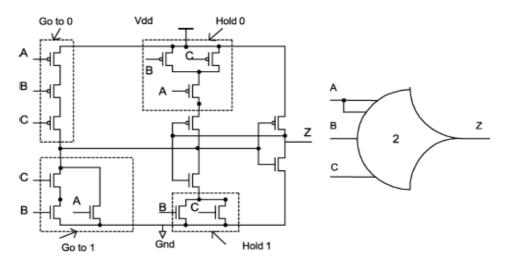

| Fig 2.2.2.3: Symbol examples of threshold gates 18                    |

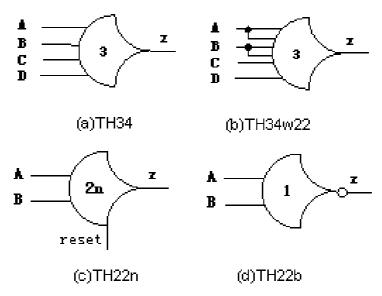

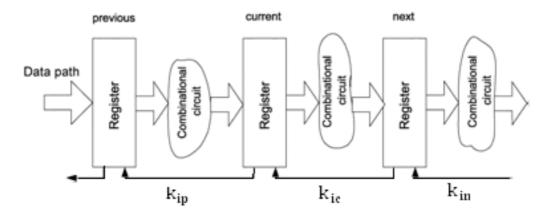

| Fig 2.2.3: Basic NCL pipeline structure 18                            |

| Fig 2.2.4: N-bit completion component 19                              |

| Fig 2.3.1: Threshold gate implemented on FPGAs 21                     |

| Fig 2.3.2: TH34w2 gates on Altera Cyclone II                          |

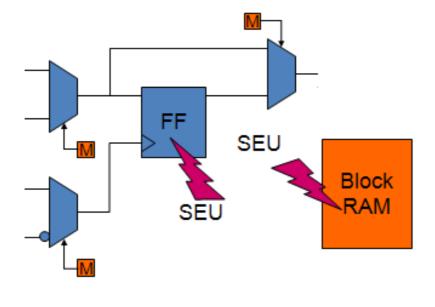

| Fig 3.1.1.1: An SEU affects inverter gates and makes a bit-flip error |

| Fig 3.1.1.2: SEU hit on FF and Block RAM in FPGA                      |

| Fig 3.1.2.1.1: Open errors in switch blocks                                                                   |

|---------------------------------------------------------------------------------------------------------------|

| Fig 3.1.2.1.2: Short errors in switch blocks                                                                  |

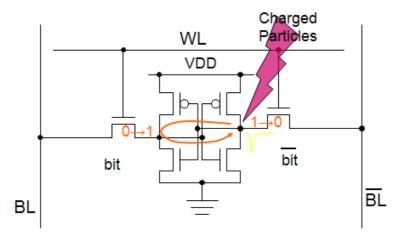

| Fig 3.1.2.2: SEU hits on SRAM cell 29                                                                         |

| Fig 3.2.1: Quartus II design flow 31                                                                          |

| Fig 3.2.2: Netlist viewer in tool button 32                                                                   |

| Fig 3.2.3: Technology Map Viewer of TH34w2 gate 34                                                            |

| Fig 3.2.4: Resource property editor for fault injection 34                                                    |

| Fig 4.1.1: TH34w2 implemented on FPGA 36                                                                      |

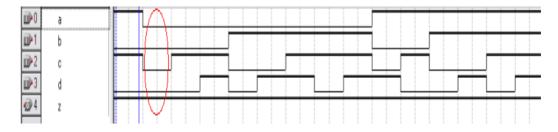

| Fig 4.1.2: No error appears at output Z (soft error setting set LUT: 0000 $(0 \rightarrow 1)$ )               |

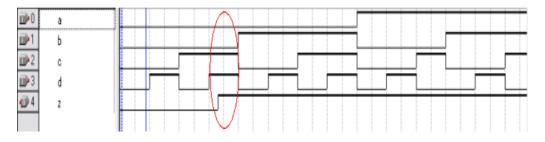

| Fig 4.1.3: Premature fire appears at output Z (soft error setting set LUT: 0011 ( $0 \rightarrow 1$ )) 37     |

| Fig 4.1.4: No fire appears at output Z (soft error setting set LUT: 0111 $(1 \rightarrow 0)$ )                |

| Fig 4.1.5: No return to 0 appears at output Z (soft error setting Reset LUT:0000 $(0 \rightarrow 1)$ ) 38     |

| Fig 4.1.6: Early return to 0 appears at output Z (soft error setting Reset LUT: 0001 $(1 \rightarrow 0)$ ) 38 |

| Fig 4.1.7: No fire appears at output Z (soft error setting Reset LUT: 0111 $(1 \rightarrow 0)$ )              |

| Fig 4.1.8: Oscillating appears at output Z (soft error setting hold LUT: 111 $(1 \rightarrow 0)$ )            |

| Fig 4.1.9: No return to 0 appears at output Z (soft error setting hold LUT $001(0 \rightarrow 1)$ ) 40        |

| Fig 4.1.10: Premature fire appears at output Z (soft error setting hold LUT 010 ( $0 \rightarrow 1$ )) 40     |

| Fig 4.1.11: Early return to 0 appears at output Z (soft error setting hold LUT 011 ( $1 \rightarrow 0$ )) 40  |

| Fig 4.1.12: Summarized simulation results of TH34w2 gate with different soft errors                           |

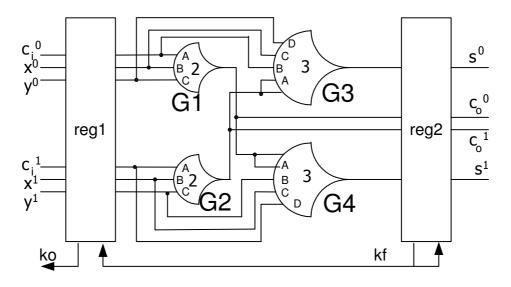

| Fig 4.2.1: Normal simulated circuit pipeline 43                                                               |

| Fig 4.2.2: Circuit simulated 43                                                                               |

| Fig 4.2.3: Invalid "11" appears at the output sum (soft error setting: Set LUT 0110 $(0 \rightarrow 1)$ in    |

| G3 gate in full adder) 45                                                                                     |

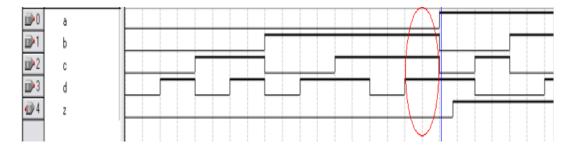

| Fig 4.2.4: Deadlock in the pipeline when no fire at sum (soft error setting: Set LUT 1001 $(1 \rightarrow 0)$ ) |

|-----------------------------------------------------------------------------------------------------------------|

| in G3 gate in full adder) 45                                                                                    |

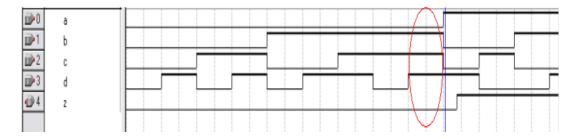

| Fig 4.2.5: Deadlock in the pipeline when no return to 0 at sum (soft error setting: hold LUT                    |

| 001(0->1) in G3 gate in full adder) 46                                                                          |

| Fig 4.2.6: Invalid "11" appears at sum when G3 ocsillating (soft error setting: Hold LUT 000                    |

| $(0 \rightarrow 1)$ in G3 gate in full adder)                                                                   |

| Fig 4.2.7: No error appears at the output when G3 ocsillating (soft error setting: Hold LUT                     |

| $(011(1 \rightarrow 0))$ in G3 gate in full adder)                                                              |

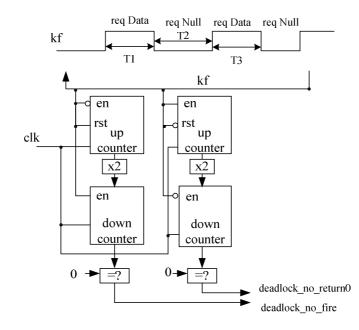

| Fig 5.1.1: Scheme of soft error detection 50                                                                    |

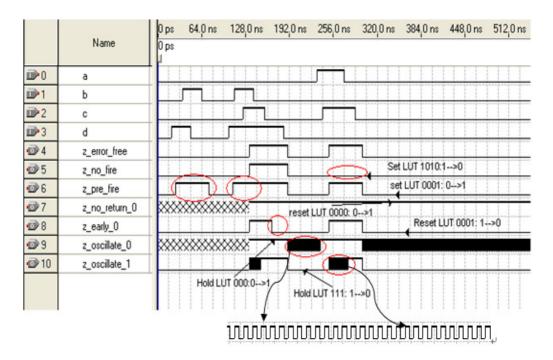

| Fig 5.2.1: Simulation of proposed detected circuit 51                                                           |

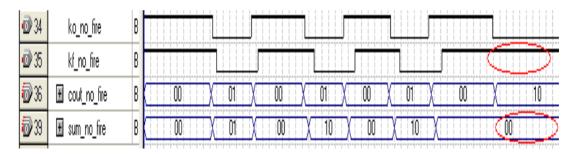

| Fig 5.2.2: The detect_no_fire output is 1 when no fire appears at sum (soft error setting: Set LUT              |

| 1001 (1->0) in G3 gate)                                                                                         |

| Fig 5.2.3: The detect_ no_return0 output is 1 when no return to 0 appears at sum (soft error                    |

| setting: hold LUT 001(0->1) in G3 gate)                                                                         |

#### CHAPTER I

#### INTRODUCTION

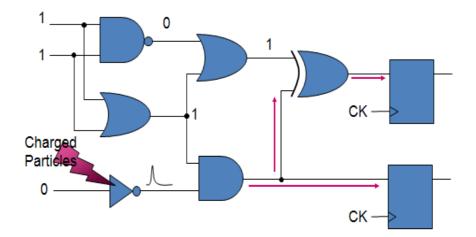

Soft error is called transient faults or single-event upsets (SEUs). SEUs are caused due to electrical noise or external radiation rather than design or manufacturing defects. As CMOS device sizes decrease, they are more easily affected by the low energy particles resulting from collisions between cosmic rays and particles in the atmosphere, potentially leading to a much higher rate of soft errors [3]. A Field Programmable Gate Array (FPGA) is an integrated semiconductor device designed to be programmed or configured any number of times using a schematic design or a source code in HDL (hardware description language) that describe the user's hardware design [1]. FPGAs can be configured with dense logic and have very high logic capacity. However, sensitive to Single Event Upsets (SEU) limit their widespread use in mission-critical application. The circuit implemented in FPGAs may be changed functionality by SEUs. Different from synchronous circuits, the asynchronous circuits use handshaking protocols to communicate between modules or parts of the circuits for the operations to be down in sequence, so that they are not governed by a clock circuit or global clock signal, but instead need only wait for the signals that indicate completion of instructions and operations. Since the asynchronous circuit [2] is a circuit in which the parts are largely autonomous, the effect of SEU hitting on Asynchronous circuits implemented FPGA should be explored.

#### 1.1 Overview of modern FPGA

The FPGA industry sprouted from programmable read-only memory (PROM) and programmable logic devices (PLDs). Both PROMs and PLDs had the option of being programmed in batches in the field (field programmable), however, programmable logic was hard-wired between logic gates [1]. In 1970s, the mask programmable logic arrays (MPGA) were invented and used to implement application-specific integrated circuits (ASICs). The MPGAs make up of an array of pre-fabricated transistors that can be customized into the logic circuit. The specifying metal interconnect perform customization during chip fabrication, it means that in order to use an MPGA a large setup cost is involved and manufacturing time is long. MPGA gave motivation to the design of FPGAs. In the earlier 1980s, the monolithic memories Inc (MMI) programmable array logic (PAL) was introduced by AMD. The MMI PALs were commercially very successful. The PALs consist of an array of programmable AND gate, which link to array of programmable OR gate, thus, the output can be produced conditionally complemented. However, the PAL is only a single level that wired AND plane that feeds fixed OR-gates.

Nowadays, FPGAs are widely known in many applications such as industrial productions, spacecraft and embedded applications, according to their high performance, no non-refundable-engineering cost and fast time response. The strengths of modern FPGAs are quick prototyping and time-to-market, reprogramability, relatively easy to use. The weaknesses are, cost, density, and speed.

The FPGAs are handy thing to have on the workbench; it means they can be used for rapid prototyping. With the obvious advantages that compare with ASIC, FPGAs are used in critical applications and are replacing ASICs on a regular basis. The last decade, FPGAs are ever increasingly collect attention by most researchers in areas of DSP applications, automotive applications, space applications, robotics, computer security, and reconfigurable computing.

## 1.2 Soft error background and previous work

Soft errors, also called transient errors, are intermittent malfunctions of hardware that are not reproducible [2], arise from Single Event Upset (SEU). Soft error was first discovered in memory element like Dynamic random-access memory (DRAMs) in 1970s [3]. Since then DRAMs were the focus of soft error also because it occupies most of the susceptible surface area. DRAMs of 256 KB with 1980s technology had flips of five to six bits from single alpha particle [5]. The present devices employ more flips for the same alpha particle.

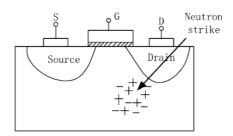

These SEUs are caused by energetic neutrons originating from cosmic rays or alpha particles coming from radioactive contaminants in the package material hitting the surface of silicon devices. Device scaling significantly affects the susceptibility of integrated circuits to soft error [4]. The cause factors of intensity of these soft errors lie in energy of hitting particles, the location of the device, geometry of the impact, and design of the logic circuit. The Soft Error Rate (SER) is measured by Failures In Time (FIT): one FIT is one error per billion hours of operation. Alternative unit is mean time between failures (MTBF). EX: 1 year MTBF= $\frac{10^9}{(365 \times 24)} = 114,115$  FIT. The Fig.1.2.1 shows the mechanism of soft errors in a

Metal Oxide Semiconductor Field Effect Transistor (MOSFET).

Fig.1.2.1 mechanism of soft errors in MOSFET

Electron-hole pairs with a very high carrier concentration are generated as the particle loses energy in silicon when a particle hits the drain of the MOSFET, and the resulting charges can be rapidly collected by the electric field to create a large transient current at that node [8]. The transient current can be modeled as [8]

$$I(t) = \frac{2Q}{T\sqrt{\pi}}\sqrt{\frac{t}{T}} \cdot \exp\left(-\frac{t}{T}\right)$$

where Q is the amount of collected charge, and T is a process technology-dependent time constant. The detailed discussion about this model and related parameters can be found in [9]. The Fig 1.2.2 shows the induced current caused by soft error.

Fig.1.2.2 Induced current

The case of the current is injected into or drawn from the node depends on the type of victim drain of transistor. For example, a current is injected into the node if particle hit occurs at a p-type drain, so that it increases the node voltage. If this node of logic circuit is transmitting

logic 0 under the current injected to the node, a transient positive glitch (0-1-0) may occur at the node. Similarly, the negative transient glitch (1-0-1) may be generated if an n-type drain is hit.

Since FPGAs are vulnerable to single event upsets (SEUs) [7], an SEU with sufficient energy changes the logic state of memory element, producing a soft error [8]. For sake of SEU mitigation of FPGAs, the SEU Mitigation Techniques are therefore desirable. Many studies have focused on solution either at device level or architecture level. At device level, one solution is to use radiation-hardened FPGA devices. However, these devices are much more expensive than Commercial-Off-The-Shelf (COTS) FPGAs [7]. At architecture level, redundancy designs such as Triple Module Redundancy (TMR) are explored to protect FPGAs from soft error [10]. TMR-based mitigation techniques impose more than 200% overhead in terms of area and power. Scrubbing, i.e., the periodic refresh of the configuration memory, is another effective approach, especially when used in conjunction with TMR. Others Mitigation Techniques are multiple redundancy with voting, error detection and correction codes (EDAC), and FPGA-specific methods, such as reconfiguration, partial configuration, rerouting design.

#### 1.3 Brief background work on asynchronous circuit

For last three decades, most circuits designed and fabricated are "synchronous". However, as lock rates have significantly increased while feature size has decreased, clock skew has become a major problem. Most of performance chips must dedicate increasingly larger portions for clock drivers to generate acceptable skew, causing these chips to dissipate increasingly higher power, especially at the clock edge, when switching is most prevalent. With the process of these trends, the clock is becoming more and more difficult to manage, while clocked circuits' inherent power inefficiencies are emerging as the dominant factor hindering increased performance. These concerns caused renewed interest in asynchronous circuit. Asynchronous, clockless circuits require less power, generate less noise, and produce less electro-magnetic interference (EMI), compare to synchronous circuits, without degrading performance. Furthermore, these delay-insensitive (DI) asynchronous circuits have some additional advantages, especially when designing complex circuit, such as system-on-a-chip (SoCs), including substantially reduced crosstalk between analog and digital circuits, ease of integrating multi-rate circuits, and facilitation of component reuse. Recently, companies such as ARM, Phillips, Intel, and others are incorporating asynchronous logic into some of their products using their own proprietary tools.

Asynchronous circuits can be classified into two main categories: bounded-delay and delay-insensitive models. Bounded-delay models, such as micropipelines [12], assumed that delays in both gates and wires are bounded. Delays are added based on worse-case scenarios to avoid hazard conditions. This leads to extensive timing analysis of worse-case behavior to ensure correct circuit operation. Delay-insensitive circuits assume delays in both logic elements and interconnects to be unbounded, although they assume that wire forks within basic components, such as full adder, are isochronic, meaning that the wire delays within a component are much less than the logic element delays within the component, which is a valid assumption even in future nanometer technologies. Wires connecting components do not have to adhere to the isochronic fork assumption. This implies the ability to operate in the presence of indefinite arrival times for the reception of inputs. Completion detection of the output signals allows for handshaking controlling input wavefronts. Delay-intensive design styles therefore require very little, if any, timing analysis to ensure correct operation (i.e., they are correct by construction),

and also yield averge-case performance rather than the worse-case performance of bounded-delay and traditional synchronous paradigms.

## CHAPTER II

## ASYNCHRONOUS CIRCUIT ON FPGAS

The modern FPGAs use schematic design or a resource code in HDL (hardware description language) to program and configure circuit. The modern CAD tool can implement both synchronous and asynchronous circuits by using HDL. The previous soft error mitigation method are more focus on synchronous circuit implemented on FPGA, however, the asynchronous circuits, especially Null Convention Logic (NCL), implemented on FPGA have much easier detection signal when the soft error injected in asynchronous circuit implemented FPGAs. In order to analyze behavior of soft error injected in asynchronous circuit implemented FPGAs, the FPGA architecture, NCL circuit, and FPGA implementation NCL circuit are necessary understood and introduced.

#### 2.1 FPGA architecture

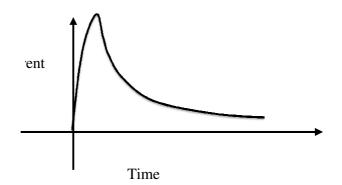

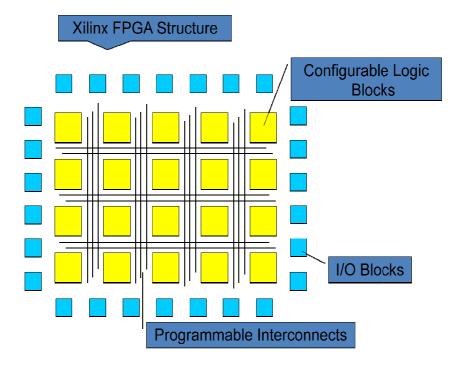

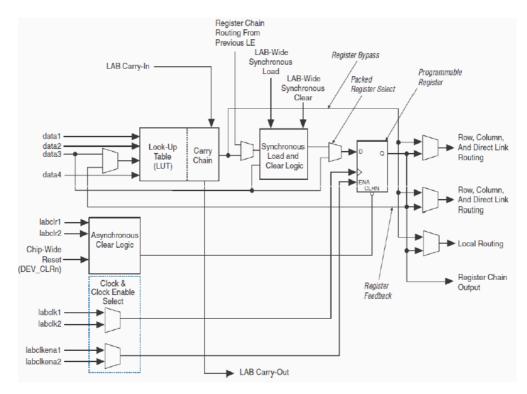

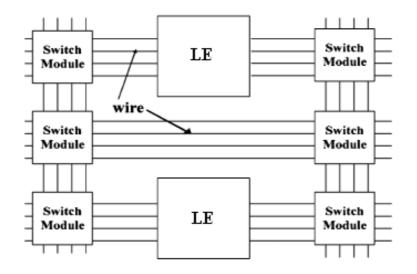

FPGA is logic devices that contain basic components LUT (look-up-table), flip-flops, multiplexors, I/O blocks, programmable switching matrices, interconnect, clocks. These basic elements compose the functional blocks in FPGAs, such as configurable logic blocks, I/O blocks, and programmable interconnects. The FPGA structure is shown in Fig2.1.1 [13]. The two-dimensional arrays of generic logic elements (LEs) as shown in Fig.2.1.2 [13], and programmable switches are main elements specifying the functionality of circuit mapped into the FPGAs.

Fig 2.1.2 Logic Elements (LEs) [13]

A logic element can be configured (i.e., programmed) to perform a simple function, and a programmable switch can be customized to provide interconnections among the logic elements. A custom design can be implemented by specifying the function of each logic element and selectively setting the connection of each logic element and selectively setting the connection of each logic element usually contains a programmable look-up table (LUT), programmable interconnects, and flip-flops (FF). An *n-input* look-up table is typically implemented by a static random access memory (SRAM), and is used to implement any *n-input* combinational function. The flip-flops can be selectively used to implement sequential circuits. Most FPGA devices also embed certain macro cells, such as BlockRAMs, dedicated multipliers, clock managers, and I/O interface circuits. Logic elements are usually grouped into logic array blocks (LABs).

For example, the architecture of Altera Cyclone II FPGAs is shown in Fig.2.1.3 [14]. The logic array consists of Logic Array Blocks (LABs), with 16 LEs in each LAB. Each LE includes a four-input LUT, a D-flip-flop and connections. The phase-locked loops (PLLs) provide general-purpose clocking with clock synthesis and phase shifting as well as external outputs for high-speed differential I/O support. The input/output elements (IOEs) contain a bidirectional I/O buffer and three registers for complete embedded bidirectional single data rate transfer. The devices also contain embedded memory and multipliers.

| PLL  | IOEs        |        |             |             |             | PLL    |             |      |

|------|-------------|--------|-------------|-------------|-------------|--------|-------------|------|

| IOEs | Logic array | Memory | Logic array | multipliers | Logic array | Memory | Logic array | IOEs |

| PLL  | IOEs        |        |             |             |             | PLL    |             |      |

Fig 2.1.3 The architecture of Cyclone FPGAs [14]

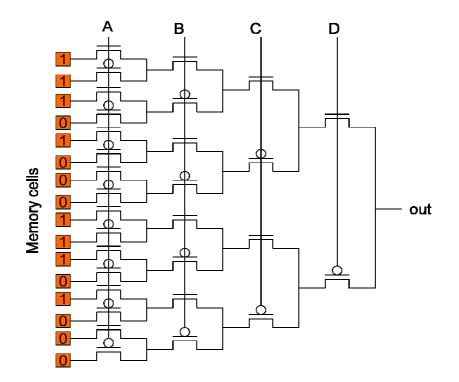

The architecture of an SRAM-based 4-input look-up table, implementing a logic function f(D,C,B,A), is illustrated by Fig.2.1.4. The truth table of f(D,C,B,A) is stored in the memory cells. For instance, binary data  $1110\_1000$  1110\_1000 is stored in the memory cells as shown in Fig.2.1.4, to implement logic function is  $f D, C, B, A \circ AB + BC + AC$ .

Fig 2.1.4 Architecture of SRAM-based 4-input look-up table (LUT)

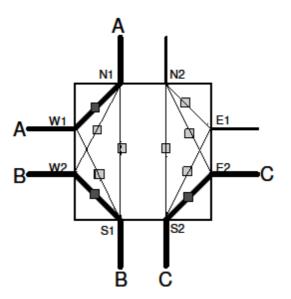

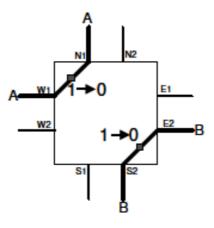

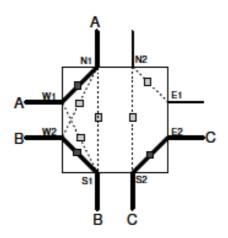

These SRAM-based 4-input LUTs are used to implement digital circuits while switch modules provide the interconnection between resources, shown in Fig.2.1.5. The switch module consists of several switch blocks. The programmable switch blocks provide the selective connectivity of horizontal as well as vertical routing channels placed between logic blocks which consist of nets of different length [17]. Inside switch block, a pass transistor controlled by a user-SRAM cell play a role as programmable switches. Each of this architecture with pass transistor and user-SRAM cell is called Programmable interconnect points (PIPs). Consider the matrix shown in Fig. 2.1.6, three different nets are PIPs (W1, N1), (W2, S1), (S2, E2). The PIPs can control the net open or close. The light line shows the possible connection nets, while the PIP is closed.

Fig 2.1.5 SRAM-FPGA architecture model [22]

Fig 2.1.6 PIPs control in switch block [23]

## 2.2 Null Convention Logic (NCL) circuit

Null Convention Logic (NCL) [16] is a delay-insensitive asynchronous paradigm meaning that NCL circuits will operate correctly regardless of delay of components and wires. NCL circuits utilize dual-rail or quad-rail logic to achieve delay-insensitivity. For this thesis, the designs employ the dual-rail logic.

## 2.2.1 Completion Criteria

NCL uses two completeness criteria to achieve its delay-insensitive behavior: symbolic completeness of expression and completeness of input. A symbolically complete expression is defined as an expression that only depends on relationships of the symbols presented in the expression. Dual-rail signals state logic value (NULL, DATA0, and DATA1) achieve symbolic completeness of expression. A dual-rail signal D is encoded by two wires D<sup>1</sup>, D<sup>0</sup>, as shown in Table 2.2.1.

| Dual-rail encoding<br>(D <sup>1</sup> , D <sup>0</sup> ) | Logic value |

|----------------------------------------------------------|-------------|

| (0,0)                                                    | NULL        |

| (0,1)                                                    | DATA0       |

| (1,0)                                                    | DATA1       |

| (1,1)                                                    | Invalid     |

Table 2.2.1 dual-rail encoding

The DATA0 state  $(D^1 = 0, D^0 = 1)$  corresponds to a Boolean logic 0, the DATA1 state  $(D^1 = 1, D^0 = 0)$  corresponds to a Boolean logic1, and the NULL state  $(D^1 = 0, D^0 = 0)$  corresponds to empty set meaning that the value of D is not available. Two rails are mutually exclusive, such that both rails can never be asserted simultaneously, this state is defined as an illegal state.

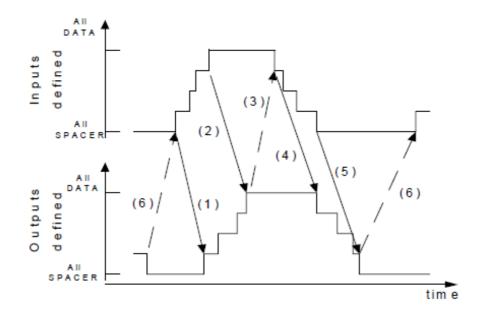

The second criterion is completeness of input for NCL combinational circuit, 1) the output may not transition from NULL to a complete set of DATA until the input values are completely DATA, 2) the output may not transition from DATA to a complete set of NULL values until the input values are completely NULL. The criterion, equivalent to Seitz's "weak condition" [17], is shown in Fig 2.2.1.1.

Fig 2.2.1.1 weak conditions for NCL completeness of input

- (1) Some inputs become DATA before some outputs become DATA.

- (2) Some inputs become NULL before some outputs become NULL.

- (3) All inputs become DATA before all outputs become DATA.

- (4) All outputs become DATA before some inputs become NULL.

- (5) All inputs become NULL before all outputs become NULL.

- (6) All outputs become NULL before some inputs become DATA.

## 2.2.2 Threshold Gates with Hysteresis

NCL uses a special type of gates, namely threshold gates with hysteresis [18], as basic units to build NCL circuits. The format that describes threshold gate is thmnWn<sub>1</sub>n<sub>2</sub>n<sub>3</sub> ... n<sub>w</sub>, where 'th' is stand for threshold gate, m is the threshold, n is the number of inputs, W means the following 'n<sub>1</sub>', 'n<sub>2</sub>'... 'n<sub>w</sub>' are weights of the first 'W' inputs and the weights of other inputs are one by default. The following figures are schematic and symbol of TH23 and TH23w2.

Fig 2.2.2.1 Schematic and symbol of TH23

Fig 2.2.2.2 Schematic and symbol of TH23W2

NCL circuits are comprised of a family of threshold gates with hysteresis. The primary type of threshold gate is TH*mn* gate where *n* is the number of inputs, *m* is the threshold, and  $1 \le m \le n$ . A THmn gate will set its output high when any *m* inputs have gone high and it will reset its output low when all *n* inputs are low. A more general type of threshold gate with hysteresis is referred to as a weighted threshold gate, denoted as TH*mn*Ww<sub>1</sub>w<sub>2</sub>...w<sub>R</sub>, where *n* is the number of inputs,

*m* is the threshold,  $w_1, w_2, \dots, w_R$   $(1 < w_i \le m, 1 \le R < n)$  are the integer weights of *input 1*, *input* 2, ... input R, respectively. For example, TH34 has 4 inputs (A, B, C, D) and a threshold of 3, as shown in Fig 2.2.2.3 (a). When any three inputs go high, its output will be asserted to high. Only when all inputs are low, the output will be reset to low. For all other input patterns, the output will remain unchanged. A weighted gate TH34W22 has the same number of inputs (4) and threshold (3) as TH34 gate, but there is a weight 2 applied to each of the first two inputs (A and B), as shown in Fig 2.2.2.3 (b). For the gate TH34W22, the output is asserted only when either input A is high along with any other input, or input B is high along with any other input. The output is deasserted only when all inputs are low. NCL threshold gates may also include a reset input to initialize the output. Either a d or an n is attached at the end of the gate name to designate these gates, such as TH22n shown in Fig 2.2.2.3 (c). d denotes the gate as being reset to high while n to low. These resettable gates are used in the design of registers. A bubble attached at the output denotes an inverter connected at the output, as shown in Fig 2.2.2.3 (d). The principle of transistor-level threshold gate design can be found in [18]. The design of computational blocks, registers and completion detection blocks using threshold gates is available in [18].

Fig 2.2.2.3. Symbol examples of threshold gates

## 2.2.3 NCL Pipeline

The framework for NCL systems consist of delay-insensitive combinational logic sandwiched between delay-insensitive registers. This combination of NCL registers along with completion detection circuitry and combinational logic is called NCL pipeline [17]. A typical NCL pipeline architecture consists of NCL registers, completion detection circuitry and NCL combinational logic like exor, full-adder, etc. the following Fig 2.2.3 shows basic NCL pipeline structure.

Fig 2.2.3 Basic NCL pipeline structure

The NCL allows DATA and Null pass through the NCL pipeline alternately. The input request for each register gate comes from the detection gate of the next register. Two adjacent register stages interact through their request and acknowledge signals k<sub>i</sub>, k<sub>o</sub>, respectively, to prevent the current DATA wavefront from overwriting the previous DATA wavefront, by ensuring that the two DATA wavefronts are always separated by a NULL wavefront. For example, assume that all the circuits are in a NULL state and that input request signals of the current register (kic) and the next register (kin) are requesting DATA, at same time, the previous register is transiting a complete DATA to its combinational circuit. As the wavefront propagates through the previous combinational circuit to the current register, the current register passes the data since its control line is requesting DATA. When a complete data is received by current detection circuitry, it gives control line (kip) to the previous register to indicating that the current register has received and stored the data wavefront, thus, the previous registers can pass NULL. The requested NULL by previous register may arrive at the current register, however, the NULL wavefront will be blocked at current register until control line (kic) is requesting NULL, and the current register will maintain presentation DATA values to the current combinational circuit. When the next register receives and stores the DATA wavefront, the DATA set no longer needs to be maintained by the current register. Since the next completion detection circuit detects the complete DATA set and transitions its acknowledge line (kic) to request NULL indicating that it has received DATA wavefront and the current register can allow a NULL wavefront.

#### 2.2.4 NCL register

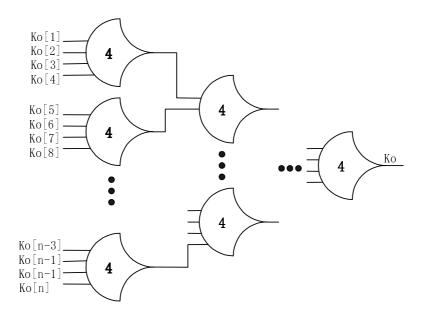

An N-bit register stage, comprised of N single-bit dual-bit NCL registers, requires N completion signals, one for each bit. The NCL completion component, shown in Fig 2.2.4, uses these  $Nk_0$  lines to detect complete DATA and NULL sets at the output of every register stage

and request the next NULL and DATA set, respectively. In full-world completion, the single-bit output of the completion component is connected to all  $k_i$  lines of the previous register stage. Since the maximum input threshold gate is the TH44 gate, the number of logic levels in the completion component for N-bit register is given by  $[\log_4 N]$ . Likewise, the completion component for an N-bit quad-rail registration stage requires  $\frac{N}{2}$  inputs, and can be realized in a similar fashion using TH44.

Fig 2.2.4 N-bit completion component

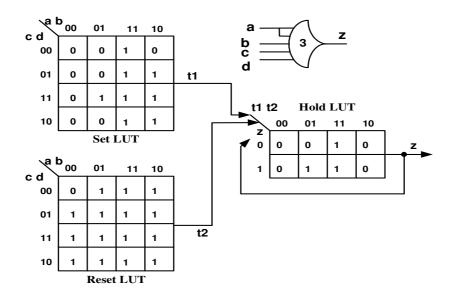

### 2.3 FPGA implementation of NCL circuits

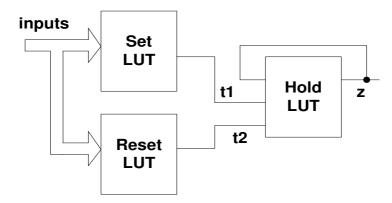

Generally, a threshold gate is synthesized into three logic elements in FPGAs, as shown in Fig 2.3.1 Each logic element, utilizing an SRAM LUT, performs *Set, Reset, and Hold* respectively. The function of *Set LUT* is defined as this: its output t1 is "1" when the number of inputs equal to "1" reaches (or more than) the threshold *m*; otherwise the output is "0". For example, the *Set* function of TH23 is t1 = AB + BC + AC, and the *Set* function of TH34w2 (A has a weight of 2) is t1 = A(B + C + D) + BCD. The function of *Reset LUT* for all threshold gates is an OR gate

delivering "0" when all inputs are "0". The *Hold LUT* delivers the final output with hysteresis using a feedback. It is easy to find out that its function is  $z = t2 \cdot (t1 + z)$  for all threshold gates.

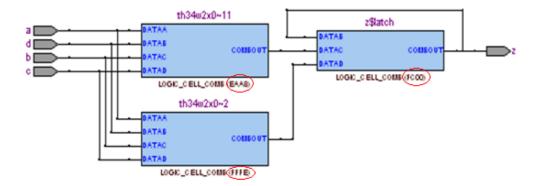

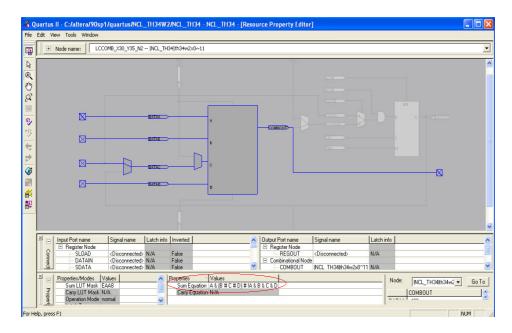

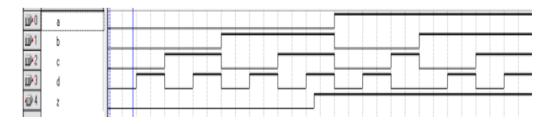

The Quartus II provides the way to look at schematic of design. By looking at the schematic of design at software, it shows three LUT to implement Threshold gate. Each LUT may restore the truth table to generate function of threshold gate. The concept in Fig 2.3.1 has been verified by implementing TH23 and TH34w2 gates on Altera Cyclone II EP2C35F672C6N chip, as shown in Fig 2.3.2.

Fig 2.3.1 Threshold gate implemented on FPGAs

Fig 2.3.2. TH34w2 gates on Altera Cyclone II

The Fig 2.3.2 shows Th34w2 gates implemented in Altera Cyclone II FPGA by Quartus II software. It has 4 inputs going to Set LUT (th34w2x0~11) and Reset LUT (th34w2x0~2). The Hold LUT (z\$latch) delivers final output with hysteresis using output feedback and output of set LUT and reset LUT. The red circle is the value of sum LUT mask. The sum LUT mask is simply the hexadecimal representation of the LUT output. Take set LUT for example: the function equation of set LUT is t1 = A(B + C + D) + BCD, so that the truth table of set LUT can be described in Table 2.3:

| D | С | В | A | OUTPUT |  |  |  |  |

|---|---|---|---|--------|--|--|--|--|

| 0 | 0 | 0 | 0 | 0      |  |  |  |  |

| 0 | 0 | 0 | 1 | 0      |  |  |  |  |

| 0 | 0 | 1 | 0 | 0      |  |  |  |  |

| 0 | 0 | 1 | 1 | 1      |  |  |  |  |

| 0 | 1 | 0 | 0 | 0      |  |  |  |  |

| 0 | 1 | 0 | 1 | 1      |  |  |  |  |

| 0 | 1 | 1 | 0 | 0      |  |  |  |  |

| 0 | 1 | 1 | 1 | 1      |  |  |  |  |

| 1 | 0 | 0 | 0 | 0      |  |  |  |  |

| 1 | 0 | 0 | 1 | 1      |  |  |  |  |

| 1 | 0 | 1 | 0 | 0      |  |  |  |  |

| 1 | 0 | 1 | 1 | 1      |  |  |  |  |

| 1 | 1 | 0 | 0 | 0      |  |  |  |  |

| 1 | 1 | 0 | 1 | 1      |  |  |  |  |

| 1 | 1 | 1 | 0 | 1      |  |  |  |  |

| 1 | 1 | 1 | 1 | 1      |  |  |  |  |

Table 2.3 truth table of set LUT

From this truth table the set LUT function can be represented by following binary sting: 1110\_1010\_1010\_1000, the sum LUT mask in hexadecimal for this binary string is : EAA8. Similarly, the reset LUT and hold LUT mask can be found by this way too.

#### CHAPTER III

# SOFT ERROR MODELS AND EXPERIMENTAL FAULT INJECTION

In the previous chapter, basic works on asynchronous circuit implemented in FPGAs have been done. With help of these basic works, effects of soft error injecting asynchronous circuit implemented FPGA are obvious to observe. Therefore, the soft error models and experimental fault injection method are concluded as part of this research and explained in CHAPTER 3. This chapter explains soft error models in FPGAs and possible experimental fault injection method are described.

### 3.1 Soft error models in FPGAs

The effects of single event upsets (SEUs) on digital circuits can be classified into 1) transient and 2) permanent errors. The transient errors are caused by SEUs hitting on combinational logic components, which can be propagated and captured in flip-flops. These errors are called transient errors because they may be corrected using detection techniques. These errors could be occurred and found in memory elements and caches, register files and flip-flops (FFs). The permanent errors are caused by SEUs hitting on memory bits, and these errors alter the contents of configuration bits. This case may keep erroneous until the new configuration is downloaded and rewrited into the FPGA.

The research and analysis of transient errors have been described in [18]. They inject faults into the simulation or emulation models of the design to investigate the behavior of combination logic circuit. The alteration of memory elements such as data-path registers and control-unit registers are injected by faults with faults injection techniques [20].

The research of permanent errors that changes contents of configuration bits are more complex to analyze, since the simple bit flip fault model cannot be exploited. An SEU can changes interconnect inside configurable logic block (CLBs) and also the routing signals between different CLBs. Moreover, a SEU may change the content of look-up-tables (LUTs).

There are two major types of memory resources in FPGAs: user bits and configuration bits. An SEU on user bits cause a transient error, and an SEU on configuration bits leads to a permanent error.

## 3.1.1 Transient errors

The transient errors do not change the content of SRAM configuration bits, but affect user-defined logic and flip-flops. An SEU affecting a combination part makes transient error on the combinational part inside CLBs. These errors can be propagated to next part to make a bit-flip error. The Fig 3.1.1.1 describes SEU makes bit-flip error in a flip-flop. It has been shown that in ASIC designs, combinational logic is less susceptible to soft error than memory elements [21]. This is because the combinational logic provides some natural resistance to soft errors [22].

Fig 3.1.1.1 An SEU affects inverter gates and makes a bit-flip error

An SEU may also affect the contents of flip-flop and memory. The content of the Flip-Flops (FFs) and memory will keep erroneous until another data write to FFs or corrected by detecting circuit. The Fig 3.1.1.2 is shown the SEU hit on FF and Block RAM.

Fig 3.1.1.2. SEU hit on FF and Block RAM in FPGA

## 3.1.2 Permanent error

A single event upset (SEU) induced by a particle strike in a user bit causes a transient error, whereas an SEU in a configuration bit would lead to a permanent error which remains in the FPGA until the next reconfiguration of a new design. This permanent error may result in a logic error or routing error depending on which part of the configuration memory is affected. A logic error may lead to complement one of the entries of the LUT modifying the functionality of the mapped logic function. A routing error may lead to a signal getting misrouted or disconnected [23]. This type of error is the major error type in FPGAs because the number of SRAM cells

dominates user-defined memory elements. Typically, the amount of SRAM configuration cells is more than 98% of all memory elements inside an FPGA [23].

There are two types configuration memory bits, are sensitive and non-sensitive bits, based on their vulnerabilities to SEUs. When the SEU hit at the sensitive configuration bits, it affects the functionality of the circuit which mapped into FPGA. On the other hand, the non-sensitive configuration bits play role as "don't care" for the design mapped into FPGA.

Since a transient error is not lasting ever and easy to be detected by detection correcting circuit, permanent error is more difficult to correct. Our research is more focus on permanent error. Permanent error can be classified into routing errors, LUT bit-flips, and control/clocking bit-flips.

#### 3.1.2.1 Routing error

The programmable routing network of FPGA consist of Programmable interconnect points (PIPs), multiplexers and buffers. An SEU changing a configuration routing bit causes PIPs switch open, switch short. Normally, the PIPs employ the NMOS transistor as switch. Since the SRAM cell control the NMOS transistor with logic 1 close, the changing a PIP control from 1 to 0 by SEU will cause a switch open in this nets resulting in an open error in the gate-level netlist, is shown in Fig 3.1.2.1.1. It's easy to see the close connection nets break out by the changing of PIP control cell from 1 to 0. However, the short error is a little bit different with open error. An SEU (0 to 1) on unused PIP (W1,S1) or (N1,S1) causes a bridging error between nets A and B. it's called short error. On the other hand some unused PIP (N2, E1) not cause any bridging errors since no nets are adjacent to this PIP. Therefore, we may define PIP as two categories, sensitive PIP and non-sensitive PIP. The Fig 3.1.2.1.2 shows the sensitive PIP and non-sensitive PIP in short error case.

Fig 3.1.2.1.1 open errors in switch blocks

Fig 3.1.2.1.2 short errors in switch blocks

# 3.1.2.2 Bit-flip on Look up Table (LUT) configuration bits

As the previous chapter's illustration, a logic function can be implemented by storing all values for the truth table in LUT. The look up table (LUT) consists of SRAM cell. A SEU may lead to complement one of the entries of the LUT modifying the functionality of the mapped logic function permanently. Fig 3.1.2.2 the SRAM cell changes its stored value by SEU.

Fig 3.1.2.2 SEU hits on SRAM cell

### 3.1.2.3 Bit-flip on control/clocking bits

There are some control bits in CLBs and I/0 blocks to determine miscellaneous functionalities. For example, the control bits may determine whether the LUT performs as a look up table, a dual-ported RAM, or a programmable shift register. Furthermore, some SRAM cells also works for clock signal routing throughout the circuit. In summary, bit-flip on the control/clock bits affects the functionality of the mapped design drastically [24].

### 3.2 Fault injection method

The soft error propagation both in signal NCL gate and NCL pipeline has been derived in next chapter. In order to verify our analysis and conclusion of soft error, the simulation with soft error injected environment must be generated, so that the fault injection techniques are employed to reach our aim. In modern society, the approaches to fault injection have been classified by three categories:

- Hardware fault injection

- Software fault injection

- Simulation fault injection

The hardware fault injection cause faults in circuit physically. The advantages of hardware fault injection are realistic good fault coverage, good for low latency faults, and low perturbation. On other hand, it's harder to control and expensive to build up system in safety limit their widespread use. The hardware injection with contact uses pin-level injection such as, probes, socket insertion, but without contact uses heavy ion radiation and electromagnetic interference. The common used hardware tools are Messaline, FIST and MARS. The software fault injection injects the soft error by software programmatically. It has compile-time injection and runtime injection. The software injection is cheaper, controllable and more targeted and flexible, but it's more perturbation and limited coverage. The common software tools are Ferrari, Ftage, Xception. The simulation injection injects faults during the simulation time. It's not closed to real environment.

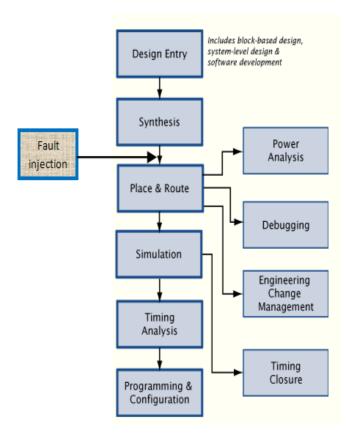

The fault injection in this thesis is performed by Quartus II software properties resource editor. It also can be called software fault injection. Quartus II provides an easy way to change the content of a desired LUT SRAM cell after compiling the VHDL files. This change is equivalent to a fault injection to the cell. After saving the change, it can simulate the behavior of the circuit with a fault injection. The Fig 3.2.1 shows the Quartus II design flow with fault injection.

Fig 3.2.1 Quartus II design flow

From Quartus II tools, it provides lots of powerful and useful tools, such as in system content memory editor, in system source and probes editor and so on. One of them is called net viewers allow you to view schematic representations of internal structure of your designs. Fig 3.2.2 shows netlist viewers in tool box.

| Quartus II - C:/altera/90sp1/quartus/NCL_] File Edit View Project Assignments Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                      | pilation Report - Flow Summary]                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In Call Ver Hogan Boginalist Hoccord<br>Project Navigator     Entity     Logic Cells     Dedica     Cyclone II: EP2C35F672C6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Run EDA Simulation Tool                                                                              | Image: Simulation Report - Simulation       Image: Simulation Report - Simulation       Image: Simulation Report - Fl         Flow Summary       Image: Simulation Report - Simulation       Image: Simulation Report - Fl |

| Image: NCL_TH34         Image: Second se                            | ImeQuest Timing Analyzer         Advisors         Y         Chip Planner (Floorplan and Chip Editor) | Flow Status Successful - Wed May 11 11:49:44 2011<br>Quartus II Version 9.0 Build 184 04/29/2009 SP 1 SJ Web Edition<br>ettir Revision Name NCL_TH34<br>Top-level Entity Name NCL_TH34<br>Family Cyclone II                |

| TasksFlow: Compilation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Design Partition Planner      Netlist Viewers      SignalTap II Logic Analyzer                       | Device         EP2C35F672D6                                                                                                                                                                                                |

| Task @<br>✓ □ ► Compile Design<br>✓ □ ► Analysis & Synthesis<br>↓ □ Edit Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 🚍 In-System Memory Content Editor                                                                    | Technology Map Viewer (Post-Mapping)         3 / 33,216 (<1 %)                                                                                                                                                             |

| Euk of unity served     E | SignalProbe Pins<br>Programmer                                                                       | Total pins 5/475(1%)<br>Total vitual pins 0                                                                                                                                                                                |

| <ul> <li>Info: Running Quartus II</li> <li>Info: Command: quartus ta</li> <li>Warning: Timing Analysis</li> <li>Warning: No paths found f</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | y 🖳 SOPC Builder<br>Tol Scripts                                                                      | settings_files=off_NCL_TH34 -c_NCL_TH34timing_analysis_only<br>mal_loops_as_latches                                                                                                                                        |

| Info: Quartus II Classic<br>↓ Info: Quartus II Full Com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                      | rrors, 3 warnings<br>10 warnings                                                                                                                                                                                           |

| Image: System (4)         Processing (56)         Image: Extra Info         Image: Image: Image: Extra Info         Image: Image: Extra Info         Image: Im                                                                                                                                        | Cystomize Compilation Report<br>Options for Report Window                                            | ror 入 Suppressed (6) 入 Flag /                                                                                                                                                                                              |

Fig 3.2.2: Netlist viewer in tool button

If you are ready find out the netlist viewer button as shown in Fig 3.2.2, the software will provide four different functional views ask you choose. The RTL viewer can view a schematic of the design netlist after Analysis & Elaboration and netlist extraction, but before Quartus II synthesis and fitting optimizations. This view is not the final structure of the design, because not all optimizations are included; instead it is the closest possible view to the original design. If the design uses integrated synthesis, this view shows how the Quartus II software interprets the design files; if you are using a third-party EDA synthesis tool, this view shows the netlist as written by the EDA synthesis tool. The Technology Map Viewer can view a low-level, technology-specific schematic of the design netlist after fitting or after Analysis & Synthesis.

You can access the post-fitting view of the schematic with the Technology Map Viewer; or you can access the post-mapping view of the schematic, regardless of the synthesis tool you use, with the Technology Map Viewer (Post-Mapping). When opened from a timing path in the Timing Analyzer report, the Technology Map Viewer also displays detailed timing delay information for the timing path. The State Machine Viewer provides a high-level view of finite state machines in the design and displays the internal structure of state machines in the design, including a more detailed view of the fan-in and fan-out of individual state nodes. The State Machine Viewer also displays the node transitions in table format. We use the technology map viewer to find out schematic of our design. With help of this function we can find out the TH34w2 is implemented on three LUTs: Set LUT, Reset LUT, and Hold LUT, as shown in Fig.3.2.3. The K-map, truth table, and logic function are available for each LUT in *Properties* pop-up window. The "Resource property editor" can be used to change the logic function of any LUT so that the K-map and truth table are changed accordingly as desired is shown as Fig 3.2.4. The resource property editor has a block to show and edit equation provides possibility to change the truth table by editing sum equation, is shown as Fig 3.2.5, thus, we can achieve fault injection by changing the truth table.

| 🏶 Quartus II - C:/altera/90sp1/quartus/NCL_TH34W2/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Viewer - Post-Mapping]                                                      |                 |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| $rac{2}{6}$ File Edit View Project Assignments Processing Tools W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ndow Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                             | _ 8 ×           |  |  |  |  |  |

| 🗋 🗅 🚅 🖬 👹 🎒 👗 🖻 💼 🗠 🗠 NCL_TH34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 💢 / 🏈 🏼                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 🐵 🕨 🧒 🔥 😓 🕹 🕲 😐                                                             |                 |  |  |  |  |  |