### UNIVERSITÀ DEGLI STUDI DI PAVIA

#### FACOLTÀ DI INGEGNERIA

Dipartimento di Ingegneria Industriale e dell'Informazione

Doctoral Thesis in Microelectronics CICLO: XXXV

# Mach-Zehnder Modulator Driver Designs in 28 nm CMOS Technology for Coherent Optical Systems

Supervisor:

Chiar.mo Prof. Danilo Manstretta

Coordinator:

Chiar.mo Prof. Piero Malcovati

Ph.D. Dissertation of Nicola Cordioli

# Declaration of Authorship

I, Nicola Cordioli, declare that this thesis titled Mach-Zehnder Modulator Driver Designs in 28 nm CMOS Technology for Coherent Optical Systems, and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given.

With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed: Nicola Cordioli

Date: 13/02/2023

#### UNIVERSITÀ DEGLI STUDI DI PAVIA

## Abstract

Facoltà di Ingegneria

Dipartimento di Ingegneria Industriale e dell'Informazione

#### Mach-Zehnder Modulator Driver Designs in 28 nm CMOS Technology for Coherent Optical Systems

by Nicola Cordioli

Since the beginning of the Internet, the number of connected devices has experienced an exponential growth. While increasing in users number, also an huge amount of services and applications have been made available through the network. The forecasts tell us that we are still at the beginning of this journey, even if the numbers are already hard to catch. In order to satisfy these demands, always more capable networks have been developed. Optical links have been proven to be the best candidates for long reach backbone connections, given the low losses introduced. The final target of a link is to deliver the highest amount of signals for a given bit error rate (BER). So, coherent modulations move towards this direction, providing better spectral efficiency compared with other schemes. Quadrature Phase Shift Keying (QPSK) and Quadrature Amplitude Modulation (QAM) can be exploited, but linearity and phase become crucial both for the electrical and optical design. Electro-optical modulators (EOM) are used to combine laser beams with different amplitudes and phases to provide such complex schemes. CMOS technology is not so widely spread through coherent applications, mainly because of the higher break-down voltage and  $g_m/I_D$  of BiCMOS devices. Yet CMOS has some interesting features, such as scalability and integration between analog and digital circuits, that might result in a reduction on the overall system costs. Furthermore in the latest technology knots, p- and n-type MOS transistors have very similar performance, making available complementary structures which can compensate for the poor MOS transconductance efficiency. The required electrical signal at the EOM input should be large enough to fully steer the light phase, linear to preserve phase and amplitude, and broad-band to achieve the highest bit rate. This thesis reports two CMOS designs. A first driver has been designed, fabricated and tested. The proposed structure is a four stages chain, with two gain blocks, a pre-driver and a main driver. To reach good linearity, cascoded pseudo-differential structures have been implemented, apart for the pre-driver. The cascode transistor allows to bias the common source (CS) in triode region, resulting in a linear voltage-to-current conversion. Working in triode region means a lower transistor efficiency, and a stronger relation between transconductance and biasing. In this way gain variability can be introduced relying on the  $g_m$  dependency by the drain-to-source voltage. The pre-driver is a pn source follower, which feeds the main driver without impairing the gain at high frequency. This solution is capable to provide 1.5  $V_{\rm pp-diff}$ , with a total harmonic distortion (THD) lower than 1.8%. The gain variation over frequency is always below 3 dB up to 58 GHz.

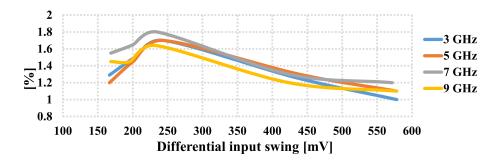

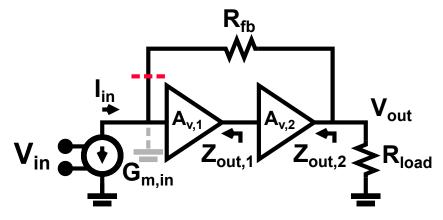

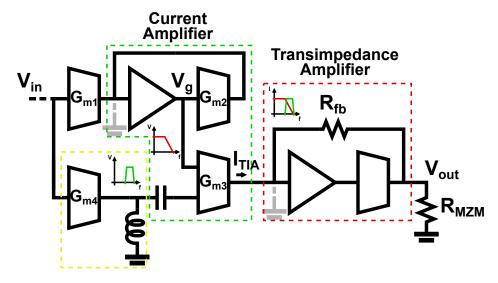

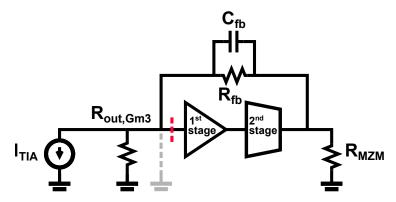

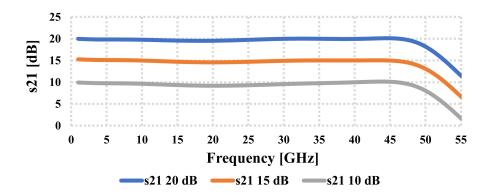

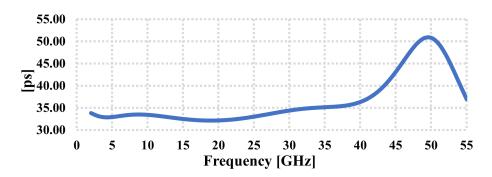

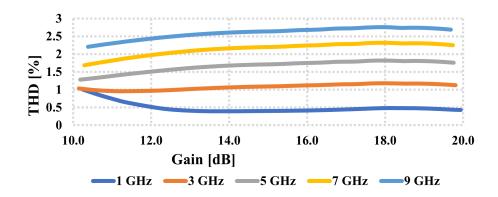

A second design has been realized and sent for fabrication, but at the moment of this dissertation not yet available. The first stage of this design is a transconductor, which provides a first voltage-to-current conversion, since the amplitude involved is small, the amount of distortion introduced (which is proportional to the voltage swing) is very poor. Part of the gain is provided in current domain through a current mirror-like structure, allowing, at least in principle, self cancellation of spurious components. Then, the output current-to-voltage conversion is realized over a closed-loop transimpedance amplifier (TIA). This solution intend to exploit loop gain ( $G_{loop}$ ) in order to reduce the distortion. At the same time, a loop designed with a phase margin (PM) lower than 60°, results in high frequency peak for the closed-loop transfer function. The simulated THD for 1.5  $V_{pp-diff}$  is frequency dependent, and it ranges from 0.3% at 1 GHz, up to 2% at 9 GHz. Fluctuations in the transfer function are below 3 dB up to 51 GHz, for all the gain configurations.

Not many CMOS works can be found in literature, making these two works a proof that this technology is viable even in terms of performance.

# Acknowledgments

A special thanks to professor Danilo Manstretta and professor Rinaldo Castello for the chance of being part of this PhD program and for the helps during these years.

An acknowledgment to Huawei for the partnership in this project. A special thanks to all the Milano Huawei R&D guys, who taught me a lot during these years.

Thanks to all the new people met during this journey, who became friends.

Thanks to my special family, who never lets me down.

Thanks to each one of you, who meant, means and will mean something important to me. I am grateful to have you in my life.

# Contents

| In | trod | uction                 |                                                  | 1  |

|----|------|------------------------|--------------------------------------------------|----|

| 1  | Intr | roducti                | ion of Optical Communications                    | 5  |

|    | 1.1  |                        | al Links                                         | 5  |

|    |      | 1.1.1                  | A brief introduction                             | 5  |

|    |      | 1.1.2                  | Optical systems                                  | 6  |

|    |      | 1.1.3                  | Laser diodes                                     | 6  |

|    |      | 1.1.4                  | Electro-optical modulator (EOM)                  | 8  |

|    |      | 1.1.5                  | Optical fibers                                   | 9  |

|    |      | 1.1.6                  | Photodiodes                                      | 10 |

|    | 1.2  | $\operatorname{Coher}$ | rent Optical Applications                        | 11 |

|    |      | 1.2.1                  | Coherent optical communication through the years | 11 |

|    |      | 1.2.2                  | Coherent and IM·DD                               | 12 |

|    |      | 1.2.3                  | Coherent transceiver                             | 12 |

|    |      | 1.2.4                  | Multi-level modulation formats                   | 14 |

|    | 1.3  | Laser                  | and Modulator Drivers                            | 16 |

|    |      | 1.3.1                  | Requirements and challenges                      | 16 |

|    |      | 1.3.2                  | Design approaches                                | 18 |

|    | 1.4  | State-                 | of-the-art solutions                             | 25 |

| 2  | A 5  | 8 GHz                  | z Bandwidth, Linear, Mach-Zehnder Driver         | 29 |

|    | 2.1  |                        | rity and Distortion                              | 29 |

|    |      | 2.1.1                  | Harmonic distortion                              | 29 |

|    |      | 2.1.2                  | Triode region                                    | 32 |

|    | 2.2  | Transı                 | mitter Design                                    | 33 |

|    | 2.3  |                        | ole Gain Amplifier                               | 35 |

|    |      | 2.3.1                  | Gain programmability                             | 35 |

|    |      | 2.3.2                  | Reverse triple resonant network                  | 35 |

|    |      | 2.3.3                  | Common-mode gain                                 | 37 |

ii CONTENTS

| 2.4   | Second amplification stage                | 38 |

|-------|-------------------------------------------|----|

|       | 2.4.1 Triple resonant network             | 39 |

|       | 2.4.2 Common-mode gain                    | 40 |

| 2.5   | Pre-Driver                                | 40 |

| 2.6   | Main driver                               | 42 |

| 2.7   | Input line                                | 43 |

| 2.8   | Sample measurements and validations       | 45 |

| 3 A I | MZM Driver Based on Closed-Loop Solutions | 49 |

| 3.1   | Closed-loop Distortion and Bandwidth      | 49 |

|       | 3.1.1 Distortion in closed-loop systems   | 49 |

|       | 3.1.2 Bandwidth in closed-loop systems    | 51 |

| 3.2   | Transmitter block diagram                 | 53 |

| 3.3   | Transconductor $G_{m1}$                   | 54 |

| 3.4   | Closed-loop Current Amplifier             | 55 |

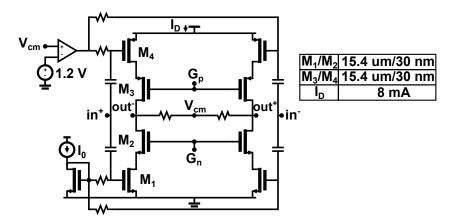

|       | 3.4.1 Operational Amplifier               | 56 |

|       | 3.4.2 Transconductor $G_{m2}$             | 57 |

|       | 3.4.3 Transconductor $G_{m3}$             | 57 |

| 3.5   | Narrowband High Frequency Amplifier       | 58 |

| 3.6   | Output TIA design                         | 60 |

|       | 3.6.1 TIA 1 <sup>st</sup> stage           | 61 |

|       | $3.6.2$ TIA $2^{\mathrm{nd}}$ stage       | 63 |

| 3.7   | Design Simulations                        | 63 |

| Concl | usion                                     | 67 |

# List of Figures

| 1.1  | Simplified communication optical system                      | 6  |

|------|--------------------------------------------------------------|----|

| 1.2  | Laser diode input-output characteristic                      | 7  |

| 1.3  | Optical communication system with an external optical modu-  |    |

|      | lator                                                        | 8  |

| 1.4  | PSK modulated signal from a V <sub>RF</sub> one              | 9  |

| 1.5  | Fiber section.                                               | 10 |

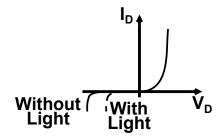

| 1.6  | Voltage-current photodiode characteristic                    | 11 |

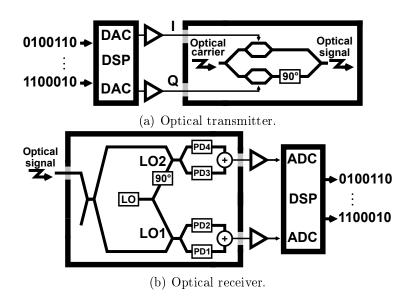

| 1.7  | DSP based optical transceiver                                | 13 |

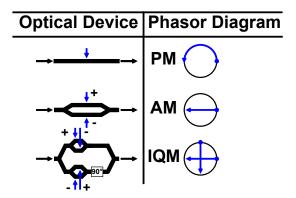

| 1.8  | Phasor diagram and optical device structures for PM, AM and  |    |

|      | IQM                                                          | 14 |

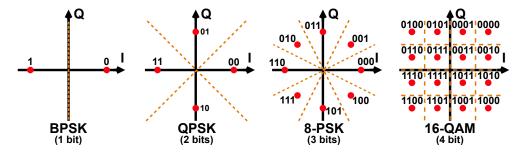

| 1.9  | Constellation masks for BPSK, QPSK, 8PSK and 16QAM mod-      |    |

|      | ulation formats                                              | 15 |

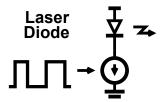

| 1.10 | Laser driver schematic                                       | 16 |

| 1.11 | Eye diagram mask                                             | 17 |

| 1.12 | Small signal model for two stages cascaded amplifiers        | 18 |

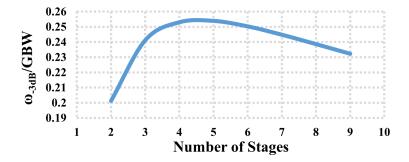

| 1.13 | Normalized bandwidth as a function of N for $A_{tot} = 20dB$ | 20 |

| 1.14 | Laser diode current steering                                 | 20 |

| 1.15 | Cascade of a main driver, pre driver and a gain stage        | 21 |

| 1.16 | Source follower output impedance analysis.                   | 22 |

| 1.17 | Voltage swing improvements in a cascoded solution            | 23 |

|      | Main driver with no current source                           | 24 |

| 1.19 | Schematic solution proposed by [13]                          | 25 |

|      | Schematic solution proposed by [14]                          | 27 |

| 2.1  | Simple non-linear model for a transconductor                 | 30 |

| 2.2  | Cascoded transconductor analysis.                            | 31 |

| 2.3  | THD versus $V_d$ amplitude                                   | 32 |

| 2.4  | THD versus V <sub>in</sub> amplitude                         | 32 |

| 2.5  | Transmitter block diagram.                                   | 33 |

| 2.6  | Variable gain amplifier schematic                                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------|

| 2.7  | Variable gain amplifier THD versus gain                                                                                  |

| 2.8  | VGA third harmonic component versus gain                                                                                 |

| 2.9  | Small signal model for Figure 2.6                                                                                        |

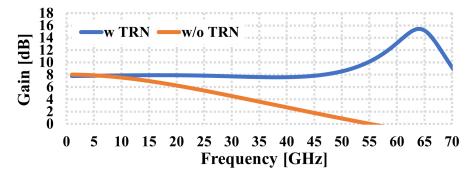

| 2.10 | VGA gain with and without the reverse triple resonant network. 37                                                        |

| 2.11 | Second amplification stage                                                                                               |

| 2.12 | Small signal model for Figure 2.11                                                                                       |

|      | Second stage gain with and without the triple resonant network. 40                                                       |

|      | Pre-driver schematic                                                                                                     |

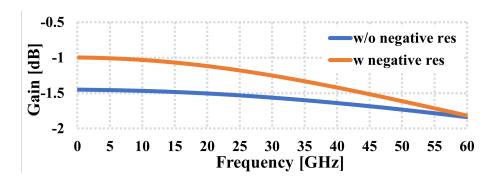

| 2.15 | Source follower gain, with and without negative resistance 41                                                            |

| 2.16 | Main driver schematic                                                                                                    |

|      | Common sources triode biasing distortion for 1.5 V <sub>ppdiff</sub> 42                                                  |

|      | Input line model                                                                                                         |

|      | S-parameters of the input line model proposed in Figure 2.18 44                                                          |

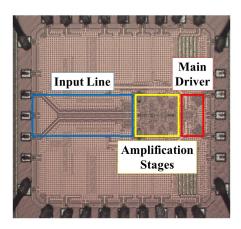

|      | Fabricated die microphotography                                                                                          |

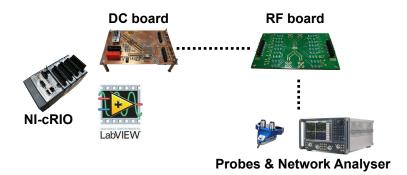

|      | Measurements setup                                                                                                       |

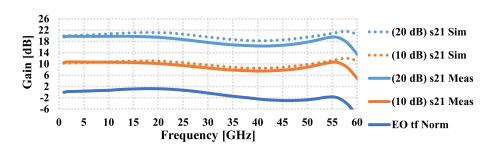

|      | $s_{21}$ measured and simulated                                                                                          |

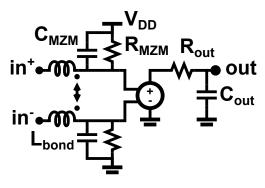

| 2.23 | MZM model used as loading for the electro-optical simulation 46                                                          |

| 2.24 | Measured group delay over frequency                                                                                      |

|      | THD with a fixed output swing of 1.5 V <sub>ppdiff</sub>                                                                 |

| 2.26 |                                                                                                                          |

|      |                                                                                                                          |

| 3.1  | Two stages loop implementation                                                                                           |

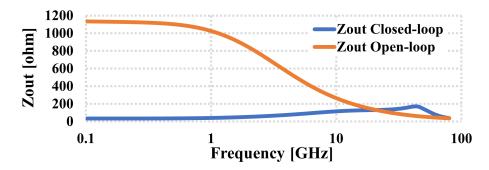

| 3.2  | Open-loop and closed-loop output impedance                                                                               |

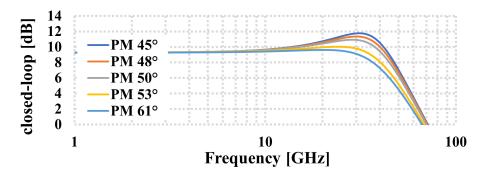

| 3.3  | Closed-loop transfer function at different phase margin value 52                                                         |

| 3.4  | Proposed transmitter block diagram                                                                                       |

| 3.5  | Transconductor $G_{m1}$                                                                                                  |

| 3.6  | Closed-loop current amplifier                                                                                            |

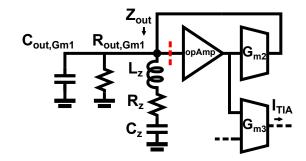

| 3.7  | Z <sub>out</sub> with and without the zero                                                                               |

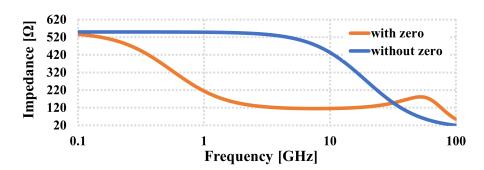

| 3.8  | First stage Operational amplifier                                                                                        |

| 3.9  | Second stage, transconductor $G_{m2}$                                                                                    |

| 3.10 | Transconductor $G_{m2}$                                                                                                  |

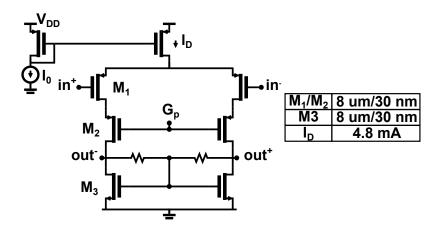

|      | VGA third harmonic component versus gain                                                                                 |

|      | Currents flowing into the out TIA over frequency                                                                         |

|      | Output TIA                                                                                                               |

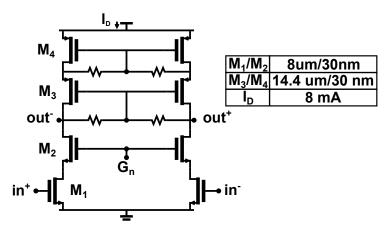

|      | TIA 1 <sup>st</sup> stage schematic                                                                                      |

| 3.15 | Biasing replica                                                                                                          |

| 2 16 |                                                                                                                          |

|      | TIA $1^{st}$ stage, transconductance normalized to $g_m$ ( $g_{m,M3/M4}$ ). 62                                           |

| 3.17 | TIA $1^{\text{st}}$ stage, transconductance normalized to $g_m$ $(g_{m,M3/M4})$ . 62 TIA $2^{\text{nd}}$ stage schematic |

| LIST OF FIGURES | V |

|-----------------|---|

|-----------------|---|

| 3.20 | Simulated group delay over frequency | 64 |

|------|--------------------------------------|----|

|      |                                      |    |

# List of Tables

## Introduction

Forecasts say that in the upcoming years (up to 2023) nearly 5.3 billion of people will have Internet access. In average, each person, will connect to the network 3.6 devices. An important share of these numbers will be the growth of Machine-to-Machine (M2M) connections, which will cover half of the global connections. Within this category, also referred as Internet of Things (IoT), connected home applications will have the largest share, while connected car applications will be the fastest to grown up. Together with the growing number of on-line devices, networks performance are expected to improve. The average mobile connection speed will reach 43.9 Mbps, while for the fresh 5G the data rate will hit 575 Mbps [1]. Taking into account these growing broadband requirements of individuals, homes and enterprises, fiber networks are expected to deliver to these users 10-gigabit connections. To get this possible, future access network and backbone equipments will need to support terabitlevel interfaces. Especially the second one will support from 40 to 100 Tbit/s. Terabit-level speed will also interest many other parts of the network besides the backbone, as data center. So far 200G and 400G Ethernet connections are already available, but to cope with the previous requirement, interface technology that support speeds of 800 Gbit/s or even 1.6 Tbit/s has to be standardized. Two ways are under investigation, pluggable optics modules and co-packaged optics (CPO). Both of them will have place into this market, but the CPO is preferable because of the power and density issues of the pluggable solutions. Furthermore, the demand of long-distance transmission capacity of more than 100 Tbit/s per fiber will push the development of wavelength division multiplexing (WDM) equipments and newer high-band rate electro-optic modulation schemes. For both backbone and home connections, coherent detection technology will be used. This will significantly improve the receiver sensitivity, while supporting modulation formats with higher spectral rates. More complex schemes as quadrature shift keying (QPSK) and m-quadrature amplitude modulation (m-QAM), will be available, in order to achieve higher data rates [2].

2 INTRODUCTION

Design of electrical and optical components are no more stand alone process. For short-reach applications, as data center networks, silicon photonics (SiPh) solutions are already available [3]. The availability of always more scaled and aggressive silicon technology, allows to acquire very high-speed electrical signal. This enables digital signal process (DSP) cores to equalize linear transmission impairments. CMOS and FinFET give the chance of integrating on the same die both the acquisition and processing function, lowering the system costs. Optical links are proving to be the proper infrastructure, capable to bear and even to push this massive demand of connections between devices, machines and people.

The next pages will be organized as described:

In Chapter 1: an overview of an optical communication link is reported, and why coherent applications are moving a lot of interests. To get familiar with the topic optical components as EOMs, fibers and photodiodes are introduced. Theory about coherent transmission and detection are reported, together with the most used modulation schemes. Then the focus is moved on the silicon world, introducing transmitter and receiver, and what they are supposed to do. The electrical specifications required to these devices are highlighted, with a brief dissertation on why CMOS has been preferred against the commonly exploited BiCMOS.

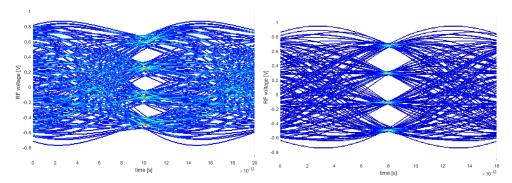

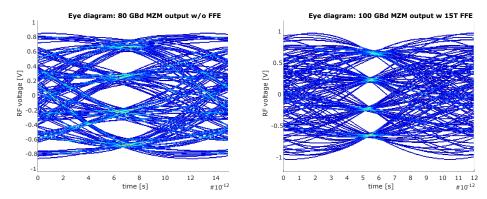

In Chapter 2: a linear Mach-Zenhder modulator driver is presented. This work has been fabricated and electrically fully characterized. A four stages cascade compose the transmission chain, the first two of them provide most of the gain, while the last two are designed for bandwidth and linearity purposes. To improve the linearity of each stage, the transistor triode region has been exploited. A continuous 10 dB gain variation is provided, moving the MOS among the triode biasing. The resulting THD is always lower than 1.8 % at 1.5  $V_{pp\text{-}diff}$ , and it is reduced for larger input amplitude. The -3 dB electrical bandwidth reach 58 GHz, and resonant networks have been introduced to extend it. The overall power consumption is 297 mW.

In **Chapter 3:** a second linear modulator driver is presented. This chapter reports post-layout simulations, because the chip fabrication is on going. The design is mostly based on closed-loop circuits. An input voltage-to-current conversion is realized through a transconductor, then part of the gain in realized in the current domain, with a current mirror-like solution. The output current-to-

voltage conversion is realized by a closed-loop TIA, so over a resistor which is linear in principle. Designing loops with a phase margin lower than  $60^\circ$  results in high frequency peaking for the closed-loop transfer function. The distortion now is frequency dependent, and ranges from 0.3% at 1 GHz, to 2.1% at 9 GHz. The power consumption is 235 mW, while the -3 dB bandwidth is 52 GHz.

4 INTRODUCTION

# Chapter 1

# Introduction of Optical Communications

#### Abstract

Through the years fibers have been preferred to coaxial cables when it comes to transport high-speed and large volumes of data. By the way, low losses and large bandwidth are not enough to stand the ever growing demand for always more capable link. Spectral efficiency has became a key parameter in the last decade, introducing the need of always more complex modulation schemes. This chapter deals with an introduction to optical systems, describing the main building blocks and how they works. Advantages and requirements of coherent detection are introduced. Transmitter and receiver electrical features are described, with the required performance. To conclude, some usual transistor level solutions with benefits and drawbacks are presented.

## 1.1 Optical Links

#### 1.1.1 A brief introduction

The reasons behind the widespread use of optical communication for high-speed data, should be found on the large bandwidth and the poor losses provided by optical fiber. To make a comparison, at 1 GHz, coaxial cable losses can reach 500 dB/km, while fiber attenuation at 50 GHz is 0.2 dB/km. Considering also wireless communications, for carriers around GHz the losses per meter reach several decibels, with 100 Mb/s as data rates. The large available free bandwidth, allows to cast several channels over different wavelengths (frequencies), on the same physical mean. Historically, this has started the Tb/s data rate

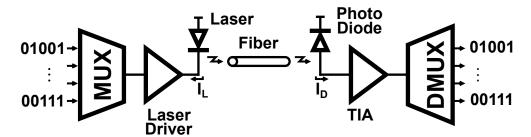

Figure 1.1: Simplified communication optical system.

era. This can easily clear up why when it comes to long reach communication links (e.g. the internet traffic between Europe and the United States), there is no better solution than exploiting the light. Theory in the next sections are inspired by [4].

#### 1.1.2 Optical systems

Figure 1.1 shows a very simplified optical system. The communication starts with a multiplexer (MUX), which serialize the parallel bit streams coming from a DSP. A driver takes the bit stream, and it feeds the electro-optical transducer with the right power level. The transducer (e.g. a laser) converts the electrical power into optical form (e.g. light on for logical ONEs and light off for ZEROs), making the data suitable to travel through the fiber. On the receiver side, light is back converted into current through a photodetector (e.g. a photodiode). A TIA turns this current into voltage, allowing the demultiplexer (DEMUX) to restore the parallel bit streams. The system in Figure 1.1 is still far away from a proper optical link, but it introduces enough elements to get familiar with the topic and for the purpose of this dissertation. Through the years, the introduced blocks have changed a lot, because of newer technologies, architectures and requirements in both the electrical and optical fields, but still the overall system can be represented as Figure 1.1. The next sections will deal briefly with lasers, photo-diodes and fibers, then the focus is moved to the electrical part.

#### 1.1.3 Laser diodes

A laser is an electro-optical transducer, based on semiconductor material, capable to turn electrical signal into light. The spectrum of this light is very sharp, it means that the energy provided is heavily concentrated around one frequency. Furthermore, the beam produced is very focused on space, so it can travel for long distance without scattering or spreading. It is composed by pn

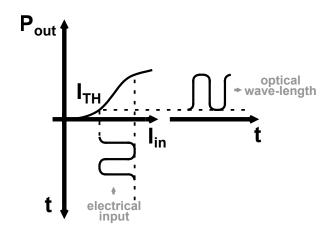

FIGURE 1.2: Laser diode input-output characteristic.

junction and mirrors. While current flows through the junction, electrons jump from conduction to valence band, releasing energy as photons. Mirrors and lens create an oscillation which is responsible of the spectrum sharpness. The input-output laser characteristic is reported in Figure 1.2. I<sub>TH</sub> is the threshold current, and while the current is below this value no output power is generated. Exceeding I<sub>TH</sub>, the output power changes almost linearly with the input current, up to the saturation level. The more efficient the laser, the lower is the current required for the same amount of output power. The quantum efficiency is given by the ration of the output photons and the input electrons, for a given time interval. So this defines the required input power to provide a given optical power. As told, in principle a laser generates a single wave-length, so a perfect monochromatic light. Actually, the light spectrum contains side modes, which lead to other issues while propagating through the fiber.  $I_{TH}$  is a biasing current, so no information is carried by this current. Lowering as much as possible this current means increasing the efficiency. Furthermore, moving in this direction, also the ratio between high and low output power is increased, making the detection between ONEs and ZEROs easier. Voltage drop across the device is defined by the threshold current and the signal current, ranging from 1.5 to 3 V. This means that high supply voltages are required, making the transistor breakdown voltage an issues. Fiber attenuations and receiver sensitivity defines the required output power from the laser. To provide high power level, the semiconductor area is increased, introducing higher input parasitic capacitance, lowering the speed.

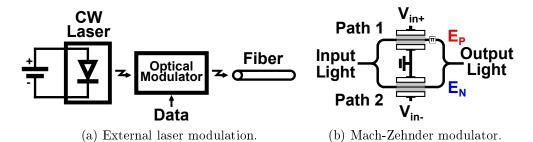

FIGURE 1.3: Optical communication system with an external optical modula-

#### 1.1.4 Electro-optical modulator (EOM)

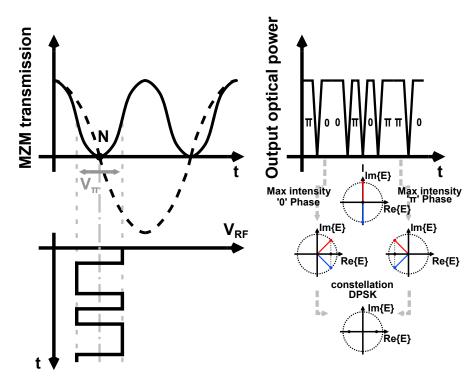

Laser diode has several limits as turn-on delay, relaxation oscillation, frequency chirping. This dissertation does not deal with such phenomena because more related to the physic of the device. Nonetheless, given these non idealities, directly driving the laser results in limitations for data rate and fiber length. For high-speed applications is common to have a continuous source of light provided by a laser, which can be considered as the *carrier*, while an external modulator provides the information as shown in Figure 1.3a. This kind of devices are also called interferometer, because through them an electrical signal can interfere with light. For our purposes the EOM used is a Mach-Zehnder Modulator (MZM). In this device the propagation velocity depends by the applied field across it. This allows light phase shifting based on the electrical signal applied. As shown in Figure 1.3b the same source of light can be splitted in different paths which experience different phase shifts. Recombining them together, the output amplitude will depend by the delay, and so a function of the electrical signal. This allows to exploit complex modulation as m-QAM and m-QPSK.  $V_{\pi}$  is the voltage required by the MZM to introduce 180° of phase shift. This value trades with the device length, increasing it will reduce the  $V_{\pi}$ . At the same time, a wider MZM will introduce higher parasitic capacitance limiting the speed. So to define the electrical requirements is mandatory to know the modulator involved. Figure 1.4 shows how to proper bias Figure 1.3b to obtain a phase shift keying modulation from a driver V<sub>RF</sub> signal. V<sub>RF</sub> is equal to the difference between V<sub>in+</sub> and V<sub>in-</sub> from Figure 1.3b. To provide the PSK modulation, the MZM should be biased at the null bias point (N). The two optical paths are affected by signals with the same magnitude but opposite phases, this enables the phase modulation of the optical field.  $V_{RF}$ is a NRZ driving signal. With a common mode signal as V<sub>RF</sub> means that E<sub>P</sub>

Figure 1.4: PSK modulated signal from a  $V_{\rm RF}$  one.

and  $E_N$  experiences the same phase shift, resulting with opposite phases at the combiner, yielding a zero output optical power. While, when a differential signal representing a logic ONE is applied as  $V_{RF}$ , the phase shifts of  $E_P$  and  $E_N$  would be in opposite directions, meaning a non-zero optical signal and a point on the real axis of the constellation map. A logic ZERO is represented by a  $V_{RF}$  with opposite phase, resulting in a output signal with the same magnitude as the ONE but with a  $\pi$  phase shift. For this modulation, ONEs and ZEROs have the same magnitude while a  $\pi$  phase shifted optical field. To further increase the spectral efficiency, the NRZ amplitude modulation can be substitute with a PAM-4 signal, making the constellation a 4-PSK [5]. Deeper analysis about modulations, constellations and spectral efficiency are available in the next sections.

#### 1.1.5 Optical fibers

In optical systems, light travels through fibers. As introduced, for long reach communications, fibers are preferred to twisted and coaxial cables, because of

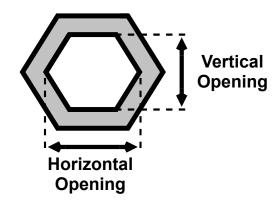

FIGURE 1.5: Fiber section.

Cladding

their wider bandwidth and the lower attenuation. A section of a fiber is represented in Figure 1.5. The laser beam travels along the core, made by silica (a material derived by silicon dioxide), and it is confined there thanks to the cladding. The jacket works as shield, to protect the fiber. Core diameter ranges from 5 to 10  $\mu$ m, a jacket can reach around 100  $\mu$ m. The small dimension makes the alignment between fibers very hard, and results in poor stiffness. Losses introduced by fibers directly define the maximum distance between transmitter and receiver. Two kind of losses can be found. Absorptive losses, when the travelling wavelength excites atomic resonances in the fiber material or in the impurities. Radiative losses, when, because of the scattering, light exits the core radiating through the cladding. The higher cost and mechanical difficulties have pushed the development of different material than silica. Plastic materials as, polymethylmethacrylate, polystyrene and polycarbonate are used for fibers. These materials allow to have larger core diameter, solving stiffness and mechanical issues. One of the most important drawbacks are the higher losses introduced.

#### 1.1.6 Photodiodes

Light or photons travelling through the fiber are converted into electrical signal by means of a photodiode. As the EOM for the transmission side, the photodiode defines some receiver electrical requirements as speed and sensitivity. Photons can be seen as packs of energy. These packs hitting the photodiode pn junction enable electrons to jump from the valence to the conduction band. Electrons and holes are formed in this way, and reverse biasing the diode a current flow can be generated. In Figure 1.6 it is highlighted that reverse biasing in the proper way the junction, the presence of light lets current flows.

The current generated, I<sub>P</sub>, is proportionally linear with the optical power P<sub>OP</sub>

FIGURE 1.6: Voltage-current photodiode characteristic.

$$I_P = R_{PH} \times P_{OP},\tag{1.1}$$

where R<sub>PH</sub> is the diode *responsivity*. This value can be increased with wider junction, introducing higher parasitic capacitance. In the latest systems, to have higher performance, an optical amplifier is placed between the fiber and the photodiode.

## 1.2 Coherent Optical Applications

#### 1.2.1 Coherent optical communication through the years

In optical communications, coherent solutions have always been considered for the receiver high sensitivity, so for the unrepeated transmission distance. The counterpart of this solution is the intensity-modulation and direct-detection (IM·DM), which attracted lots of interests during the '90, thanks to the high-capacity wavelength-division multiplexing (WDM). Digital carrier-phase estimation in coherent receivers, has moved back interest for coherent applications in the last fifteen years. Such an interest is manly due because of the possibilities of exploiting m-PSK and m-QAM, meaning an increased spectral efficiency compared with IM·DM. Coherent detection allows to preserve phase information after detection, so linear transmission impairments, as group-velocity dispersion (GVD) and polarization-mode dispersion (PMD), can be equalized thanks to DSP. Coherent detection assisted with high-speed DSP, together with WDM channels with 50 GHz spaced grids, prove a capability up to 8.8 Tb/s through a single fiber. The request for the coming years, are bit rates close to 400 Gb/s per WDM channel. The next sections will follow [6].

#### 1.2.2 Coherent and IM·DD

IM·DD is a widely employed optical communication scheme. It is based on the intensity modulation of a semiconductor laser, transmitted through an optical fiber then detected by a square-law detector. Since the detection relies on the received amplitude, carrier phase and state of polarization (SOP) of the light does not affect the sensitivity, making this solution the preferred one. On the other hand, coherent detection involves a local oscillator (LO) to retrieve the phase information, which is defined by the in-phase and quadrature (IQ) components (or amplitude and phase) of the complex amplitude and the SOP of the incoming signal. This makes the coherent receiver very sensitive to phase and polarization fluctuations. So coherent detection tends to be more complicated than IM·DD. The SOP receiver dependency has been solved detecting each polarization of the transmitted signal through orthogonally polarized LO lasers, and post-processing. This is known as polarization-diversity scheme. In order to further increase the unrepeated transmission distance, quantumnoise-limited receiver has been introduced. This limit can be hit increasing sufficiently the LO power injected into the coherent receiver. Heterodyne systems involved a down conversion to an intermediate-frequency (IF). The most common modulation was the frequency-shift keying (FSK), because the easiness of modulating the laser frequency by changing the biasing current. The required IF frequency should be much higher than the signal bit rate. For homodyne receivers, the downconversion falls directly on the base band, so no high frequency IF is required. Here the carrier phase should be tracked in the optical domain by the LO, so an optical phase-locked loop (OPLL) is required. The phase error between the LO and the carrier takes a while before closing the loop on the LO controller. Because of such loop delay, it is not easy to maintain the stability and the bandwidth is usually limited to 1 MHz. So for large frequency drift, tracking results very hard. The high IF required and the difficulty in tracking carrier with large frequency fluctuation, make the heterodyne and homodyne solutions much more complex than the IM·DD one.

#### 1.2.3 Coherent transceiver

From the previous section, looking for simplicity, the IM·DD is the best choice. But trends and forecasts say that the target is the link capability. A viable solution has been found in combining WDM and coherent detection. WDM allows to use a number of optical carrier signals onto a single optical fiber by using different wavelengths of laser light. This increases straightforward the amount of data that can travel through a link. Despite the already introduced struggles,

FIGURE 1.7: DSP based optical transceiver.

coherent broadens the data processing chance. Functions as compensation for GVD and PMD of fibers can be implemented, and multi-level modulation formats can be introduced. For example, with a QPSK modulation/demodulation scheme, with optical IQ modulation (IQM), the bit rate can be doubled with the same baud rate [7]. These equalization operations have been made available thanks to very high speed DSPs. Figure 1.7 shows the main building blocks of a transceiver. The data come to the transmitter as parallel streams of bit (Figure 1.7a). A DSP serializes these streams and groups bits to provide the I and Q signals. The modulated signals are impressed on the carrier by an EOM driven through an electrical buffer. Mixing and 90° carrier phase shift are performed in the optical domain. So now we talk about optical IQ components. On the receiver side (Figure 1.7b), the modulated optical carrier is down-converted at baseband by optical mixers. The electrical I and Q signal are restored after photodiodes and TIAs. A DSP processes and de-serializes the bit streams [8] [9]. The introduced homodyne receiver block diagram does not deal with the already told optical phase locking issue. This because DSP itself provides a reliable and efficient carrier phase estimation, removing the stability concerns introduced by the OPLL. Because of all of these post-detection processing, this has been renamed digital coherent receiver. This introduces the requirement for very high-speed ADC and DSP.

FIGURE 1.8: Phasor diagram and optical device structures for PM, AM and IQM.

#### 1.2.4 Multi-level modulation formats

Coherent detection opens the possibilities to exploit any kind of multi-level modulation formats [10]. Phase modulation (PM), amplitude modulation (AM) and (IQM) lead to different phasor diagrams and they require different optical device structures as shown in Figure 1.8. Light phase-modulation can be achieved through non-centrosymmetric crystal, introducing a refractive-index variation linearly proportional with the applied voltage. Light phase can also be modulated through interferometer as MZM, driven in push-pull mode. Then recombining paths with different phases results in AM. The IQM can be provided by phase modulating lights with MZMs, while introducing a phase shift of  $\pi/2$ . The last one can perform any kind of multi-level modulation format. Another degree of freedom can be introduced by light polarization. Electromagnetic wave can travel with different spatial orientations, called polarizations. This enable to send two orthogonally polarized laser beams on the same fiber, obtaining a polarization multiplexed-signal. SOP of the incoming signal can be estimated thanks to digital signal processing. WDM, multi-level modulations and light polarizations are all uncorrelated modes, meaning that they introduce more degrees of freedom in data transmission and detection. Spectrum efficiency (SE) is a figure of merit defined as bit/s/Hz/polarization, so it normalizes the bit rate to the light bandwidth (WDM) and polarization. For a binary modulation format the spectral efficiency is 1 bit/s/Hz/polarization. In a multi-level format with m bits of information per symbol, the spectral efficiency reaches m bit/s/Hz/polarization. As examples, Figure 1.9 represents the constellation distributions for BPSK, QPSK, 8PSK and 16QAM schemes. Respectively, these formats can group 1, 2, 3, 4 bits for each symbol.

FIGURE 1.9: Constellation masks for BPSK, QPSK, 8PSK and 16QAM modulation formats.

The single channel link capacity C is defined by the Shannon theorem [11]

$$C = \frac{WD}{2}log_2(1 + \frac{S}{N}), \tag{1.2}$$

in which W is the channel bandwidth, D the modulation format dimension and S/N is the signal to noise ratio. As examples, for an IQ single polarization transmission the dimension is 2, becoming 4 for dual polarization transmission. Writing (1.2) as

$$\frac{C}{W(D/2)} = log_2 \bigg[ 1 + \frac{C}{W(D/2)} \frac{E_b}{N_0} \bigg], \tag{1.3} \label{eq:1.3}$$

where the SNR has been rewritten as the Shannon limit of the spectral efficiency  $(SE_{lim} = C/[W(D/2)])$  multiplied by the ratio of energy-per-bit to noise spectral density. So the (1.2) becomes

$$SE_{lim} = log_2 \left[ 1 + SE_{lim} \frac{E_b}{N_0} \right]. \tag{1.4}$$

Once defined the Shannon limit of the spectral efficiency provided by the channel, the required energy-per-bit to noise spectral density ratio can be defined as

$$\frac{E_b}{N_0} = \frac{2^{SE_{lim}} - 1}{SE_{lim}}. (1.5)$$

Given a specific modulation format, with M as number of symbols, the SE can be written as

$$SE = \frac{log_2M}{D/2}. (1.6)$$

FIGURE 1.10: Laser driver schematic.

Another important specification is the bit error rate, which defines how many wrong bit detections are allowed. The incoming signals are corrupted by noise, phase drifts and others non idealities. Hence the detected symbols can be described with a Gaussian density function, centered around the ideal values reported in Figure 1.9. The stronger the non idealities the higher is the possibilities that one symbol crosses the thresholds, leading to a wrong detection. There is only one bit difference between adjacent symbols (Gray coding), in this way wrong detection means just one bit error. Spreading the Gaussian because of non idealities can increase the BER as much as reducing distances between levels. Multilevel formats help to increase the SE as proven by (1.6) but it also requires higher  $E_b/N_0$  (1.5) to maintain the same BER. Increasing the energy per bit improves the spacing between levels, while reducing the noise spectral density squeezes the Gaussian. Therefore, decided or given the modulation format, and the BER required by the standard, the  $E_b/N_0$  can be found by simulations.

#### 1.3 Laser and Modulator Drivers

#### 1.3.1 Requirements and challenges

The easiest way to describe a driver is to consider it as a simple current source for the electro-optical device (EOD), switching between on and off based on the bit stream to be transmitted (Figure 1.10).

There are several important requirements to be provided. Switching speed is fundamental to ensure light modulation with minimal inter-symbol interference. To generate enough optical power corresponding to logical ONEs, high output current is required. The high current generates voltage swing across the diode, so the driver output impedance is preferred to be high, in order to have as less as possible current variation. For what concern EOM drivers, previously introduced, speed is still a mandatory specification, while regarding the electrical signal to be generated there is something different. As reported

FIGURE 1.11: Eye diagram mask.

in Figure 1.3a, an external generator provides the optical power, while the EOM modulate the light amplitude and phase. The electrical signal should be capable to generate an electrical field strong enough to introduce the needed phase drift into the optical system. The impedance of these EOMs is very low, ranging from 30 to 50  $\Omega$ . This leads to large voltage and current signals. Based on the applications, distortion becomes relevant. PAM4 modulations are not so demanding in terms of linearity, while m-QPSK and m-QAM are based on poor distortion design. Speed and large swing go in opposite direction in terms of technology. Short channel transistors are mandatory to reach high frequencies. The shorter the channel the lower the breakdown voltage available, which is not suitable for large amplitude applications. Matching these two specifications with the same technology is a tough design challenge. At this large amplitude, transistor small signal modelling is good to understand whether the proposed solution is suitable or not. However, to assess a design goodness other tools are preferred. Eye diagram together with inter-symbol interference (ISI), allow a reliable glance to the system performance. Rise and fall times should be below the symbol period. Time is not the only constrain if multilevel modulation is involved. Amplitude overshoot and ringing can lead to detection impairments. In order to evaluate if the transmitted signal is suitable for a specific standard, masks are defined (Figure 1.11). Maximum tolerable eye closure in vertical and horizontal directions are defined by these tools. Since the high frequencies involved, these applications can be defined as millimeter-wave. This involves broadband matched terminations even for short distances. The silicon die and the EOM are usually co-packaged, or mounted one on the top of the other (flip-chip), so, matching for this termination is not required. Whereas for the input, the DSP which generates the data bit stream can be placed in a differ-

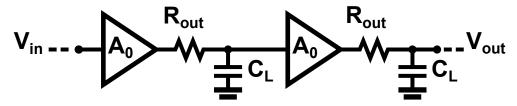

FIGURE 1.12: Small signal model for two stages cascaded amplifiers.

ent die and package, and connections are realized through transmission lines. Broadband input matching is then mandatory, to avoid back reflection and power losses.

#### 1.3.2 Design approaches

This paragraph reports several guidelines, in order to properly start a driver design. Given the required amplification, considerations about the number of stages involved can be done. Small signal analysis is a good approach at this level. Each stage can be represented as a voltage amplifier  $A_0$ , an output resistance  $R_{\rm out}$  and a load capacitance  $C_{\rm L}$ , as shown in Figure 1.12, and it behaves as low-pass filter, because of the single pole introduced.

The limited bandwidth affects the eye opening both horizontally and vertically, introducing ISI. In a two levels modulation, when a series of ZEROs are followed by a ONE (or the other way around) the settling voltage at each output can be described as

$$V_{out} = V_0 \left( 1 - e^{-\frac{t}{\tau}} \right), \tag{1.7}$$

where  $\tau$  is the time constant defined as  $R_{out}C_L$ . Given the bit period  $T_b$ , the error between  $V_{out}$  at  $t = T_b$  and the final value is

$$V_0 - V_{out}(T_b) = V_0 \cdot e^{-\frac{T_b}{\tau}}$$

$$= V_0 \cdot e^{-\frac{2\pi f_{-3dB}}{R_b}},$$

(1.8)

writing  $T_b = 1/R_b$  and  $f_{-3dB} = 1/(2\pi R_{out}C_L)$ . It is straightforward that, for a given  $f_{-3dB}$ , the error increases with the bit rate. Choosing  $R_b$  close to  $2f_{-3dB}$  leads to a 8.32% normalized amplitude error (taking into account both the high and low level ISIs), hence a total eye closure of |20log(1-8.32%)| = 0.754 dB. In a one-pole system is quite easy to relate the bandwidth to the eye opening,

as in this case. Considering more poles and zeros, as in Figure 1.12, system level simulations are used to estimate the transmitter speed requirement. The small signal transfer function from  $V_{\rm in}$  to  $V_{\rm out}$  (with  $R_{out}$ ,  $C_L$  and  $A_0$  equal through the chain) can be defined as

$$H(s) = \left(\frac{A_0}{1 + \frac{s}{\omega_0}}\right)^2,\tag{1.9}$$

where the the -3 dB bandwidth of each stage is  $\omega_0 = 1/(R_{out}C_L)$ . -3 dB bandwidth can be used as a small signal measure for the circuit speed. Applying this attenuation to the amplitude of the (1.9),

$$\left[\frac{A_0}{\sqrt{1 + (\frac{\omega_{-3dB}}{\omega_0})^2}}\right]^2 = \left(\frac{A_0}{\sqrt{2}}\right)^2,\tag{1.10}$$

the cascade  $\omega_{-3dB}$  results

$$\omega_{-3dB} = \omega_0 \sqrt{\sqrt{2} - 1} \approx 0.644\omega_0.$$

(1.11)

The (1.11) shows that cascading two identical stages, means almost a 35% of bandwidth reduction. Repeating for N identical stages, the resulting -3 dB bandwidth can be defined as

$$\omega_{-3dB} = \omega_0 \sqrt{\sqrt[N]{2} - 1}. (1.12)$$

So, the bit rate and eye opening knowledge can be used to understand the transmitter  $\omega_{-3dB}$  required, and then the  $\omega_0$  of each stage. A gain-bandwidth (GBW) trade-off should be found in order to decide a proper number N of stages. Given the overall gain  $(A_{tot})$ , it can be achieved with a large number of stages with wide bandwidth and poor gain, or the other way around. The GBW product can be defined as  $A_0\omega_0$  and assumed to be constant for the same technology and power consumption. The transfer function of each stage can be then defined as

$$H(s) = \frac{\frac{GBW}{\omega_0}}{1 + \frac{s}{\omega_0}}. (1.13)$$

With N identical stages,  $A_{tot} = (GBW/\omega_0)^N$  and so  $\omega_0 = B/\sqrt[N]{A_{tot}}$ , results in a overall bandwidth approximatively

$$\omega_{-3dB} \cong GBW \frac{0.9}{\sqrt{N} \sqrt[N]{A_{tot}}}.$$

(1.14)

FIGURE 1.13: Normalized bandwidth as a function of N for  $A_{tot} = 20dB$ .

Figure 1.14: Laser diode current steering.

The (1.14) maximum can be achieved at the denominator minimum, which is not a monotonic function, therefore an optimum in function of N can be found. As shown in the curve reported in Figure 1.13, suitable N values are 4 and 5.

Since the last stage is asked to drive the laser or the electro-optical modulator, several constraints relay on this block. Depending on the kind of modulation and on the electro-optical transducer involved, the signal specifications can be different. For m-QAM modulation at the far-end, to retrieve the original data, amplitude and phase are used, hence the distortion introduced by the transmitter can corrupt the transmitted information. A laser requires a current signal to work properly, while a Mach-Zehnder modulator is a voltage driven device. This means that the last stage design is strongly related to the

FIGURE 1.15: Cascade of a main driver, pre driver and a gain stage.

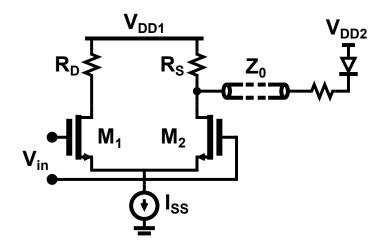

following optical systems. In Figure 1.14 a possible implementation of a laser driver is reported. Even though the laser diode requires a single ended (SE) signal, differential signals are preferred for many reasons. SE signals cannot be distinguished from common mode, so any corruption coming from the supply (noise, supply fluctuation...) directly affects the information carried. While differential structures allow to delete any common mode impairment as long as the symmetry between the two anti-phase signals holds. Since a laser diode is a SE device just one side is taken as output, while the other one is terminated over a resistance  $R_D$  to maintain the symmetry.

In the earlier transceiver the electrical and optical parts were realized in different packages, requiring impedance matching to avoid back reflection. From the laser side, the impedance showed is much lower than the characteristic impedance  $Z_0$ , therefore a series resistance is added. Since in Figure 1.14 the current steering is realized by an open-drain, a resistor  $R_S$  lowers the output impedance ensuring matching. This results in a two times larger current to be provided, because half of the signal is "wasted" on  $R_S$ . Silicon photonics overcome this issue, making available highly integrated photonic systems. Photonic and electronic functions are not realized on the same process, because they have requirements, sizes and costs very different (electronic requires advanced and fine CMOS processes which are not required for photonic components). Yet hybrid approaches have been implemented. The electronic integrated circuit responsible to drive the photonic modulators is a discrete component flip-chip mounted on the silicon photonic platform. Flip-chip integration ensure high-speed operations, and matching is no longer a requirement [12].

- (a) Loaded source follower.

- (b) Source follower output impedance.

FIGURE 1.16: Source follower output impedance analysis.

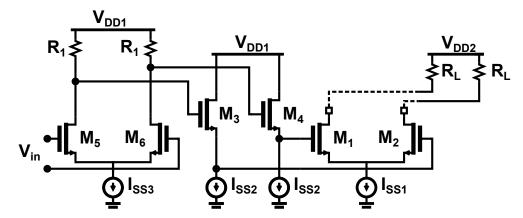

Figure 1.15 shows an example of driver chain. Since matching is no longer required the main driver is designed as an open drain, and  $R_L$  is the off-chip loading provided by the electro-optical modulator. The output stage design begins with the signal to be provided to the EOM. Assuming a load impedance  $R_L=50 \Omega$ , and a required differential output amplitude of 750 mV, results in a minimum tail current I<sub>SS1</sub> of 15 mA. The transistors M<sub>1</sub> and M<sub>2</sub> must be sized in order to steer the previous current. The smaller the MOS size ratio W/L the higher is the overdrive  $(V_{gs} - V_{th})$  required to drive the whole current. This allows to have less parasitic capacitances from M<sub>1</sub> and M<sub>2</sub>, while demanding a larger input swing, provided by increasing  $R_1$ . Since the  $R_1$  grows faster than the parasitics reduction, a pre-driver can be used to preserve the behaviour in frequency. Implementing this pre-driver as a source follower, as in Figure 1.15, allows to have a lower impedance driving M<sub>1</sub> and M<sub>2</sub>, hence an higher frequency pole. Nonetheless this solution has some drawbacks. In order to provide enough gain  $R_1$  should be large enough, ending in a voltage drop defined as  $R_1 \cdot I_{SS3}/2$ . Then  $V_{\rm gs,M3/4}$  and  $V_{\rm gs,M1/2}$  shifts down the DC voltage. So an higher  $V_{\rm DD1}$  can be required to leave some voltage headroom to I<sub>SS1</sub> to work properly. Besides the headroom consumption, also stability concern is introduced. The output impedance of the follower reported in Figure 1.16a can be described as

$$Z_{out} = \frac{1}{g_m} \frac{1 + sC_{gs}R_S}{1 + s\frac{C_{gs}}{a_m}}.$$

(1.15)

Comparing Figure 1.16a to Figure 1.15,  $R_S$  is meant to be higher than  $g_m$ . This leads to an inductive behaviour over frequency for the source follower output impedance, as shown in Figure 1.16b. Since the input of the main driver can be

FIGURE 1.17: Voltage swing improvements in a cascoded solution.

modelled as a big capacitance  $C_{in}$ , the resonance between this capacitance and the output impedance should happen out of band in order to avoid instability.

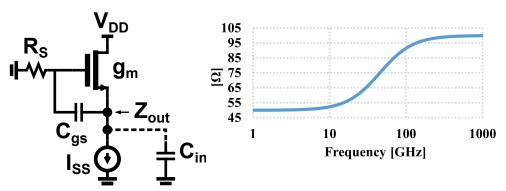

In long reach-applications, where the number of parallel optical links is a tight constraint, the bandwidth of the EOM becomes crucial. This is mainly defined by the parasitics introduced by the optical device, making the component size a bottle neck for speed. Hence smaller components lead to higher bit rates. Considering a MZM, the interferometer length affect both the bandwidth and the  $V_{\pi}$ , but in opposite direction. The shorter the MZM the higher is the voltage required to generate an electrical field capable to change the light phase. This can introduce some issues from the transistor reliability point of view. The latest CMOS technologies allow to have channel length up to tens of micrometers, enabling the chance to process millimeter wave signals. While the speed is increased, the junction break-down voltage is reduced. Technology knots that can reach hundreds of GHz of ft can support voltages up to 1 Volt (even less considering thin-oxide options). Figure 1.17 shows how cascoding can help to increase the swing efficiency avoiding junction failure. Especially in Figure 1.17b, the achievable peak-to-peak single ended voltage is wider than the drop over a single transistor. Thanks to  $M_{3/4}$  the theoretical maximum voltage achievable is  $V_{ds,I_{SS}} + V_{dsmax,M_1} + V_{dsmax,M_3}$ , while for the main driver in Figure 1.15 is  $V_{ds,I_{SS}} + V_{dsmax,M_1}$ . This newer upper voltage boundary can be used as a V<sub>DD</sub> value. The main driver power consumption is defined as

FIGURE 1.18: Main driver with no current source.

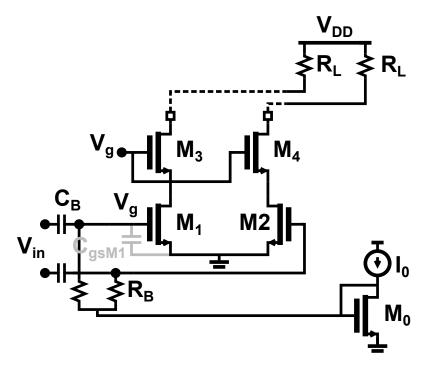

$V_{DD}I_{SS}$ , where  $I_{SS}$  is mainly defined by the required output voltage swing while  $V_{DD}$  by the number of stacked transistors (in order to have them all working in saturation). Then, with regard to the power consumed, cascoding is a weakness. As reported in Figure 1.18,  $I_{SS}$  can be removed and  $V_{ds,I_{SS}}$  can be spared. The current is defined by the size of  $M_1$  ( $M_2$ ) and the gate level at the first order. DC coupling the gate with the rest of the chain introduces a strong dependency of the current from process variations. AC coupling is therefore preferred, while the gate level is set through a diode connection, resulting in no effects over the current because of process. The proper design of  $R_B$  and  $C_B$  is not trivial, because the AC coupling introduce an attenuation and high-pass behaviour. Considering the parasitic  $C_{gs,M1}$ , the signal  $V_g$  is defined as

$$V_g = V_{in} \times \frac{C_B}{C_B + C_{qs.M1}},\tag{1.16}$$

hence choosing  $C_B = C_{gs,M1}$  results in a 6 dB attenuation from  $V_{in}$  to  $V_g$ . To avoid any attenuation,  $C_{gs,M1}$  should be negligible compared with  $C_B$ .  $C_{gs,M1}$  is proportional with M1 width, resulting in large amount of parasitic since it has to carry all the main driver current.  $C_B$  cannot be arbitrarily high

Figure 1.19: Schematic solution proposed by [13].

for two reasons, first, integration of large capacitor is not easy and can lead to manufacturing issues, second, the capacitor parasitics between the bottom plate and the substrate are proportional with the size. So these are the trade-off for  $C_B$ . Assuming a two-levels modulation (ONE or ZERO) non-return to zero (NRZ), the high-pass behaviour limits the number of consecutive ONEs. The time constant  $1/R_BC_B$  defines the maximum number of ONE periods in a row before the voltage crosses the threshold resulting in a wrong detection.

#### 1.4 State-of-the-art solutions

In this section a couple of already fabricated and published solutions are briefly described and discussed. The literature is quite poor about works which address the design of CMOS optical driver for coherent applications, but still it is useful to understand the main circuit solutions involved in the modulator driver field.

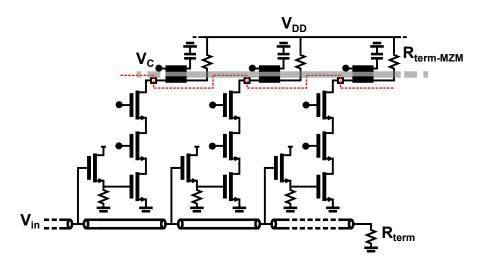

The need of very large transistors to be capable to steer all the current required to generate the output voltage swing introduces a no negligible bandwidth limitations. One available solution is to exploit the properties of a transmission line [4]. A lossless transmission line shows an infinite bandwidth and a constant delay, so a linear behaviour in phase. The characteristic impedance  $Z_0$  and the propagation velocity are respectively defined as

$$Z_0 = \sqrt{\frac{L_0}{C_0}} \tag{1.17}$$

$$v = \frac{1}{\sqrt{L_0 C_0}} \tag{1.18}$$

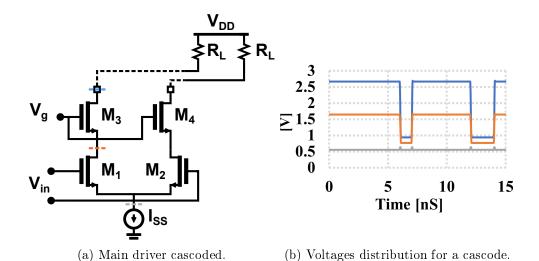

where L<sub>0</sub> and C<sub>0</sub> are the inductance and capacitance per unit length. A large transistor can then be sliced m times in m times smaller transistors and it can be distributed along the transmission line. In this way the parasitic input capacitance of each slice is reduced by a factor of m and can be considered together with the C<sub>0</sub>, which in turns can be redesigned to get back the desired line characteristic input impedance. The same holds for the output side of the transistor. So ideally a distributed amplifier shows infinite bandwidth and input and output low impedance, which are useful features for a MZM driver. The main limitation of a real transmission line comes from the metal resistivity which introduces losses (and so bandwidth limitation) and the finite range of characteristic impedance achievable (defined by the metal stack made available by the technology). An example of this technique is reported in [13]. In this case a distributed MZM driver has been fabricated in a 45-nm CMOS SOI technology, reaching an electrical bandwidth of 26 GHz. As shown in Figure 1.19 (a single ended version of the circuit is reported), instead of driving a MZM through a single large electrode, it has been broken in several smaller segments each one driven by single slice of the integrated distributed amplifier. The amplifier input transmission line should be designed to match the phase delay introduced by the MZM. In case of differences between the input and output phase delay, the transfer function will suffer from ripple. Each slice is realized by a source follower, which reduces the loading over the input line. A stack of three transistors provides a  $2.2 V_{pp}$  single-ended signal for the MZM. Stacking more than one transistors is required to avoid any breakdown given the high voltage involved. This solution is open collector, so the supply voltage comes from the resistive electro-optical modulator terminations. This work shows how co-design between electrical and optical components can be used to improve the system performance. Distributed solution can results in very broadband circuits, but it is very expensive in terms of area and power consumption. Transmission line requires a lot of space to be effective (the line should be electrically long compared with the wave-length of the signal). Furthermore, cascade of more stages (e.g. for gain control) could become an issue because of the low impedance provided by the driver input transmission line.

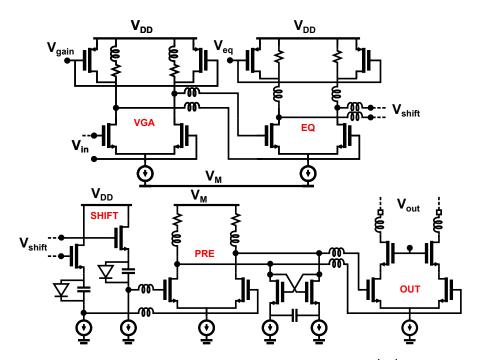

The MZM driver reported in [14] and shown in Figure 1.20, has been fabri-

Figure 1.20: Schematic solution proposed by [14].

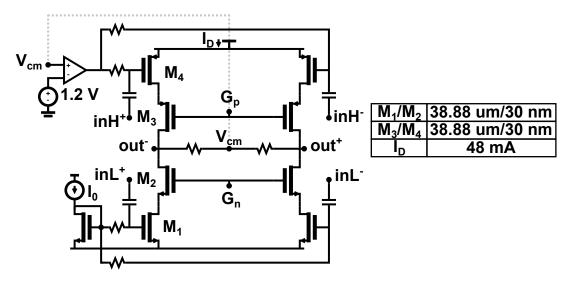

cated in a 65-nm CMOS technology, and it is intended for coherent applications. The differential output swing provided is  $2.9 \text{ V}_{pp}$  for a differential load ranging from 50 to 100  $\Omega$ , with an electrical bandwidth close to 35 GHz. The distortion measured at 2 V<sub>pp,diff</sub> is 5% at 1 GHz. The transmitter is realized as a four stages chain, involving a variable gain amplifier, an equalization stage, a pre-amplifier and an output stage implemented as an open-drain. To reduce power consumption current reuse has been implemented by stacking the first two stages with the pre amplifier. A level shifter has been used to accommodate the DC common mode between the equalizer and the pre amplifier. Gain control is implemented at the first stage by a gilbert-cell to reduce as much as possible the distortion along the chain. All the stages are implemented as differential pair with passive loads realized by resistors and inductors to extend the bandwidth. The equalizer allows to control the frequency behaviour tuning the amount of peaking by changing the resonance quality factor. The pre amplifier is usually a 0 dB gain block which feeds the main driver without loading to much the previous stages. A negative capacitance compensates part of the parasitics coming from the last differential pair. It is implemented by an explicit capacitance and closing in a positive loop two transistors. The output amplifier

#### 28 CHAPTER 1. INTRODUCTION OF OPTICAL COMMUNICATIONS

is open drain and cascoded, to allow large swing avoiding breakdown. In this publication, most of the known techniques to extend the bandwidth have been implemented. It is also interesting because a fully electrical characterization is provided, reaching a good eye opening for  $50~\mathrm{Gb/s}$  and an optical measure of a  $56~\mathrm{Gb/s}$  QPSK constellation. This can help to relate electrical and optical performance, in case of lack of system level measurements.

## Chapter 2

## A 58 GHz Bandwidth, Linear, Mach-Zehnder Driver

#### Abstract

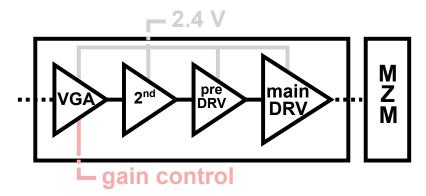

In the following pages the design and realization of a linear Mach-Zehnder modulator driver is presented. The aim of such a design is to prove that, even if the mainstream technologies for this application are Silicon-Germanium BiCMOS (SiGe-BiCMOS) and Indium Phosphide Double Hetero-junction Bipolar Transistor (InP-DHBT), CMOS is a viable solution. The main benefits on doing this would be the lower technology cost. Looking at the future, this can bridge the gap between digital-oriented highly scaled processes, such as fin field-effect transistor (FinFET), and purely analog functions. The chance to integrate all the functionalities on the same die would strongly reduce the system costs while enhancing the performance because of the interconnections removal between discrete components. The chapter describes specifications and how they have been satisfied, through schematics, simulations and testing. The driver is required to have a voltage swing of 1.5  $V_{pp,diff}$  over a 50  $\Omega$  impedance with a distortion below 1.8 %. The gain can be tuned from 20 to 10 dB (for the same output signal amplitude) with a better linearity for the lower values. The power consumed at maximum gain is 297 mW with a single supply voltage of 2.4 V.

## 2.1 Linearity and Distortion

#### 2.1.1 Harmonic distortion

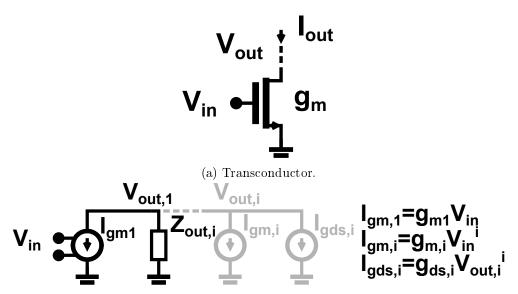

A small signal approach is often used for integrated circuit design. It is useful in order to estimate the frequency behaviour of schematic solutions and it is

(b) Transconductor model with non-linear contributors.

FIGURE 2.1: Simple non-linear model for a transconductor.

reliable when the involved amplitude is not so large. When the signal amplitude is no more negligible, modelling the transistor with an input transconductance and output conductance at the fundamental frequency is not enough. Figure 2.1b shows a possible way to model also non linear components coming from the transconductor in Figure 2.1a [15]. The output voltage is then defined

$$V_{out} = \sum_{i=0}^{n} V_{out,i}, \tag{2.1}$$

where the index *i* refers to the components placed at  $\omega_{\rm in}$ ,  $2\omega_{\rm in}$ , ...,  $n\omega_{\rm in}$ .  $\omega_{\rm in}$  is the input tone frequency.  $V_{{\rm out},1}$  is the desired element, defined as

$$V_{out,1} = V_{in} \cdot g_{m1} \cdot Z_{out,1} \tag{2.2}$$

$$= V_{in} \cdot A_V, \tag{2.3}$$

and A<sub>V</sub> is the linear gain. The spurious harmonics are defined as

$$V_{out,i} = I_{out,i} \cdot Z_{out,i} \tag{2.4}$$

$$= (I_{qm,i} + I_{qds,i}) \cdot Z_{out,i}. \tag{2.5}$$

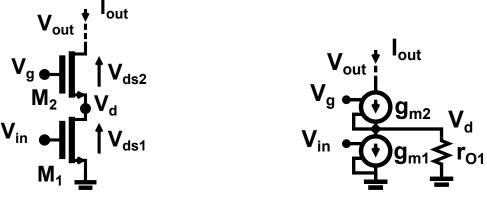

(a) Cascoded transconductor.

(b) Model of a cascoded transconductor.

FIGURE 2.2: Cascoded transconductor analysis.

From (2.5) Figure 2.1b, it is easy to notice the two distortion sources. An input component is described by  $g_{m,i}$ , and an output one by  $g_{ds,i}$ . Hence, knowing the frequency behaviour of the output impedance  $Z_{out}$ , a rough model of Figure 2.1a including non-linearity can be realized. Since  $g_{m,i}$  and  $g_{ds,i}$  are non-linear coefficients, the model is reliable for a bounded amplitude range. These coefficients can be derived from  $I_{out,i}$  as

$$\begin{cases}

g_{m,i} = \frac{I_{out,i}}{V_i^i} & \text{with } V_{out} = 0; \\

g_{ds,i} = \frac{I_{out,i}}{V_{out,1}^i} & \text{with } V_{in} = 0;

\end{cases}$$

(2.6)

Through the relation between  $V_{in}$  and  $V_{out,1}$  of (2.3), the coefficients of the (2.6) can be referred to the input or to the output in order to make a fair comparison.

$$\begin{cases} g_{m,i-out} = \frac{I_{out,i}}{V_{in,1}^{i}} \cdot A_{V}^{i} & \text{with } V_{out} = 0; \\ g_{ds,i} = \frac{I_{out,i}}{V_{out,1}^{i}} & \text{with } V_{in} = 0; \end{cases}$$

(2.7)

As an example in (2.7), both the coefficients are referred to the output. If the dynamic range to be covered becomes large, the coefficients  $g_{m,i}$  and  $g_{ds,i}$  turns to be amplitude dependent, so more complex modelling would be required. Still, Figure 2.1b is a good approximation to understand which is the main distortion source. For instance, if the main contributor results to be the input side, increasing the gain (so reducing the input amplitude for a given output swing) may help to increase the performance in term of linearity.

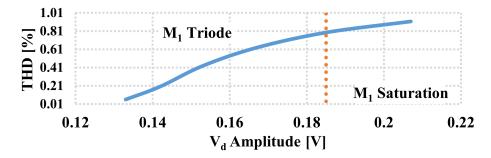

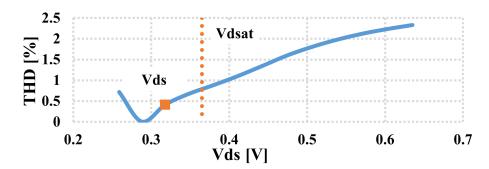

Figure 2.3: THD versus  $V_d$  amplitude.

Figure 2.4: THD versus  $V_{in}$  amplitude.

#### 2.1.2 Triode region

In the previous paragraph a tool to understand which is the main source of distortion is reported. As told, in order to reduce the input distortion the amplitude can be reduced by increasing the gain. This cannot work for the output component in case of fixed swing. The fabricated design is intended to propose a way to improve the transmitter behaviour at large signal regime. Figure 2.2 shows a cascoded transconductor (Figure 2.1a) and its model (Figure 2.1b).  $M_1$  and  $M_2$  have the same size, and the node  $V_g$  can be arbitrarily decided. The two transistors are interested by the same current  $I_{out}$  defined by  $V_{in}$ ,  $V_{ds1}$  and the transistor size. The gain from  $V_{in}$  to  $V_d$  can be written as

$$A_{V_{in},V_d} = \frac{g_{m1}}{g_{m2} + \frac{1}{r_{o1}}},\tag{2.8}$$

since  $M_1$  and  $M_2$  work in saturation,  $g_{m1}$  and  $g_{m2}$  are the same and  $1/r_{o1}$  is negligible, hence (2.8) becomes 1. This means that the amplitudes of  $V_{in}$  and  $V_{d}$  are the same. It is straightforward that, the larger the input amplitude the larger the voltage swing at  $V_{d}$ , which in turn increases the current modulation

FIGURE 2.5: Transmitter block diagram.

and so the distortion (Figure 2.1). Lowering the V<sub>g</sub> node, for a fixed I<sub>out</sub> current, lowers the V<sub>d</sub> voltage of the same amount. This allows to decide in which region M<sub>1</sub> works, triode or saturation. Towards the triode region g<sub>m1</sub> and  $r_{o1}$  are both reduced, while  $g_{m2}$  is almost kept constant. Back to the (2.8), it means that an attenuation is introduced from V<sub>in</sub> to V<sub>d</sub>, so the I<sub>out</sub> is less affected by the drain modulation. In Figure 2.3 the linearity behaviour of Figure 2.2a is reported as a function of the V<sub>d</sub> amplitude, maintaining the output swing  $V_{out}$  constant. The amplitude reduction is achieved pushing  $M_1$ in triode. The orange dotted line is the triode threshold, and it can be noticed how the linearity is improved working below this limit. Working in triode means a lower  $g_{m1}$  so an attenuation in term of gain. To have a constant output a larger input amplitude is then required. Figure 2.3 shows how the distortion is reduced, while the input amplitude is increased for the same output swing. This is interesting, because usually, larger signal amplitude means linearity impairments. This behaviour is exploited in the fabricated solution to perform gain variation without introducing linearity degradation.

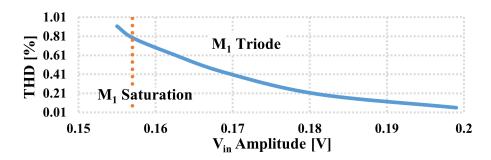

## 2.2 Transmitter Design

The transmitter proposed is made of four stages, where the first, the second and the last one are implemented exploiting the transistor triode region as described in the previous paragraph. The third one, a pre-driver, is a source follower which is responsible to feed the parasitic capacitances of the fourth big stage, without affecting the bandwidth. The transmitter has been designed to drive a Mach-Zehnder Modulator terminated over 50  $\Omega$ (a behavioural model has been provided by the company, but we are not allowed to share any graph or

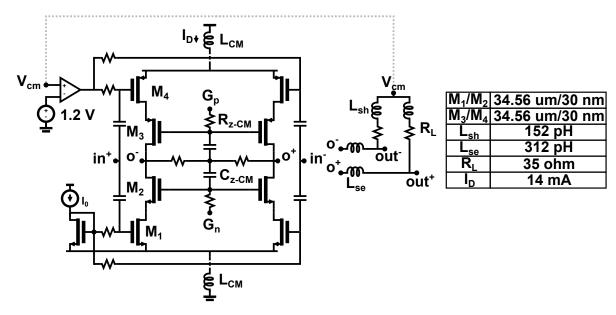

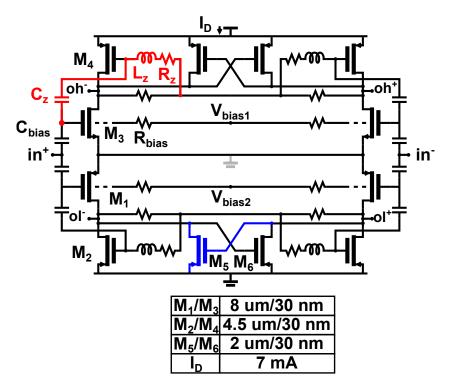

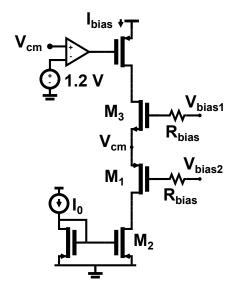

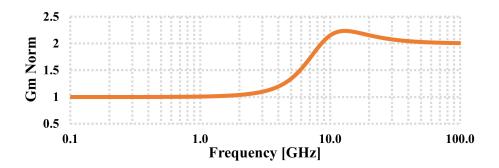

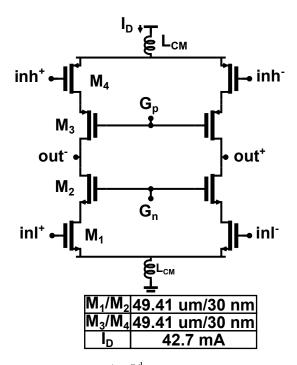

FIGURE 2.6: Variable gain amplifier schematic.

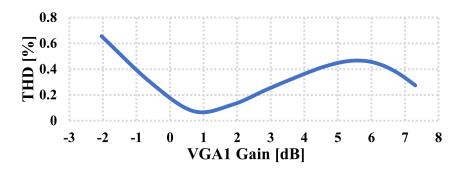

FIGURE 2.7: Variable gain amplifier THD versus gain.

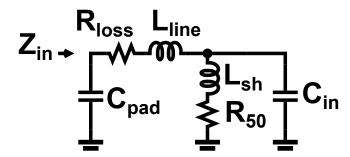

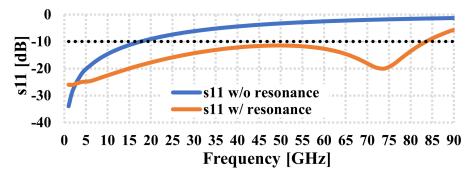

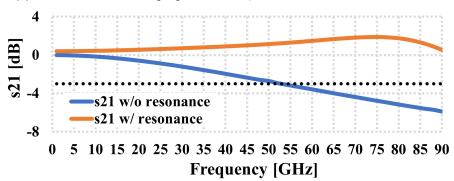

related information about it). At this stage, the gain is hand controlled taking DC signals off-chip and the whole variation is provided by the first amplifier. In next realizations, the gain control will be performed automatically through a feedback loop made by a photodiode and a peak detector. A single 2.4 V supply voltage has been used, provided by an external low drop-out (LDO) regulator. Since we are not yet able to integrate the digital part, the digital-to-analog converter and the analog transmitter, input matching is required to reduce the return loss (and also for testing purpose)

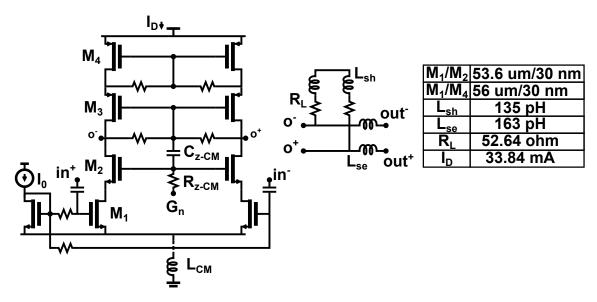

### 2.3 Variable Gain Amplifier

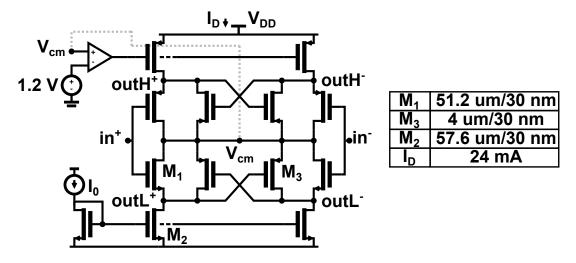

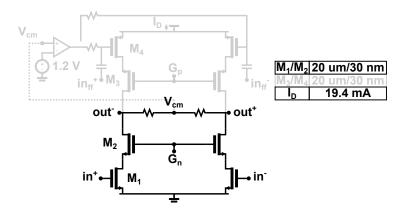

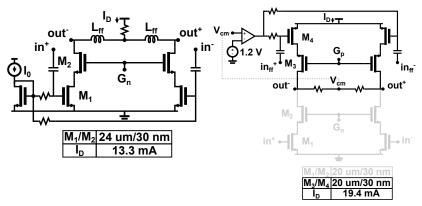

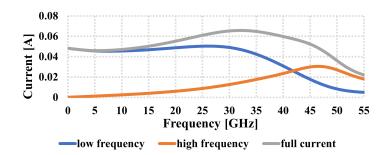

The first stage (Figure 2.6) provides the whole 10 dB gain variation. In this way the signal amplitude for the following stage is constant through all the gain configurations, so they can be optimized in term of linearity. In Figure 2.3 the proposed schematic is reported. An inverter-like solution is proposed, exploiting in this way both the p- and n- side  $g_m$  saving current. To spare voltage headroom the biasing current is defined by  $M_1$  so the common mode current mirror is removed. AC coupling helps to fit all the four transistor stacking without reaching the break-down voltage.

#### 2.3.1 Gain programmability

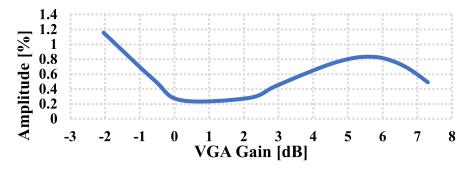

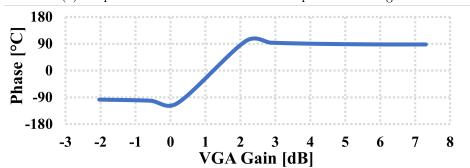

Terminal  $G_p$  and  $G_n$  are taken off-chip and used as knob for the gain variability. Gain variation is performed by pushing  $M_1$  and  $M_4$  from linear to triode region, as explained in the previous paragraph. As shown in Figure 2.7 the VGA has better linearity performance at lower gain, and this holds for the positive range. Below 0 dB, when the VGA is attenuating the signal, the distortion get worse. The main distortion contributor is the third harmonic, and in Figure 2.8 it is reported how it changes with the gain. In Figure 2.8a, the third harmonic amplitude drops with the gain in the positive range, while it increases when an attenuation is introduced. From gain to attenuation, the phase of this component experiences 180° shift, as in Figure 2.8b. Since all the following stages introduce gain, the third components injected are in anti-phase with this first one, so a cancellation happens through the overall transmitter. Hence, while attenuating, a pre-distortion mechanism is provided by the VGA.

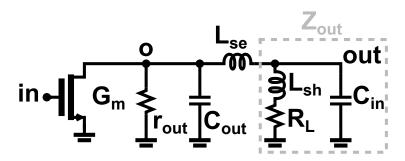

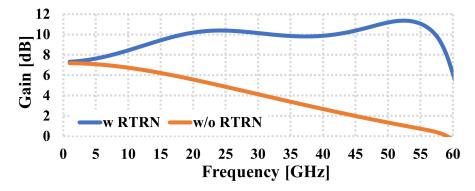

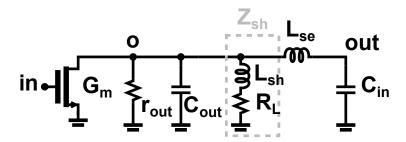

#### 2.3.2 Reverse triple resonant network

A differential resistor  $R_L$  is used to achieve the desired gain by this stage. Bandwidth limitations are mostly defined by parasitic capacitances coming from the stage itself and from the following stage. A simple small signal model of Figure 2.6 is reported in Figure 2.9, which helps to understand the frequency behavior.  $C_{out}$  and  $r_{out}$  are respectively the capacitive and resistive loading coming from the VGA itself while  $C_{in}$  comes from the next stage. Without considering the explicit inductors the -3 dB frequency would be

$$\omega_{-3dB} = \frac{1}{(C_{in} + C_{out})(R_L||r_{out})}.$$

(2.9)

The purpose of the series  $(L_{se})$  and shunt  $(L_{sh})$  inductors is to create resonances together with the parasitic capacitances to compensate the gain drop over

(a) Amplitude of the third harmonic component versus gain.

(b) Phase of the third harmonic component versus gain.

FIGURE 2.8: VGA third harmonic component versus gain.

FIGURE 2.9: Small signal model for Figure 2.6.

frequency, increasing the -3 dB crossing. This circuit is called Reverse Triple Resonant Network (RTRN) because three resonances can be found [16]. During circuit design, the modelling of Figure 2.9 is still rough. Assuming the parasitics as grounded capacitors is not sufficient to proper fit the Figure 2.6 behaviour,

FIGURE 2.10: VGA gain with and without the reverse triple resonant network.

because the whole chain affects these impedance values. However, simulation tools are available and reliable for a fine design, which means that Figure 2.9 is enough to get an idea whether the network would be of help or not. (2.9) defines the starting bandwidth, while the DC gain is  $g_m(r_{out}||R_L)$ . The first resonance is given by the parallel of L<sub>sh</sub>, C<sub>in</sub> and C<sub>out</sub> at  $\omega_1 \cong 1/\sqrt{L_{sh}(C_{in} + C_{out})}$ , hence the node "o" can be considered an high impedance. The gain at  $\omega_1$  can then be written as

$$A_{V,RTRN}(\omega_1) \cong G_m \cdot r_{out} \cdot \frac{Z_{out}(\omega_1)}{Z_{out}(\omega_1) + j\omega_1 L_{se}},$$

(2.10)

where  $Z_{out}(\omega_1) = C_{in}||(R_L + j\omega_1 L_{sh})$ . A series resonance happen at  $\omega_2 \cong \sqrt{L_{se}C_{in}}$ , where most of the  $G_m$  current flow into  $C_{in}$  giving approximately

$$A_{V,RTRN}(\omega_2) \cong G_m \cdot \frac{1}{j\omega_2 C_{in}}.$$

(2.11)

The last resonance is again a series resonance between  $L_{se}$ ,  $C_{in}$  and  $C_{out}$  at  $\omega_3 \cong 1/\sqrt{L_{se} \frac{C_{in}C_{out}}{C_{in}+C_{out}}}$ , giving

$$A_{V,RTRN}(\omega_3) \cong G_m \cdot r_{out} \cdot \frac{Z_{out}(\omega_3)}{Z_{out}(\omega_3) + j\omega_3 L_{se}}.$$

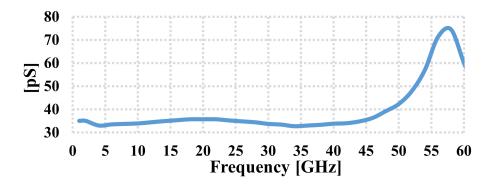

(2.12)