| High-Speed Equalization and Transmission in Electrical Interconnections |

|-------------------------------------------------------------------------|

| Hogesnelheidsegalisatie en -transmissie in elektrische interconnecties  |

| Yu Ban                                                                  |

|                                                                         |

Promotoren: prof. dr. ir. J. Bauwelinck, dr. ir. G. Torfs Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Informatietechnologie Voorzitter: prof. dr. ir. D. De Zutter Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2015 - 2016

ISBN 978-90-8578-840-9 NUR 959

Wettelijk depot: D/2015/10.500/84

#### Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur Vakgroep Informatietechnologie

Promotor: Prof. Dr. Ir. Johan Bauwelinck

Dr. Ir. Guy Torfs

Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur

Vakgroep Informatietechnologie Sint-Pietersnieuwstraat 41, B-9000 Gent, België

Tel.: +32-9-264.33.40 Fax.: +32-9-264.35.93

Proefschrift tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek Academiejaar 2015-2016

#### Dankwoord

How time flies! Now I can still clearly remember the first day when I stepped into the door of the INTEC\_design Laboratory. After 4.5 years of study and research as a PhD student in this pleasant atmosphere, the writing of this dissertation symbolizes the end of my 24 years student life. Truly, the road to persue a PhD degree is not always easy or flat, but full of challenges. Luckily I am not alone, as there are so many people around me, providing me with their guidance, assistance, encouragement and companionship. Without these, this PhD would not have been accomplished. So here I would like to thank you all, for helping me finally reach this stage. First of all, I would like to thank Prof. Jan Vandewege and Prof. Xing-Zhi Qiu, who provided me an opportunity to study at INTEC\_design, and they gave me a powerful motivation in my academic research and daily life.

I would like to express my sincerest gratitude to my promoter, Prof. Johan Bauwelinck for his patience and supervision throughout my doctoral studies. His experience and enthusiasm led me to the correct direction, and he always encouraged me whenever I met challenges. The PhD life has been a wonderful experience to me, and I believe sincerely Johan is an excellent supervisor and a gentleman. I also give my deepest appreciation to my co-promoter dr. Guy Torfs for his continuous guidance and advices on my research work and publications. The discussions with him were always beneficial and his immense experience in chip design and layout helped me a lot throughout this research.

I am also grateful to the other senior staff members in this group: Prof. Xin Yin for his numerous technical discussions and valuable suggestions. Now I can still remember his help on my first tape-out; Special thanks to Jan Gillis for his technical assistance during the tape-out and PCB fabrication. Whenever I needed some help for a software or license problem, he was always the first one I looked for. I would like to thank Mike Van Puyenbroeck, for his constant help throughout my PhD.

I extend my acknowledgment to my fellow labmates in the Design Lab, it was a great pleasure to work with all of you. I would especially thank Timothy De Keulenaer as we worked closely together during the past 4 years, and it was really an exciting moment when we got the 84Gbit/s transmission working. I would like to thank my colleagues: Guus Colman, Jasmien Put, Punithavathi Duraiswamy, Zhisheng Li, Christophe Van Praet, Jochen Verbrugghe, Xiao Li, Renato Vaernewyck, Ramses Pierco, Arno Vyncke, Bart Moeneclaey, Koen Verheyen, Wouter Soenen, Michael Vanhoecke, Marijn Verbeke, Jochem Verbist, Gertjan Coudyzer, Haolin Li and Joris Van Kerrebrouck. You all helped me and contributed to create an active and pleasant working environment.

During my PhD, I also received a lot of help from outside of this group. This research was mostly performed together with Alcatel-Lucent Bell Labs and FCI Electronics. I would like to thank all the project colleagues. Special thanks to Bartek Kozicki, Koen Hooghe, Geert De Peuter, Jeffrey Sinsky from Bell Labs and Jan De Geest, Stefaan Sercu from FCI, for their valuable discussions during the collaboration and their helpful comments on the research and publications. Besides, I would like to acknowledge the IWT, Alcatel-Lucent Bell Labs, the China Scholarship Council (CSC) and the Special Research Fund (BOF) of Ghent University, for the financial support during my PhD research.

Furthermore, I would like to thank all my friends I met in Ghent during my PhD life. Especially, I owe my sincerest appreciation to Ms. Guangling Cui. It was a coincidence for us to meet each other the first-time in Ghent, and later on this coincidence turned into a period of fantastic time and a part of unforgettable memory all my life.

Finally, I would like to express my deepest gratitude to my parents for their continuous support and encouragement. Although they live in Beijing, eight thousand kilometers away, but in my heart they are together with me all the time.

Ghent, May 2015

Yu Ban

## Table of Contents

| Da | ankw           | oord     |                                                 | i    |

|----|----------------|----------|-------------------------------------------------|------|

| No | ederla         | ındstali | ge samenvatting                                 | xxi  |

| Eı | nglish         | summa    | ary                                             | xxv  |

| Li | st of <b>j</b> | publicat | tions                                           | xxix |

| 1  | Intr           | oductio  | on                                              | 1    |

|    | 1.1            | Backg    | round                                           | 2    |

|    |                | 1.1.1    | Network architecture and access nodes           | 2    |

|    |                | 1.1.2    | Technical challenges                            | 4    |

|    | 1.2            | Overv    | iew of this work                                | 5    |

|    | 1.3            | Organ    | ization of this dissertation                    | 6    |

| 2  | Bac            | kplane : | systems and modulation schemes                  | 11   |

|    | 2.1            | Introd   | uction                                          | 11   |

|    | 2.2            | Backp    | plane channel and design challenges             | 12   |

|    |                | 2.2.1    | Backplane channel                               | 12   |

|    |                | 2.2.2    | Bandwidth limitation                            | 13   |

|    |                | 2.2.3    | Backplane implementation                        | 16   |

|    |                |          | 2.2.3.1 Transmission line traces                | 17   |

|    |                |          | 2.2.3.2 Backplane connectors                    | 18   |

|    |                | 2.2.4    | Prototype backplane                             | 20   |

|    | 2.3            | Transr   | mitter design challenges                        | 21   |

|    |                | 2.3.1    | Overview                                        | 21   |

|    |                | 2.3.2    | Equalizer functions                             | 22   |

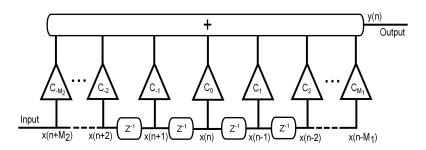

|    |                |          | 2.3.2.1 Feed-forward Equalizer (FFE)            | 22   |

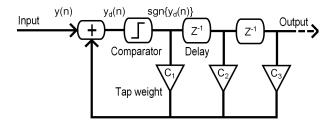

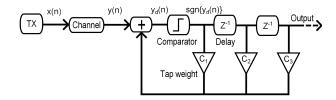

|    |                |          | 2.3.2.2 Decision-feedback Equalizer (DFE)       | 24   |

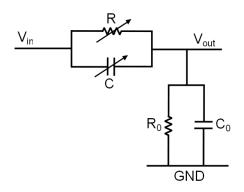

|    |                |          | 2.3.2.3 Continuous time linear equalizer (CTLE) | 27   |

|    |                |          | 2.3.2.4 Conclusion                              | 30   |

|   |      | 2.3.3    | Transmitter topology                              | 31 |

|---|------|----------|---------------------------------------------------|----|

|   | 2.4  | Modul    | lation                                            | 31 |

|   |      | 2.4.1    | Modulation techniques                             | 32 |

|   |      |          | 2.4.1.1 NRZ                                       | 32 |

|   |      |          | 2.4.1.2 PAM-4                                     | 33 |

|   |      |          |                                                   | 36 |

|   |      |          | 2.4.1.4 Polybinary                                | 88 |

|   |      | 2.4.2    |                                                   | 10 |

|   |      |          | 2.4.2.1 NRZ                                       | 10 |

|   |      |          | 2.4.2.2 Duobinary                                 | 10 |

|   |      |          |                                                   | 1  |

|   |      | 2.4.3    | Conclusion                                        | 12 |

|   | 2.5  | Techno   | ology selection                                   | 13 |

|   |      | 2.5.1    |                                                   | 13 |

|   |      | 2.5.2    |                                                   | 14 |

|   | 2.6  | Summ     | nary                                              | 16 |

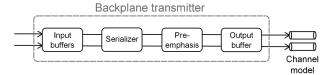

| 3 | Bacl | kplane 1 | transmitter 5                                     | 55 |

|   | 3.1  | Transn   | mitter architecture                               | 55 |

|   | 3.2  | Multip   | blexer                                            | 6  |

|   |      | 3.2.1    |                                                   | 56 |

|   |      | 3.2.2    |                                                   | 6  |

|   |      | 3.2.3    |                                                   | 57 |

|   |      | 3.2.4    | Simulation results                                | 59 |

|   | 3.3  | Feed-f   | Forward equalizer                                 | 59 |

|   |      | 3.3.1    |                                                   | 59 |

|   |      | 3.3.2    | FFE Topology                                      | 51 |

|   |      |          |                                                   | 51 |

|   |      |          | 3.3.2.2 Proposed FFE topology for improved testa- |    |

|   |      |          | 1 1 2 1                                           | 52 |

|   |      | 3.3.3    | Circuit design                                    | 54 |

|   |      |          |                                                   | 64 |

|   |      |          | ·                                                 | 59 |

|   |      |          |                                                   | 31 |

|   |      | 3.3.4    | 1 1                                               | 35 |

|   |      | 3.3.5    |                                                   | 36 |

|   |      |          |                                                   | 37 |

|   |      |          | E                                                 | 88 |

|   |      | 3.3.6    |                                                   | 90 |

|   |      |          |                                                   |    |

|   |     | 3.3.7   | Conclusi           | on                                          | 91  |

|---|-----|---------|--------------------|---------------------------------------------|-----|

|   | 3.4 | Transr  | nitter over        | view                                        | 92  |

|   |     | 3.4.1   | Top-leve           | l design                                    | 92  |

|   |     | 3.4.2   |                    |                                             | 92  |

| 4 | Evn | erimen  | tal evaluat        | tions                                       | 97  |

| • | 4.1 |         |                    |                                             | 97  |

|   | 4.2 |         |                    | struments                                   | 97  |

|   | 4.3 | Transr  |                    |                                             | 98  |

|   | т.Э | 4.3.1   |                    | easurements                                 | 99  |

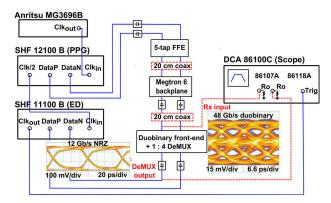

|   |     | 7.5.1   | 4.3.1.1            | Experimental setup                          | 99  |

|   |     |         | 4.3.1.2            | Results                                     | 100 |

|   |     |         | 4.3.1.3            | Conclusion                                  | 100 |

|   |     | 4.3.2   |                    | surements                                   | 101 |

|   |     | 4.3.2   |                    |                                             | 103 |

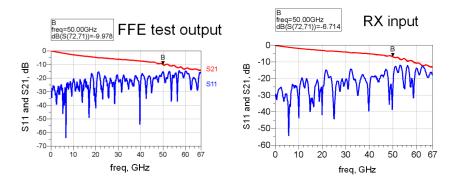

|   |     |         | 4.3.2.1<br>4.3.2.2 | Frequency domain                            | 103 |

|   |     | 4.3.3   |                    | Time domain                                 | 110 |

|   |     | 4.3.3   |                    | ter measurements                            |     |

|   |     |         | 4.3.3.1            | Experimental setup                          | 111 |

|   |     |         | 4.3.3.2            | Results                                     | 112 |

|   |     | <b></b> | 4.3.3.3            | Conclusion on the FFE measurements .        | 119 |

|   | 4.4 |         |                    | ceiver data links over PCB traces           | 120 |

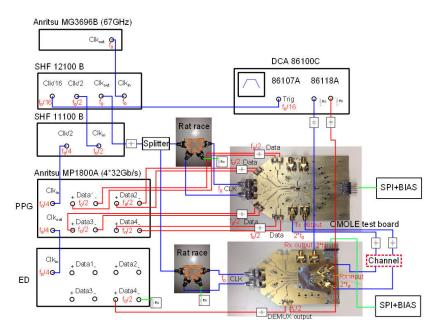

|   |     | 4.4.1   |                    | ental setup                                 | 120 |

|   |     | 4.4.2   |                    |                                             | 121 |

|   |     | 4.4.3   |                    | on                                          | 123 |

|   | 4.5 |         |                    | ceiver data links over commercial backplane |     |

|   |     | 4.5.1   |                    | tion                                        | 125 |

|   |     | 4.5.2   |                    | ADA Whisper backplane demonstrator          | 125 |

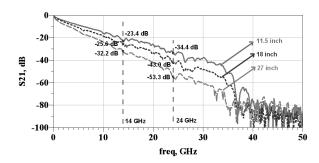

|   |     |         | 4.5.2.1            | Backplane channels                          | 125 |

|   |     |         | 4.5.2.2            | Experimental setup                          | 126 |

|   |     |         | 4.5.2.3            | Results                                     | 128 |

|   |     |         | 4.5.2.4            | Conclusion                                  | 129 |

|   |     | 4.5.3   | FCI Exal           | MAX® backplane demonstrator                 | 130 |

|   |     |         | 4.5.3.1            | Backplane channels                          | 130 |

|   |     |         | 4.5.3.2            | Experimental setup                          | 131 |

|   |     |         | 4.5.3.3            | Results                                     | 132 |

|   |     |         | 4.5.3.4            | Conclusion                                  | 135 |

|   | 4.6 | Conclu  | usion              |                                             | 135 |

| 5 | Conclusion |                      |  |     |  |  |

|---|------------|----------------------|--|-----|--|--|

|   | 5.1        | Summary of this work |  | 139 |  |  |

|   | 5.2        | Future work          |  | 141 |  |  |

## List of Figures

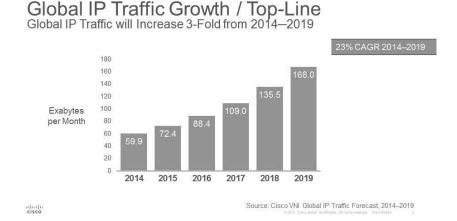

| 1.1  | Global IP traffic growth                                    | 2  |

|------|-------------------------------------------------------------|----|

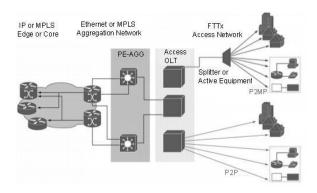

| 1.2  | Network architecture overview                               | 3  |

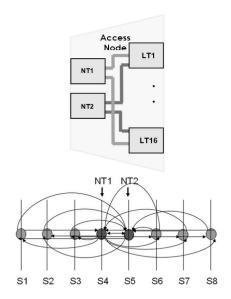

| 1.3  | Access nodes with star architecture                         | 3  |

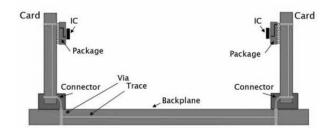

| 2.1  | A typical backplane system [7]                              | 13 |

| 2.2  | FCI ExaMAX® backplane connector [8]                         | 13 |

| 2.3  | FCI ExaMAX® backplane                                       | 14 |

| 2.4  | Measured loss of a FCI ExaMAX® backplane                    | 14 |

| 2.5  | Impulse response of a FCI ExaMAX® backplane                 | 15 |

| 2.6  | 80 Gb/s NRZ signal transmission over different sections of  |    |

|      | a commercial ExaMAX® backplane without equalization         | 15 |

| 2.7  | Measured loss of FX-2 PCB striplines                        | 18 |

| 2.8  | Measurement setup of the FCI backplane connector            | 19 |

| 2.9  | Frequency response of the FCI prototype backplane connector | 20 |

| 2.10 | FCI prototype backplane                                     | 20 |

| 2.11 | Frequency response of the FCI prototype backplane           | 21 |

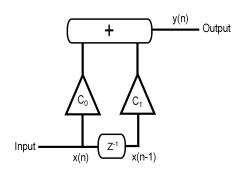

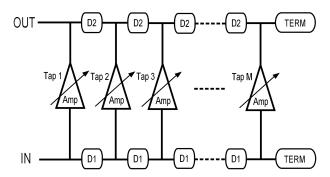

| 2.12 | Conventional 2-Tap FFE topology                             | 23 |

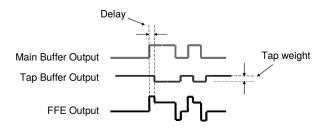

|      | Output waveforms of a 2-Tap FFE [26]                        | 23 |

|      | M-Tap FFE topology                                          | 23 |

|      | A digital signal degraded by ISI causing bit errors         | 25 |

|      | Basic DFE function to eliminate errors                      | 25 |

| 2.17 | M-Tap DFE topology                                          | 26 |

|      | An electrical link employing an M-tap DFE                   | 26 |

| 2.19 | A typical passive CTLE topology                             | 28 |

|      | A typical active CTLE employing amplifiers                  | 28 |

| 2.21 | Transmitter topology                                        | 31 |

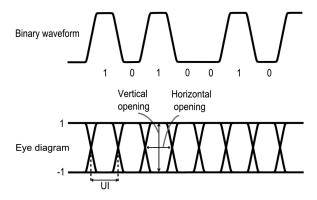

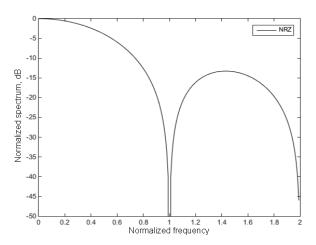

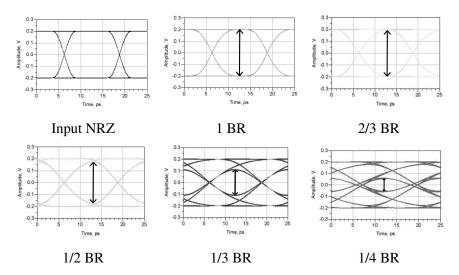

|      | NRZ waveform and eye diagrams                               | 33 |

| 2.23 | Spectrum of NRZ signals                                     | 34 |

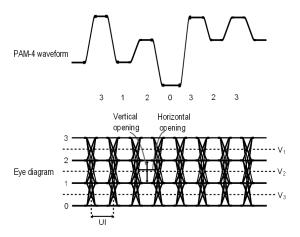

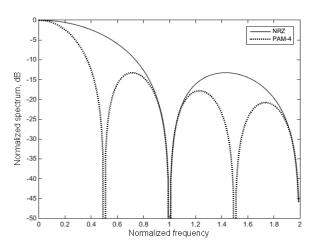

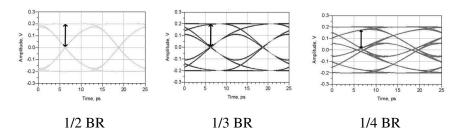

| 2.24 | PAM-4 waveform and eye diagrams                             | 34 |

|      | Spectrum of PAM-4 signals                                   | 35 |

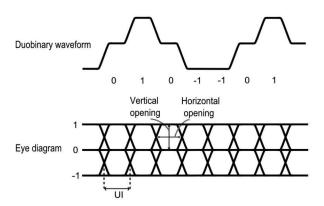

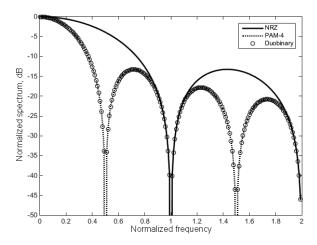

| 2.26 | Duobinary waveform and eye diagrams                         | 36 |

| 2.27 | Spectrum of duobinary signals                                   | 37 |

|------|-----------------------------------------------------------------|----|

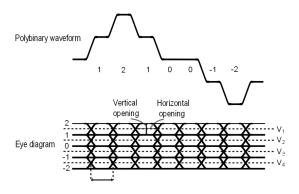

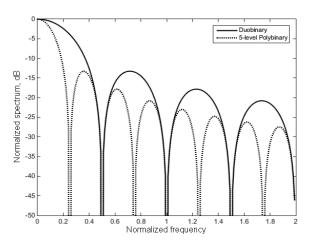

|      | Five-level polybinary waveform and eye diagrams                 | 38 |

|      | Spectrum of five-level polybinary signals                       | 39 |

|      | Transient simulation of 80 Gb/s NRZ signal transmission         |    |

|      | with different Bessel BW channels                               | 41 |

| 2.31 | Transient simulation of 80 Gb/s NRZ signals, illustrating       |    |

|      | the duobinary eye opening with different Bessel BW chan-        |    |

|      | nels                                                            | 41 |

| 2.32 |                                                                 |    |

|      | sion with different Bessel BW channels                          | 42 |

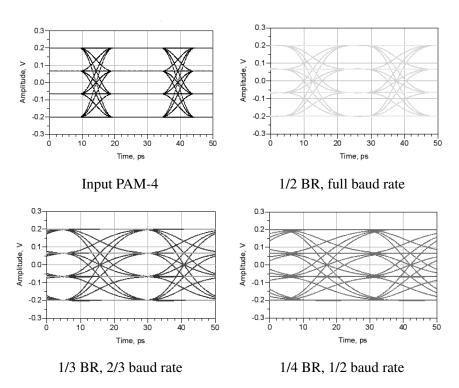

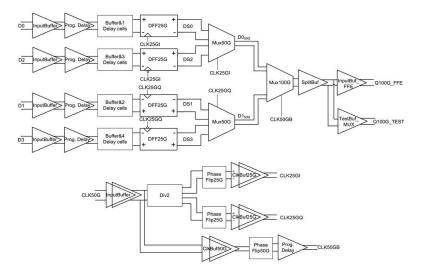

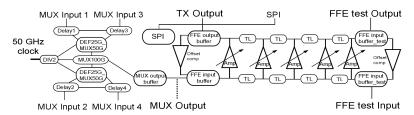

| 3.1  | Transmitter architecture                                        | 55 |

| 3.2  | Topology of the MUX                                             | 56 |

| 3.3  | Schematic of the data input buffer                              | 57 |

| 3.4  | Schematic of the clock input buffer                             | 58 |

| 3.5  | Schematic of the output buffer                                  | 58 |

| 3.6  | Schematic of the test output buffer                             | 58 |

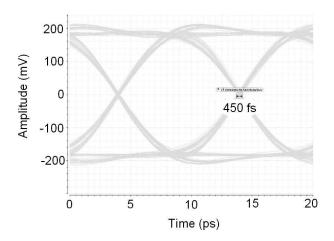

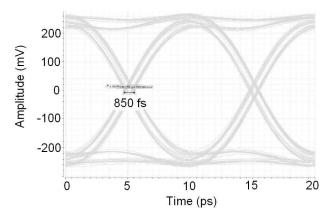

| 3.7  | Simulated eye diagram of the test output                        | 60 |

| 3.8  | Simulated eye diagram of the FFE input                          | 60 |

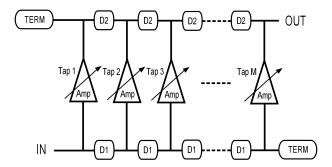

| 3.9  | Conventional FFE topology (1)                                   | 61 |

| 3.10 | Conventional FFE topology (2)                                   | 62 |

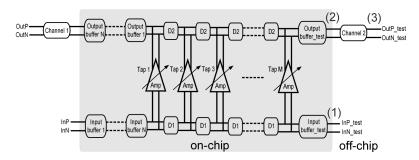

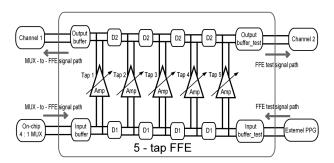

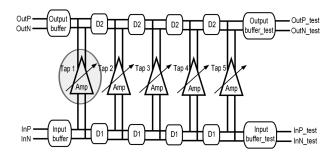

| 3.11 | Proposed FFE topology with additional test ports                | 63 |

| 3.12 | Fully integrated FFE structure                                  | 64 |

| 3.13 | Return loss (dashed), insertion loss (dotted) and phase shift   |    |

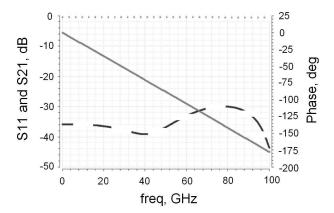

|      | (solid) of one TML section                                      | 66 |

| 3.14 | TML matching of input (dashed) and output (50 $\Omega$ : solid, |    |

|      | 35 $\Omega$ : dashdotted)                                       | 66 |

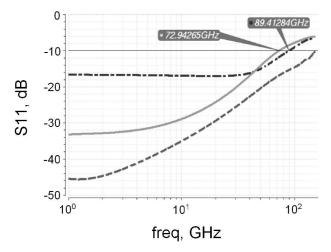

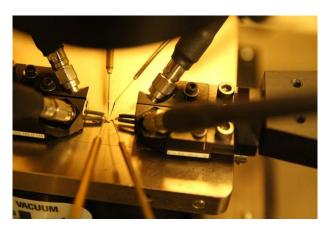

| 3.15 | Probing setup of on-chip TML test structures                    | 68 |

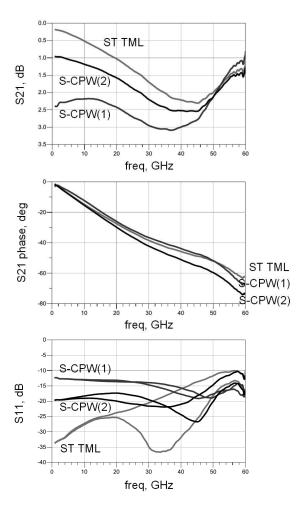

|      | Layout of the measured TML structures                           | 69 |

| 3.17 | Overview of the on chip TMLs, in red the ST TML, in blue        |    |

|      | and black two different types of slow-wave TMLs                 | 70 |

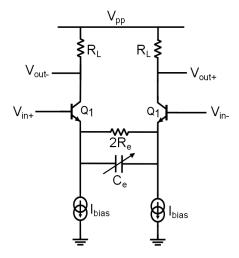

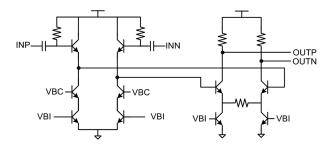

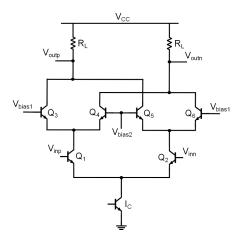

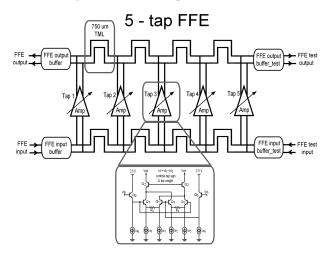

| 3.18 | 5-tap FFE building blocks                                       | 71 |

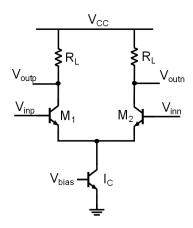

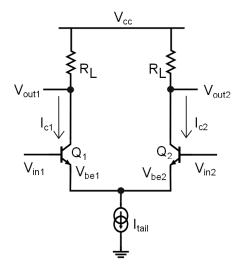

| 3.19 | Basic VGA configuration with a differential pair                | 71 |

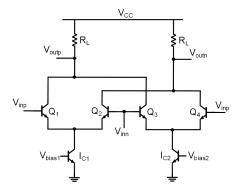

| 3.20 | Typical VGA configuration with two differential pairs           | 72 |

| 3.21 | Typical VGA configuration with gilbert cell (1)                 | 73 |

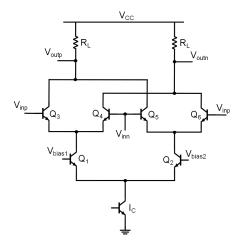

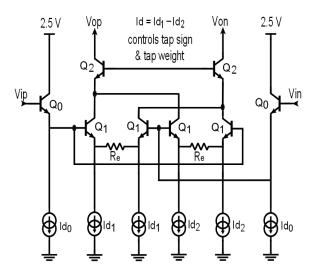

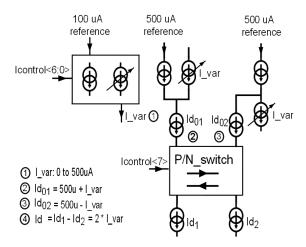

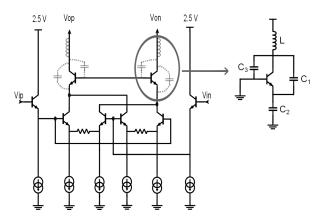

| 3.22 | Typical VGA configuration with gilbert cell (2)                 | 74 |

| 3.23 | Variable gain stage, controlled by the tail current difference  |    |

|      | $I_d = I_{d1} - I_{d2}  \dots  \dots  \dots  \dots  \dots$      | 75 |

|      | Current DAC                                                     | 76 |

| 3.25 | Parasitics causing resonances in the FFE                        | 78 |

| 3.26 | Gain cell layout                                                          | 79  |

|------|---------------------------------------------------------------------------|-----|

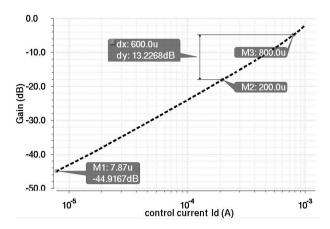

| 3.27 | Tunable gain as function of control current $I_d$                         | 79  |

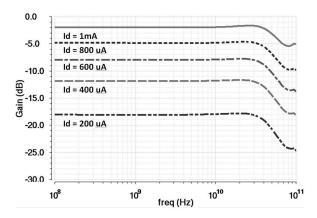

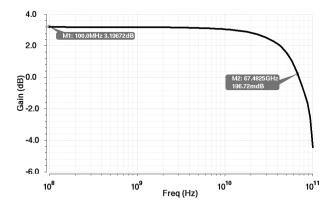

| 3.28 | Frequency response for different control current settings .               | 80  |

|      | 100 Gb/s output eye diagram for (a) $I_d = 200 \mu\text{A}$ and (b) $I_d$ |     |

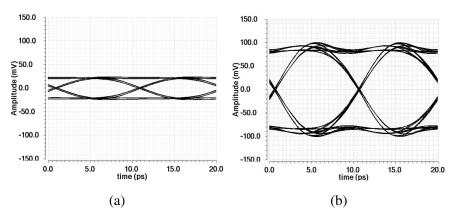

|      | = 800 μA, yielding a 12 dB gain difference                                | 80  |

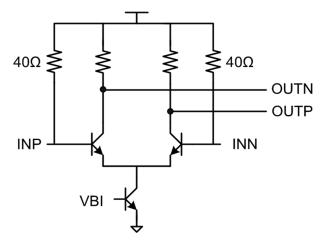

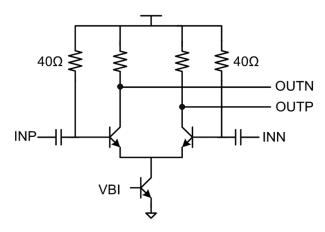

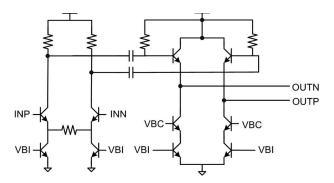

| 3.30 | Emitter-coupled differential pair                                         | 82  |

|      | FFE buffer schematic                                                      | 84  |

|      | Frequency response of the output buffer                                   | 85  |

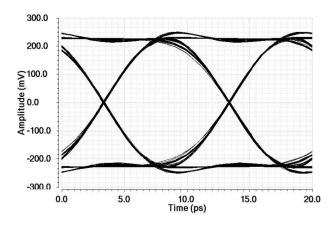

|      | Eye diagram of the output buffer                                          | 85  |

|      | 5-tap FFE block diagram                                                   | 86  |

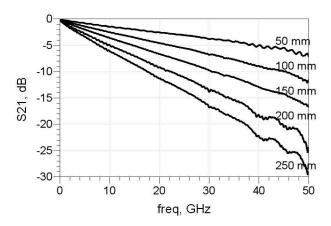

|      | FX-2 stripline channel characteristics                                    | 87  |

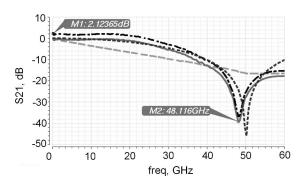

|      | Frequency response: measured loss of 150 mm TML (dashed).                 | ,   |

|      | FFE shaped (dashdotted), normalized channel (solid), ideal                |     |

|      | 100 Gb/s duobinary (dotted)                                               | 88  |

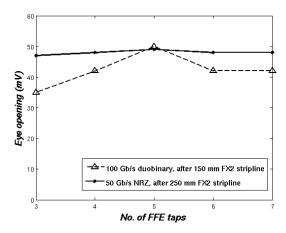

| 3.37 | Number of FFE taps comparison                                             | 89  |

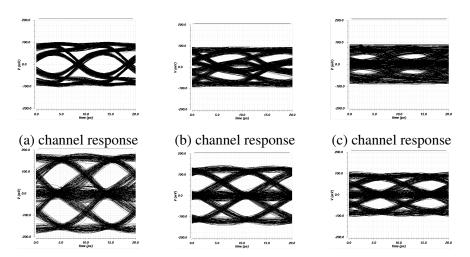

| 3.38 |                                                                           |     |

|      | 5-tap FFE on measured traces for (a) 50 mm, (b) 100 mm                    |     |

|      | and (c) 150 mm. The simulation without FFE simply shows                   |     |

|      | the channel response                                                      | 90  |

| 3.39 |                                                                           | 91  |

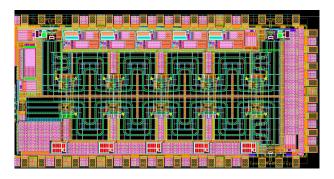

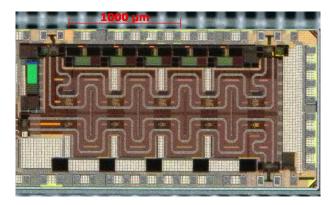

| 3.40 | Die micrograph of the FFE                                                 | 91  |

|      | Transmitter building blocks                                               | 92  |

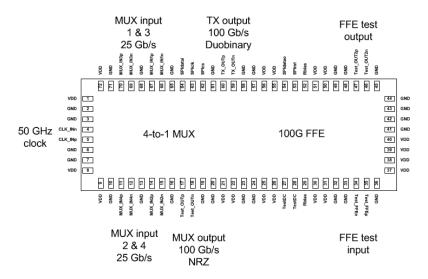

| 3.42 | Pinout of the transmitter chip                                            | 93  |

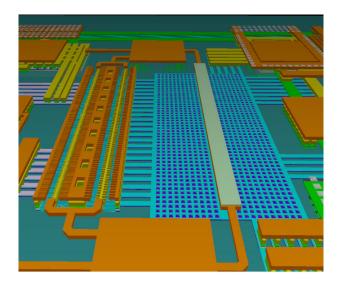

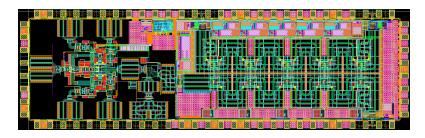

|      | Layout view of the backplane transmitter                                  | 94  |

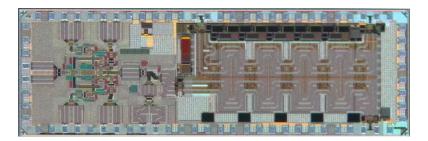

|      | Die micrograph of the transmitter chip                                    | 94  |

|      |                                                                           |     |

| 4.1  | MUX measurement setup                                                     | 100 |

| 4.2  | 64 Gb/s output eye diagram of the 4:1 MUX                                 | 101 |

| 4.3  | 72 Gb/s output eye diagram of the 4:1 MUX                                 | 101 |

| 4.4  | 84 Gb/s output eye diagram of the 4:1 MUX                                 | 102 |

| 4.5  | 100 Gb/s output eye diagram of the 4:1 MUX                                | 102 |

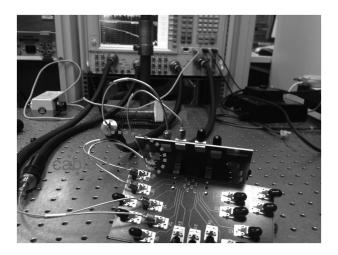

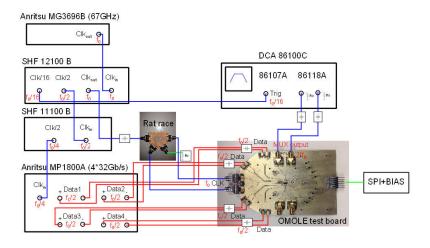

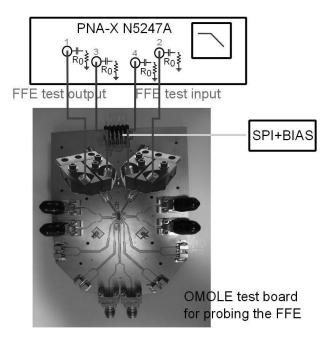

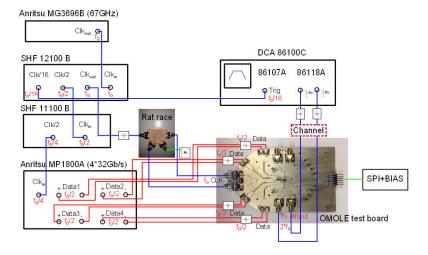

| 4.6  | FFE measurement setup                                                     | 103 |

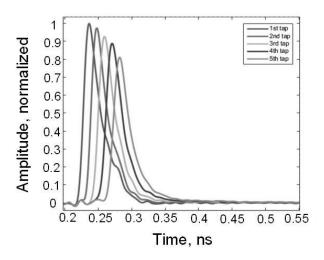

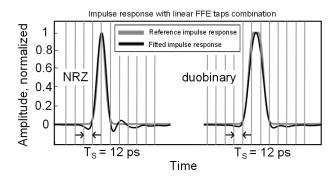

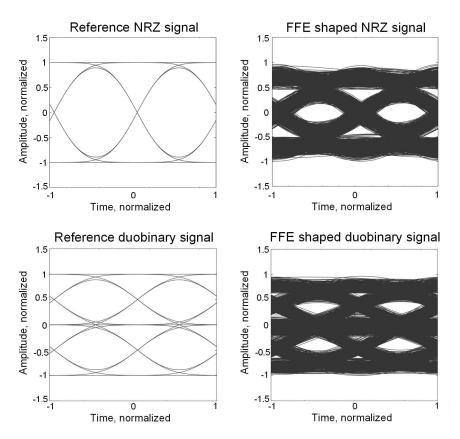

| 4.7  | Impulse response                                                          | 104 |

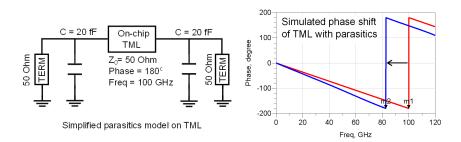

| 4.8  | Increased on-chip TML phase shift with parasitics                         | 105 |

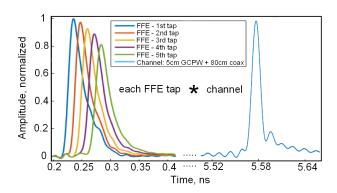

| 4.9  | Impulse responses of each FFE tap and a lossy channel                     | 105 |

| 4.10 | Equalized channel response fitted to NRZ or duobinary re-                 |     |

|      | sponse                                                                    | 106 |

| 4.11 | Simulated eye diagrams of the impulse response fitting                    | 107 |

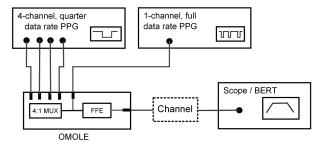

| 4.12 | Block diagram of two optional time domain measurement                     |     |

|      | setups                                                                    | 107 |

| 4.13 | Time domain FFE measurement setup through the FFE test        |     |

|------|---------------------------------------------------------------|-----|

|      | input / output                                                | 108 |

| 4.14 | Loss and reflection of 20 cm coax cable                       | 108 |

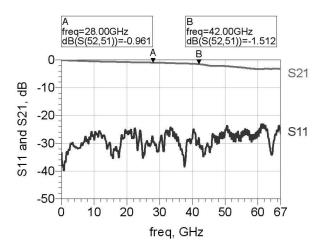

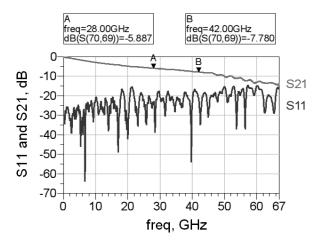

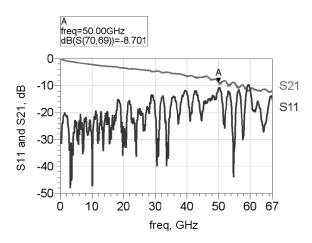

| 4.15 | Loss and reflection of the output trace on the test board     | 109 |

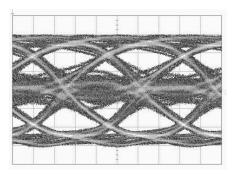

| 4.16 | 56 Gb/s duobinary (PRBS 7) eye diagram of the FFE (5          |     |

|      | ps/div, 50 mV/div)                                            | 110 |

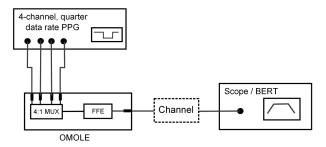

| 4.17 | Block diagram of the TX time-domain measurement setup         | 110 |

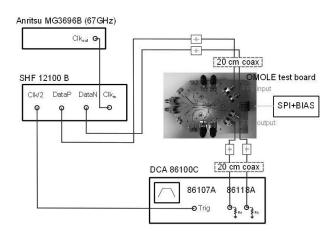

| 4.18 | TX measurement setup                                          | 111 |

| 4.19 | Loss and reflection of the TX output trace on the test board  | 112 |

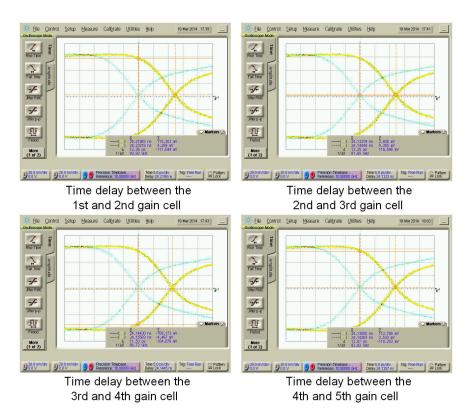

| 4.20 | Measured tap delays of the FFE                                | 113 |

|      | Measured loss of various channels                             | 113 |

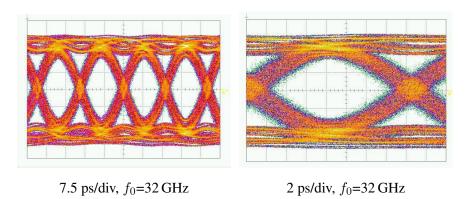

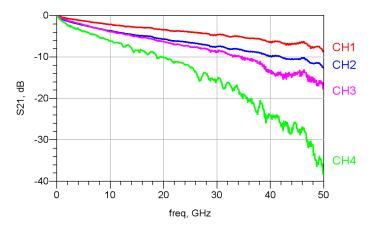

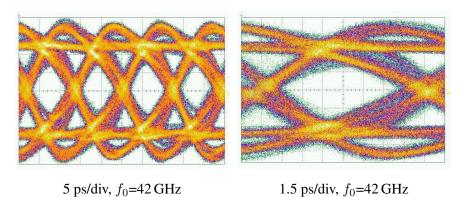

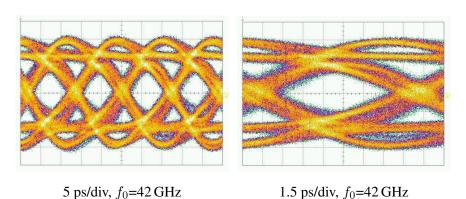

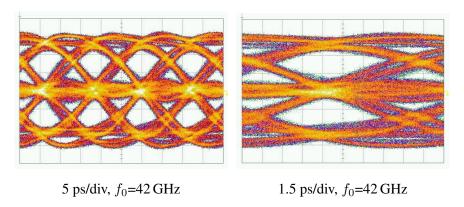

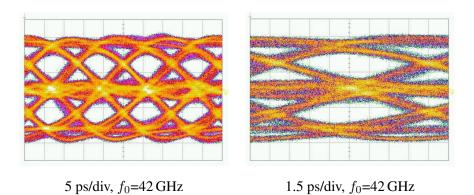

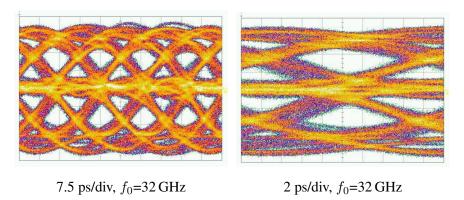

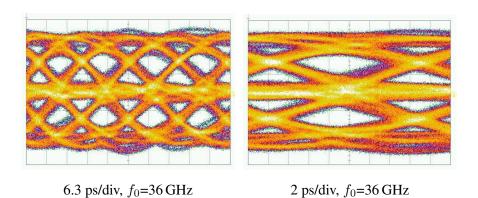

| 4.22 | 84 Gb/s after Channel 1: NRZ                                  | 114 |

| 4.23 | 84 Gb/s after Channel 1: Duobinary                            | 114 |

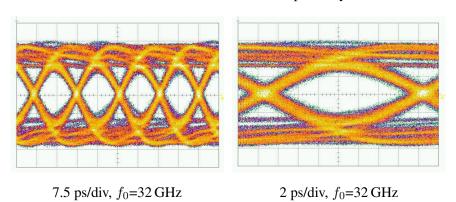

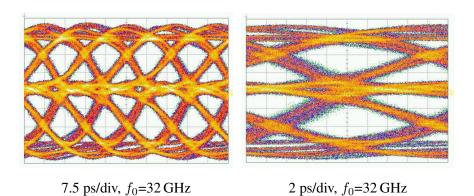

| 4.24 | 64 Gb/s after Channel 2: NRZ                                  | 115 |

| 4.25 | 64 Gb/s after Channel 2: Duobinary                            | 115 |

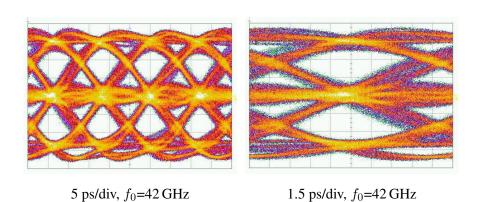

| 4.26 | 84 Gb/s after Channel 2: NRZ                                  | 116 |

| 4.27 | 84 Gb/s after Channel 2: Duobinary                            | 116 |

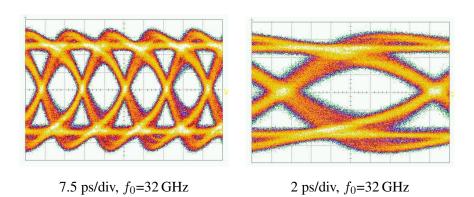

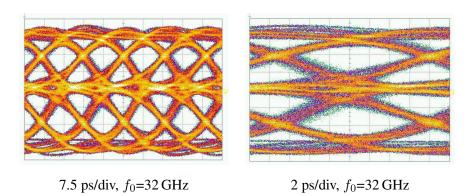

| 4.28 | 64 Gb/s after Channel 3: NRZ                                  | 117 |

| 4.29 | 64 Gb/s after Channel 3: Duobinary                            | 117 |

| 4.30 | 84 Gb/s after Channel 3: Duobinary                            | 117 |

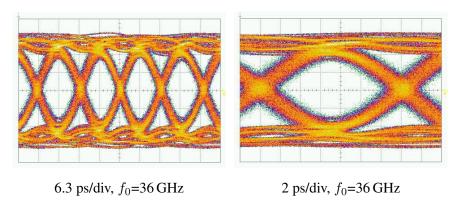

|      | 64 Gb/s after Channel 4: Duobinary                            | 118 |

| 4.32 | 72 Gb/s after Channel 4: Duobinary                            | 118 |

|      | TX-to-RX measurement setup                                    | 121 |

| 4.34 | Measured loss of the complete channels between TX and RX      | 122 |

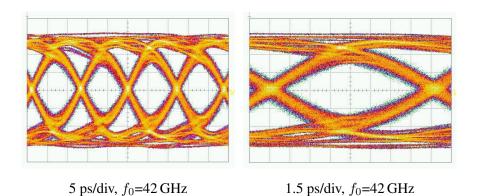

| 4.35 | TX-to-RX interconnects with Channel 1                         | 123 |

| 4.36 | TX-to-RX interconnects with Channel 2                         | 123 |

| 4.37 | TE STRADA Whisper backplane demonstrator                      | 126 |

|      | Insertion loss of backplane demonstrator channels with length | s   |

|      | of 11.5 inch, 18 inch and 27 inch                             | 126 |

| 4.39 | Experimental test setup for 48 Gb/s duobinary serial trans-   |     |

|      | mission over an 11.5 inch Megtron 6 backplane                 | 127 |

| 4.40 | Loss and reflection of the PCB traces added to the back-      |     |

|      | plane channel                                                 | 127 |

| 4.41 | Channel insertion loss including TE backplane and the PCB     |     |

|      | test boards                                                   | 128 |

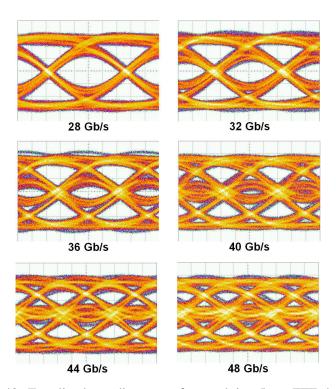

| 4.42 | Equalized eye diagrams after applying 5-tap FFE through       |     |

|      | an 11.5 inch backplane (vertical: 15 mV/div, horizontal:      |     |

|      | 6.6 ps/div)                                                   | 129 |

| 4.43 | Equalized 28 Gb/s output eye diagrams after applying 5-        |     |

|------|----------------------------------------------------------------|-----|

|      | tap FFE through different backplane lengths (vertical: 15      |     |

|      | mV/div, horizontal: 6.6 ps/div)                                | 130 |

| 4.44 | NRZ and duobinary BER measurements with increasing             |     |

|      | data rates over an 11.5 inch backplane                         | 130 |

| 4.45 | FCI ExaMAX® backplane demonstrator                             | 131 |

| 4.46 | Channel insertion loss including FCI backplane and the PCB     |     |

|      | test boards                                                    | 132 |

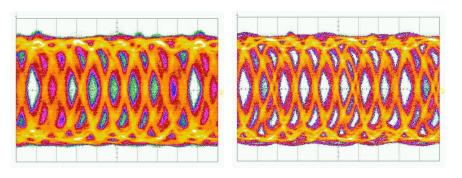

| 4.47 | 40 Gb/s output eye diagrams travelling across a 13.7 inch      |     |

|      | FCI backplane channel (Left figure: vertical 50 mV/div,        |     |

|      | horizontal 7 ps/div; Right figure: vertical 20 mV/div, hori-   |     |

|      | zontal 7 ps/div)                                               | 133 |

| 4.48 | 40 Gb/s output eye diagrams travelling across different back-  |     |

|      | plane lengths (Left figure: vertical 20 mV/div, horizontal 7   |     |

|      | ps/div; Right figure: vertical 10 mV/div, horizontal 5 ps/div) | 134 |

| 4.49 | The vertical eye-opening (red) and the BER (blue) as a         |     |

|      | function of the overall channel loss at the Nyquist frequency  |     |

|      | for 40 Gb/s signal transmission over the FCI backplane         | 134 |

| 4.50 | Output eye diagrams through a 13.7 inch FCI backplane          |     |

|      | (vertical: 10 mV/div, horizontal: 5 ps/div)                    | 135 |

|      |                                                                |     |

## List of Tables

| 2.1 | Materials parameters                                    | 18  |

|-----|---------------------------------------------------------|-----|

| 2.2 | An overview of reported FFEs beyond 40 Gb/s             | 24  |

| 2.3 | An overview of recently reported DFEs                   | 27  |

| 2.4 | An overview of recently reported CTLEs                  | 29  |

| 2.5 | A general comparison of FFEs, DFEs and CTLEs            | 30  |

| 2.6 | High-BW ADCs and DACs                                   | 32  |

| 2.7 | Overview of state-of-the-art BiCMOS processes           | 45  |

| 3.1 | Simulation results of the interface                     | 59  |

| 3.2 | An overview of reported VGAs                            | 81  |

| 4.1 | Summary of the losses added by the measurement environ- |     |

|     | ment                                                    | 109 |

| 4.2 | A summary of the measured FFE outputs with different    |     |

|     | data rates for duobinary                                | 119 |

| 4.3 | A summary of the measured FFE outputs with different    |     |

|     | data rates for NRZ                                      | 119 |

| 4.4 | A summary of the back-to-back measurements with differ- |     |

|     | ent data rates for duobinary                            | 124 |

| 4.5 | A summary of the back-to-back measurements with differ- |     |

|     | ent data rates for NRZ                                  | 124 |

| 4.6 | Summary of the losses added by the experimental setup   | 132 |

## List of Acronyms

#### $\mathbf{A}$

AM Amplitude Modulation

#### B

BER Bit Error Rate

BERT Bit Error Rate Tester

BJT Bipolar Junction Transistor

BP BackPlane board

Bit Error Rate

BR Bit Rate BW Bandwidth

#### $\mathbf{C}$

CPW Coplanar Waveguide

CTLE Continuous Time Linear Equalizer

#### D

DC Daughter Card DeMUX Demultiplexer

DFE Decision-Feedback Equalizer

DSP Digital Signal Processing

$\mathbf{E}$

ED Error Detector

EF Emitter Follower

ESD Electrostatic Discharge

F

FFE Feed-Forward Equalizer

FIR Finite Impulse Response

FoM Figure of Merit

G

GP General Purpose

GSSG Ground-Signal-Signal-Ground

H

HDTV High-Definition Television

I

IC Integrated Circuit I/O Input/Output

IP Internet Protocol

IPTV Internet Protocol Television ISI Inter-Symbol Interference

#### K

KVL Kirchhoff's Voltage Law

#### L

LP Low Power

LPF Low Pass Filter

LSE Least Square Error

LT Line Termination

#### M

MOS Metal Oxide Semiconductor

MPW Multi-Project Wafer M2M Machine-to-Machine

MUX Multiplexer

#### $\mathbf{N}$

NRZ Non-Return-to-Zero

NRZ-OOK Non-Return-to-Zero On/Off Keying

NT Network Termination

#### $\mathbf{0}$

OFDM Orthogonal Frequency-Division Multiplexing

P

PAM Pulse Amplitude Modulation

PCB Printed Circuit Board

PHY Physical Layer

PPG Pulse Pattern Generator

PRBS Pseudo-Random Binary Sequence

PSD Power Spectral Density

Q

QAM Quadrature Amplitude Modulation

R

RX Receiver

$\mathbf{S}$

SDTV Standard-Definition Television

Sinc Cardinal Sine function SNR Signal-to-Noise Ratio

$\mathbf{T}$

TML Transmission Line

Tuning Range Transmitter TR TX

U

Ultra-High-Definition Television Unit Interval UHDTV

UI

$\mathbf{V}$

VGA Variable Gain Amplifier Vector Network Analyzer VNA

# Nederlandstalige samenvatting -Dutch Summary-

De niet aflatende groei van het dataverkeer en de toenemende verwerkingskracht van digitale chips vragen om steeds snellere chip-naar-chip en chipnaar-module interconnecties. Met toenemende datasnelheden zal de kwaliteit van de datasignalen echter meer en meer degraderen na transmissie over een printplaat (PCB) verbinding. Frequentie-afhankelijk verlies en overspraak leiden tot een gereduceerde oogopening, een gereduceerde signaaltot-ruis verhouding en een toenemende inter-symbool-interferentie (ISI). Deze problemen vereisen het gebruik van betere signaalverwerking of betere PCB materialen om de bandbreedtebeperkingen te overwinnen en om de signaalintegriteit te verbeteren. Door een optimale combinatie van egalisatie en ontvangerelektronica, samen met bandbreedte-efficiënte modulatieschema's, kan de transmissiesnelheid over seriële elektrische verbindingen verhoogd worden. Bij de start van dit onderzoek, werkten de meeste industriële backplane connectoren, zoals gemaakt door FCI of TE connectivity, volgens IEEE of OIF specificaties, aan een maximale snelheid van 25 Gb/s.

Dit onderzoek kwam vooral tot stand in het kader van het IWT Shorttrack project. Het doel van dit onderzoek was om de transmissiesnelheid over elektrische backplanes te verhogen tot 100 Gb/s per kanaal voor toekomstige telecom- en datacom-systemen. Deze doelstelling ging veel verder dan de toenmalige stand van zaken, welke beperkt was tot 25 Gb/s voor duobinaire modulatie en 42.8 Gb/s PAM-4 transmissie over een Megtron 6 backplane met lage verliezen, echter gebruik makende van signaalverwerking in Matlab.

De succesvolle implementatie van een geïntegreerde zenderchip, beschreven in dit werk, en een geïntegreerde ontvangerchip, beschreven in het doctoraat van collega Timothy De Keulenaer, tonen duidelijk de haalbaarheid aan van seriële interconnecties voor meer dan 80 Gb/s met het potentieel om 100 Gb/s seriële verbindingen te realiseren in een recente chiptechnologie.

Naast onze bijdrage tot de stand van zaken in het domein van de zeer snelle zendontvangers en backplane transmissie in het algemeen, heeft de demonstratie van dit werk ook veel aandacht gekregen voor heel snelle optoelektronische communicatietoepassingen zoals toegangsnetwerken, actieve optische kabels en optische backplanes.

De achtergrond van dit onderzoek, een overzicht van dit werk en de organisatie van dit proefschrift worden geïllustreerd in Hoofdstuk 1. In Hoofdstuk 2 wordt een systeemanalyse voorgesteld die aantoont dat de kanaalverliezen de transmissiesnelheid over backplanes beperken. Om de seriële datasnelheid te verhogen over backplanes en om de signaaldegradatie te verminderen, worden verschillende technologieën besproken zoals signaal-egalisatie en modulatietechnieken. Eerst wordt er een prototype backplane kanaal met verbeterde connectoren van projectpartner FCI gekarakteriseerd. Dan wordt er een geïntegreerd transversaal feedforward egalisatie filter (FFE) voorgesteld, gebaseerd op een overschouwing van de kanaalperformantie, de analoge egalistie-mogelijkheden, implementatiecomplexiteit en vermogenverbruik.

NRZ, duobinair en PAM-4 zijn de meest eenvoudige modulatieschema's voor uiterst snelle elektrische backplane-communicatie. Na een vergelijking op basis van simulaties, werd het duobinair formaat geselecteerd voor zijn hoge bandbreedte-efficiëntie en zijn redelijke circuitcomplexiteit. Verschillende chiptechnologieën werden vergeleken en het ST 130 nm SiGe BiCMOS9MW proces (met een  $f_T$  groter dan 200 GHz) werd gekozen als compromis tussen snelheid en prototyping kost. Daarnaast biedt dit proces heel goede analoge opties met o.a. een geïntegreerd microstripmodel, dat gebruikt zal worden als vertragingselement in de FFE.

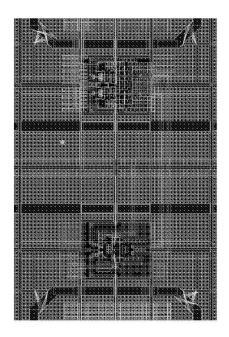

Hoofdstuk 3 illustreert het chipontwerp van de snelle backplane zenderchip, bestaande uit een multiplexer (MUX) en een 5-tap FFE. De 4:1 MUX combineert vier tragere datastromen tot 1 zeer snel NRZ signaal tot 100 Gb/s als input voor de FFE schakeling. Deze MUX werd ontworpen door collega dr. Zhisheng Li. De 5-tap FFE uit mijn onderzoek is geïmplementeerd met een nieuwe topologie met uitgebreide testmogelijkheden, zodat de FFE performantie individueel gekarakteriseerd kan worden in het tijd- en frequentiedomein, zonder de MUX te moeten loskoppelen. Dit helpt ook om de FFE instellingen te optimaliseren. Verschillende instelbare versterkerconfiguraties werden vergeleken. De Gilbert configuratie toont de meeste voordelen, met zowel een goede hoogfrequent performantie en een eenvoudige manier om positieve/negatieve versterking in te stellen. De totale chip, met inbegrip van de MUX en de FFE, verbruikt 750 mW uit een 2.5 V voeding en

DUTCH SUMMARY xxiii

beslaat een oppervlakte van  $4.4 \,\mathrm{mm} \times 1.4 \,\mathrm{mm}$ .

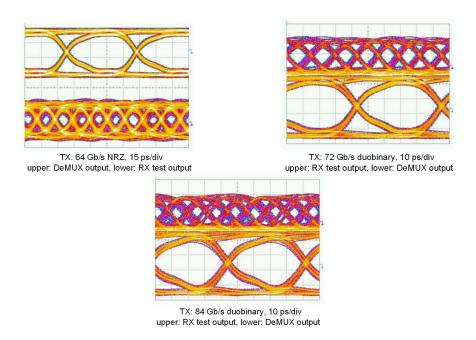

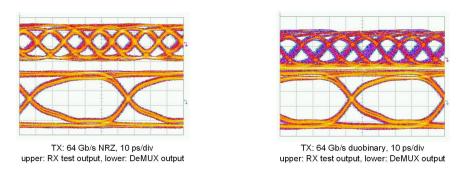

In Hoofdstuk 4 wordt de Tx chip gedemonstreerd tot 84 Gb/s. Eerst werd de FFE performantie gekarakteriseerd in het frequentiedomein, wat aantoonde dat de FFE duobinaire signalen kan maken tot 84 Gb/s. Naast de werking van de verschillende sub-blokken, werd ook de combinatie van MUX en FFE getest. De geëgaliseerde Tx signalen werden opgemeten voor verschillende kanalen en voor zowel NRZ en duobinair aan snelheden van 64 Gb/s tot 84 Gb/s. Dan werd een seriële transmissielink gedemonstreerd door toevoeging van een duobinaire ontvanger (doctoraat Timothy De Keulenaer). Het kanaal bestond hierbij eerst uit een paar 10 cm coax kabels en 5 cm FX-2 stripline transmissielijnen. Het 13.5 dB verlies bij de Nyquist frequentie werd gecompenseerd door de FFE. De ontvangerchip decodeerde het geëgaliseerde duobinaire signaal en demultiplexeerde het signaal naar vier NRZ uitgangen aan een vierde van de snelheid. Deze link had een bitfoutprobabiliteit (BER) van minder van  $10^{-11}$ .

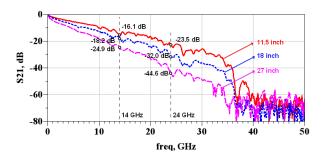

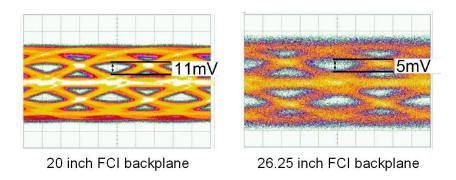

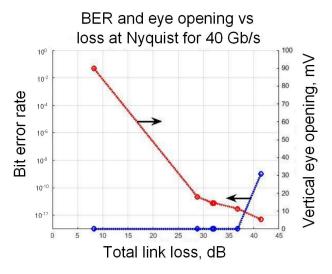

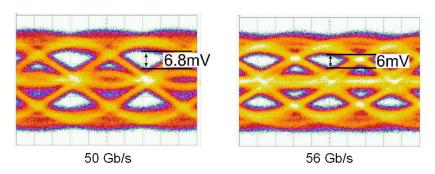

Ten slotte werd ook foutloze transmissie tussen zender en ontvanger gedemonstreerd over twee commerciële backplanes. Eerst werd er met een 11.5 inch Megtron 6 backplane aan een snelheid van 48 Gb/s aangetoond dat duobinair beter werkt dan NRZ voor lange kanalen. Later, werd er met een ExaMAX® backplane demonstrator, het maximum foutvrij kanaalverlies onderzocht aan een snelheid van 40 Gb/s. De oogpatronen en de BER metingen werden uitgevoerd voor zeer lange kanalen tot 26.25 inch. De resultaten tonen aan dat de ontworpen FFE, een groot totaalverlies van 37 dB bij de Nyquist frequentie kan overwinnen met foutvrije duobinaire transmissie, en voor een BER van  $10^{-8}$  is zelfs een kanaalverlies van 42 dB overbrugbaar. Een overzicht van de conclusies is samengevat in Hoofdstuk 5, met een aantal suggesties voor verder onderzoek.

#### **English summary**

The relentless growth of data traffic and increasing digital signal processing capabilities of integrated circuits (IC) are demanding ever faster chip-to-chip / chip-to-module serial electrical interconnects. As data rates increase, the signal quality after transmission over printed circuit board (PCB) interconnections is severely impaired. Frequency-dependent loss and crosstalk noise lead to a reduced eye opening, a reduced signal-to-noise ratio and an increased inter-symbol interference (ISI). This, in turn, requires the use of improved signal processing or PCB materials, in order to overcome the bandwidth (BW) limitations and to improve signal integrity. By applying an optimal combination of equalizer and receiver electronics together with BW-efficient modulation schemes, the transmission rate over serial electrical interconnections can be pushed further. At the start of this research, most industrial backplane connectors, meeting the IEEE and OIF specifications such as manufactured by e.g. FCI or TE connectivity, had operational capabilities of up to 25 Gb/s.

This research was mainly performed under the IWT ShortTrack project. The goal of this research was to increase the transmission speed over electrical backplanes up to 100 Gb/s per channel for next-generation telecom systems and data centers. This requirement greatly surpassed the state-of-the-art reported in previous publications, considering e.g. 25 Gb/s duobinary and 42.8 Gb/s PAM-4 transmission over a low-loss Megtron 6 electrical backplane using off-line processing.

The successful implementation of the integrated transmitter (TX) and receiver (RX) <sup>1</sup>, clearly shows the feasibility of single lane interconnections beyond 80 Gb/s and opens the potential of realizing industrial 100 Gb/s links using a recent IC technology process. Besides the advancement of the state-of-the-art in the field of high-speed transceivers and backplane transmission systems, which led to several academic publications, the output of this work also attracts a lot of attention from the industry, showing

<sup>&</sup>lt;sup>1</sup>The duobinary receiver was developed by my colleague Timothy De Keulenaer, as described in his PhD dissertation.

xxvi English summary

the potential to commercialize the developed chipset and technologies used in this research for various applications: not only in high-speed electrical transmission links, but also in high-speed opto-electronic communications such as access, active optical cables and optical backplanes.

In this dissertation, the background of this research, an overview of this work and the thesis organization are illustrated in Chapter 1.

In Chapter 2, a system level analysis is presented, showing that the channel losses are limiting the transmission speed over backplanes. In order to enhance the serial data rate over backplanes and to eliminate the signal degradation, several technologies are discussed, such as signal equalization and modulation techniques. First, a prototype backplane channel, from project partner FCI, implemented with improved backplane connectors is characterized. Second, an integrated transversal filter as a feed-forward equalizer (FFE) is selected to perform the signal equalization, based on a comprehensive consideration of the backplane channel performance, equalization capabilities, implementation complexity and overall power consumption. NRZ, duobinary and PAM-4 are the three most common modulation schemes for ultra-high speed electrical backplane communication. After a system-level simulation and comparison, the duobinary format is selected due to its high BW efficiency and reasonable circuit complexity. Last, different IC technology processes are compared and the ST microelectronics BiCMOS9MW process (featuring a  $f_T$  value of over 200 GHz) is selected, based on a trade-off between speed and chip cost. Meanwhile it also has a benefit for providing an integrated microstrip model, which is utilized for the delay elements of the FFE.

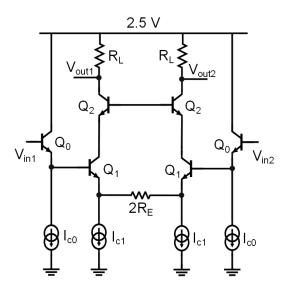

Chapter 3 illustrates the chip design of the high-speed backplane TX, consisting of a multiplexer (MUX) and a 5-tap FFE. The 4:1 MUX combines four lower rate streams into a high-speed differential NRZ signal up to 100 Gb/s as the FFE input. The 5-tap FFE is implemented with a novel topology for improved testability, such that the FFE performance can be individually characterized, in both frequency- and time-domain, which also helps to perform the coefficient optimization of the FFE. Different configurations for the gain cell in the FFE are compared. The gilbert configuration shows most advantages, in both a good high-frequency performance and an easy way to implement positive / negative amplification. The total chip, including the MUX and the FFE, consumes 750 mW from a 2.5 V supply and occupies an area of 4.4 mm  $\times$  1.4 mm.

In Chapter 4, the TX chip is demonstrated up to 84 Gb/s. First, the FFE performance is characterized in the frequency domain, showing that the

English summary xxvii

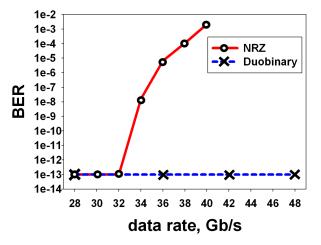

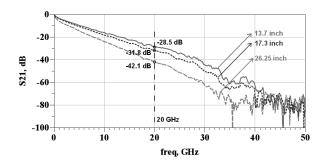

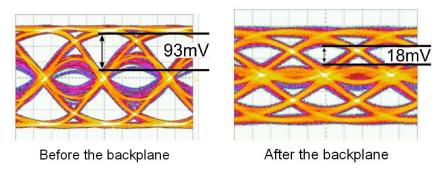

FFE is able to work up to 84 Gb/s using duobinary formats. Second, the combination of the MUX and the FFE is tested. The equalized TX outputs are captured after different channels, for both NRZ and duobinary signaling at speeds from 64 Gb/s to 84 Gb/s. Then, by applying the duobinary RX <sup>2</sup>, a serial electrical transmission link is demonstrated across a pair of 10 cm coax cables and across a 5 cm FX-2 differential stripline. The 5-tap FFE compensates a total loss between the TX and the RX chips of about 13.5 dB at the Nyquist frequency, while the RX receives the equalized signal and decodes the duobinary signal to 4 quarter rate NRZ streams. This shows a chip-to-chip data link with a bit error rate (BER) lower than  $10^{-11}$ . Last, the electrical data transmission between the TX and the RX over two commercial backplanes is demonstrated. An error-free, serial duobinary transmission across a commercial Megtron 6, 11.5 inch backplane is demonstrated at 48 Gb/s, which indicates that duobinary outperforms NRZ for attaining higher speed or longer reach backplane applications. Later on, using an ExaMAX® backplane demonstrator, duobinary transmission performance is verified and the maximum allowed channel loss at 40 Gb/s transmission is explored. The eye diagram and BER measurements over a backplane channel up to 26.25 inch are performed. The results show that at 40 Gb/s, a total channel loss up to 37 dB at the Nyquist frequency allows for error-free duobinary transmission, while a total channel loss of 42 dB was overcome with a BER below  $10^{-8}$ .

An overview of the conclusions is summarized in Chapter 5, along with some suggestions for further research in this field.

<sup>&</sup>lt;sup>2</sup>Described in the PhD dissertation of Timothy De Keulenaer.

# List of publications

# **Publications in international journals**

- Y. Ban, T. De Keulenaer, G. Torfs, J.H. Sinsky, B. Kozicki and J. Bauwelinck, *Experimental evaluation of NRZ and duobinary up to 48 Gbit/s for electrical backplanes*, Electronics Letters, vol. 51, no. 8, pp. 617-619, April 2015.

- T. De Keulenaer, G. Torfs, **Y. Ban**, R. Pierco, R. Vaernewyck, A. Vyncke, Z. Li, J.H. Sinsky, B. Kozicki, X. Yin and J. Bauwelinck, 84 *Gbit/s SiGe BiCMOS duobinary serial data link including serialiser/deserialiser (SERDES) and 5-tap FFE*, Electronics Letters, vol. 51, no. 4, pp. 343-345, February 2015.

- Y. Ban, T. De Keulenaer, Z. Li, J. Van Kerrebrouck, J.H. Sinsky, B. Kozicki, J. Bauwelinck and G. Torfs, A wide-band, 5-tap transversal filter with improved testability for equalization up to 84 Gb/s, accepted by the IEEE Microwave and Wireless Components Letters.

# **Publications in international conferences**

- T. De Keulenaer, J. De Geest, G. Torfs, J. Bauwelinck, Y. Ban, J.H. Sinsky and B. Kozicki, 56+ Gb/s serial transmission using duobinary signaling, Proceedings of IEC DesignCon, Santa Clara USA, January 2015.

- T. De Keulenaer, Y. Ban, G. Torfs, S. Sercu, J. De Geest and J. Bauwelinck, *Measurements of millimeter wave test structures for high speed chip testing*, 18th IEEE Workshop on Signal and Power Integrity (SPI), Ghent Belgium, May 2014, pp. 1-4.

- T. De Keulenaer, Y. Ban, Z. Li and J. Bauwelinck, Design of an 80 Gbit/s SiGe BiCMOS fully differential input buffer for serial elec-

XXX OVERVIEW

*trical communication*, 19th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Seville, December 2012, pp. 237-239.

# **Publications in national conferences**

- Y. Ban, G. Torfs and J. Bauwelinck, *High speed data transmission over electrical backplane channels*, 15th FEA PhD symposium, Interactive poster session, Ghent Belgium, December 2014.

- Y. Ban and J. Bauwelinck, *High-speed transmitter design for communication beyond 40 Gb/s*, 13th FEA PhD symposium, Presentation session, Ghent Belgium, December 2012.

# **Patents**

• J. Bauwelinck, G. Torfs, **Y. Ban** and T. De Keulenaer, *Improvements in test circuits*, European patent application, EP14161772.0, filed in March 2014.

# 1

# Introduction

Nowadays, people are increasingly relying on the internet and expecting ever faster connectivity to either their workplace or home. First of all, the impressive evolution of video-based internet consumption demands much higher data rates from data networks. Second, the implementations of internet protocol television (IPTV) have experienced a number of generations, from standard-definition television (SDTV), high-definition television (HDTV) and ultra-high-definition television (UHDTV), gradually evolving to 3D television. This development pushes the demand for widely deployed, high-bandwidth (BW) services [1]. Therefore, both internet users and content providers have been demanding larger and larger network BW supporting higher data rates. Meanwhile, factors expected to drive traffic growth further include global increases in the number of internet users, personal devices and machine-to-machine (M2M) connections. It has been predicted that from 2014 to 2019, global internet protocol (IP) traffic will increase 3-fold and reach 168 exabytes per month by 2019, which is depicted in Figure 1.1 [2].

Figure 1.1: Global IP traffic growth

# 1.1 Background

#### 1.1.1 Network architecture and access nodes

The ever increasing BW demands pose increasingly challenging requirements for network switches and core routers in high-speed data communication systems. As an essential part of network core routers, access nodes terminate various user connections (such as: xDSL, GPON, 10GPON) and aggregate the data from various end-users. This data stream is forwarded at a high speed along optical fibers in the internet backbone, metro and access networks. Figure 1.2 presents the general structure of a modern telecommunication network [3].

The progressive growth of network traffic from the data center to the endusers requires an ever faster data rate across the access nodes. Meanwhile, as the oversubscription rate [4] may decrease, it potentially triggers a faster growth on the internal capacity of access nodes compared to end-users. Moreover, some operators expect an even higher user BW and higher access rate for next-generation internet networks in the future. Therefore, a rapidly increasing BW requirement within access nodes, either internal or external, can be foreseen in next-generation data transmission networks [5].

The architecture of an access node, as shown in Figure 1.3, is a star topology. The interfaces towards the end-users are terminated on a card called line termination (LT) card, while the interfaces towards the metro network are terminated on a card called network termination (NT) card. All LT cards

Introduction 3

Figure 1.2: Network architecture overview

are connected with the NT card via a backplane. For redundancy reasons, sometimes a second NT is used. This architecture is called a star architecture because each LT card has a point-to-point connection with the NT card. Therefore, extending the throughout over a backplane is a critical part for enhancing the overall operational speed across access nodes [5] [6].

Figure 1.3: Access nodes with star architecture

At the beginning of this research, most industrial backplane systems operated at serial data rates between 10 Gb/s and 28 Gb/s per lane [7] [8]. These backplane systems consist of integrated backplane transceivers and indus-

trial backplane channels (including a big multi-layer PCB and connectors), such as manufactured by e.g. FCI Electronics or TE Connectivity [9].

### 1.1.2 Technical challenges

Extending the serial backplane channel throughput (e.g. beyond 40 Gb/s) is very challenging due to various aspects across the end-to-end communication channel.

First of all, a great challenge is the inter-dependency of the different aspects of the end-to-end solution. For example, the selection of the modulation scheme depends on the characteristics of the backplane traces / connectors. But the design of backplane connectors and the selection of backplane materials are relevant to the required system BW, which depends on the selected modulation scheme. Meanwhile, the design of transceiver electronics depends not only on the selected modulation and coding scheme, but also on the characteristics of the backplane channel: BW, linearity, noise, equalizer requirements...

Second, the transceiver design is highly challenging due to the very tough high-speed requirements, which went far beyond the state-of-the-art. The dependency between transceiver electronics and modulation format creates a challenge as different modulation schemes have specific characteristics and trade-offs among power dissipation, chip area and performance. Investigation of packaging technologies will also be necessary to eliminate the signal degradation along the connection between the die and the board. At high frequencies, reflections and termination issues due to process variation and parasitics also require investigation.

In addition, there is a challenge for the backplane and connector suppliers to enhance the BW of the passive backplane channel. Different backplane transmission line (TML) configurations (micro-strips, striplines, coplanar waveguides...) and dielectric materials (FR-4, Megtron6, Nelco 4000-13...) need to be investigated. Meanwhile, the design challenges of backplane connectors are manifold, due to their 3D structure and mechanical tolerances, including e.g. the connector to board termination and associated via holes. The impact of component tolerances on the component and system performance needs to be researched as well, since at high-frequency, small variations can have a significant impact.

Last, the modulation and coding challenge is to define schemes that maximize the throughput with minimal complexity (low-cost transceivers), taking into account the limitations of the connectors and reasonably priced backplane materials. At the targeted very high throughput, the design complexity becomes rapidly an important issue as additional interconnections

INTRODUCTION 5

and additional circuit elements increase the amount of parasitics in the network, and it will be crucial to keep the complexity under control. In the meantime, besides NRZ, other schemes such as PAM-4 and duobinary will be investigated as well. These schemes, although being more complex, reduce the required BW, which could be beneficial in reducing the overall backplane cost. Another trade-off is the complexity of the modulation versus the required number of transceivers. The extra complexity and cost of a transceiver can be counteracted by the fact that fewer transceivers are necessary to provide a comparable capacity. Next to these challenges the resulting solution should be a green solution in the sense that power consumption per capacity unit should be reduced or comparable to current systems.

To answer all the above-mentioned technical questions, the INTEC Design lab was engaged in a big research project together with Alcatel-Lucent Bell Labs and FCI, with the objective to study and to demonstrate next-generation transceiver circuits with speeds well beyond state-of-the-art.

#### 1.2 Overview of this work

This dissertation is mainly based on the author's research in the frame of the IWT project ShortTrack, over the past 4.5 years at the Design laboratory in the department of Information Technology (INTEC).

The overall innovation goal of ShortTrack was to investigate and to develop the building blocks to increase the transmission speed over electrical backplanes with reasonable power consumption, which enhances the overall system capacity and constrains cost. In this research, the first activities focused on the definition of the circuit specifications deriving from the system requirements and the initial assumptions of the channel characteristics. In parallel, various technologies and circuit techniques were explored to evaluate the feasibility of the inital specifications. The resulting requirements have been established end-to-end with a final goal to increase serial data rates up to 100 Gb/s per lane over electrical backplanes with on-board interconnects of around 10 cm long.

Backplane communication operating at high data rates poses great challenges as it requires a very high BW across the electrical link, while increased data rates face excessive frequency dependent attenuation, reflection and inter-symbol interference (ISI) [10]. These degrading effects become much more pronounced at higher frequencies as they scale more than linearly with frequency. As a result, in high-speed communication links, the received data waveforms can be significantly distorted after travelling through coaxial cables or printed circuit board (PCB) interconnects [11]. To compensate the ISI and to improve the channel BW efficiency, advanced

modulation and equalization were used in transmitter (TX) and receiver (RX) circuits. Besides, a 4-to-1 serializer which combined lower speed input signals to higher speed output signals was added in the TX. The serializer and its output buffer were designed together with our colleague Zhisheng Li.

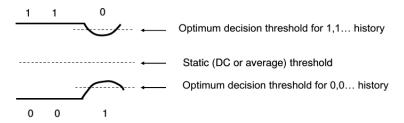

Duobinary signaling is a valuable candidate of modulation formats, especially in band-limited eletrical transmission systems. Duobinary holds great potential for attaining high-speed or long-reach electrical transmission systems, as it utilizes the available BW more efficiently and allows confining the signal power spectral density (PSD) to lower frequencies compared to non-return-to-zero (NRZ). However, the implementation of the duobinary format involves a bit more complexity in the transceiver design due to the need for a precoder and decoder operating at the line rate.

The PCB traces in backplanes introduce frequency-dependent losses. Meanwhile, the parasitics introduced by the connectors, together with the termination resistors, generate a low-pass filter and further reduce the BW of the backplane link. All those effects introduce signal ISI and degrade the signal transmission performance, especially at high frequencies. Therefore, the development and optimization of high-speed electrical backplane channels is an important part in this project, mainly performed by project partner FCI Electronics.

My work focused on investigating and developing high-speed TX circuits, optimized for duobinary modulation. After the implementation of the TX and RX chips, together with my colleague Timothy De Keulenaer, we demonstrated an error-free, serial electrical duobinary transmission across an electrical backplane at a record speed, showing the potential to realize next-generation data links.

The results of this research can be applied in a variety of telecom and datacom systems, where high-speed electrical links are also relevant with various chip-to-chip / chip-to-module interconnects, as described in [12].

# 1.3 Organization of this dissertation

Chapter 1 presents the background of this research, an overview of this work and the organization of this dissertation. In this first chapter, high-speed access nodes, as essential parts connecting internet end-users with content providers, have been briefly described. As a core part of the access nodes, high-speed data transmission over electrical backplanes has been researched in this work, aiming to increase the serial data rate. In order to eliminate the signal degradation, Chapter 2 illustrates a system level analysis, and discusses several potential technical improvements, including sig-

Introduction 7

nal equalization and modulation techniques. The design and optimization of a high-speed integrated TX, consisting of a multiplexer (MUX) and a 5-tap feed-forward equalizer (FFE), are illustrated in Chapter 3. The 5-tap FFE is implemented with an innovative topology for improved testability, such that the FFE performance can be individually characterized. Chapter 4 demonstrates the measurement results of the TX chip up to 84 Gb/s, showing progress beyond the state-of-the-art in both speed and power efficiency. Besides, system level measurements are performed in combination with an integrated RX chip. Error-free, electrical data transmission across various channels has been demonstrated, with serial data rates up to a record 84 Gb/s using duobinary modulation. Finally, this dissertation ends with a summary of the most important conclusions of this work in Chapter 5.

# References

- [1] C. Denison, Your 1080p TV is old already: Everything you need to know about Ultra HD 4K. Digital Trends, May 2014.

- [2] D. Webster, Cisco Visual Networking Index Predicts IP Traffic to Triple from 2014-2019; Growth Drivers Include Increasing Mobile Access, Demand for Video Services. Cisco Press Release, San Jose USA, May 2015.

- [3] Cisco Systems, Inc. *Broadband access in the 21st century: applications, services and technologies.* White Paper, San Jose USA, 2011.

- [4] TechTarget Ltd., *Oversubscription*. Storage hardware Glossary, SAN switch, TechTarget Ltd.

- [5] Ethernite Networks Ltd., *Next generation multi service access node universal line card processor*. White Paper, Ethernite Networks, Lod Israel, September 2009.

- [6] B. Pauwels and G. Taildeman, *An access node and method for reliable bonding of subscriber lines*. European Patent File, EP1962544 B1, Alcatel Lucent, April 2011.

- [7] Y. Hidaka, W. Gai, T. Horie, J.H. Jiang, Y. Koyanagi and H. Osone, *A 4-Channel 1.25 to 10.3 Gb/s backplane transceiver macro with 35 dB equalizer and sign-based zero-forcing adaptive control.* IEEE Journal of Solid-State Circuits, vol. 44, no. 12, pp. 3547-3559, December 2009.

- [8] A. Adamiecki, M. Duelk and J.H. Sinsky, *25 Gbit/s electrical duobi-nary transmission over FR-4 backplanes*. Electronics letters, vol. 41, no. 14, pp. 826-827, July 2005.

- [9] A. Healey and C. Morgan, *A comparison of 25 Gbps NRZ & PAM-4 modulation used in legacy & premium backplane channels*. Design-Con Conference, Santa Clara USA, January 2012.

[10] E. Song, J. Cho, W. Lee, M. Shin and J. Kim, A wide-band passive equalizer design on PCB based on near-end crosstalk and reflections for 12.5 Gbps serial data transmission. IEEE Microwave and Wireless Components Letters, vol. 18, no. 12, pp. 794-796, December 2008.

- [11] J.H. Sinsky, M. Duelk and A. Adamiecki, *High-speed electrical back-plane transmission using duobinary signaling*. IEEE Transactions on Microwave Theory and Techniques, vol. 53, no. 1, pp. 152-160, January 2005.

- [12] V. Stojanovic, *High-speed serial links: design trends and challenges*. Proceedings 5th International Workshop on System-on-Chip for Real-Time Applications, July 2005.

# 2

# Backplane systems and modulation schemes

# 2.1 Introduction

The relentless growth of data traffic and digital signal processing capabilities are demanding for ever faster interconnections between chips and other modules. Therefore, in the electrical backplane links, an increased channel bandwidth (BW) is required, in order to increase the transmission data rate. From the literature study, we found that most reported backplane systems are operating at the data rate of 10 Gb/s or 28 Gb/s per lane [1]- [3]. Recently, standard groups such as the IEEE P802.3bs 400 GbE and the OIF CEI-56G-VSR/MR have been looking into serial data rates above 50 Gb/s as the line rate of future generation physical layers (PHYs) [4]. In this section, we investigate the feasibility of serial backplane transmission beyond 40 Gb/s, and try to find the bottlenecks limiting the transmission performance. Therefore, a careful system level analysis and optimization is required.

At very high data rates, the signal quality in a low-cost printed circuit board (PCB) transmission line (TML) is severely impaired by frequency dependent losses leading to a reduced eye opening, reduced signal-to-noise ratio and increased inter-symbol interference (ISI). Meanwhile, as part of the channel, backplane connectors are very critical with respect to signal re-

flections and channel BW. In addition, advanced modulation and/or equalization are widely used in the transmitter (TX) / receiver (RX), in order to compensate the ISI and to improve the channel BW efficiency [5]. The performance of these techniques, together with new PCB technologies and backplane connectors, needs to be evaluated in order to satisfy both the specific channel throughput and power constraints [6]. Moving beyond 40 Gb/s data rate, however, poses great challenges on the integrated circuit design due to the semiconductor technology limitations and the related layout parasitics, which will degrade the chip performance, especially at high frequencies. Therefore, care has to be taken in the selection of the IC fabrication process, taking into account the circuit design limitations, while minimizing the power consumption and chip cost.

# 2.2 Backplane channel and design challenges

A backplane system groups a number of electrical PCBs (e.g. daughter boards) through a number of backplane connectors, which are placed in parallel on a backplane board, as illustrated in Figure 2.1. A backplane is commonly used as a backbone in routers or network switches in servers and network attached storage arrays, to realize high-speed communcation between several PCBs. In addition, cable backplanes using coaxial cables are recently employed as an alternative for traditional PCB backplanes, due to its advantages of lower loss and higher flexibility. In this work, we mainly focused on the conventional backplane concepts using PCB traces as signal paths.

#### 2.2.1 Backplane channel

A typical backplane system is depicted in Figure 2.1, showing two daughter cards (DC) and one backplane board (BP). The DCs are plugged into the BP, by using through-hole backplane connectors. One DC receives the electrical / optical signals from external networks or external equipment, and sends the signal to the other DC via the backplane system. As presented in Figure 2.1, the transceiver chips are mounted in packages and located on the DCs, with one chip on each side. Therefore, a full signal path over the backplane channel from one chip to the other chip is generated. The backplane channel consists of the traces on two DCs, the trace on the BP as well as two backplane connectors.

Figure 2.1: A typical backplane system [7]

# 2.2.2 Bandwidth limitation

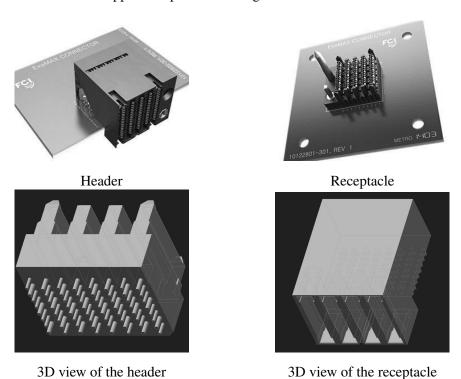

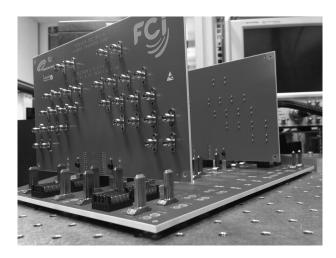

At the start of this research, industrial backplane connectors, such as manufactured by e.g. FCI or TE connectivity, had operational capabilities up to 25 Gb/s. The FCI ExaMAX® connector is depicted in Figure 2.2 and Figure 2.3. [9] shows that it is possible to transmit a serial 25 Gb/s signal over a 17 inch copper backplane including two ExaMAX® connectors.

Figure 2.2: FCI ExaMAX® backplane connector [8]

Figure 2.3: FCI ExaMAX® backplane

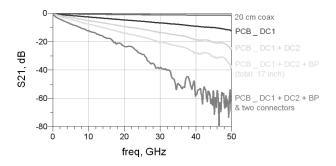

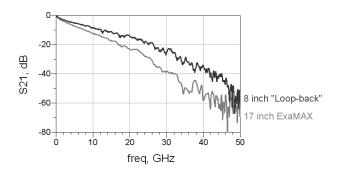

Figure 2.4 elaborates our measurement results of a 17 inch long ExaMAX® backplane channel, including a 5 inch BP and two 6 inch DCs.

Figure 2.4: Measured loss of a FCI ExaMAX® backplane

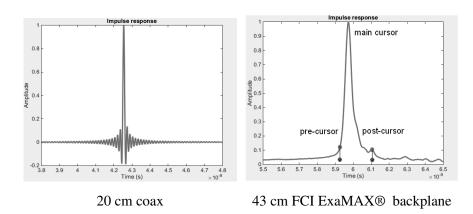

The impulse response, shown in Figure 2.5, of a 17 inch (around 43 cm) ExaMAX® channel, extended with 20 cm coax test cables, is calculated from the frequency response shown in Figure 2.4. The impulse response of the ExaMAX® channel is clearly broadened due to the limited BW of the channel, resulting in pre- and post-cursors.

Transmitting a serial 80 Gb/s non-return-to-zero (NRZ) signal without equalization over the 17 inch ExaMAX® backplane demonstrator provides the output eye diagrams shown in Figure 2.6. It is clear that, due to the BW limitation, the output eye diagrams are totally closed when operating the ExaMAX® backplane demonstrator at 80 Gb/s. This result indicates that the performance of currently available backplane channels needs to be im-

Figure 2.5: Impulse response of a FCI ExaMAX® backplane

proved, in order to enhance the serial data rate. Such improvements are underway in the form of e.g. cable backplanes or orthogonal backplane connections [10].

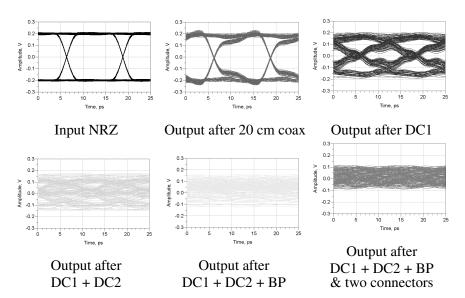

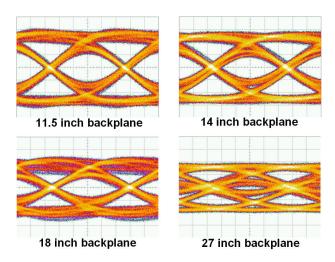

Figure 2.6: 80 Gb/s NRZ signal transmission over different sections of a commercial ExaMAX® backplane without equalization

As shown in Figure 2.4, the performance of the backplane channel is mainly limited by the BW of the backplane connector, and the slope of the channel insertion loss that is mainly attributed to the trace length and dielectric ma-

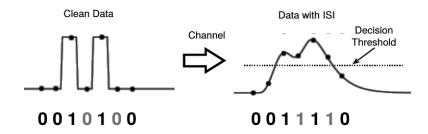

terial. Meanwhile, there are several notches in the frequency response due to the impedance mismatch from the routing geometries and the connector via holes. All those BW-limiting effects need to be minimized in order to realize high speed signal transmission. In high speed backplane applications, as the channels have low-pass filter characteristics, a perfect narrow pulse transmitted at the input of the channel is greatly attenuated in amplitude and the received pulse becomes much wider at the channel output, with several pre- and post-cursors around the main cursor caused by pulse dispersion and the low-pass filter characteristics. In the meantime, due to the reflections caused by impedance discontinuities, ripples can be found in the received waveform at the output of the backplane link. Each of those effects degrades the quality of the signal transmission by increasing the ISI and this makes it increasingly difficult for the RX to recover the transmitted bit sequences. For the same link, the time-domain response of a pulse with the same width is deterministic, and the ISI effect will become worse at higher data rate as the period of the transmitted signal decreases. Therefore. ISI is one of the dominant factors that limit the maximum achievable data rate over a high speed backplane channel. In this work, the bottlenecks for transmitting a high speed signal over a copper backplane system are investigated, so that an appropriate solution for these bottlenecks will be generated.

# 2.2.3 Backplane implementation

As mentioned above, a backplane signal is generated on one DC (with a TX chip) and travels along a number of PCB traces in order to arrive at the other DC (with a RX chip). The frequency-dependent losses of the PCB traces introduce signal attenuation. In the meantime, the parasitics introduced from the connectors, together with the termination resistors of the channel, generate a low-pass filter and further reduce the BW of the backplane link. All those effects introduce signal ISI and degrade the signal transmission performance, especially at high frequencies.

Therefore, in order to achieve high speed data communication between transceiver chips, the frequency response of the whole backplane channel needs to be evaluated and each part of the backplane channel needs to be modelled and included in simulations. In the following parts, the characteristics of backplane traces and connectors are briefly illustrated.

#### 2.2.3.1 Transmission line traces

The frequency-dependent attenuation of backplane traces is mainly due to conductor losses and dielectric losses. At high frequencies, due to skin effect, the current flows along the edge of the metal trace, which reduces the actual metal cross section. Therefore, the resistance and conductor loss of a TML increases with frequency. Dielectric loss is another dominant factor which determines the total TML losses. In high speed applications a PCB designed with a low loss tangent (tan  $\delta$ ) material is preferred due to its lower loss at high frequencies. Besides the materials used in a TML, the configuration of the TML also plays a considerable role with respect to performance.

There are several types of TMLs that can be used as transmission path to convey electromagnetic waves or high speed signals at radio frequencies, such as: micro-strips, striplines, coplanar waveguides (CPW) and coaxial lines. Taking the physical structures and dimensions of backplane systems into account, micro-strips and striplines are the two most common TML structures in backplane links [11]. Compared to micro-strips, striplines always offer larger BW and higher isolation, so lower crosstalk between adjacent traces. Meanwhile, due to the sandwiched structure of striplines, with a strip conductor located between a pair of groundplanes, the capacitance per meter is higher (compared to microstrips) so that a stripline PCB is always much thicker for a given impedance (such as  $50 \Omega$ ) and the strip width is smaller (compared to microstrips), so closer to fabrication constraints. Therefore, it is harder and more expensive to manufacture a stripline PCB than a micro-strip PCB. However, in general, thanks to its better performance, it is recommended to implement high-speed backplane links with striplines [12]. In Table 2.1 the parameters of the most commonly used materials are elaborated. FR-4 is commonly used in low cost PCB design. However, it has a high frequency-dependent loss. Therefore, for high speed board design, other materials with lower dielectric loss are considered [9]. As presented in Table 2.1, compared to FR-4, the RO4000 series and Megtron6 have a lower dielectric loss. For instance, currently Megtron6 is commonly used in high speed BPs [16] [17]. However, Megtron6 is much more expensive than FR-4 [18] [19]. Therefore, people are trying to find alternative materials, with a better performancecost ratio. As shown in Table 2.1, FX-2 has a lower frequency-dependent loss than Nelco 4000-13 and a comparable loss as Megtron6. Therefore, it has been accepted as an alternative material for high frequency signal traces [20] [21].

|               | Dielectric constant (Dk) | Dielectric loss (Df) |  |

|---------------|--------------------------|----------------------|--|

| FR-4          | 4.4                      | 0.02@ 1 GHz          |  |

| RO4003 [13]   | 3.38                     | 0.0027@ 10 GHz       |  |

| RO4350 [13]   | 3.48                     | 0.0037@ 10 GHz       |  |

| Megtron6 [14] | 3.4                      | 0.002@ 1 GHz         |  |

| Nelco 4000-13 | 3.7                      | 0.01@ 1 GHz          |  |

| FX-2 [15]     | 3.44                     | 0.0015@ 1 GHz        |  |

Table 2.1: Materials parameters

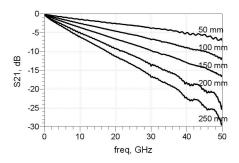

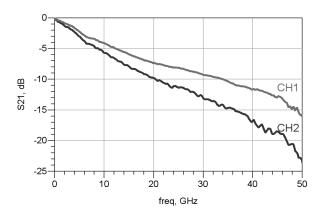

For our measurements, FX-2 striplines were chosen as the BP traces. In order to evaluate the PCB traces performance, several FX-2 striplines are fabricated and the losses of different lengths are measured and presented in Figure 2.7.

Figure 2.7: Measured loss of FX-2 PCB striplines

# 2.2.3.2 Backplane connectors

High speed backplane connectors for data rates beyond 40 Gb/s are very challenging to develop. Also the connector to board transition and the assiciated via holes or stubs are very critical to optimize, as depicted in Figure 2.2. In [22], it has been identified that backplane via stubs introduce capacitances and behave as a low pass filter (LPF). Due to the intrinsic and complex physical nature, increasing the BW of via holes is one of the most critical challenges. In the meantime, backplane via stubs are one of the main sources of frequency selective reflections. For example, a stub as short as one mm, may introduce unacceptable impedance discontinuities

and mismatch, and cause signal reflection or resonances in the frequency range of interest, which greatly degrade the signal transmission quality. Thus, in order to minimize the noise caused by the reflections, an optimal footprint design between the connector and board termination becomes very improtant, in combination with via backdrilling. In addition, at high frequencies, every small detail of the connectors becomes important. For example, the skew between the lanes in each differential pair needs to be compensated in the connector design. Resonances on ground pins / structures caused by standing waves need to be avoided as well. All these details need to be considered in order to increase the BW of backplane connectors and backplane links. In addition, the crosstalk between the channels needs to be minimized as well, in order to realize parallel multi-channel signal transmission in the backplane [23].

After understanding the physical phenomena and the related design details, we are aware of the main bottlenecks that limit the BW of backplane connectors in backplane systems. By applying an optimal combination of connector footprints with less parasitics, an improved impedance matching of via holes / stubs, together with a reduced coupling between different channels, the capacity of backplane connectors will be pushed higher by connector manufacturers and backplane system designers.

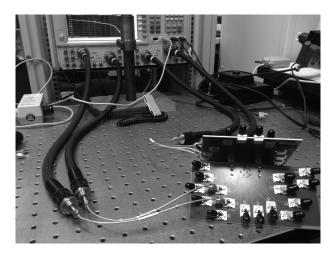

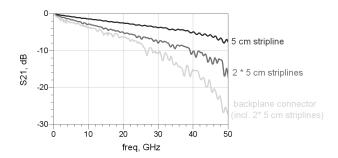

In our measurements, a test structure consisting of an improved backplane connector (provided by FCI) and two 5 cm, FX-2 differential striplines is evaluated. Figure 2.8 and Figure 2.9 illustrate the measurement setup and measurement results respectively.

Figure 2.8: Measurement setup of the FCI backplane connector

Figure 2.9: Frequency response of the FCI prototype backplane connector

# 2.2.4 Prototype backplane