Design and Technology of Ultra Thin Chip Packages for High-Frequency Applications up to 60 GHz

Ontwerp en technologie voor ultradunne chipverpakkingen voor hoogfrequentietoepassingen tot 60 GHz

Liang Wang

Promotoren: prof. dr. ir. J. Vanfleteren, dr. W. De Raedt, dr. ir. M. Cauwe Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Elektrotechniek

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. J. Van Campenhout Faculteit Ingenieurswetenschappen en Architectuur Academiejaar 2013 - 2014

ISBN 978-90-8578-654-2 NUR 959 Wettelijk depot: D/2013/10.500/87

Ghent University Faculty of Engineering and Acchitecture Centre for Microsystmes Technology

Promoters:

Prof. dr. ir. Jan Vanfleteren (Ghent University)Ir. Walter De Raedt (IMEC)Dr. ir. Maarten Cauwe (Ghent University)

Other Members of the Examination Committee: **Prof. dr. ir. Rik Van de Walle** (Ghent University), *Chairman*  **Prof. dr. ir. Johan Bauwelinck** (Ghent University), *Secretary*  **Prof. dr. ir. Bart Nauwelaers** (KU Leuven) **Ir. Philippe Kertesz** (Thales Airborne Systems)

# **Table of Contents**

| Chapter 1. General Introduction1                            |

|-------------------------------------------------------------|

| 1.1 Integrated circuit packaging1                           |

| 1.1.1 Requirements for IC packaging1                        |

| 1.1.2 History of IC packaging                               |

| 1.1.3 Basic Elements of Package Structure15                 |

| 1.2 System on Chip (SoC) and System in Package (SiP)16      |

| 1.3 IC Packaging for RF Application17                       |

| 1.4 Ultra Thin Chip Package (UTCP)17                        |

| 1.5 Thesis Content Overview                                 |

| Scientific Contributions in the PhD Period                  |

| References                                                  |

|                                                             |

| Chapter 2. UTCP Technology Using Photosensitive Polyimide27 |

| 2.1 Introduction                                            |

| 2.2 Process Flow                                            |

| 2.3 Test Design                                             |

| 2.4 Fabrication Process And Optimization                    |

| 2.4.1 Substrate Preparation                                 |

| 2.4.2 Chip Placement                                        |

| 2.4.3 Via Formation                                         |

|                                                             |

| 2.4 Fabrication Process And Optimization     |    |

|----------------------------------------------|----|

| 2.4.1 Substrate Preparation                  | 32 |

| 2.4.2 Chip Placement                         | 34 |

| 2.4.3 Via Formation                          | 35 |

| 2.4.4 Metallization and Circuit Interconnect | 41 |

| 2.4.5 Package Release                        | 43 |

| 2.5 UTCP Characterization                    | 44 |

| 2.5.1 Electrical Measurement                 | 44 |

| 2.5.2 Bending Test                           | 46 |

| 2.5.3 Reliability Test                       | 47 |

| 2.6 Conclusion                               | 49 |

|                                              |    |

| References                                                                        |                                              |

|-----------------------------------------------------------------------------------|----------------------------------------------|

| Chapter 3. Self Aligned Flat UTCP                                                 |                                              |

| 3.1 Introduction                                                                  |                                              |

| 3.2 Process Flow                                                                  |                                              |

| 3.3 Test Die and Design                                                           |                                              |

| 3.4 Fabrication Process and Optimization                                          |                                              |

| 3.5 Characterization                                                              |                                              |

| 3.5.1 Electrical Measurements                                                     |                                              |

| 3.5.2 Reliability Test                                                            |                                              |

| 3.6 Conclusion                                                                    |                                              |

| References                                                                        |                                              |

|                                                                                   |                                              |

|                                                                                   |                                              |

| Chapter 4. Characterization of Thin Film Dielectric Material                      | 71                                           |

| Chapter 4. Characterization of Thin Film Dielectric Material<br>4.1 Introduction  |                                              |

|                                                                                   | 71                                           |

| 4.1 Introduction                                                                  | 71<br>72                                     |

| <ul><li>4.1 Introduction</li><li>4.2 Experiment</li></ul>                         | 71<br>72<br>74                               |

| <ul><li>4.1 Introduction</li><li>4.2 Experiment</li><li>4.3 Methodology</li></ul> | 71<br>72<br>74<br>76                         |

| <ul> <li>4.1 Introduction</li></ul>                                               | 71<br>72<br>74<br>76<br>80                   |

| <ul> <li>4.1 Introduction</li></ul>                                               | 71<br>72<br>74<br>76<br>80<br>81             |

| <ul> <li>4.1 Introduction</li></ul>                                               | 71<br>72<br>74<br>76<br>80<br>81<br>82       |

| <ul> <li>4.1 Introduction</li></ul>                                               | 71<br>72<br>74<br>76<br>80<br>81<br>82<br>83 |

| <ul> <li>4.1 Introduction</li></ul>                                               | 71<br>72<br>74<br>76<br>                     |

| Chapter 6. Embedded Passive Compoments | 113 |

|----------------------------------------|-----|

| 6.1 Introduction                       | 113 |

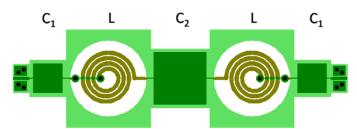

| 6.2 Process Description                | 114 |

| 6.3 Characterization and Analysis      | 117 |

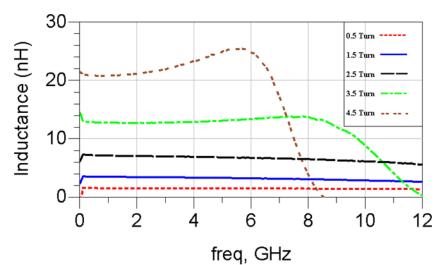

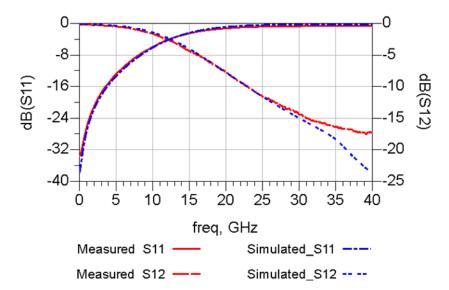

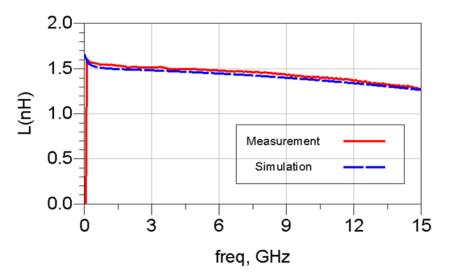

| 6.3.1 Spiral Inductors                 | 118 |

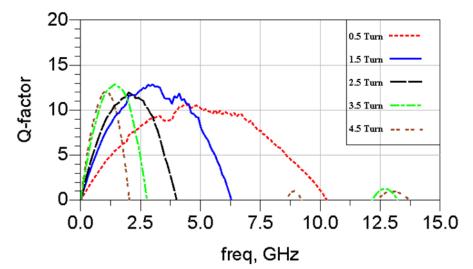

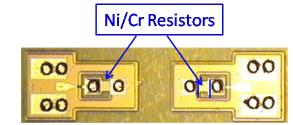

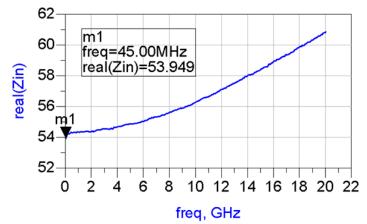

| 6.3.2 Resistors                        | 120 |

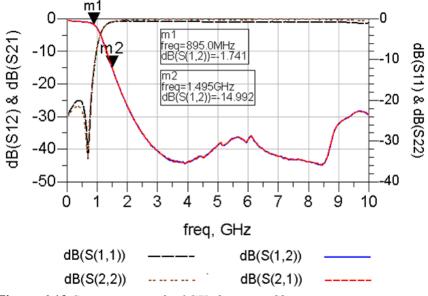

| 6.3.3 Low Pass filter                  | 121 |

| 6.4 Electromagnetic Simulation         | 123 |

| 6.5 Conclusion                         | 124 |

| References                             |     |

| Chapter 7 Conclusion and Outlook       | 127 |

| Chapter 7. Conclusion and Outlook |  |

|-----------------------------------|--|

| 7.1 Main Achievements             |  |

| 7.2 Future work                   |  |

-IV-

### **Summary**

In recent years, the demand for communication bandwidth has been growing rapidly. In order to have a higher bandwidth, the operating frequency needs to be increased proportionally. The current research focuses on developing a communication system working at 60 GHz, which is appealing as the next generation wireless standard. One of the main challenges in developing the 60 GHz system is how to package the RF CMOS chips with high efficiency and low cost. This is not an easy task can be accomplished using existing package technologies, such as advanced wire bonding or flip chip. Although the wire bonding technique can achieve a fairly small pitch connection, its long bonding wires also introduce excessive parasitic inductance, which can not be well compensated. The parasitic factors require excessive power and degrade the performance achieved at chip level. The flip chip assembly, on the other hand, can improve the high frequency performance of the mounted package. However, flip chip puts rather strict requirements on the substrate where the chip is mounted on. First the substrate has to be rigid and second the size and pitch of the substrate has to match dimension of the bond pads on the chip. This makes it difficult to flip chip package advanced RF chip using standard low cost board.

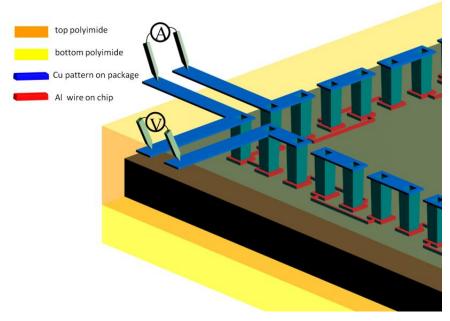

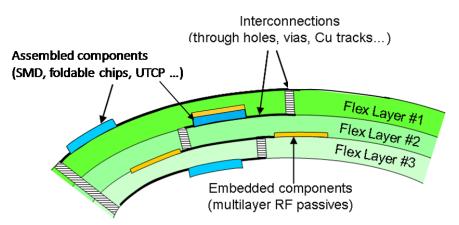

In order to overcome the current limitation of conventional packaging technologies, CMST has developed a unique concept for packaging ultrathin chips: the Ultra Thin Chip Package (UTCP). In this technology, silicon chips with thickness below 30  $\mu$ m can be embedded inside organic resin, composing of cured spin-coated polyimide layers. The interconnection to the chip is realized by forming micro-via through the coated top polyimide film to chip bond pads. The micro-via based connection is able to meet the fine pitch requirement for the chip connection. Moreover, a fan out design on the package level can bridge the pitch mismatch between the chip and coarse circuit board. The UTCP is able to be used independently or serves as an interposer, which can be further embedded inside PCB or FCB (flexible circuit board) and replace the needs for directly embedding of bare die. Furthermore, the known good die (KGD) problem is solved, because the functionality of UTCP can be easily tested before embedding it in the main board.

So far UTCP is designed and fabricated as a single chip package for low frequency application (<5 GHz) only. The aim of this PhD is to exploit the use of UTCP to go beyond the current limitation and develop design strategies for embedded modules at radio frequency up to 60 GHz. Such work opens a door for ultra-miniaturized high speed system and gives a cost effective powerful hybrid solution for the next generation RF packaging.

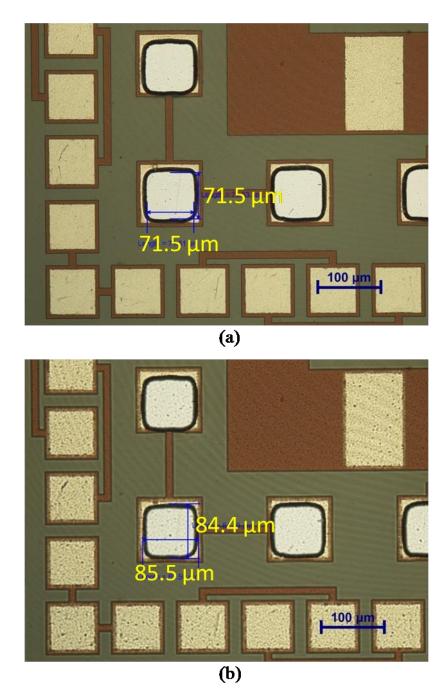

According to the main objective and the scope of this PhD work, the fabrication process of the UTCP technology is first optimized to make it more suitable for high volume manufacturing and high speed transfer. All individual process steps of UTCP technology are discussed in detail in Chapter 2. The original dielectric material PI-2611 is replaced by a photosensitive polyimide HD-4110. By using the new material, the generation of microvias can be achieved by generic photolithography process, which is more reliable than laser ablation and more cost-effective compared to dry etching based microvia generation. An easy release of the UTCP from the rigid carrier is obtained by introducing an evaporated potassium chloride (KCl) film before the deposition of base polyimide layer. The result is a very thin and flexible chip package with a total thickness around 50  $\mu$ m.

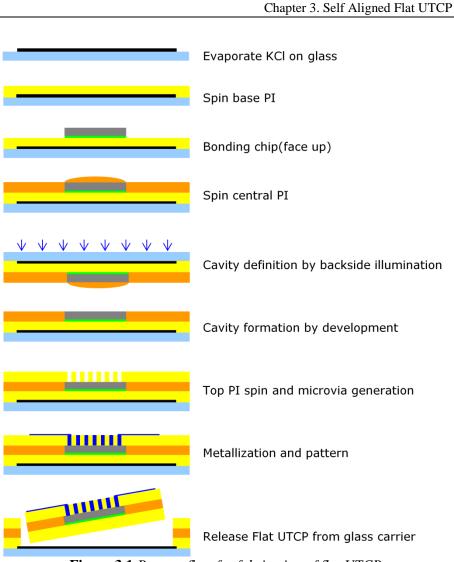

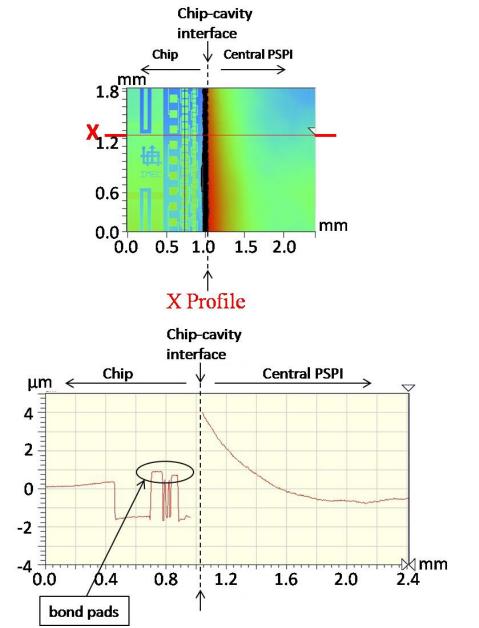

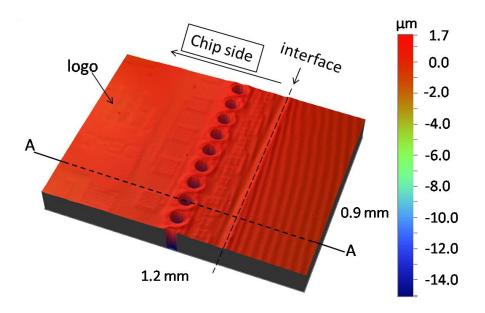

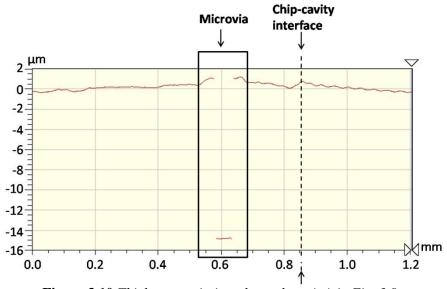

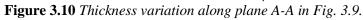

Another further improvement of UTCP fabrication is presented in Chapter 3. Flat package topography is a key to build up multilayer structure on the UTCP package. An innovative self-alignment lithography step is introduced to make a cavity in dielectric for chip thickness compensation by using the chip itself as a photo-mask. The realized flat UTCP does not increase its total thickness and still can be released from the carrier. The feasibility of the updated fabrication process is verified by DC electrical test and several reliability tests. Desired flexibility and reliability is observed.

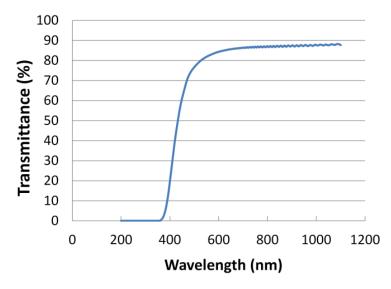

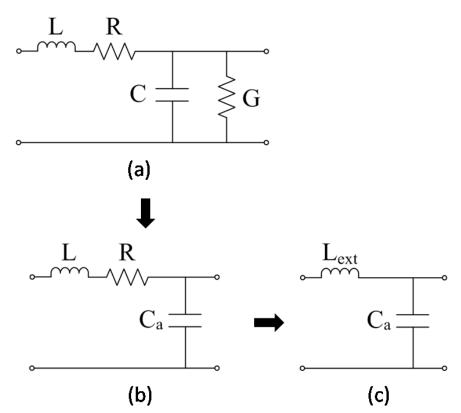

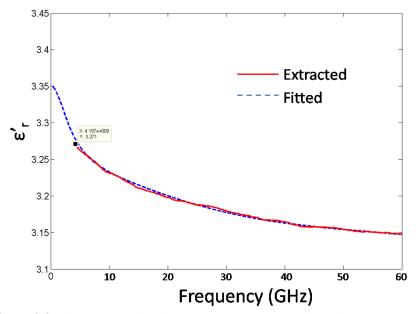

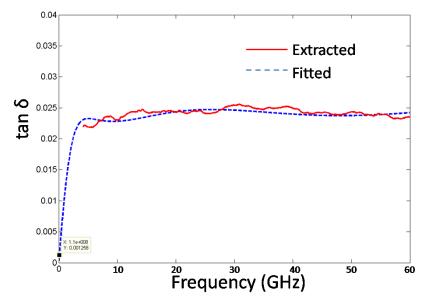

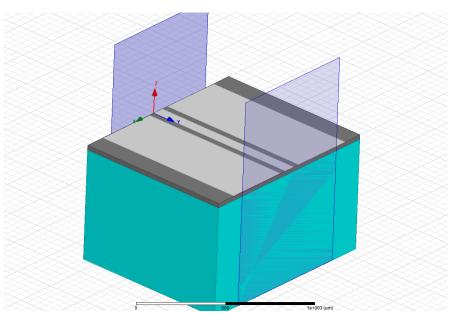

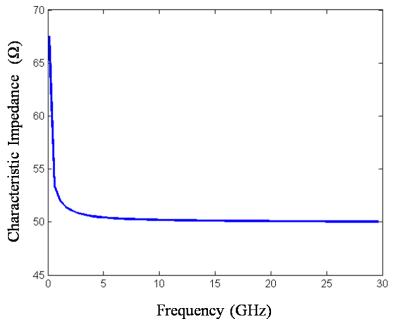

Chapter 4 presents high frequency material characterization of HD-4110, which is used in UTCP fabrication. A 3D full wave simulation is employed for modeling and parameter extraction. Its dielectric constant and loss tangent factor is extracted from 10 MHz up to 60 GHz. The extracted material property is well fitted by a rational dielectric model, which satisfies the causality constraints.

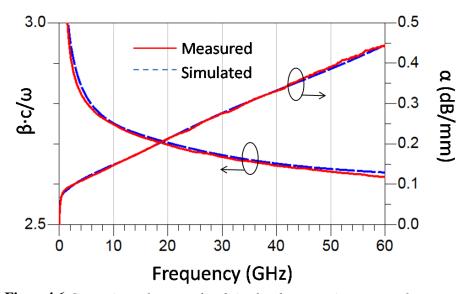

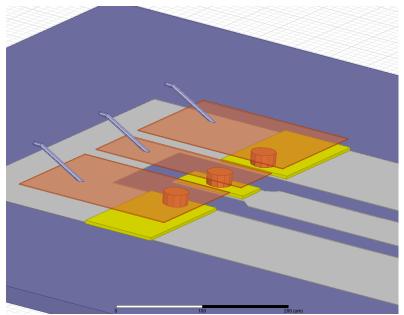

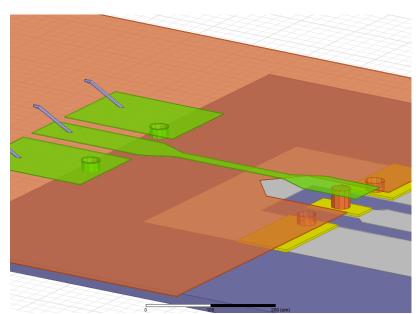

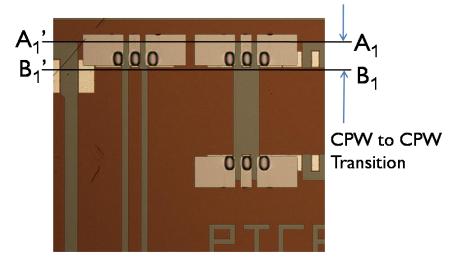

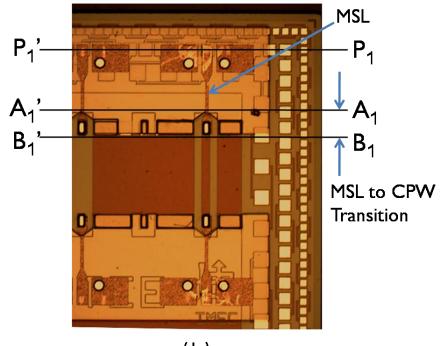

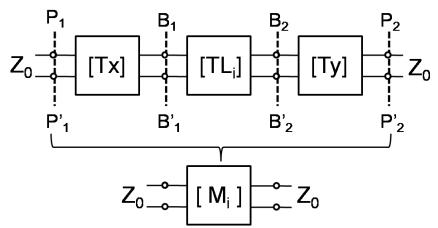

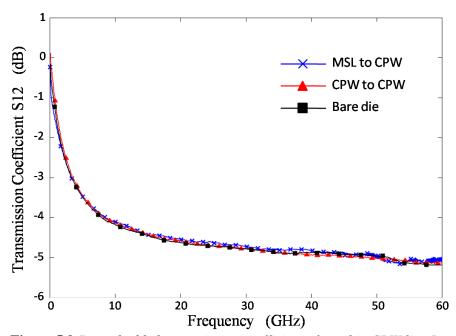

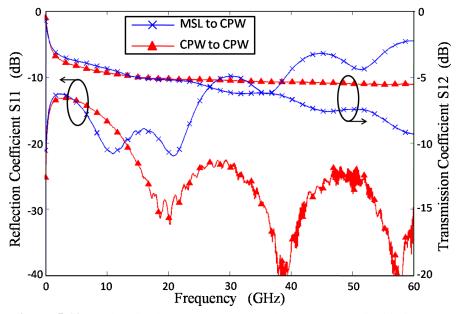

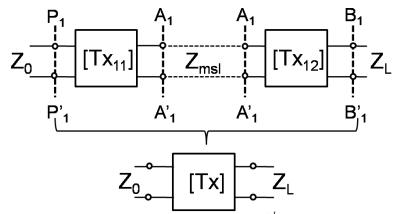

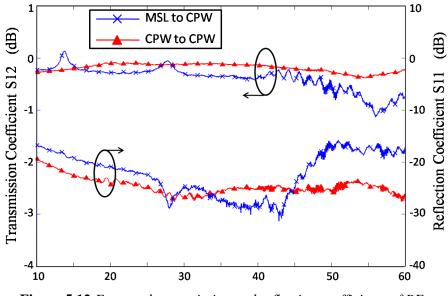

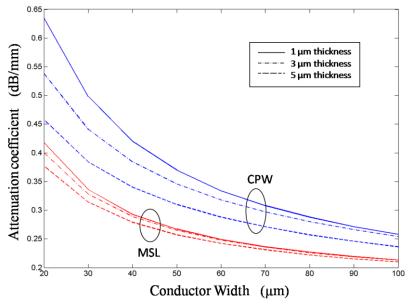

Two types of transition structure were fabricated for high frequency connection of UTCP embedded chips. Their design, fabrication and characterization are discussed in Chapter 5. One type of connection is CPW to CPW transition and the other type is MSL to CPW transition. The transmission and reflection coefficient is extracted for both transition structures from 10 GHz up to 60 GHz. A good impedance matching and small insertion loss can be achieved by both transition structures. Compared with the results of the other advanced package methods from literatures, the UTCP package shows one of the best performances.

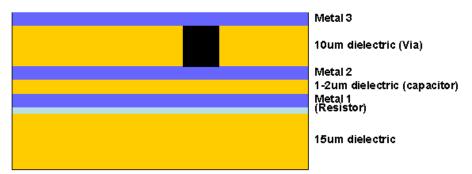

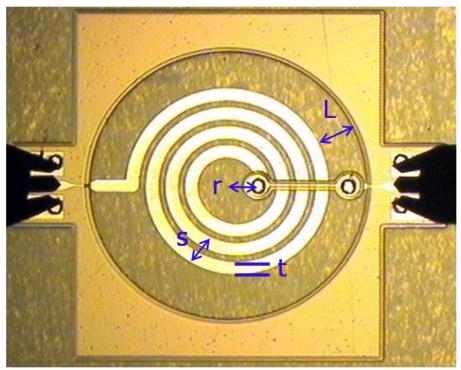

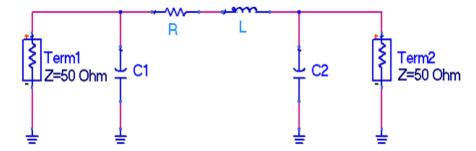

The thin film deposition technique for the UTCP fabrication can also be applied to produce thin film passive devices. In the frame of EU SHIFT project, off-chip RF passives are produced based on thin film technology. Finally, Chapter 6 briefly describes the process flow and shows measurement results of the realized passive elements including resistor, spiral inductors and a low pass filter. Since the applied fabrication technique is compatible with the UTCP processing, the passive elements and the UTCP can be integrated together to work as a complete system.

## Samenvatting

De vraag naar bandbreedte voor communicatietoepassingen is recent sterk gestegen. De toename in bandbreedte wordt veelal gerealiseerd door de werkingsfrequentie op te drijven. Het huidige onderzoek legt zich toe op het ontwikkelen van een communicatiesysteem dat werktbij 60 GHz, in overeenstemming met de toekomstige standard voor draadloze gegevensoverdracht. Een van de belangrijkste uitdagingen in de ontwikkeling van een dergelijk hoogfrequent systeem is een performante en betaalbare oplossing voor het verpakken van hoogfrequente CMOS chips. De huidige technieken voor het verpakken van chips, in het bijzonder draaden flip-chip verbindingen, hebben elk hun nadelen voor hoogfrequente toepassingen. Draadverbindingen zijn compatibel met de geringe afstand tussen de bondpaden op de chip, maar de lange draadverbindingen hebben een grote parasitaire inductantie, wat nefast is voor transmissie van hoogfrequent signalen. Het gebruik van flip-chip assemblage kan deze problemen verhelpen, maar heeft dan weer het nadeel dat het zware eisen stelt aan het substraat waarop de chip gemonteerd wordt. Dit substraat dient niet alleen rigide te zijn, maar de grootte van de structuren op het substraat moet overeenkomen met de afstand tussen de bondpaden op de chip. Gezien hoogfrequente chips gebruik maken van zeer geringe afstanden tussen de bondpaden, resulteert dit in zeer dure substraten en dus een hoge totale kost.

De hogervermelde tekortkomingen van de huidige verpakkingstechnieken kunnen vermeden worden door gebruik te maken van de ultradunne chip verpakking UTCP, welke ontwikkeld werd binnen CMST. Deze technologie maakt gebruik van silicium chips met een dikte van minder dan 30  $\mu$ m, welke ingebed worden in lagen van uitgehard polyimide. De verbinding met de chip wordt gerealiseerd aan de hand van microvias doorheen de bovenste polyimide laag tot op de bondpaden van de chip. Deze op microvias gebaseerd verbinding is compatibel met de geringe afstand tussen de bondpaden op de chip. Daarenboven laat deze technologie toe om het verschil in grootte van de structuren op de chip t.o.v. het substraat te overbruggen. De ultradunne chip verpakking kan alleenstaand gebruikt worden of als tussenoplossingen ingebed worden in een al-dan-niet flexibele gedrukte schakeling. Door het uitspreiden van de contactpaden kan de chip voor het inbedden getest worden, wat niet mogelijk is bij naakte chips. Tot nu toe werd de ultradunne chip verpakking steeds ontworpen en gerealiseerd voor laagfrequente toepassingen (<5 GHz). Het doel van dit doctoraatsonderzoek is om de prestaties van de ultradunne chip verpakkingen voor frequenties tot 60 GHz te evalueren. Hiertoe zullen specifieke ontwerpregels opgesteld worden die het mogelijk maken om sterk geminiaturiseerde systemen te bouwen voor de hoogfrequente toepassingen van de volgende generatie.

Teneinde de doelstellingen van dit doctoraatswerk te kunnen bereiken, werd het fabricageproces voor ultradunne chip verpakkingen herbekeken met het oog op productie in grote volumes. Alle processtappen voor het realiseren van de ultradunne chip verpakking worden in detail beschreven in hoofdstuk 2. Het diëlektrische materiaal PI-2611, wat oorspronkelijk gebruikt werd voor het realiseren van ultradunne chip verpakkingen, werd vervangen door het fotogevoelige polyimide HD-4110. Dankzij deze wijziging kunnen de microvias verwezenlijkt worden met behulp van een foto-lithografisch proces, welke betrouwbaarder is dan laser boren en goedkoper dan het gebruik van droge etstechnieken. Het losmaken van de ultradunne chip verpakking van de rigide drager wordt vergemakkelijkt door het opdampen van een kalium chloride (KCl) film voor het aanbrengen van de eerste polyimide laag.

Een bijkomende verbetering in het fabricageproces wordt beschreven in hoofdstuk 3. Een vlakke topografie van de verpakking is essentieel om meerlaagse structuren binnen de ultradunne chip verpakking te realiseren. Hiertoe werd een innovatie lithografie stap geïntroduceerd waarbij een caviteit rond de chip gerealiseerd wordt in het fotogevoelige polyimide. De totale dikte van de afgevlakte ultradunne chip verpakking blijft echter gelijk. De haalbaarheid en de betrouwbaarheid van het vernieuwde fabricageproces worden aangetoond aan de hand van elektrische testen. De gewenste betrouwbaarheid en flexibiliteit werden hierbij behaald.

Hoofdstuk 4 beschrijft de hoogfrequente materiaalkarakterisering van HD-4110. Een driedimensionale golfsimulatie wordt gebruikt voor het bepalen van de parameters. De diëlektrische constante en de verlieshoek warden berekend voor een frequentiebereik van 10 MHz tot 60 GHz. De gevonden waarden komen goed overeen met het opgestelde fysische model, welke voldoet aan de vereisten van causaliteit. Twee types overgangen tussen de chip en de ultradunne verpakking warden ontworpen en gerealiseerd. Het ontwerp, de fabricage en de karakterisering worden beschreven in hoofdstuk 5. Het eerste type is een overgang van vlakke golfgeleider naar vlakke golfgeleider. Het andere type maakt gebruik van een tussenliggende microstrip golfgeleider. De transmissie- en reflectiecoëfficiënt werd voor beide overgangen bepaald in een bereik van 10GHz tot 60 GHz. Een goede aanpassing van de impedantie en lage verliezen kunnen met beide overgangen gerealiseerd worden. In vergelijking met overgangen gebruikt in andere hoogfrequent verpakkingstechnieken, presteert de ultradunne chip verpakking bovenmaats.

De dunne-filmtechnieken die gebruikt worden voor het realiseren van de verbindingen in de ultradunne chip verpakking kunnen eveneens toegepast worden voor het fabriceren van passieve elementen. In het kader van het Europees project SHIFT werden dergelijke passieve componenten gerealiseerd. Hoofdstuk 6 beschrijft de bijhorende processtappen en bespreekt de meetresultaten van de gerealiseerde weerstanden, spoelen en laagdoorlaatfilters. Gezien de toegepaste technologieën volledig compatible zijn met de ultradunne chip verpakking kunnen beide technieken op eenvoudige manier gecombineerd worden.

# List of Acronyms

| Acronym | Description                         |

|---------|-------------------------------------|

|         |                                     |

| ACA     | Anisotropic Conductive Adhesive     |

| BCB     | Benzocyclobutene                    |

| BEOL    | Back End of Line                    |

| BGA     | Ball grid array                     |

| BBUL    | Bumpless Build-Up Layer             |

| CiP     | Chip in Polymer                     |

| COB     | Chip-On-Board                       |

| COF     | Chip-On-Flex                        |

| CSP     | Chip Scale Package                  |

| CTE     | Coefficient of Thermal Expansion    |

| CPW     | Coplanar Waveguide                  |

| DIP     | Dual In-line Package                |

| EBGA    | Enhanced Ball Grid Array            |

| ECG     | Electrocardiogram                   |

| EEG     | Electroencephalogram                |

| EPC     | Embedding Passive Component         |

| ENIG    | Electroless Nickel / Immersion Gold |

| EMG     | Electromyogram                      |

| FBGA    | Fine Pitch Ball Grid Array          |

| FCB     | Flexible Circuit Board              |

| FCOB    | Flip-Chip On Board                  |

| GSG     | Ground Signal Ground                |

| IC      | Integrated Circuit                  |

| I/O     | Input / Output                      |

| n m   |                               |

|-------|-------------------------------|

| IMB   | Integrated Module Board       |

| ICA   | Isotropic Conductive Adhesive |

| KGD   | Known Good Die                |

| LRM   | Line-Reflection-Match         |

| LCP   | Liquid Crystal Polymer        |

| MIM   | Metal-Insulator-Metal         |

| MSL   | Microstrip Line               |

| MCM   | Multi-chip-module             |

| PCB   | Printed Circuit Board         |

| PSPI  | Photosensitive Polyimide      |

| PVD   | Physical Vapor Deposition     |

| PI    | Polyimide                     |

| PoP   | Package on Package            |

| QFP   | Quad flat package             |

| RIE   | Reactive Ion Etching          |

| SiP   | System in Package             |

| SMD   | Surface Mount Technology      |

| SoC   | System on Chip                |

| SOLT  | Short-Open-Line-Thru          |

| TAB   | Tape Automated Bond           |

| TFMSL | Thin Film Microstrip Line     |

| TRL   | Thru–Reflection-Line          |

| TLine | Transmission line             |

| TSV   | Through Silicon Via           |

| UBM   | Under Bump Metallization      |

| UTCP  | Ultra Thin Chip Package       |

| VNA   | Vector Network Analyzer       |

| WLP   | Wafer Level Packaging         |

-XII-

# CHAPTER ]

# **General Introduction**

#### 1.1 Integrated circuit packaging

In electronic manufacturing, integrated circuit (IC) packaging is the final stage of device fabrication [1]. The main purpose of the IC packaging is to provide electrical connection between the chip and the external circuitry on the system board. Furthermore, the package should help for heat removal from on-chip transistors to the ambient air, and also protect the chip against environment contamination, such as dirt, finger prints, and moisture ingress. After the packaging step, device will be submitted to a functional test. So, in summary, IC packaging bridges the gap between the semiconductor chip manufacturing and the final product application [2], [3].

#### 1.1.1 Requirements for IC packaging

The trend in semiconductor manufactorinng has significant impact on the evolution of IC packaging and interconnects [4-5]. According to Moores' law, the number of transistors on an integrated circuit will be doubled every 18 months [6]. This trend is first observed in 1965, and it is still valid today and expected to continue during the next decade. As a result of the Moores'

law, in the past century semiconductor chip technology has been improved continuesly in the following aspects [4],[7]:

1) The transistor dimensions are scaled down from sub-micrometer to around a few tens of nanometers. The current state-of-art lithography tool enables the minimum feature size in chip manufacturing to shrink from  $0.8\mu$ m in 1990s to 22nm and even below;

2) Along with the increasing transistor density, more and more functionality can be integrated on a single chip. In the meanwhile, the number of chip input/output (I/O) counts needs to increase at the same pace to enable complex operations. For high end devices, the I/O counts increased from below 100 to over a few thousands by a rate of 50% (x1.5) every 18 months.

3) Although the supply voltage is reduced in every technology generation, the power density of the chip is increased almost exponentially with time from around 1 W/cm<sup>2</sup> to above 50 W/cm<sup>2</sup>.

4) For the sake of faster computing speed, the operating clock frequency is also increased. In 1971, the first commercially available microprocessor Intel 4004 only works at 108 kHz [8], and the maximum record in 2011 has reached 5.2 GHz, which is 5000 times higher than the first one.

In the above discussed trend, the advances in semiconductor chips create great challenges to the packaging technology and reform the packaging method to adapt for new requirements in the following aspects:

1) The increasing I/O chip pin counts means that the same number of interconnect channels should be realized on package level. Assuming the chip area remains the same, which is normally the case, if more functionality is integrated, a tighter interconnect pitch is required. And correspondingly, the circuit on the package board should be more dense and fine.

2) When the dissipated power density becomes higher, the generated heat is also higher. If the heat cannot quickly spread to the ambient environment, it will be trapped around the chip, which may damage the chip functionality and cause some reliability problems. Thus packaging needs to improve interface materials, in order to obtain a better thermal conductivity. Sometimes, more complex cooling systems should be constructed in a package for better heat dissipation. 3) According to the microwave scaling rule, when the operating frequency becomes higher, all circuit dimensions should be scaled down proportionally to obtain the same performance. Therefore, the increasing chip clock rate requires the package circuit to have finer pitch and higher resolution. Low-k dielectric with low dielectric loss is preferred to reduce propagation delay time and signal power attenuation.

4) Apart from requirements driven by IC advances, one more need for packaging is miniaturization. For portable and mobile devices, it is important to control the weight and volume of the final product.

#### 1.1.2 History of IC packaging

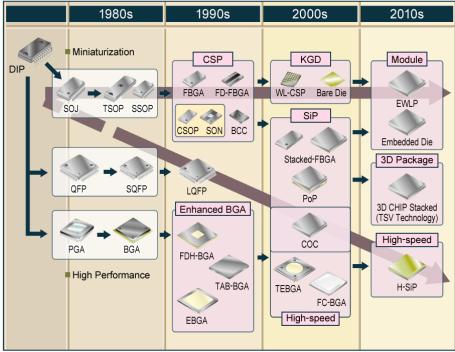

The requirements for IC packaging listed above are reflected on the package structures in its historic evolution. Fig. 1.1 shows different types of package during the past decades.

Figure 1.1 The evolution of IC packaging[9].

In the following context, we will briefly review some important packaging types, which are the most commonly used ones in the past and at present. The sequence of the description is mainly in chronological order starting from the 1970s up to now in steps of ten years.

1970s

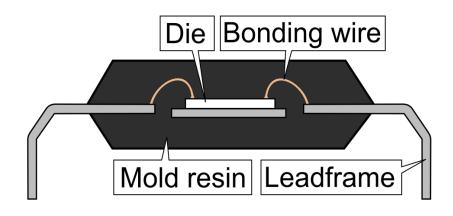

Dual in-line Package (DIP) is the first to be discussed. DIP is a kind of through hole mounted package which was widely used in 1970s [10]. The above mentioned first commercial available microprocessor Intel 4004 was packaged in the standard DIP packaging [8]. As shown in Fig. 1.2, DIP packages are made of opaque molded plastic resin with plated lead frames. Inside the package, the IC chip is cemented in the center of a rectangular chamber and is connected to the outside through the lead frames. The package can be mounted by either through hole soldering to printed circuit board or inserting in sockets. DIP is a low cost and easy handling package with very robust attachment of lead in hole. However, the interconnect pitch is limited to about 2.5 mm and the number of I/O is limited to numbers below 64. Consequently, the circuit density on PCB board is also limited. The operating frequency of DIP is normally from 2 to 160 MHz.

Figure 1.2 Schematic cross section of DIP [11].

1980s

In order to avoid the cost of drilling holes in the PCB and to obtain a higher interconnect density, through hole technology was mostly replaced by surface mount technology (SMT) by the end of 1980s [12]. Two

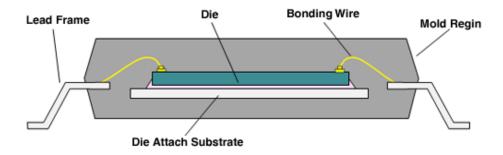

representative types of SMT are quad flat package (QFP) [13] and the later invented ball grid array (BGA) package [14].

Although components in a QFP were first introduced in 1970s and already been used in Japanese consumer electronics since then, it became popular in the world until late eighties. QFP component is similar to DIP, which has four sides with leads extending from the component body to all four directions. But instead of through hole lead as DIP, QFP uses "gull wing" leads, as shown in Fig. 1.3, which can be mounted directly onto the surface of PCBs.

Figure 1.3 Schematic cross section of QFP [15].

A QFP lead frame is normally made of iron/nickel alloy or copper alloy to guarantee good thermal and electrical performance. Because of its surface mount capability, compared to DIP component, QFP can achieve tighter lead pitch and higher I/O count. Different versions of QFP offer I/O counts ranging from 32 to 304 pins with a lead pitch from 0.4 to 1 mm. Therefore, QFP can allow increased circuit density on PCB.

However, QFP has connections only around the periphery of the package. In order to increase the number of pins, the interconnect pitch has to be reduced. This tight lead spacing may cause solder short problems and put higher demands on the soldering process with more advanced alignment of components. As a result, when tighter pitches are needed, the yield of QFP is relatively low and the overall cost becomes high. The later BGA package allows for high pin counts with similar package size, as well as alleviates the problem caused by close lead spacing.

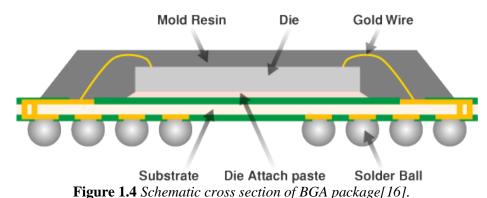

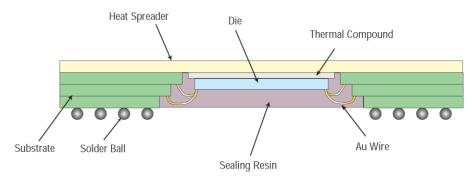

BGA package utilizes laminated or ceramic multilayer interconnect substrate instead of metal lead frame. This multilayer interconnect substrate is also called as "interposer" of the package. The structure of BGA package is shown in Fig. 1.4. In a BGA package, the chip is mounted on the multilayer substrate and interconnected through bonding wire. The area array connections from the package "interposer" to the PCB are realized using solder balls. These solder sphere can be placed manually or by automatic machine and held under the interposer with tacky flux until soldering begins. The BGA package is then placed on PCB contact pads, which has the same pattern of ball grid array. Normally, the soldering is carried out by heating the assembly in a reflow oven to melt the solder ball. Before solder balls cools down and hardens, surface tension aligns the package on PCB at correct separation distance.

BGA package can alleviate the problem of producing a miniature IC package with hundreds of I/O counts. The ball pitch is normally of 1.00, 1.27 or 1.5mm, and the number of I/O can reach to 420. Besides the advantage of higher pin counts, the distance of solder ball connection between the package and PCB is shorter than leaded connection, which lowers the parasitic inductance and therefore minimizes the signal distortions in high speed application.

All package structures have their drawbacks, and BGA package is not an exception. There are mainly two problems in BGA package [17]. First, the thermal stress between the package interposer and PCB is accumulated at the solder joint, and becomes a reliability issue. So it's common to select a plastic material which more closely matches the thermal characteristic of PCB. Second problem is that it is hard to inspect the balls and joints for soldering defects, as the package is soldered down on the PCB. To overcome the second problem, various machines, were developed to look underneath the soldered package, such as x-ray machine, industrial CT scanning machine, as well as some special microscopes.

#### 1990s

In the early 1990s, it becomes clear that the evolution of IC packaging proceeds toward two directions. One direction is developed for high-end electronic device, which has very high pin counts and high power consumption. The package for high-end devices needs to allocate more connect channel and has better thermal management. A couple of methods were proposed to meet the new requirements. Enhanced ball grid array (EBGA) is one of these methods, which has been widely used [18]. The other direction is to make miniature package for portable electronics. As the fast growing of mobile electronic market, there is a huge demand to make mobile devices smaller and lighter. Then it is necessary to shrink the size of IC packaging. The concept of chip scale package (CSP) was proposed and developed for portable devices [19]. A typical CSP is fine pitch ball grid array (FBGA) package. Next, we will describe the structures of EBGA and FBGA, and see what it the improvement in these two types of packaging.

EBGA is descended from traditional plastic BGA technology. With thermally and electrically enhancement, EBGA is capable to package chips for high-end devices. The configuration of an EBGA package is present in Fig. 1.5. As a descendant of BGA, connection between the package and the main board is still using solder balls. Inside EBGA, the chip is attached on a heat spreader in a face down cavity. The die attach material is a special compound with better thermal conductivity. So the heat generated from chip can quickly transfer to the spreader.

Figure 1.5 Schematic cross section of a EBGA package [18].

The connection of the chip to package is realized by wire bonding. Unlike normal BGA, two-tier substrate is offered in the EBGA for the wire bonding.

So, more I/O connections can be realized around the chip perimeter. Furthermore, the separation of power and ground planes in two-tie substrate can make electrical performance better. Normally, EBGA package can has total I/O counts up to 700.

Besides the direction for high-end electronics, CSP is the other package progress direction targeting for portable electronics. The definition of CSP is a single die surface mounted package with an area of no more than 1.2 times that of the original die area. The concept of CSP only put requirement on the package size without specific details in package structure. Various types of CSP were proposed, and flip chip CSP (fcCSP) is one of the main CSP solutions. The fcCSP is a miniature version of standard BGA, whose configuration is similar to the one shown in Fig. 1.4 except for the replacement of wire bonding by flip. However, fcCSP has a chip scale size, with lower profile and less weight than standard BGA. More importantly, fcCSP offers a finer solder ball pitch, ranging from 0.4 mm to 1 mm. The number of I/O is normally between 40 and 460. But the number of connection is not a stringent requirement for portable devices.

#### 2000s

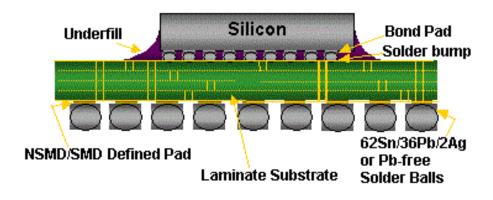

During the 21th century, package technology continues to develop towards two directions for high-end devices and portable devices. More advanced package methods were invented, such as wafer level packaging (WLP) [20]. The flip chip ball grid array (FCBGA) is another type of package, which already existed in 1990s and becomes popular in 21th century [21].

WLP is a true chip scale package technology, offering the smallest possible footprint of the same size of the die. The low profile and improved signal characteristic make WLP ideal for portable electronics. In addition, WLP has the ability to integrate package process in wafer fab, which provides a streamline from the silicon start to customer shipment. The WLP cross section and a close-up backside image are presented in Fig. 1.6.

As can be seen, WLP does not use an interposer, and the solder balls are realized on the chip by wafer level processing. The solder ball pad is routed within the chip outline from the chip perimeter contact pad, which is so called a "fan-in" design. The ball pitch can be as small as 0.3 mm. But, as the WLP is directly mounted on PCB, ball pitch larger than 0.4 mm is necessary to ensure high yield and reliability. Another limitation of WLP is

<image><text><text>

the number of I/O count. Since the package area and ball pitch are confined, the total number of I/O count is normally no more than 100.

**Figure 1.6** *WLP* (*a*) *Schematic cross section* [18] *and* (*b*) *backside photography* [22].

In parallel with the development for miniature package, FCBGA package is a technology designed for devices requiring extremely high pin count and high performance. In the past, the chip connection to the package interposer was realized by wire bonding. For the sake of higher pin count, which is the same reason drive lead frame package to BGA, the chip connection to the interposer can move from wire bonding to area array bonding, primarily by flip chip solder bump. The configuration of FCBGA is shown in Fig. 1.7.

Figure 1.7 Schematic cross section of FCBGA [23].

First, the solder bumps are deposited on the silicon chip. The bumped chip is then flipped over and placed face down onto the interposer. The bump pitch is 0.25 or 0.35 mm, which is much smaller than the ball pitch for package level connection. Due to the small bump pitch, the interposer material should provide equal pattern resolution, and reliable attachment. Co-fired ceramic was first used as interposer material because its coefficient of thermal expansion (CTE) is very close to that of silicon. Later, some high resolution organic substrates are also used to lower the total cost. But compared with ceramic substrate, the reliability of flip chip bonding on the organic substrates is still an issue needs further improvement [24]. Since the traditional wire bonding is replaced by flip chip bonding, the maximum I/O count could increase effectively up to more than 2000. Another benefit is better electrical performance, as the short connection length of flip chip bonding causes less parasitic inductance and resistance.

#### 2010s-present

Some new technologies are emerging in the 21th century and their mass production was gradually launched around 2010s. These emerging technologies are the current state of the art and some of them are still the focus of research. Embedded chip package [25] and 3-dimension (3D)packaging [26], [27] are two representatives of the new emerging technologies.

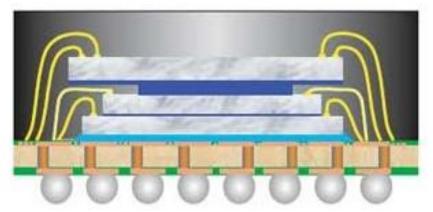

3D packaging exploits the third or Z height dimension to provide a compact miniature package solution for high end electronics. There are basically two approaches in 3D packaging, which are known as stacked packages and stacked dies. It's obvious that the vertical stack of elements is a highly space save configuration, which results in increasing functionality, density and performance of the final product. 3D packaging is very useful for high tech electronics, such as smart phone, tablet computer, ultrabook, etc.

Die Stacking is a process of mounting multiple chips on top of each other to form a single electronic package. There are numerous ways developed to make connection between the stacked chips. So far wire bonding is still the predominant 3D interconnect technology. But sometimes a hybrid of flip chip and wire bonding has been applied to improve warpage control and package integrity. Because multiple die were stacked together, it's important to limit the total pile height. Otherwise, the wire bonding length for top chips is too far to reach. So the chips are normally thinned down to about 30  $\mu$ m before they are mounted together. Fig. 1.8 is a schematic cross section for a traditional 3D package of three stacked die using wire bonding as interconnection. The high density bonding wires have ultra fine pitch of 60 $\mu$ m or even below. Using the thinned chips and fine pitch wire bonding, a stack of 24 chips was realized and demonstrated by Amkor.

Figure 1.8 Triple chip stacked cross section [28].

#### Chapter 1. General Introduction

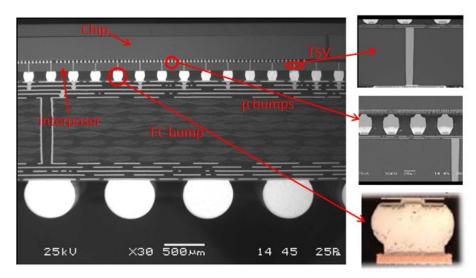

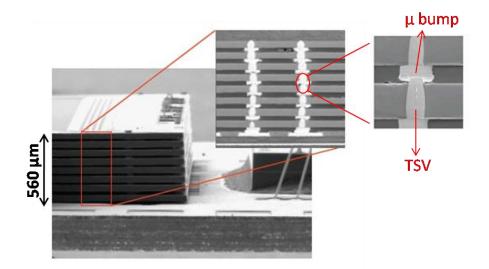

Combined with mirco bump of flip chip bonding, through silicon via (TSV) technology is another way for stacked die connection. 3D die stacking based on TSV and micro bumping holds the promise of the highest integration density and performance, and it is currently a very hot research topic in IC packaging. TSV is a vertical electrical connection passing completely through a silicon die. The use of TSV is first found in IBM's Silicon Carrier Packaging Technology, where multiple chips are side-by-side flip bonded on a silicon interposer containing TSVs to route the chips to the bottom package level connection, as shown in Fig. 1.9. At present, the thinned silicon chip itself contains TSVs and can be directly bonded to another thinned chip with micro bumps, as present in Fig. 1.10.

Figure 1.9 Stacked silicon on TSV based interposer [29].

Figure 1.10 Eight 2Gb NAND flash die stack. (Courtesy of Samsung Electronics Co., Ltd)

Although 3D die stacking is a very promising technology, it suffers from problems of reliability and yield optimization. Thermal mechanical management is a key challenge for 3D stacked die due to its high power density and lack of thermal dissipation. At present, a lot of analysis is carrying to improve the reliability. "Known good die" (KGD) is another issue related to package yield. Since multiple die are used in one package, one nonfunctional die can result in failure of the package and yield loss. So it's important to know if the chip is good before placing it in the stack. However, functionality test on chip level is difficult, especially for thinned chip with TSVs.

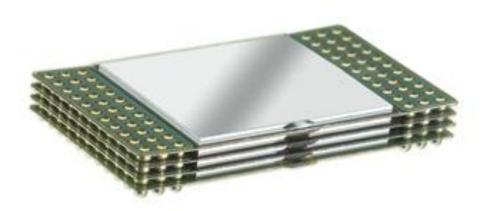

As an alternative to die stacking, another 3D technology is package on package (PoP), whose sub-unit is an individual chip package after processing and test. PoP has the similar ability of high density integration and board footprints saving. Compared with die stacking, PoP can easily test the functionality of its sub unit and only choose the "known good" package to use. Besides, PoP brings some flexibility in sub-unit selection and replacement. On the other hand, additional connection length is required for interoperating parts in PoP, which leads to longer propagation delay than stacked die. Numerous PoP architectures have been developed. Some renowned types include  $\mu$ Z–ball stacked package,  $\mu$ PILR flash and DRAM PoP (both from Tessera [30], [31]) and SMAFTI package (from NEC [32],

[33]). Fig. 1.11 depicts a realized 3D packaging using Tessera's  $\mu$ PILR technology.

**Figure 1.11** *Photography of*  $\mu$ *PILR*<sup>TM</sup> *PoP device* [31].

The last technology discussed here is embedded chip package. It's a new revolution for single die package to achieve the highest degree of miniaturization. The concept of embedded chip is first proposed as a continuation of WLP. Because WLP has limited surface area for solder ball arrangement, the chip can be embedded in a mold frame, which provides a "fan out" area. Then the concept is extended to integrate the bare dies directly inside PCB or other multilayer substrate, where passive components are incorporated on the top and bottom layers. A number of approaches for die embedding have been presented. One of the first was bare die assembly of chips on flex substrate, also known as Chip on Flex (COF) shown by General Electric [34]. Intel announced its Bumpless Build-Up Layer (BBUL) for their future microprocessors [35]. Helsinki University of Technology developed the so-called Integrated Module Board (IMB) technology, which was further industrialized by Imbera [36]. In the frame of European "Hiding Dies" project, the Chip in Polymer (CIP) is presented by joint institute of Fraunhofer IZM and the Technical University of Berlin [37].

All the above listed embedding methods use microvias on chip pad for electrical connection. The Chip embedded packaging can meet system requirements for signal frequencies in the order several GHz which could not be met by long bonding wires and interconnect path on a board. But it is obvious that the KGD issue is still needs to be solved. At IMEC-CMST, an ultra thin chip package (UTCP) technology was developed as a solution of the KGD problem [38]. UTCP serves as an interposer, which can be tested before embedding in the main board. The main content of this PhD work is development and optimization of the UTCP technology and the use of UTCP's in high frequency applications.

#### 1.1.3 Basic Elements of Package Structure

The last section reviewed some major types of IC packaging in historic evolution. Viewing from another perspective, we can examine an IC package by dividing its configuration into basic elements. Table 1.1 gives basic elements common to various package types and their existing approaches.

| Basic elements          | Approaches                                    |

|-------------------------|-----------------------------------------------|

| Electrical connection   | *Wire bond                                    |

| from chip to package    | *Micro bump                                   |

|                         | *Microvia                                     |

|                         | *Flip chip solder bump                        |

|                         | *Tape automated bond (TAB) [39]               |

|                         | *Conductive adhesives: (ACA, ICA, ects. [40]) |

| Electrical connection   | *Through hole                                 |

| from package to circuit | *Leaded                                       |

| board                   | *Leadless                                     |

|                         | *Array pads                                   |

|                         | *BGA                                          |

| Substrates              | *Plastic                                      |

|                         | *Ceramic                                      |

|                         | *Metal                                        |

|                         | *Glass                                        |

| Encapsulation of chip   | *Underfill [41]                               |

|                         | *Overmold [42]                                |

|                         | *transfer molding [43]                        |

**Table.1.1** The basic elements in a package structure and their common implementation approaches

The structure of an IC package is defined by a combination of the listed four basic elements. For each structure element, the selection of implementation techniques depends on the specific application, system requirements and overall cost.

#### 1.2 System on Chip (SoC) and System in Package (SiP)

The terminology SoC refers to a very large scale integration circuit, which integrate an electronic system on a single chip [44]. The embedded electronic system is able to combine all needed functions, including microprocessor, memory, optical, oscillator, and often radio-frequency, etc. SoC has a couple of advantages. Because everything is integrated on a single chip, the fabrication process can be well controlled, which leads to higher yields and higher system reliability. Normally the overall performance for SoC is better than SiP due to the compact connection. There are however some issues posed by SoC technology, such as very high design and prototyping cost, long development cycle time.

Given the high cost of SoC early development, SiP provides an alternative method to make up a complete electronic system [45]. In contrast to SoC, SiP incorporates multiple chips into a single package. Each incorporated chip handles a part of functions in the whole system, and the combined system can operate the same as if it was integrated by SoC. SiP is actually a broader sense of an old concept called multi-chip-module (MCM). MCM normally refers to assembly of multiple chips side-by-side on a single ceramic substrate using traditional connecting processes, such as wire bonding and flip chip. Regarded as the next level of MCM technology, SiP is designed with the ability to assembly multiple chips not only horizontally (on the same plane), but vertically as well. The above mentioned 3D die stacking and package stacking technology are encompassed in the concept of SiP. Sometimes, SiP even integrates several 3D structures on a single substrate in the same manner as MCM. With SiP technology, electronic companies can drastically reduce development time and risk, which overcomes the limitations of SoC development. But as mentioned before, the KGD issue is still an obstacle for successful SiP implement and high yield production.

SoC and SiP have their own pros and cons [44]. It's believed that SoC is more suitable for high volume production of systems with low complexity. And SiP is a good choice for low volume production of high complex systems.

#### **1.3 IC Packaging for RF Application**

Due to the rapid growth of mobile marcket, there is an increasing demand for higher bandwidth and higher communication speed. As discussed in previous sections, IC packaging technology is developed to improve the system performance for a higher operating frequency.

The current packaging technologies mainly use wire bonding or flip chip to realize the interconnection for the RF chips. From the perspective of RF performance, the wire bonding technique is somehow obsolete. The long bonding wire introduces excessive parasitic inductance, which can not be easily compensated. A recent research reports that the insertion loss of a common wire bonding connection is as high as 2.2 dB at only 9.5 GHz [46]. On the other hand, the flip chip bonding is a more promising candidate for high frequency application. A lot of study has been carried out to improve the RF performance of flip chip bonding. Normally, chips with GSG contact pads are flipped and bonded to the coplanar waveguide on the package substrate to form a CPW to CPW transition. The final RF performance of the transition depends on the bonding pitch, the involved bonding material, as well as the compensation structures. In general, a compensated flip chip bonding with small pitch and low resistive material can significantly reduce the insertion and reflection losses. The state of art flip-chip bonding using micro bump technology presents an insertion loss of 0.2 dB up to 90 GHz [47].

#### 1.4 Ultra Thin Chip Package (UTCP)

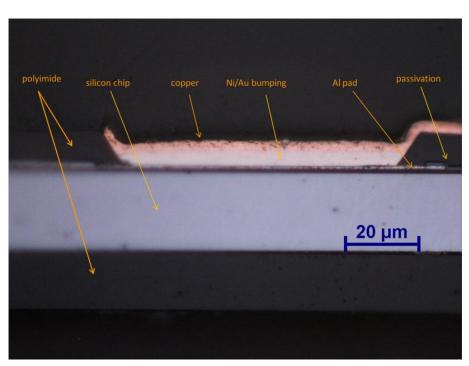

The UTCP technology is a kind of embedded chip package, which was developed by IMEC-CMST in the framework of EU funded SHIFT project. In this technology, a thinned silicon chip, with thickness below 30  $\mu$ m, is encapsulated in organic substrates, consisting of cured spin-on polyimide film. Contacts of the chip to the outside world are realized using laser drilling or reactive ion etching (RIE) through the polyimide to the chip pads and thin film interconnection metallization. The result of UTCP is a very thin package with a total thickness of only 50-60  $\mu$ m, which becomes even flexible and can be bent including the chip.

The UTCP technology is developed to meet an increasing demand of high frequency chip package. Since the current RF chips are realised by cmos technology, the chip size is shrinked as the scaling down of the transistors. But due to the strigent requirement of connection pitch, the chip bond pads can not be reduced as quickly as the chip size. Therefore the bond pads

cosume a considerably large area of the chip surface, which leads to a higher fabrication cost. It has been presented that the UTCP package with mirovia connection provides fine pitch capability and can further make the bond pads smaller. The fan out design provided by UTCP eliminates the need for precise placement and high density circuit board.

Although the wire bonding can also achieve connection pitch smaller than  $60\mu$ m, the long wire introduces excessive parasitive inductance and degrades the transmission quality. Since the UTCP microvias mimic the solder bump in the case of flip chip bonding, which should show similar performances. The flip chip bonding is proved to have superior quality over the wire bonding [48], but is only in coarse pitch connection. Then it is expected that the UTCP can surpass the wire bonding in RF performance, and maintains the fine pitch capability.

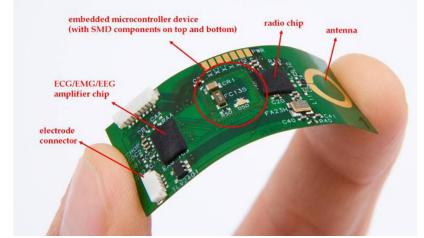

The UTCP is albe to be used independently or serves as an interposer, which can be further embedded inside PCB or FCB (flexible circuit board) and replace the needs for directly embedding of bare die. The KGD problem is solved, because the functionality of UTCP can be easily tested before embedding it in the main board. Fig. 1.12 shows a functional electrocardiography (ECG) measurement circuit, where a TI microcontroller was packaged using UTCP technology and embedded inside FCB. The functionality of the microcontroller after thinning down to 25  $\mu$ m has been proved by test of the UTCP.

Figure 1.12 Flexible wireless ECG monitoring circuit with embedded UTCP of TI microcontroller [49].

# **1.5 Thesis Content Overview**

This PhD research is a continuation study on the development of UTCP technology. The original UTCP is designed and fabricated as a single chip package for low frequency application (<5 GHz) only. In this PhD work, we exploit the use of UTCP to go beyond the current limitation and develop design strategies for embedded modules at radio frequency up to 60 GHz.

According to the main objective and scope discussed in previous section, this dissertation is organized as follows:

- Chapter 1 is a general introduction.

- Chapter 2 presents the design and optimization of microvia process for embedded chip interconnection (via size, shape, and generation method). A new process flow is estabilished for photosesitive polyimide.

- Chapter 3 presents another improvement in the UTCP fabrication process to achieve a flat UTCP topography. A flat surface is more suitable for multilayer build up and 3D PoP stacking.

- Chapter 4 demonstrates ultra-high frequency characterization of the dielectric material used in UTCP technology, especially for cured spin-on polyimide film.

- In Chapter 5, design, simulation and optimization of thin film structure is elaborated for high frequency interconnections to embedded chips. Two types of connection are built up. Their insertion and reflection properties were analyzed and compared with each other.

- Chapter 6 discussed passive devices which are realized by generic thin film technology in combination with the UTCP processing. A set of passive elements are designed and fabricated in EU SHIFT project. This chapter briefly explains the used process flow and mainly presents the RF characteristic of the realized passive devices.

- Finally, Chapter 7 summarizes the results presented in this dissertation and gives an outlook for future research.

# Scientific Contributions in the PhD Period

#### Journal contributions

- L.Wang, T. Sterken, M. Cauwe, D. Cuypers, and J. Vanfleteren, "Fabrication and characterization of flexible ultrathin chip package using photosensitive polyimide," *IEEE Trans on Compon Packag and Manuf. Technol*, vol. 2, No. 7, pp 1099-1106, 2012.

- L.Wang, M. Cauwe, S. Brebels, W. D. Raedt and J. Vanfleteren, "Self-Aligned Flat Ultra-Thin Chip Package for Flexible Circuits," *Circuit World*, vol. 39, Iss: 4, 2013.

#### **Conference contributions**

- L. Wang, W. Christiaens, S. Brebels, W. De Raedt, and J. Vanfleteren, "A novel approach to embed off-chip RF passives in PCB based onthin film technology," in Proc. Electron. Syst.-Integr. Technol. Conf., Sep. 2010, pp. 1–4.

- T. Sterken, M. O. de Beeck, F. Vermeiren, T. Torfs, L. Wang, S.Priyabadini, K. Dhaenens, D. Cuypers, and J. Vanfleteren, "High yieldembedding of 30 μm thin chips in a flexible PCB using a photopatternable polyimide based ultra-thin chip package (UTCP)," in Proc. 45<sup>th</sup> Int. Symp. Microelectron., Sep. 2012, pp. 940–945.

- S. Priyabadini, T. Sterken, L. Wang, K. Dhaenens, B. Vandecasteele, S. Van Put, A. E. Petersen, and J. Vanfleteren, "An approach to produce a stack of photo definable polyimide based flat UTCPs," in 2012 4th Electronic System-Integration Technology Conference, 2012, pp. 1–4.

## References

[1] William J. Greig, *Integrated circuit packaging, assembly and interconnections*. Springer, 2007.

[2] C. Harper, *Electronic Packaging and Interconnection Handbook 4/E*. McGraw-Hill Professional, 2004, p. 1000.

[3] W. Greig, Integrated Circuit Packaging, Assembly and Interconnections (Springer Series in Advanced Microelectronics). Springer, 2007, p. 328.

[4] International Roadmap Committee, (2012), "The International Technology Roudmap for Semiconductor." [Online]. Available: http://www.itrs.net/home. html

[5] Association Connecting Electronics Industries, (2013), "Current industry trend." [Online]. Available: www.ipc.org/

[6] Gordon E. Moore, "Cramming More Components onto Integrated Circuits," *Electronics*, pp. 114–117, April 19, 1965.

[7] ISSCC, (2013), "ISSCC 2013 Tech Trends." [Online]. Available: http://isscc.org/doc/2013/2013\_Trends.pdf

[8] Intel, (2008), "The intel4004." [Online]. Available: http://www.intel4004.com/qa4004.htm

[9] Fujitsu Semiconductor Lt,(2011) "IC Package," [Online]. Available: http://www.fujitsu.com/downloads/MICRO/fma/pdf/a810000114e.pdf

[10] K. A. Jackson and W. Schröter, *Handbook of Semiconductor Technology: Electronic structures and properties of semiconductors*. Wiley-VCH, 2000, p. 842.

[11] Dummer, G.W.A. *Electronic Inventions and Discoveries*, 2nd ed. Pergamon Press, 1978, p.204.

[12] P. M. (editor), *Surface Mount Council; Surface Mount Technology; Status of the Technology; Indus.* EIA, 1990.

[13] A. Seth, E. Pope, and S. Gordon, "Plastic quad flat pack," in *Proceedings. Japan IEMT Symposium, Sixth IEEE/CHMT International Electronic Manufacturing Technology Symposium*, pp. 90–100.

[14] B. Freyman and R. Marrs, "Ball Grid Array (BGA): The New Standard For High I/O Surface Mount Packages," in *Proceedings of Japan International Electronic Manufacturing Technology Symposium*, pp. 41–45.

[15] Toshiba, (2013), "QFP Packages." [Online]. Available: http://www.semicon.toshiba.co.jp/eng/product/asic/package/package2/ lqfp.html

[16] Toshiba, (2013), "BGA Packages." [Online]. Available: http://www.semicon.toshiba.co.jp/eng/product/asic/package/package2/ pbga.html

[17] S. T. Rao, "Ball grid array assembly issues in manufacturing," in *Proceedings of 16th IEEE/CPMT International Electronic Manufacturing Technology Symposium*, pp. 347–348.

[18] Fujitsu Semiconductor Ltd, (2002) "ASIC Packaging," [Online]. Available: www.fujitsu.com/downloads/MICRO/fma/pdf/ASIC20PKG.pdf

[19] M. Yasunaga, S. Baba, M. Matsuo, R. Matsushima, S. Nakao, and T. Tachikawa, "Chip scale package (CSP) 'a lightly dressed LSI chip'," in *Proceedings of 16th IEEE/CPMT International Electronic Manufacturing Technology Symposium*, pp. 169–176.

[20] P. Elenius, "Ultra CSP/sup TM/: a wafer level package," in *Proceedings International Symposium on Advanced Packaging Materials. Processes, Properties and Interfaces (IEEE Cat. No.99TH8405)*, pp. 241–245.

[21] Texas Instruments, (2005), "Flip Chip Ball Grid Array Package Reference Guide," [Online]. Available: http://www.ti.com/lit/ug/spru811a/spru811a.pdf

[22] J. Jackson and A. O'Donnell, (2007), "MicroCSP<sup>TM</sup> Wafer Level Chip Scale Package," *Analog Devices*. [Online]. Available: www.analog.com/static/imported-files/application\_notes/AN\_617.pdf [23]Freescale, (2013), "FCPBGA." [Online]. Available: http://www.freescale.com/webapp/sps/site/overview.jsp?code=CSIC\_PACK AGING

[24] T. Y. Wu, Y. Tsukada, and W. T. Chen, "Materials and mechanics issues in flip-chip organic packaging," in *1996 Proceedings 46th Electronic Components and Technology Conference*, pp. 524–534.

[25] A. Ostmann, D. Manessis, J. Stahr, M. Beesley, M. Cauwe, and J. De Baets, "Industrial and technical aspects of chip embedding technology," in 2008 2nd Electronics System integration Technology Conference, 2008, pp. 315–320.

[26] W. R. Davis, J. Wilson, S. Mick, C. Mineo, A. M. Sule, M. Steer, and P. D. Franzon, "Demystifying 3D ICs: The Pros and Cons of Going Vertical," *IEEE Design and Test of Computers*, vol. 22, no. 6, pp. 498–510, Jun. 2005.

[27] S. F. Al-Sarawi, D. Abbott, and P. D. Franzon, "A review of 3-D packaging technology," *IEEE Transactions on Components, Packaging, and Manufacturing Technology: Part B*, vol. 21, no. 1, pp. 2–14, 1998.

[28] M. Kada and L. Smith, "Advancements in stacked chip scale packaging provides system in a package functionality for wireless and handheld applications," in *Proc. 5th Pan Pacific Microelectron. Symp.*, 2000, p. pp.246–251.

[29] Amkor Technology, (2013). "Through Silicon Via (TSV) Wafer Finishing & Flip Chip Stacking." [Online]. Available: http://www.amkor.com/index.cfm?objectid=7478706F-E1C7-1A4D-E62795E72380FA68

[30] Tessera Inc, (2013). "µPILR Package-on-Package (PoP) interconnect solution" [Online]. Available: http://www.tessera.com/technologies/intellectualproperty/substrateinterconn ect/Pages/uPILR-PoP.aspx

[31] V. Solberg, "µPILR trade package-on-package technology: development and reliability testing," in 2007 9th Electronics Packaging Technology Conference, 2007, pp. 55–60.

[32] Y. Kurita, K. Soejima, K. Kikuchi, M. Takahashi, M. Tago, M. Koike, K. Shibuya, S. Yamamichi, and M. Kawano, "A Novel 'SMAFTI' Package for Inter-Chip Wide-Band Data Transfer," in *56th Electronic Components and Technology Conference 2006*, pp. 289–297.

[33] Y. Kurita, N. Motohashi, S. Matsui, K. Soejima, S. Amakawa, K. Masu, and M. Kawano, "SMAFTI packaging technology for new interconnect hierarchy," in *2009 IEEE International Interconnect Technology Conference*, 2009, pp. 220–222.

[34] R. Fillion, B. Burdick, D. Shaddock, and P. Piacente, "Chip scale packaging using chip-on-flex technology," in *1997 Proceedings 47th Electronic Components and Technology Conference*, pp. 638–642.

[35] H. Braunisch, S. N. Towle, R. D. Emery, and G. J. Vandentop, "Electrical performance of bumpless build-up layer packaging," in *52nd Electronic Components and Technology Conference 2002. (Cat. No.02CH37345)*, pp. 353–358.

[36] P. Palm, R. Tuominen, and A. Kivikero, "Integrated Module Board (IMB); an advanced manufacturing technology for embedding active components inside organic substrate," in 2004 Proceedings. 54th Electronic Components and Technology Conference (IEEE Cat. No.04CH37546), pp. 1227–1231.

[37] L. Boettcher, D. Manessis, A. Neumann, A. Ostmann, and H. Reichl, "Chip embedding by chip in polymer technology," in *Proc. Device Packaging Conference*.

[38] W. Christiaens, E. Bosman, and J. Vanfleteren, "UTCP: A Novel Polyimide-Based Ultra-Thin Chip Packaging Technology," *IEEE Transactions on Components and Packaging Technologies*, vol. 33, no. 4, pp. 754–760, Dec. 2010.

[39] S. M. Wentworth, D. P. Neikirk, and C. R. Brahce, "The high-frequency characteristics of tape automated bonding (TAB) interconnects," *IEEE Transactions on Components, Hybrids, and Manufacturing Technology*, vol. 12, no. 3, pp. 340–347, 1989.

[40] H. Kristiansen and J. Liu, "Overview of conductive adhesive interconnection technologies for LCDs," *IEEE Transactions on Components,*

*Packaging, and Manufacturing Technology: Part A*, vol. 21, no. 2, pp. 208–214, Jun. 1998.

[41] K. K. Wang, "Analysis of the flow of encapsulant during underfill encapsulation of flip-chips," *IEEE Transactions on Components, Packaging, and Manufacturing Technology: Part B*, vol. 20, no. 4, pp. 424–433, 1997.

[42] S. Ouimet and M.-C. Paquet, "Overmold technology applied to cavity down ultrafine pitch PBGA package," *IEEE Transactions on Advanced Packaging*, vol. 22, no. 2, pp. 123–128, May 1999.

[43] T. Braun, K.-F. Becker, M. Koch, V. Bader, U. Oestermann, D. Manessis, R. Aschenbrenner, and H. Reichl, "Wafer level encapsulation - a transfer molding approach to system in package generation," in *4th Electronics Packaging Technology Conference, 2002.*, 2002, pp. 235–244.

[44] R. Wilson, (2005)."The Great Debate: SOC vs. SIP." [Online]. Available: http://www.eetimes.com/electronics-news/4052047/The-Great-Debate-SOC-vs-SIP

[45] M. Romig and V. Gupta, (2012). "System-in-package provides viable integration solution." [Online]. Available: http://www.eetimes.com/design/eda-design/4236765/System-in-package-provides-viable-integration-solution-

[46] C. H. J. Poh, C. E. Patterson, S. K. Bhattacharya, S. D. Philips, N. E. Lourenco, J. D. Cressler, and J. Papapolymerou, "Packaging Effects of Multiple X-Band SiGe LNAs Embedded in an Organic LCP Substrate," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 2, no. 8, pp. 1351–1360, Aug. 2012.

[47] A. Jentzsch and W. Heinrich, "Theory and measurements of flip-chip interconnects for frequencies up to 100 GHz," *IEEE Transactions on Microwave Theory and Techniques*, vol. 49, no. 5, pp. 871–878, May 2001.

[48] T. Krems, W. Haydl, H. Massler, and J. Rudiger, "Millimeter-wave performance of chip interconnections using wire bonding and flip chip," in *1996 IEEE MTT-S International Microwave Symposium Digest*, vol. 1, pp. 247–250.

Chapter 1. General Introduction

[49] W. Christiaens, T. Torfs, W. Huwel, C. Van Hoof, and J. Vanfleteren, "3D integration of ultra-thin functional devices inside standard multilayer flex laminates." in *Microelectronics and Packaging Conference (EMPC)*, 2009, pp1-5.

# CHAPTER 2

# **UTCP Technology Using Photosensitive Polyimide**

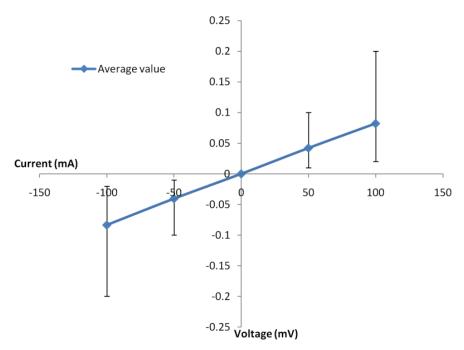

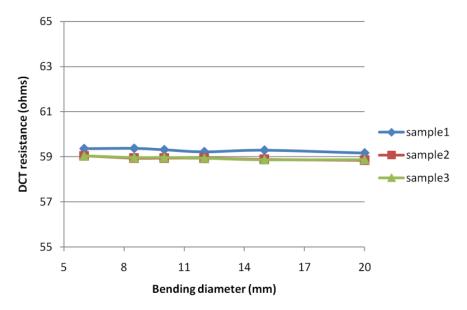

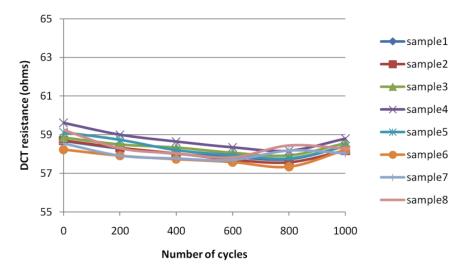

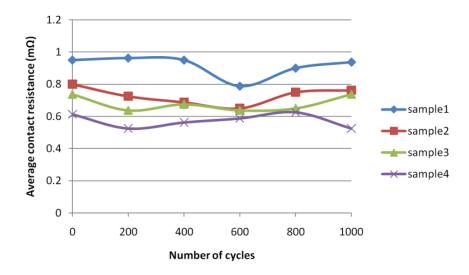

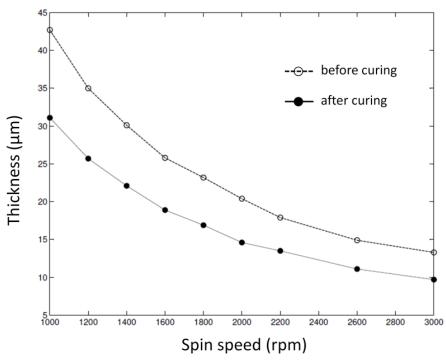

This chapter describes an improved UTCP process flow with microvia formation by standard UV lithography through photosensitive polyimide (PSPI). Such microvia formation method proved to be more reliable than laser drilling techniques and simpler than a dry etching process. Since the used PSPI is self-priming, a thin layer of potassium chloride (KCl) was introduced as a release layer. In the end, the polyimide encapsulation of thinned die can be released from the carrier substrate and becomes a flexible chip package with a total thickness of around 50  $\mu$ m. Daisy chain test dies were encapsulated inside spin-coated polyimide films. Excellent chip-to-package interconnection was demonstrated by electrical daisy chain and contact resistance measurements. Bending tests and thermal cycling tests were also performed on the daisy chain test vehicles. Desired flexibility and reliability of UTCP's was observed.

# 2.1 Introduction

The development of integrated circuits leads to an increase in components density, which requires chip packaging technologies to enable higher lead count, finer pitch, and smaller size. This trend is clear in the evolution of packaging. In the evolution from DIP to BGA, typical pin count increases from 24 to 280, while the thickness decreases from 4 mm to 1 mm and the area is reduced from 32 mm x 14 mm to 9 mm x 9 mm [1, 2].

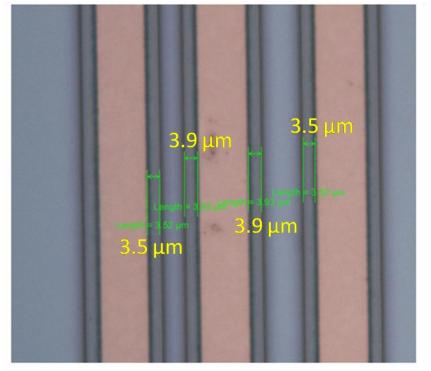

Recently, assembly of thinned die has become the focus of research to further lower the package profile [3-5]. A thinned silicon die is either flip bonded onto or embedded into thin film substrates [5-9]. The chip embedded approach is one promising candidate for the next generation System-in-Package (SiP) technology by reason of its high-density interconnection capability and superb electrical performance [10]. As described in chapter 1, one of the most prominent embedding approaches is Chip-in-Polymer (CiP) technology developed by Fraunhofer IZM in corporation with TU Berlin [11]. The basic concept of CiP is to laminate thinned die in dielectric resin and then make contact to chip bond pads by laser ablation and direct metallization [9-11]. In UTCP technology, thinned die was encapsulated inside spin-on polyimide layers [12]. The result of UTCP is a very thin and even flexible chip package, with a total thickness around 50 µm. This technology allows the fabrication of ultra thin flexible electronics, which have attracted a lot of attention because of their conformal property [13-15]. Flexible electronics create possibilities for many applications in portable electronics, sensor array systems and aerospace [16-18]. The flexibility of an end product is often limited by the rigid components mounted on the surface of the substrate. An introduction of ultra-thin chips, which are well bendable in contrast to bulk silicon chips, can further enhance the mechanical flexibility of the electronic circuitry.

This chapter presents an updated version of IMEC's UTCP technology. In previous work, via-holes connecting die contact pads were generated by laser drilling through a PI-2611 polyimide (from HD Microsystems) covering layer [12]. In doing so, besides the reported problem of laser beam misalignment, the high intensity power of the laser beam has the potential to damage the metal bump pad on the chip [19]. In today's high density PCB industry, laser drilling with either UV lasers or CO2 lasers is a well established and widely adopted method for microvia formation. If the drilling process is properly controlled, the damage to the bond pads can be eliminated or minimized to an acceptable level [11, 12]. Photo definition is another well known via formation process by introducing photosensitive material. In this work, photo definition is used as an alternative to laser drilling. Via formation using photosensitive polyimide (PSPI) is similar in process sequence to a generic photolithography technique, which is more reliable than laser ablation and is more cost-effective than dry etching based

via formation techniques. However, if PSPI is selected as the covering material, in order to avoid CTE mismatch between the top and base dielectric layer, the same PSPI should also be used as the base material. Since most of the PSPI is self-priming and cannot be easily released from the rigid carrier substrate, a new release method based on potassium chloride (KCl) evaporation is invented and discussed in this chapter.

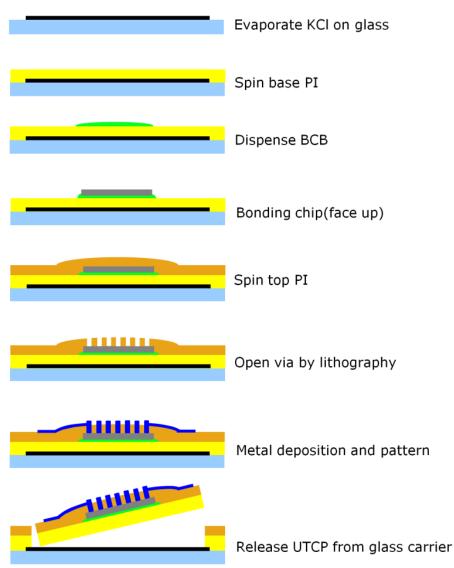

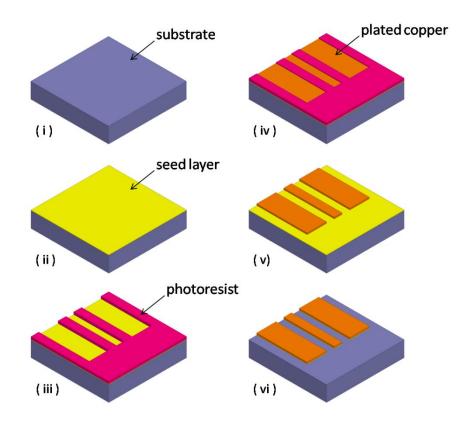

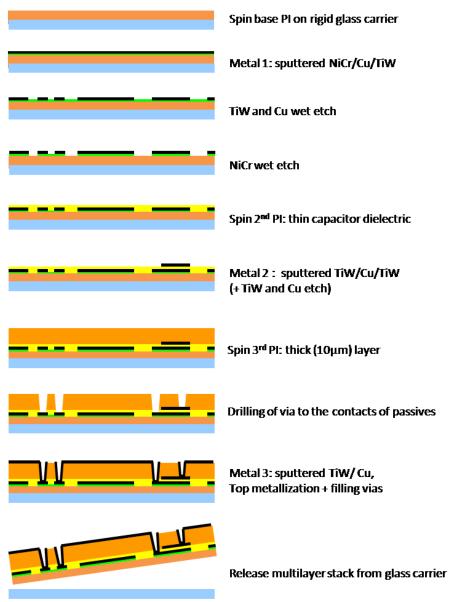

# **2.2 Process Flow**

The improved technique was developed to embed a thinned die into two PSPI films. The schematic process flow is depicted in Fig. 2.1. First, a 400nm layer of KCl is thermally evaporated on a rigid glass carrier substrate. Then the base PSPI is spin-coated on the KCl film and fully cured. The thinned die is glued on the base PSPI (face up) using benzocyclobutene (BCB) as adhesive. After the curing of BCB, the top PSPI layer is spincoated, illuminated through a mask and developed to define the microvias to the chip contact pads. Finally, the top PSPI is cured and the metal pattern is realized on top. After the whole process, the multilayer assembly of thinned die can be released from the glass carrier, and becomes a flexible ultrathin chip package (UTCP).

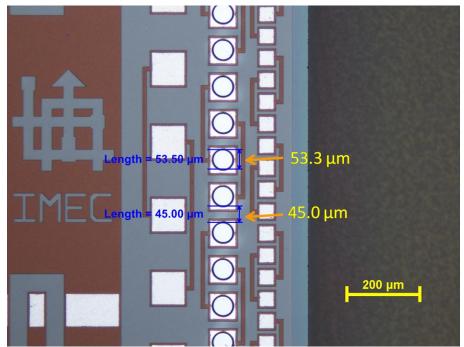

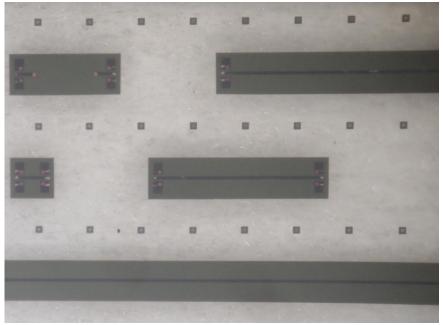

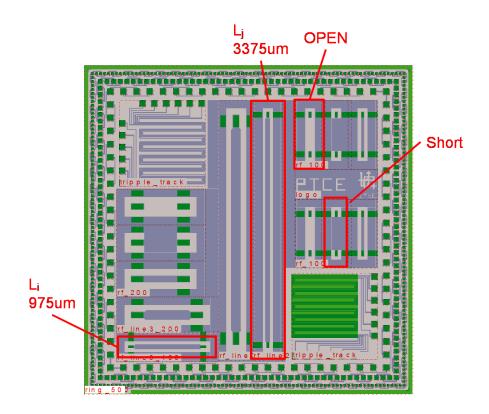

### 2.3 Test Design

PTCE chips from IMEC are selected as test dies for the embedding trials. The PTCE chip is a 5 mm  $\times$  5 mm daisy chain silicon chip which has been thinned down from 675 µm to 20 µm on wafer level. Wafer thinning and separation by coarse grinding and sawing are no longer feasible when the thickness is below 150 µm, due to large stress and deep cracks in silicon [20].

For the purpose of fabricating the ultra-thin chips, an additive process technology, Chipfilm, is developed at IMS [21,22]. The main feature of Chipfilm is the precise control of chip thickness and uniformity. Such technology can provide good mechanical stability of ultra-thin chips with high yield, which paves the way for future flexible electronic applications. However Chipfilm technology is not available at our facility. In contrast to Chipfilm, wafer backside grinding is used for this work. Wafer thinning down to 50  $\mu$ m or less is common for 3D integration. But wafer dicing by use of a conventional sawing machine can generate deep cracks in the silicon

which is detrimental for ICs' reliability especially in case of thinned chips. Therefore, instead of dicing a thinned wafer, the Dicing-by-Thinning concept was employed to accomplish this task [23].

Figure 2.1 Process flow to produce UTCP using PSPI.

There are three types of daisy chains around the chip edge with different pitches (60, 100 and 200  $\mu m).$  The trials in this work only use the coarsest

-30-

Chapter 2. UTCP Technology Using Photosensitive Polyimide

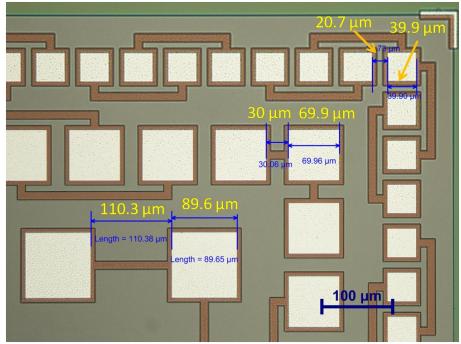

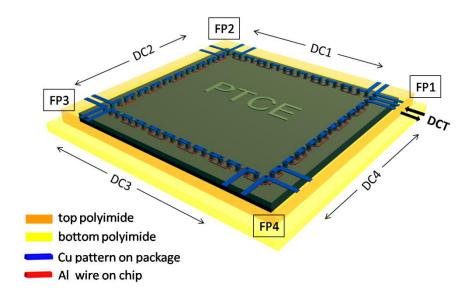

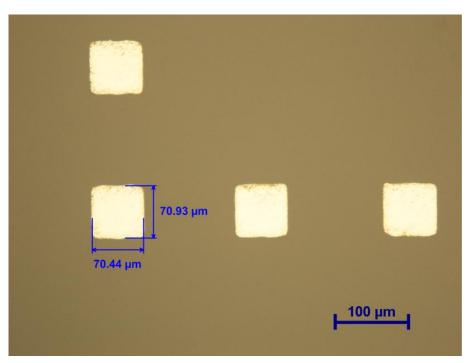

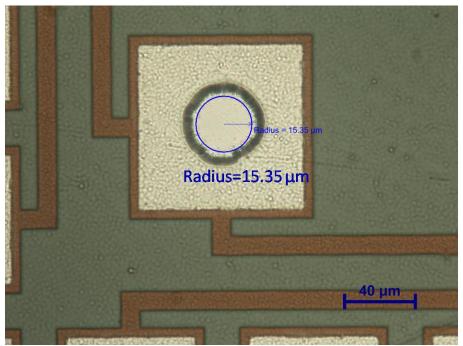

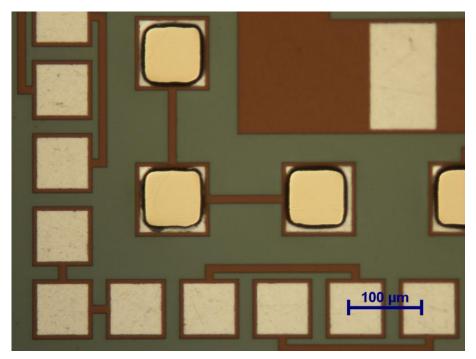

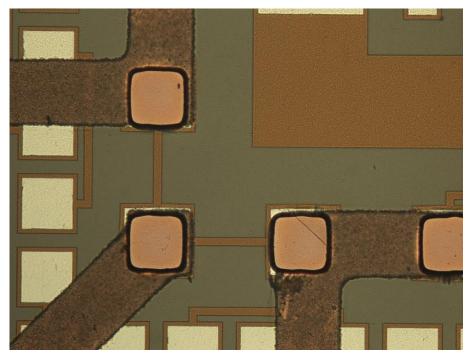

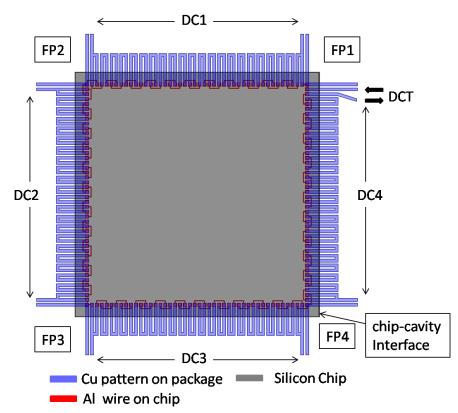

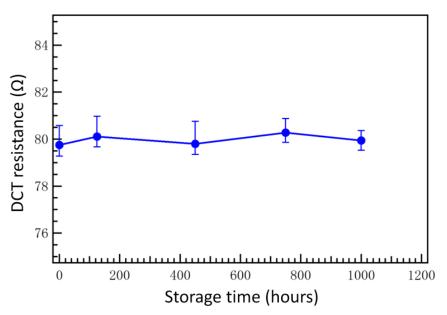

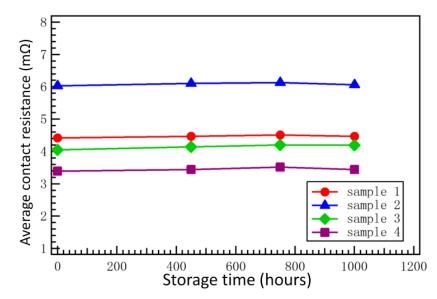

pitch which has  $90\mu m \times 90\mu m \times 1\mu m$  (length  $\times$  width  $\times$  thickness) aluminum contact pads and 110  $\mu m$  wide space in between (Fig. 2.2). In order to characterize the feasibility of the technology, a metallization pattern is designed to interconnect the bond pads. The layout of the metallization is shown in Fig. 3 together with the chip layout. This design includes four short daisy chains (DC1-4) along the edges, each connecting 20 peripheral bond pads. A series link from DC1 to DC4 forms a long daisy chain DCT. Four four-point Kelvin structures (FP1-4) are also fabricated at corners of the chip for contact resistance measurements.

Figure 2.2 Peripheral bond pads with different pitch on PTCE chip.

Figure 2.3 Schematic graph showing UTCP of PTCE chip and its interconnect layout.

# 2.4 Fabrication Process And Optimization

#### 2.4.1 Substrate Preparation

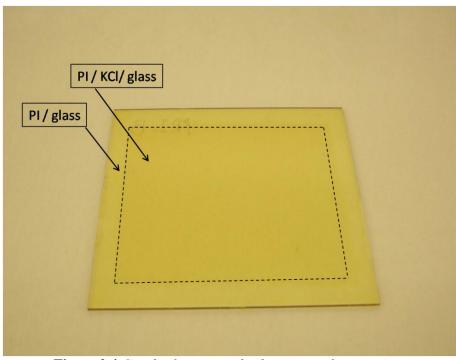

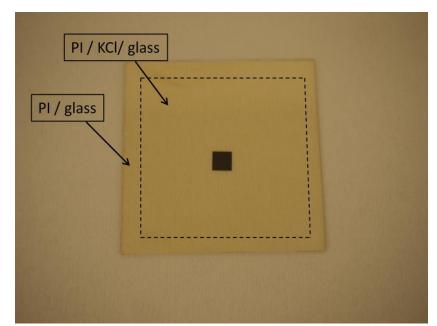

The assembly of thinned die was built up on a 5 cm  $\times$  5 cm rigid glass carrier purchased from Praezisions Glas and Optik. The glass should be thoroughly cleaned in RBS, IPA and DI water in sequence to remove dust and grease from manufacturing and transport. Next, a 400 nm thick KCl layer was thermally evaporated on the glass, the edges of which were covered by aluminum foil. Since the PSPI is self-priming and becomes hard to peel off after curing when directly deposited on glass, such KCl film, which can be easily dissolved in water, serves as a release layer between the base PSPI and the glass carrier. Moreover, the base PSPI on the edge of the glass can protect KCl from any solvent during the whole process. A major concern about the use of KCl is that K+ and Cl- ions are common contaminants which can have detrimental impact on a semiconductor processing line especially with the high temperature diffusion. But the fabrication of UTCP is carried out in a thin film package environment which does not need to meet the high purity level for semiconductor production. Additionally, the evaporation of KCl is performed in a confined physical vapor deposition (PVD) chamber under high vacuum condition to avoid exposure to ambient air. Due to the presence of KCl in PVD, it is not recommended to process other materials by the same machine. By doing this, KCl contamination can be reduced to an acceptable level.

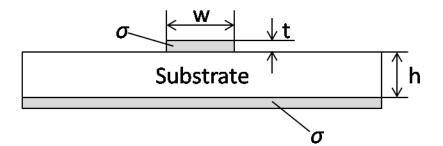

HD-4110 from HD Microsystems was used for both the base and top PSPI in order to avoid CTE mismatch [24]. The first PSPI layer was then spin-coated at 1000 rpm for 10 s, followed by a final speed of 1800 rpm for 1 min. The lower starting speed is used to spread the highly viscous HD-4110 in order to form a more uniform layer. After the spinning, the substrate was cured in a vacuum oven for 6 hours with 5 sccm nitrogen flow. The curing temperature profile was as follows: increase from 20 °C (room temperature) to 200 °C with a ramp rate of 4°C/min; hold the temperature of 200 °C for 30 min; increase to the final curing temperature of 375 °C with a ramp rate of 2.5°C/min; and maintain the elevated temperature for an hour; then let it cool down naturally. The thickness of base PSPI after curing is 15  $\mu$ m.

In order to improve the adhesion to the bonding material and the top PSPI, an increase in surface roughness of the base PSPI is preferred by a plasma etching treatment. This was done by Reactive Ion Etching (RIE), first using a CHF3/O2 mixture gas with a flow rate of 5/20 sccm for 2 min, and another 2 min using pure O2 with a flow rate of 25 sccm, both at a fixed power of 150 W and a pressure of 100 mTorr. Fig. 2.4 shows a substrate after RIE which is ready for the next chip bonding step. The dashed line in the graph encloses the area where the KCl film was deposited.

Chapter 2. UTCP Technology Using Photosensitive Polyimide

Figure 2.4 Graph of a prepared substrate on glass carrier.

#### 2.4.2 Chip Placement

The PTCE chip tends to curl after thinning to  $20 \ \mu m$  thick due to its internal stress. The chip warpage can cause multiple reflections of the light during exposure, which leads to unsuccessful opening of the microvias. Therefore, bonding the thinned chip in a flat plane on the substrate is of vital importance.

BCB of the Cyclotene 3000 Series from Dow Chemical Co. was selected as an adhesive material. A droplet of BCB (about 50 nL) was put on the substrate and was subjected to a soft bake on a hot plate at 60 °C for 5 min. The purpose of the soft bake is to evaporate solvent in the BCB and to dehydrate the base PSPI layer. Without performing this step, some air bubbles could be trapped underneath the chip during the BCB curing. The thinned chip was then manually placed face-up on the BCB and a release film ACC-3 (from Holders Technology PLC) was put on the top of the chip. The release film, which has resistance against different chemicals, was used to prevent BCB from sticking to the press plate in the next bonding process.

The bonding of the die was accomplished in two steps. The preliminary bonding was done in a Logitech wafer bonder at an elevated temperature of 150 °C for 1 hour under a pressure of 500 mBar and followed by a quick cooling down to room temperature. After preliminary bonding, the BCB was only partially cured. In case a small amount of BCB overflowed between the chip and the ACC-3 film, it still can be removed by acetone. IPA and DI water was used to clean the residual acetone and the sample was dried in the air. Afterwards, the final BCB curing was carried out in a nitrogen oven with 1kg weights applied to enhance the bonding strength. The BCB hard curing profile was the following: heat from 20 °C to 150 °C with a ramp rate of 4 °C/min followed by an increase to 250 °C with a ramp rate of 2.5 °C/min, and maintain the temperature of 250 °C for 1 hour before cooling down.

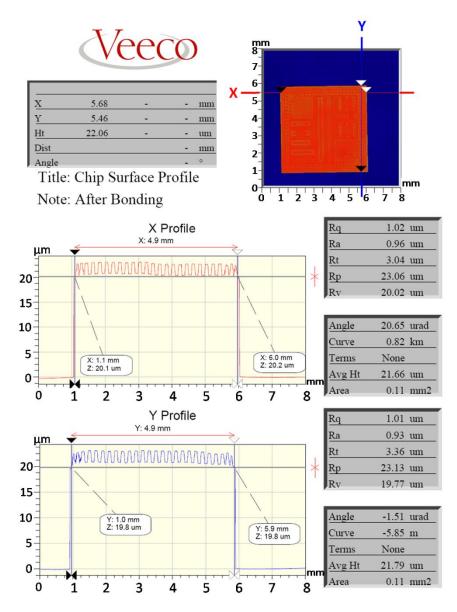

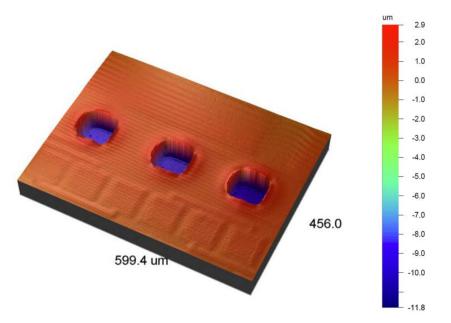

The die surface topography was scanned by a Wyko optical profilometer as shown in Fig. 2.5. Compared to the chip profile before bonding, the radius of curvature increases from about 100 mm to more than 5 meters, showing a virtually flat chip assembly as desired.

#### **2.4.3 Via Formation**