Snelle-simulatietechnieken voor de exploratie van de microarchitecturale ontwerpruimte

Fast Simulation Techniques for Microprocessor Design Space Exploration

Davy Genbrugge

Promotor: prof. dr. ir. L. Eeckhout Proefschrift ingediend tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Computerwetenschappen

Vakgroep Elektronica en Informatiesystemen Voorzitter: prof. dr. ir. J. Van Campenhout Faculteit Ingenieurswetenschappen Academiejaar 2009 - 2010

ISBN 978-90-8578-328-2 NUR 980

Wettelijk depot: D/2010/10.500/4

### **Dankwoord**

Bij de aanvang van dit onderzoek had ik slechts een vaag idee over het pad dat ik zou bewandelen. Al snel had ik door dat onderzoek niet over een rechte geplaveide weg loopt, maar op een kronkelig pad vol obstakels. Meerdere malen ben ik mezelf tegengekomen. Gelukkig kon ik rekenen op de steun van een aantal mensen, die onmisbaar waren bij het tot stand komen van dit werk. Graag wil ik hen uitvoerig bedanken.

In de eerste plaats wil ik mijn promotor prof. Lieven Eeckhout bedanken. Verscheidene malen heb ik me kunnen beroepen op de expertise van Lieven wanneer ik door de bomen het bos niet meer zag. Hij heeft me (met het nodige geduld) de knepen van het vak geleerd, en kon steeds weer begrip opbrengen wanneer ik in de fout ging. Ook op momenten dat de moed me in de schoenen zonk wist hij me te motiveren om verder te gaan. Zonder zijn hulp had ik nooit de tal van mooie ervaringen kunnen opdoen en had ik niet gestaan waar ik nu sta.

In de tweede plaats wil ik prof. Koen De Bosschere bedanken. Reeds meer dan dertien jaar bouwt Koen een onderzoeksgroep uit die jonge mensen de kans geeft zich te verdiepen in computerarchitectuur. Door zijn enthousiasme en gedrevenheid weet hij steeds opnieuw tal van mensen te overtuigen om een onderzoek aan te vatten. Jaren terug heb ik ervoor gekozen om me te vervoegen bij de groep van Koen; iets wat ik mij nog nooit heb beklaagd.

I also would like to thank all members of my PhD committee for their effort to evaluate this thesis. I would like to thank prof. Brad Calder from Microsoft and prof. Erik Hagersten from Acumem and Uppsala University in Sweden. I really appreciate it that you have found the time to read my thesis and to serve on my committee; I know that you have a tight schedule. Your comments were invaluable for improving my thesis. Verder wil ik ook de binnenlandse leden van mijn doctoraatscommissie bedanken voor hun inspanning om dit werk te beoordelen: prof. Diederik Verkest, prof.

Chris Develder, prof. Koen De Bosschere en prof. Jan Van Campenhout. Uw suggesties waren van onschatbare waarde om mijn thesis sterker te maken. Uiteraard wil ik ook prof. Rik Van de Walle bedanken om de taak van voorzitter op zich te nemen.

Jarenlang heb ik kunnen werken in een aangename collegiale werksfeer. In de eerste plaats bedank ik mijn bureaugenoten: Andy, Dries, Kris, Frederick, Stijn en Max. Het was/is een plezier om met jullie een bureau te delen. In de afgelopen jaren heb ik ontzettend veel bijgeleerd ondermeer van mijn collega's: Michiel, Stijn, Andy, Jonas, enz. Ongetwijfeld ben ik een aantal mensen vergeten, daarom wil ik *iedereen* bedanken voor die mooie jaren. In het bijzonder wil ik Andy en Stijn nog eens bedanken om mijn thesis na te lezen.

Gedurende mijn onderzoeksactiviteiten was ik tewerkgesteld op een aantal projecten. Bij deze wens ik dan ook het Institiuut voor de aanmoediging van Innovatie door Wetenschap en Technologie in Vlaanderen (IWT), het Fonds voor Wetenschappelijk Onderzoek Vlaanderen (FWO) en de Universiteit Gent bedanken voor de financiering van dit onderzoek.

Tot slot wens ik ook mijn familie en vrienden te bedanken om mij al die jaren te steunen. Ik was niet altijd het zonnetje in huis, zeker niet op moment dat er een *deadline* moest gehaald worden. Vaak heb ik tegen mijn kameraden 'nee' moeten zeggen wegens 'geen tijd'. Daarom bedankt voor al jullie begrip! In het bijzonder, mama, papa en zus (en Pieter), jullie zijn zoals altijd de beste! Genoeg reden voor mij om te blijven doorgaan, dank u.

Davy Genbrugge Gent, 22 januari 2010

### Examencommissie

Prof. Rik Van de Walle, voorzitter

Vakgroep ELIS, Faculteit Ingenieurswetenschappen Universiteit Gent

Prof. Jan Van Campenhout, secretaris

Vakgroep ELIS, Faculteit Ingenieurswetenschappen Universiteit Gent

Prof. Lieven Eeckhout, promotor

Vakgroep ELIS, Faculteit Ingenieurswetenschappen

Universiteit Gent

Prof. Brad Calder

Department of Computer Science and Engineering

University of California in San Diego

Microsoft USA

Prof. Koen De Bosschere

Vakgroep ELIS, Faculteit Ingenieurswetenschappen

Universiteit Gent

Prof. Chris Develder

Vakgroep INTEC, Faculteit Ingenieurswetenschappen

Universiteit Gent

Prof. Erik Hagersten

Department of Information Technology

Uppsala University

Acumem

Sweden

Prof. Diederik Verkest Vakgroep ETRO, Faculteit Ingenieurswetenschappen Vrije Universiteit Brussel IMEC Leuven

### Leescommissie

Prof. Brad Calder

Department of Computer Science and Engineering

University of California in San Diego

Microsoft

**USA**

Prof. Chris Develder

Vakgroep INTEC, Faculteit Ingenieurswetenschappen

Universiteit Gent

Prof. Lieven Eeckhout, promotor

Vakgroep ELIS, Faculteit Ingenieurswetenschappen

Universiteit Gent

Prof. Erik Hagersten

Department of Information Technology

Uppsala University

Acumem

Sweden

Prof. Diederik Verkest

Vakgroep ETRO, Faculteit Ingenieurswetenschappen

Vrije Universiteit Brussel

**IMEC** Leuven

# Samenvatting

Het ontwerpen van een nieuwe microprocessor is enorm tijdrovend: het kan tot zeven jaar duren alvorens een processor op de markt komt. Processorontwerpers maken gebruik van cyclusgetrouwe simulatoren tijdens de verschillende stadia van het ontwerpproces, bijvoorbeeld bij het nemen van hoog-niveaubeslissingen tijdens de initiële verkenning van de ontwerpruimte. Architecturale simulatoren modelleren de microarchitectuur in software. Deze simulatoren zijn zeer nauwkeurig en zeer flexibel in gebruik, maar hebben als nadeel dat ze drie tot vier grootteordes trager zijn dan de hardware die ze modelleren. Bovendien vraagt het veel tijd om ze te ontwikkelen.

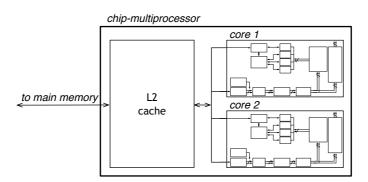

De huidige trendverschuiving naar chip-multiprocessors maakt deze laatstgenoemde problemen erger. Chip-multiprocessors combineren meerdere kernen op één enkele chip, en delen een aantal systeemhulpbronnen zoals caches, geheugenbussen, hoofdgeheugen, enz. Draden die gelijktijdig worden uitgevoerd kunnen elkaars prestatie beïnvloeden via deze gedeelde componenten. Bijvoorbeeld, een draad kan trager vooruitgang boeken dan een andere draad ten gevolge van bijkomend conflictgedrag. Bovendien kan een verandering in de microarchitectuur ervoor zorgen dat andere delen van de draden op hetzelfde moment in uitvoering zijn, wat op zijn beurt leidt tot een verschillend conflictgedrag en dus een verschillende relatieve vooruitgang van de draden. Deze verstrengeling van prestatie tussen de draden in uitvoering maakt het moeilijk om de prestatie van chip-multiprocessors te modelleren. Naarmate het aantal kernen op een processor toeneemt, neemt de simulatiesnelheid aan belang toe.

Onderzoekers en computerarchitecten zijn zich bewust van het simulatieprobleem en hebben reeds tal van technieken voorgesteld om de simulatie te versnellen. In dit proefschrift stellen we twee technieken voor die de simulatiesnelheid aanzienlijk verbeteren, namelijk, statistische simulatie en intervalsimulatie. viii SAMENVATTING

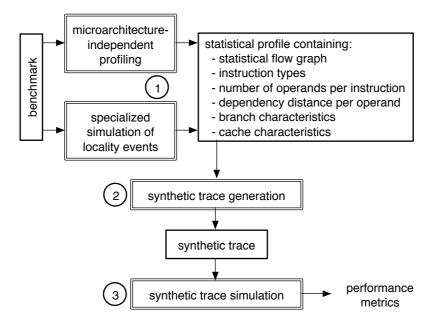

Statistische simulatie versnelt de simulatie door het aantal gesimuleerde instructies te verminderen. Dit gebeurt in drie stappen. Eerst meten we een aantal programmakarakteristieken op in een zogenaamd statistisch profiel door middel van functionele simulatie of andere profileringshulpmiddelen. Op basis van dit profiel wordt dan een synthetische trace gegenereerd met dezelfde eigenschappen, maar bestaande uit veel minder instructies – in de orde van enkele miljoenen instructies. Door de synthetische trace te simuleren verkrijgen we snel een schatting van de prestatie.

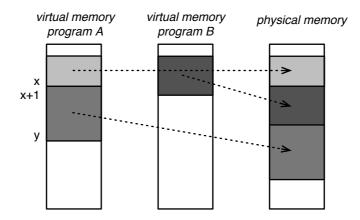

We leveren twee belangrijke bijdragen aan het statistische simulatieparadigma. Ten eerste verbeteren we de nauwkeurigheid door een betere modellering van de geheugendatastromen; dit houdt onder andere in dat we geheugenparallellisme, secundaire cachemissers, en loadstore data-afhankelijkheden modelleren. Ten tweede breiden we het statistische simulatieparadigma uit om het conflictgedrag in gedeelde systeemhulpbronnen van chip-multiprocessors die meerdere programma's uitvoeren te kunnen vatten. Dit vereist dat we toegangen tot het geheugensubsysteem onafhankelijk van de microarchitectuur modelleren; hiervoor gebruiken we metrieken zoals hergebruiksafstand en stapeldiepte. Een bijkomend voordeel van een microarchitecturaalonafhankelijke modellering is dat er meerdere ontwerppunten kunnen geëvalueerd worden met eenzelfde statistisch profiel, wat de bruikbaarheid van statistische simulatie ten goede komt. In het geval van chip-multiprocessorsimulatie is het belangrijk om het fasegedrag van programma's nauwkeurig te vatten, aangezien dit een niet onbelangrijke invloed op totale prestatie heeft.

Deze bijdragen maken van statistische simulatie een snelle en nauwkeurige oplossing voor het simulatieprobleem van chip-multiprocessoren, en is in het bijzonder goed geschikt om de microarchitecturale ontwerpruimte te verkennen.

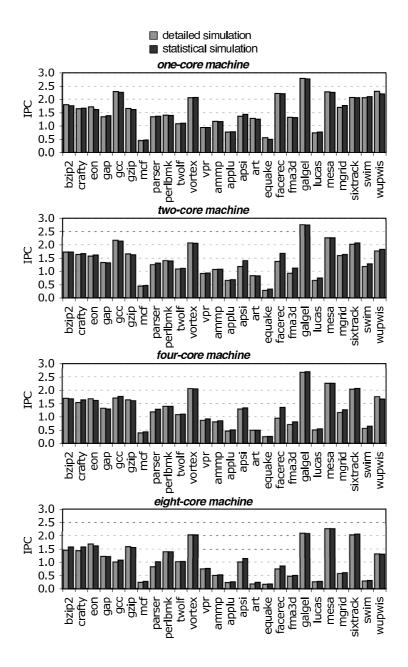

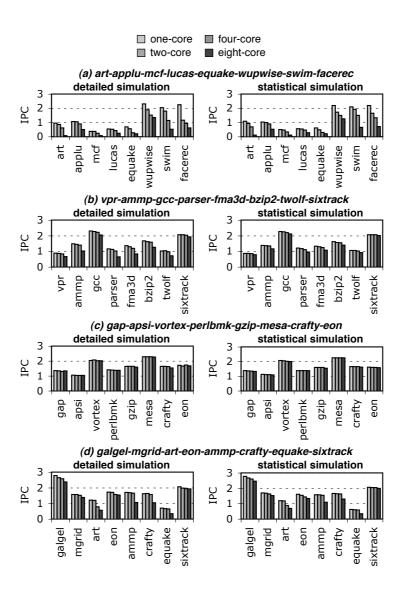

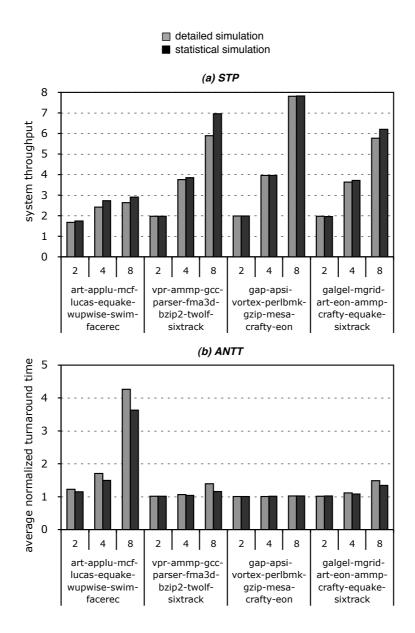

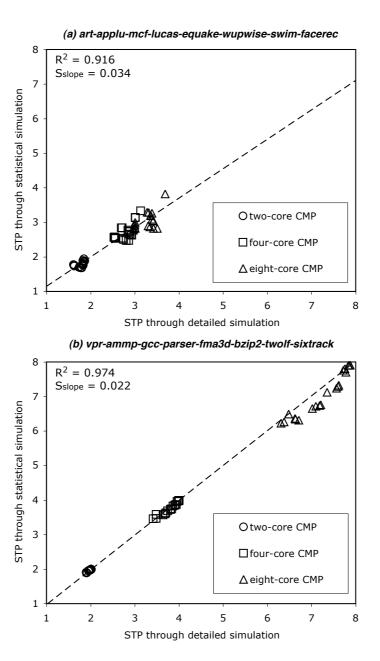

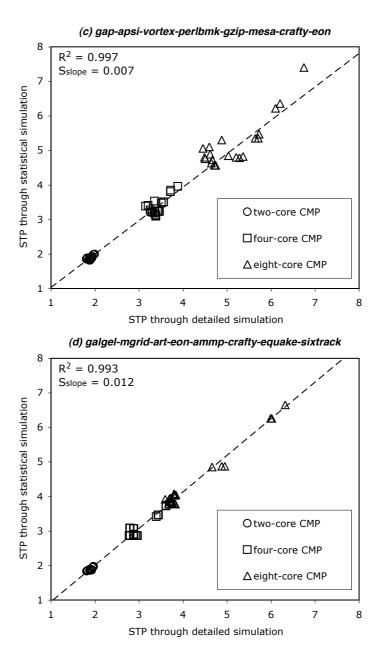

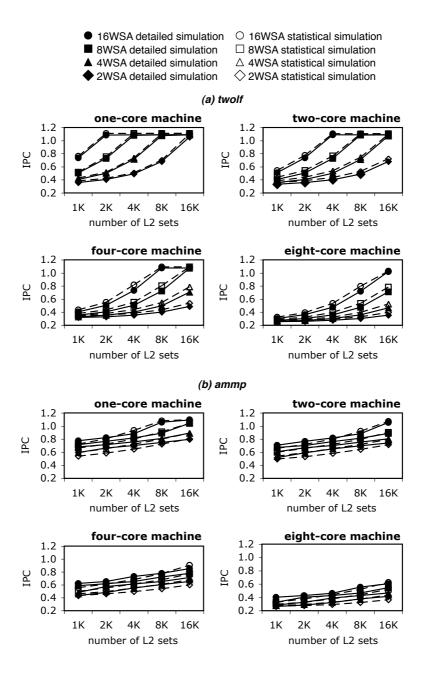

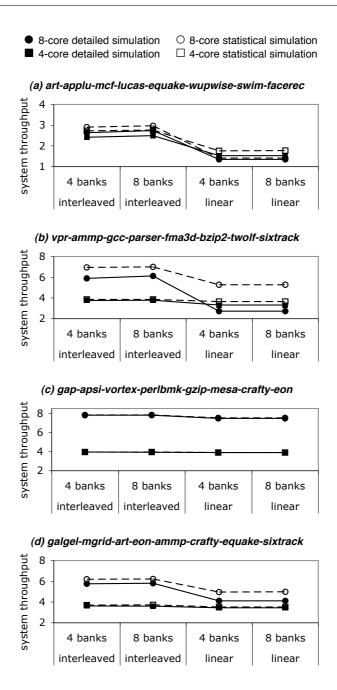

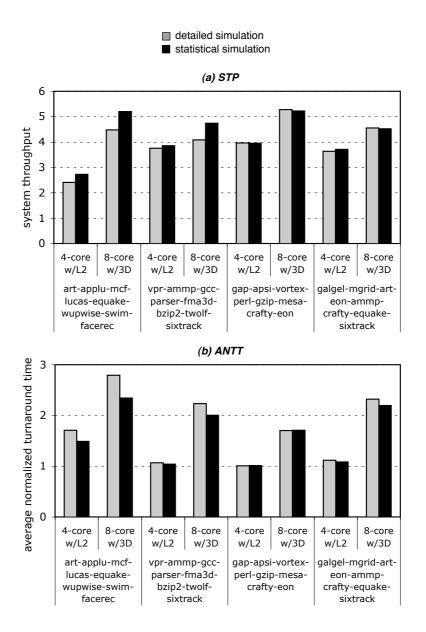

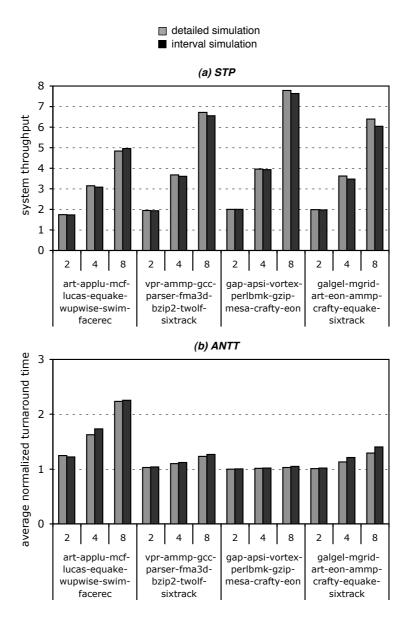

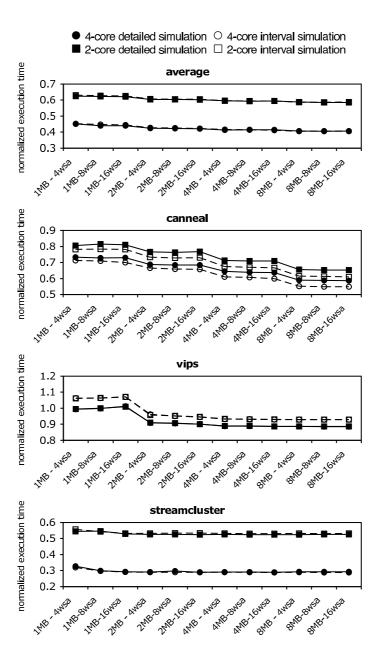

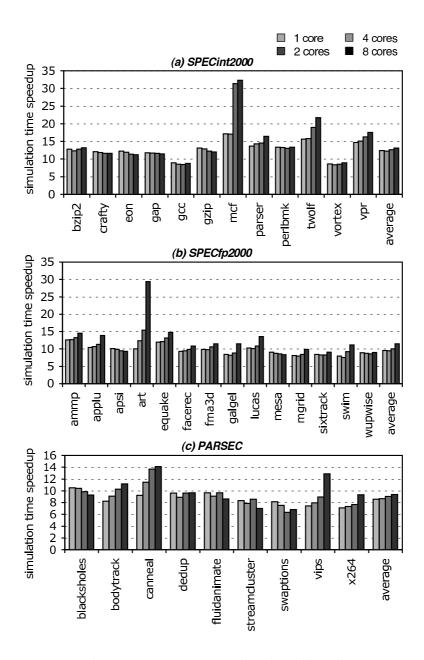

De gemiddelde fout op de prestatieschatting voor een chip-multiprocessor met één, twee, vier en acht kernen bedraagt respectievelijk 2.1%, 5.6%, 6.3% en 7.3%, terwijl de simulatie gemiddeld één tot vier grootteordes versneld wordt. Ondanks deze absolute fouten observeren we dezelfde prestatietrends met statistische simulatie als met cyclusgetrouwe simulatie. Bijvoorbeeld, statistische simulatie leidt tot dezelfde conclusie wanneer we de afweging maken tussen het aantal kernen enerzijds en de grootte van de gedeelde cache anderzijds. Bovendien identificeert het duidelijk welke benchmarks onderhevig zijn aan het delen van de cache tussen de verschillende processorkernen.

Intervalsimulatie is een nieuw, snel, nauwkeurig en eenvoudig te implementeren simulatieparadigma dat het abstractieniveau in architecturale simulatie verhoogt; het vervangt het cyclusgetrouwe model voor de processorkern door een mechanistisch analytisch model.

In het cyclusgetrouwe model worden de individuele instructies stap voor stap gevolgd doorheen de pijplijn van de superscalaire outof-order processor, terwijl de intervalsimulator de eigenlijke stroom van instructies doorheen de pijplijn beschouwt. Intervalsimulatie pakt het simulatieprobleem op twee fronten aan: het doel is om de simulatiesnelheid te verbeteren én het ontwerp van een simulator te vereenvoudigen, zonder al te veel aan nauwkeurigheid in te boeten.

De inzichten verkregen uit intervalanalyse laten ons toe om nauwkeurig de timing van instructies te modelleren. De basis voor dit mechanistisch analytisch model is dat in een superscalaire out-of-order processor de instructies vlot doorheen de pijplijn stromen in afwezigheid van missers. Missers (cachemisser, foutief voorspelde sprong, etc.) delen de instructiestroom op in geïsoleerde intervallen; dit is het best waarneembaar in de dispatch-trap van de pijplijn. De analytische modellen voor de individuele kernen raadplegen de sprongvoorspellingen de geheugenhiërarchiesimulatoren om de missers en de bijhorende latenties te bepalen – de lengte van een interval is afhankelijk van het type en de latentie van de misser. Zowel de prestatie op niveau van de processorkern als op niveau van het gehele systeem wordt bepaald door de lengte van deze intervallen, wat op zijn beurt de timing van toekomstige missers zal bepalen.

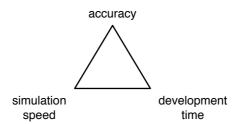

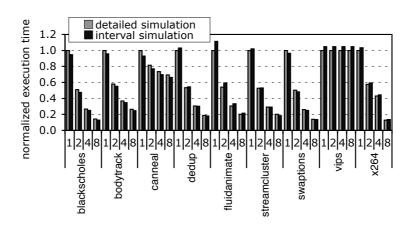

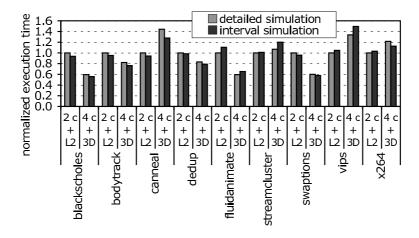

Onze experimentele resultaten tonen aan dat intervalsimulatie nauwkeurig is; we melden een gemiddelde schattingsfout van 4.6% voor de full-system simulatie van de meerdradige PARSEC benchmarks. Bovendien leidt intervalsimulatie tot correcte beslissingen in praktische studies, terwijl de simulatie een grootteorde sneller is dan de cyclusgetrouwe simulatie. Tevens is intervalsimulatie makkelijk te implementeren; ons model telt niet meer dan duizend regels code, in plaats van tienduizenden regels code in cyclusgetrouwe simulatoren. Aldus kunnen we besluiten dat intervalsimulatie een goede afweging maakt tussen ontwikkelingstijd, simulatietijd en nauwkeurigheid.

## **Summary**

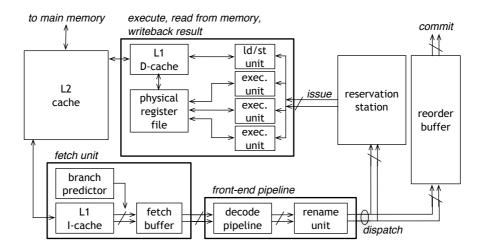

Designing a microprocessor is extremely time-consuming: it can take up to seven years before a next-generation processor hits the market. Computer architects heavily rely on cycle-level (and in many cases truly cycle-accurate) simulators in various stages of the design of a new processor, e.g., to drive high-level design decisions during early stage design space exploration. Architectural simulators model the microarchitecture in software, at some level of abstraction. The benefit of architectural simulators is that they yield relatively accurate performance results, are highly parameterizable and are very flexible to use. The downside, however, is that they are at least three or four orders of magnitude slower than real hardware execution.

While this is true for single-core superscalar out-of-order processor simulation, the current trend towards chip-multiprocessors or multicore processors, only exacerbates the problem. A multicore processor combines several cores on a single chip, sharing some resources such as last-level caches, off-chip bandwidth, main memory, etc. Co-executing threads affect each other's performance through the shared resources, e.g., conflict misses due to cache sharing may cause some threads to make slower progress than others. Moreover, changes in the microarchitecture may change which parts of the threads execute together, which in turn may lead to different conflict behavior and thus different relative progress rates for the co-executing threads. This tight performance entanglement between co-executing threads makes it hard to model performance of a multicore processor. As the number of cores on a multicore processor increases, simulation speed has become a major concern in computer architecture research and development.

Researchers and computer designers are well aware of the (multicore) simulation problem and have been proposing various methods for coping with it. In this dissertation, we propose and evaluate two simulation techniques, namely statistical simulation and interval simuxii SUMMARY

lation, which both reduce the simulation time significantly.

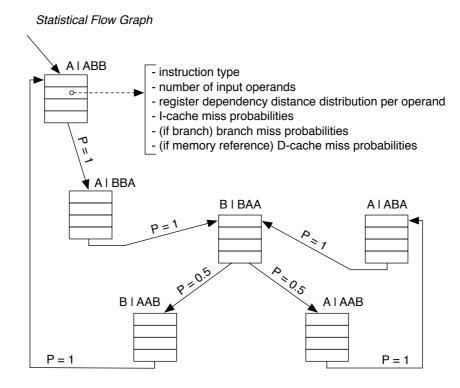

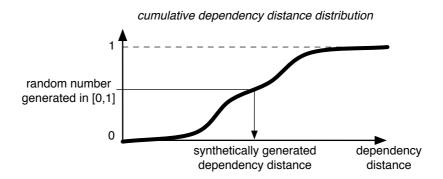

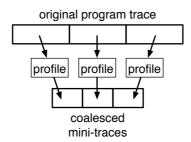

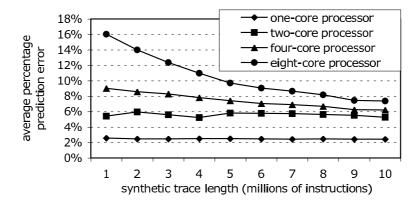

Statistical simulation. The basic idea behind statistical simulation is to speedup the simulation by reducing the dynamic instruction count. Essentially, statistical simulation is performed in three steps. First, we measure a statistical profile of a program execution through functional simulation or through profiling; a statistical profile collects a number of program execution characteristics, such as instruction mix, interinstruction dependence distributions, branch behavior information and memory behavior information. These statistics are then used to build a synthetic trace; this synthetic trace exhibits the same execution characteristics as the original program trace by construction, but it is much smaller in terms of its dynamic instruction count. Simulating this synthetic trace then yields a performance estimate. Given its short length (on the order of a couple millions of instructions), simulating a synthetic trace is done very quickly.

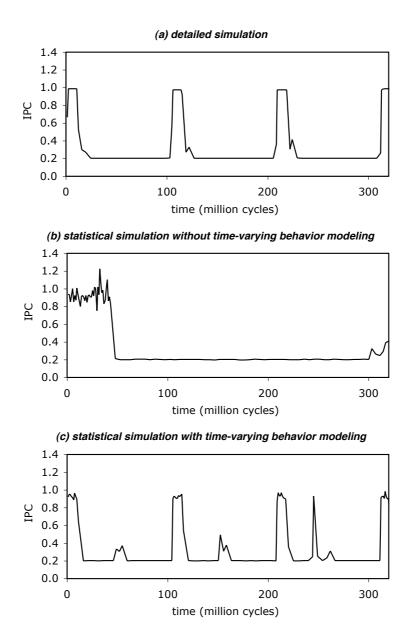

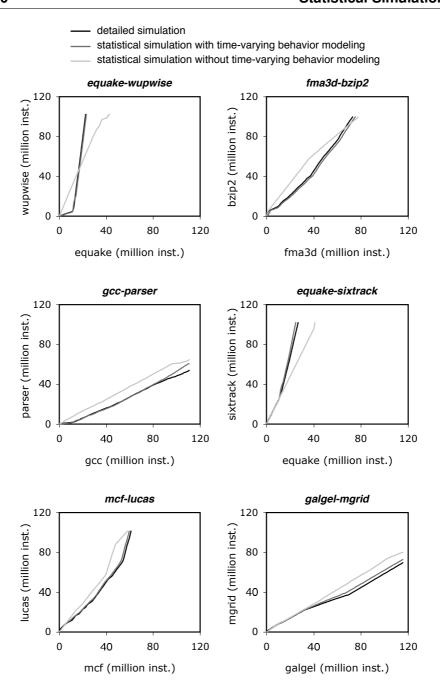

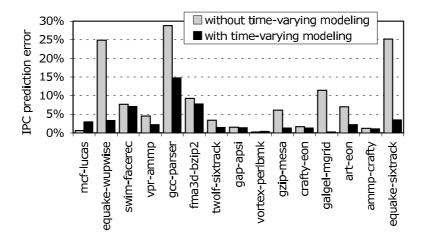

We make two contributions to the statistical simulation paradigm. First, we improve statistical simulation for single-core processors by accurately modeling the memory data flow in order to capture memorylevel parallelism, secondary miss events, and load/store aliasing and bypassing. Second, we extend the statistical simulation paradigm to chip-multiprocessors running multiprogram workloads in order to capture the conflict behavior in shared resources. This requires that we model accesses to the memory hierarchy in a microarchitectureindependent way, using metrics as memory location reuse distance and stack distance. Moreover, microarchitecture-independent memory data flow modeling allows to evaluate more microarchitectural design points based on a single statistical profile, and thus improves the applicability of statistical simulation. Furthermore, we show that in case of multicore simulation it is important to accurately model time-varying program execution behavior, i.e., overall performance is affected by the phase behavior of the co-executing programs.

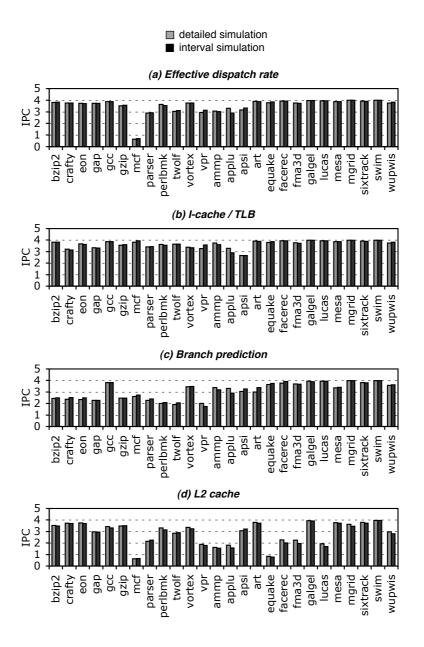

Both contributions make statistical simulation a fast and accurate solution to the multicore simulation problem, and make it a viable simulation approach to chip-multiprocessor design space exploration. For our baseline superscalar out-of-order architecture, we obtain an average overall performance estimation error of 2.1% for a single-core, 5.6% for a two-core, 6.3% for a four-core, and 7.3% for an eight-core processor, while achieving a simulation speedup of one order of magnitude. Despite these absolute errors, the same design space performance

trends are observed with statistical simulation as with cycle-accurate simulation. For example, statistical simulation leads to the same conclusion when making a trade-off between the number of cores on a chip and the size of the shared last-level cache. In addition, it clearly identifies which benchmarks are susceptible to cache sharing.

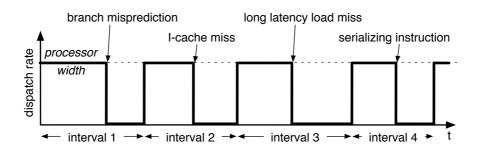

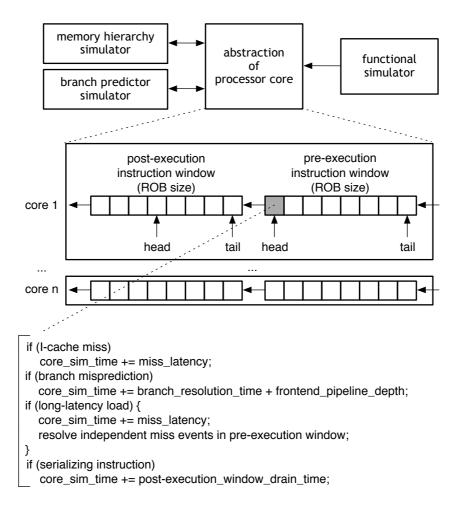

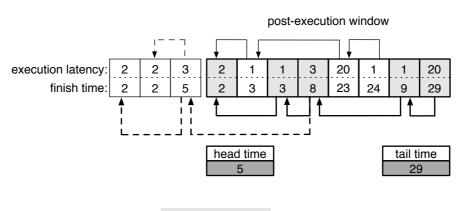

Interval simulation. Interval simulation is a novel, fast, accurate and easy-to-implement multicore simulation paradigm that raises the level of abstraction in architectural multicore simulation, i.e., it replaces the core-level cycle-accurate simulation model by a mechanistic analytical model. The core-level model of a truly cycle-accurate simulator tracks the individual instructions as they propagate through the pipeline. On the other hand, an interval simulator considers the stream of instructions through the dispatch stage of the pipeline. Interval simulation tackles the multicore simulation problem on two fronts: it reduces both the development and evaluation time, while not compromising accuracy too much.

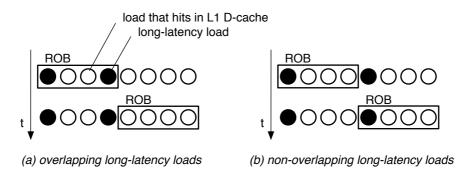

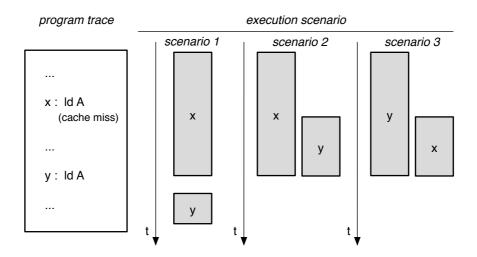

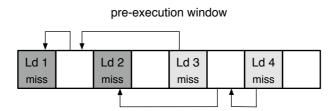

Insights from interval analysis enable us to accurately model the timing of the instructions. The basis for this mechanistic analytical model is that a superscalar out-of-order core can smoothly stream instructions through its pipeline in the absence of miss events. Miss events however divide the smooth streaming of instructions into so called intervals; this is most clearly observed in the dispatch behavior of a program. The analytical timing models for the individual cores consult branch predictor, memory hierarchy and interconnection network simulators to derive miss events and their latencies. By analyzing the types of miss events and their latencies, we can derive the length of each interval, which determines core-level and system-level performance. The estimated core-level performance, in turn, drives the timing of (future) miss events.

Our experimental results show that interval simulation is fairly accurate; we report an average error of 4.6% for the multithreaded PAR-SEC benchmarks running in full-system simulation mode. Moreover, interval simulation leads to correct design decisions in practical design studies, while being one order of magnitude faster compared to cycle-accurate simulation. In addition, interval simulation is easy to implement; our model requires no more than one thousand lines of code, whereas a fully detailed simulator can easily consist of tens of thousand lines of code. Therefore, interval simulation makes a good balance between development time, simulation speed and accuracy.

xiv SUMMARY

# **Contents**

|   | Ned  | lerland | se samenvatting                                     | vii |

|---|------|---------|-----------------------------------------------------|-----|

|   | Eng  | lish Su | mmary                                               | xi  |

| 1 | Intr | oductio | on                                                  | 1   |

|   | 1.1  | Micro   | processor design challenges                         | 1   |

|   |      | 1.1.1   | Trends in single-core processor technology          | 2   |

|   |      | 1.1.2   | The shift towards chip-multiprocessors              | 4   |

|   |      | 1.1.3   |                                                     | 5   |

|   |      | 1.1.4   | Workload composition                                | 6   |

|   | 1.2  | Focus   | and contributions in this dissertation              | 6   |

|   |      | 1.2.1   | Statistical simulation                              | 6   |

|   |      | 1.2.2   | Contribution #1: Accurate memory data flow          |     |

|   |      |         | modeling in statistical simulation                  | 7   |

|   |      | 1.2.3   | Contribution #2: Multicore statistical simulation . | 8   |

|   |      | 1.2.4   | Contribution #3: Interval simulation                | 9   |

|   | 1.3  | Thesis  | soutline                                            | 10  |

| 2 | Arc  | hitectu | ral Simulation                                      | 11  |

|   | 2.1  | Funct   | ional simulation and full-system simulation         | 12  |

|   | 2.2  | Specia  | alized cache and branch predictor simulation        | 13  |

|   | 2.3  |         | driven and execution-driven cycle-accurate simu-    |     |

|   |      | lation  |                                                     | 14  |

|   | 2.4  | Accel   | erating simulation                                  | 15  |

|   |      | 2.4.1   | Sampled simulation                                  | 15  |

|   |      | 2.4.2   | Statistical simulation                              | 15  |

|   |      | 2.4.3   | Analytical modeling                                 | 16  |

|   |      | 2.4.4   | Parallelized and/or hardware-accelerated simu-      |     |

|   |      |         | lation                                              | 16  |

|   |      | 2 4 5   | Interval simulation                                 | 17  |

xvi CONTENTS

|   | 2.5   | Overv   | view and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18 |

|---|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3 | Stat  | istical | Simulation: State-of-the-Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19 |

| _ | 3.1   |         | e-core statistical simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19 |

|   | 0.1   | 3.1.1   | Statistical profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 |

|   |       | 3.1.2   | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

|   |       | 3.1.3   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |

|   | 3.2   |         | ssion on applicability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 |

|   | 3.3   |         | work in statistical modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27 |

| 4 | Acc   | urate N | Memory Data Flow Modeling in Statistical Simula-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| _ | tion  |         | 2000007 2 000 2 2000 2 2000 2000 2 2000 2000 2 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 2000 20000 2000 2000 2000 2000000 | 31 |

|   | 4.1   | Three   | shortcomings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 |

|   | 4.2   |         | e miss correlation modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32 |

|   | 4.3   |         | after-write memory dependences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35 |

|   | 4.4   |         | red hits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36 |

|   | 4.5   |         | imental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38 |

|   | 4.6   | -       | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41 |

|   |       | 4.6.1   | Simulation speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41 |

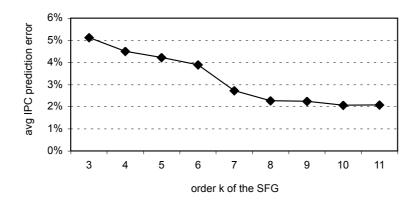

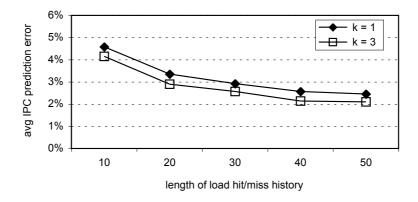

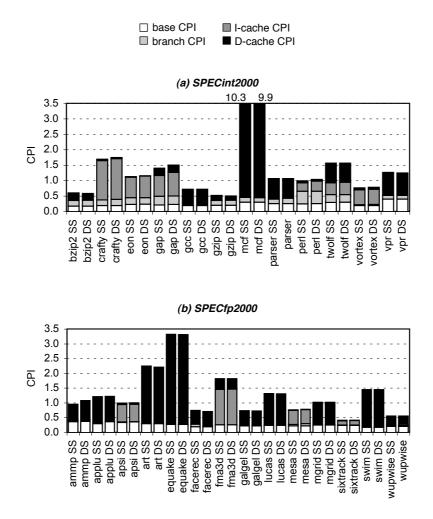

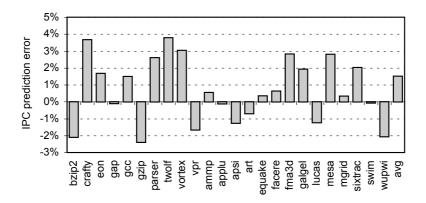

|   |       | 4.6.2   | Performance prediction accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42 |

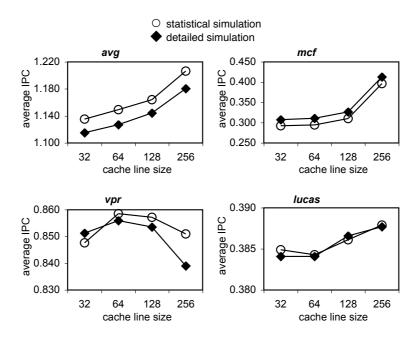

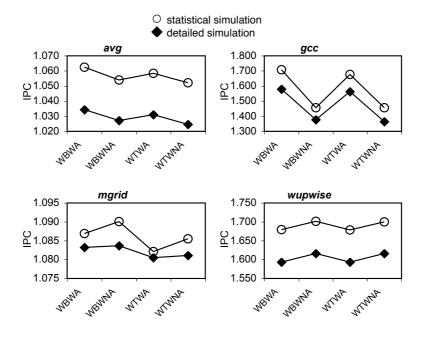

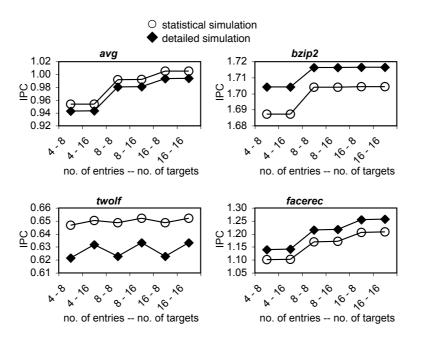

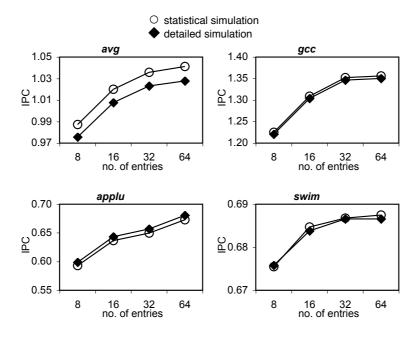

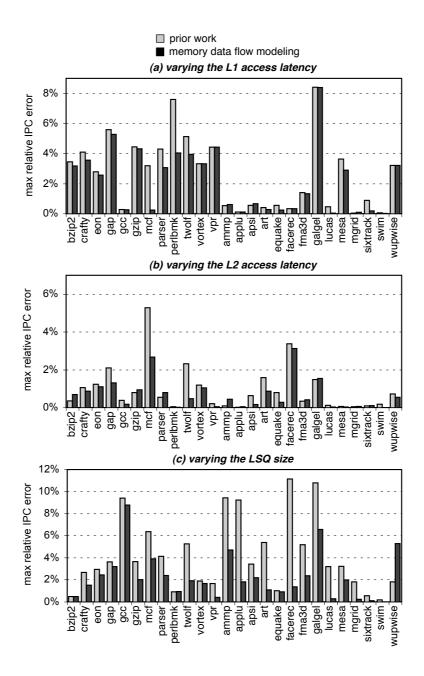

|   |       | 4.6.3   | Sensitivity to cache hierarchy parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52 |

|   |       | 4.6.4   | , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55 |

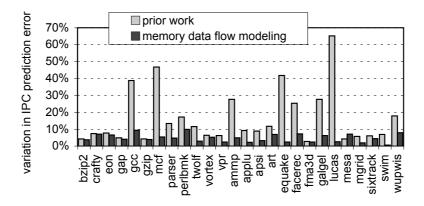

|   |       | 4.6.5   | Error distribution across the design space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57 |

|   |       | 4.6.6   | Design space exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58 |

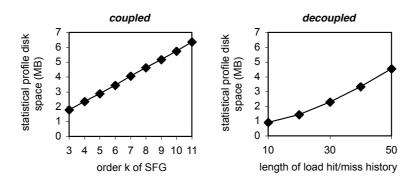

|   |       | 4.6.7   | Storage requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58 |

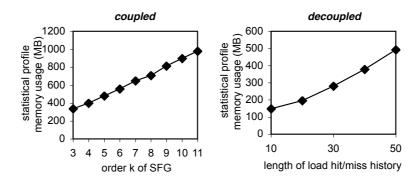

|   |       | 4.6.8   | Memory usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59 |

|   | 4.7   | Sumn    | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60 |

| 5 | Chi   | p-Mult  | iprocessor Design Space Exploration through Sta-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -  |

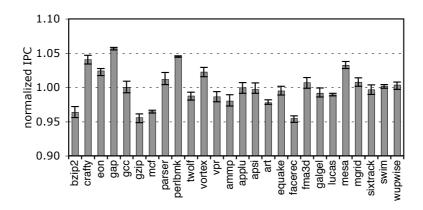

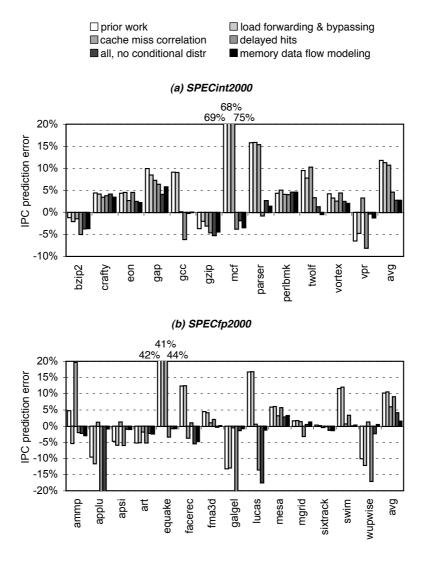

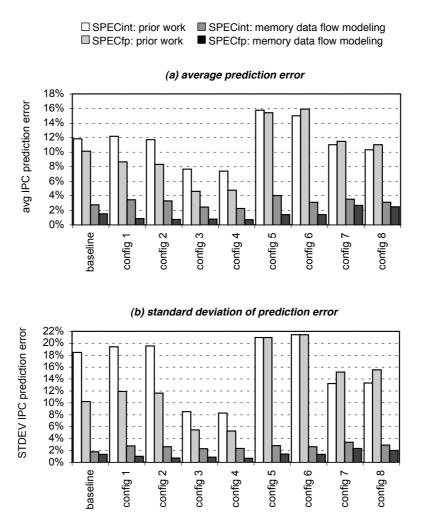

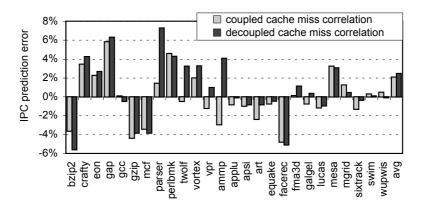

|   | tisti | cal Sin | nulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |