# Effect of mask grid on SOI arrayed waveguide grating performance

S. Pathak\*, M.Vanslembrouck, P. Dumon, D. Van Thourhout and W. Bogaerts

\*Photonics Research Group (INTEC), Ghent University - imec,

Sint-Pietersnieuwstraat 41, B-9000 Ghent, Belgium

Email: Shibnath.Pathak@intec.UGent.be

Abstract—We studied the impact of the lithography mask grid on the performance of silicon AWGs, and show a dramatic improvement in crosstalk of 5dB when going from a 5nm to a 1nm grid.

#### I. Introduction

Arrayed waveguide gratings (AWGs) are one of the commonly used devices for wavelength multiplexing [1]. However, in silicon, AWGs have always lagged in performance compared to the other techniques, such as silica [2] and InP [3]. While silicon AWGs can be much smaller because of the high refractive index contrast, the same high index contrast gives rise to phase errors and other parasitics which contribute to the overall crosstalk of the device. In general, silicon AWGs achieve crosstalk levels of -20dB, with the best devices showing -25dB crosstalk [4]–[6].

## II. PHASE ERRORS

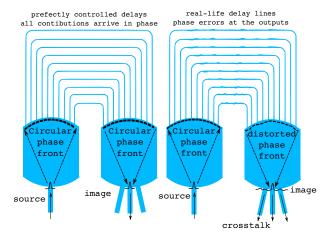

The key contributor to crosstalk in silicon AWGs is the phase errors that are accumulated along the delay lines. When the distributed light in the waveguides recombines in the free propagation region (FPR), phase errors will translate in ripples in the optical phase front. These ripples will induce sidelobes and overall crosstalk in the image at the output waveguides, resulting in optical power coupled to the wrong outputs. We can distinguish these phase errors in the delay lines into two categories: deterministic and stochastic errors. In the latter category we find sidewall roughness and line-width/thickness variations as key causes. Using wider waveguides in the delay sections can alleviate the impact of theses effects [4]–[7]. For the deterministic errors, we studied the effect of mask discretization on the performance of the AWG.

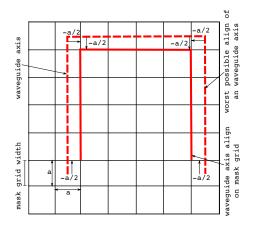

As the common design of our AWGs uses rectangular waveguide layouts [4]–[6] where the bend sections are generally identical between the delay lines, we first looked at the effect of the mask grid on the straight delay sections of the AWG. The effect is illustrated in Fig. 2. The path for the delay line is calculated along 3 sides of a rectangle (taking into account the length of the bends). During that calculation, the coordinates of the sides are calculated to high precision. However, during subsequent tape-out to a GDSII mask file, the coordinates are snapped to a fixed grid. In practice, we used a 5nm grid, which means the length deviations in each arm could be  $\pm 15$ nm, which translates in phase errors of  $\pm \pi/19$ . By going to a 1nm grid, these variations drop to  $\pm 3$ nm, or

Fig. 1. Schematic diagram of the AWG with ideal delay lines and with phase error affected delay lines.

phase errors of  $\pm \pi/96$ . While the grid snapping in our mask design is fairly random (a rounding error depending on the calculated delay length), it is a deterministic process: two identically designed AWGs will experience the same phase error contributions from grid snapping.

Fig. 2. The length deviation of a waveguides due to the grid snapping.

We studied the effect of phase errors through simulation and experimentally, by designing and simulating a set of identical AWGs on both a 1nm and a 5nm grid, and fabricated them side-by-side.

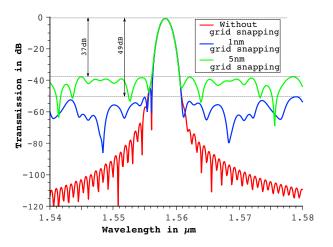

Fig. 3. Simulated transmission spectrum of  $16 \times 400 \text{GHz}$  AWG (8th channel) for 1nm, 5nm and without grid snapping.

# TABLE I COMPARISON OF MEASURED AWG INSERTION LOSS (IL, CENTER CHANNEL AND OUTER CHANNEL) AND CROSSTALK LEVEL BETWEEN 1NM AND 5NM MASK GRID DISCRETIZATION.

| Channels | Spacing | Area             | IL        | XT   | XT   | FSR  |

|----------|---------|------------------|-----------|------|------|------|

|          |         |                  |           | 5nm  | 1nm  |      |

|          | [GHz]   | $[\mu { m m}^2]$ | [dB]      | [dB] | [dB] | [nm] |

| 4        | 400     | 468 × 237        | -1.8 -2.2 | -22  | -27  | 19   |

| 8        | 400     | $490 \times 307$ | -1.3 -2.7 | -21  | -26  | 32   |

| 16       | 400     | 530 × 435        | -1.5 -3.5 | -21  | -26  | 54   |

#### III. SIMULATION

The AWGs are simulated by a semi-analytical model [5] integrated with our design software (IPKISS) [8]. As we want to illustrate the effect on the crosstalk due to the phase errors introduced by the grid snapping we didn't include any stochastic phase error due sidewall roughness.

Fig. 3 shows the simulated spectral response of the 8th channel of a  $16 \times 400 \text{GHz}$  AWG without grid snapping, and for 1nm and 5nm snapping. The simulation indicates, as expected, that the insertion loss will not be affected while the crosstalk floor will increase with increasing grid snapping. In the simulation we can see that the crosstalk is improved by 12 dB as we change the grid from 5nm to 1nm.

# IV. EXPERIMENT

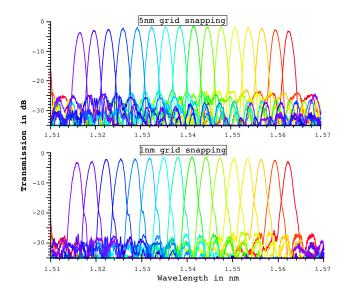

We also fabricated a set of identical AWG designs, but with a different mask discretization. Fig. 4 shows the measured spectral response of a  $16 \times 400 \text{GHz}$  AWG using 5nm and 1nm grid snapping. We see that the crosstalk is substantially higher compare to the simulated AWGs, because other crosstalk mechanisms are still present. But we do see a significant improvement for the 1nm mask grid: The crosstalk floor drops from -21dB for the 5nm grid to -26dB for the 1nm grid, making this the best published device with such a high channel count. Other AWGs, with different channel counts, show similar improvements, as listed in table I.

Fig. 4. Experimental transmission spectrum of  $16 \times 400 \text{GHz}$  AWG using 5nm and 1nm grid snapping.

## V. CONCLUSION

We demonstrate a significant improvement in silicon AWGs by going from a 5nm mask discretization to a 1nm mask grid. We see an experimental improvement of 5dB in crosstalk due to snapping-related phase errors. We illustrated this with a 16  $\times$  400GHz AWG with -26dB crosstalk level by reducing the mask grid from 5nm to 1nm.

#### ACKNOWLEDGMENT

Part of this work was carried out in the framework of IMEC's *Optical IO* Industrial Affiliation Program.

#### REFERENCES

- [1] C. Dragone, "An n×n optical multiplexer using a planar arrangement of two star couplers," *Photo. Tech. Lett.*, vol. 3, pp. 812–815, Sept 1991.

- [2] R. Adar, C. Henry, C. Dragone, R. Kistler, and M. Milbrodt, "Broad-band array multiplexers made with silica waveguides on silicon," *J. Lightwave Tech.*, vol. 11, pp. 212 –219, Feb 1993.

- [3] H. Bissessur, F. Gaborit, B. Martin, P. Pagnod-Rossiaux, J.-L. Peyre, and M. Renaud, "16 channel phased array wavelength demultiplexer on inp with low polarisation sensitivity," *Electron. Lett.*, vol. 30, pp. 336 –337, Feb 1994.

- [4] W. Bogaerts, S. Selvaraja, P. Dumon, J. Brouckaert, K. De Vos, D. Van Thourhout, and R. Baets, "Silicon-on-insulator spectral filters fabricated with cmos technology," *J. Sel. Top. Quant. Electron.*, vol. 16, pp. 33 –44, Jan-Feb. 2010.

- [5] S. Pathak, M. Vanslembrouck, P. Dumon, D. V. Thourhout, and W. Bo-gaerts, "Optimized silicon awg with flattened spectral response using an mmi aperture," *J. Lightwave Tech.*, vol. 31, pp. 87–93, Jan 2013.

- [6] S. Pathak, M. Vanslembrouck, P. Dumon, D. V. Thourhout, and W. Bogaerts, "Compact soi-based polarization diversity wavelength demultiplexer circuit using two symmetric awgs," *Opt. Express*, vol. 20, pp. B493–B500, Dec 2012.

- [7] K. Sasaki, F. Ohno, A. Motegi, and T. Baba, "Arrayed waveguide grating of 70x60 um2 size based on Si photonic wire waveguides," *Electrn. Lett.*, vol. 41, no. 14, pp. 801–802, 2005.

- [8] W. Bogaerts, P. Dumon, E. Lambert, M. Fiers, S. Pathak, and A. Ribeiro, "Ipkiss: A parametric design and simulation framework for silicon photonics," in 9th IEEE Int. Conf. Group IV Photonics, pp. 30–32, Aug 2012.