# Stochastic Macromodeling for Hierarchical Uncertainty Quantification of Nonlinear Electronic Systems

D. Spina\*, D. De Jonghe<sup>+</sup>, F. Ferranti<sup>†</sup>, G. Gielen<sup>+</sup>, T. Dhaene\*, L. Knockaert\*, G. Antonini<sup>‡</sup>

\*Dept. of Information Technology, Internet Based Communication Networks and Services (IBCN)

Ghent University – iMinds, Gaston Crommenlaan 8 Bus 201, 9050 Ghent, Belgium.

Email: {domenico.spina; tom.dhaene; luc.knockaert}@intec.ugent.be

+MICAS Laboratories, ESAT, KU Leuven, B-3001 Leuven, Belgium.

E-mail: gielen@esat.kuleuven.be

<sup>†</sup>Dept. of Fundamental Electricity and Instrumentation, Vrije Universiteit Brussel, Pleinlaan 2, B-1050 Brussels, Belgium.

Email: francesco.ferranti@vub.ac.be

<sup>‡</sup>UAq EMC Laboratory, Dipartimento di Ingegneria Industriale e dell'Informazione e di Economia, Università degli Studi dell'Aquila, Via G. Gronchi 18, 67100, L'Aquila, Italy, Email: giulio.antonini@univaq.it.

Abstract—A hierarchical stochastic macromodeling approach is proposed for the efficient variability analysis of complex nonlinear electronic systems. A combination of the Transfer Function Trajectory and Polynomial Chaos methods is used to generate stochastic macromodels. In order to reduce the computational complexity of the model generation when the number of stochastic variables increases, a hierarchical system decomposition is used. Pertinent numerical results validate the proposed methodology.

# I. Introduction

The increasing complexity, density and bandwidth of modern electronic circuits require an efficient and accurate modeling of the effects of geometrical or electrical parameter variability on the system performances [1], [2]. The variability has several sources, ranging from the manufacturing process to temperature fluctuations and aging, and requires the electrical response to be addressed from a statistical standpoint in order to properly characterize signal integrity issues. The Monte-Carlo (MC) method is the standard for the variability analysis due to its accuracy and robustness. A main drawback of the MC method is the required high number of simulations to achieve a suitable level of accuracy. Since the simulations of complex high-speed circuits are often computationally expensive, the MC approach becomes very demanding in terms of both memory and computational time.

Polynomial Chaos (PC) methods [3]–[8] represent a reliable alternative to MC-based techniques for variability analysis. In PC-based approaches, a stochastic process is represented as a series of orthogonal polynomials with suitable coefficients. The PC methodology has been extensively applied to the variability analysis of linear systems, such as lumped elements circuits [9], [10], multiconductor transmission lines [11]–[13] and generic linear multiport systems [14]. Also, the PC methodology has been proposed for the variability analysis

of nonlinear electronic circuits [15]–[18]. Recently in [18], a method has been proposed for the variability analysis of complex nonlinear systems based on the calculation of the PC expansion of Transfer Function Trajectory (TFT) [19]–[21] models. This method can be applied to a broad range of nonlinear circuits thanks to the modeling power of the TFT and it offers the efficiency and accuracy of the PC approach in performing the variability analysis. However, the generation of a PC-TFT model may become computationally expensive when the number of stochastic variables of interest increases.

Therefore, in order to reduce the computational cost needed to generate PC-TFT models in the case of a high number of stochastic variables, a hierarchical system decomposition is proposed in this paper. Subdividing a system into subsystems and generating PC-TFT models of the subsystems instead of the complete system leads to decrease the complexity of the model generation phase. This paper is structured as follows. First, an overview of the PC-TFT approach and the related modeling complexity is given in Section II. A relevant numerical example is presented in Section III to validate the proposed technique. Conclusions are given in Section IV.

# II. STOCHASTIC MACROMODELING OF NONLINEAR SYSTEMS

The goal of the stochastic macromodeling technique [18] is to express the time-domain variability of a nonlinear system which depends on a vector of normalized random variables  $\xi$  via the PC expansion [3]–[8] of the corresponding TFT model [19]–[21] implemented as a multi-channel Wiener system with a linear time-invariant block at the input and a nonlinear readout map. The resulting model is called PC-TFT model

and can be expressed as [18]:

$$\begin{cases} \dot{\widehat{\boldsymbol{x}}}(t) = & \widehat{\boldsymbol{A}}\widehat{\boldsymbol{x}}(t) + \widehat{\boldsymbol{B}}\boldsymbol{u}(t) \\ \widehat{\boldsymbol{y}}(t,\boldsymbol{\xi}) = & \sum_{i=0}^{M} \left(\widehat{\boldsymbol{C}}_{i}(\widehat{\boldsymbol{x}})\widehat{\boldsymbol{x}}(t) + \widehat{\boldsymbol{D}}_{i}(\widehat{\boldsymbol{x}})\right)\varphi_{i}(\boldsymbol{\xi}) \end{cases}$$

(1)

where the elements  $\varphi_i(\xi)$  for  $i=0,\ldots,M$ , are polynomial functions of the random variables  $\xi$ , referred as basis functions in the PC theory. In particular, the choice of the basis functions depends on the the distribution of the random variables in the vector  $\xi$  and, if such variables are independent, it is possible to express the number M+1 of basis functions in (1) as a function of the number Z of random variables and the maximum degree P of the polynomials considered as [4]:

$$M + 1 = \frac{(Z+P)!}{Z!P!}. (2)$$

Thanks to the properties of the PC expansion, it is possible to prove that (1) can be rewritten as M+1 independent systems of ordinary differential equations (ODEs) [18]:

$$\begin{cases} \dot{\widehat{\boldsymbol{x}}}(t) &= \widehat{\boldsymbol{A}}\widehat{\boldsymbol{x}}(t) + \widehat{\boldsymbol{B}}\boldsymbol{u}(t) \\ \widehat{\boldsymbol{y}}_{i}(t) &= \widehat{\boldsymbol{C}}_{i}(\widehat{\boldsymbol{x}})\widehat{\boldsymbol{x}}(t) + \widehat{\boldsymbol{D}}_{i}(\widehat{\boldsymbol{x}}) \end{cases} \quad \text{for } i = 0, \dots, M;$$

(3)

where the elements  $\hat{y}_i(t)$  are the coefficients of the PC expansion of the system output in the form:

$$\widehat{\boldsymbol{y}}\left(t,\boldsymbol{\xi}\right) = \sum_{i=0}^{M} \widehat{\boldsymbol{y}}_{i}\left(t\right) \varphi_{i}(\boldsymbol{\xi}). \tag{4}$$

The main advantage of the PC model (4) is the accurate and efficient representation of the system variability in the time-domain. Indeed, stochastic moments like the mean  $\mu_y$  and variance  $\sigma_y^2$  of the system output can be expressed via simple analytical formulas [4]:

$$\boldsymbol{\mu}_{\boldsymbol{y}}\left(t\right) = \widehat{\boldsymbol{y}}_{0}\left(t\right) \tag{5}$$

$$\boldsymbol{\sigma_y}^2(t) = \sum_{i=1}^{M} \widehat{\boldsymbol{y}}_i^2(t) < \varphi_i(\boldsymbol{\xi}), \varphi_i(\boldsymbol{\xi}) >$$

(6)

where the symbol  $<\cdot>$  represents the scalar product operator and the elements  $<\varphi_i(\xi),\varphi_i(\xi)>$  for  $i=0,\ldots,M$  can be computed solving (often analytically) suitable multidimensional integrals [3]–[8]. Apart from all moments, also complex stochastic functions, such as the probability density function (PDF) and the cumulative density function (CDF), can be computed following standard analytical formulas or numerical schemes [6].

The PC-TFT technique [18] combines the modeling power of the TFT modeling approach with the accurate and efficient representation of the system variability given by the PC expansion resulting in a robust, flexible and powerful modeling technique. It is worth to notice that the stability of the PC-TFT model in (1), fundamental property for time-domain simulations, can be guaranteed. Furthermore, any nonlinear system that can be described by a quasi-linear parameter-varying representation [22] can be modeled with the proposed PC-TFT technique, making it applicable to a broad range of nonlinear systems, including strongly nonlinear ones. Finally, the M+1 systems of equations (3) are independent: it is possible to solve them in parallel adopting standard numerical

methods (e.g. Backward Euler). Note that, it is possible to use numerical methods that minimize the total number of time samples needed by using a non-uniform sampling strategy in the time domain.

However, the computational cost to build a PC-TFT model is strongly dependent on the number of basis function M+1 used in (1). In particular, the calculation of the PC-TFT model (1) is a two-step process: first, a discrete number of TFT models with common poles is computed, corresponding to a discrete set of samples of the random variables  $\boldsymbol{\xi}$  and of the state space  $\widehat{\boldsymbol{x}}(t)$ , indicated as  $[\boldsymbol{\xi}_r]_{r=1}^K$  and  $[\widehat{\boldsymbol{x}}_j]_{j=1}^T$ , respectively. Next, the PC-TFT model in the form (1) is obtained using the linear regression method [4]. It is important to notice that, the initial number of samples K of the random variables  $\boldsymbol{\xi}$  is chosen according to:

$$K \approx 2(M+1) = 2\frac{(Z+P)!}{Z!P!}.$$

(7)

Hence, the number of initial samples in the stochastic space K depends heavily on the number of random variables Z considered and the maximum degree of the polynomials P used in (1). Consequently, the efficiency of a PC-TFT model can be greatly undermined if the computational cost to generate such a model becomes too high.

A hierarchical system decomposition is proposed in this paper to limit the computational complexity needed to generate a PC-TFT model when the number of stochastic variables increases. The main idea is to exploit the possibility of subdividing a system into subsystems and generate PC-TFT models of the subsystems instead of the complete system.

# III. NUMERICAL EXAMPLE

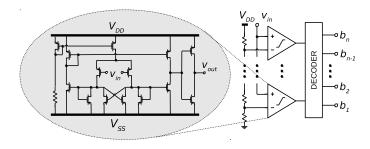

The proposed PC-TFT model is demonstrated by hierarchically modeling a flash ADC circuit in the I3T50 technology, see Fig. 1. Here, the comparator subblock was identified as a repetitive structure and it is modeled using the PC-TFT technique. The analog input signal and the reference voltage at the input of the comparator are the deterministic inputs to the model. The stochastic variables are selected based upon sensitivity screening of each stochastic variable occurring in the comparator towards the output performance. This procedure yields two dominant stochastic variables (Z = 2) that need to be included in the model for this technology, namely the variation of the threshold voltages of the input transistors. These stochastic variations introduce an input-referred offset to the comparator, which affects the effective number of bits (ENOB) of the overall ADC circuit [23]. It is assumed that the stochastic variables have a normal distribution, which is verified experimentally.

A PC model of the output mapping defined by  $C(\cdot)$ ,  $D(\cdot)$  is computed using a fifth-order polynomial chaos expansion (P=5) for accuracy reasons). Hence, the corresponding number of basis functions in the PC-TFT model is M+1=21, according to (2), which leads to a minimum number of samples in the stochastic space equal to  $K\approx 2(M+1)=42$ , according to (7). A Wiener PC-TFT model was computed using a 7-by-7 regular grid of the two stochastic variables  $\xi$  in a range between  $\pm 4\sigma$ , so K=49 SPICE simulations are required for each of the reference voltages. From the

MNA data, 49 piecewise TFT models are computed. The computation of the 49 TFT models took 529s including the training simulations. The computation of the PC model of the output mapping  $\widehat{C}_i(\cdot), \widehat{D}_i(\cdot)$  in (3) took 0.347s and the PC model (4) of the comparator output  $\widehat{y}_i$  took 0.655s.

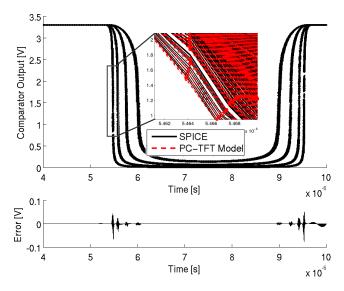

The time-domain response of the comparator subblock in SPICE and of the PC-TFT model are given in Fig. 2 for 40001 transient simulations with MC sampling of the process variations that are included in the technology data of the foundry. The models were then simulated in MATLAB and compared with circuit-level SPICE. All calculations were performed on a 4GHz dual quad-core CPU with 12GB RAM. It can be seen that the model and the original circuit are almost indistinguishable. For the sake of clarity, the difference between both sets of waveforms is also plotted. The maximum difference never exceeds 0.1V. The evaluation of the 40001MC samples took 4210s in SPICE and only 0.532s using the PC-TFT technique. Hence, a simulation speedup of 7913X was achieved for the comparator subblock. More importantly, the PC-TFT model provides an analytical expression to compute stochastic moments, such as the mean  $\mu$  and the variance  $\sigma^2$  (see equations (5) and (6)) of the output waveforms. Hence, the mean and the standard deviation of the waveform at each time point can be calculated analytically with the PC-TFT model, which only required an additional 0.065s to compute.

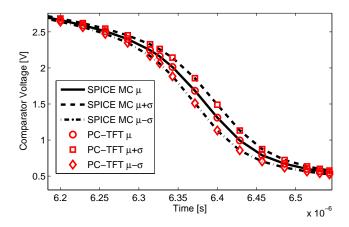

The effectiveness of this approach is illustrated by comparing the mean  $\mu$  and the range  $\mu \pm \sigma$  of the output of the comparator using both the 40001 Monte-Carlo simulations in SPICE and using the corresponding analytical expressions of the PC-TFT model. From Fig. 3 it is clear that the analytical expression is very accurate without the need for a large set of Monte-Carlo samples; only K=49 grid samples are required for computing the PC-TFT model. Next, a 3-bit ADC system is simulated by stacking the comparators as in Fig. 1. Of course, it is possible to increase the complexity of the system by including more values of the reference voltage at the expense of model computation cost. The accuracy of an ADC is typically described by the ENOB, which is in turn determined by the integral and differential nonlinearity of the converter (INL and DNL respectively) [23]:

$$ENOB = \log_{2} \left[ \frac{V_{in,min} - V_{in,max}}{max (2 \cdot INL, DNL)} \right]$$

(8)

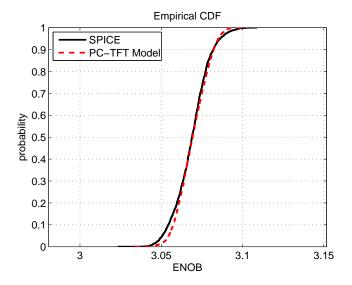

The cumulative probability plot of the ENOB of the system is given in Fig. 4 for the original SPICE simulation and the PC-TFT model for  $40001~\mathrm{MC}$  samples. The evaluation

Fig. 1. Schematic representation of a flash ADC and of the comparator building block.

Fig. 2. Top: Time-domain waveforms of the comparator subblock modeled with SPICE and the TFT model for 4 different reference voltages and 1000 Monte-Carlo samples. Bottom: the difference or error between the PC-TFT model and the SPICE simulation.

Fig. 3. The mean  $\mu$  and the range  $\mu\pm\sigma$  of the output voltage of a comparator subblock. The black lines are computed using 40001 Monte-Carlo simulations in SPICE. The red lines are computed analytically from the PC-TFT model.

time in SPICE took 8509s while the stochastic moments of the PC-TFT model were readily available in analytical form. The evaluation of the four PC-TFT models in the  $40001~\rm MC$  samples only took 2.156s, which corresponds to a simulation speedup of 3946X over SPICE.

The results of the PC-TFT model presented here agree very well with the results that are predicted by SPICE for the subblock. Also, a good correspondence between the hierarchical model and the full system simulations is observed. It is important to notice that the adoption of a hierarchical modeling approach greatly improves the efficiency of the proposed method. Indeed, the behaviour of the 3-bit ADC system in Fig. 1 depends on 8 independent random variables, namely the treshold voltages of each comparator subblock. Using again a fifth-order PC expansion (P=5), the computation of the corresponding PC-TFT model (1) would require M+1= 1287 basis functions, according to (2), leading to a number of initial TFT models  $K \approx 2574$ , according to (7). The proposed hierarchical appraoch greatly reduces the modeling complexity,

Fig. 4. The effective number of bits (ENOB) for 40001 Monte-Carlo samples evaluated with the proposed PC-TFT model (red dashed line) and 1000 samples evaluated with a full SPICE simulation (black). The ENOB CDF represents the static accuracy of the converter under the influence of process variations.

since it requires only the computation of K=49 initial TFT models corresponding to M+1=21 basis functions for each comparator subblock.

#### IV. CONCLUSIONS

This paper has presented a hierarchical technique for the efficient variability analysis of complex nonlinear systems. A nonlinear system is decomposed into a set of subsystems to reduce the computational complexity needed to generate stochastic macromodels when the number of stochastic variables increases. The stochastic macromodel for each subsystem is based on the use of a PC expansion applied to the TFT description of the subsystem. Pertinent numerical results have validated the accuracy and efficiency of the proposed method.

### **ACKNOWLEDGMENTS**

This work has been funded by the Research Foundation Flanders (FWO-Vlaanderen). Francesco Ferranti is a Post-Doctoral Research Fellow of FWO-Vlaanderen.

## REFERENCES

- [1] Y. Liu and J.-S. Yuan, "CMOS RF Power Amplifier Variability and Reliability Resilient Biasing Design and Analysis," *IEEE Trans. Electron Devices*, vol. 58, no. 2, pp. 540–546, Feb. 2011.

- [2] J. S. Ochoa and A. C. Cangellaris, "Random-Space Dimensionality Reduction for Expedient Yield Estimation of Passive Microwave Structures," *IEEE Trans. Microw. Theory Tech.*, vol. 61, no. 12, pp. 4313– 4321, Dec. 2013.

- [3] G. Blatman and B. Sudret, "An adaptive algorithm to build up sparse polynomial chaos expansions for stochastic finite element analysis," *Probabilistic Engineering Mechanics*, vol. 25, no. 2, pp. 183 – 197, Apr. 2010.

- [4] M. S. Eldred, "Recent advance in non-intrusive polynomial-chaos and stochastic collocation methods for uncertainty analysis and design," in Proc. 50th AIAA/ASME/ASCE/AHS/ASC Structures, Structural Dynamics, and Materials Conference, Palm Springs, California, May 2009.

- [5] J. A. S. Witteveen and H. Bijl, "Modeling Arbitrary Uncertainties Using Gram-Schmidt Polynomial Chaos," in *Proc. 44th AIAA Aerospace Sciences Meeting and Exhibit*, no. AIAA-2006-896, Reno, Nevada, Jan. 2006.

- [6] A. Papoulis, Probability, Random Variables and Stochastic Processes. Mcgraw-Hill College, 1991.

- [7] C. Soize and R. Ghanem, "PHYSICAL SYSTEMS WITH RAN-DOM UNCERTAINTIES: CHAOS REPRESENTATIONS WITH AR-BITRARY PROBABILITY MEASURE," SIAM J. SCI. COMPUT., vol. 26, no. 2, pp. 395–410, Jul. 2004.

- [8] D. Xiu and G. E. Karniadakis, "The Wiener-Askey Polynomial Chaos for Stochastic Differential Equations," SIAM J. SCI. COMPUT., vol. 24, no. 2, pp. 619–644, Apr. 2002.

- [9] Q. Su and K. Strunz, "Stochastic Polynomial-Chaos-Based Average Modeling of Power Electronic Systems," *IEEE Trans. Power Electron.*, vol. 26, no. 4, pp. 1167 –1171, Apr. 2011.

- [10] K. Strunz, Q. Su, "Stochastic formulation of SPICE-type electronic circuit simulation using polynomial chaos," ACM Trans. Model. Comput. Simul., vol. 18, no. 4, pp. 501–507, Sep. 2008.

- [11] I. S. Stievano, P. Manfredi, F. G. Canavero, "Parameters Variability Effects on Multiconductor Interconnects via Hermite Polynomial Chaos," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 1, no. 8, pp. 1234–1239, Aug. 2011.

- [12] —, "Stochastic Analysis of Multiconductor Cables and Interconnects," *IEEE Trans. Electromagn. Compat.*, vol. 53, no. 2, pp. 501–507, May 2011.

- [13] D. Vande Ginste, D. De Zutter, D. Deschrijver, T. Dhaene, P. Manfredi, F. G. Canavero, "Stochastic Modeling Based Variability Analysis of On-Chip Interconnects," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 2, no. 7, pp. 1182 – 1192, Jul. 2012.

- [14] D. Spina, F. Ferranti, T. Dhaene, L. Knockaert, G. Antonini, and D. Vande Ginste, "Variability Analysis of Multiport Systems Via Polynomial-Chaos Expansion," *IEEE Trans. Microw. Theory Tech.*, vol. 60, no. 8, pp. 2329 –2338, Aug. 2012.

- [15] D. Lucor, C.-H. Su, and G. E. Karniadakis, "Generalized polynomial chaos and random oscillators," *Int. J. Numer. Meth. Engng*, vol. 60, no. 3, pp. 571–596, May 2004.

- [16] A. Monti, F. Ponci, and T. Lovett, "A polynomial chaos theory approach to the control design of a power converter," in *Proc. 35th Annual IEEE Power Electronics Specialists Conference (PESC)*, vol. 6, 20-25 Jun. 2004.

- [17] M. R. Rufuie, E. Gad, M. Nakhla, R. Achar, "Generalized Hermite Polynomial Chaos for Variability Analysis of Macromodels Embedded in Nonlinear Circuits," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 4, no. 4, pp. 673–684, Apr. 2014.

- [18] D. Spina, D. De Jonghe, D. Deschrijver, G. Gielen, L. Knockaert, and T. Dhaene, "Stochastic Macromodeling of Nonlinear Systems Via Polynomial Chaos Expansion and Transfer Function Trajectories," *IEEE Trans. Microw. Theory Tech.*, vol. 62, no. 7, pp. 1454–1460, Jul. 2014.

- [19] D. De Jonghe, G. Gielen, "Efficient Analytical Macromodeling of Large Analog Circuits by Transfer Function Trajectories," in *Proc. IEEE/ACM International Conference on Computer-Aided Design (ICCAD)*, 7-10 Nov. 2011, pp. 91–94.

- [20] —, "Characterization of Analog Circuits Using Transfer Function Trajectories," *IEEE Trans. Circuits Syst. I: Regular Papers*, vol. 59, no. 8, pp. 1796–1804, Aug. 2012.

- [21] D. De Jonghe, D. Deschrijver, T. Dhaene, G. Gielen, "Extracting analytical nonlinear models from analog circuits by recursive vector fitting of Transfer Function Trajectories," in *Proc. Europe Conference* & Exhibition in Design, Automation & Test (DATE), 18-22 Mar. 2013, pp. 1448–1453.

- [22] R. Tóth, Modeling and identification of linear parameter-varying systems. Springer, 2010.

- [23] R. Van De Plasche, Integrated Analog-to-Digital and Digital-to-Analog Converters. Kluwer Academic Publishers, 1994.