561936

="1.41047" variation="10001" continuous="false

4.16"

$1.410_{47}$ , variation  $\approx 21608$ , map  $\frac{1}{\sqrt{9}}$

# Network of Excellence on High Performance and Embedded Architecture and Compilation

16999<sub>1</sub> THE HIPEAC VISION

618987

GridNode id="node 02" Coordinate value="1" GridNodeBlock

id="node 03"

GridNodeBlock

Marc Duranton, Sami Yehia, Bjorn De Sutter, Koen De Bosschere, Albert Cohen, Babak Falsafi, Georgi Gaydadjiev, Manolis Katevenis, Jonas Maebe, Harm Munk, Nacho Navarro, Alex Ramirez, Olivier Temam, Mateo Valero

Q87238928399 (23.9) 49237

15678236

16824.FG

| Contents                                        | 1        |

|-------------------------------------------------|----------|

| Executive Summary                               | 3        |

| Introduction                                    | 5        |

| 1. Trends and Challenges                        | 7        |

| Societal Challenges for ICT                     | 8        |

| Energy                                          | 8        |

| Transport and Mobility                          | 8        |

| Health                                          | 9        |

| Aging population                                | 9        |

| Environment                                     | 9        |

| Productivity                                    | 9        |

| Safety                                          | 9        |

| Application trends                              | 10       |

| Future ICT trends                               | 10       |

| Ubiquitous access                               | 10       |

| Personalized services                           | 10       |

| Delocalized computing and storage               | 10       |

| Massive data processing systems                 | 11       |

| High-quality virtual reality                    | 11       |

| Intelligent sensing                             | 11       |

| High-performance real-time embedded computing   | 11       |

| Innovative example applications                 | 12       |

| Domestic robot                                  | 12       |

| The car of the future                           | 12       |

| Telepresence                                    | 12       |

| Aerospace and avionics                          | 13       |

| Human++                                         | 13       |

| Computational science                           | 13       |

| Smart camera networks<br>Realistic games        | 14<br>14 |

| Realistic games                                 | 14       |

| Business trends                                 | 15       |

| Industry de-verticalization                     | 15       |

| More than Moore                                 | 16       |

| Less is Moore                                   | 17       |

| Convergence                                     | 17       |

| The economics of collaboration                  | 18       |

| Infrastructure as a service – cloud computing   | 18       |

| Technological constraints                       | 20       |

| Hardware has become more flexible than software | 20       |

| Power defines performance                       | 21       |

| Communication defines performance               | 21       |

| ASICs are becoming unaffordable                 | 22       |

| Worst-case design for ASICs leads to bankruptcy | 22       |

| Systems will rely on unreliable components      | 23       |

| Time is relevant                                | 23       |

| Computing systems are continuously under attack | 24       |

| Parallelism seems to be too complex for humans  | 24       |

| One day, Moore's law will end                   | 25       |

| The | HIPEAC | vision |  |

|-----|--------|--------|--|

Conclusion

References

**Technical challenges**

Power and energy

Timing predictability

Keep it simple for humans

Self-adaptation

to start thinking differently

Impact on the applications

The car of the future

Aerospace and avionics

Computational science

Smart camera networks

Realistic games

**3. Recommendations**

Strengths

Threats

Weaknesses

**Opportunities**

**Research objectives**

Virtualization

Design space exploration

Self-adaptive systems

Electronic Design Automation

Design of optimized components

Concurrent programming models and auto-parallelization

Domestic robots

Telepresence

Human++

Performance/€, performance/Watt/€

Keep it simple for the software developer

Keep it simple for the hardware developer

Keep it simple for the system engineer

Automatic Design Space Exploration

If all above is not enough it is probably time

Effective automatic parallelization

Let the computer do the hard work

Electronic Design Automation

Managing system complexity

Performance

Security

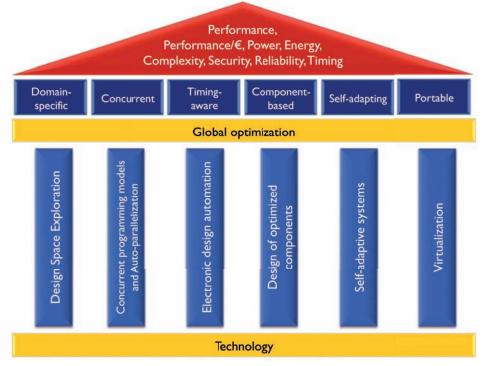

2. HiPEAC vision

Reliability

Project Acronym: HiPEAC Project full title: High Performance and Embedded Architecture and Compilation Grant agreement no: ICT- 217068

DELIVERABLE 3.5

#### The Authors

Marc Duranton, NXP, The Netherlands Sami Yehia, THALES Research & Technology, France Bjorn De Sutter, Ghent University, Belgium Koen De Bosschere, Ghent University, Belgium Albert Cohen, INRIA Saclay, France Babak Falsafi, EFPL, Switzerland Georgi Gaydadjiev, TU Delft, The Netherlands Manolis Katevenis, Forth, Greece Jonas Maebe, Ghent University, Belgium Harm Munk, NXP, The Netherlands Nacho Navarro, UPC & BCS, Spain Alex Ramirez, UPC & BCS, Spain, Olivier Temam, INRIA Saclay, France Mateo Valero, UPC & BCS, Spain Information & Communication Technology had a tremendous impact on everyday life over the past decades. In the future it will undoubtedly remain one of the major technologies for taking on societal challenges shaping Europe, its values, and its global competitiveness. The aim of the HiPEAC vision is to establish a bridge between these societal challenges and major paradigm shifts accompanied by technical challenges that the computing industry needs to tackle.

The HiPEAC vision is based on seven grand challenges facing our society in decades to come, as put forward by the European Commission: energy, transport and mobility, health, aging population, environment, productivity, and safety. In order to address these challenges, several technologies and applications will have to be pushed beyond their existing state-of-the-art, or even be reinvented completely.

Information Technology application trends and innovative applications evolve in parallel with societal challenges. The trends include the seemingly unstoppable demand for ubiquitous access, personalized services, and high-quality virtual reality. At the same time, we observe the decoupling of computing and storage together with an exponential growth of massive data processing centers. In terms of applications domestic robots, autonomous transportation vehicles, computational science, aerospace and avionics, smart camera networks, realistic games, telepresence systems, and the Human++ are all examples of solutions that aim to address future societal challenges.

The development of these applications is influenced by business trends such as cost pressure, restructuring of the industry, service-oriented business models and offloading the customer's hardware via "cloud computing". Other important aspects are the converging of functionality on devices of various sizes and shapes, and collaborative "free" development. However, several technological obstacles block the path the computing industry has to take in order for these applications to become drivers of the 21st century. The following statements summarize major obstacles our industry needs to overcome:

- 1. Hardware has become more flexible than software;

- 2. Power defines performance;

- 3. Communication defines performance;

- 4. Application-specific integrated circuits (ASIC) are becoming unaffordable;

- 5. Worst-case design for ASICs leads to bankruptcy;

- 6. Systems will have to rely on unreliable components;

- 7. Time is relevant;

- 8. Computing systems are continuously under attack;

- 9. Parallelism seems to be too complex for humans;

- 10. One day, Moore's law will end.

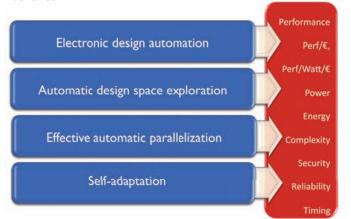

These technological roadblocks or constraints lead to technical challenges that can be summarized as improvements in seven key areas: performance, performance/€ and performance/ Watt/€, power and energy, managing system complexity, security, reliability, and timing predictability.

The HiPEAC vision explains how the HiPEAC community can work on these challenges.

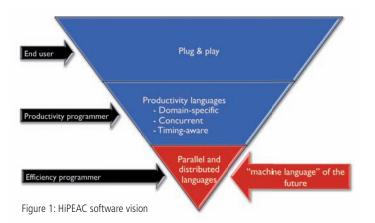

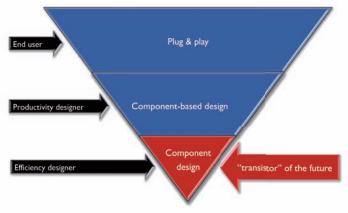

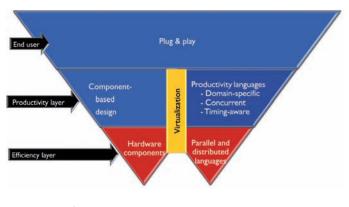

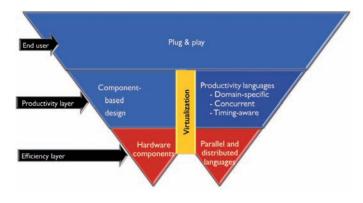

The central creed of the HiPEAC vision is: keep it simple for humans, and let the computer do the hard work. This leads to a world in which end users do not have to worry about platform technicalities, where 90% of the programmers are only concerned with programming productivity and can use the most appropriate domain-specific languages for application development, and where only 10% of the trained computer scientists have to worry about efficiency and performance.

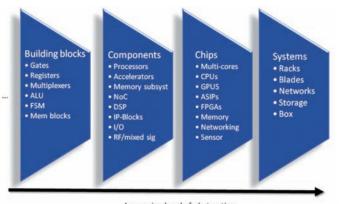

Similarly, a majority of hardware developers will use a component-based hardware design approach by composing functional blocks with standardized interfaces, some of them possibly automatically generated. Such blocks include various processor and memory organizations, domain-specific accelerators and flexible low-cost interconnects. Analogous to the software community, a small group of architects will design and optimize these basic components. Systems built from these components will be heterogeneous for performance and power efficiency reasons. Finally, system engineers will be able to depend on a virtualization layer between software and physical hardware, helping them to transparently combine legacy software with heterogeneous and quickly changing hardware.

In tandem with these human efforts, computers will do the hard work of (i) exploring the design space in search of an appropriate system architecture; of (ii) generating that system architecture automatically with electronic design automation tools; of (iii) automatically parallelizing the applications written in domain-specific languages; and of (iv) dynamically adapting the hardware and software to varying environmental conditions such as temperature, varying workloads, and dynamic faults. Systems will monitor their operation at run time in order to repair and heal themselves where possible.

The HiPEAC vision also reminds us of the fact that one day the past and current technology scaling trends will come to an end, and when that day arrives we should be ready to continue advancing the computing systems domain in other ways. Therefore our vision suggests the exploration of emerging alternatives to traditional CMOS technology and novel system architectures based on them. Finally this document presents a Strengths, Weaknesses, Opportunities, and Threats (SWOT) analysis of computing systems in Europe, and makes six recommendations for research objectives that will help to bring to fruition the HiPEAC vision. These are:

- 1. Design of optimized components;

- 2. Electronic Design Automation (EDA);

- 3. Design Space Exploration (DSE);

- 4. Concurrent programming models and auto-parallelization;

- 5. Self-adaptive systems;

- 6. Virtualization.

This vision document has been created by and for the HiPEAC community. Furthermore it is based on traditional European strengths in embedded systems. It offers a number of directions in which European computing systems research can generate impact on the computing systems industry in Europe.

## Target audience of this document

This HiPEAC vision is intended for all stakeholders in the computing industry, the European Commission, public authorities and all research actors in academia and industry in the fields of embedded systems, computer architecture and compilers.

The executive summary of this document targets decision makers and summarizes the major factors and trends that shape evolutions in the HiPEAC areas. It describes the societal and economic challenges ahead that affect or can be affected by the computing industry. It is essential for all decision makers to understand the implications of the different paradigm shifts in the field, including multi-core processors, parallelism, increasing complexity, and mobile convergence, and how they relate to the upcoming challenges and future application constraints and requirements. The more detailed trends and vision sections of this document target all industrials, academics and political actors, and in general all readers interested in the subject. The goal of these sections is to detail the challenges facing society and this particular sector of industry, and to map these challenges to solutions in terms of emerging key developments.

The last part of this document consists of recommendations for realizing the objectives of the vision, both for the HiPEAC community and for Europe. It therefore focuses on the gaps between the current developments and the directions proposed by the vision section. This part is mainly targeted at policy makers and the whole HiPEAC community. European Information & Communication Technology (ICT) research and development helped to solve many societal challenges by providing ever more computing power together with new applications that exploited these increasing processing capabilities. Numerous examples of the profound impact the computing industry had can be seen in medical imaging, chemical modeling for the development of new drugs, the Internet, business process automation, mobile communication, computer-aided design, computer-aided manufacturing, climate simulation and weather prediction, automotive safety, and many more.

Advances in these areas were only possible because of the exponential growth in computing performance and power efficiency over the last decades. By comparison, if the aviation industry had made the same progress between 1982 and 2008, we would now fly from Brussels to New York in less than a second. Unfortunately, several evolutions are now threatening to bring an end to the exponential growth path of the computer industry.

Until the early 90s, the computer industry's progress was mainly driven by a steadily improving process technology. It enabled significant speed as well as area improvements and on-die transistor budget growth at manageable power and power density costs. As a result, easily programmable uniprocessor architectures and the associated sequential execution model utilized by applications dominated the vast majority of the semiconductor industry.

One notable exception was the embedded systems domain, where the combination of multiple computing engines in consumer electronic devices was already common practice. Another exception was the high-performance computing domain, where large scale parallel processing made use of dedicated and costly supercomputer centers. Of course, both of these domains also enjoyed the advantages offered by an improving process technology.

From the late 90s on, however, two significant evolutions led to a major paradigm shift in the computing industry. In the first place the relative improvements resulting from shrinking process technology became gradually smaller, and fundamental laws of physics applicable to process technology started to constrain the frequency increases and indicate that any future increase in frequency or transistor density will necessarily result in prohibitive power consumption and power density. Secondly, consumer electronic markets, and therefore industries, started to converge. Digital watches and pagers evolved into powerful personal digital assistants (PDA) and smartphones, and desktop and laptop computers were recently reduced to netbooks. The resulting devices demand ever more computational capabilities at decreasing power budgets and within stricter thermal constraints. In pursuit of the continued exponential performance increase that the markets expect, these conflicting trends led all major processor designers to embrace the traditionally embedded paradigm of multi-core devices and special-purpose computational engines for generalpurpose computing platforms.

In the past decade, industrial developments were driven by mobile applications such as cell phones and by connectivity to the Internet. These were the applications that appealed the most to the general public and fueled the growth of the ICT industry. In the future, however, we expect to see less and less of such "killer applications": ICT will become as common in everyday life as, e.g., electrical energy and kitchen appliances. Today, most people already spend a lot of time with their PDAs, MP3players and smartphones. This will intensify competition on a global scale and will drive a trend towards specialization. Even though globalization is supposed to break down borders, we expect to see clear demographic divisions, each with its own area of expertise. Europe has to capitalize on its own strengths in this global economy.

Today, Europe is facing many new challenges with respect to energy consumption, mobility, health, aging population, environment, productivity, safety, and, more recently, the worldwide economic crisis. The role of the ICT industry in addressing these challenges is as crucial as it was ever before. The aforementioned trends have, however, made this role much more challenging to fulfill. The two major trends, multi-core parallelism and mobile convergence, have pushed the semiconductor industry to revise several previously established research areas and priorities.

In particular, parallelism and power dissipation have to become first class citizens in the design flow and design tools, from the application level down to the hardware. This in turn requires that we completely rethink current design tools and methods, especially in the light of the ever-increasing complexity of devices. Additionally, these concerns now both span the entire computing spectrum, from the mobile segment up to the data centers. The challenges arising from this paradigm shift, along with others such as reliability and the design space explosion, are exacerbated by the increasing industrial and application requirements. We nevertheless see them as opportunities for the European industry, especially given our historical leadership in the domains of embedded systems and low power electronics. However, to take advantage of these opportunities in the decade ahead, we require a vision to drive actions.

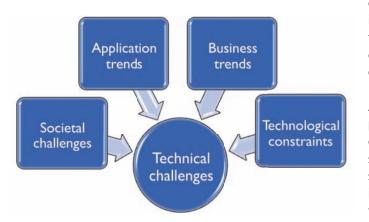

The HiPEAC Network of Excellence groups the leading European industrial enterprises and academic institutions in the domain of high-performance and embedded architectures and compilers. The network has 348 members affiliated to 74 leading European universities and 37 multinational and European companies. This group of experts is therefore ideally positioned to identify the challenges and to mobilize the efforts required to tackle them. The goal of this document is to discern the major societal challenges together with technical constraints as well as application and business trends, in order to relate them to technical challenges in computing systems. The vision then explains how to tackle the technical challenges in a global framework. This framework then leads to concrete recommendations on research areas where more effort is required.

### Approach taken

The HiPEAC community produced a first technical roadmap document in 2007. The current document complements it by a more global integrated vision, taking into account societal challenges, business trends, application trends and technological constraints. This activity was kicked off during the HiPEAC 2008 conference in January 2008.

It was followed by a survey that was sent to all HiPEAC clusters and task forces. The clusters discussed the survey at their spring cluster meeting, and produced their report by the end of June 2008.

The 13 HiPEAC clusters and task forces are:

- Multi-core architecture;

- Programming models and operating systems;

- Adaptive compilation;

- Interconnects;

- Reconfigurable computing;

- Design methodology and tools;

- Binary translation and virtualization;

- Simulation platform;

- Compilation platform

- Task force low power;

- Task force applications;

- Task force reliability and availability;

- Task force education and training.

During the ACACES 2008 summer school, the industrial participants and the teachers of the school held a brainstorming session based on this report. This material was further supplemented by the personal vision of a number of HiPEAC members. This resulted in about 100 pages of raw material.

This material was analyzed, restructured, complemented and shaped during several workshops and teleconferences, and through numerous email exchanges and updates of the document by members of the HiPEAC community, under the supervision of an editorial board.

The ACACES Summer School 2009 gave the opportunity to the industrial participants and the teachers to brainstorm about the Strengths, Weaknesses, Opportunities and Threats (SWOT) that Europe is facing in the domain of Information & Communication Technology. The results were analyzed, complemented and included in the recommendations.

## 1. Trends & Challenges

The HiPEAC vision builds on several foundations in the form of challenges, trends, and constraints. The first foundation are the European grand societal challenges.

Secondly, we look into application trends and some future applications that can help in meeting these societal challenges.

Both of these foundations are situated outside the core competences of the HiPEAC community, but they help in illustrating the larger context in which HiPEAC operates.

The third foundation are general business trends in the computing systems industry and their consequences.

Finally, we consider technological evolutions and constraints that pose challenges and limitations with which our community has to deal, leading to a list of core technical challenges.

#### Societal Challenges for ICT

The main purpose of Information and Communication Technologies (ICT) is to make the world a better place to live in for everyone. For decades to come, we consider the following seven essential societal grand challenges [ISTAG], which have deep implications for ICT.

#### Energy

Our society is using more energy than ever before, with the majority of our current energy sources being non-renewable. Moreover, their use has a significant and detrimental impact on the environment. Solving the energy challenge depends on a two-pronged approach. On the one hand, we need research into safe, sustainable alternatives to our current energy sources. On the other hand, we also have to significantly reduce our overall energy consumption.

Currently computing is estimated to consume the same amount of energy as civil aviation, which is about 2% of the global energy consumption. This energy consumption corresponds to a production of, for example, 60g CO2 per hour a desktop computer is turned on. Along similar lines, a single Google query is said to produce 7g of CO2. Making computing itself more energy-efficient will therefore already contribute to the energy challenge.

Even though computers consume a lot of power, in particular in the data centers, some reports [Wehner2008] state that they globally contribute to energy saving (up to 4x their CO2 emission) due to on-line media, e-commerce, video conferencing and teleworking. Teleworking reduces physical transport, and therefore energy. Similarly, videoconferencing reduces business trips. E-commerce also has a significant impact. Electronic forms and administrative documents reduce the volume of postal mail.

An even greater indirect impact can be expected from energy optimizations in other aspects of life and economy, by introducing electronic alternatives for other energy-consuming physical activities, and by enabling the optimization of energy-hungry processes of all sorts.

#### Transport and Mobility

Modern society critically depends on inexpensive, safe and fast modes of transportation. In many industrialized areas of the world mobility is a real nightmare: it is an environmental hazard, the average speed is very low, and it kills thousands of people every year.

ICT can help with solving the mobility challenge by optimizing and controlling traffic flows, by making them safer through more active safety features, or by avoiding them altogether, e.g., through the creation of virtual meeting places.

#### Health

The use of advanced technologies is essential to further improve health care. There is a great need for devices that monitor the health and assist healing processes, for equipment to effectively identify diseases in an early stage, and for advanced research into new cures and improving existing treatments.

ICT is indispensable in this process, e.g., by speeding up the design of new drugs such as personalized drugs, by enabling personal genome mapping, by controlling global pandemics and by enabling economically viable health monitoring.

#### Aging population

Thanks to advances in health care, life expectancy has increased considerably over the last century, and continues to do so even today. As a result, the need for health care and independent living support, such as household robots and advanced home automation, is growing significantly. ICT is at the heart of progress in these areas.

#### Environment

The modern way of living, combined with the size of the world population, creates an ecological footprint that is larger than what the Earth can sustain. Since it is unlikely that the first world population will want to give up their living standard or that the world's population will soon shrink spontaneously, we have to find ways to reduce the ecological footprint of humans.

ICT can assist in protecting the environment by controlling and optimizing our impact, for example by using camera networks to monitor crops and to apply pesticides only on those specific plants that need them, by continuously monitoring environmental parameters, by optimizing the efficiency of engines, by reducing or optimizing the traffic, by enabling faster research into more environment-friendly plastics, and in numerous other ways.

#### Productivity

In order to produce more goods at a lower price or in order to produce them more quickly, economies have to continuously improve the productivity of their industrial and non-industrial processes. In doing so, they can also remain at the forefront of global competition. ICT enables productivity enhancements in all sectors of the economy and will continue to do so in the foreseeable future.

#### Safety

Many safety-critical systems are or will be controlled by information systems. Creating such systems requires effective dealing with failing components, with timing constraints and with the correctness of functional specifications at design time.

Advancements in ICT also enable society at large to protect itself in an ever more connected world, by empowering individuals to better protect their privacy and personal life from incursions, and by providing law enforcement with sophisticated analysis and forensic means. The same applies to national defense.

#### **Application trends**

The continued high-speed evolution of ICT enables new applications and helps creating new business opportunities. One of the key aspects of these future applications, from a user perspective, is the way in which the user interacts with computing systems. Essentially, the interfaces with the computers become richer and much more implicit, in the sense that the user is often not aware of the fact that he is interacting with a computer. This is known as "the disappearing computer" [Streit2005].

This second part of our vision lists a number of application trends that we envision for the next decade. This list is by no means exhaustive. Its main purpose is to establish a list of technical application requirements for future applications. We start with an outline of potential future ICT trends continued with a list of innovative future applications.

#### Future ICT trends

We envision at least the following major trends in the use of ICT during the following decade.

#### **Ubiquitous access**

Users want to have ubiquitous access to all of their data, both personal and professional. For example, music, video, blogs, documents, and messages must follow the users in their home from room to room and on the move in the car, at work, or when visiting friends. The way and user interface through which this data is accessed may however differ depending on the situation, and so may the devices used. These include, but are not limited to, desktop computers, laptops, netbooks, PDAs, cell phones, smart picture frames, Internet radios, and connected TV sets. Since these different platforms may be built using completely dissimilar technologies, such as different processors, operating systems, or applications, it is important to agree on high quality standards that will allow for information interchange and synchronization between all these devices.

#### **Personalized services**

We expect services to become more and more personalized, both in private and professional life. Our preferences will be taken into account when accessing remote web-based services. Other examples are personalized traffic advice, search engines that take our preferences and geographical location into account, music and video sources presenting media fitting our personal taste and in the format that best suits our mobile video device, and usability adaptations for disabled people.

Personalized video content distribution is another case of ever increasing importance. Video streams can be adapted to the viewer's point of view, to his or her personal taste, to a custom angle in case of a multi-camera recording, to the viewer's location, to the image quality of the display, or to his or her consumer profile with respect to the advertisements shown around a sports field.

#### Delocalized computing and storage

As explained in the previous sections, users want to access those personalized services everywhere and through a large diversity of hardware clients. Users thus request services that require access to both private and public data, but they are not interested to know from where the data is fetched and where the computations are performed. Quality of experience is the only criterion that counts. YouTube, Google GMail, Flickr and Second Life are good examples of this evolution. The user does not know the physical location of the data and computations anymore, which may be data centers, within access networks, client devices or still other locations.

#### Massive data processing systems

We envision that three important types of data processing systems will coexist:

- Centralized cloud computing is a natural evolution of current data centers and supercomputers. The computing and storage resources belong to companies that sell these services, or trade them for information, including private information such as a profile for advertisements. However, mounting energy-related concerns require investigating the use of "greener data centers". One promising approach, in which Europe can lead, is using large numbers of efficient embedded cores, as these may provide better performance/watt/ than traditional microprocessors [Asanovic2006, Katz2009].

- Peer-to-Peer (P2P) computing is a more distributed form of cloud computing, where most of the computing elements and storage belongs to individuals as opposed to large companies. Resources are located throughout a large network so as to distribute the load as evenly as possible. This model is very well suited to optimally exploit network bandwidth, and can also be used for harvesting unused computation cycles and storage space. It continues the decentralization trends initiated by the transition from centralized telephone switches to the Internet, but at a logical rather than at a physical level. Some companies already use this technique for TV distribution, in order to avoid overloading single servers and network connections.

- Personal computing follows from ICT trends that provide end users with increasingly more storage capacity, network bandwidth, and computation power in their personal devices and at home. These come in the form of large, networked hard drives, fiber-to-the-home, and massively parallel graphical processing units (GPUs). Hence many people may simply use their "personal supercomputers", accessible from anywhere, rather than some form of cloud computing. We might even envision a future where people convert their excess photovoltaic or other power into computing cycles instead of selling it to the power grid, and then sell these cycles as computation resources, while using the dissipated power to heat their houses.

#### High-quality virtual reality

In the near future, graphic processors will be able to render photorealistic views, even of people, in real time [CEATEC2008]. The latest generations of GPUs can already render virtual actors with almost photorealistic quality in real time, tracking the movements as captured by a webcam. These avatars, together with virtual actors, will enable new high-quality virtual reality (HQVR) applications, new ways to create content, and new forms of expression. This trend has already started in Japan, for example in the form of software that enables the creation of music videos with a virtual singer [Vocaloid].

It is obvious that these techniques will also allow new ways of communication, for example by reducing the need to travel for physical meetings.

#### Intelligent sensing

Many unmanned systems, security systems, robots, and monitoring devices are limited by their ability to sense, model or analyze their surrounding environment. Adding more intelligence to sensors and allowing embedded systems to autonomously analyze and react to surrounding events in real time, will enable building more services, comfort and secure systems and will minimize human risks in situations requiring dangerous manipulations in hard-to-access or hostile environments. As a result, we will see the emergence of "smart" cities, buildings, and homes. In the future we also envision advanced sensor networks or so-called "smart dusts", where clouds of tiny sensors will simply be dropped in locations of interest to perform a variety of monitoring and sensing applications.

Less automated, but at least equally important, are tele-manipulators or robots that enable remote manual tasks. Combined with high-quality haptic feedback, it opens the path to, e.g., telesurgery.

#### High-performance real-time embedded computing

Embedded computing has long ago outgrown simple microcontrollers and dedicated systems. Many embedded systems already employ high-performance multi-core systems, mostly in the consumer electronics domain (e.g. signal processing, multimedia).

Future control applications will continue this trend not just for typical consumer functionality, but also for safety and security applications. They will do so, for example, by performing complex analyses on data gathered with intelligent sensors, and by initiating appropriate responses to dangerous phenomena. Application domains for such systems are the automotive domain, as well as the aerospace and avionics domains. Future avionic systems will be equipped with sophisticated on-board radar systems, collision-detection, more intelligent navigation and mission control systems, and intelligent communication to better assist the pilots in difficult flight situations, and thus to increase safety. Manufacturing technology will also increasingly need high-end vision analysis and high-speed robot control.

In all cases, high performance and real time requirements are combined with requirements to low power, low temperature, high dependability, and low cost.

#### Innovative example applications

The above trends manifest themselves in a number of concrete applications that clearly contribute to the societal challenges.

#### **Domestic robot**

An obvious application of the domestic robot would be taking care of routine housekeeping tasks. In case of elderly or disabled people, the domestic robot could even enable them to live independently, thereby increasing the availability of assisted living. A humanoid form seems to be the most appropriate for smooth integration into current houses without drastic changes in their structure or organization. This poses major challenges for sensors, processing and interfacing. It also requires the robots to run several radically different types of demanding computations, such as artificial intelligence and video image processing, many of which need to be performed in real time to guarantee safe operation.

Furthermore, the robots will have to continuously adapt to changes in their operating environment and the tasks at hand. For example, depending on the time of day and the room in which they operate, the lighting will be different, as will the tasks they have to carry out and potentially even the users they have to assist. Furthermore, the reliability and autonomy of the robots needs to be guaranteed, for example when for some reason the power socket cannot be reached or when there is a power outage. In that case, non-essential tasks such as house cleaning can be disabled to save energy for life-saving tasks that must remain available, such as administering drugs or food, and calling for aid.

As such, domestic robots can clearly play an important role in dealing with the aging population. The domestic robot is currently a priority for the Japanese government [Bekey2008] and we expect that a strong social demand for domestic robots will be a solid driver for computing systems research and business in the future.

#### The car of the future

Cars can be equipped with autopilots. In order to drive safely and quickly to their destination, cars can stay in touch with a central traffic control system that provides personalized traffic information for each car, such that, e.g., not all cars going from A to B will take the same route in case of congestion. Cars can also contact neighboring cars to negotiate local traffic decisions like who yields at a crossing. Autonomous vehicles can also be used by children, disabled people, the elderly or people that are otherwise not allowed to drive a car, or that are not willing to drive themselves because, e.g., they want to work/relax while traveling. Furthermore, autonomous vehicles can be used unmanned to transport goods. Advanced Driver Assistance Systems (ADAS) that combine high-end sensors enable a new generation of active safety systems that can dramatically improve the safety of pedestrians. ADAS systems require extreme computation performance at low power and, at the same time, must adhere to high safety standards. Stereovision, sensor fusion, reliable object recognition and motion detection in complex scenes are just a few of the most demanding applications that can help to reduce the number of accidents. Similar requirements are found in aerospace safety systems.

Clearly the automation and optimization of traffic on our roads can help in saving energy, reducing air pollution, increasing productivity, and improving safety.

#### Telepresence

A killer application for HQVR could be realistic telepresence, creating the impression of being physically present in another place. This could be achieved with high-resolution displays, possibly in 3D, with multi-view camera systems, and with low-latency connections. For example, at each participating site of a video-conference, a circle of participants around a meeting table can consist of some real participants and of a set of displays that show the remote participants from the point of view of the in situ participants. This way, participant A would see two participants B & C that participate from two different physical locations but are seated adjacent to each other in the virtual meeting as if they were facing each other when they have a conversation. At the same time, participants B & C will effectively face each other on their respective displays.

Such an application requires 3D modeling of all in situ participants, 3D rendering of all remote participants at all sites, and a communication and management infrastructure that manages the virtual world: who is sitting where, what background images are transmitted, the amount of detail to be transmitted, etc.

Typical applications of such systems are virtual meetings, advanced interactive simulators, virtual family gatherings, virtual travel, gaming, telesurgery, etc. In the future, these applications might be combined with, e.g., automated translation between different languages spoken during a telepresence session.

While relatively simple instances of such systems are currently designed and researched, many possible features and implementation options remain to be explored. For example, where will most of the processing take place? In centralized servers feeding images to thin set-top boxes? Or will fat set-top boxes at each participating site perform this task? What will the related business model of such systems look like? Are the participants displayed in a virtual environment or in a realistic environment? What happens if a participant stands up and walks out? Will he or she disappear in between two displays of the virtual meeting? How will the systems handle multiple participants at the same physical site? With multiple multiview cameras? With multiple display circles?

Telepresence applications clearly contribute to overcome the challenges of mobility, aging population, and productivity. By saving on physical transportation of the participants, telepresence can also reduce energy consumption [Cisco].

#### Aerospace and avionics

Aerospace and avionics systems will undergo a continued evolution towards tighter integration of electronics to increase safety and comfort. Future systems, both in the air and on the ground, will be equipped with sophisticated on-board radar systems, collision-detection, more intelligent navigation and mission control systems, and intelligent communication to better assist pilots in difficult flight situations in order to increase safety. Highly parallel on-board real-time computer systems will enable new classes of flight control systems that further increase safety in critical situations.

While on the one hand this is a continuation of ongoing automation in the aerospace and avionics industry, on the other hand it ushers in a new era in which many more decisions will be taken while airborne instead of before takeoff. This will lead to less strict a priori constraints, which will in turn lead to more efficient routes and procedures. As such, these new applications will help with the challenges of safety, the environment, and mobility.

Future space missions will be equipped with ever more complex on-board experiments and high-precision measurement equipment. Satellite-based systems will be getting more sophisticated sensors and communications systems, enabling new application domains, such as better surveillance and mobile terrestrial broadband communications.

To make this evolution economically viable, all devices that are launched should behave very reliably over a long period of time and should be light to limit launching costs. Achieving both goals will require new experimentation and application devices to include more reliability-enhancing features. By implementing those features in computing electronics themselves by means of adaptability and redundancy instead of using mechanical shields, we can save weight and thereby reduce launch costs. Furthermore, to increase the lifetime of devices and to optimize their use during their lifetime, their processing capabilities will become more flexible, enabling the uploading of new or updated applications.

#### Human++

A fascinating example of advanced intelligent sensing could be the augmented human, or the Human++. More and more, implants and body extensions will overcome limitations of the human body. For example, complex micro-electronic implants will restore senses for disabled people, as in case of cochlear implants or bionic eyes. Other implants will control internal body functions, for example by releasing hormones such as insulin precisely when they are needed, or by detecting epileptic seizures and releasing medicine in time to avoid the most dangerous stages of a seizure.

Exoskeletons will enable people to work more productively, for example by offering them finer gesture control. In order to steer the actuators in such exoskeletons, electronics will be connected to the human brain and nervous systems through interfaces that require no conscious interaction by the user [Velliste2008]. Augmented reality devices such as glasses and hearing aids, or recording and analyzing devices [GC3], can also help healthy people in their daily life.

Human++ can clearly help in meeting the challenges relating to health and the aging population. It can also help to improve productivity.

#### **Computational science**

Computational science is also called the third mode of science (in silico) [GC3]. It creates detailed mathematical models that simulate physical phenomena such as chemical reactions, seismic waves, nuclear reactions, and the behavior of biological systems, people and even financial markets. A common characteristic of all these applications is that the precision is mostly limited by the available computing power. More computing power allows using more detailed models leading to more precise results. E.g. in global climate modeling, results are more precise if not only the atmosphere and the oceans, but also the rainforests, deserts and cities are modeled. Computing all these coupled models, however, requires an insatiable amount of floating-point computing power.

Today's supercomputers offer petaflop-scale sustained performance but this is not yet sufficient to run the most advanced models in different disciplines, nor does it allow us to run the algorithms at the desired granularity. The next challenge is to develop exascale computing with exaflop-scale performance. Exascale computing differs from the cloud in the sense that exascale computing typically involves very large parallel applications, whereas the cloud typically refers to running many (often smaller) applications in parallel. Both types of computing will have to be supported by appropriate software and hardware, although large fractions of that software and hardware should be common. The impact of computational science is huge. It enables the development of personalized drugs, limits the number of experiments on animals, allows for accurate long term weather predictions, helps us to better understand climate change, and it might pave the way to anticipate health care based on detailed DNA screening. Computers for computational science have always been at the forefront of computing in the sense that most high-performance techniques were first developed for supercomputers before they became available in commodity computing (vector processing, high speed interconnects, parallel and distributed processing).

Computational science definitely helps in solving the energy and health challenges.

#### Smart camera networks

Right now, camera networks involving dozens or even hundreds of cameras are being installed for improving security and safety in public spaces and buildings and for monitoring traffic Companies are already envisaging "general purpose" home camera networks that could be used for a variety of purposes such as elderly care, home automation and of course security and safety. At the European level, there is a strong push to introduce cameras and other sensors into cars, for improving traffic safety through assisted driving. Finally, camera technology is introduced in a wide range of specialized applications, such as precision agriculture, where crops are monitored to limit the use of pesticides.

In many of these emerging applications, it is impossible for a human to inspect or interpret all available video streams. Instead, in the future computers will analyze the streams and present only relevant information to the operator or take appropriate actions autonomously.

When camera networks grow to hundreds of cameras, the classical paradigm of processing video streams on centralized dedicated servers will break down because the communication and processing bandwidth does not scale sufficiently with the size of the camera networks. Smart cameras cooperating in so-called distributed camera systems are the emerging solution to these problems. They analyze the video data and send condensed meta-data streams to servers and to each other, possibly along with a selection of useful video streams. This solution scales better because each new camera adds additional distributed processing power to the network. However, several challenges remain, e.g., the development of mechanisms for privacy protection, as well as the development of hardware/software platforms that enable both productive programming and power-efficient execution. The latter is particularly important for wireless cameras that offer many advantages such as easier ad hoc installation.

Just like video processing in future cars and in future domestic robots will have to adapt to changing circumstances, so will the software that analyses video streams. An example is when the operation mode of a camera network monitoring a large crowd has to switch from statistical crowd motion detection to following individual suspects.

Clearly smart camera networks can help with societal challenges, including safety, productivity and the environment.

#### **Realistic games**

According to the European Software Association [ESA], the computer and video game industry's revenue topped \$22 billion in 2008. Gaming is a quickly growing industry and it is currently a huge driver for innovations in computing systems. GPUs now belong to the most powerful computing engines, already taking full advantage of the many-core roadmap. Gaming will definitely be one of the future "killer applications" for high-end multi-core processors, and we expect gaming to remain one of the driving forces for our industry.

It can be expected that at least some games will bridge the gap between virtual worlds and the real world. For example, at some point a player might be playing in front of his PC display, but at another point in the same game he might go searching for other players in this hometown, continuing some mode of the game on his PDA with Bluetooth and GPS support. Such games will need to support a very wide range of devices. This contrasts with existing games for which a large fraction of the implementation effort is spent on implementing device-specific features and optimizations.

Gaming does not directly address one of the societal challenges, but together with the entertainment industry it contributes to the cultural evolution of our society. It also helps people to enjoy their leisure time and improves their wellbeing.

#### **Business trends**

Current business trends, independent of the economic downturn, have a deep impact on ICT. The economic downturn only speeds up those trends, deepening the short-term and middleterm impact. This section describes the most important recent business trends in ICT.

#### Industry de-verticalization

The semiconductor industry is slowly changing from a high-tech into a commodity industry: chips and circuits are everywhere and need to be low cost. This will have wide raning implications, and what happened to the steel industry could repeat itself for the silicon industry. We observe industrial restructuring or "de-verticalization": instead of having companies controlling the complete product value chain, the trend is to split big conglomerates into smaller companies, each of them more specialized in their competence domain. For example, big companies are spinning off their semiconductor divisions, and the semiconductor divisions spin off the IP creation, integration and foundry, thus becoming "fabless" or "fablight". Examples are Siemens, Philips, and, in the past, Thomson.

Consolidation by merging and acquisition also allows companies to gain critical mass in their competence area, sometimes leading to quasi monopolies. One of the reasons is cost pressure: only the leader or the second in a market can really break even.

A horizontal market implies more exchanges between companies and more cost pressure for each of them. An ecosystem is required to come to a product. Sharing of IP, tools, software and foundries are driving an economy of scale. Standardization and cooperation on defining common interfaces is mandatory, such that different pieces can be integrated smoothly when building a final product.

At least two side effects can result from this approach: higher cost pressure offsets the advantages of the economy of scale, and final products are less optimized. Both side effects are caused by the same fundamental reason: each design level in a system is optimized to maximize benefits for all of its target uses, but not for any particular end product. In other words, all design levels are optimized locally rather than globally. In an integrated approach, not applying a local optimization to an isolated level or applying that optimization differently could lead to a better global optimization. Furthermore, interoperability and communication add extra layers, and therefore costs. Those costs can be of a financial nature, or they may come in the form of lower performance or lower power efficiency.

#### More than Moore

Moore's Law has driven the semiconductor industry for decades, resulting in extremely fast processors, huge memory sizes and increasing communication bandwidth. During those decades, ever more demanding applications exploited these growing resources almost as soon as they arrived on the market. These applications were developed to do so because the International Technology Roadmap for Semiconductors (ITRS) and Moore's Law told them when those resources would become available. So during the last decades, computing systems were designed that reflected the CMOS technology push resulting from Moore's Law, as well as the application pull from ever more demanding applications. A major paradigm shift is taking place now, however, both in the technology push and in the application pull. The result of this paradigm shift has been called the "More than Moore" era by many authors; see for example [MtM].

From the point of view of the technology push, two observations have to be made. First of all, the cost levels for systemon-chip development in advanced CMOS technology are going through the roof, for reasons described in more detail in later sections. Secondly, the continuing miniaturization will have to end Moore's Law one day in the not so distant future.

From the application pull perspective, it has become clear that consumers and society have by and large lost interest in new generations of applications and devices that only feature more computational power than their previous generation. For improving the consumer experience, and for solving the societal challenges, radically new devices are needed that are more closely integrated in every-day life, and these require sensors, mechatronics, analog- and mixed-signal electronics, ultralow-power or high-voltage technologies to be integrated with CMOS technology.

The Emerging IT platform (Courtesy J. Rabaey, UC Berkeley)

Devices that embed multiple technologies are instances of the "More than Moore" approach: combining generic CMOStechnology with new technologies for building more innovative, dedicated, smarter and customer-tailored solutions. This new era of added-value systems will certainly trigger innovation, including new methodologies for architecting, modeling, designing, characterizing, and collaborating between the domains required for the various technologies combined in a "More than Moore" system.

The "More Moore" race towards ever-larger numbers of transistors per chip and the "More than Moore" trend to integrate multiple technologies on silicon are complementary to achieve common goals such as application-driven solutions, better system integration, cost optimization, and time to market. Some companies will continue to follow the "More Moore" approach, while others will shift towards the "More than Moore" approach. This will drive industry into a direction of more diversity and wider ecosystems.

#### Less is Moore

Together with the "More than Moore" trend, we observe another trend fueled by Moore's law: people no longer only want more features and better performance, but are increasingly interested in devices with the same performance level at a lower price. This is particularly true for personal computers. The sudden boom of netbooks, based on low cost and lower performance processors such as Intel Atom or ARM processors, is an example of this new direction. People notice that these devices offer enough performance for everyday tasks such as editing documents, listening to music and watching movies on the go.

The limited processor performance also reduces power consumption and therefore improves mobility. For example, netbooks have up to 12h autonomy, much better than laptops. Due to their lower price, they also open new markets, allowing better access to ICT for developing countries as was tried in the One Laptop Per Child project.

This trend also has an impact on software, as it now needs to be optimized to run smoothly on devices with less hardware resources. Contrary to previous versions, new operating system releases seem to be less compute-intensive. This can be seen in comparing the minimum requirements of Microsoft's Windows 7 to those of Microsoft's Vista, and Apple's Snow Leopard OS also claims improvements in the OS internals rather than new features. This trend extended the lifetime of Windows XP, and gave rise to a wider introduction of Linux on consumer notebooks.

This trend is also leading to computers specifically designed to have extreme low power consumption. The appearance of ARM-based netbooks on the market demonstrates that even the once sacred ISA compatibility is sacrificed now. This creates excellent opportunities for Europe.

#### Convergence

Another business trend is convergence: TVs and set-top-boxes share more and more functionality with PCs and even have access to the Internet and Web 2.0 content. Telecom companies are proposing IP access to their customers, and broadcast companies are challenged by IP providers who deliver TV programs over IP (ADSL). End users want to restrict the number of different providers, and expect to have voice, data, TV and movies accessible both on their wired and wireless devices.

When using devices compliant with Internet standards, TV viewers can now have full access to all of its contents and to cloud computing. TV shows can be recorded on a Network Attached Storage or NAS device, or be displayed from YouTube. The TV and other devices such as mobile phones, can also access all the user's pictures and music.

The convergence mainly relies on common standards and protocols such as DLNA, Web standards, Web 2.0, and scripting languages, and not so much on closed proprietary software. As a result, the hardware platform on which applications run is becoming irrelevant: commonly used ISAs like x86 are not compulsory anymore, so other ISAs like ARM can also be used where beneficial. End users care more about their user experience, including access to the web, email, their pictures and movies, etc., than they care about a platform supporting all these services.

Today, most desktop and laptop computers are based on the x86 architecture, while mobile phones use the ARM architecture, and high end game consoles use the PowerPC architecture. The main factor preventing architectures other than x86 to be used for desktops and laptops is the operating system. If Microsoft Windows were ported to different processor architectures such as the ARM architecture, the market could change. Other OSes, like Apple's Mac OS X and Google's Android, could also challenge the desktop market, thanks to their support for the ARM architecture in the mobile domains.

Legacy software for the desktop and laptop can be an important roadblock for the adoption of different ISAs and OSes. Emulation of another ISA is still costly in terms of performance, but has now reached a level of practical usability. For example, Apple's Mac OS X running on the Intel architecture can execute native PowerPC binaries with no significant user hurdle.

Another convergence is optimally making use of the hardware's heterogeneous processing resources, for example by better dividing tasks between the CPU and the GPU where the GPU is the number cruncher, and the CPU serves as the orchestrator. Common software development in OpenCL [OpenCL] and GrandCentral [Grandcentral] tool flows will help to define applications that can efficiently use all the hardware resources available on the device, including multi-core CPUs and GPUs.

#### The economics of collaboration

The Internet has boosted the appearance of new communities and collaborative work. People are contributing their time and sharing knowledge and expertise with others like never before. This phenomenon is increasingly visible in all ICT domains:

- In the software field, Linux and gcc are two prominent examples. A state-of-the-art operating system and compiler have been built, and are offered under free licenses as the result of tremendous work by hundreds of specialists. The developer community groups a diverse crowd of independent contributors, company employees, and students. Apart from financial advantages, contributors are motivated by factors such as reputation, social visibility, ethics, the raw technical challenge, and the eventual technical advantage.

- In terms of expert knowledge, Wikipedia has caused the disappearance of Microsoft Encyclopaedia (Encarta). The Web 2.0 evolution has brought about a boom in terms of content creation by end users. Free, community-built content-management software such as Drupal also plays an important role in this development.

- Regarding social culture, YouTube and other portals make available video and music offered by their authors under so-called Copyleft licenses, which allow freedom to use and redistribute contents.

All this community-generated content has grown thanks to the use of novel licensing terms such as the GNU General Public License (GPL) and the Creative-Commons Copyleft license. These licenses focus on the protection of the freedom to use, modify and redistribute content rather than on limiting their exploitation rights.

This has led to increased competition both in the software and in the content generation markets. At the same time it enables more reuse and stimulates investing resources in opening niche markets that would otherwise be too unprofitable to enter. Moreover, people want to share and exchange their creations, resulting in more demand for interoperability.

User-generated content and independent publishers represent an increasingly important share of the media available on the Internet, resulting in increased competition for publishing houses. This trend also redefines the communication, storage and computation balance over the network.

#### Infrastructure as a service cloud computing

Another business trend is the evolution towards providing services instead of only hardware. The main financial advantage is to have continuous revenue, instead of "one shot" at the sale of the product. After-sales revenue has also decreased because nowadays most consumer devices are designed to be discarded rather than repaired, and product lifetime has also been reduced to continuously follow the latest fashion trends for, e.g., mobile phones. The fact that most modern consumer devices are not really repairable has a bad impact on the environment, but it also fuels the recycling business.

The infrastructure service model requires the provider to have a large ICT infrastructure that enables simultaneously serving a large number of customers. If the service is offering processing power, the large scale is also a way to reduce peak load. This can be done by exploiting the fact that not all users will require peak performance at the same time, if necessary by providing dedicated billing policies that encourages users to adapt their usage profile so as to spread peak consumption. It is then better to have a shared and common infrastructure that is dimensioned for average load, as opposed to having many unused resources at the customer side due to over-dimensioning to cope with sparse peak requests.

Processing power and storage services, such as for indexing the web or administrating sales, are also increasingly offered to end-users. Google first provided storage with Gmail and later on for applications, Amazon now provides computing power, and there are many other recent examples. Together with ubiquitous connectivity, this leads to "cloud computing": data and resources from the end user will be stored somewhere on the cloud of servers of a company providing services.

When the cloud provides storage and processing power, the end-user terminal device can be reduced to input, output and connectivity functionality and can therefore become inexpensive. This model has already started with mobile phones, where the cost for the user is primarily in the subscription and not in the hardware of the terminal itself.

We even see this model being considered for high-end gaming [AMD], where a set of servers generates high-end graphics and delivers them to a rather low-cost terminal. This model could also be an answer to unlicensed software use and multimedia content: the game software will run on the server and will never be downloaded to the client. For media, streamingonly could deliver similar benefits. However, this model has several implications:

- The client should always be connected to the cloud's servers.

- Compression techniques or high-bandwidth connections are required (mainly for high-definition video and gaming)

- The customer should trust the provider if he/she stores private data on the provider's cloud.

- The cloud should be reliable 24/24, 7/7, 365/365.

As of 2009, companies like Google, Microsoft and Amazon still face problems in this regard with, for example, web services going down.

The necessity to be constantly connected accompanied by privacy concerns may hamper the success of this approach: "computing centres" were inevitable in the 80's, but the personal computer restored the individual users' freedom. These two opposites consisting of resources centralized at the provider with a dumb client, versus a provider only providing the pipes and other computing and storage resources belonging to the customer, still have to be considered.

Therefore, companies are looking more and more into providing services. IBM is a good example for the professional market, while Apple is an example for the consumer market with its online store integrated in iTunes. Console providers also add connectivity to their hardware devices to allow online services. Connectivity also allows upgrading the device's software, thereby providing the user with a "new" device without changing the hardware.

#### **Technological constraints**

This section gives an overview of the key technological evolutions and limitations that we need to overcome in order to realize the applications of the future in an economically feasible manner.

#### Hardware has become more flexible than software

This trend is also called the hardware-software paradox. It is a consequence of the fact that the economic lifetime of software is much longer than the economic lifetime of hardware. Rather than looking for software to run on a given hardware platform, end users are now looking for hardware that can run their existing and extremely complex software systems. Porting software to a completely new hardware platform is often very expensive, can lead to instability, and in some cases requires re-certification of the software.

At the same time, hardware is evolving at an unprecedented pace. The number of cores and instruction set extensions increases with every new generation, requiring changes in the software to effectively exploit the new features. Only the latest software is able to take full advantage of the latest hardware improvements, while older software benefits much less from them.

As a result, customers are increasingly less inclined to buy systems based on the latest processors, as these provide little or no benefit when running their existing applications. This is particularly true for the latest multi-core processors given the many existing single-threaded applications.

#### Power defines performance

Moore's law and the associated doubling of the number of transistors per IC every process generation, has until recently always been accompanied by a corresponding reduction in supply voltage, keeping the power envelope fairly stable. Unfortunately, voltage scaling is becoming less and less effective, because further reducing the supply voltage leads to increased leakage power, offsetting the savings in switching power. At the same time, the ITRS projects that integration will continue due to smaller feature sizes for at least another five generations [ITRS]. Therefore, while future chips are likely to feature many cores, only a fraction of the chip will likely be active at any given time to maintain a reasonable power envelope.

Since it will not be possible to use all cores at once, it makes little sense to make them all identical. As a result, functional and micro-architectural heterogeneity is becoming a promising direction for both embedded and server chips to meet demands in terms of power, performance, and reliability. This approach enables taking full advantage of the additional transistors that become available thanks to Moore's Law.

Heterogeneous processors are already widely used in embedded applications for power and chip real-estate reasons. In the future, heterogeneity may be the only approach to mitigate power-related challenges, even if real-estate no longer poses any significant problems. For example, Intel's TCP/IP processor is two orders of magnitude more power-efficient when running a TCP/IP stack at the same performance as a Pentium-based processor [Borkar2004].

Energy efficiency is a major issue for mobile terminals because it determines autonomy, but it is also very important in other domains: national telecom providers are typically the second largest electricity consumers after railway operators, and the CO<sub>2</sub> impact of data centers is increasing continuously.

#### Communication defines performance

Communication and computation go hand in hand. Communication — or, in other words, data transfers — is essential at three levels: between a processor and its memory; among multiple processors in a system; and between processing systems and input/output (I/O) devices. As transistors and processors become smaller, the relative distance of communication increases, and hence so does its relative cost. At the first level, as the number of megabytes of memory per processor increases, so does memory access time measured in processor clock cycles. Caches mitigate this problem to some extent, but at a complexity cost. At the second level, with more processors on a chip or in a system, traditional buses no longer suffice. Switches and interconnection networks are needed, and they come at a non-negligible cost. At the third level, chip and system I/O is a primary component of system cost, both in terms of power dissipation and of wiring area or system volume.

Because of the high cost of communication, locality becomes essential. However, communication and locality management are expensive in terms of programmer time. Programmers prefer the shared memory programming models, whereby they view all data as readily available and accessible by address at a constant cost, independent of its current location. Real multiprocessor memory however has to be distributed for performance reasons. Yet, we prefer not to burden programmers with managing locality and transfers: in case of coherent caches hardware is responsible for these tasks, and modern research into run-time software enables implementing more sophisticated locality algorithms than those available when relying on hardware alone.

The system not only has to communicate with various memory hierarchies, but also has to exchange data with the outside world. This external communication also requires large amounts of bandwidth for most applications. For example, a stream of High Definition images at 120 fps leads to bandwidth requirements of about 740 MB/s. This is more than transferring the content of a CD in one second.

#### ASICs are becoming unaffordable

The non-recurring engineering (NRE) costs of complex application-specific integrated circuits (ASICs) and Systems on a Chip (SoCs) are rising dramatically. This development is primarily caused by the exponential growth of requirements and use cases they have to support, and the climbing costs of creating masks for new manufacturing technologies. The ESIA 2008 Competitiveness Report [ESIA2008] illustrates this trend. In addition to the cost of managing the complexity of the design itself, verification and validation are also becoming increasingly expensive. Finally, the integration and software development costs also have to be taken into account.

These costs have to be recuperated via income earned by selling chips. However, the price per unit cannot be raised due to strong competition and pressure from customers. As a result, the development costs can only be recovered by selling large quantities of these complex ASICs. ASICs are by definition, however, application-specific and are often tuned to the requirements of a few big customers. Therefore, they cannot be used "as is" for multiple applications or customers. This leads to a deadlock: the market for these chips may not be large enough to amortize the NRE costs. That is, of course, unless newer technologies help to drastically reduce these costs.

Fortunately, every cloud has a silver lining. As it happens, the multi-core roadmap is creating new opportunities for specialized accelerators. In the past, general-purpose processor speed increased exponentially, so an ASIC would quickly lose its performance advantage. Recently, however, this processor trend has considerably slowed down. As a result, the performance benefits offered by ASICs can now be amortized over a longer period of time [Pfister2007].

#### Worst-case design for ASICs leads to bankruptcy

Current chips for consumer applications are designed to function even in the worst-case scenario: at the lowest voltage, the worst process technology corner and the highest temperature. Chip binning, i.e., sorting chips after fabrication according to capabilities, is usually not performed because the testing costs outweigh the income from selling the chips. Microprocessors are an exception to this rule, as the selling price of these chips is so high that the binning cost is relatively low. Nevertheless, even for microprocessors chip binning is only applied for a few parameters, such as stable clock frequency, and not yet for others, such as correctly functioning cache size.

The practical upshot is that most consumer chips are overdimensioned. In most realistic cases typical use is far from the worst case, and this gap is even widening with the use of very dense technologies at 45 nm and below, because of process variability. The increasing complexity of SoCs is also a factor that widens the gap due to the composition of margins. If the architecture and design methodologies do not change, we will eventually end up with such large overheads that it will become economically infeasible to produce any more chips.

New design methodologies and architectures will be required to cope with this problem. For example, the "Razor" concept [Ernst2004, Blaauw2008] is one solution. In this case errors are allowed to occur from time to time when typical conditions are not met, but they are detected and subsequently corrected. Alternative methods are using active feedback and quality of service assessments in the SoC. One very important issue is that most of the techniques currently under development decrease the system's predictability, and thereby also any hard real-time characteristics it may have had.

## Systems will rely on unreliable components

The extremely small feature sizes mean that transistors and wires are no longer going to behave in the way we are used to. Projections for transistor characteristics in future fabrication processes indicate that scaling will lead to dramatically reduced transistor and wire reliability. Radiation-induced soft errors in latches and SRAMs, gate-oxide wear-out and electromigration with smaller feature sizes, device performance variability due to limitations in lithography, and voltage and temperature fluctuation are all likely to affect future scaling.

An important consequence is that the variability of different parameters such as speed and leakage is quite high and changing over time. Sporadic errors, a.k.a. soft errors and aging problems, are consequently becoming so common that new techniques need to be developed to handle them. This development has only just started; in the near future, reliable systems will have to be designed using unreliable components [Borkar2005].

For Europe, this evolution is an opportunity since it can apply its extensive knowledge of high-availability systems in the commodity market.

#### Time is relevant